LDMOS device with multilayer super-junction structure

A device and active region technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as device damage, reduced breakdown resistance, and uneven distribution of impurities in the column area, so as to improve the contact area, The effect of high resistance to breakdown

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be further described below in conjunction with the accompanying drawings, which are not drawn to scale for the convenience of illustration.

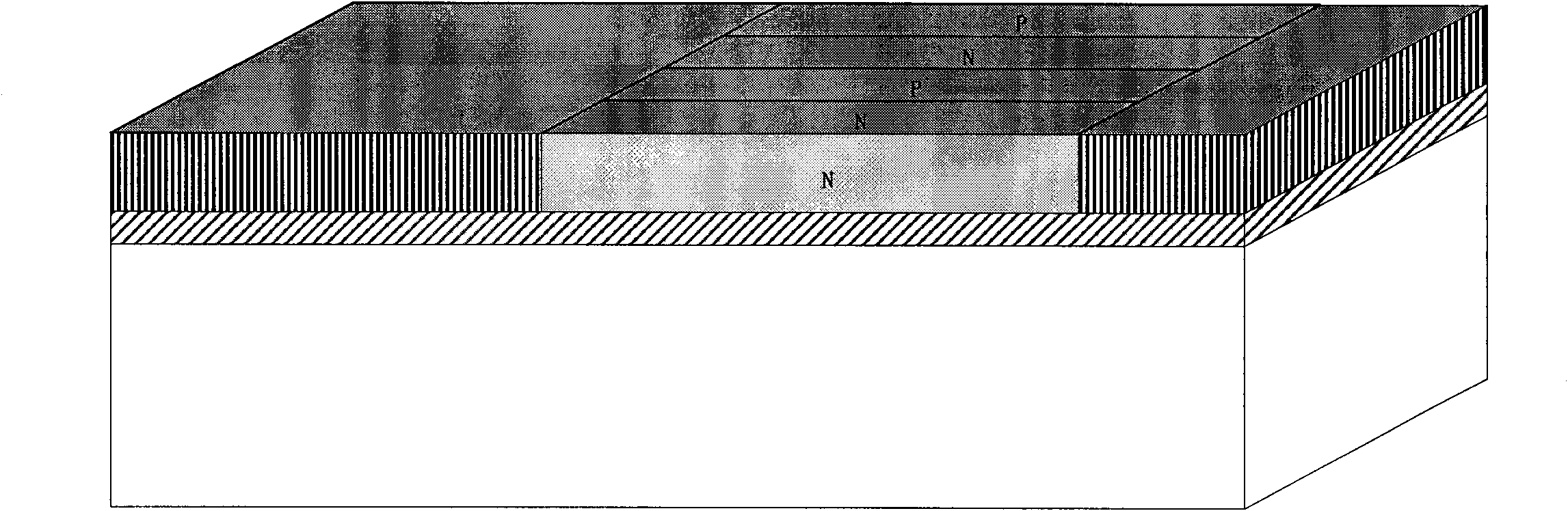

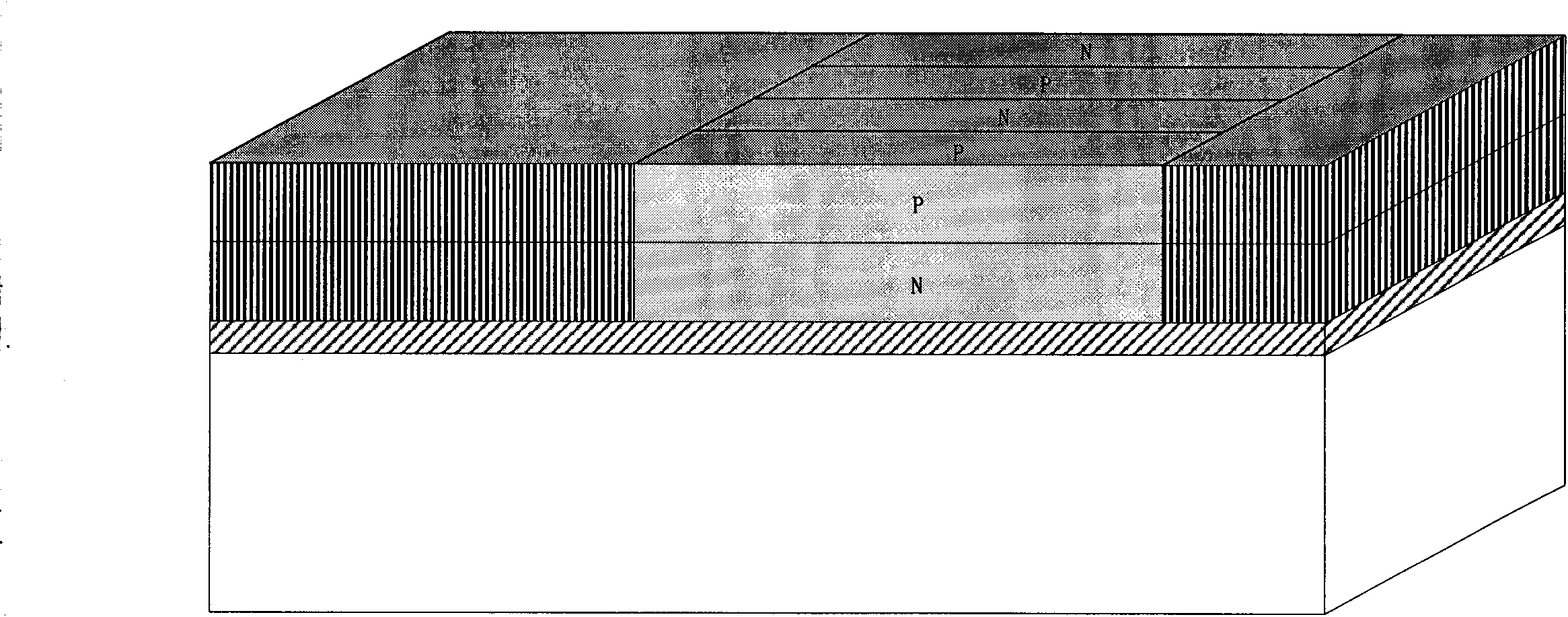

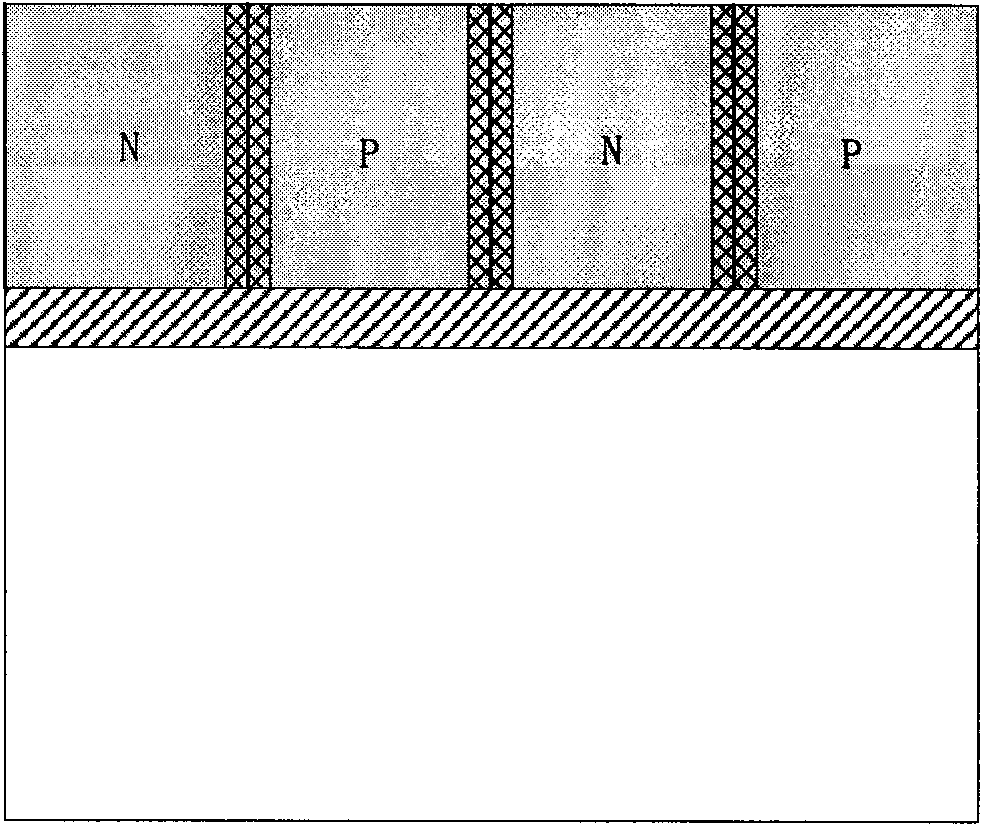

[0039] Such as Figure 5 As shown, an LDMOS device with a multilayer superjunction structure includes a substrate and an active region on the substrate, and its active region includes: a gate region, a source region 11 and a drain region on both sides of the gate region 16. A body region 12 located under the gate region, a multilayer super junction structure located between the body region 12 and the drain region 16; the multilayer super junction structure includes at least two layers of super junction structures ( Including the first layer of super junction structure 14 and the second layer of super junction structure 15), each layer of super junction structure is composed of n-type pillar regions 5 and p-type pillar regions 4 alternately arranged laterally, which can share the breakdown voltage. Where...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More