SOI LDMOS device with interface N<+> layer

A semiconductor and interface technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of low withstand voltage and low withstand voltage, improve the vertical withstand voltage, improve the withstand voltage, ease the breakdown voltage and on-resistance The conflicting effect between

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings; it should be understood that the preferred embodiments are only for illustrating the present invention, rather than limiting the protection scope of the present invention.

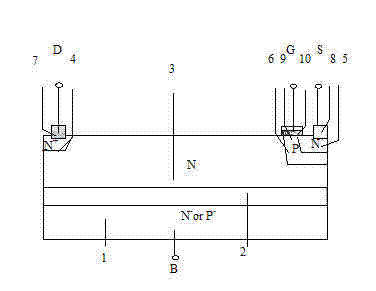

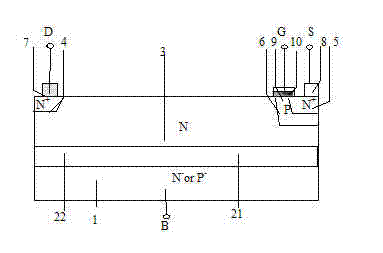

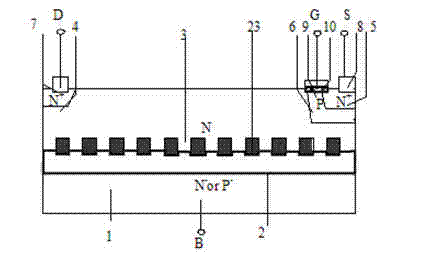

[0031] Figure 7 with interface N + layer SOI LDMOS semiconductor device structure, as shown in the figure: the invention provides a + Layered SOI LDMOS semiconductor devices, including a substrate silicon layer, a dielectric buried layer and an active top layer silicon, the dielectric buried layer is arranged between the substrate silicon layer and the active top layer silicon, and the active top layer silicon includes N-type Silicon layer, P-type silicon layer and N + silicon layer, the N + The silicon layer is disposed on the dielectric buried layer, and the P-type silicon layer is disposed on the N + Above the silicon layer, the N-type silicon layer is disposed ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More