Multi-gate SOI-LDMOS device structure

A device structure and gate structure technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of transconductance characteristics, forward conduction resistance, self-heating effect, poor radiation resistance, etc., and achieve improved radiation resistance, The effects of small forward conduction resistance and high radiation resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

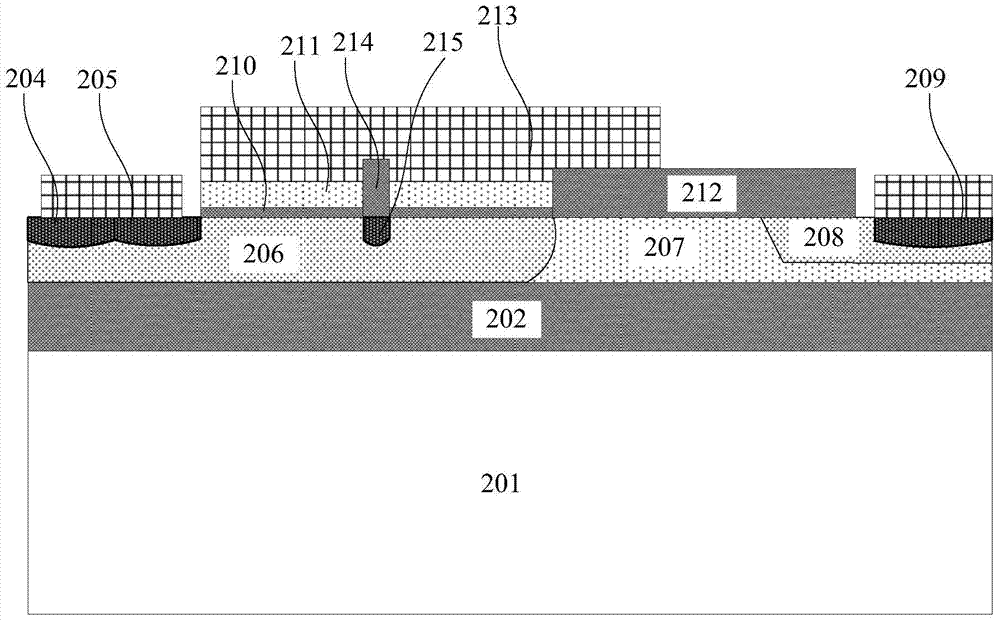

[0048] Such as figure 2 As shown, this embodiment provides a multi-gate SOI-LDMOS device structure, including at least:

[0049] SOI substrate, including silicon substrate 201, buried oxide layer 202 and top silicon layer;

[0050] Active regions 204 and 205 are formed in the top silicon layer, including source regions 204 and 205, channel regions 206, drift regions 207, lightly doped drain regions 208, and drain regions 209 connected in sequence;

[0051] A polysilicon gate, including a gate oxide layer 210 and a polysilicon layer 211 bonded to the surface of the channel region 206, the polysilicon gate is separated into at least two short gate structures by at least one dielectric layer 214, and corresponds to the bottom of the dielectric layer 214 A heavily doped region 215 of an opposite doping type to that of the channel region 206 is formed in the channel region 206 .

[0052] The source regions 204 and 205, as an example, include that the source regions 204 and 205 i...

Embodiment 2

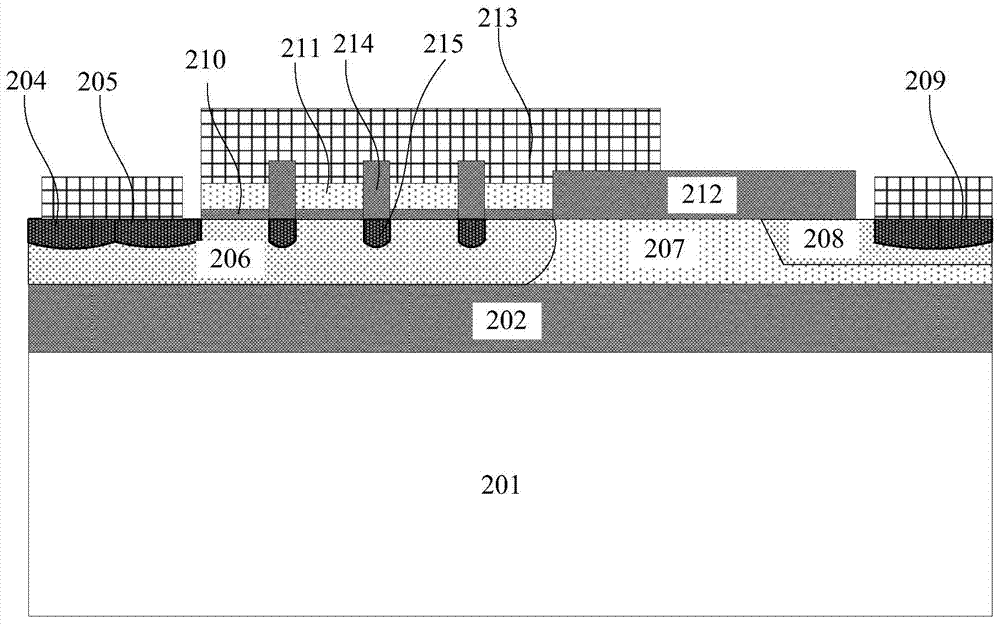

[0061] Such as image 3 As shown, this embodiment provides a multi-gate SOI-LDMOS device structure, including at least:

[0062] SOI substrate, including silicon substrate 201, buried oxide layer 202 and top silicon layer;

[0063] Active regions 204 and 205 are formed in the top silicon layer, including source regions 204 and 205, channel regions 206, drift regions 207, lightly doped drain regions 208, and drain regions 209 connected in sequence;

[0064] A polysilicon gate, including a gate oxide layer 210 and a polysilicon layer 211 bonded to the surface of the channel region 206, the polysilicon gate is separated into at least two short gate structures by at least one dielectric layer 214, and corresponds to the bottom of the dielectric layer 214 A heavily doped region 215 of an opposite doping type to that of the channel region 206 is formed in the channel region 206 .

[0065] The source regions 204 and 205, as an example, include that the source regions 204 and 205 in...

Embodiment 3

[0080] This embodiment provides a multi-gate SOI-LDMOS device structure, the basic structure of which is as in Embodiment 1, wherein the source region includes a heavily doped N-type region and a heavily doped P-type region, and the heavily doped P type region is connected to the channel region; the doping type of the channel region is N type, the doping type of the drift region, shallow doped drain and drain region is P type, and the heavily doped region The doping type is P-type.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More