Patents

Literature

268results about How to "Increase the on-resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

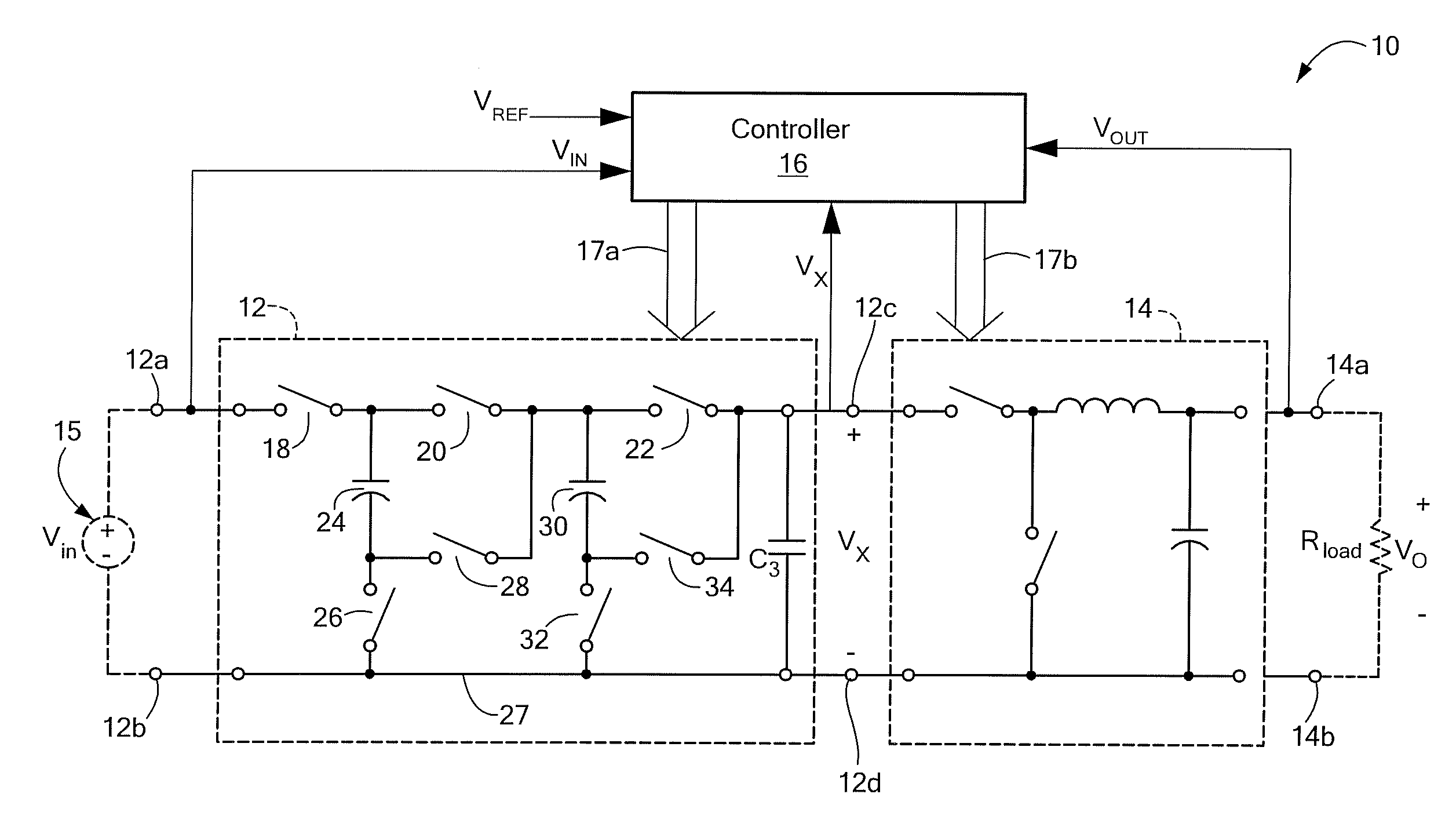

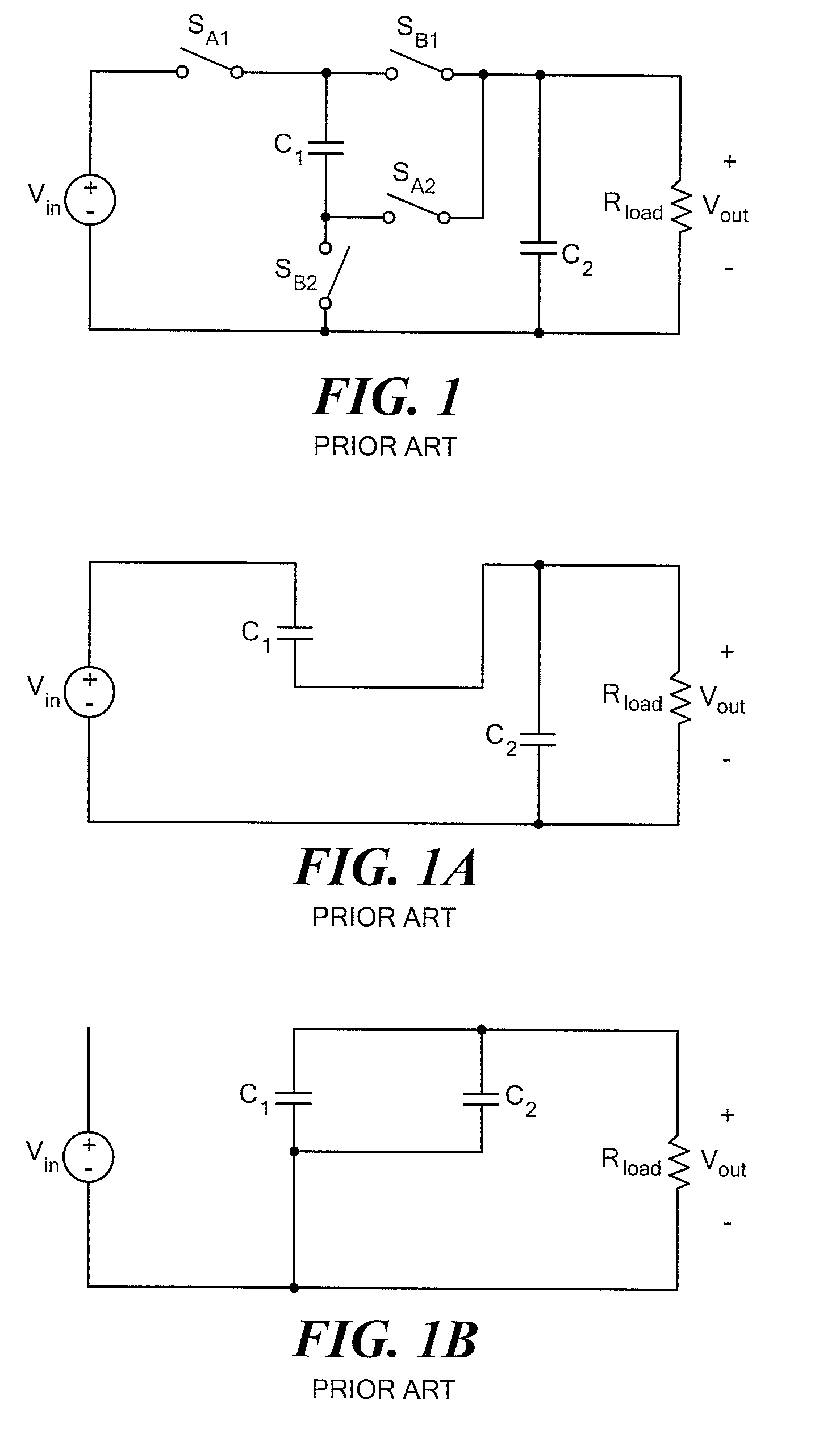

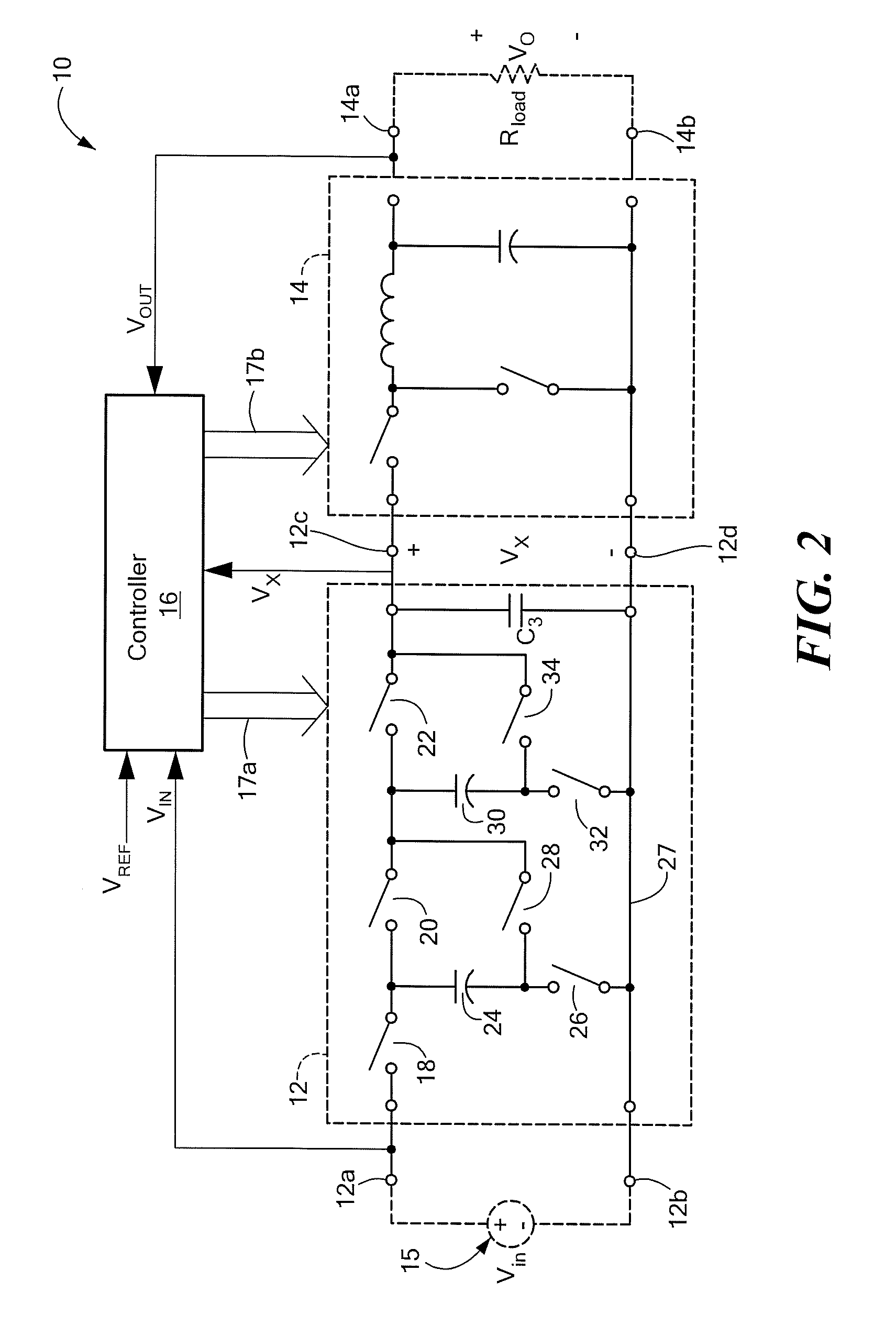

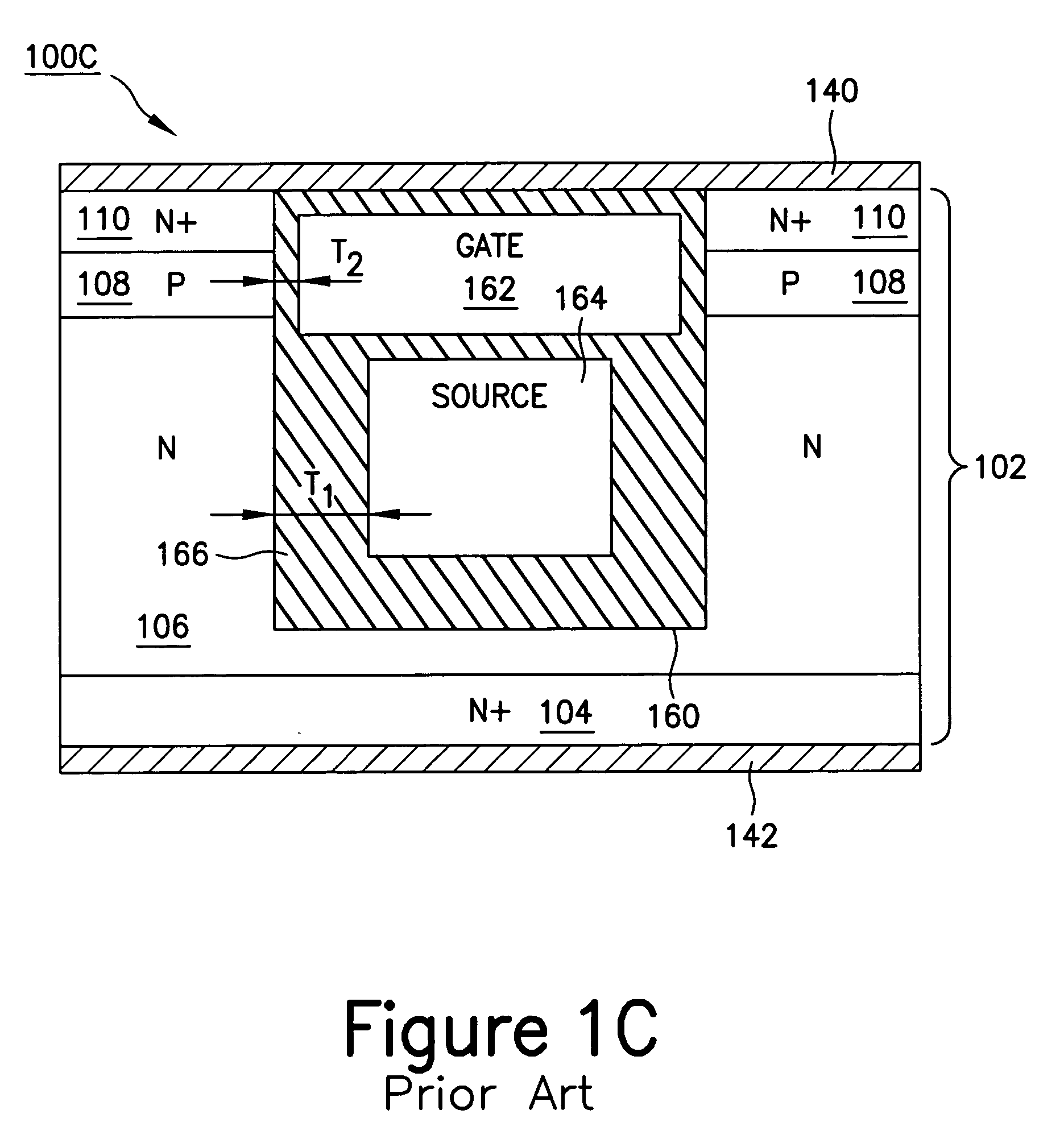

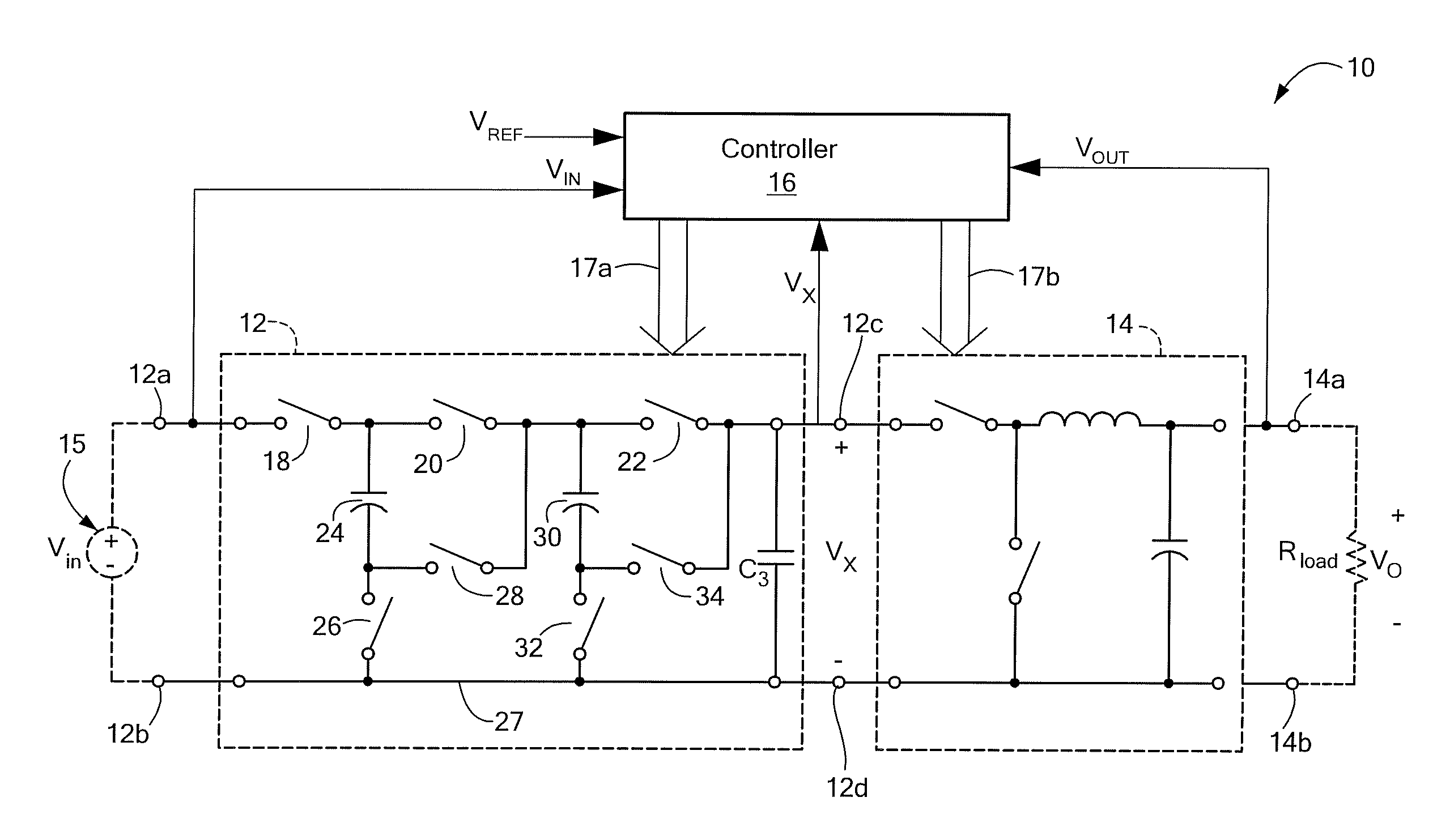

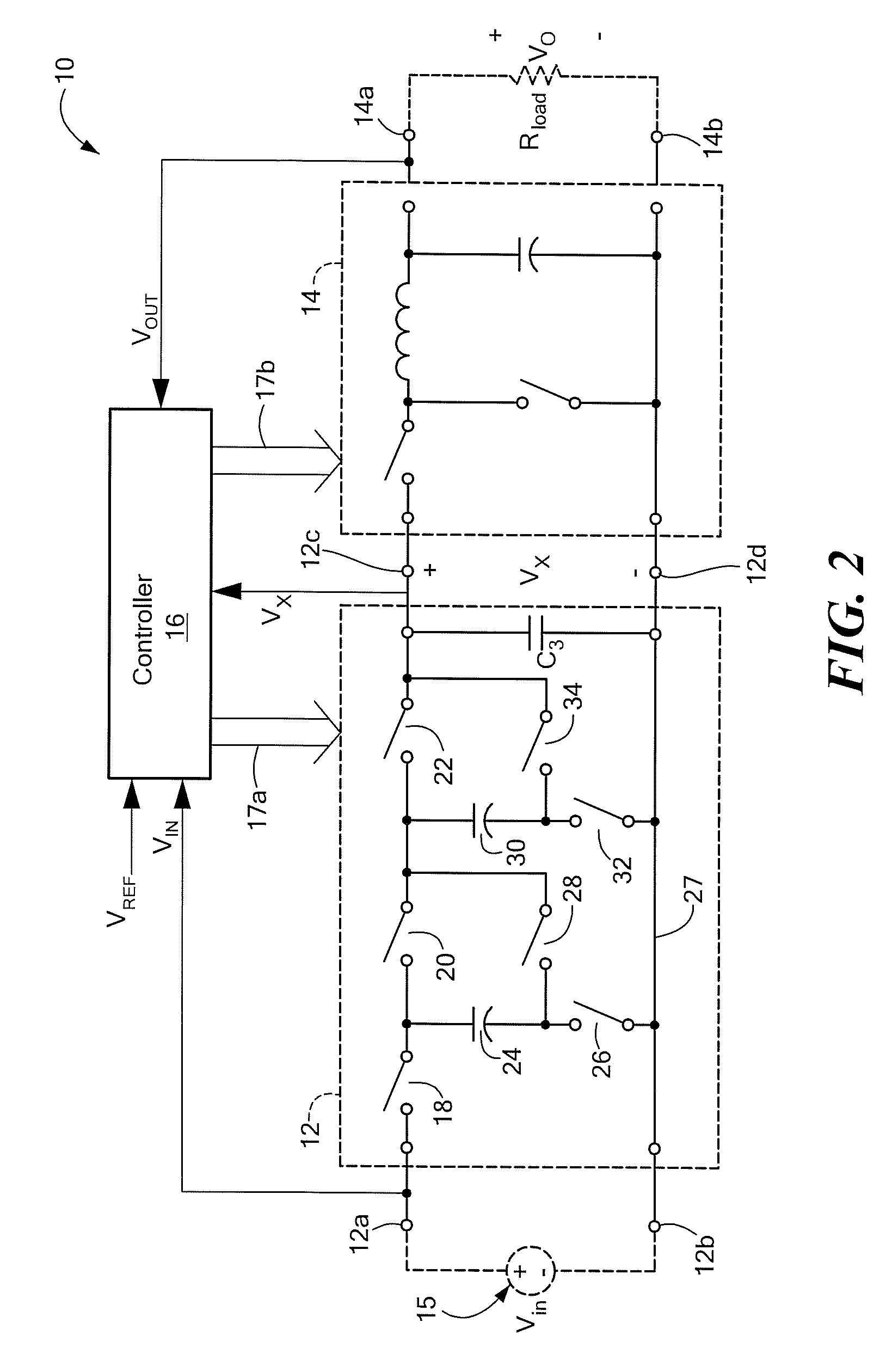

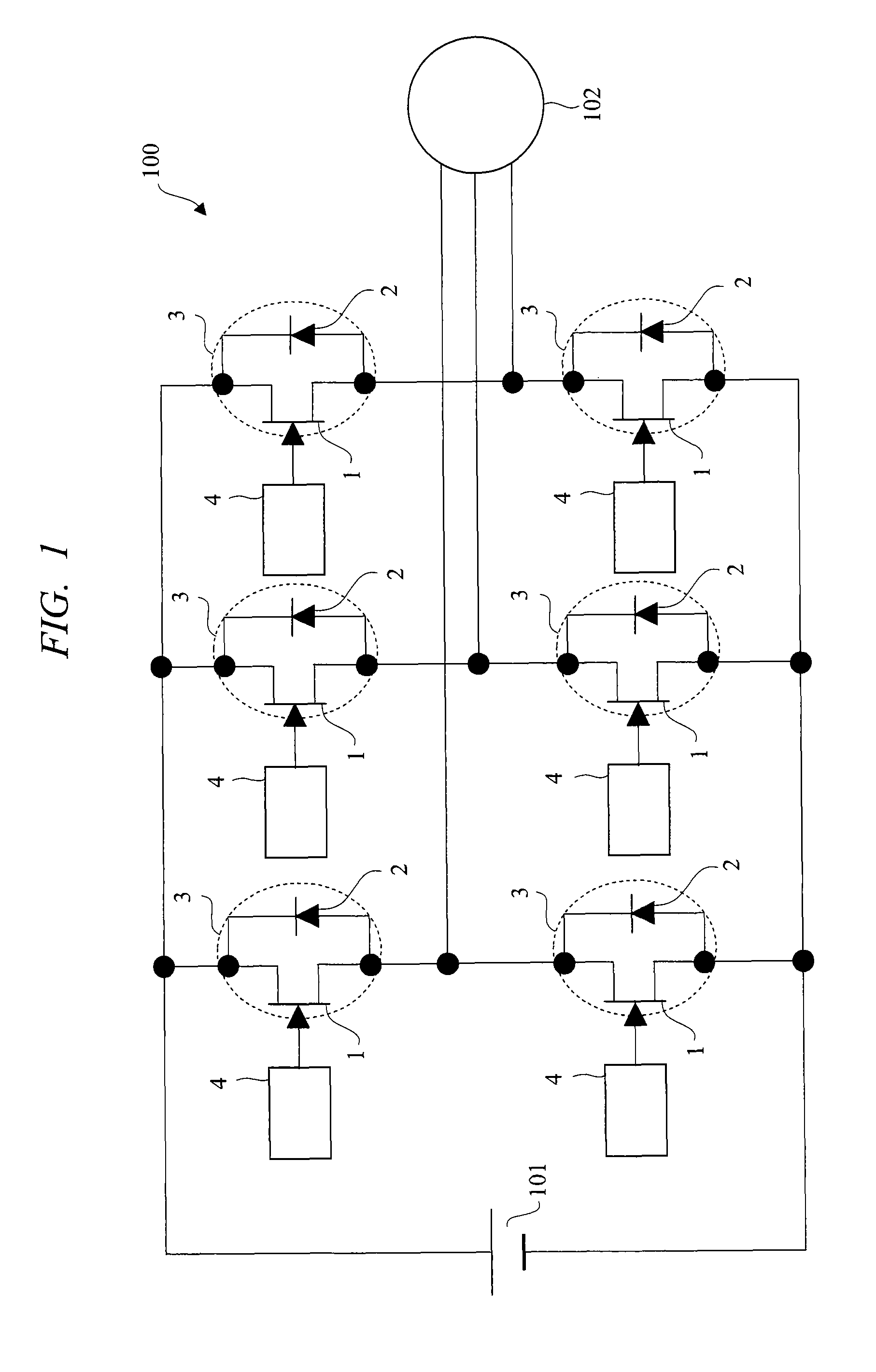

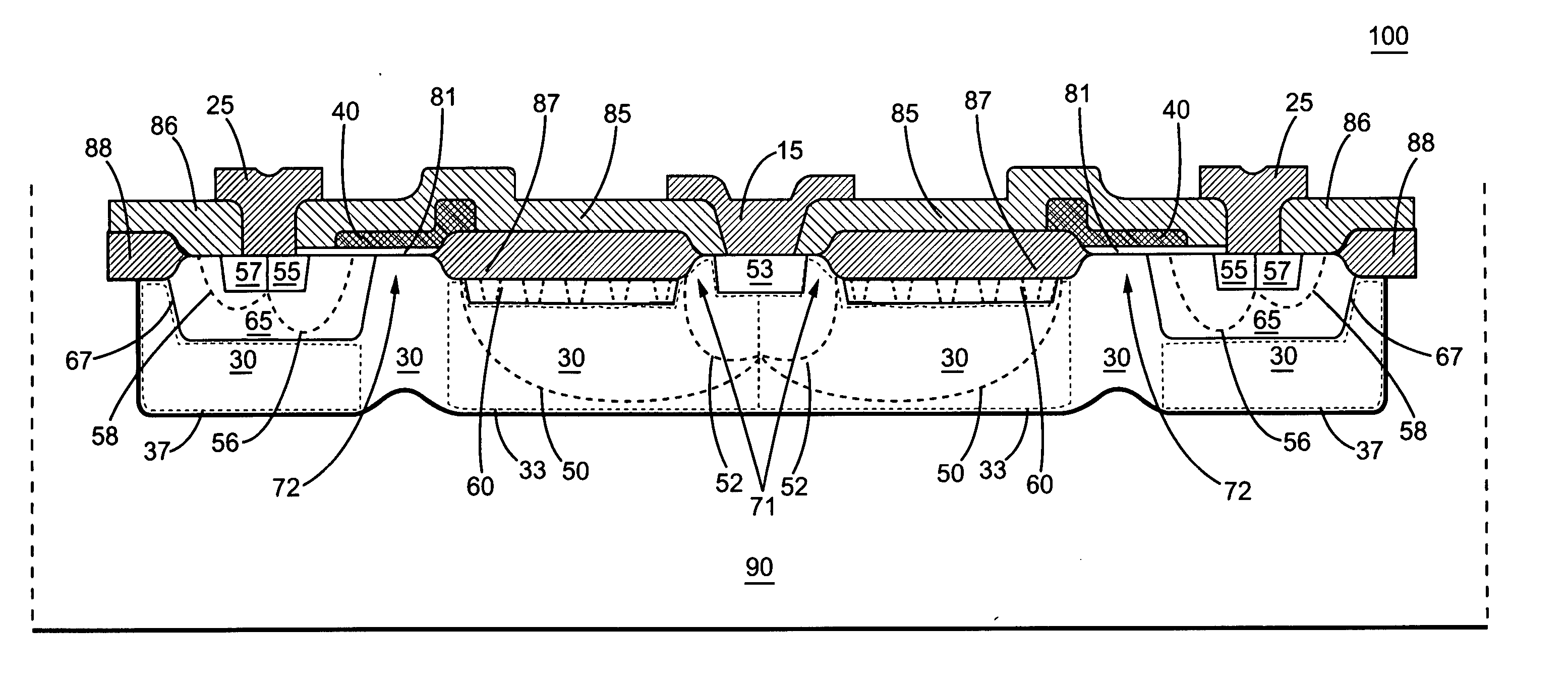

Power Converter with Capacitive Energy Transfer and Fast Dynamic Response

ActiveUS20090278520A1High power density power conversionImprove power densityEfficient power electronics conversionApparatus without intermediate ac conversionEnergy transferVoltage range

A converter circuit and related technique for providing high power density power conversion includes a reconfigurable switched capacitor transformation stage coupled to a magnetic converter (or regulation) stage. The circuits and techniques achieve high performance over a wide input voltage range or a wide output voltage range. The converter can be used, for example, to power logic devices in portable battery operated devices.

Owner:MASSACHUSETTS INST OF TECH

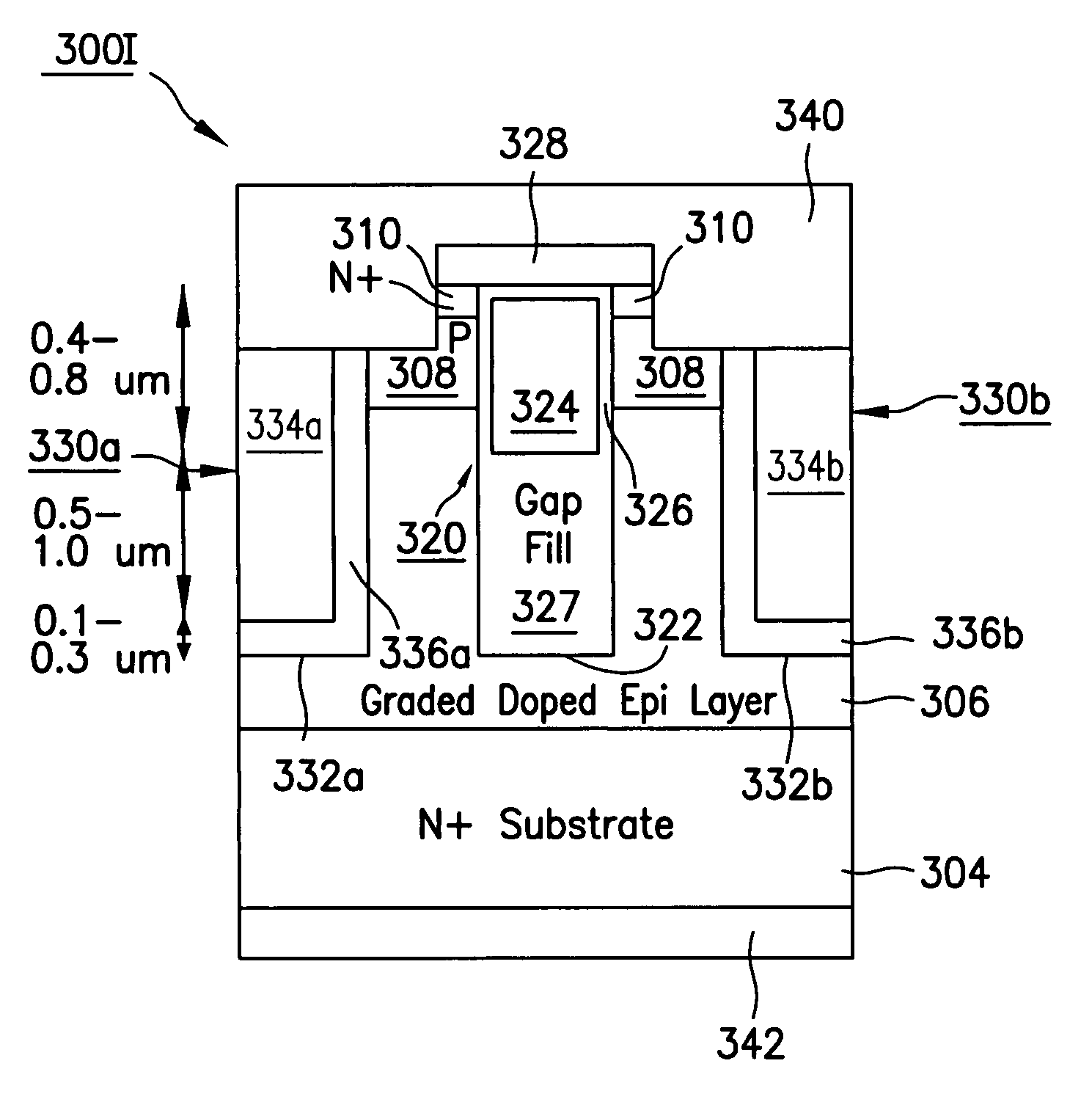

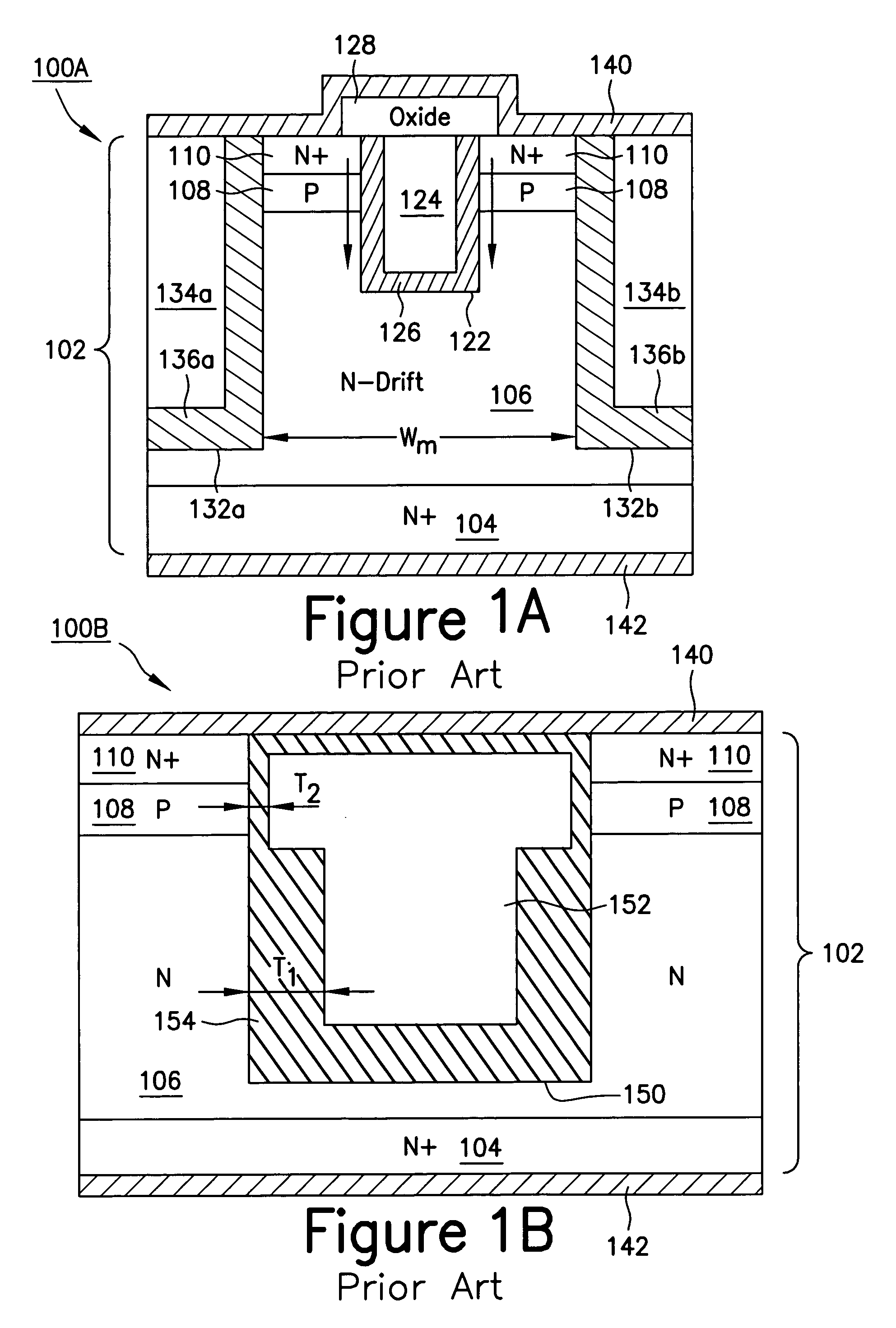

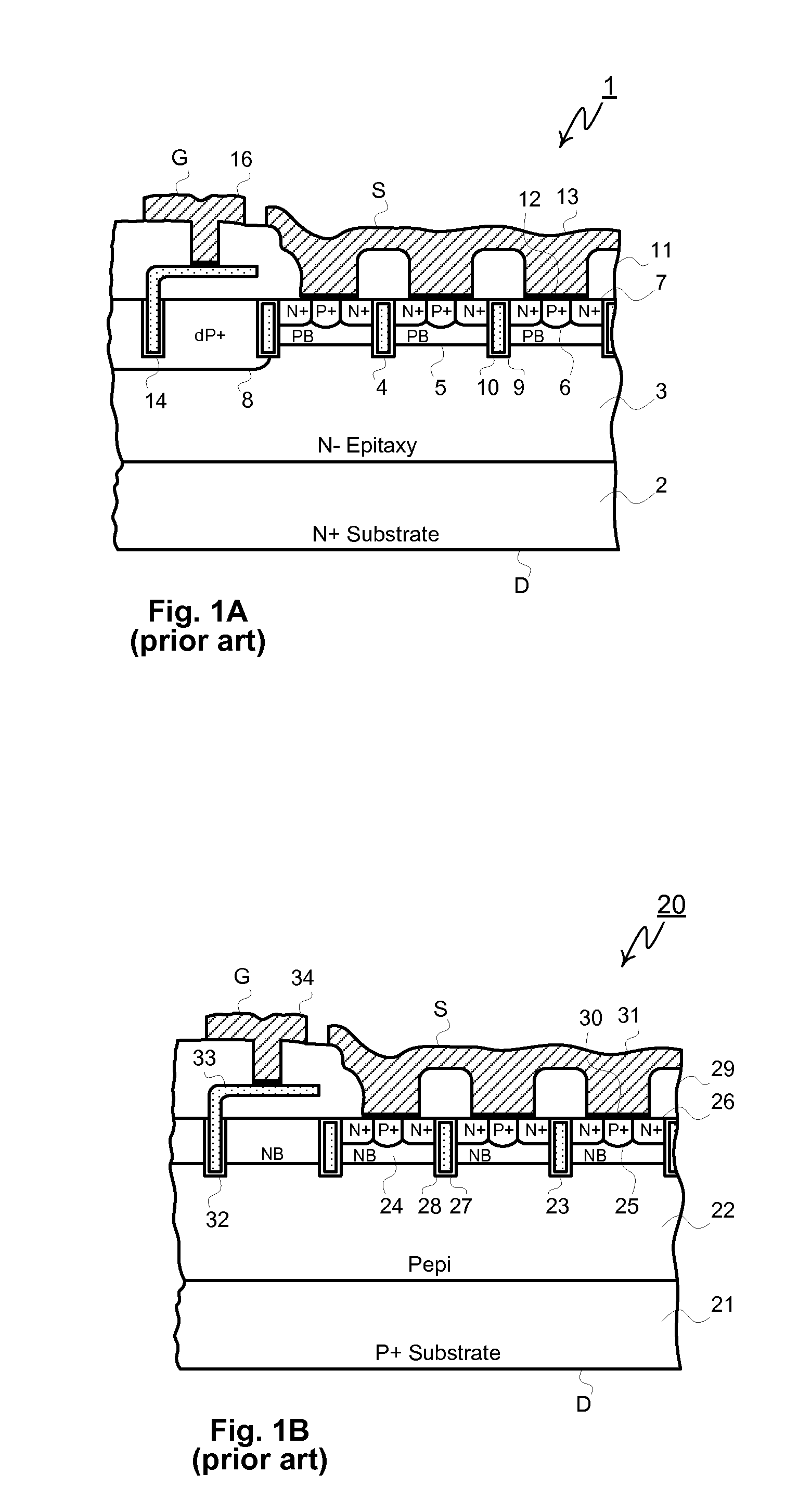

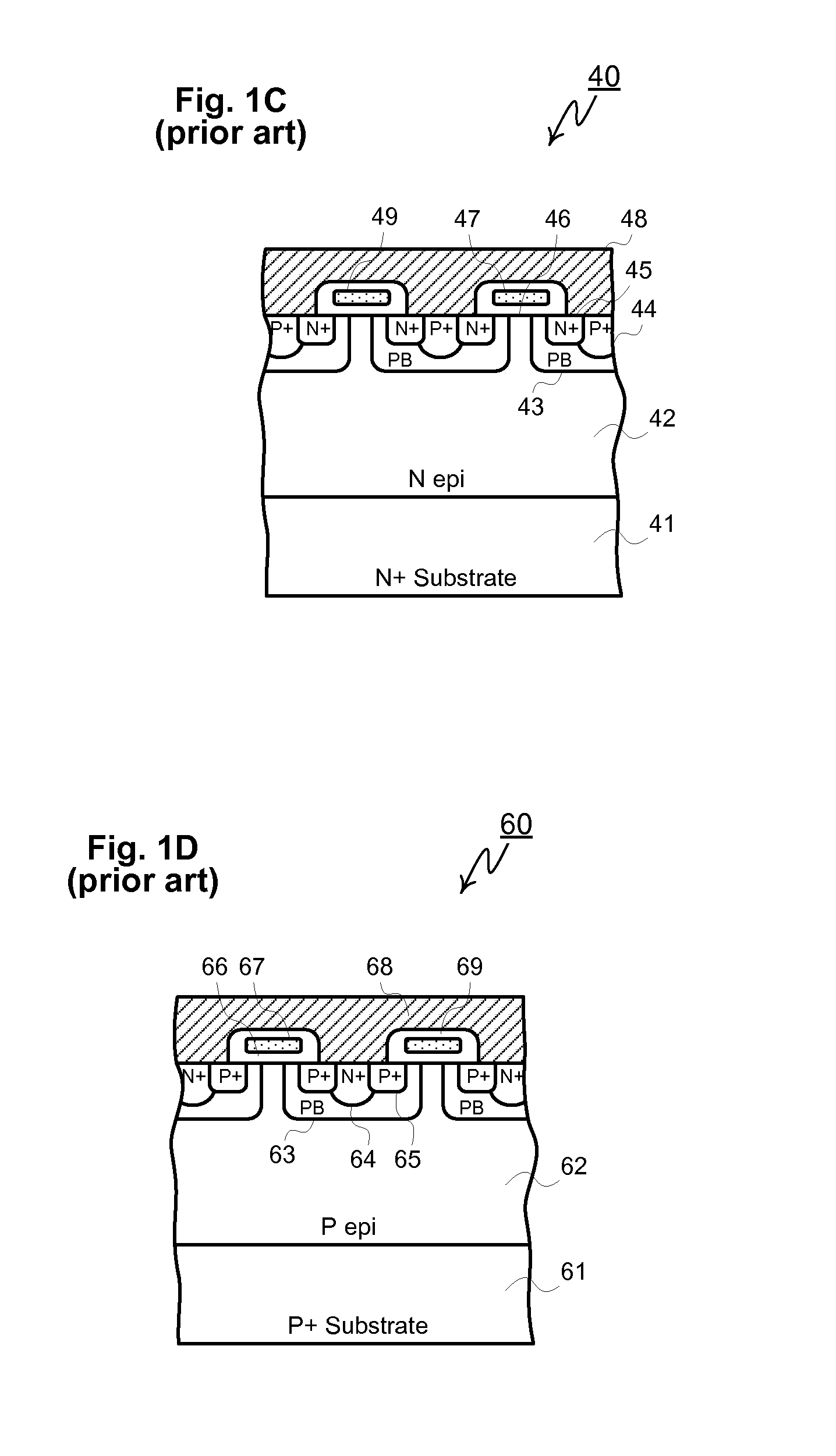

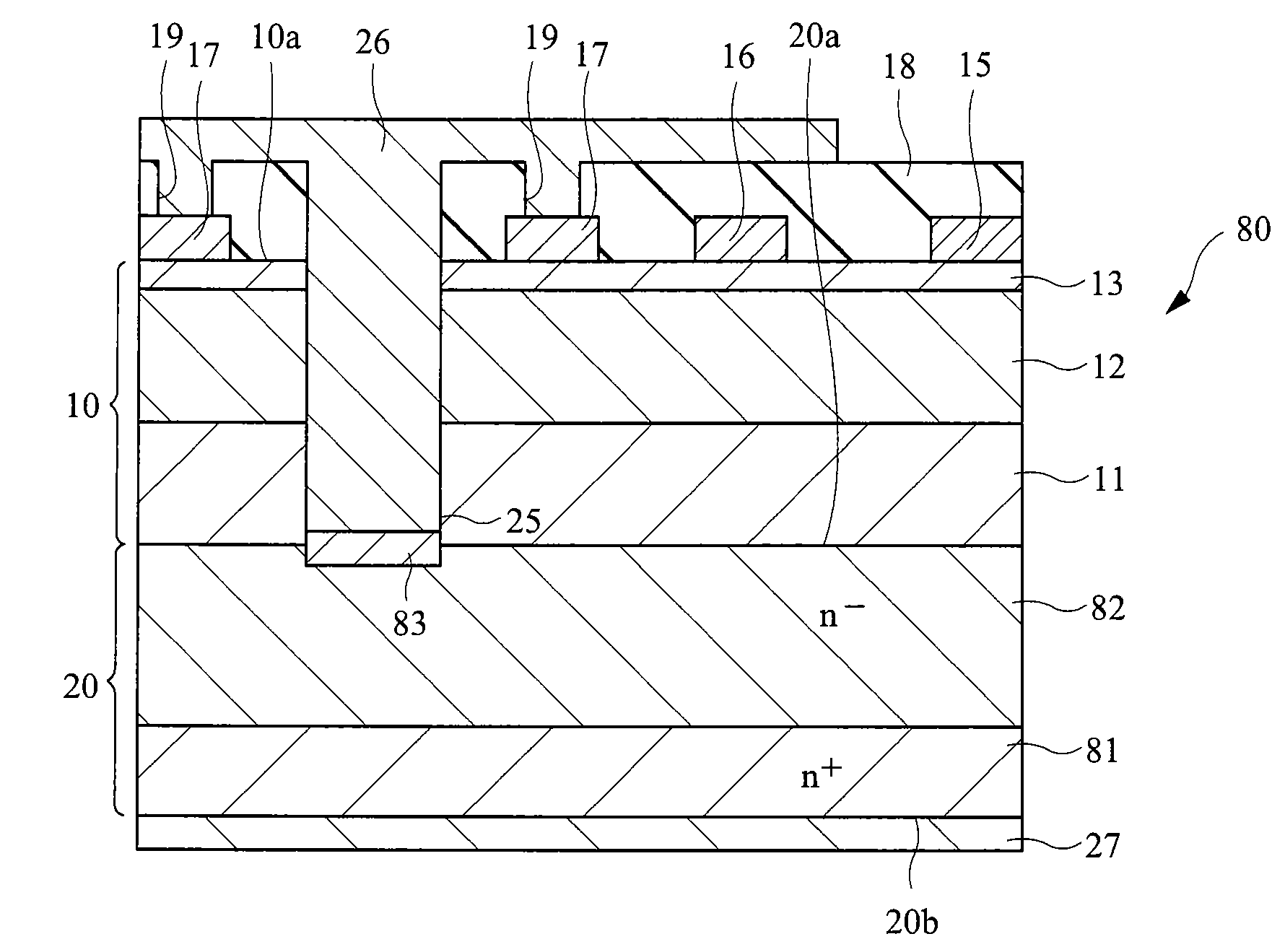

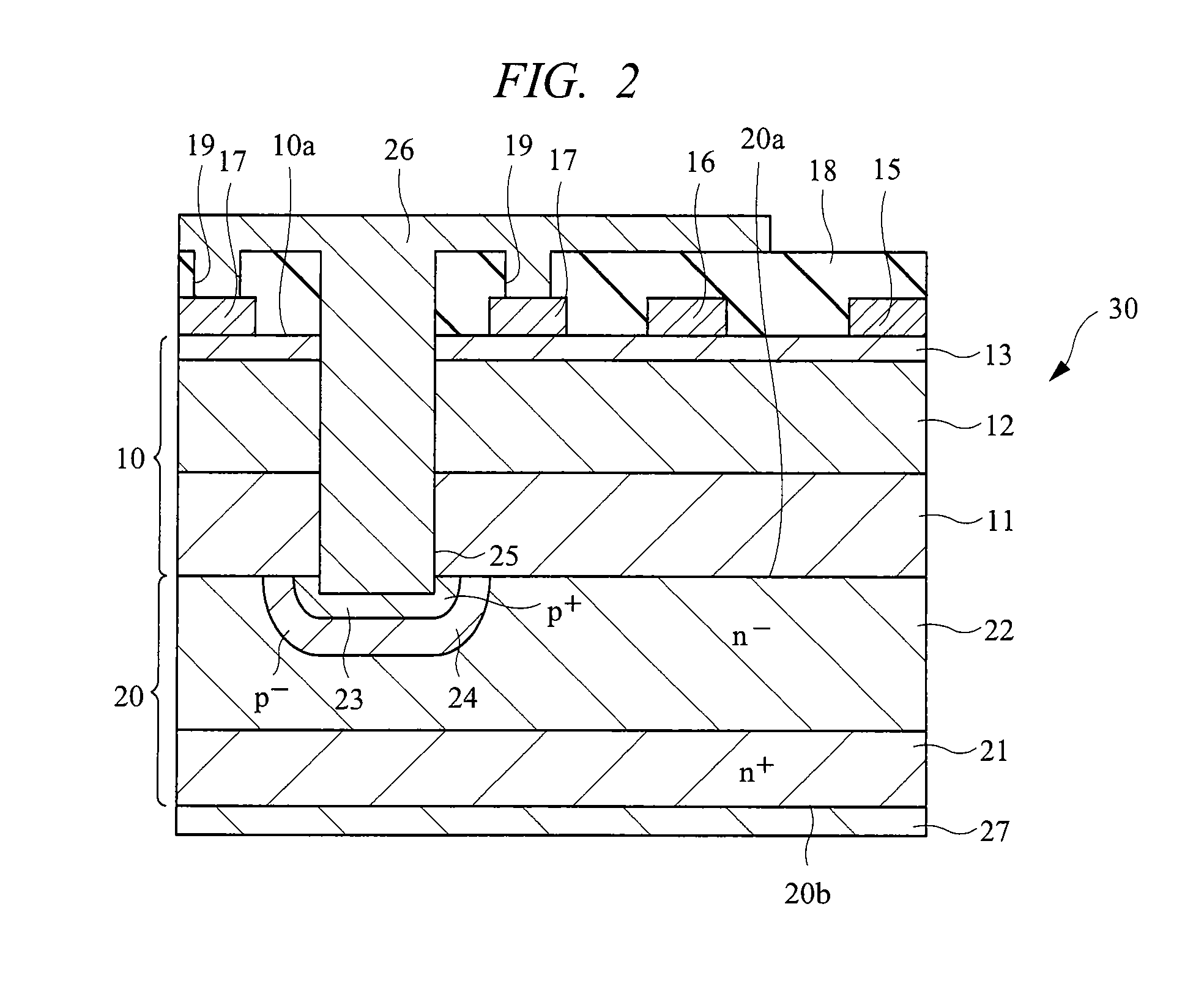

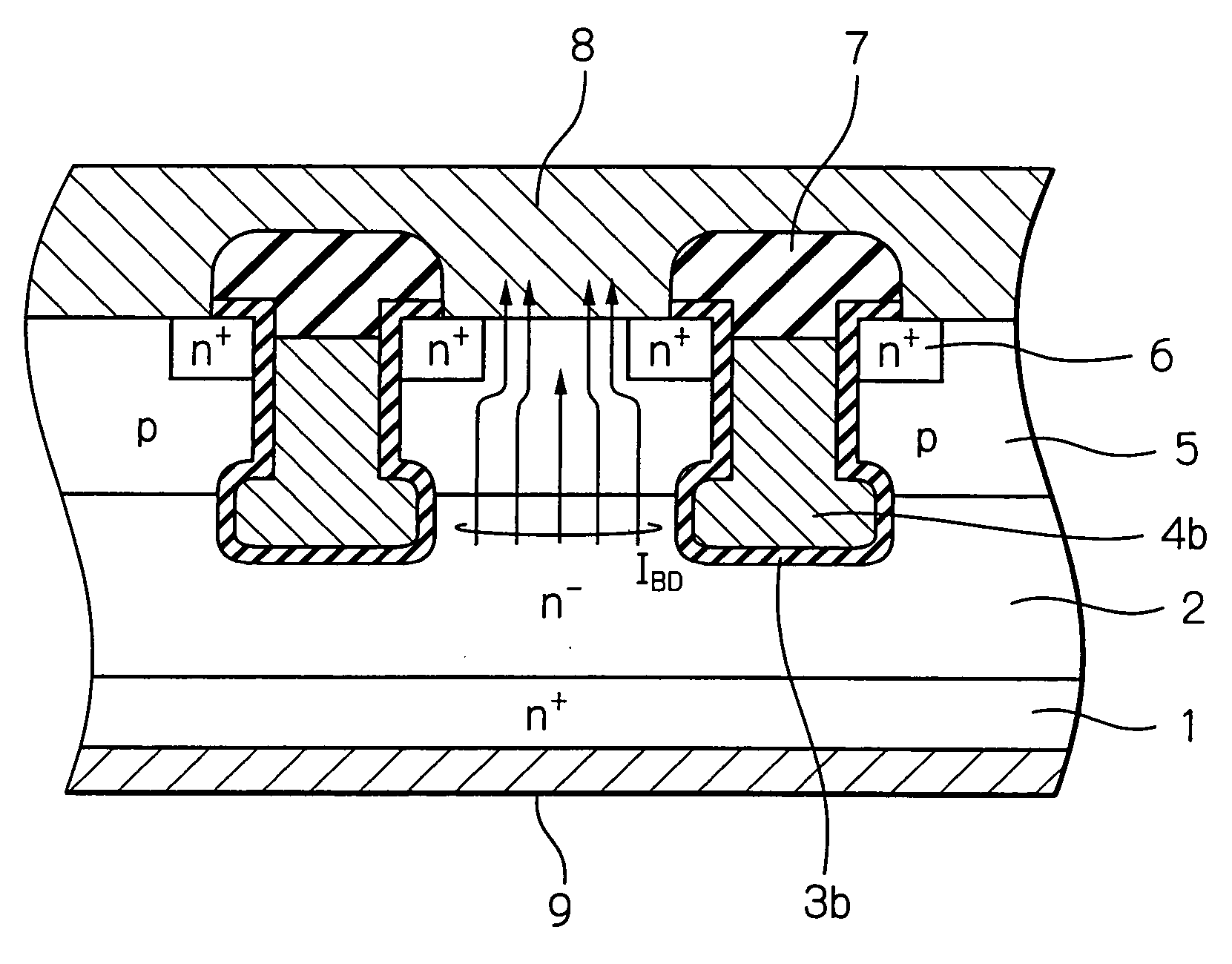

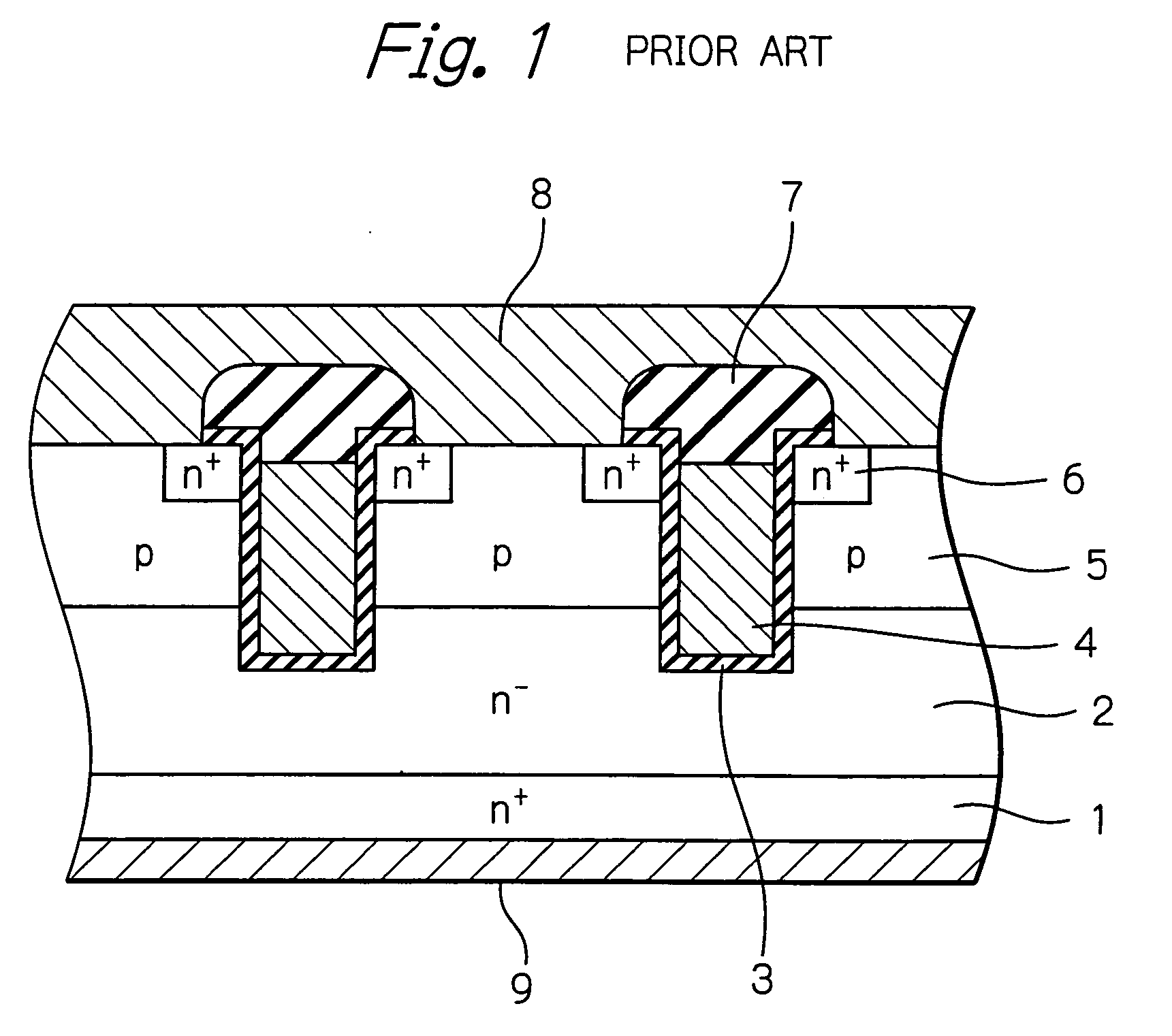

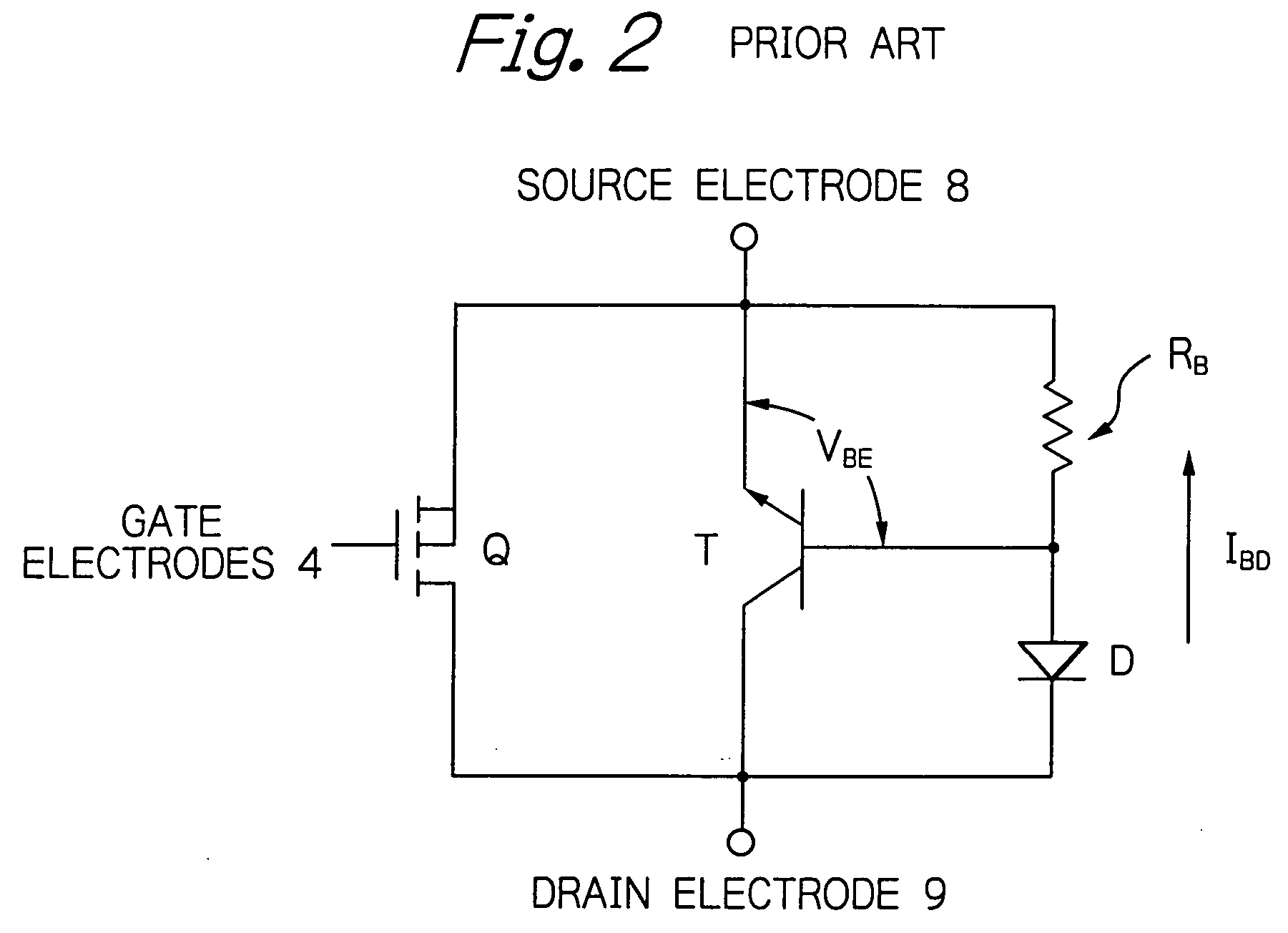

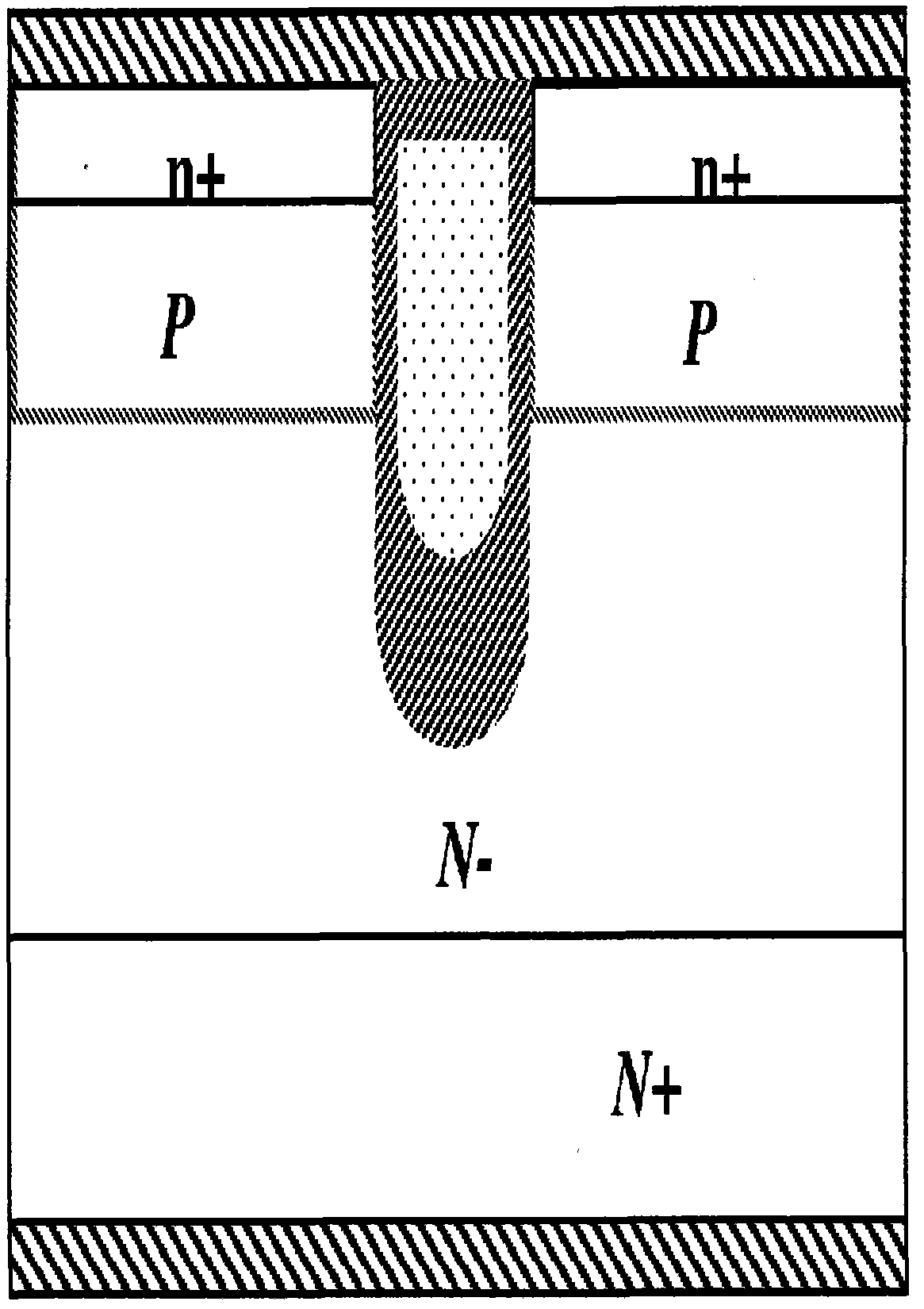

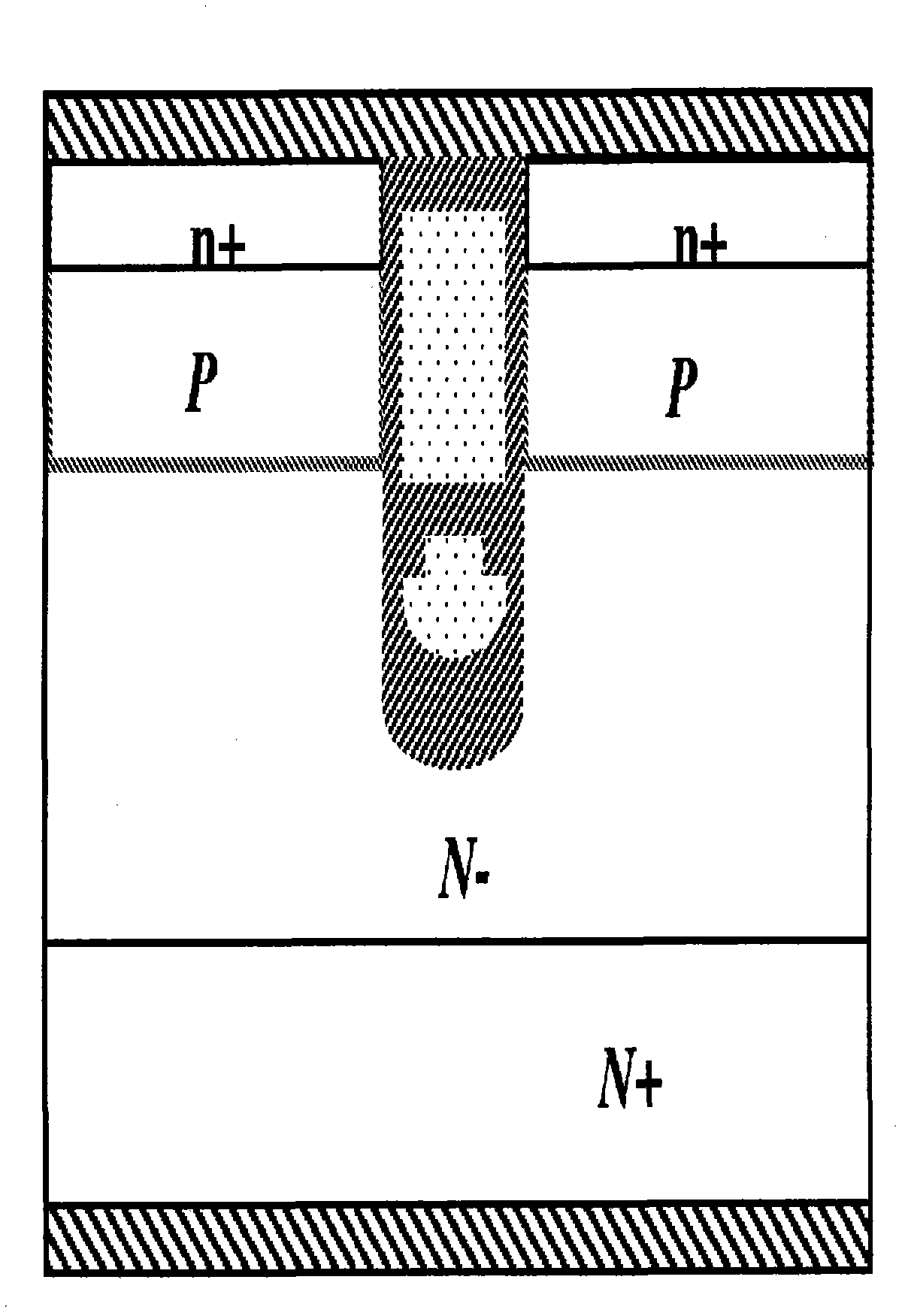

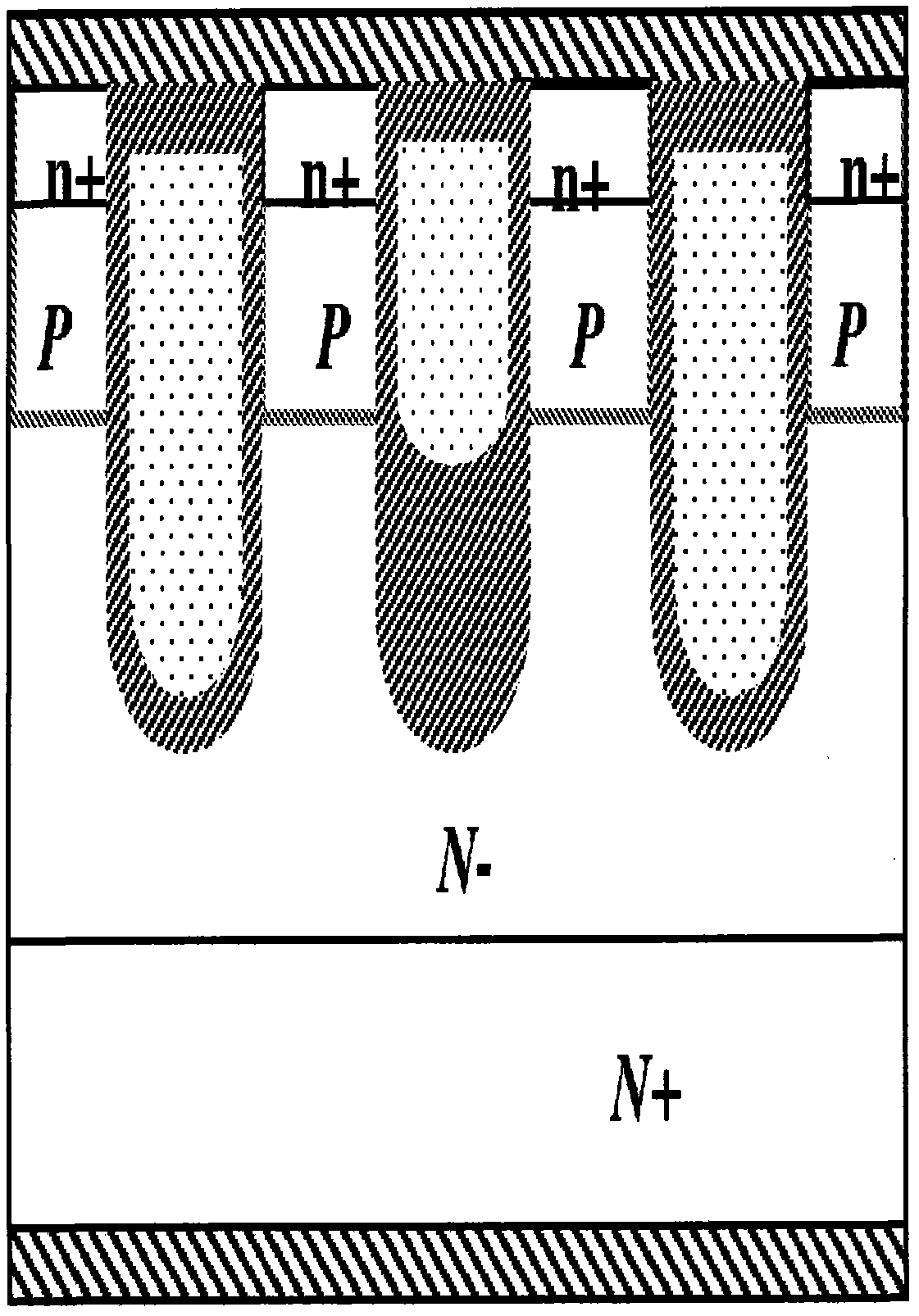

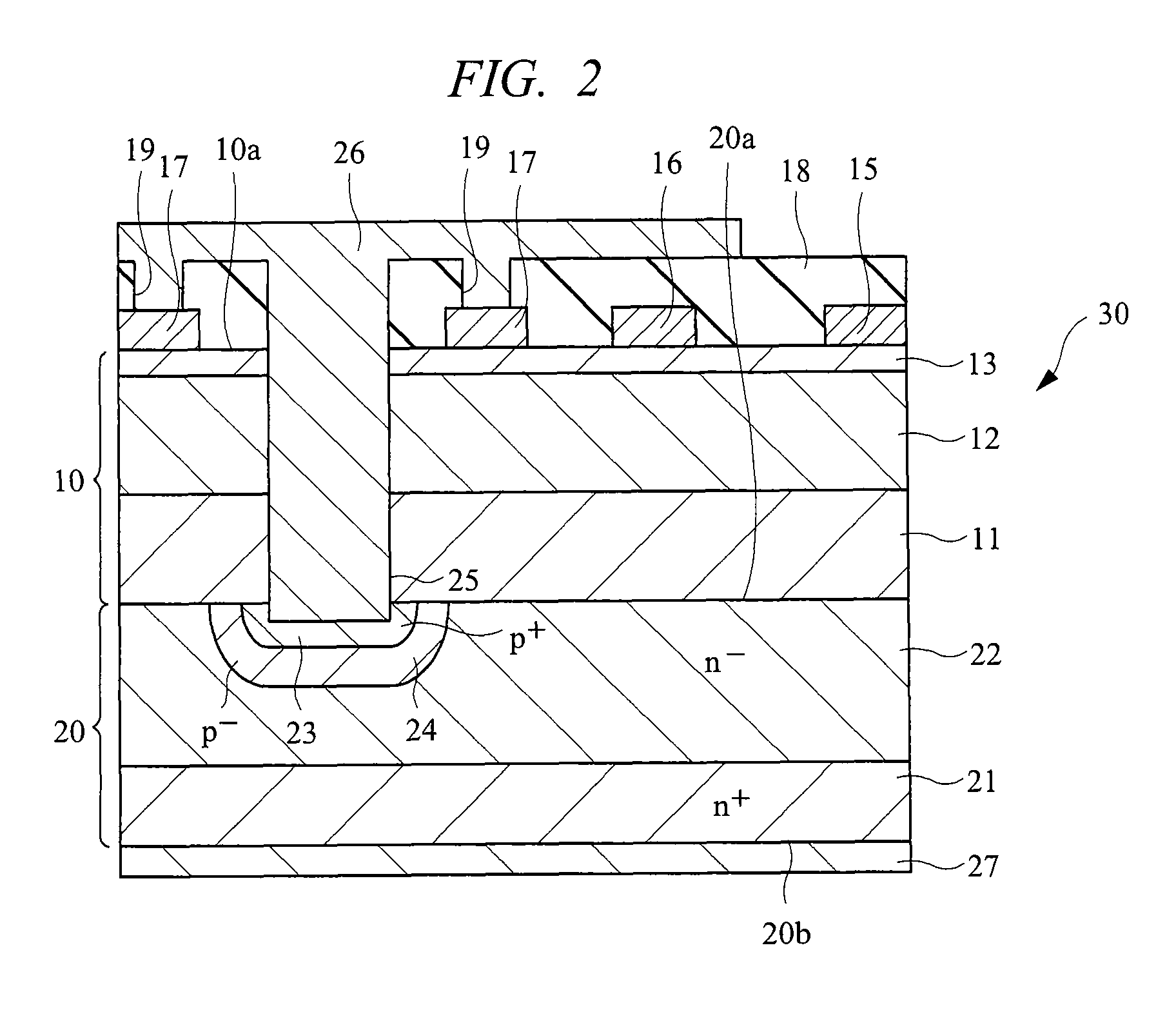

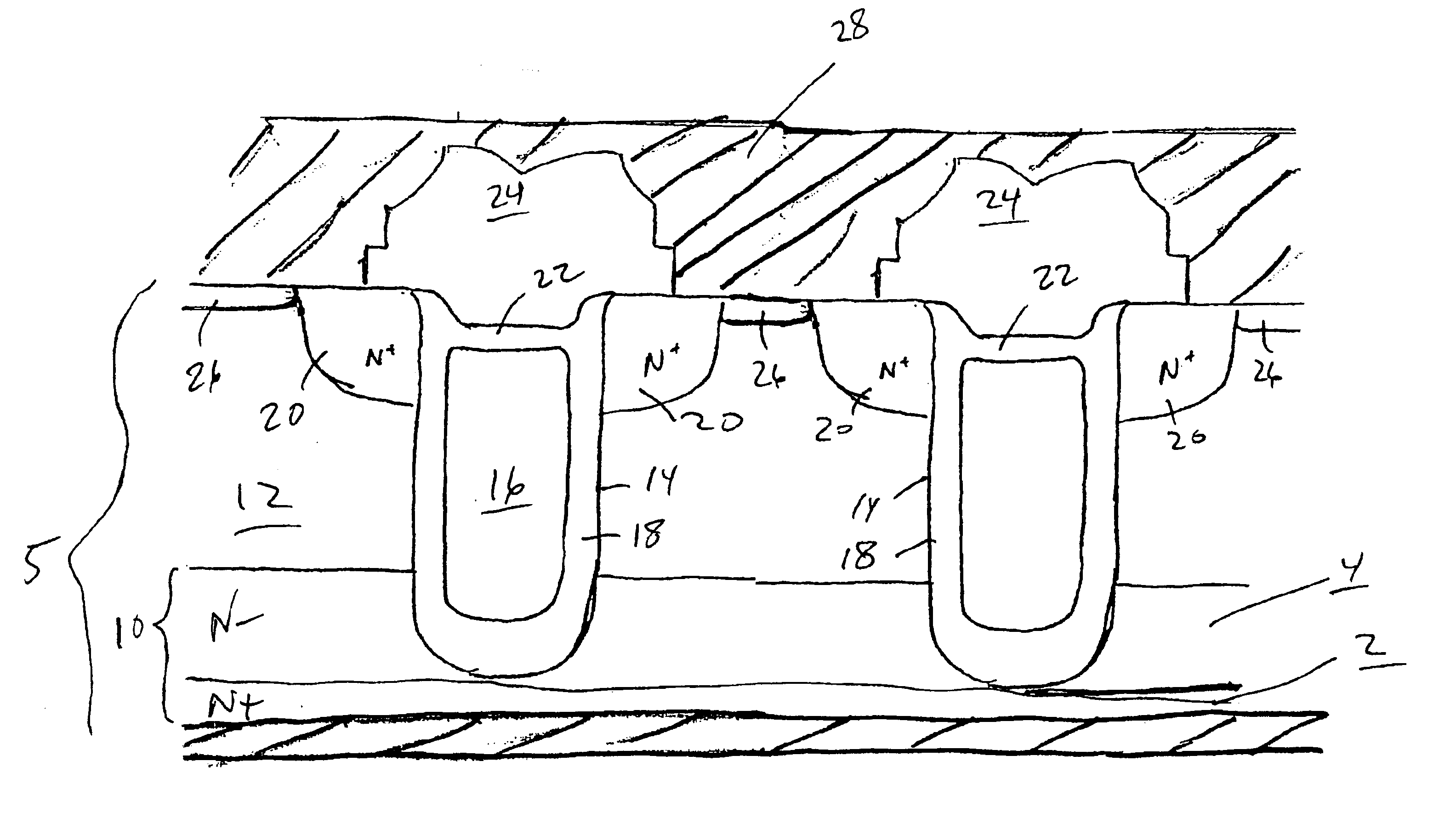

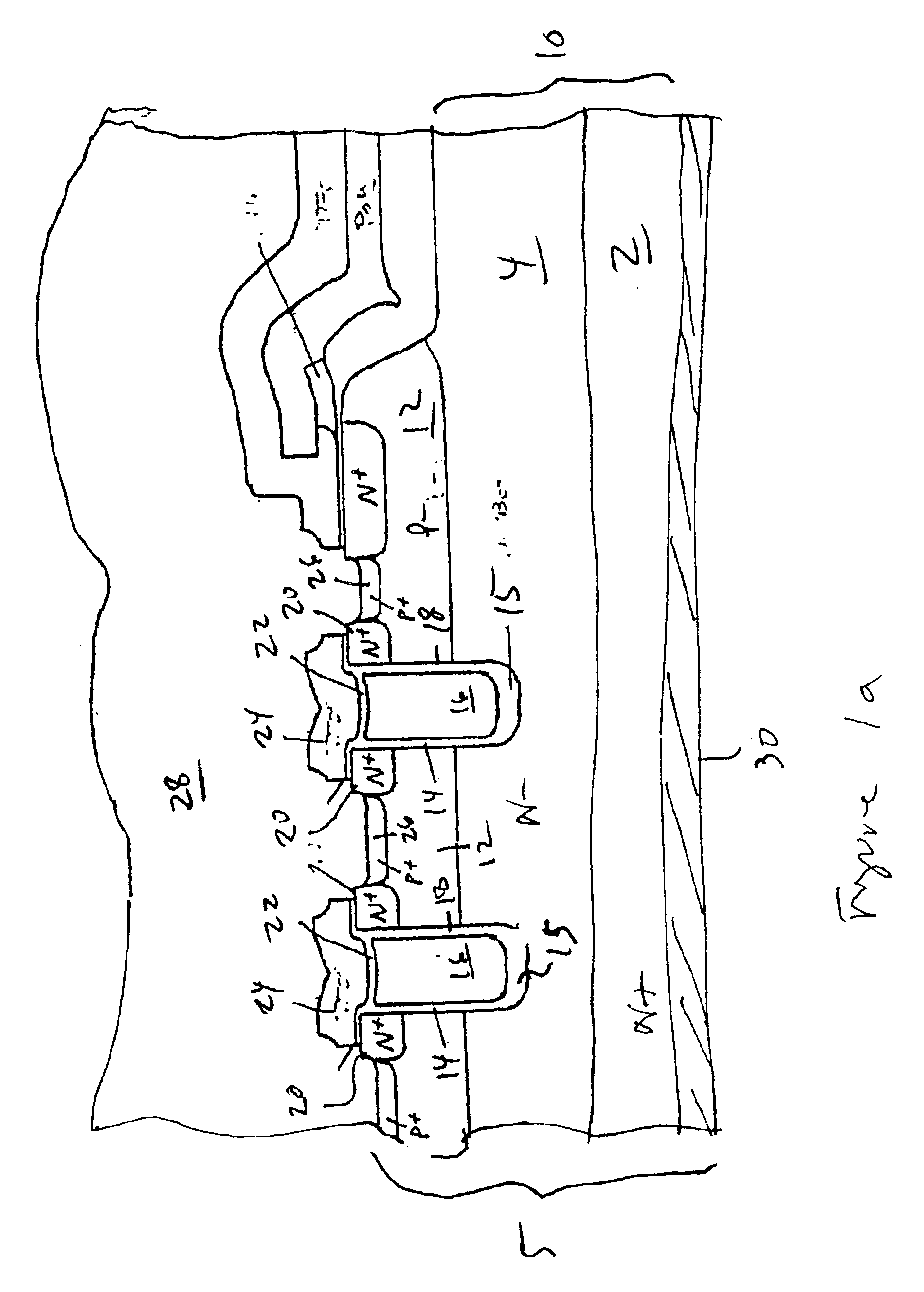

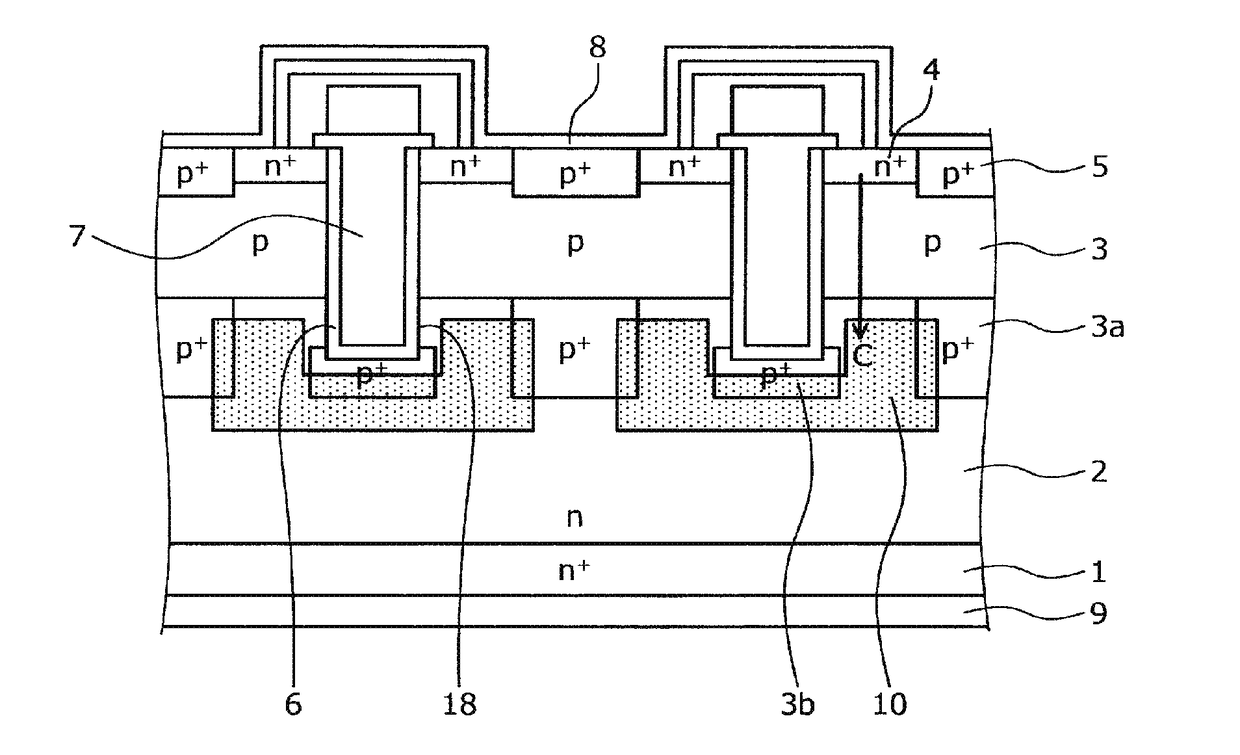

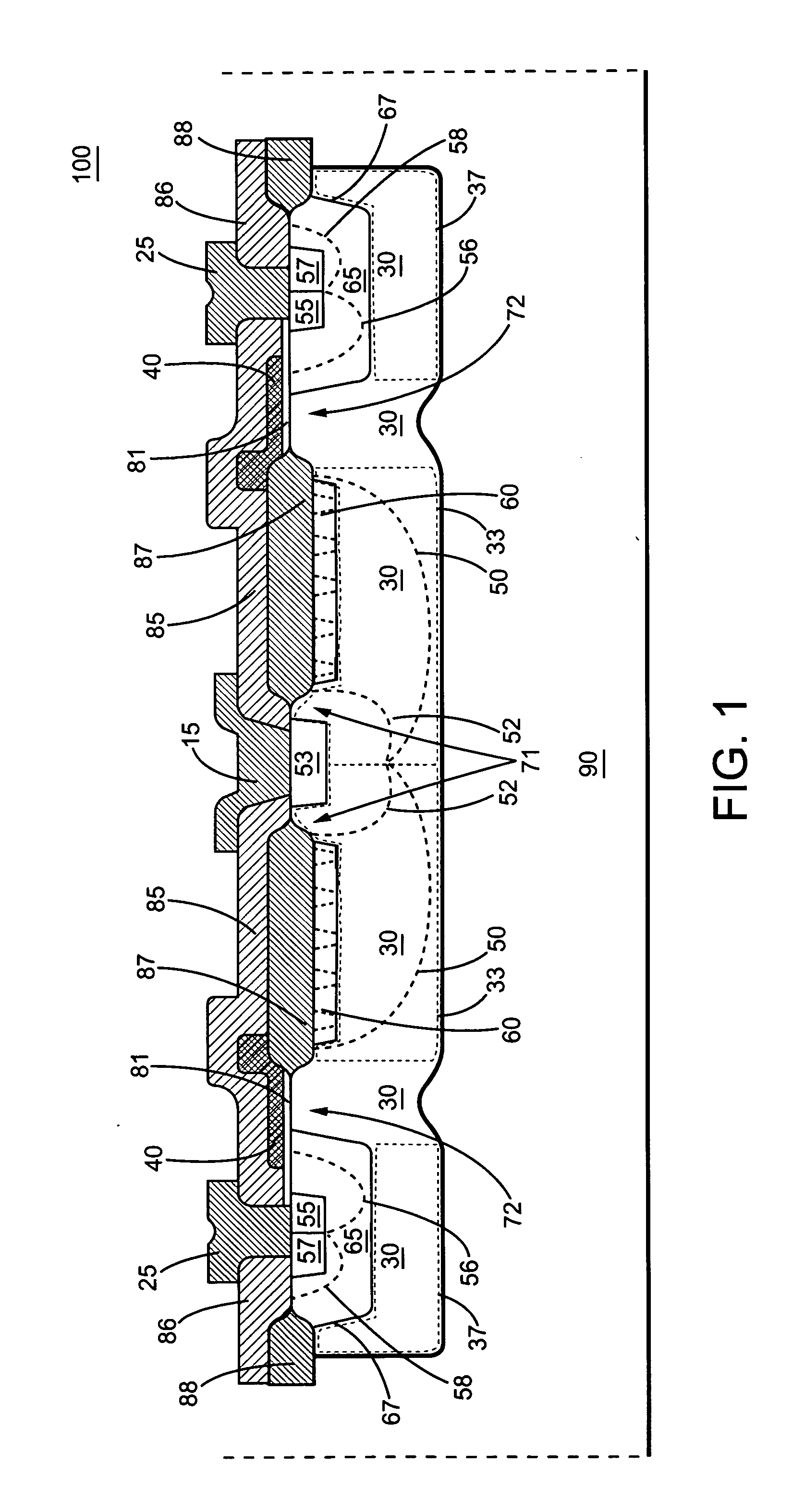

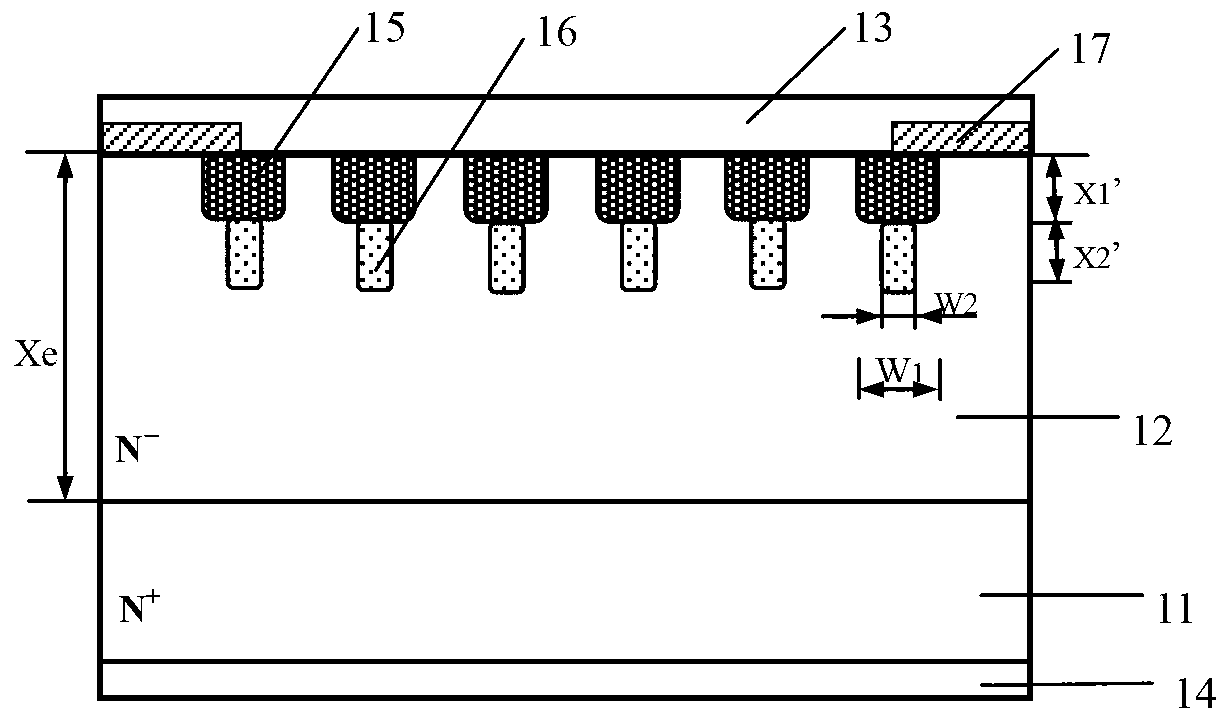

Power devices having trench-based source and gate electrodes

ActiveUS20060060916A1Improve breakdown voltageIncrease the on-resistanceSemiconductor/solid-state device manufacturingDiodePower semiconductor deviceDevice material

A power semiconductor device includes a plurality of trenches formed within a semiconductor body, each trench including one or more electrodes formed therein. In particular, according to embodiments of the invention, the plurality of trenches of a semiconductor device may include one or more gate electrodes, may include one or more gate electrodes or one or more source electrodes, or may include a combination of both gate and source electrodes formed therein. The trenches and electrodes may have varying depths within the semiconductor body.

Owner:INFINEON TECH AMERICAS CORP

Power converter with capacitive energy transfer and fast dynamic response

ActiveUS8212541B2Improve performanceIncrease conversionsEfficient power electronics conversionApparatus without intermediate ac conversionCapacitanceConverters

A converter circuit and related technique for providing high power density power conversion includes a reconfigurable switched capacitor transformation stage coupled to a magnetic converter (or regulation) stage. The circuits and techniques achieve high performance over a wide input voltage range or a wide output voltage range. The converter can be used, for example, to power logic devices in portable battery operated devices.

Owner:MASSACHUSETTS INST OF TECH

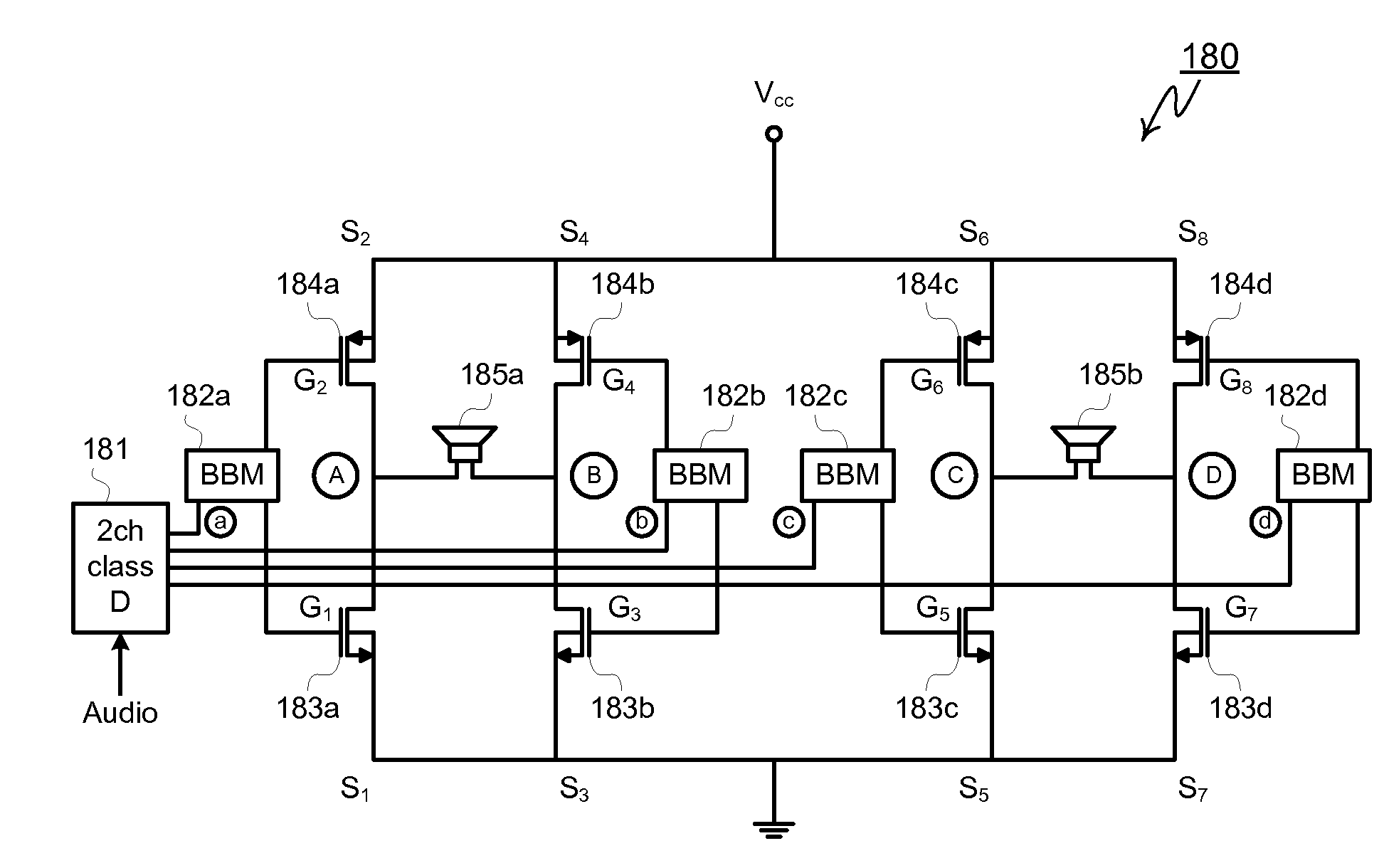

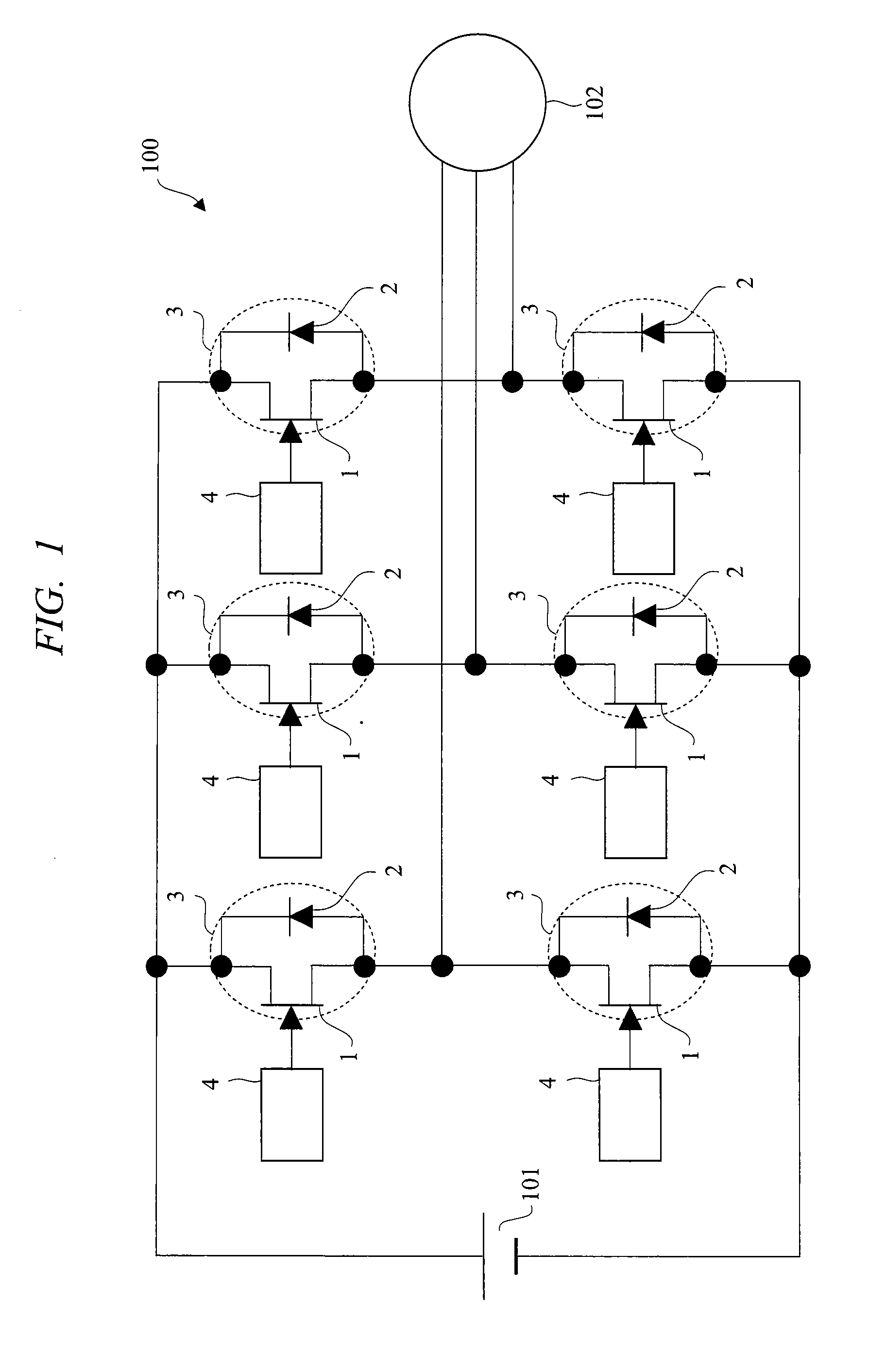

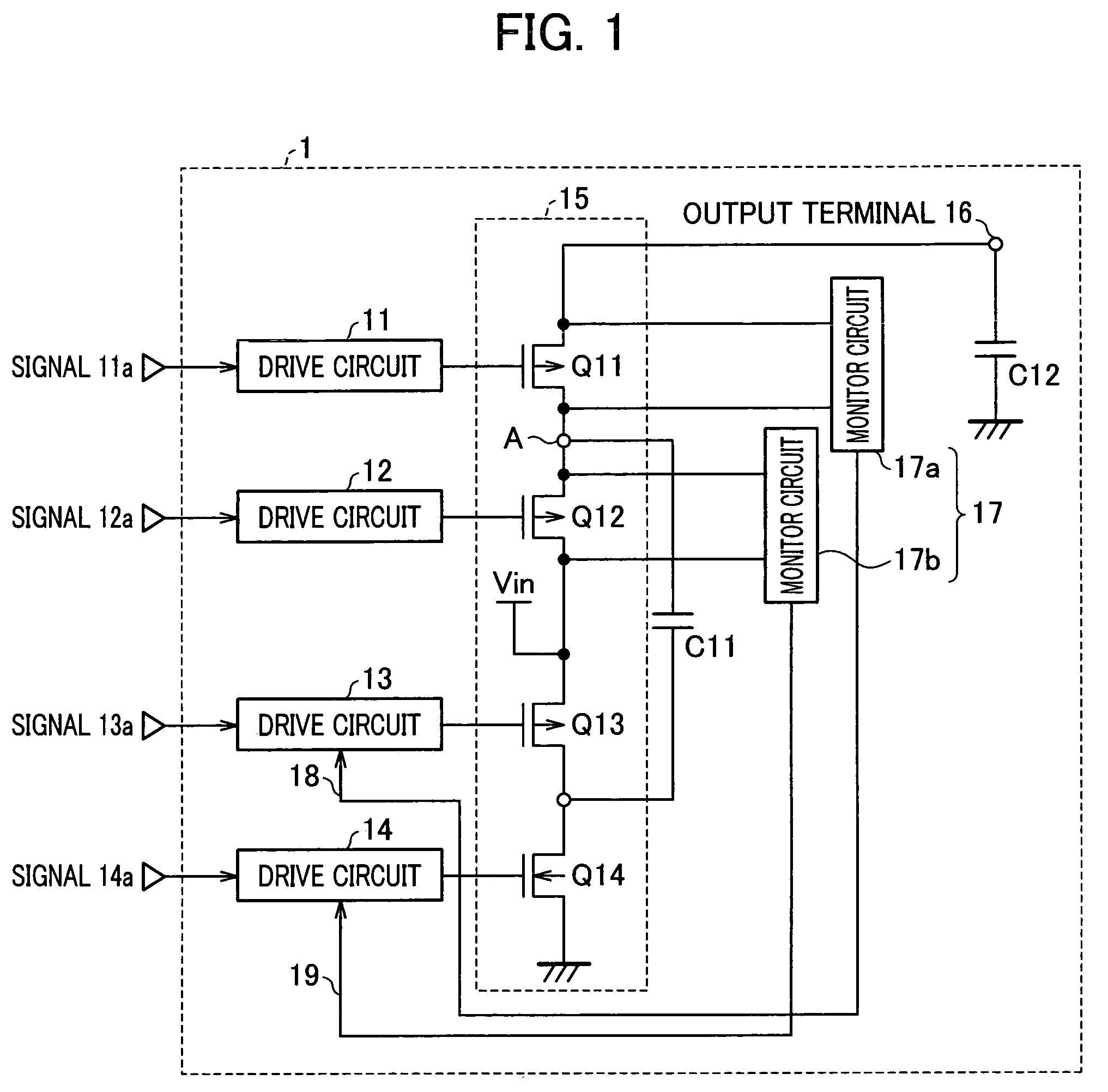

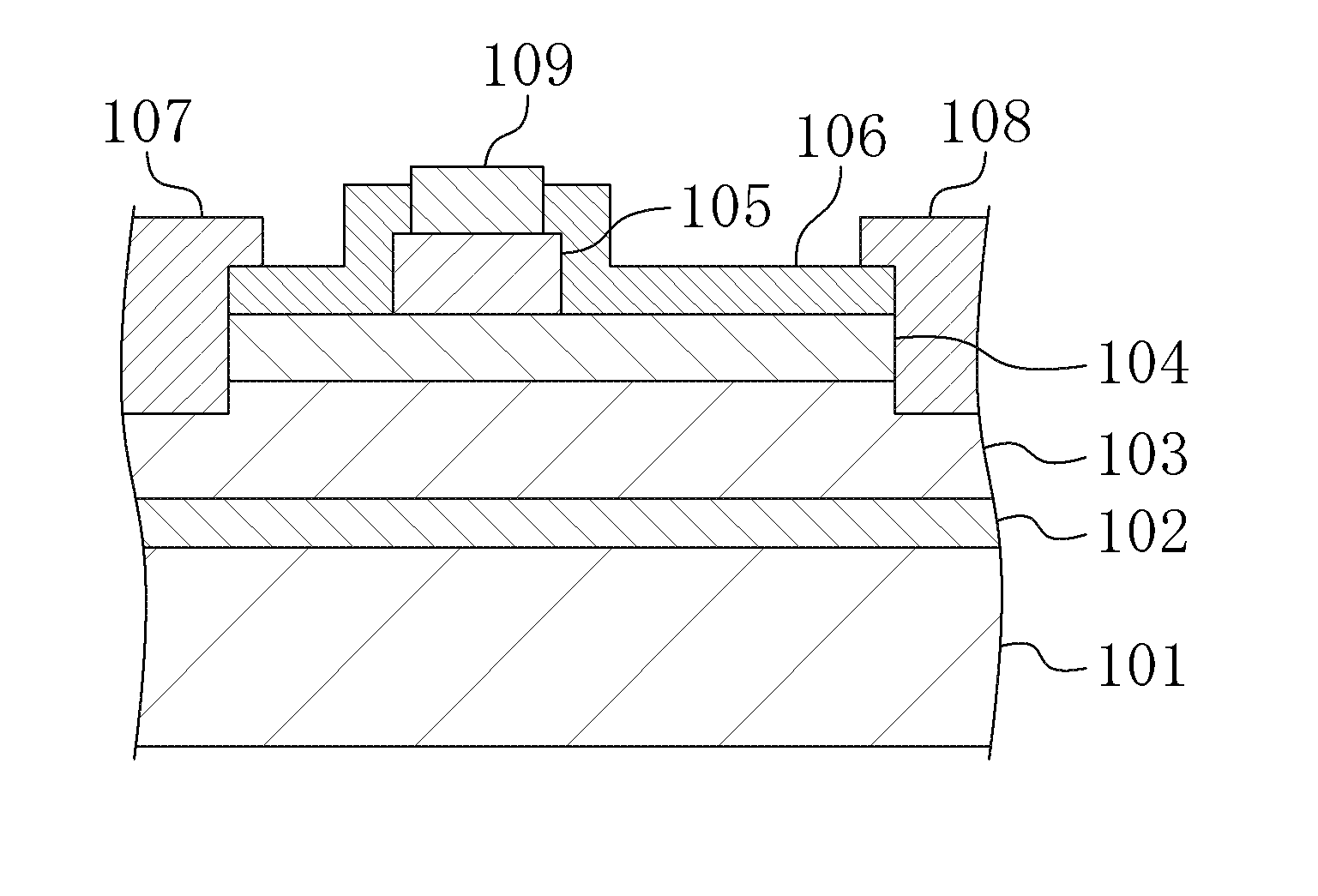

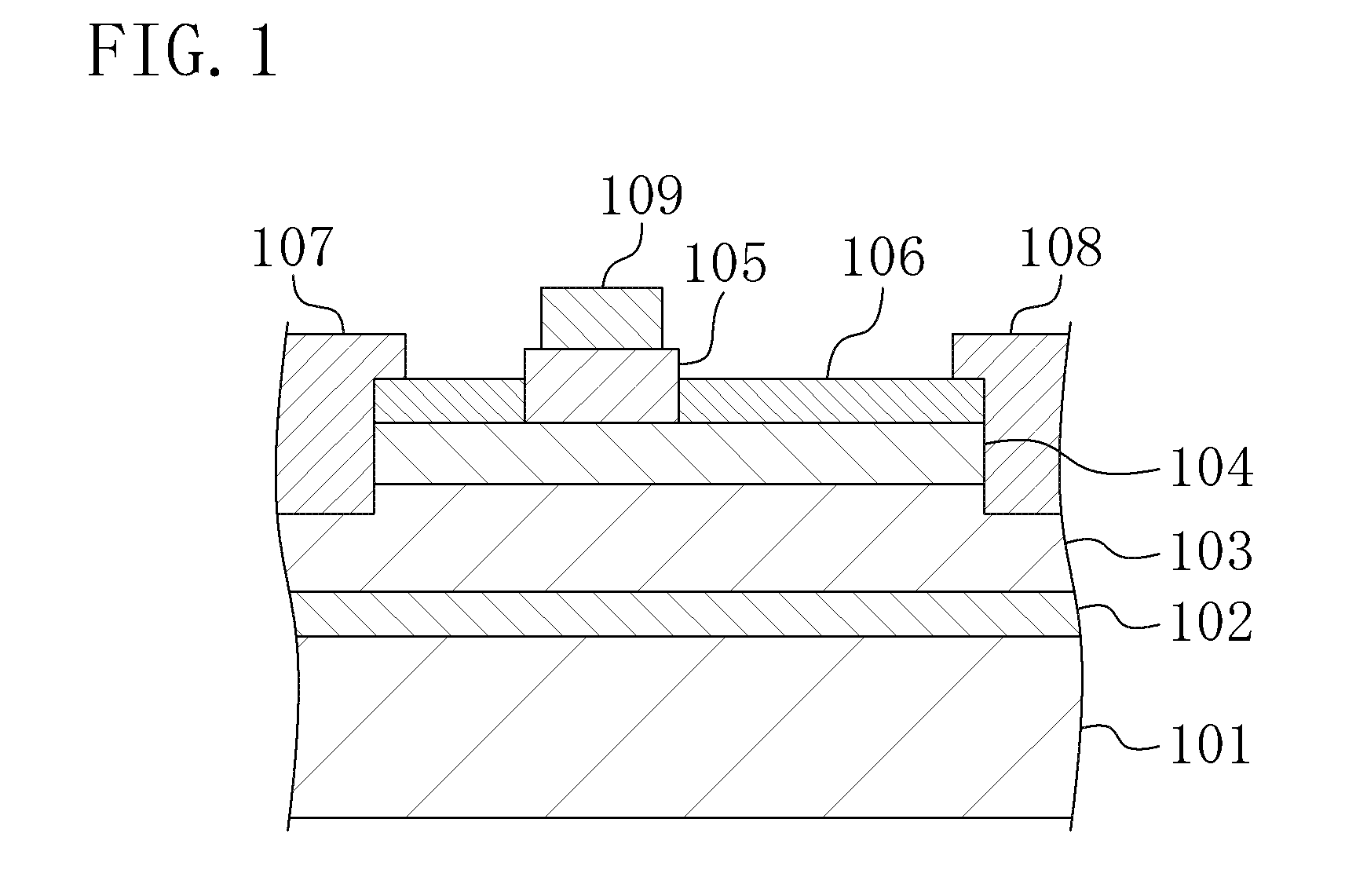

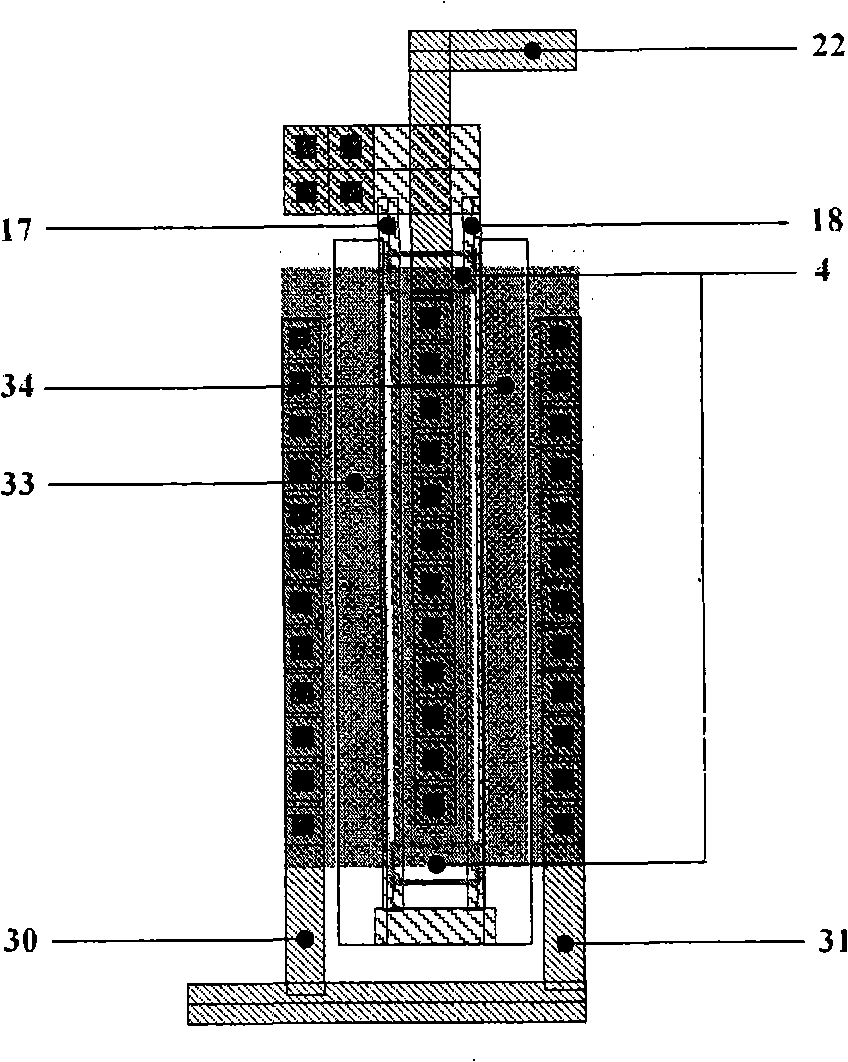

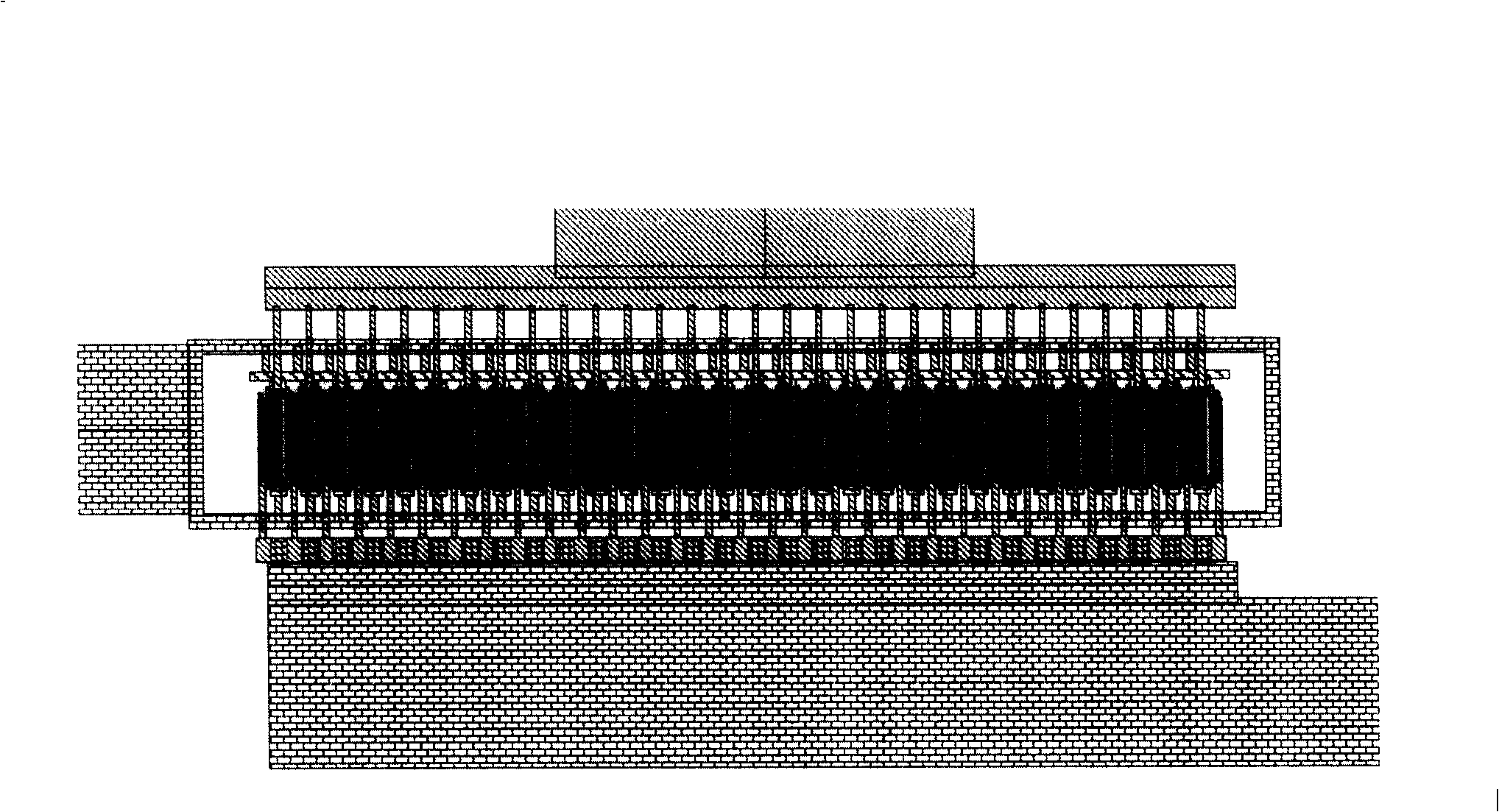

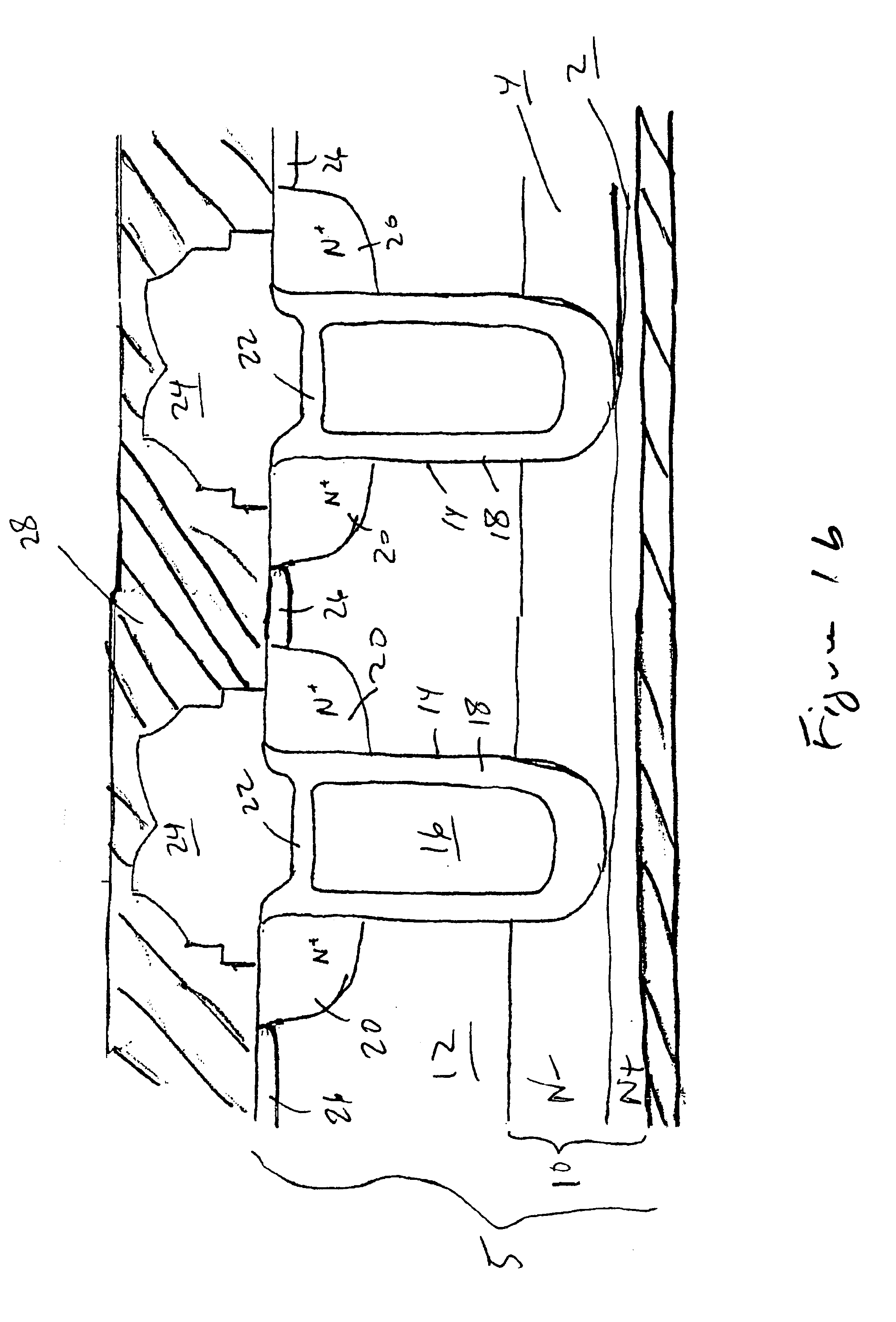

Power-MOSFETs with Improved Efficiency for Multi-channel Class-D Audio Amplifiers and Packaging Thereof

InactiveUS20080252372A1Lower on-resistanceSimple preparation techniqueTransistorSemiconductor/solid-state device detailsGround contactAudio power amplifier

A stereo class-D audio system includes a first die including four monolithically integrated NMOS high-side devices and a second a second die including four monolithically integrated PMOS low-side devices. The audio system also includes a set of electrical contacts for connecting the high and low-side devices to components within the a stereo class-D audio system, the set of electrical contacts including at least one supply contact for connecting the drains of the high-side devices to a supply voltage (Vcc) and at least one ground contact for connecting the drains of the low-side devices to ground, the electrical contacts also including respective contacts for each source of the high and low-side devices allowing the source of each high-side device to be connected to the source of a respective low-side device to form two H-bridge circuits.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

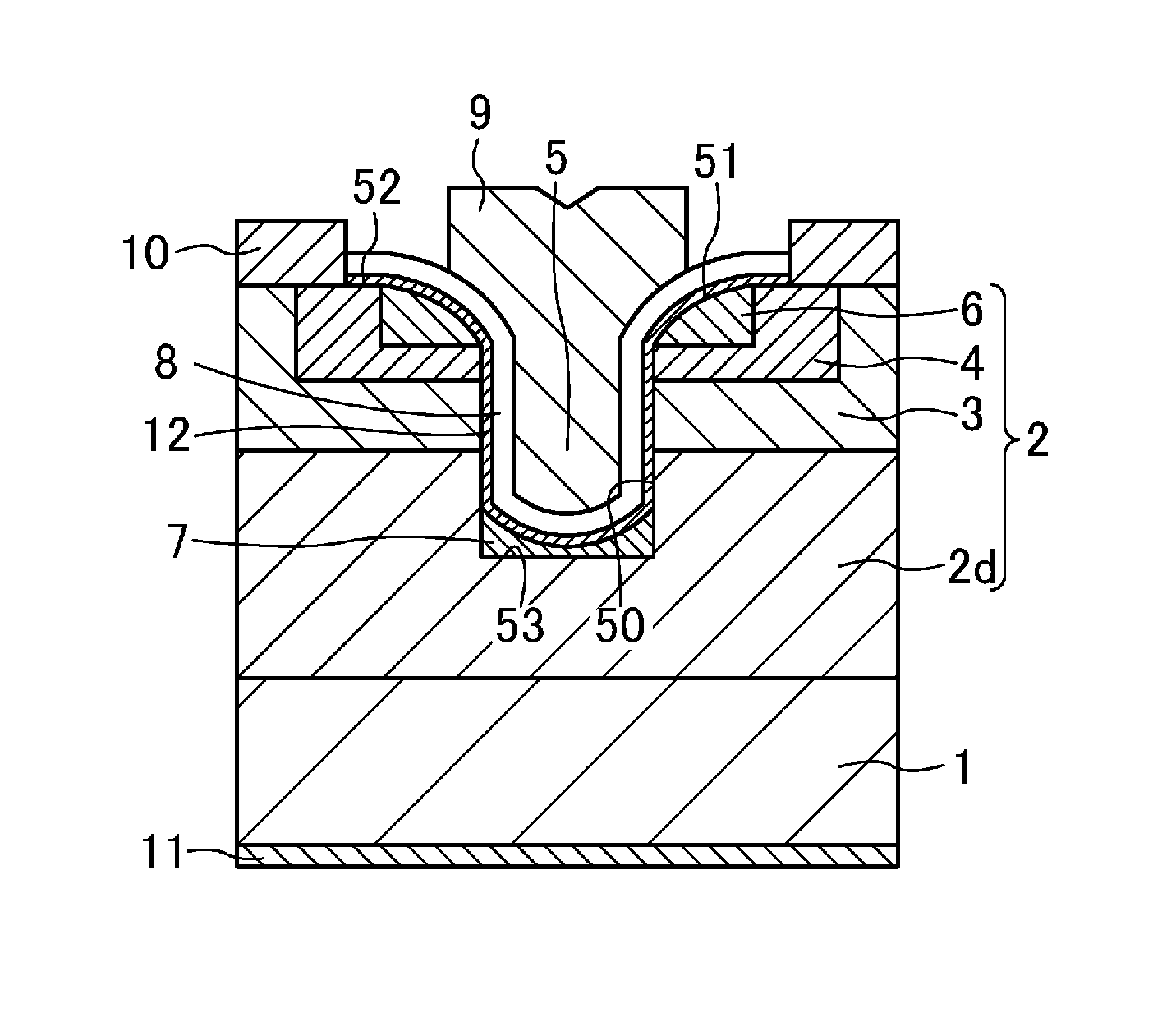

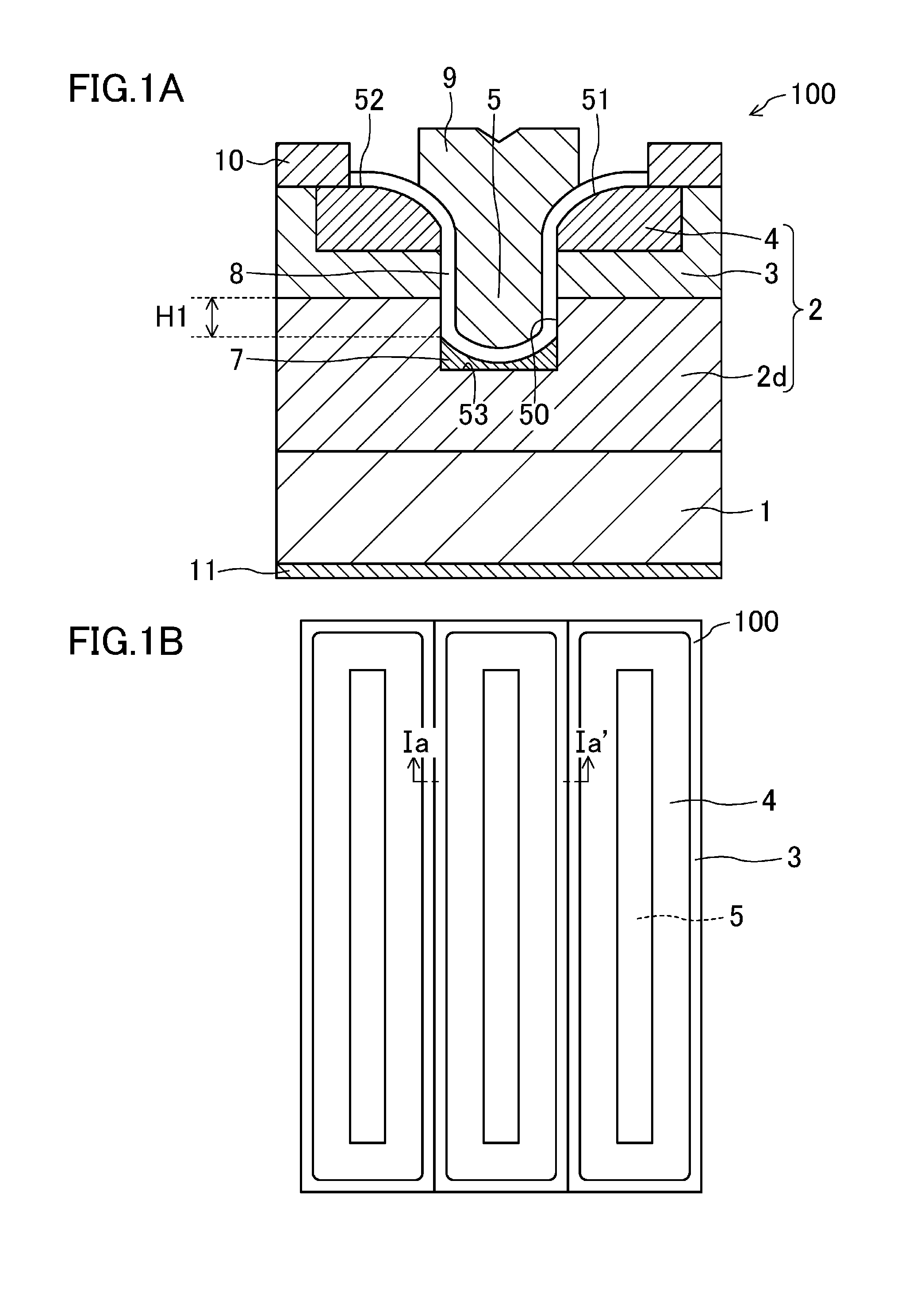

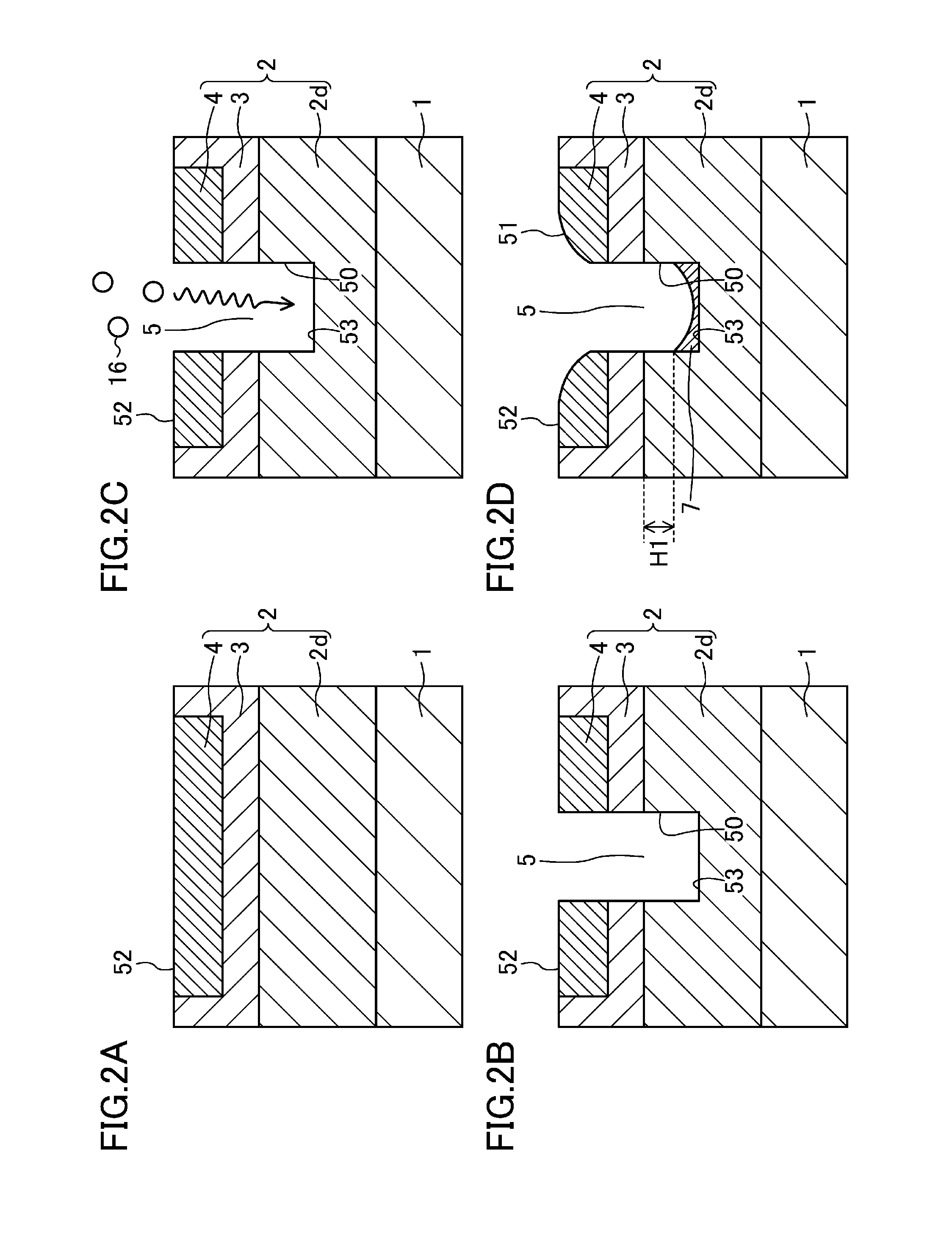

Semiconductor device and power conversion device using the same

ActiveUS20080315257A1Large switching lossIncreased power lossTransistorSolid-state devicesDevice materialSemiconductor chip

In a semiconductor device in which a diode and a high electron mobility transistor are incorporated in the same semiconductor chip, a compound semiconductor layer of the high electron mobility transistor is formed on a main surface (first main surface) of a semiconductor substrate of the diode, and an anode electrode of the diode is electrically connected to an anode region via a conductive material embedded in a via hole (hole) reaching a p+ region which is the anode region of the main surface of the semiconductor substrate from a main surface of the compound semiconductor layer.

Owner:RENESAS ELECTRONICS CORP

Charge pump DC/DC converter circuit

ActiveUS7224591B2Increase the on-resistanceAvoid switchingAc-dc conversionApparatus without intermediate ac conversionPotential differenceSemiconductor

Owner:SHARP KK

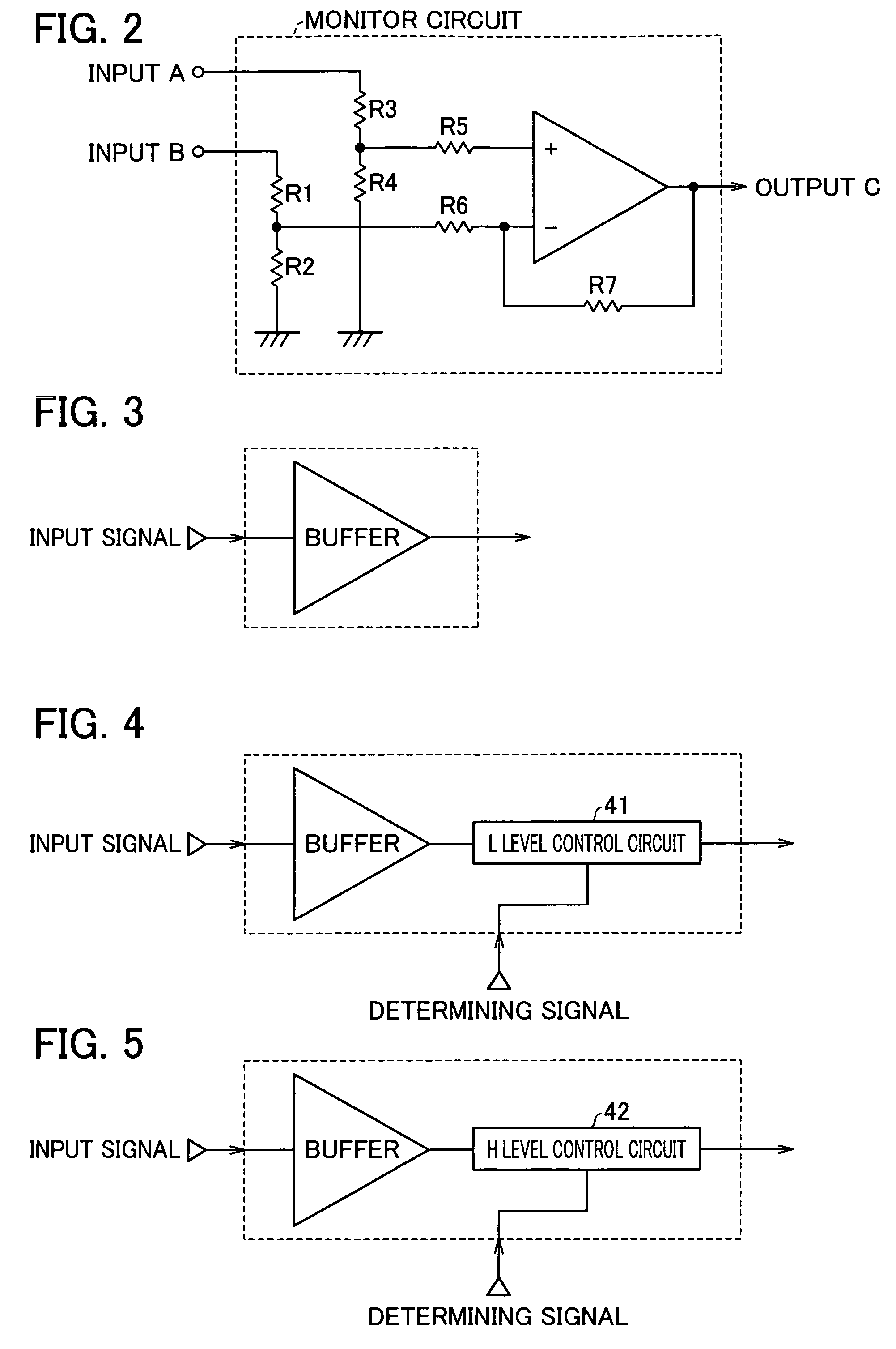

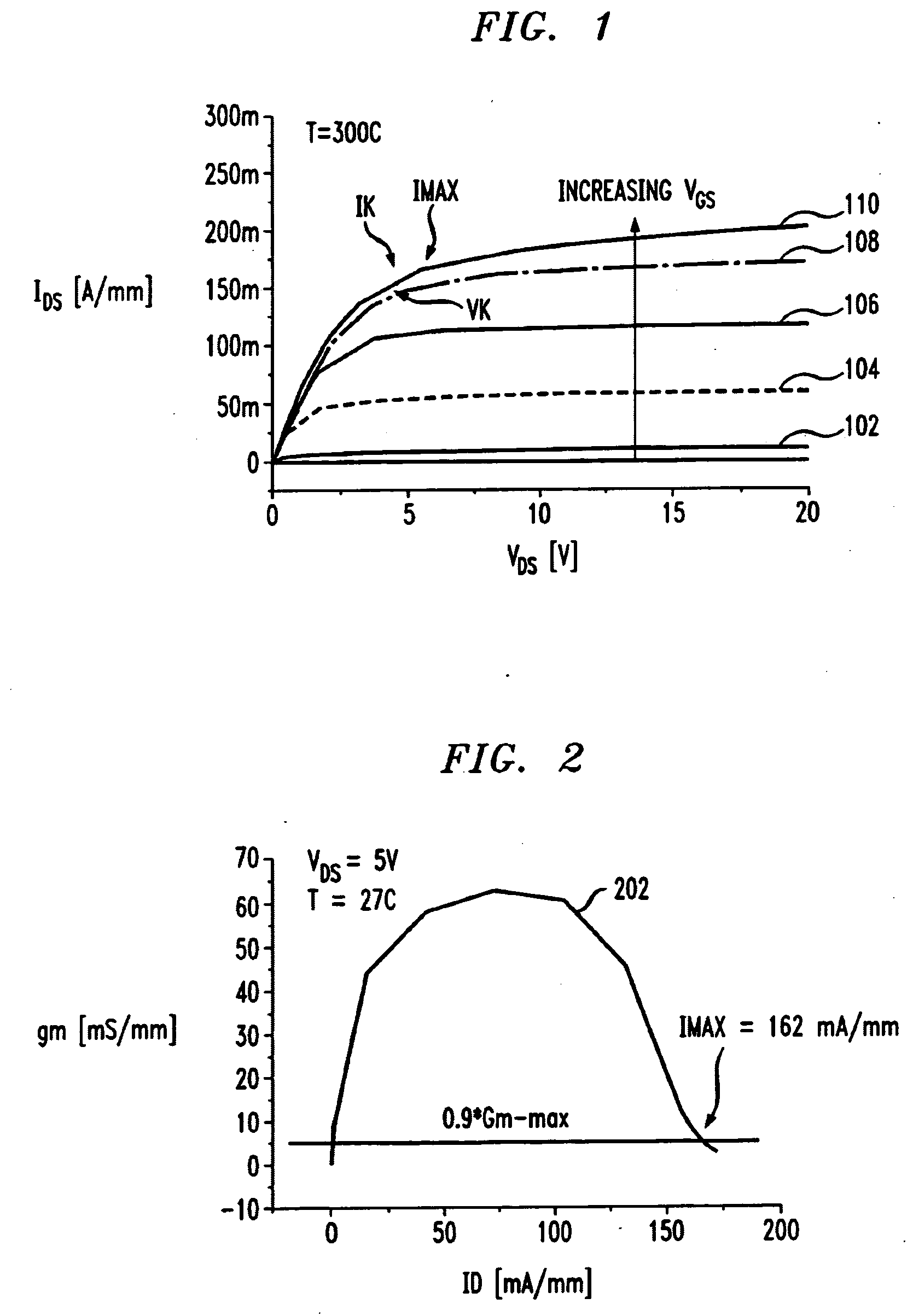

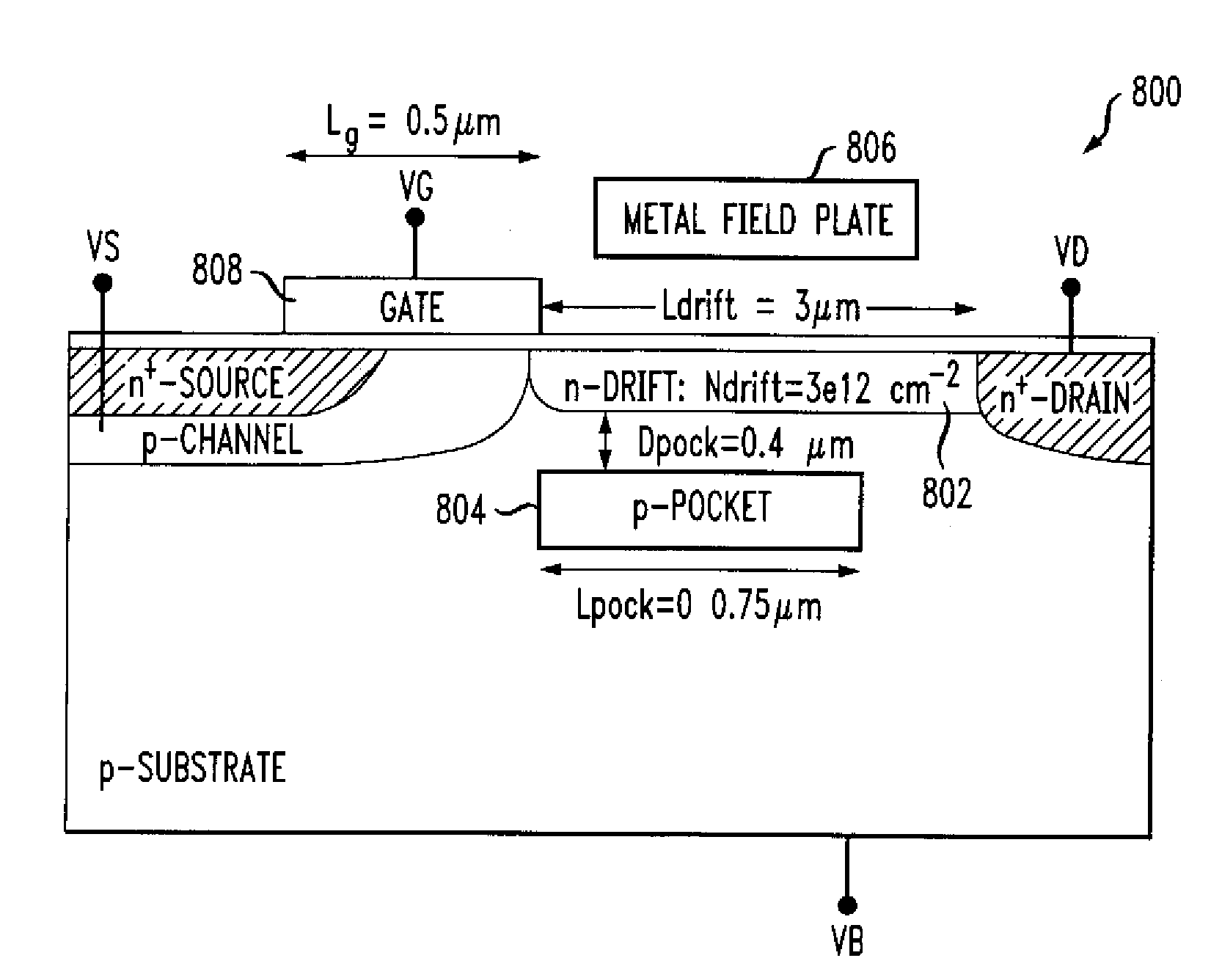

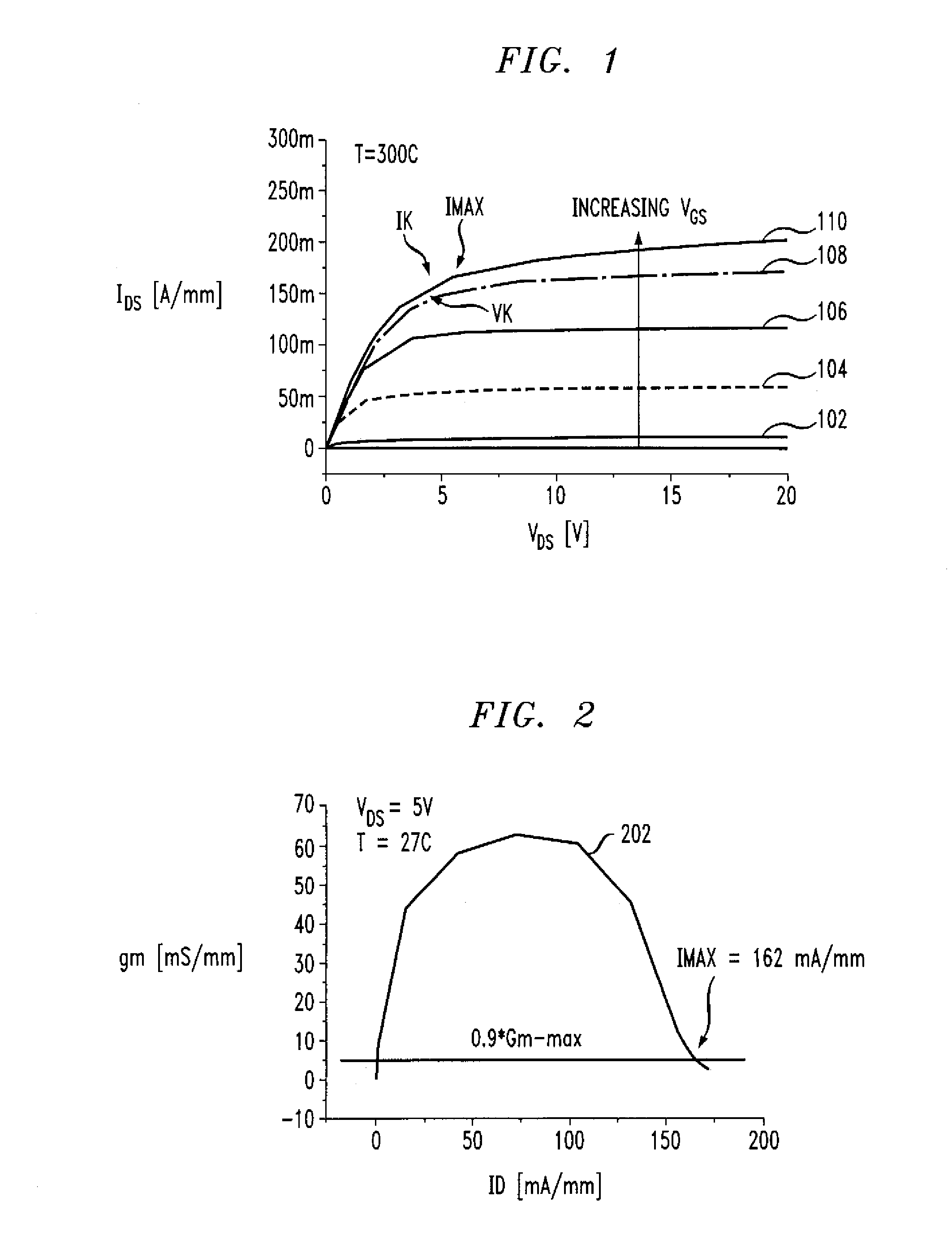

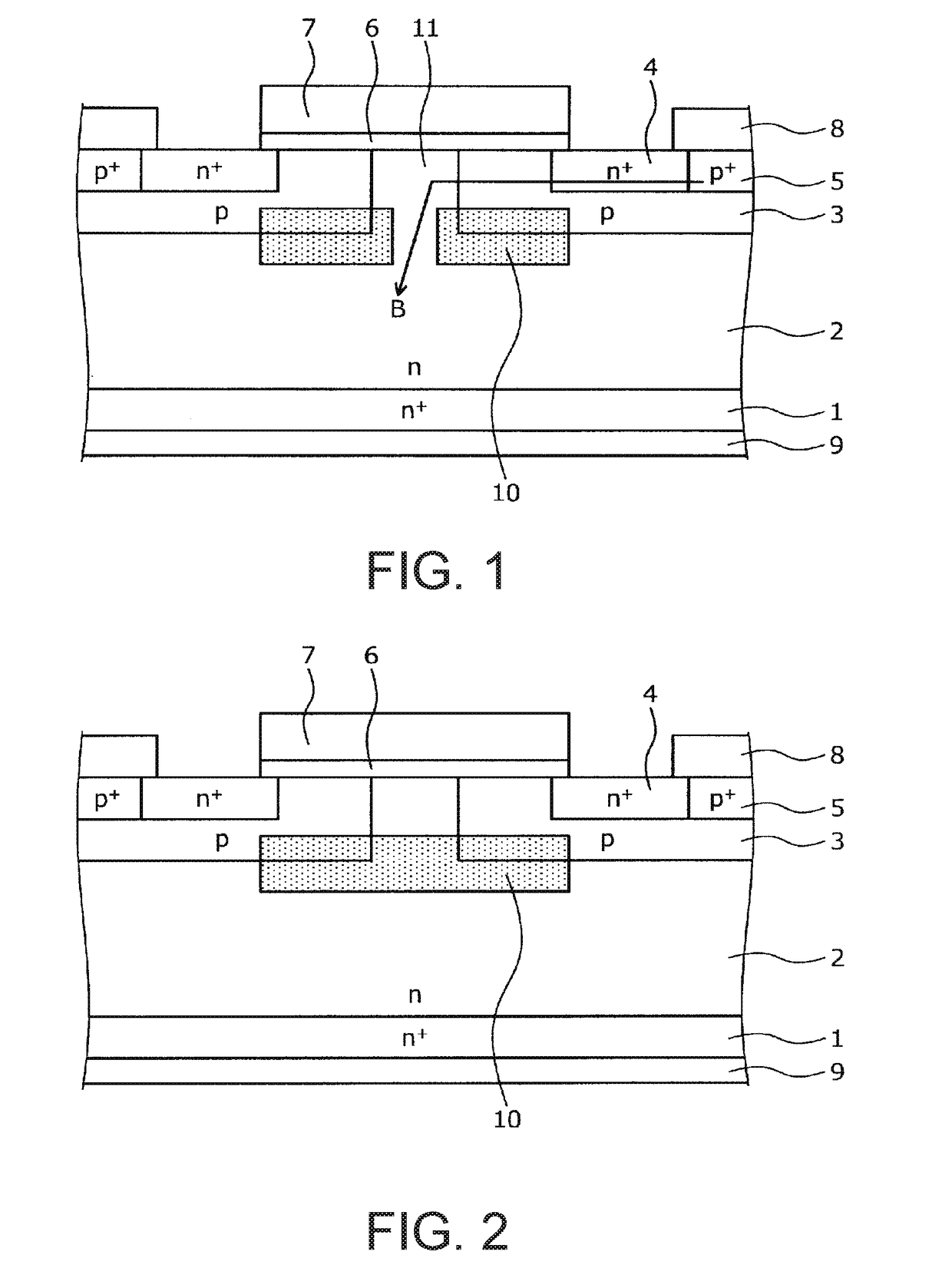

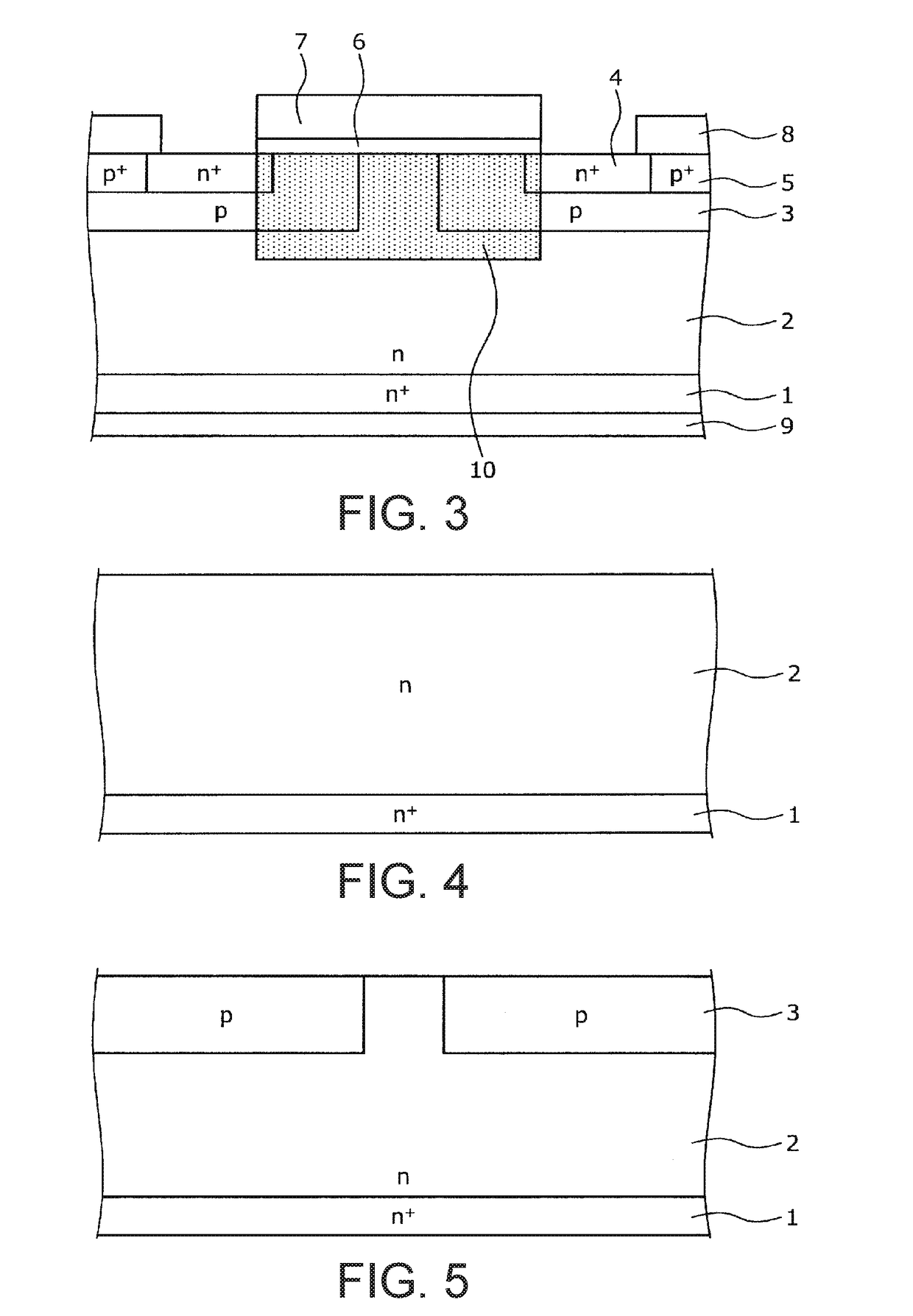

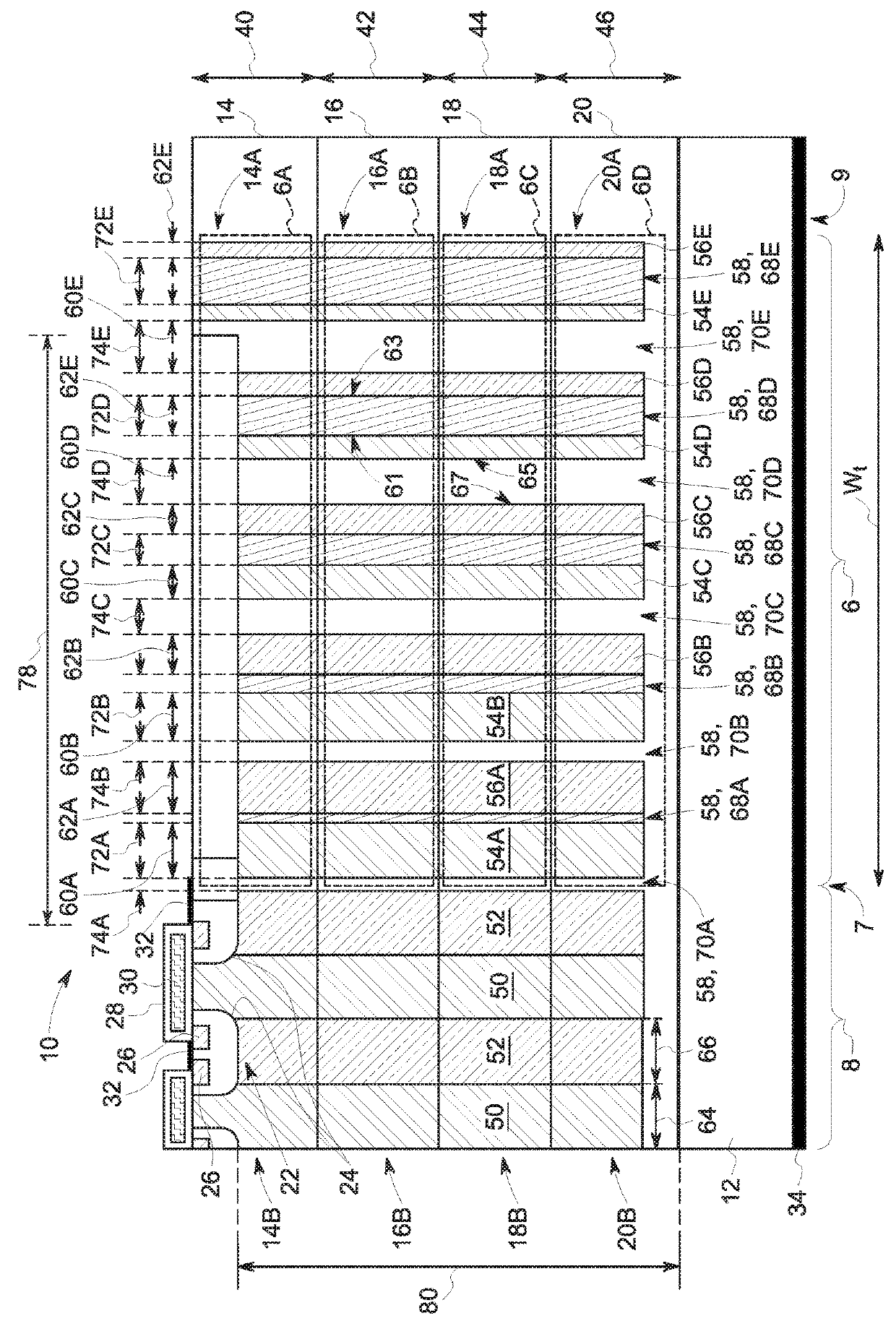

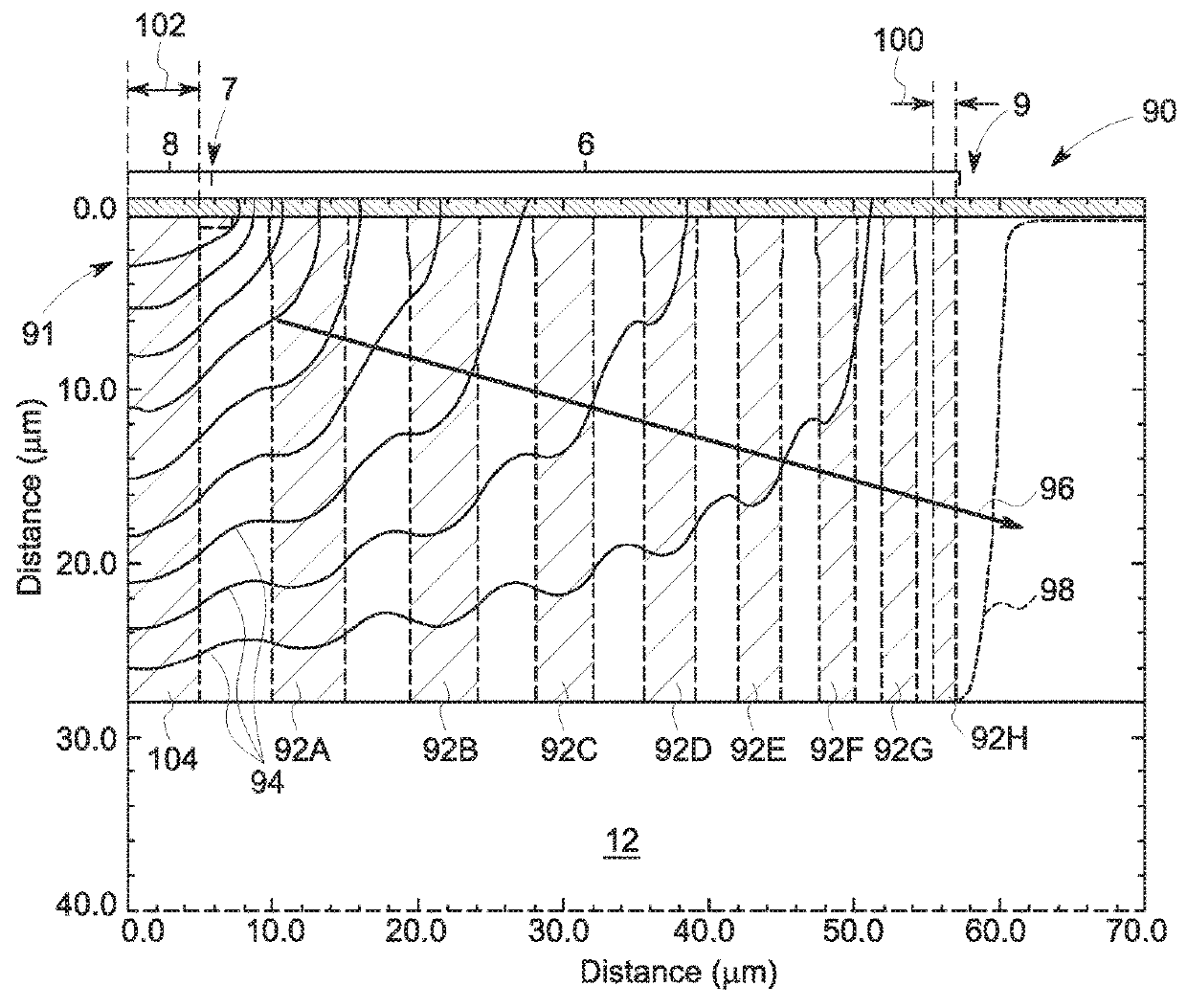

Semiconductor device having improved power density

ActiveUS20060113625A1Improve power densityIncrease the on-resistanceSemiconductor/solid-state device detailsSolid-state devicesClose relativesImpurity doping

An MOS device is formed including a semiconductor layer of a first conductivity type, and source and drain regions of a second conductivity type formed in the semiconductor layer proximate an upper surface of the semiconductor layer. The source and drain regions are spaced apart relative to one another. A drift region of the second conductivity type is formed in the semiconductor layer proximate the upper surface of the semiconductor layer and at least partially between the source and drain regions, the drift region having an impurity doping concentration greater than about 2.0e12 atoms / cm2. An insulating layer is formed on at least a portion of the upper surface of the semiconductor layer. The device further includes a gate formed on the insulating layer at least partially between the source and drain regions, and a buried layer of the first conductivity type formed in the semiconductor layer in close relative proximity to and beneath at least a portion of the drift region. A substantially vertical distance between the buried layer and the drift region, and / or one or more physical dimensions of the buried layer are configured so as to optimize a power density of the device relative to at least one of an on-resistance and a maximum drain current of the device.

Owner:BELL SEMICON LLC

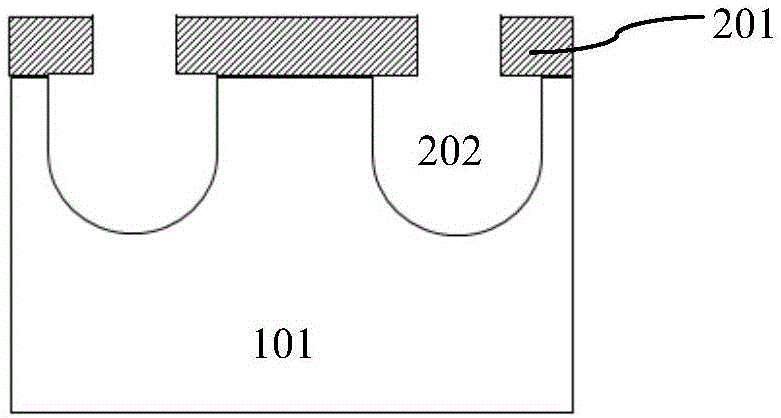

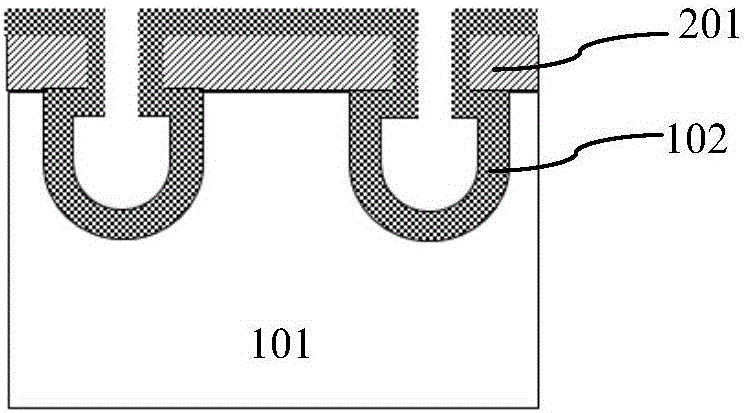

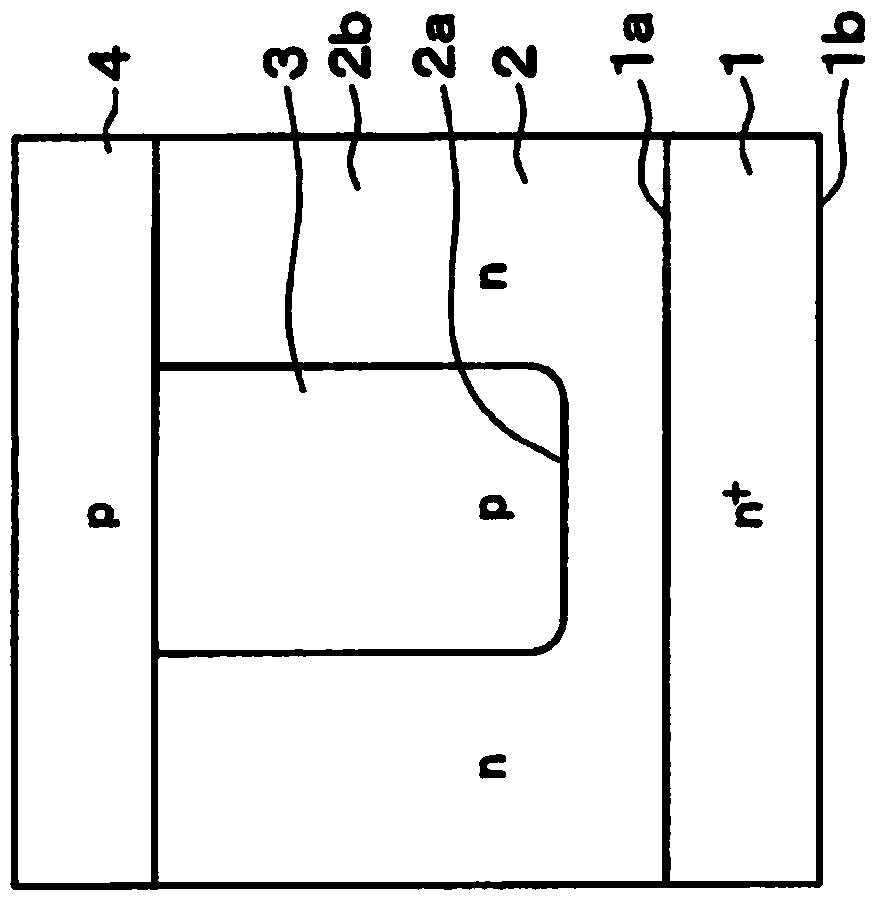

Trech-type vertical semiconductor device having gate electrode buried in rounded hump opening

InactiveUS20060267085A1Lower breakdown voltageIncrease the on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialSemiconductor

In a semiconductor device including a gate electrode buried in a trench of the device, the trench is constructed by a first opening with a uniform width the same as that of an upper portion of the first opening and a second opening beneath the first opening with a width larger than the uniform width. A bottom of a base region adjacent to the trench is adjacent to the second opening.

Owner:RENESAS ELECTRONICS CORP

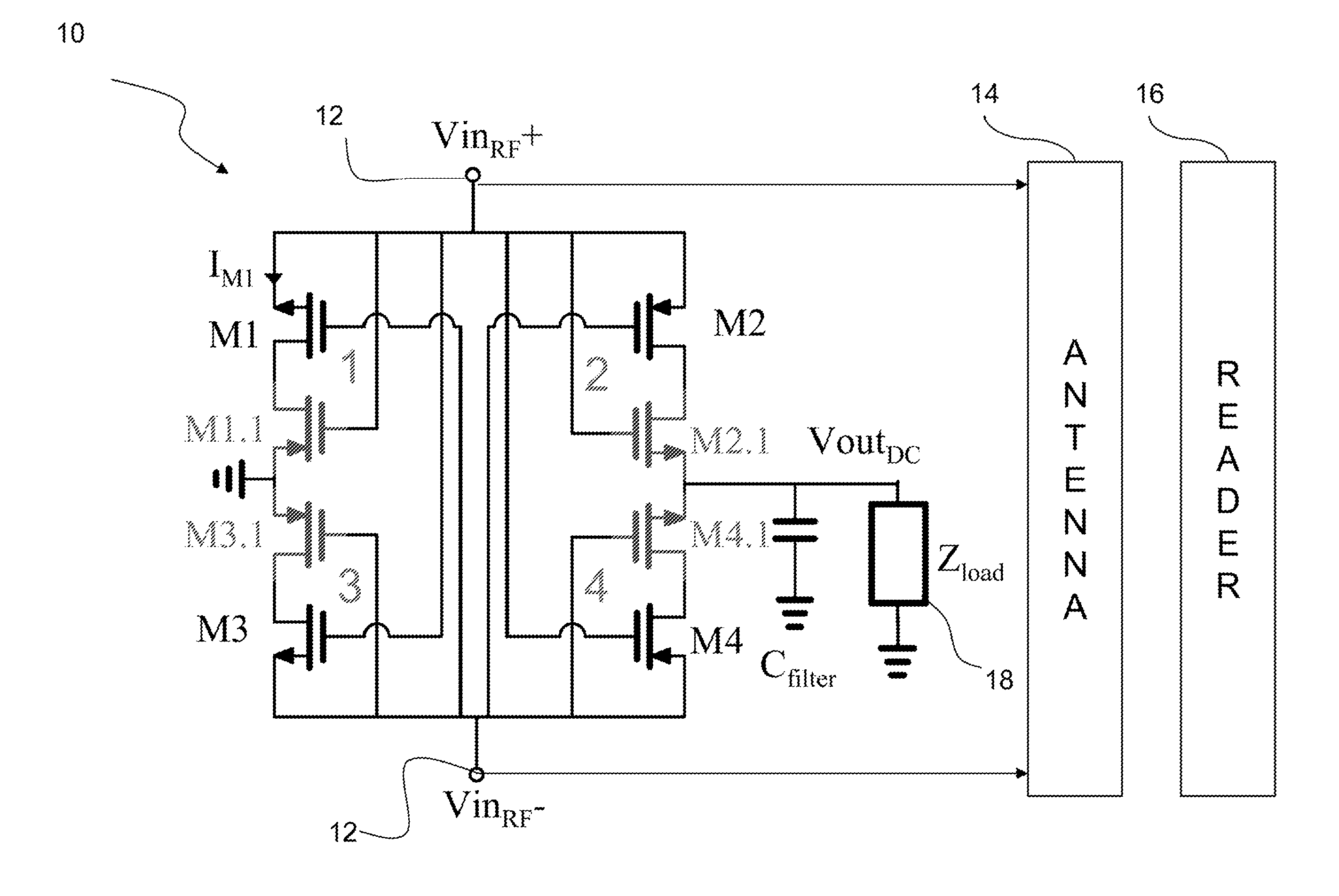

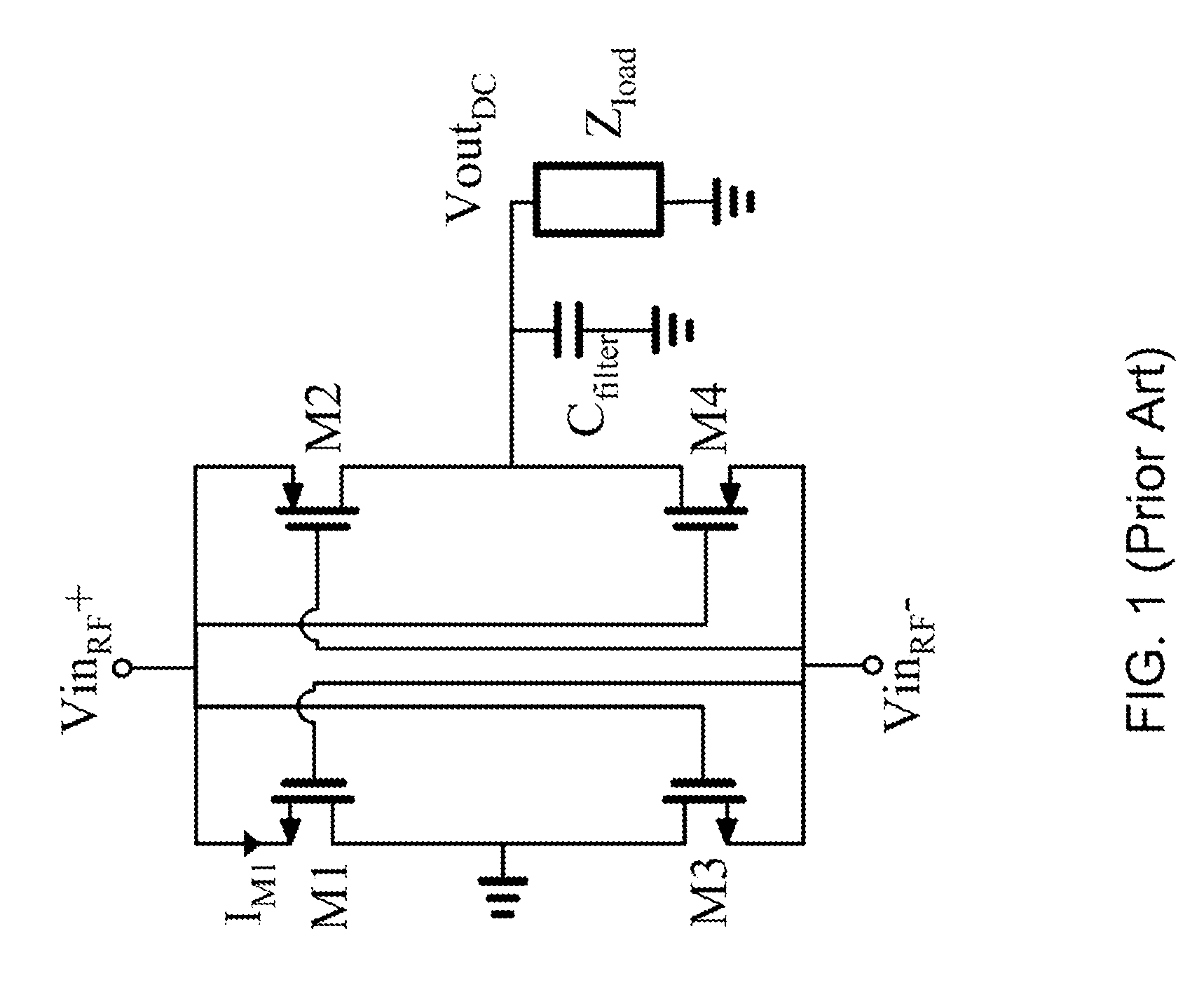

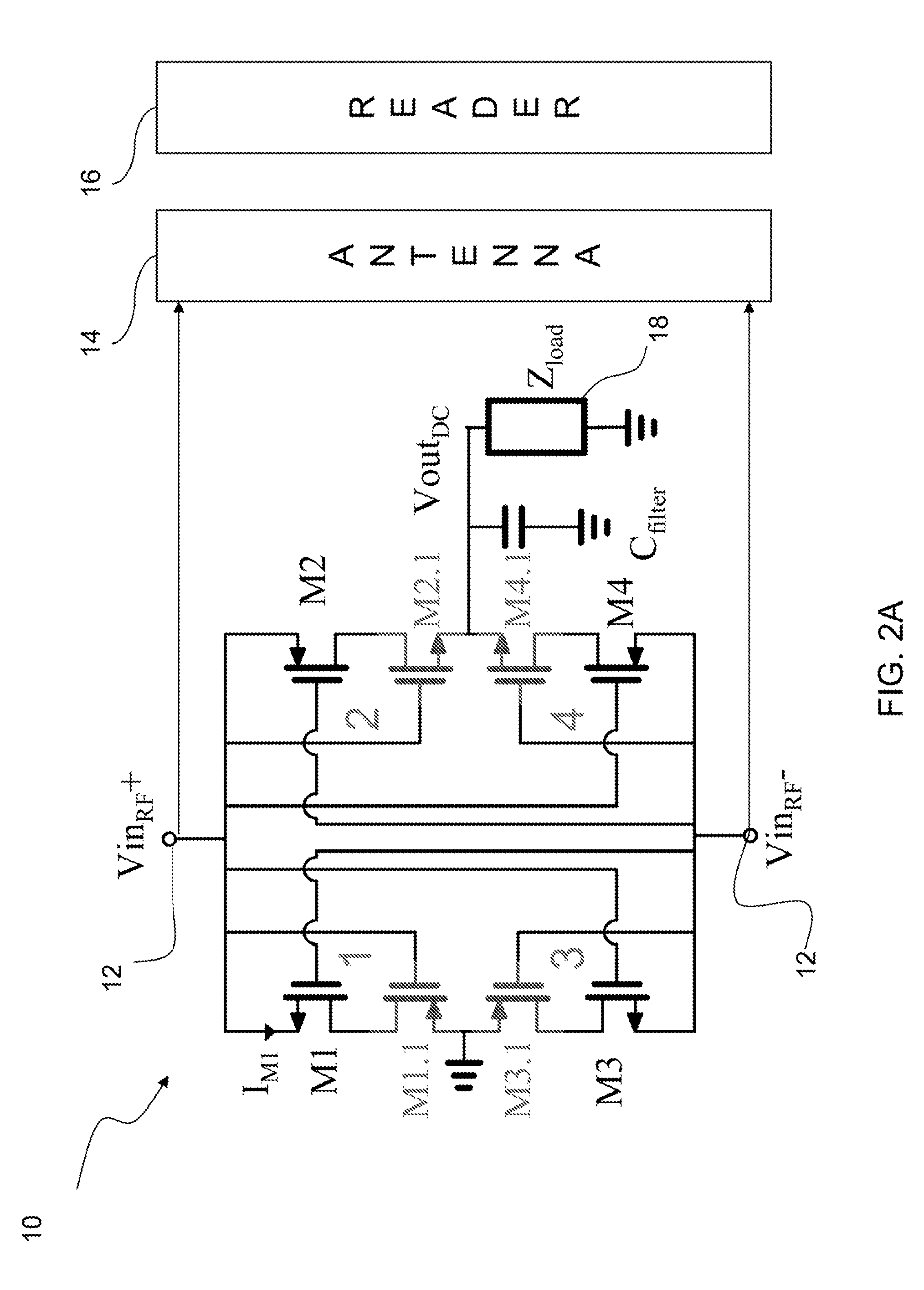

Switch mode voltage rectifier, RF energy conversion and wireless power supplies

InactiveUS20110124310A1Avoids reverse conduction problemIncrease the on-resistanceEfficient power electronics conversionCircuit arrangementsEngineeringDc voltage

Embodiments of the present invention provide cross-coupled rectifiers that use near zero-threshold transistors in a switching topology, but provide a topology that avoids reverse conduction problems. Importantly, preferred embodiment rectifiers of the invention only provide a slightly increased on-resistance in each branch, while providing both very high operating efficiency and very low turn-on voltage. An embodiment of the invention is a voltage rectifier for the conversion of RF energy into DC voltage with a turn-on threshold voltages approaching 0V.

Owner:RGT UNIV OF CALIFORNIA

Semiconductor device having improved power density

ActiveUS7262476B2Improve power densityIncrease the on-resistanceSemiconductor/solid-state device detailsSolid-state devicesClose relativesImpurity doping

An MOS device is formed including a semiconductor layer of a first conductivity type, and source and drain regions of a second conductivity type formed in the semiconductor layer proximate an upper surface of the semiconductor layer. The source and drain regions are spaced apart relative to one another. A drift region of the second conductivity type is formed in the semiconductor layer proximate the upper surface of the semiconductor layer and at least partially between the source and drain regions, the drift region having an impurity doping concentration greater than about 2.0e12 atoms / cm2. An insulating layer is formed on at least a portion of the upper surface of the semiconductor layer. The device further includes a gate formed on the insulating layer at least partially between the source and drain regions, and a buried layer of the first conductivity type formed in the semiconductor layer in close relative proximity to and beneath at least a portion of the drift region. A substantially vertical distance between the buried layer and the drift region, and / or one or more physical dimensions of the buried layer are configured so as to optimize a power density of the device relative to at least one of an on-resistance and a maximum drain current of the device.

Owner:BELL SEMICON LLC

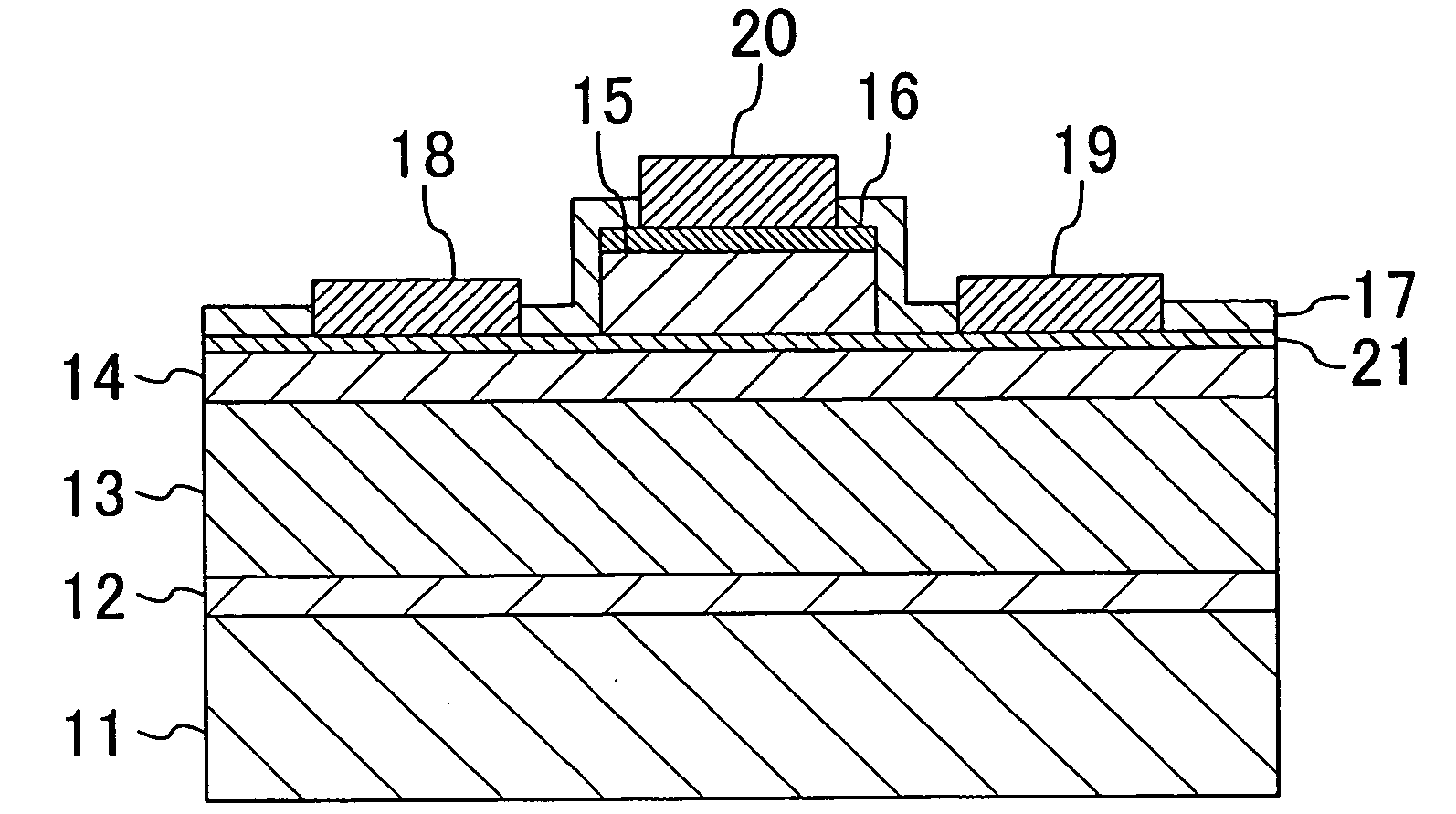

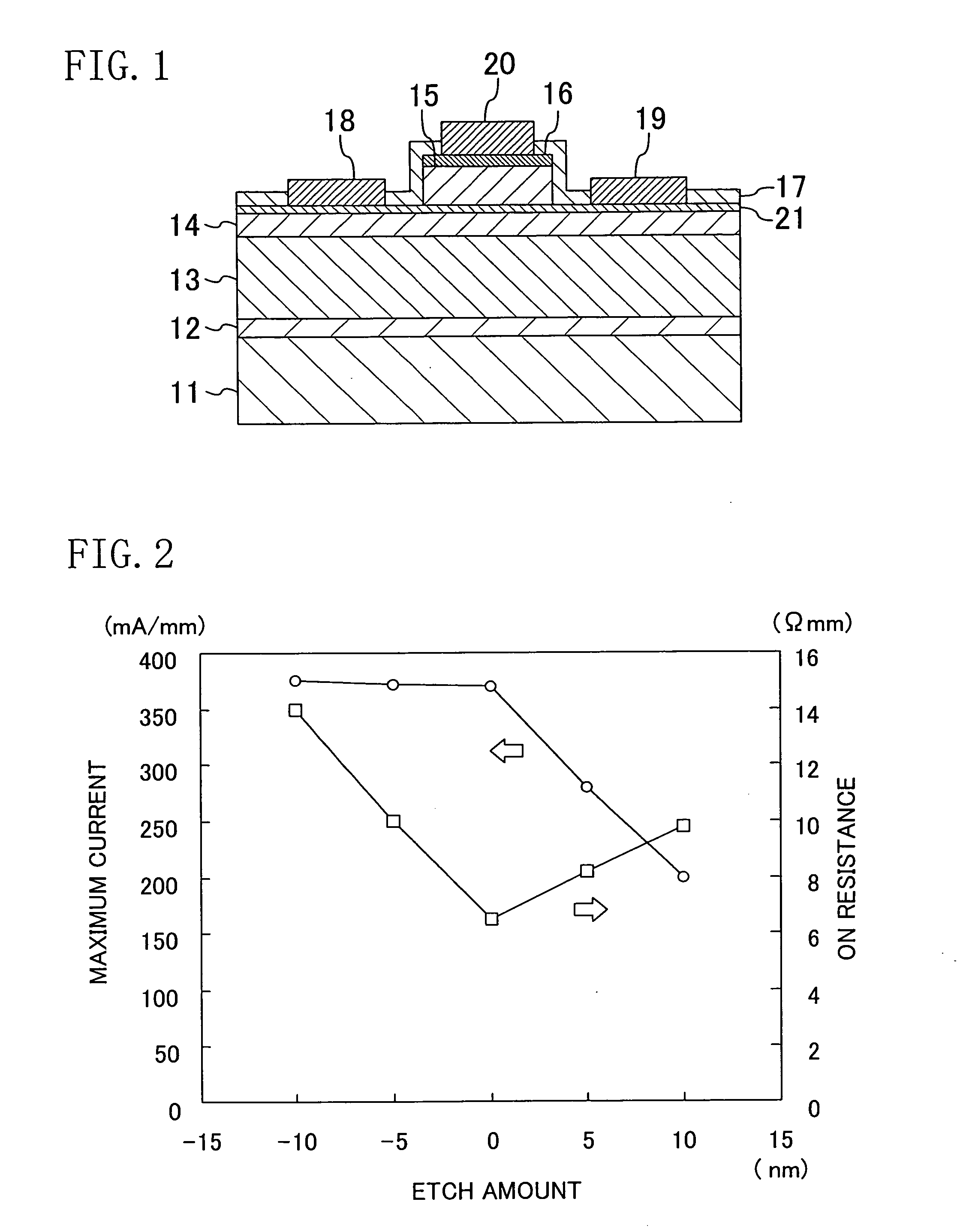

Transistor

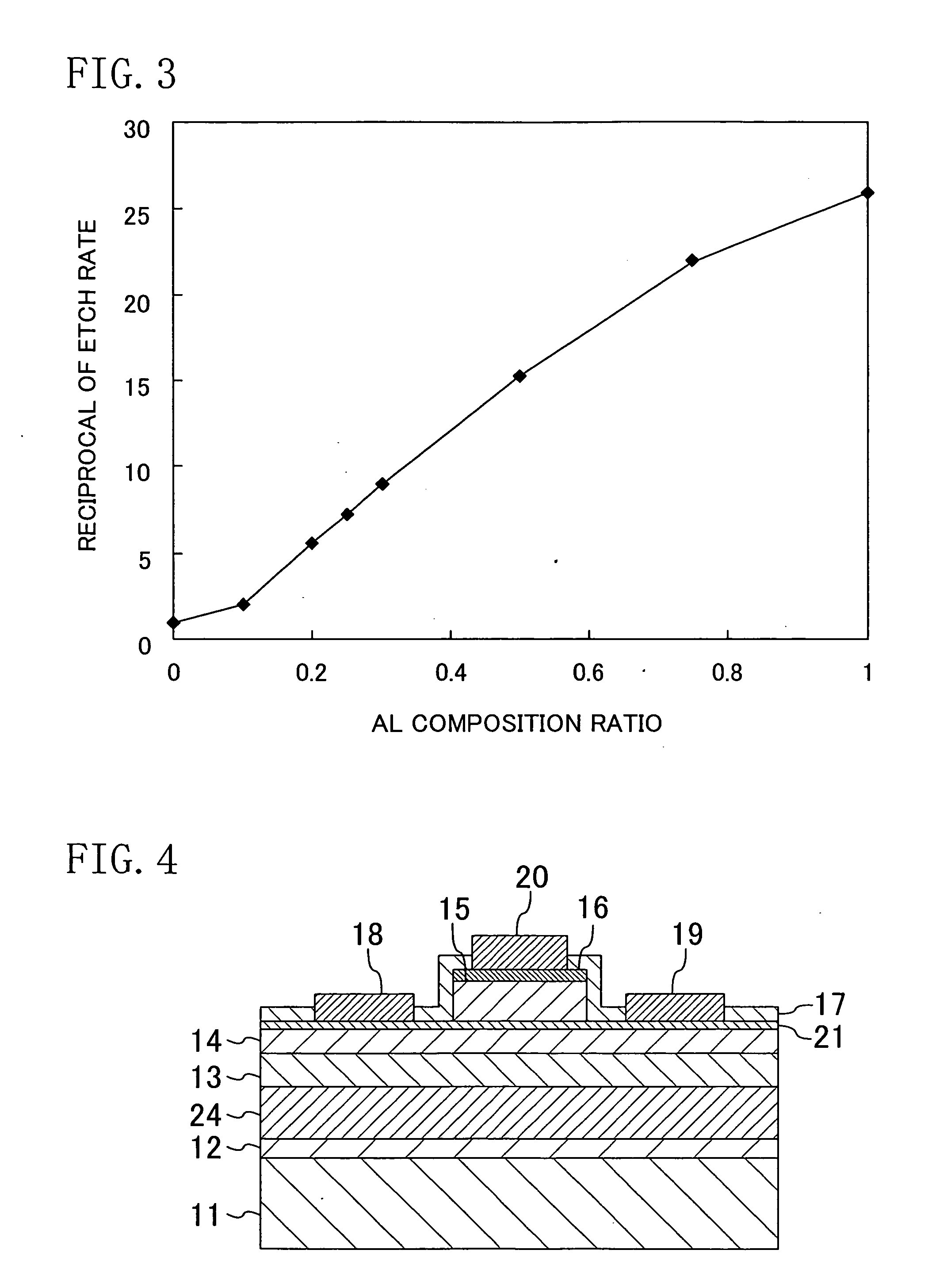

ActiveUS20070176215A1Deterioration of characteristicHigh currentSemiconductor/solid-state device manufacturingSemiconductor devicesControl layerElectrical conductor

A transistor includes a first semiconductor layer formed on a substrate, a second semiconductor layer formed on the first semiconductor layer and has a band gap larger than that of the first semiconductor layer, a control layer formed on the second semiconductor layer and contains p-type impurities, a gate electrode formed in contact with at least part of the control layer and a source electrode and a drain electrode formed on both sides of the control layer, respectively. A third semiconductor layer made of material having a lower etch rate than that of the control layer is formed between the control layer and the second semiconductor layer.

Owner:PANASONIC CORP

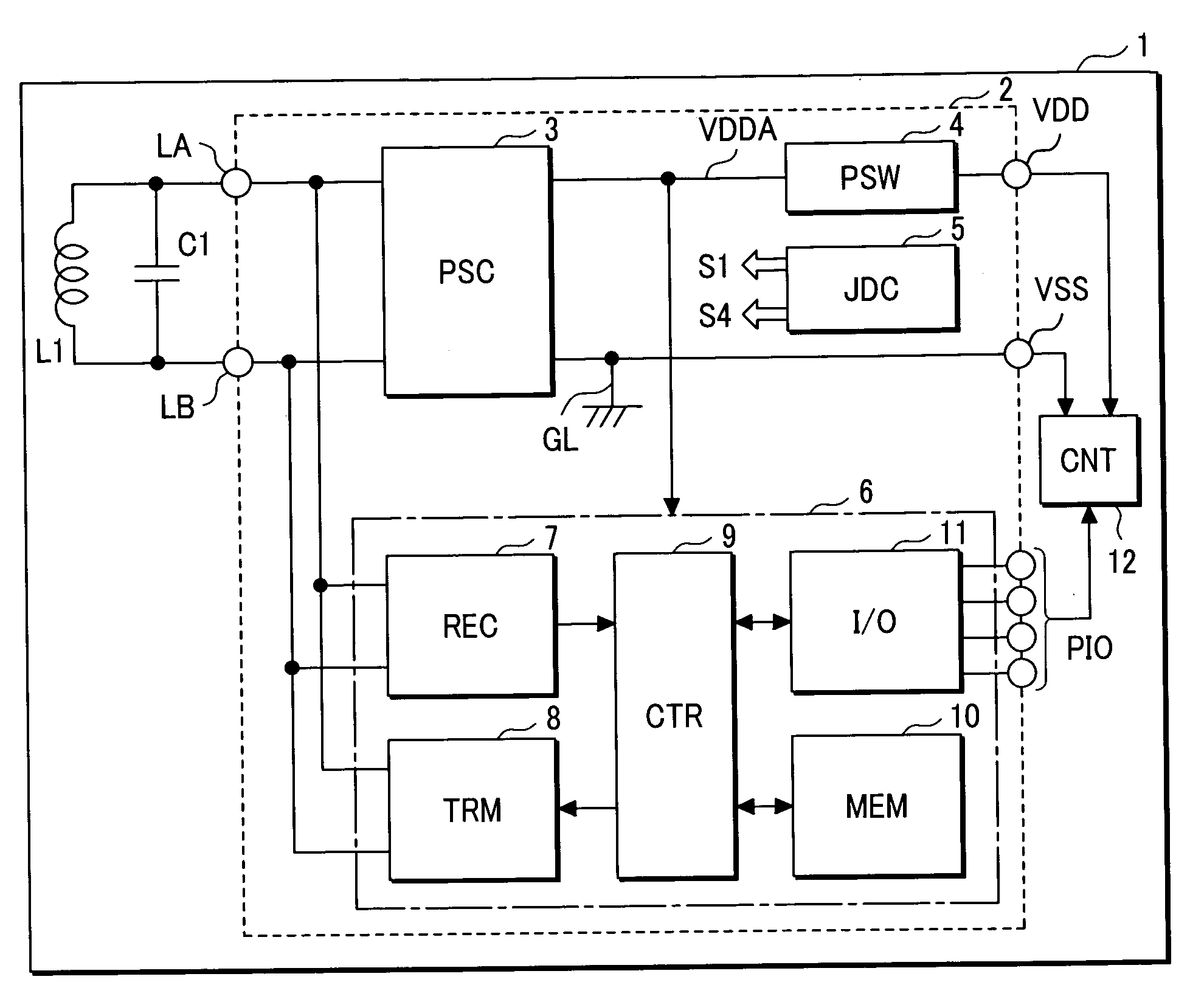

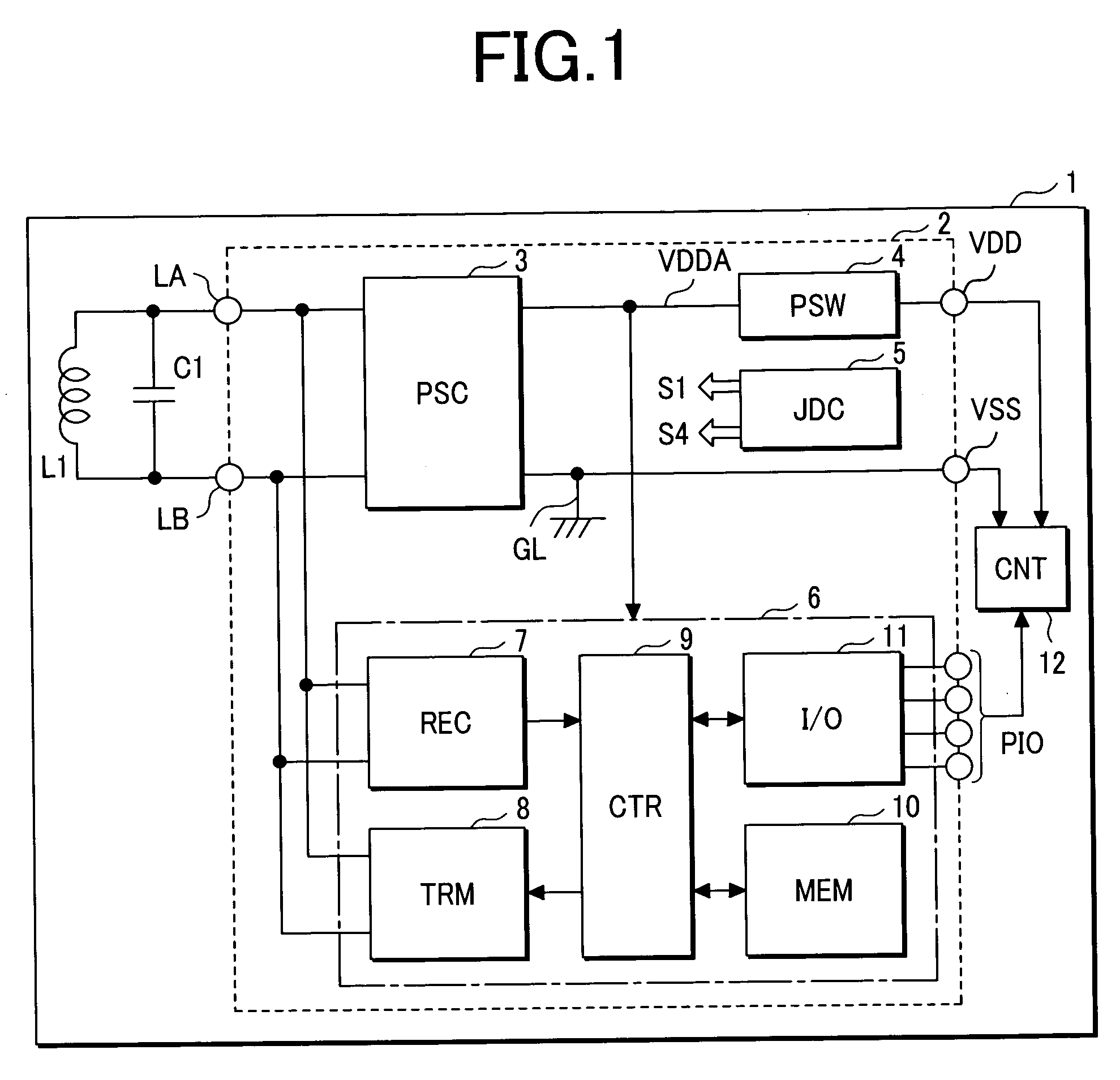

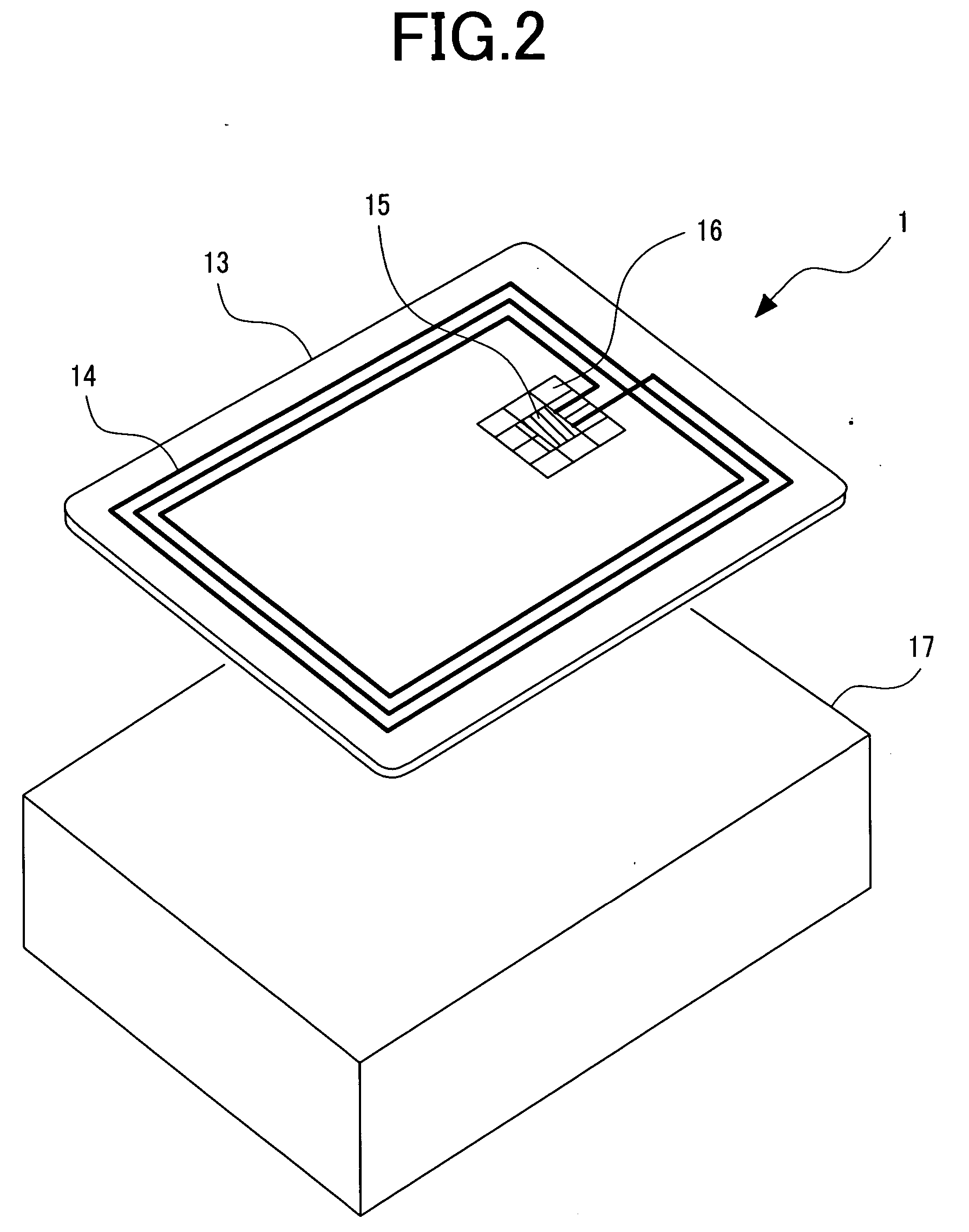

Semiconductor integrated circuit device and IC card equipped with the same

ActiveUS20070127185A1Reduce decreaseSmall sizeDigital data processing detailsHardware monitoringPower switchingSemiconductor

There is a need for turning off a transistor in a power supply switch circuit irrespective of relative potential relationship between a contact power supply terminal and an internal power supply line and making it possible to decrease an on-resistance of an MOS transistor without increasing the size of the MOS transistor constituting the power supply switch circuit. The power supply switch circuit is comprised of two PMOS transistors whose gate terminals connect with two pull-up circuits. A charge pump circuit generates a negative voltage and is connected to a pull-down circuit. The pull-down circuit is connected to the gate terminals in common. During a contactless operation, the pull-up circuit short-circuits one gate terminal to a contact power supply terminal VDD and the other gate terminal to an internal power supply line VDDA. During a contact operation, the pull-up circuit supplies both gate terminals with a negative voltage from the charge pump circuit.

Owner:RENESAS ELECTRONICS CORP

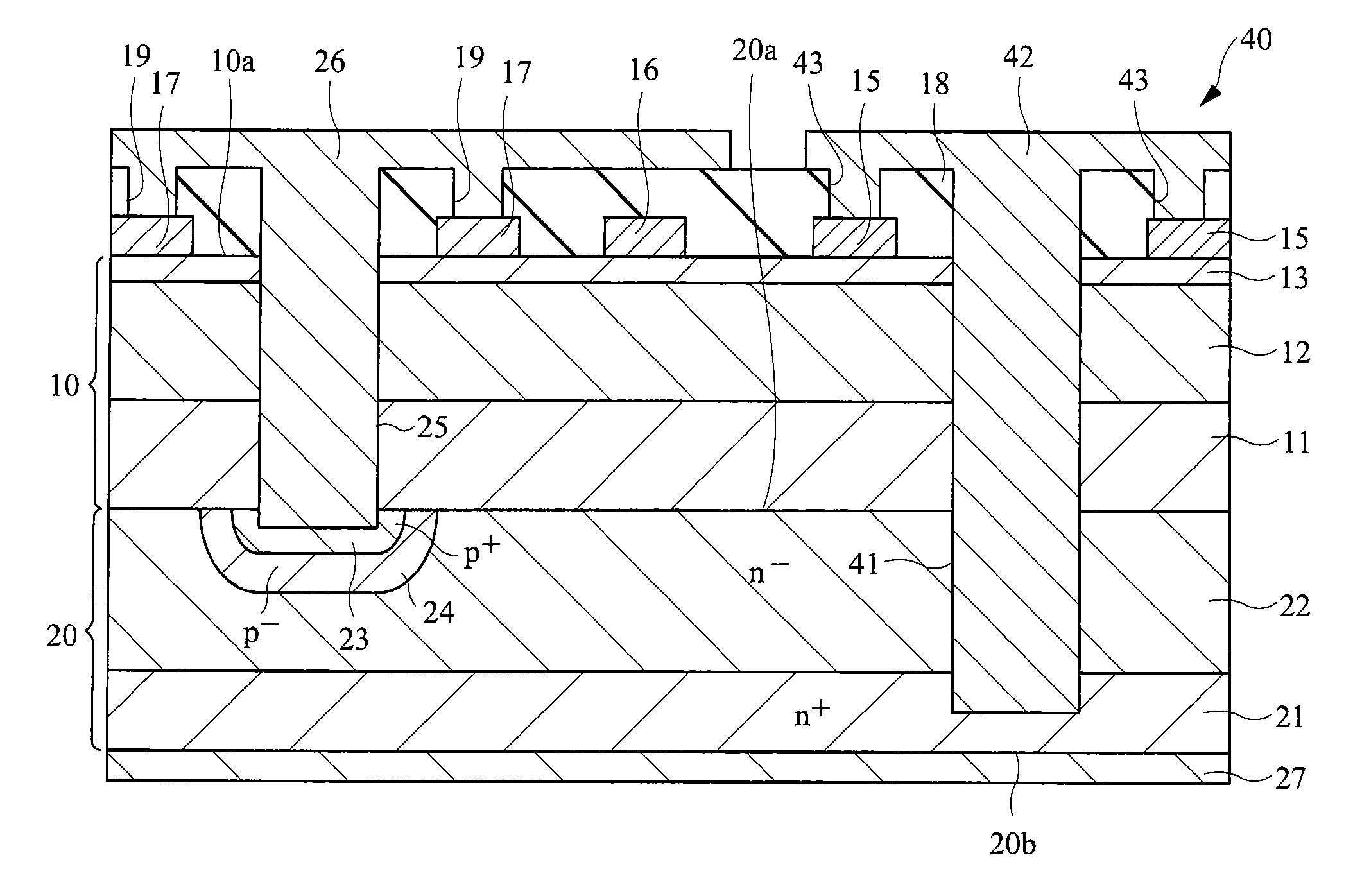

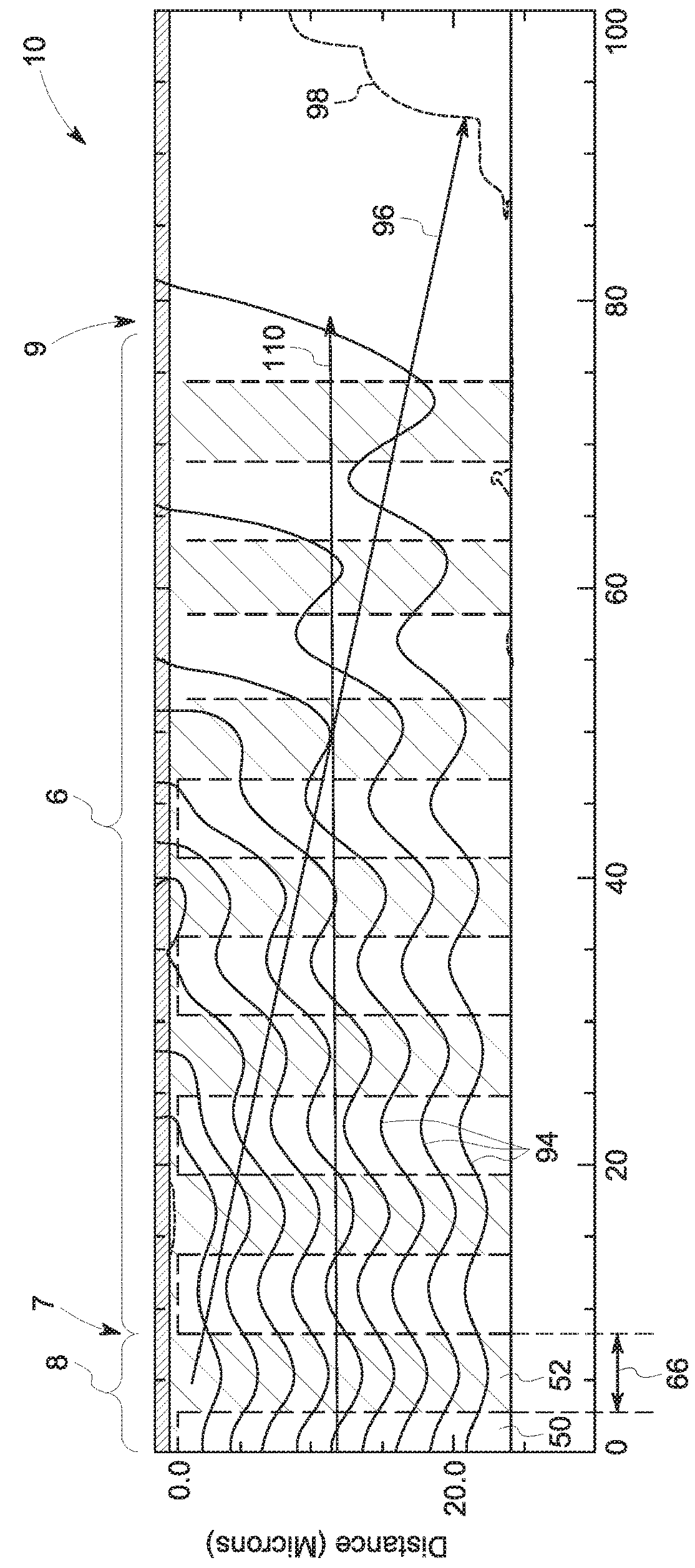

Semiconductor device structures and related processes

ActiveCN102007584AIncrease the on-resistanceImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETDopant

Improved highly reliable power RFP structures and fabrication and operation processes. The structure includes plurality of localized dopant concentrated zones beneath the trenches of RFPs, either floating or extending and merging with the body layer of the MOSFET or connecting with the source layer through a region of vertical doped region. This local dopant zone decreases the minority carrier injection efficiency of the body diode of the device and alters the electric field distribution during the body diode reverse recovery.

Owner:MAXPOWER SEMICON INC

Semiconductor device and power conversion device using the same

ActiveUS7838907B2Increased power lossIncrease the on-resistanceTransistorSolid-state devicesSemiconductor chipConductive materials

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and method of manufacturing the device

ActiveUS20110266554A1Lower on-resistanceReduce gas concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorDevice material

In a manufacturing method of a semiconductor device, first, a first semiconductor layer, a second semiconductor layer, and a p-type third semiconductor layer are sequentially epitaxially grown on a substrate. After that, the third semiconductor layer is selectively removed. Then, a fourth semiconductor layer is epitaxially grown on the second semiconductor layer. Then, a gate electrode is formed on the third semiconductor layer.

Owner:PANASONIC CORP

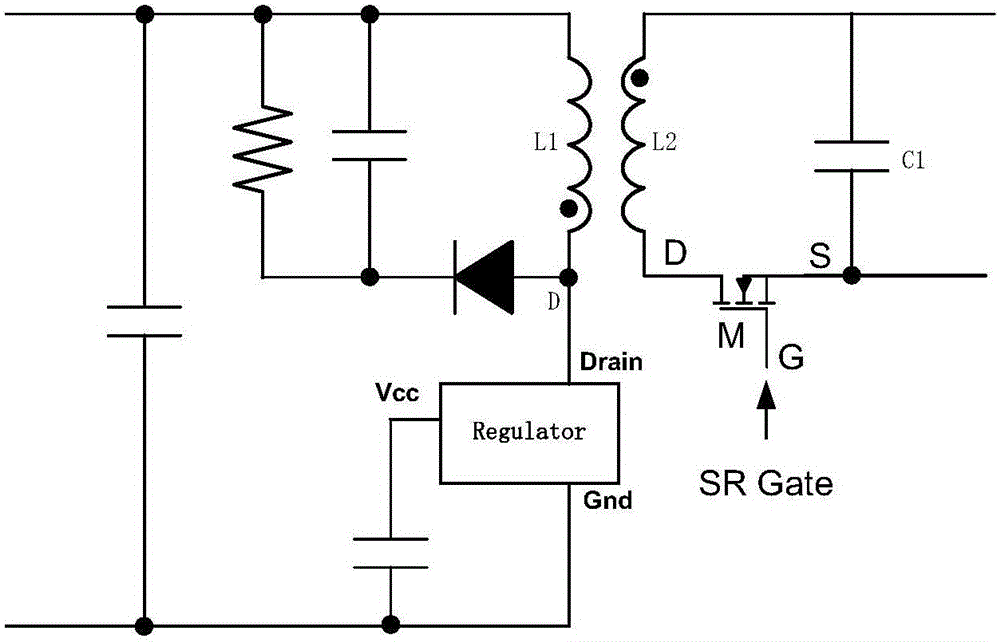

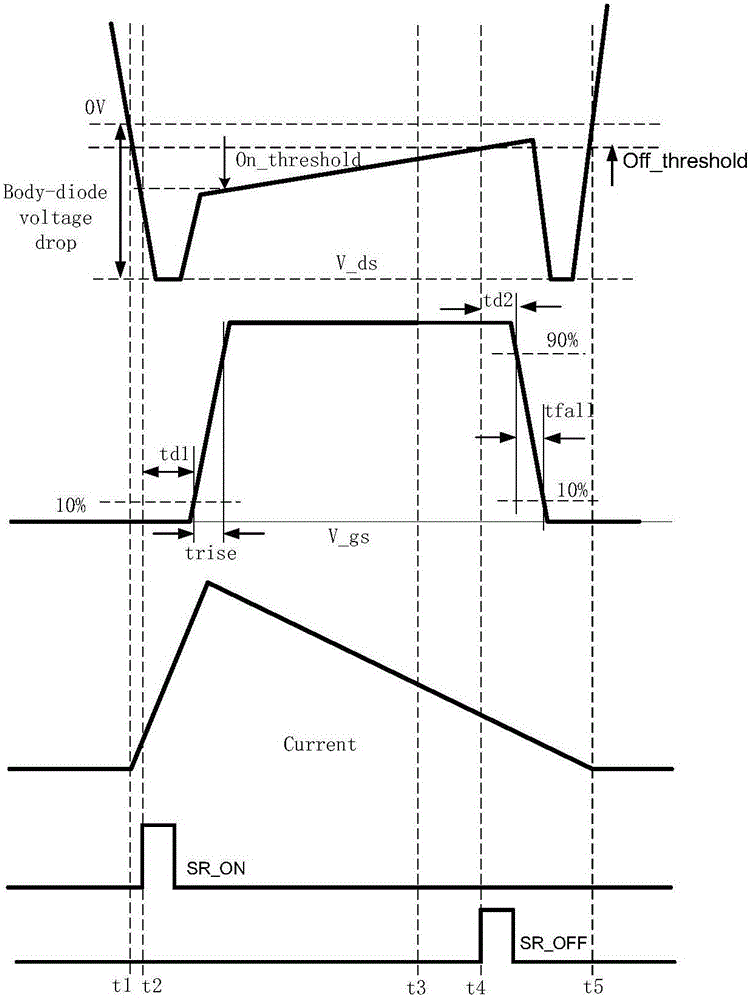

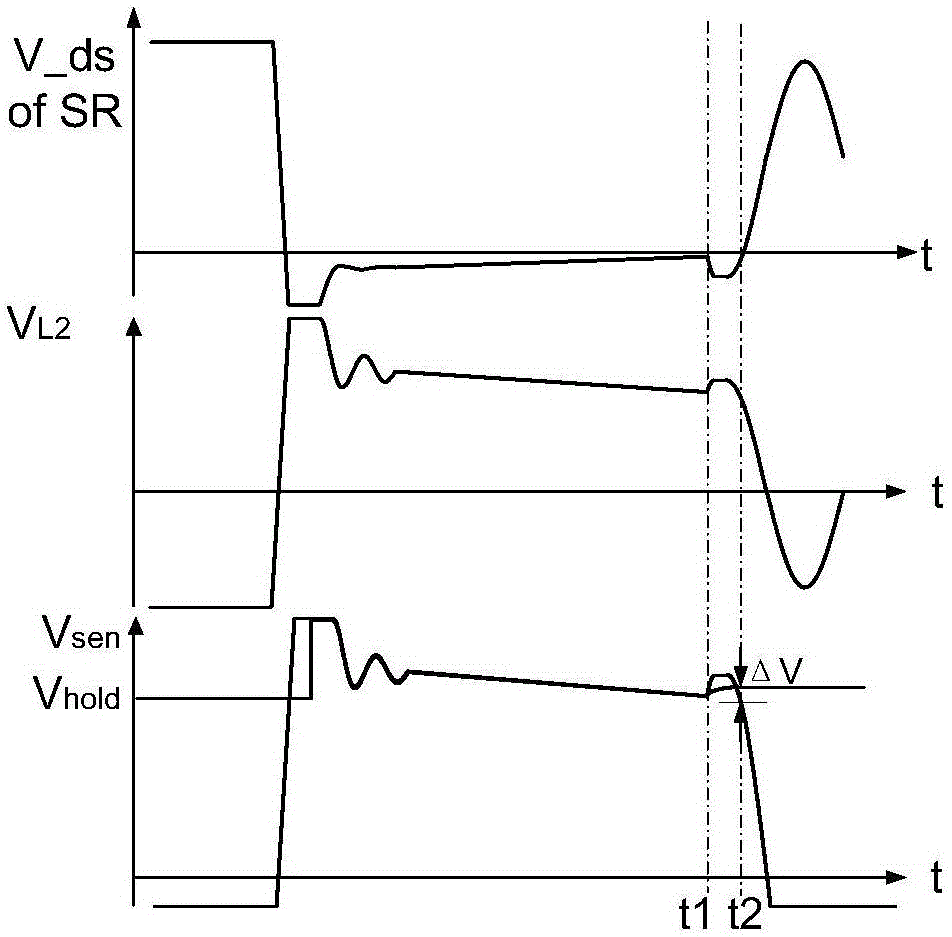

Synchronous rectification control method and circuit

ActiveCN105119505APrimary edge detection is accuratePrecise shutdownAc-dc conversionOff timeZero crossing

The invention discloses a synchronous rectification control method and circuit, and the method comprises a plurality of working steps. At a later working stage of synchronous rectification, a drain-source voltage rises to a closed-loop threshold voltage along with the decrease of a current, and a grid-source voltage starts to decrease, thereby enabling conduction resistance to increase. Through enabling a drain-source voltage of a synchronous rectification tube to be close to a reference voltage, the drain-source voltage remains equal to the closed-loop threshold voltage. Therefore, the drain-source voltage remains unchanged in a later period of synchronous rectification conduction, and primary side detection is enabled to be more accurate. Meanwhile, a grid-source switching-off threshold voltage is used for judging the switching-off time, thereby guaranteeing that the synchronous rectification tube is precisely switched off at a moment of current zero crossing.

Owner:SILERGY SEMICON TECH (HANGZHOU) CO LTD

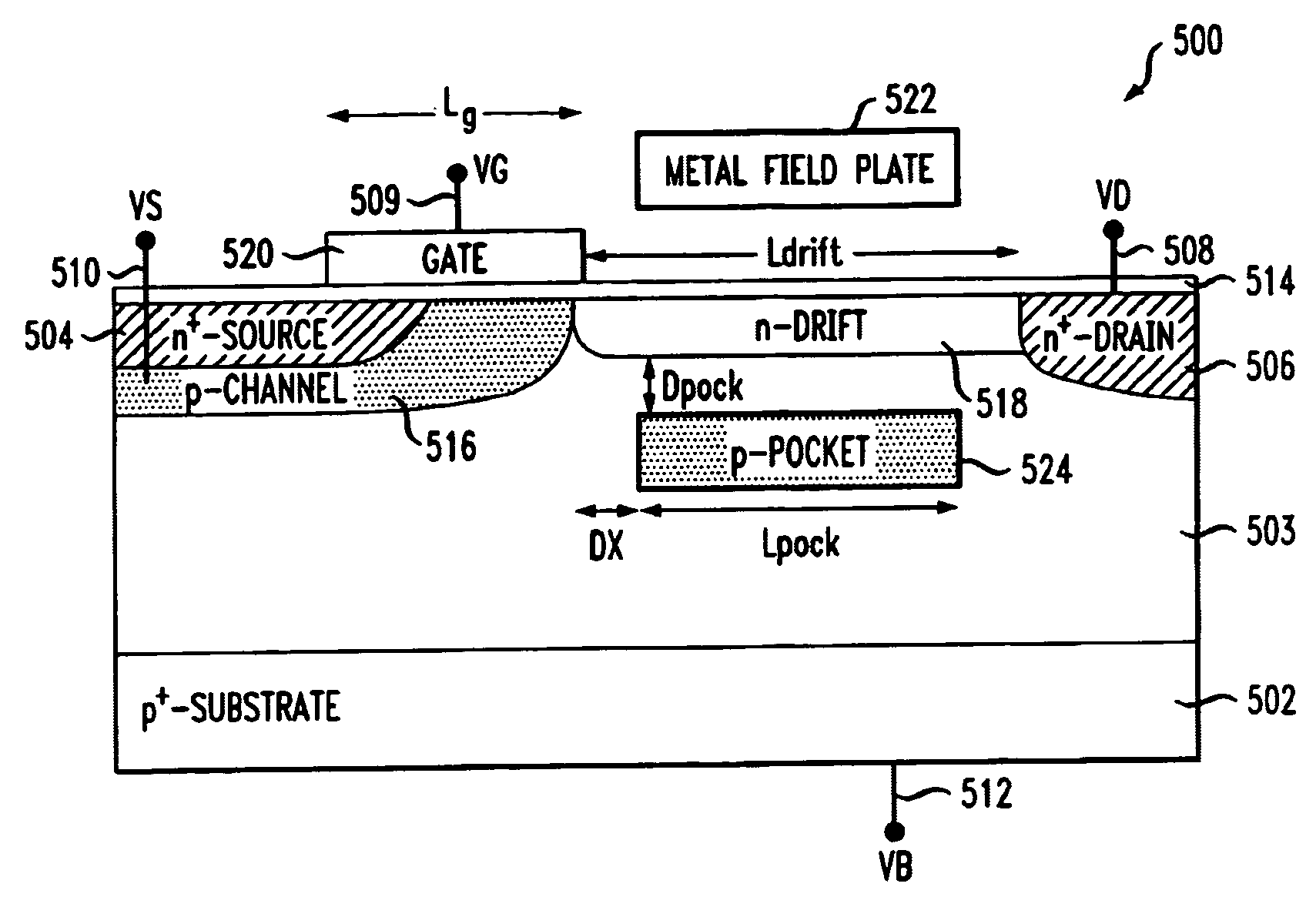

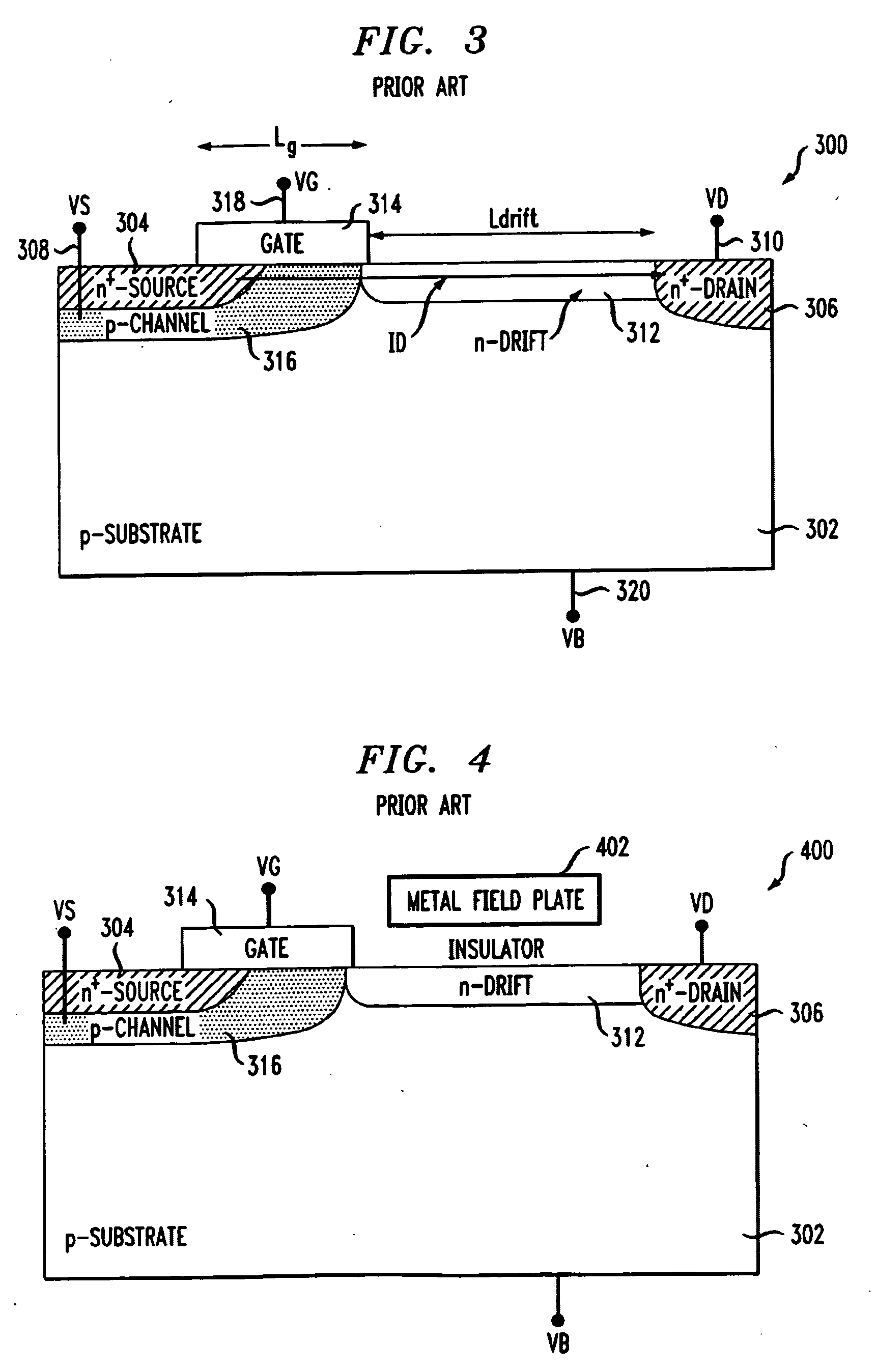

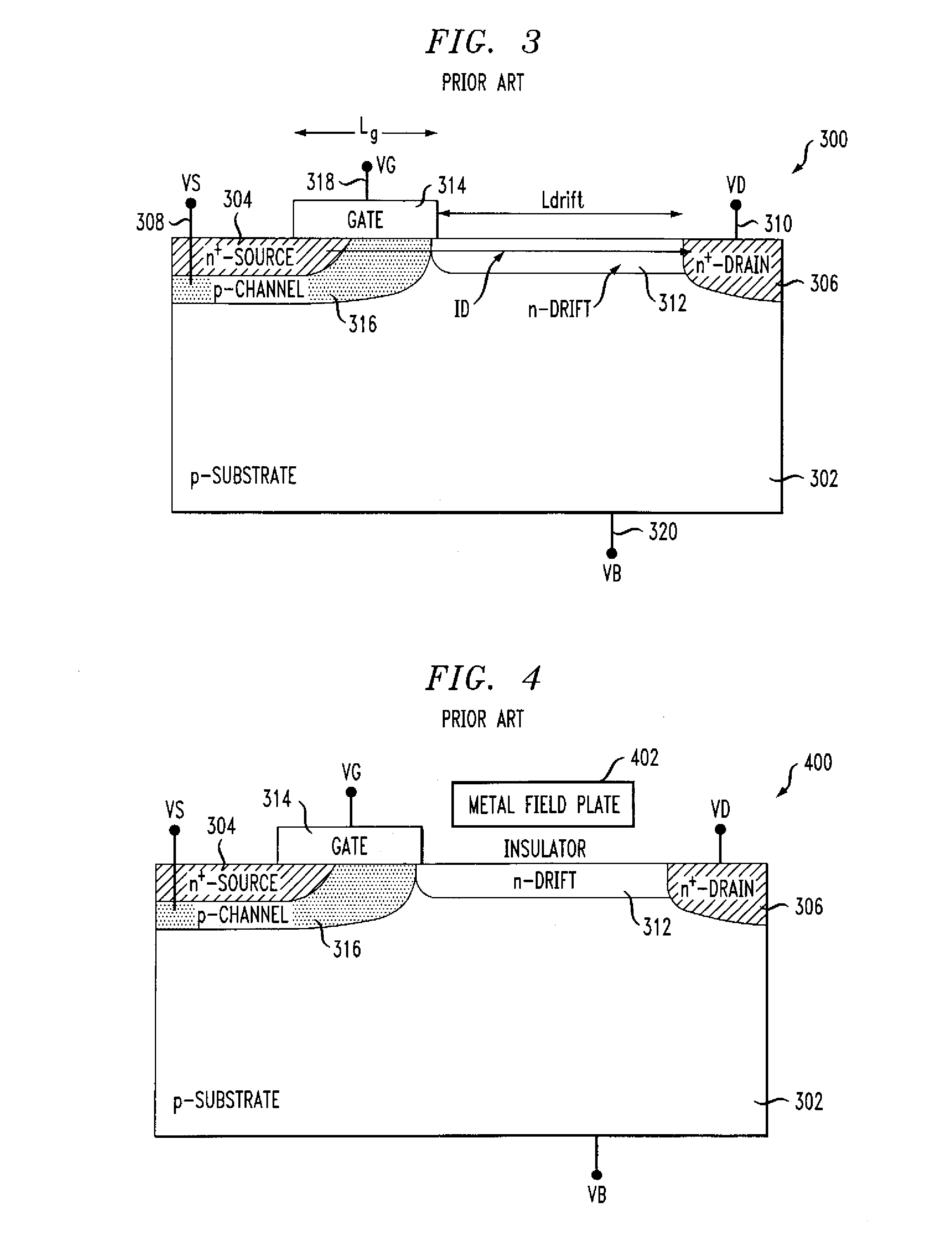

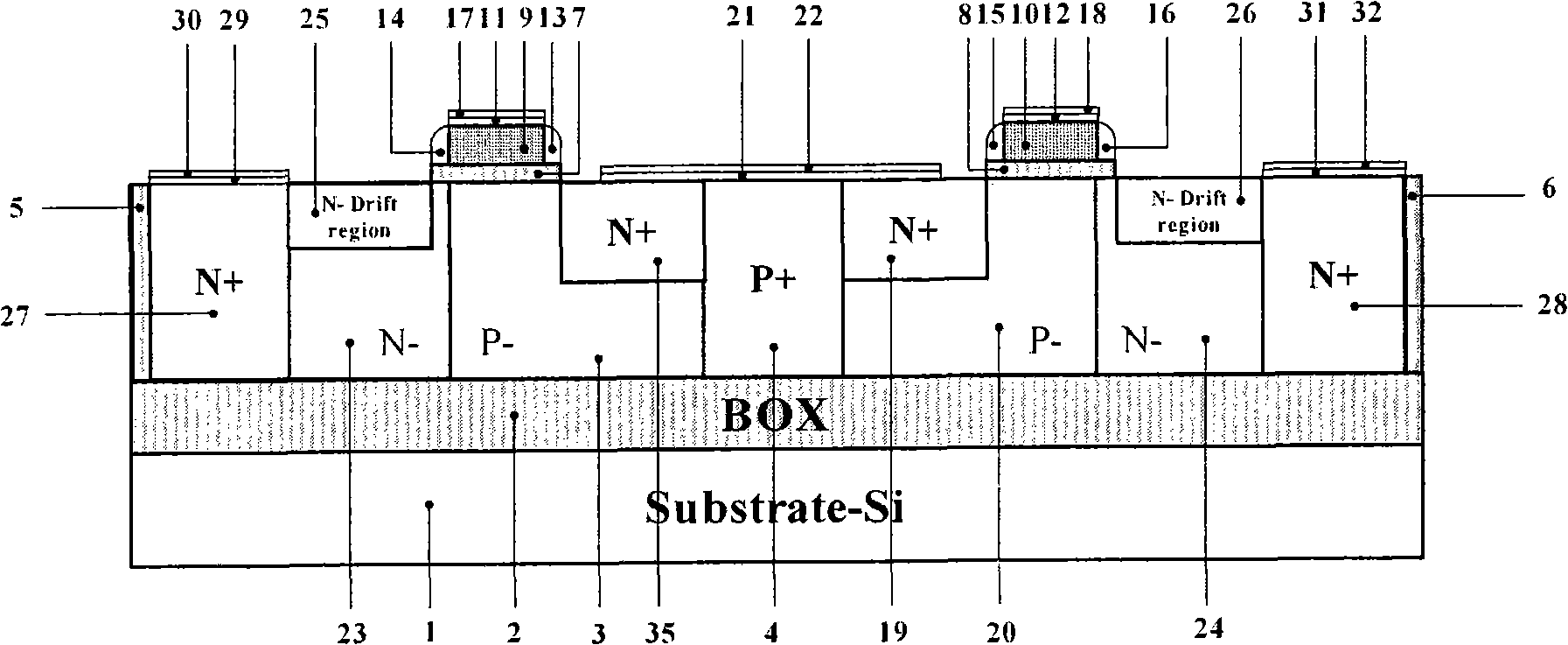

Radio frequency SOI LDMOS device with close body contact

InactiveCN101515586AIncrease working frequencyImprove breakdown voltageTransistorSemiconductor/solid-state device detailsRadio frequencyBody region

The invention relates to the field of a radio frequency power device, and discloses a radio frequency SOI LDMOS device with close body contact. The device comprises bottom layer silicon, an embedding oxidation layer, top layer silicon, a P region an N region, a gate oxidation layer, a polysilicon gate layer, a gate poly-silicide layer, a gate electrode, a silicon nitride side wall, an N drift region, a drain region, a drain region silicide layer, a drain electrode, a source region, a body contact region, a body region, a source region silicide layer and a source electrode. The radio frequency LDMOS device is manufactured on an SOI substrate, and forms the close body contact which is in short circuit with the source region by utilizing a heavily doped region in the same form as the P region; the source / body, a drain / body and the gate and the electrodes are interconnected by the silicide; a plurality of gate bars are connected in parallel in the forked mode so as to improve the driving capability of the device; a method for adjustment, back-gate injection, N region injection and N drift region injection, which is compatible with the CMOS process, is designed; and a method for hiding the silicide in the N drift region, which is compatible with the CMOS process, is designed.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

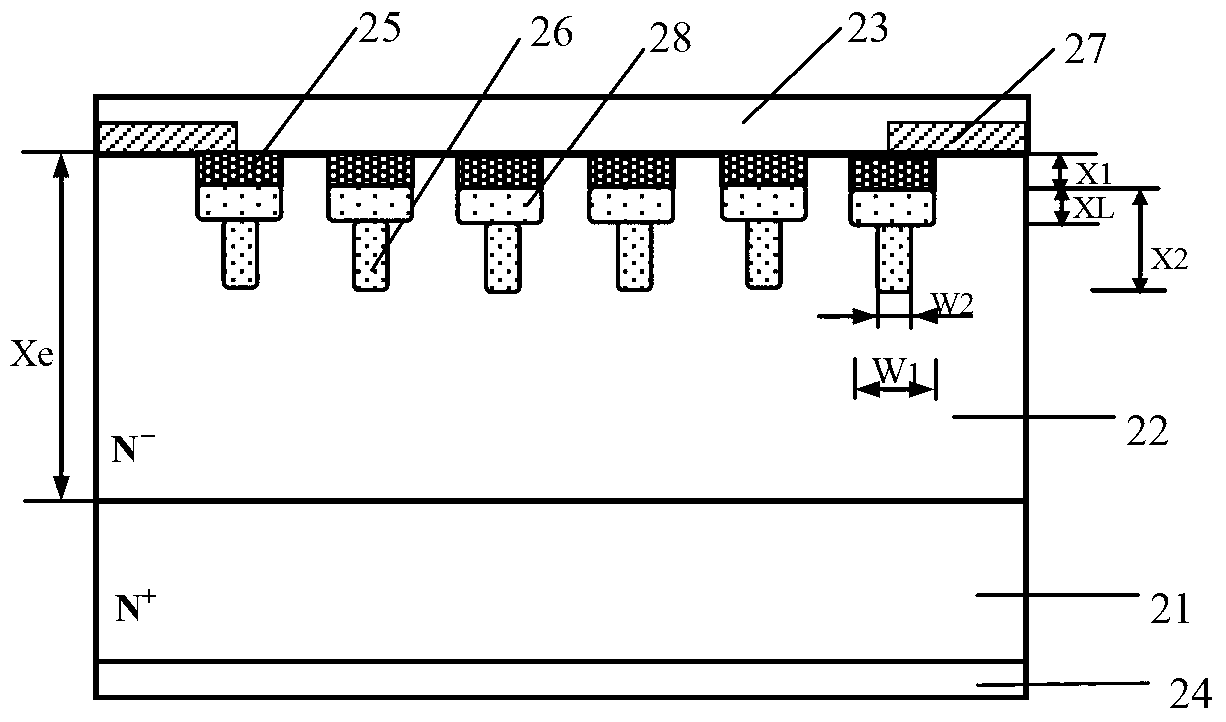

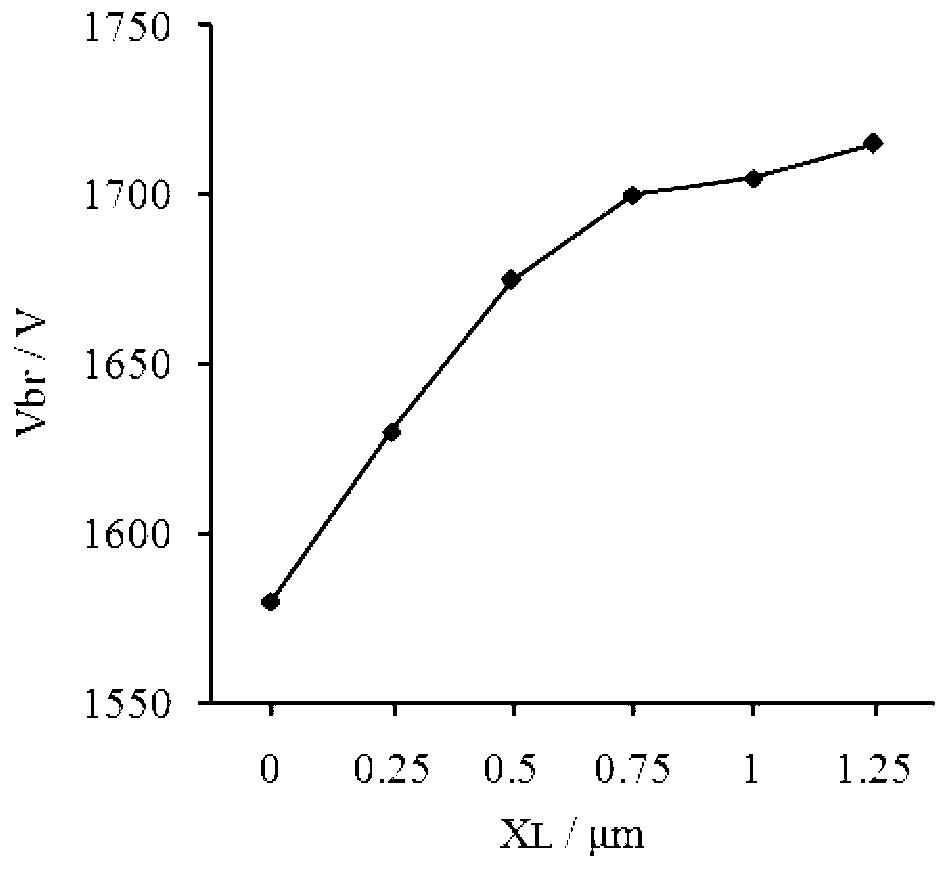

Shield gate trench MOSFET and manufacture method

ActiveCN107527948AReduce gate-to-drain capacitanceFast switching speedSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceTrench mosfet

The invention discloses a shield gate trench MOSFET. The gate trench includes a top trench and a bottom trench. A polysilicon gate is formed on both sides of the top trench. Source polysilicon is located in the middle of the gate trench and extends longitudinally through the entire gate trench. Channel regions are formed on semiconductor substrate surfaces between gate structures and source regions are formed on the surfaces of the channel regions. A polysilicon gate on one side of the top trench is connected to a gate formed by a front metal layer. A polysilicon gate on the other side of the top trench and the source regions are connected to a source through a second contact hole to form a structure for reducing the gate-drain capacitance of a device. The second contact hole reduces the distance between the gate trenches and reduces the on-resistance of the device and form an on-resistance compensation structure. The invention also discloses a method for manufacturing the shield gate trench MOSFET. The shield gate trench MOSFET can reduce the gate-drain capacitance, can increase the switching speed of the device, and can reduce the size of a unit device and improve an integration level.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

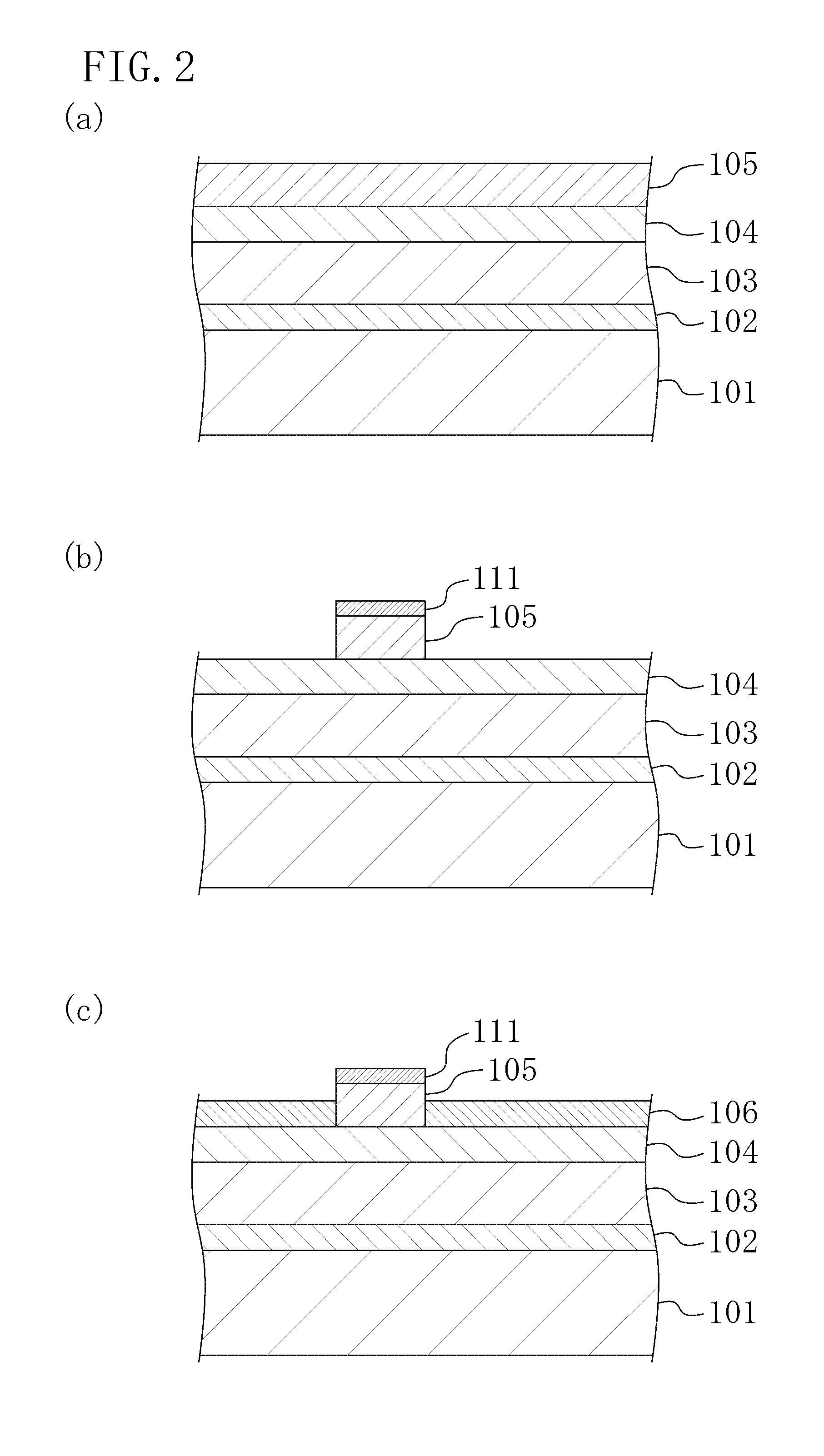

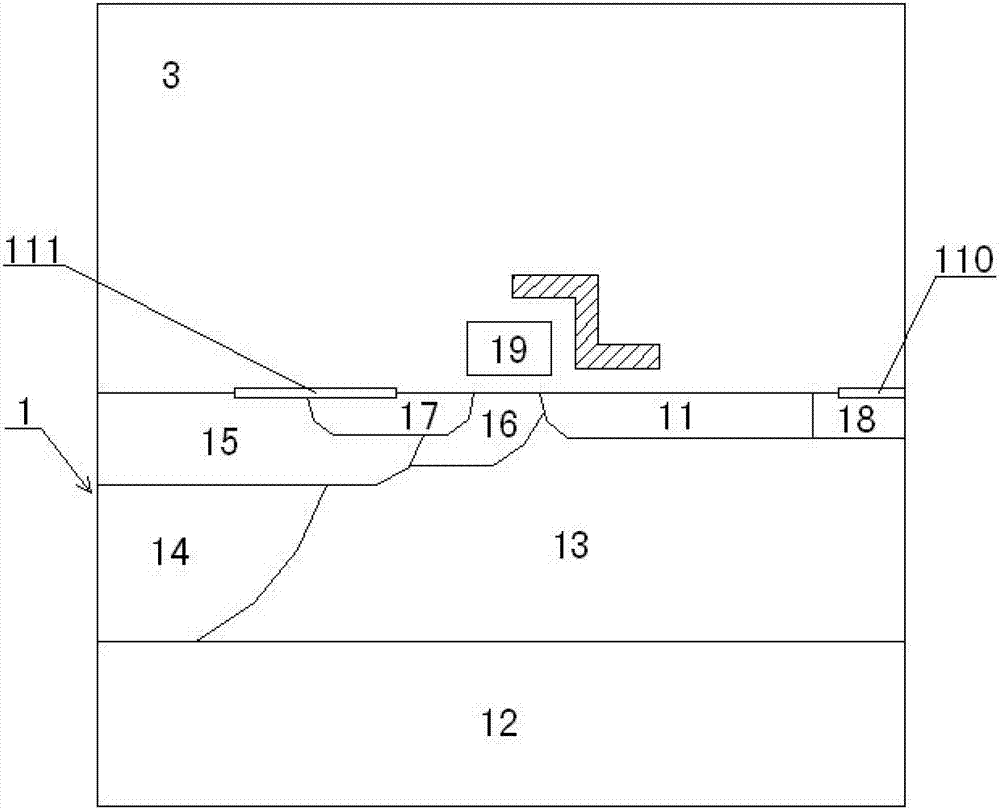

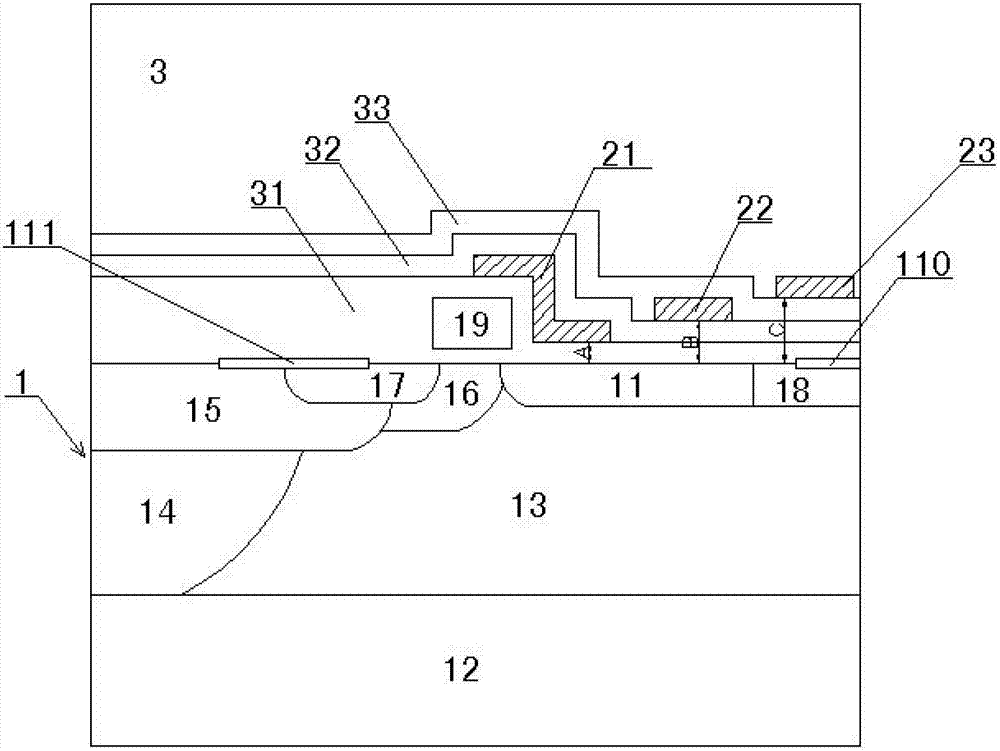

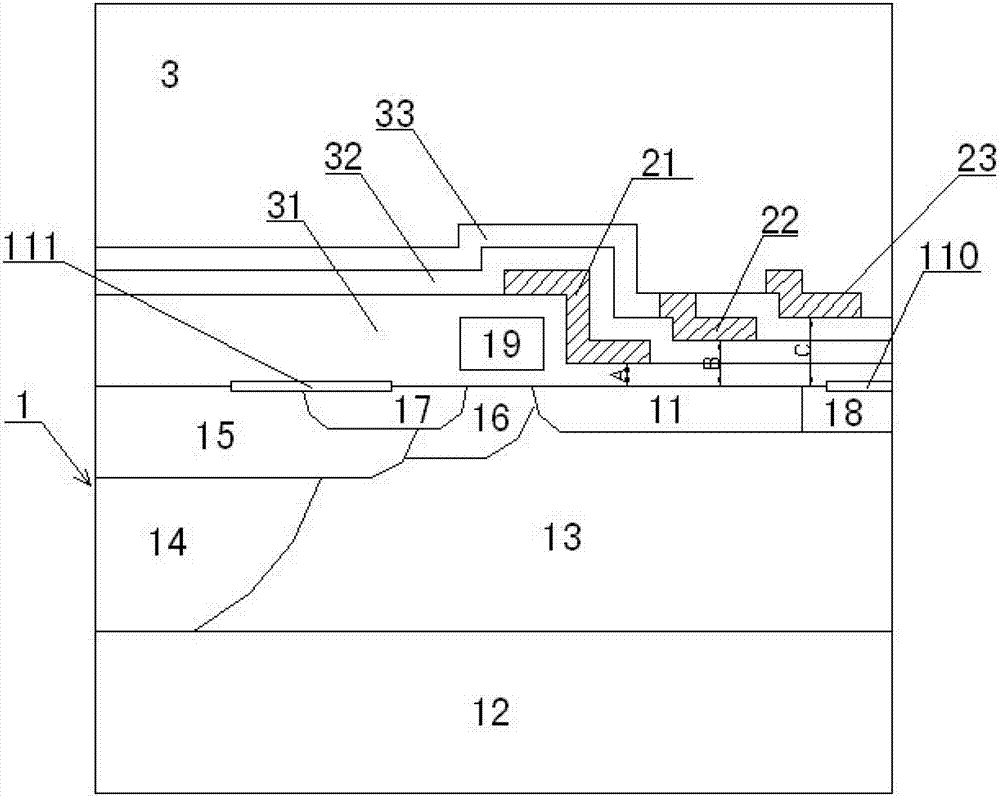

LDMOS device with stepped multiple discontinuous filed plate and manufacturing method for LDMOS device

ActiveCN102790086AIncrease the on-resistanceIncrease the doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSMedia layer

The invention discloses an LDMS (Laterally Diffused Metal Oxide Semiconductor) device with a stepped multiple discontinuous filed plate and a manufacturing method for the LDMS device. The LDMS device comprises a semiconductor body, wherein the semiconductor body comprises a semiconductor substrate region, a semiconductor epitaxial layer and a semiconductor medium layer which are sequentially arranged from bottom to top; a grid extending along a channel and at least two field plates are arranged in the semiconductor medium layer; at least two field plates are sequentially arranged in a horizontal direction from the grid to a leakage-drift region; a first field plate adjacent to the grid horizontally extends in the leakage-drift region; field plates which are not adjacent to the grid are respectively in a horizontal strip shape; the distance between every two field plates is greater than zero; the distance between a second field plate adjacent to the first field plate and the leakage-drift region is greater than the distance between a horizontally-extending part of the first field plate and the leakage-drift region; and the distance between other horizontal strip field plates and the leakage-drift region is gradually increased. According to the LDMS device disclosed by the invention, the contradiction between source and drain breakdown voltage and the optimal requirement of a conducting resistor is relieved and the performance of the LDMS device is improved.

Owner:INNOGRATION SUZHOU

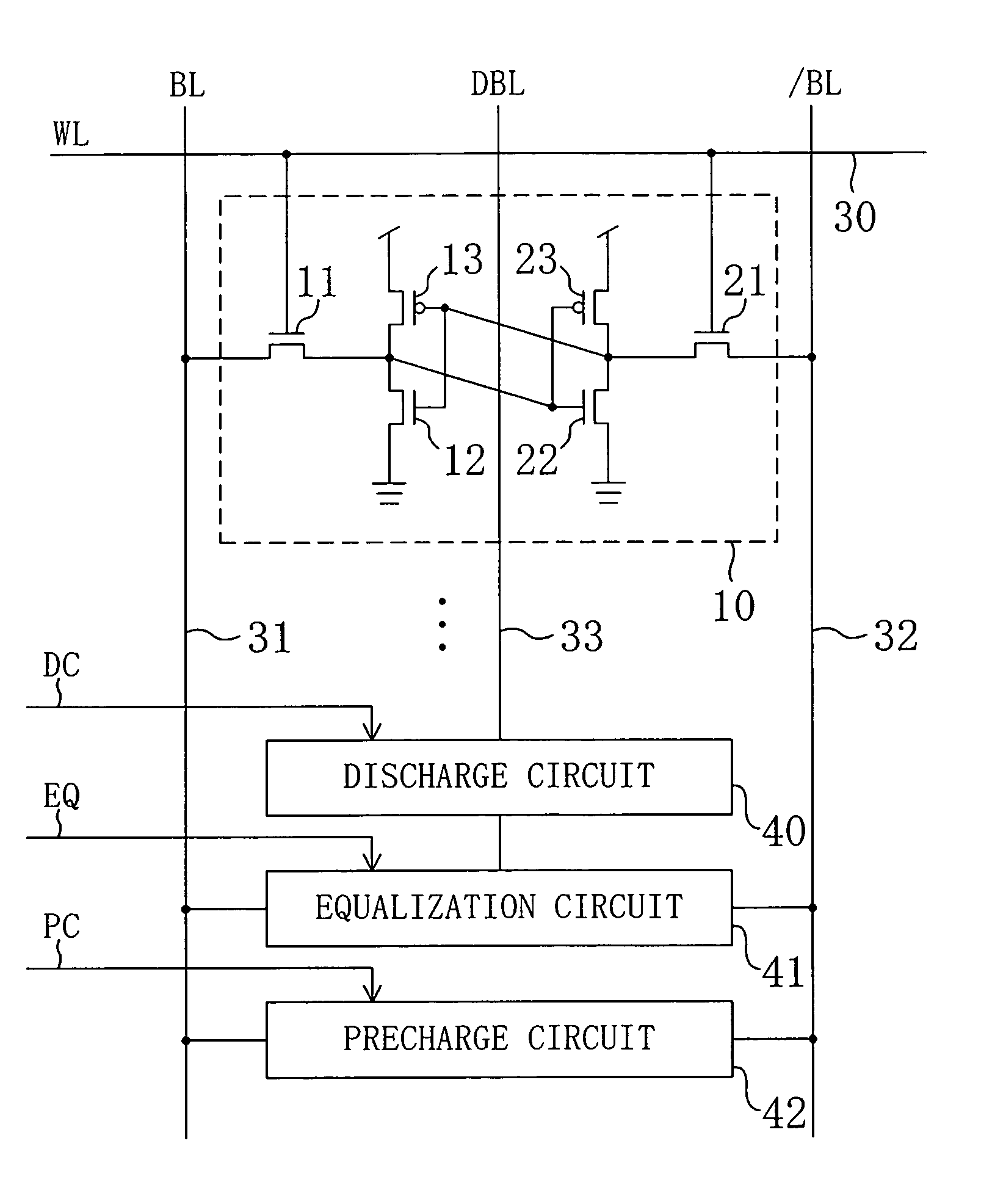

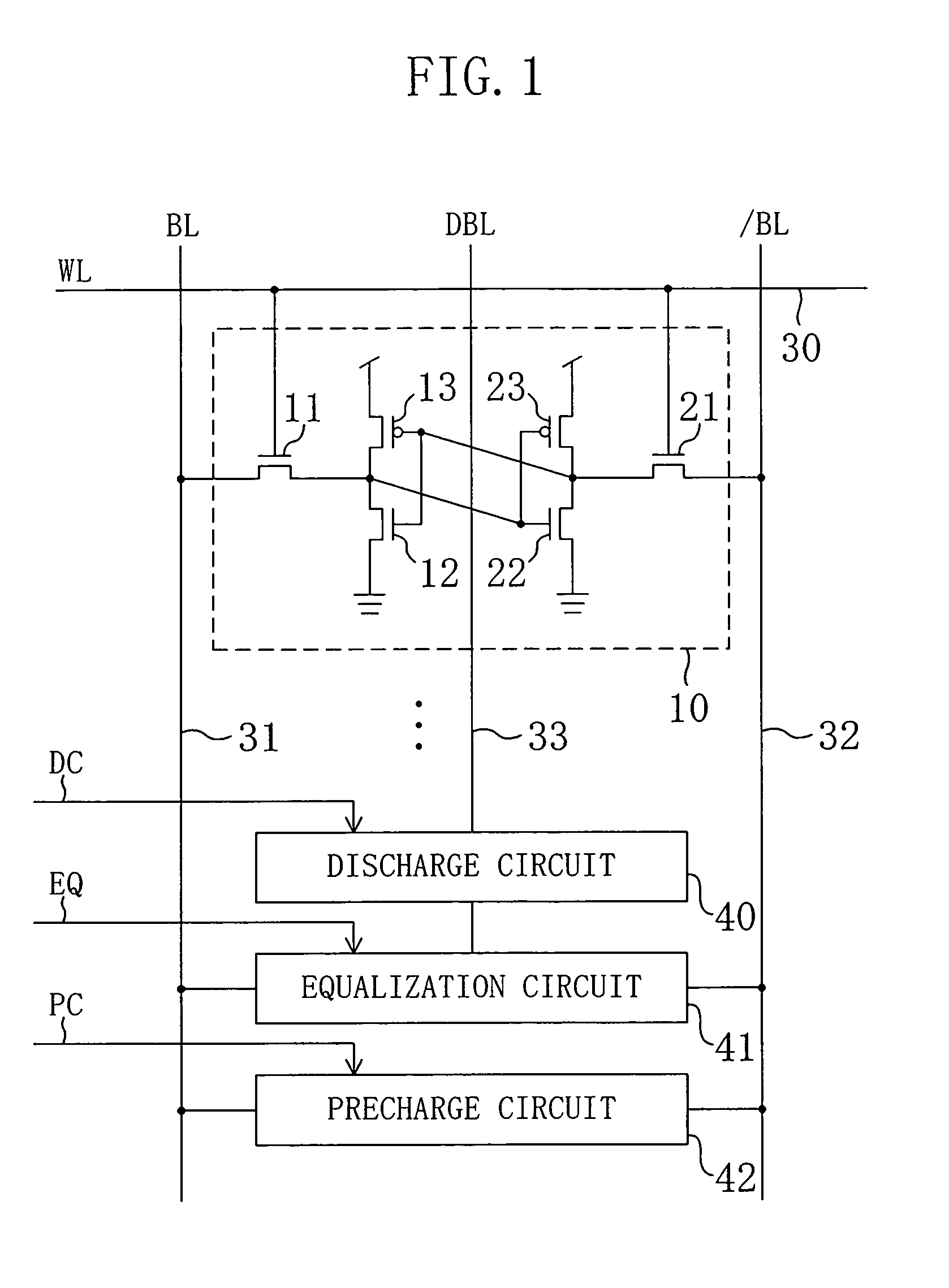

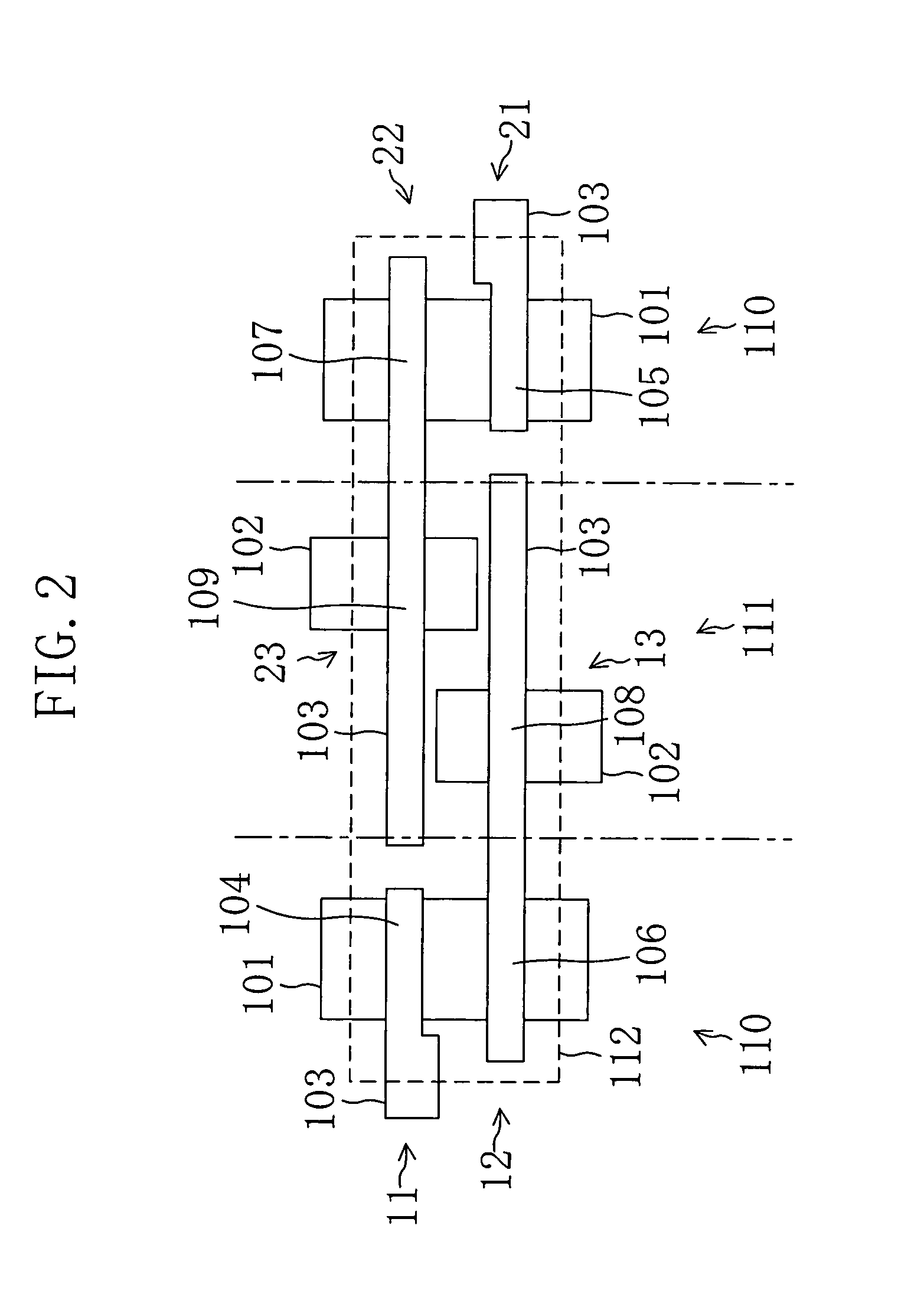

Semiconductor memory device

InactiveUS6982899B2Reduce voltageAvoid failureSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringStatic noise margin

A dummy bit line is provided between a pair of bit lines. The pair of bit lines is set at a power supply voltage and the dummy bit line is set at a ground voltage, and then the pair of bit lines and the dummy bit line are equalized. When a word line is activated in subsequent read operation, the pair of bit lines is at an intermediate potential lower than the power supply voltage, so that an apparent current drive capability of an access transistor decreases, and the static noise margin of a memory cell increases.

Owner:PANASONIC CORP

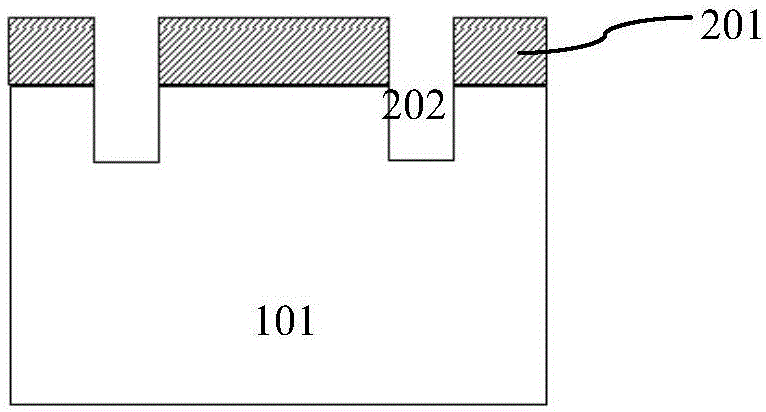

Semiconductor device and method for manufacturing same

ActiveUS20150333175A1Reduce electric field concentrationIncrease the on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesImpuritySemiconductor

A method for manufacturing a semiconductor device includes the steps of: forming, on a principal face of a substrate, a semiconductor layer including a first semiconductor region of a first conductivity type; and forming, in the semiconductor layer, a trench having a bottom located in the first semiconductor region. The method further includes a step of forming a trench bottom impurity region being of a second conductivity type and covering the bottom of the trench by performing annealing to cause part of the semiconductor layer corresponding to an upper corner portion of the trench to move to be placed on the bottom of the trench.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

Method for manufacturing a semiconductor device with a trench termination

ActiveUS6921699B2High current capabilityEfficient power supplySemiconductor/solid-state device manufacturingSemiconductor devicesOxideSemiconductor

A process for manufacturing a semiconductor device of the trench variety with reduced feature sizes and improved characteristics which process includes forming a termination structure having a field oxide disposed in a recess below the surface of the semiconductor die in which the active elements of the device are formed, and forming source regions after the major thermal steps have been performed.

Owner:INFINEON TECH AMERICAS

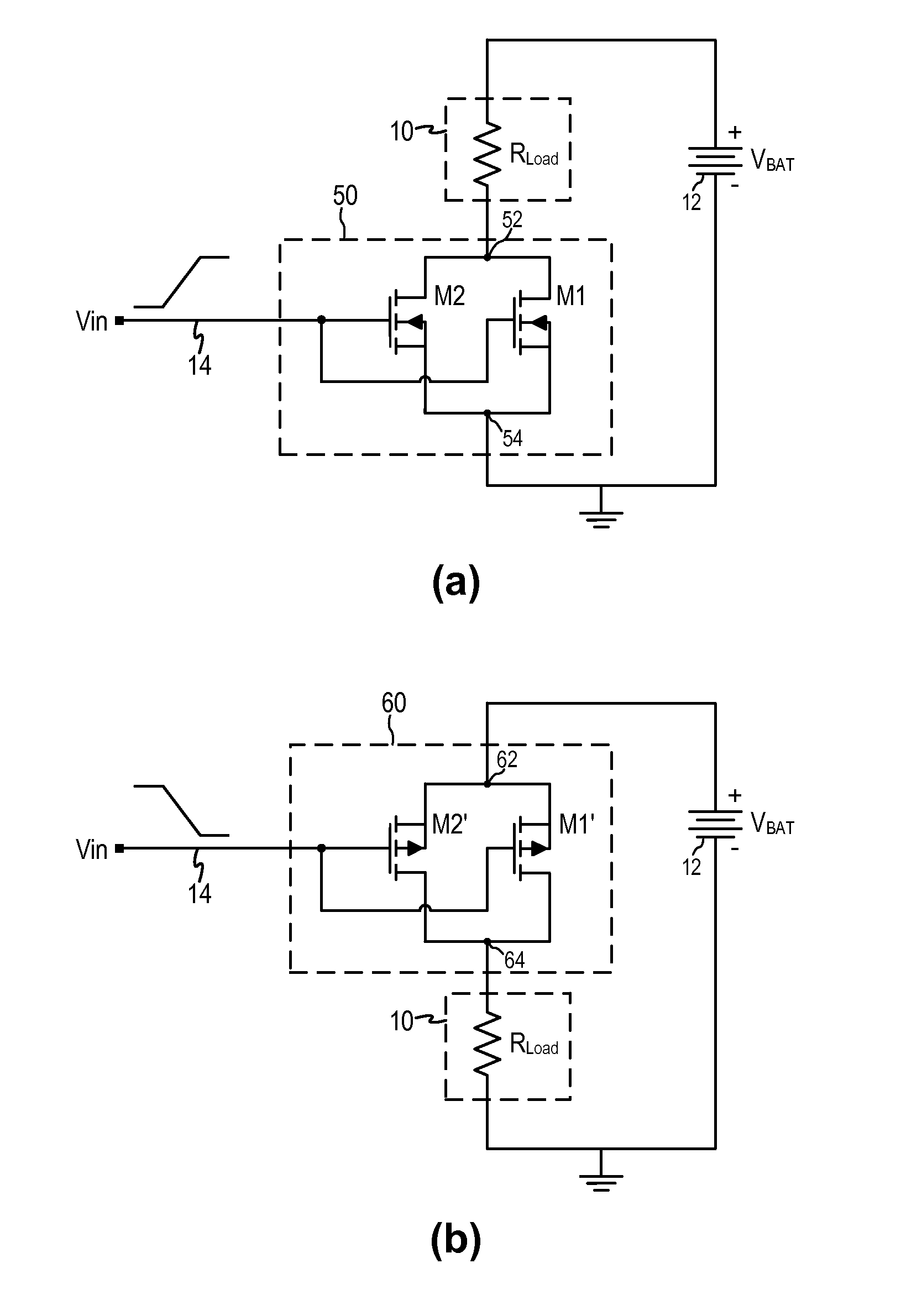

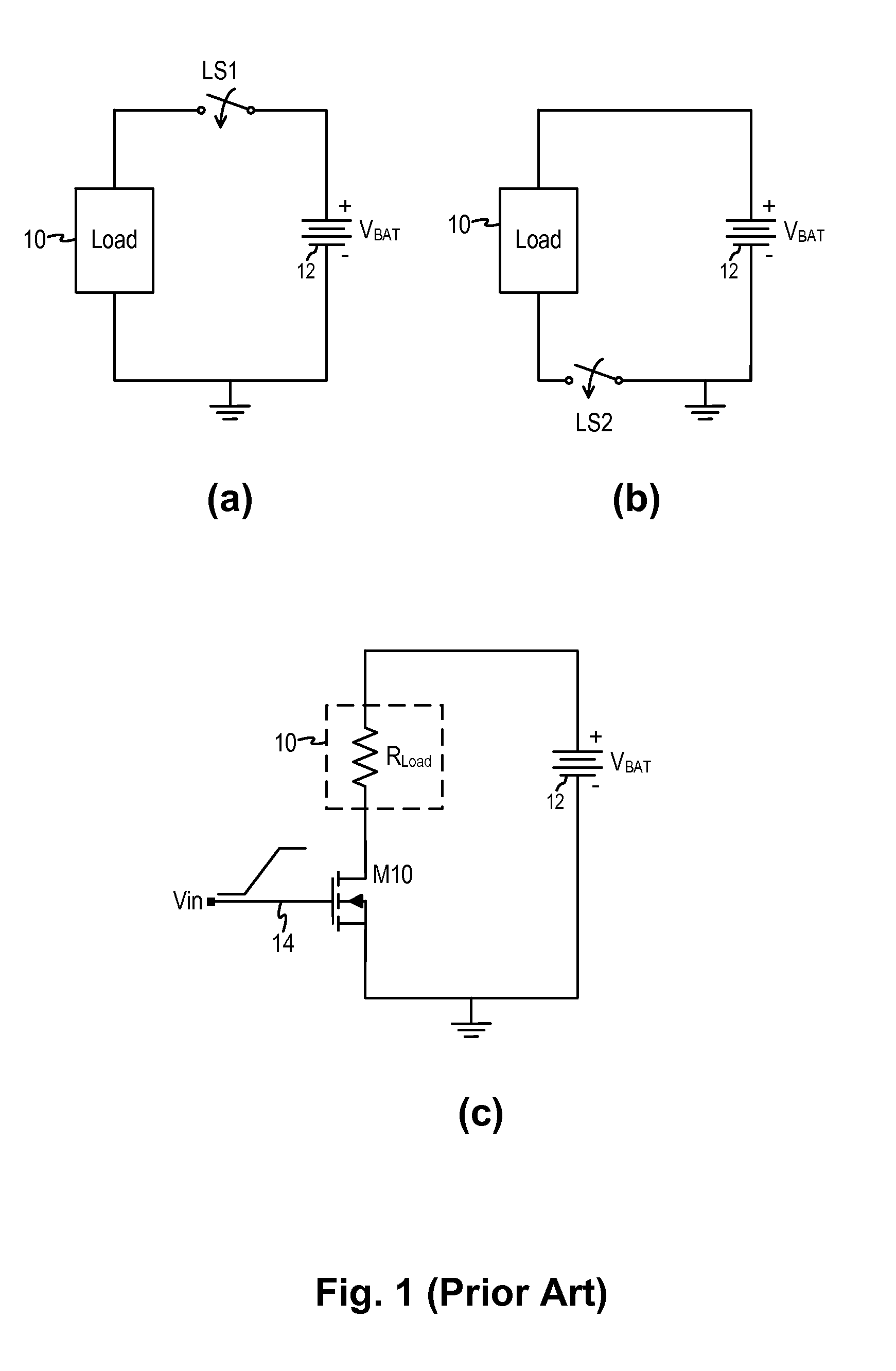

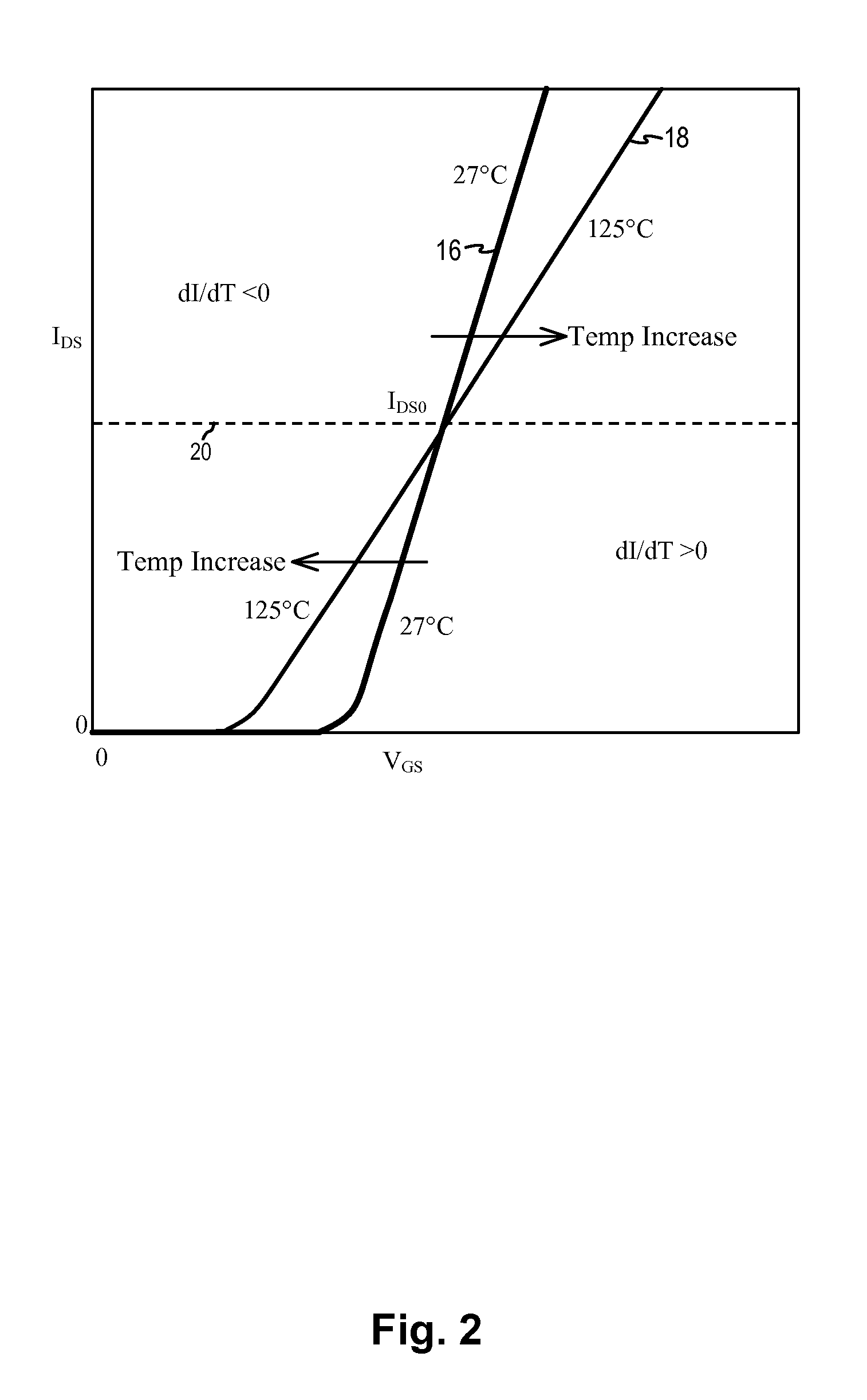

Mosfet switch circuit for slow switching application

A switch circuit includes a first MOS transistor and a second MOS transistor of a same conductivity type connected in parallel between a first terminal and a second terminal. The first and second MOS transistors have respective gate terminals coupled to the control terminal to receive a control signal to turn the switch circuit on or off where the control signal transitions from a first voltage level to a second voltage level at a slow rate of change. The first MOS transistor has a first threshold voltage and the second MOS transistor has a second threshold voltage where the first threshold voltage is less than the second threshold voltage

Owner:ALPHA & OMEGA SEMICON INC

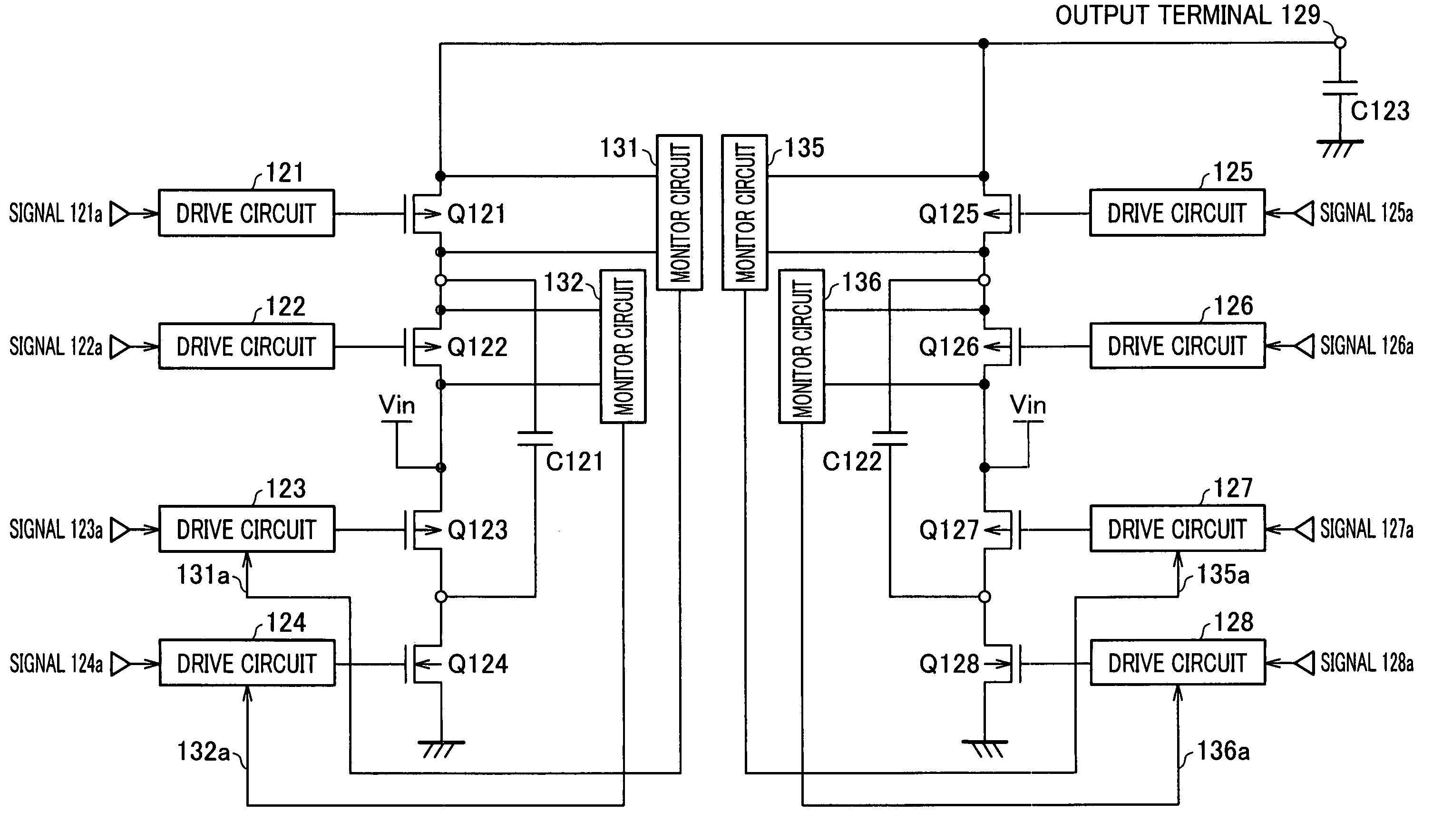

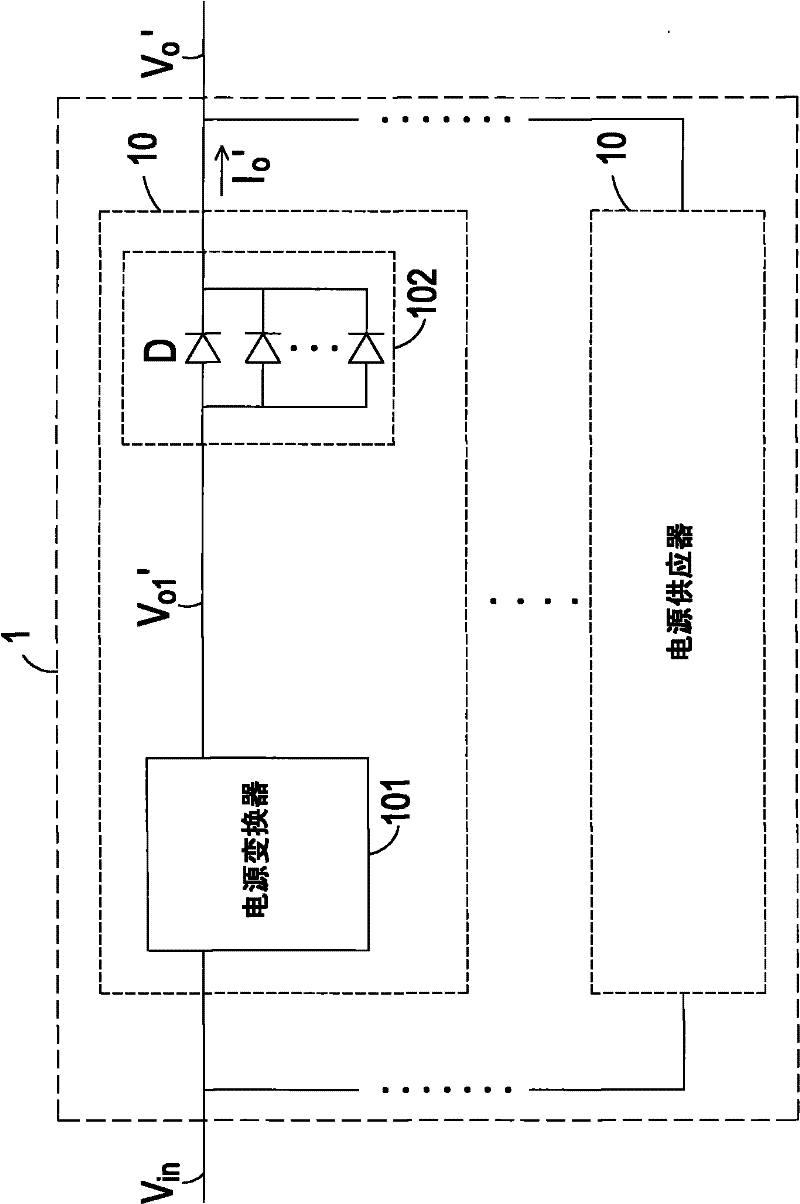

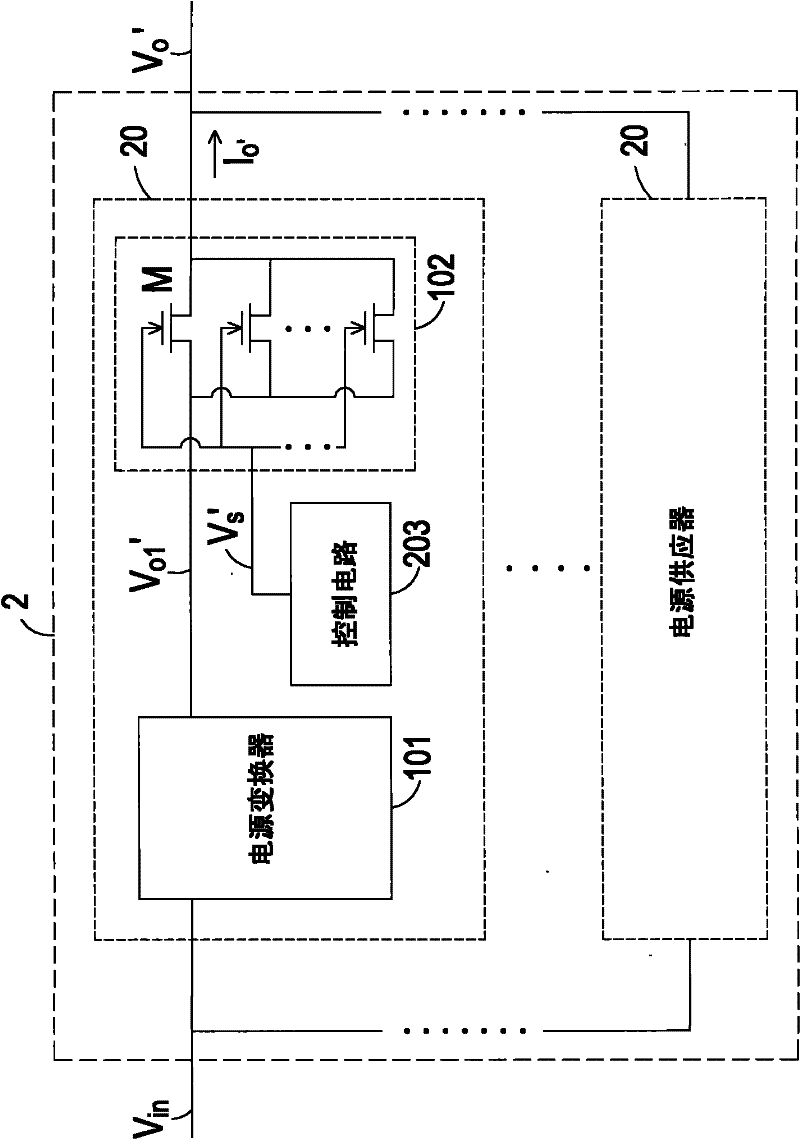

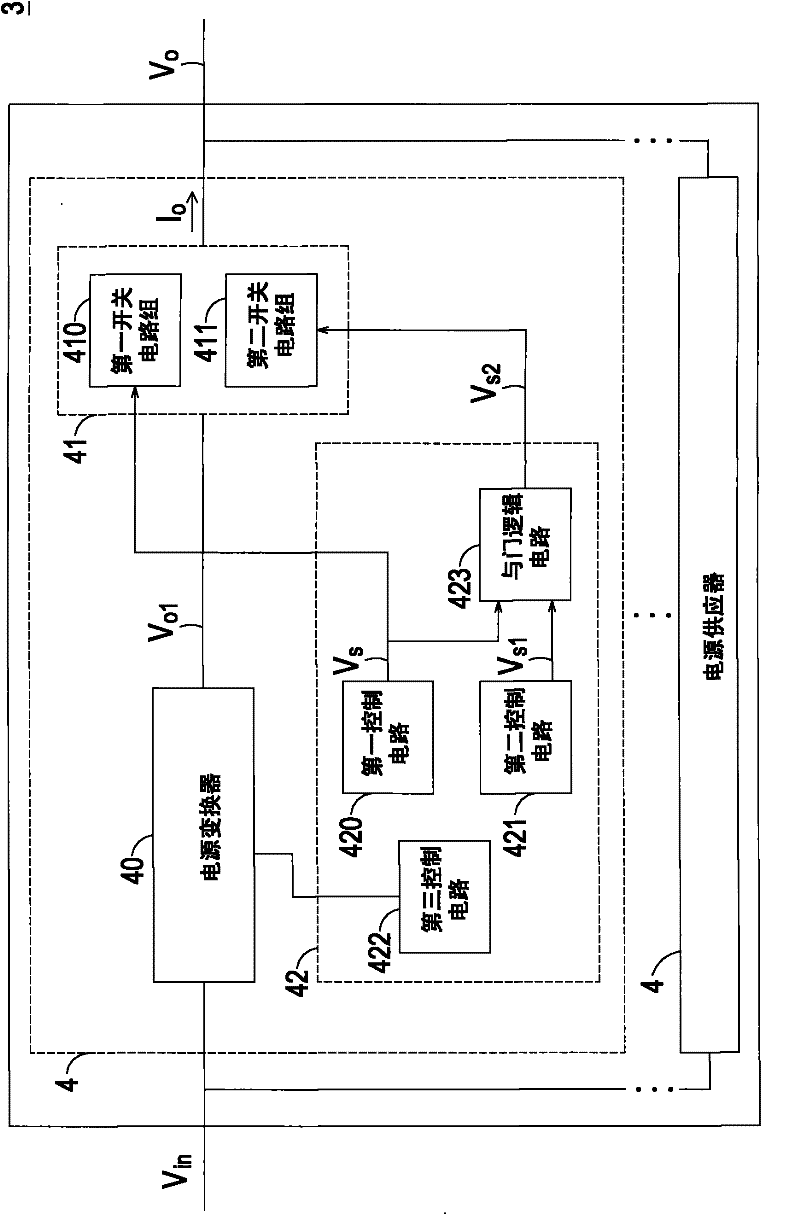

Power supply and power supply system with multiple power supplies

ActiveCN102457047AReduce manufacturing costIncrease the on-resistanceEmergency protective circuit arrangementsEmergency power supply arrangementsElectricityPower flow

The invention discloses a power supply and a power supply system with multiple power supplies. The power supply is used for receiving an electric energy of an input voltage and generating an output voltage and an output current. The power supply comprises a power convertor, an output protecting circuit and a control unit, wherein the power convertor is used for receiving the electric energy of the input voltage and generating an inner output voltage; the output protecting circuit is connected with an output end of the power convertor and comprises a plurality of switch circuit sets in parallel connection; the output protecting circuit is used for limiting a current direction of the output current under an switch-on / off action of the switch circuit sets; the control unit is electrically connected with the output protecting circuit; and the control unit is used for outputting a plurality of control signals for respectively controlling the switch circuit sets, wherein at least two control signals are included and are used for respectively controlling at least two switch circuit sets to switch off at different moments. The power supply provided by the invention can be used for increasing power supply efficiency under the normal running of the power supply and the production cost is lower.

Owner:DELTA ELECTRONICS INC

Semiconductor device with lifetime killers and method of manufacturing the same

ActiveUS20180233564A1Easy for current to flowIncreases degree of variation in conductivityTransistorSemiconductor/solid-state device manufacturingElectrical conductorP–n junction

A semiconductor device includes a semiconductor substrate, a first semiconductor layer of a first conductivity type, a second semiconductor layer of a second conductivity type, a first semiconductor region of the first conductivity type, a second semiconductor region of the second conductivity type, a gate insulating film, and a gate electrode. The semiconductor device further includes, in a region of the first semiconductor layer across or adjacent to a p-n junction therein that does not overlap the second semiconductor region in a plan view except lateral edges thereof, a lifetime killer region having lifetime killers implanted therein.

Owner:FUJI ELECTRIC CO LTD

High voltage and low on-resistance LDMOS transistor having radiation structure and isolation effect

InactiveUS20060033156A1Avoid failureIncrease the on-resistanceSemiconductor devicesEngineeringHigh pressure

A high voltage LDMOS transistor according to the present invention includes at least one P-field block in the extended drain region of the N-well. The P-field blocks form junction-fields in the N-well for equalizing the capacitance of parasitic capacitors between the drain region and the source region and fully deplete the drift region before breakdown occurs. A higher breakdown voltage is therefore achieved and the N-well having a higher doping density is thus allowed. The source region and P-field blocks enclose the drain region, which makes the LDMOS transistor self-isolated.

Owner:SEMICON COMPONENTS IND LLC

System and method for edge termination of super-junction (SJ) devices

ActiveUS20180166531A1Reduce doping concentrationIncrease the on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSubject matterEngineering

The subject matter disclosed herein relates to super-junction (SJ) power devices and, more specifically, to edge termination techniques for SJ power devices. A semiconductor super-junction (SJ) device includes one or more epitaxial (epi) layers having a termination region disposed adjacent to an active region. The termination region includes a plurality of vertical pillars of a first and a second conductivity-type, wherein, moving outward from the active region, a respective width of each successive vertical pillar is the same or smaller. The termination region also includes a plurality of compensated regions having a low doping concentration disposed directly between a first side of each vertical pillar of the first conductivity-type and a first side of each vertical pillar of the second conductivity-type, wherein, moving outward from the active region, a respective width of each successive compensated region is the same or greater.

Owner:GENERAL ELECTRIC CO

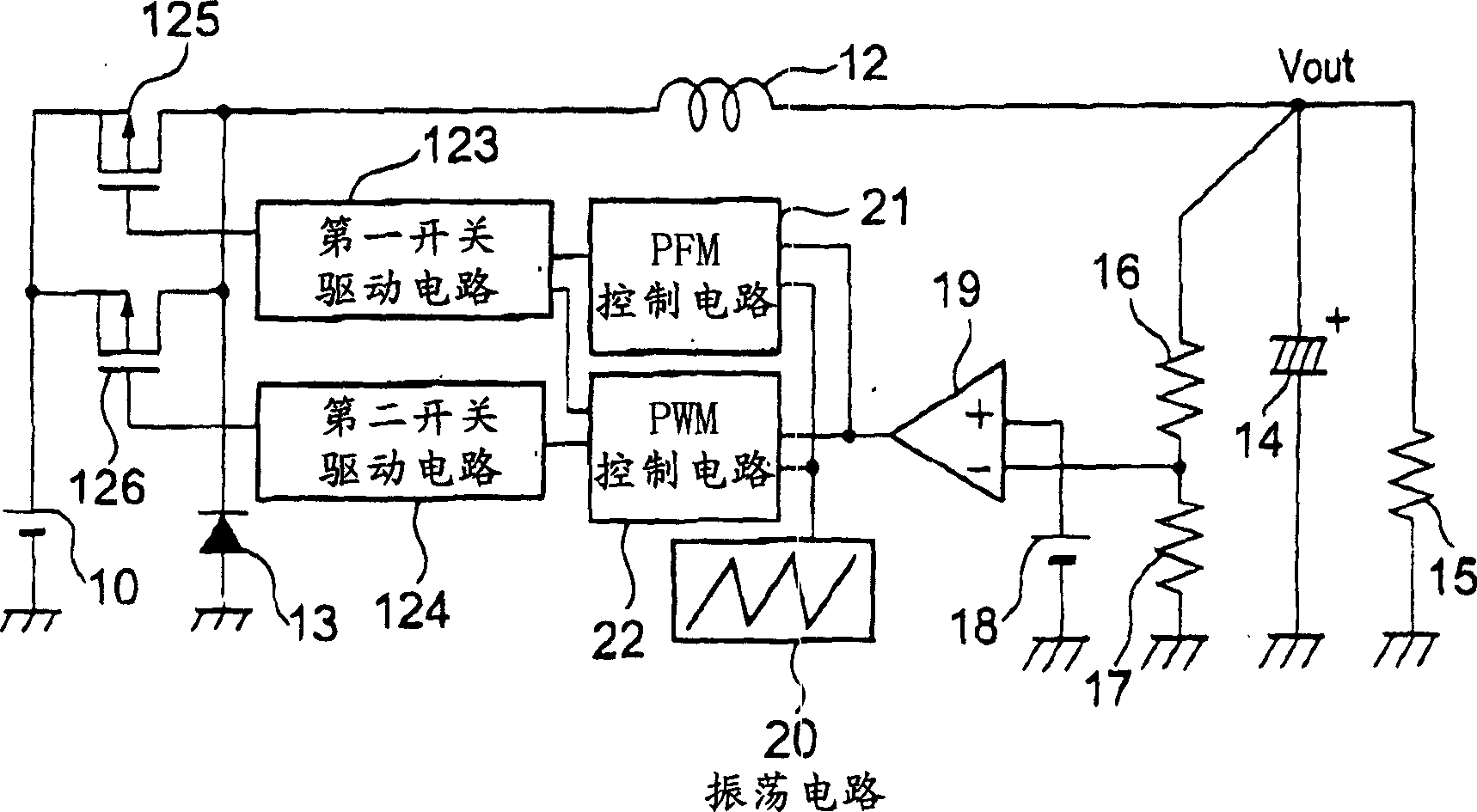

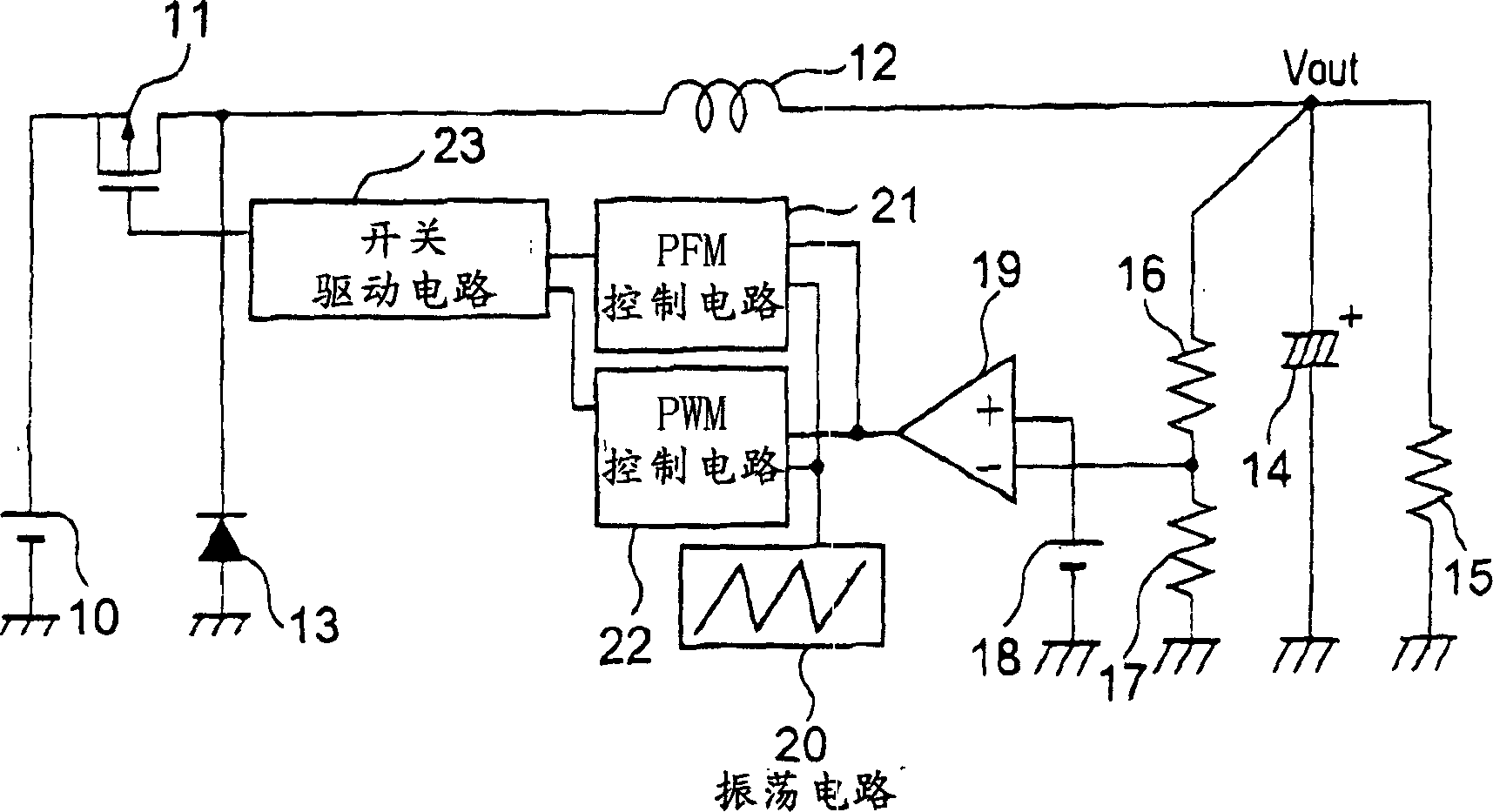

Switching regulator control circuit

InactiveCN1578086AIncrease the on-resistanceReduce gate capacitanceEfficient power electronics conversionDc-dc conversionCapacitanceControl theory

The present invention provides an SW regulator control circuit that is efficient in both of the cases where the load is heavy and where the load is light. Two switch MOS transistors are disposed as switching elements of the SW regulator in parallel which are large in an on-resistance and small in a gate capacity, and in the case where a load of the SW regulator is heavy, the two switch MOS transistors are driven in parallel to lessen the on-resistance whereas in the case where the load is light, one of the two switch MOS transistors is driven to lessen the gate capacity.

Owner:SEIKO INSTR INC

SiC junction barrier Schottky diode and manufacturing method thereof

ActiveCN103346169AIncrease BFOM valueReduce the effect of fringe electric field concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactOptoelectronics

The invention relates to a SiC junction barrier Schottky diode and a manufacturing method of the SiC junction barrier Schottky diode. The SiC junction barrier Schottky diode comprises a substrate of a first conductive type, an epitaxial layer of the first conductive type, a Schottky metal contact, a heavily doped region of a second conductive type, a light doped region of the second conductive type, a light doped trap of the second conductive type and an ohmic contact, wherein the epitaxial layer of the first conductive type is formed on the substrate, the Schottky metal contact is formed on the epitaxial layer, the heavily doped region of the second conductive type is formed below the Schottky metal contact, the light doped region of the second conductive type is formed below the heavily doped region, the light doped trap of the second conductive type is formed below the light doped region, the width of the light doped trap is smaller than that of each light doped region, and the ohmic contact is formed on the reverse side of the substrate. The SiC junction barrier Schottky diode can obviously reduce the electric field concentration effect in the corner of a PN junction, and further improves the reverse breakdown voltage of a device and a quality factor (BFOM) value of Baliga.

Owner:TSINGHUA UNIV

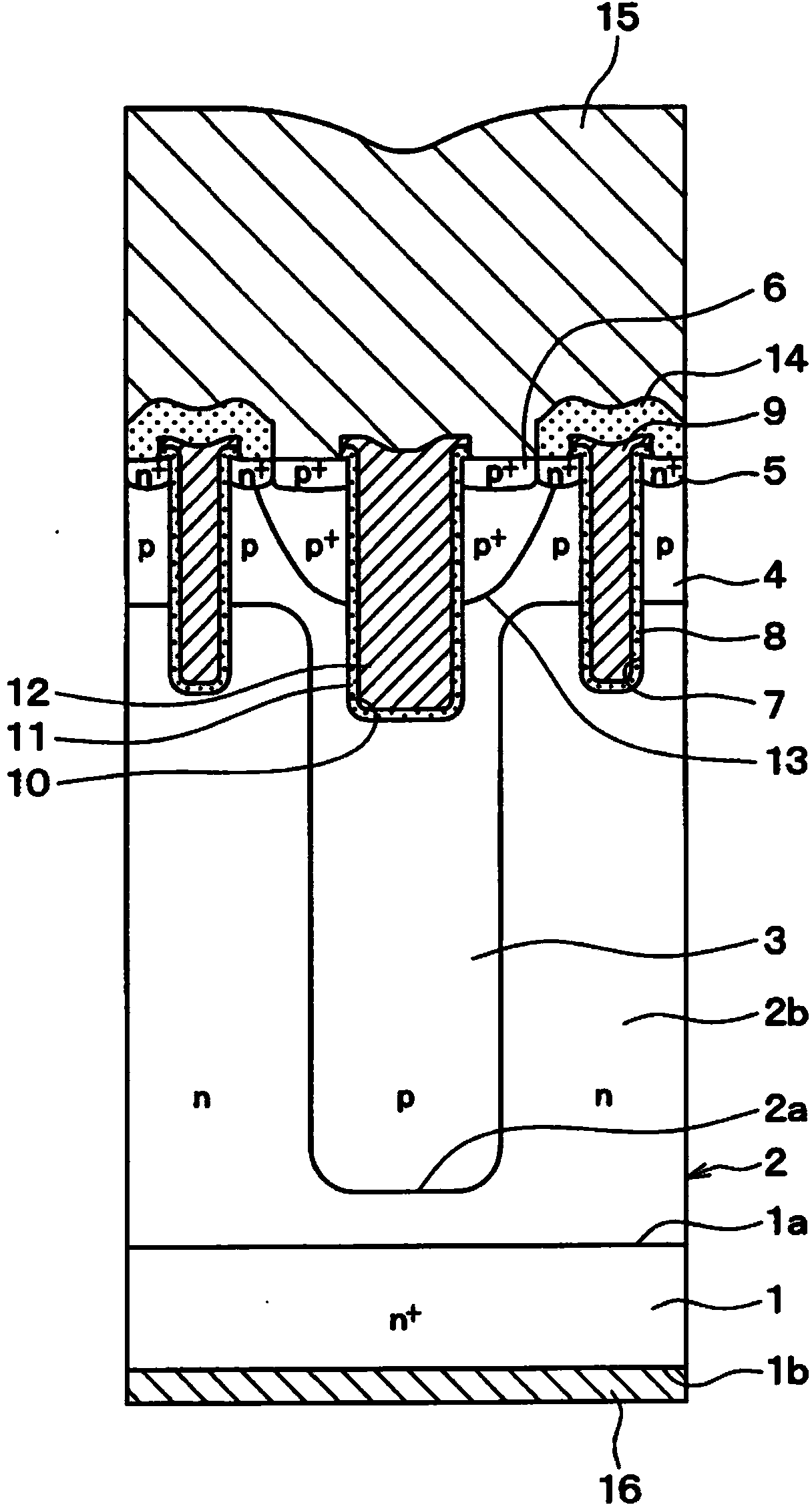

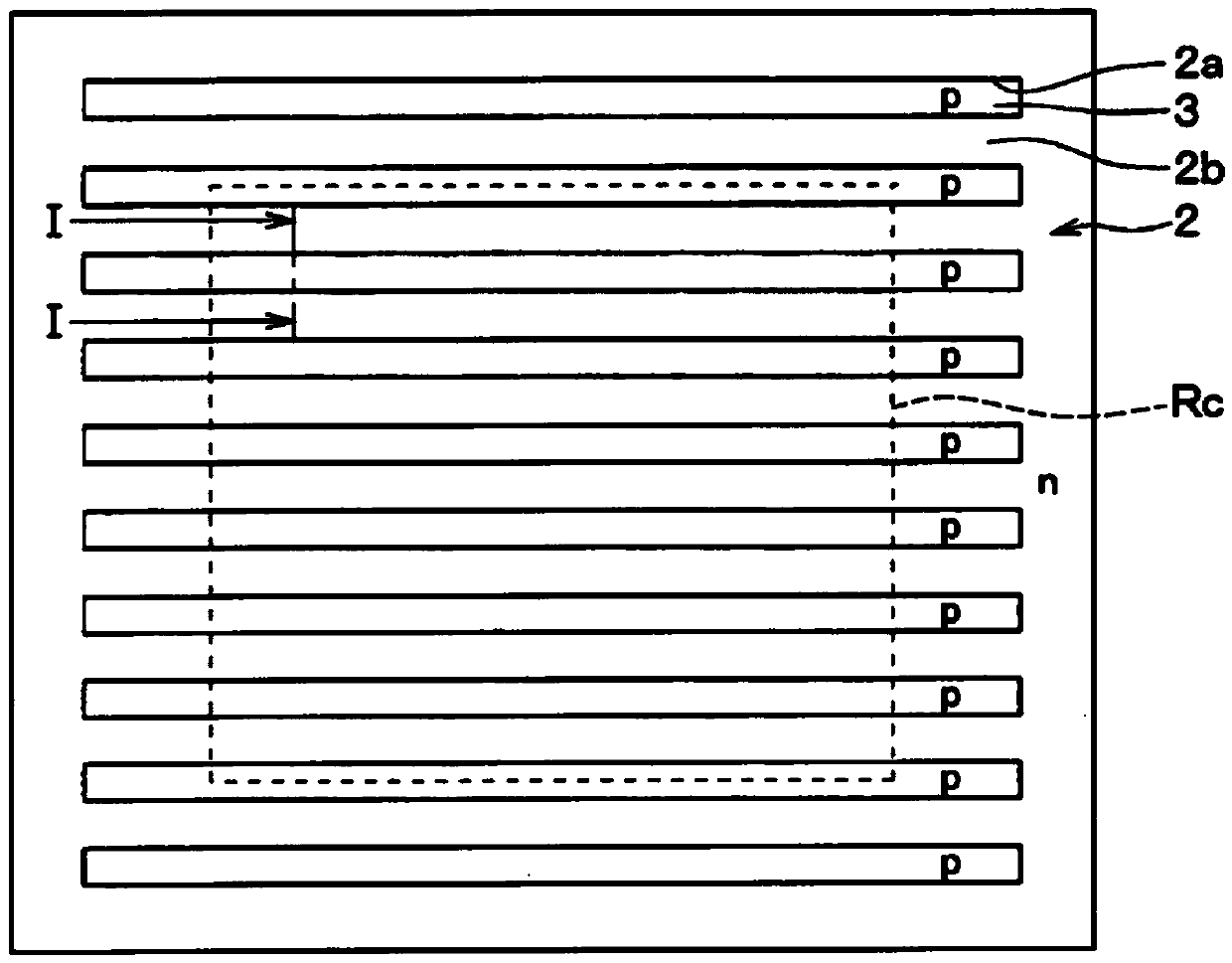

Semiconductor device provided with vertical semiconductor element

InactiveCN103828058AIncrease the on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceTrench gate

This semiconductor device that is provided with a vertical semiconductor element has a trench gate structure and a dummy gate structure. The trench gate structure has a first trench (7) which is formed to reach a first conductivity-type region (2b) in a super junction structure by penetrating a first impurity region (5) and a base region (4). The dummy gate structure has a second trench (10), which reaches the super junction structure by penetrating the base region (4), and is formed deeper than the first trench (7).

Owner:DENSO CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com