Patents

Literature

240results about How to "Increased power loss" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

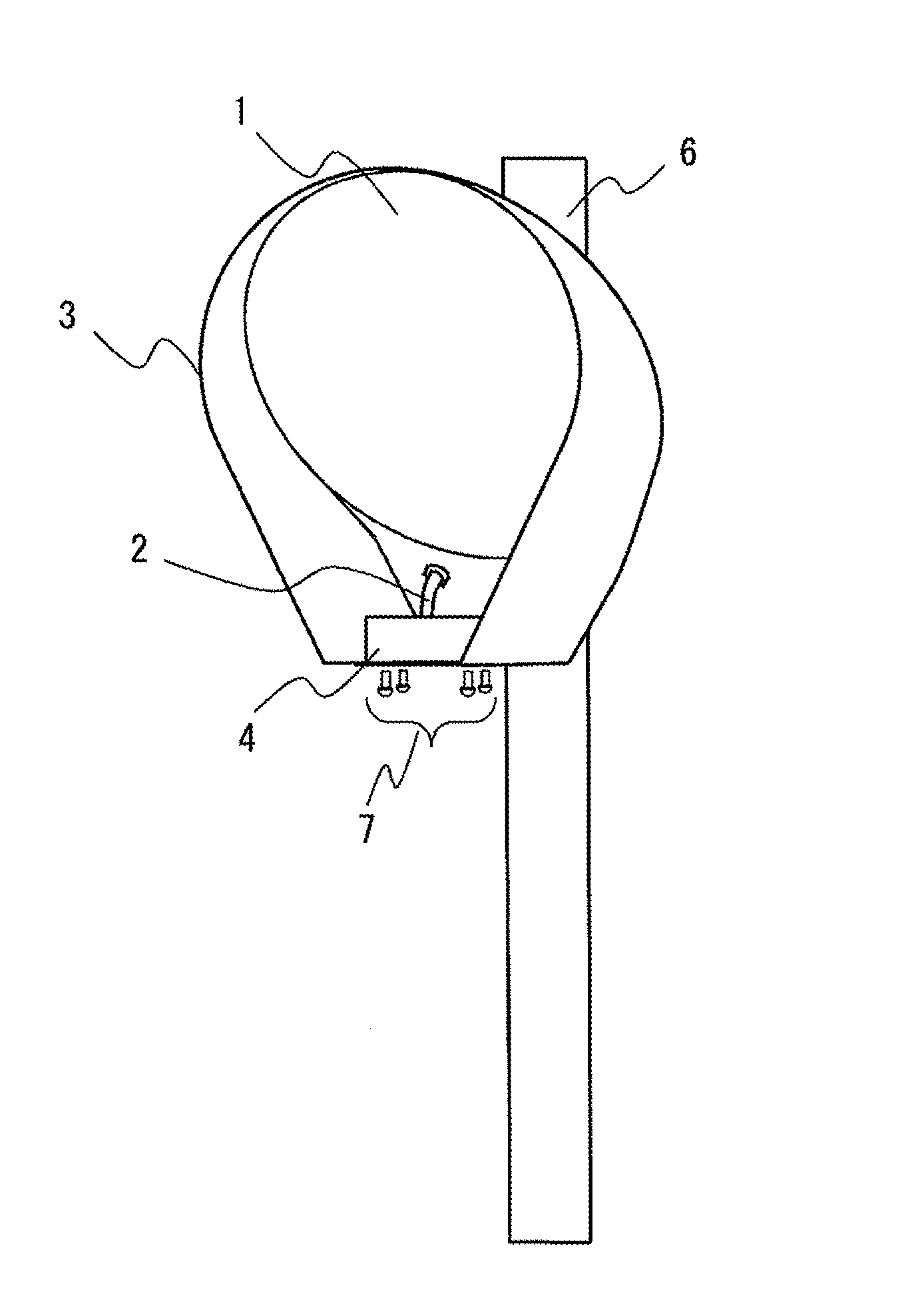

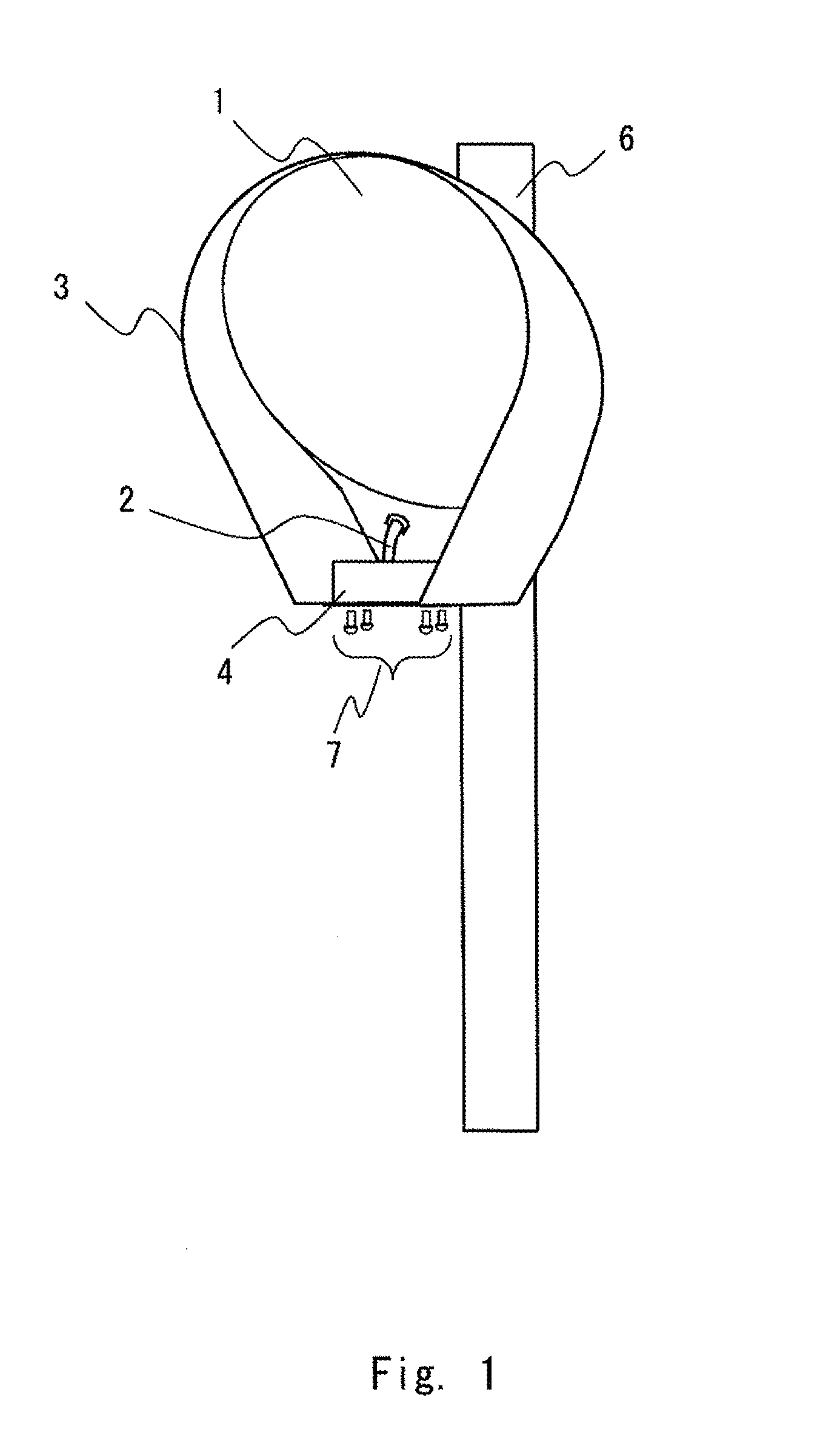

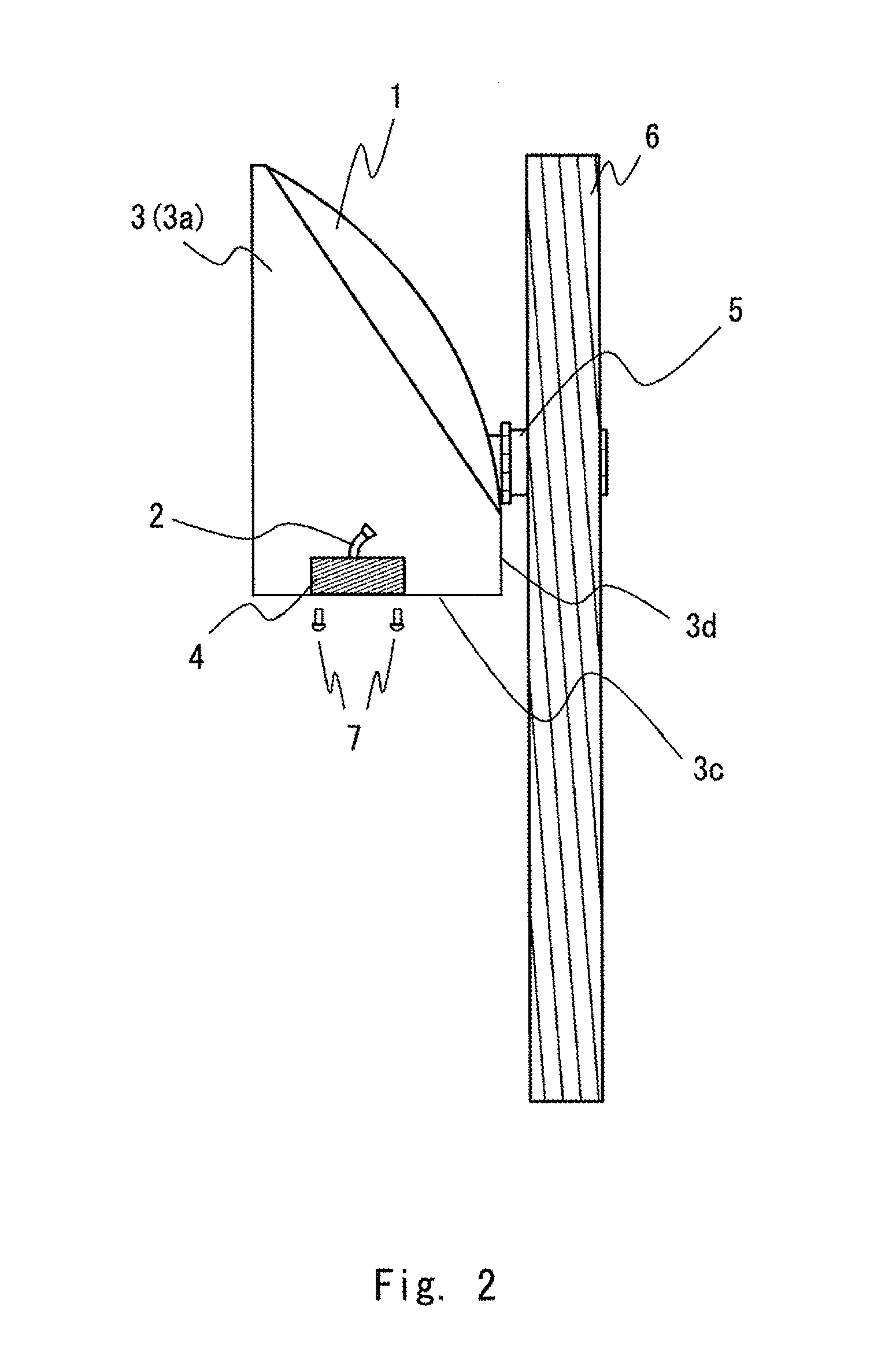

Antenna device and method for attaching the same

ActiveUS20150138022A1Low costImproved strength characteristicAntenna supports/mountingsAntenna couplingsPhysicsRadio wave

An antenna device includes: a radio device for radio wave transmission; a primary radiator that has a function to radiates radio waves generated by the radio device; a parabolic reflector that reflects the radio waves radiated from the primary radiator; a shroud that shields against unnecessary radiation radio waves among the radio waves radiated from the primary radiator and reflected by the parabolic reflector; and an antenna mounting mechanism that fits the parabolic reflector to an antenna attachment pole. The shroud is arranged so as to cover at least a right and left of the parabolic reflector, the radio device and the primary radiator are arranged inside the shroud, and the antenna mounting mechanism fits the parabolic reflector to the antenna attachment pole so that the antenna attachment pole is located at a lateral center position of the parabolic reflector.

Owner:NEC CORP

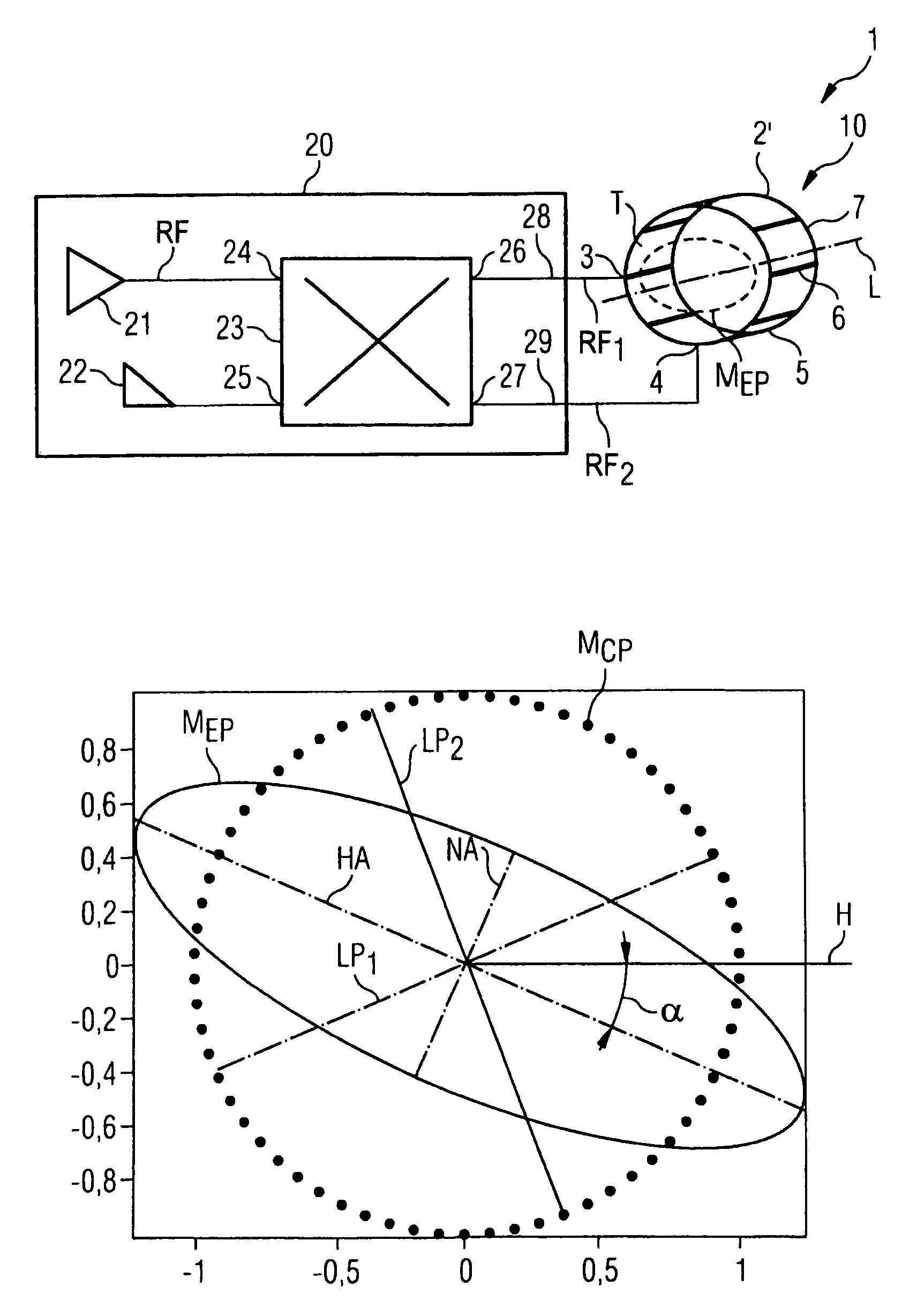

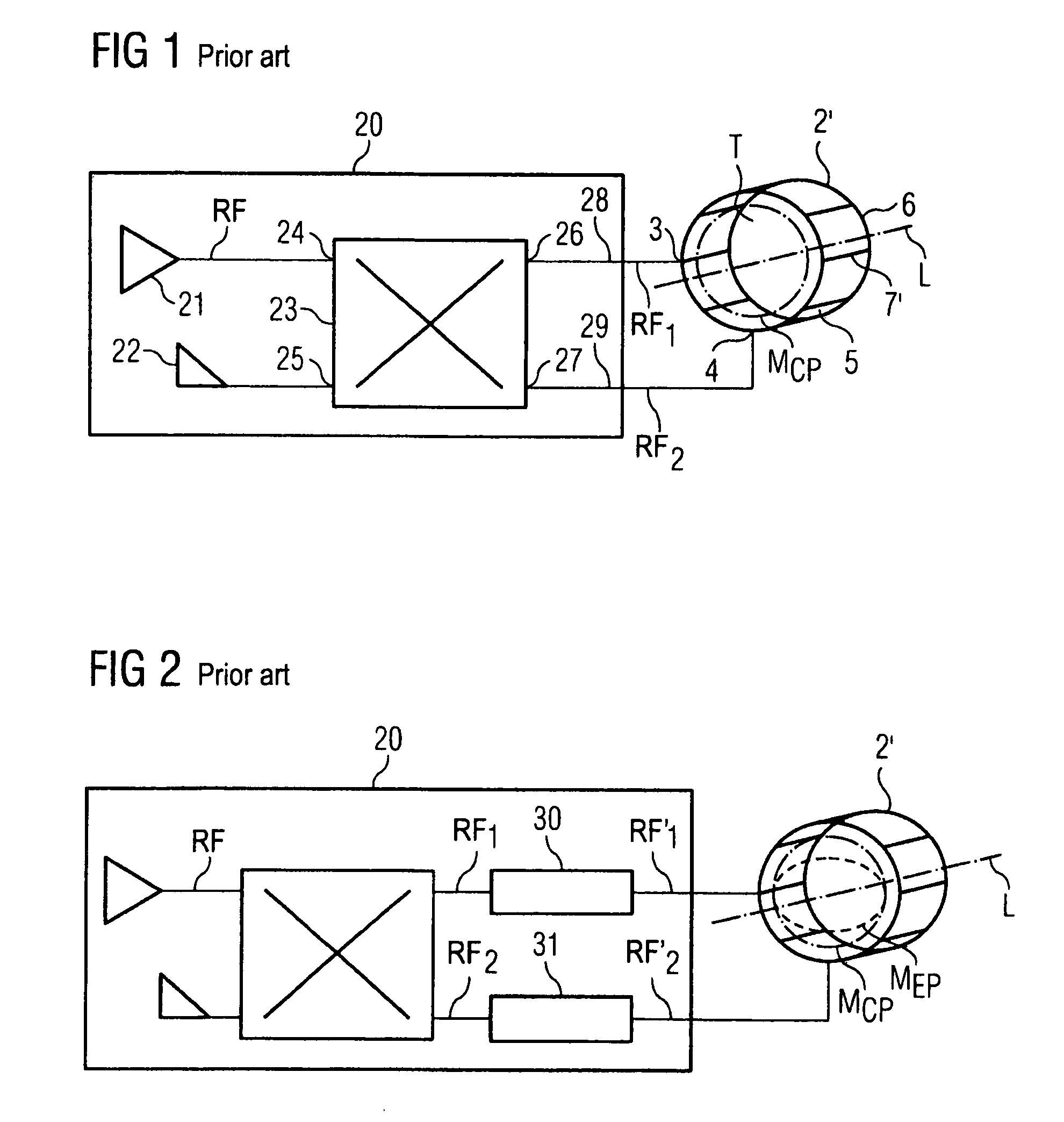

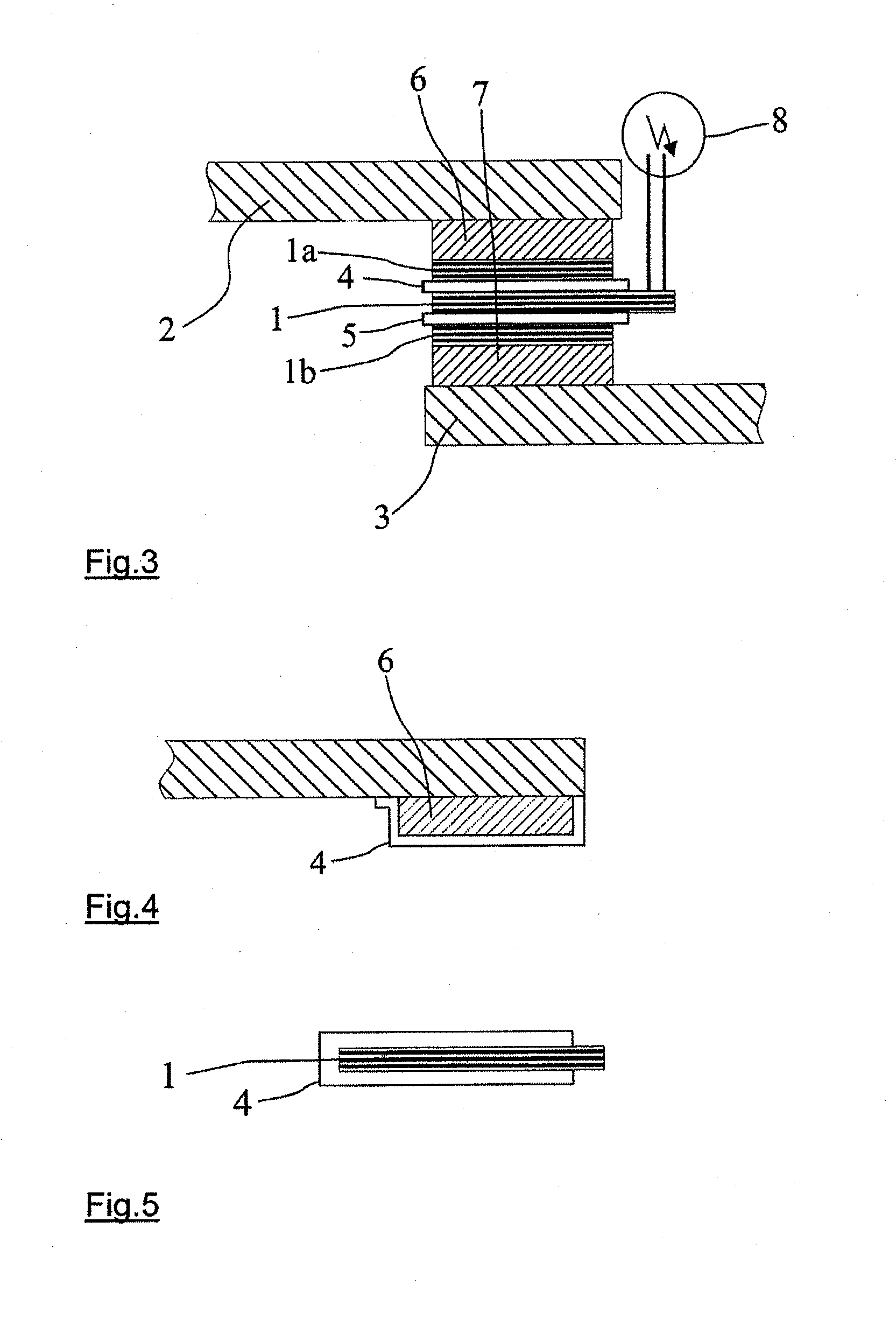

Magnetic resonance whole body antenna system, elliptically polarized with major ellipse axis tilted/non-horizontal at least when unoccupied by an examination subject

ActiveUS8362775B2Improved field distributionLittle effortMagnetic measurementsDiagnostic recording/measuringWhole bodyElliptical polarization

A magnetic resonance system obtaining magnetic resonance exposures of an examination subject, has an examination tunnel, a whole-body antenna with two connection terminals. The whole-body antenna cylindrically extends around the examination tunnel along a longitudinal axis. The system has a radio-frequency supply device in order to respectively supply the whole-body antenna with radio-frequency signals for emission of a radio-frequency field in the examination tunnel. The radio-frequency supply device has a radio-frequency generator for generation of a radio-frequency signal, a signal splitter that divides a radio-frequency signal coming from the radio-frequency generator into two partial signals that are phase-shifted by 90° relative to one another. Two radio-frequency feed lines are connected with the two connection terminals of the whole-body antenna. Via these radio-frequency feed lines, the two partial signals are fed into the whole-body antenna. The whole-body antenna has an intrinsic transmission characteristic such that a radio-frequency field is emitted that is elliptically polarized in a defined manner in a plane lying perpendicular to the longitudinal axis (at least in the unloaded state of the examination tunnel).

Owner:SIEMENS HEALTHCARE GMBH

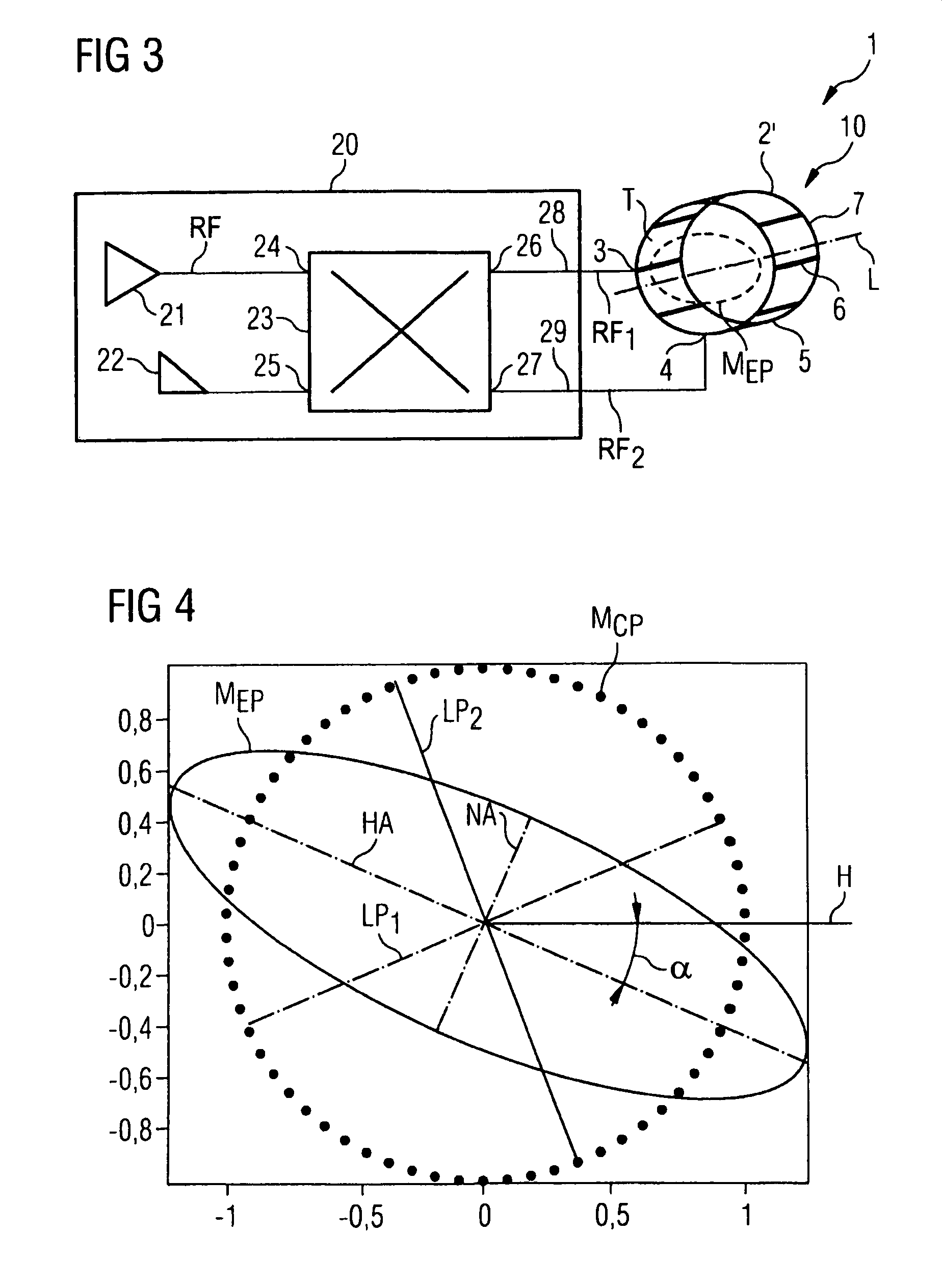

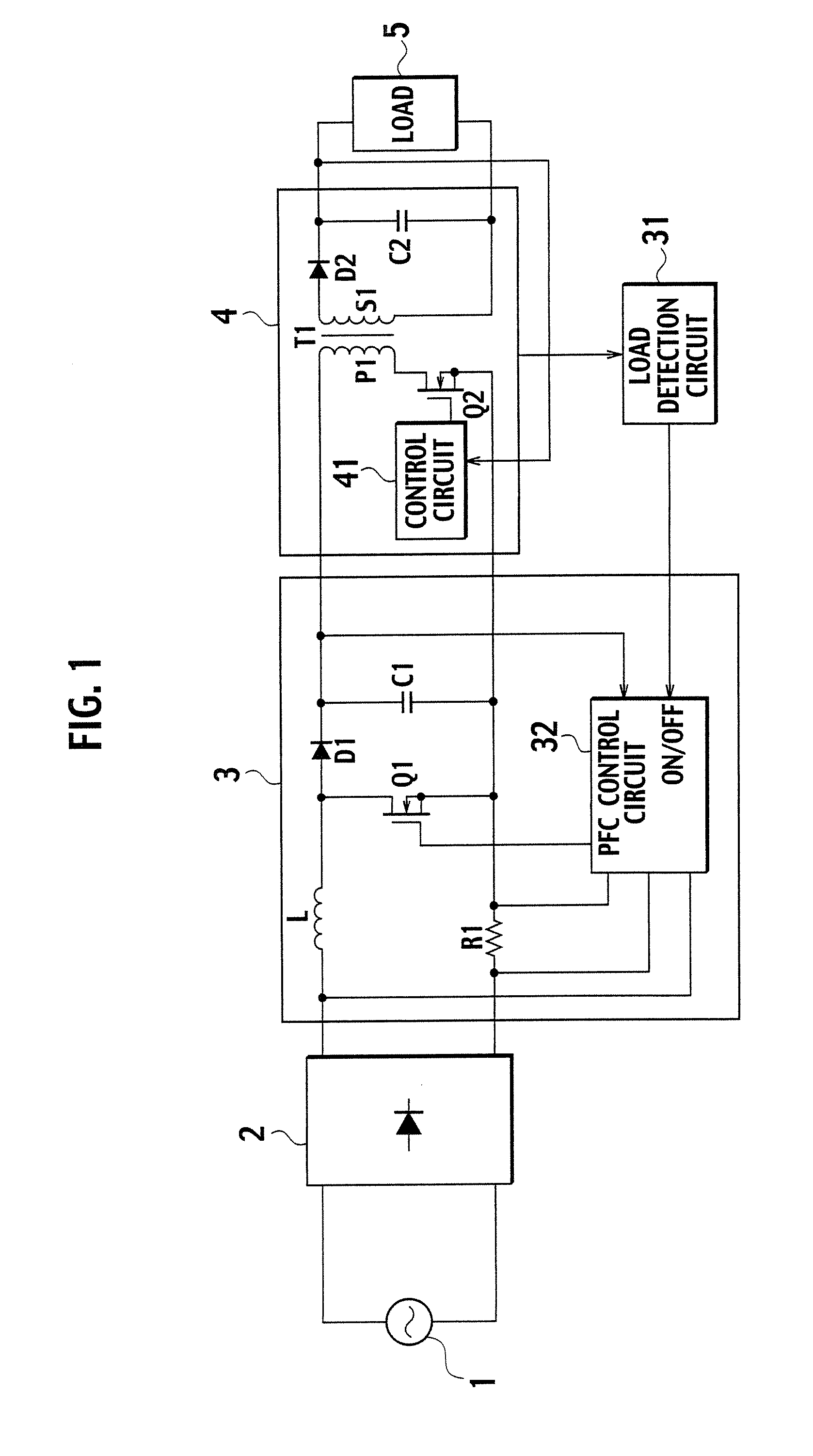

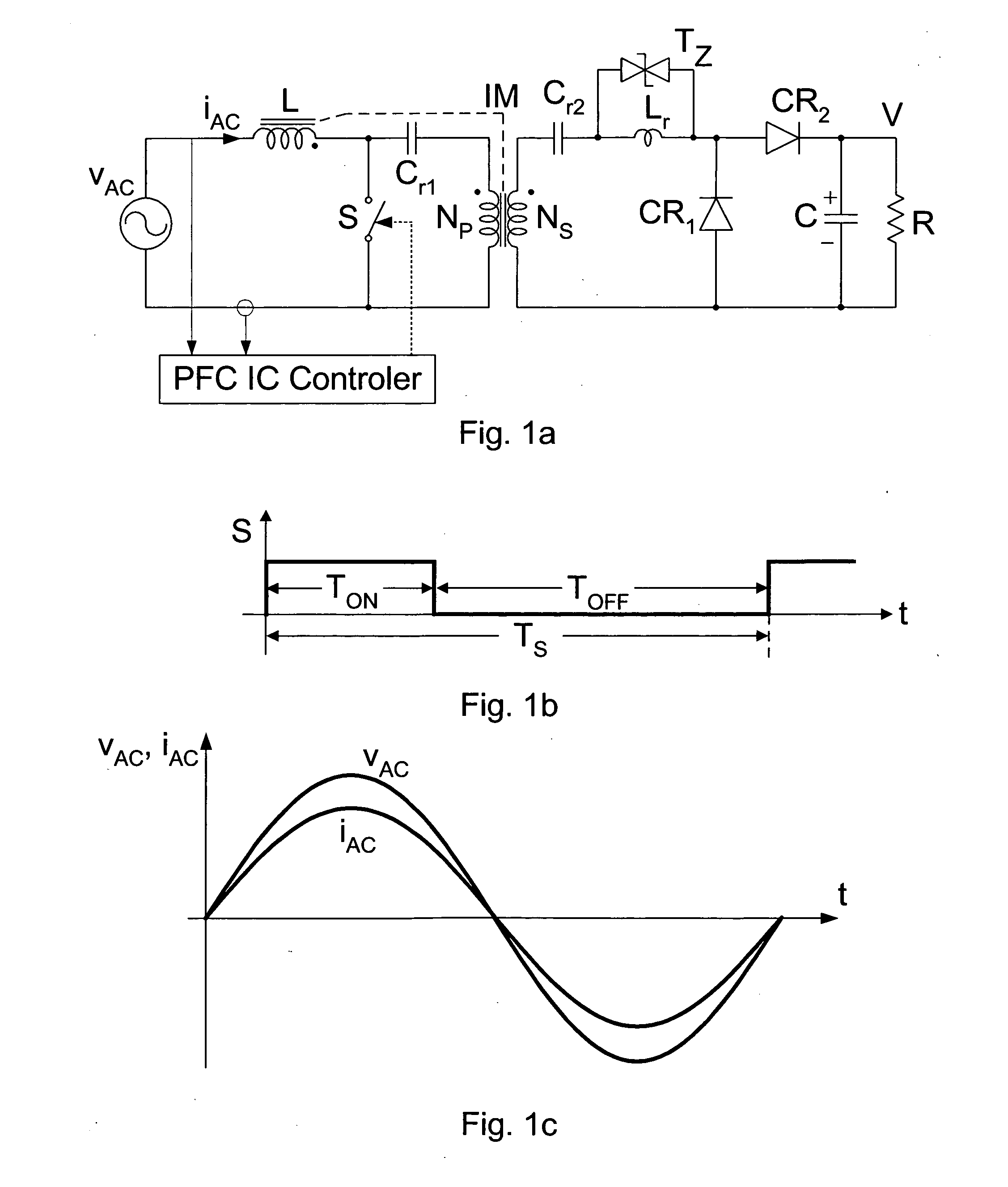

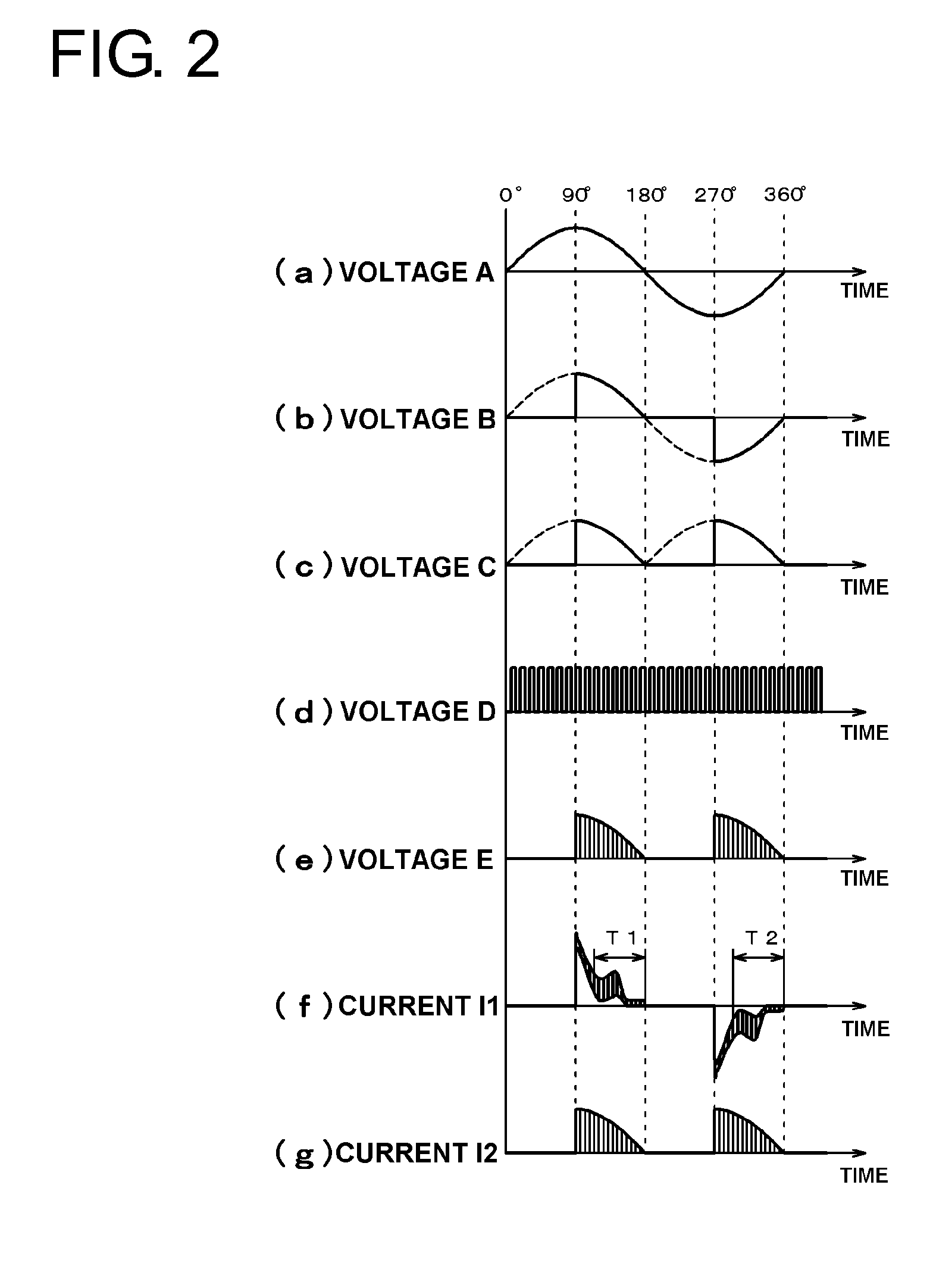

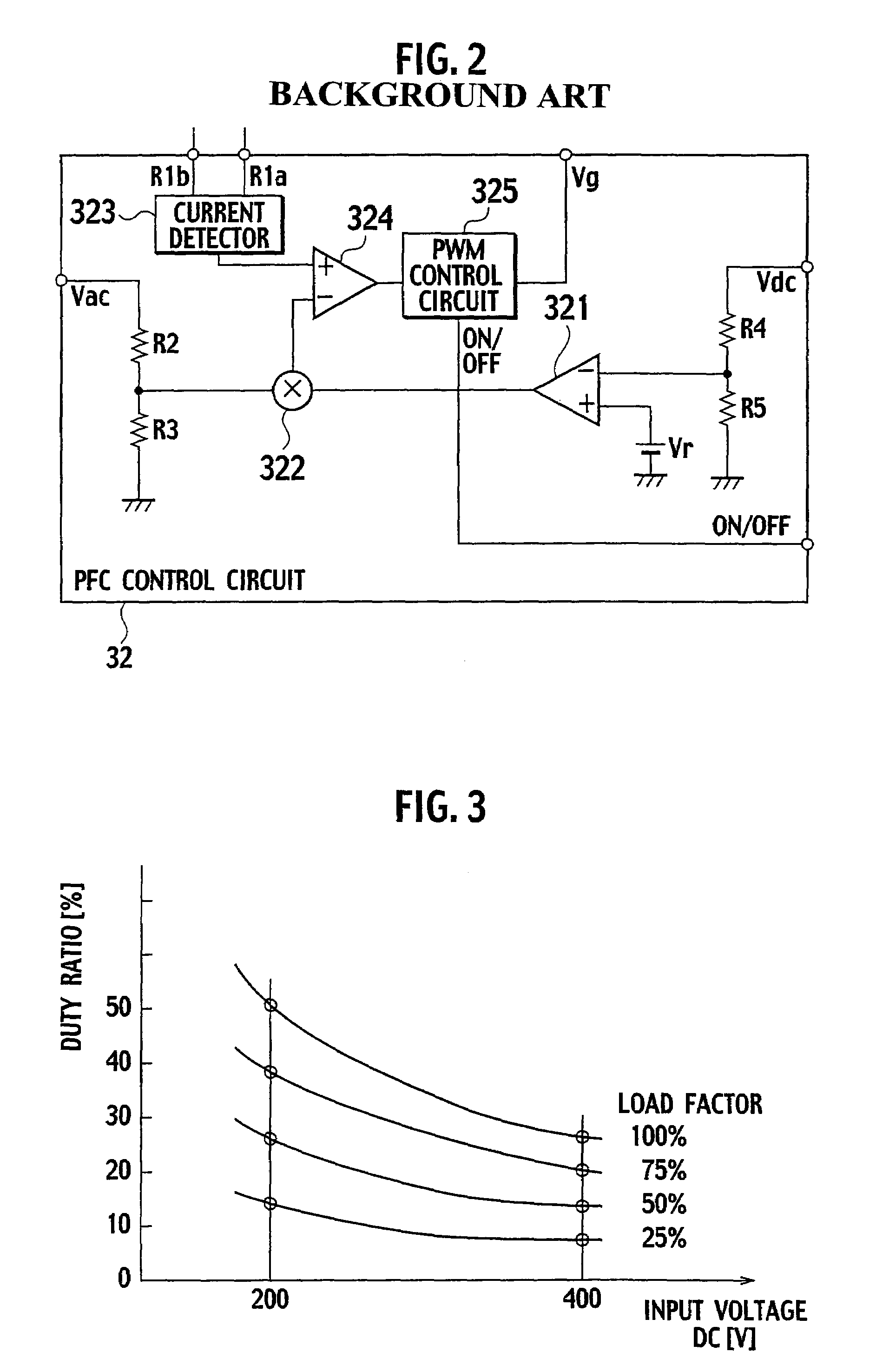

Power factor improving circuit

InactiveUS20070103949A1Power loss increaseReduce efficiencyEfficient power electronics conversionAc-dc conversionSine waveAC power

A power factor improving circuit including: a boost reactor that inputs a rectified voltage obtained by rectifying an AC power supply voltage of an AC power supply by a rectifier circuit; a main switch that inputs the rectified voltage through the boost reactor and is turned on / off; a converting section that converts a voltage obtained when the main switch is turned on / off into a DC output voltage; and a control section that controls turn-on / off of the main switch to shape an AC power supply current to a sine wave form, controls an output voltage of the converting section to a predetermined voltage, and controls a switching frequency of the main switch according to a value of current flowing into the AC power supply, or that of current flowing into the rectifier, or that of current flowing into the main switch.

Owner:SANKEN ELECTRIC CO LTD

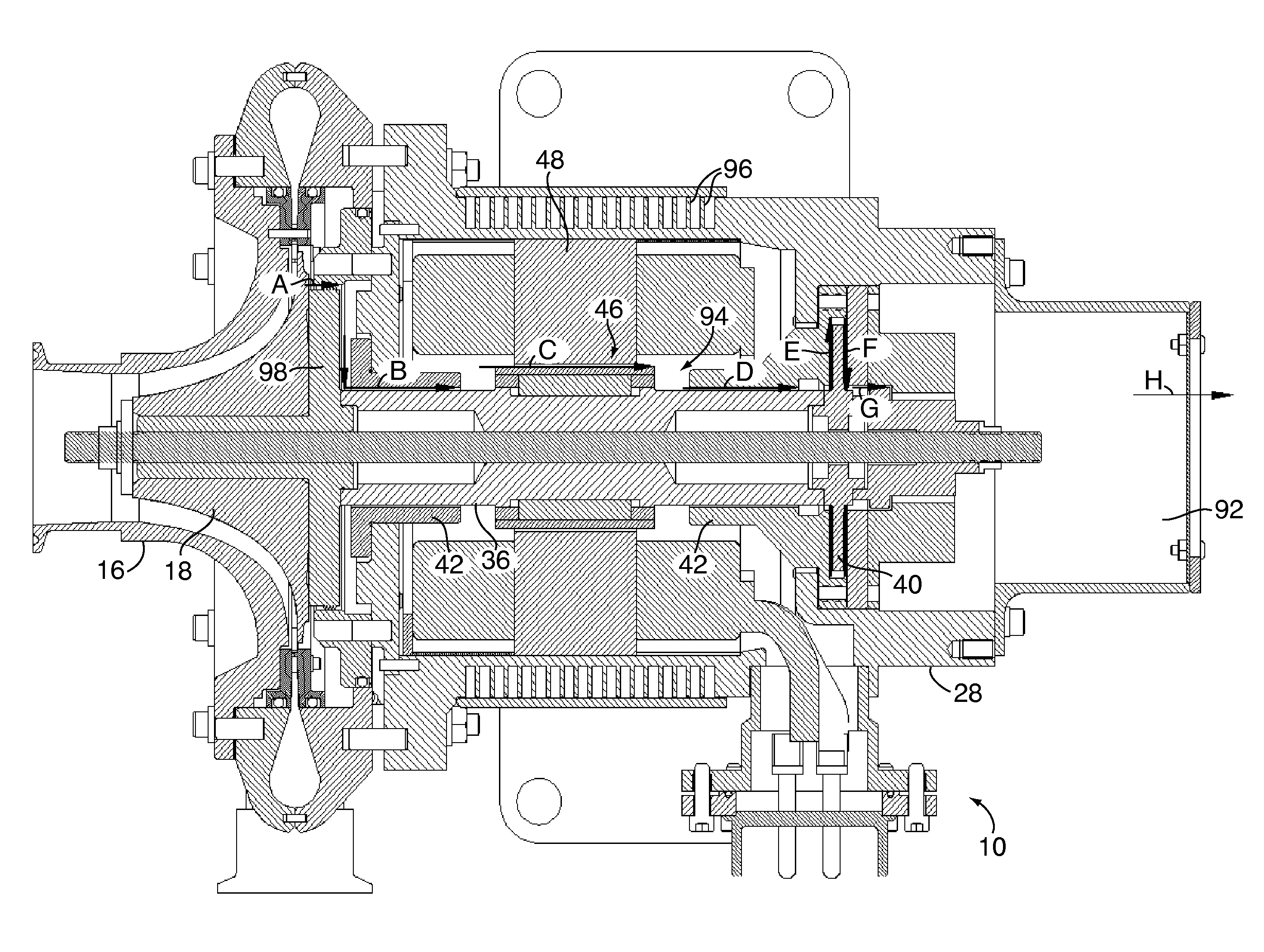

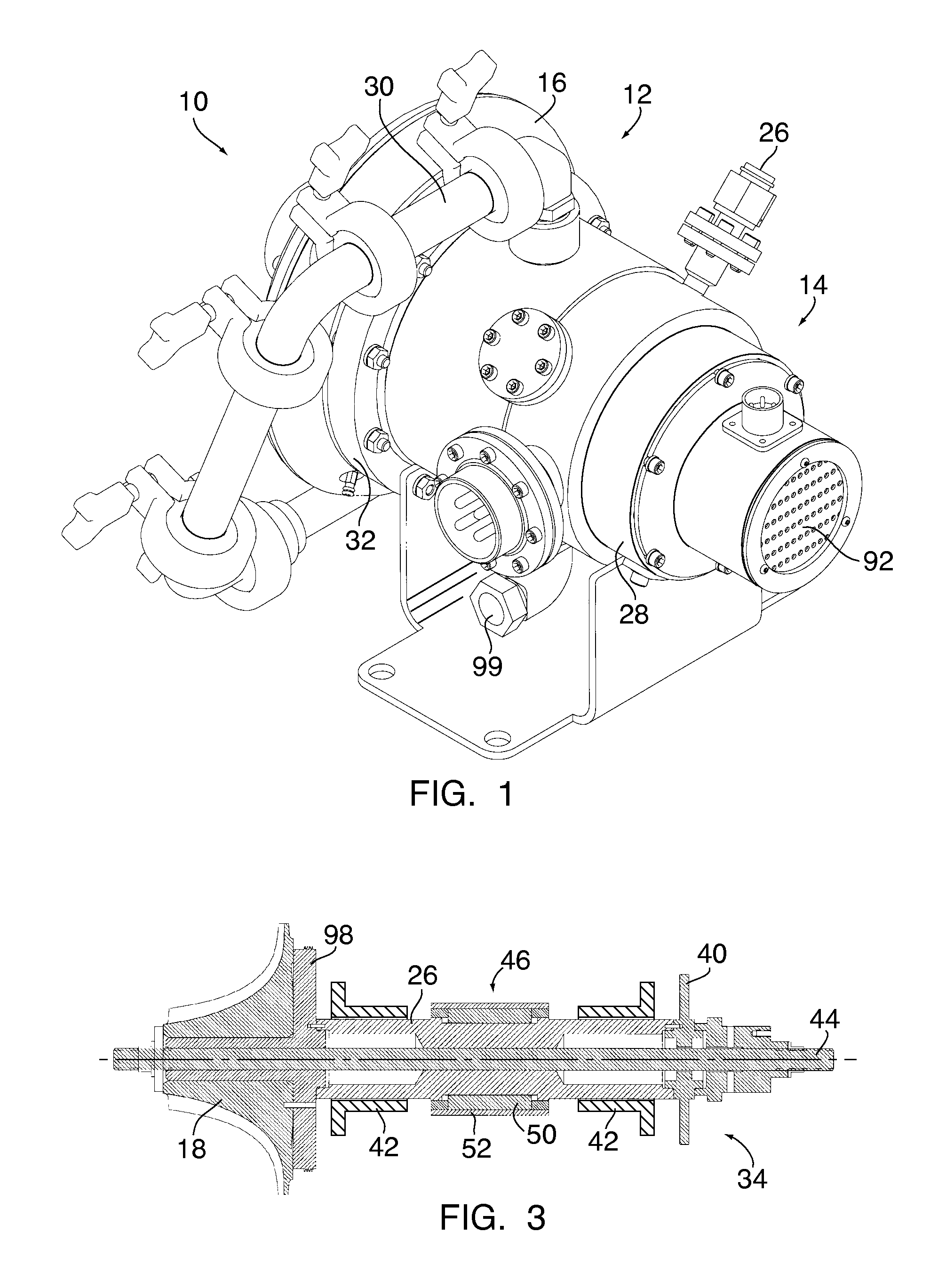

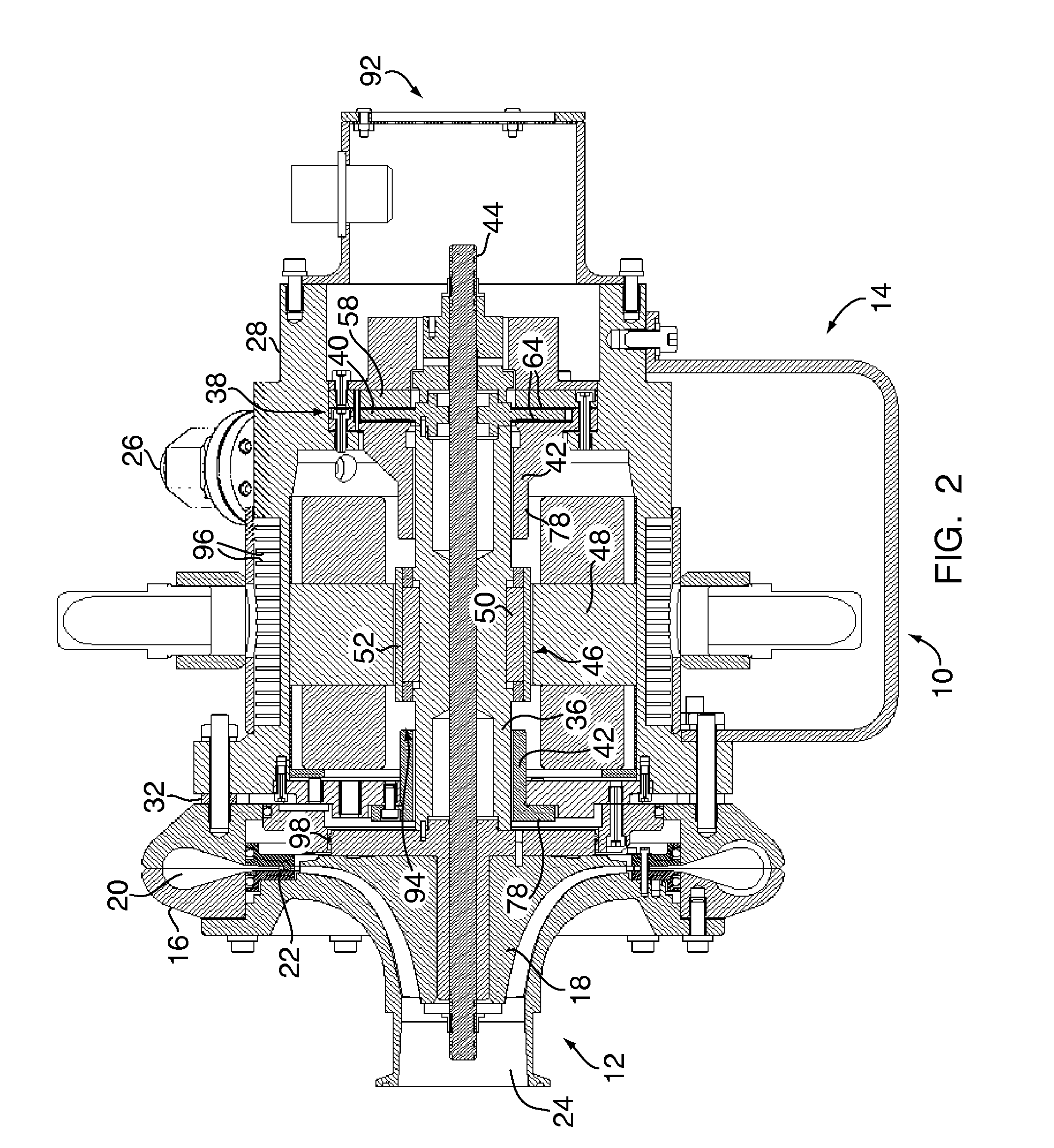

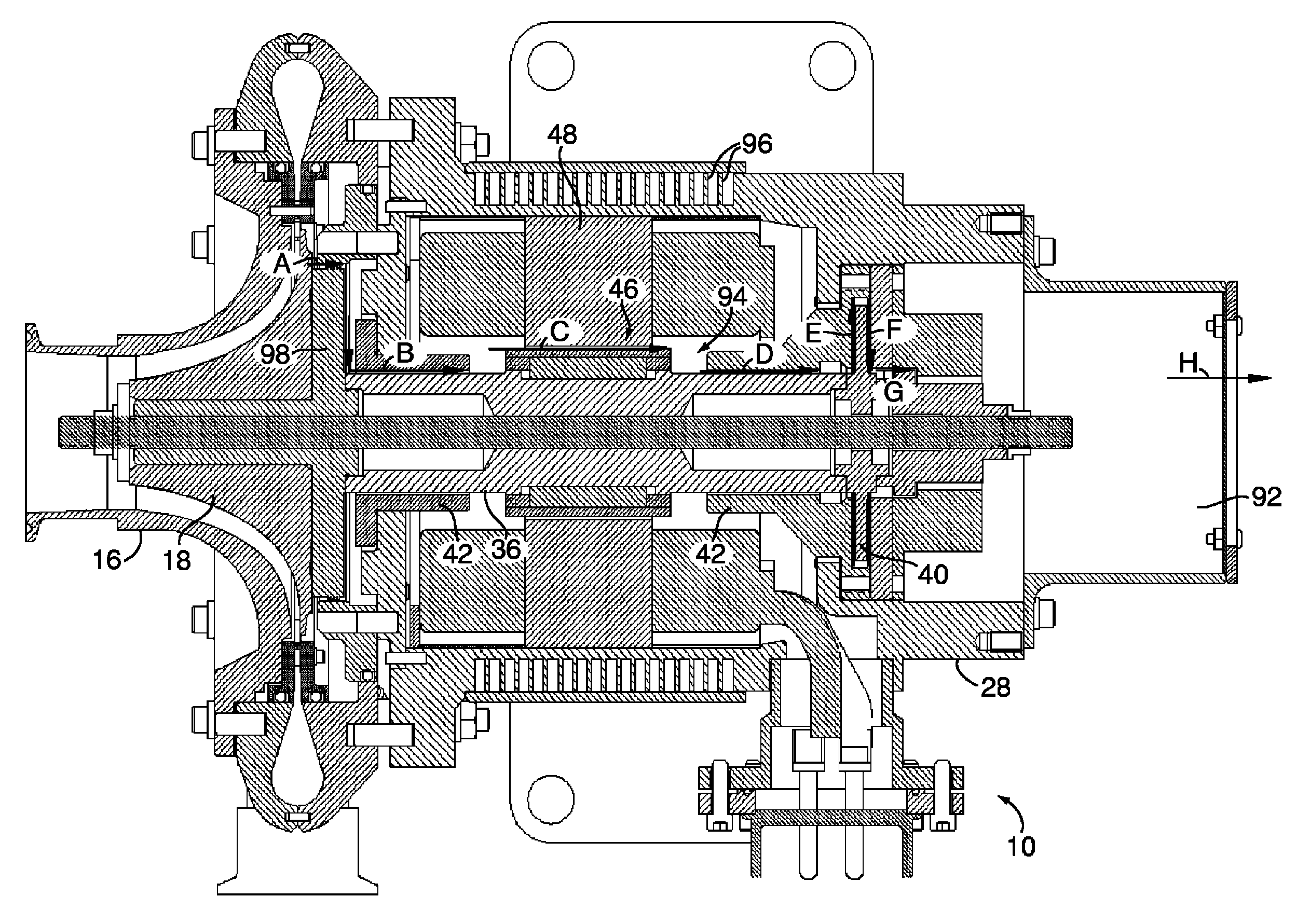

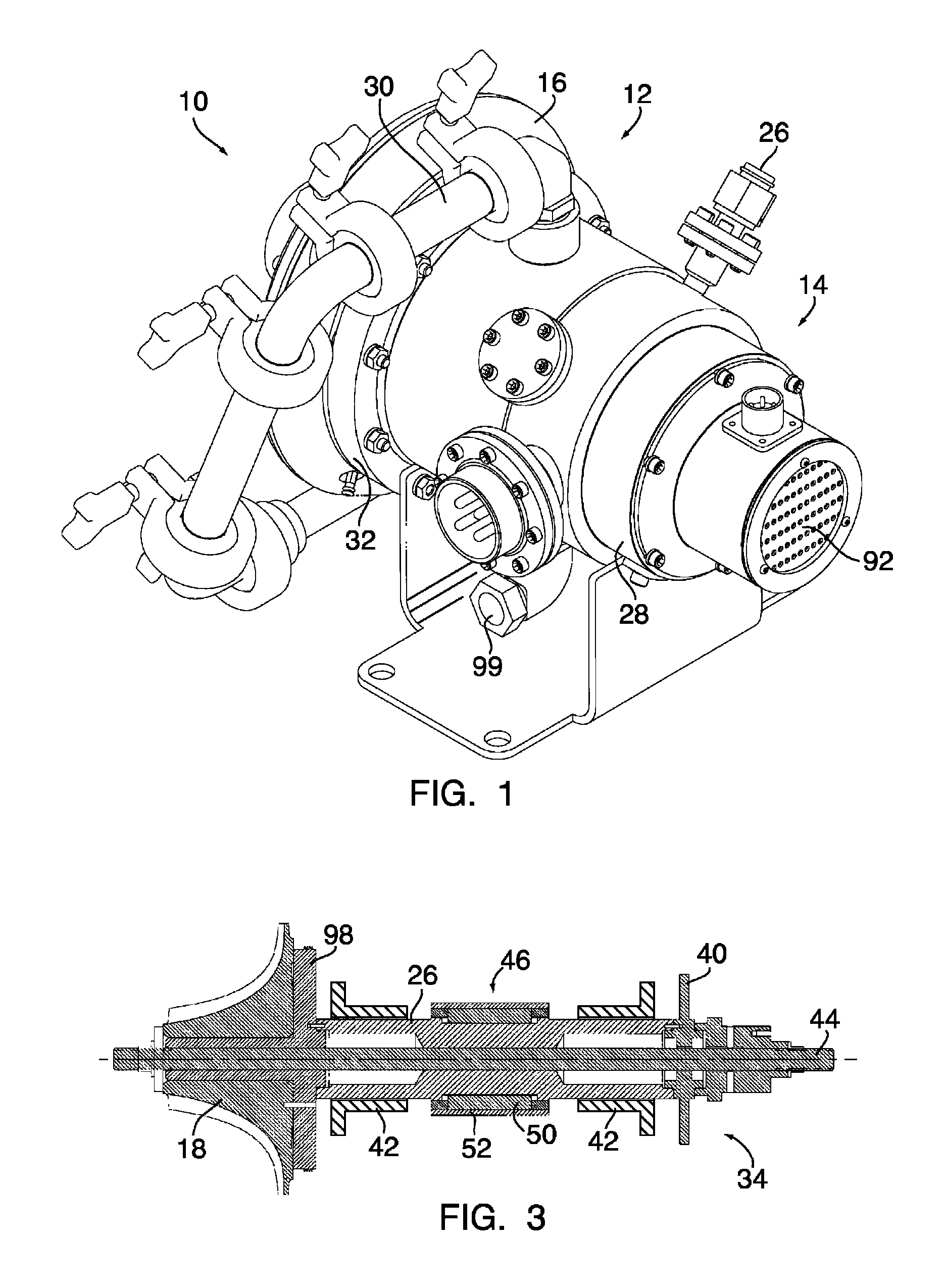

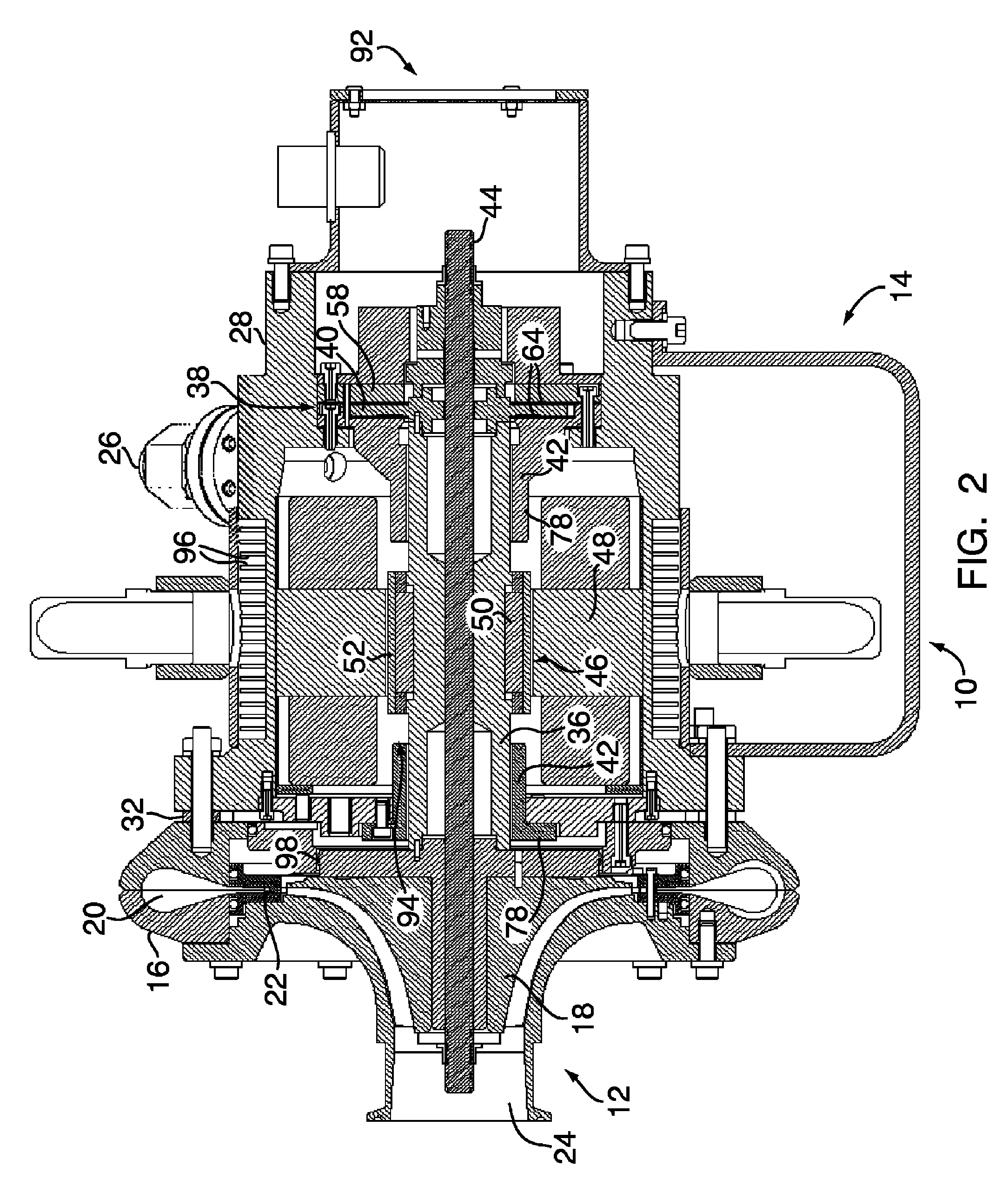

Turboalternator with hydrodynamic bearings

ActiveUS20080246281A1Recovery of wasted energyReduce pressureLiquid degasificationPump componentsStored energyAlternator

This invention provides a small, high efficiency, oil-free turbine-driven alternator (i.e. turboalternator) suitable for conversion of stored energy in a process gas to electrical power, facilitating recapture of energy during operation that would otherwise be wasted. The turboalternator includes a turbine and a generating device operatively connected together by a rotating shaft capable of rotating at high speeds. The rotating shaft is supported by foil gas bearings.

Owner:R & D DYNAMICS

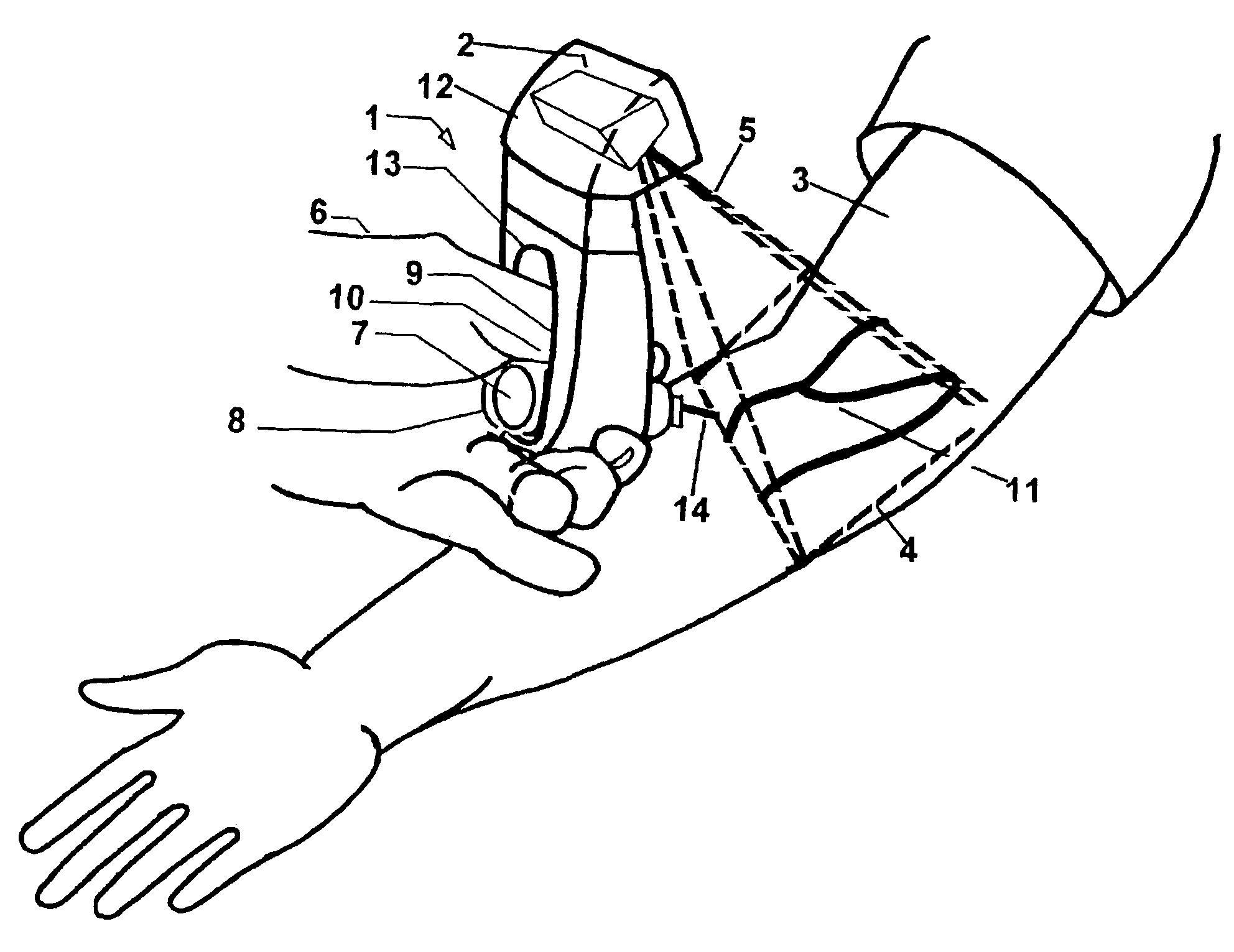

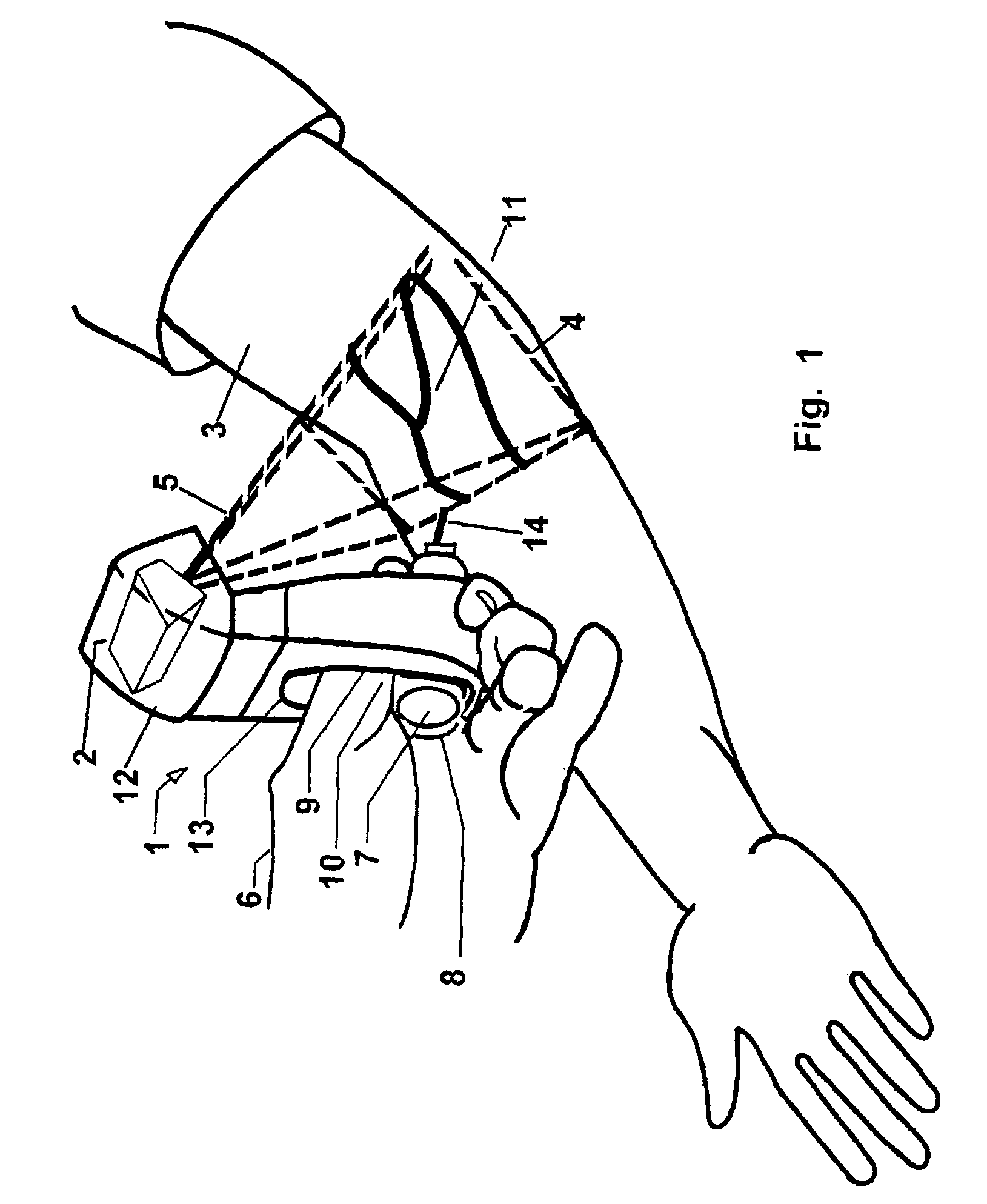

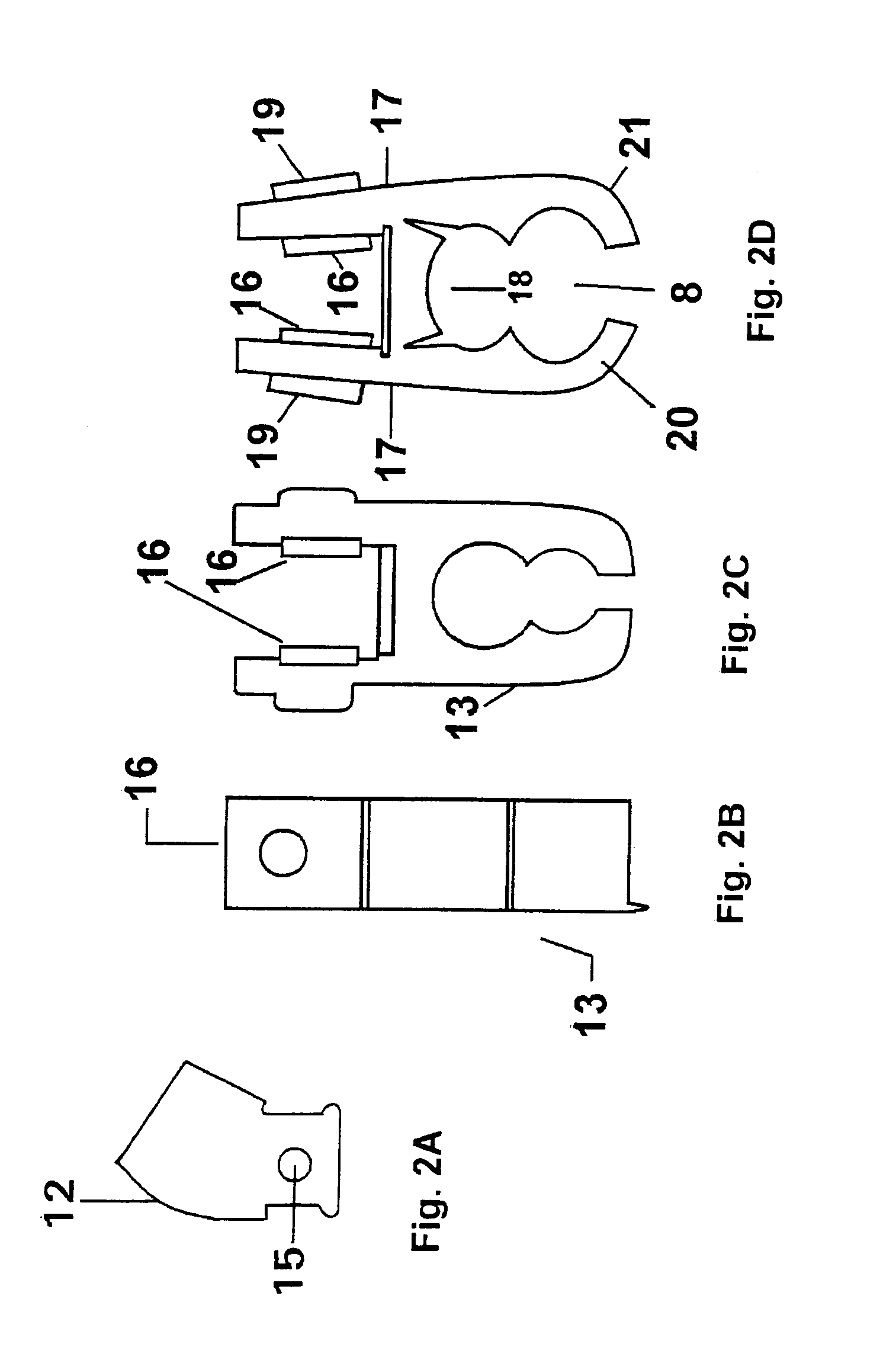

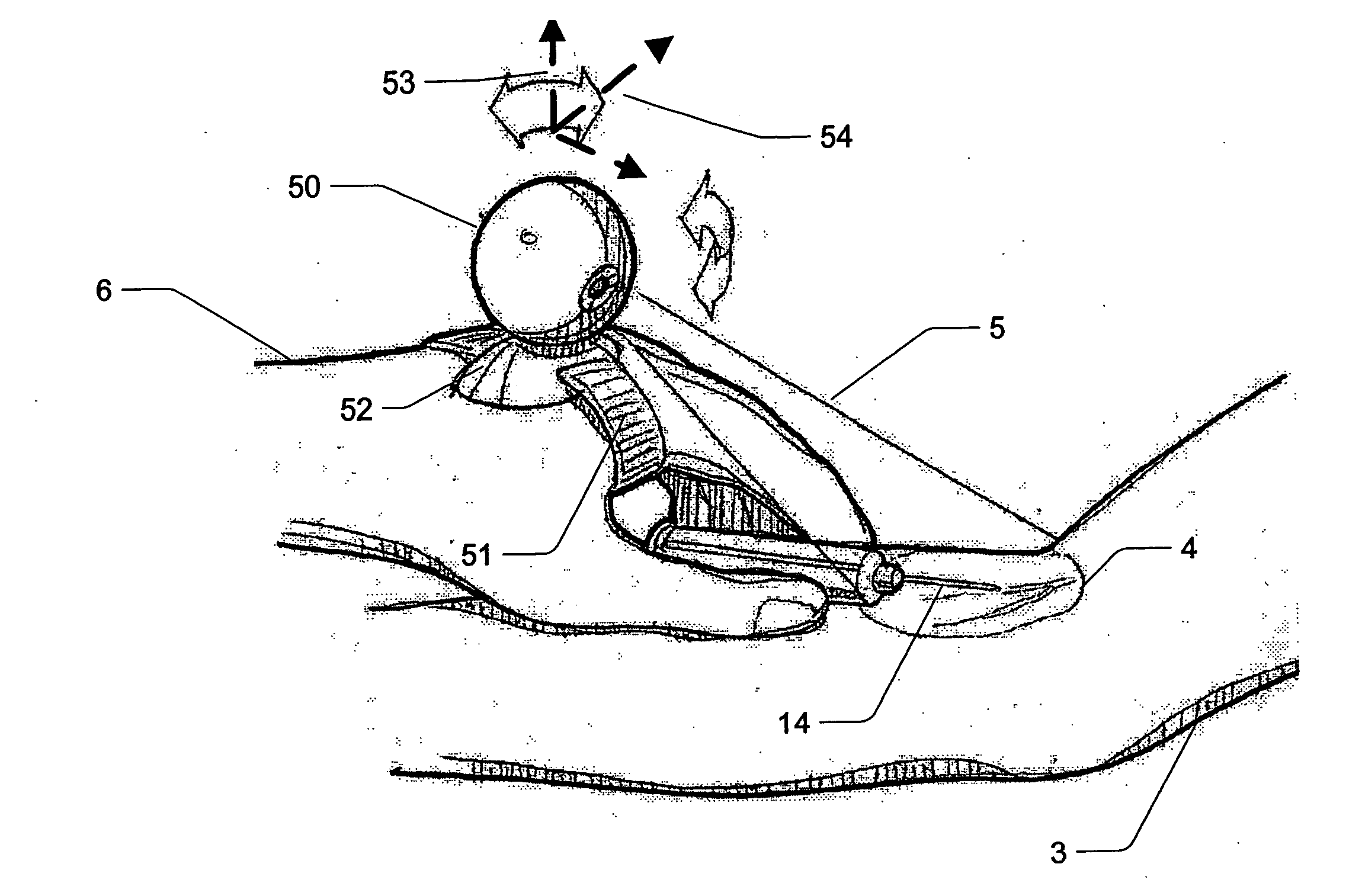

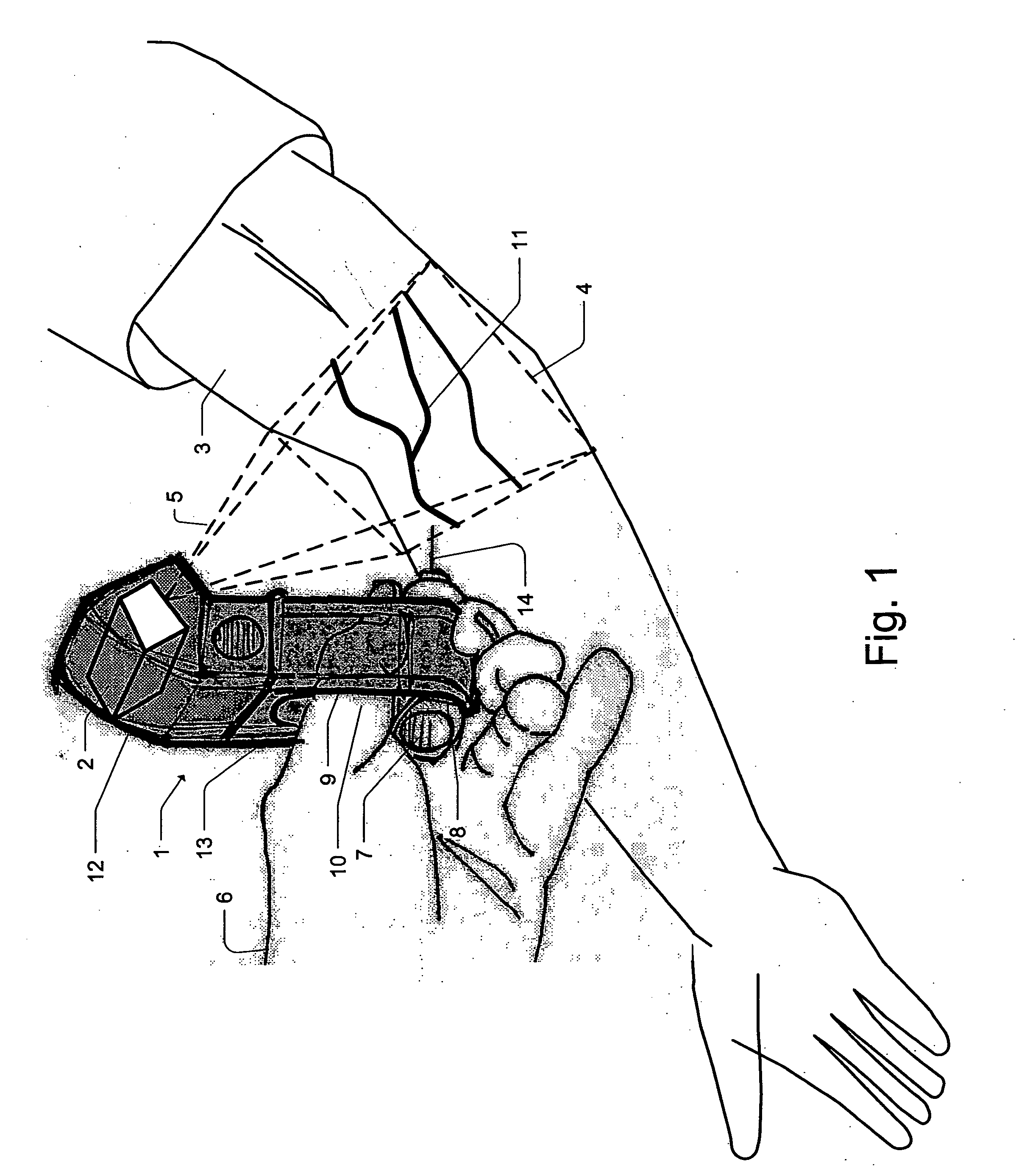

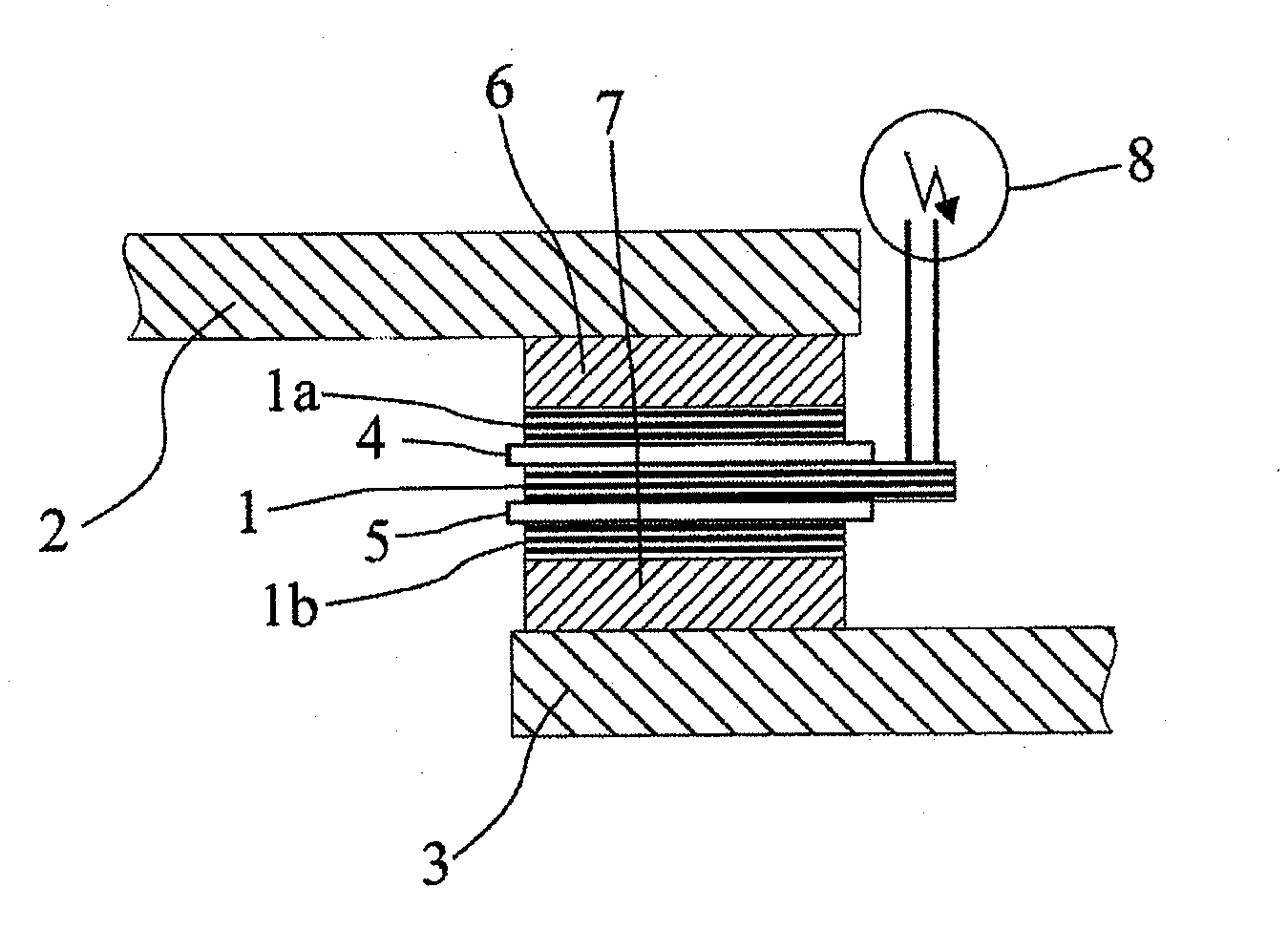

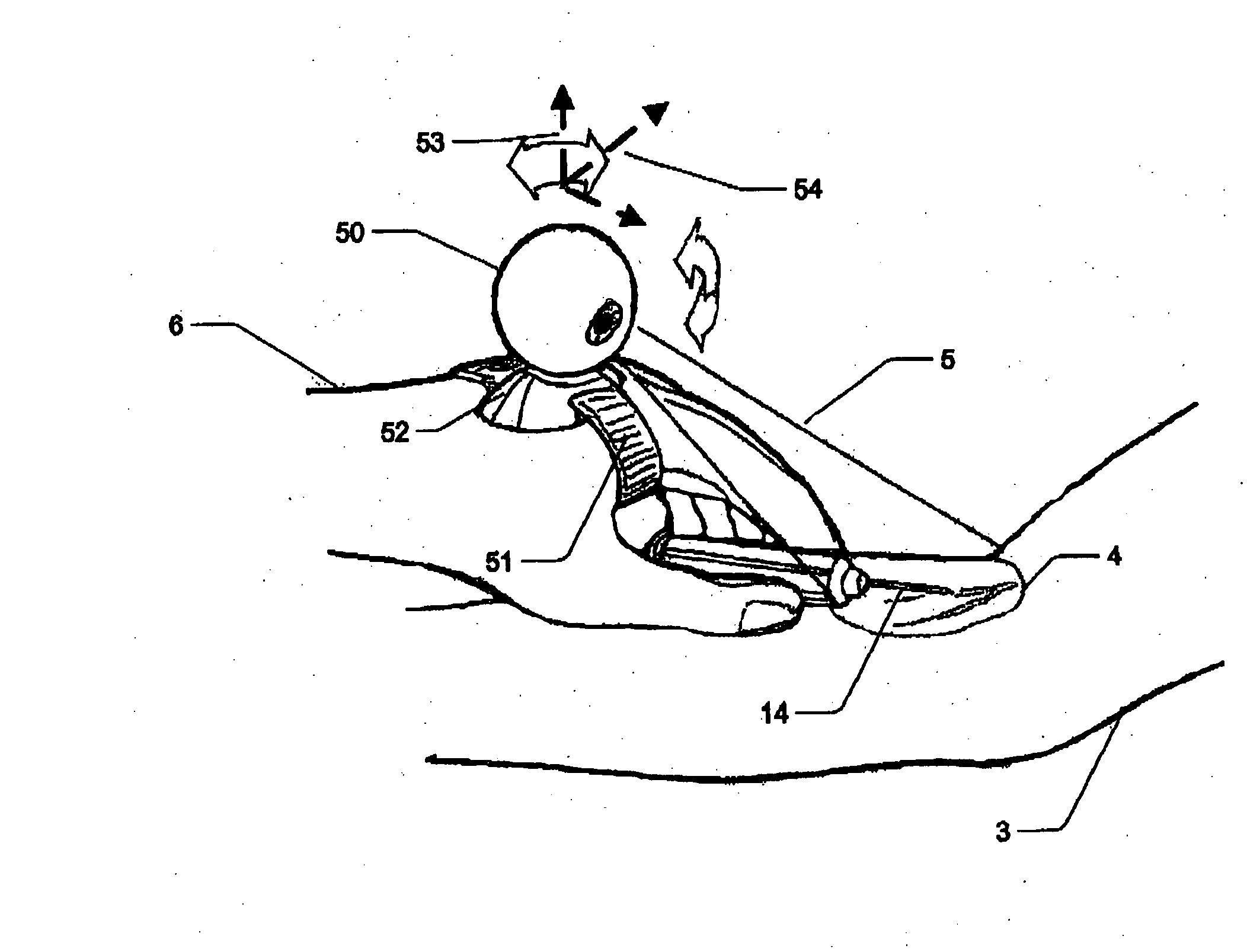

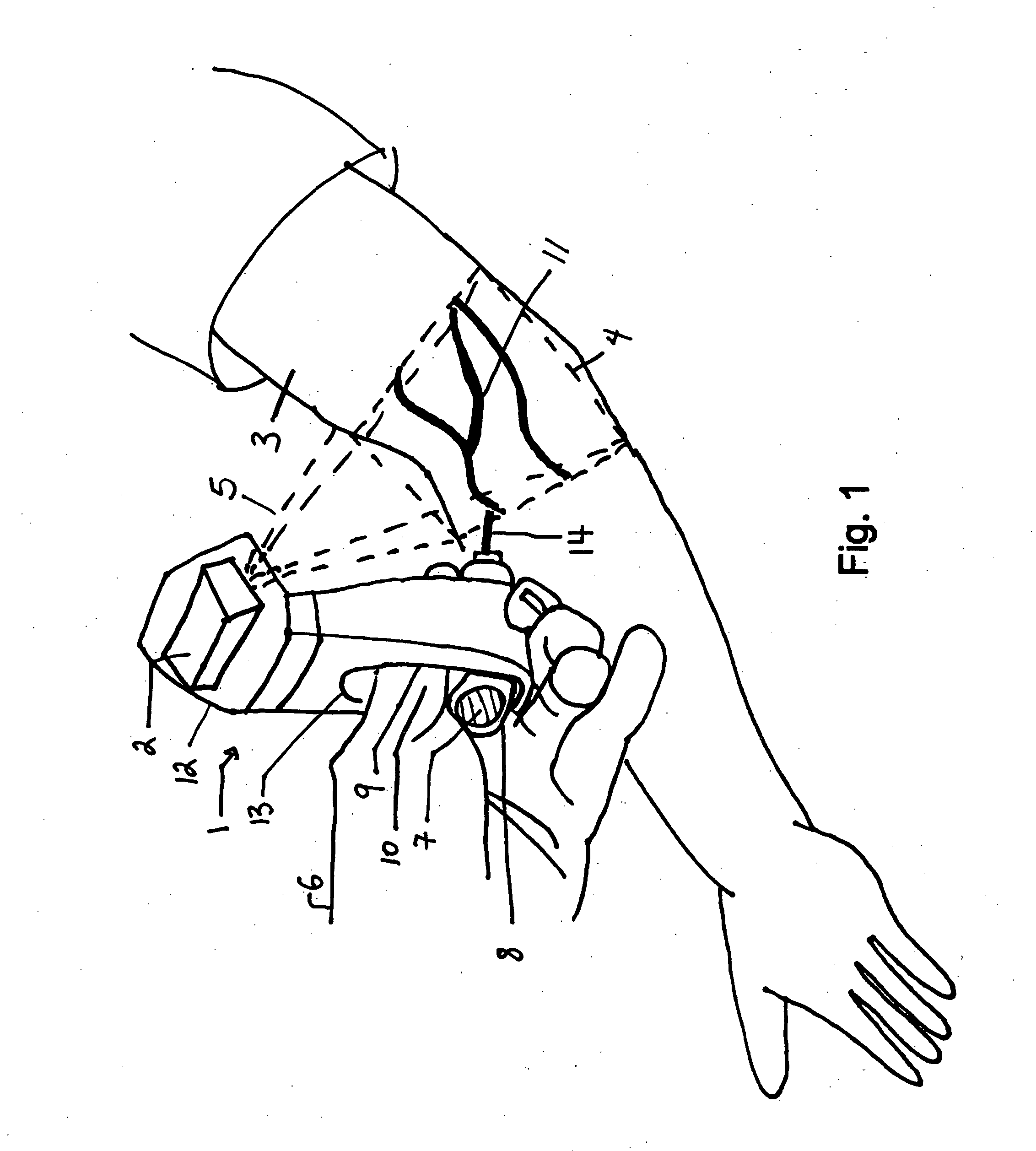

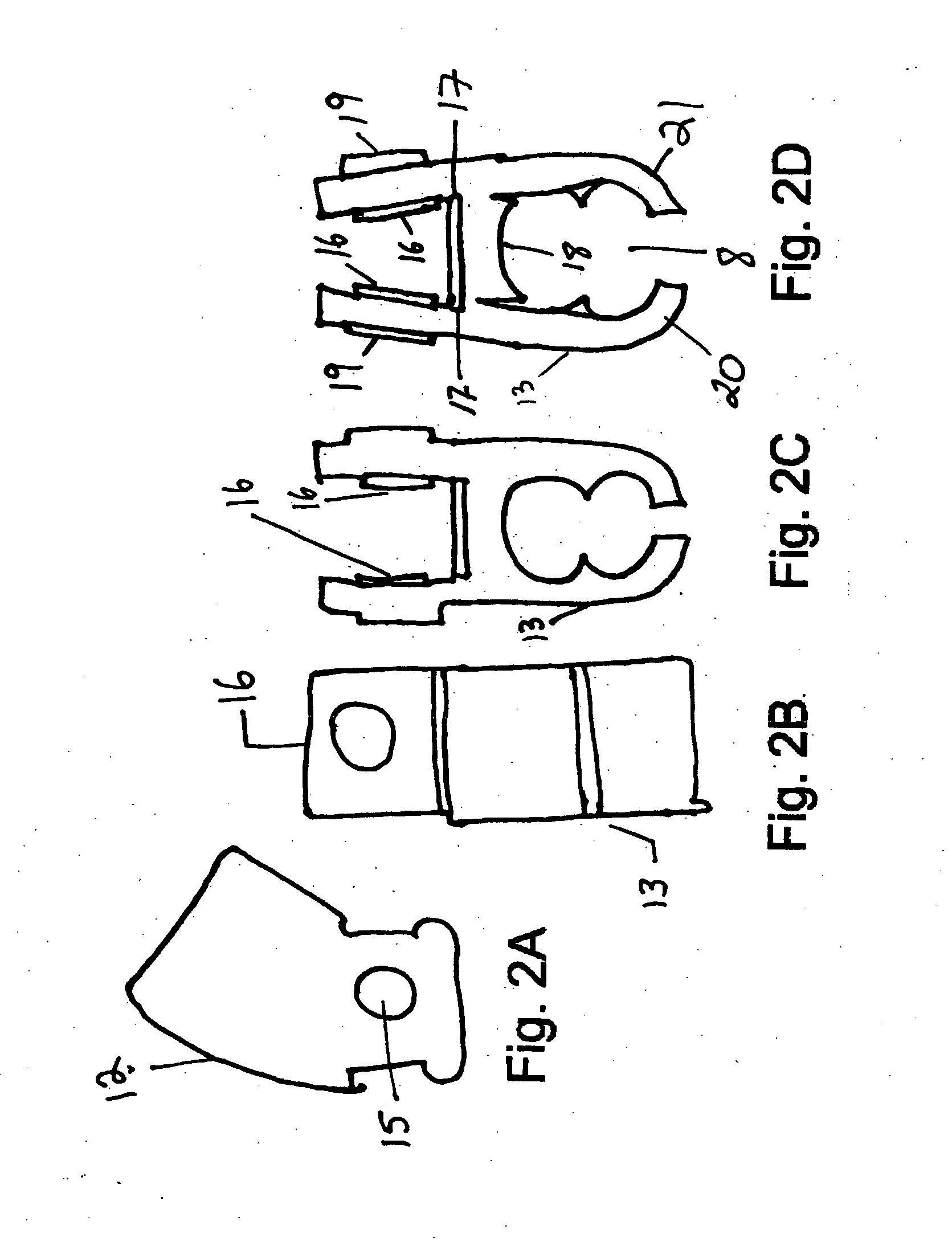

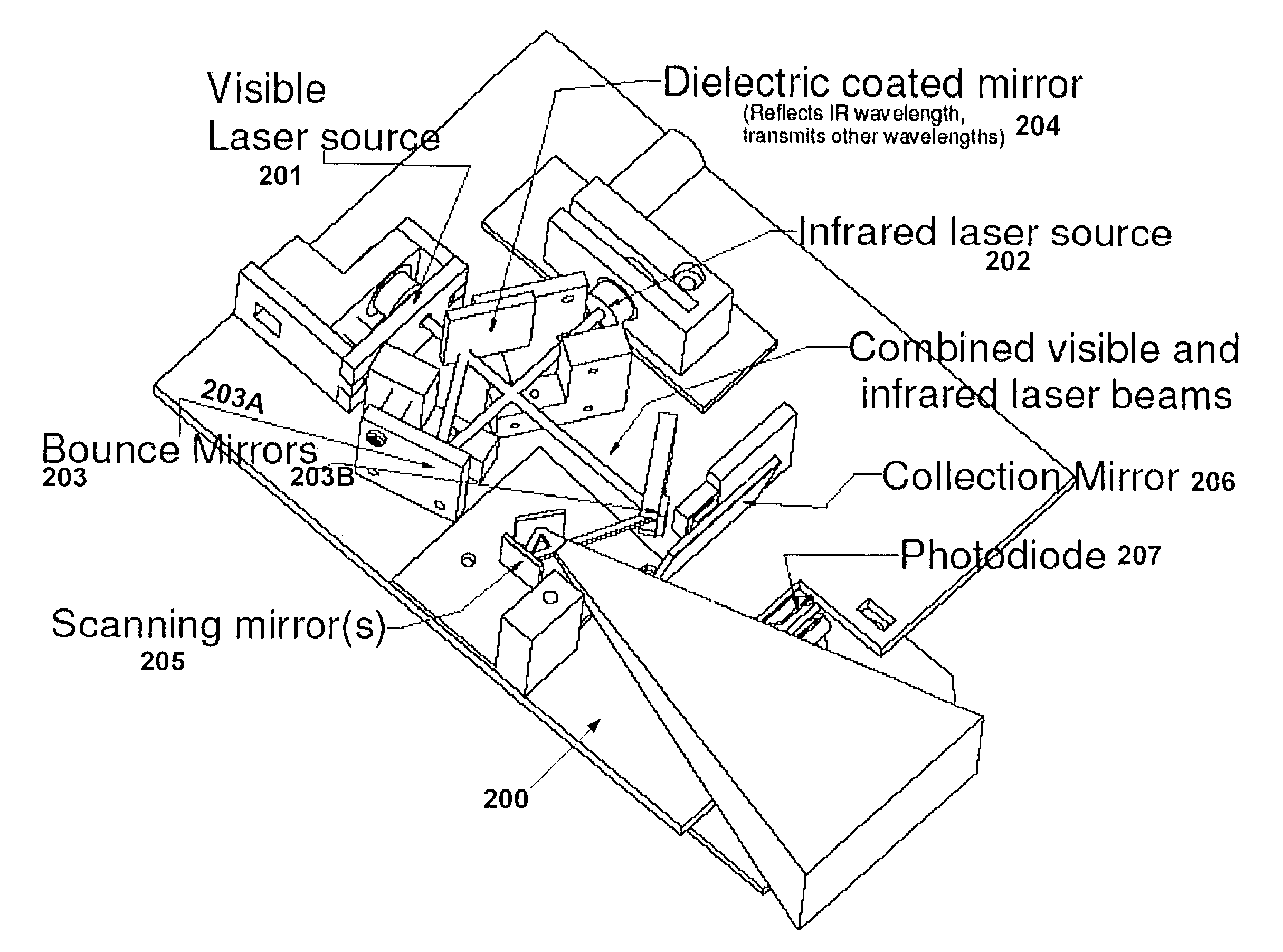

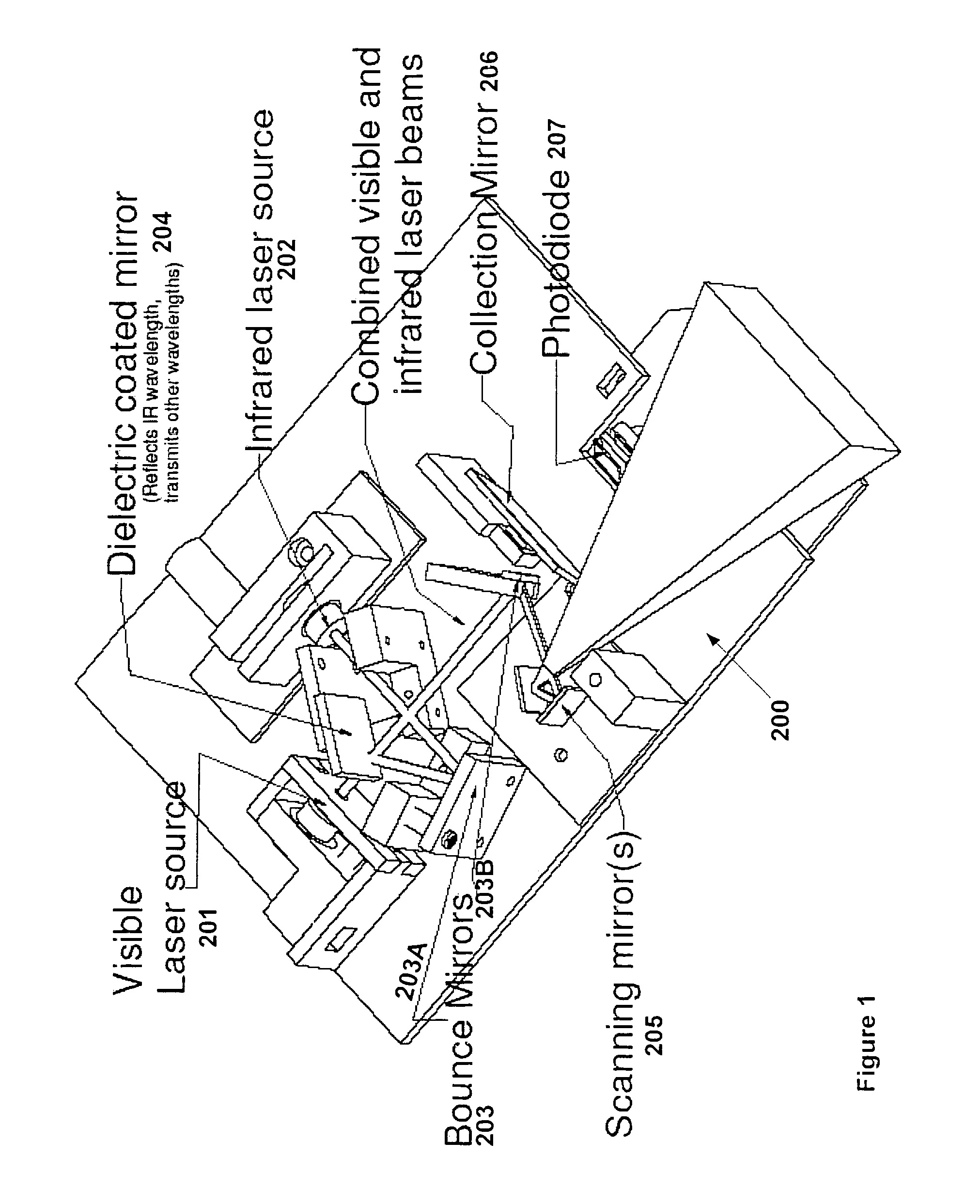

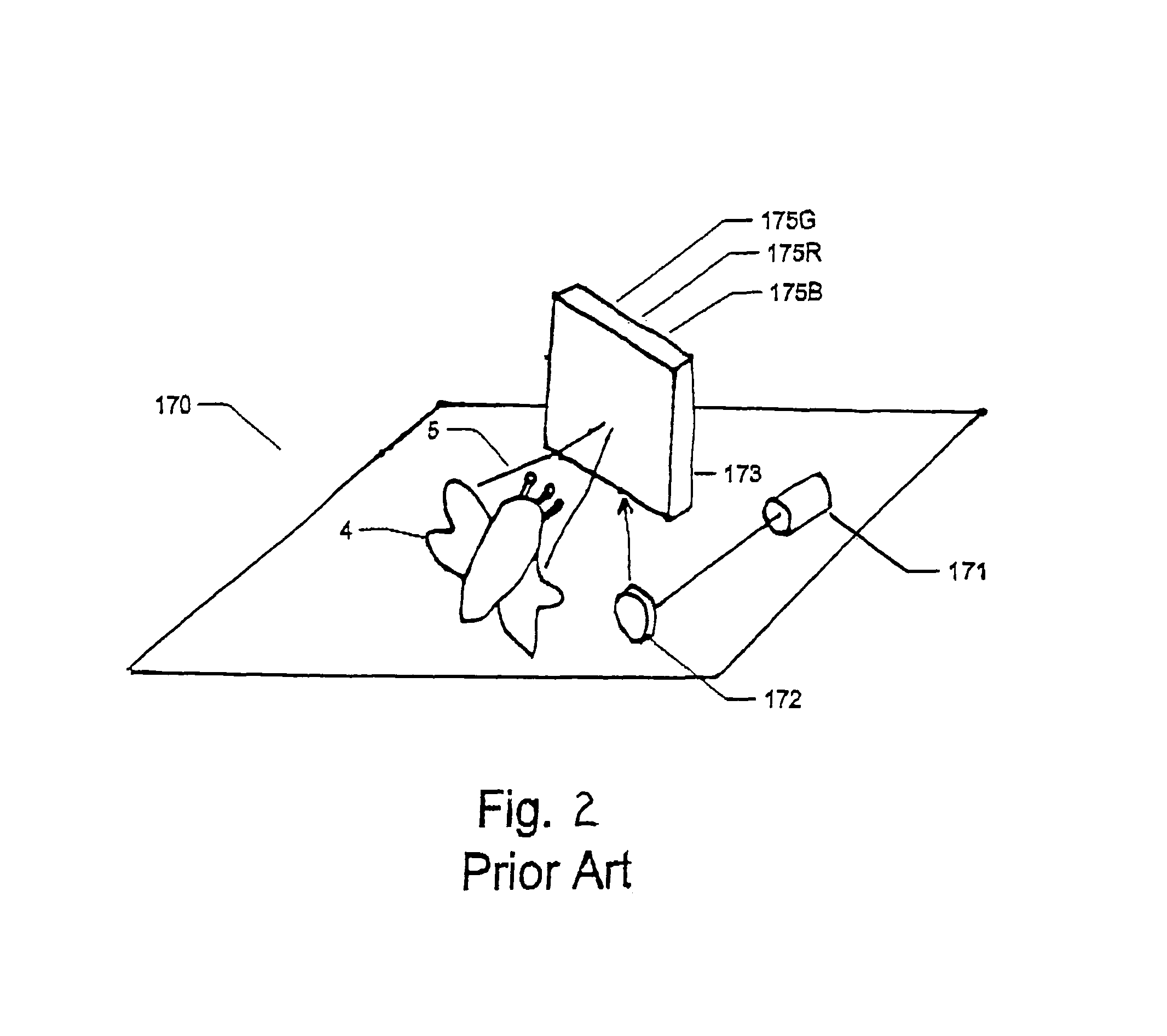

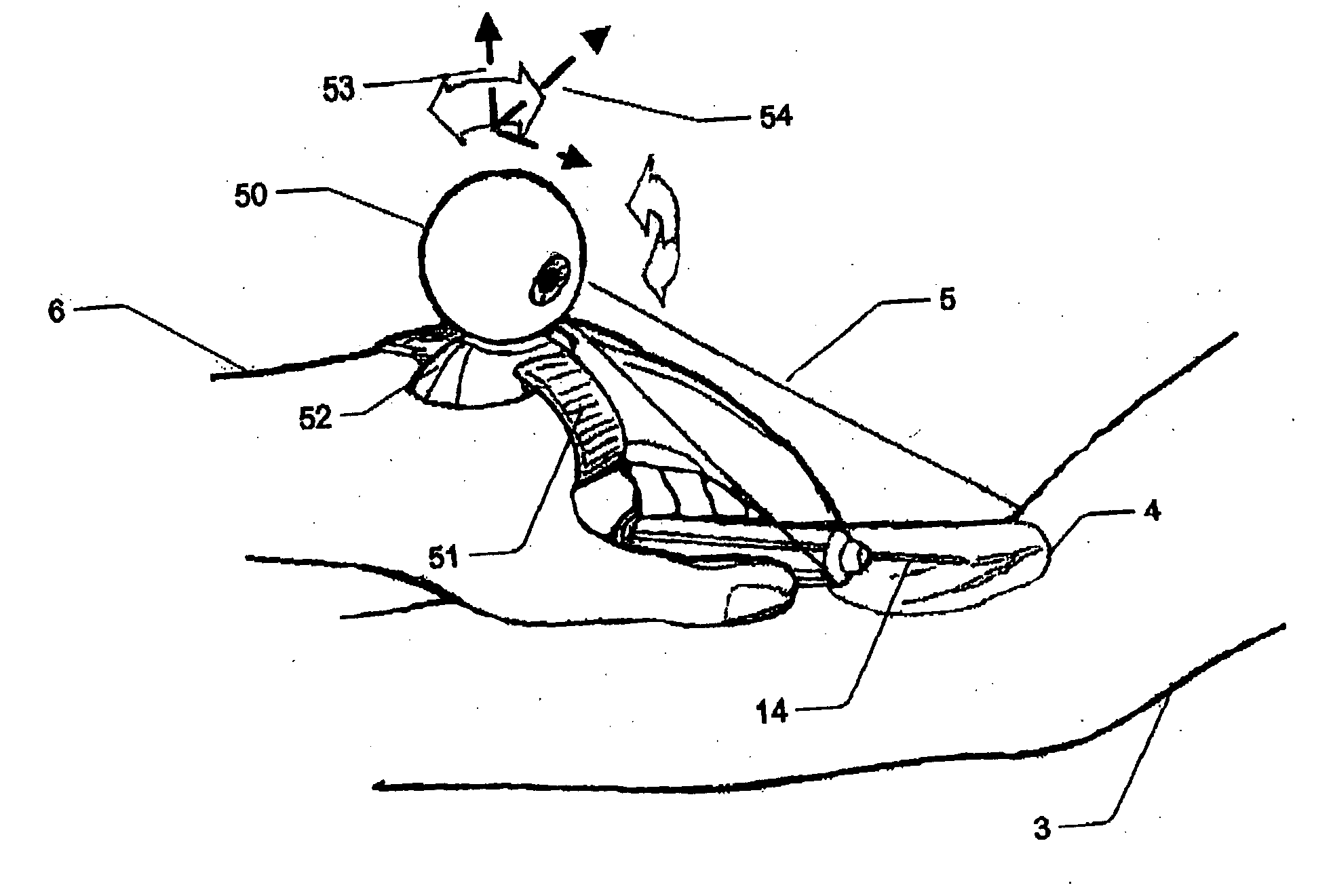

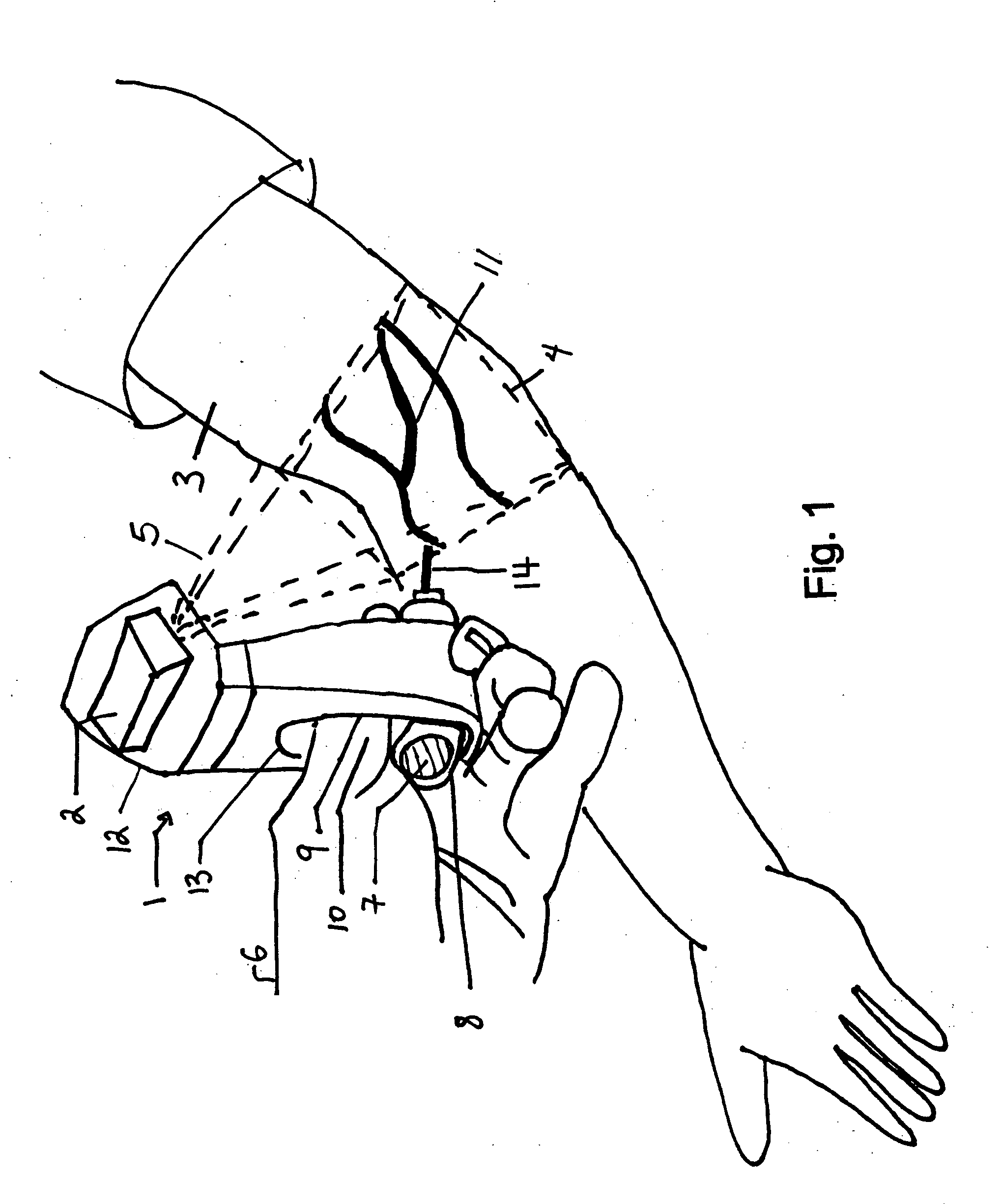

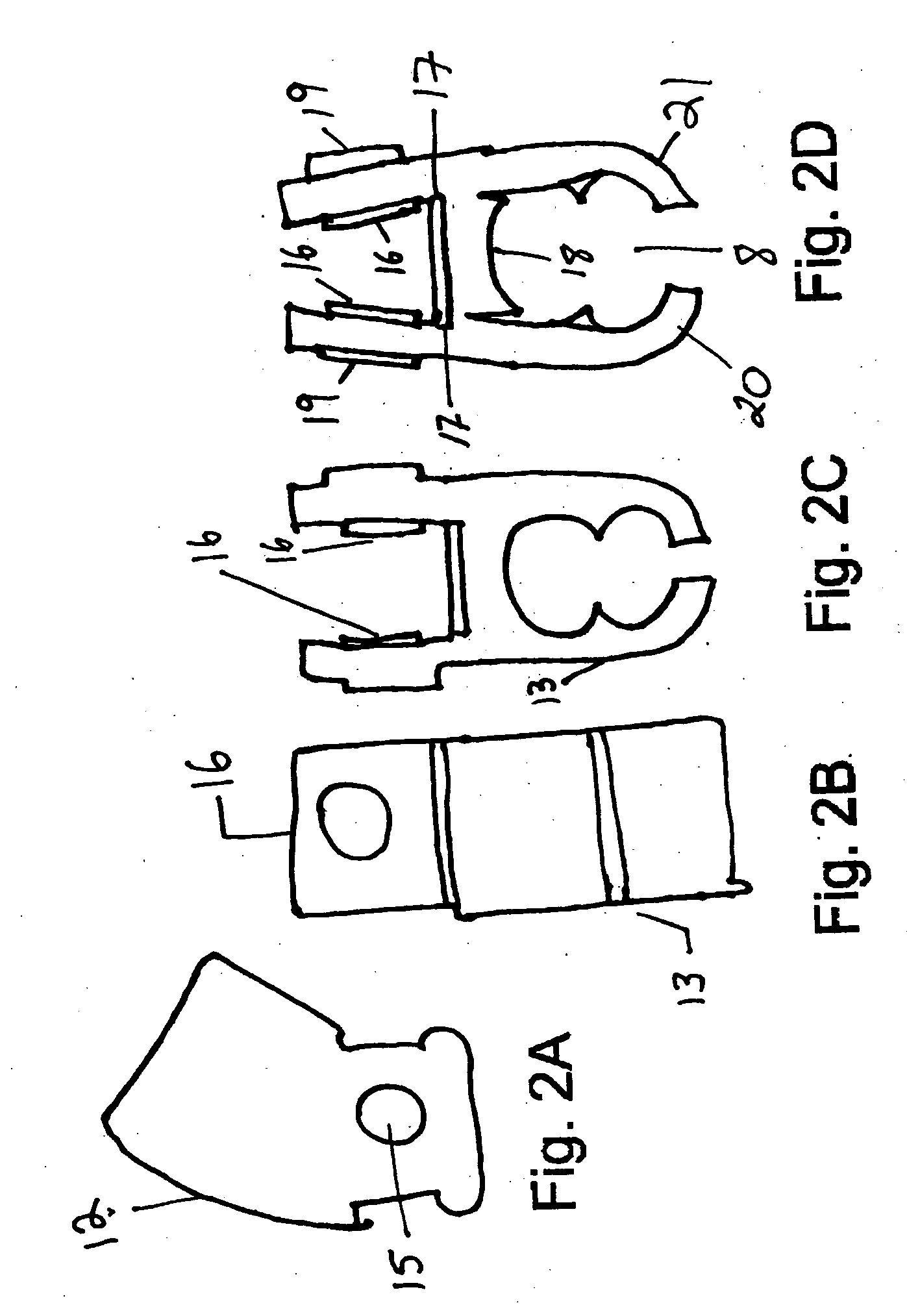

Micro vein enhancer

ActiveUS7904138B2Reduce impactExpand the scope of workImage analysisDiagnostics using lightVeinBlood test

The present invention is a Miniature Vein Enhancer that includes a Miniature Projection Head. The Miniature Projection Head may be operated in one of three modes, AFM, DBM, and RTM. The Miniature Projection Head of the present invention projects an image of the veins of a patient, which aids the practitioner in pinpointing a vein for an intravenous drip, blood test, and the like. The Miniature projection head may have a cavity for a power source or it may have a power source located in a body portion of the Miniature Vein Enhancer. The Miniature Vein Enhancer may be attached to one of several improved needle protectors, or the Miniature Vein Enhancer may be attached to a body similar to a flashlight for hand held use. The Miniature Vein Enhancer of the present invention may also be attached to a magnifying glass, a flat panel display, and the like.

Owner:ACCUVEIN

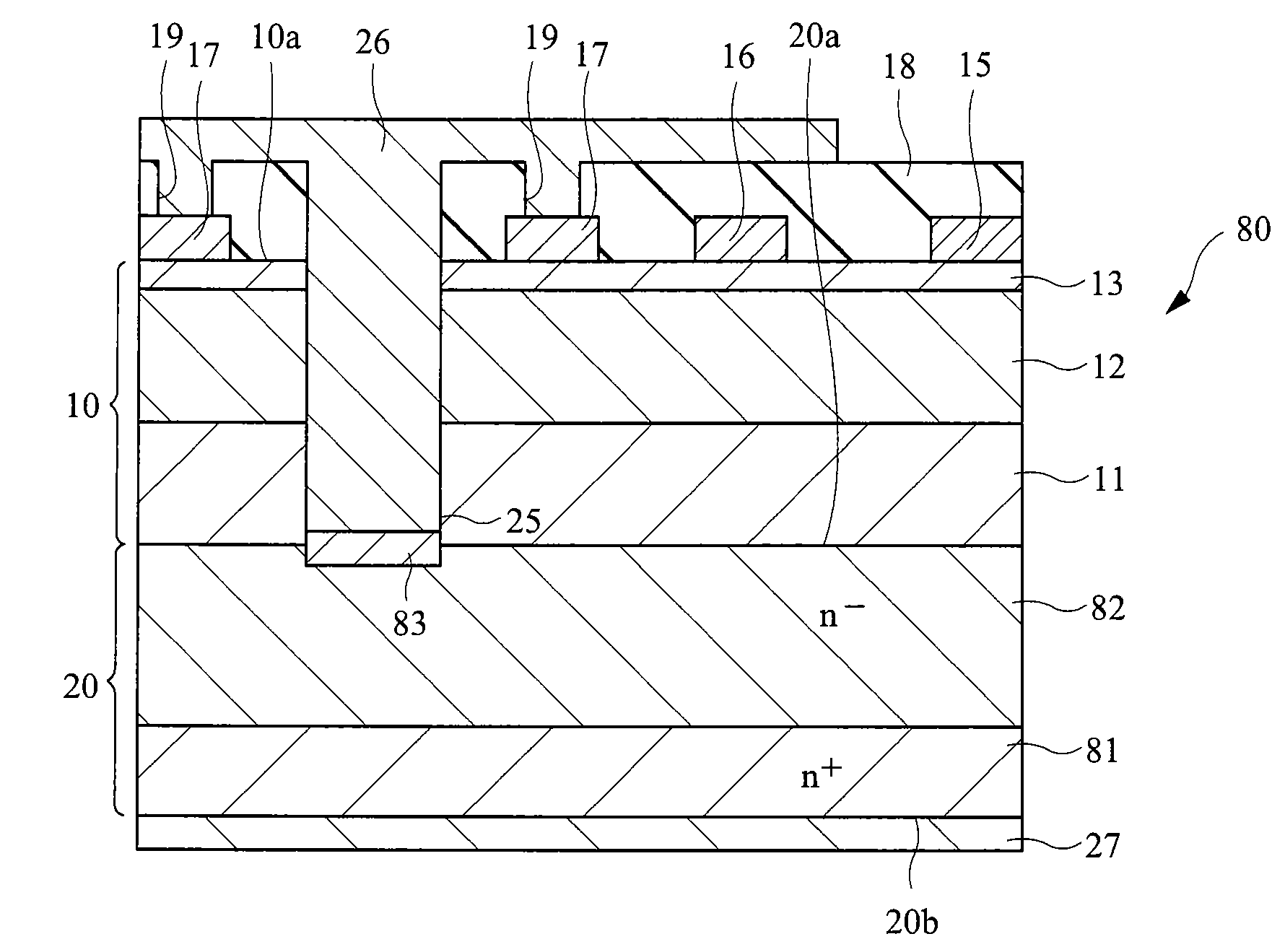

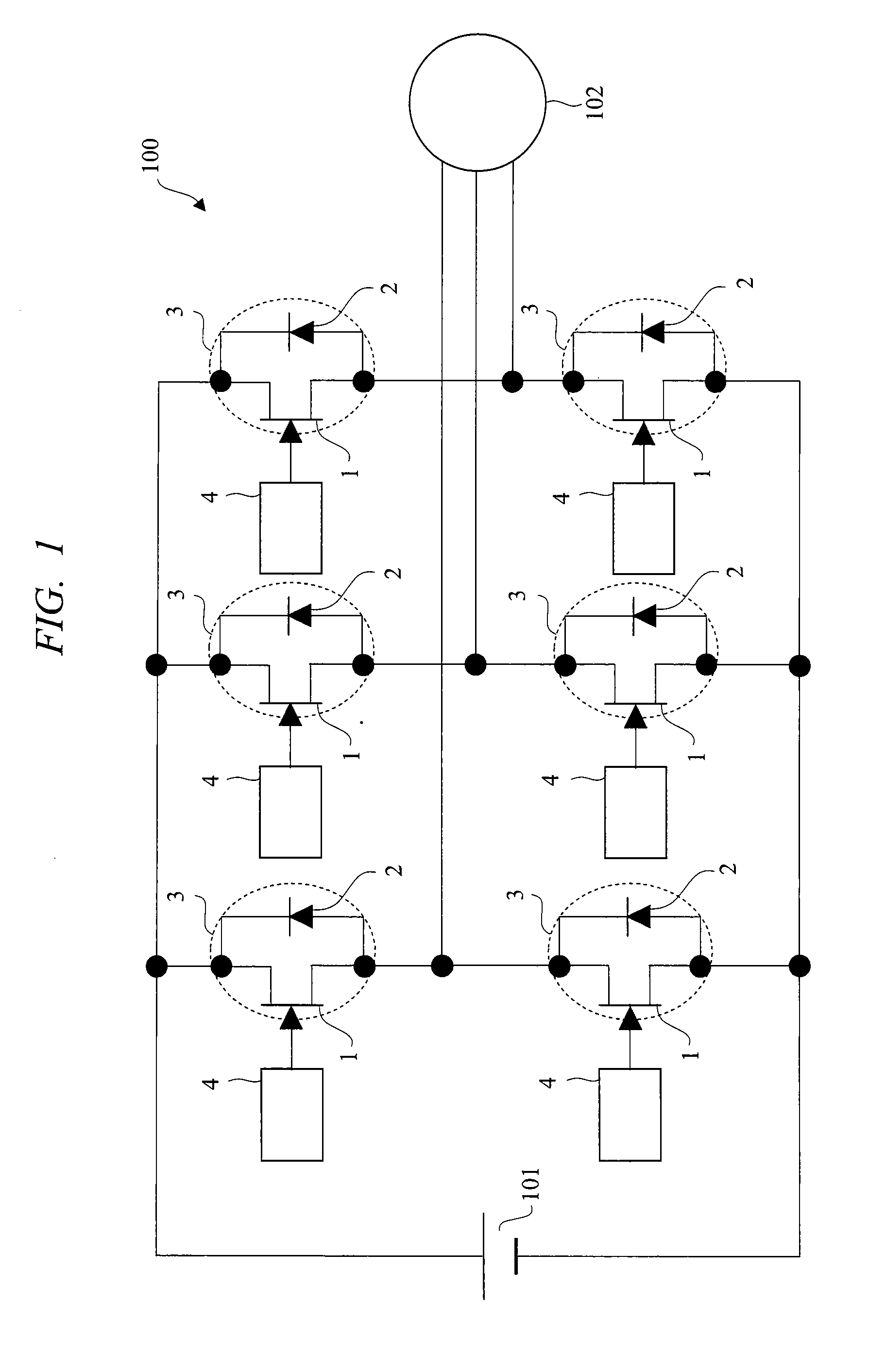

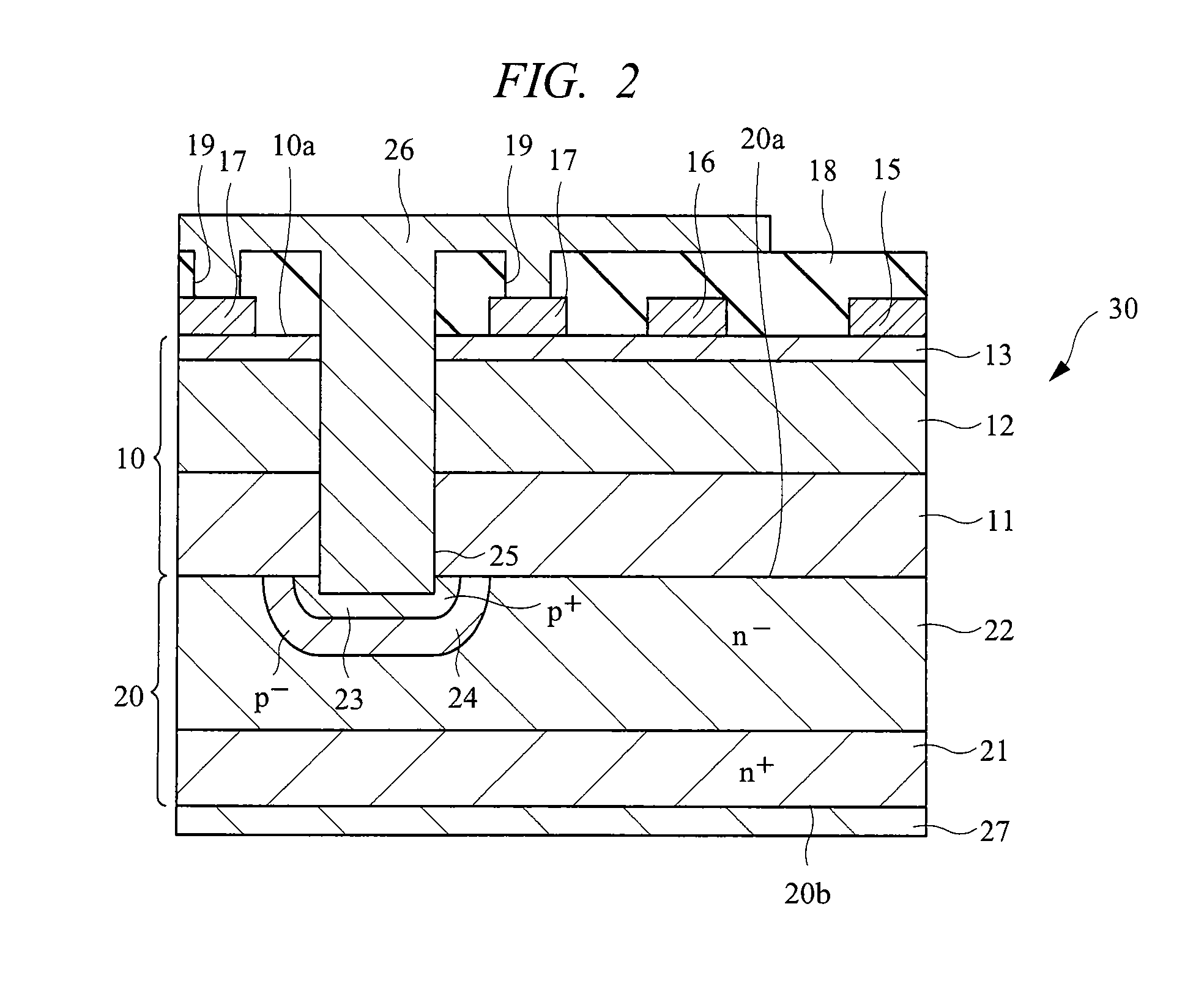

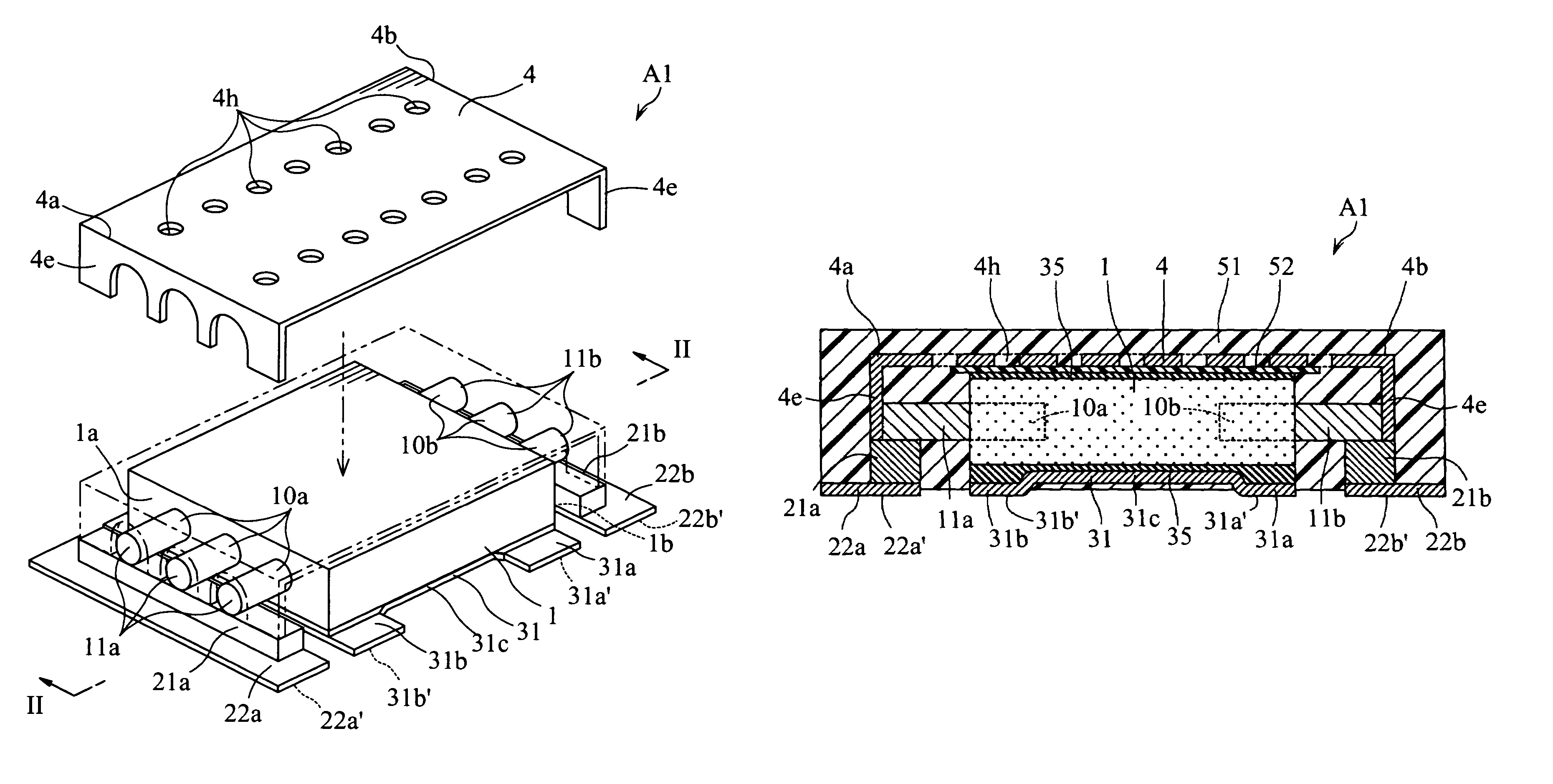

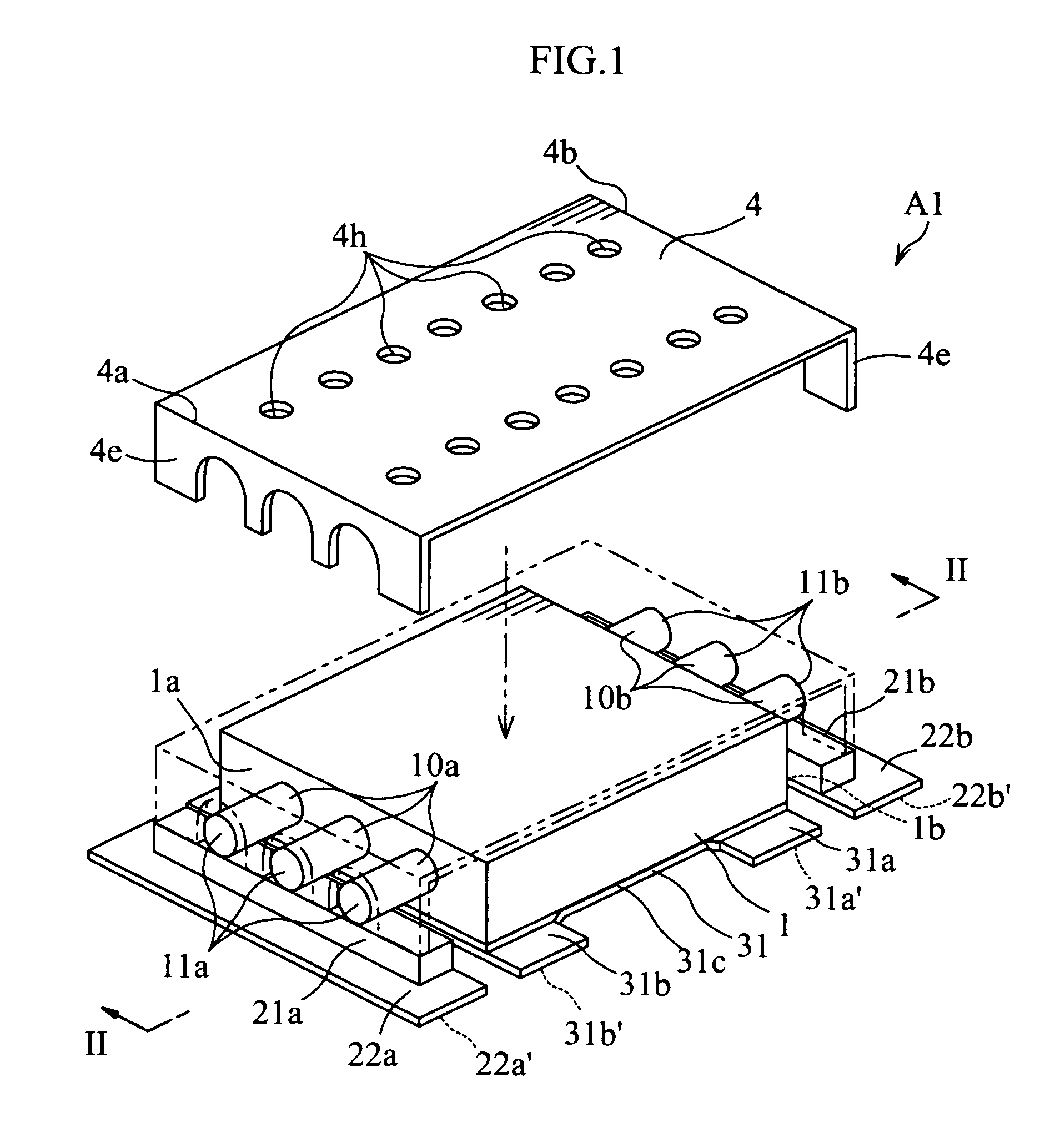

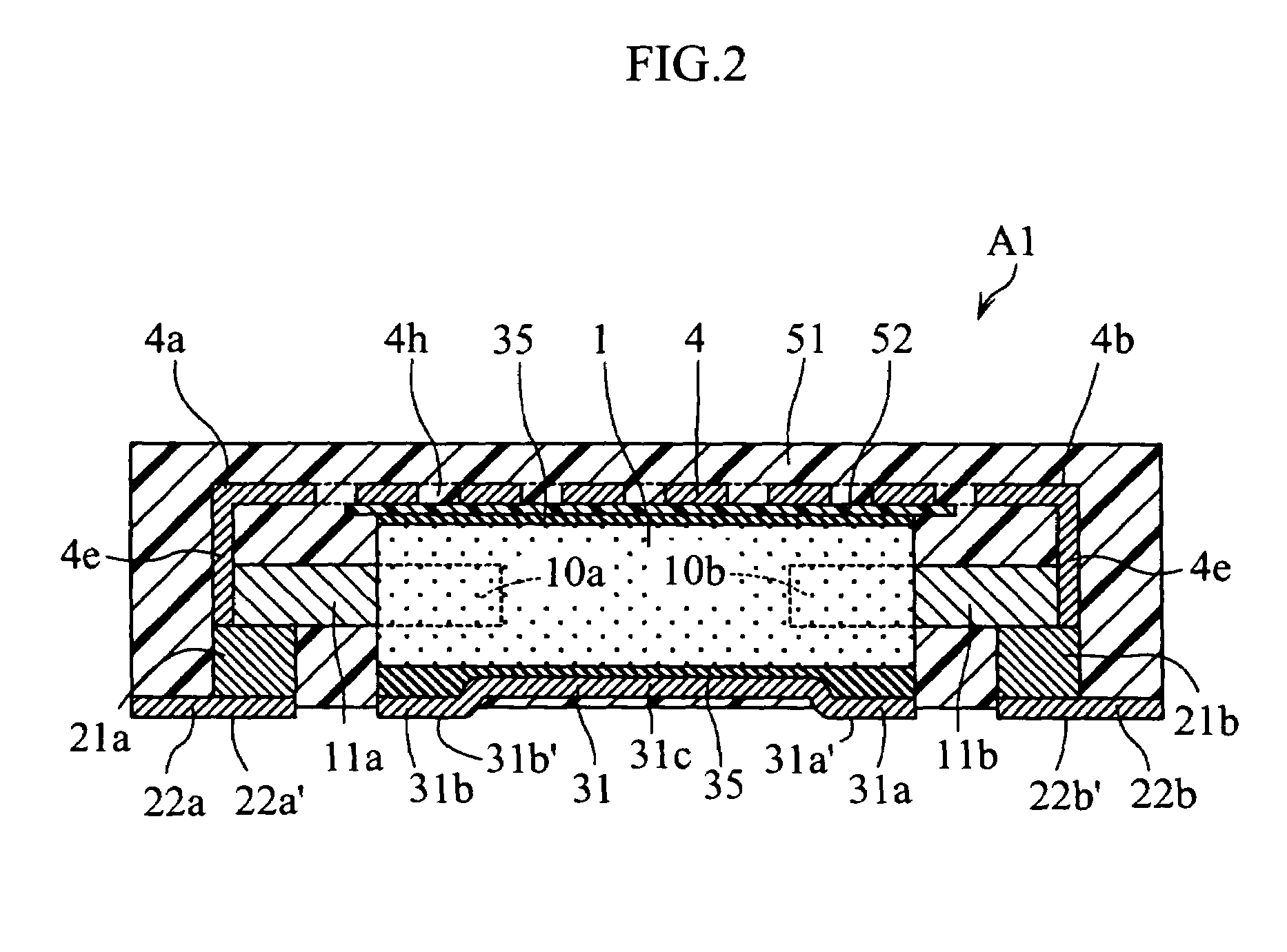

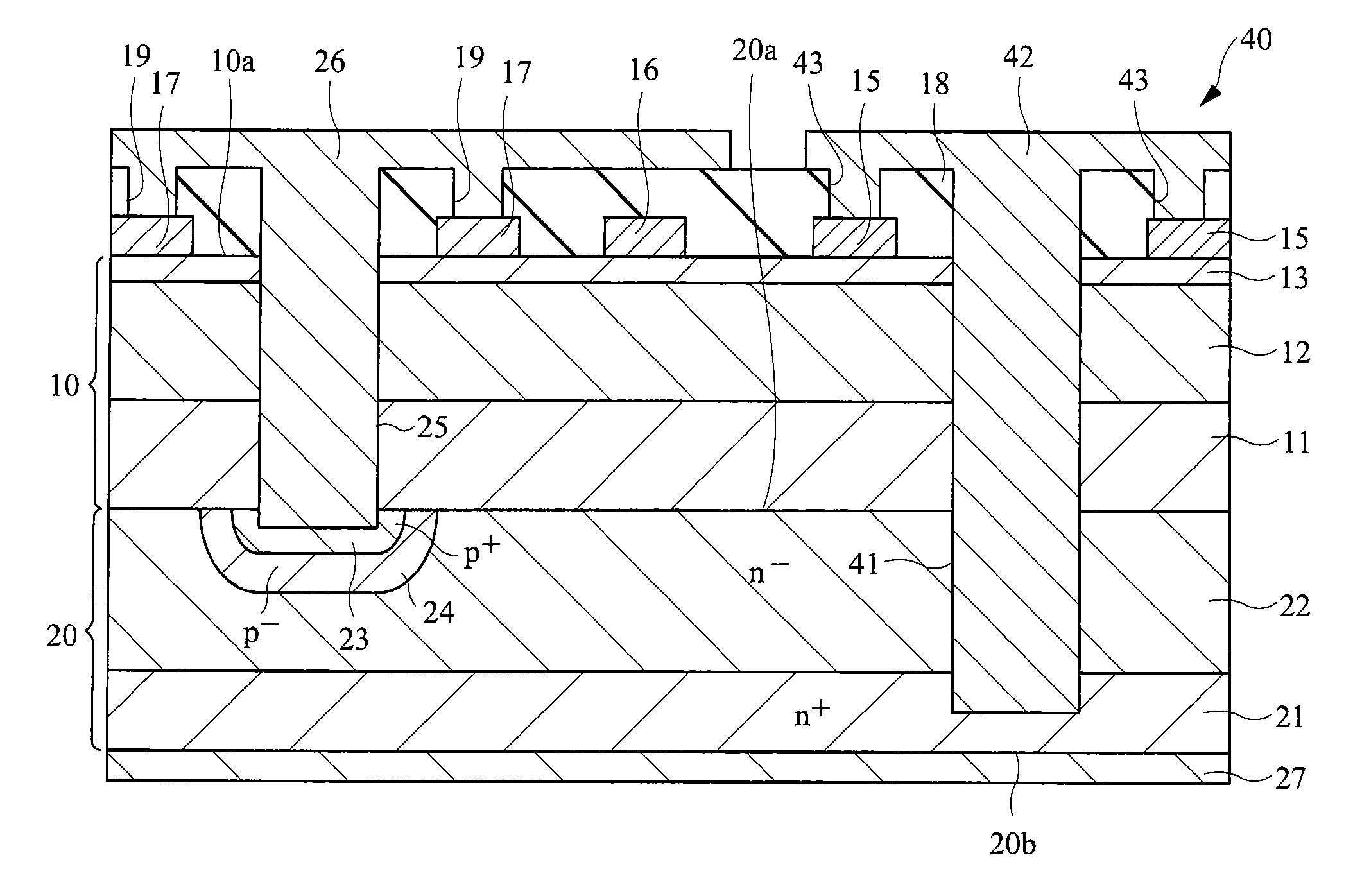

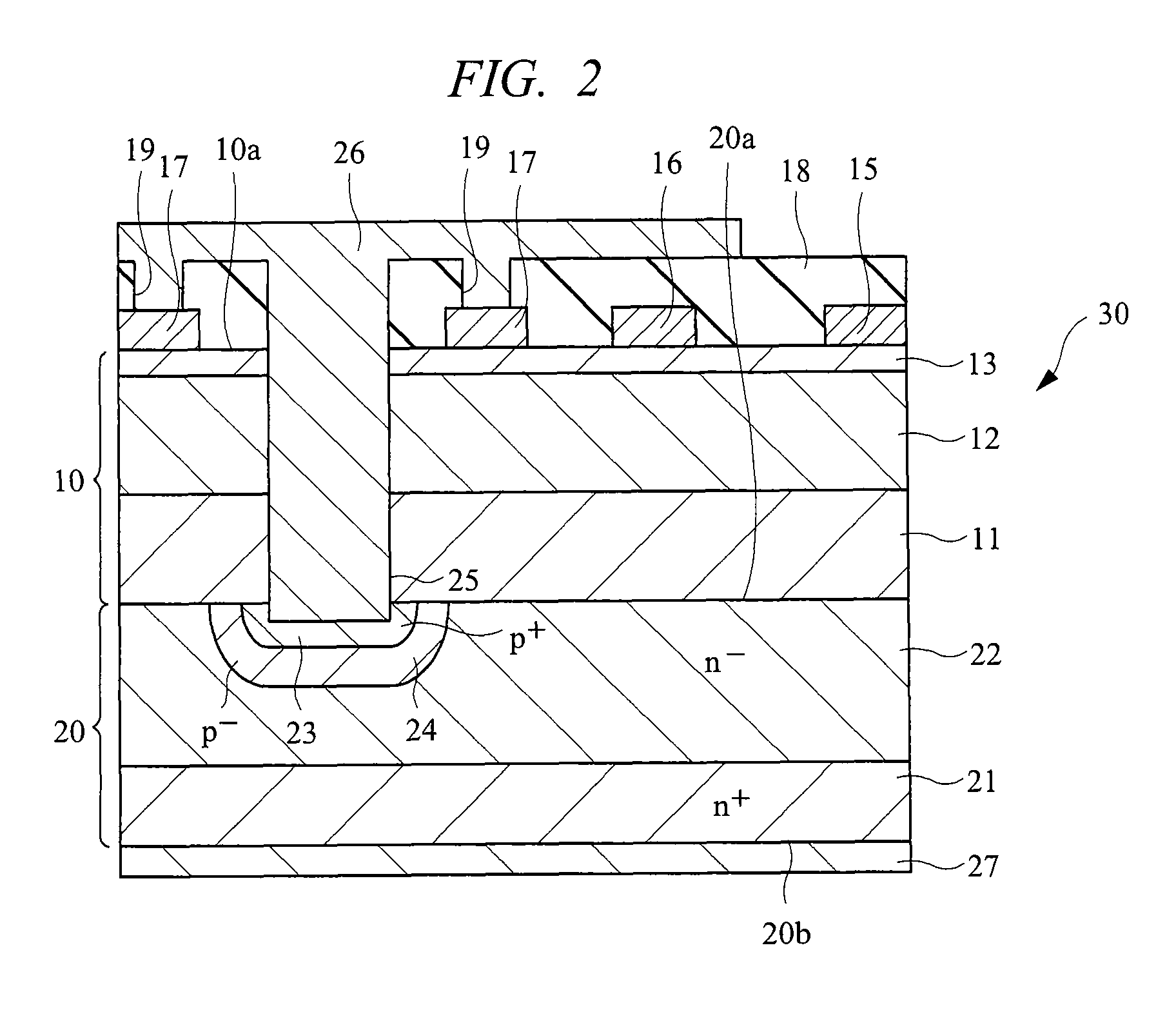

Semiconductor device and power conversion device using the same

ActiveUS20080315257A1Large switching lossIncreased power lossTransistorSolid-state devicesDevice materialSemiconductor chip

In a semiconductor device in which a diode and a high electron mobility transistor are incorporated in the same semiconductor chip, a compound semiconductor layer of the high electron mobility transistor is formed on a main surface (first main surface) of a semiconductor substrate of the diode, and an anode electrode of the diode is electrically connected to an anode region via a conductive material embedded in a via hole (hole) reaching a p+ region which is the anode region of the main surface of the semiconductor substrate from a main surface of the compound semiconductor layer.

Owner:RENESAS ELECTRONICS CORP

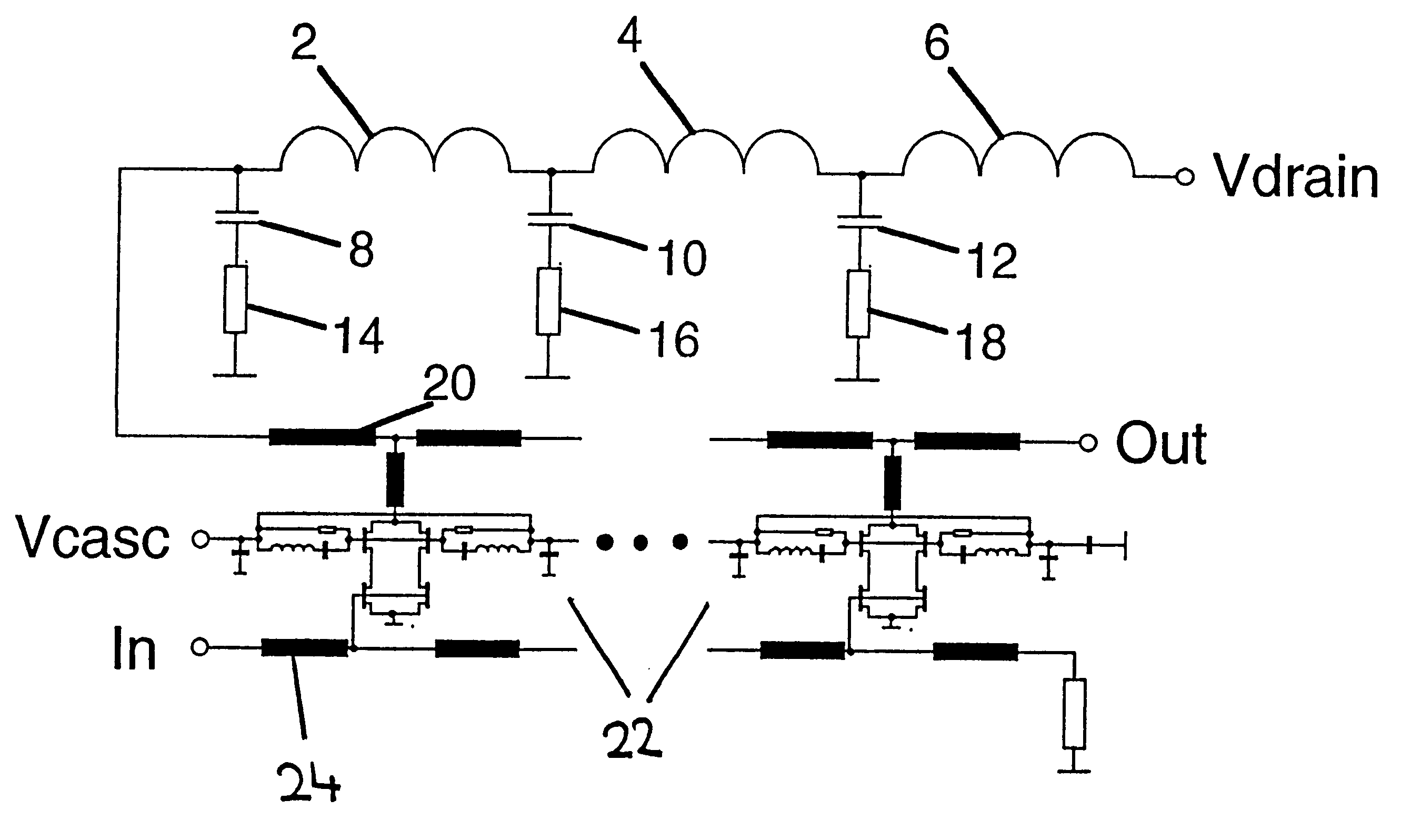

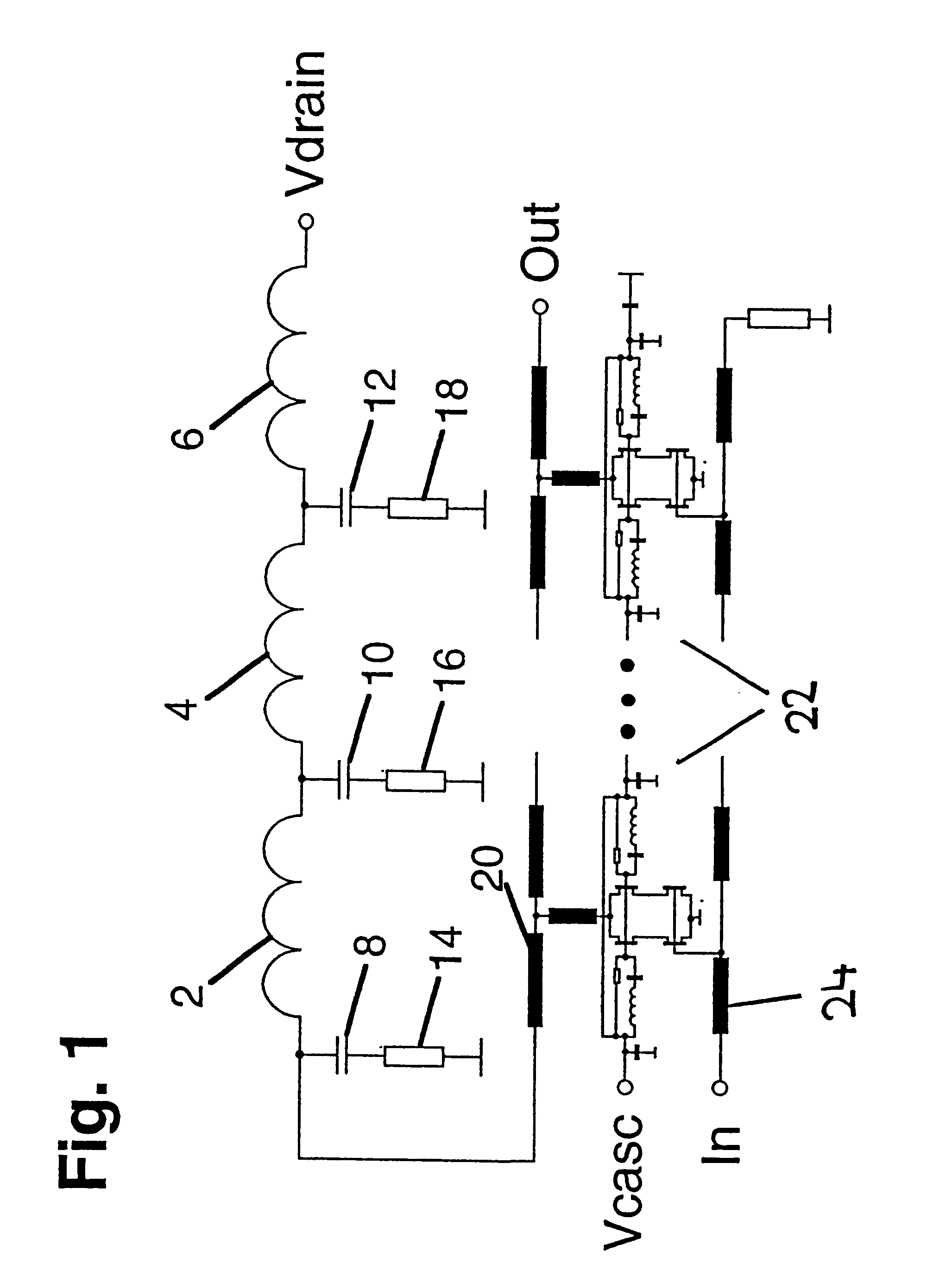

Supply voltage decoupling device for HF amplifier circuits

InactiveUS6653903B2Inhibit currentLittle power lossAmplifier modifications to reduce temperature/voltage variationAmplifiers wit coupling networksElectrical resistance and conductanceDistributed amplifier

A device for decoupling a supply voltage for HF amplifier circuits is described which includes an output line for coupling out an amplified signal, wherein one end of the output line, which is not used for coupling out signals, is connected to a circuit element designed as decoupling circuit. The circuit element has a low ohmic d.c. resistance and presents an HF-power absorption capacity that increases as the frequency increases, thus constituting a reflection-free termination for high frequencies. The circuit element is preferably constituted by several discrete subcircuits connected in succession. The device permits the operation of integrated distributed amplifiers of high performance at a low power loss caused by the decoupling circuit.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

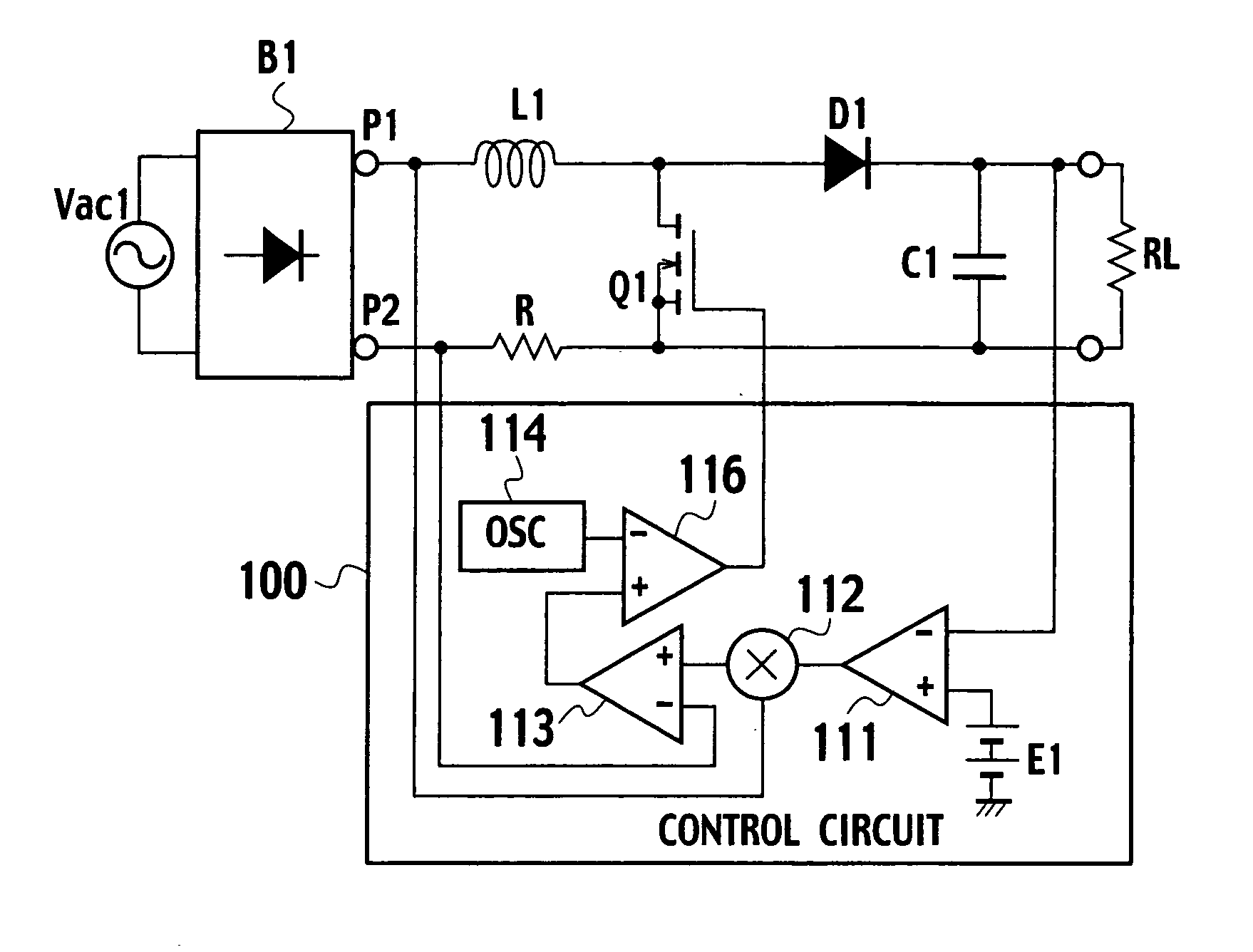

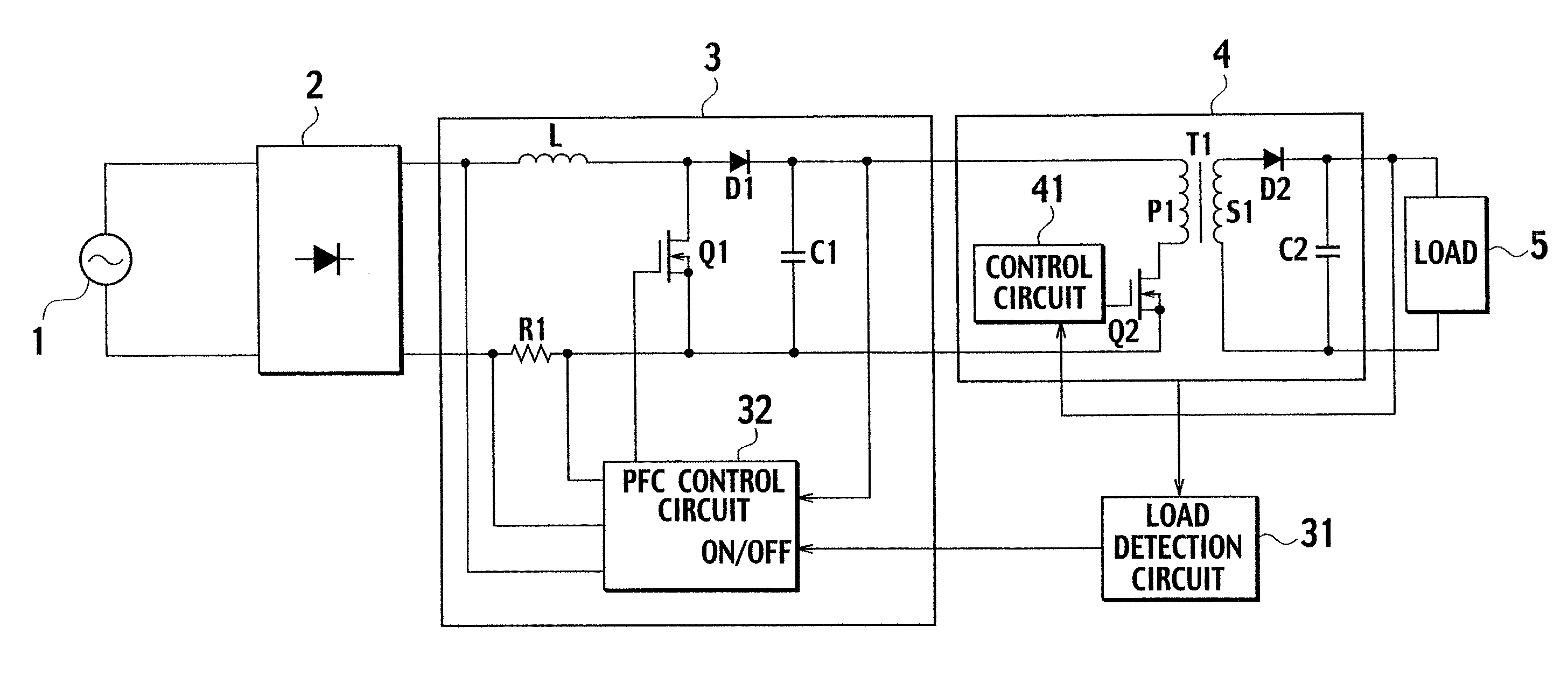

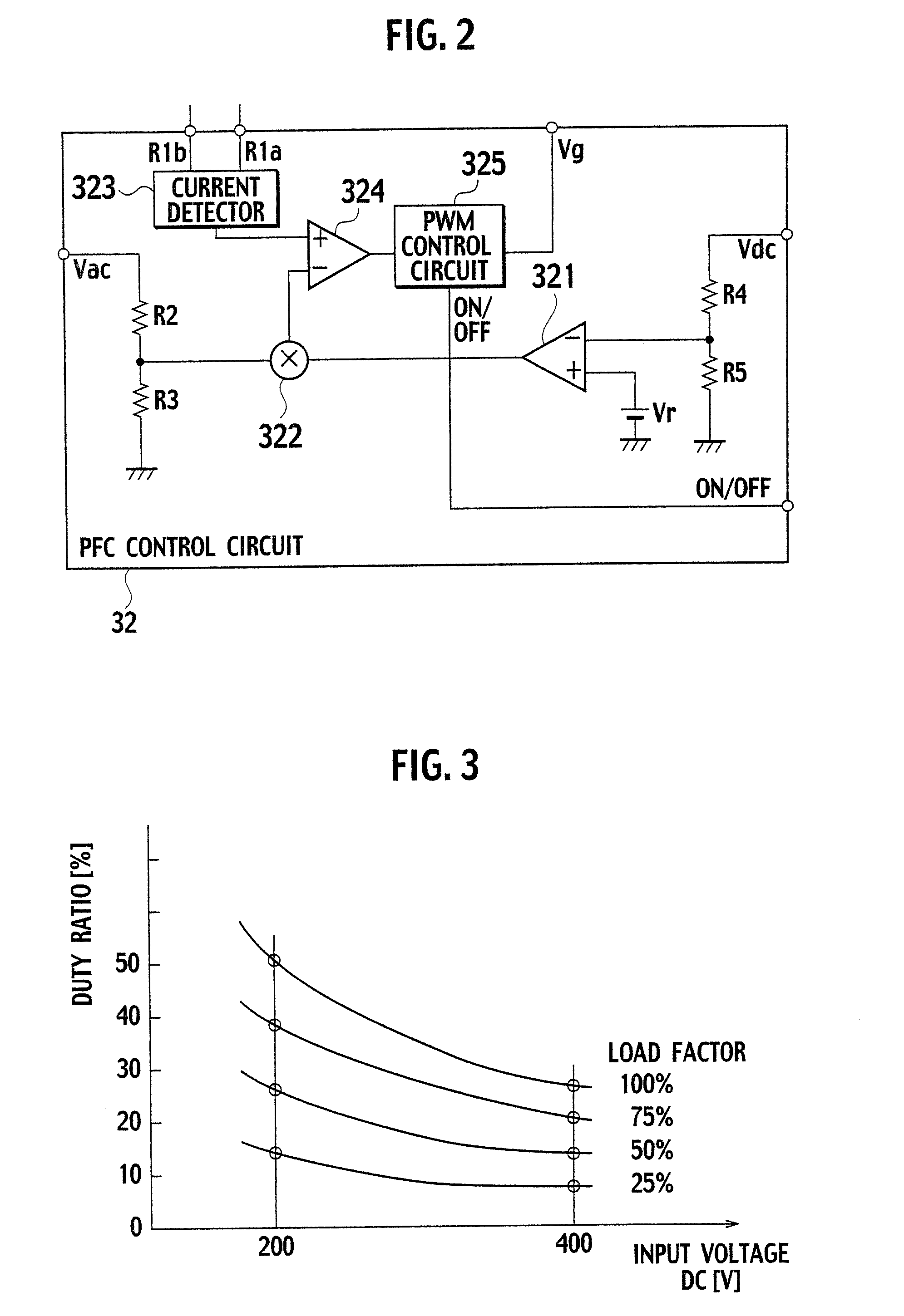

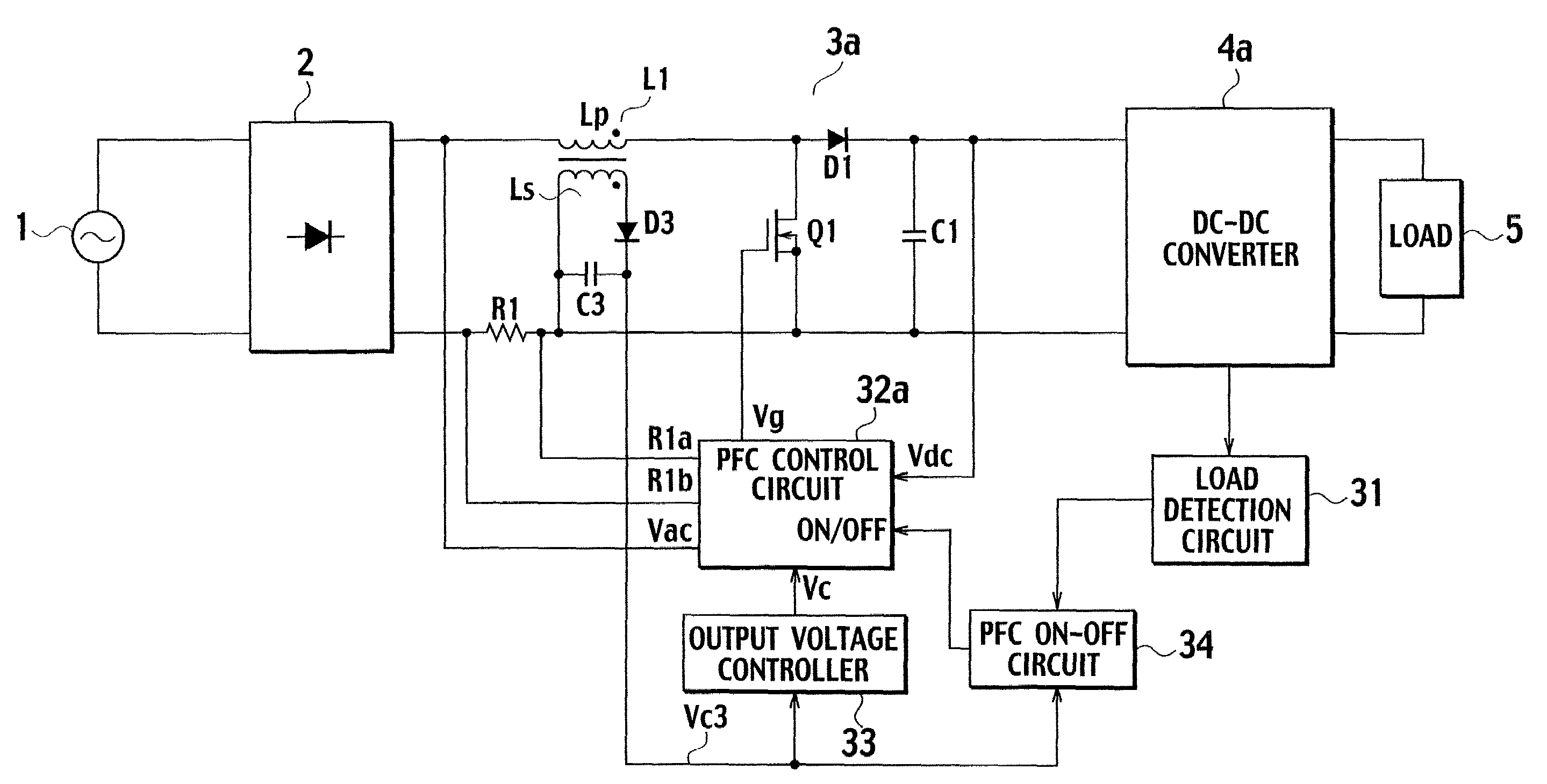

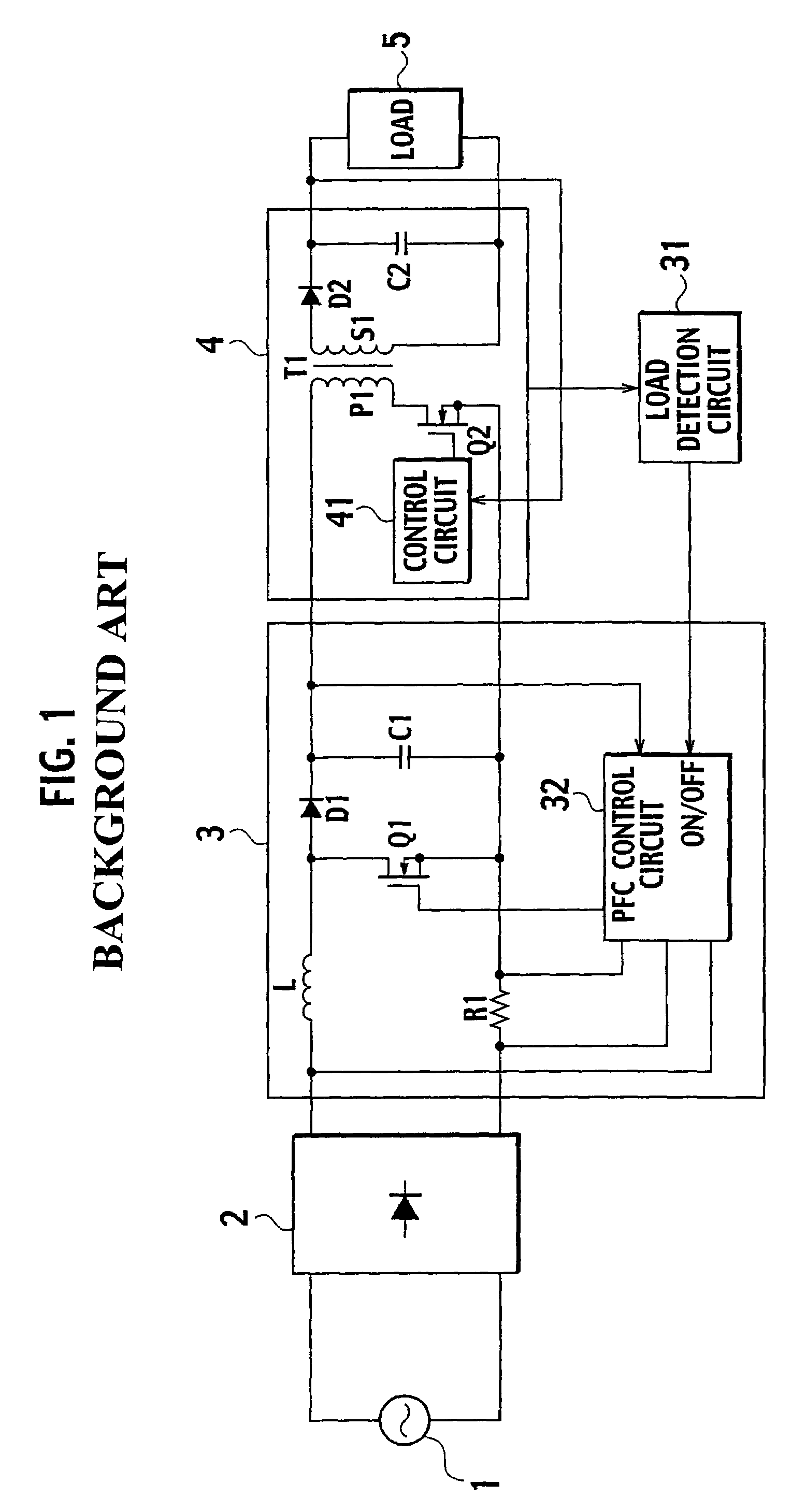

Switching power supply device

InactiveUS20070145956A1Improve power conversion efficiencyImprove conversion efficiencyEfficient power electronics conversionElectric variable regulationDc dc converterEngineering

A switching power supply device has a boost power converter which converts a wide range of AC input voltages into a DC voltage larger than an amplitude of the AC input voltage to supply to a DC-DC converter. The switching power supply device includes a load detection circuit, an input voltage detection circuit, and a power conversion controller for the boost power converter. The power conversion controller corrects the determination reference value in accordance with the AC input voltage detected in the input voltage detection circuit. When a light load is detected based on a comparison between the corrected determination reference value and the detection value output from the load detection circuit, the controller disables the boost power converter.

Owner:SANKEN ELECTRIC CO LTD

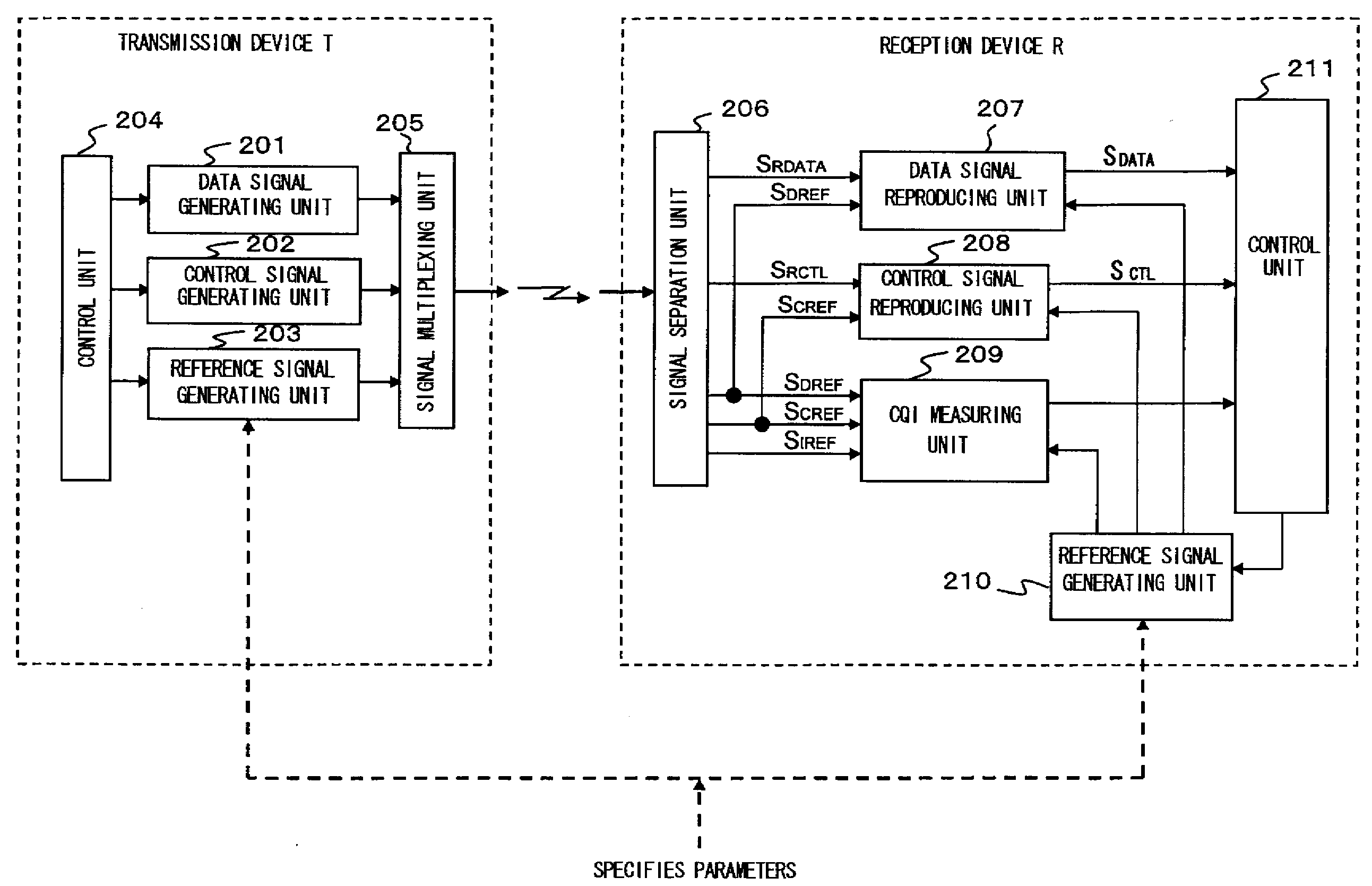

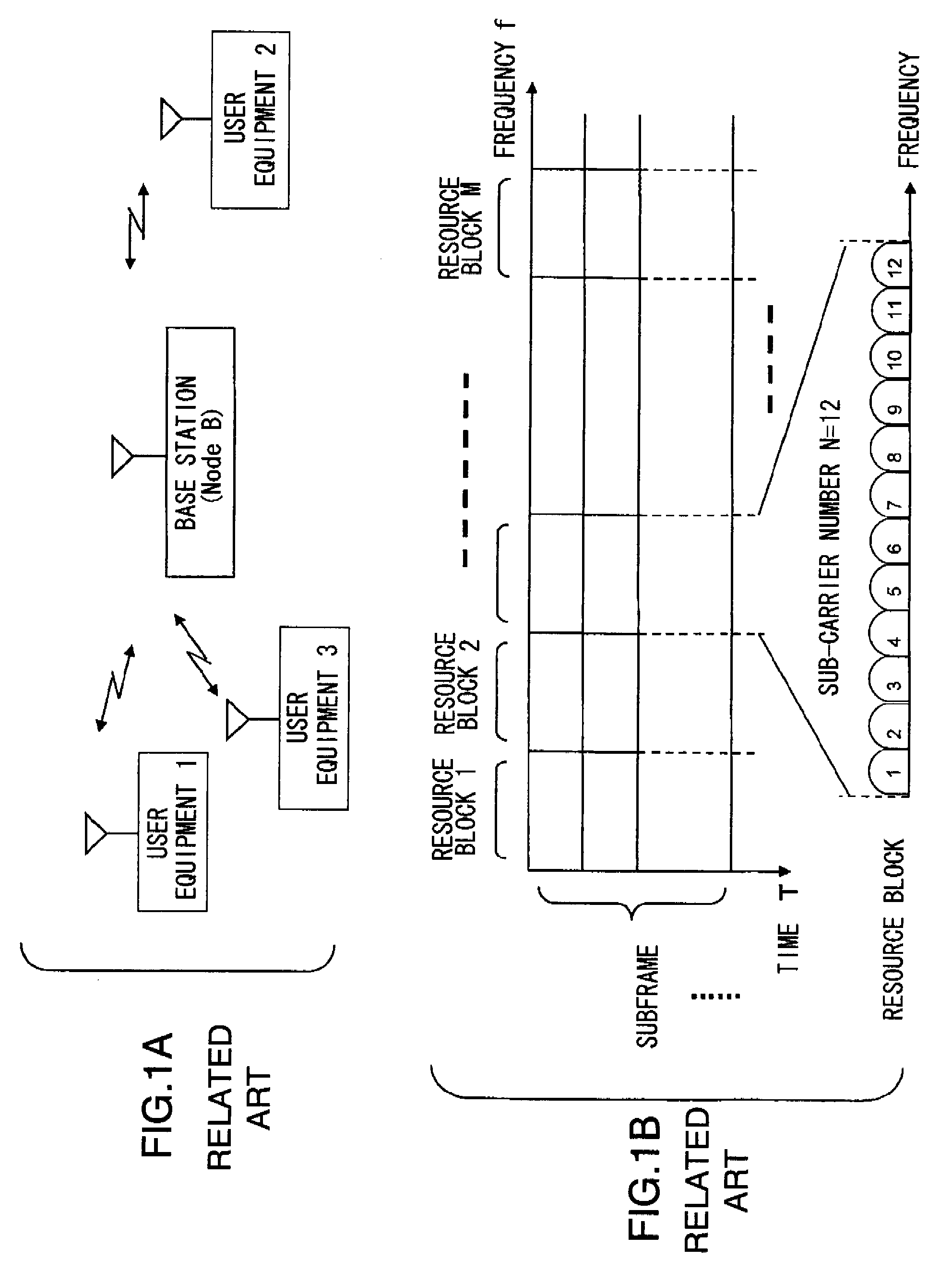

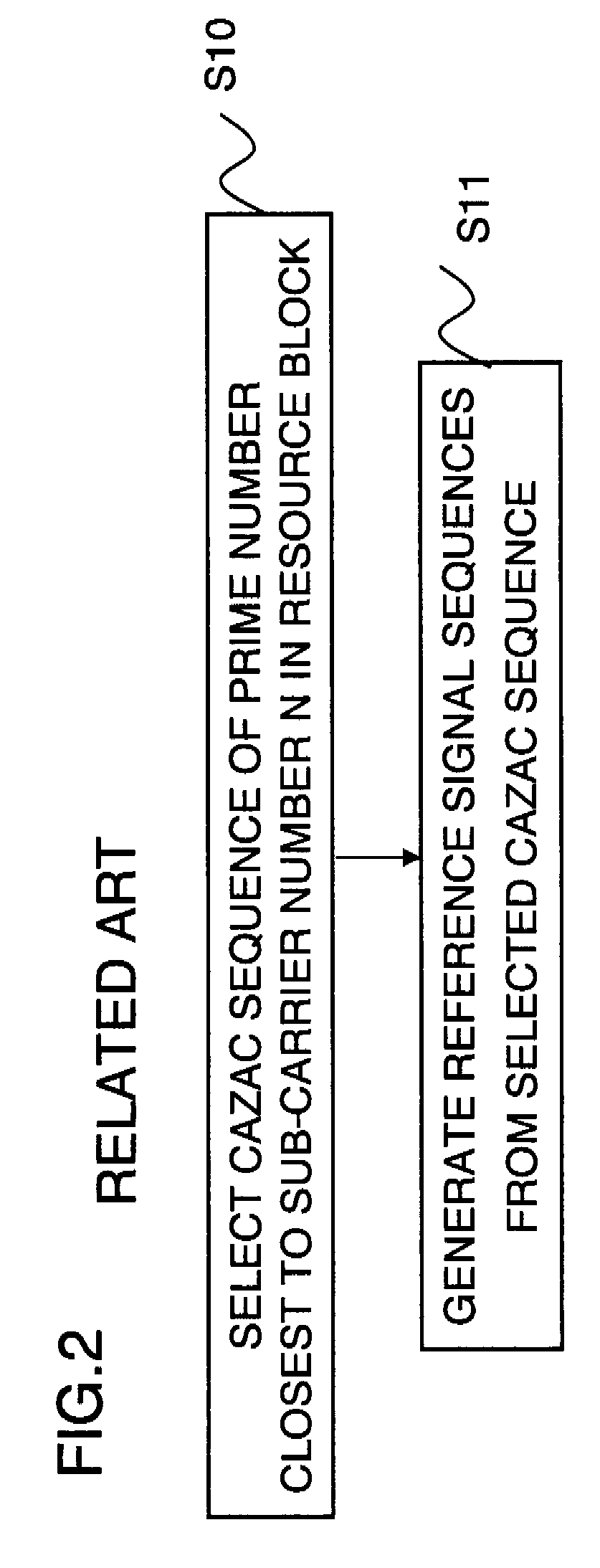

Method and apparatus for reference signal generation in wireless communication system

ActiveUS20080253484A1Excellent cross (mutual)-correlation propertyDifferenceFrequency-division multiplexAmplitude-modulated carrier systemsCommunications systemResource block

To provide a reference signal generation method and apparatus capable of obtaining many reference signal sequences having excellent properties. CAZAC sequences that satisfy the condition that the absolute value (|N−L|) of a difference between a sub-carrier number N in a resource block and a CAZAC sequence length L is not larger than a threshold value K are selected, and a sequence having a largest among greatest prime factors among the prime factors constituting the sequence length(s) is further selected from the initially selected sequences. Then, a reference signal sequence(s) is generated from a selected CAZAC sequence.

Owner:NEC CORP

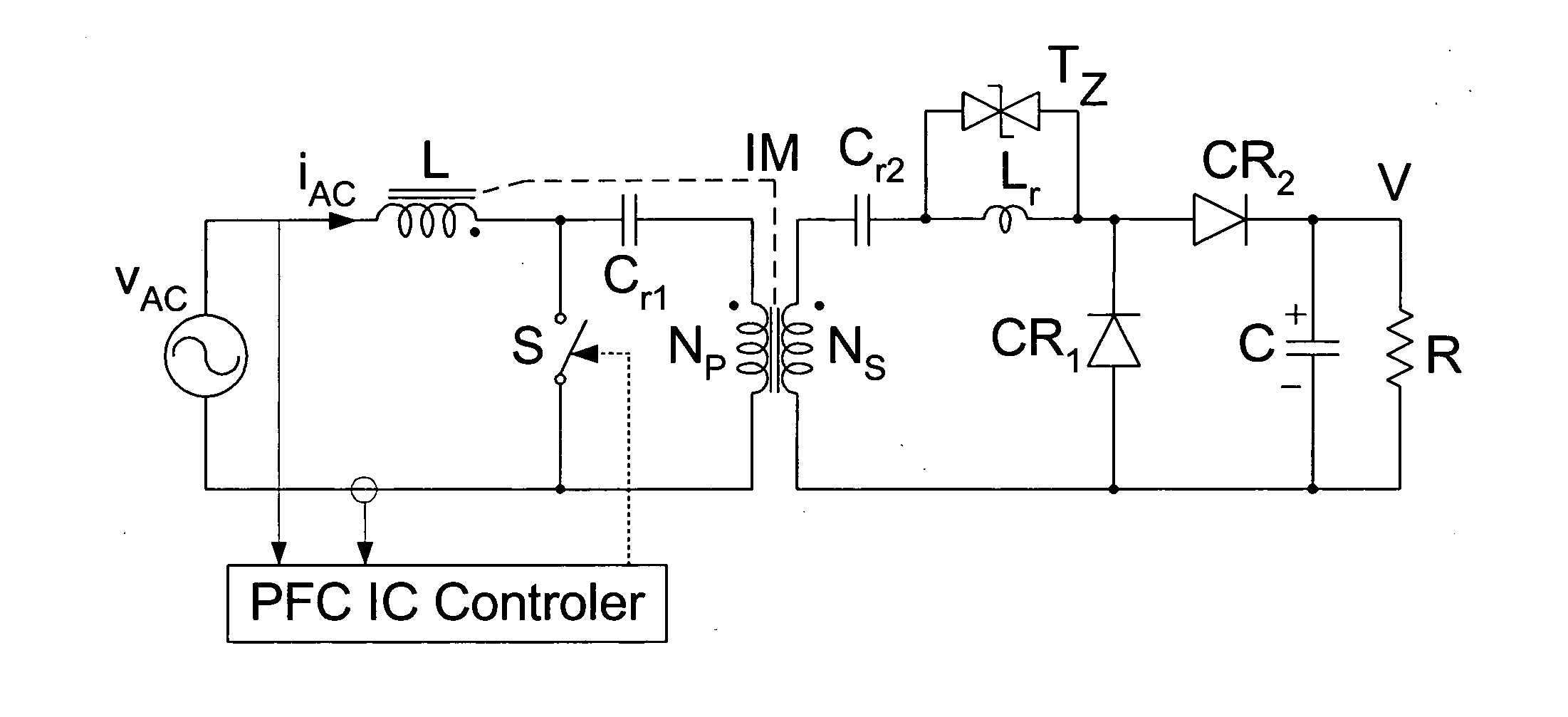

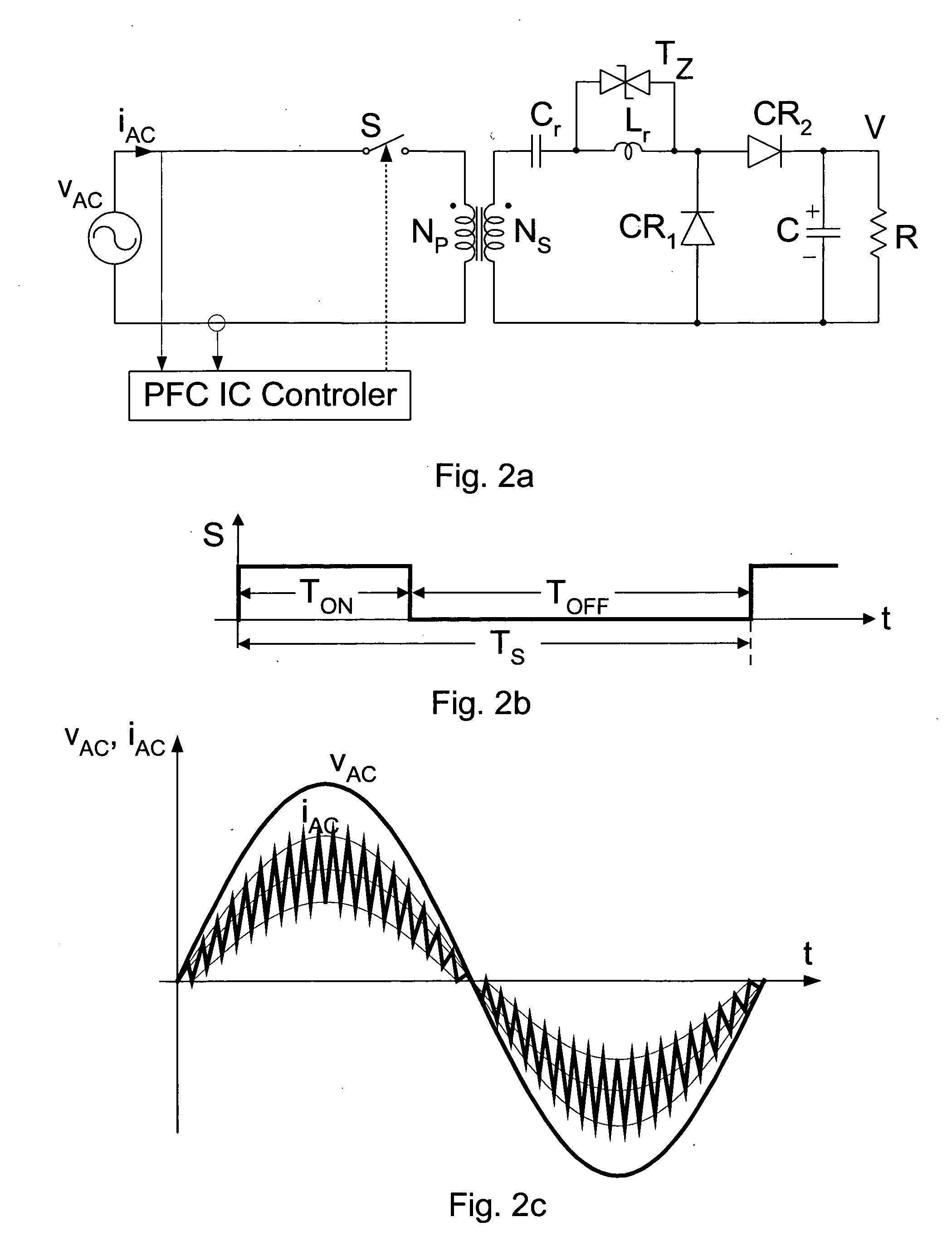

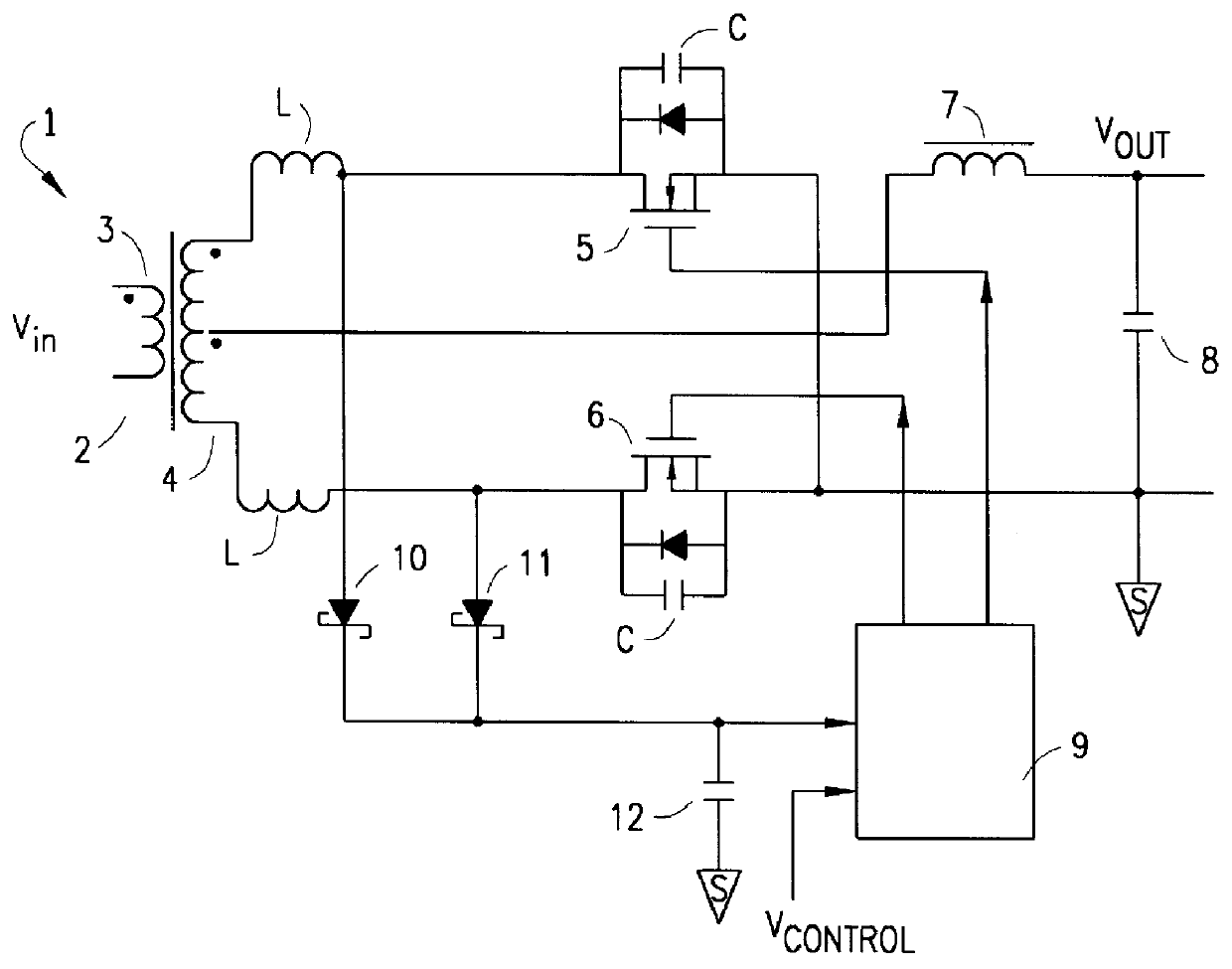

Single-stage AC-to-DC converter with isolation and power factor correction

InactiveUS20110292703A1Reduce Harmonic DistortionLow efficiencyAc-dc conversion without reversalEfficient power electronics conversionSingle stageLow voltage

A new class of Single-Stage AC-DC converters with built-in Isolation and PFC feature is introduced along with the companion hybrid switching conversion method. Several different converter topologies are introduced, which all feature three switches only, single magnetic component and low voltage stresses on all switches.

Owner:CUKS

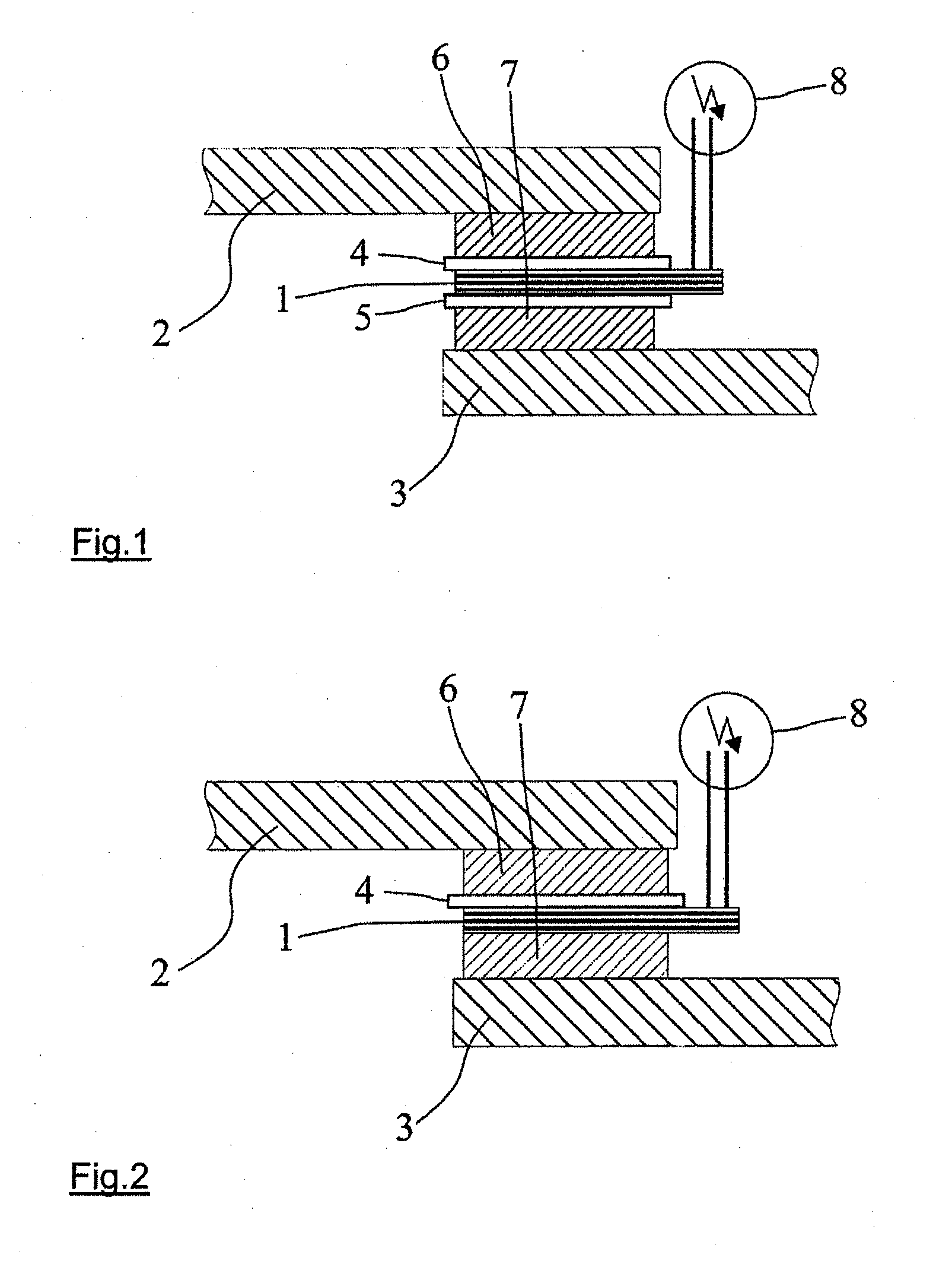

Solid electrolytic capacitor and electric circuit

InactiveUS7031141B2Large capacitanceLow ESRSolid electrolytic capacitorsLiquid electrolytic capacitorsElectrolysisOptoelectronics

A solid electrolytic capacitor includes a cathode including a solid electrolytic layer, an anode, and a dielectric layer provided between the cathode and the anode. The anode includes an anode body, an input anode terminal and an output anode terminal. A bypass current path for causing circuit current to detour around the anode body is formed between the input anode terminal and the output anode terminal.

Owner:ROHM CO LTD

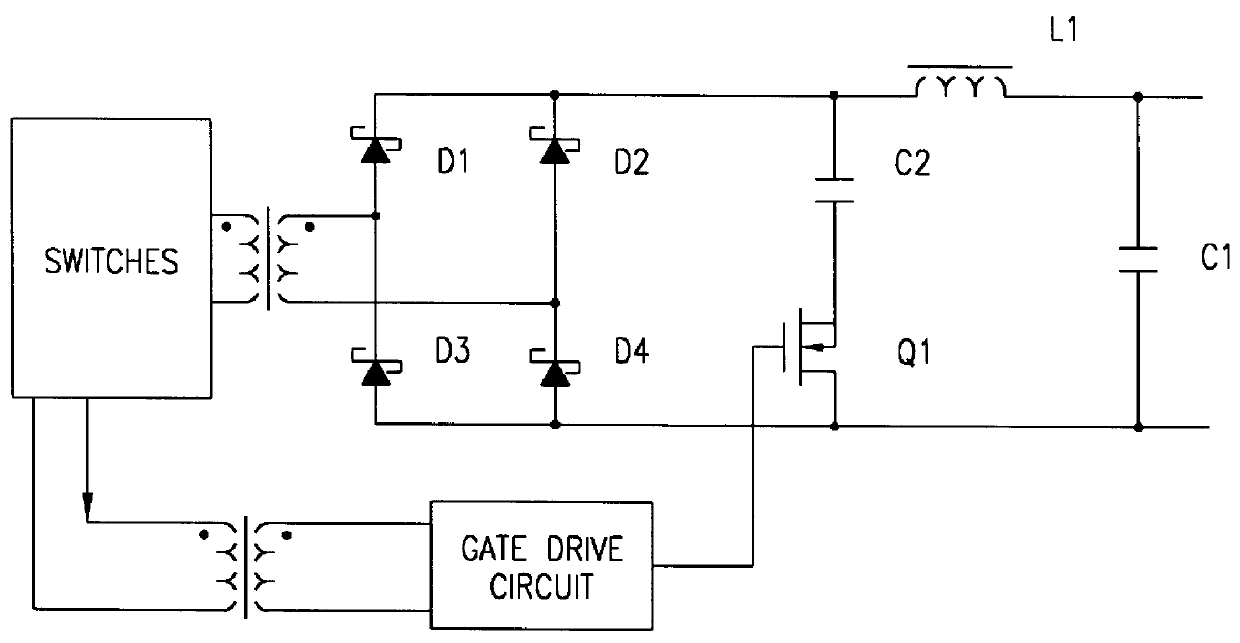

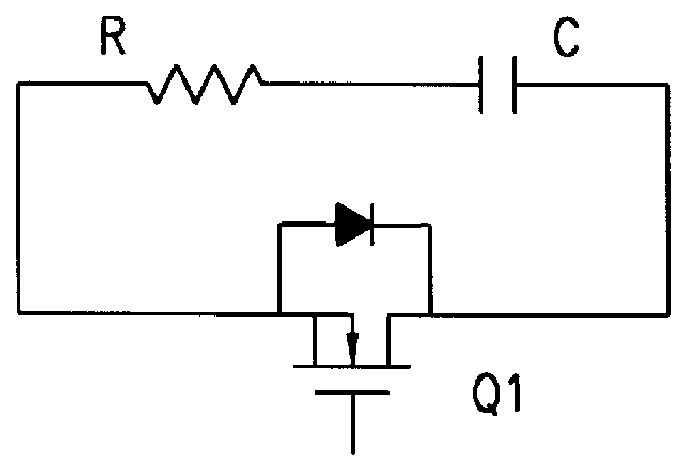

Clamping circuit and method for synchronous rectification

InactiveUS6128206ASuppress high voltage spikeReduce peak voltageAc-dc conversion without reversalEfficient power electronics conversionVoltage spikeTransformer

A rectifier circuit having voltage clamping circuitry is disclosed. The rectifier circuit includes a transformer having a primary winding and a secondary winding and transistor switches each being connected to an end of the secondary winding of the transformer. The rectifier circuit further includes a first diode having an anode terminal connected to a first end of the secondary winding and a second diode having an anode terminal connected to a second end of the secondary winding. The cathode terminals of the first and second diodes are coupled to a capacitor. The energy stemming from voltage spikes and / or high frequency ringing appearing at the transistor switches due to parasitic effects is effectively absorbed by the first and second diodes and collected in the capacitor. The collected energy is recycled to control the operation of the transistor switches.

Owner:ERICSSON INC

Atmosphere control method for sintering process of high-frequency wide-temperature low-loss MnZn ferrite

ActiveCN107555984AHigh densityIncreased power lossInorganic material magnetismInductances/transformers/magnets manufactureHeat conservationFerrite (magnet)

The invention provides a sintering atmosphere control method in preparation of high-frequency wide-temperature low-loss MnZn ferrite. The method comprises the following steps: carrying out primary heating and heat preservation, carrying out secondary heating and heat preservation, cooling, carrying out heat preservation, and finally cooling. According to the method, corresponding oxygen partial pressure is adjusted at different temperatures and in different temperature changing processes, zinc loss in a sintering process can be reduced, and element valence change and impure phase precipitationat high temperature are inhibited, so that the soft magnetic property of the material is improved; and by adding reasonable heat preservation time, sintering internal stress can be effectively reduced, and the material is prevented from cracking in the sintering process. The method provided by the invention is applicable to preparation of multiple MnZn ferrites, and the wide-temperature low-lossMnZn power ferrite used at the frequency of 0.1-5MHz can be obtained; reasonable technological parameters can improve yield in preparation process, and a product with uniform and stable performance can be beneficially obtained; and the method is simple and practicable and has practical value.

Owner:ZHEJIANG UNIV +1

Micro vein enhancer

The present invention is a Miniature Vein Enhancer that includes a Miniature Projection Head. The Miniature Projection Head may be operated in one of three modes, AFM, DBM, and RTM. The Miniature Projection Head of the present invention projects an image of the veins of a patient, which aids the practitioner in pinpointing a vein for an intravenous drip, blood test, and the like. The Miniature projection head may have a cavity for a power source or it may have a power source located in a body portion of the Miniature Vein Enhancer. The Miniature Vein Enhancer may be attached to one of several improved needle protectors, or the Miniature Vein Enhancer may be attached to a body similar to a flashlight for hand held use. The Miniature Vein Enhancer of the present invention may also be attached to a magnifying glass, a flat panel display, and the like.

Owner:ACCUVEIN

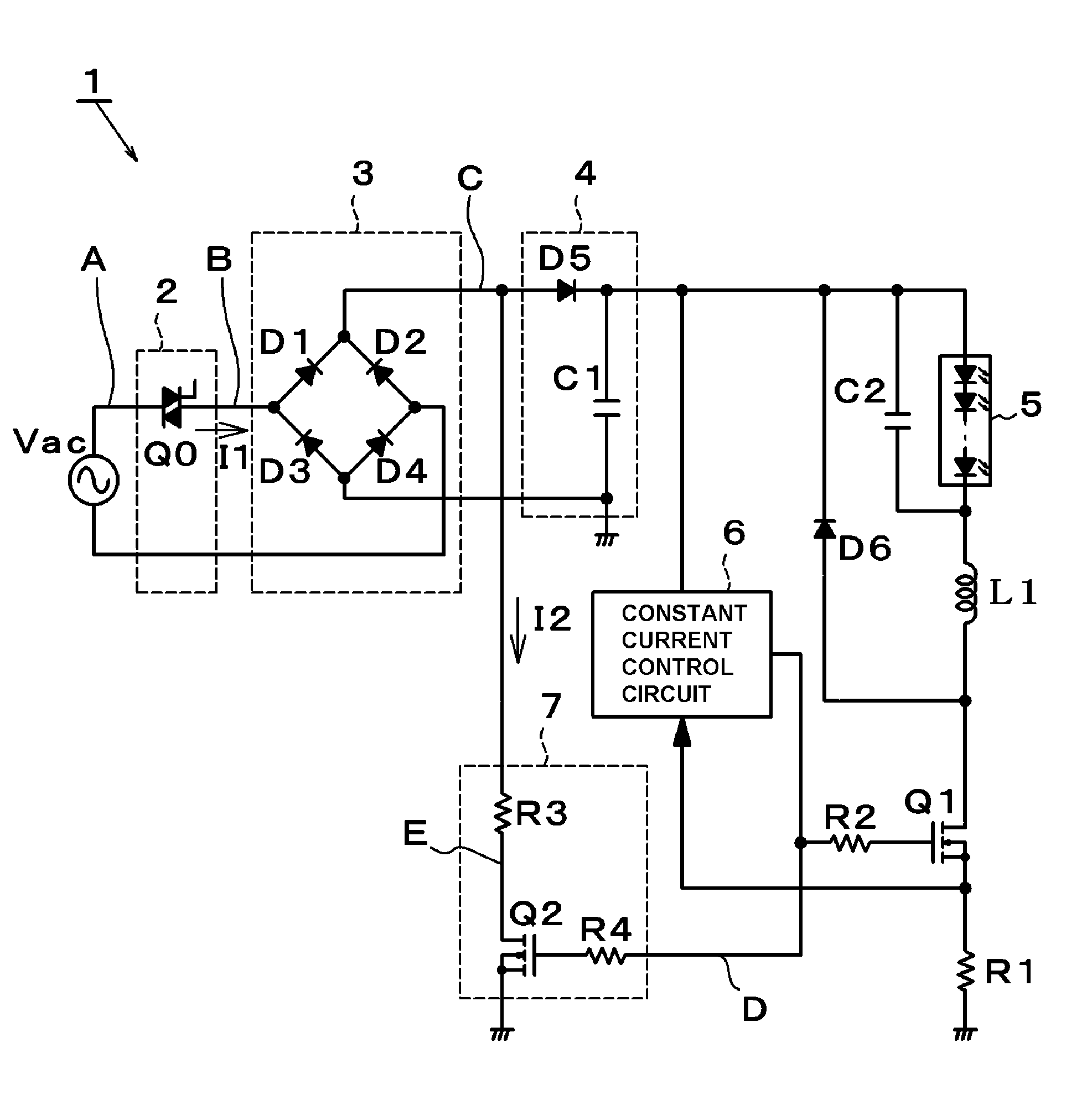

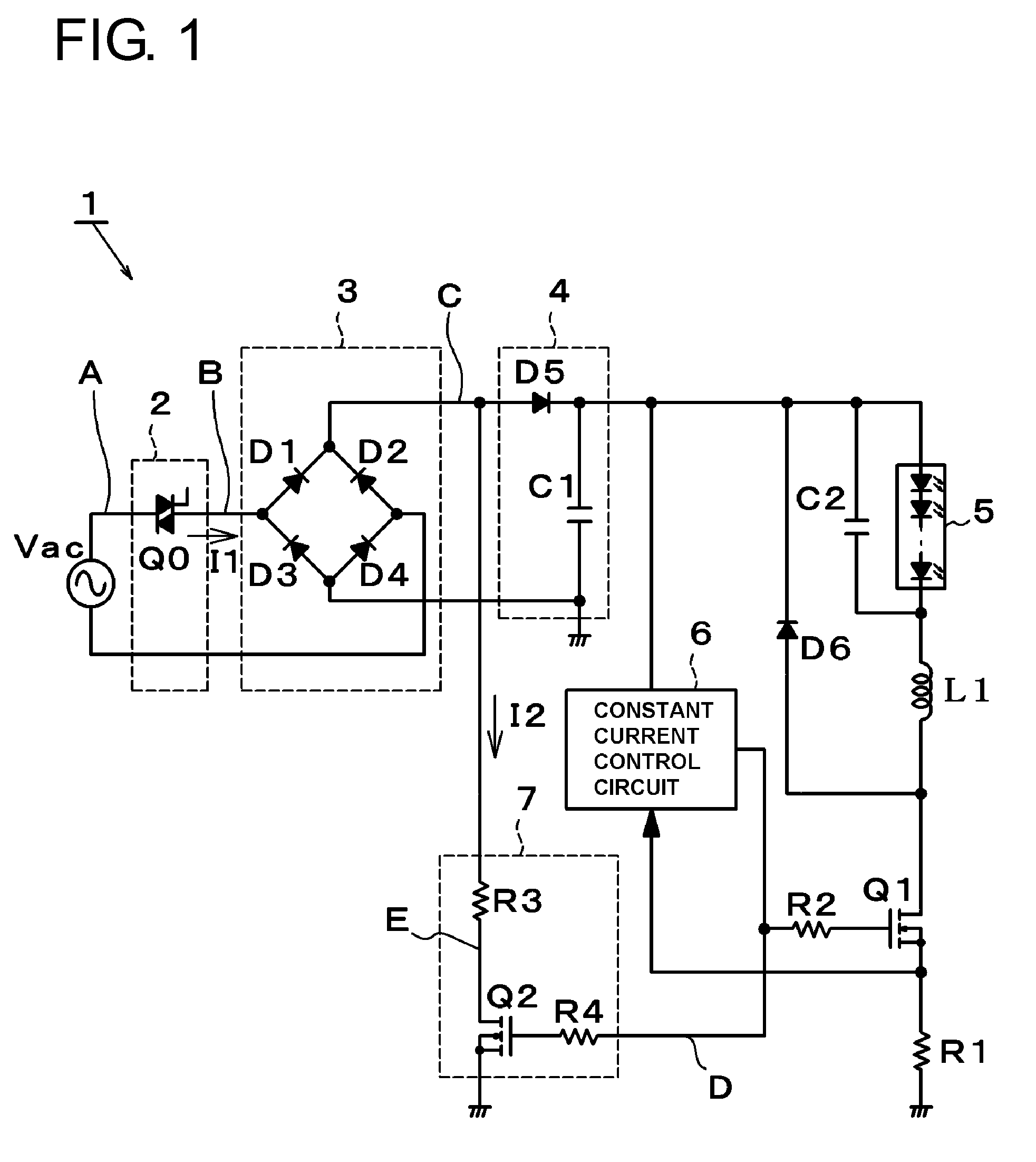

LED driving circuit

ActiveUS20110140622A1Simple circuit configurationMalfunction can be prevented and reducedElectrical apparatusElectroluminescent light sourcesEngineeringAlternating current

An LED driving circuit includes a dimming circuit that controls a conducting angle of an alternating current supplied from a power supply to phase-control a current to be supplied to an LED, a rectifier circuit that rectifies an alternating-current voltage output from the dimming circuit, a smoothing circuit that smoothes a direct current voltage output from the rectifier circuit, a switching device that is connected with the LED in series; a constant current control circuit that outputs a high frequency pulse signal to the switching device to control the switching device, and a bleeder circuit that is provided between an output terminal of the rectifier circuit and a ground and that has a bleeder resistance and a bleeder switch connected in series. The high frequency pulse signal is input to the bleeder switch so that a bleeder current having a high frequency pulse form flows in the bleeder resistance.

Owner:MINEBEAMITSUMI INC

Turboalternator with hydrodynamic bearings

ActiveUS7948105B2Low efficiencyOptimum powerLiquid degasificationPump componentsStored energyAlternator

Owner:R & D DYNAMICS CORPORATION

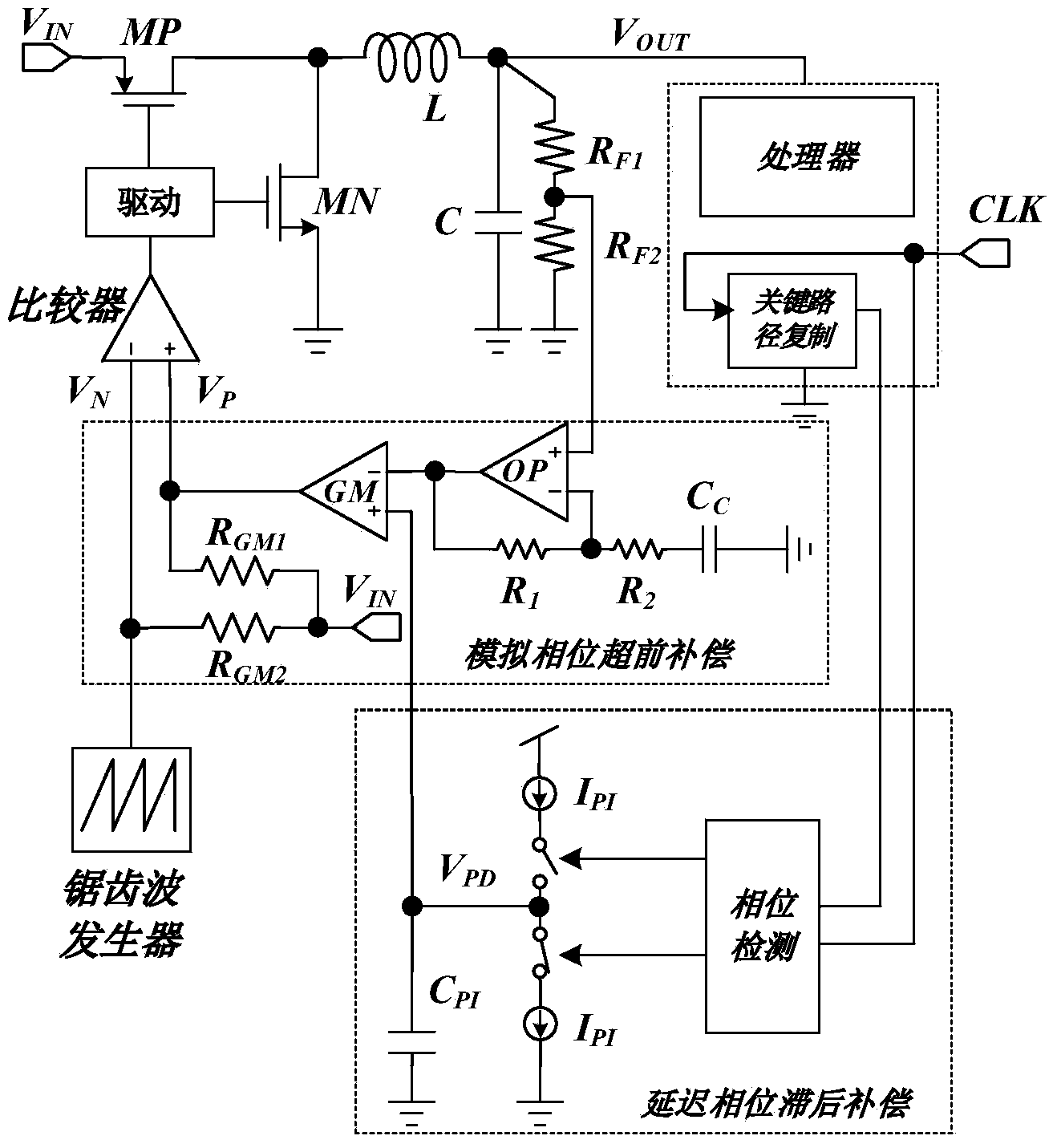

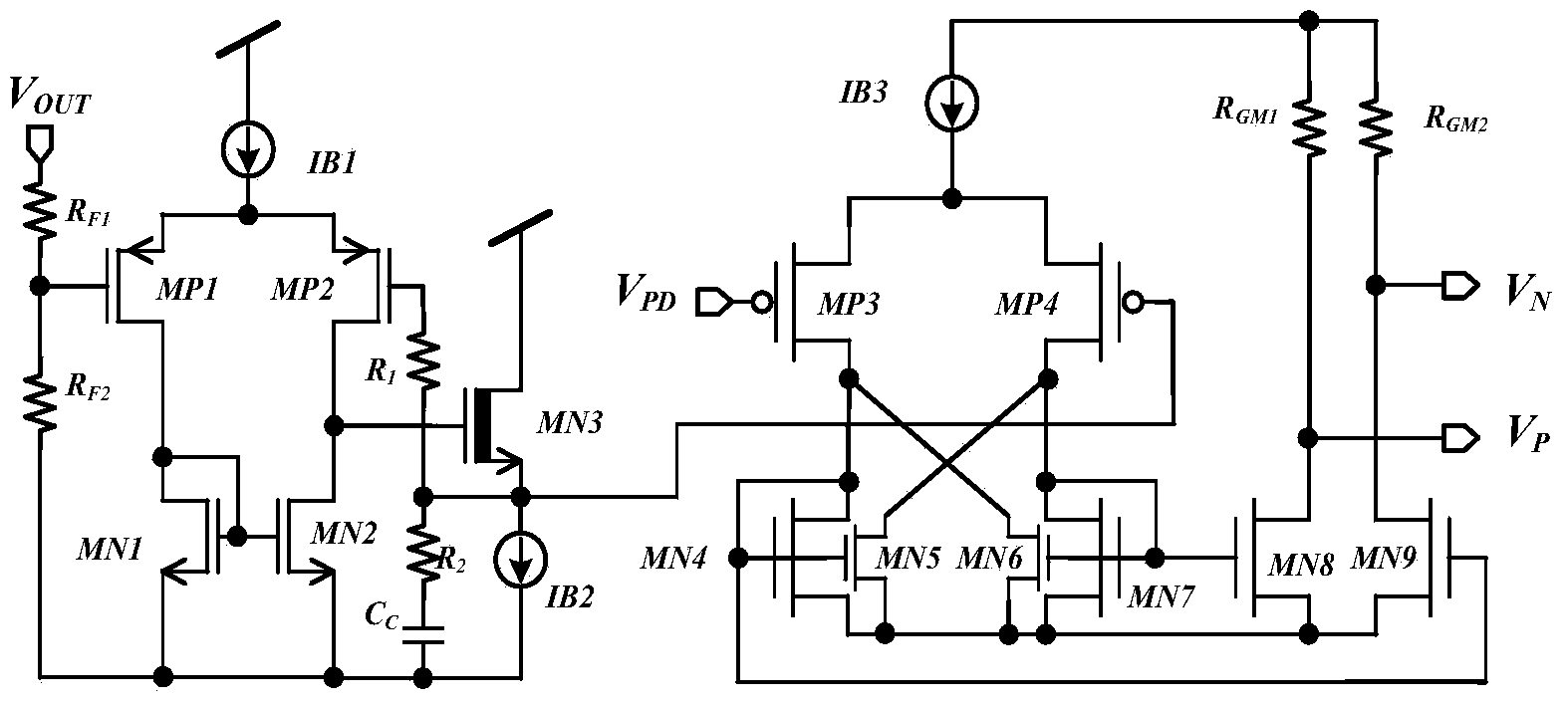

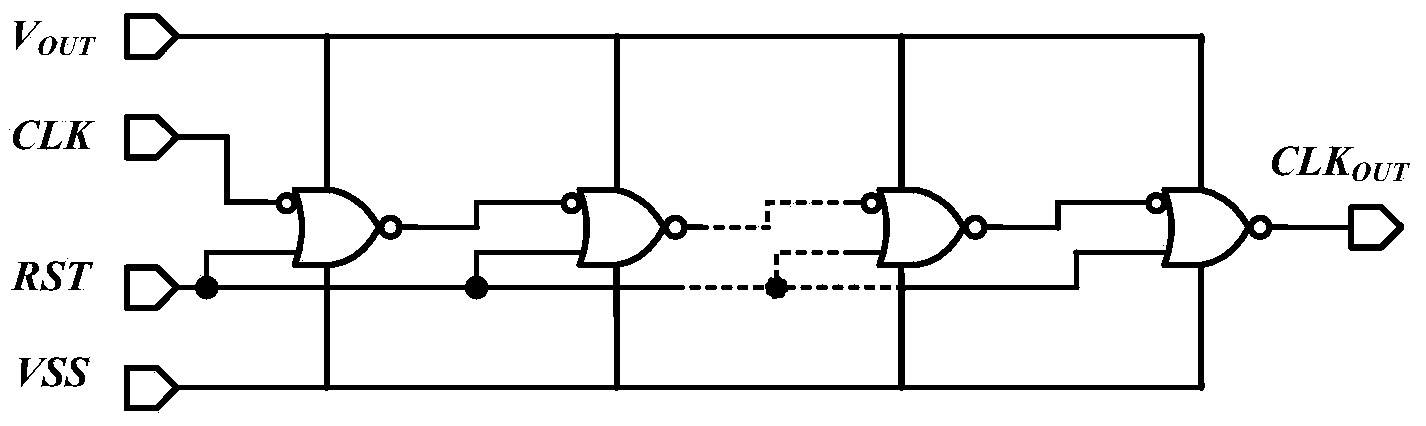

Self-adaptation voltage regulator circuit

InactiveCN104300788AReduce power lossIncreased power lossDc-dc conversionElectric variable regulationCapacitancePhase lead

The invention belongs to the technical field of power sources and relates to a self-adaptation voltage regulator circuit. The self-adaptation voltage regulator circuit comprises a power tube MP, a power tube MN, an inductor L, a capacitor C, a first resistor RF1, a second resistor RF2, a simulation phase lead compensation module, a delay phase lag compensation module, a critical path duplication module, a sawtooth wave generating module, a comparator and a power tube driver. The output voltage Vout is partitioned by the first resistor RF1 and the second resistor RF2. Simulation phase lead compensation is achieved through an operational amplifier, the resistor R1, the resistor R2 and the capacitor C. A load of an operational transconductance amplifier GM is RGM1 and provides the loop gain of APD compensation. The delay of the duplication of the critical path is compared with a system clock CLK through phase detection. Then, delay error signals are integrated through a charge pump. The output voltage VPD of the charge pump is connected to the positive going input end of the operational transconductance amplifier GM. PWM waveforms can be obtained by comparing the sawtooth wave current generated by an oscillator OSC and the output current of the GM. By means of the self-adaptation voltage regulator circuit, the power loss of a digital circuit is greatly reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Switching power supply device

InactiveUS7453248B2Improve conversion efficiencyIncreased power lossEfficient power electronics conversionElectric variable regulationDc dc converterBoost power converter

Owner:SANKEN ELECTRIC CO LTD

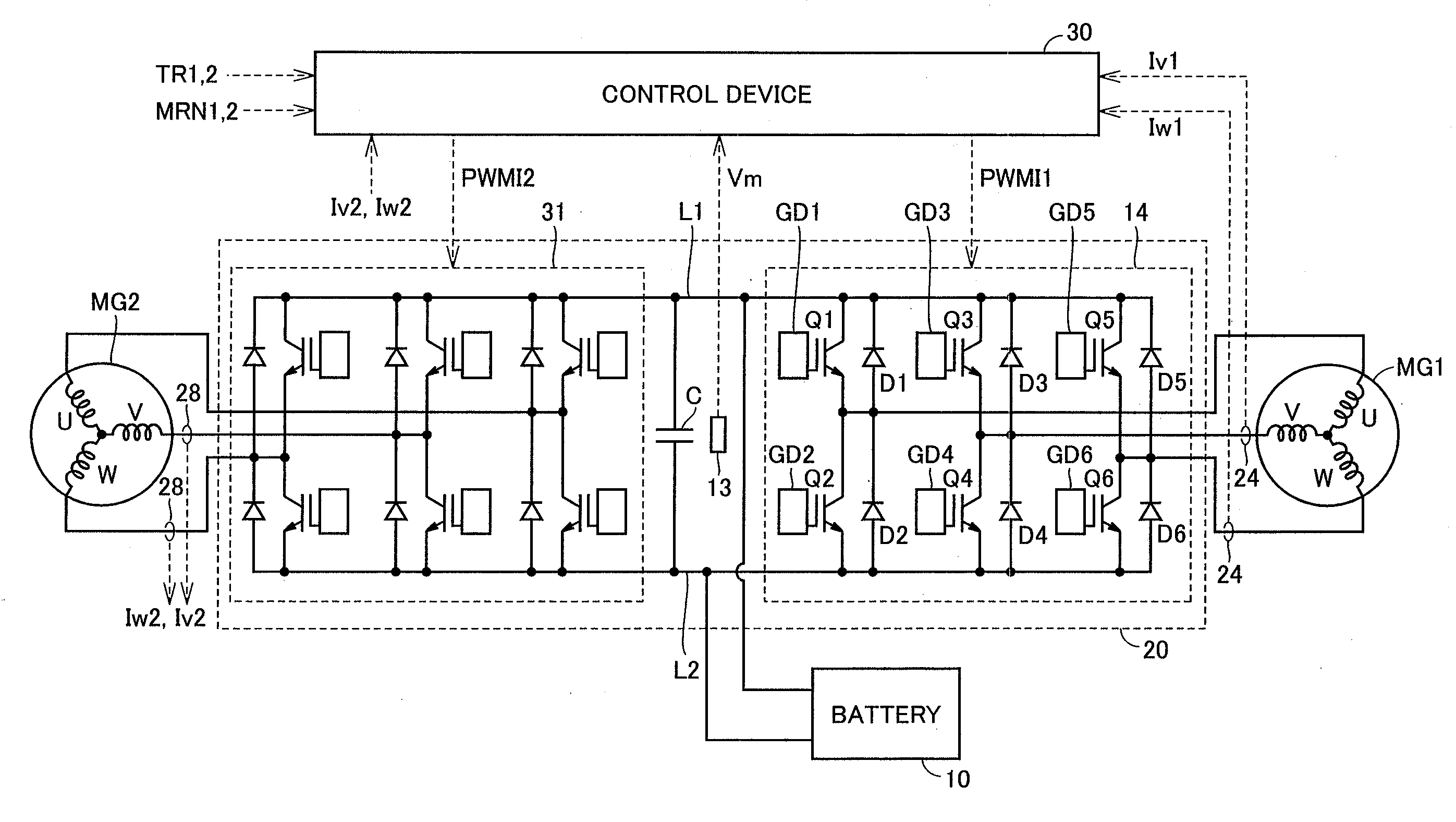

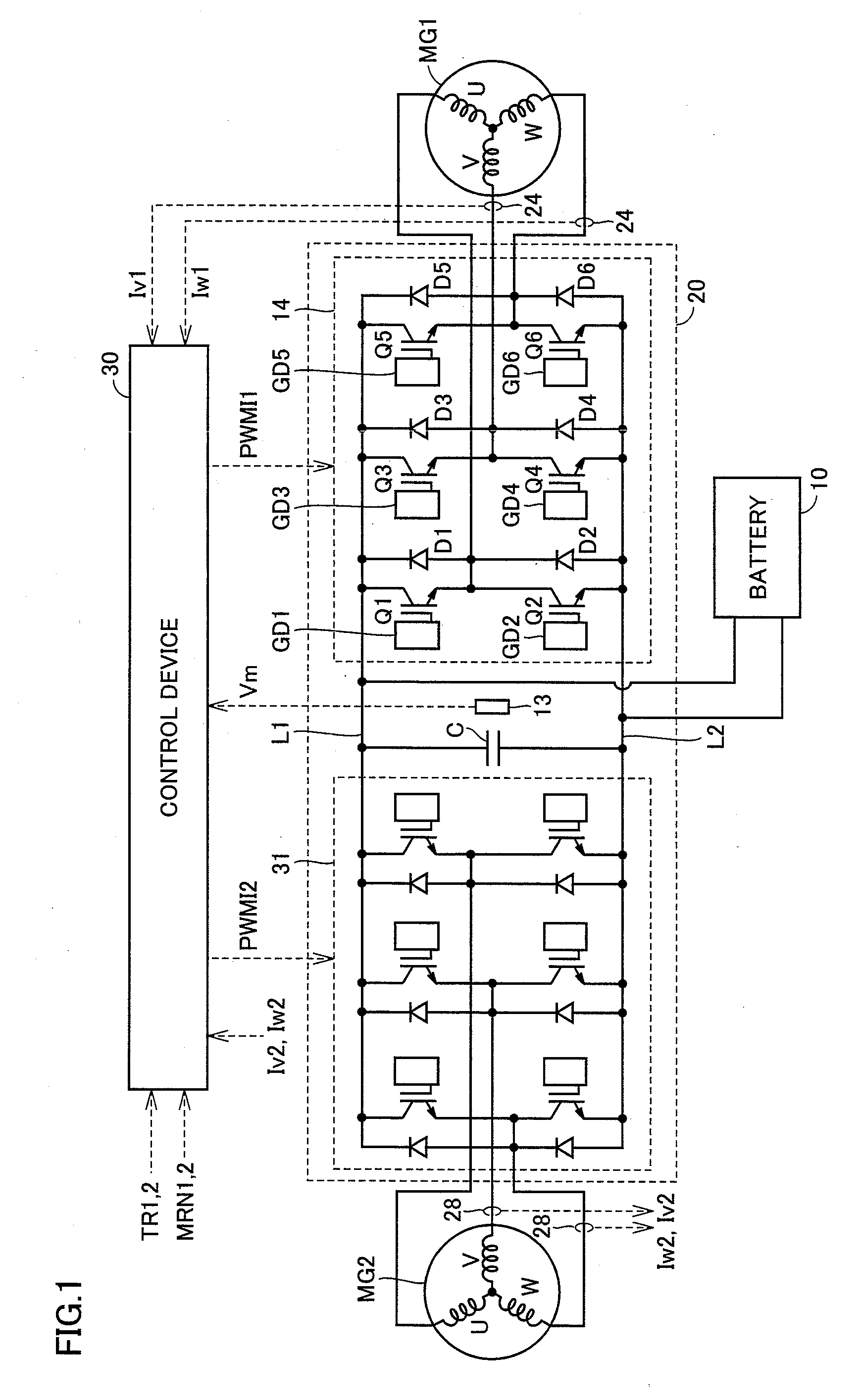

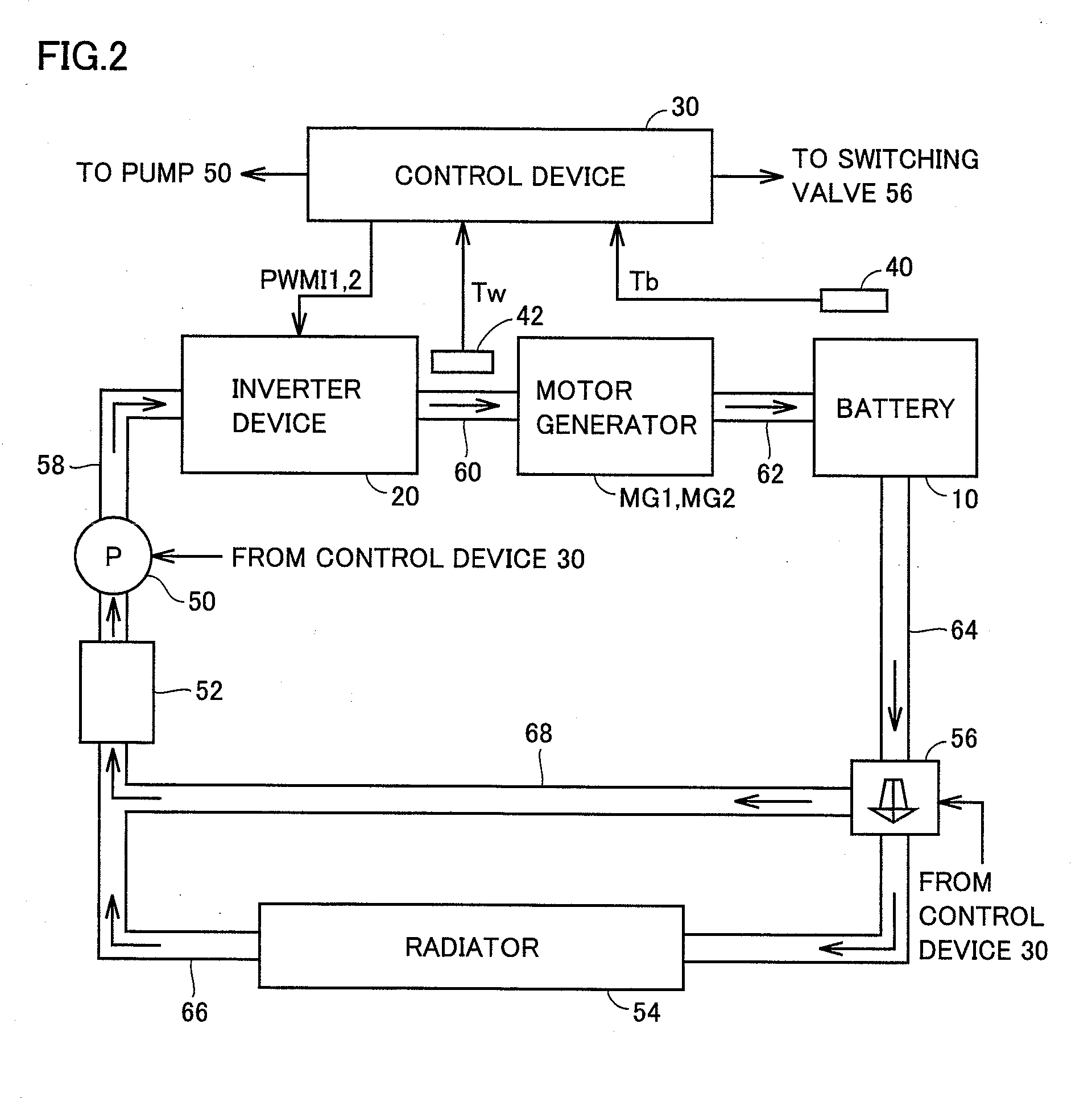

Cooling system

ActiveUS20100050676A1Efficiently and rapidly warmRapid increase in temperatureDomestic cooling apparatusLighting and heating apparatusLower limitEngineering

A cooling system has a configuration in which a cooling system for an inverter device and a motor generator also serves as a cooling system for a battery. In this configuration, a control device performs temperature-raising control of the battery when a battery temperature is below a prescribed temperature lower limit value. The control device controls an operation of a switching valve such that cooling water from a cooling medium path is outputted to a bypass path. Further, if a cooling water temperature is lower than a prescribed temperature, the control device controls the inverter device such that a power loss during a switching operation in a switching element included in the inverter device becomes larger than a power loss during normal control. As a result, the cooling system having a small-sized, low-cost configuration rapidly recovers capacity decline of the battery, which occurs at low temperatures.

Owner:TOYOTA JIDOSHA KK

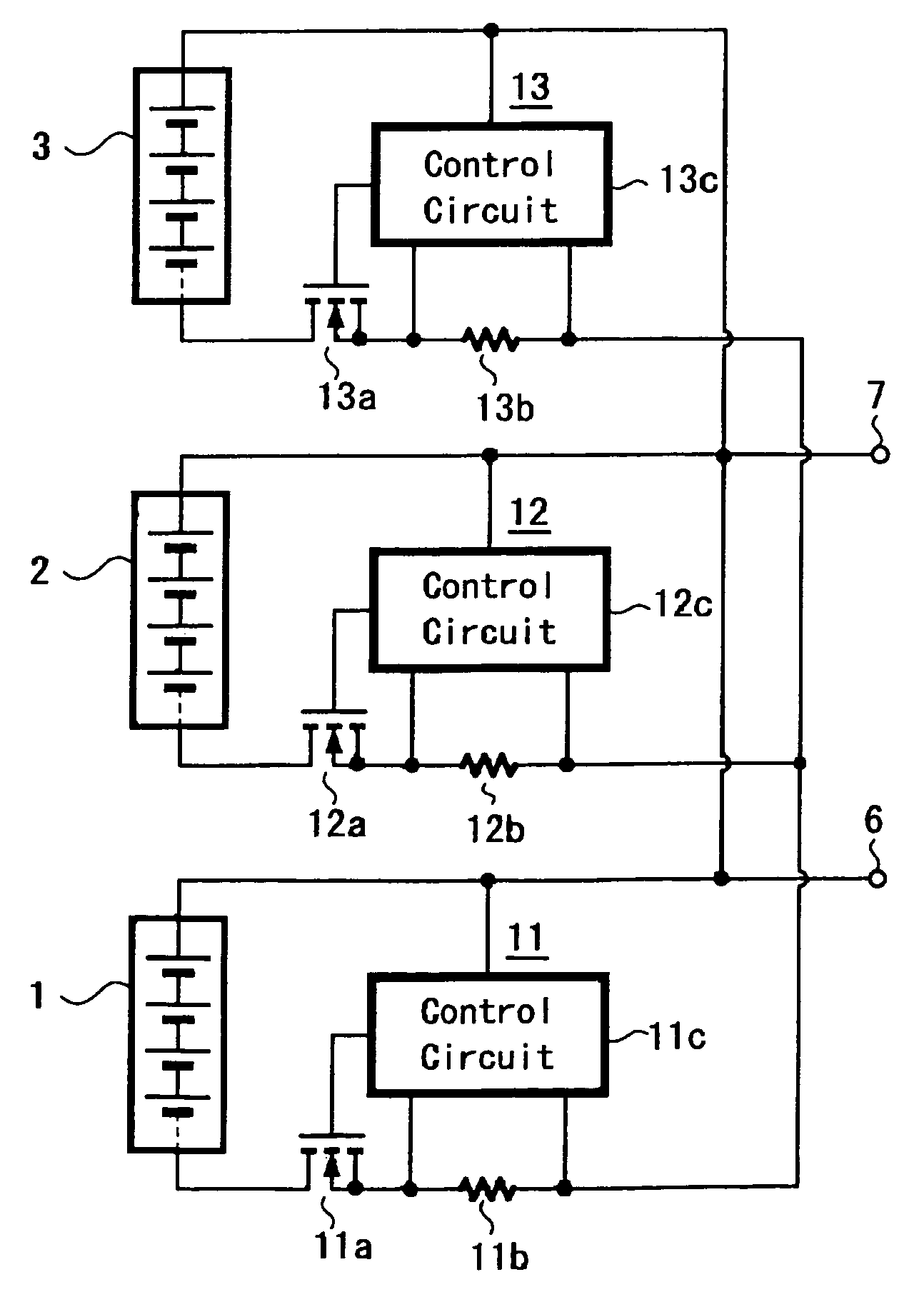

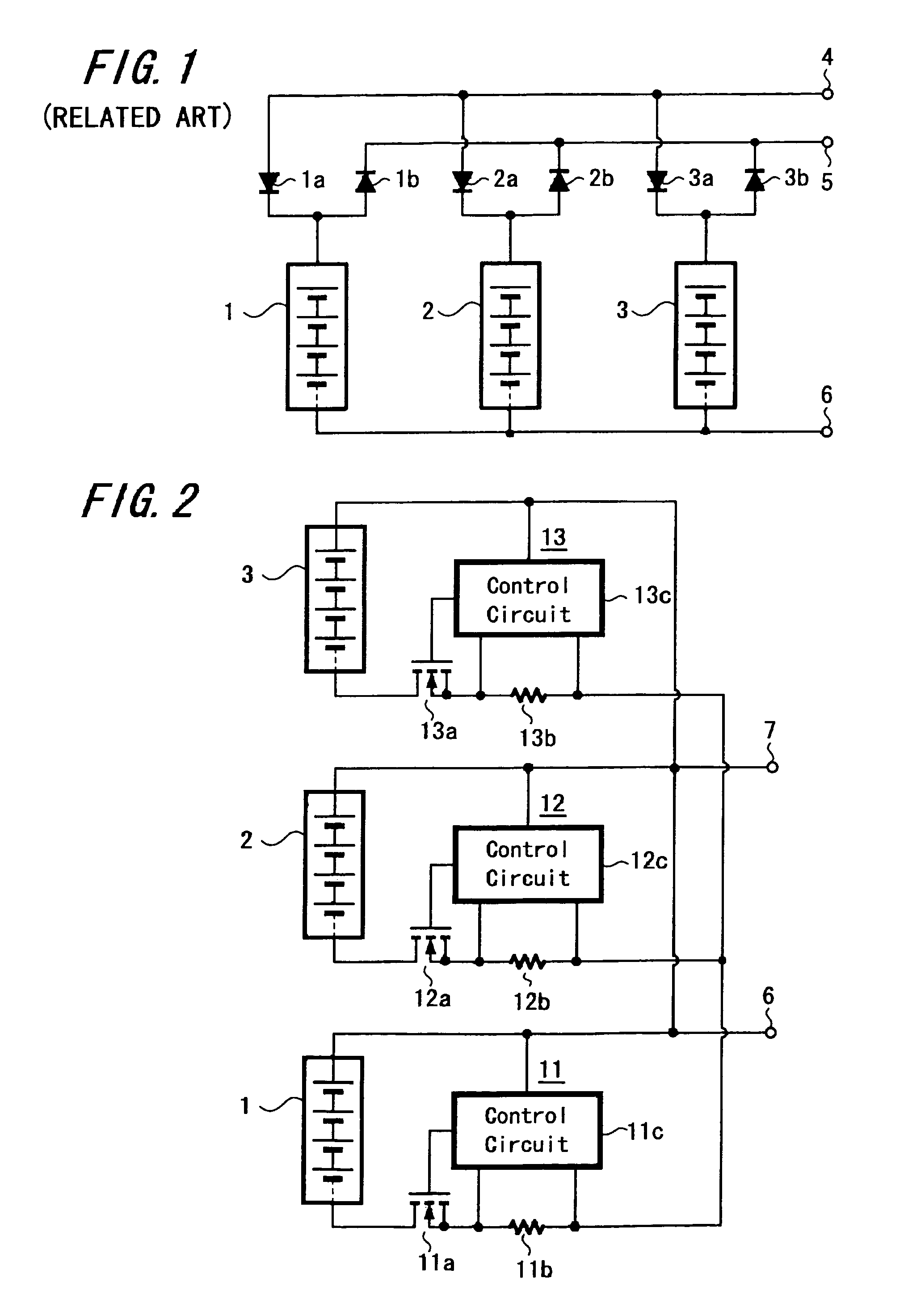

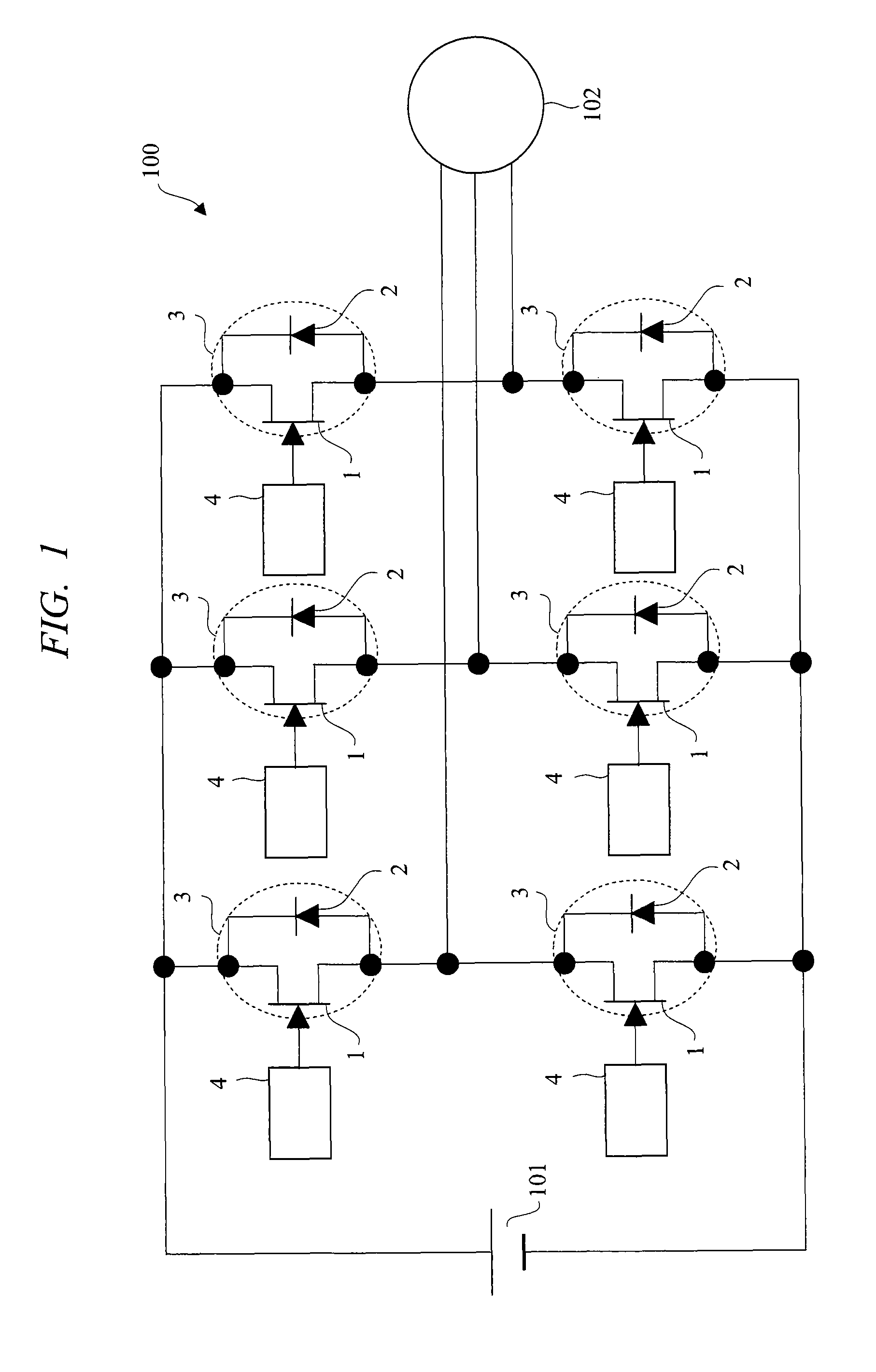

Power supply apparatus with transistor control for constant current between series-connected battery blocks

ActiveUS7463008B2Increased power lossReduce capacityCharging managementSecondary cellsElectrical batteryControl circuit

A power supply device having a plurality of series-connected-battery blocks which are connected in parallel and in which two or more secondary cells capable of charging and discharging are connected in series, includes a constant-current control circuit provided for each of the series-connected-battery blocks.

Owner:SONY CORP

Semiconductor device and power conversion device using the same

ActiveUS7838907B2Increased power lossIncrease the on-resistanceTransistorSolid-state devicesSemiconductor chipConductive materials

Owner:RENESAS ELECTRONICS CORP

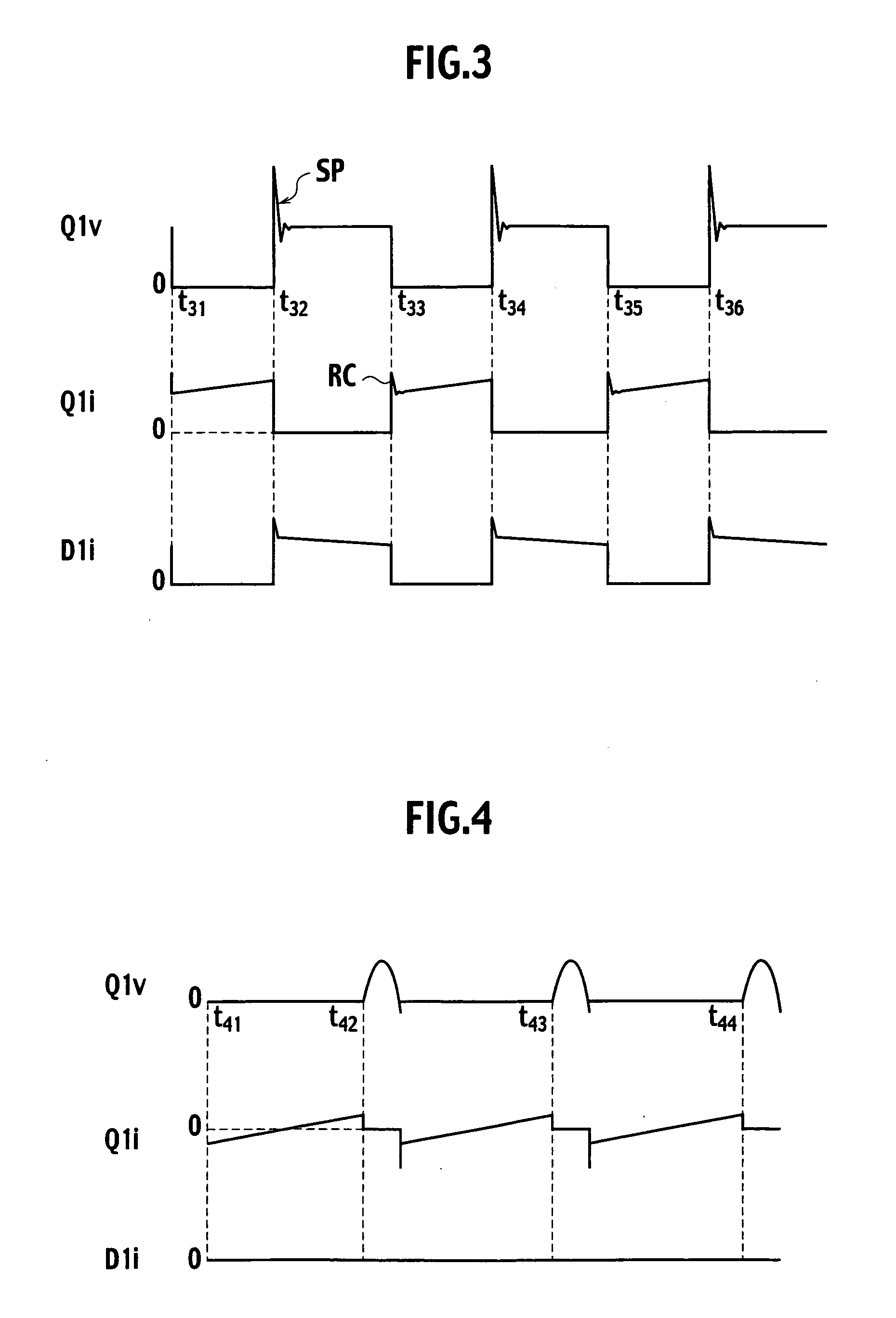

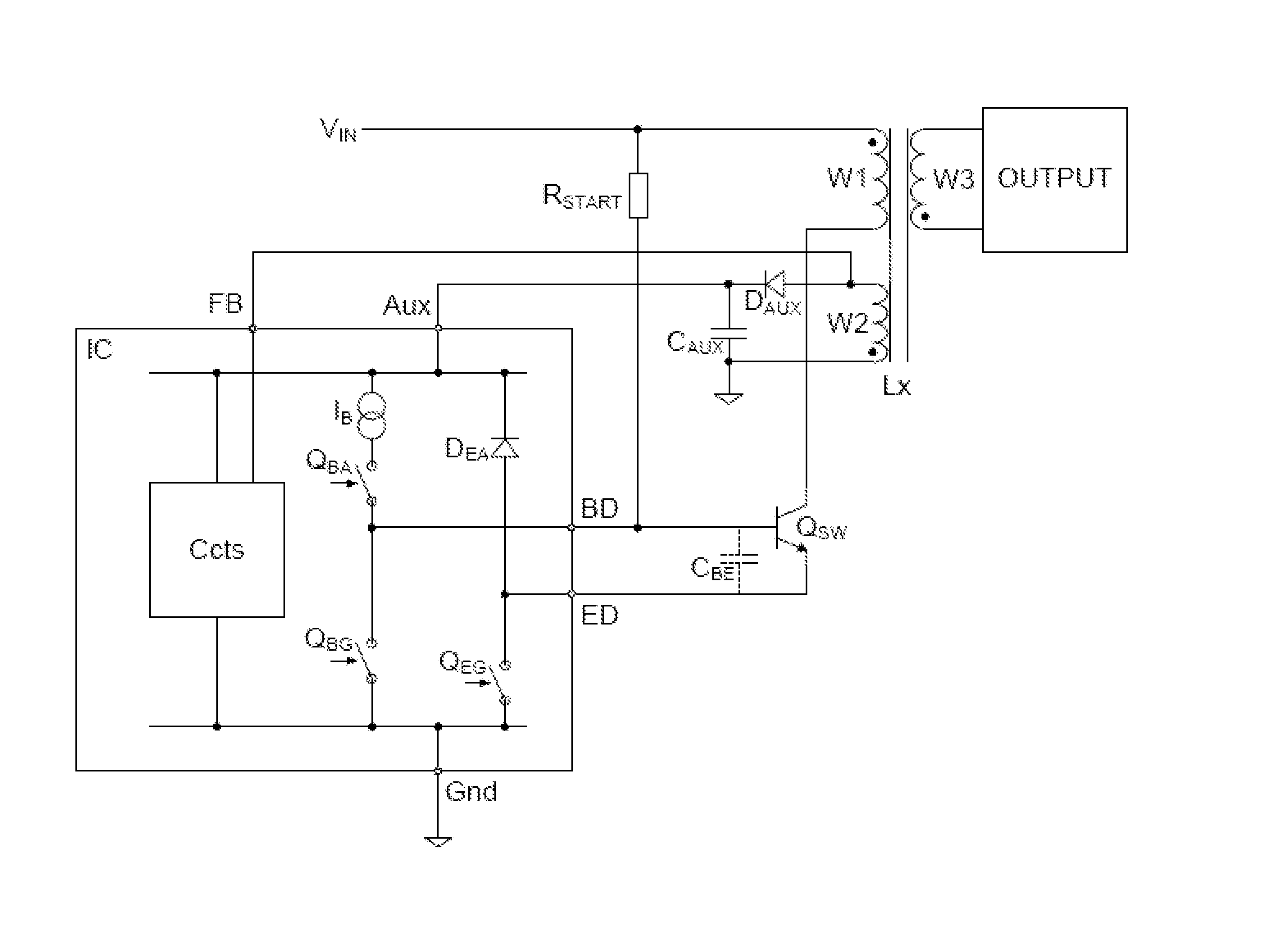

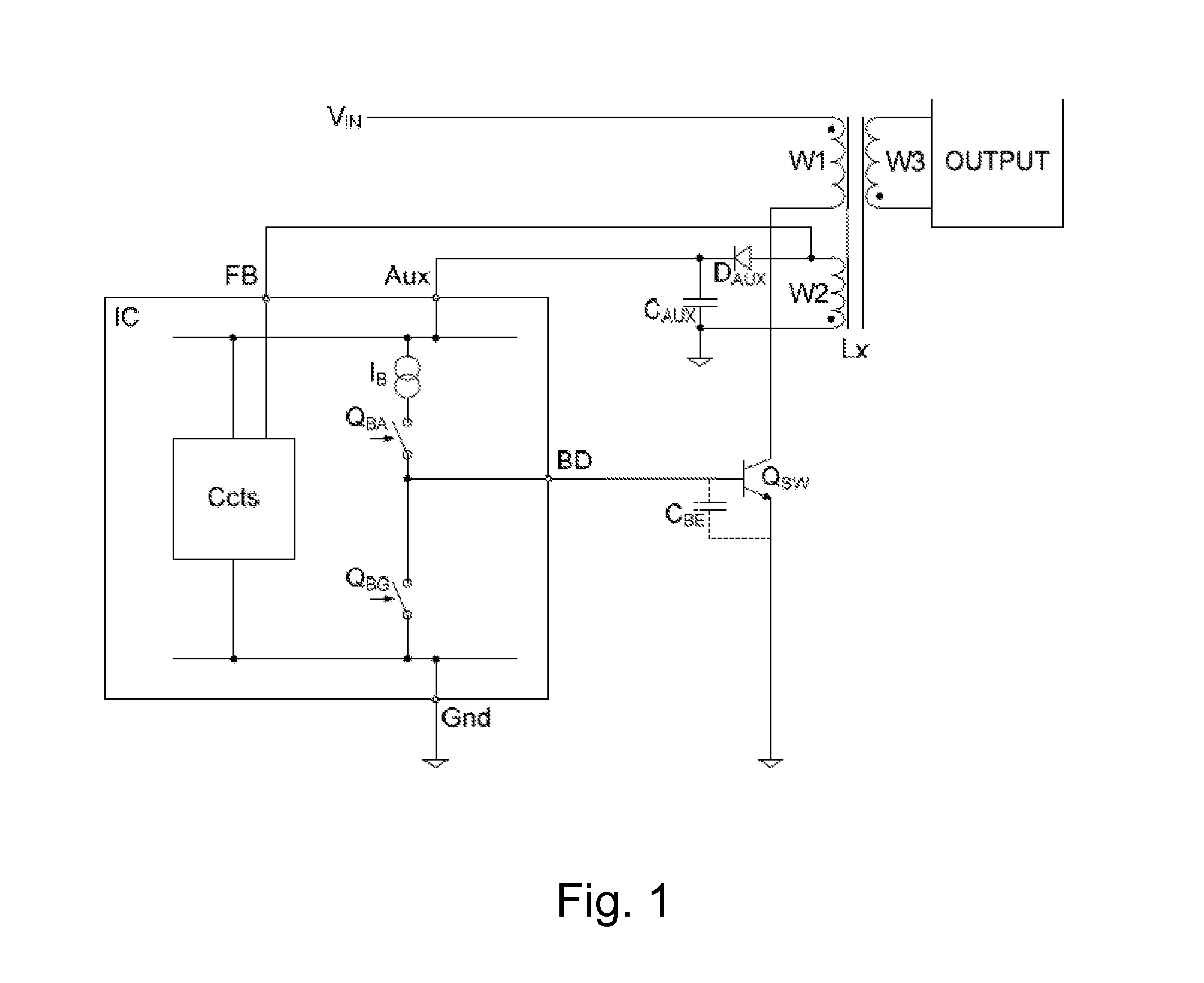

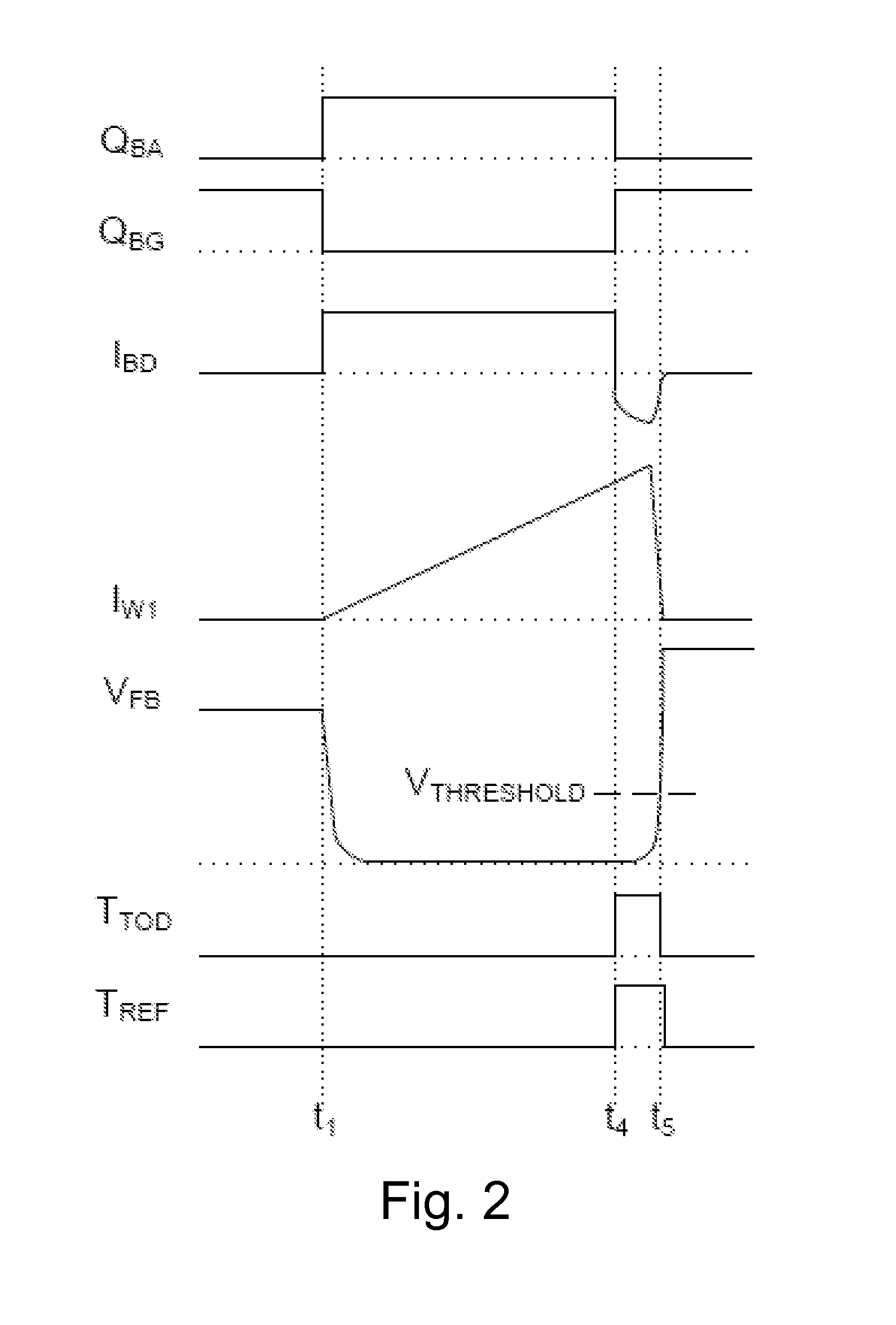

Storage time control

InactiveUS20140355314A1Reduce control signalingHigh first amplitudeTransistorEfficient power electronics conversionSwitching cycleTime delays

We describe a method of controlling turn off time delay of a switching device of a switch mode power converter (SMPC). The SMPC has an inductive component comprising an input winding coupled to receive power from an input; and a switching device to, when on, conduct input winding current. In embodiments the method comprises applying turn on and turn-off signals to the switching device; applying at least one turn off signal, to initiate turning off of the switching device, and detecting a sensing signal from a further winding of the inductive component, inductively coupled to the input winding, to thereby indicate an end of a turn off time delay or duration. The method controls the turn on signal for a subsequent switching cycle of the SMPC device to regulate the turn off delay time.

Owner:POWER INTEGRATIONS INC

Electrical bypass element, in particular for storage cells of an energy storage device

ActiveUS20130252039A1Increased power lossGood disintegrationProtecting/adjusting hybrid/EDL capacitorEmergency protective circuit arrangementsThermal energyElectricity

An electrical bypass element, suitable for bypassing defective storage cells in energy storage devices includes two electrical conductors between which is formed a layer sequence with at least one electrical insulation layer and one or more reactive layer stacks, in which an exothermic reaction can be triggered. The reactive layer stacks and the insulation layer are matched to one another such that the insulation layer disintegrates as a result of the thermal energy released during the exothermic reaction and an electrical connection is produced between the electrical conductors. The electrical bypass element can be actively triggered even before the ultimate failure of a storage cell so that higher power losses in the energy storage device can be avoided.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

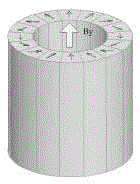

Holbach magnet shim coil and design method thereof

InactiveCN105548925ARapid designImprove the uniformity of the magnetic fieldMagnetic measurementsPermanent magnetsCurrent distributionBiot–Savart law

The invention discloses a Holbach magnet shim coil and a design method thereof. Aimed at the structural characteristic of a Holbach magnet and the direction of a main magnetic field, a current density function is designed flexibly according to the structural feature of the magnetic field, the relation between the current density and the main magnetic field is derived by utilizing the Biot-Savart Law, a current distribution function is inverted, and the coil structure is optimized by considering requirements for parameters including the power loss function and the linearity of the shim coil. Coils of two different structures are provided for the Halbach magnet, each coil structure has advantages and disadvantages in the aspects of structural complexity and performance, and the coils can be selected flexibly according to practical requirements.

Owner:SUZHOU INST OF BIOMEDICAL ENG & TECH CHINESE ACADEMY OF SCI

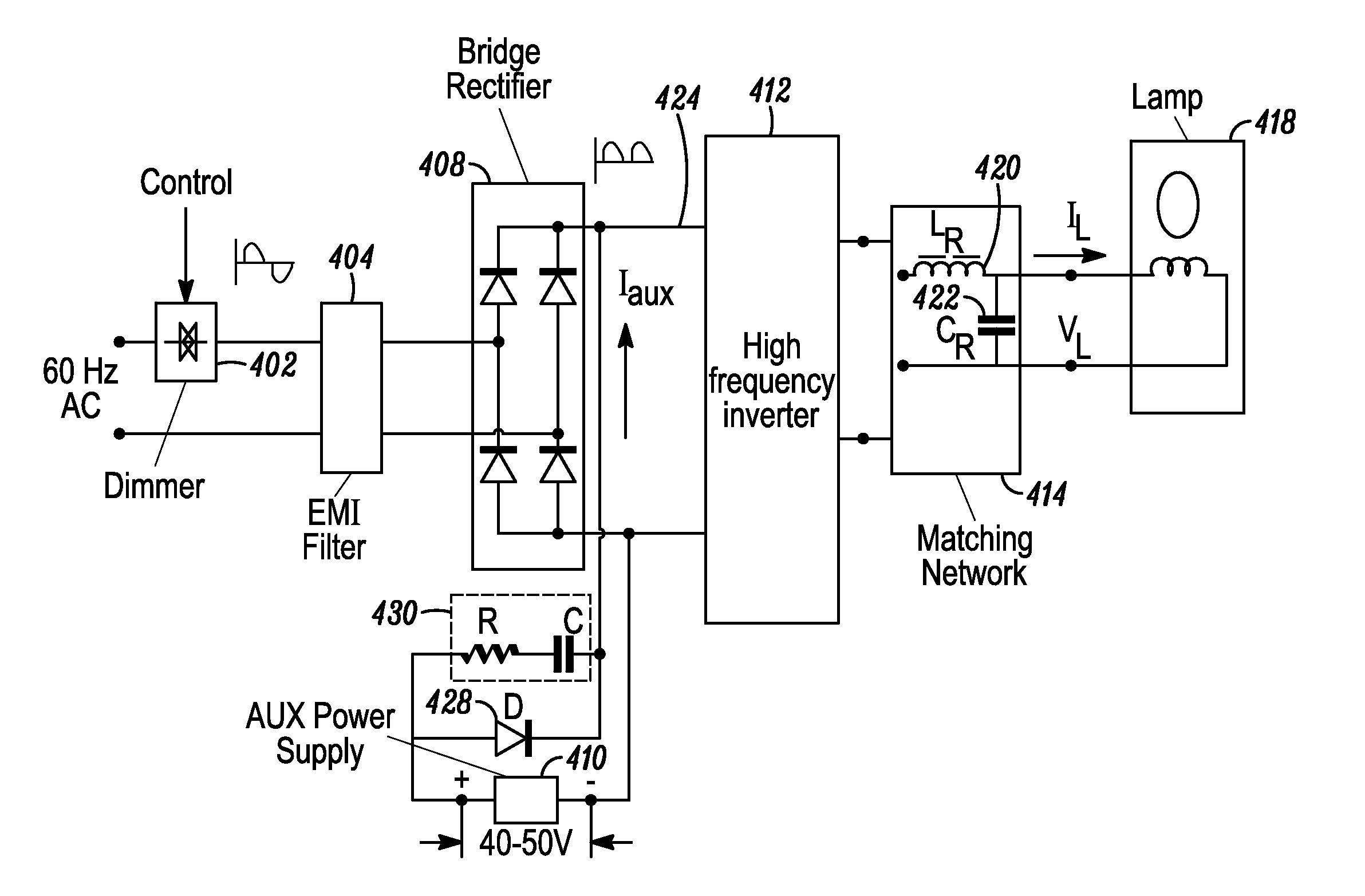

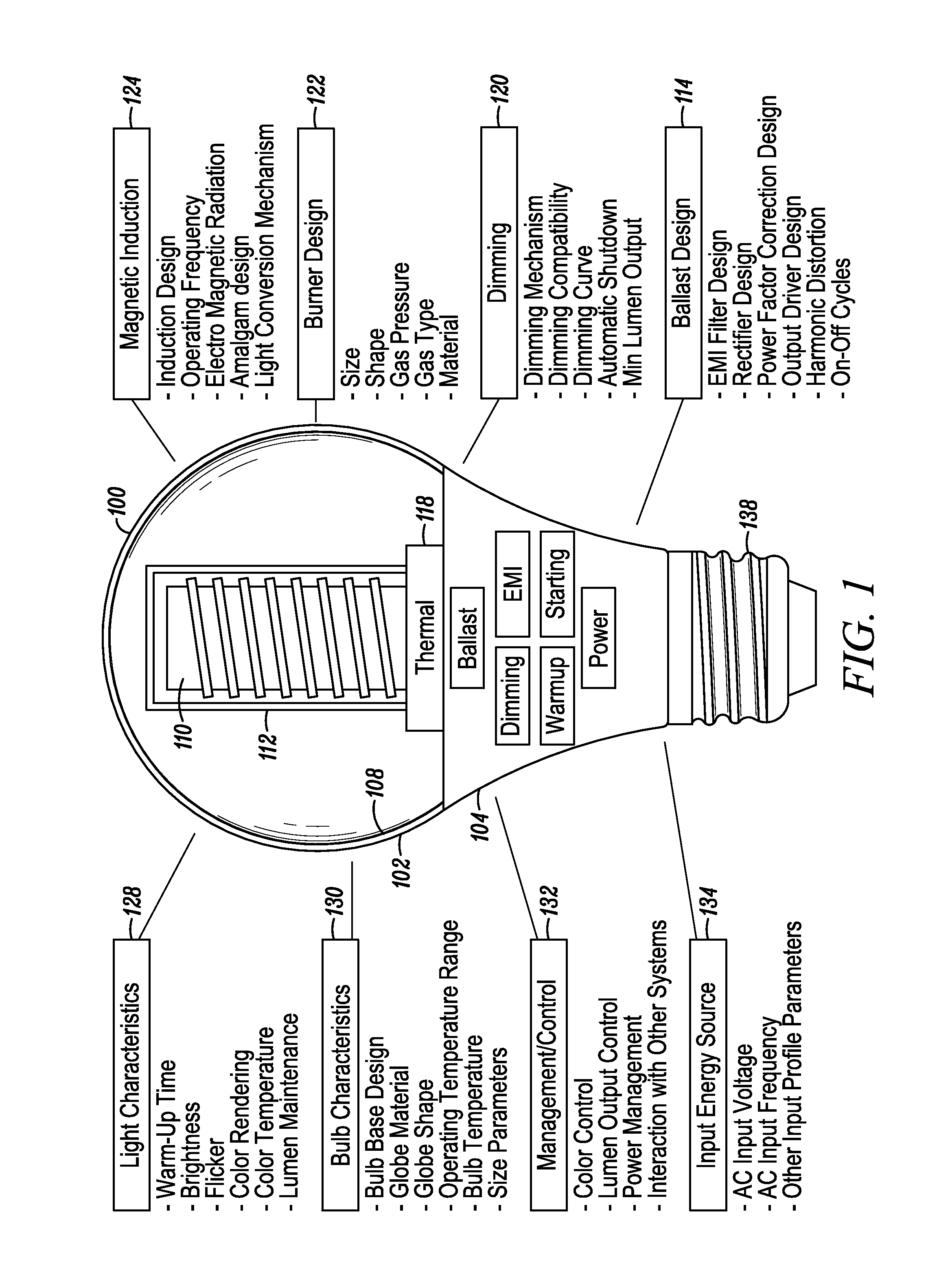

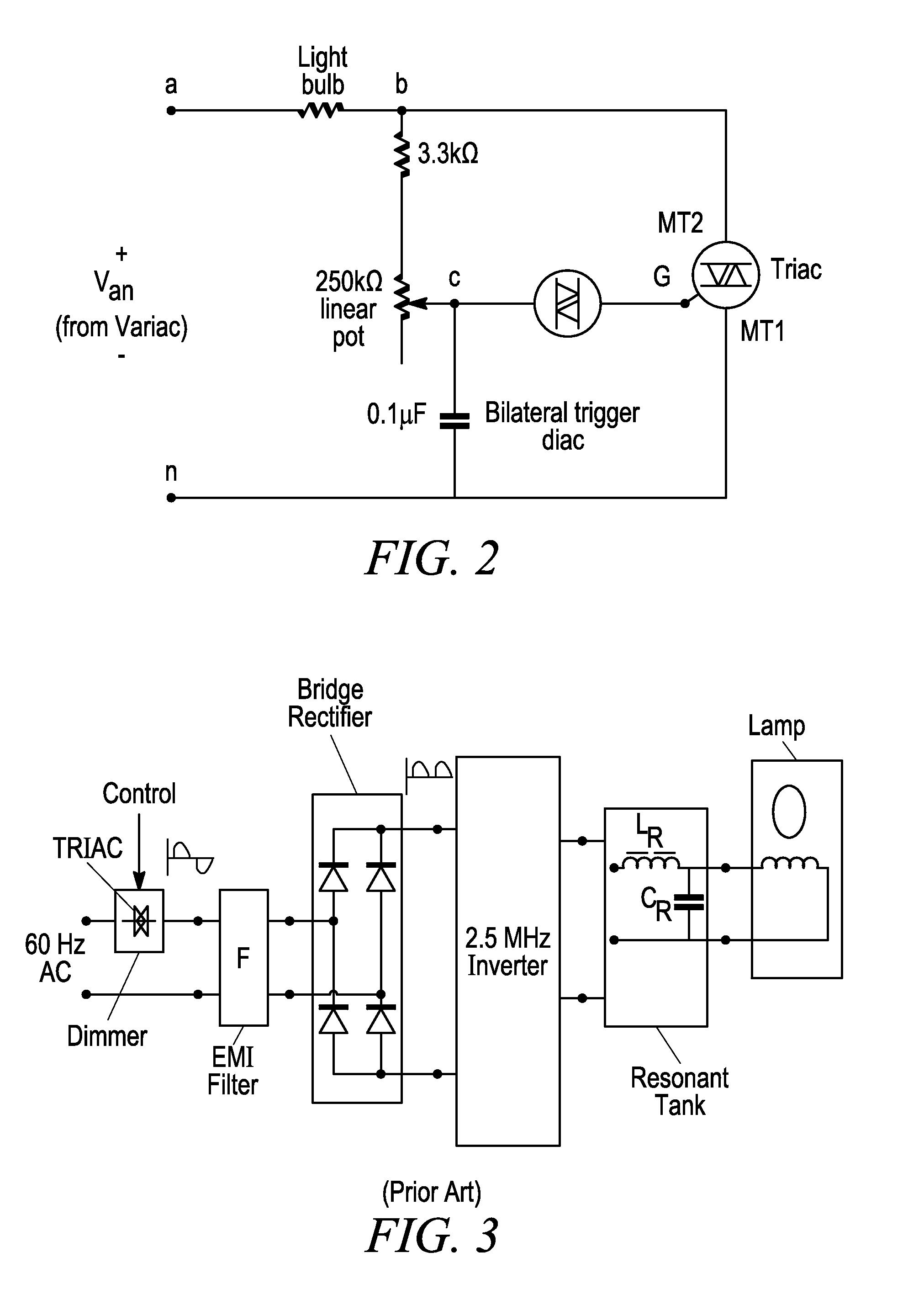

Electronic Ballast Having Improved Power Factor and Total Harmonic Distortion

ActiveUS20140145614A1Enhanced power factor correctionReduce power lossElectric discharge tubesElectric lighting sourcesTotal harmonic distortionPeak value

An electronic ballast for driving a gas discharge lamp includes an EMI filter, a bridge rectifier coupled to a DC bus without a conventional electrolytic capacitor, a passive valley fill circuit built as a network having 4 charge / discharge energy storage capacitors and 9 diodes (4C9C), and a resonant DC to AC high frequency inverter for powering gas discharge lamp. The 4C9D circuit divides the rectified peak voltage by four and the low output voltage of the circuit is used to provide continuous lamp operation. The result is a ballast having substantially improved power factor, total harmonic distortion, and current crest factor. The electronic ballast is provided with a dimming capability from a TRIAC based wall dimmer.

Owner:LUCIDITY LIGHTS

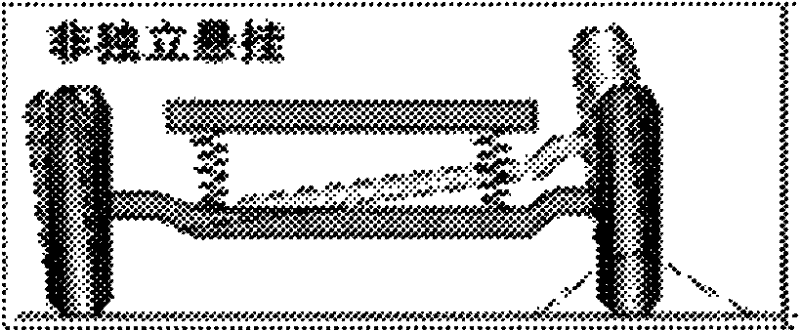

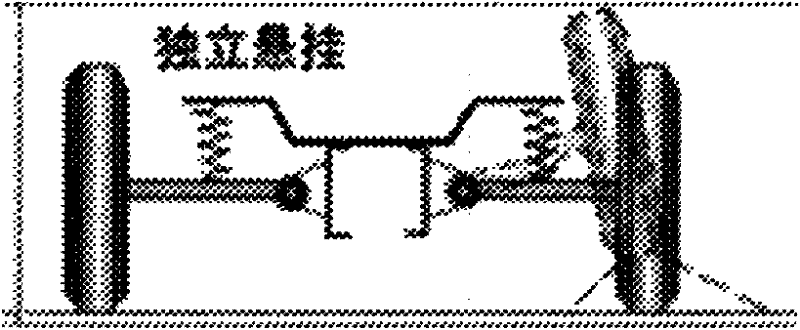

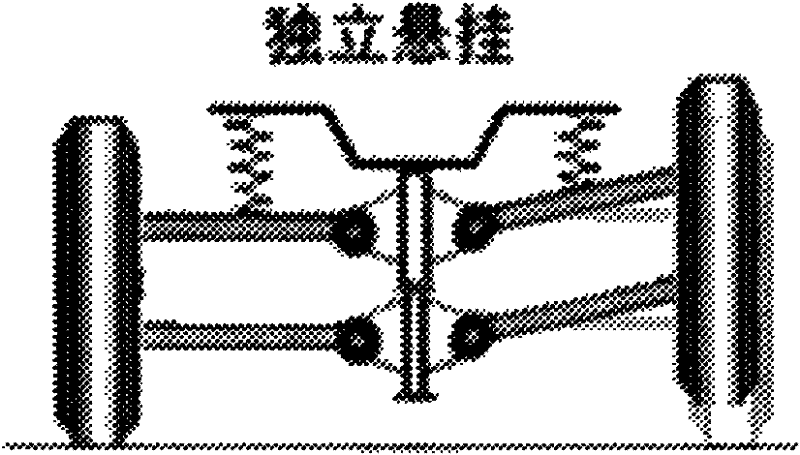

Self compensation floating swing arm independent suspension system

ActiveCN102363408AIdeal handlingIdealized securityInterconnection systemsResilient suspensionsAnti-roll barCamber angle

The invention provides a self compensation floating swing arm independent suspension system, comprising a self compensation floating swing arm independent suspension device and a centrifugal force control scissors-type anti-roll bar device. The two mechanisms can be used in combination or independently and are applicable to both front wheels and rear wheels. The self compensation floating swing arm independent suspension system guarantees that wheels perform line bounce along a vertical direction of a car body on various kinds of road surfaces when a car runs at a low speed or at a high speed or makes turns and guarantees maximum contact area between the wheels and the road surfaces, with the parameters of king pin angle, toe-in angle, camber angle, wheel track, and axle base being maintained the same as original parameters; and, when the car makes turns, the centrifugal force control scissors-type anti-roll bar device works automatically, offsets a roll force with a force equal to the roll force in magnitude and opposite to the roll force in direction, and enables the car body to lower automatically, thereby improving anti-roll capacity and realizing idealization of controllability, safety, stability and comfort of the car. The self compensation floating swing arm independent suspension system has a simple structure, excellent performance, and low cost, and is easy to realize.

Owner:侯贺

Micro Vein Enhancer

ActiveUS20070161909A1Reduce in quantityEasy to operateImage analysisDiagnostics using lightBlood testFlat panel display

The present invention is a Miniature Vein Enhancer that includes a Miniature Projection Head. The Miniature Projection Head may be operated in one of three modes, AFM, DBM, and RTM. The Miniature Projection Head of the present invention projects an image of the veins of a patient, which aids the practitioner in pinpointing a vein for an intravenous drip, blood test, and the like. The Miniature projection head may have a cavity for a power source or it may have a power source located in a body portion of the Miniature Vein Enhancer. The Miniature Vein Enhancer may be attached to one of several improved needle protectors, or the Miniature Vein Enhancer may be attached to a body similar to a flashlight for hand held use. The Miniature Vein Enhancer of the present invention may also be attached to a magnifying glass, a flat panel display, and the like.

Owner:ACCUVEIN

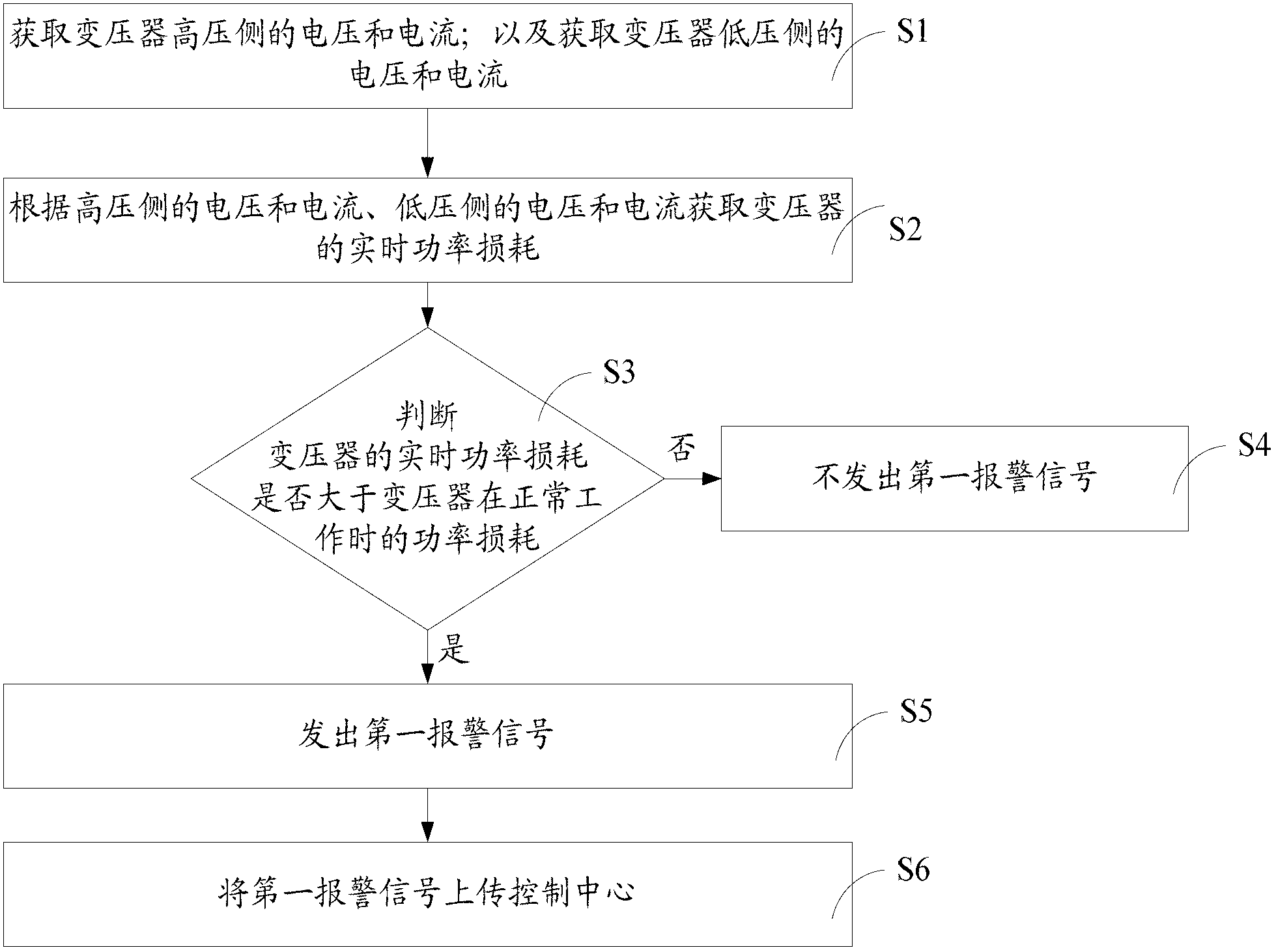

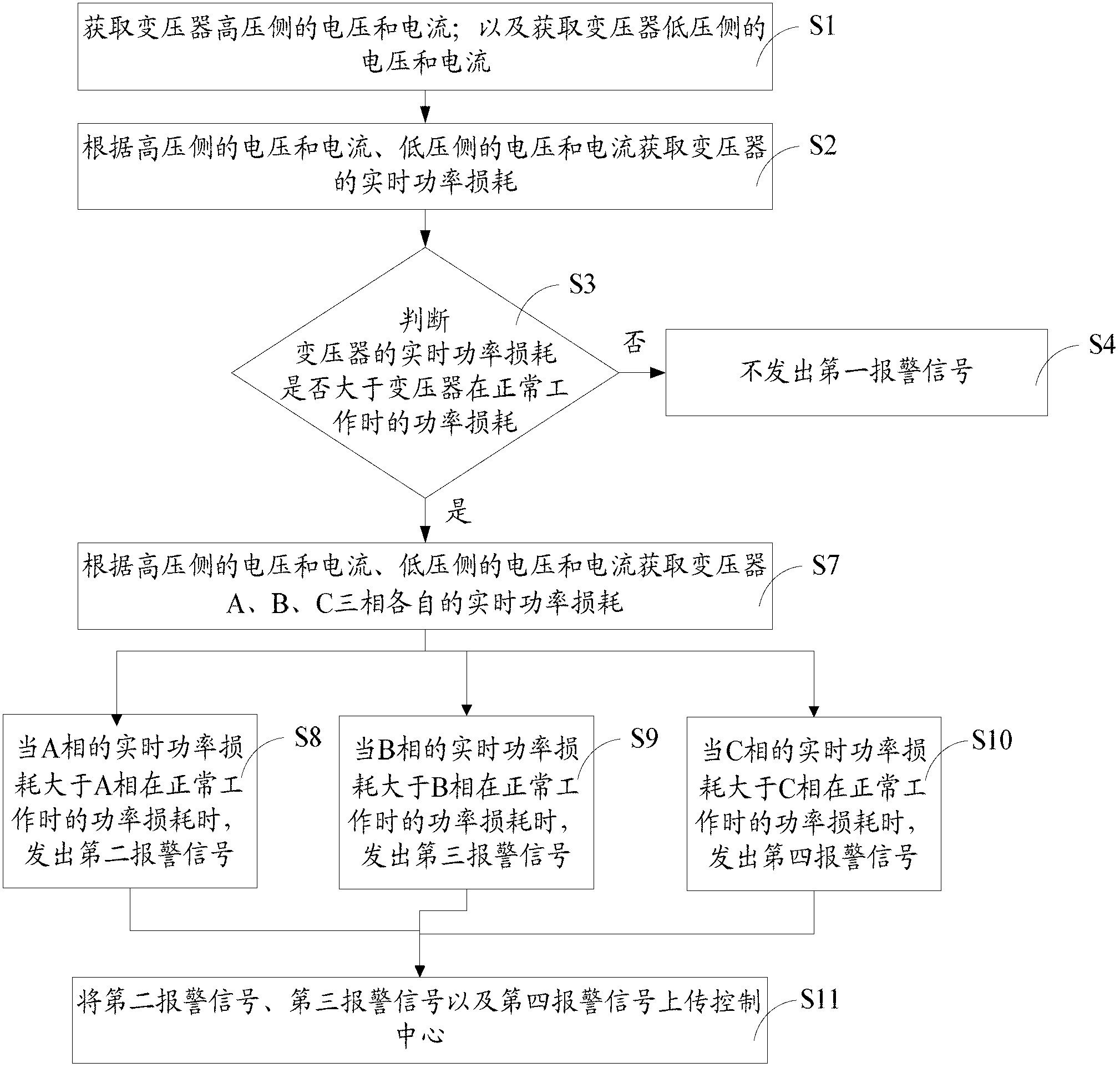

On-line monitoring method and device of distribution transformer turn-to-turn short circuit

InactiveCN103063974ATimely detection of turn-to-turn short circuit faultsIncreased power lossElectrical testingShort-circuit testDistribution transformer

The invention provides an on-line monitoring method of distribution transformer turn-to turn short circuit. The on-line monitoring method includes the following steps: under the no-load condition, voltage and currents of the high-pressure side of a transformer are obtained, and voltage and currents of the low-pressure side of the transformer are obtained; real-time power losses are obtained according to the voltage and the currents of the high-pressure side and the voltage and the currents of the low-pressure side; the real-time power losses are judged whether to be larger than power losses or not when the transformer works normally; if so, a first alarm signal is sent out, and if not, the first alarm signal is not sent out; and the first alarm signal is uploaded to a control center. The invention provides an on-line monitoring device of the distribution transformer turn-to-turn short circuits. The on-line monitoring device of the distribution transformer turn-to turn short circuit can carry out on-line monitoring in real time and detect failures of the transformer turn-to-turn short circuit timely. Engineering practices are relatively simple, and obvious influences on an original system and structure can not occur.

Owner:GUANGZHOU POWER SUPPLY CO LTD +1

Micro vein enhancer

The present invention is a Miniature Vein Enhancer that includes a Miniature Projection Head. The Miniature Projection Head may be operated in one of three modes, AFM, DBM, and RTM. The Miniature Projection Head of the present invention projects an image of the veins of a patient, which aids the practitioner in pinpointing a vein for an intravenous drip, blood test, and the like. The Miniature projection head may have a cavity for a power source or it may have a power source located in a body portion of the Miniature Vein Enhancer. The Miniature Vein Enhancer may be attached to one of several improved needle protectors, or the Miniature Vein Enhancer may be attached to a body similar to a flashlight for hand held use. The Miniature Vein Enhancer of the present invention may also be attached to a magnifying glass, a flat panel display, and the like.

Owner:ACCUVEIN

Micro vein enhancer

ActiveUS20070161908A1Reduce in quantityEasy to operateImage analysisDiagnostics using lightVeinBlood test

The present invention is a Miniature Vein Enhancer that includes a Miniature Projection Head. The Miniature Projection Head may be operated in one of three modes, AFM, DBM, and RTM. The Miniature Projection Head of the present invention projects an image of the veins of a patient, which aids the practitioner in pinpointing a vein for an intravenous drip, blood test, and the like. The Miniature projection head may have a cavity for a power source or it may have a power source located in a body portion of the Miniature Vein Enhancer. The Miniature Vein Enhancer may be attached to one of several improved needle protectors, or the Miniature Vein Enhancer may be attached to a body similar to a flashlight for hand held use. The Miniature Vein Enhancer of the present invention may also be attached to a magnifying glass, a flat panel display, and the like.

Owner:ACCUVEIN