Self-adaptation voltage regulator circuit

A technology of self-adapting voltage and regulating circuit, applied in the direction of regulating electrical variables, control/regulating systems, electrical components, etc., can solve the problem that the tracking speed of operating frequency is easily limited by interface speed, performance limited nonlinearity and loop delay, Large output voltage ripple and other problems, to achieve the effects of good step response, reduced power loss, and fast voltage adjustment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] Below in conjunction with accompanying drawing and embodiment the present invention is described in detail

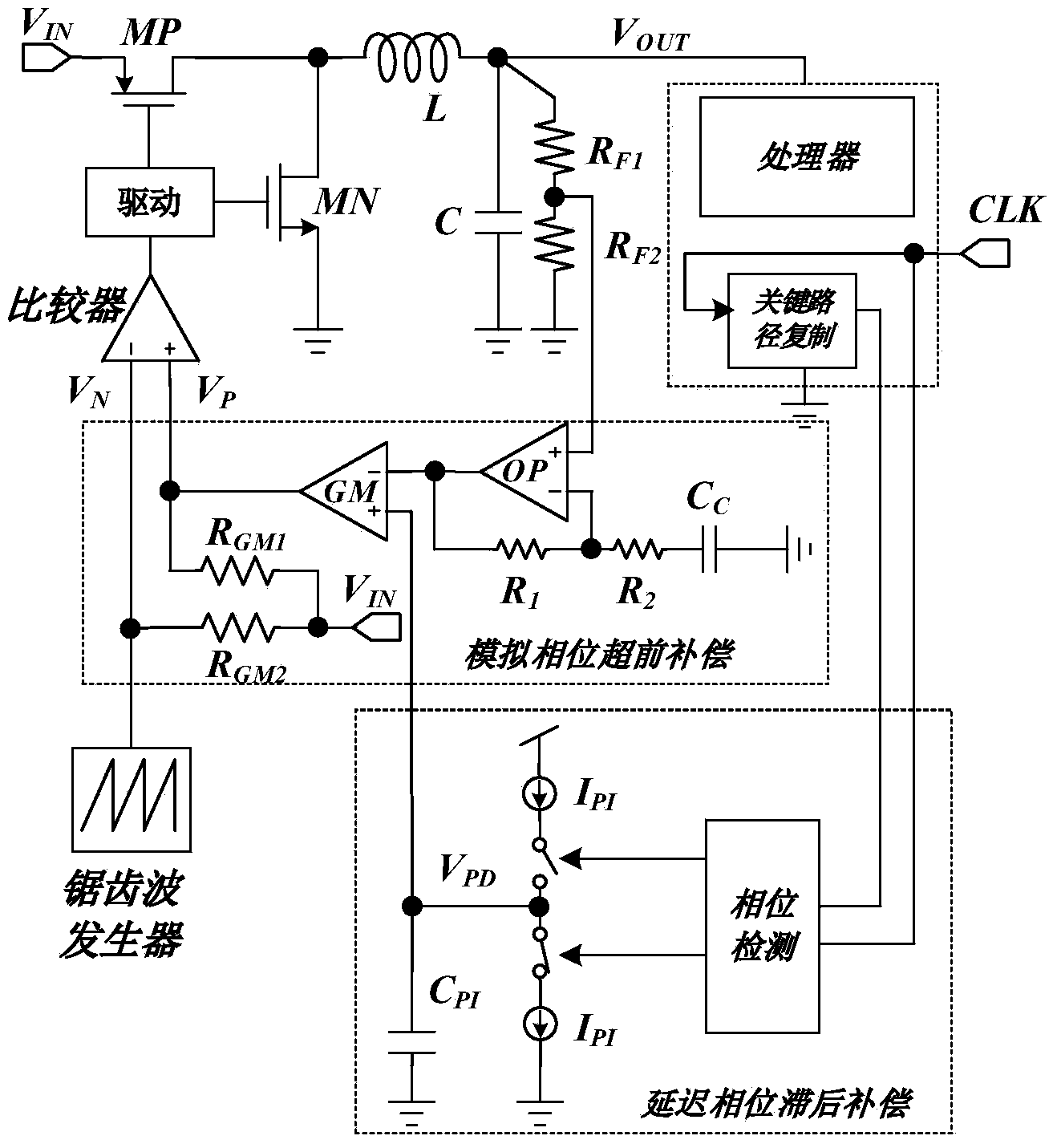

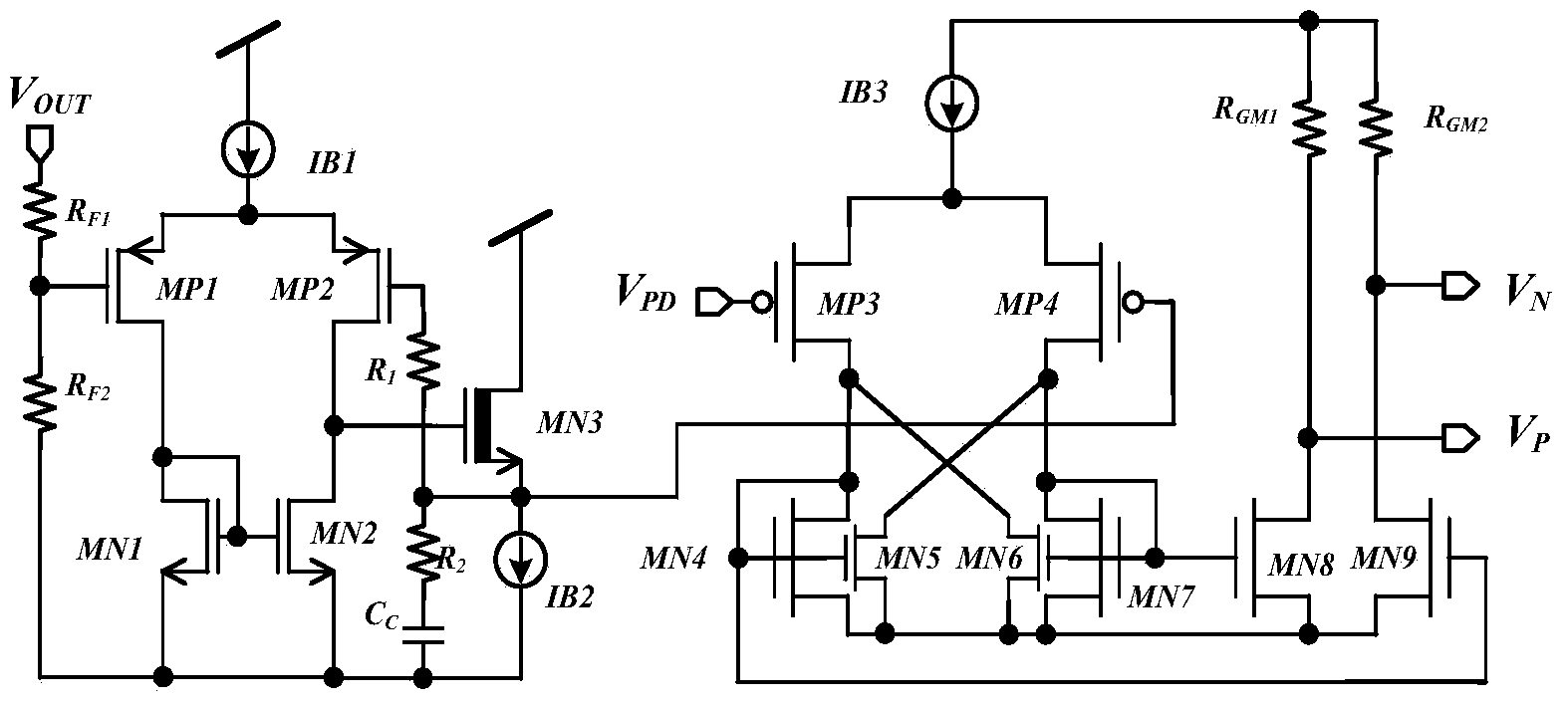

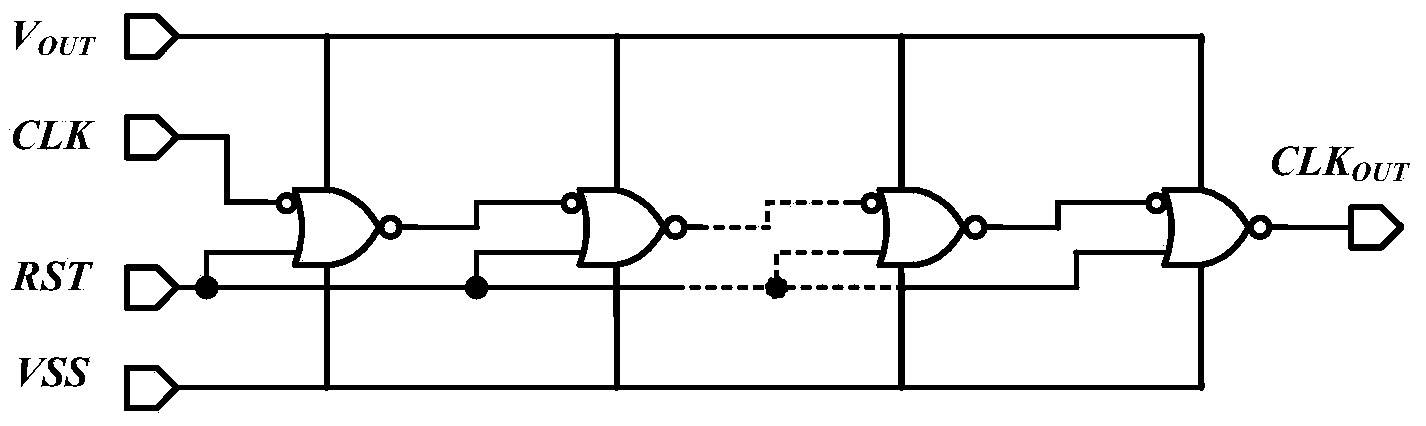

[0019] Such as figure 1 As shown, the present invention is an AVS circuit based on pseudo three-type compensation, including power transistors MP and MN, inductor L, capacitor C, first resistor RF1, second resistor RF2, analog phase lead compensation module, delay phase lag compensation Module, critical path replication module CPR, sawtooth wave generation module OSC, comparator Comp, power tube driver Driver. The output voltage Vout is divided by resistors Rf1 and Rf2. Operational amplifier OP, resistors R1 and R2, and capacitor Cc realize analog phase lead compensation. The operational transconductance amplifier GM load is R GM1 , which provides the loop gain for APD compensation. The delay of the critical path replication (CPR) is compared with the system clock CLK via phase detection (PD). Then, the delayed error signal is integrated by a charge pump. T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More