Semiconductor device and method for manufacturing same

a technology of semiconductor devices and semiconductor devices, which is applied in the direction of semiconductor devices, basic electric elements, electrical equipment, etc., can solve the problems of dielectric breakdown of gate insulating films on the bottom of trenches, and achieve the effect of increasing on-resistance and reducing electric field concentration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0048]—Structure of Semiconductor Device—

[0049]An illustrative semiconductor device 100 according to a first embodiment of the present disclosure and a manufacturing method thereof will be described below with reference to the drawings.

[0050]For example, the semiconductor device 100 includes a plurality of unit cells each of which is a SiC-metal-insulator-semiconductor field-effect transistor (SiC-MISFET) having a trench gate structure.

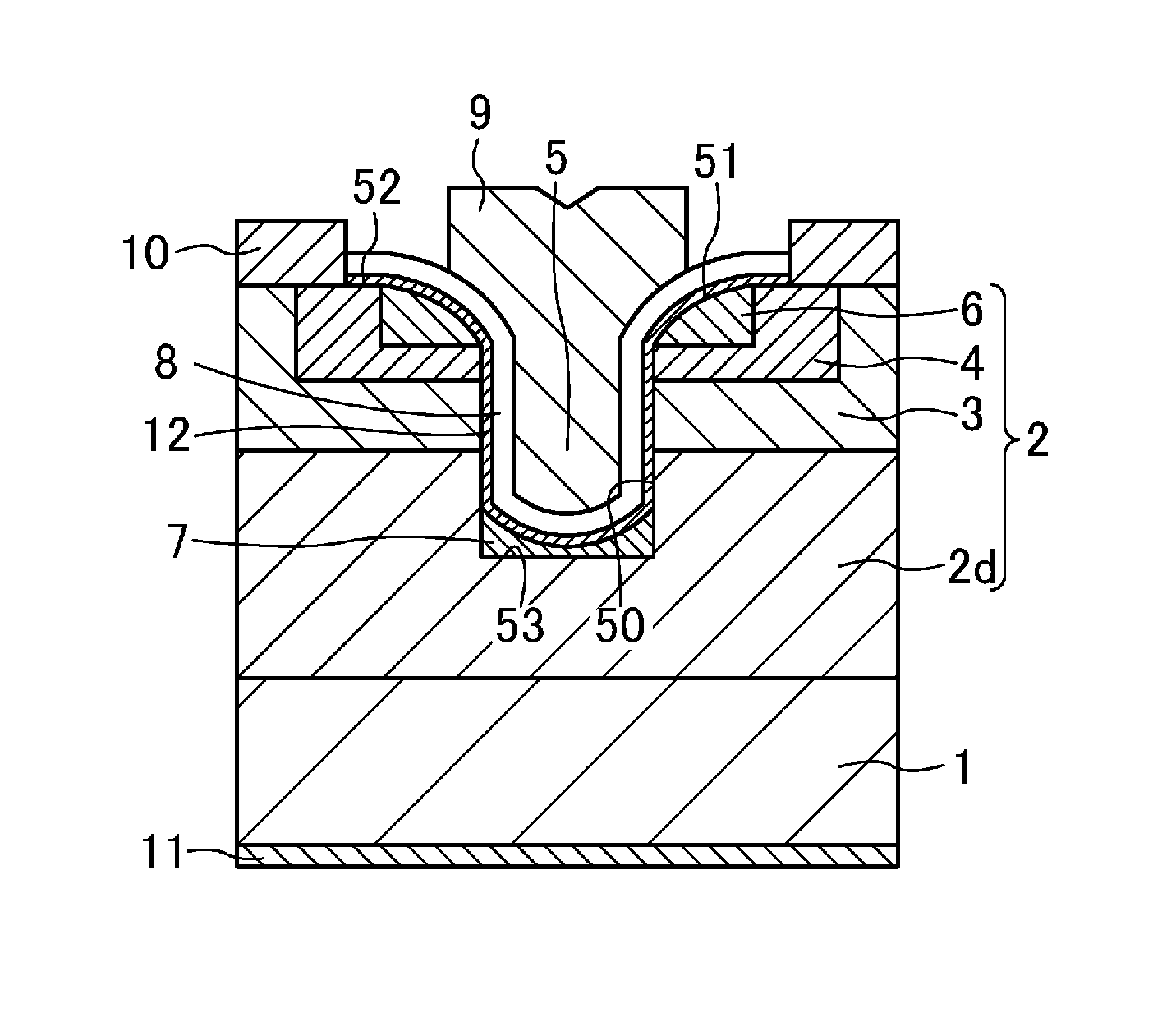

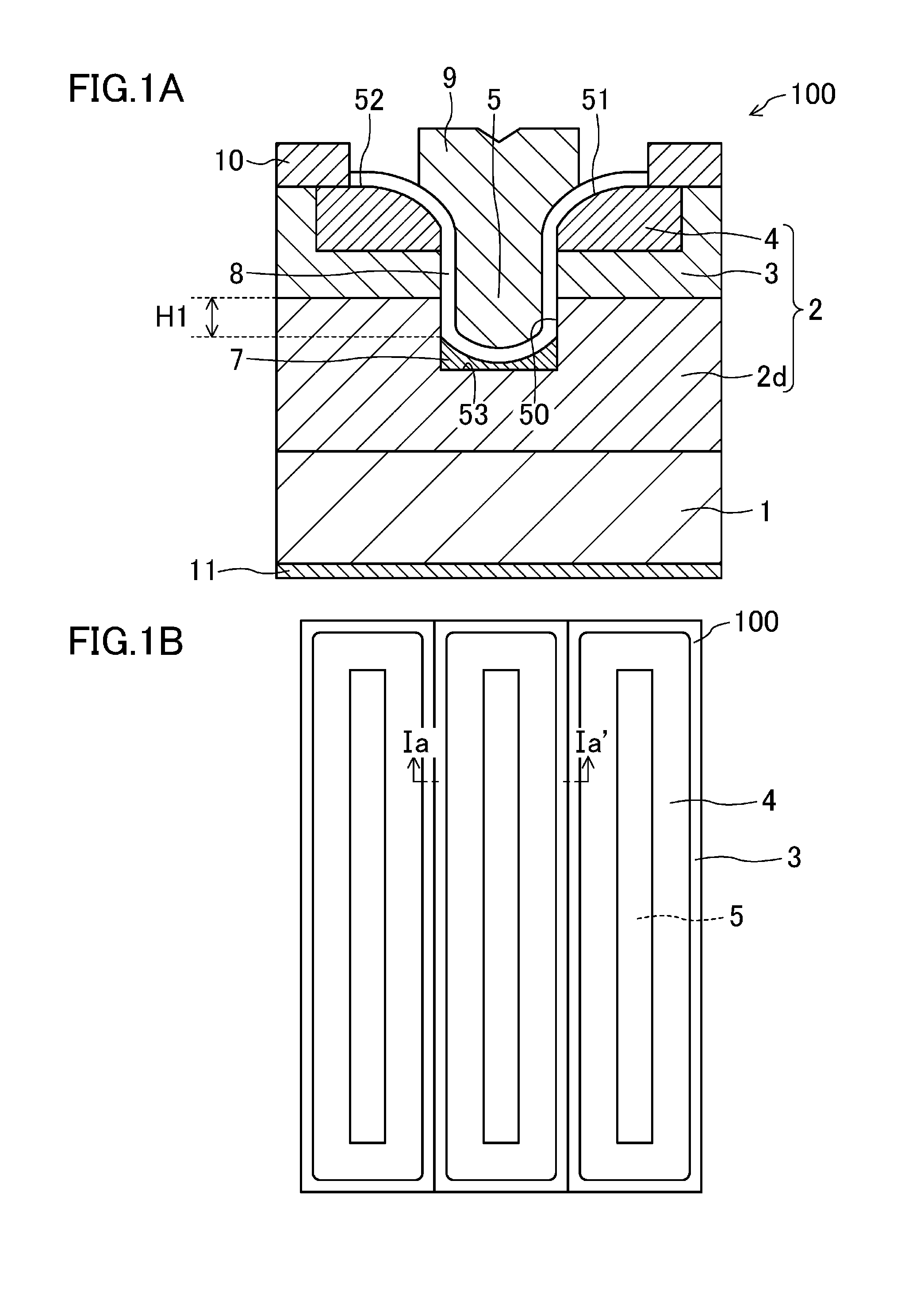

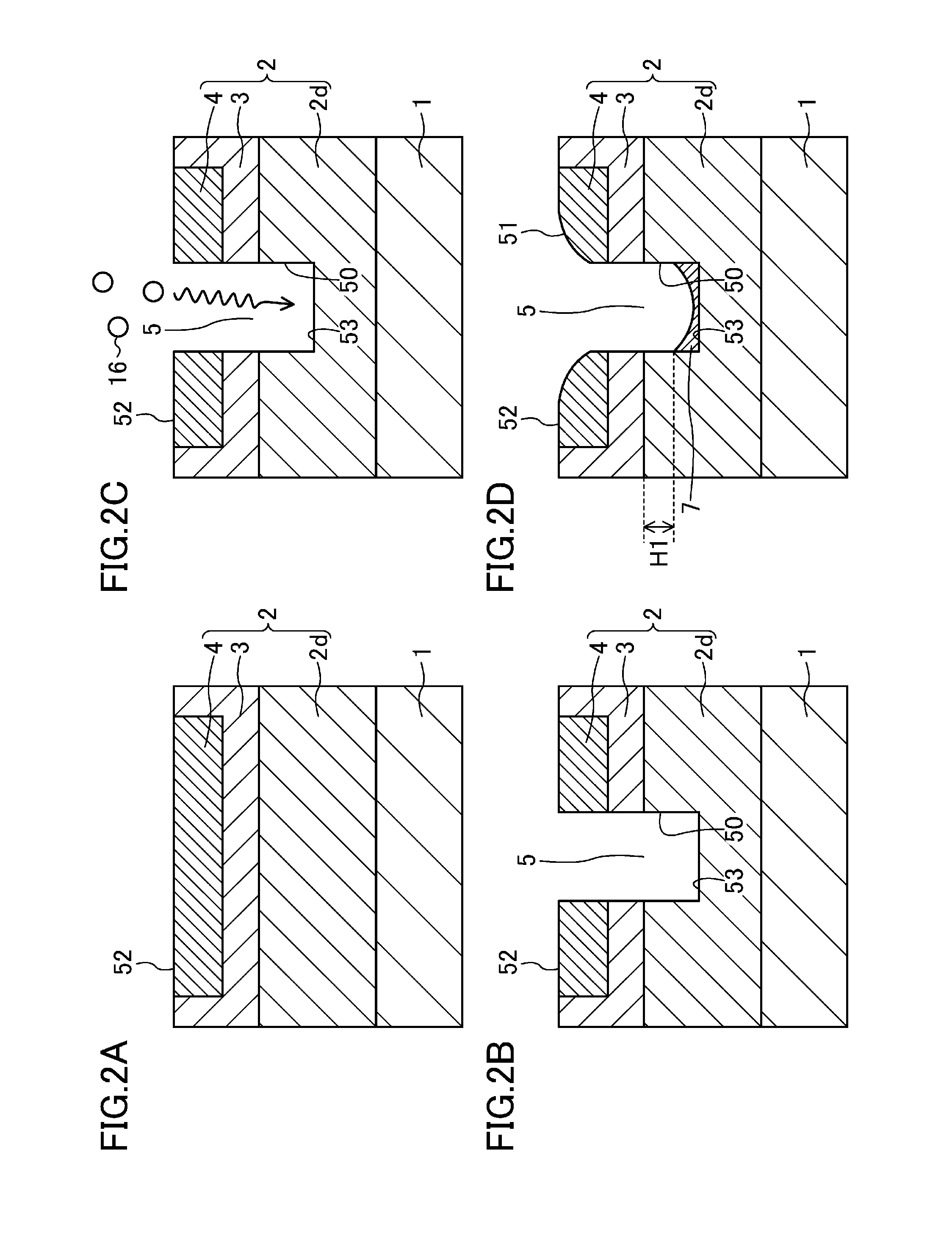

[0051]FIG. 1A schematically illustrates a cross-sectional configuration of one of the plurality of unit cells included in the semiconductor device 100. FIG. 1B schematically illustrates an exemplary configuration of the semiconductor device 100 viewed from above, specifically, the surfaces of silicon carbide layers of the plurality of unit cells (three unit cells in this embodiment). FIG. 1A is the cross-sectional view taken along the line Ia-Ia′ in FIG. 1B. FIG. 1B illustrates an arrangement of body regions 3, source regions 4, and trenches 5 while o...

second embodiment

[0136]—Structure of Semiconductor Device—

[0137]An illustrative semiconductor device 100a according to a second embodiment of the present disclosure and a manufacturing method of the semiconductor device 100a will be described below with reference to the drawings.

[0138]For example, the semiconductor device is a silicon carbide semiconductor device, and specifically, includes a plurality of unit cells each of which is a SiC-metal-insulator-semiconductor field-effect transistor (SiC-MISFET) having a trench gate structure.

[0139]FIG. 9A schematically illustrates a cross-sectional configuration of one of the plurality of the unit cells included in the semiconductor device 100a. FIG. 9B schematically illustrates an exemplary configuration of the semiconductor device 100a viewed from above, specifically, the surfaces of silicon carbide layers of the plurality of unit cells (three unit cells in this case). FIG. 9A is the cross-sectional view taken along the line Xia-XIa′ in FIG. 9B. FIG. 9B ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More