Patents

Literature

219 results about "Impurity doping" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

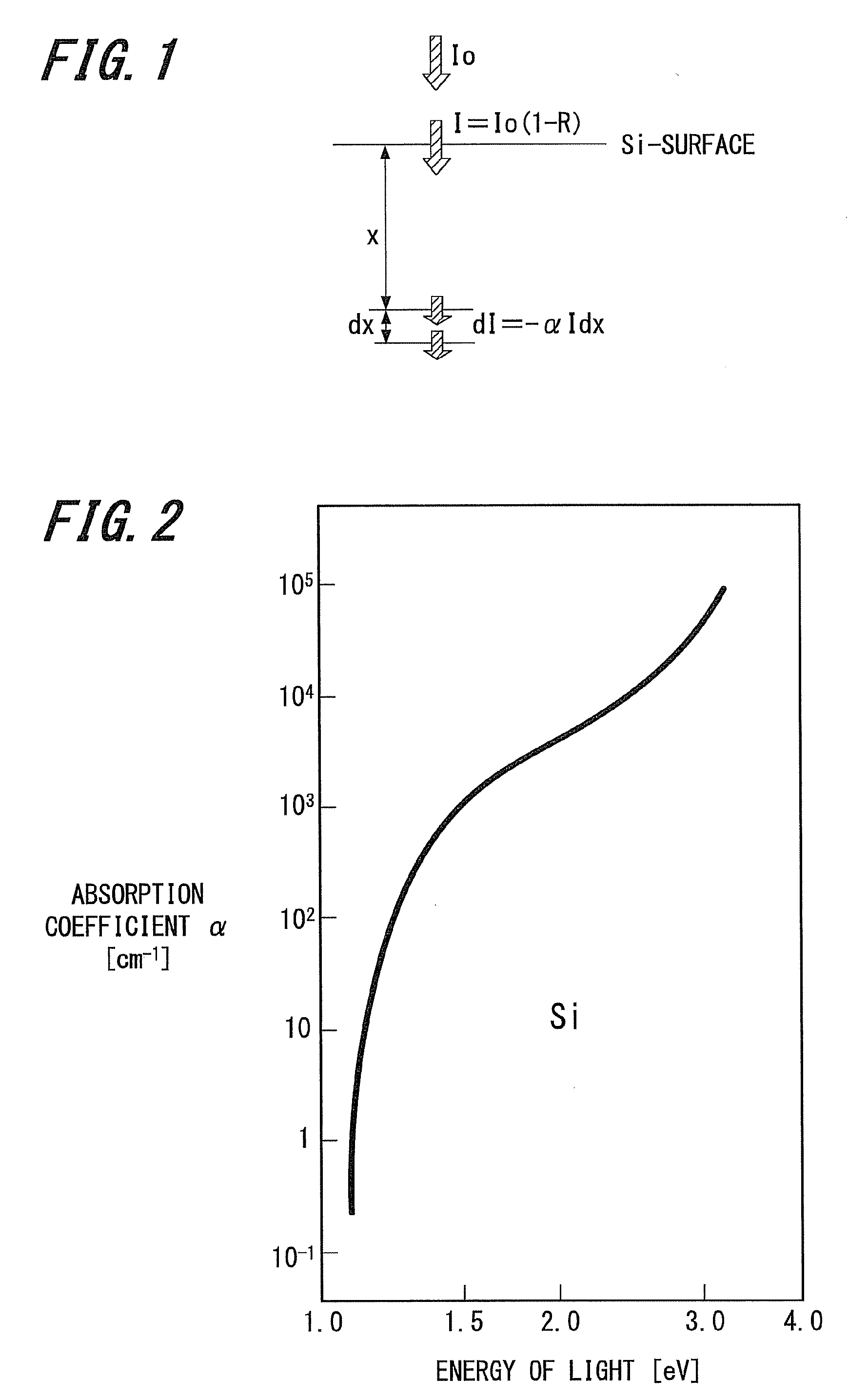

Doping is the process of adding impurities to intrinsic semiconductors to alter their properties. Normally Trivalent and Pentavalent elements are used to dope Silicon and Germanium. When an intrinsic semiconductor is doped with Trivalent impurity it becomes a P-Type semiconductor.

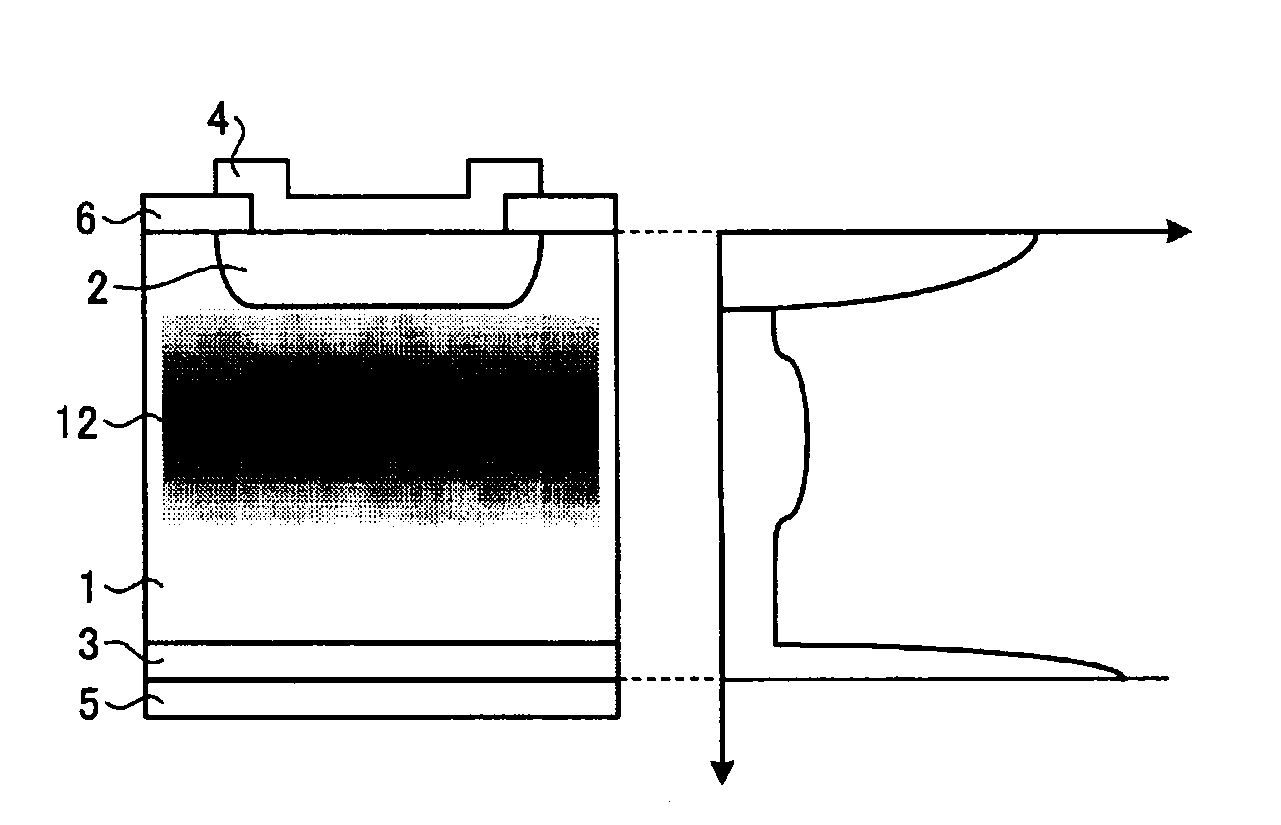

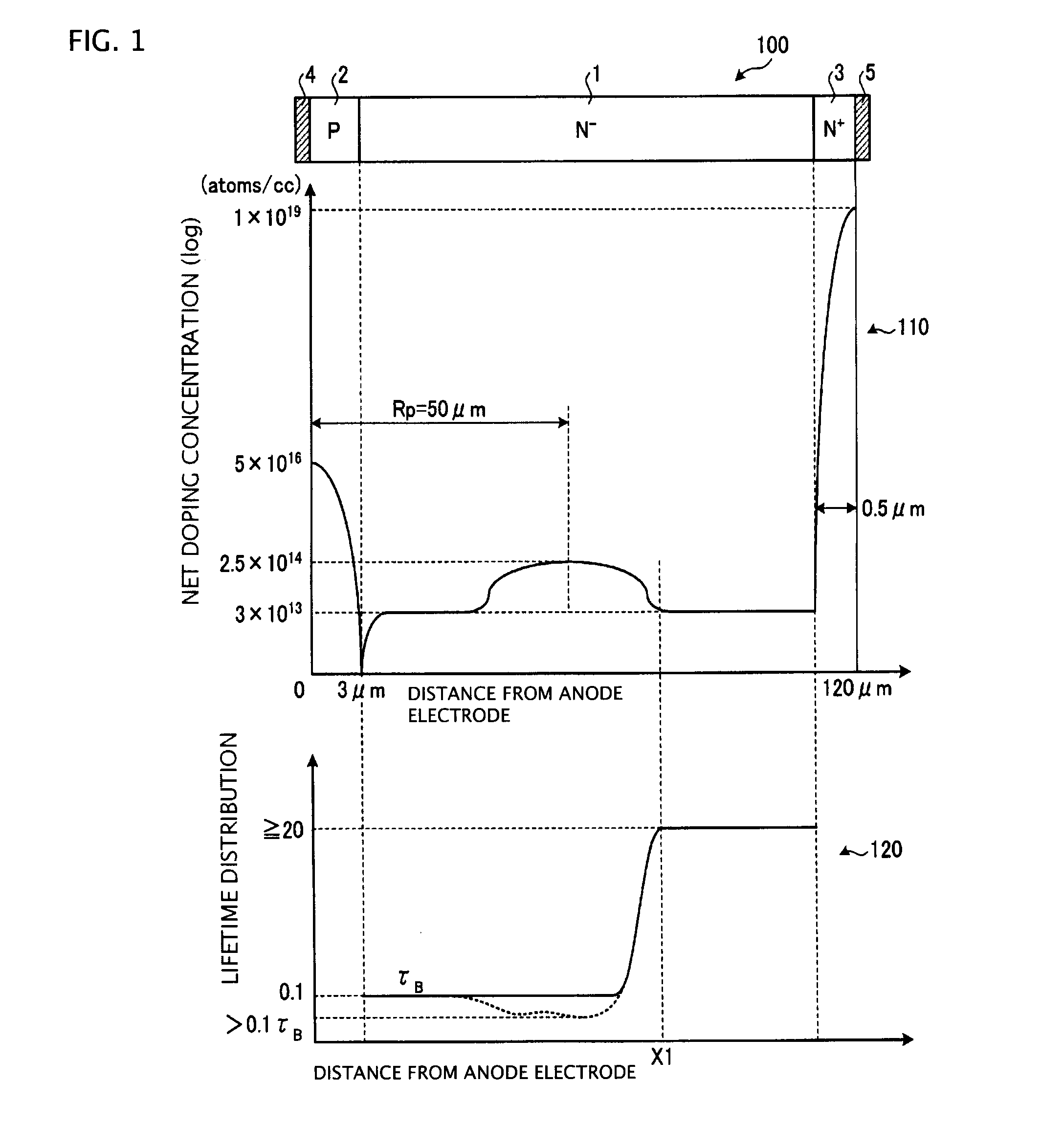

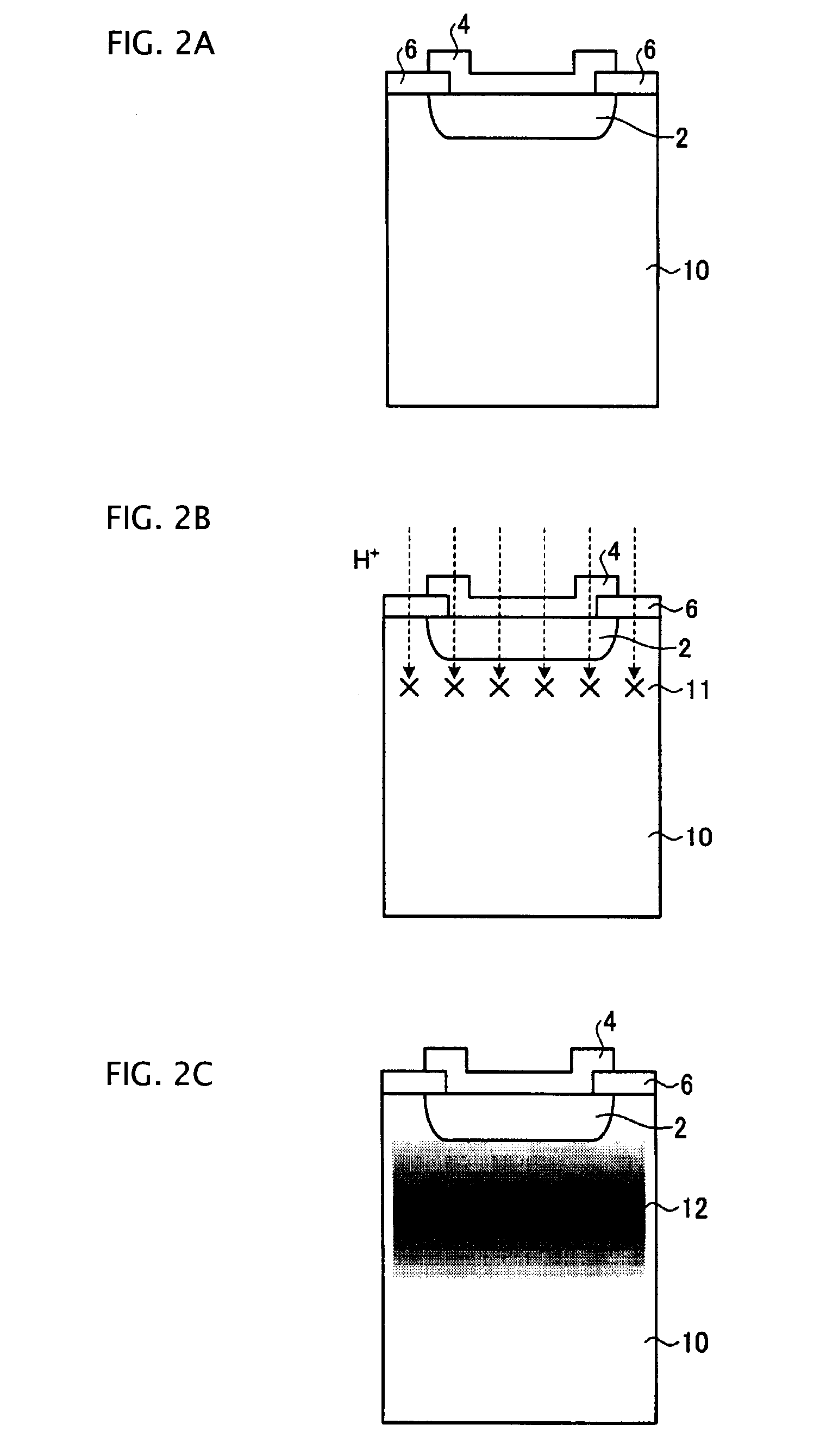

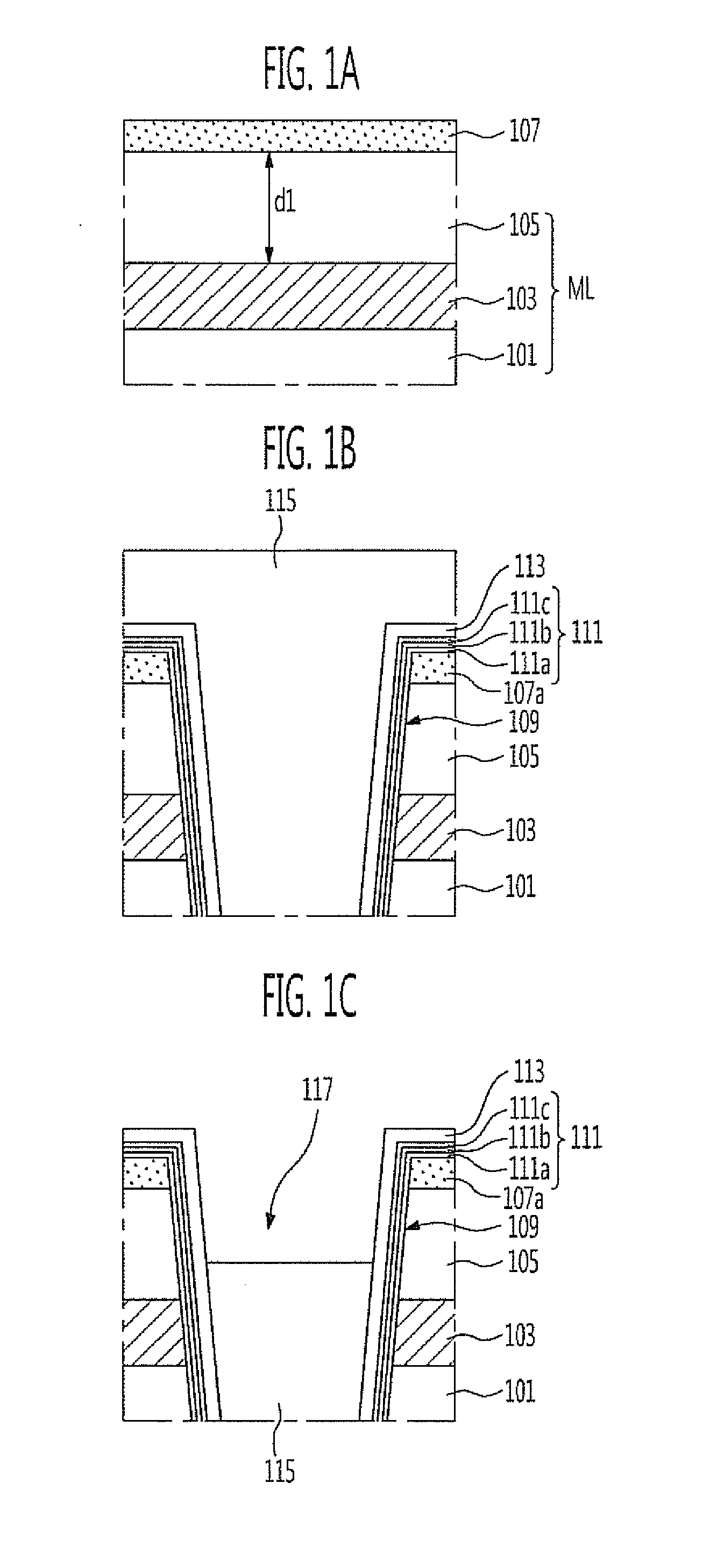

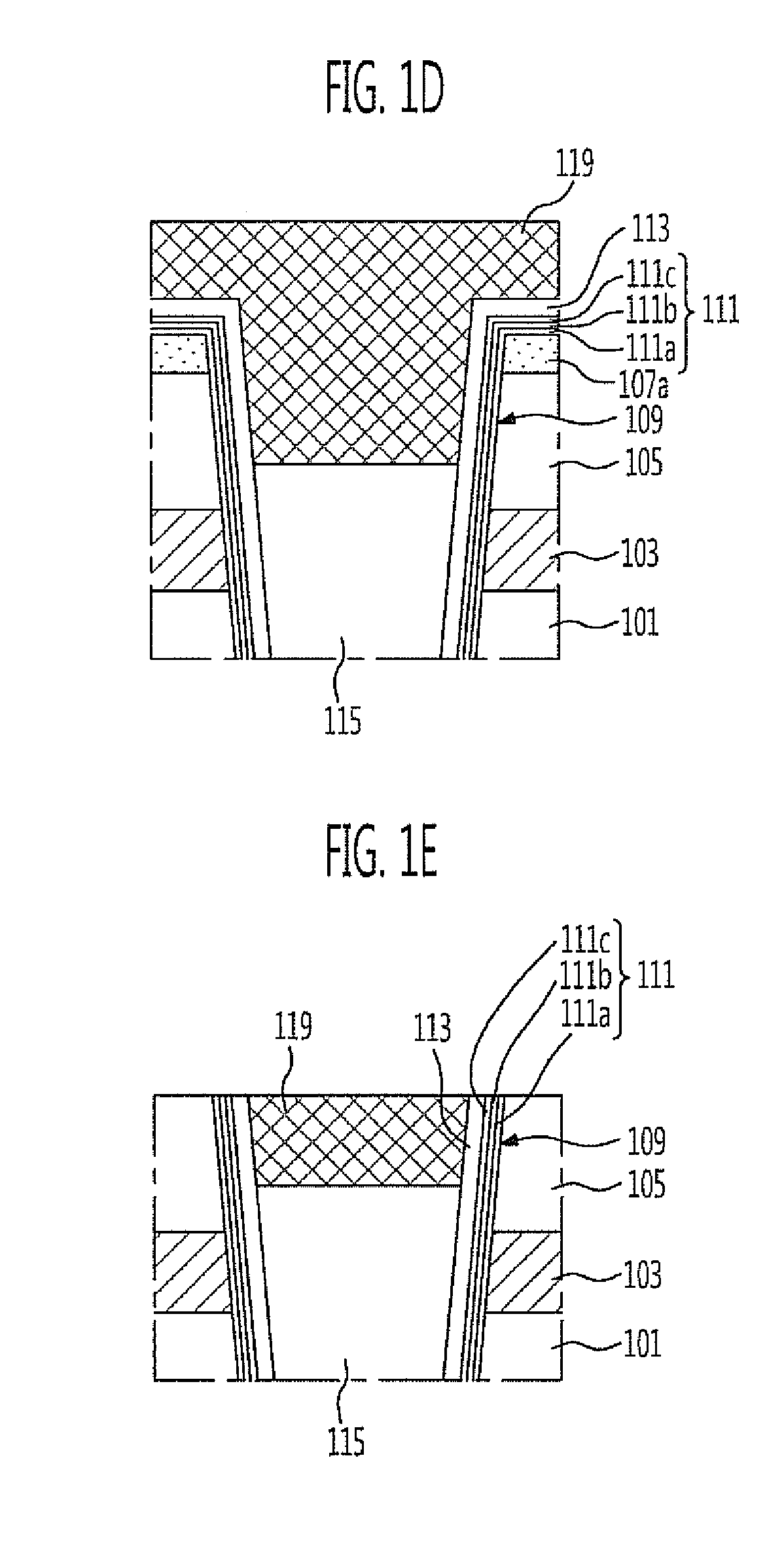

Semiconductor device and method of producing the same

ActiveUS20090224284A1Soft recovery characteristicHigh-speed and low-loss characteristicSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorImpurity doping

A semiconductor substrate and a method of its manufacture has a semiconductor substrate having a carbon concentration in a range of 6.0×1015 to 2.0×1017 atoms / cm3, both inclusively. One principal surface of the substrate is irradiated with protons and then heat-treated to thereby form a broad buffer structure, namely a region in a first semiconductor layer where a net impurity doping concentration is locally maximized. Due to the broad buffer structure, lifetime values are substantially equalized in a region extending from an interface between the first semiconductor layer and a second semiconductor layer formed on the first semiconductor layer to the region where the net impurity doping concentration is locally maximized. In addition, the local minimum of lifetime values of the first semiconductor layer becomes high. It is thus possible to provide a semiconductor device having soft recovery characteristics, in addition to high-speed and low-loss characteristics, while suppressing a kinked leakage current waveform.

Owner:FUJI ELECTRIC CO LTD

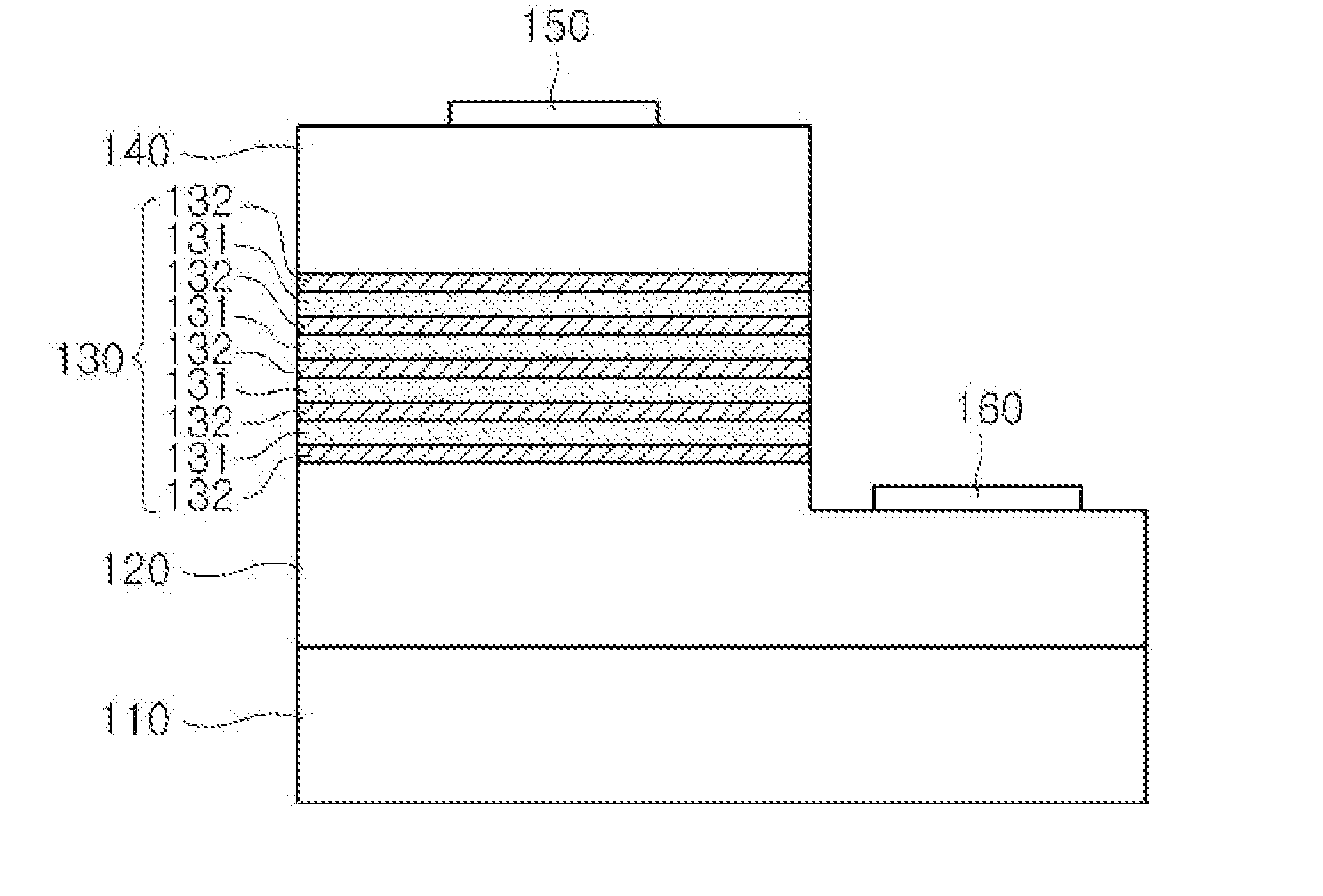

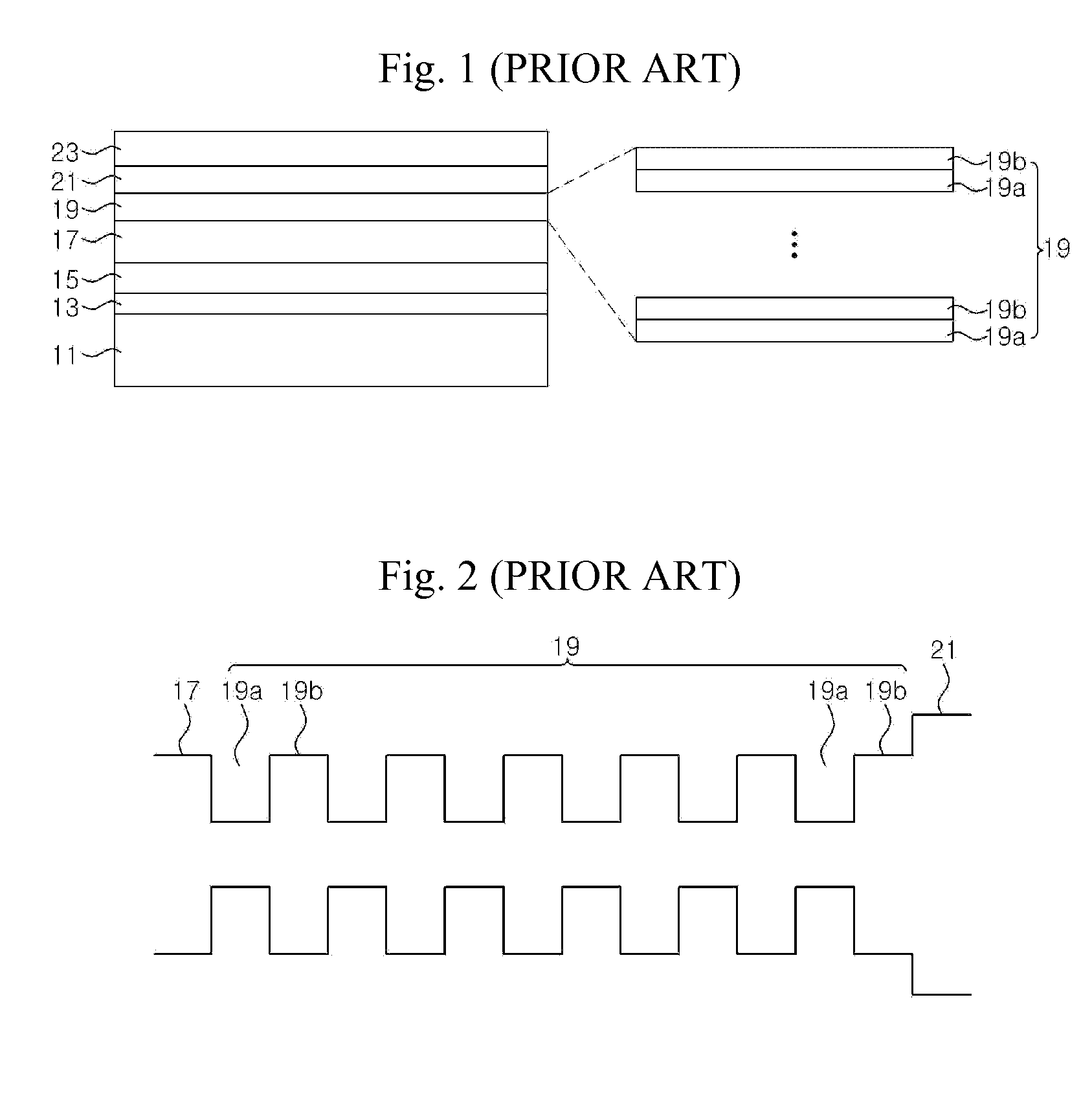

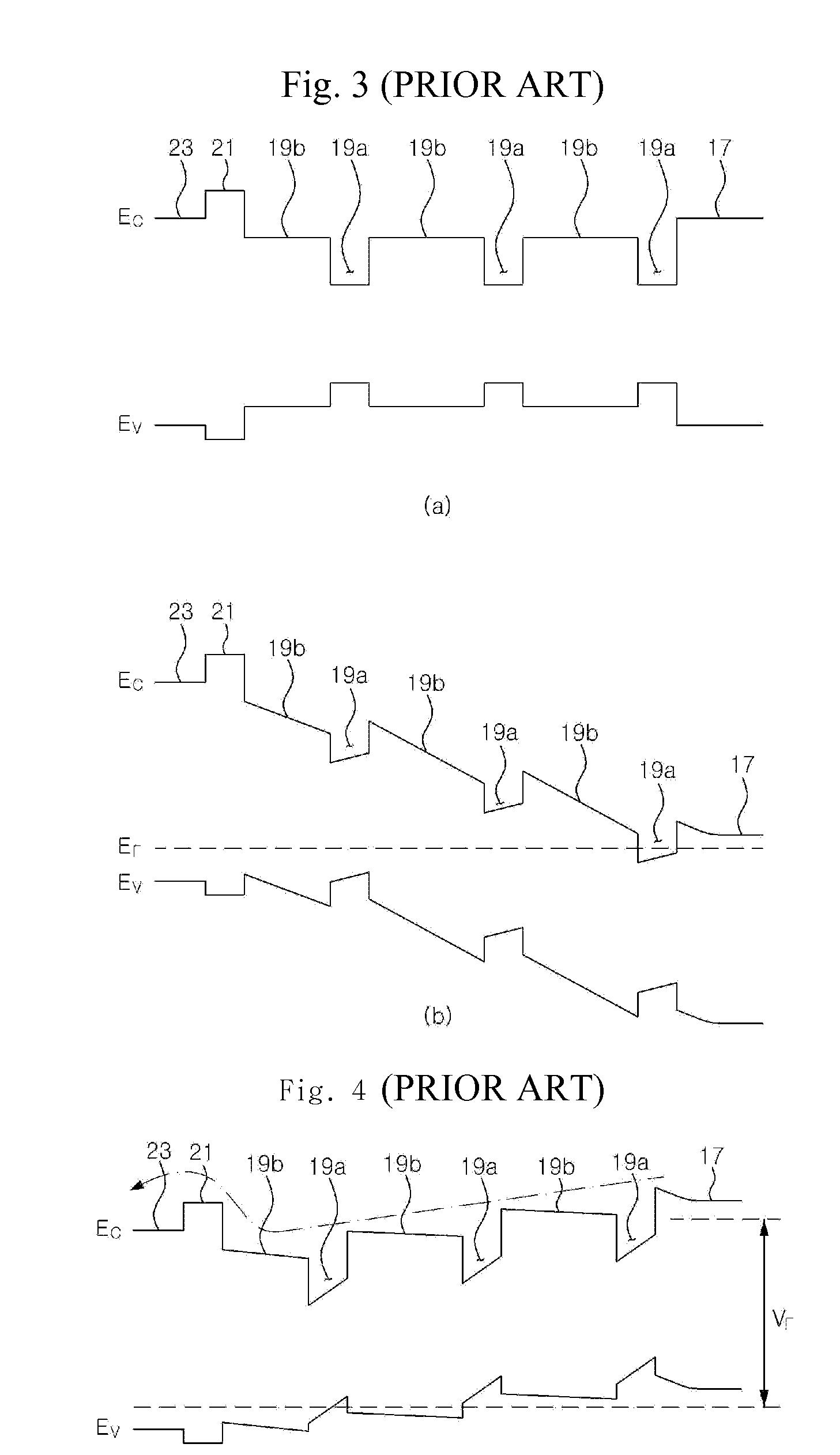

Light emitting diode having active region of multi quantum well structure

ActiveUS20080308787A1Improve luminous efficiencyEnhance rate of recombinationSemiconductor devicesImpurity dopingLight-emitting diode

Disclosed is a light emitting diode (LED) having an active region of a multiple quantum well structure in which well layers and barrier layers are alternately laminated between a GaN-based N-type compound semiconductor layer and a GaN-based P-type compound semiconductor layer. The LED includes a middle barrier layer having a bandgap relatively wider than the first barrier layer adjacent to the N-type compound semiconductor layer and the n-th barrier layer adjacent to the P-type compound semiconductor layer. The middle barrier layer is positioned between the first and n-th barrier layers. Accordingly, positions at which electrons and holes are combined in the multiple quantum well structure to emit light can be controlled, and luminous efficiency can be enhanced. Furthermore, an LED is provided with enhanced luminous efficiency using a bandgap engineering or impurity doping technique.

Owner:SEOUL VIOSYS CO LTD

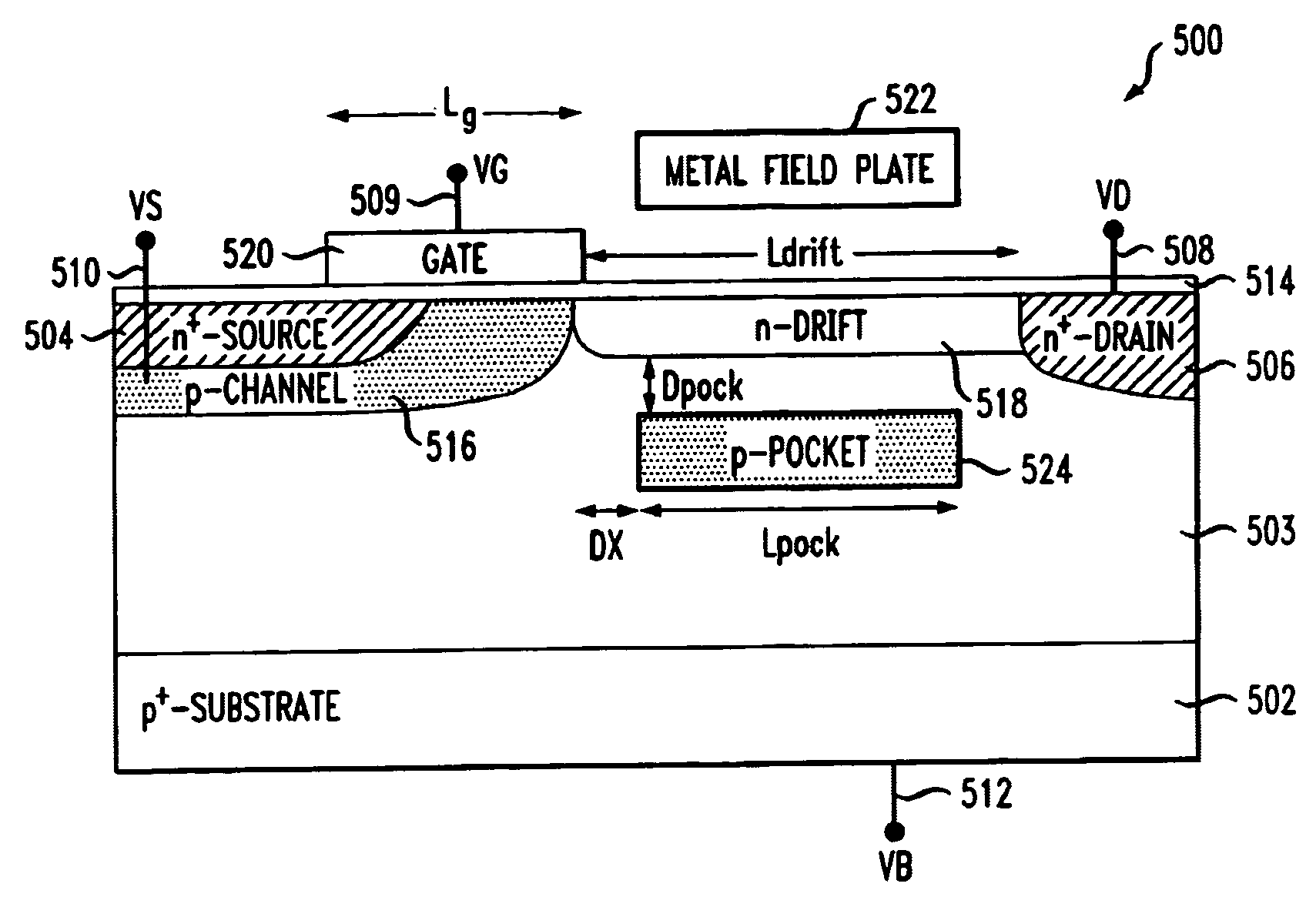

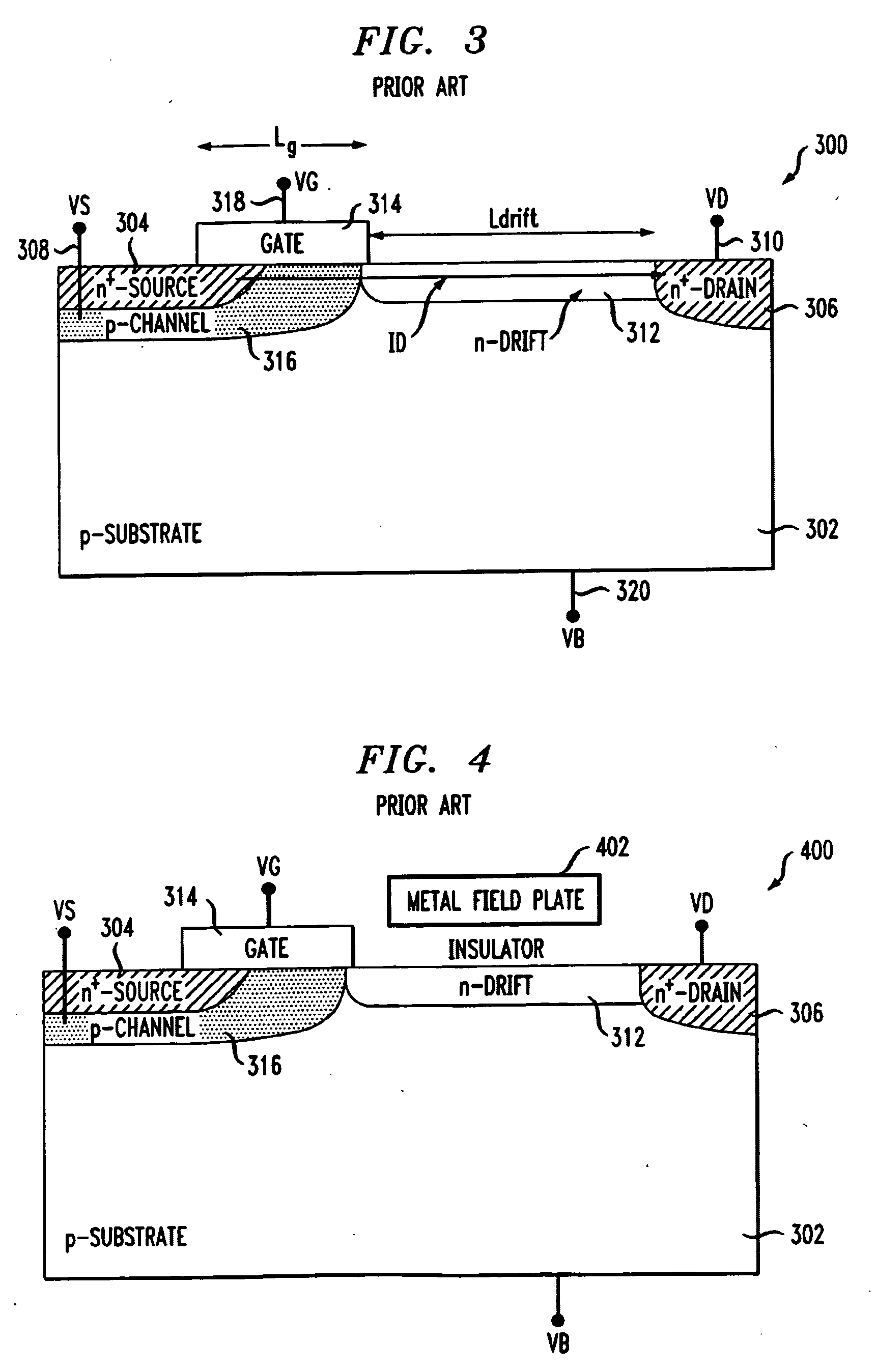

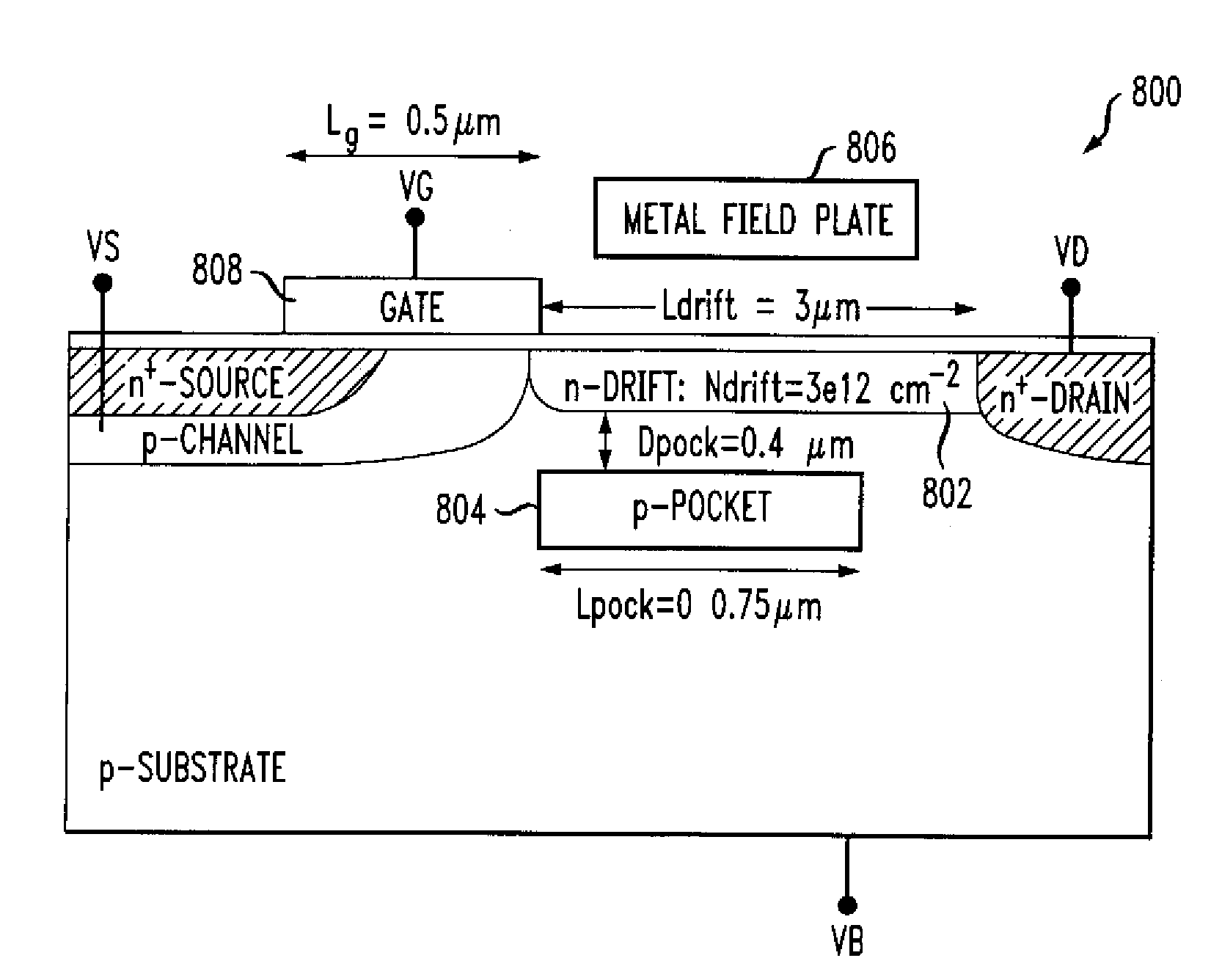

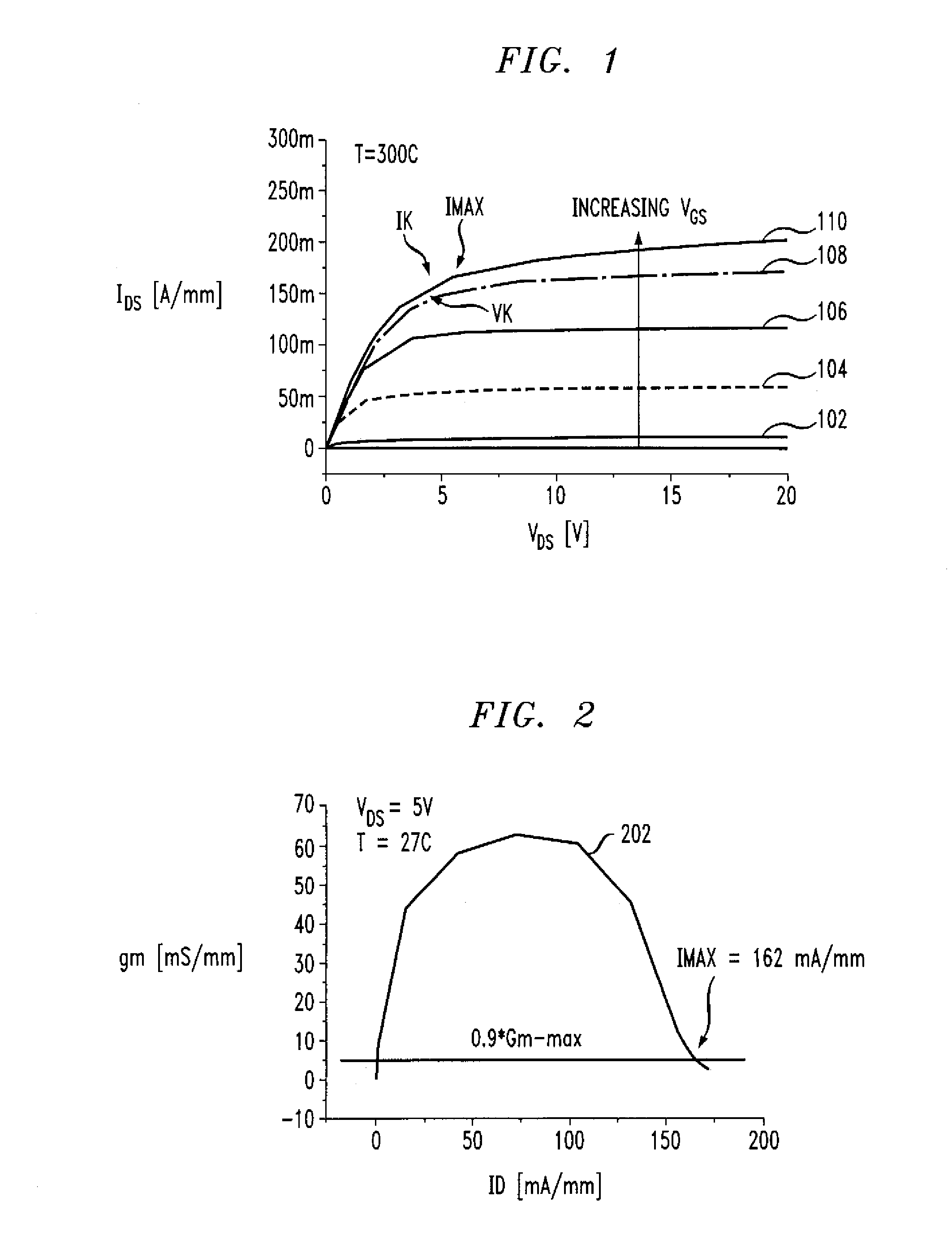

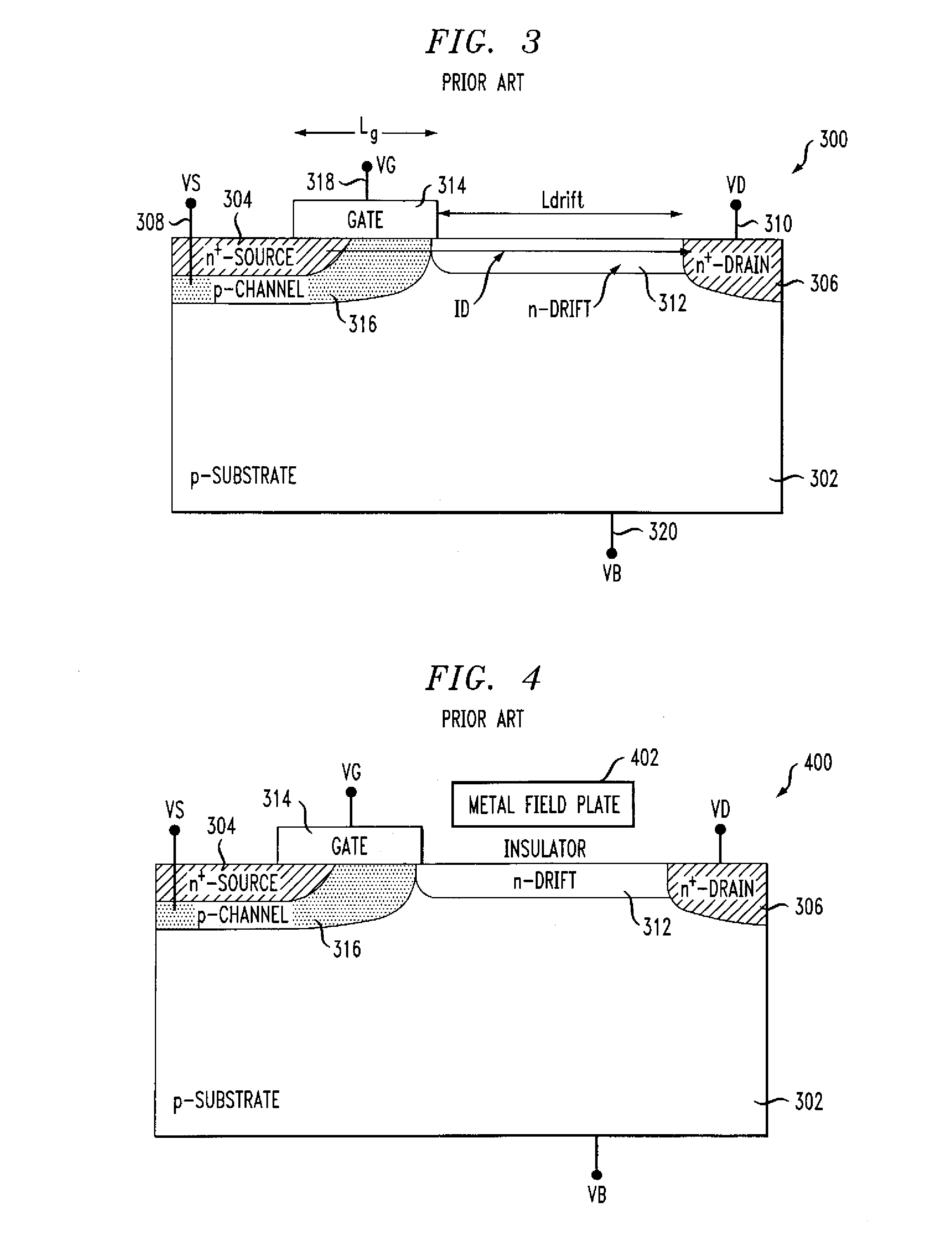

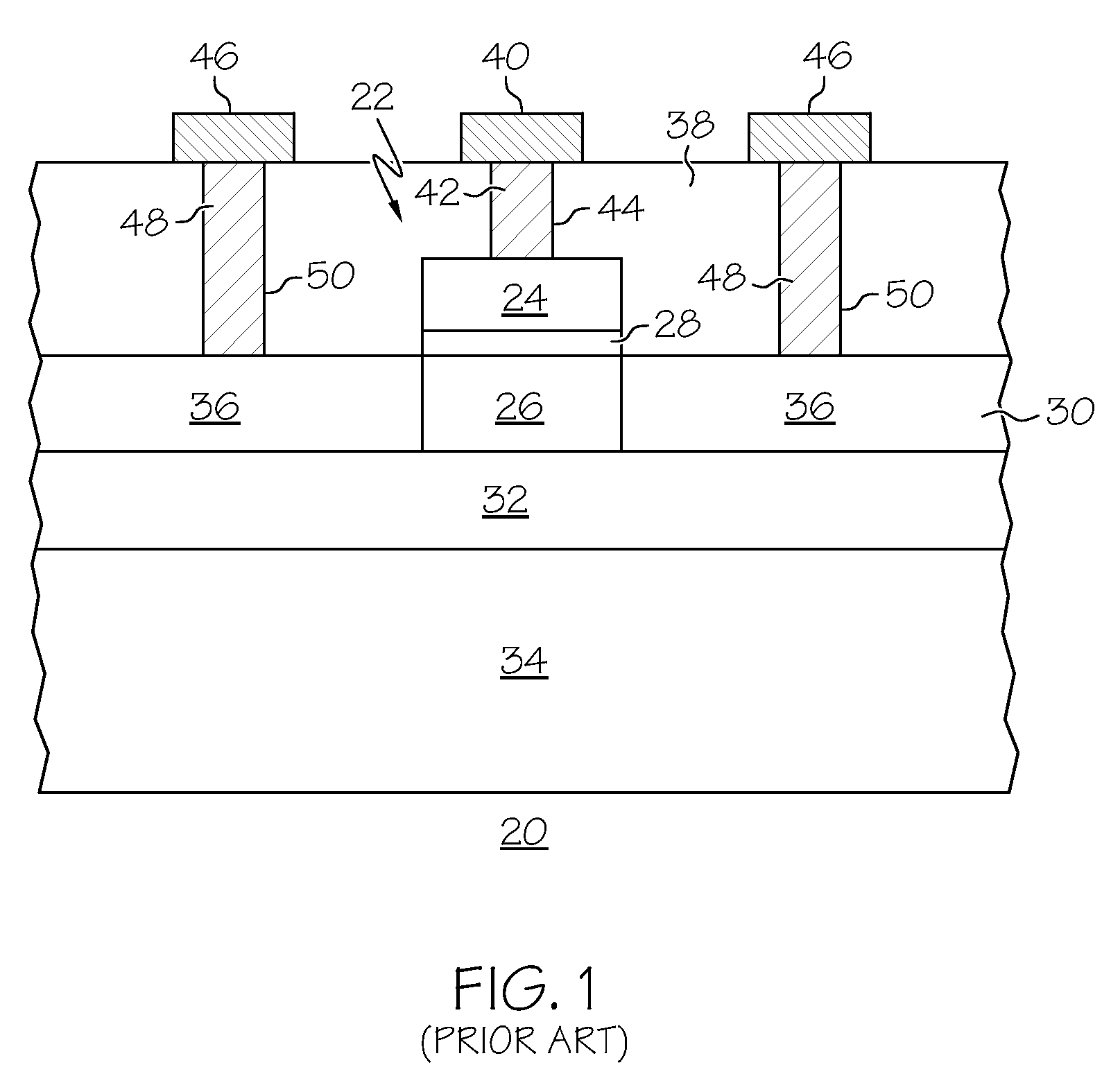

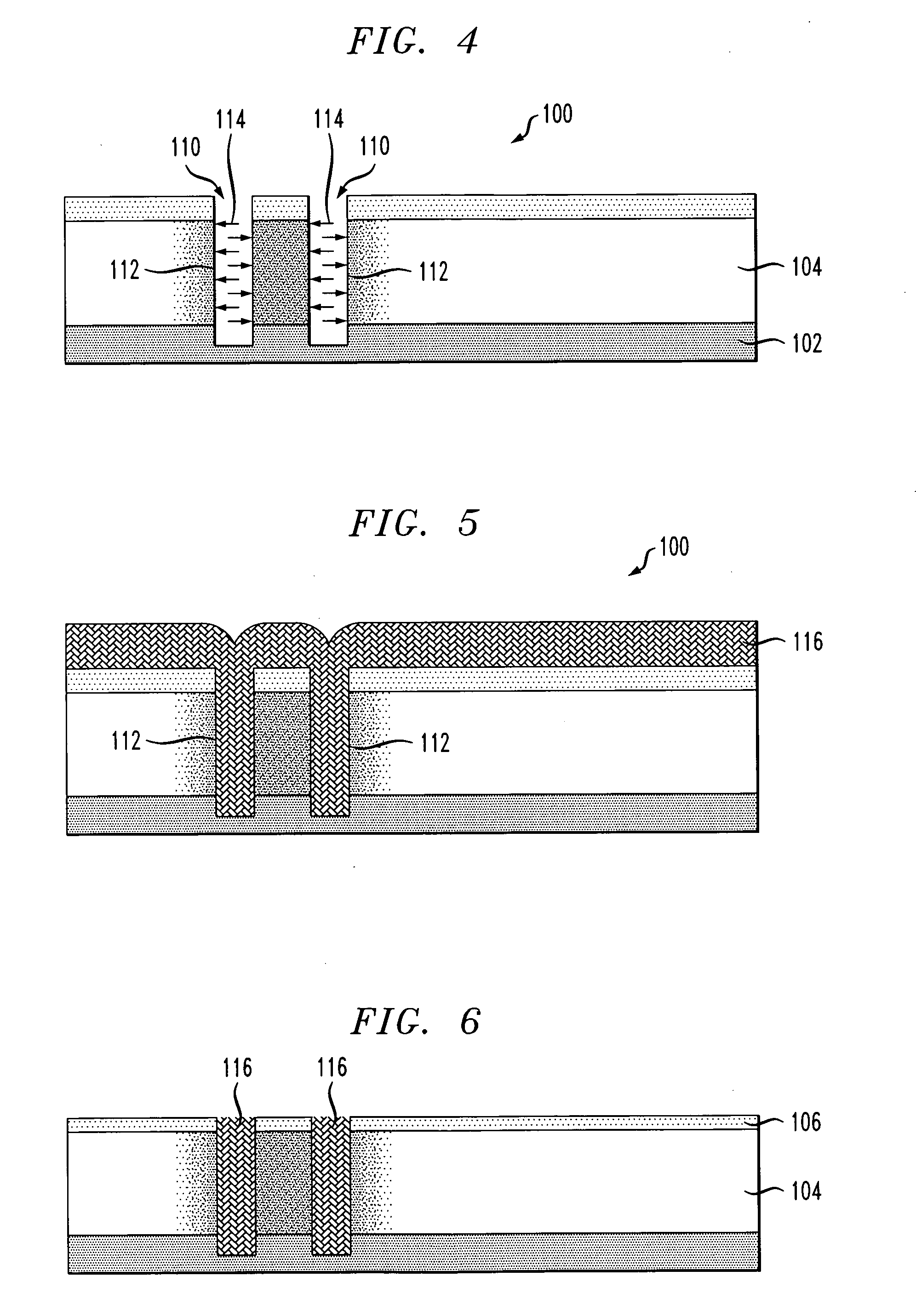

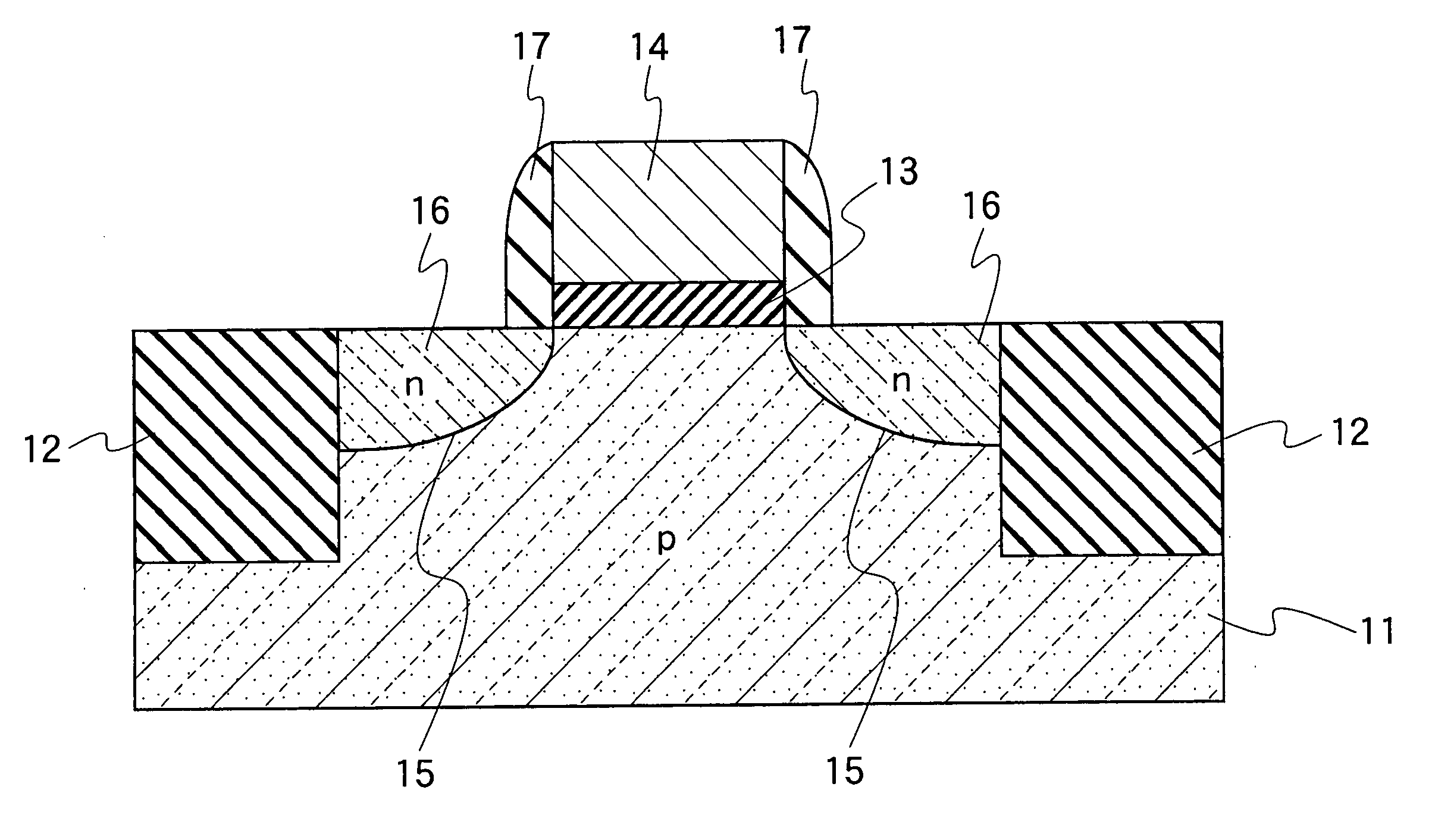

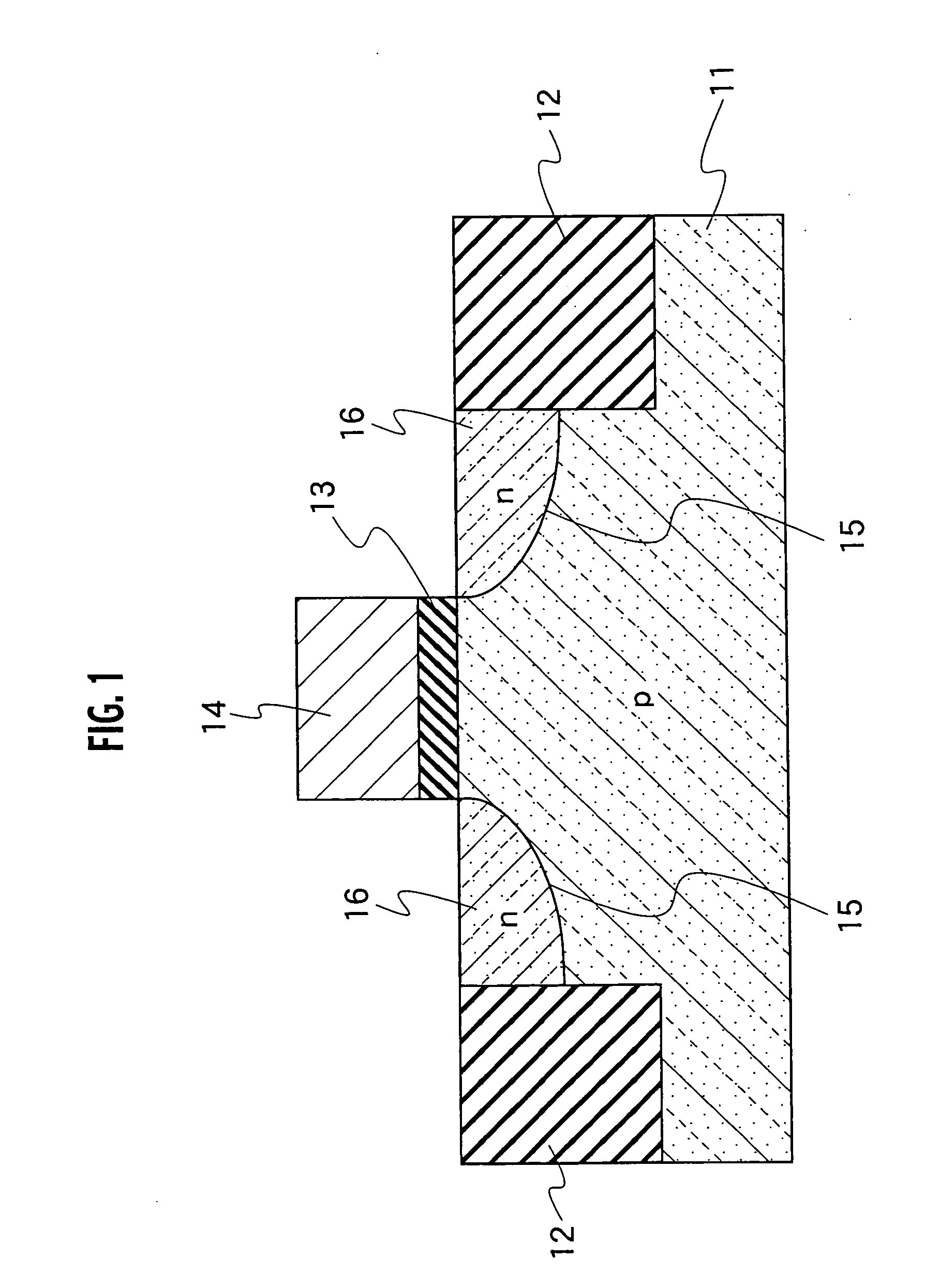

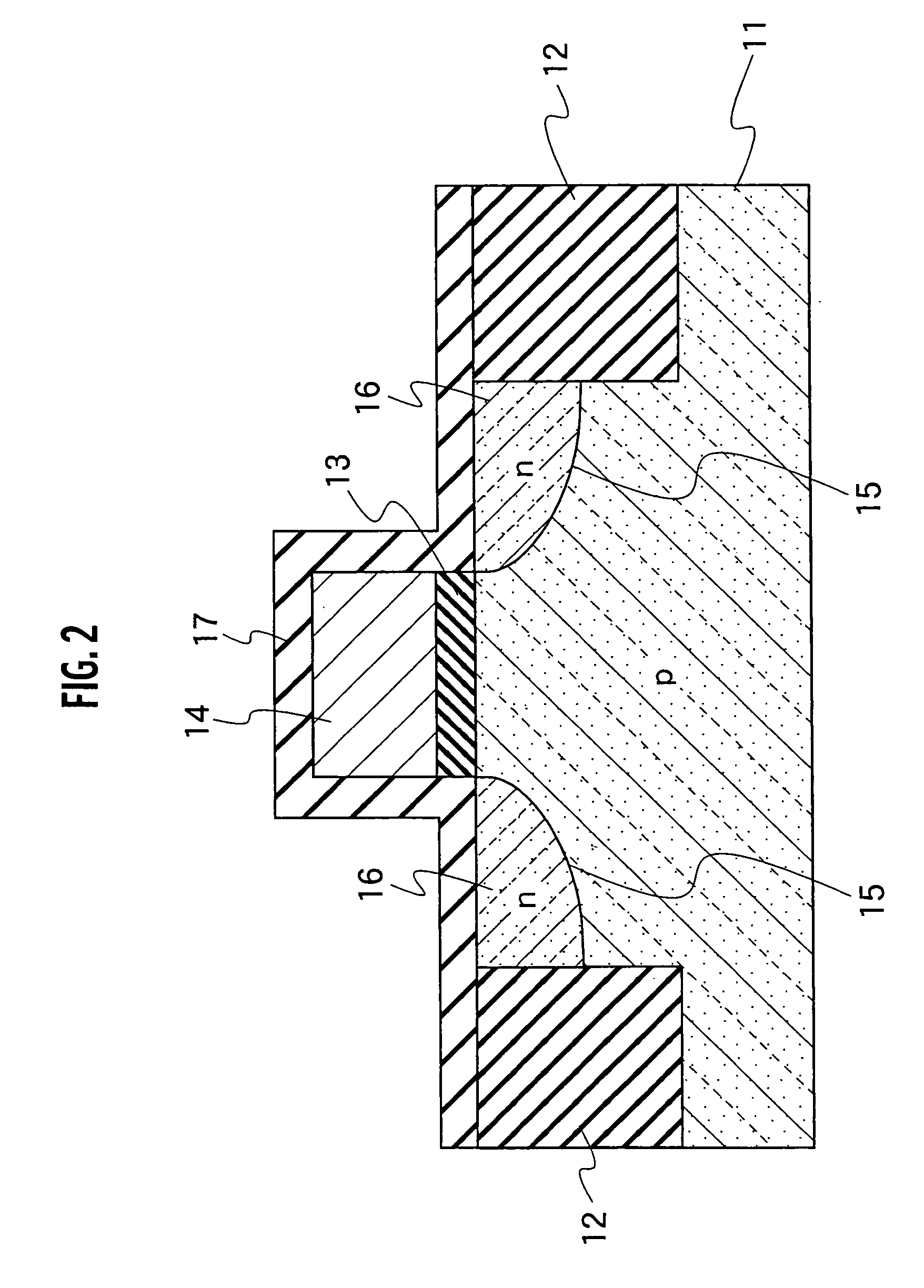

Semiconductor device having improved power density

ActiveUS20060113625A1Improve power densityIncrease the on-resistanceSemiconductor/solid-state device detailsSolid-state devicesClose relativesImpurity doping

An MOS device is formed including a semiconductor layer of a first conductivity type, and source and drain regions of a second conductivity type formed in the semiconductor layer proximate an upper surface of the semiconductor layer. The source and drain regions are spaced apart relative to one another. A drift region of the second conductivity type is formed in the semiconductor layer proximate the upper surface of the semiconductor layer and at least partially between the source and drain regions, the drift region having an impurity doping concentration greater than about 2.0e12 atoms / cm2. An insulating layer is formed on at least a portion of the upper surface of the semiconductor layer. The device further includes a gate formed on the insulating layer at least partially between the source and drain regions, and a buried layer of the first conductivity type formed in the semiconductor layer in close relative proximity to and beneath at least a portion of the drift region. A substantially vertical distance between the buried layer and the drift region, and / or one or more physical dimensions of the buried layer are configured so as to optimize a power density of the device relative to at least one of an on-resistance and a maximum drain current of the device.

Owner:BELL SEMICON LLC

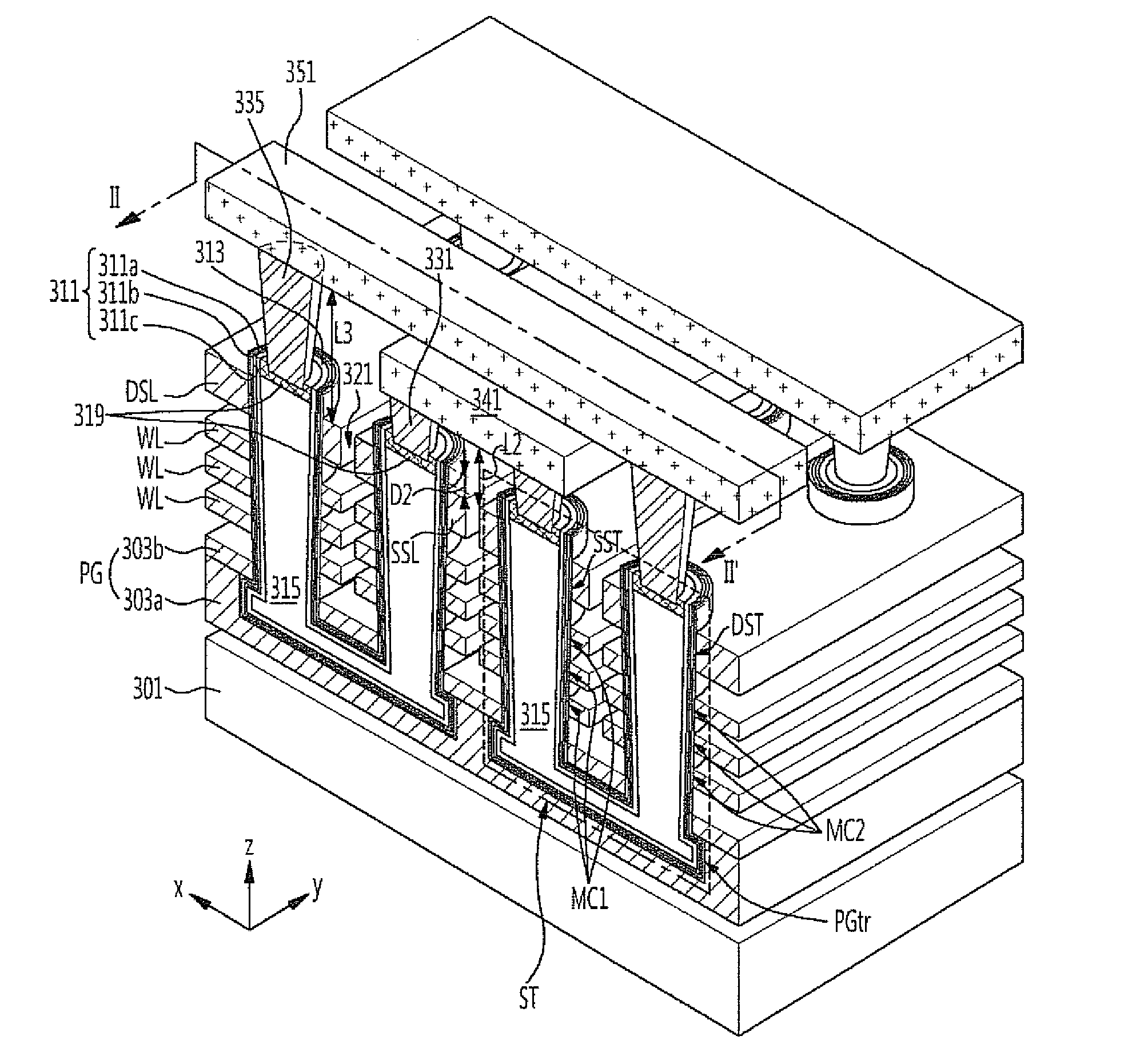

Semiconductor device and method of manufacturing the same

ActiveUS20130161731A1Improve reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceEngineering

A three-dimensional (3D) semiconductor device includes first interlayer dielectric layers and word lines that are alternately stacked on a substrate; select lines formed on the first interlayer dielectric layers and the word lines; etch stop patterns formed on the select lines to contact the select lines; channel holes formed to pass through the select lines, the first interlayer dielectric layers, and the word lines; channel layers formed on surfaces of the channel holes; insulating layers formed in the channel holes, the insulating layers having an upper surface that is lower than upper surfaces of the etch stop patterns; impurity-doped layers formed in channel holes on upper surface of the insulating layers; and a second interlayer dielectric layer formed over the etch stop patterns and the impurity-doped layers.

Owner:SK HYNIX INC

Semiconductor device having improved power density

ActiveUS7262476B2Improve power densityIncrease the on-resistanceSemiconductor/solid-state device detailsSolid-state devicesClose relativesImpurity doping

An MOS device is formed including a semiconductor layer of a first conductivity type, and source and drain regions of a second conductivity type formed in the semiconductor layer proximate an upper surface of the semiconductor layer. The source and drain regions are spaced apart relative to one another. A drift region of the second conductivity type is formed in the semiconductor layer proximate the upper surface of the semiconductor layer and at least partially between the source and drain regions, the drift region having an impurity doping concentration greater than about 2.0e12 atoms / cm2. An insulating layer is formed on at least a portion of the upper surface of the semiconductor layer. The device further includes a gate formed on the insulating layer at least partially between the source and drain regions, and a buried layer of the first conductivity type formed in the semiconductor layer in close relative proximity to and beneath at least a portion of the drift region. A substantially vertical distance between the buried layer and the drift region, and / or one or more physical dimensions of the buried layer are configured so as to optimize a power density of the device relative to at least one of an on-resistance and a maximum drain current of the device.

Owner:BELL SEMICON LLC

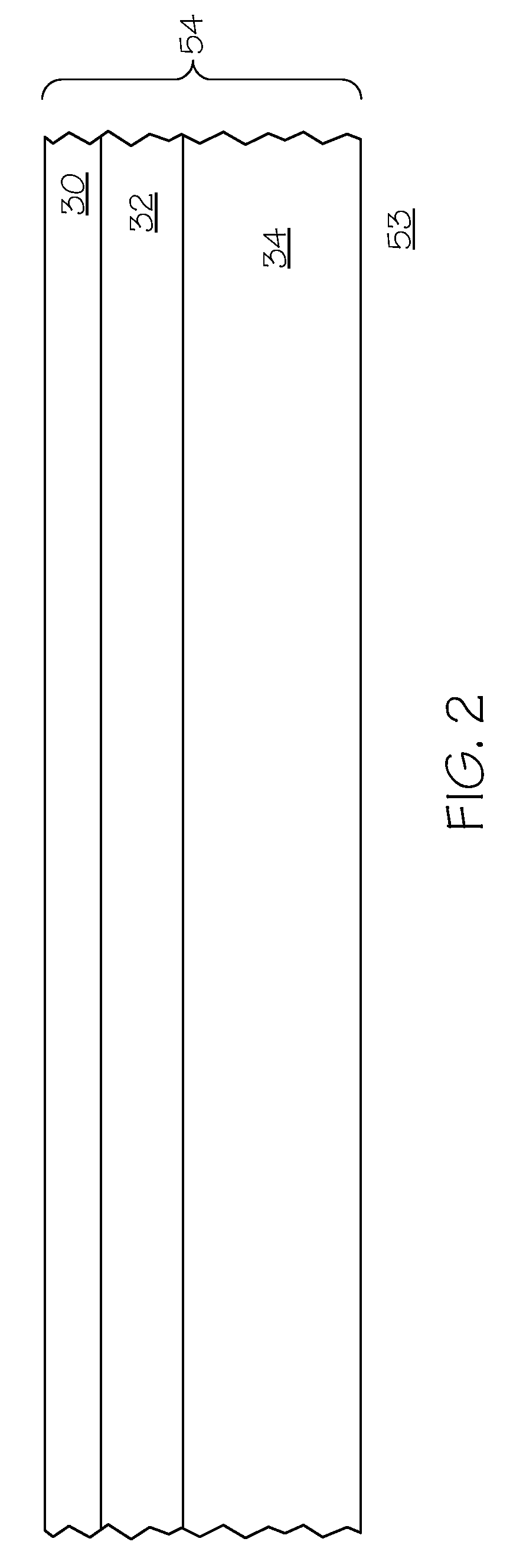

Soi device and method for its fabrication

A silicon on insulator (SOI) device and methods for fabricating such a device are provided. The device includes an MOS capacitor coupled between voltage busses and formed in a monocrystalline semiconductor layer overlying an insulator layer and a semiconductor substrate. The device includes at least one electrical discharge path for discharging potentially harmful charge build up on the MOS capacitor. The MOS capacitor has a conductive electrode material forming a first plate of the MOS capacitor and an impurity doped region in the monocrystalline silicon layer beneath the conductive electrode material forming a second plate. A first voltage bus is coupled to the first plate of the capacitor and to an electrical discharge path through a diode formed in the semiconductor substrate and a second voltage bus is coupled to the second plate of the capacitor.

Owner:GLOBALFOUNDRIES US INC

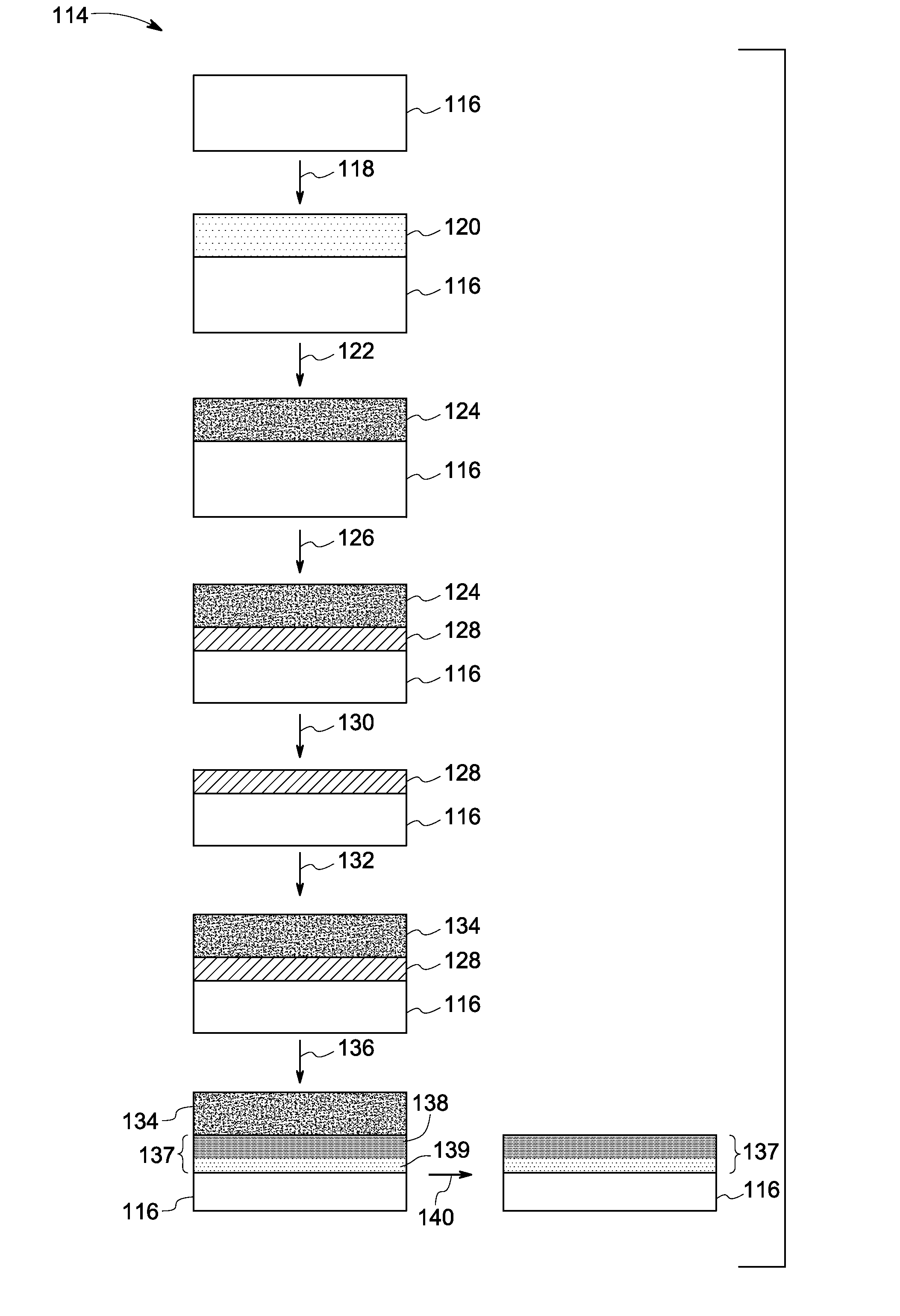

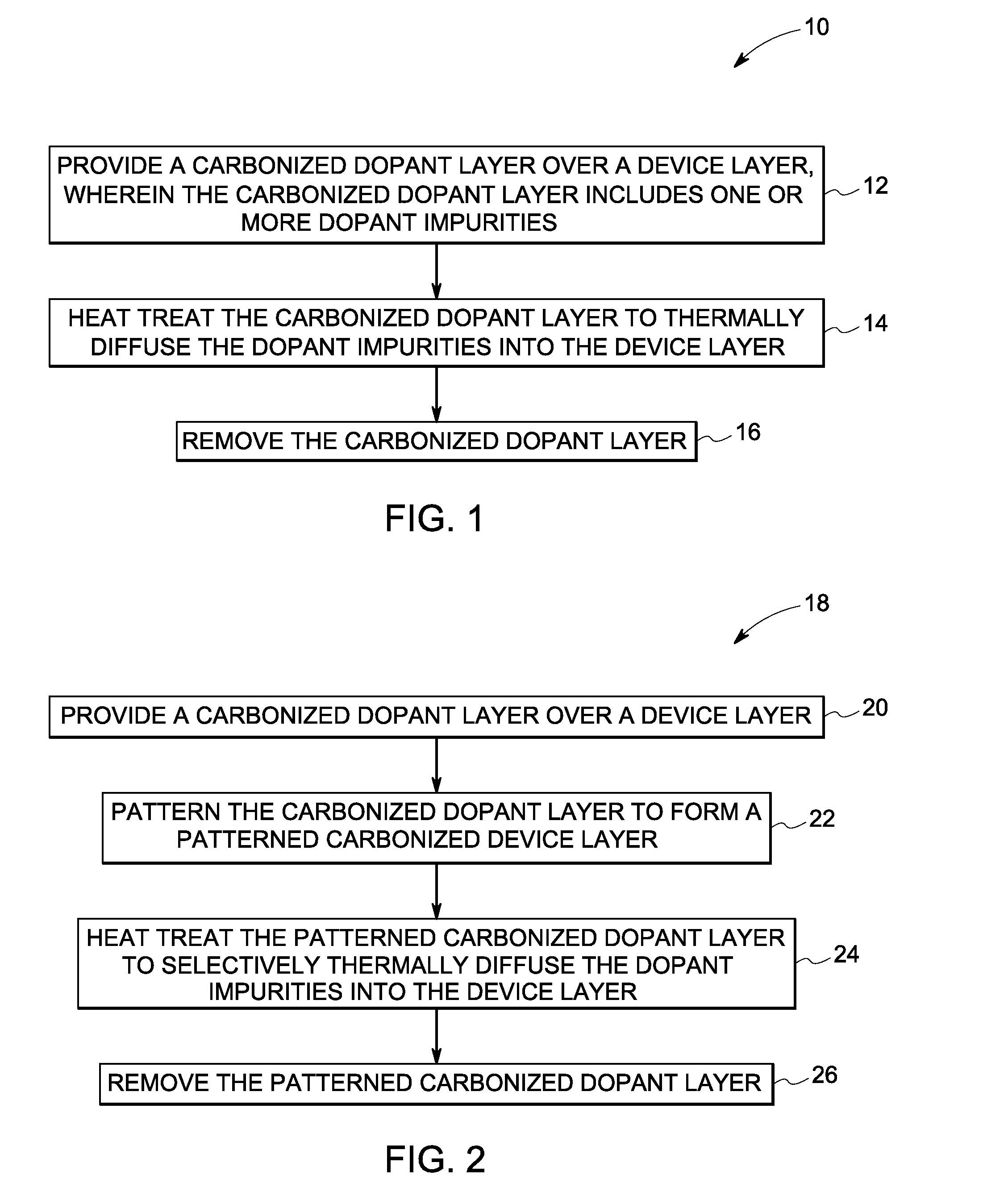

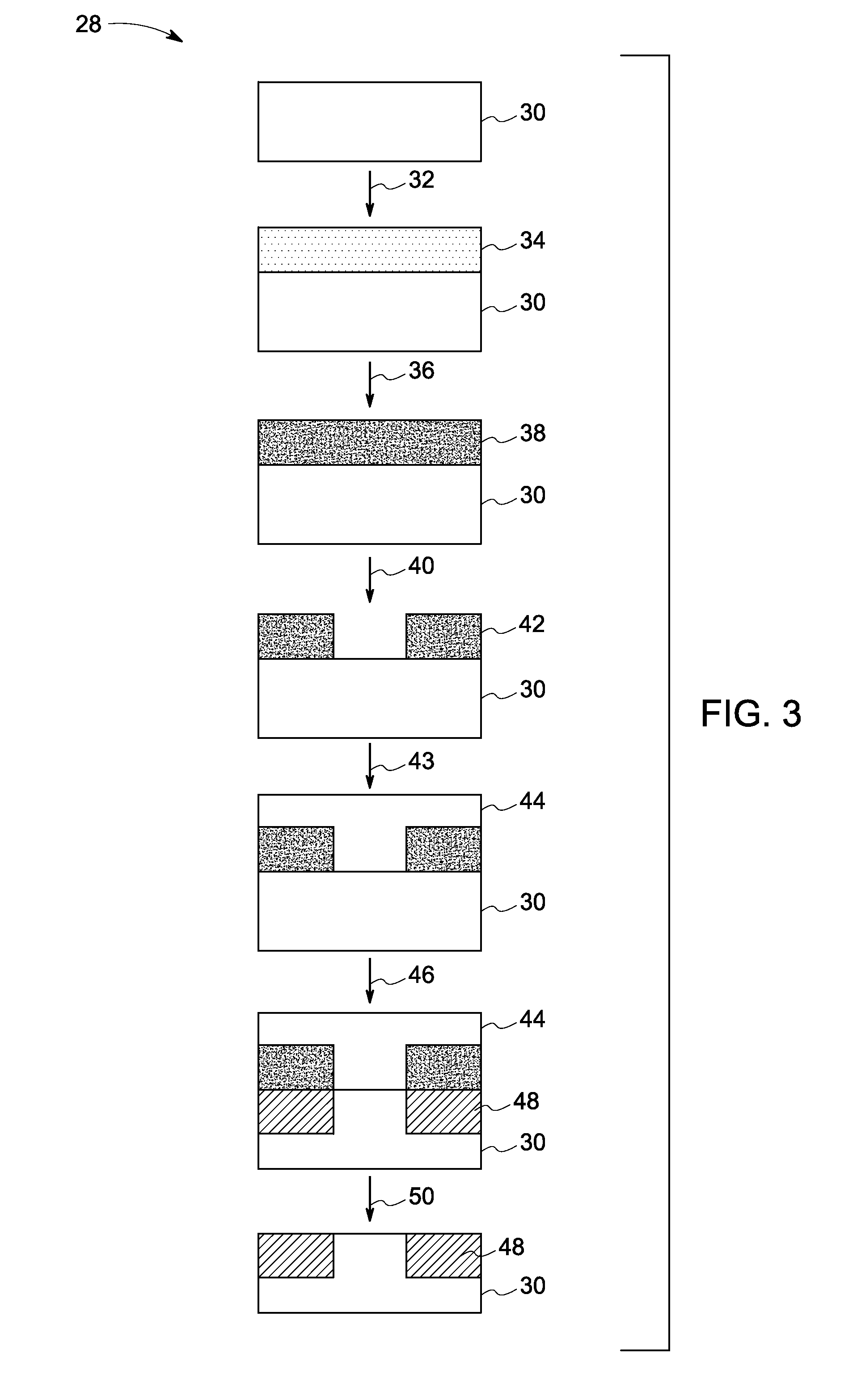

Method for doping impurities

A method for doping impurities into a device layer is provided. The method includes providing a carbonized dopant layer over a device layer, wherein the carbonized dopant layer comprises one or more dopant impurities, and heat treating the carbonized dopant layer to thermally diffuse the dopant impurities into the device layer.

Owner:GENERAL ELECTRIC CO

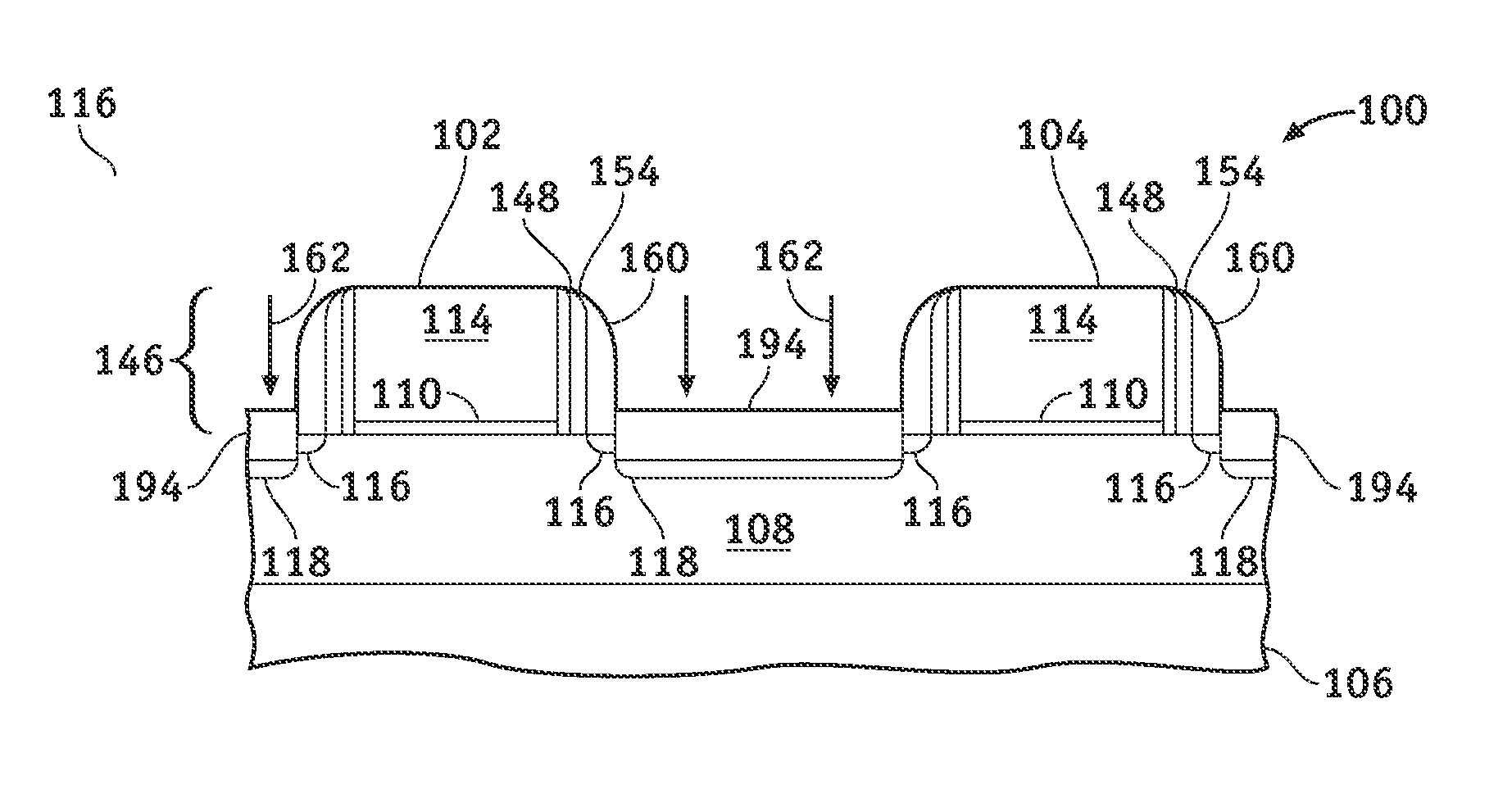

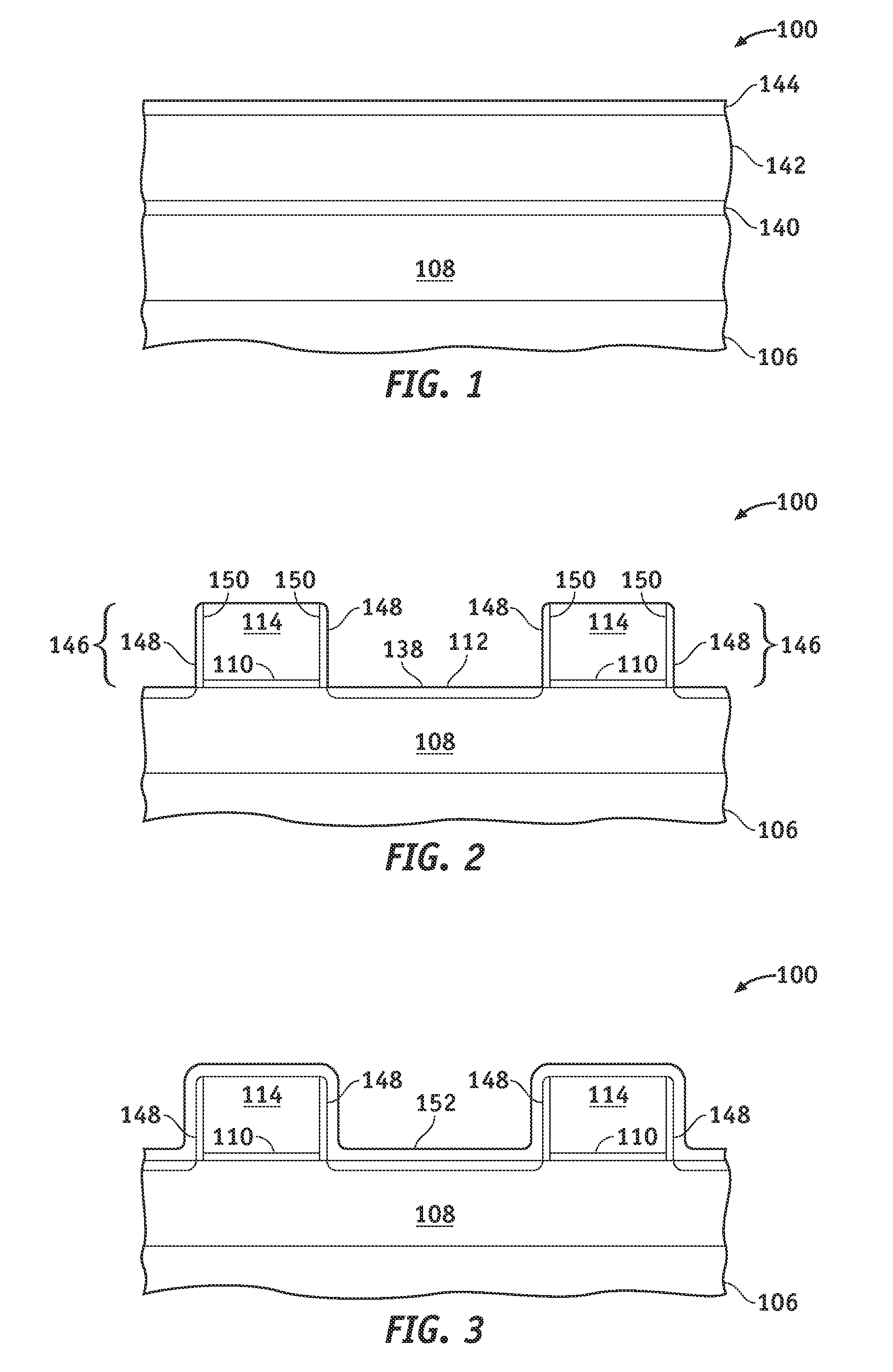

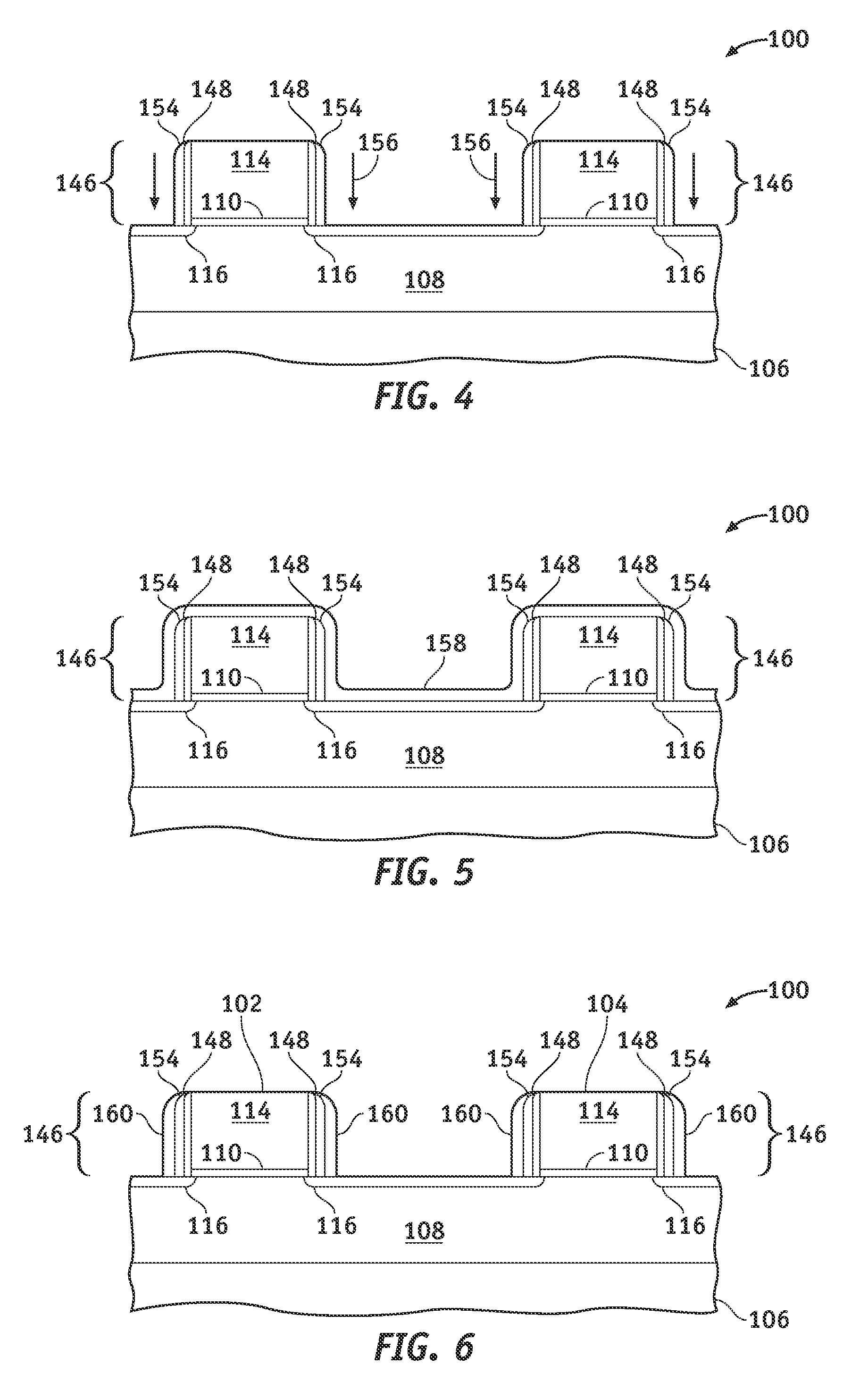

Mos structures that exhibit lower contact resistance and methods for fabricating the same

ActiveUS20090050984A1Semiconductor/solid-state device detailsSolid-state devicesMetal silicideGate stack

MOS structures that exhibit lower contact resistance and methods for fabricating such MOS structures are provided. In one method, a semiconductor substrate is provided and a gate stack is fabricated on the semiconductor substrate. An impurity-doped region within the semiconductor substrate aligned with the gate stack is formed. Adjacent contact fins extending from the impurity-doped region are fabricated and a metal silicide layer is formed on the contact fins. A contact to at least a portion of the metal silicide layer on at least one of the contact fins is fabricated.

Owner:GLOBALFOUNDRIES US INC

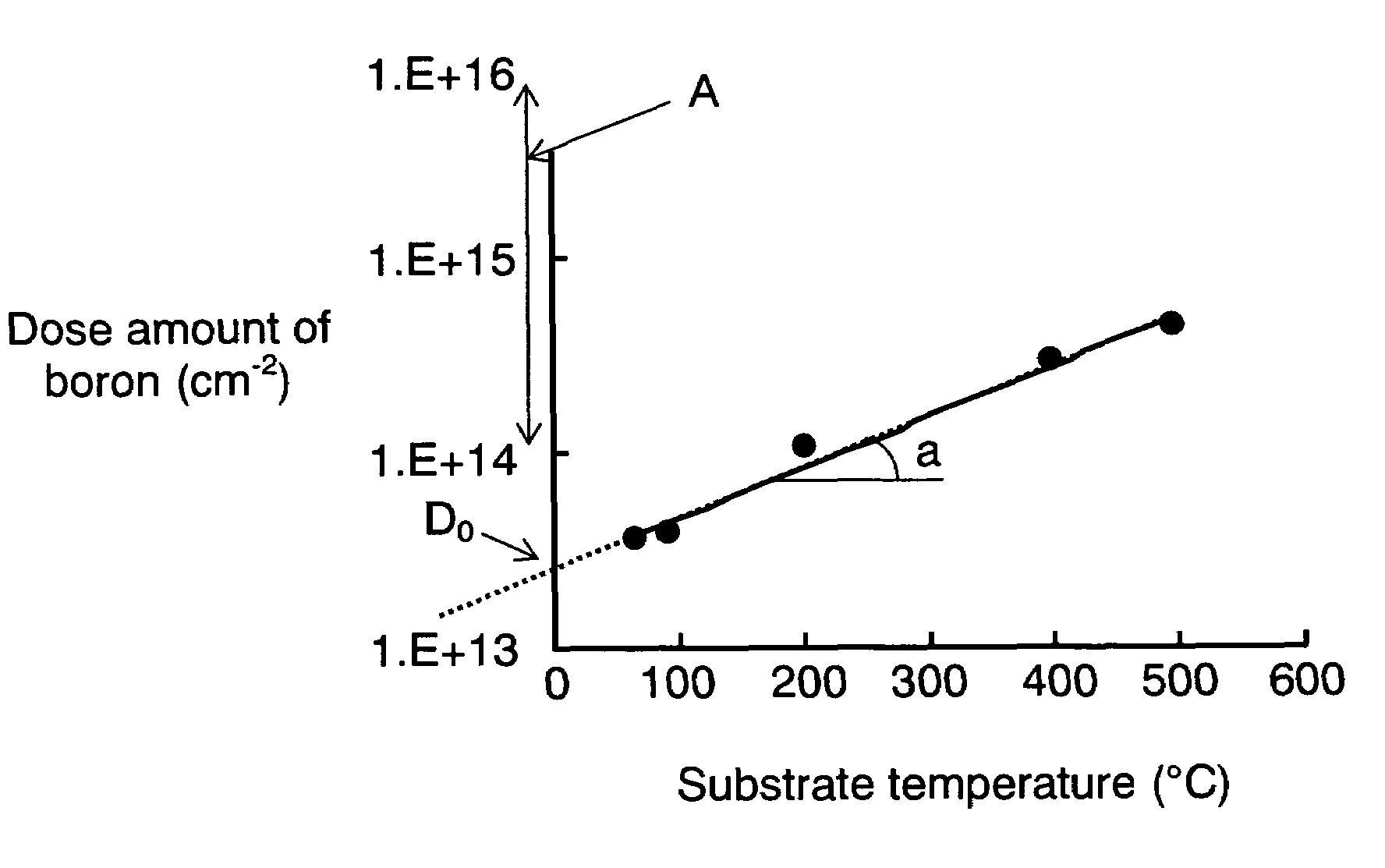

Method of controlling impurity doping and impurity doping apparatus

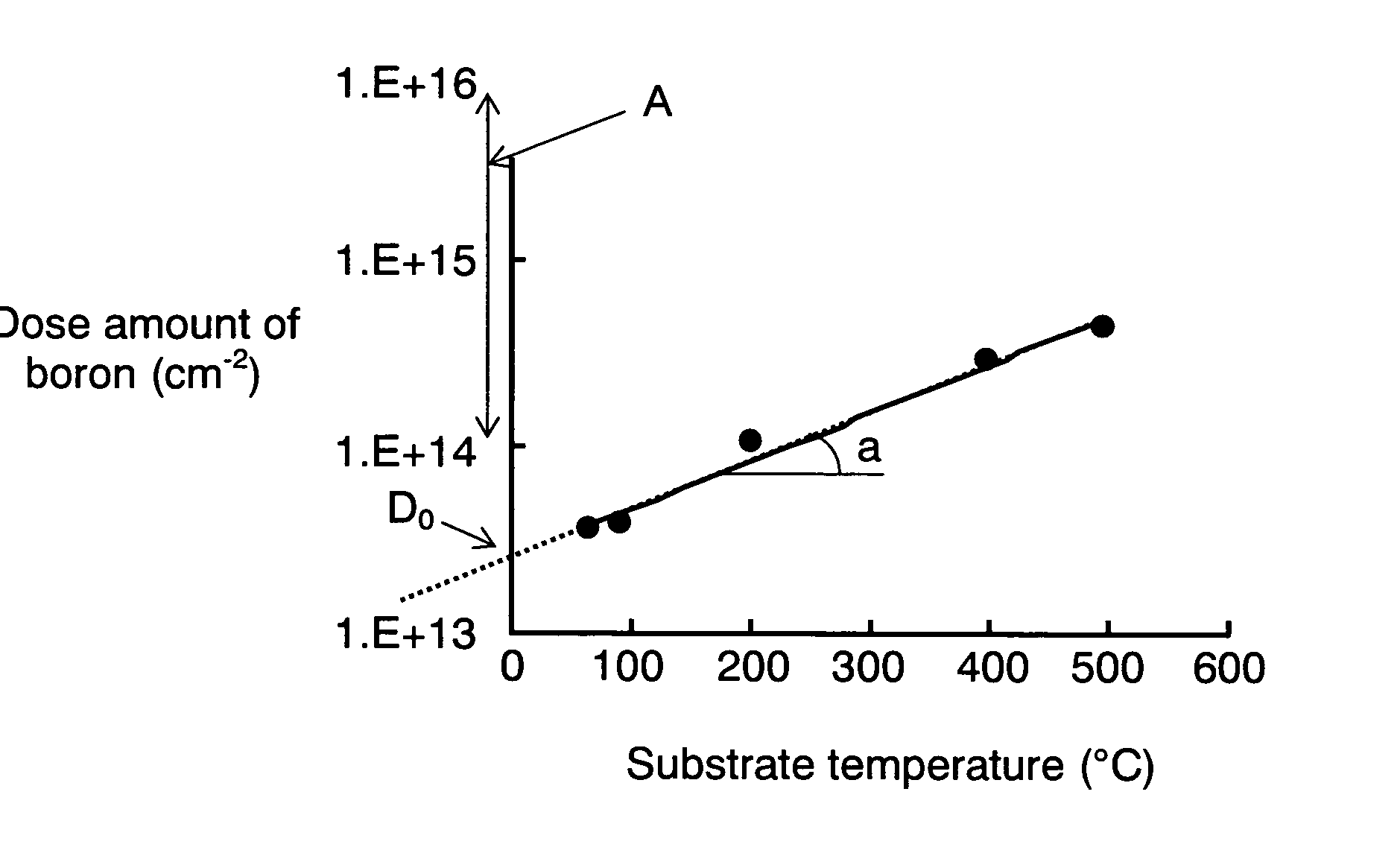

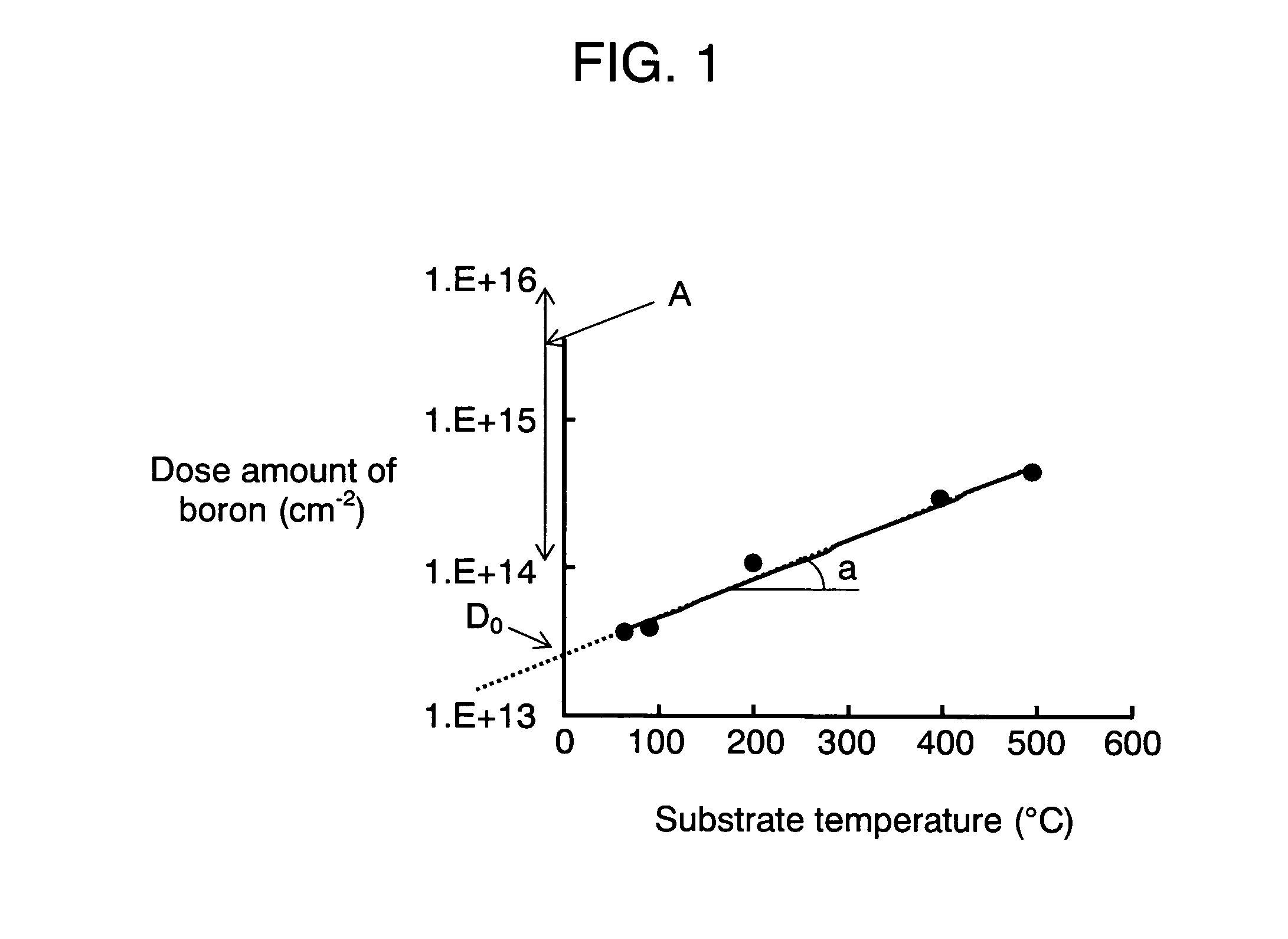

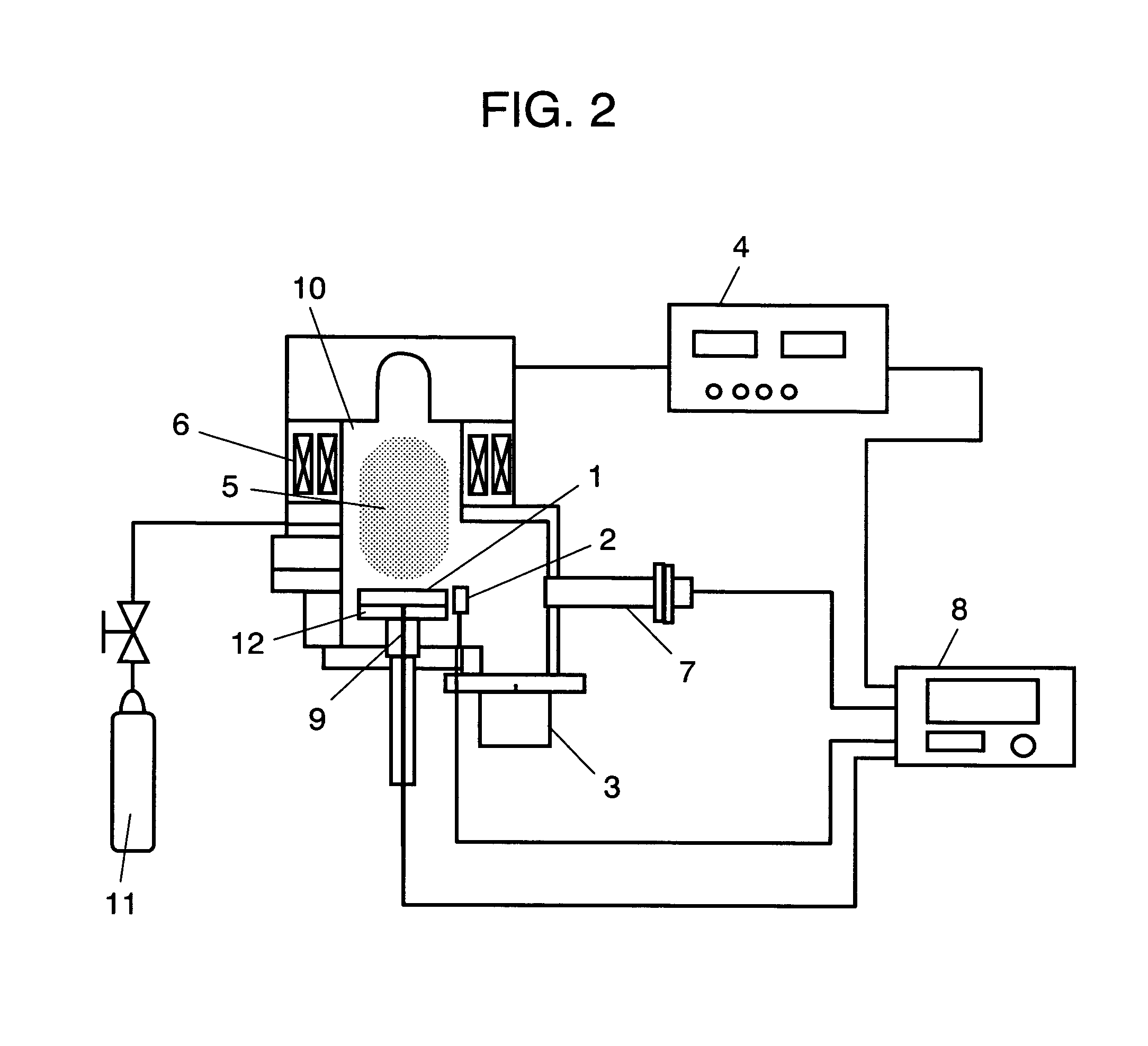

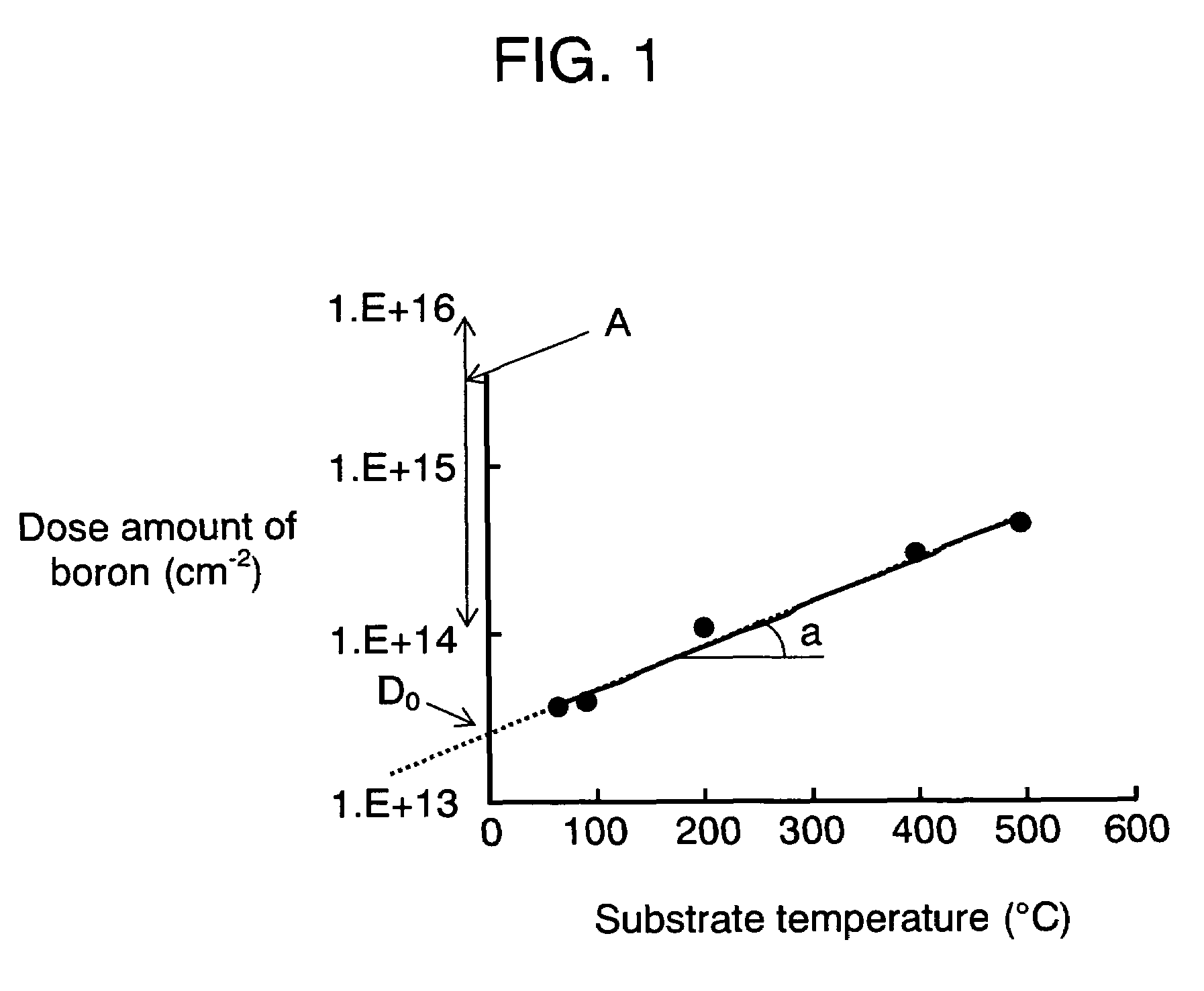

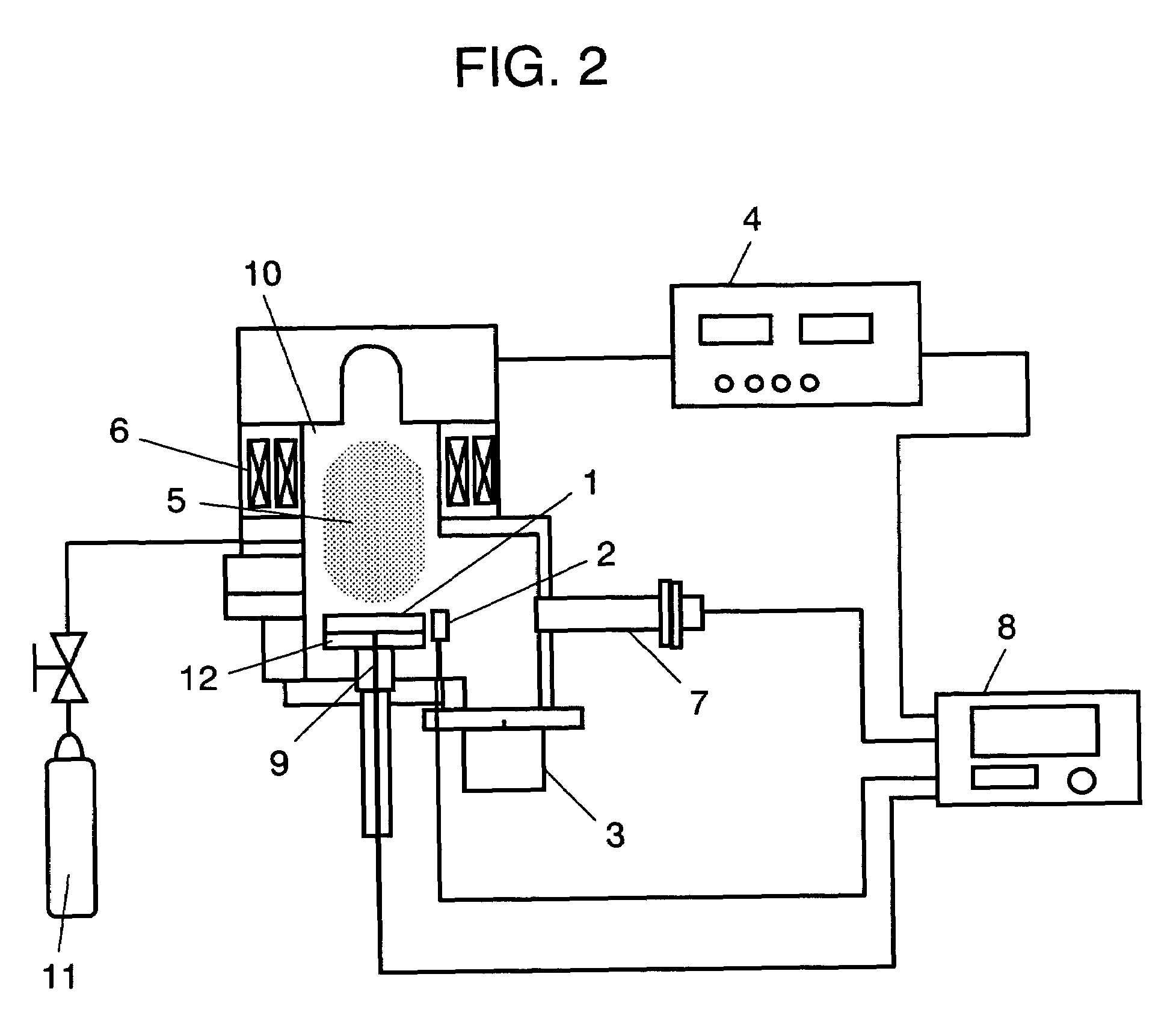

InactiveUS20070059848A1Minimized variation in qualityImprove accuracySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingDopantImpurity doping

Disclosed here is a method of controlling a dose amount of dopant to be doped into object (1) to be processed in plasma doping. According to the method, the doping control is formed of the following processes: determining the temperature of object (1), the amount of ions having dopant in plasma that collide with object (1), and types of gases in plasma during doping; calculating a dose amount by neutral gas according to the temperature of object (1), and a dose amount by ions from the determined amount of ions containing dopant that collide with object (1); and carrying out doping so that the sum of the dose amount by neutral gas and the dose amount by ions equal to a predetermined dose amount.

Owner:PANASONIC CORP

Semiconductor device with floating trap type nonvolatile memory cell and method for manufacturing the same

ActiveUS20050023604A1Reduce processing timeSlow changeTransistorSolid-state devicesDevice materialImpurity doping

The present invention discloses a semiconductor device having a floating trap type nonvolatile memory cell and a method for manufacturing the same. The method includes providing a semiconductor substrate having a nonvolatile memory region, a first region, and a second region. A triple layer composed of a tunnel oxide layer, a charge storing layer and a first deposited oxide layer on the semiconductor substrate is formed sequentially. The triple layer on the semiconductor substrate except the nonvolatile memory region is then removed. A second deposited oxide layer is formed on an entire surface of the semiconductor substrate including the first and second regions from which the triple layer is removed. The second deposited oxide layer on the second region is removed, and a first thermal oxide layer is formed on the entire surface of the semiconductor substrate including the second region from which the second deposited oxide layer is removed. The semiconductor device can be manufactured according to the present invention to have a reduced processing time and a reduced change of impurity doping profile. The thickness of a blocking oxide layer and a high voltage gate oxide layer can be controlled.

Owner:SAMSUNG ELECTRONICS CO LTD

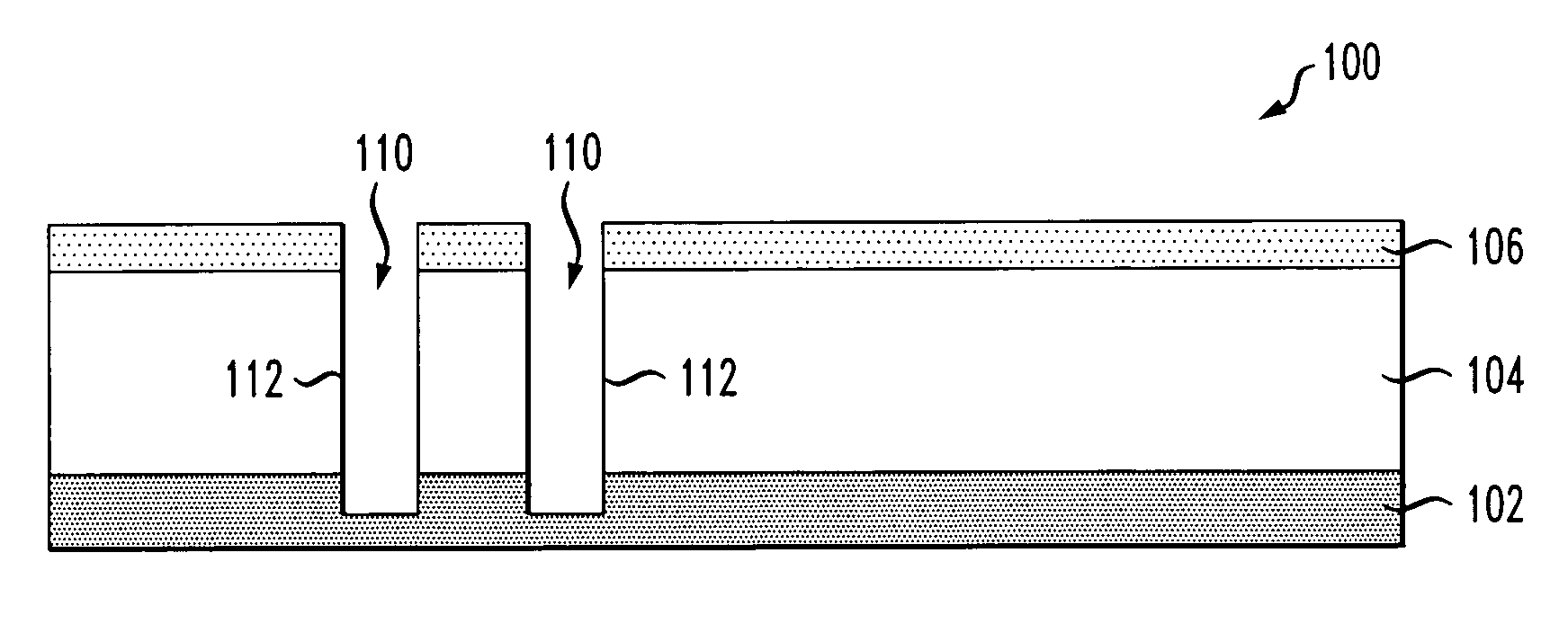

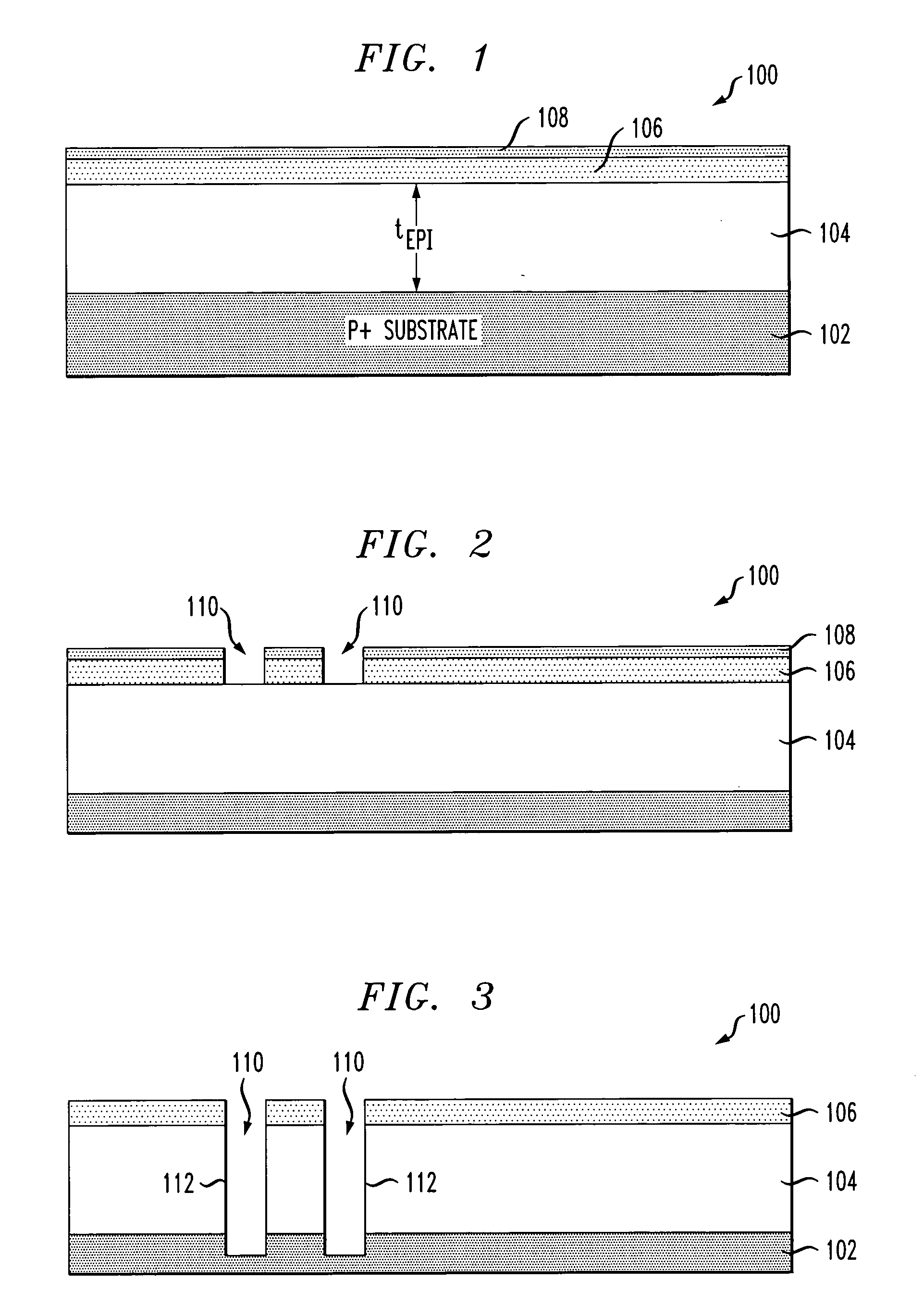

Enhanced substrate contact for a semiconductor device

ActiveUS20050093097A1Low resistance goodSmooth connectionTransistorSolid-state devicesDevice materialSemiconductor structure

A method of forming a semiconductor structure in a semiconductor wafer includes the steps of forming an epitaxial layer on at least a portion of a semiconductor substrate of a first conductivity type and forming at least one trench through the epitaxial layer to at least partially expose the substrate. The method further includes doping at least one or more sidewalls of the at least one trench with an impurity of a known concentration level. The at least one trench is then substantially filled with a filler material. In this manner, a low-resistance electrical path is formed between an upper surface of the epitaxial layer and the substrate.

Owner:BELL SEMICON LLC

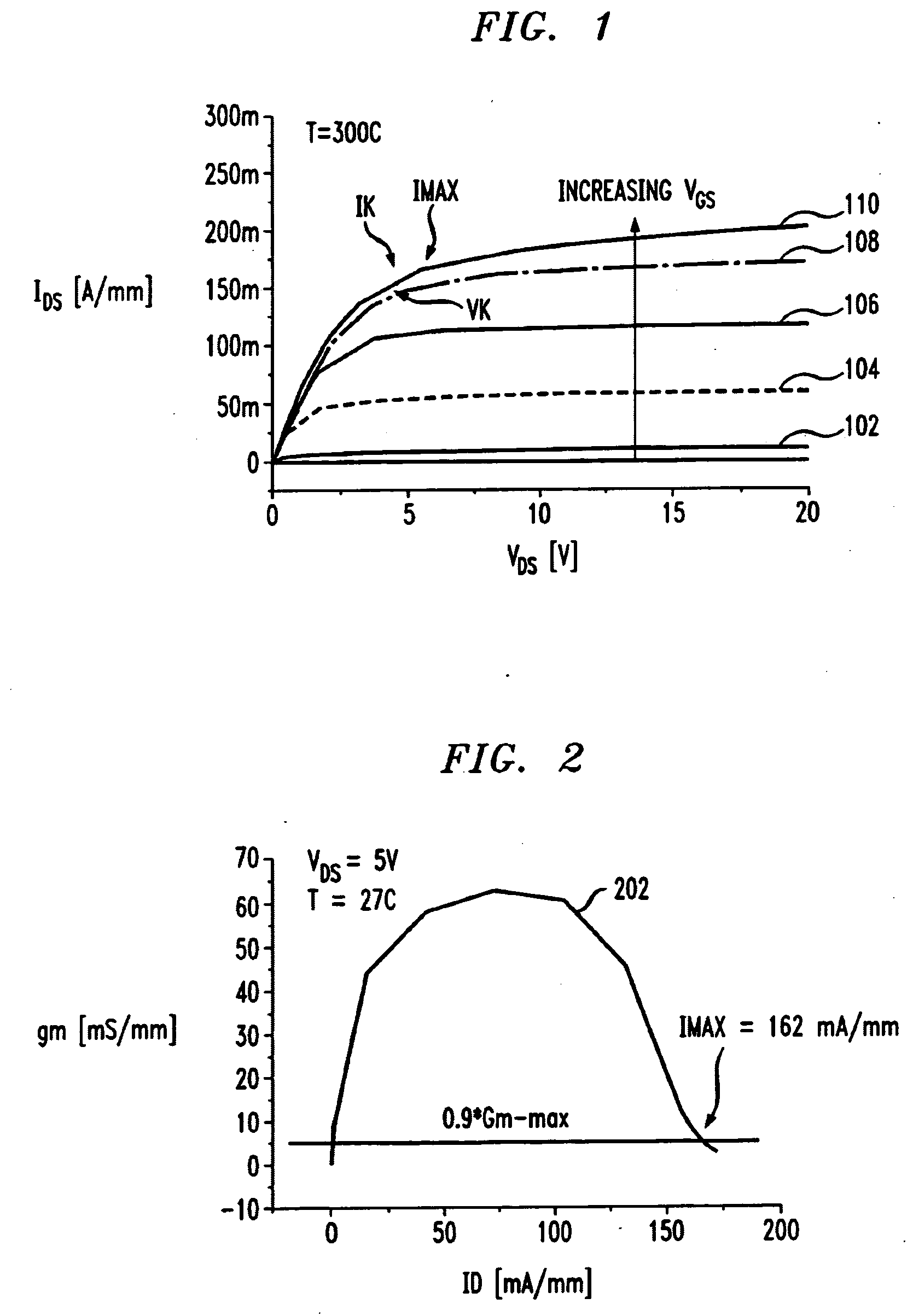

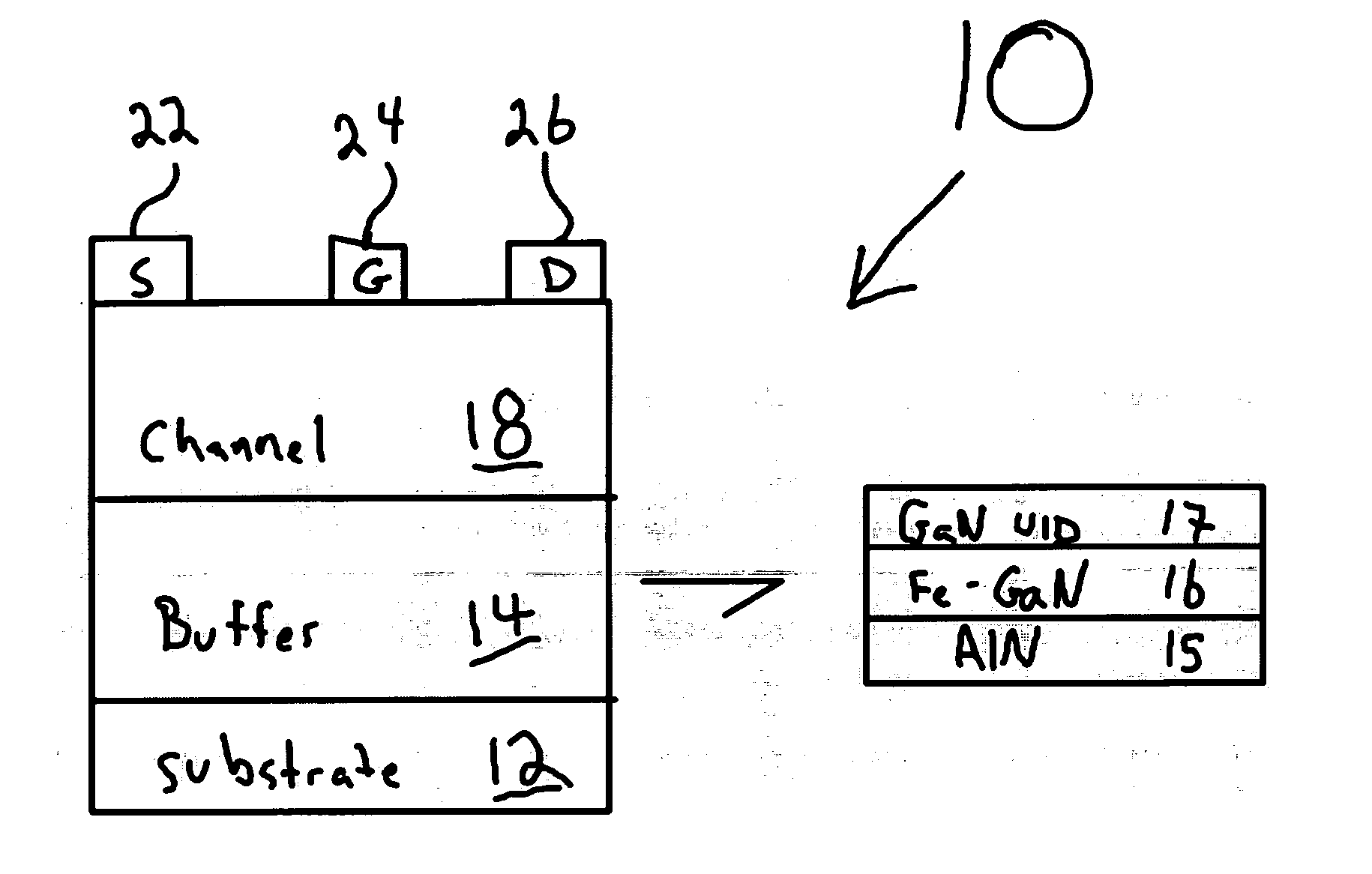

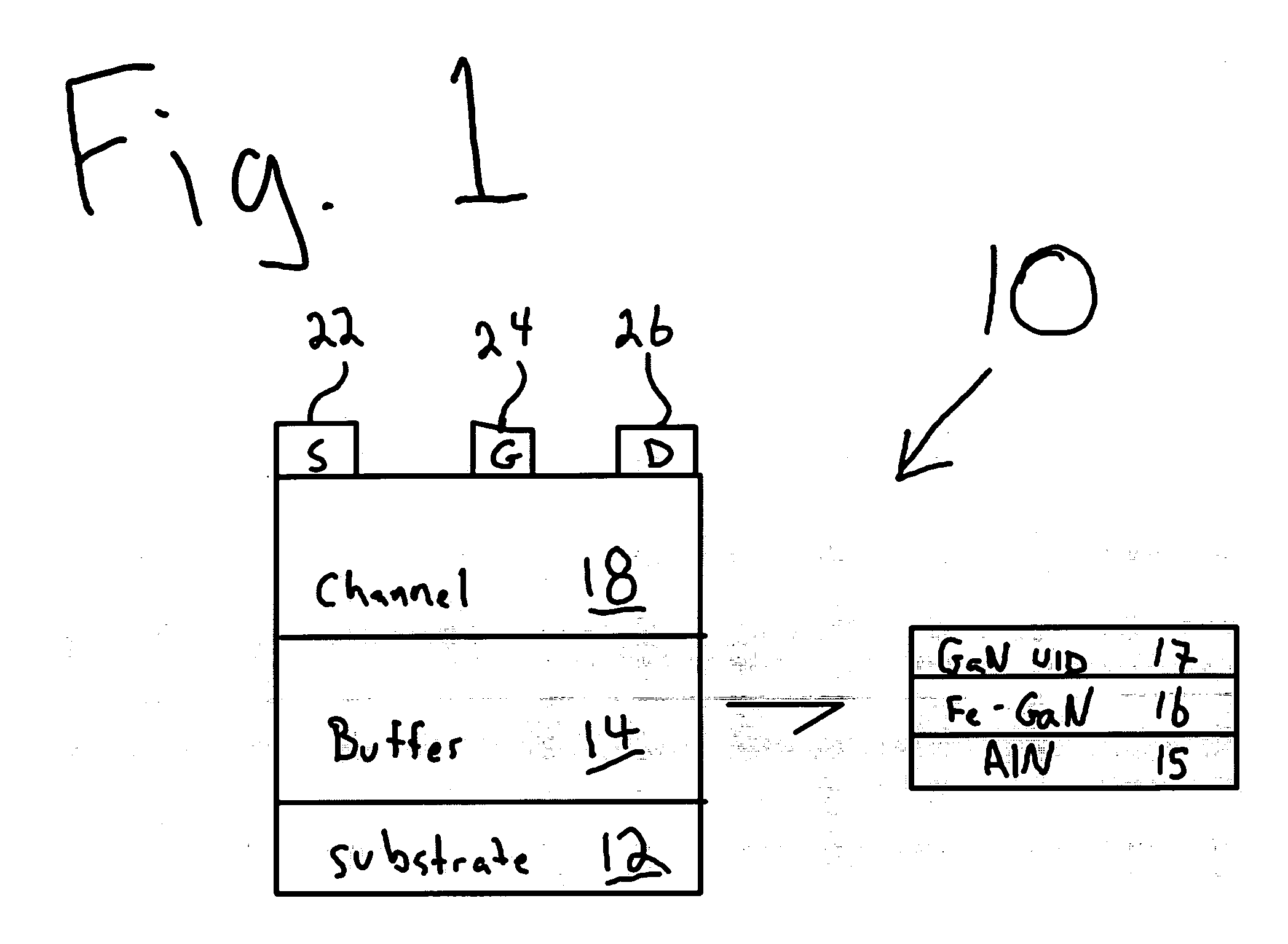

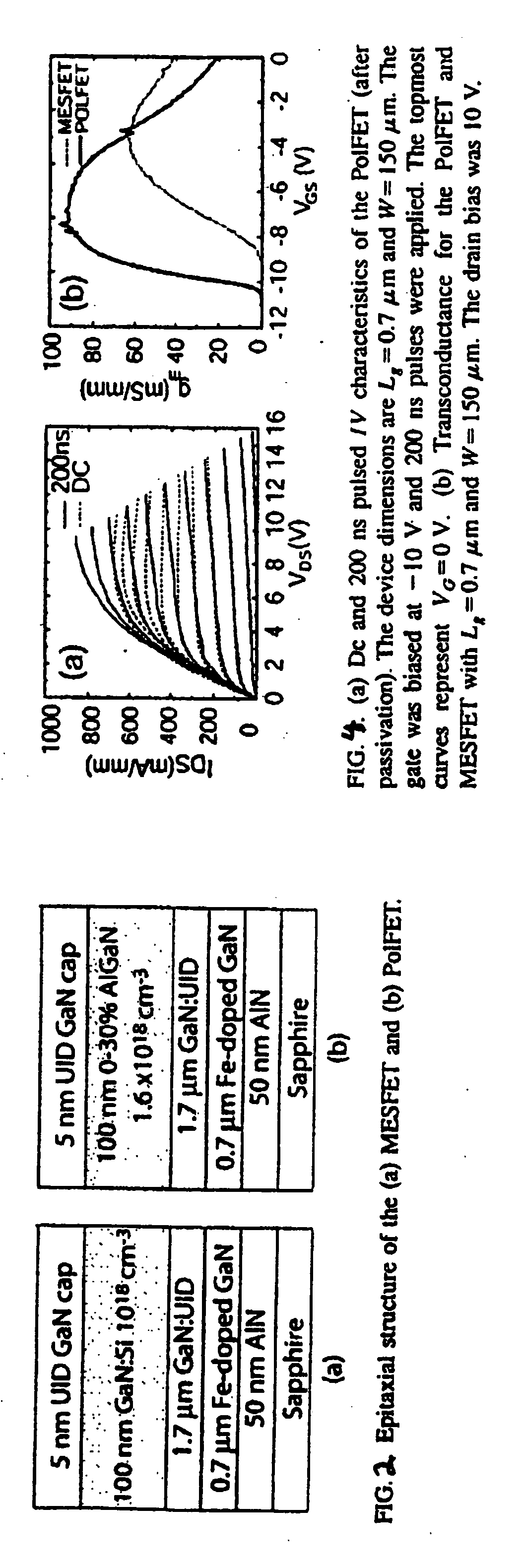

Polarization-doped field effect transistors (POLFETS) and materials and methods for making the same

Novel GaN / AlGaN metal-semiconductor field-effect transistor (MESFET) structures grown without any impurity doping in the channel. A high-mobility polarization-induced bulk channel charge is created by grading the channel region linearly from GaN to Al0.3Ga0.7N over a distance, e.g., 1000 Å. A polarization-doped field effect transistor (PolFET) was fabricated and tested under DC and RF conditions. A current density of 850 mA / mm and transconductance of 93 mS / mm was observed under DC conditions. Small-signal characterization of 0.7 μm gate length devices had a cutoff frequency, ƒτ=19 GHz, and a maximum oscillation of ƒmax=46 GHz. The PolFETs perform better than comparable MESFETs with impurity-doped channels, and are suitable for high microwave power applications. An important advantage of these devices over AlGaN / GaN HEMTs is that the transconductance vs. gate voltage profile can be tailored by compositional grading for better large-signal linearity.

Owner:RGT UNIV OF CALIFORNIA

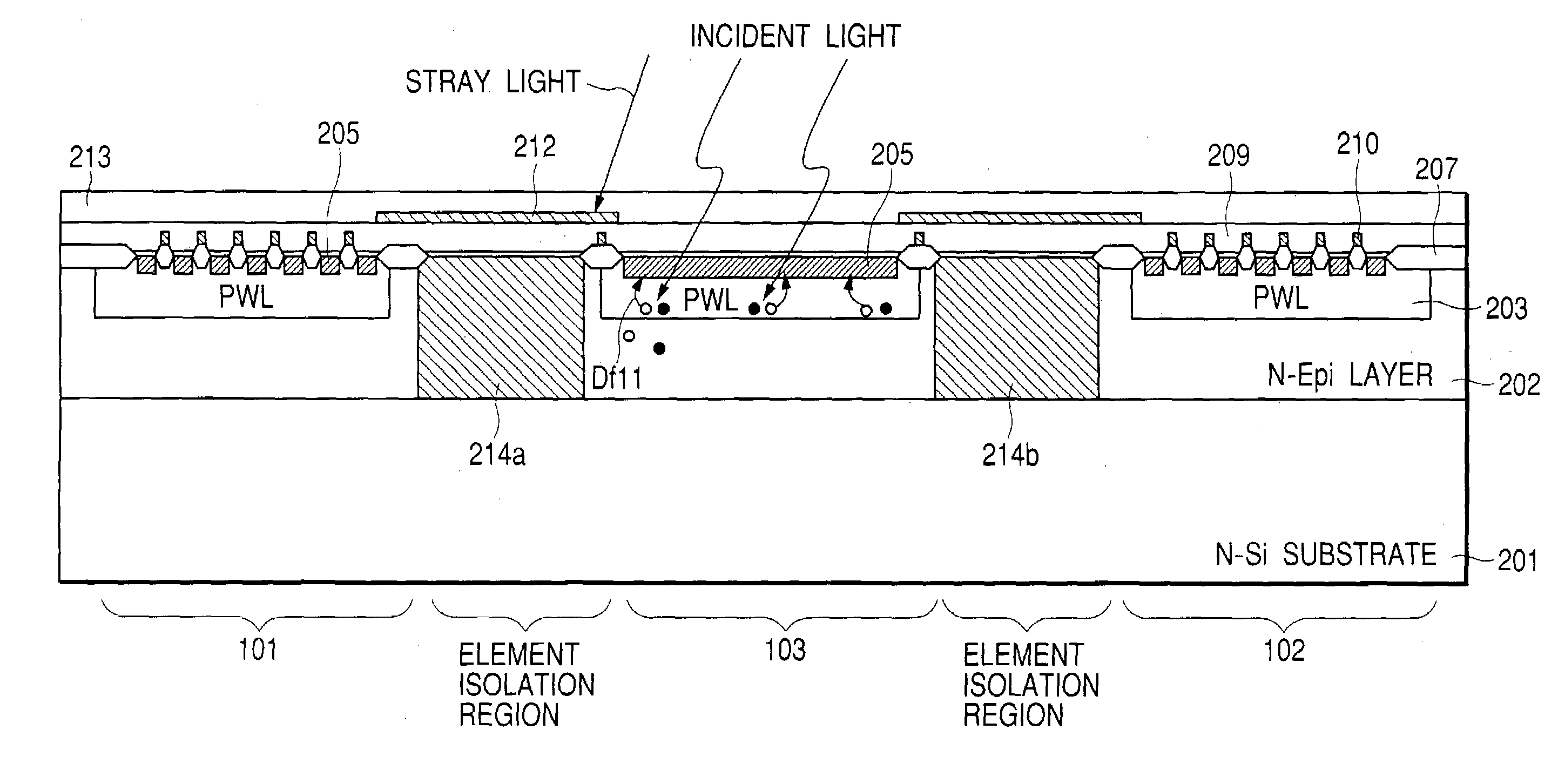

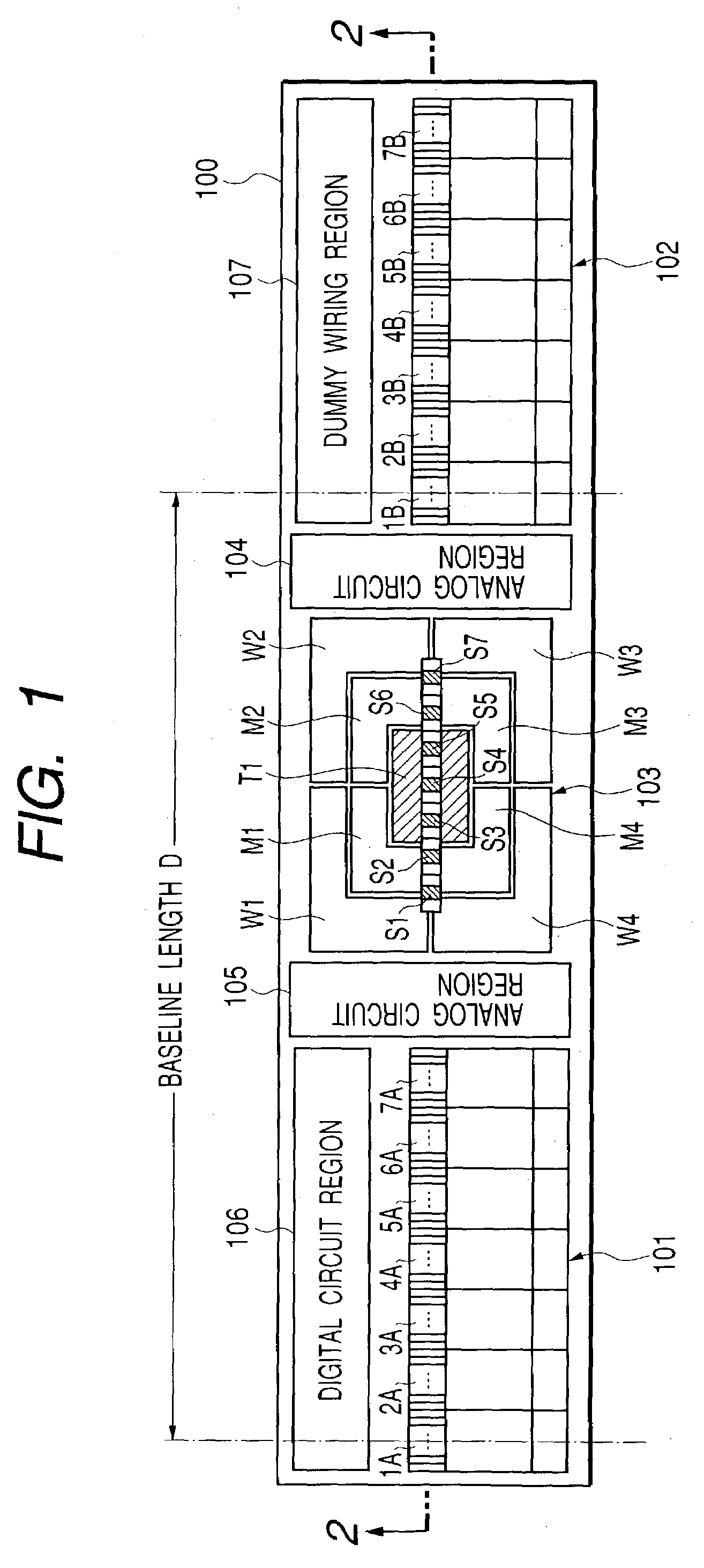

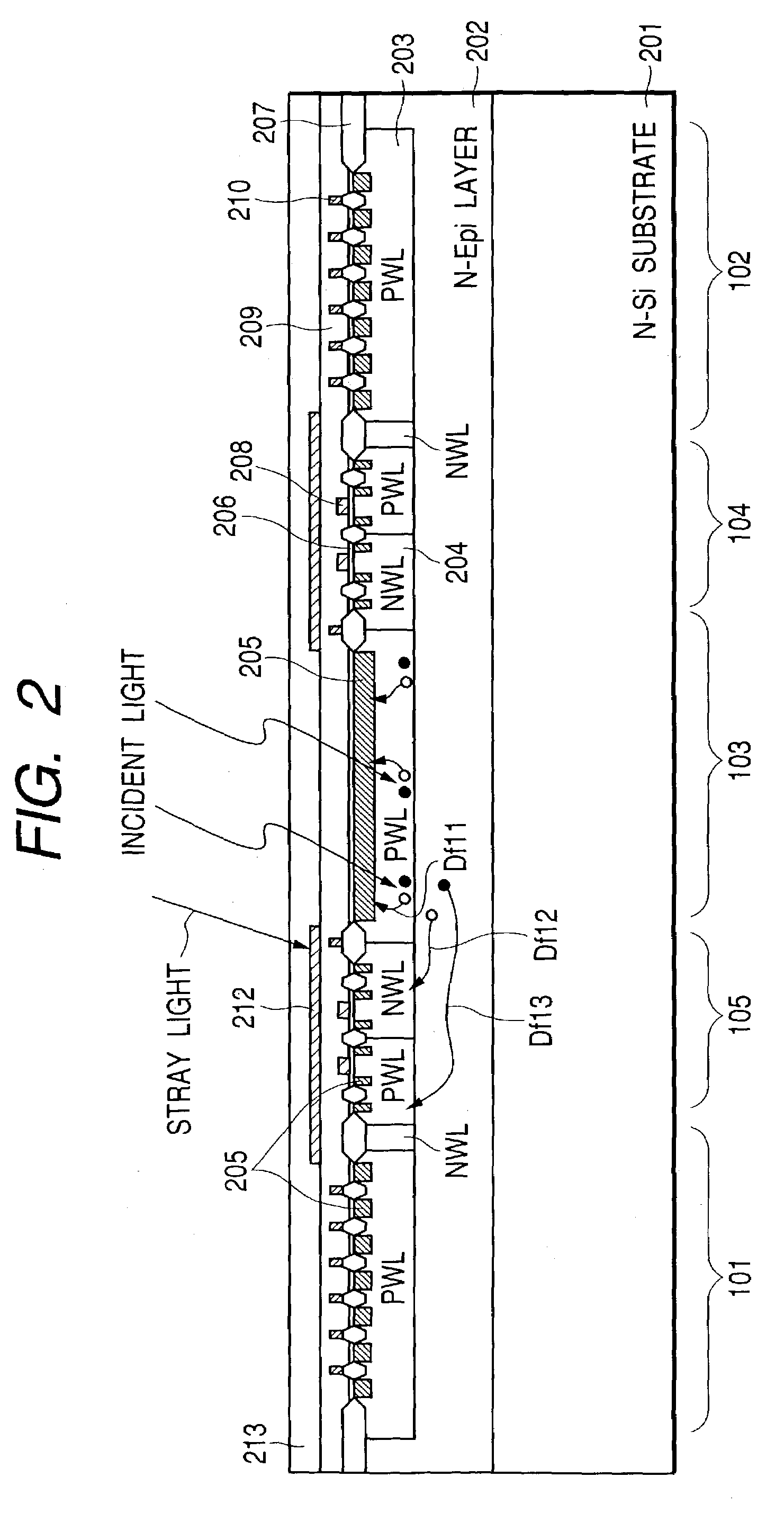

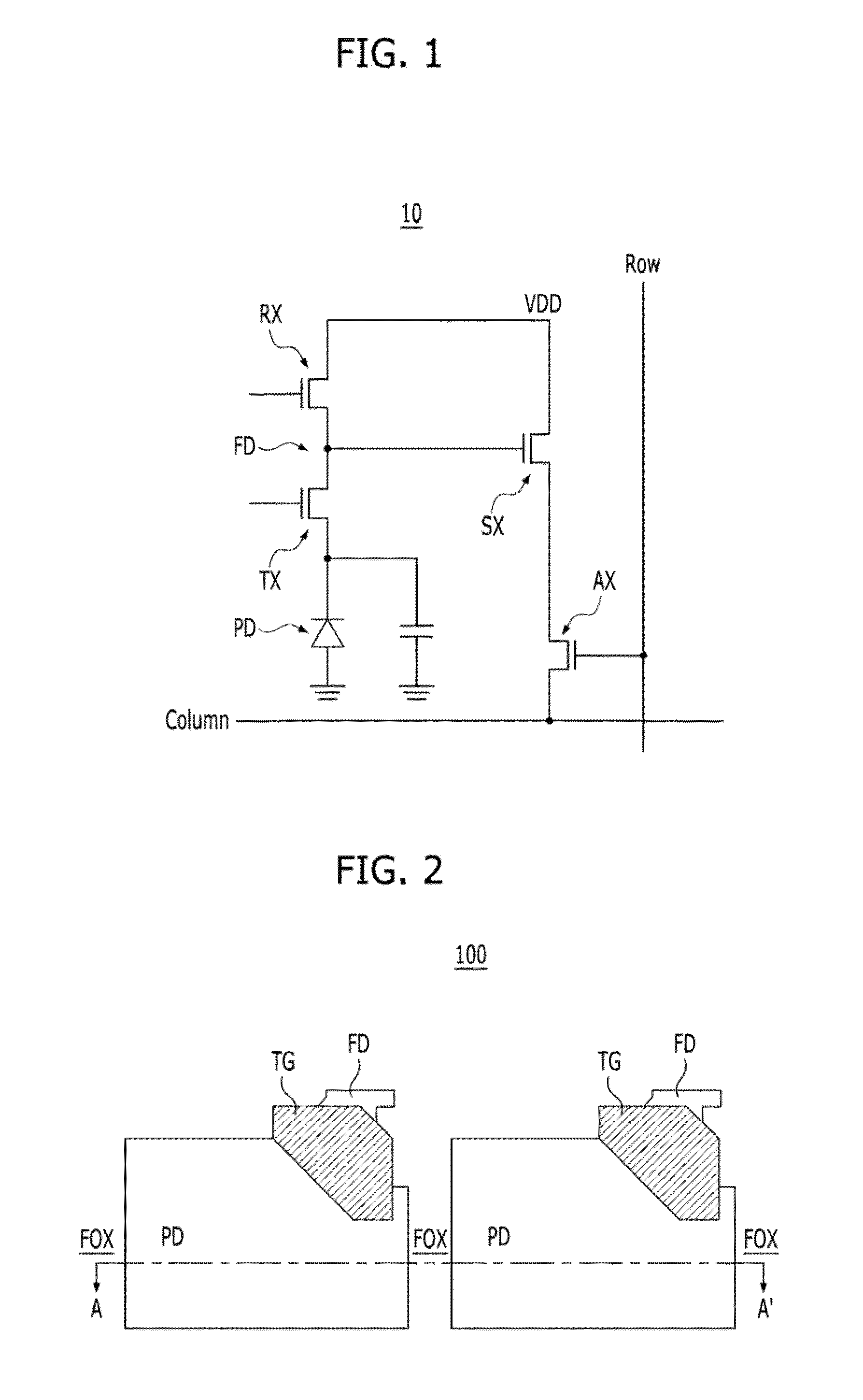

Solid state image pickup device

InactiveUS7164447B2High precisionSuppress incidentTelevision system detailsTelevision system scanning detailsImpurity dopingPhotoelectric conversion

A solid state image pickup device is provided which can reduce crosstalks between range finding photoelectric conversion elements (AF sensor) and photometry photoelectric conversion elements (AE sensor). The solid state image pickup device has an n-type epitaxial semiconductor region, a p-type first well region formed in the semiconductor region, a p-type second well region formed in the semiconductor region and electrically separated from the first well, an n-type first impurity doped region formed in the first well region and an n-type second impurity doped region formed in the second well, wherein a photometry photoelectric conversion element is formed by using the p-type first well region and n-type first impurity doped region, and a range finding photoelectric element is formed by using the p-type second well region and n-type impurity doped region.

Owner:CANON KK

Method of controlling impurity doping and impurity doping apparatus

InactiveUS7666770B2Improve accuracyVariation in qualitySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingDopantImpurity doping

A method is provided for controlling a dose amount of dopant to be doped into an object to be processed in plasma doping. According to the method, the doping control is formed of the following processes: determining the temperature of the object, the amount of ions having dopant in plasma that collide with the object, and types of gases in plasma during doping; calculating a dose amount by neutral gas according to the temperature of the object, and a dose amount by ions from the determined amount of ions containing dopant that collide with the object; and carrying out doping so that the sum of the dose amount by neutral gas and the dose amount by ions equal to a predetermined dose amount.

Owner:PANASONIC CORP

Diffusion method for polycrystalline silicon solar photovoltaic cell silicon chip

ActiveCN102569523AReduce concentrationReduce compound rateFinal product manufactureDiffusion/dopingImpurity dopingPhysical chemistry

The invention relates to a diffusion method for a polycrystalline silicon solar photovoltaic cell silicon chip. The method comprises the following steps of: 1, putting the silicon chip into a furnace; 2, oxidizing; 3, diffusing a phosphorus source for the first time; 4, performing impurity distribution for the first time; 5, diffusing the phosphorus source for the second time; 6, performing impurity distribution for the second time; 7, gettering; and 8, taking the chip out of the furnace. The diffusion method for the polycrystalline silicon solar photovoltaic cell silicon chip has the advantages that: the phosphorus impurity doping concentration distribution is good, the diffusion rate has high controllability, the first pass yield of diffusion of the silicon chip is improved, the minority carrier lifetime of a polycrystalline silicon chip is prolonged, and the utilization rate of the phosphorus source in the diffusion process is high.

Owner:SUZHOU AIKANG PHOTOELECTRIC TECH CO LTD

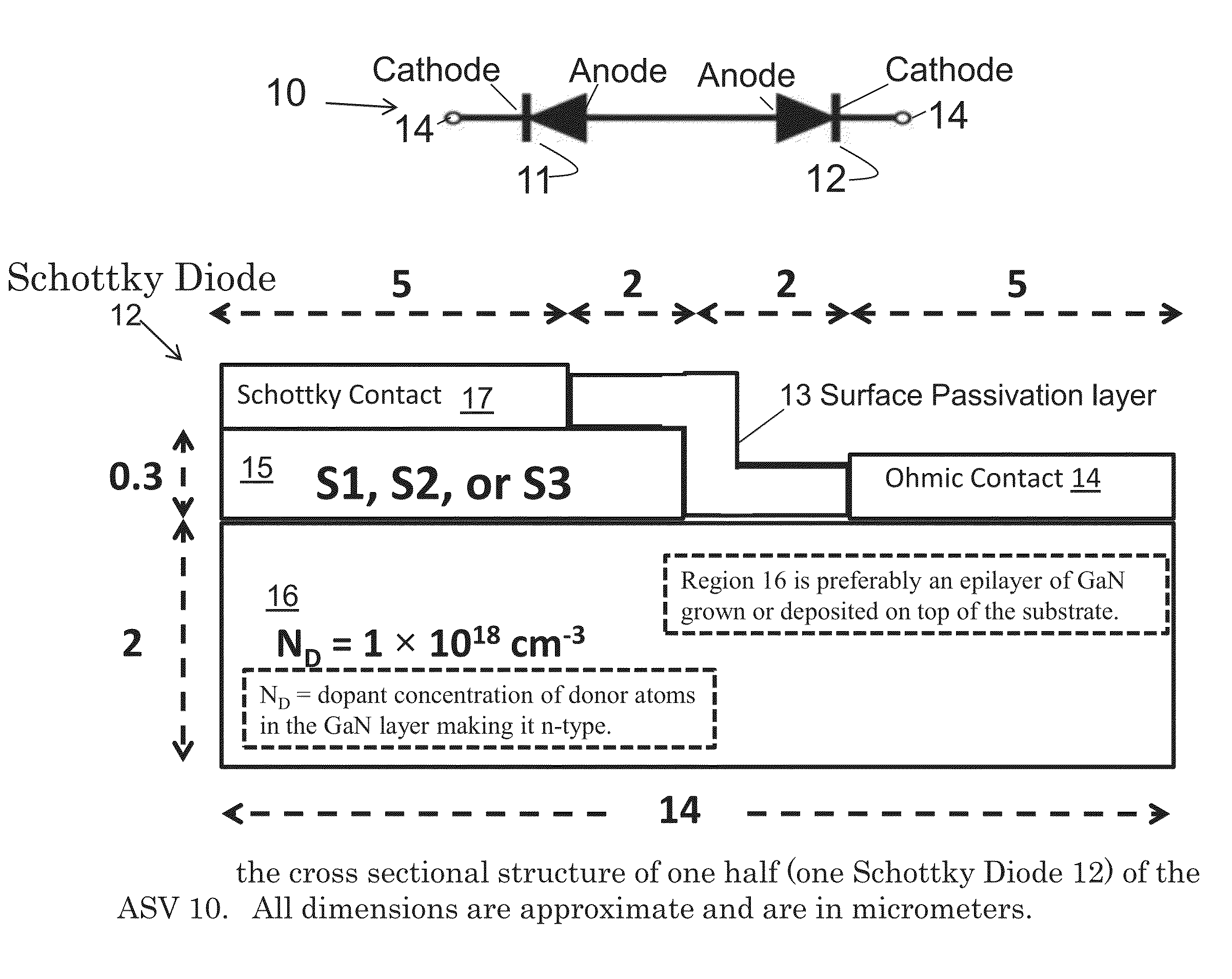

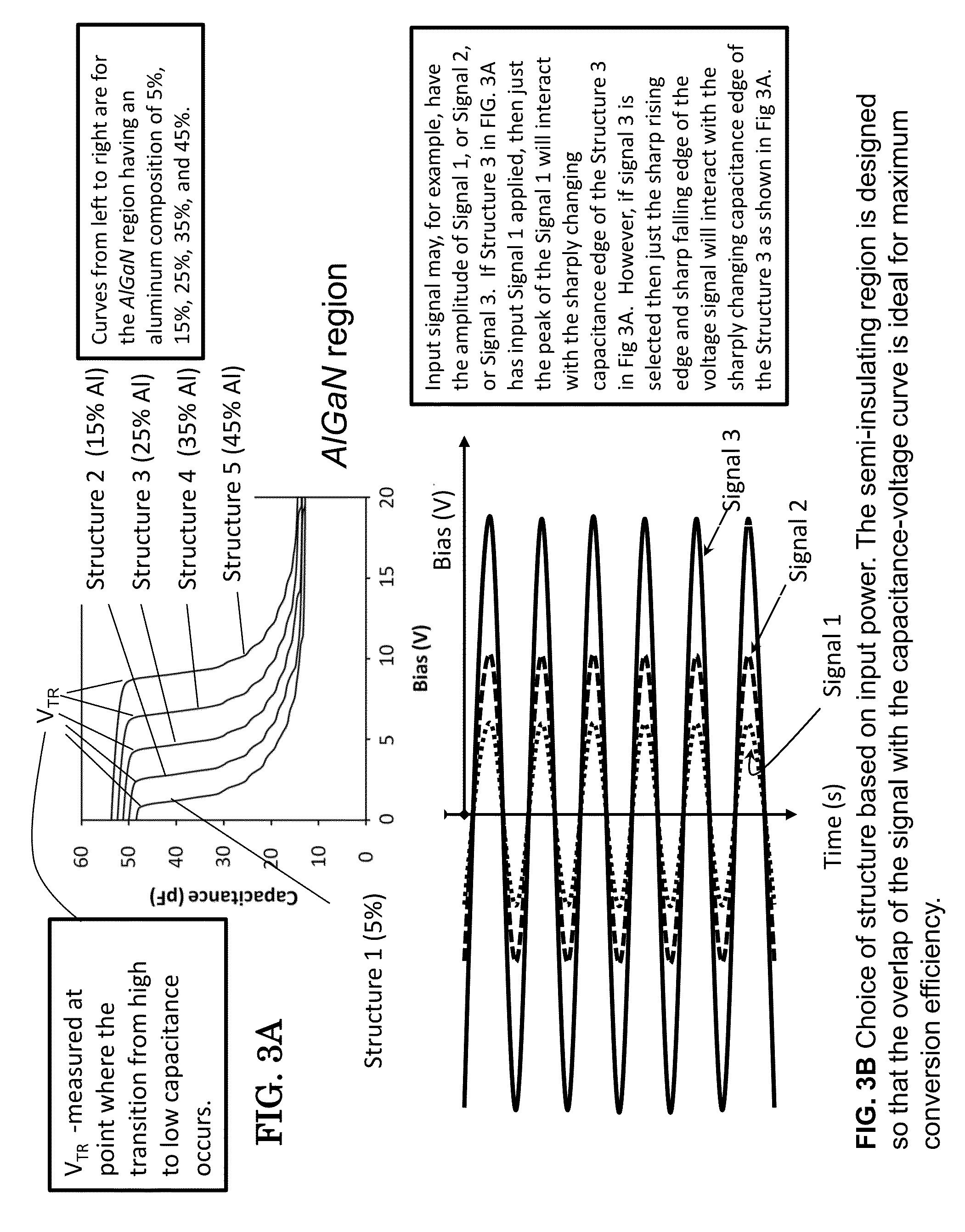

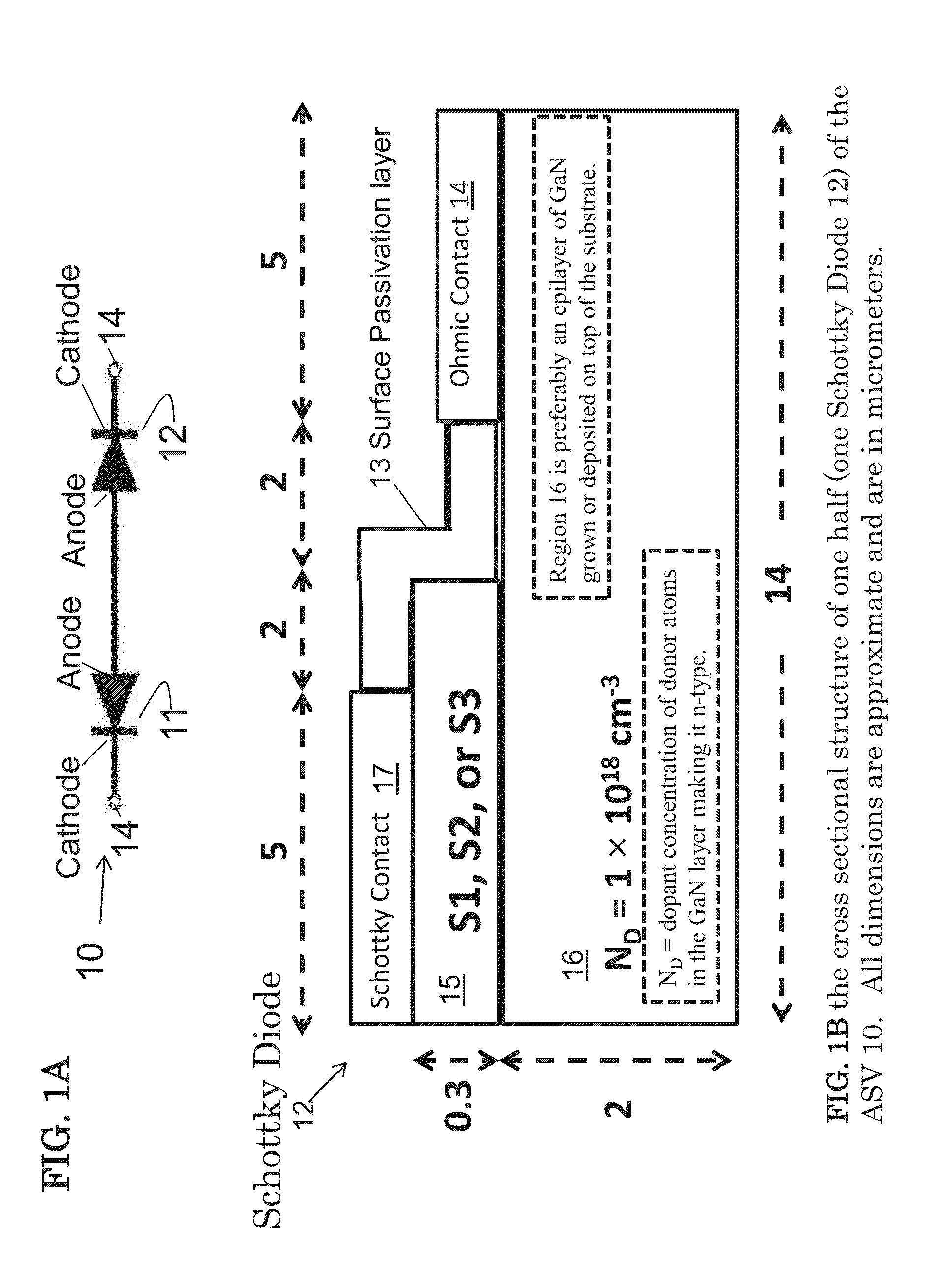

Method of optimizing a ga-nitride device material structure for a frequency multiplication device

InactiveUS20140239305A1Reduced life-timeImprove efficiencyCAD circuit designSoftware simulation/interpretation/emulationImpurity dopingDevice material

A preferred method of optimizing a Ga-nitride device material structure for a frequency multiplication device comprises:determining the amplitude and frequency of the input signal being multiplied in frequency;providing a Ga-nitride region on a substrate;determining the Al percentage composition and impurity doping in an AlGaN region positioned on the Ga-nitride region based upon the power level and waveform of the input signal and the desired frequency range in order to optimize power input / output efficiency; andselecting an orientation of N-face polar GaN or Ga-face polar GaN material relative to the AlGaN / GaN interface so as to orient the face of the GaN so as to optimize charge at the AlGaN / GaN interface. A preferred embodiment comprises an anti-serial Schottky varactor comprising: two Schottky diodes in anti-serial connection; each comprising at least one GaN layer designed based upon doping and thickness to improve the conversion efficiency.

Owner:US SEC THE ARMY THE

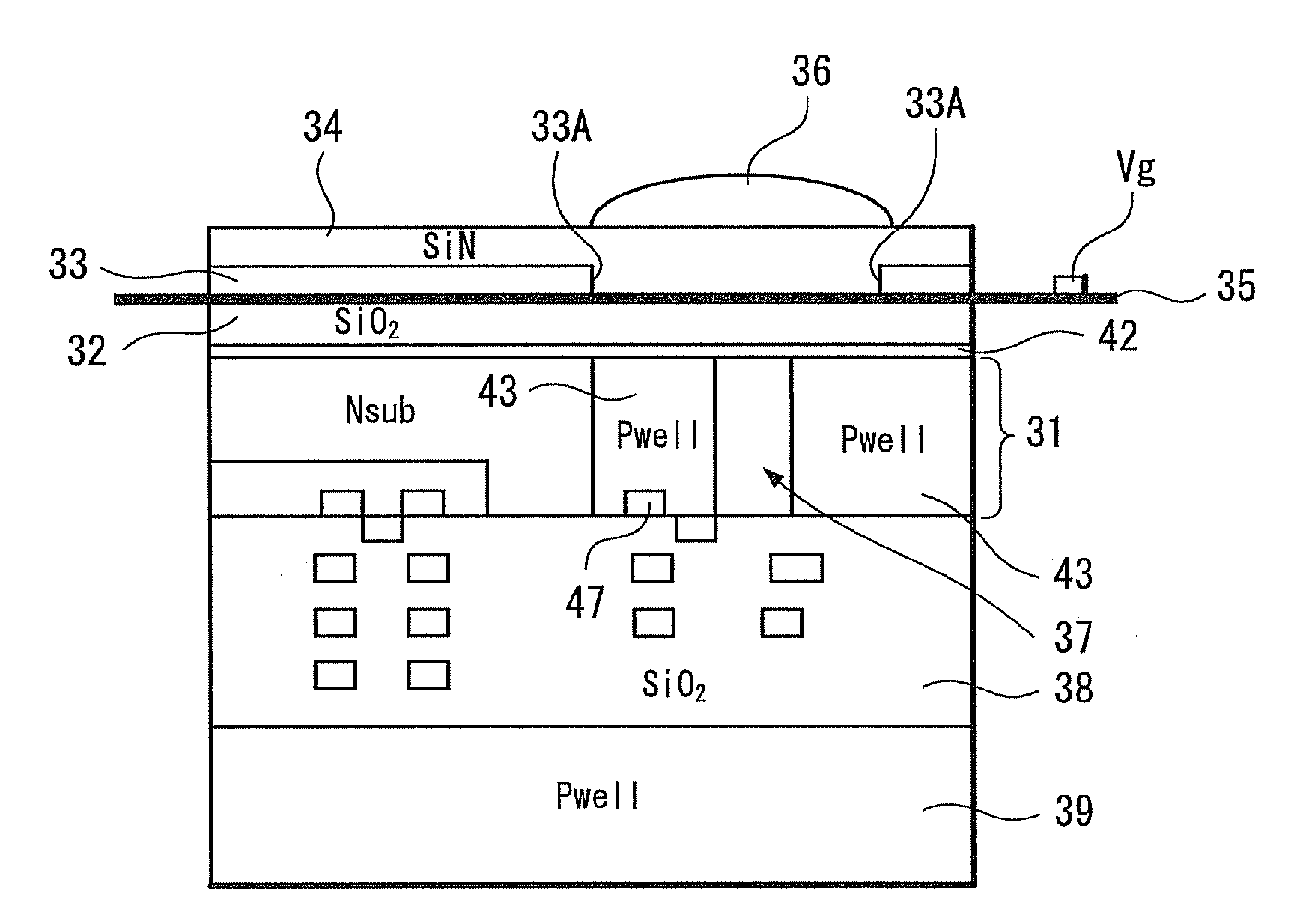

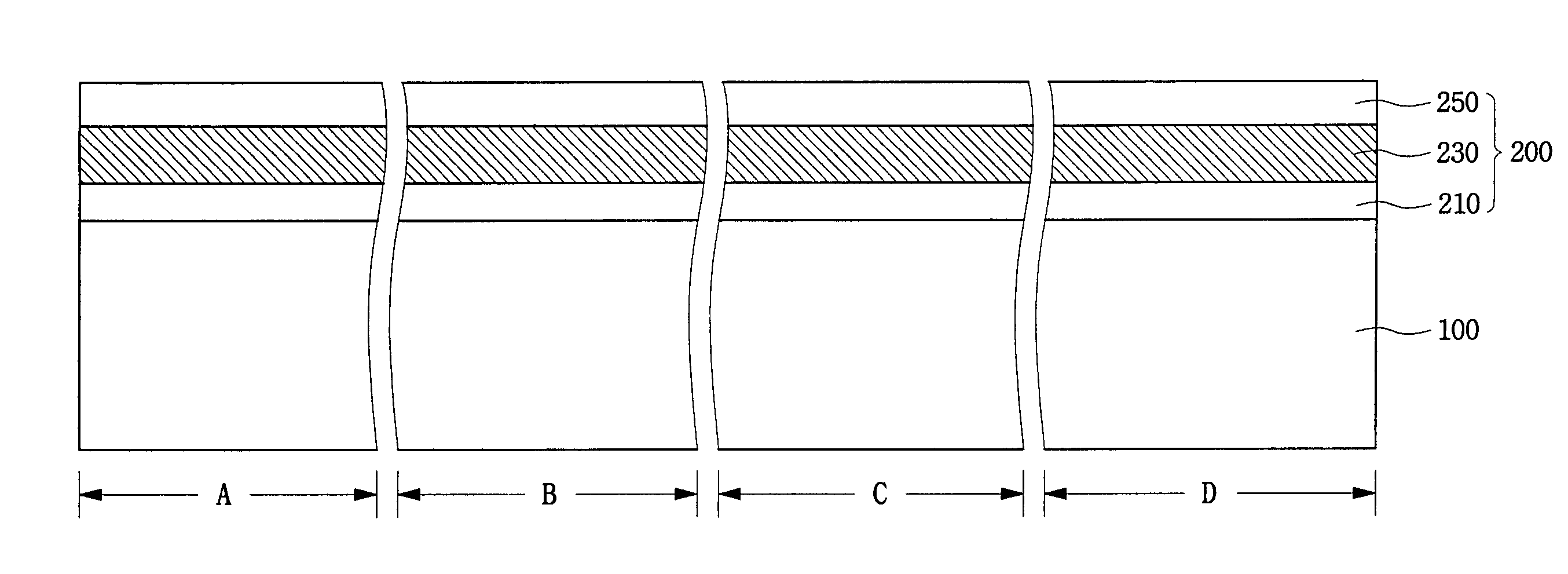

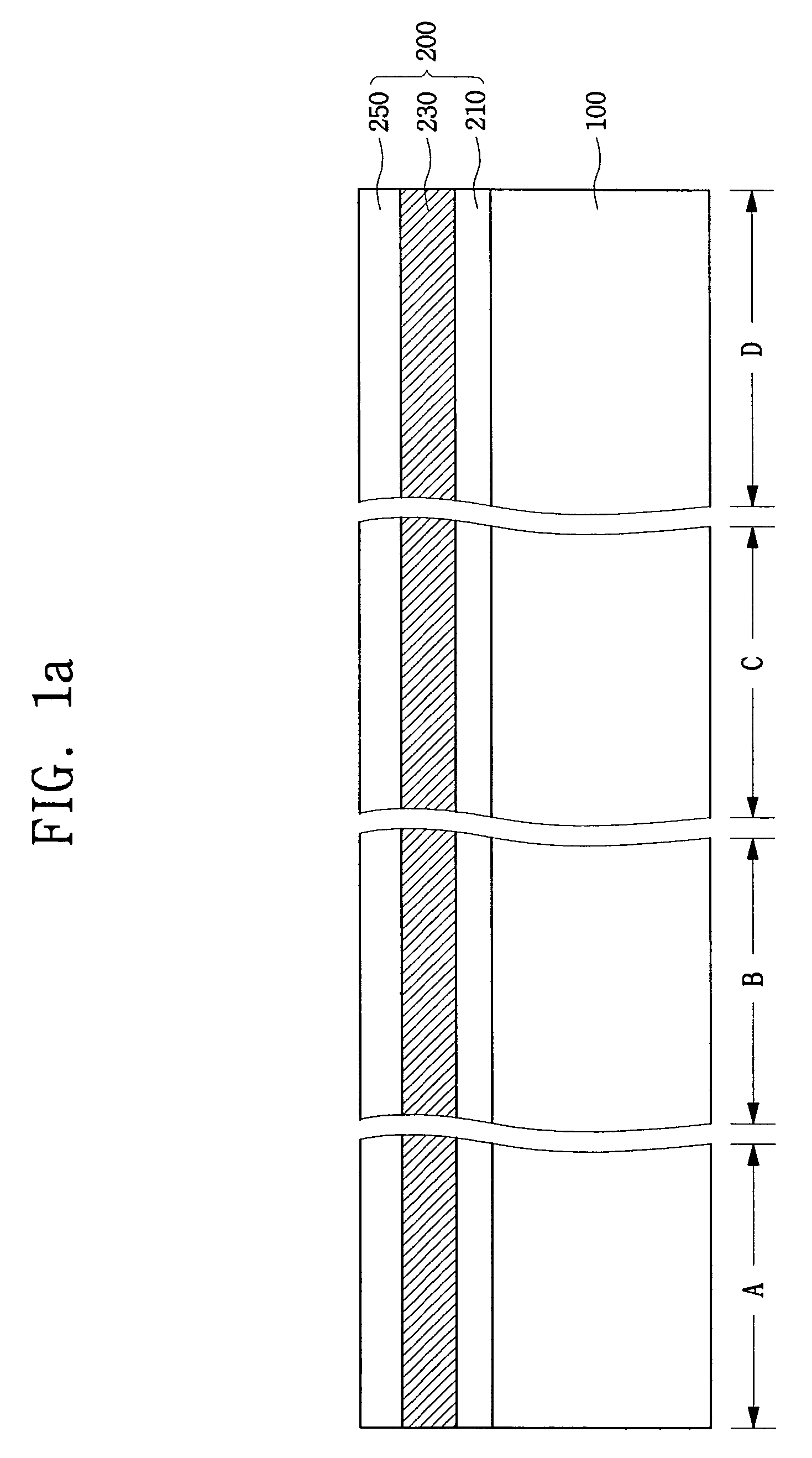

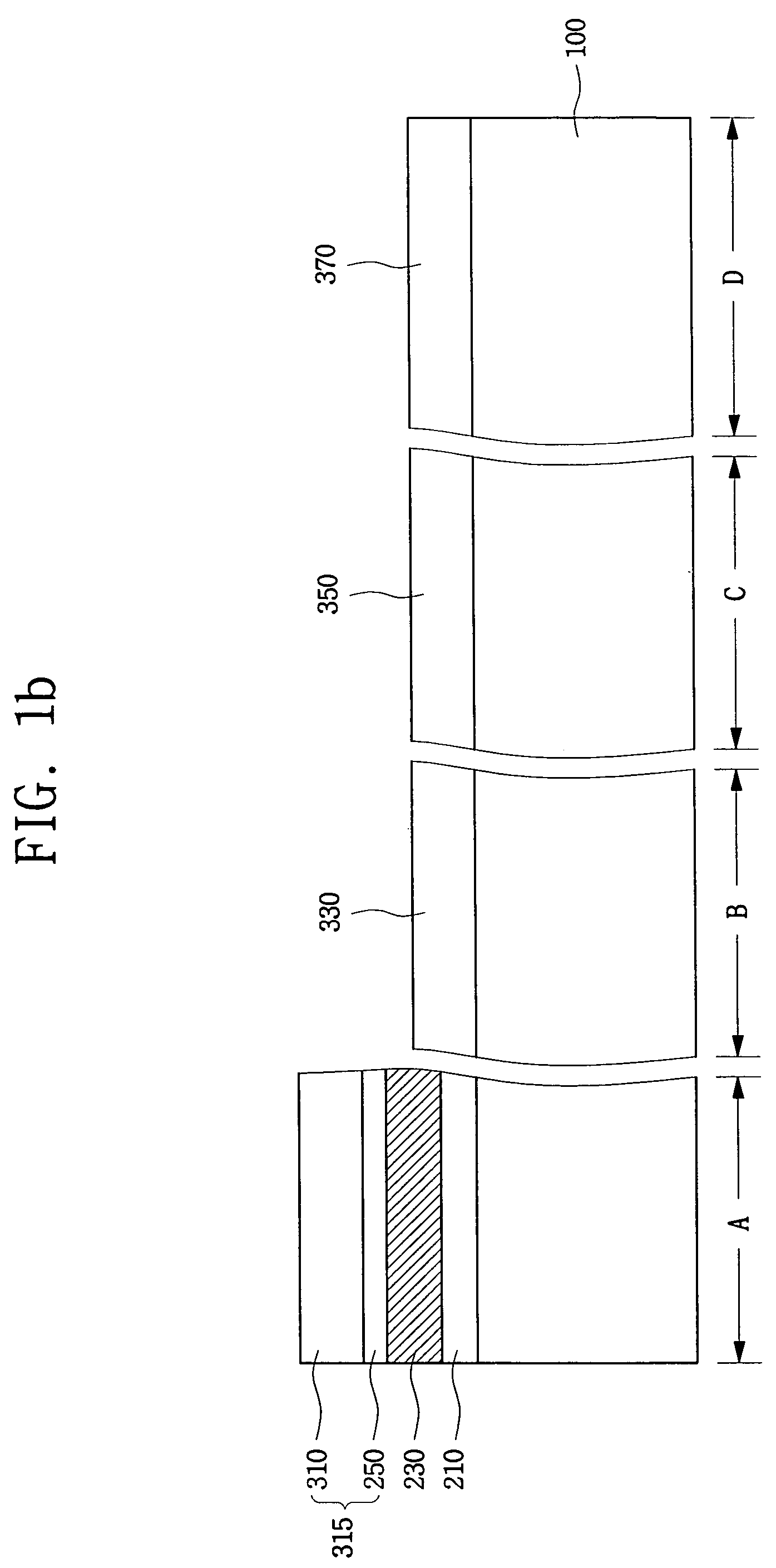

Sensor, solid-state imaging device, and imaging apparatus and method of manufacturing the same

InactiveUS20090184387A1High sensitive determinationTransistorSpectrum investigationImpurity dopingGate voltage

A sensor is provided. The sensor includes semiconductor layer; a photodiode, an impurity-doped polycrystalline silicon layer; and a gate electrode. The photodiode is formed in the semiconductor layer. The impurity-doped polycrystalline silicon layer is formed above the semiconductor layer. The gate electrode applies a gate voltage to the polycrystalline silicon layer. A wiring layer is provided on a first surface of the semiconductor layer and light is incident on a second surface thereof.

Owner:SONY CORP

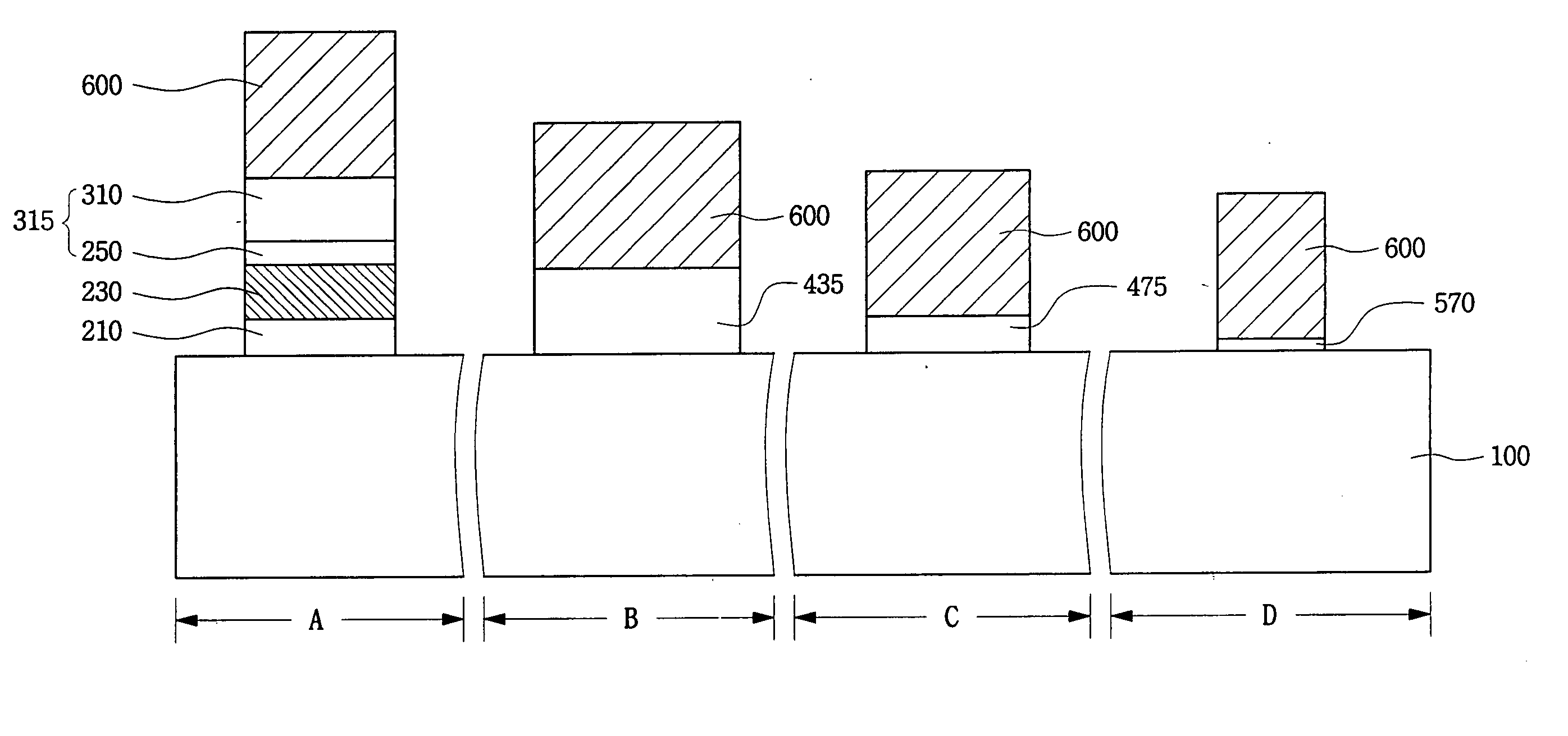

Fabrication method for semiconductor device and manufacturing apparatus for the same

A shallow p-n junction diffusion layer having a high activation rate of implanted ions, low resistivity, and a controlled leakage current is formed through annealing. Annealing after impurities have been doped is carried out through light irradiation. Those impurities are activated by annealing at least twice through light irradiation after doping impurities to a semiconductor substrate 11. The light radiations are characterized by usage of a W halogen lamp RTA or a flash lamp FLA except for the final light irradiation using a flash lamp FLA. Impurity diffusion maybe controlled to a minimum, and crystal defects, which have developed in an impurity doping process, may be sufficiently reduced when forming ion implanted layers in a source and a drain extension region of the MOSFET or ion implanted layers in a source and a drain region.

Owner:KIOXIA CORP

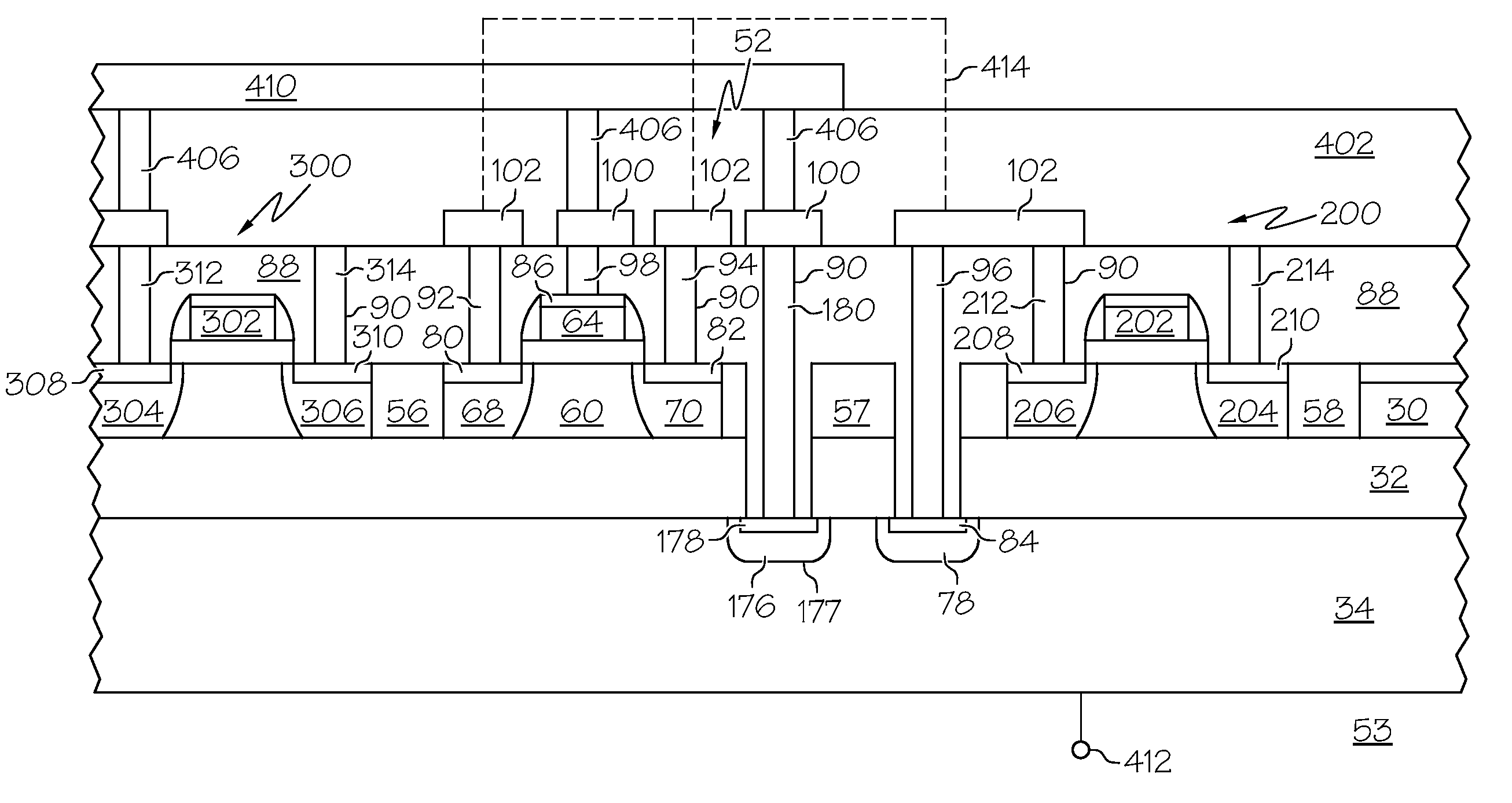

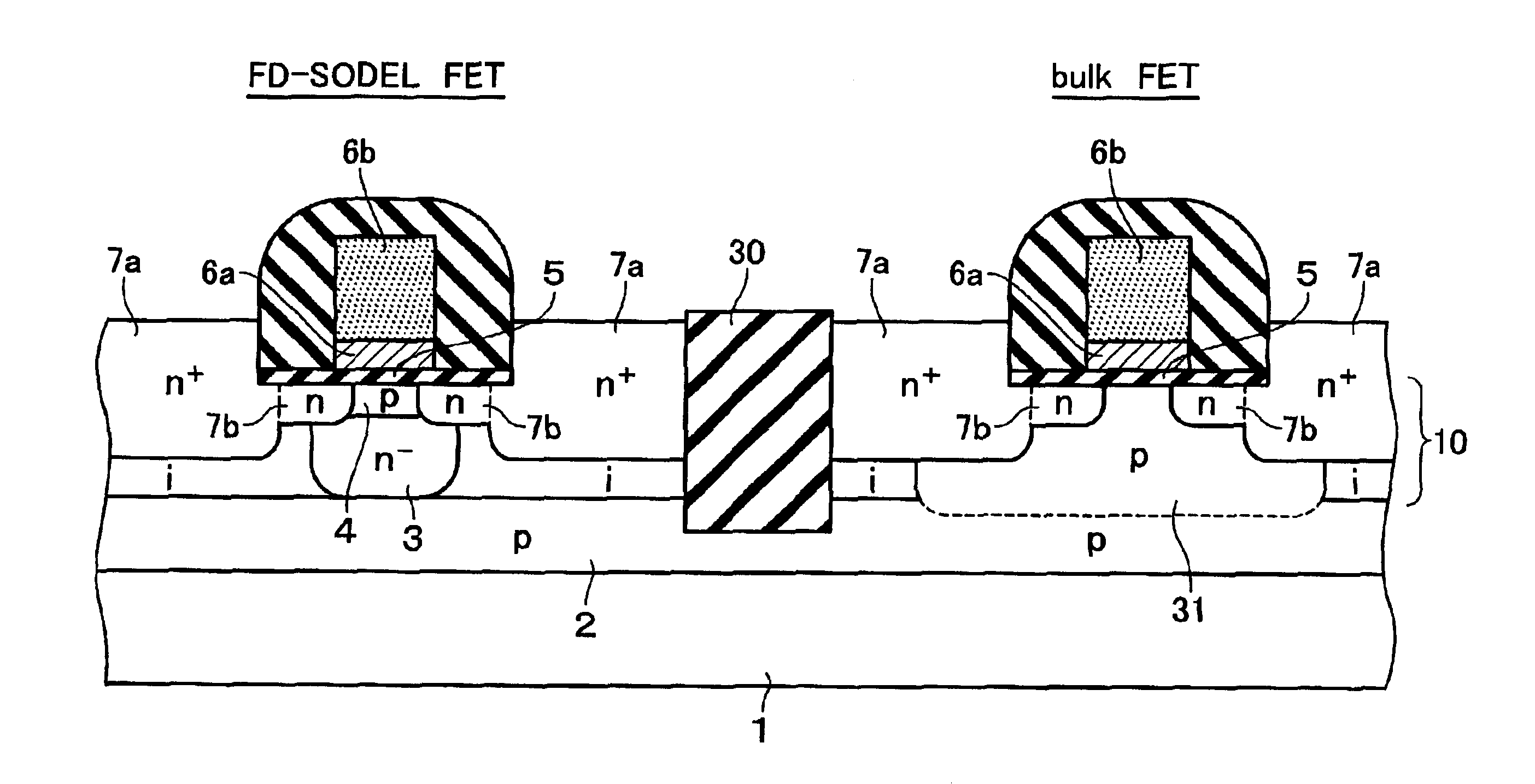

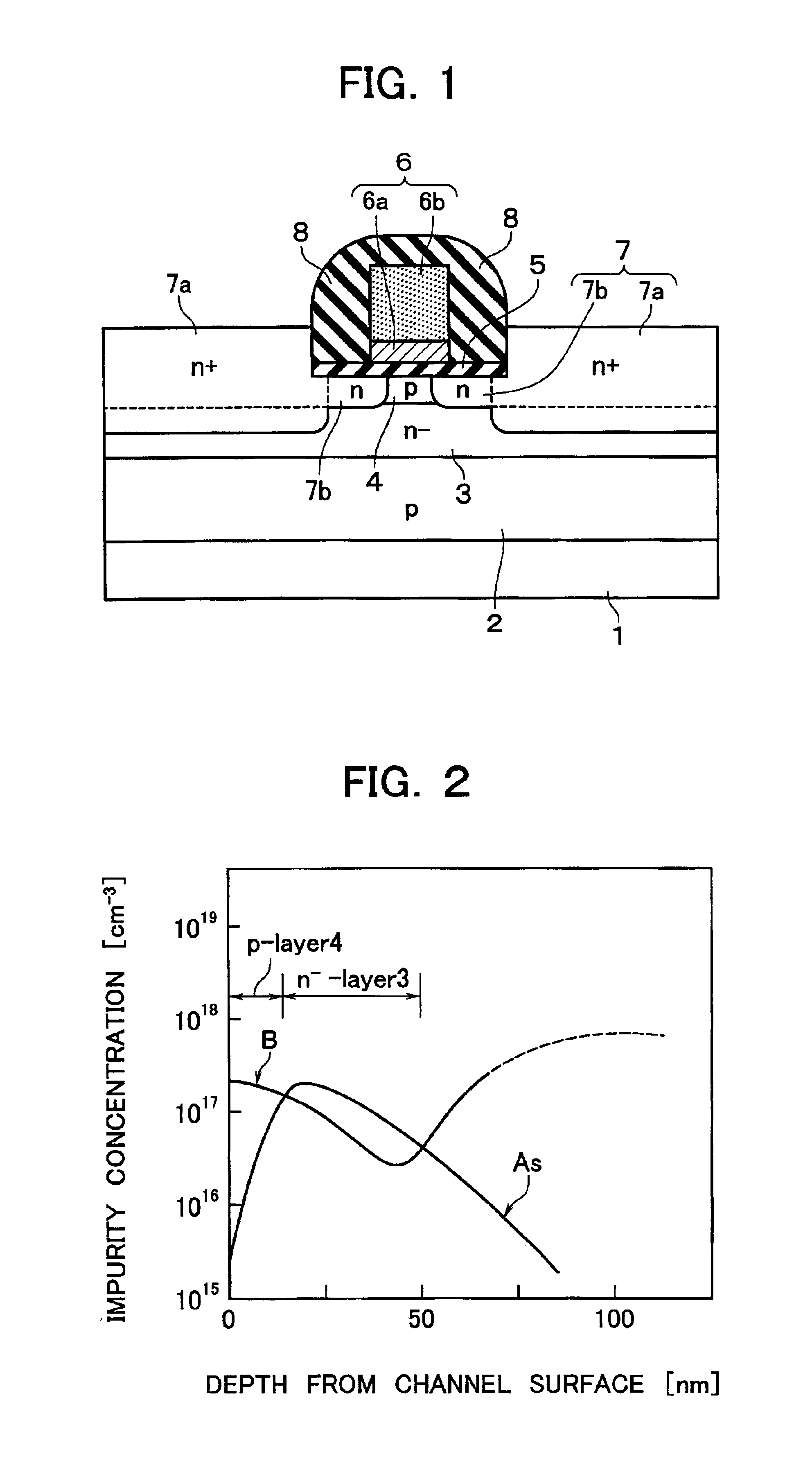

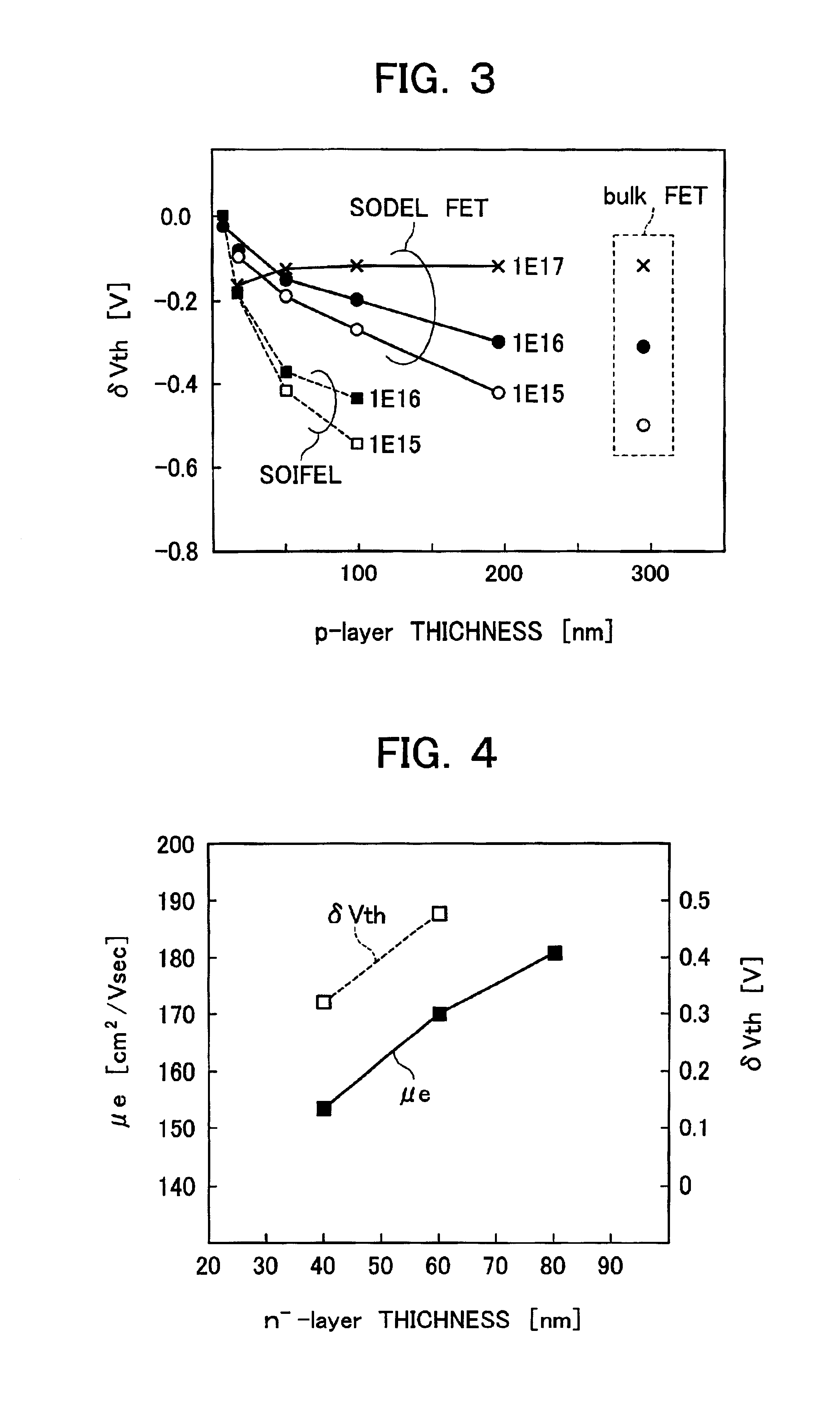

Semiconductor device realizing characteristics like a SOI MOSFET

Owner:KIOXIA CORP

Preparation method of germanium-base schottky transistor

ActiveCN101635262AGood lookingImprove performanceSemiconductor/solid-state device manufacturingVery large scale integrated circuitsManufacturing technology

The invention discloses a preparation method of a germanium-base schottky transistor, which belongs to the technical field of a manufacturing process of ultra large scale integrated circuits (ULSI). The method comprises the following steps: manufacturing an MOS transistor structure on a germanium-base substrate; depositing a metal thin film; carrying out heat treatment for the first time for quick heat annealing so as to ensure that the metal thin film layer and the germanium layer below the metal thin film layer react to form metal germanide; removing the unreacted metal thin film layer; doping impurities in the germanide layer generated by the reaction; carrying out heat treatment for the second time for annealing so as to ensure that the doped impurities are activated to drive in; and finally forming contact holes and metal connection wires. The method carries out the impurity doping and the activated drive-in annealing after forming the germanide through the first annealing and can effectively regulate and control a barrier height of the contact of a metal semiconductor and also improve the surface appearance of the germanide.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

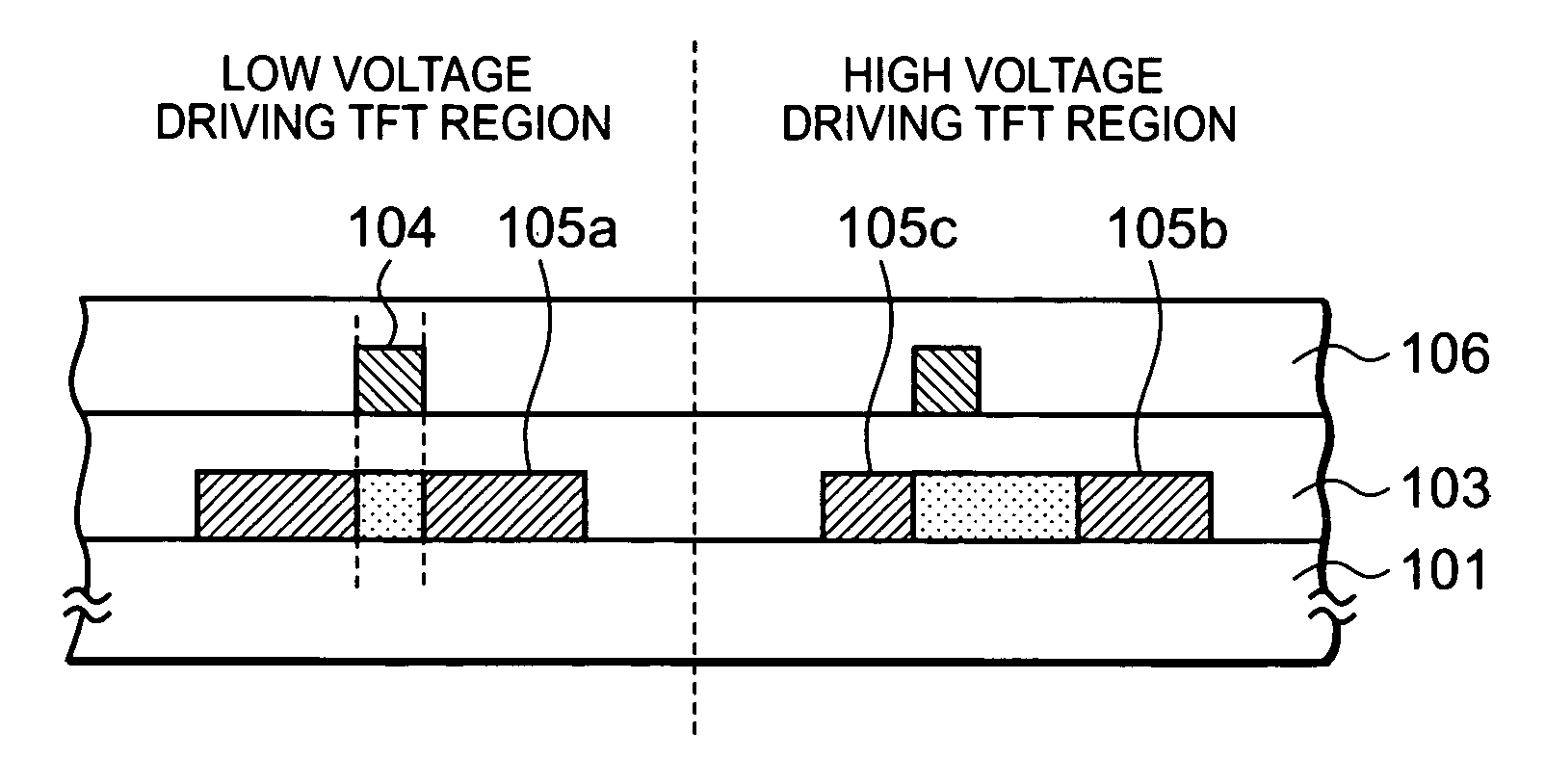

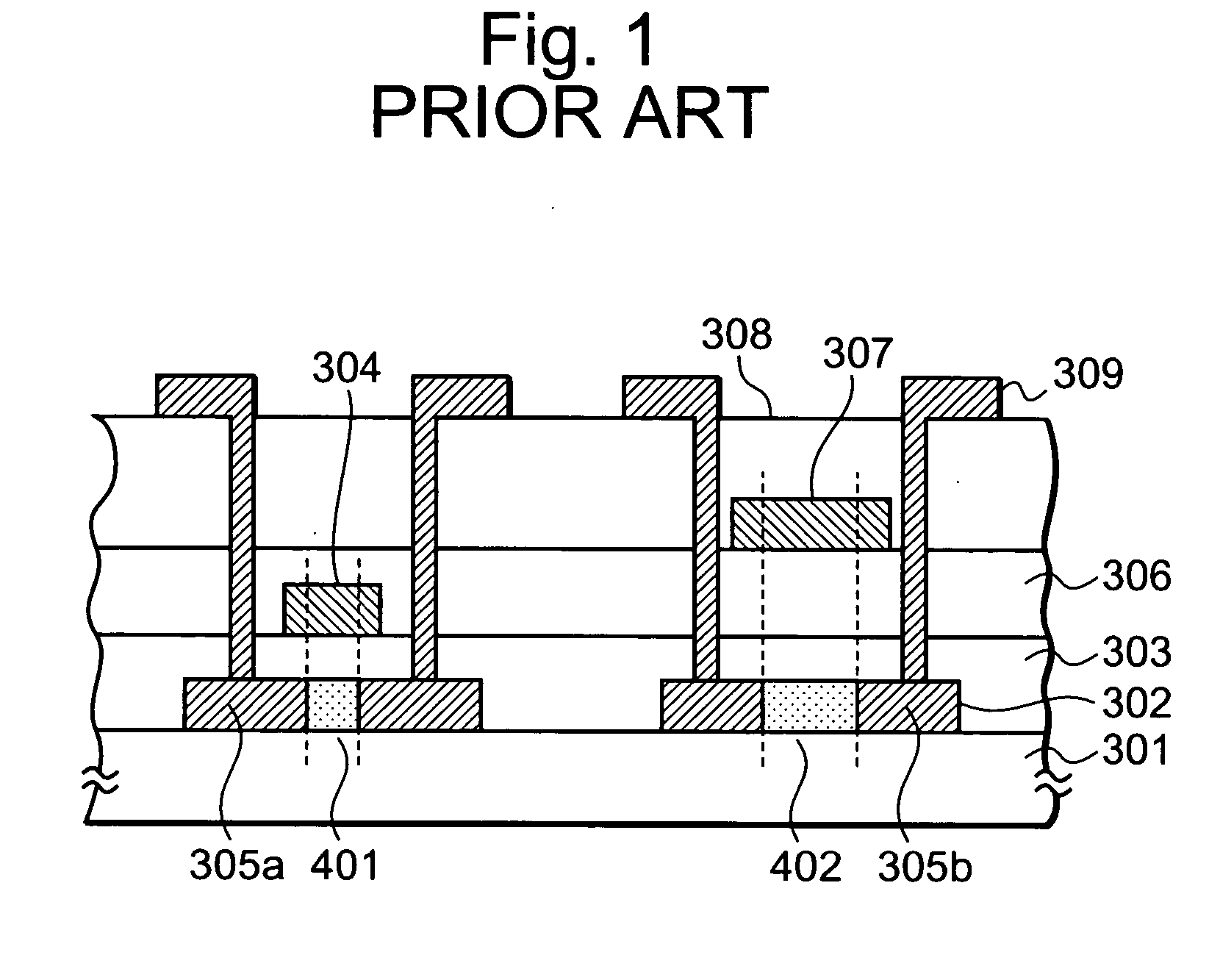

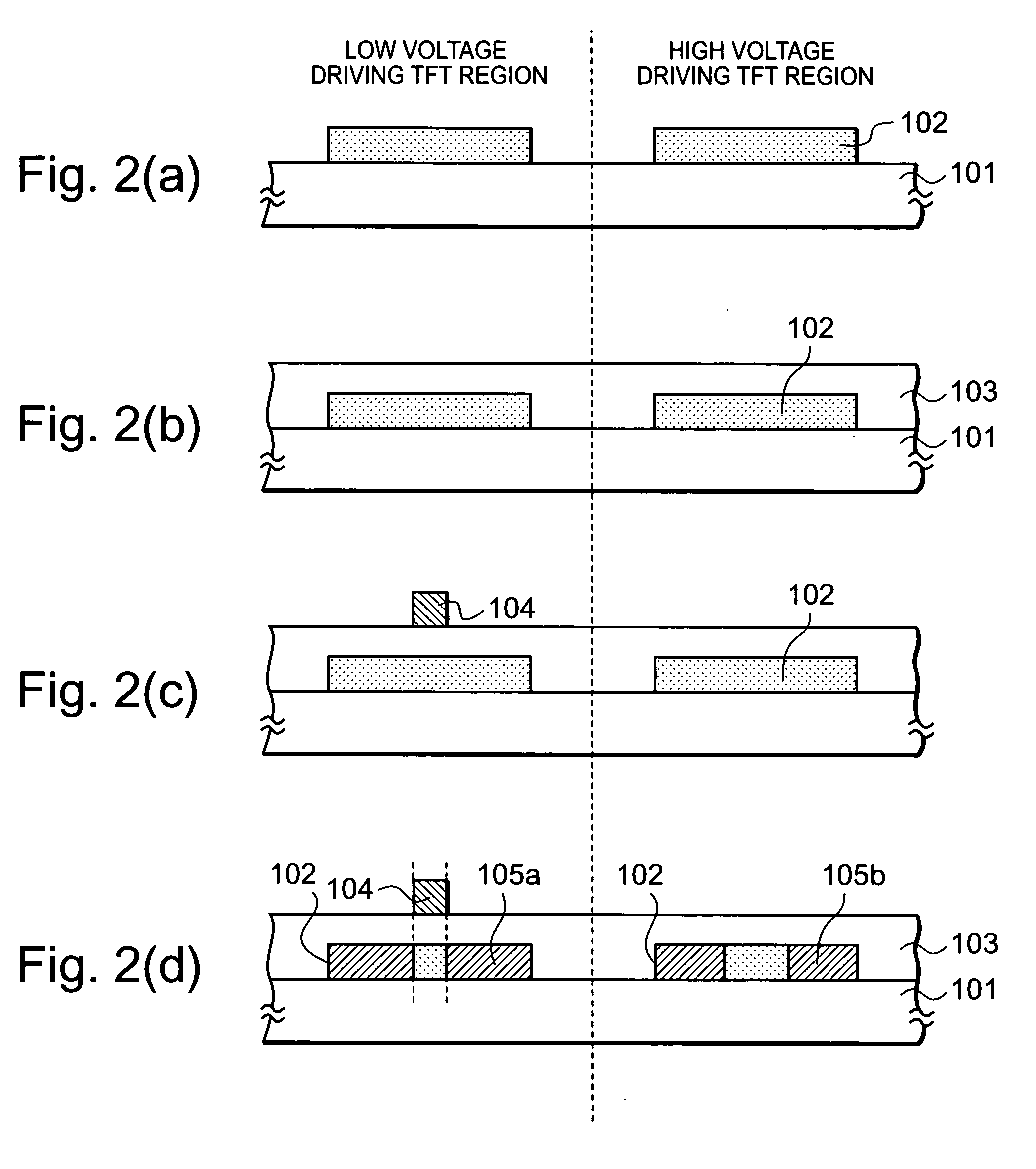

Thin film transistor substrate and method for manufacturing the same

A thin film transistor substrate is provided including a first thin film transistor and a second thin film transistor. The first thin film transistor comprises a first active layer, a first gate insulating film, and a first gate electrode. The second thin film transistor comprises a second active layer formed, a second gate insulating film, and a second gate electrode. A thickness of the second gate insulating film is larger than a thickness of the first gate insulating film, the second active layer has at least two impurity doping regions which overlap the second gate electrode, the first active layer has at least two impurity doping regions formed in a self-aligning manner with respect to the first gate electrode, and the second gate electrode comprises a semiconductor layer.

Owner:HANNSTAR DISPLAY CORPORATION

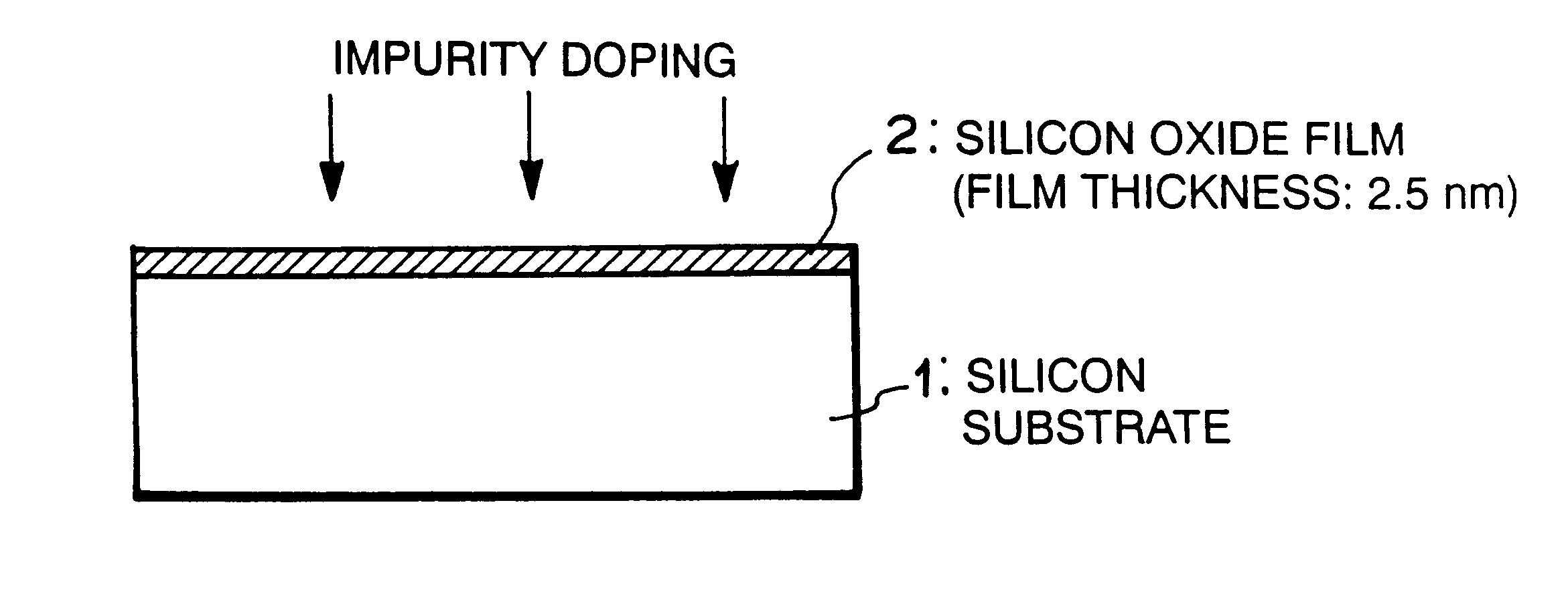

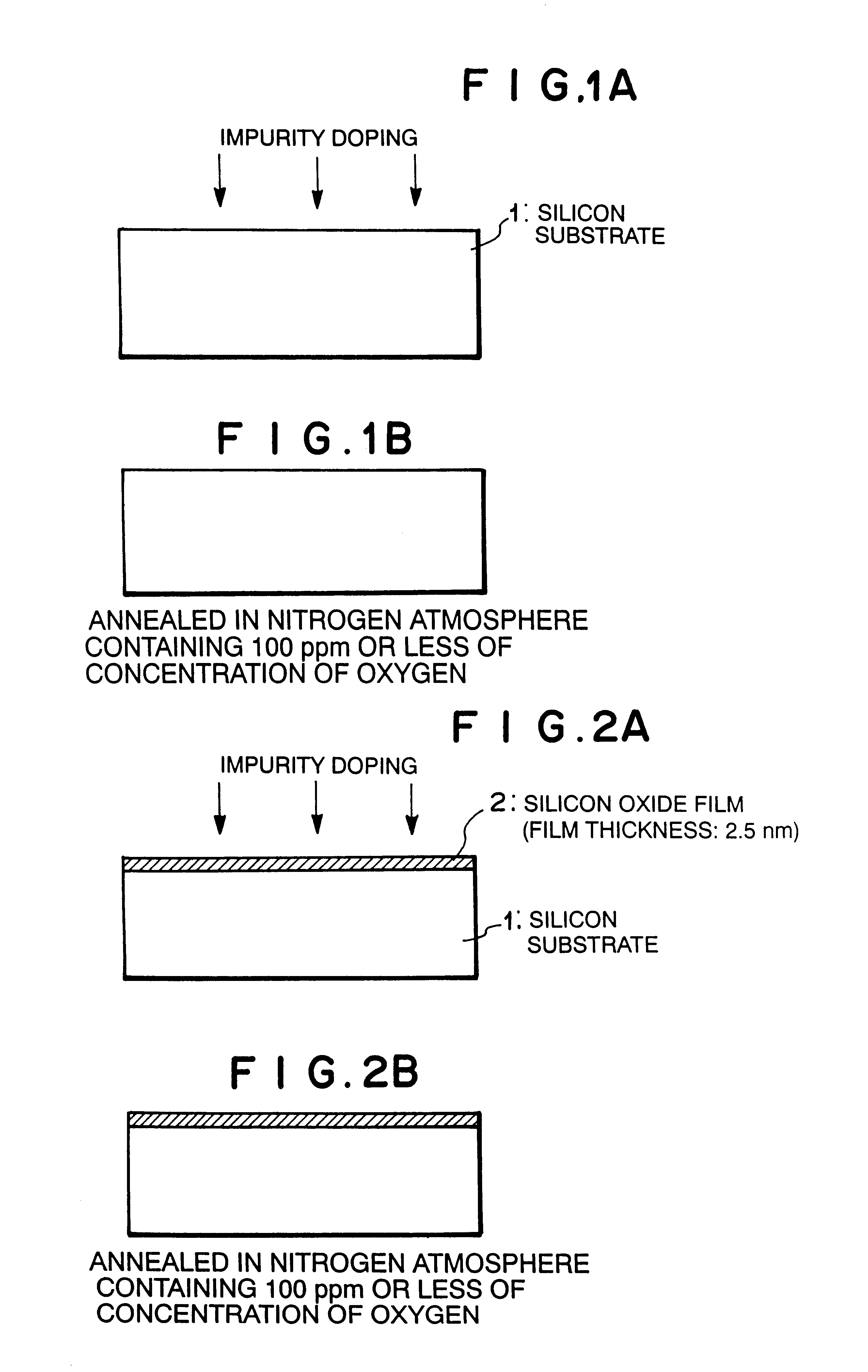

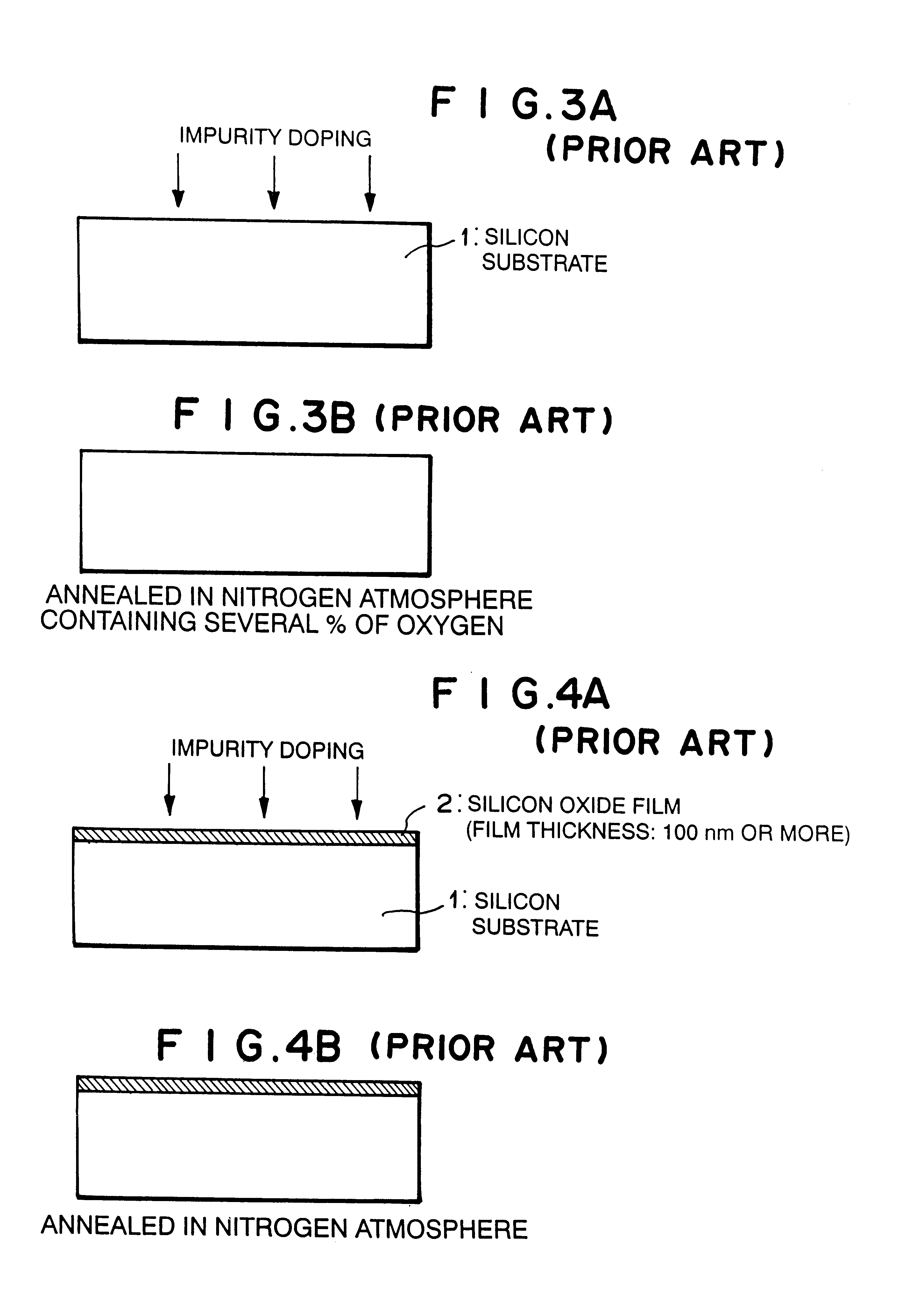

Method of manufacturing semiconductor device having shallow junction

InactiveUS6218270B1Avoid formingAvoid concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesImpurity diffusionImpurity doping

A method of manufacturing a semiconductor device having a silicon substrate containing an impurity diffusion layer is disclosed, that comprises the steps of doping impurities to the silicon substrate through a silicon oxide film with a thickness of 2.5 nm or less at an accelerating voltage of 3 keV or less, the silicon oxide film being formed on the silicon substrate and annealing the silicon substrate with the oxide film left.

Owner:RENESAS ELECTRONICS CORP

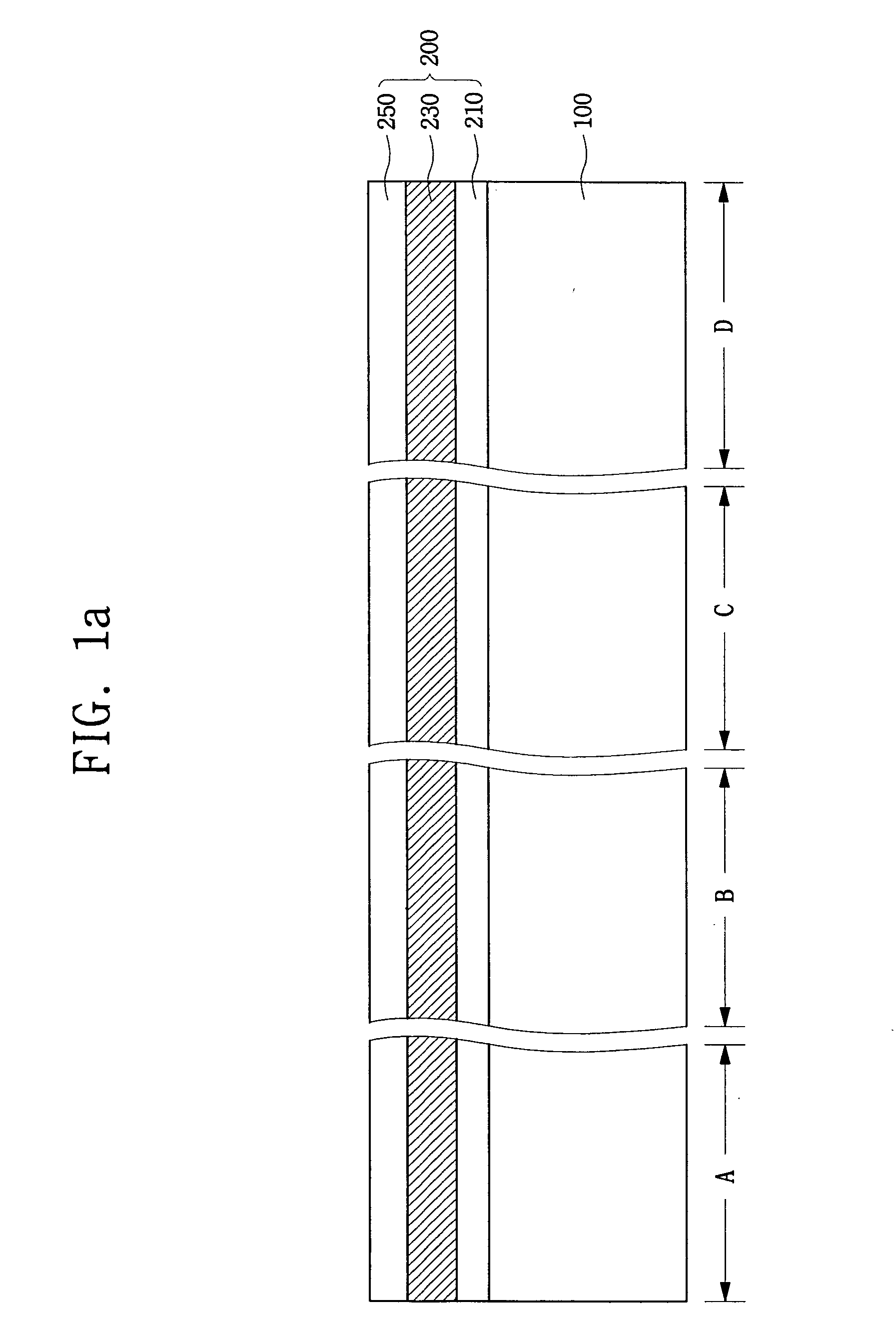

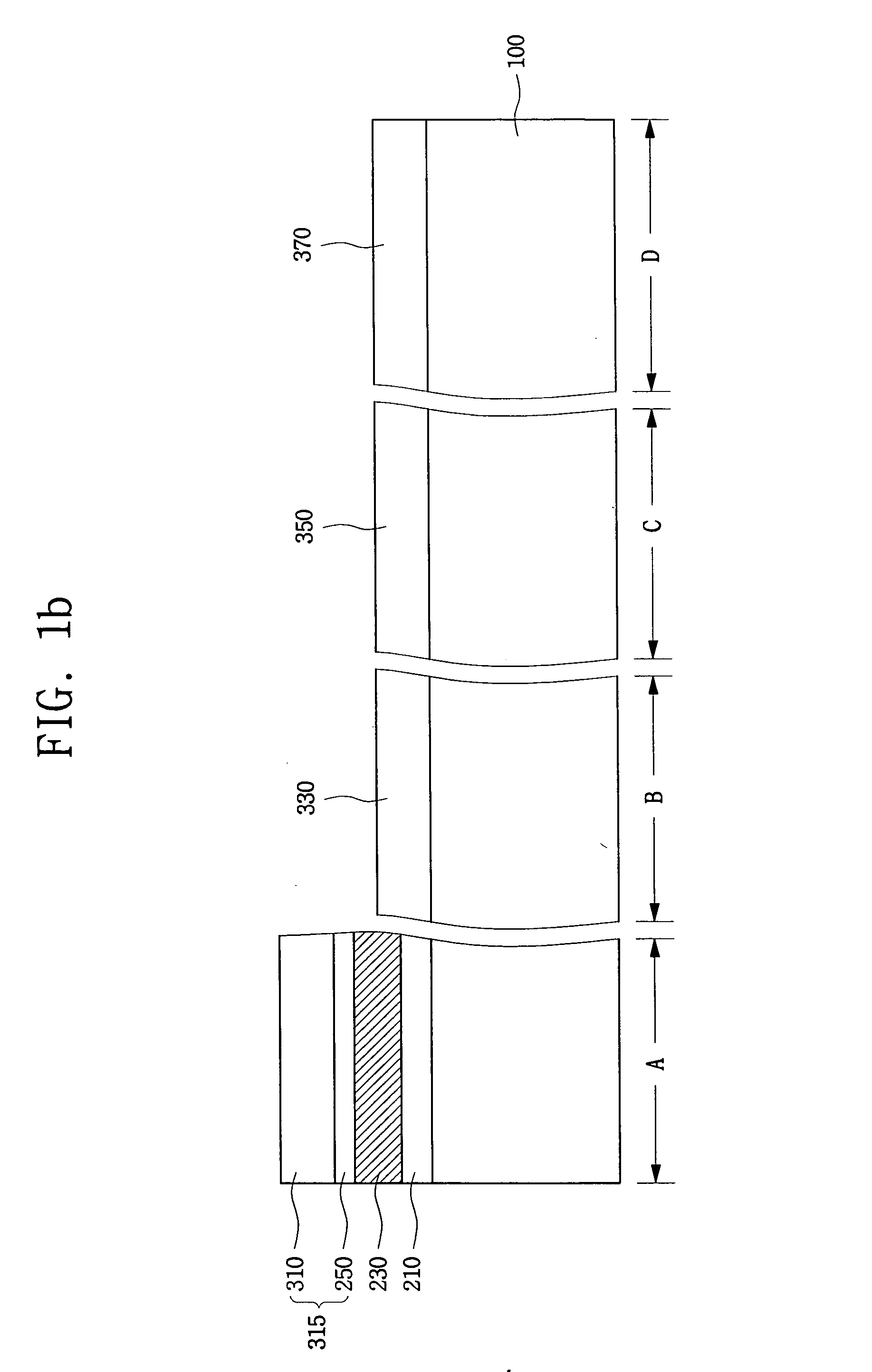

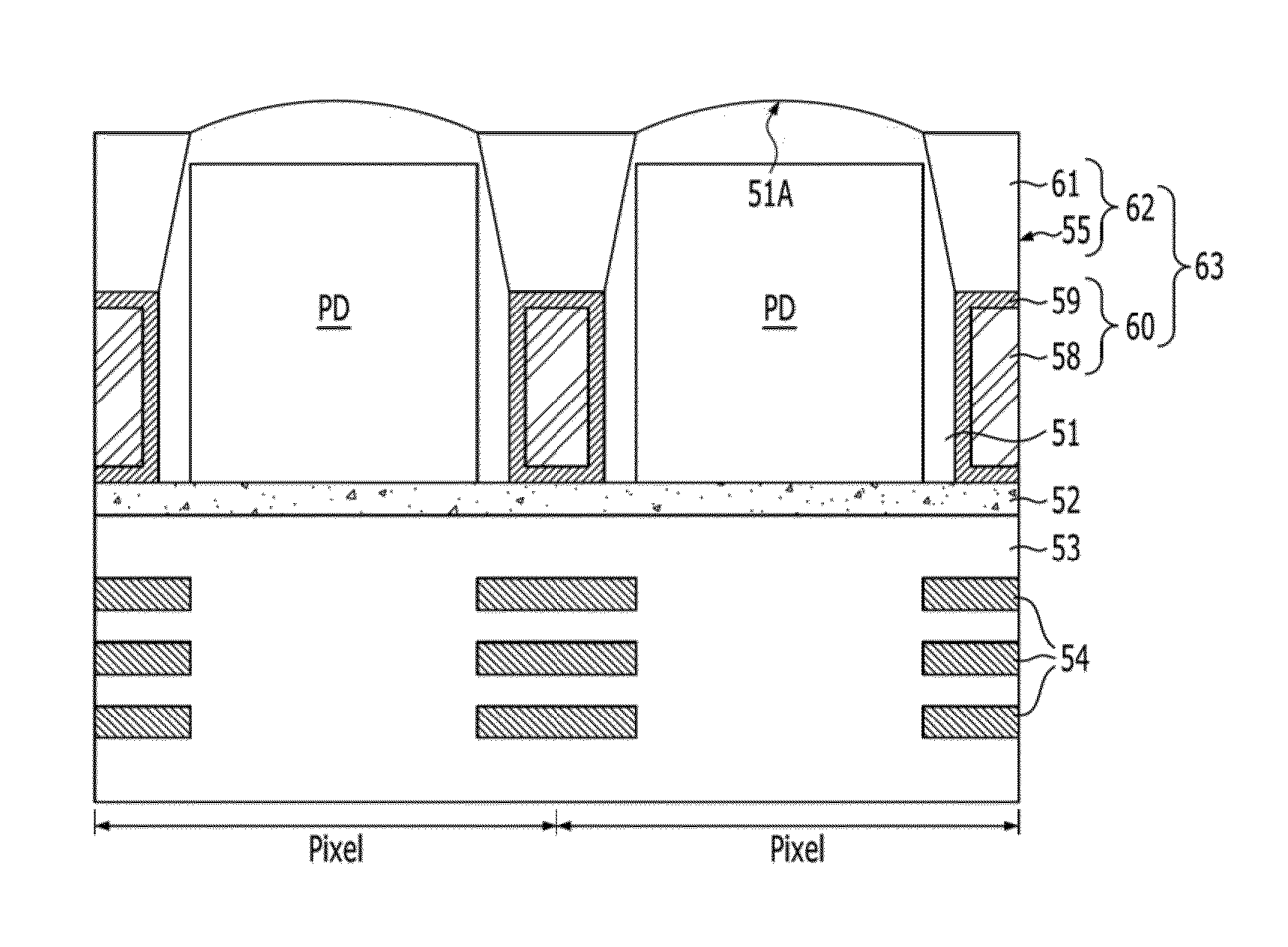

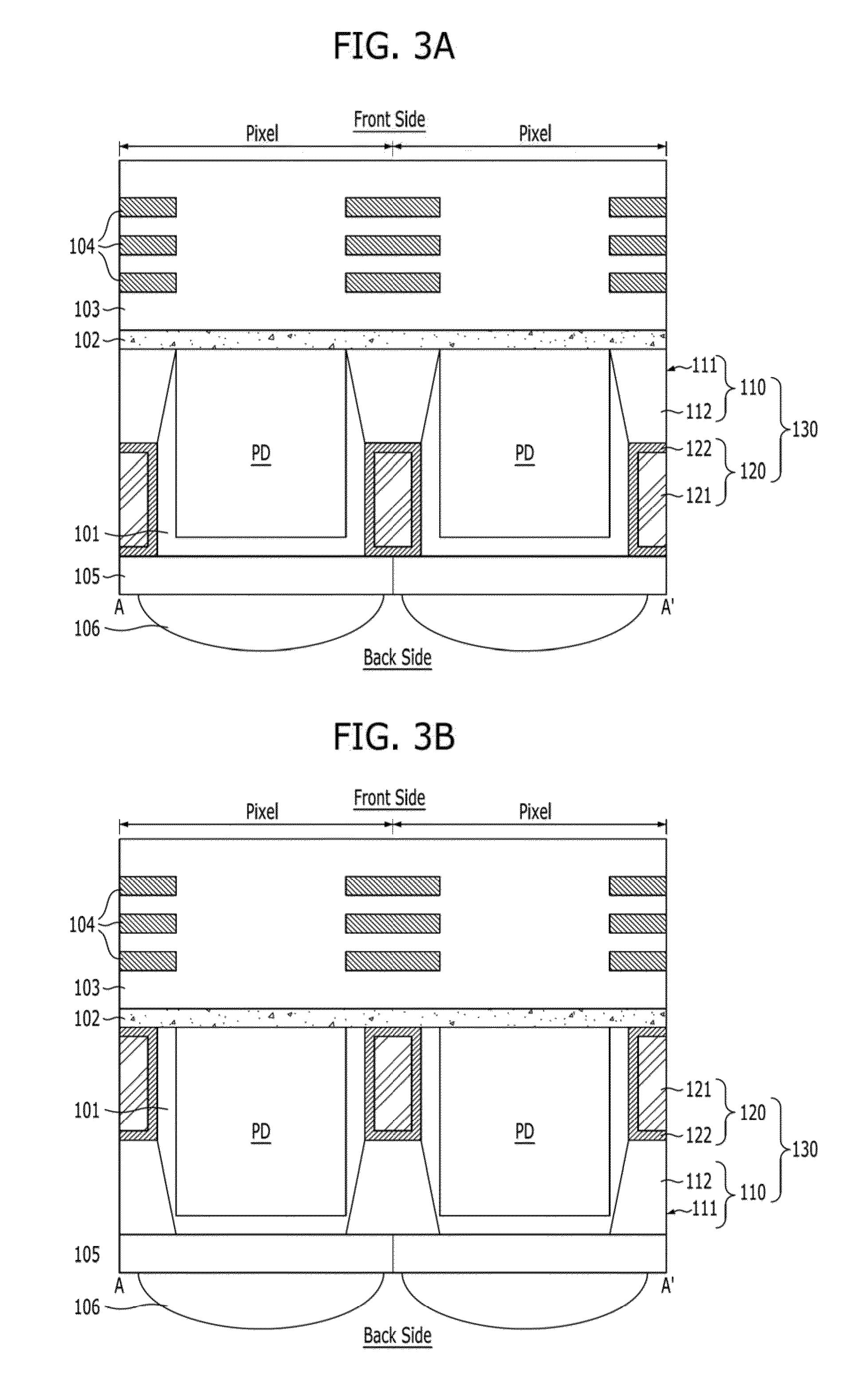

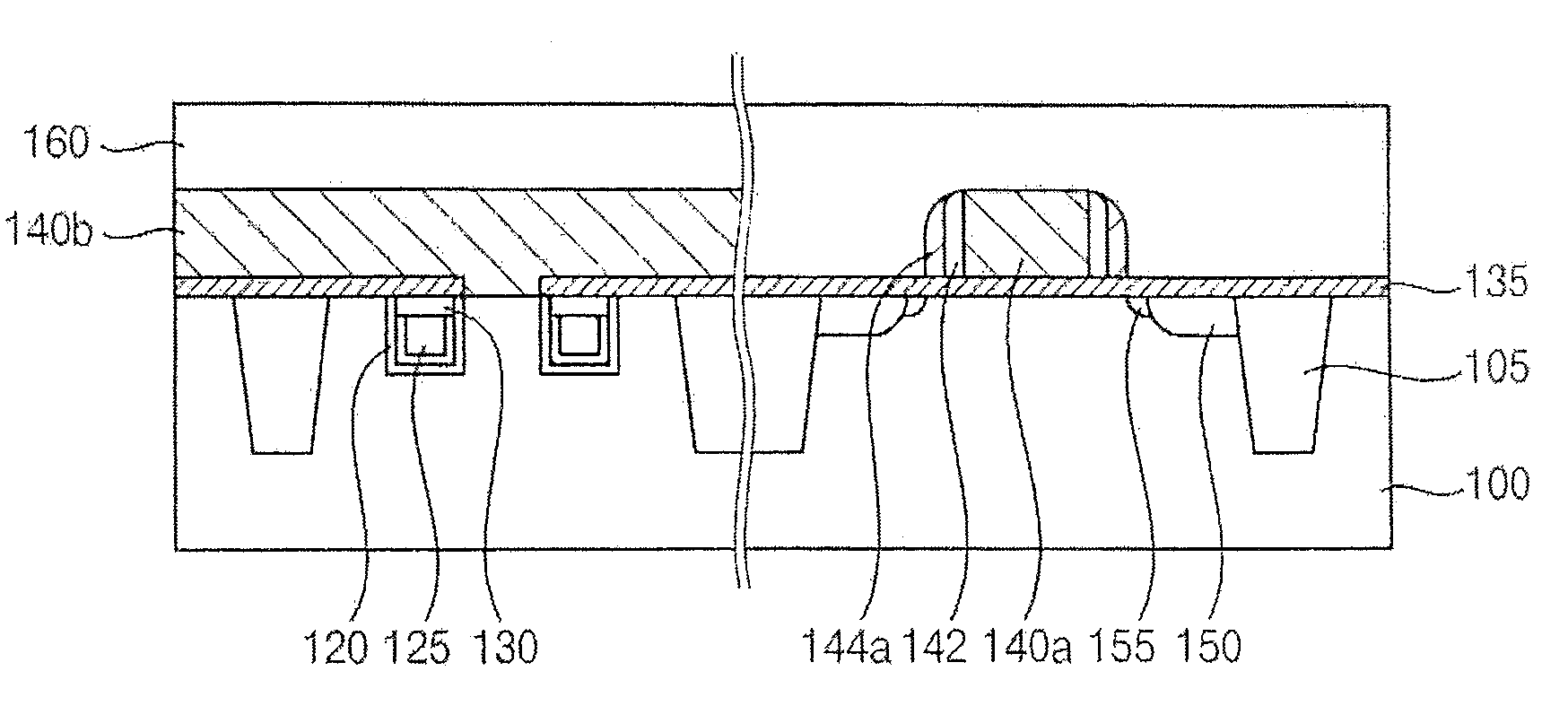

Isolation structure and method for forming the same, and image sensor including the isolation structure and method for fabricating the image sensor

ActiveUS20140353468A1Low refractive indexSolid-state devicesMaterial analysis by optical meansInsulation layerImpurity doping

An isolation structure and method of forming the same. The isolation structure includes a first isolation structure having including an insulation layer formed in a trench in a substrate and a second isolation structure, formed on the first isolation structure. The second isolation structure includes a first impurity region formed in the substrate, the first impurity region having a first impurity doping concentration, and a second impurity region that is formed around the first impurity region, the second impurity region having a second impurity doping concentration that is greater than the first doping concentration.

Owner:SK HYNIX INC

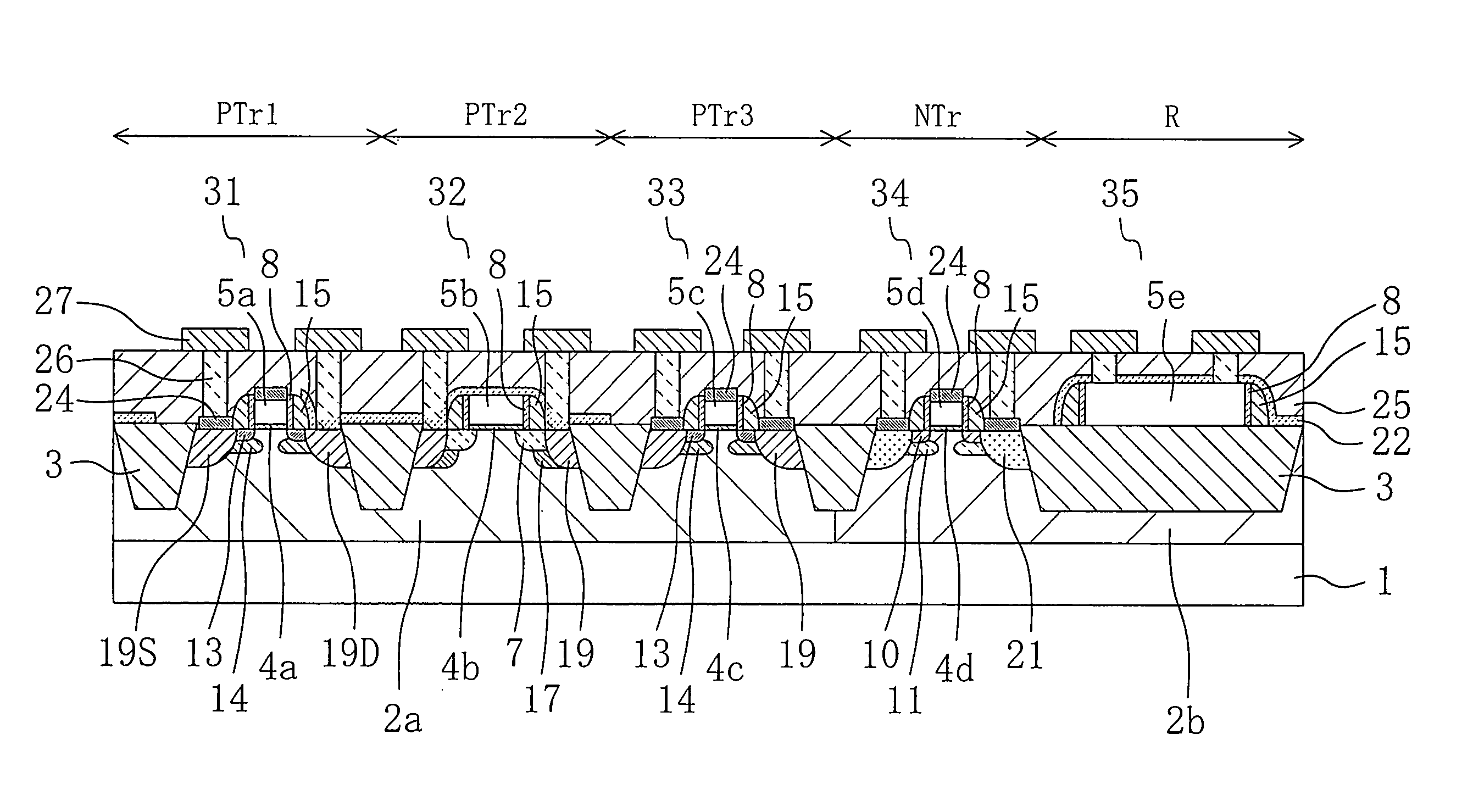

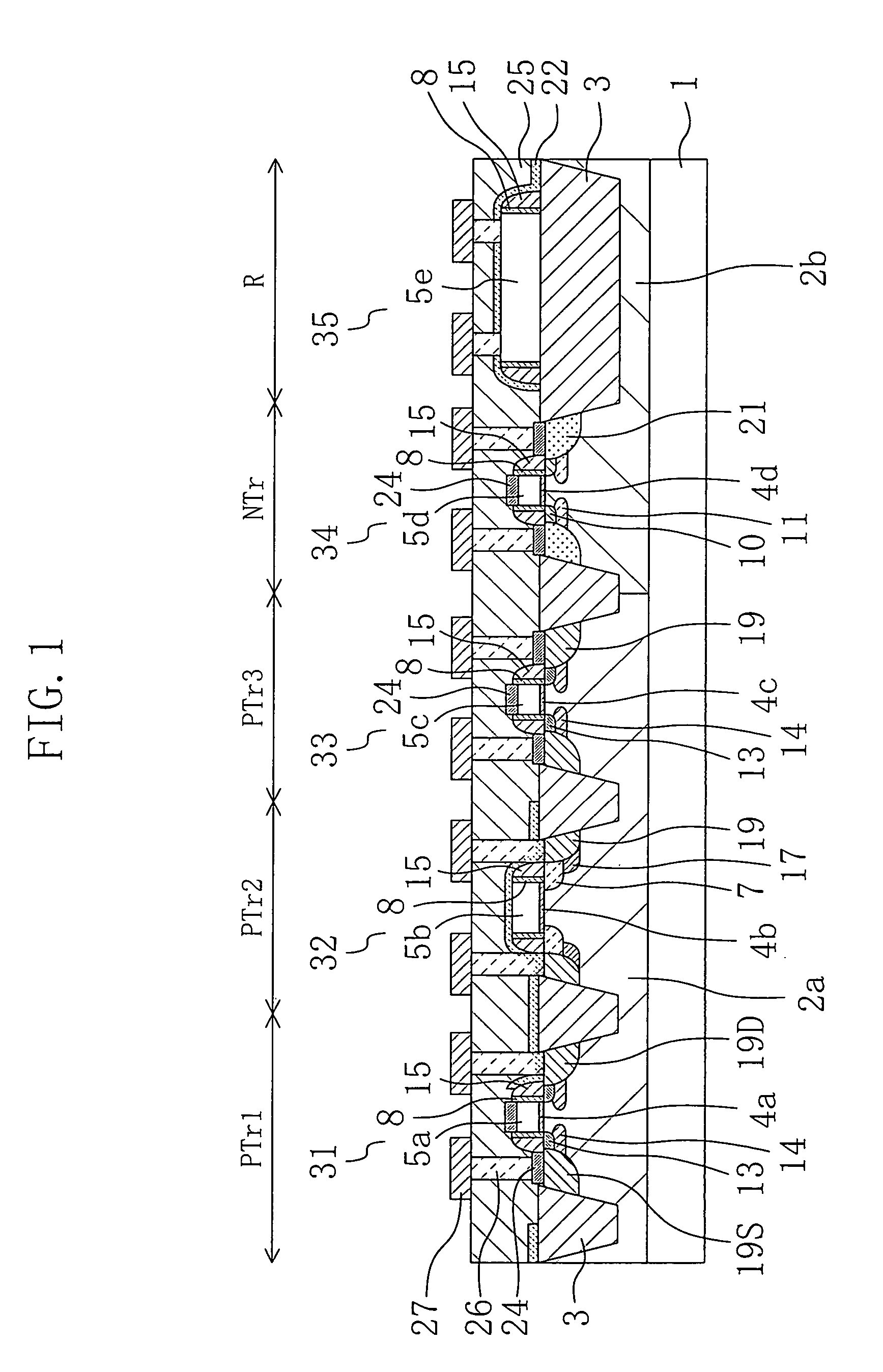

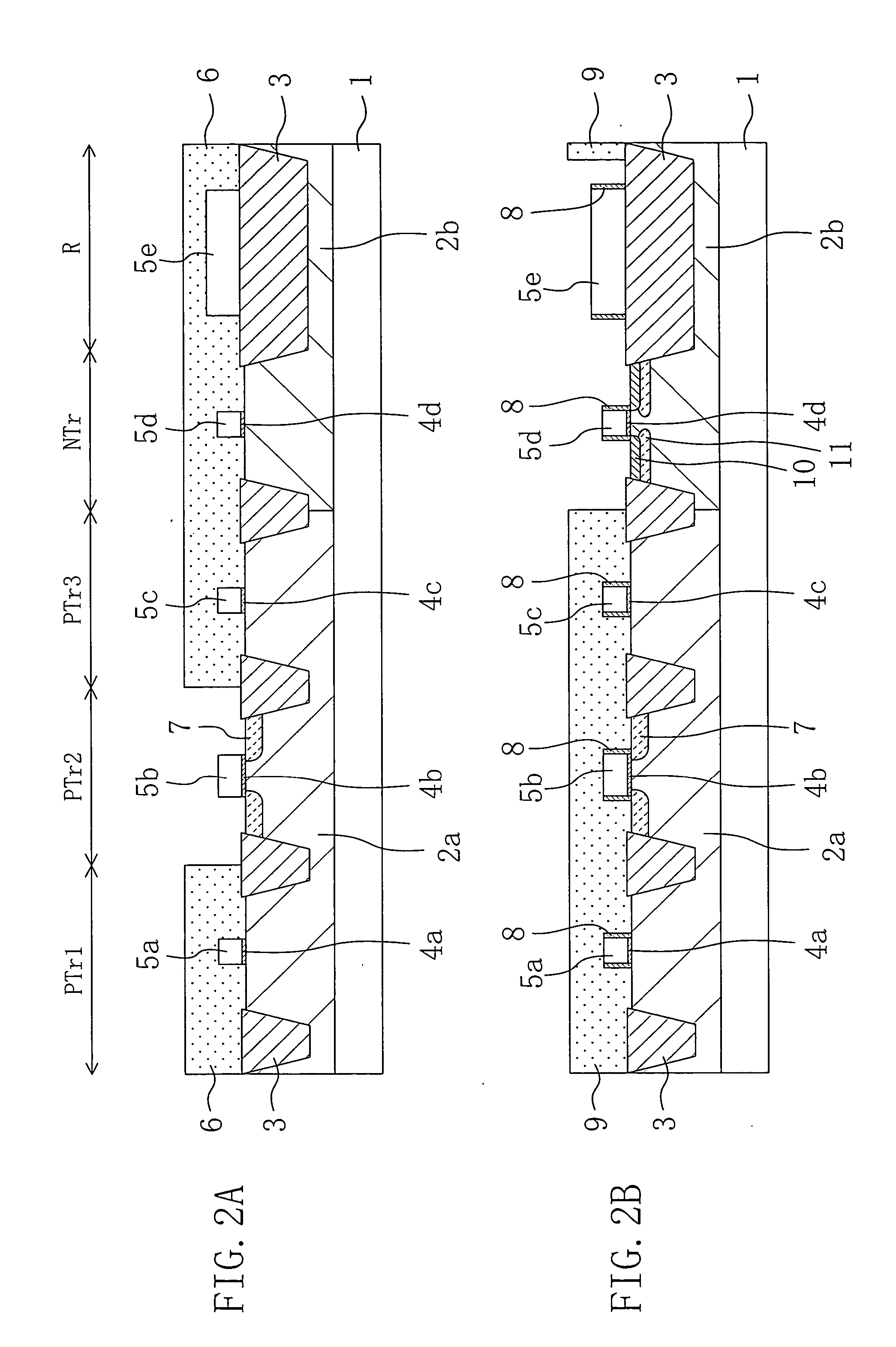

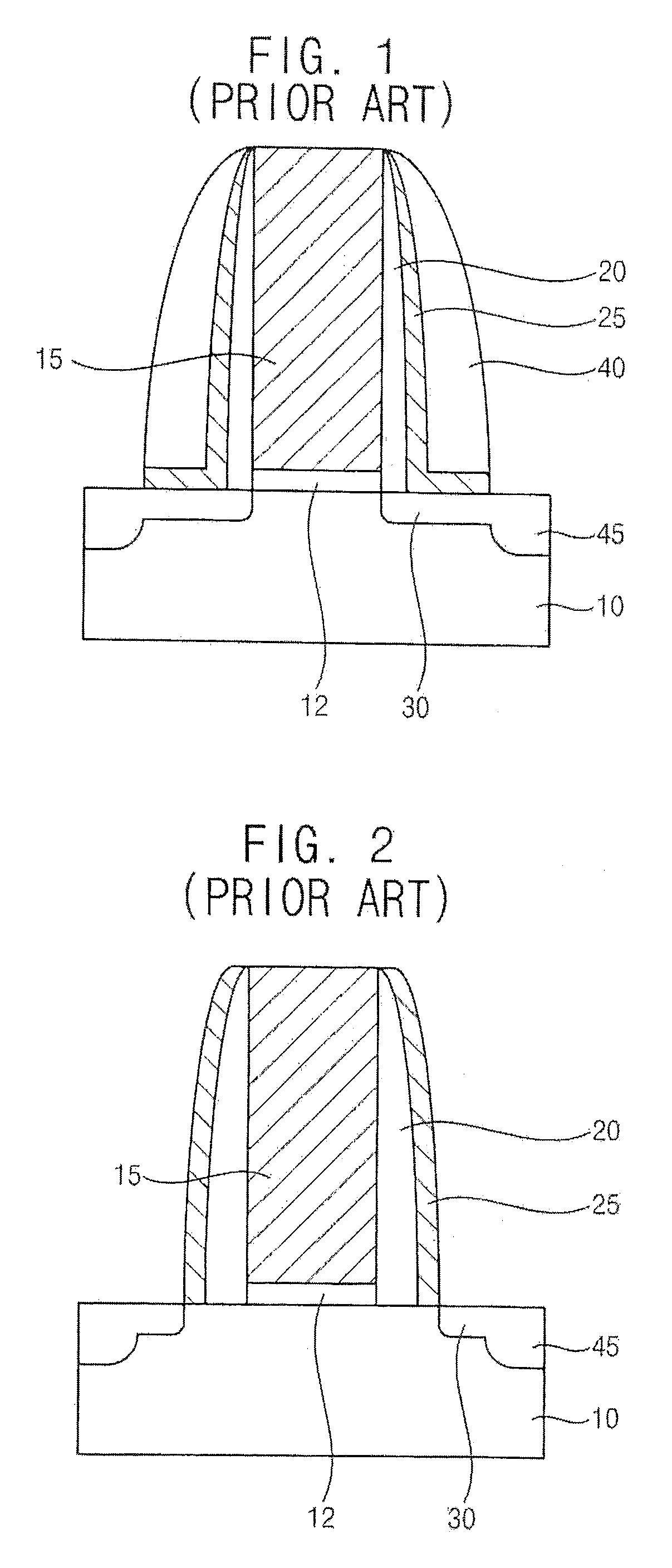

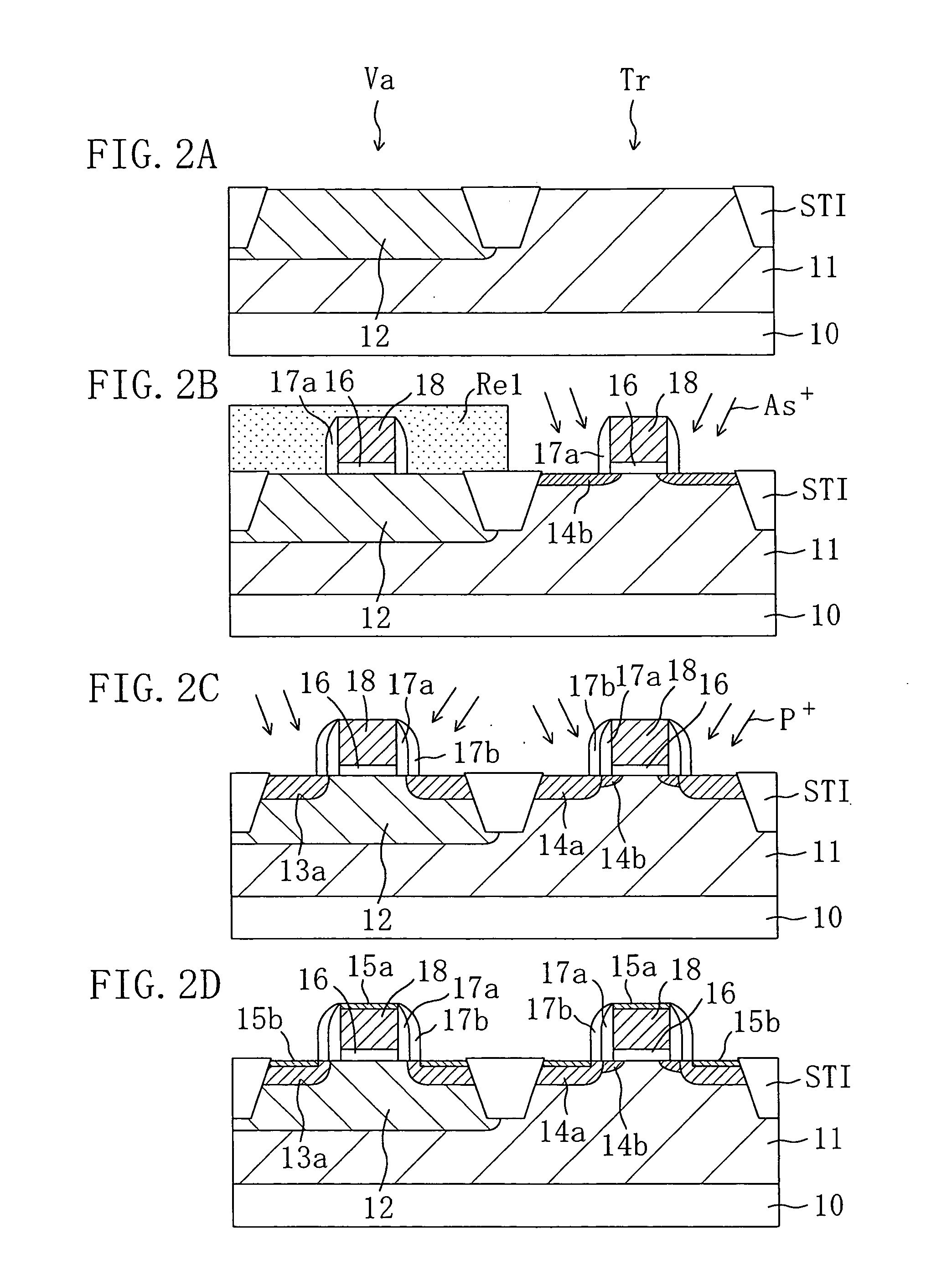

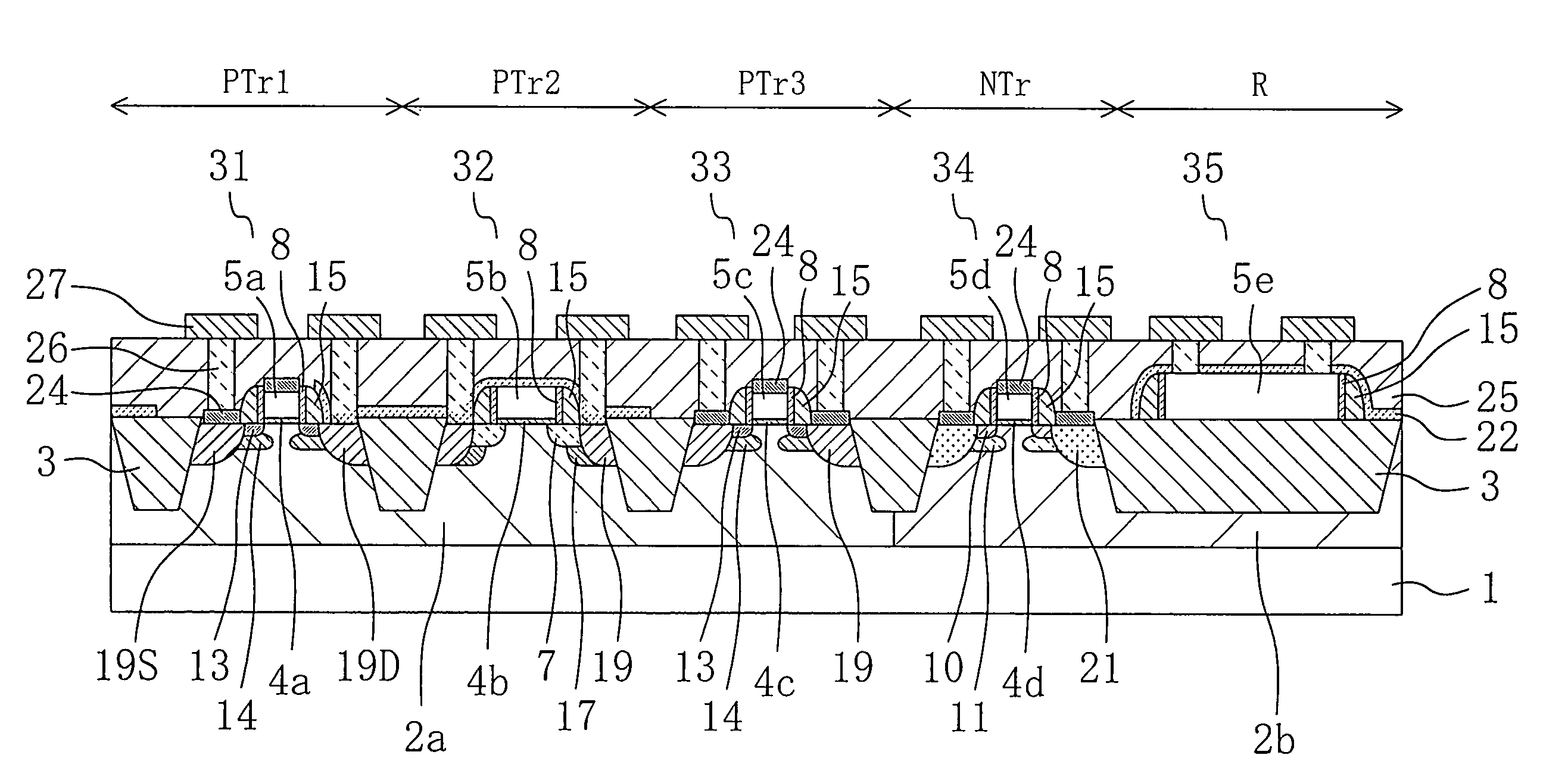

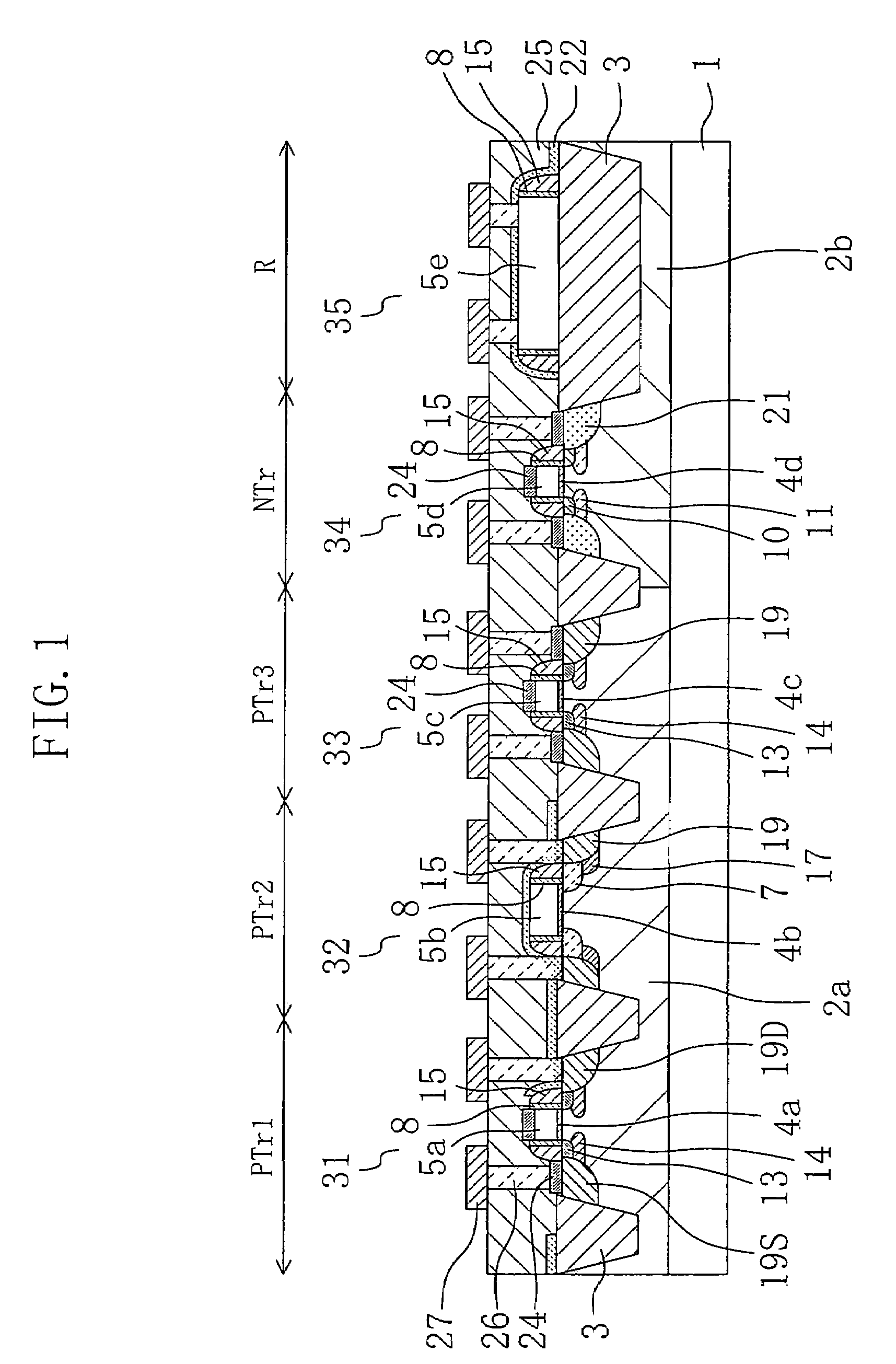

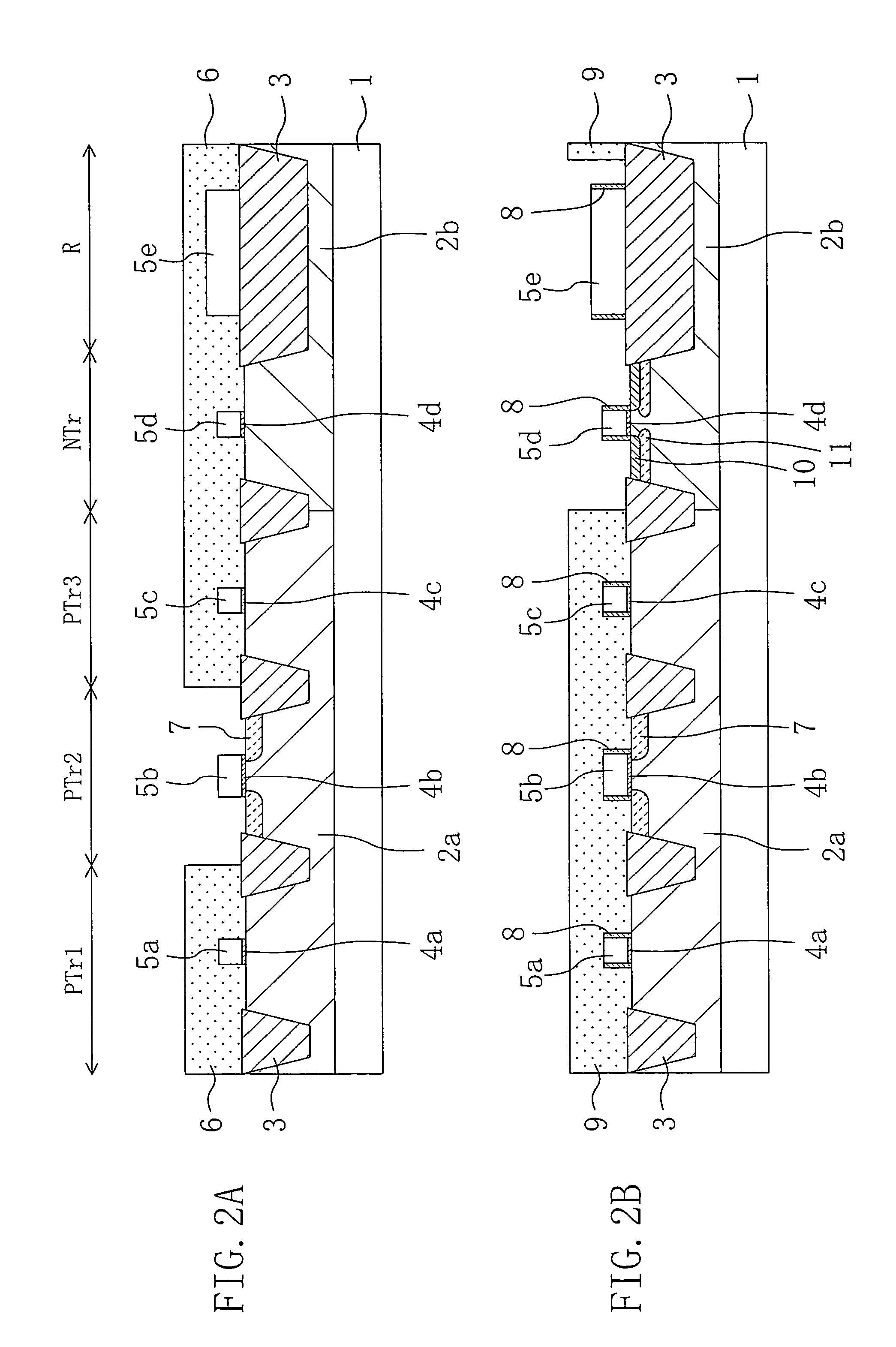

Semiconductor device and method for fabricating the same

ActiveUS20060017117A1The process steps are simpleAvoid failureTransistorSolid-state devicesElectrical resistance and conductanceDevice material

A semiconductor device includes a resistor element covered by a silicon oxide film. In the semiconductor device, with respective gate electrodes of MIS transistors and impurity doped layers, i.e., non-silicide regions exposed, thermal treatment for activating an impurity and silicidization are performed. Thus, auto-doping of an impurity is suppressed, so that variations in a resistance value of a resistor are suppressed. Also, the gate electrodes of the MIS transistors and the like are exposed when thermal treatment for activating an impurity, and therefore breakdown of respective gate insulation films of the MIS transistors hardly occurs.

Owner:GK BRIDGE 1

Method of Manufacturing Semiconductor Device

ActiveUS20110124173A1Improve electric characteristicExcellent electrical propertiesTransistorSolid-state devicesSemiconductorSemiconductor device

Methods of manufacturing a semiconductor device include forming a gate electrode on a semiconductor substrate, forming spacers on side walls of the gate electrode, and doping impurities into the semiconductor substrate on both sides of the spacers to form highly doped impurity regions. The spacers are selectively etched to expose portions of the semiconductor substrate, and more lightly doped impurity regions are formed in the semiconductor substrate between the highly doped impurity regions and the gate electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

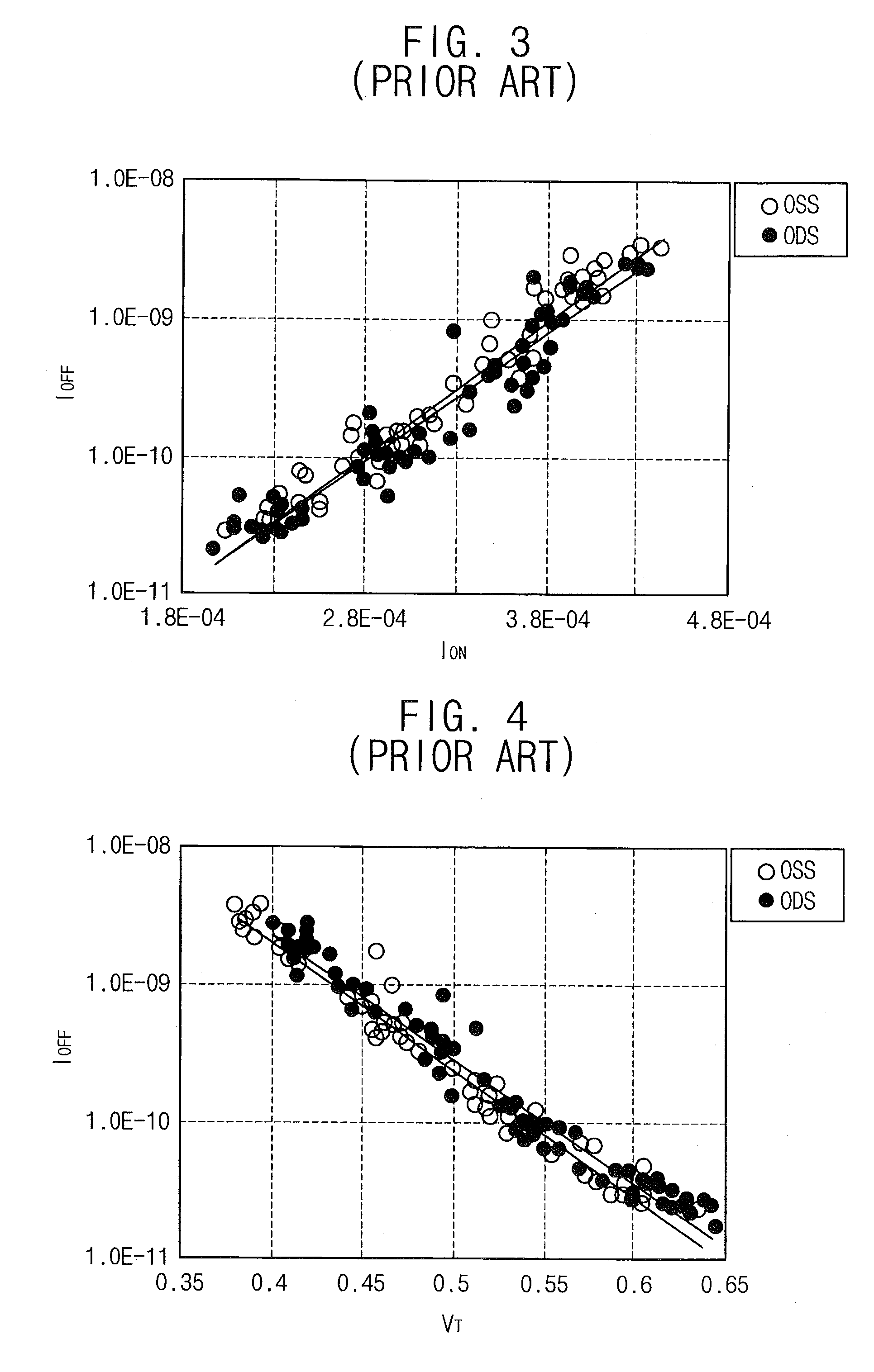

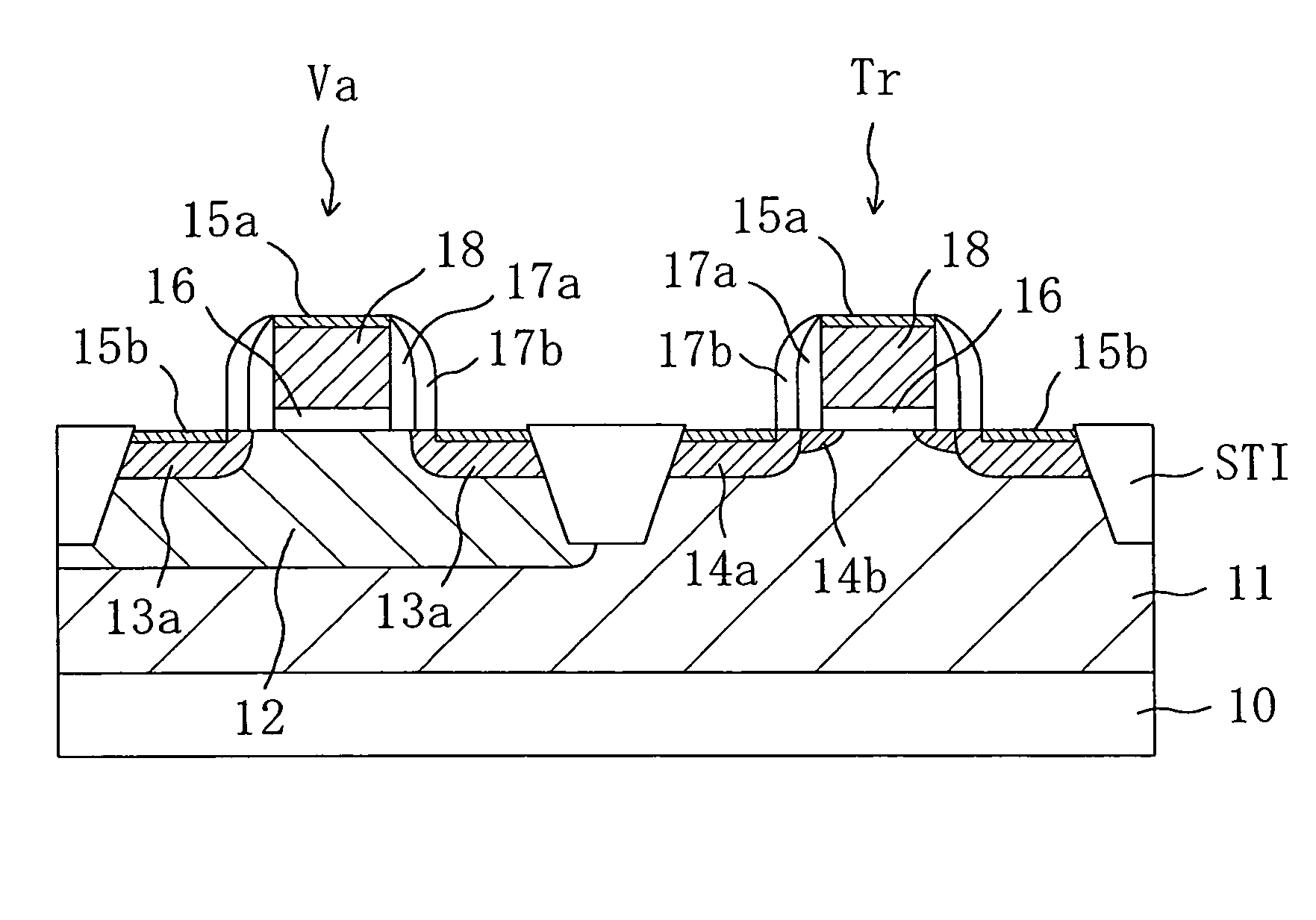

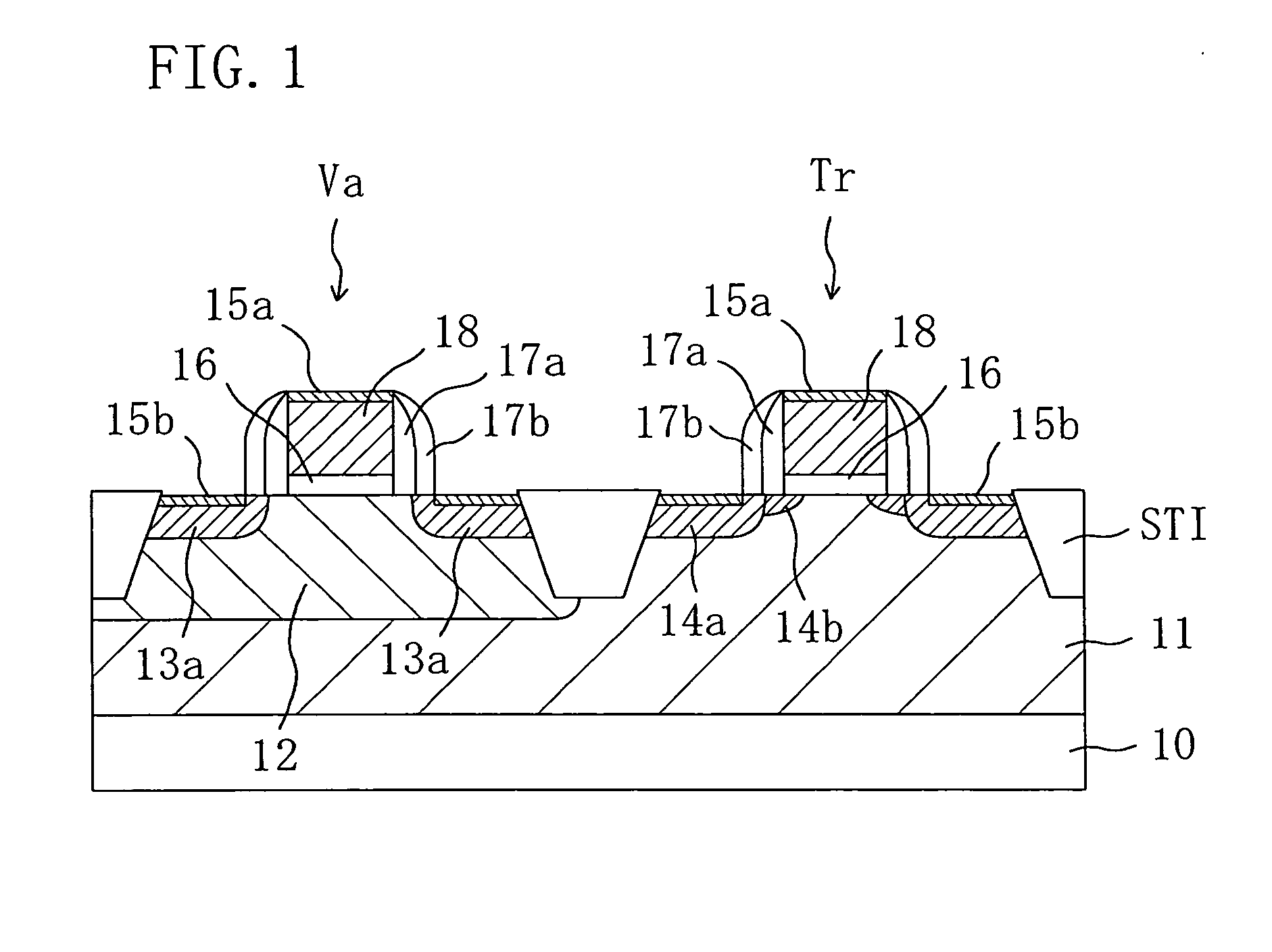

Semiconductor device and method for fabricating the same

ActiveUS20050045888A1Range of depletionVariable capacitance range can be kept wide enoughTransistorSolid-state devicesHigh concentrationImpurity diffusion

A semiconductor device comprises varactor regions Va and transistor regions Tr. An active region for a varactor is formed with a substrate contact impurity diffusion region obtained by doping an N well region with N-type impurity at a relatively high concentration. However, any extension region (or LDD region) as in a varactor of a known semiconductor device is not formed in the active region for a varactor. On the other hand, parts of a P well region located to both sides of the polysilicon gate electrode in the transistor region Tr are formed with high-concentration source / drain regions and extension regions. Therefore, the extendable range of a depletion layer is kept wide to extend the capacitance variable range of the varactor.

Owner:GK BRIDGE 1

Semiconductor device with floating trap type nonvolatile memory cell and method for manufacturing the same

ActiveUS7045850B2Reduce processing timeSlow changeSolid-state devicesSemiconductor/solid-state device manufacturingImpurity dopingTriple layer

The present invention discloses a semiconductor device having a floating trap type nonvolatile memory cell and a method for manufacturing the same. The method includes providing a semiconductor substrate having a nonvolatile memory region, a first region, and a second region. A triple layer composed of a tunnel oxide layer, a charge storing layer and a first deposited oxide layer on the semiconductor substrate is formed sequentially The triple layer on the semiconductor substrate except the nonvolatile memory region is then removed. A second deposited oxide layer is formed on an entire surface of the semiconductor substrate including the first and second regions from which the triple layer is removed. The second deposited oxide layer on the second region is removed, and a first thermal oxide layer is formed on the entire surface of the semiconductor substrate including the second region from which the second deposited oxide layer is removed. The semiconductor device can be manufactured according to the present invention to have a reduced processing time and a reduced change of impurity doping profile. The thickness of a blocking oxide layer and a high voltage gate oxide layer can be controlled.

Owner:SAMSUNG ELECTRONICS CO LTD

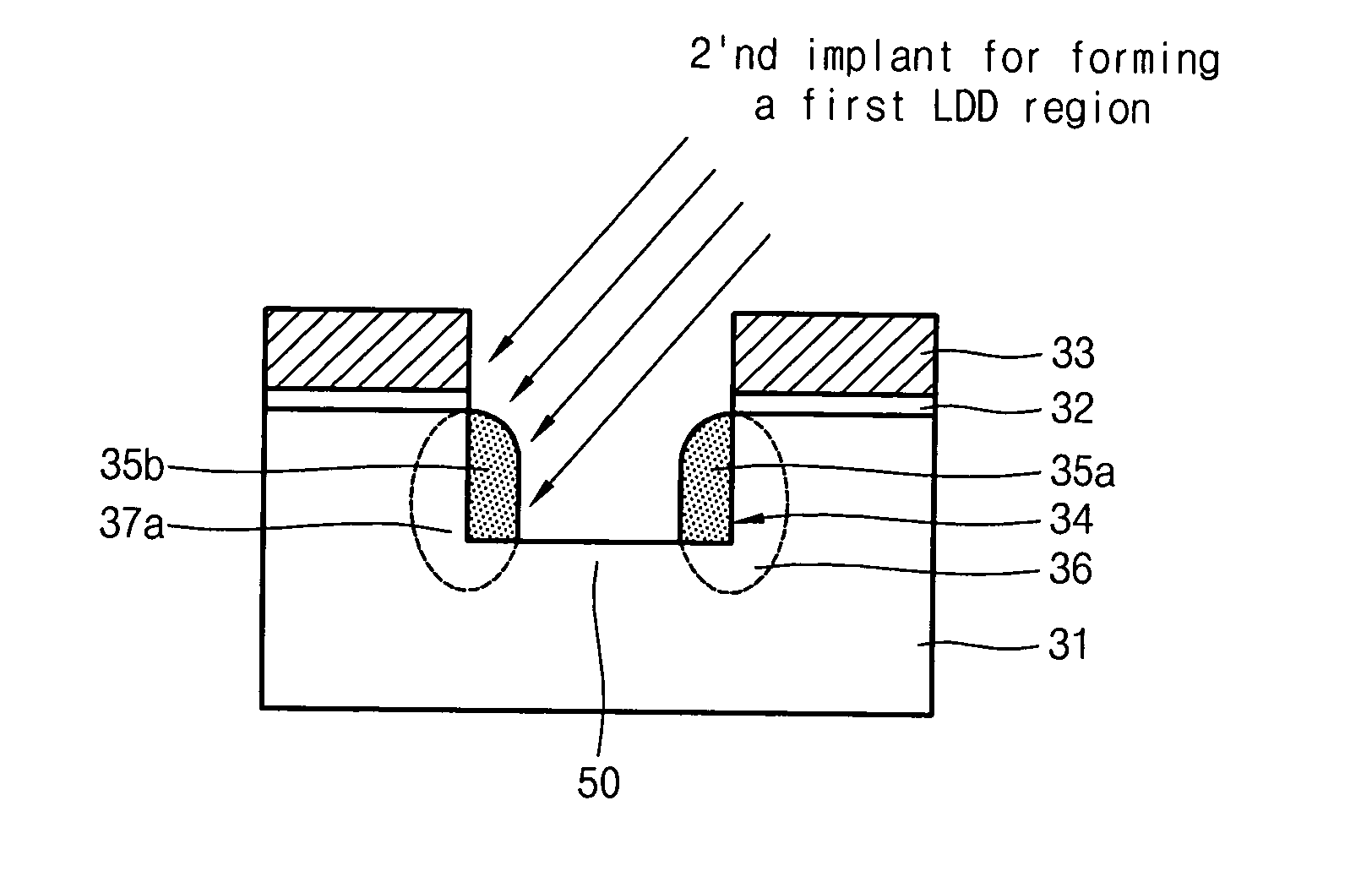

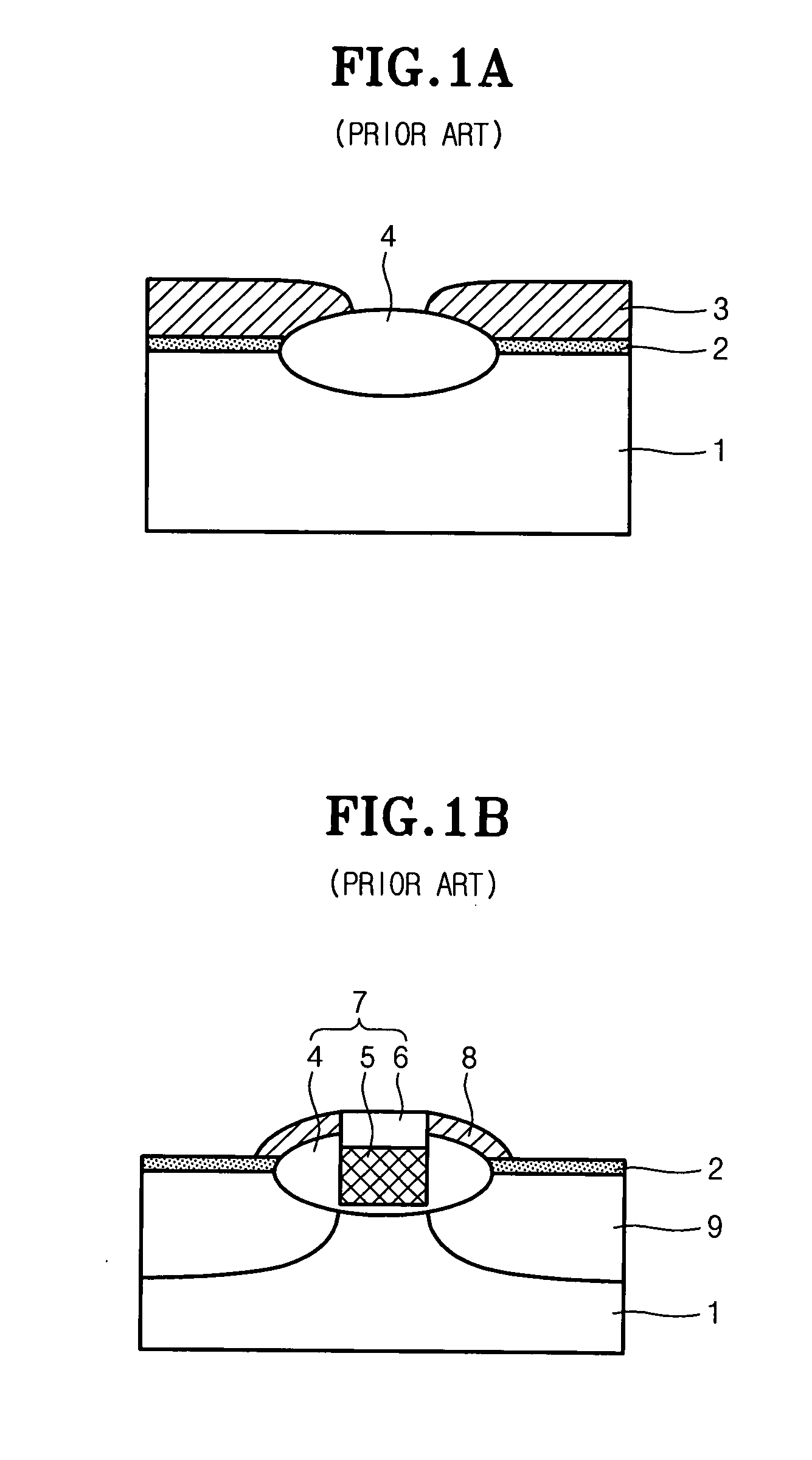

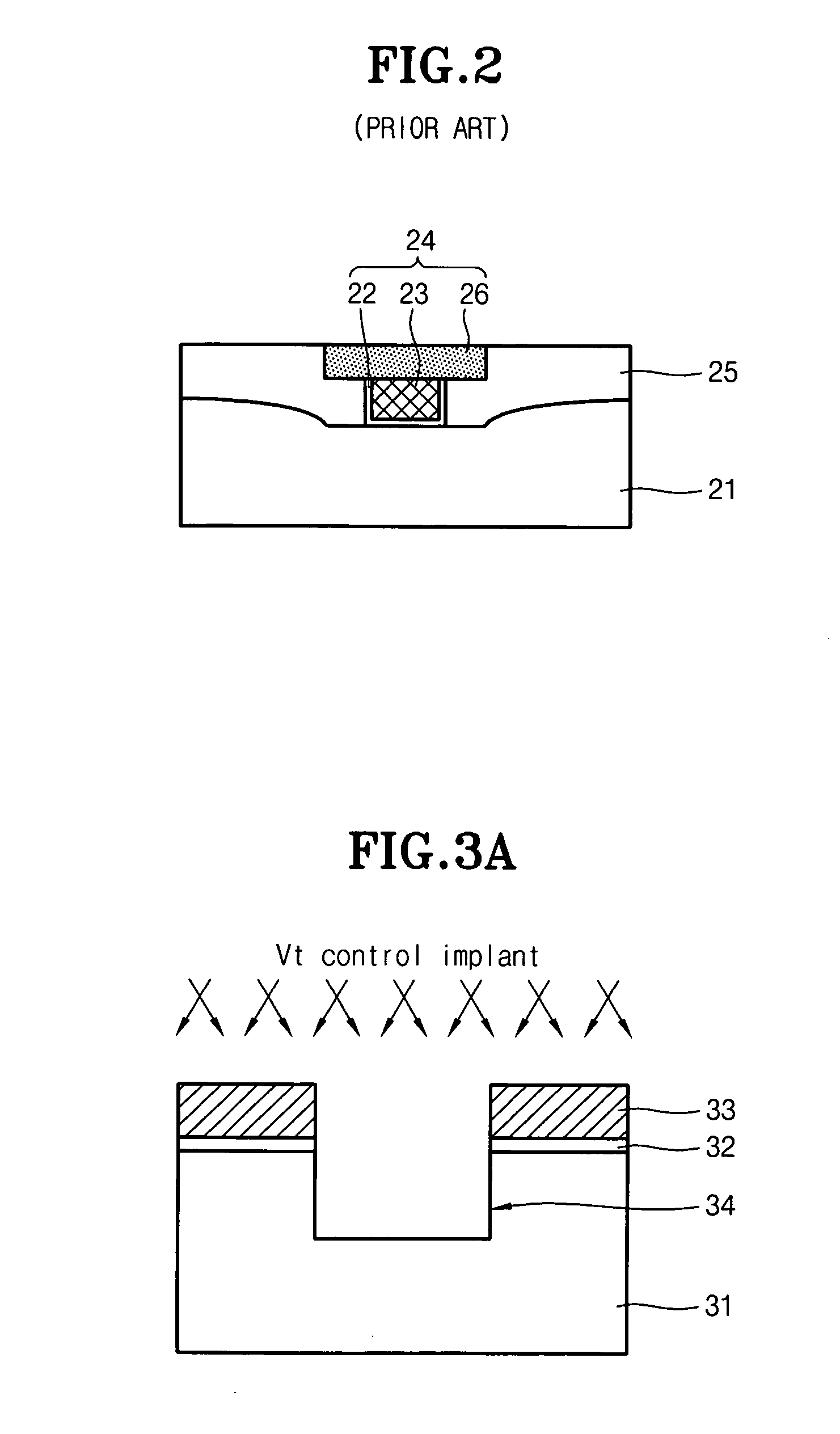

Semiconductor device having a recess gate for improved reliability

ActiveUS20070004126A1Suppression of short channel effectsReduce parasitic series resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesImpurity dopingDevice material

A semiconductor device having a recess gate is formed by first forming a recess below the upper surface of the substrate. A spacer is formed at each sidewall of the recess. An impurity doping area is formed in a source area. A first LDD area is formed in a drain area. A gate comprising a gate insulating layer and a gate conductive layer is then formed in the recess. A second LDD area is formed on the upper surface of the semiconductor substrate. A gate spacer is formed at each sidewall of the gate. Then a source / drain area having an asymmetrical structure is formed on each side of the gate.

Owner:SK HYNIX INC

Semiconductor device and method for fabricating the same

Owner:GK BRIDGE 1

A method for preparing high-purity low-sulfur expanded graphite

InactiveCN102286753ANo pollution in the processNo dopingElectrolysis componentsElectrolysisPolypropylene mesh

The invention discloses a method for preparing high-purity low-sulfur expanded graphite, which belongs to the preparation method of expanded graphite. The existing chemical method of the present invention to prepare expanded graphite has the technical problems of low product purity and high production cost. The method of the present invention: 1. high-temperature purification of phosphorus flake graphite; 2. putting it into a polypropylene mesh bag, soaking it in peroxide water, and lifting it to pour water; 3. wrapping the graphite block with a polypropylene mesh bag as an anode, and putting In the graphite electrolytic cell, then inject the electrolyte solution, use graphite as the cathode, and then electrolyze. During the electrolysis process, the polypropylene mesh bag is inflated and stirred; 4. Constant temperature drying and expansion; that is, high-purity low-sulfur expanded graphite is obtained. The method of the invention is simple and easy to operate, and the degree of intercalation can be controlled by adjusting the current intensity and electrolysis time, and the prepared high-purity expanded graphite is low in sulfur, and there is no pollution to the water body during the washing process, and no other impurities are doped in the product. The invention uses a small amount of oxidant to trigger, little or almost no pollution in production, and relatively low production cost.

Owner:HEILONGJIANG UNIVERSITY OF SCIENCE AND TECHNOLOGY