Patents

Literature

928results about "Diffusion/doping" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Conductor treating single-wafer type treating device and method for semi-conductor treating

InactiveUS7235137B2High processing temperatureLiquid surface applicatorsDecorative surface effectsElectrical conductorEngineering

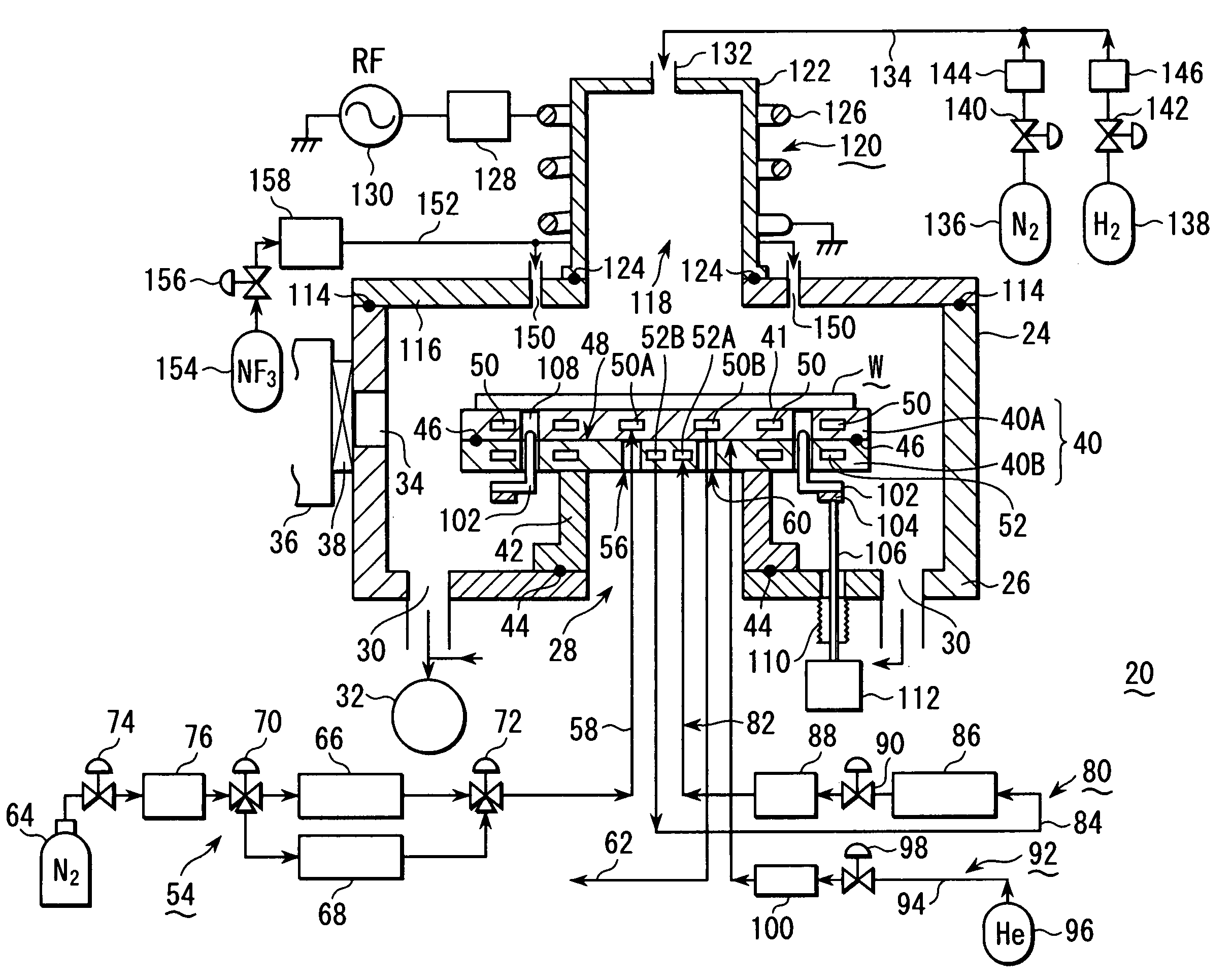

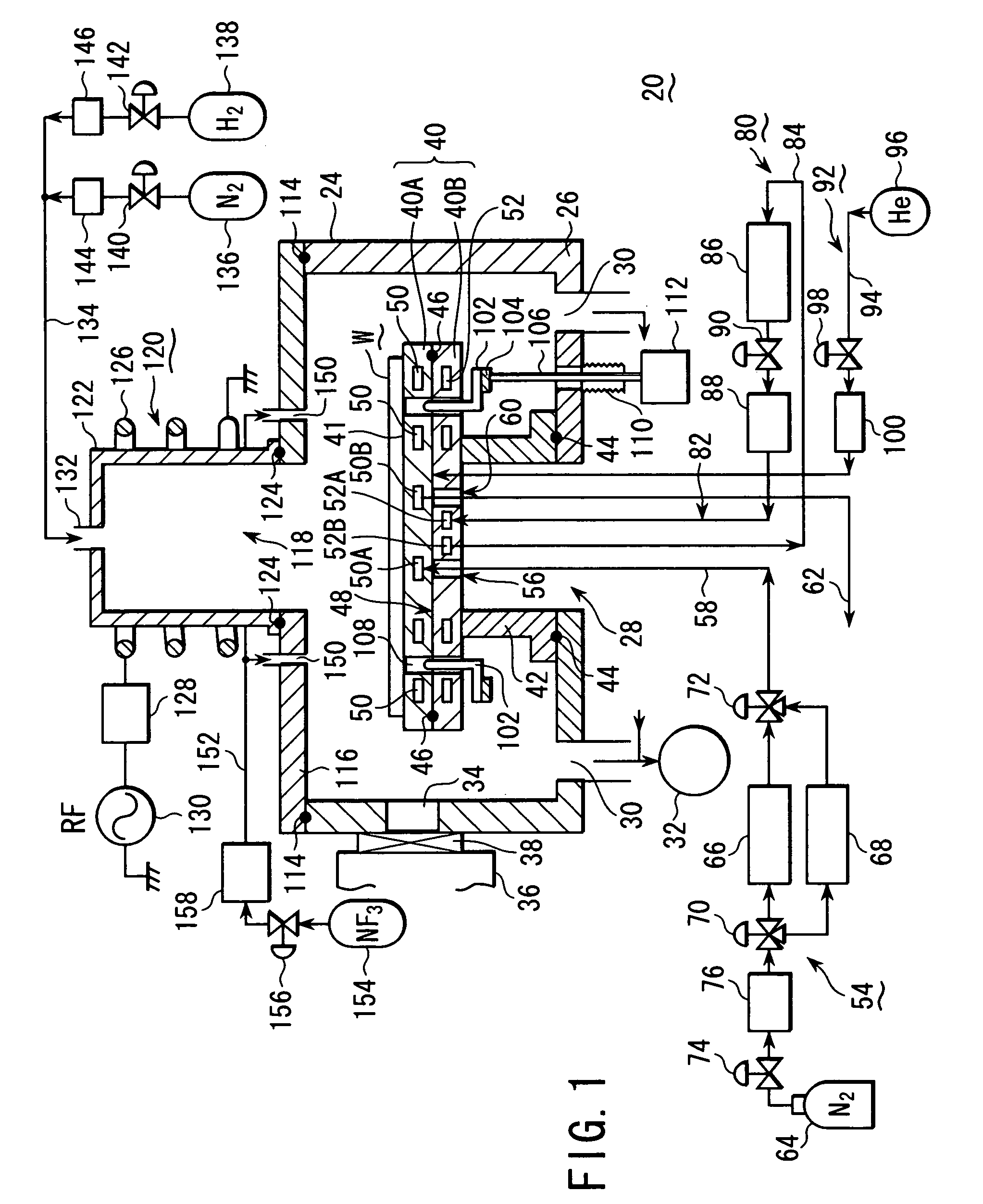

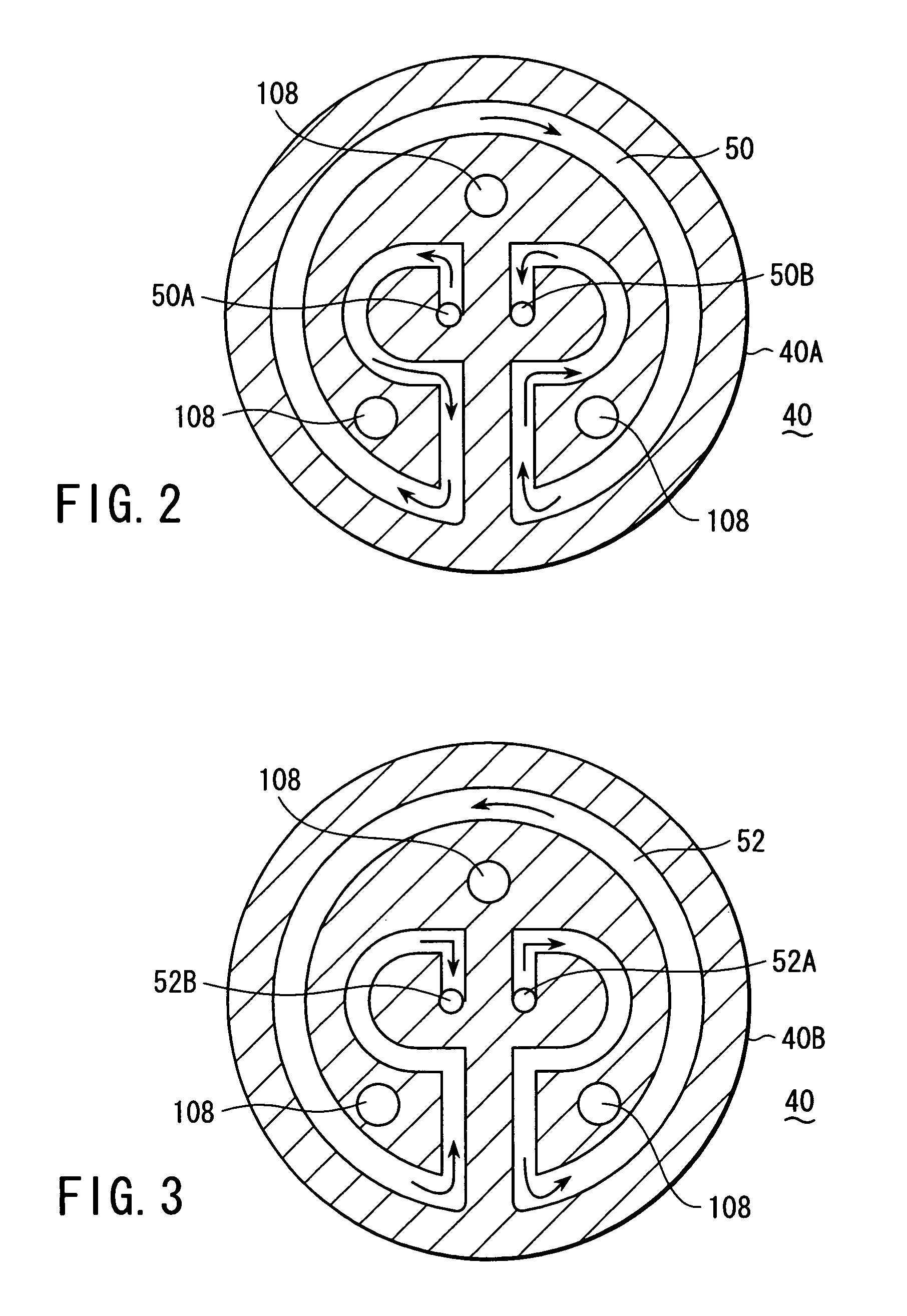

A single-substrate processing apparatus (20) has a worktable (40) disposed in a process chamber (24), which accommodates a target substrate (W). The worktable (40) has a thermally conductive mount surface (41) to place the target substrate (W) thereon. The worktable (40) is provided with a flow passage (50) formed therein, in which a thermal medium flows for adjusting temperature of the target substrate (W) through the mount surface (41). The flow passage (50) is connected to a thermal medium supply system (54), which selectively supplies a cooling medium and a heating medium.

Owner:TOKYO ELECTRON LTD

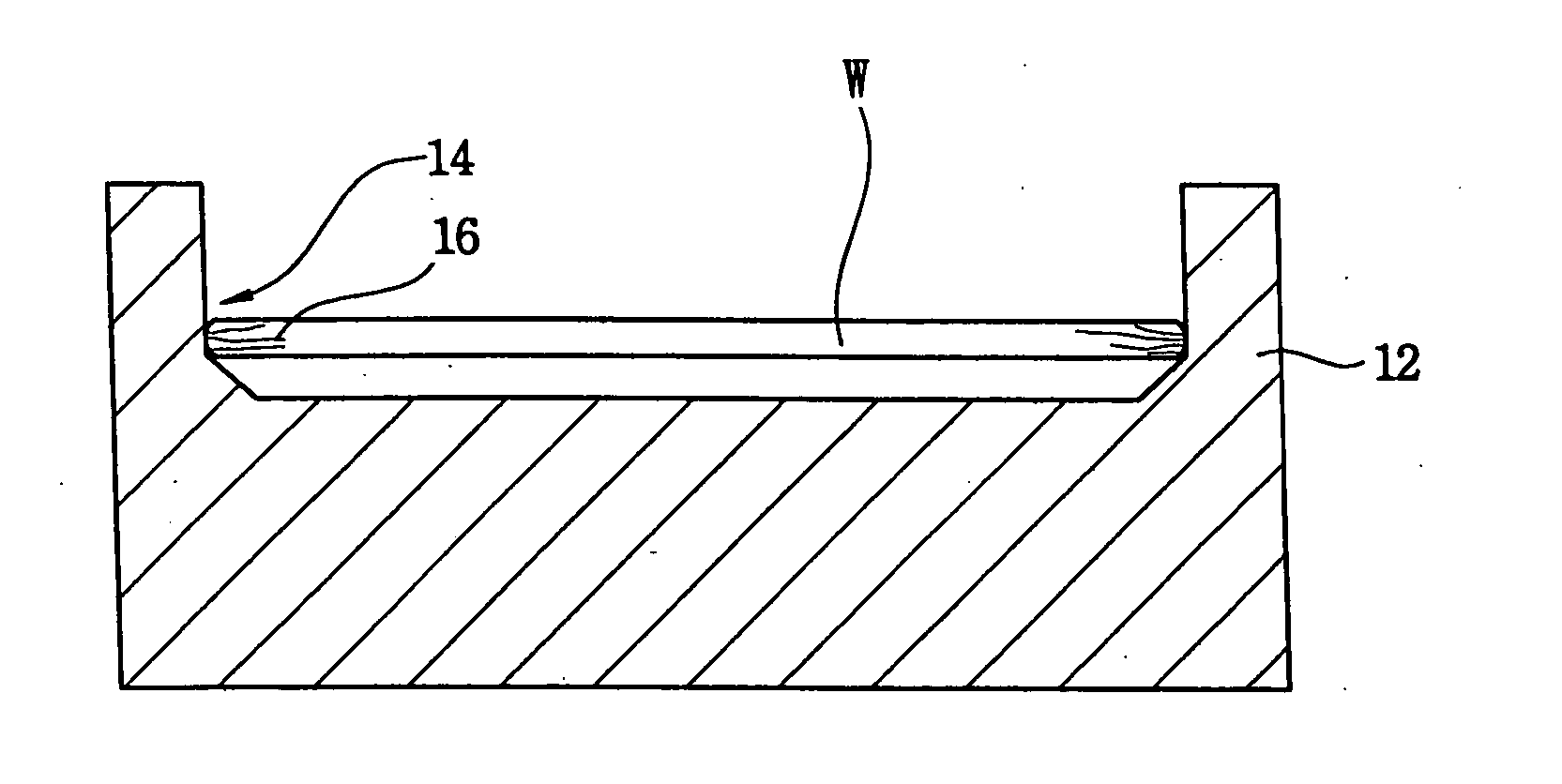

Heat treatment jig for semiconductor substrate

ActiveUS7329947B2Reduce stressSlips can be suppressed from occurringSemiconductor/solid-state device detailsCharge supportsSemiconductorSilicon

Owner:SUMITOMO MITSUBISHI SILICON CORP

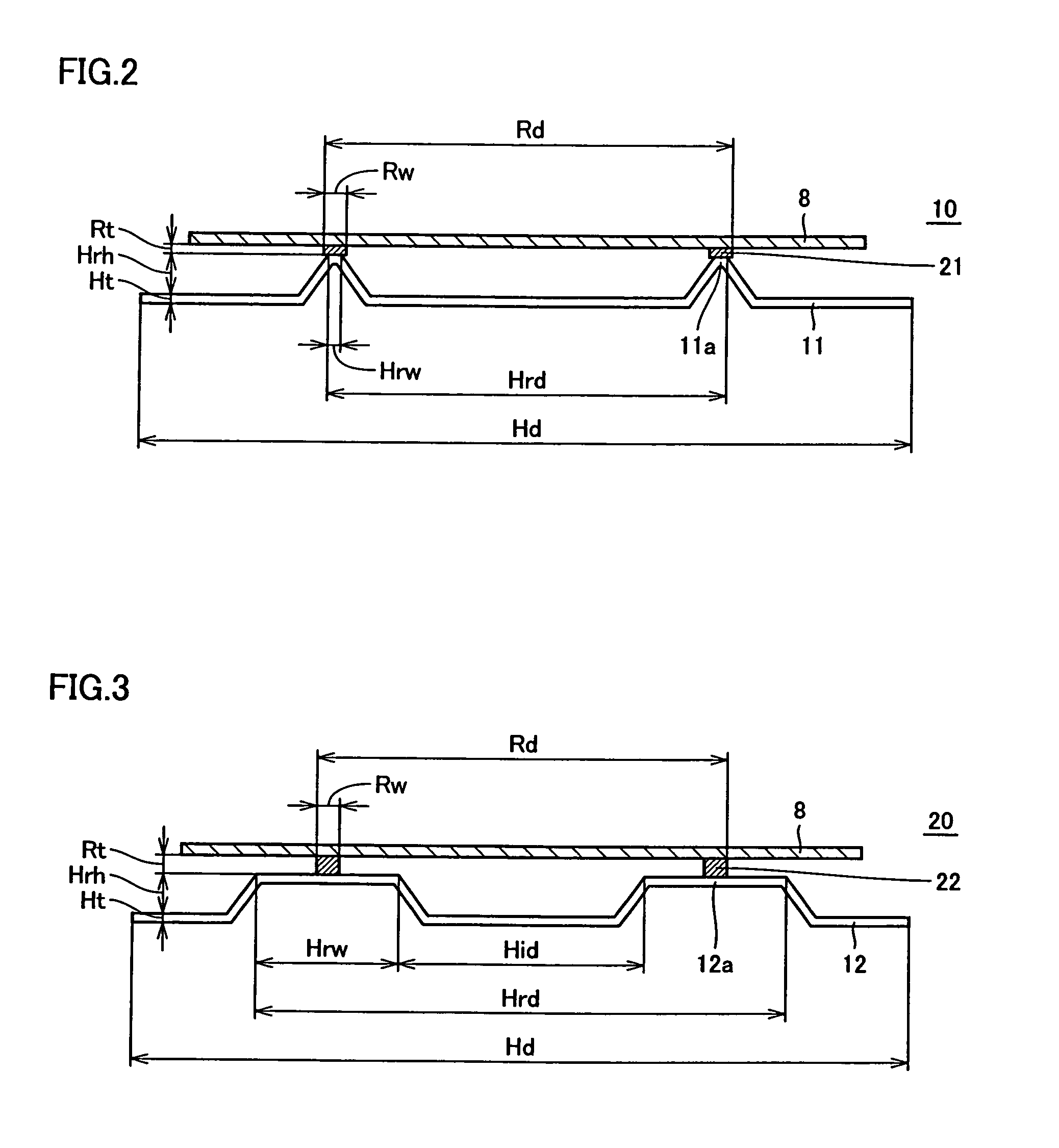

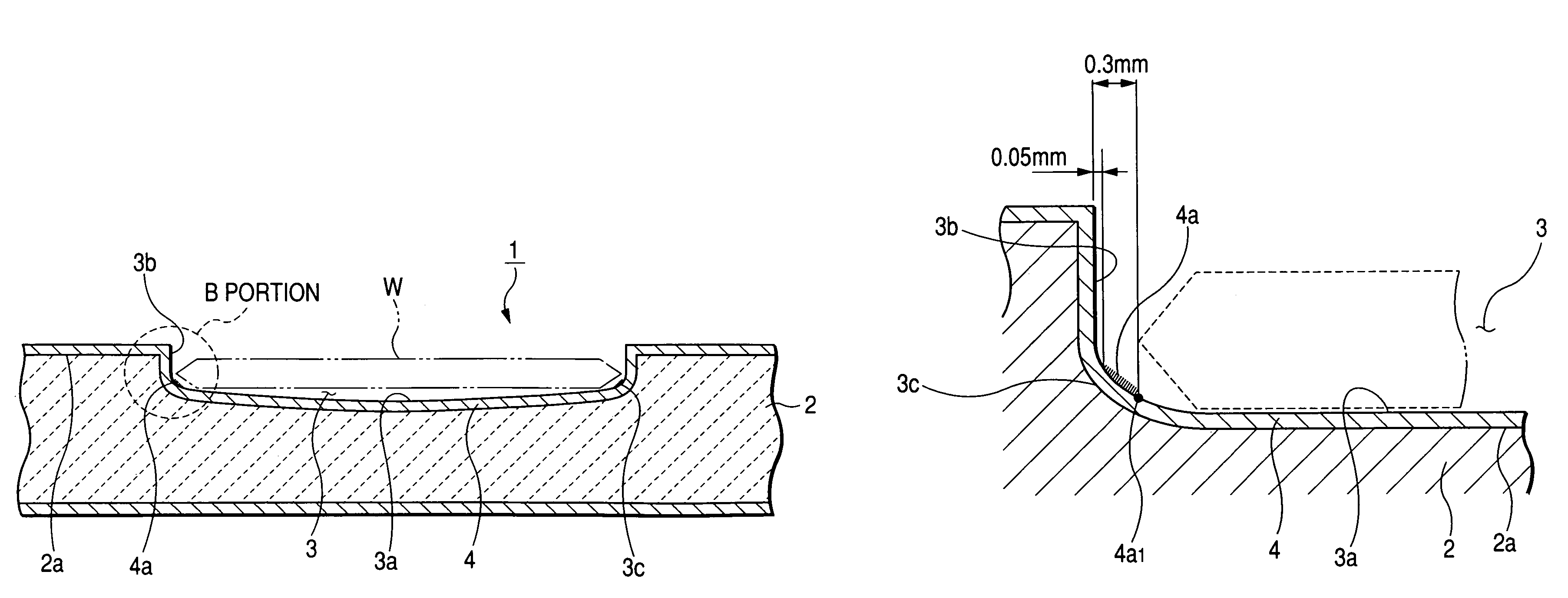

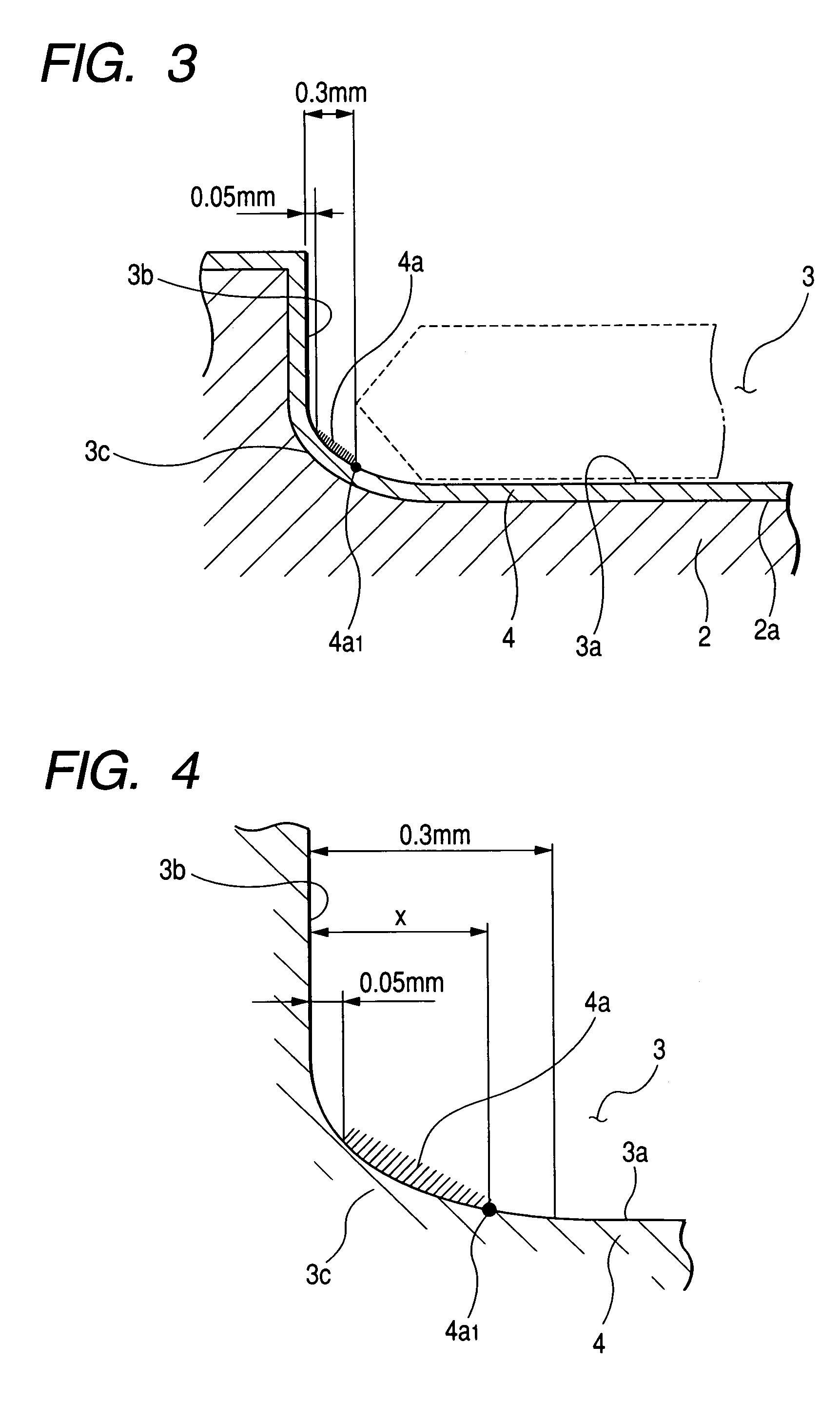

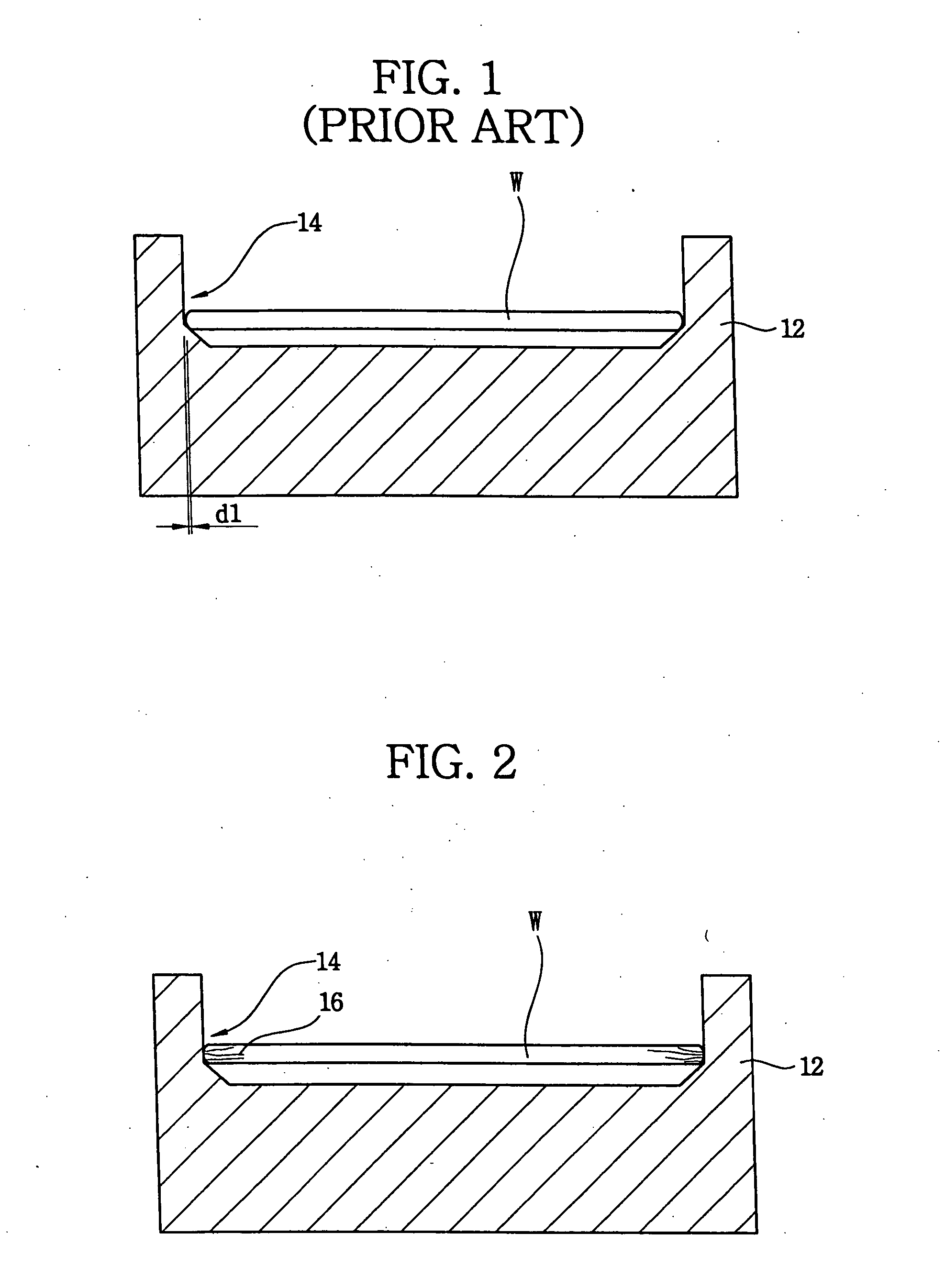

Susceptor

ActiveUS7393418B2Stably holdUnified performanceLiquid surface applicatorsDiffusion/dopingSusceptorSurface roughness

A susceptor at least a surface thereof being coated with SiC, includes a recess where an wafer is mounted, the recess having an round portion disposed on a lower portion of an outer circumferential portion of the recess, a ring-shaped SiC crystal growth surface portion provided within the round portion in a range of 0.05 mm or more and 0.3 mm or less defined from an outer circumference vertical portion of the recess and a contact portion, where the susceptor contacts with the wafer on the recess, having a surface roughness Ra in a range of 0.5 μm or more and 3 μm or less.

Owner:COORSTEK INC

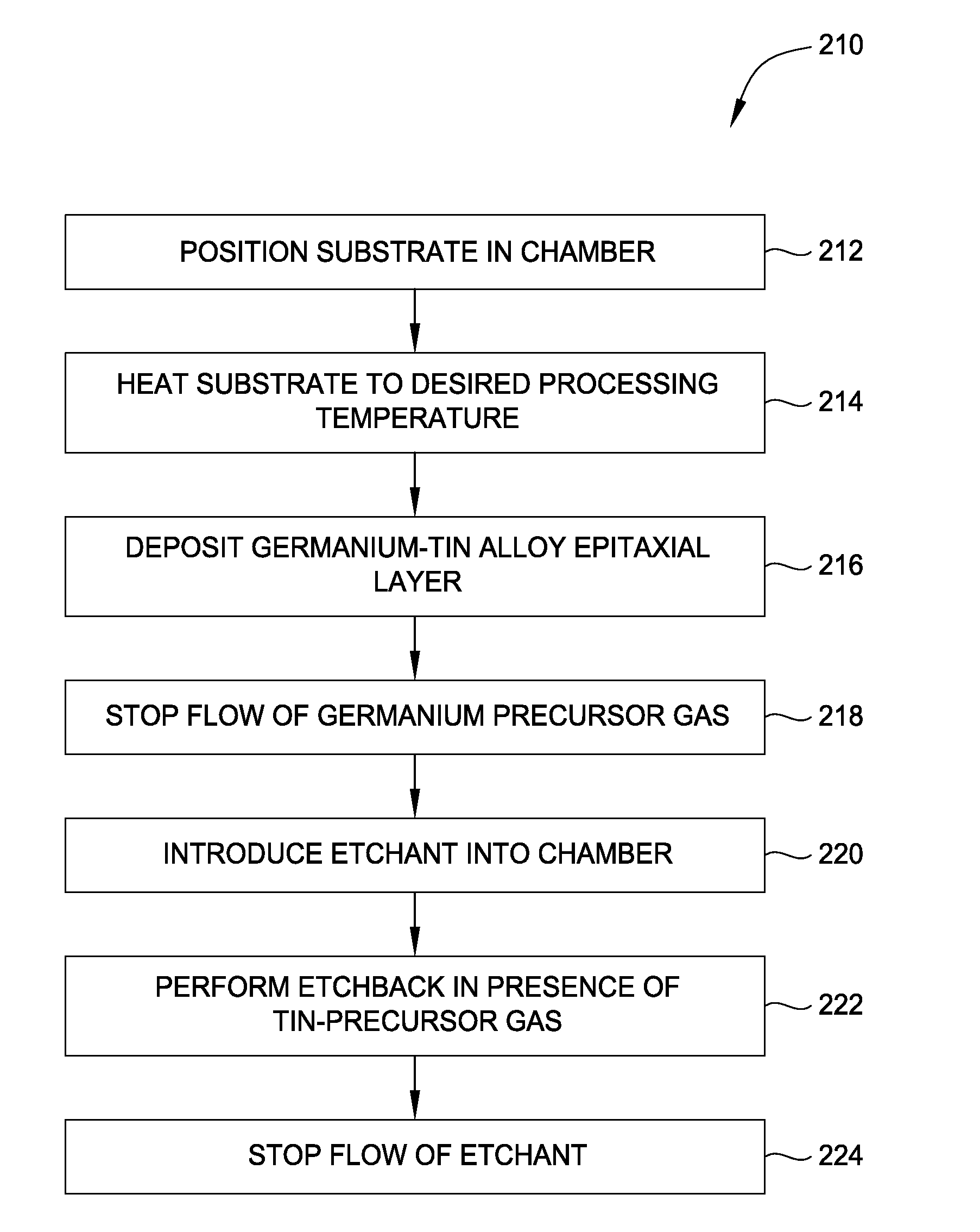

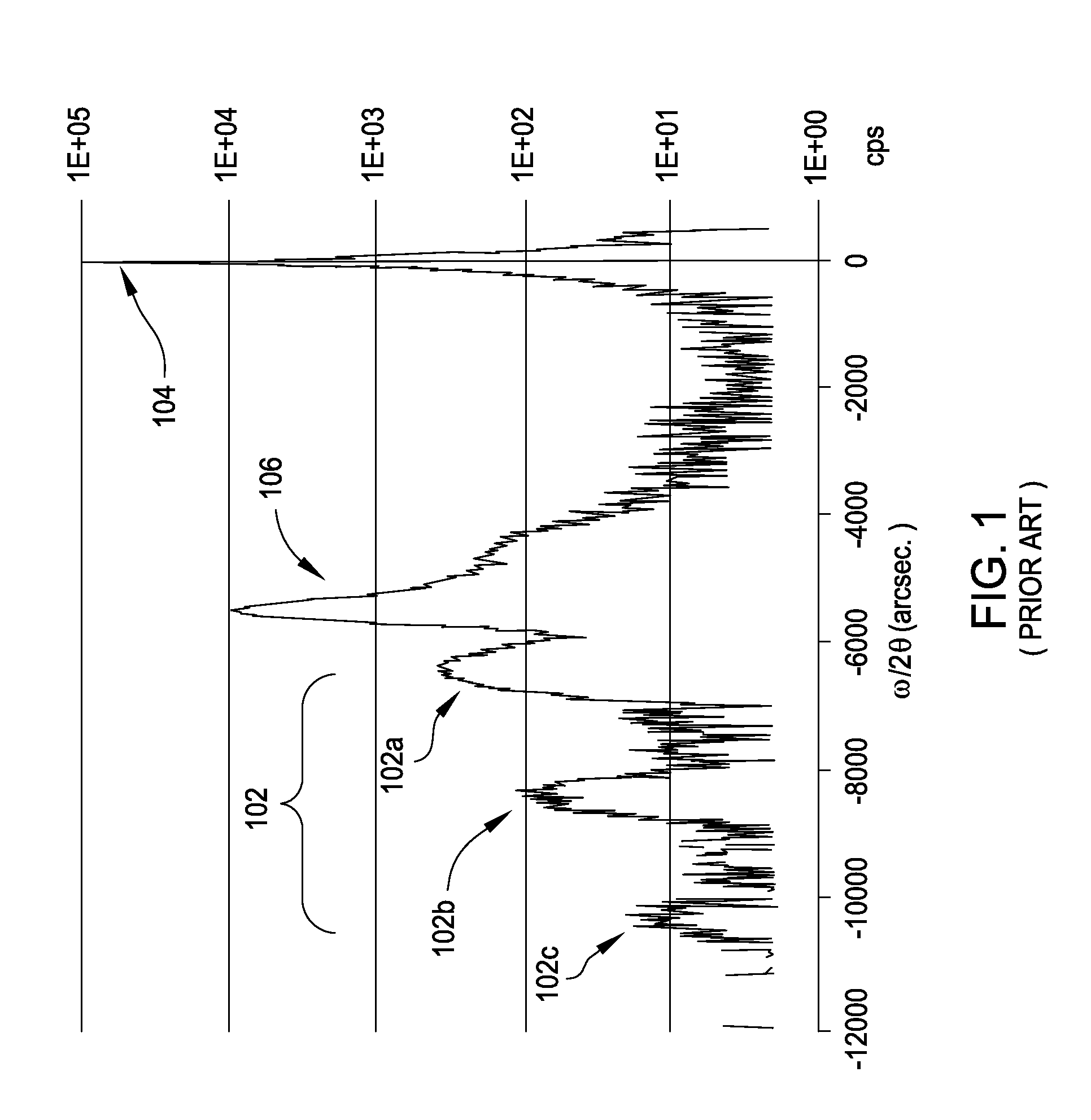

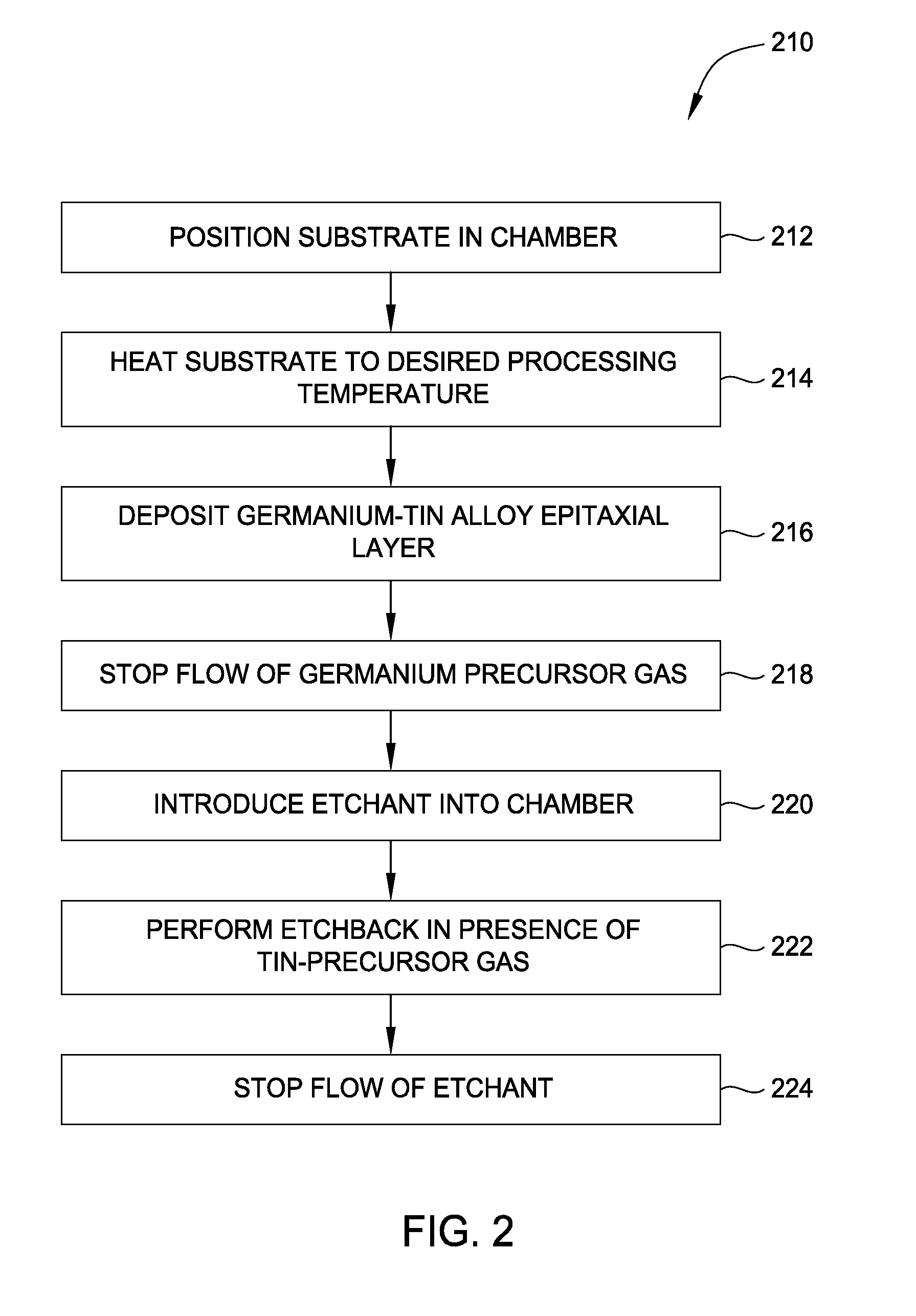

Method of semiconductor film stabilization

InactiveUS20130330911A1Polycrystalline material growthAfter-treatment detailsMetallurgySemiconductor

Embodiments of the invention generally relate to methods for forming silicon-germanium-tin alloy epitaxial layers, germanium-tin alloy epitaxial layers, and germanium epitaxial layers that may be doped with boron, phosphorus, arsenic, or other n-type or p-type dopants. The methods generally include positioning a substrate in a processing chamber. A germanium precursor gas is then introduced into the chamber concurrently with a stressor precursor gas, such as a tin precursor gas, to form an epitaxial layer. The flow of the germanium gas is then halted, and an etchant gas is introduced into the chamber. An etch back is then performed while in the presence of the stressor precursor gas used in the formation of the epitaxial film. The flow of the etchant gas is then stopped, and the cycle may then be repeated. In addition to or as an alternative to the etch back process, an annealing processing may be performed.

Owner:APPLIED MATERIALS INC

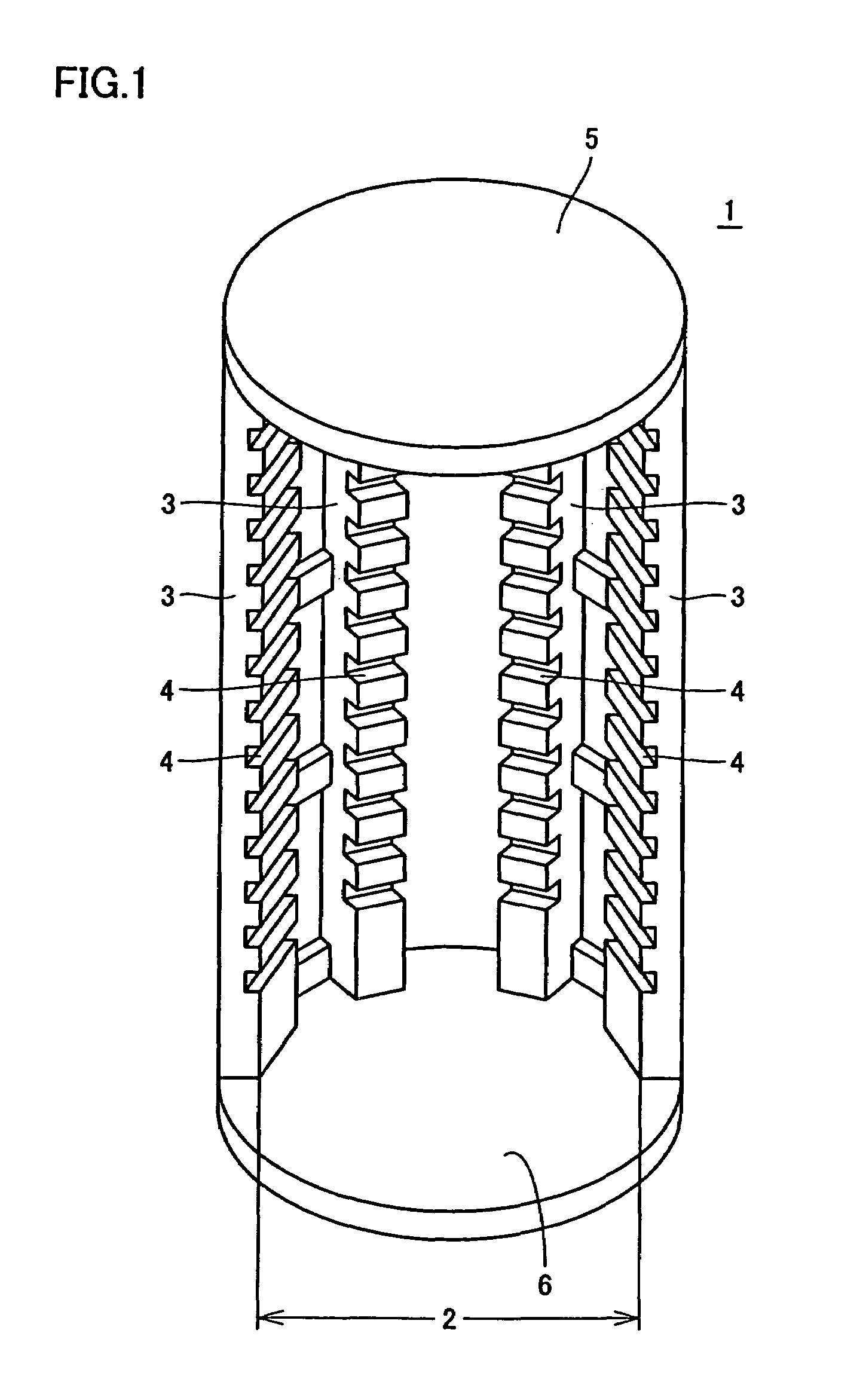

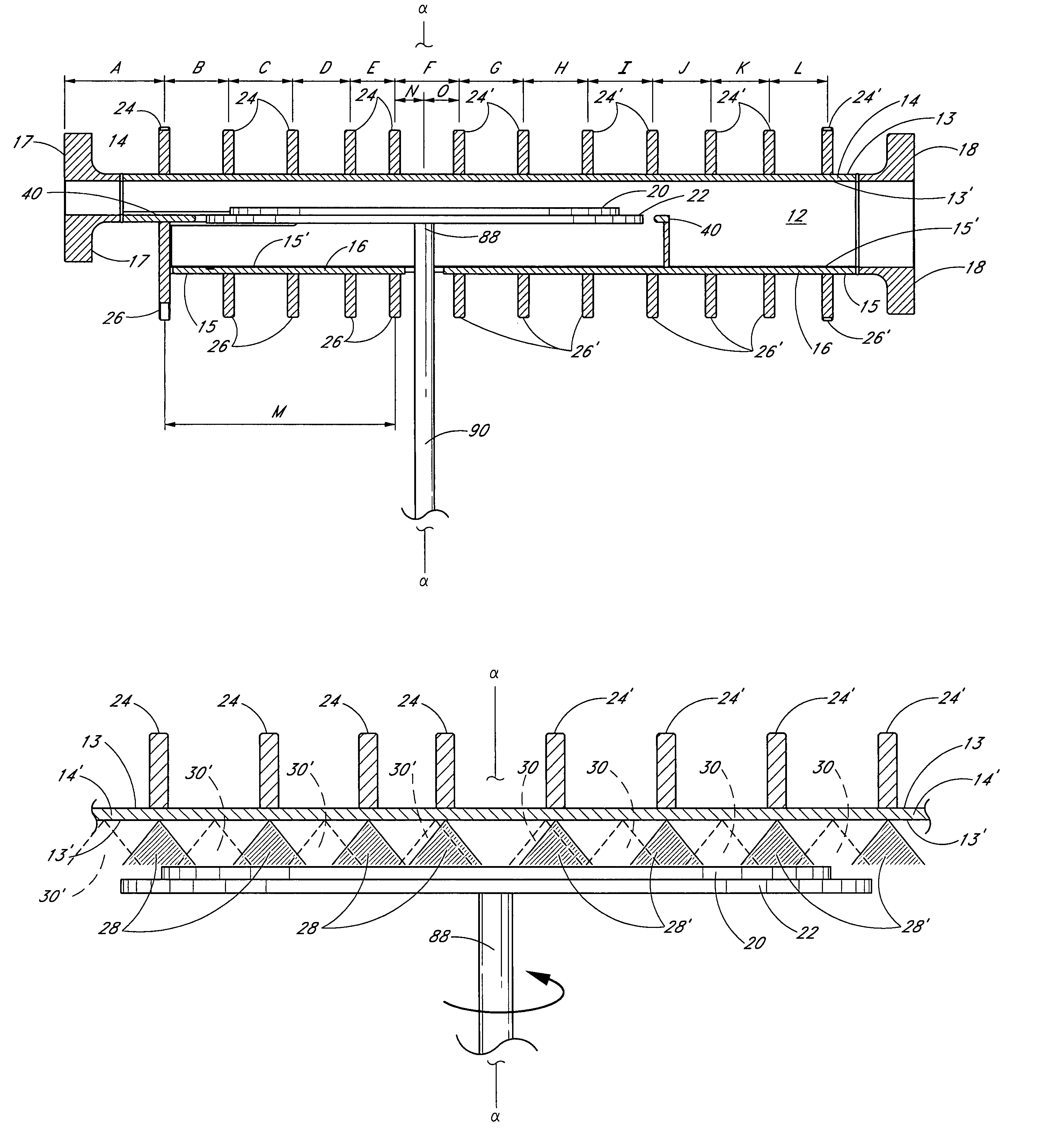

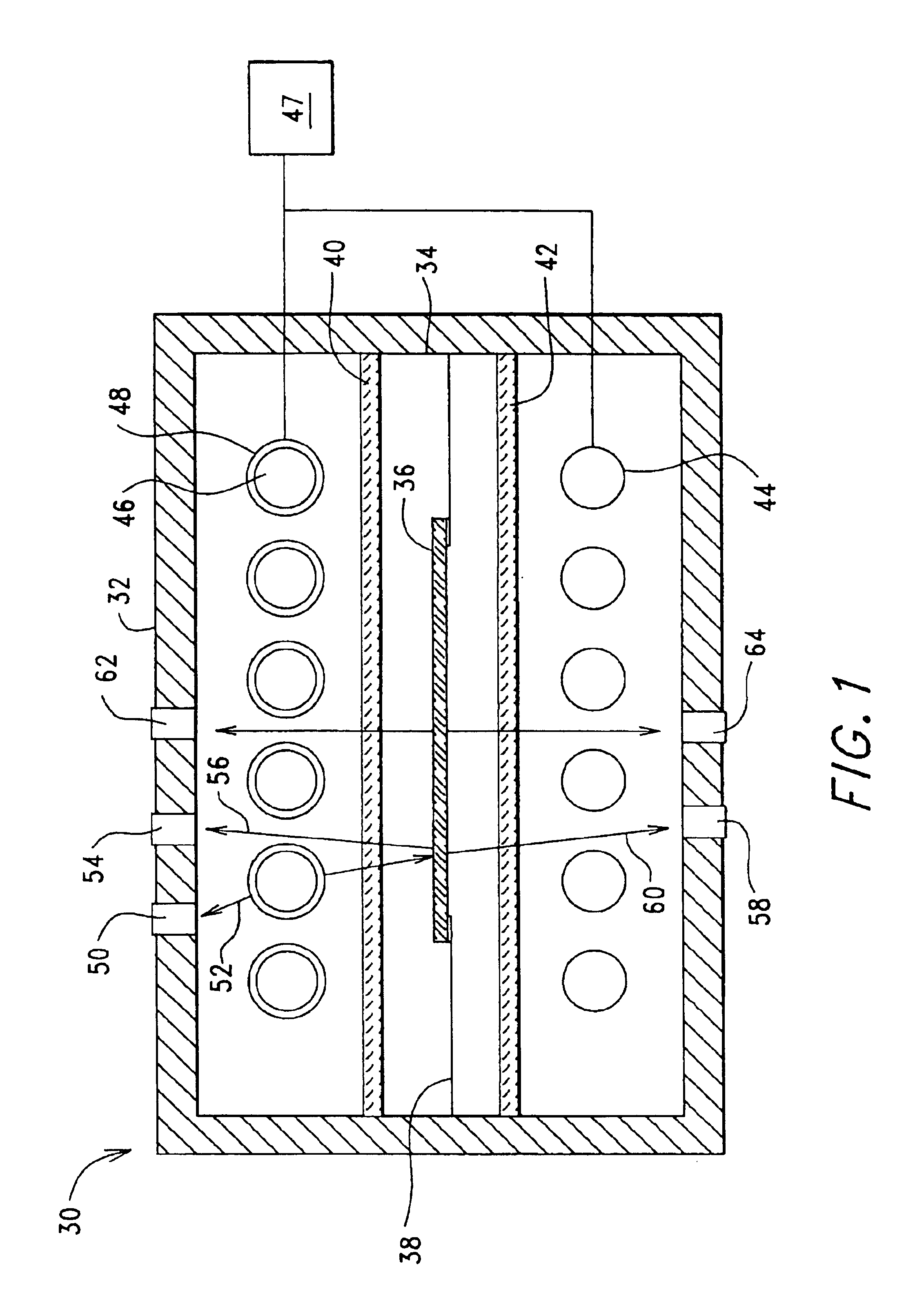

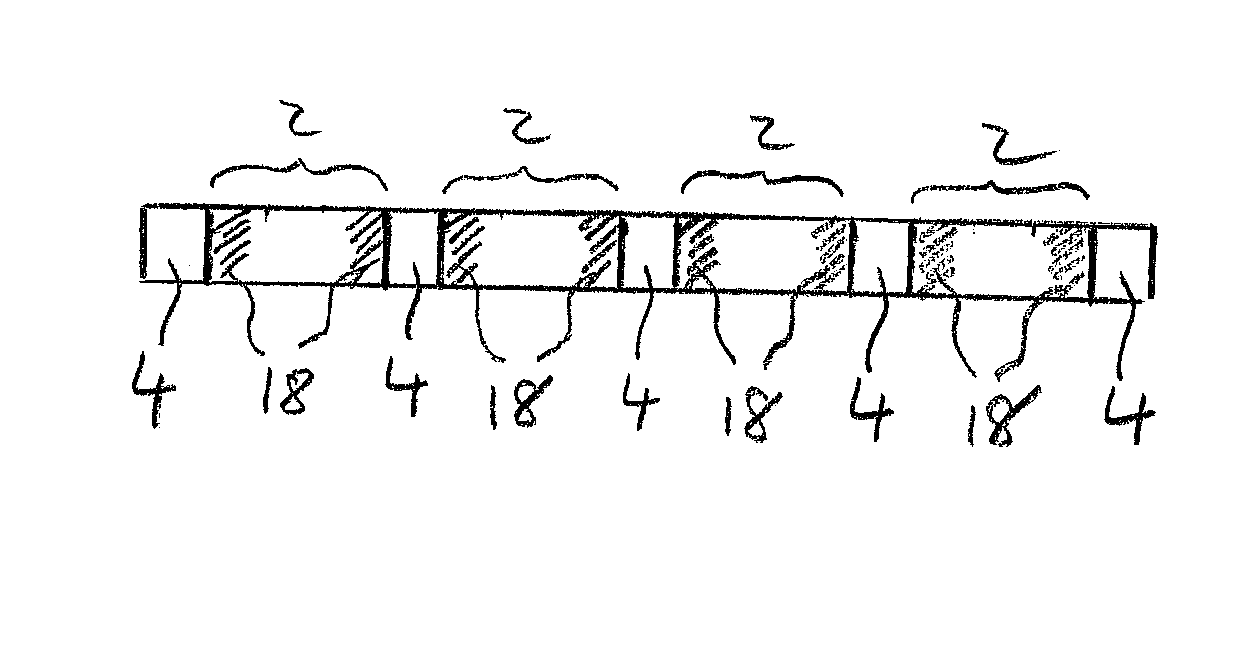

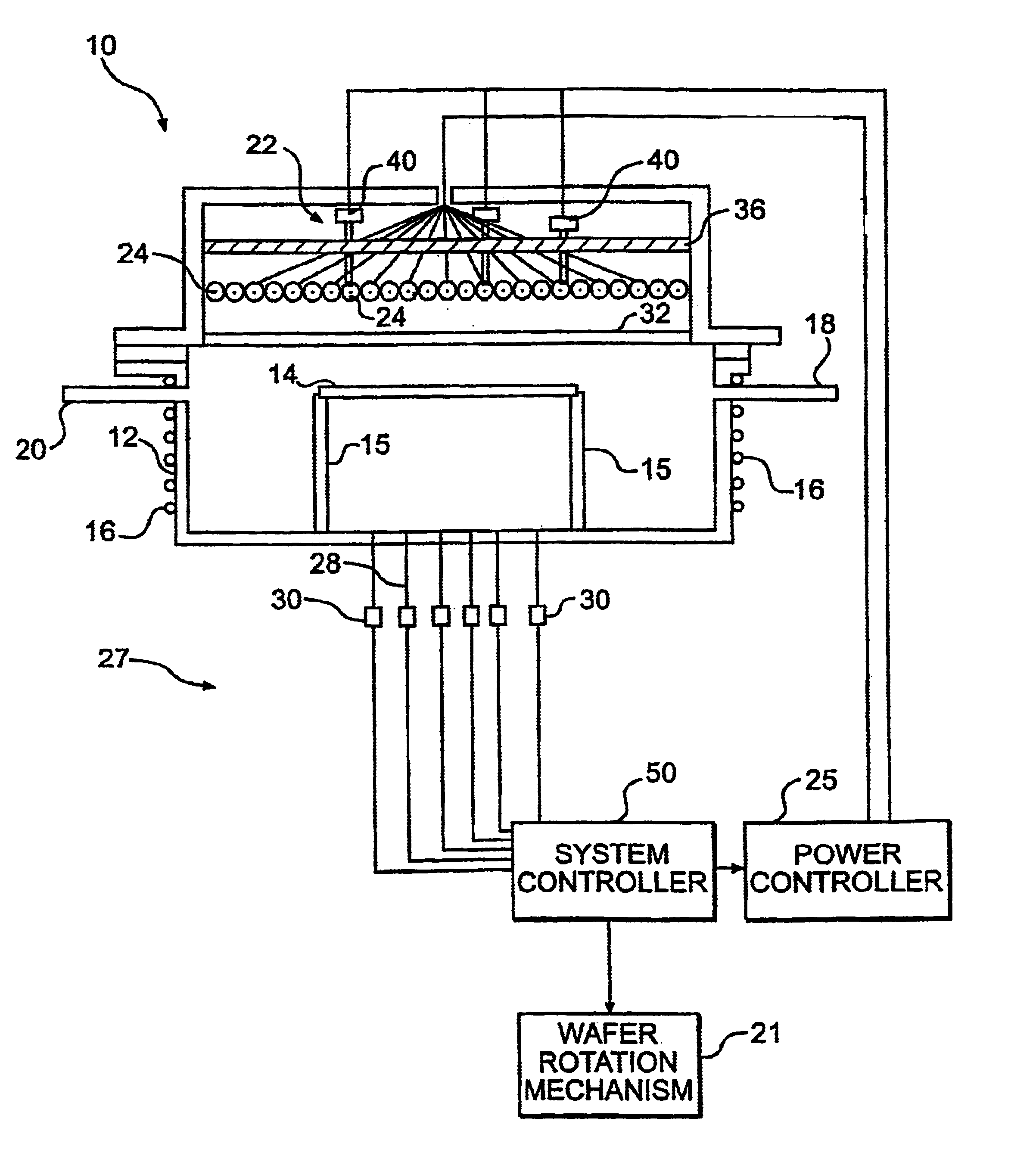

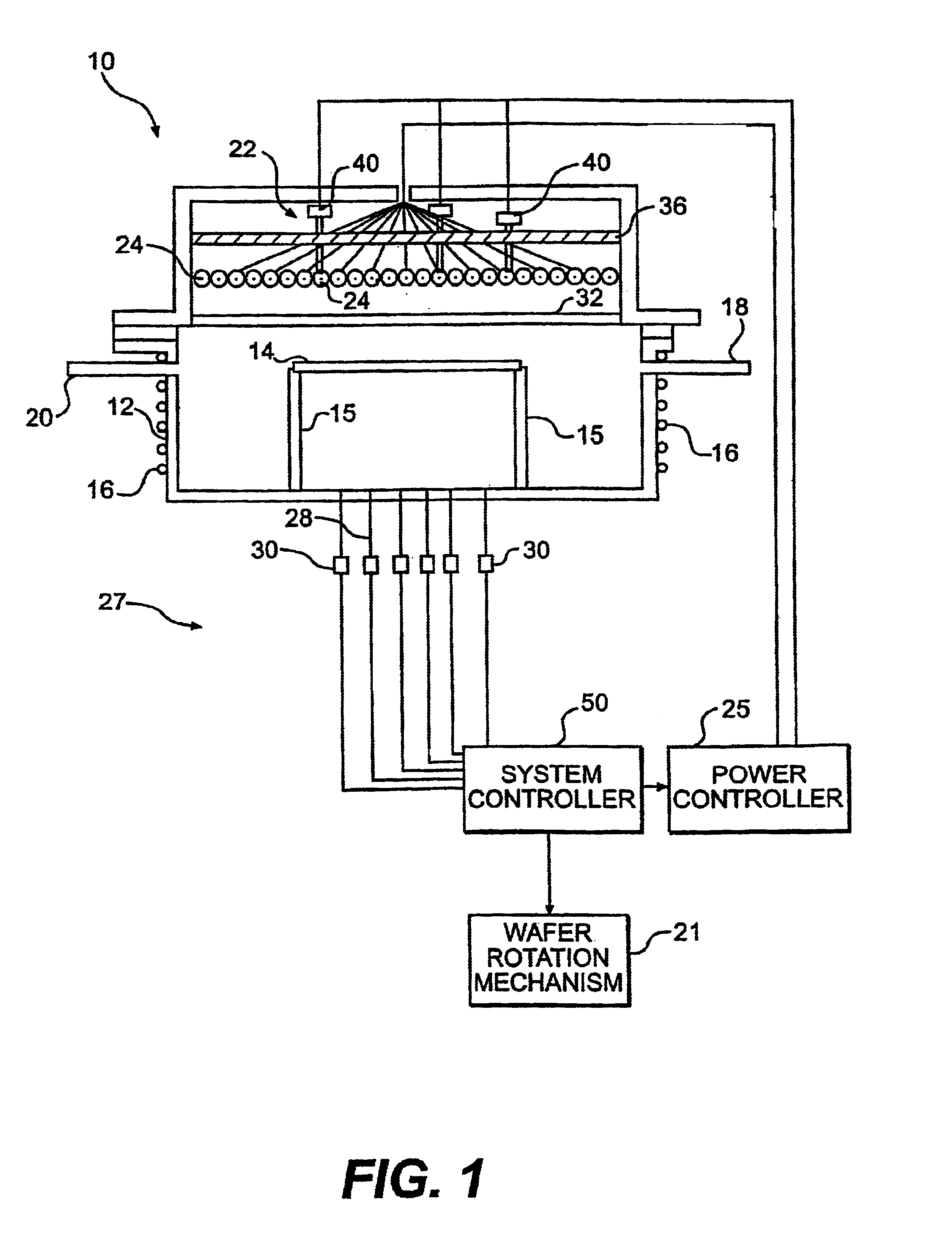

Staggered ribs on process chamber to reduce thermal effects

ActiveUS7108753B2Diffusion/dopingSemiconductor/solid-state device manufacturingEngineeringThermal effect

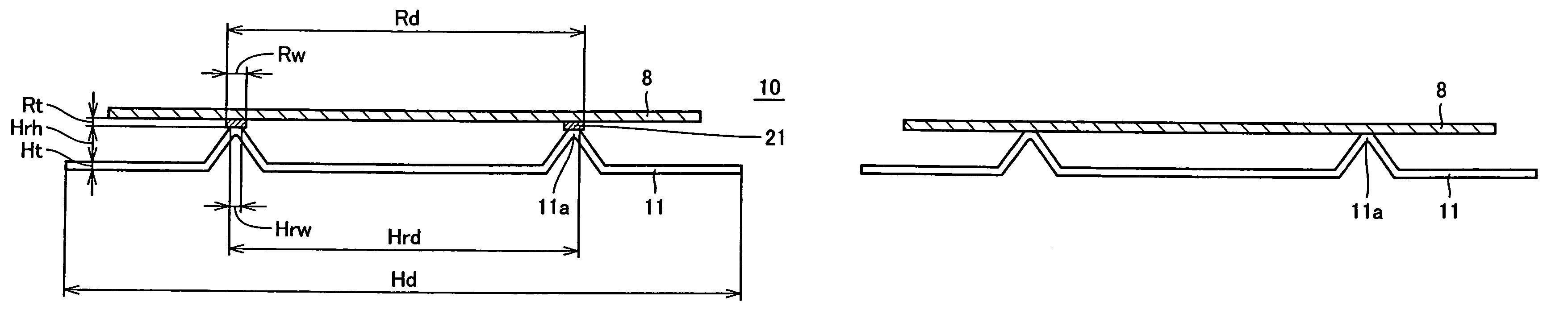

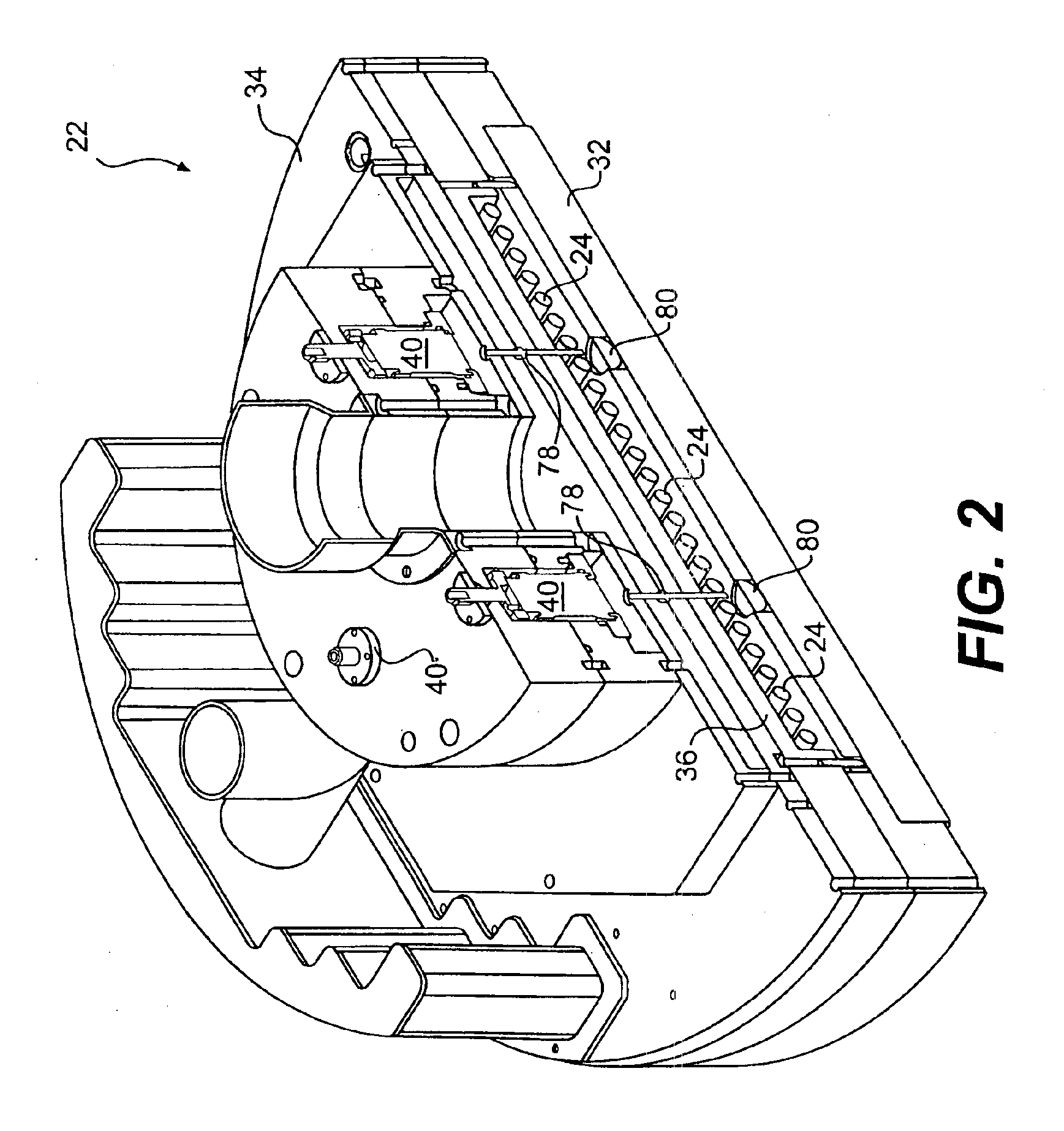

A semiconductor processing chamber having a plurality of ribs on an exterior surface of the chamber is provided. The ribs are positioned relative to the chamber such that shadows cast into the chamber by the ribs are offset from one another, thus more uniformly distributing radiant energy entering the chamber. In one embodiment, the ribs are positioned on the exterior surface of the chamber so that they have dissimilar radial distances from a center of the chamber. When a substrate rotates within the chamber, shadows produced by the ribs on a first side of the chamber fall substantially between secondary shadows produced by the ribs on a second side of the chamber. Likewise, shadows produced by the ribs on the second side of the chamber fall substantially between the secondary shadows produced by the ribs on the first side of the chamber.

Owner:ASM IP HLDG BV

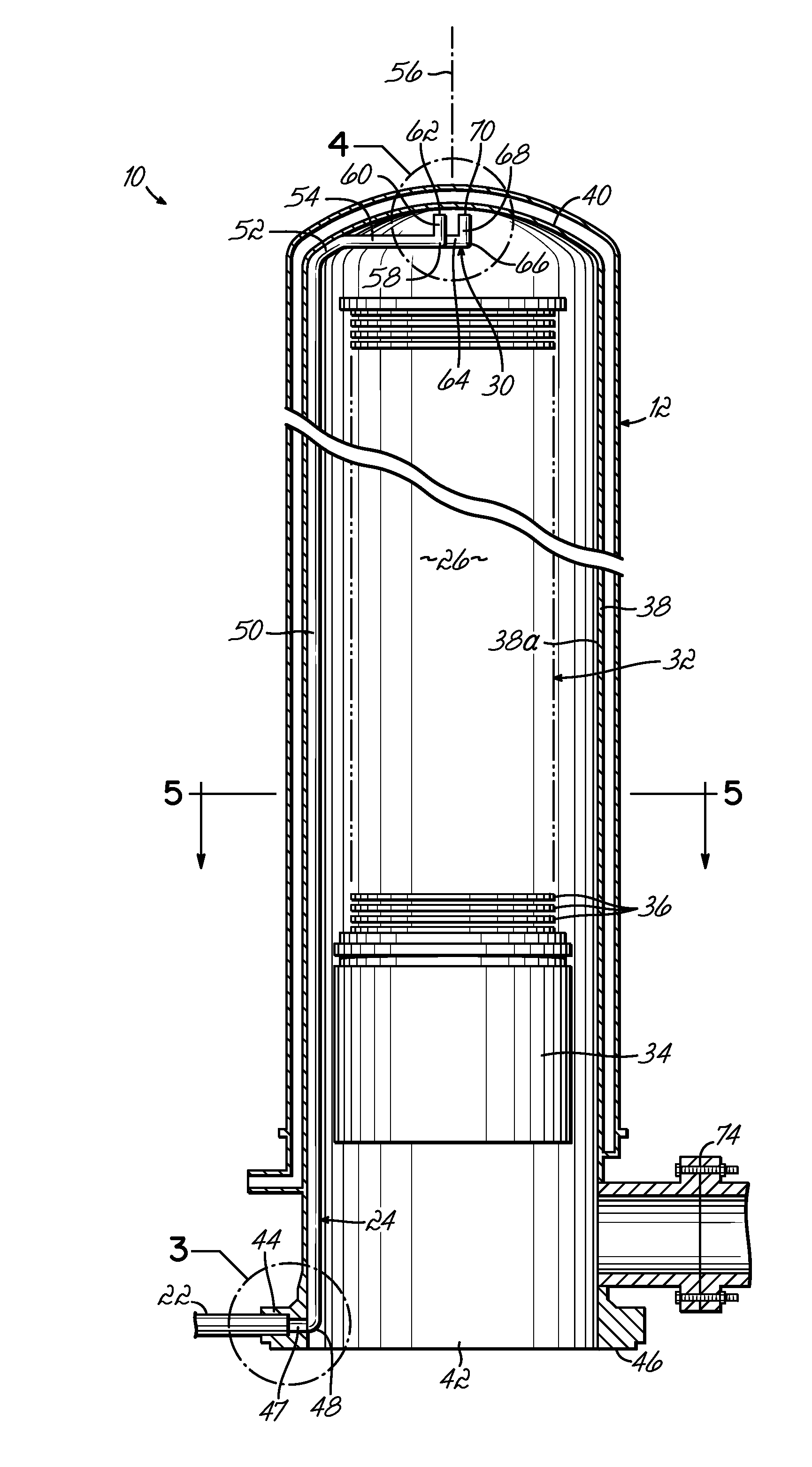

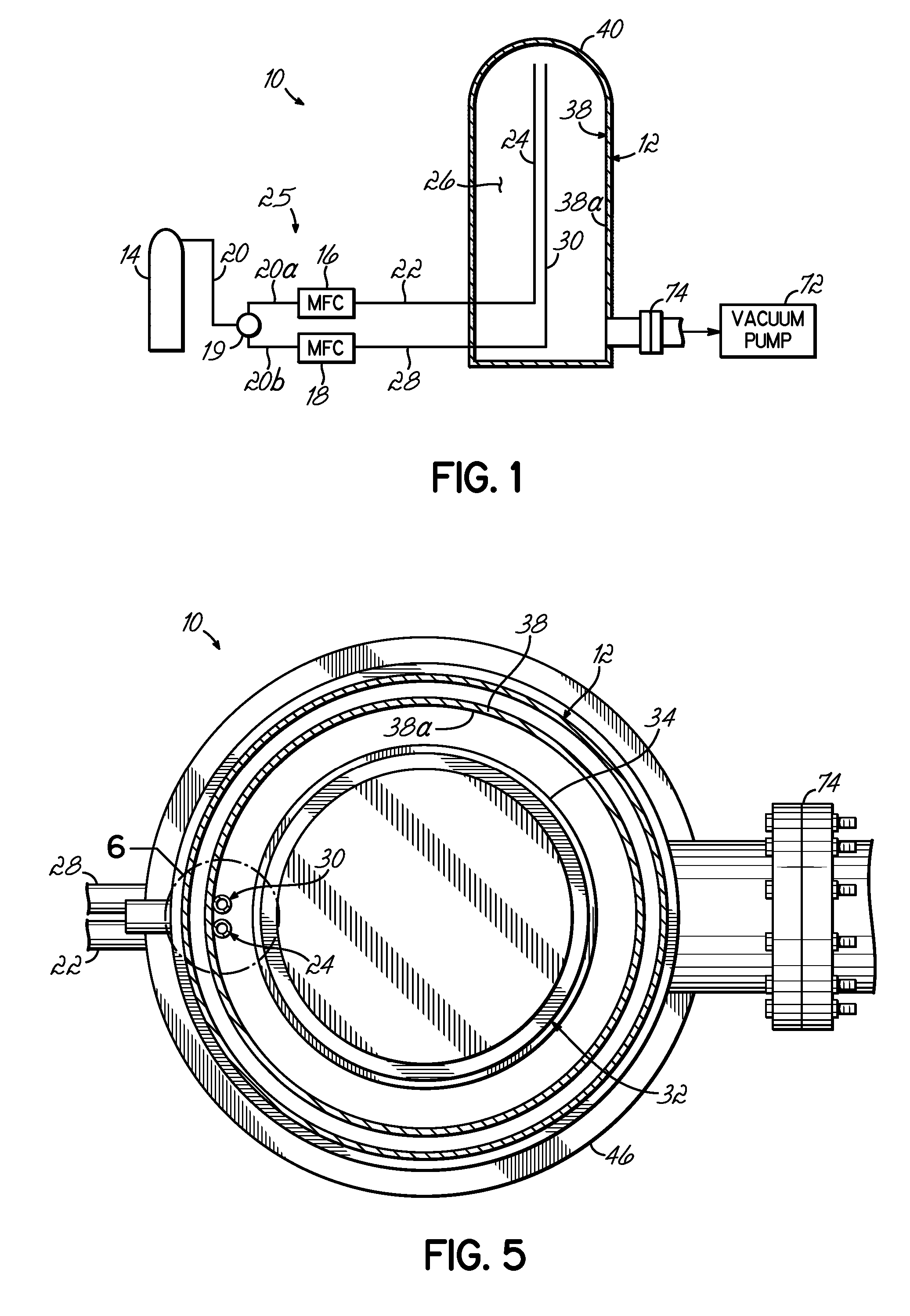

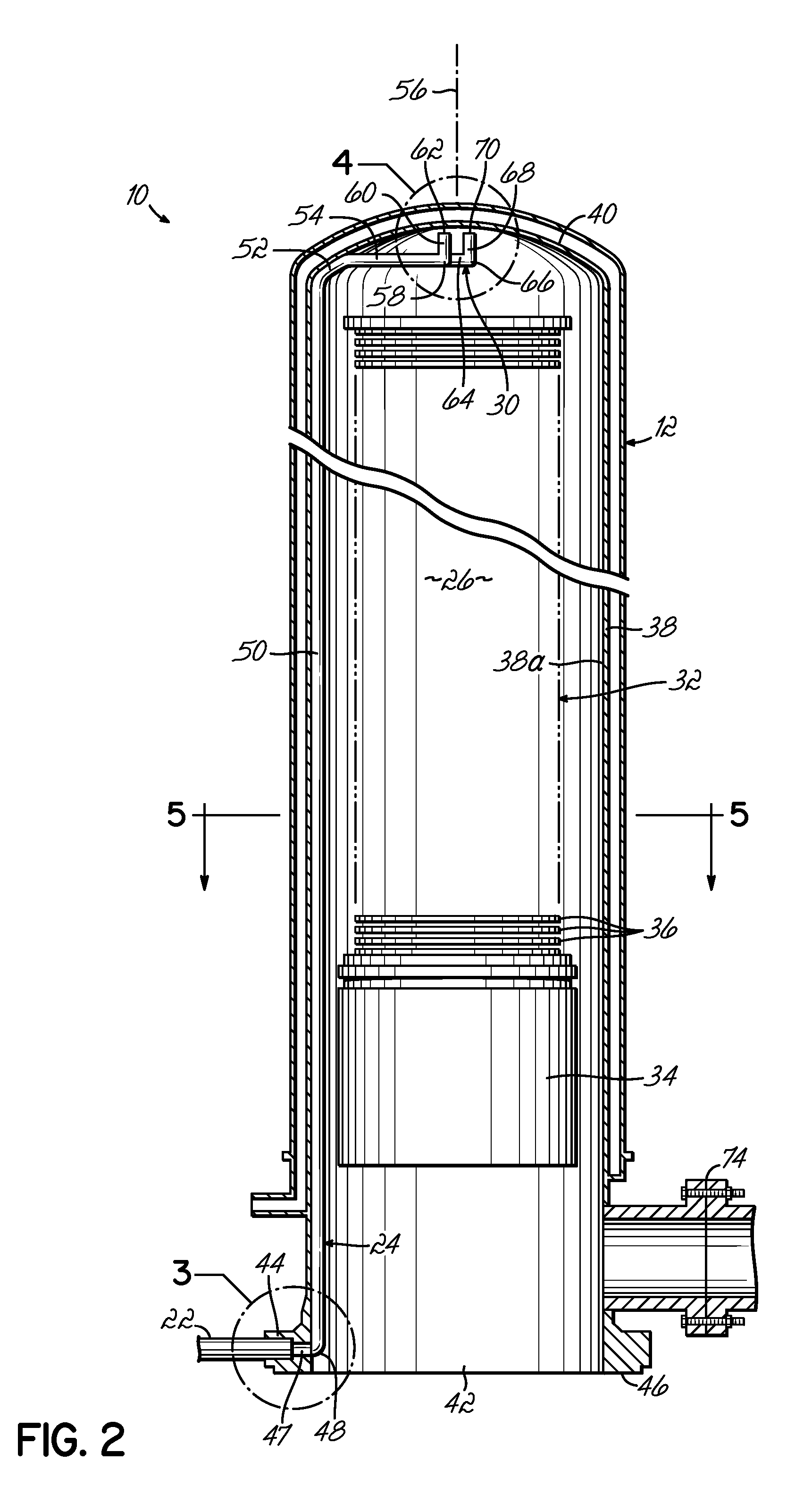

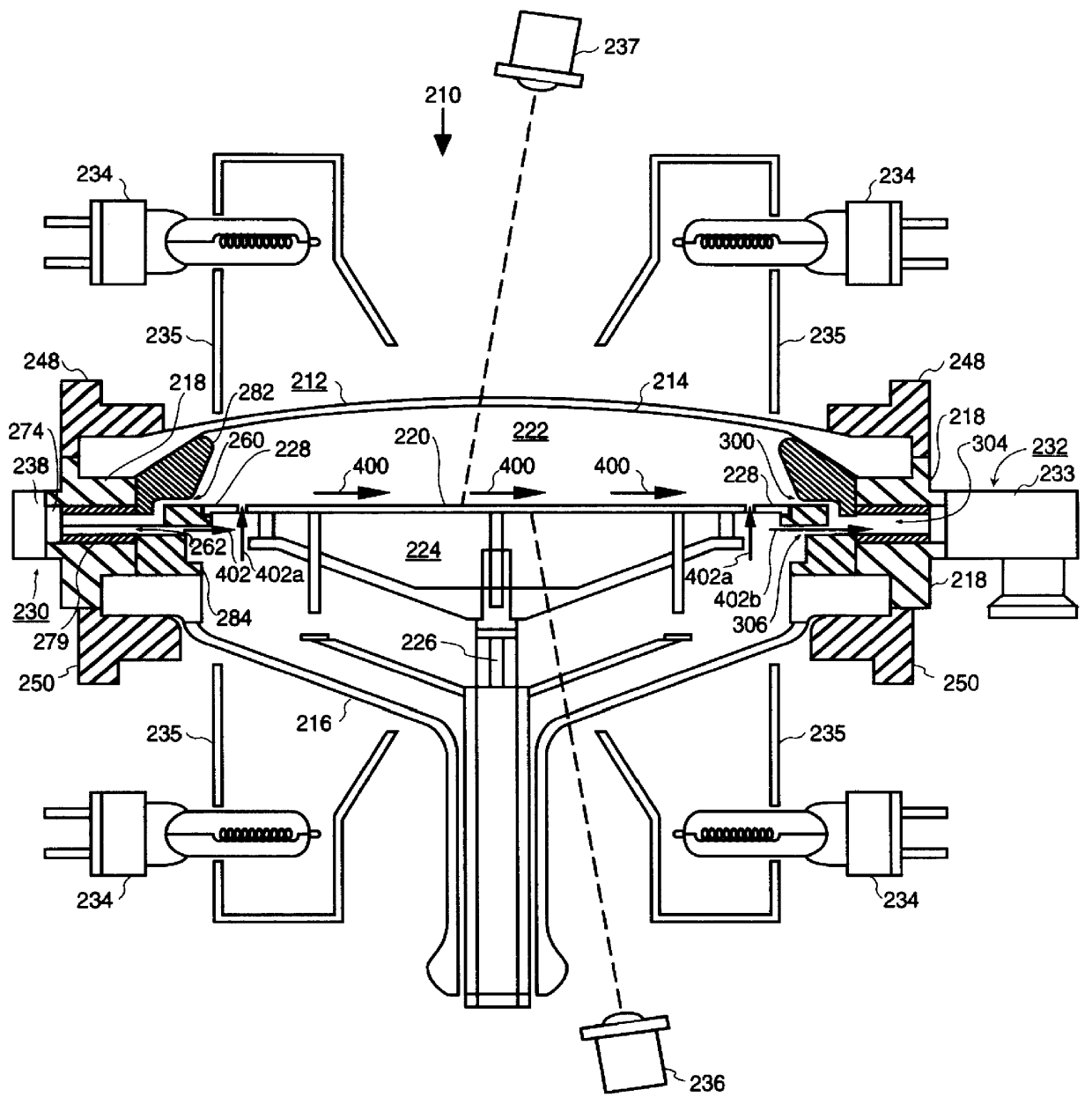

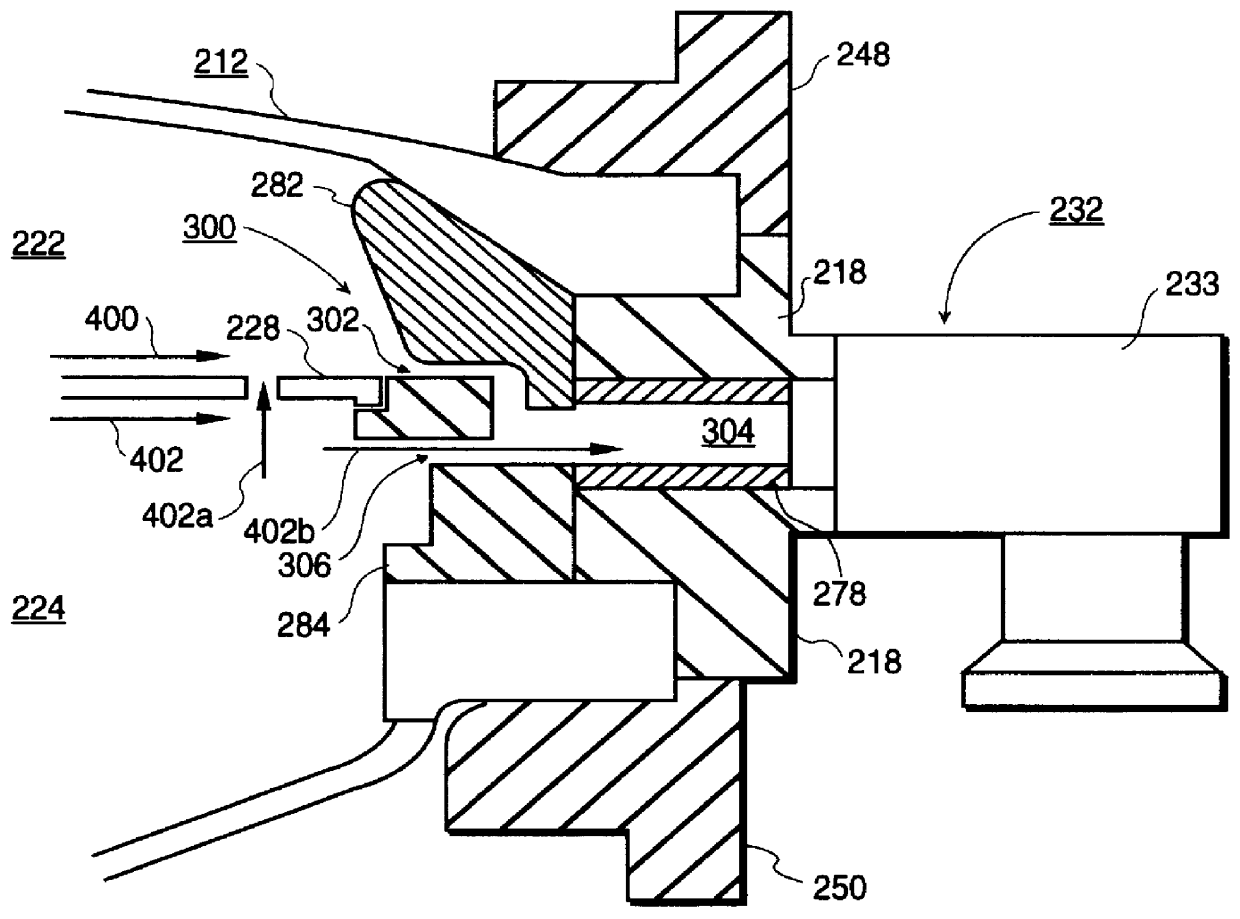

Thermal processing furnace, gas delivery system therefor, and methods for delivering a process gas thereto

InactiveUS7910494B2After-treatment apparatusCombustion using gaseous and pulverulent fuelProcess engineeringGas supply

A gas delivery system for supplying a process gas from a gas supply to a thermal processing furnace, a thermal processing furnace equipped with the gas delivery system, and methods for delivering process gas to a thermal processing furnace. The gas delivery system comprises a plurality of regulators, such as mass flow controllers, in a process gas manifold coupling a gas supply with a thermal processing furnace. The regulators establish a corresponding plurality of flows of a process gas at a plurality of flow rates communicated by the process gas manifold to the thermal processing furnace. The gas delivery system may be a component of the thermal processing furnace that further includes a liner that surrounds a processing space inside the thermal processing furnace.

Owner:TOKYO ELECTRON LTD

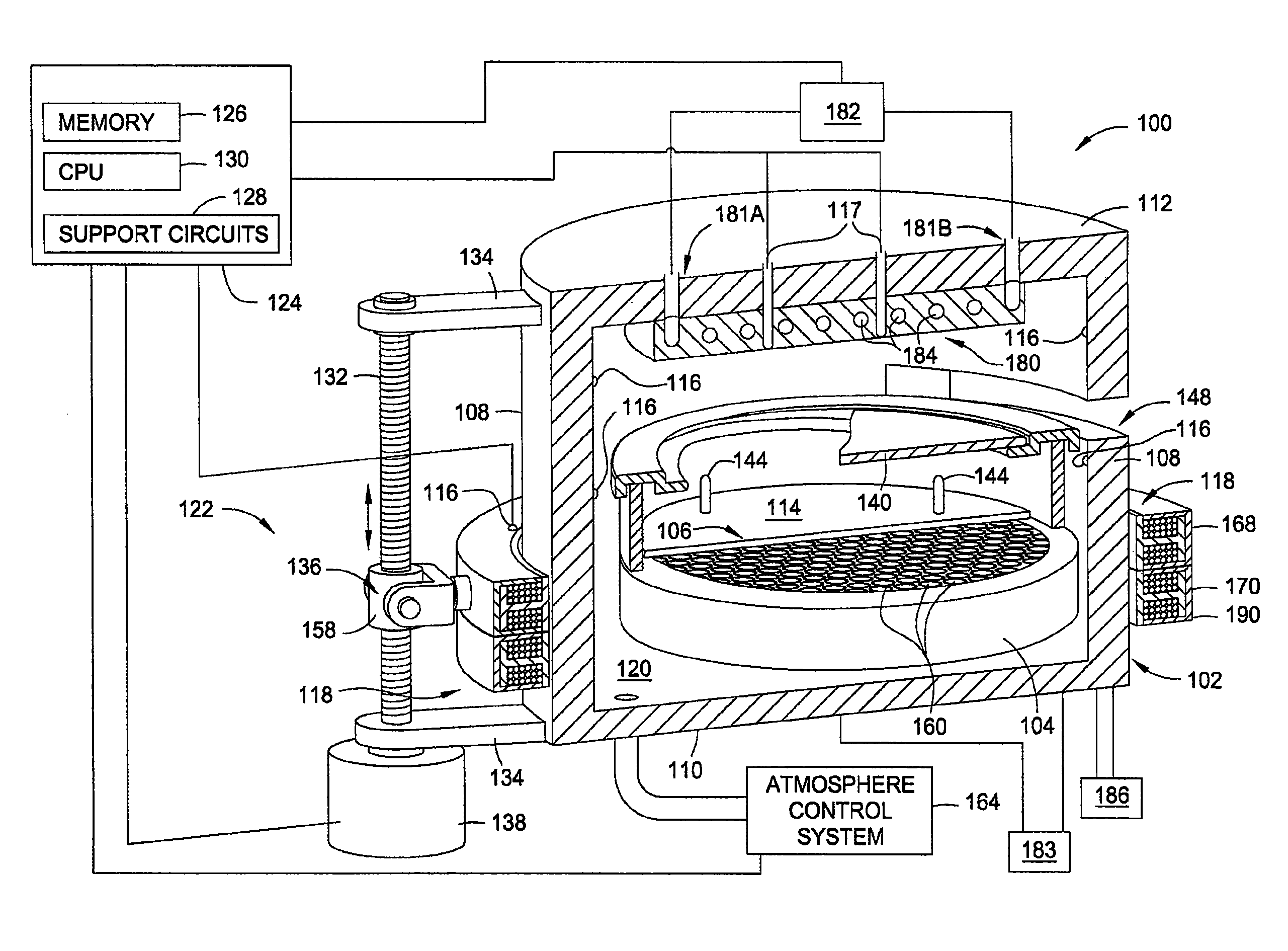

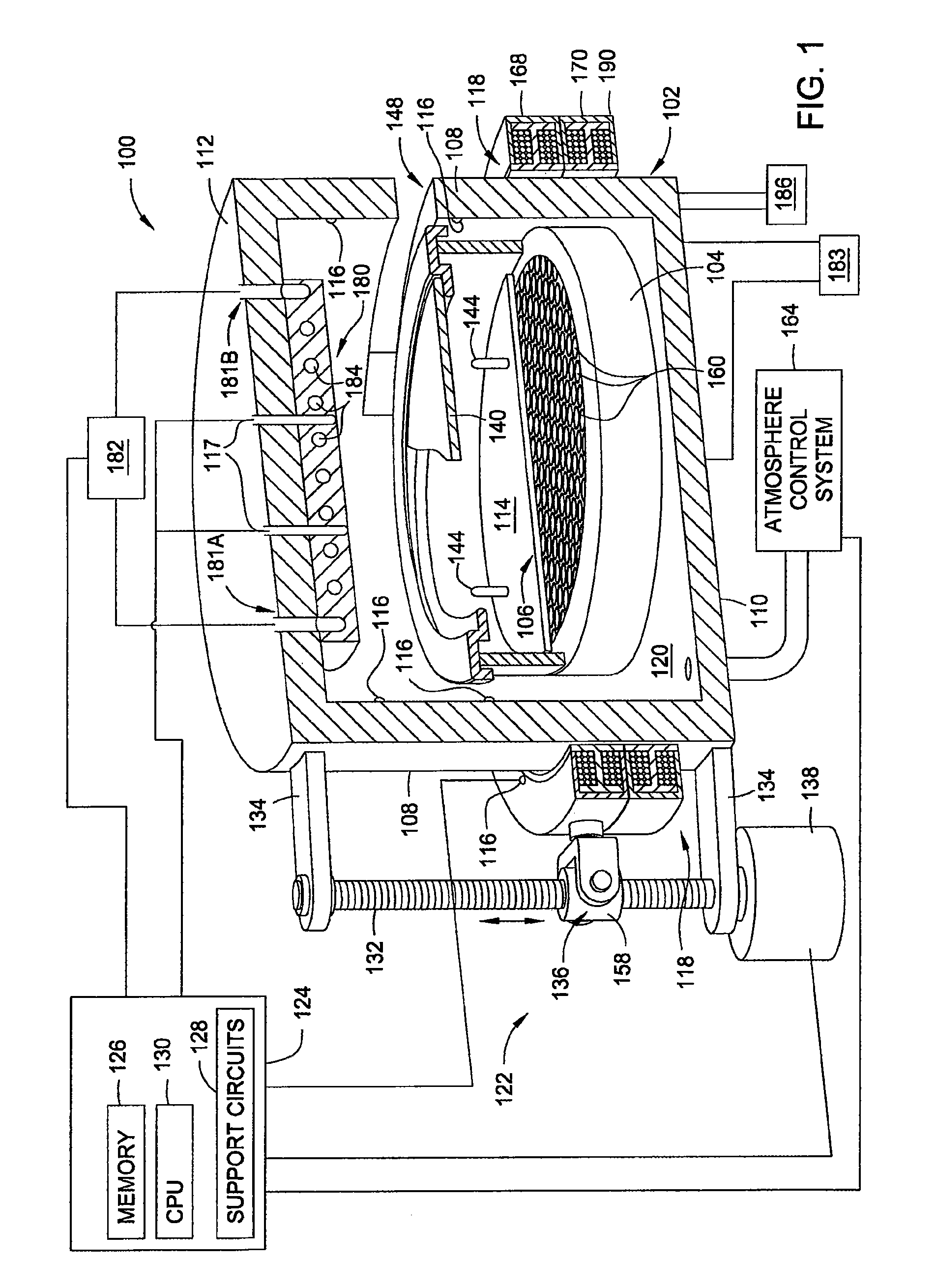

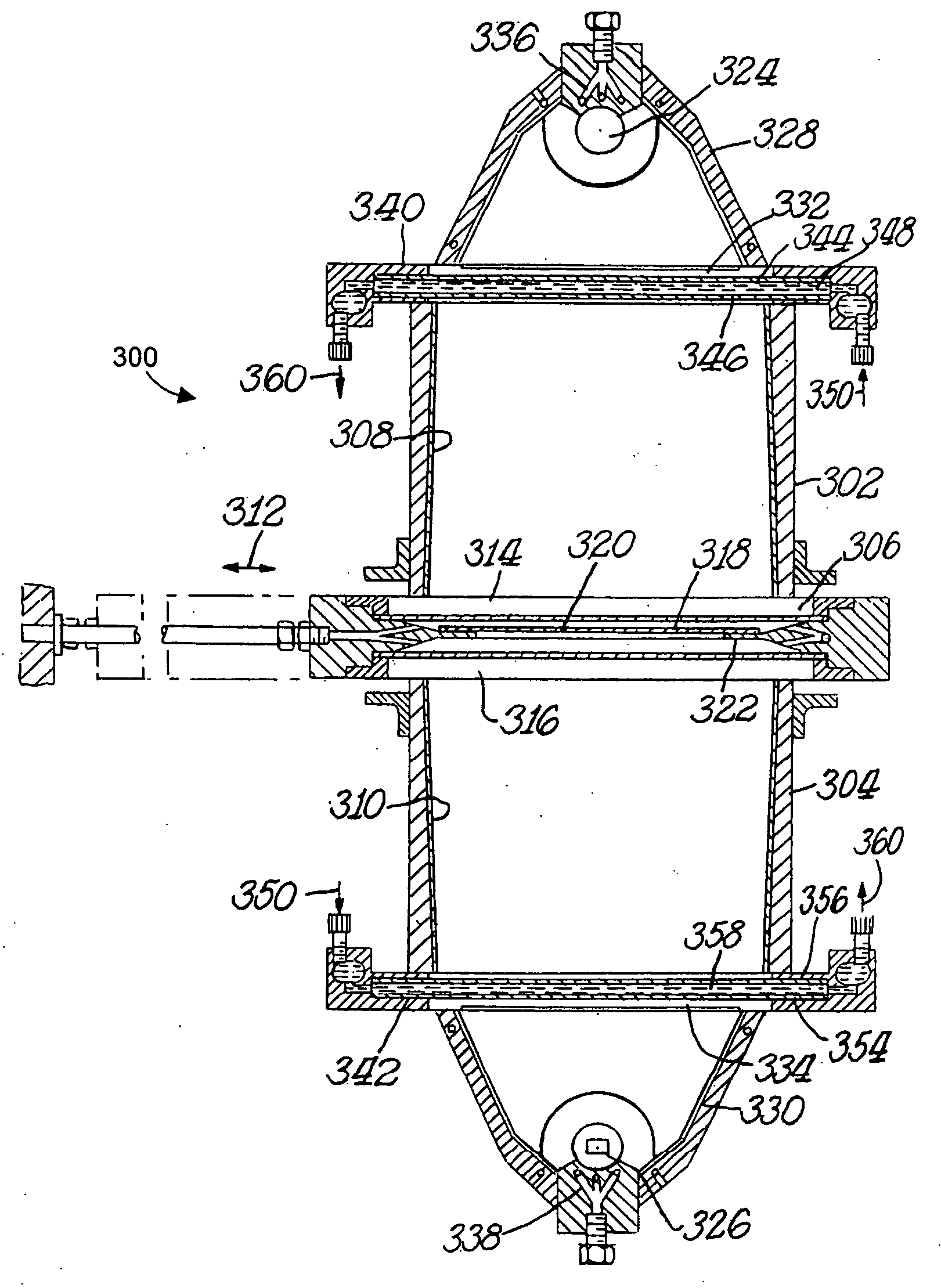

Rapid conductive cooling using a secondary process plane

A method and apparatus for thermally processing a substrate is described. The apparatus includes a substrate support configured to move linearly and / or rotationally by a magnetic drive. The substrate support is also configured to receive a radiant heat source to provide heating region in a portion of the chamber. An active cooling region comprising a cooling plate is disposed opposite the heating region. The substrate may move between the two regions to facilitate rapidly controlled heating and cooling of the substrate.

Owner:APPLIED MATERIALS INC

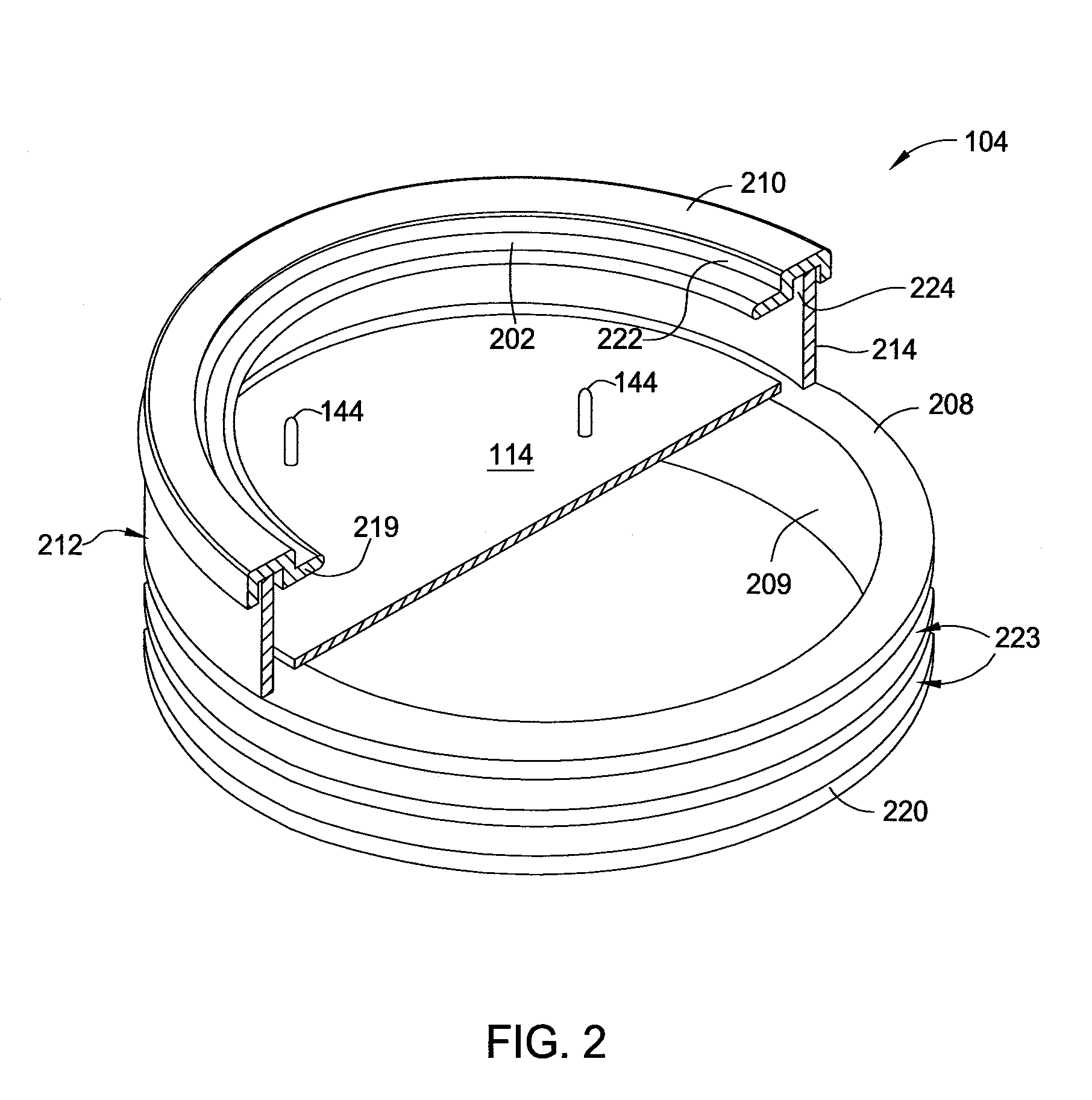

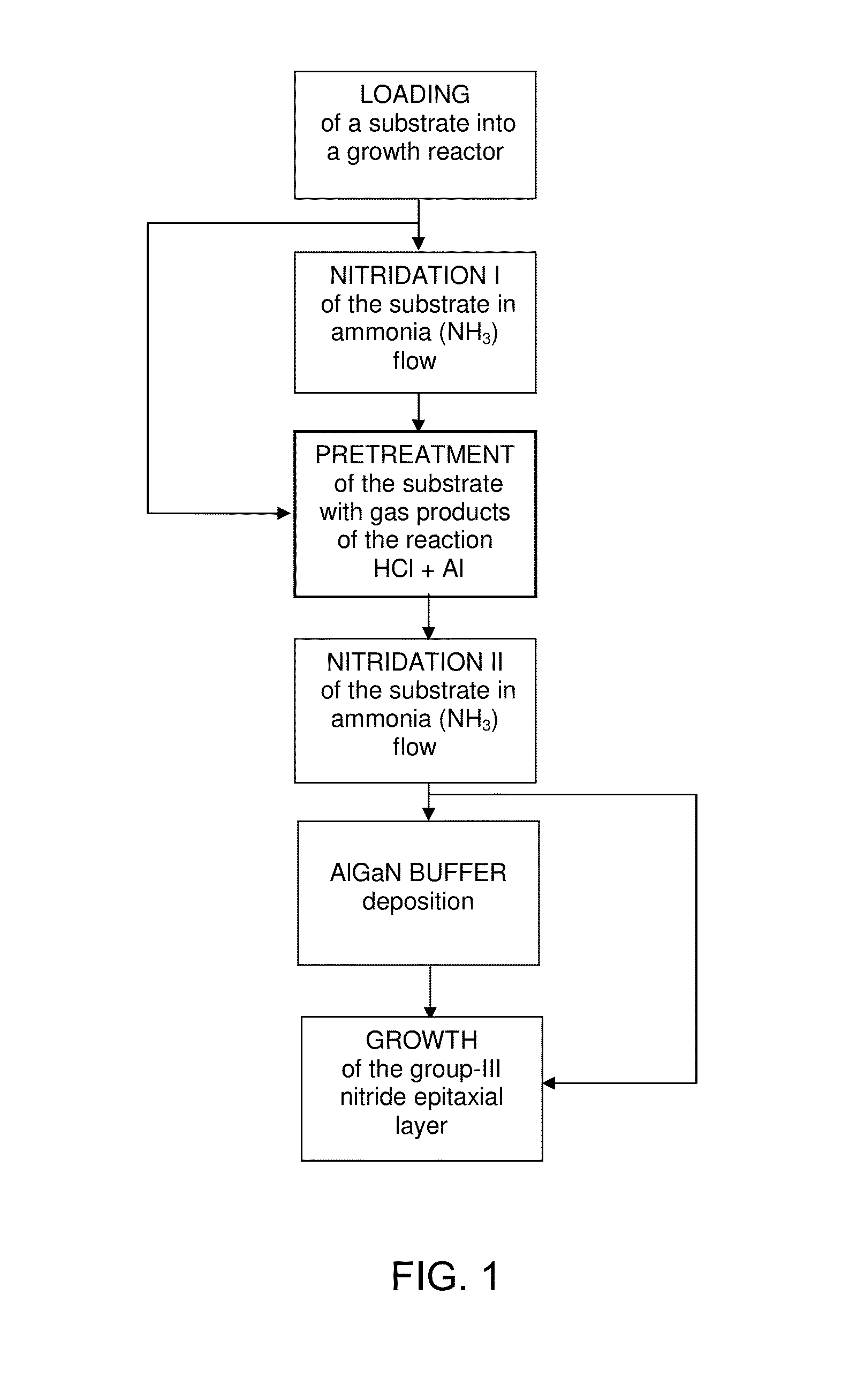

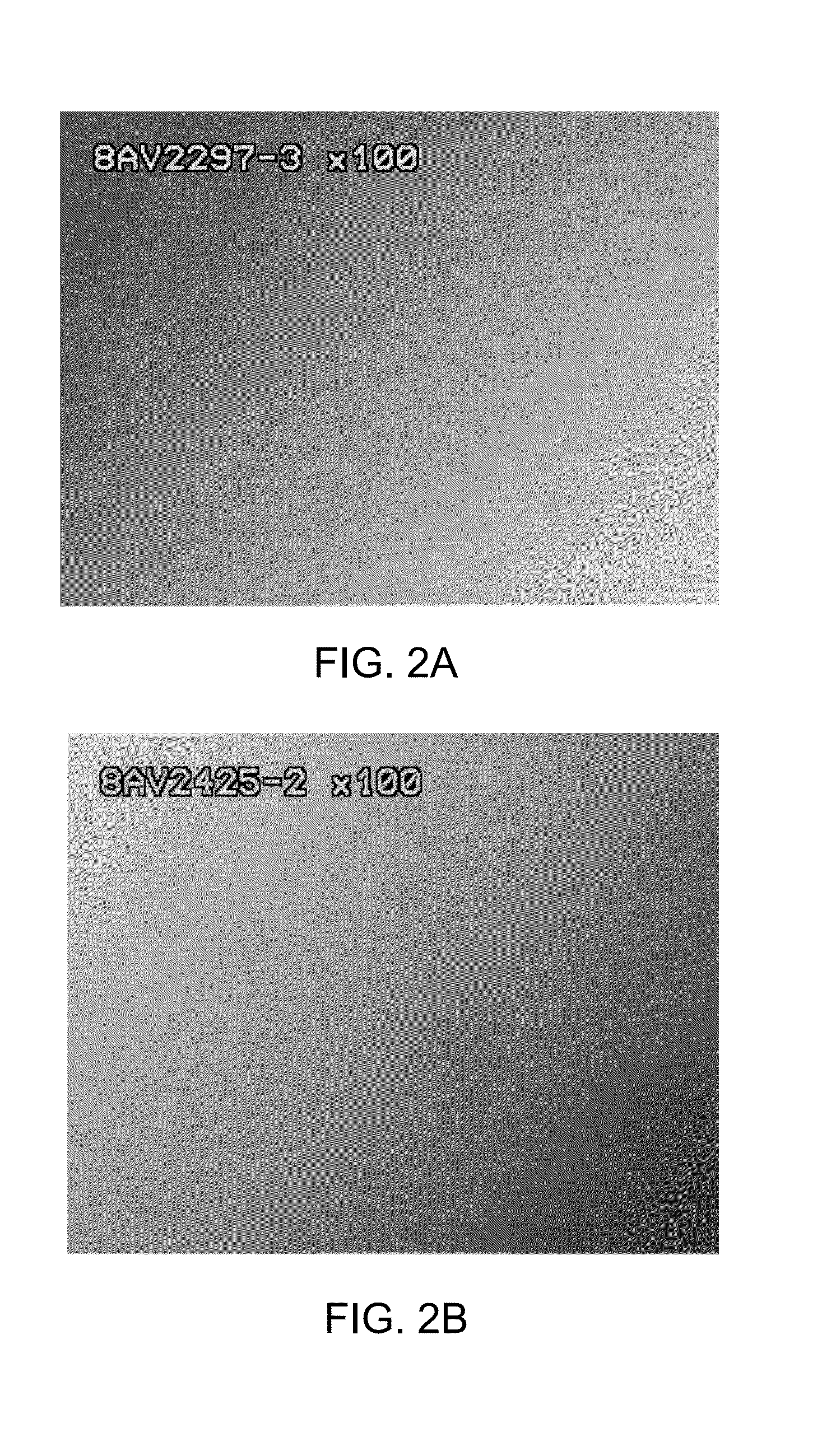

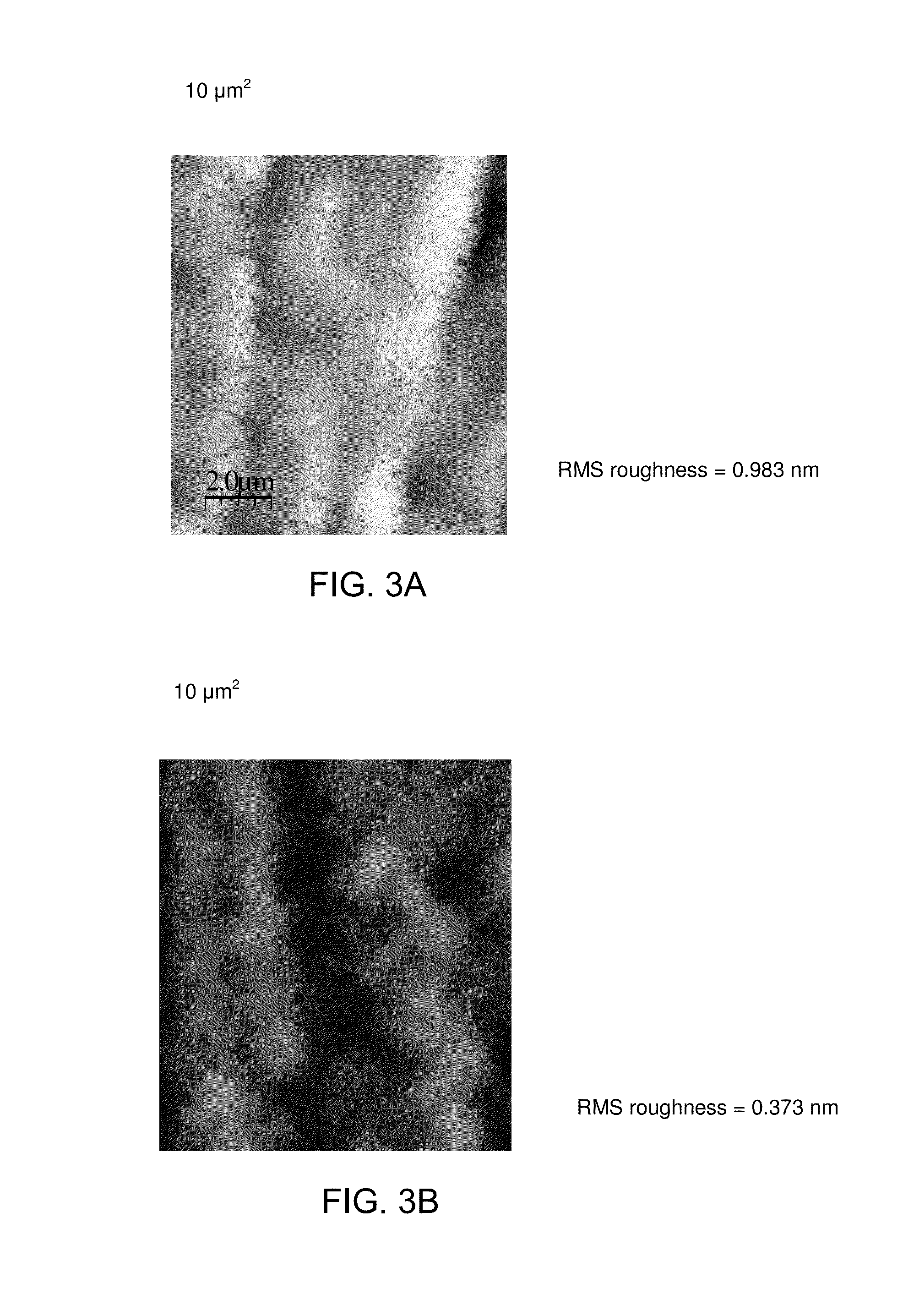

Method for Substrate Pretreatment To Achieve High-Quality III-Nitride Epitaxy

The present invention relates to a method for producing a modified surface of a substrate that stimulates the growth of epitaxial layers of group-III nitride semiconductors with substantially improved structural perfection and surface flatness. The modification is conducted outside or inside a growth reactor by exposing the substrate to a gas-product of the reaction between hydrogen chloride (HCl) and aluminum metal (Al). As a single-step or an essential part of the multi-step pretreatment procedure, the modification gains in coherent coordination between the substrate and group-III nitride epitaxial structure to be deposited. Along with epilayer, total epitaxial structure may include buffer inter-layer to accomplish precise substrate-epilayer coordination. While this modification is a powerful tool to make high-quality group-III nitride epitaxial layers attainable even on foreign substrates having polar, semipolar and nonpolar orientation, it remains gentle enough to keep the surface of the epilayer extremely smooth. Various embodiments are disclosed.

Owner:OSTENDO TECH INC

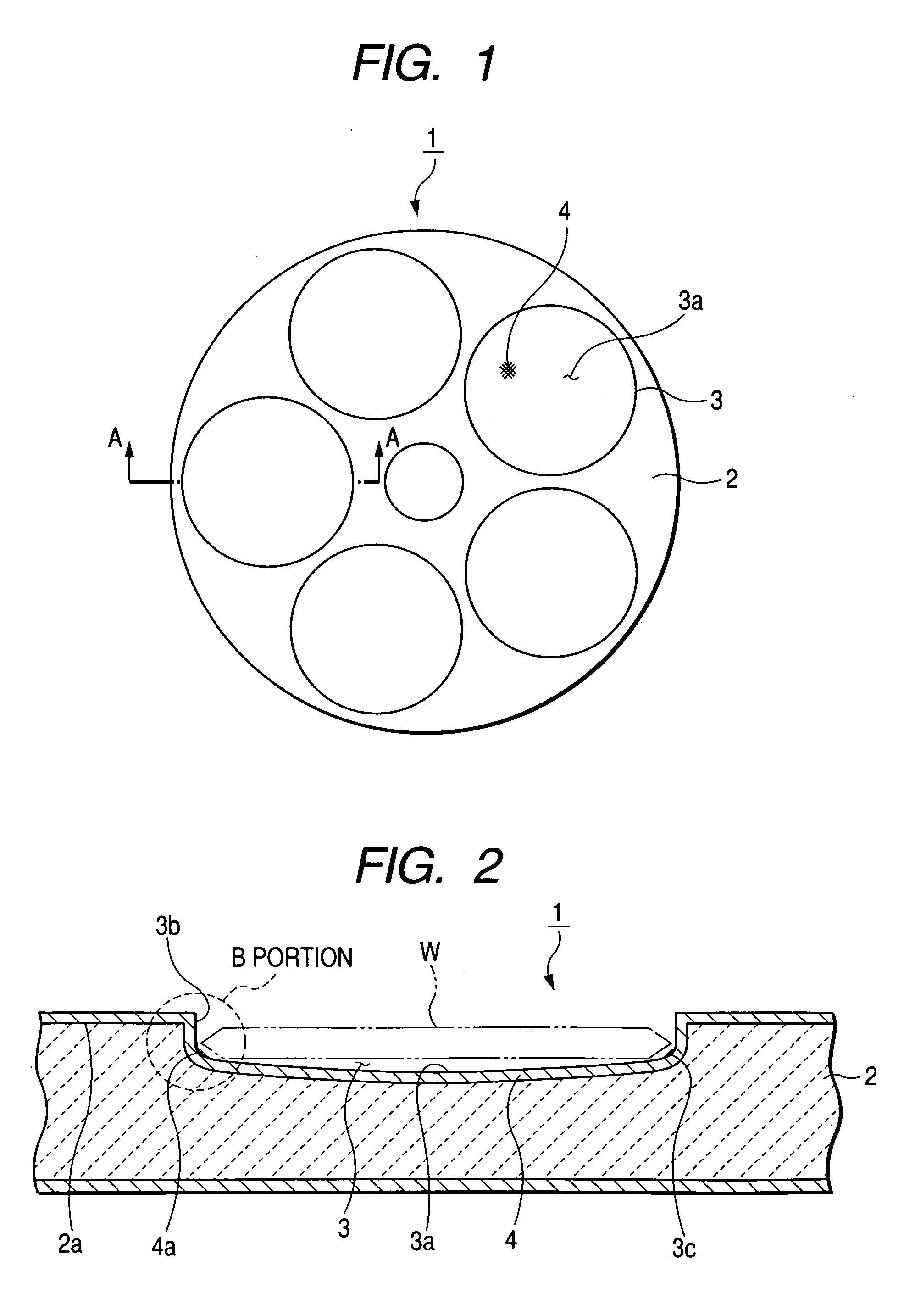

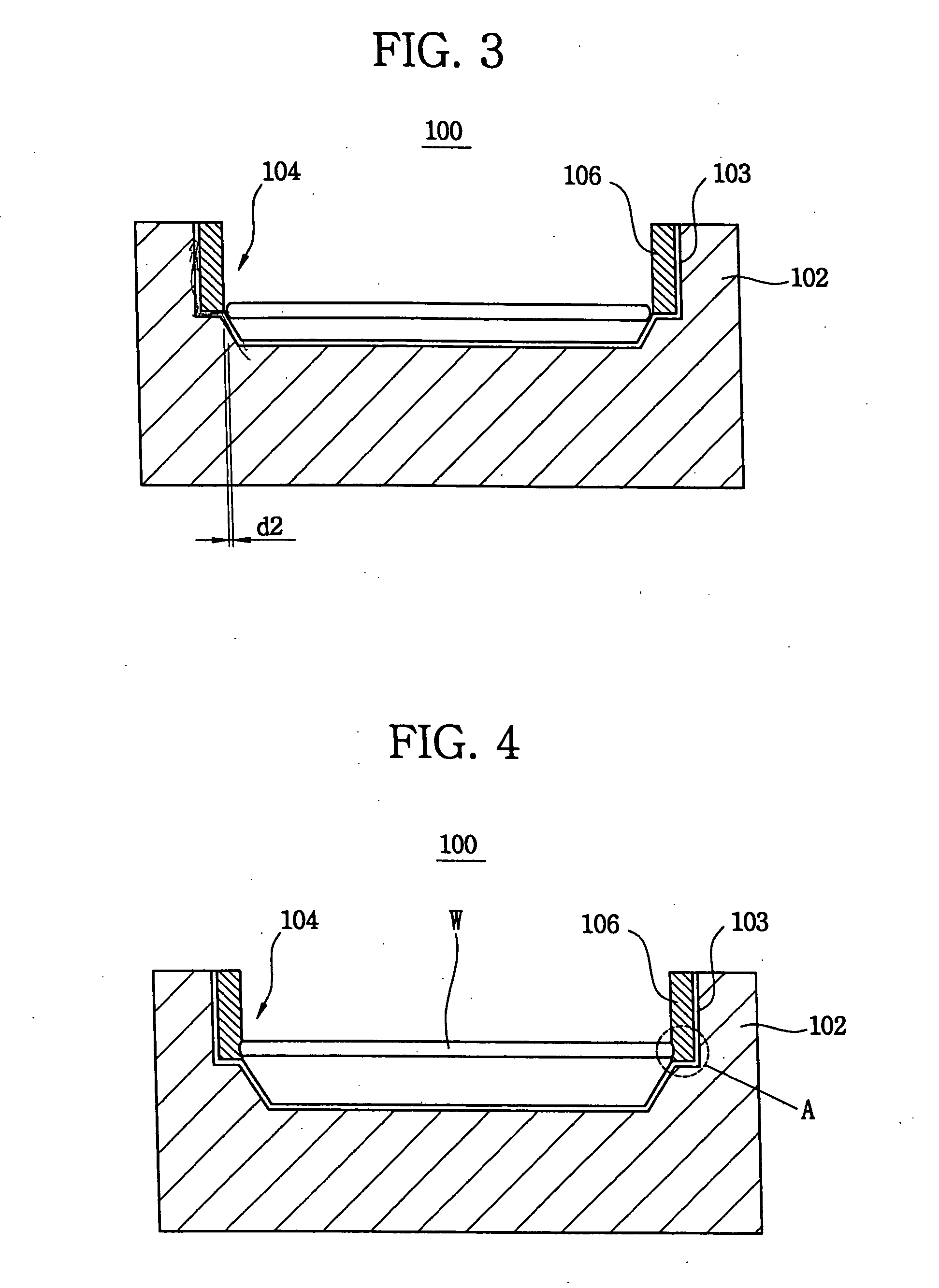

Susceptor and deposition apparatus including the same

InactiveUS20050016470A1Minimize physical impactMinimizing slip dislocationDiffusion/dopingSemiconductor/solid-state device manufacturingSusceptorEngineering

A susceptor for use in a deposition apparatus includes a recess in which a wafer is received, and a stress-reducing bumper disposed along the side of the recess. The stress-reducing bumper is of material having ductility at a relatively high temperature. Therefore, when the wafer contacts the stress-reducing bumper, such as may occur due to thermal expansion of the wafer during processing, the force of the impact on the wafer is minimized by an elastic deformation of the stress-reducing bumper. As a result, defects, such as slip dislocations at the outer peripheral edge of the wafer, are prevented.

Owner:SAMSUNG ELECTRONICS CO LTD

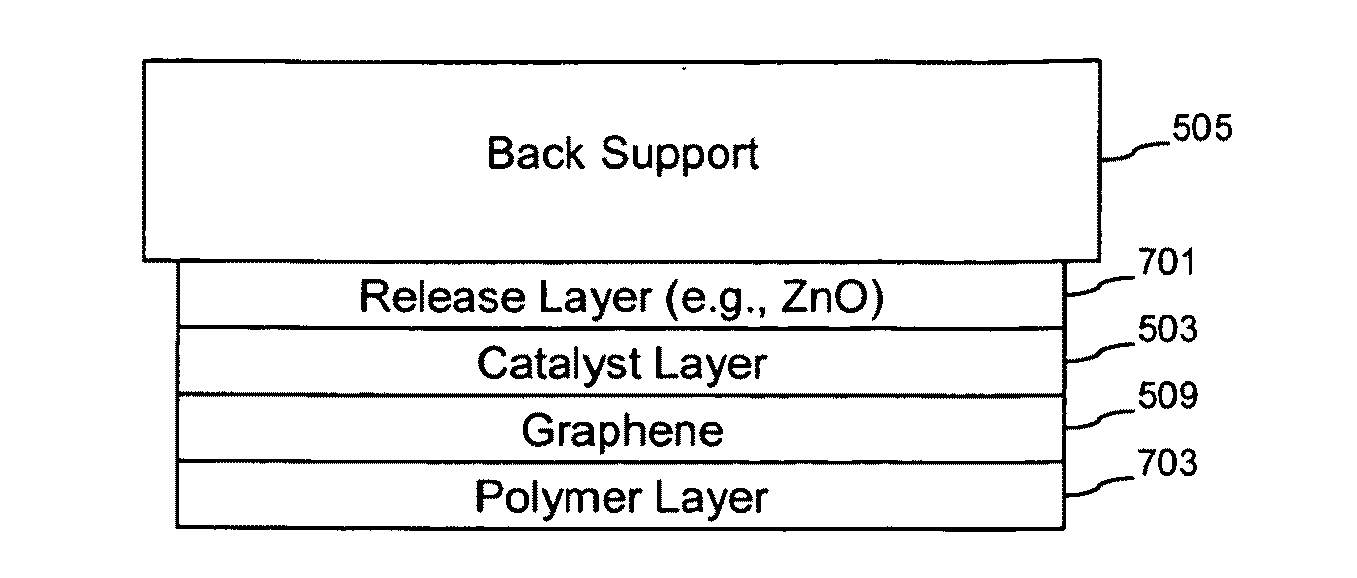

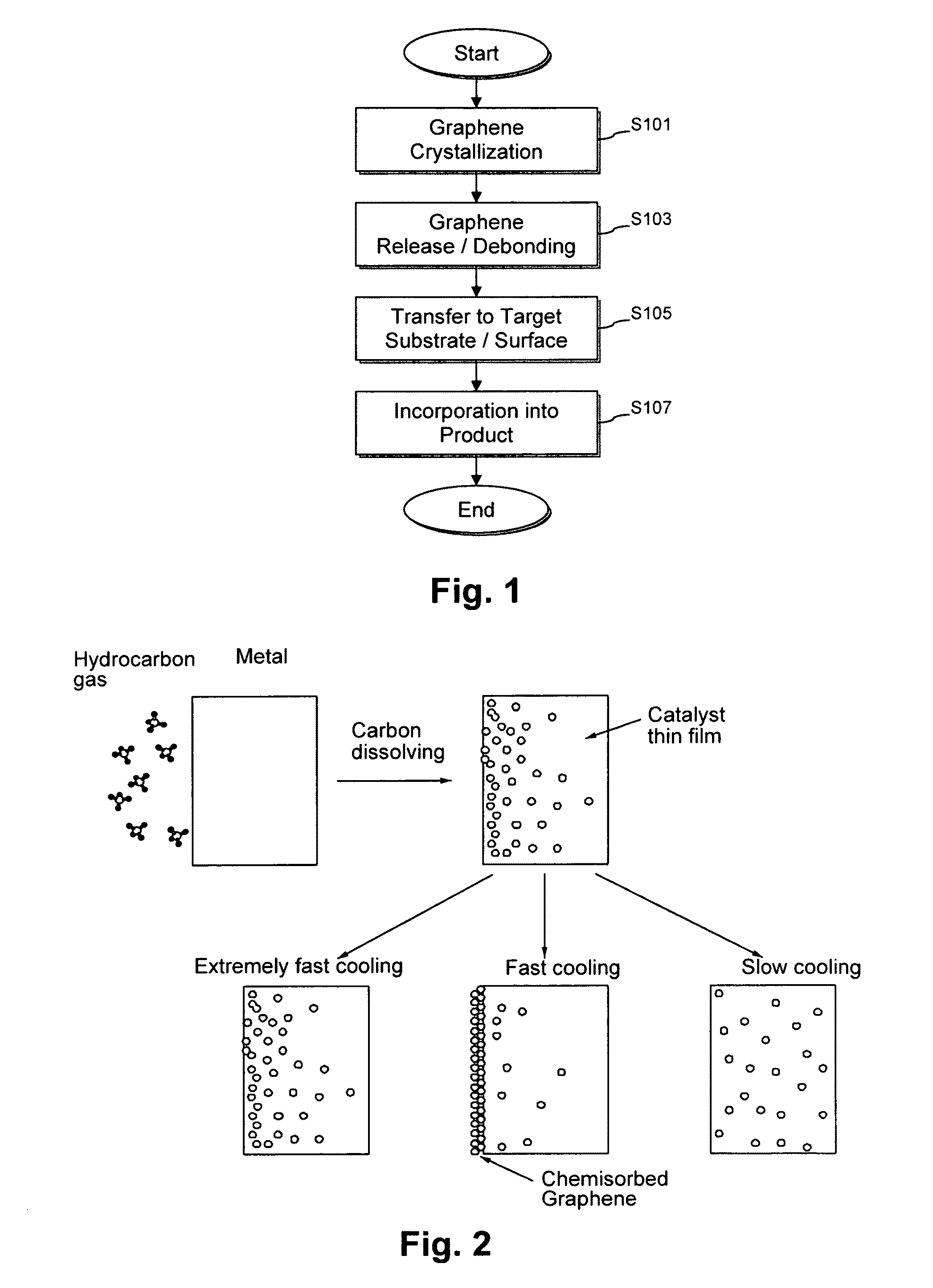

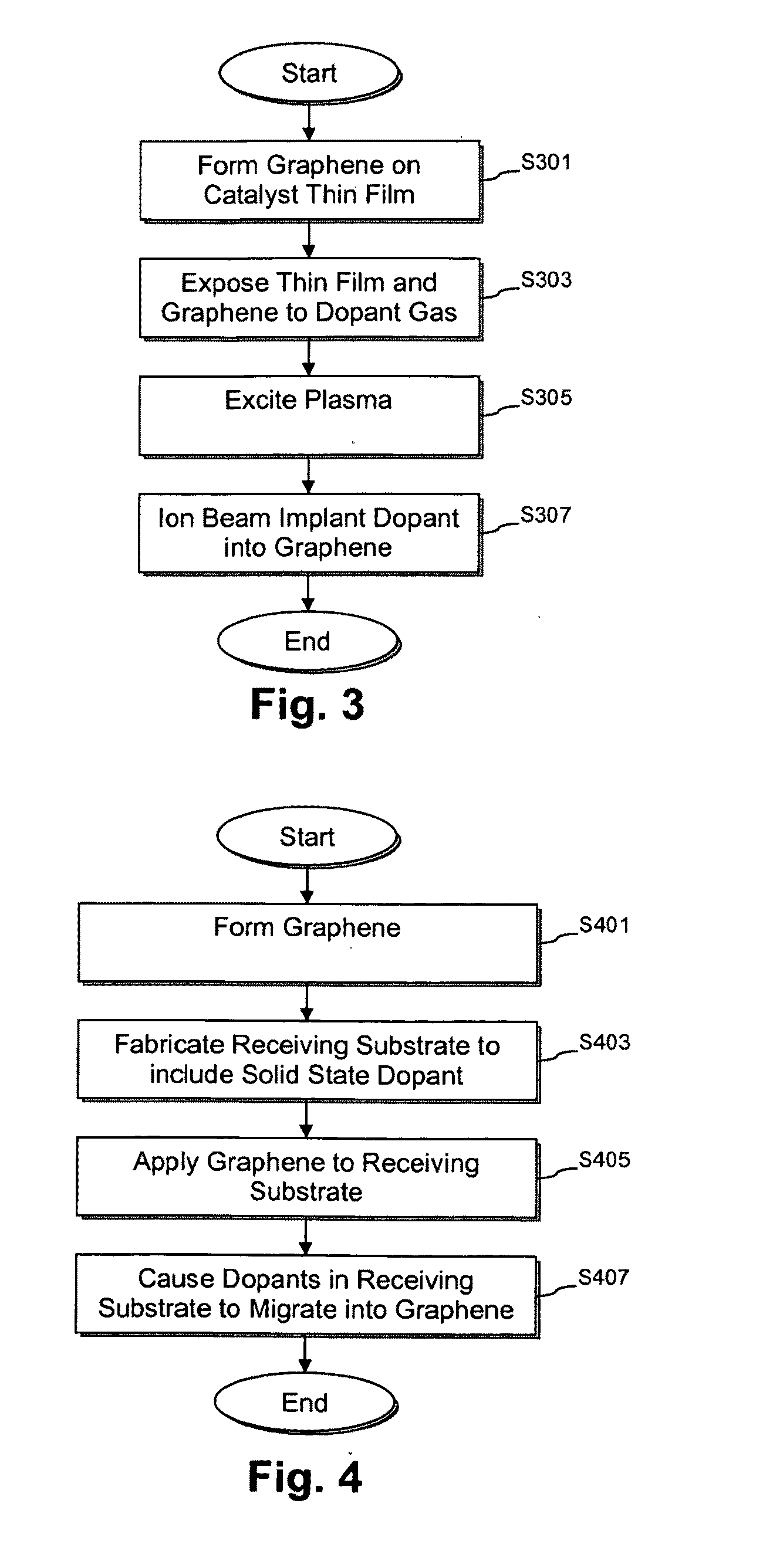

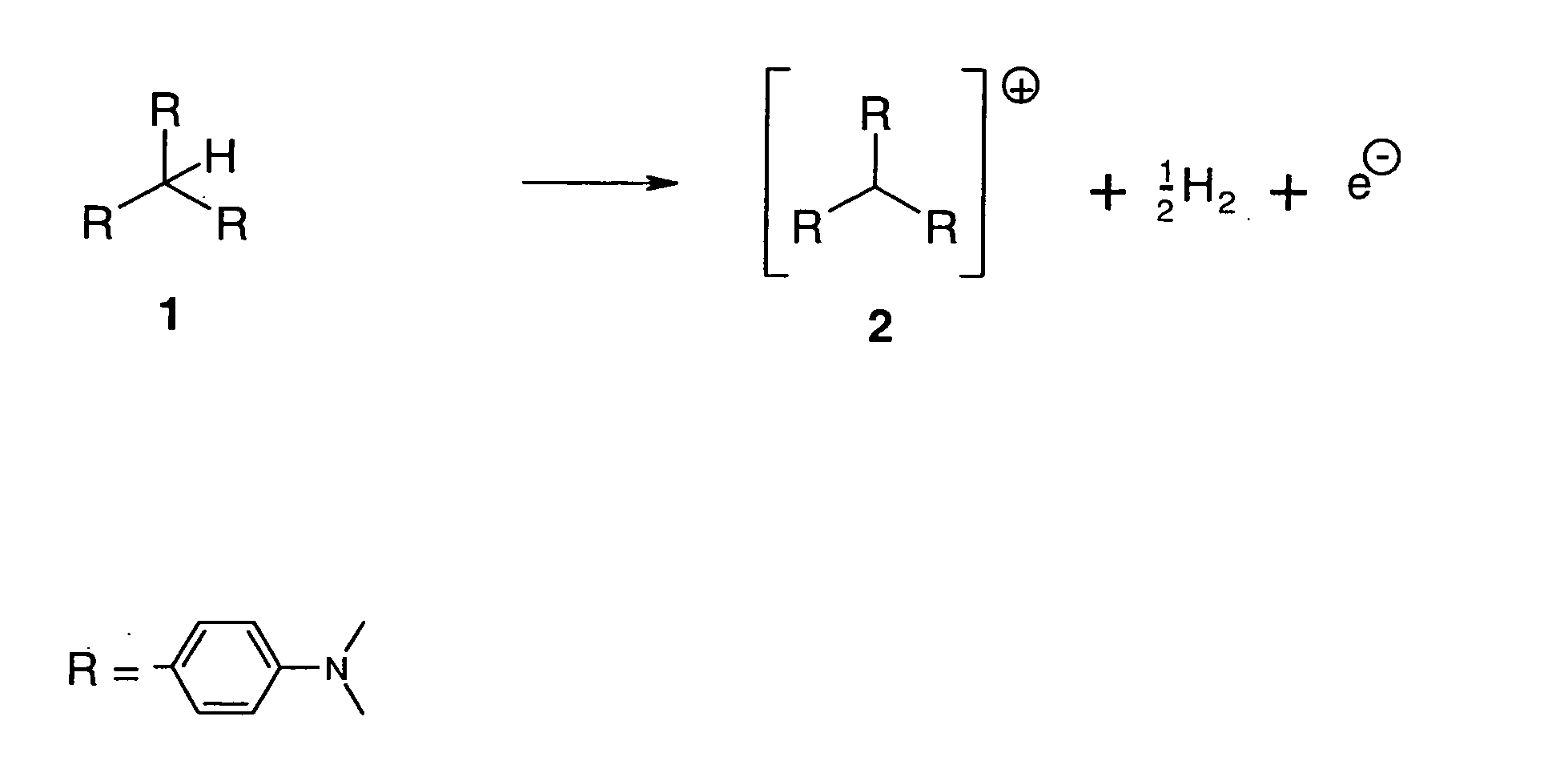

Large area deposition and doping of graphene, and products including the same

InactiveUS20110030991A1Reduced dimensionGood effectMaterial nanotechnologyNon-insulated conductorsConductive coatingTransmittance

Certain example embodiments of this invention relate to the use of graphene as a transparent conductive coating (TCC). In certain example embodiments, graphene thin films grown on large areas hetero-epitaxially, e.g., on a catalyst thin film, from a hydrocarbon gas (such as, for example, C2H2, CH4, or the like). The graphene thin films of certain example embodiments may be doped or undoped. In certain example embodiments, graphene thin films, once formed, may be lifted off of their carrier substrates and transferred to receiving substrates, e.g., for inclusion in an intermediate or final product. Graphene grown, lifted, and transferred in this way may exhibit low sheet resistances (e.g., less than 150 ohms / square and lower when doped) and high transmission values (e.g., at least in the visible and infrared spectra).

Owner:GUARDIAN GLASS LLC

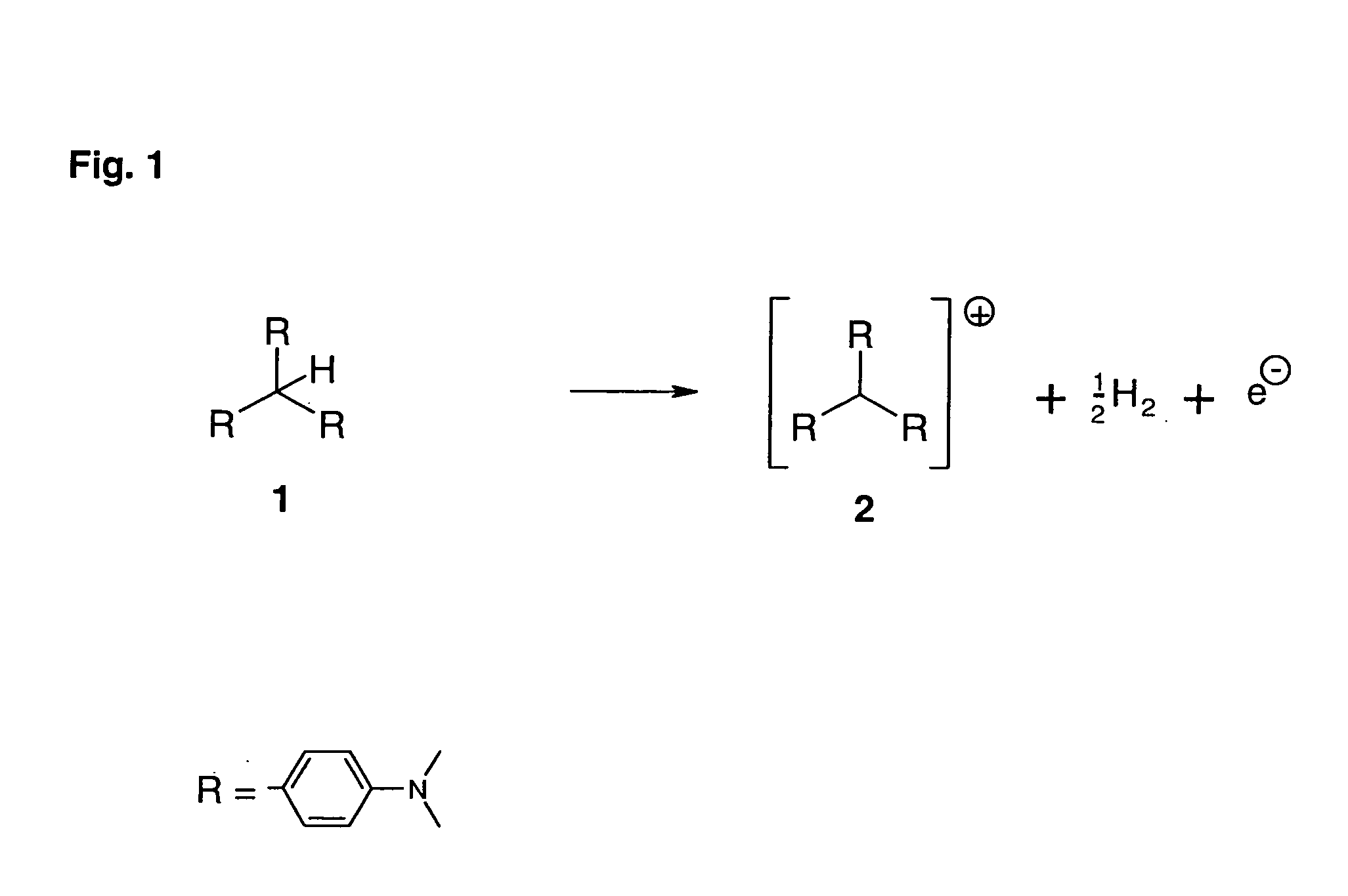

Doped organic semiconductor materials and process for their preparation

ActiveUS20050061232A1Simple materialHigh light efficiencyOrganic chemistryFinal product manufactureSemiconductor materialsCharge carrier mobility

The present invention relates to a process for the preparation of doped organic semiconductor materials having an increased charge carrier density and effective charge carrier mobility, by doping with a dopant, a process in which after mixing the dopant into the organic semiconductor material, hydrogen, carbon monoxide, nitrogen or hydroxyl radicals are split off and at least one electron is transferred to the semiconductor material or from the semiconductor material. The process is distinguished by the fact that an uncharged organic compound is used as dopant. Doped organic semiconductor materials are obtainable by one of the processes. The semiconductor materials are distinguished by the fact that the doped layer contains cations of at least one organic compound, the uncharged form of the organic compound being unstable in air.

Owner:NOVALED GMBH

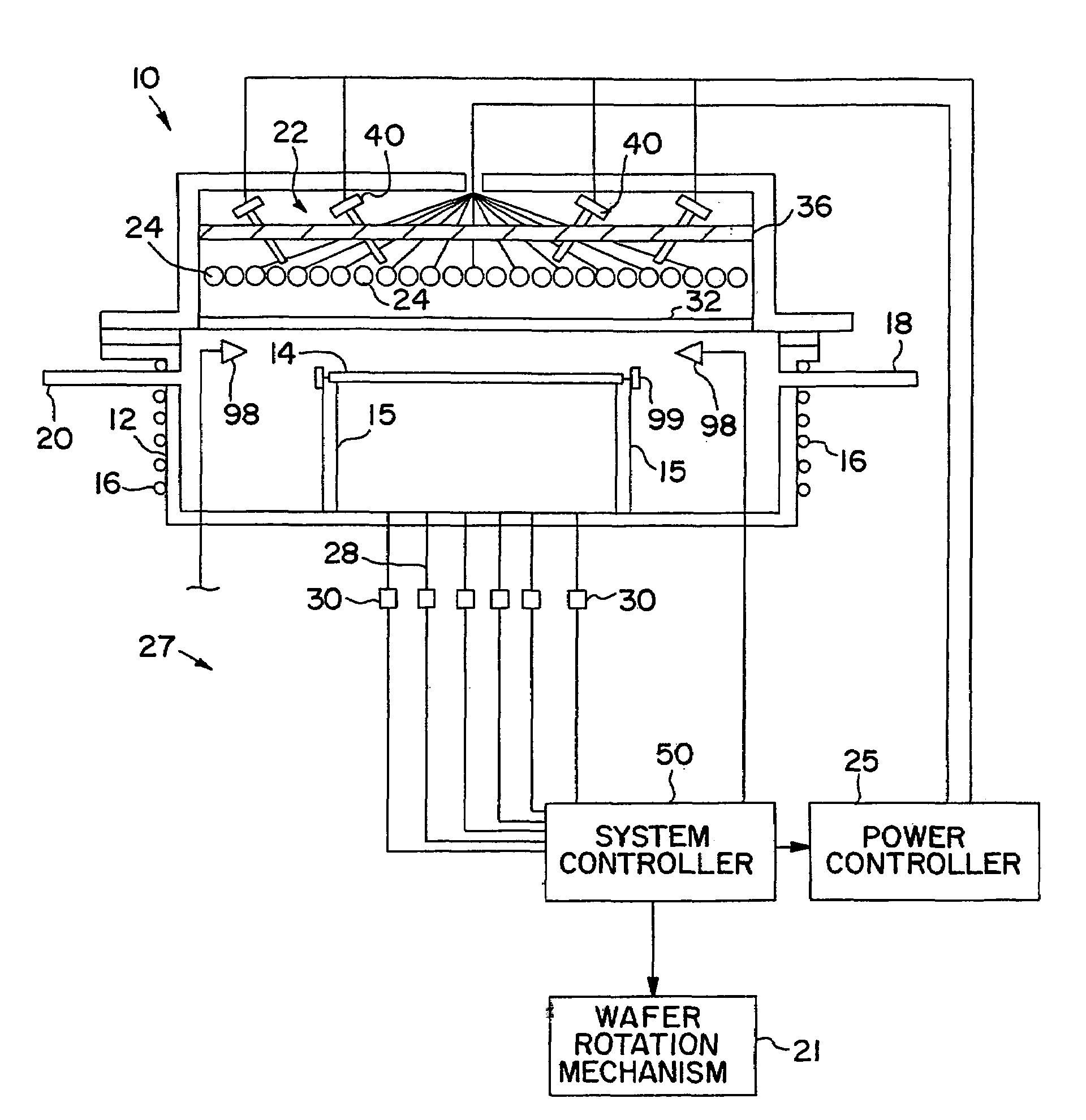

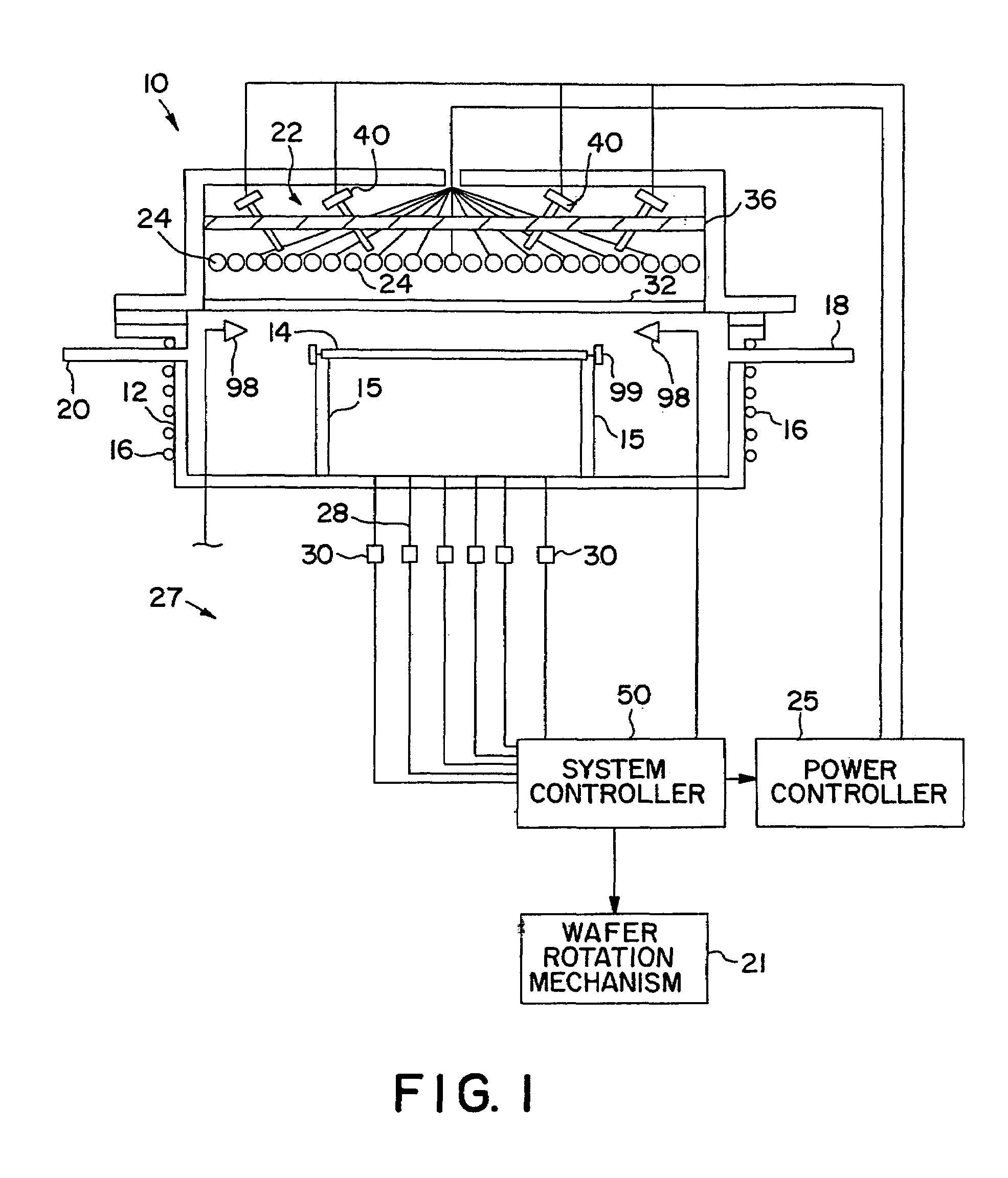

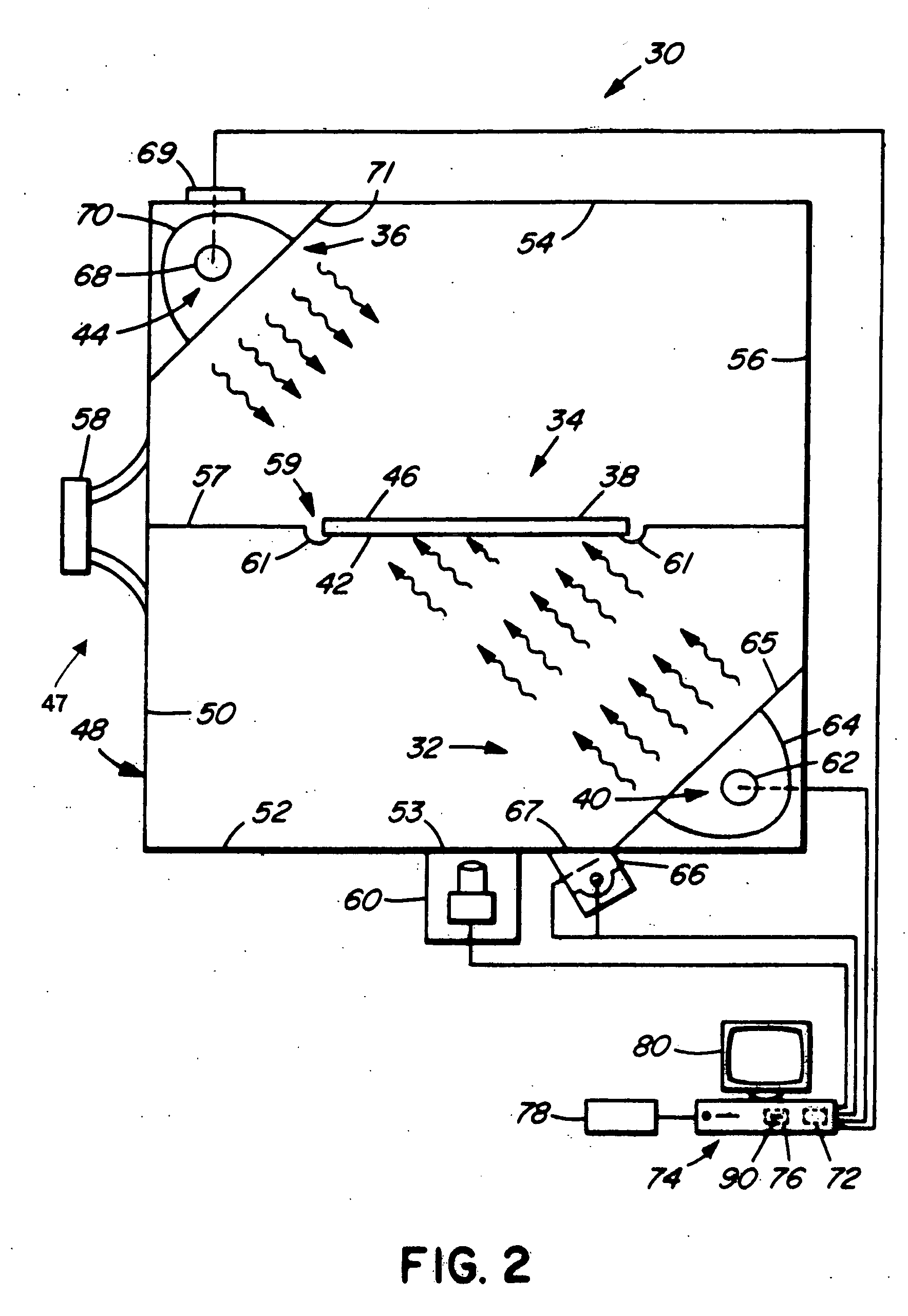

System and process for heating semiconductor wafers by optimizing absorption of electromagnetic energy

InactiveUS7015422B2Excessive heatingDrying solid materials with heatMuffle furnacesAngle of incidenceLight energy

Various processes for heating semiconductor wafers is disclosed. In particular, the present invention is directed to configuring light sources emitting light energy onto a wafer in order to optimize absorption of the energy by the wafer. Optimization is carried out by varying the angle of incidence of the light energy contacting the wafer, using multiple wavelengths of light, and configuring the light energy such that it contacts the wafer in a particular polarized state. In one embodiment, the light energy can be emitted by a laser that is scanned over the surface of the wafer.

Owner:MATTSON TECHNOLOGY +1

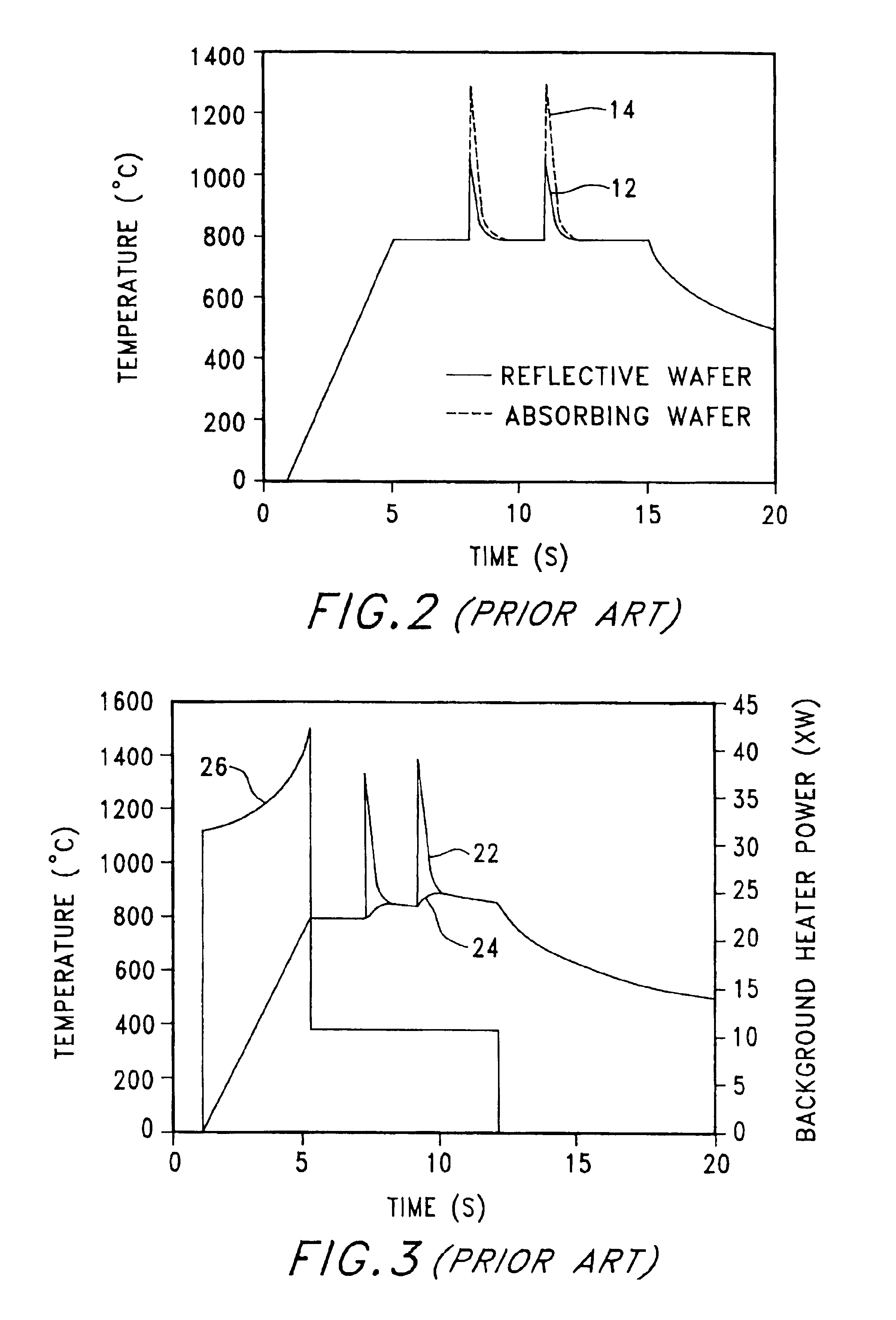

Pulsed processing semiconductor heating methods using combinations of heating sources

InactiveUS6951996B2Heating fastIncrease temperatureMuffle furnacesSemiconductor/solid-state device manufacturingPulse parameterEngineering

Pulsed processing methods and systems for heating objects such as semiconductor substrates feature process control for multi-pulse processing of a single substrate, or single or multi-pulse processing of different substrates having different physical properties. Heat is applied a controllable way to the object during a background heating mode, thereby selectively heating the object to at least generally produce a temperature rise throughout the object during background heating. A first surface of the object is heated in a pulsed heating mode by subjecting it to at least a first pulse of energy. Background heating is controlled in timed relation to the first pulse. A first temperature response of the object to the first energy pulse may be sensed and used to establish at least a second set of pulse parameters for at least a second energy pulse to at least partially produce a target condition.

Owner:MATTSON TECHNOLOGY +1

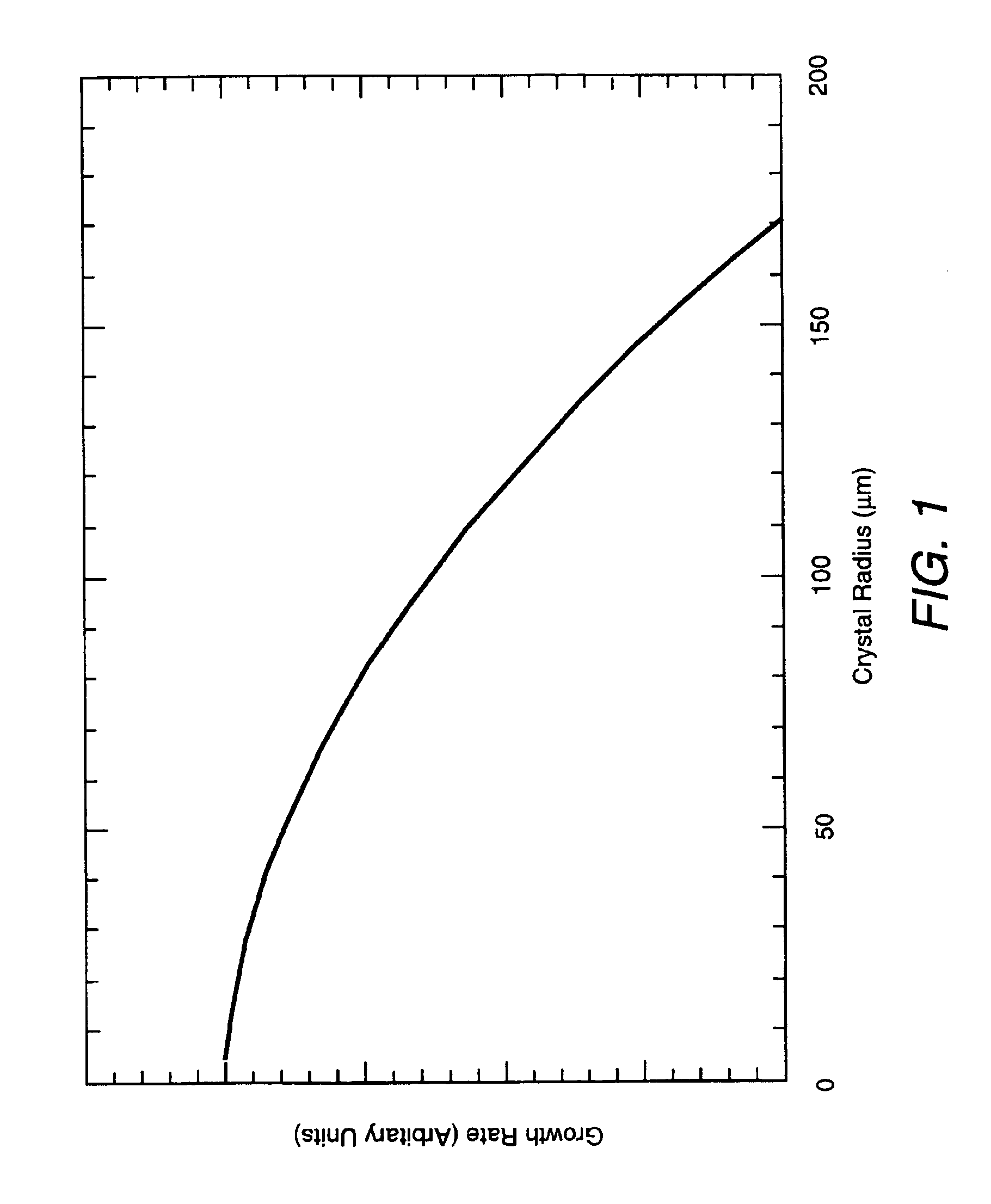

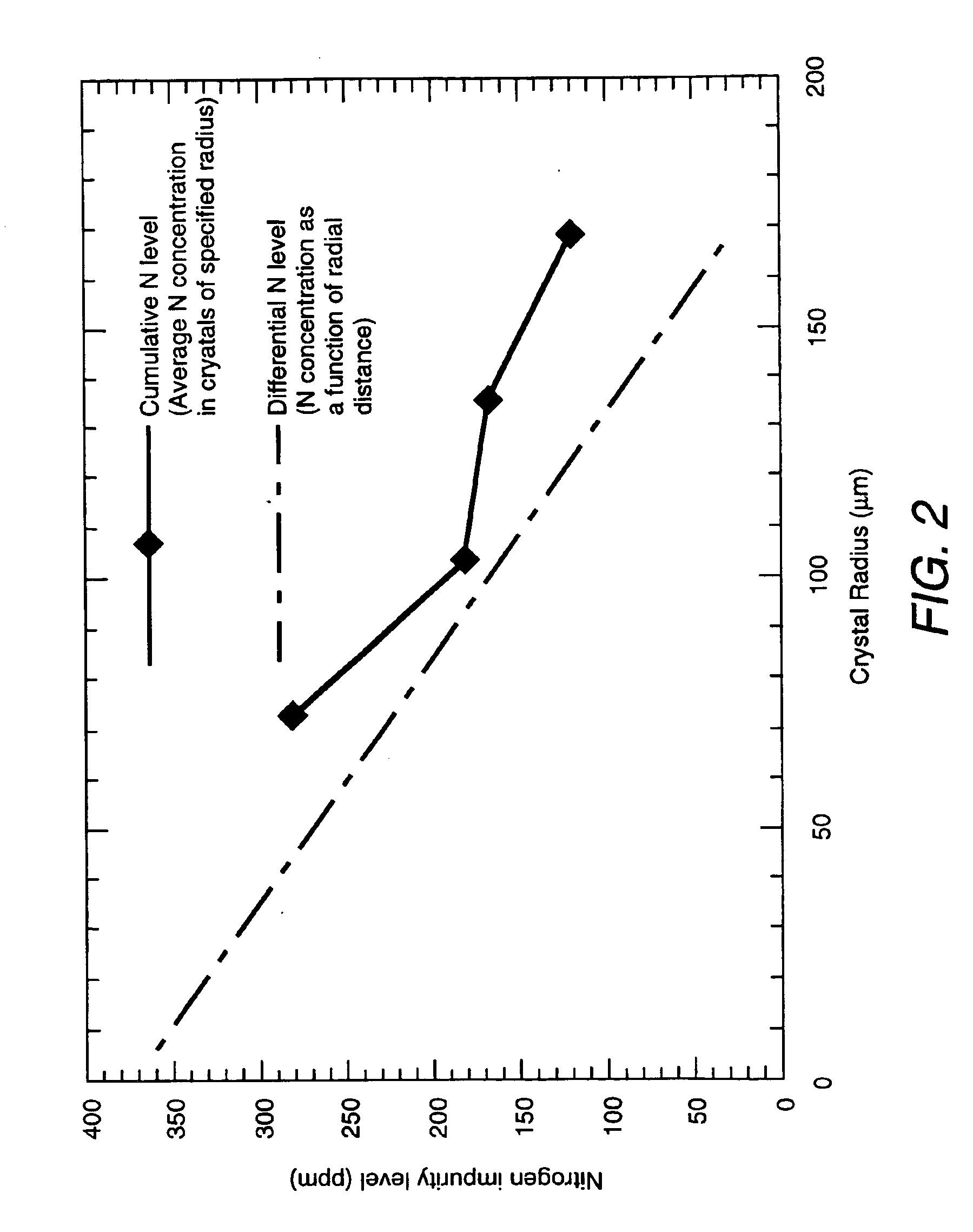

Surface impurity-enriched diamond and method of making

InactiveUS6887144B2Increases compressive fracture strengthHigh breaking strengthPolycrystalline material growthUltra-high pressure processesDopantMicrometer

An element-doped diamond crystal is disclosed herein. The crystal includes at least one dopant element which has a greater concentration toward or near an outermost surface of the crystal than in the center of the crystal. The concentration of the dopant element is at a local minimum at least about 5 micrometers below the surface. The concentration-profile of the dopant element for these diamond crystals causes an expansion of the diamond lattice, thereby generating tangential compressive stresses at the surface of the diamond crystal. These stresses beneficially increase the compressive fracture strength of the diamond.

Owner:DIAMOND INNOVATIONS INC

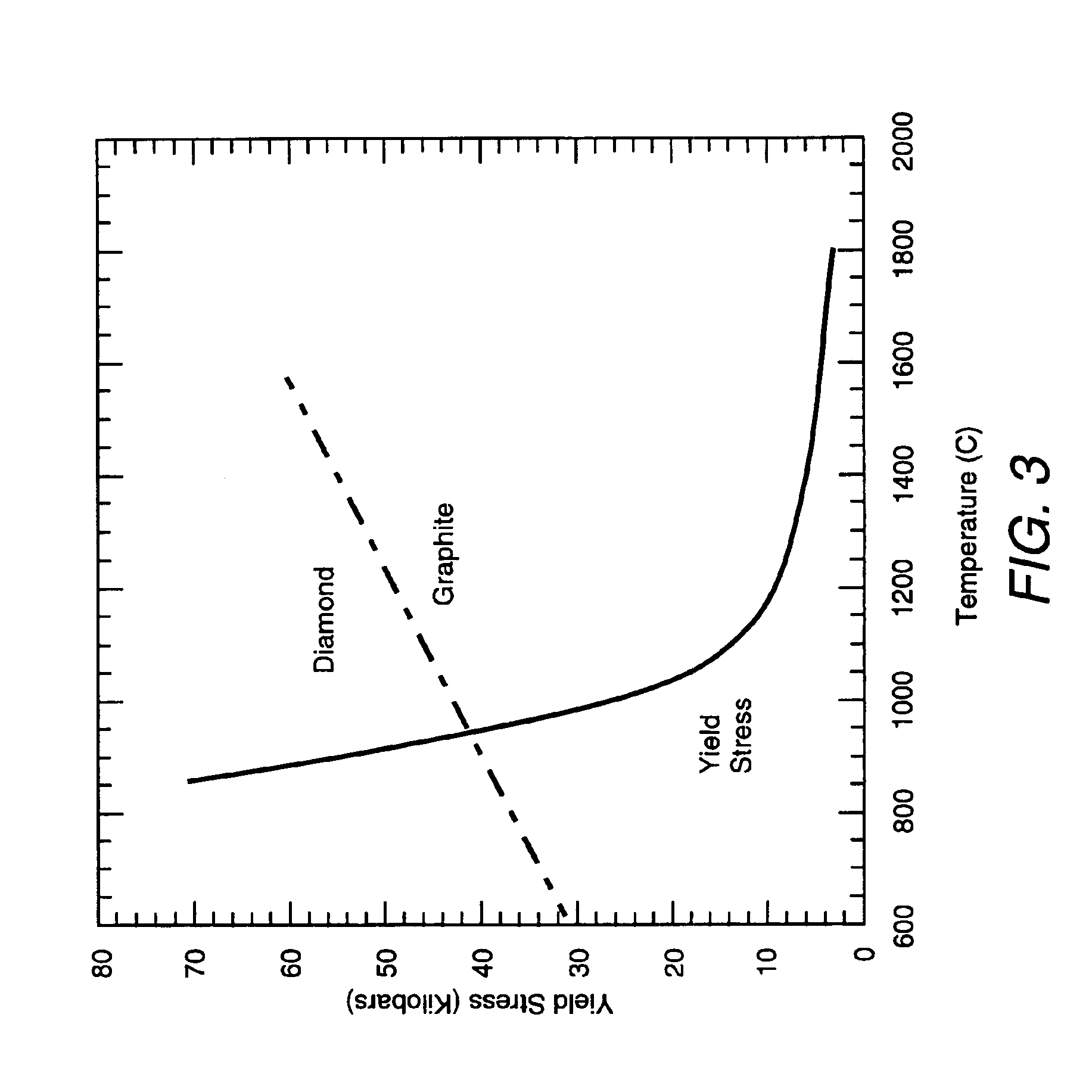

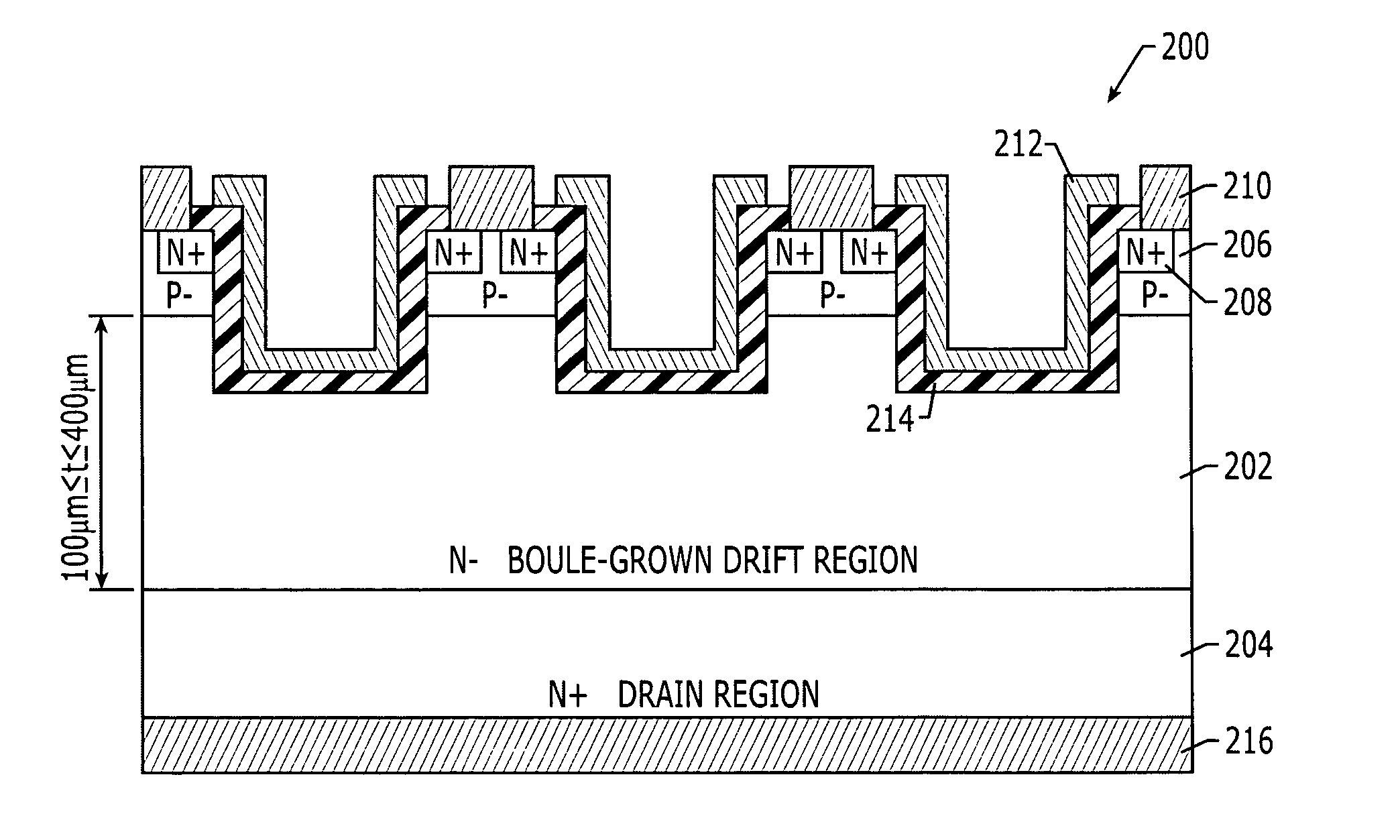

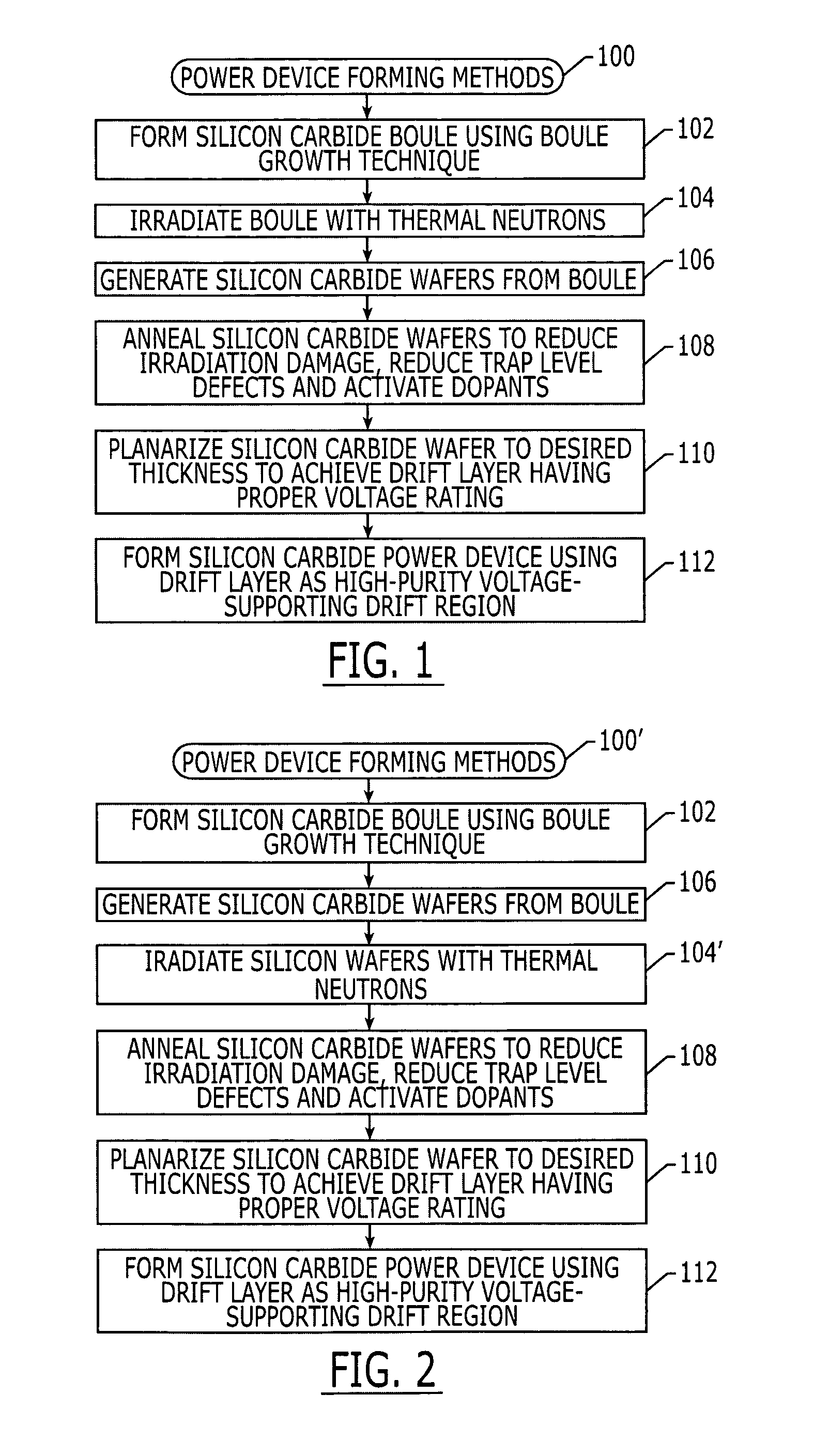

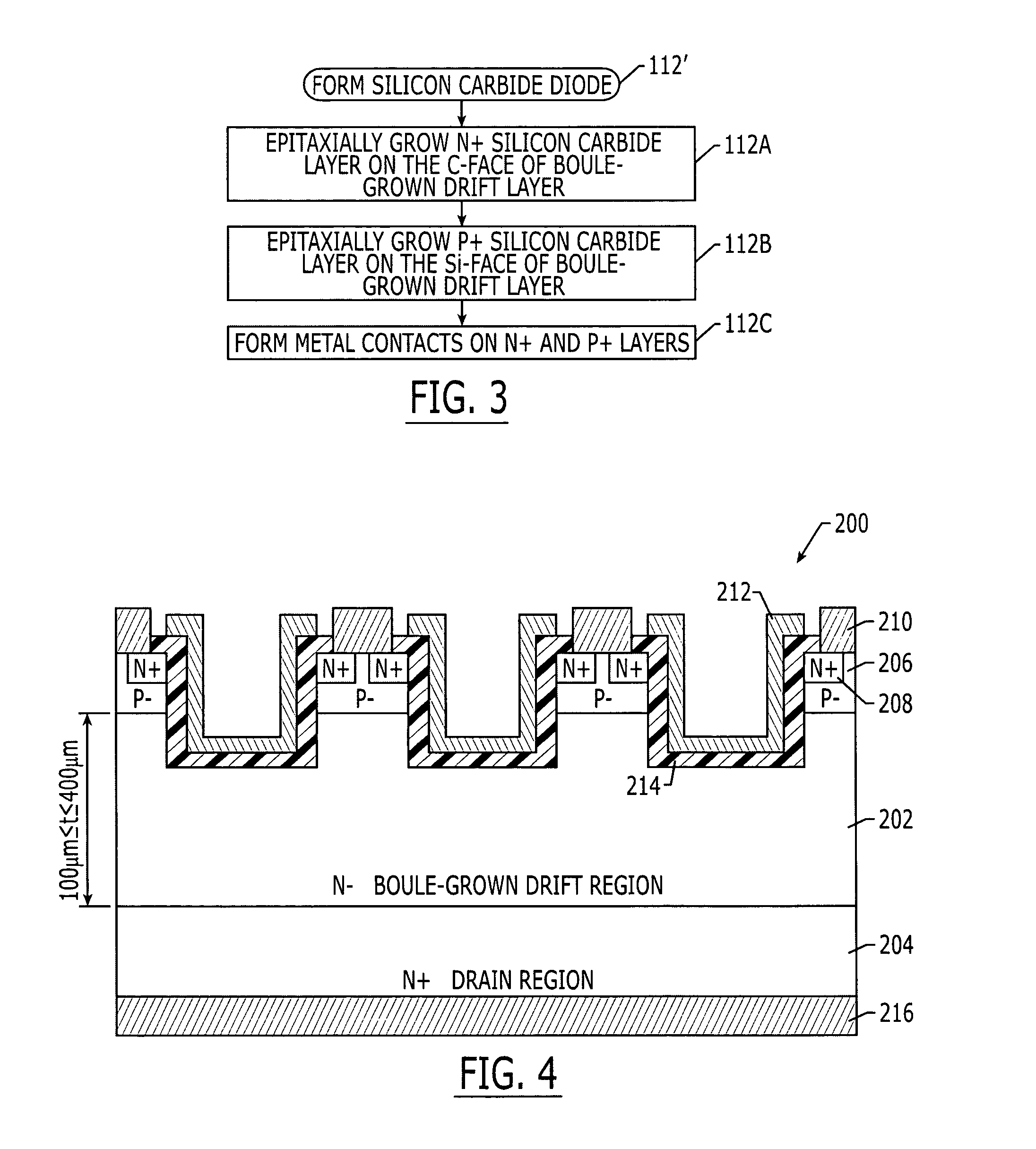

Methods of forming power semiconductor devices using boule-grown silicon carbide drift layers and power semiconductor devices formed thereby

ActiveUS20050082542A1High dopingPolycrystalline material growthDiffusion/dopingPower semiconductor deviceDopant

Methods of forming high voltage silicon carbide power devices utilize high purity silicon carbide drift layers that are derived from high purity silicon carbide wafer material, instead of prohibitively costly epitaxially grown silicon carbide layers. The methods include forming both minority carrier and majority carrier power devices that can support greater than 10 kV blocking voltages, using drift layers having thicknesses greater than about 100 um. The drift layers are formed as boule-grown silicon carbide drift layers having a net n-type dopant concentration therein that is less than about 2×1015 cm−3. These n-type dopant concentrations can be achieved using neutron transmutation doping (NTD) techniques.

Owner:CREE INC

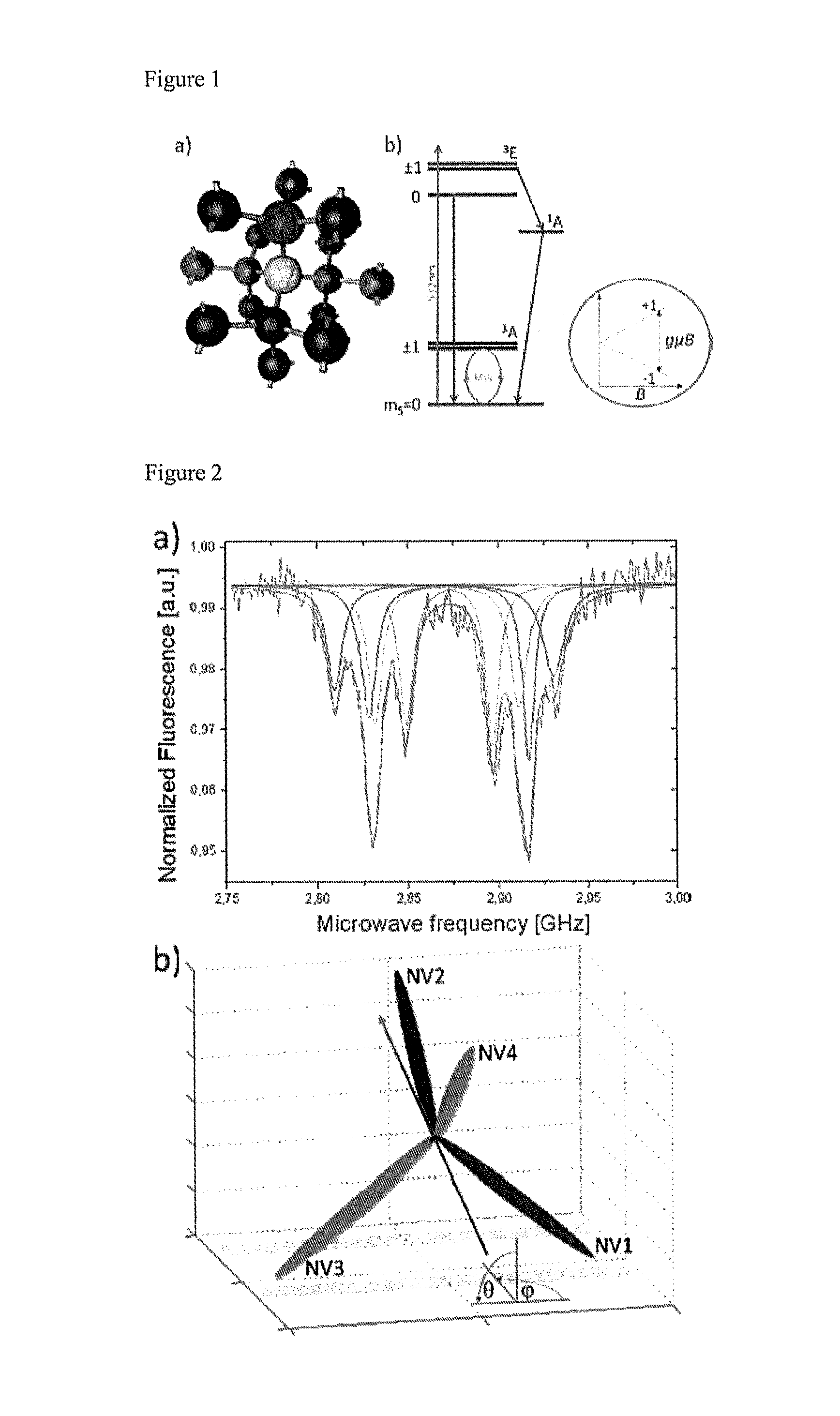

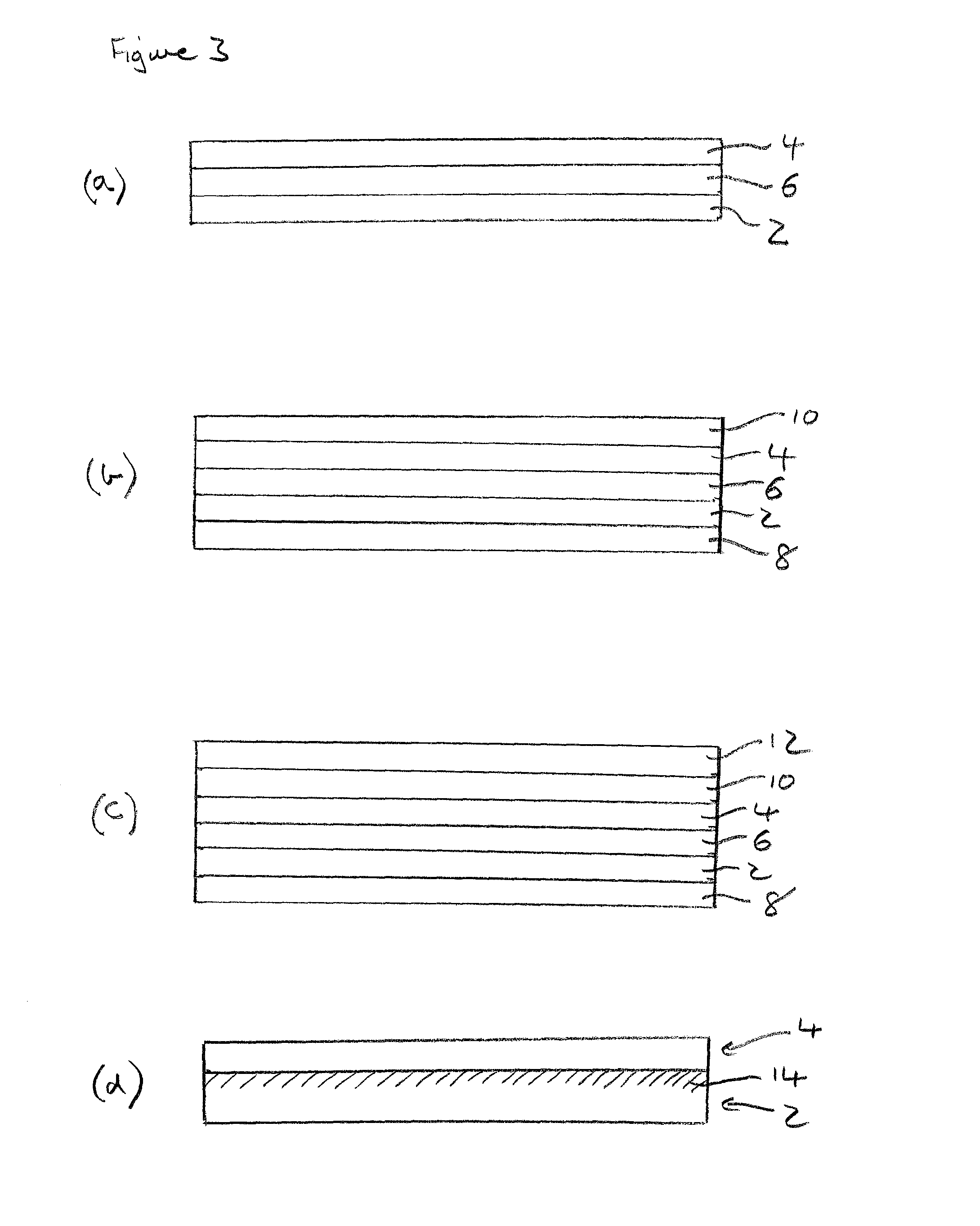

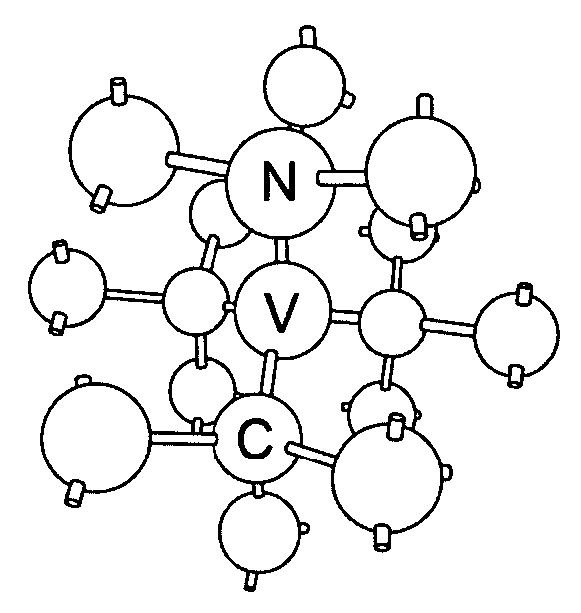

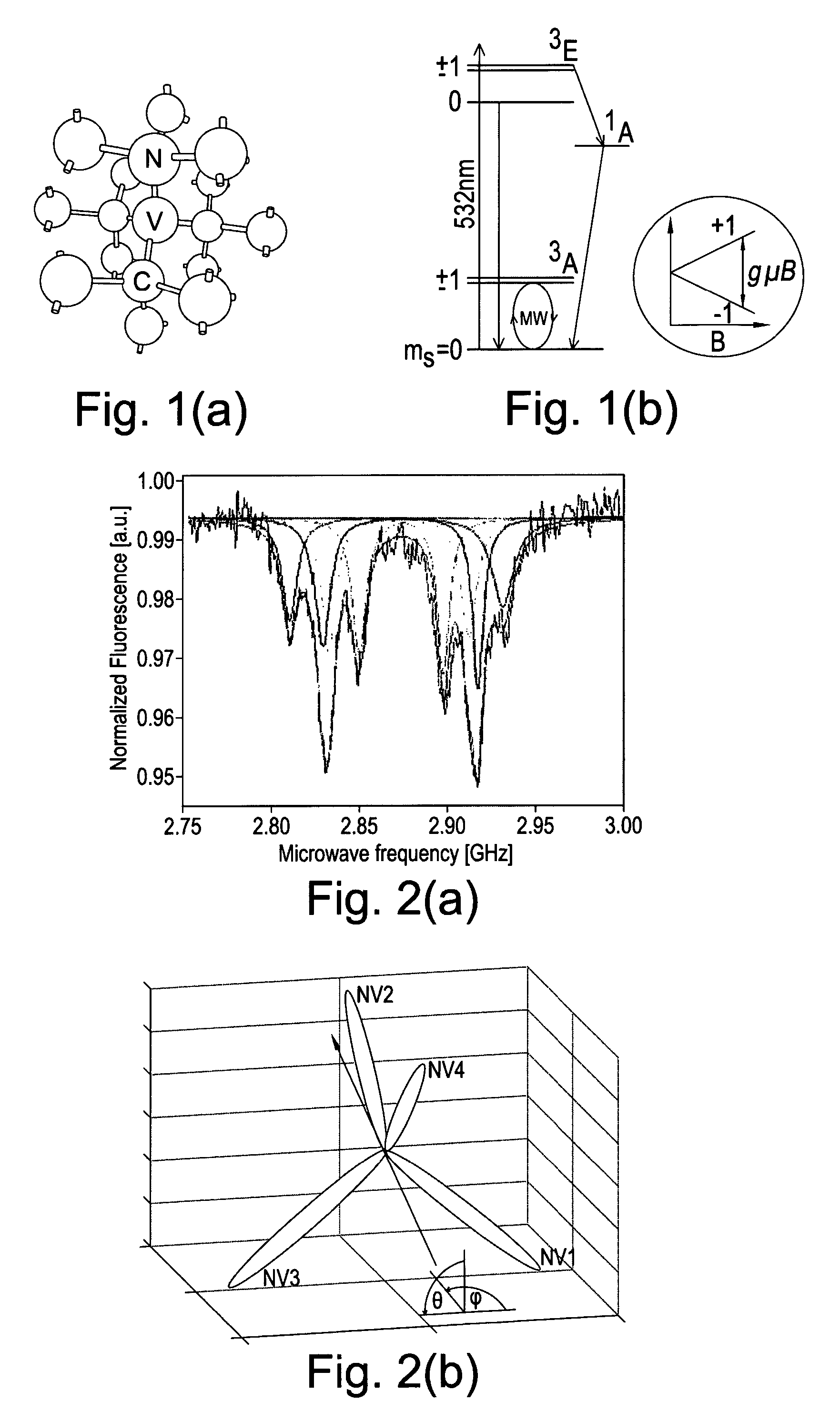

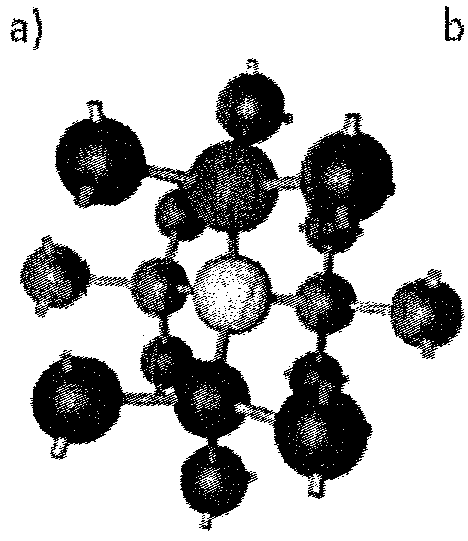

Diamond sensors, detectors, and quantum devices

ActiveUS20140037932A1High purityMinimizes strainQuantum computersPolycrystalline material growthElectron donorQuantum devices

A synthetic single crystal diamond material comprising: a first region of synthetic single crystal diamond material comprising a plurality of electron donor defects; a second region of synthetic single crystal diamond material comprising a plurality of quantum spin defects; and a third region of synthetic single crystal diamond material disposed between the first and second regions such that the first and second regions are spaced apart by the third region, wherein the second and third regions of synthetic single crystal diamond material have a lower concentration of electron donor defects than the first region of synthetic single crystal diamond material, and wherein the first and second regions are spaced apart by a distance in a range 10 nm to 100 μm which is sufficiently close to allow electrons to be donated from the first region of synthetic single crystal diamond material to the second region of synthetic single crystal diamond material thus forming negatively charged quantum spin defects in the second region of synthetic single crystal diamond material and positively charged defects in the first region of synthetic single crystal diamond material while being sufficiently far apart to reduce other coupling interactions between the first and second regions which would otherwise unduly reduce the decoherence time of the plurality of quantum spin defects and / or produce strain broaden of a spectral line width of the plurality of quantum spin defects in the second region of synthetic single crystal diamond material.

Owner:ELEMENT SIX LTD

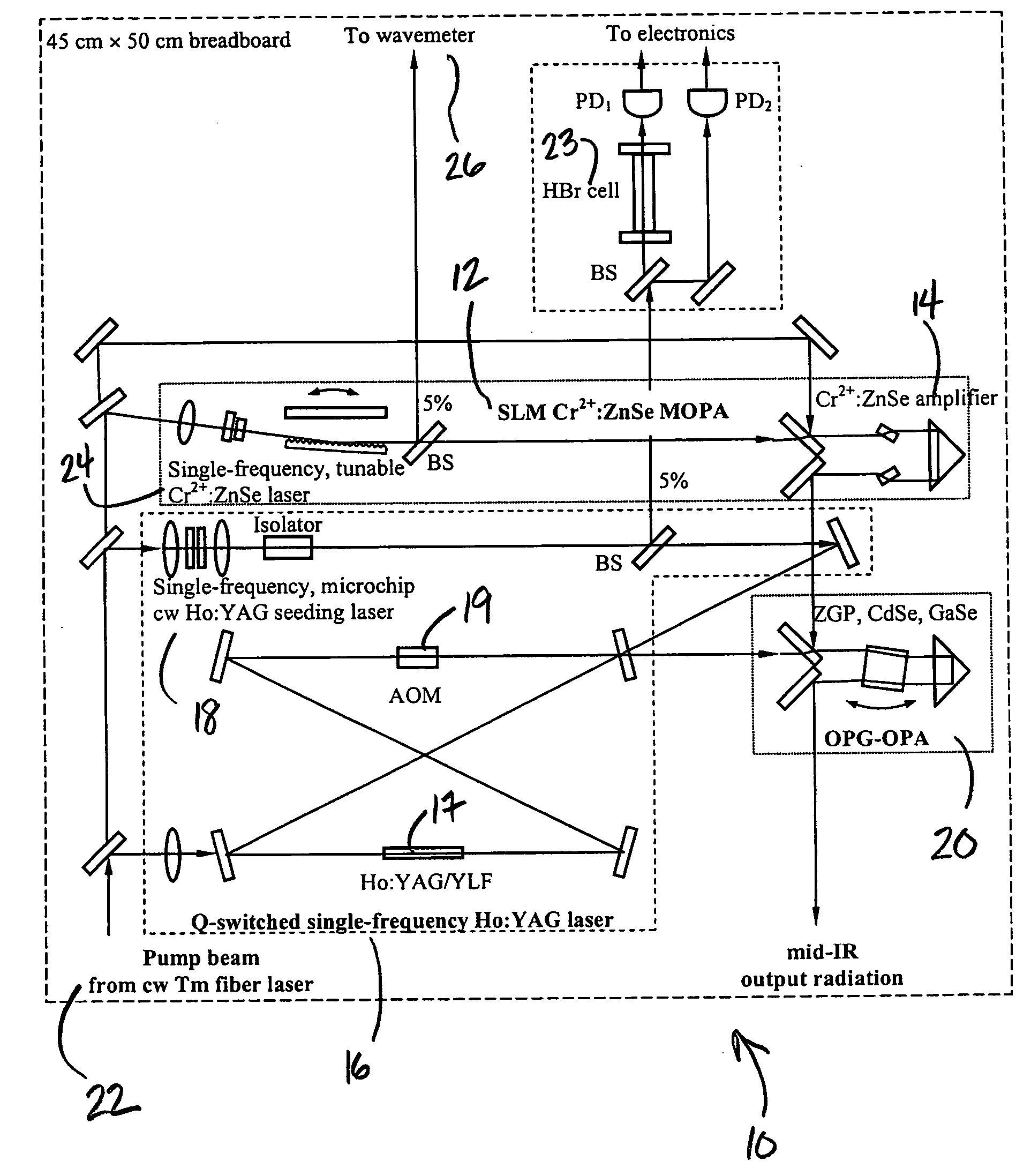

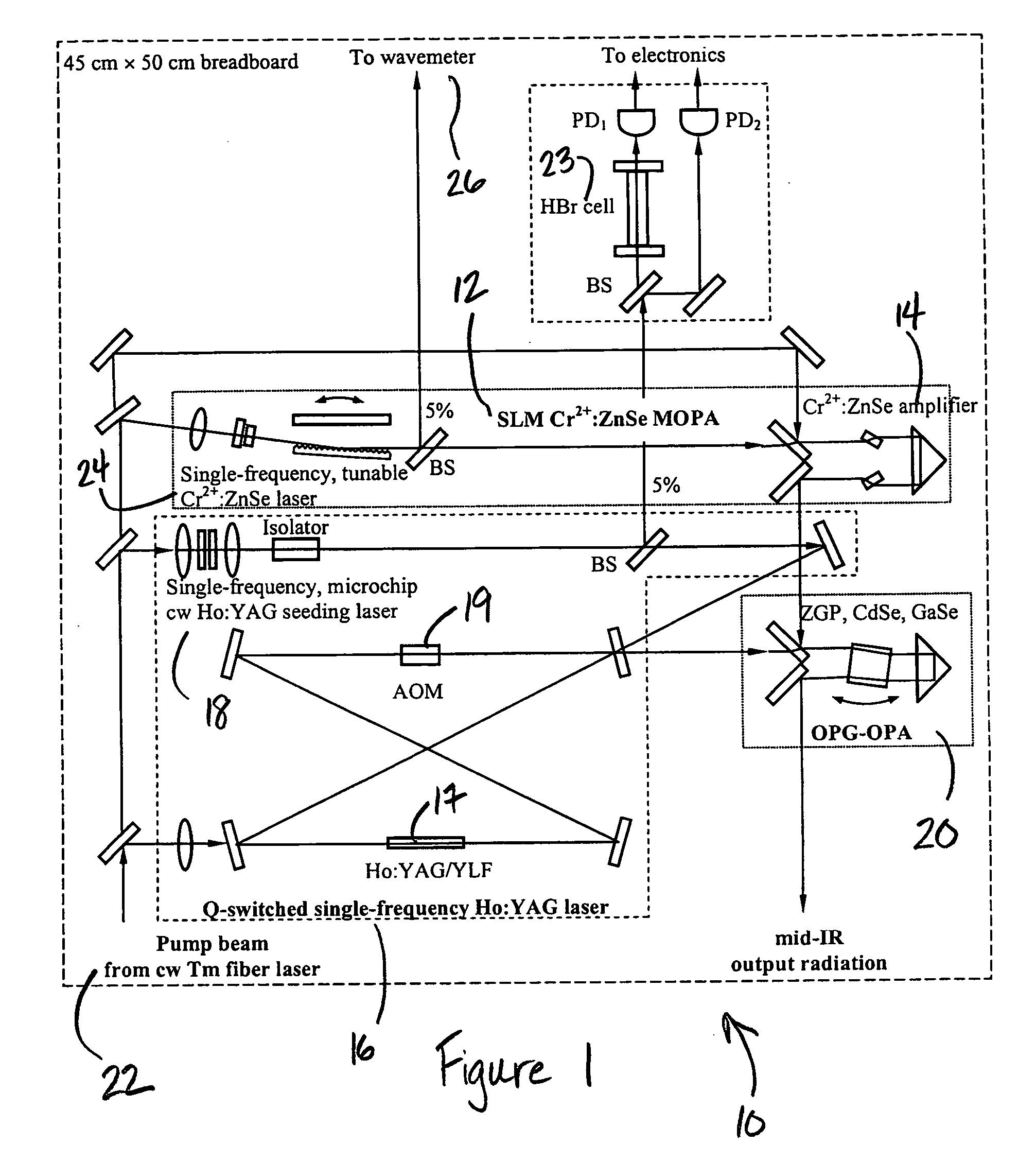

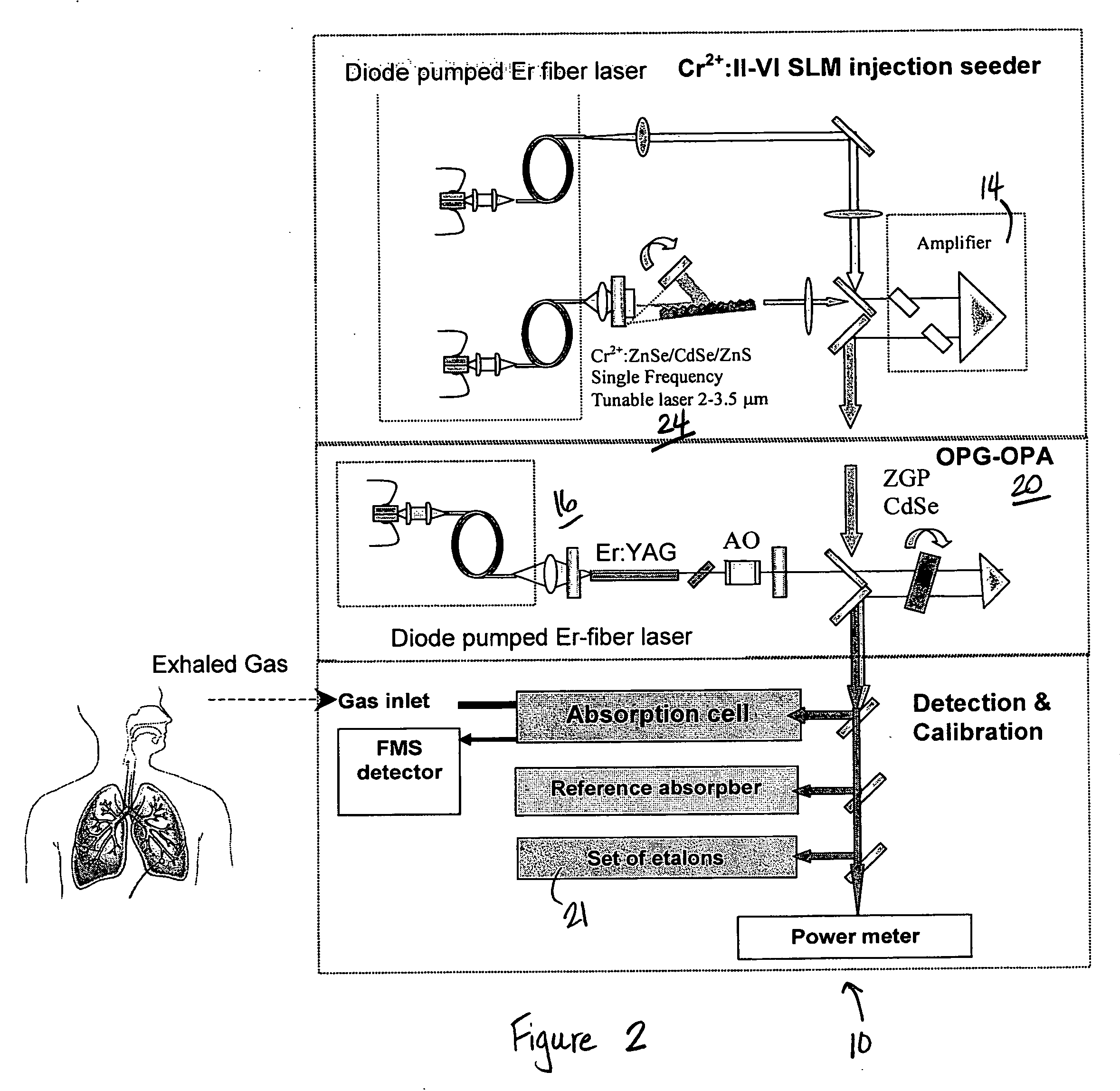

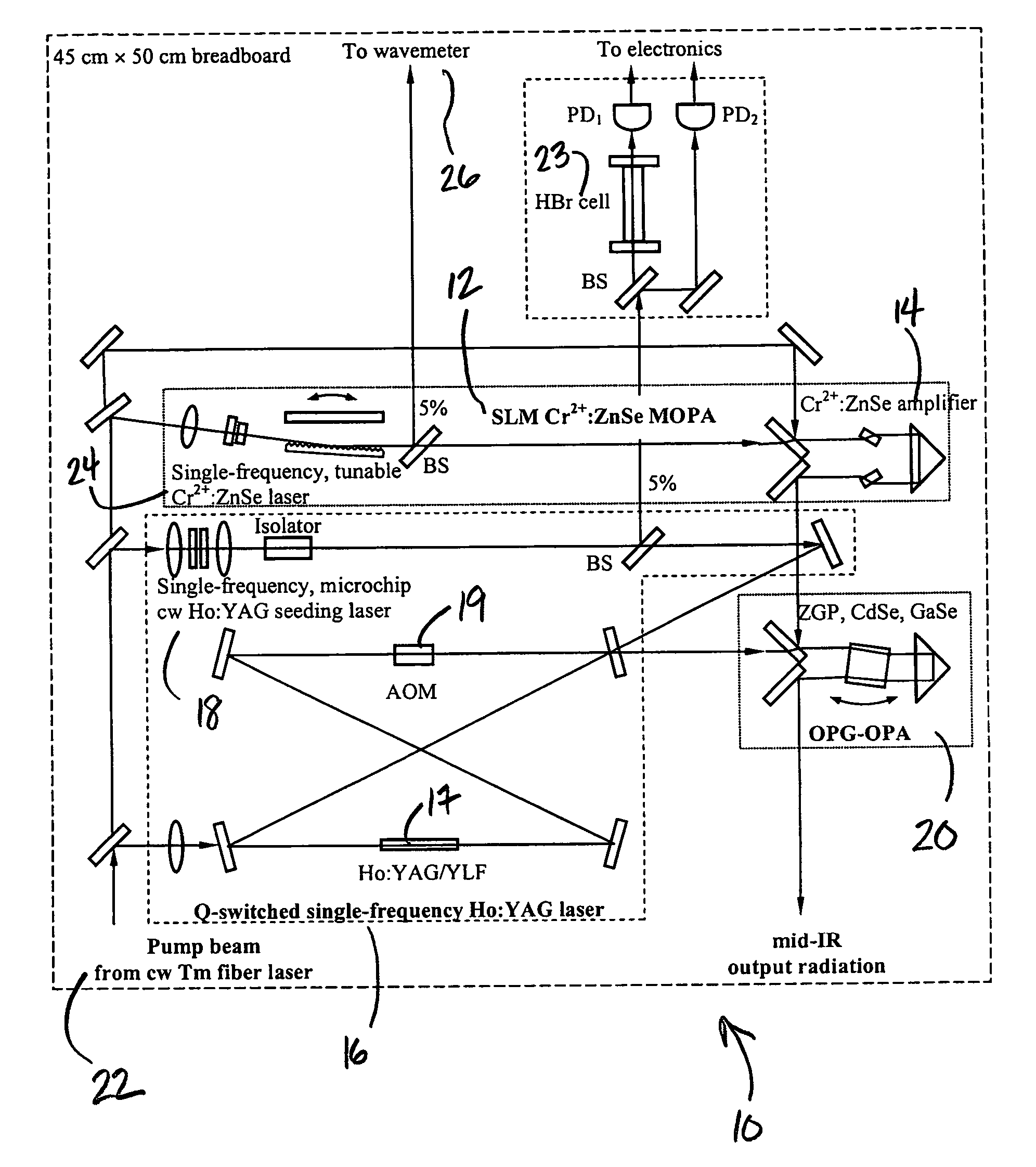

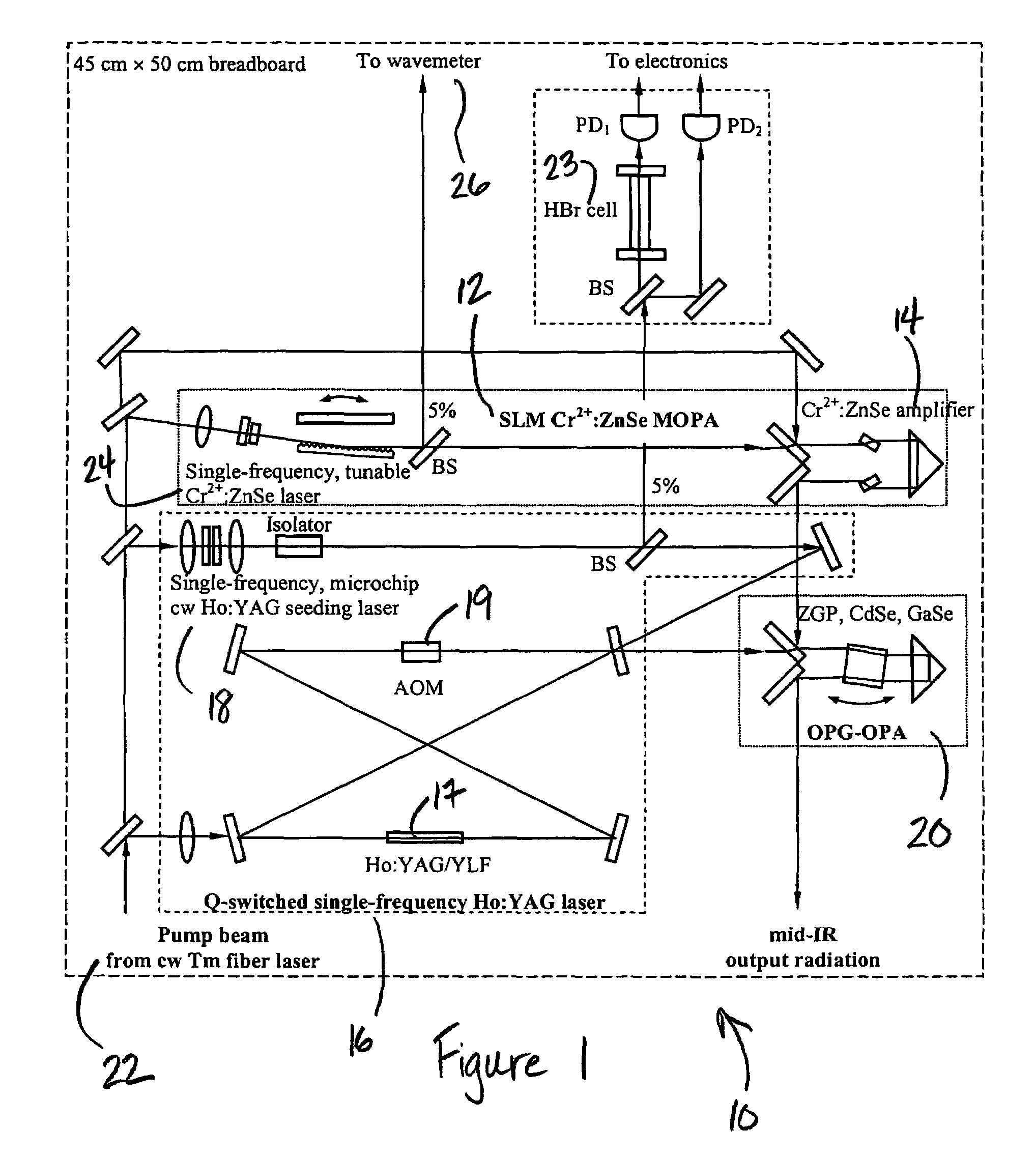

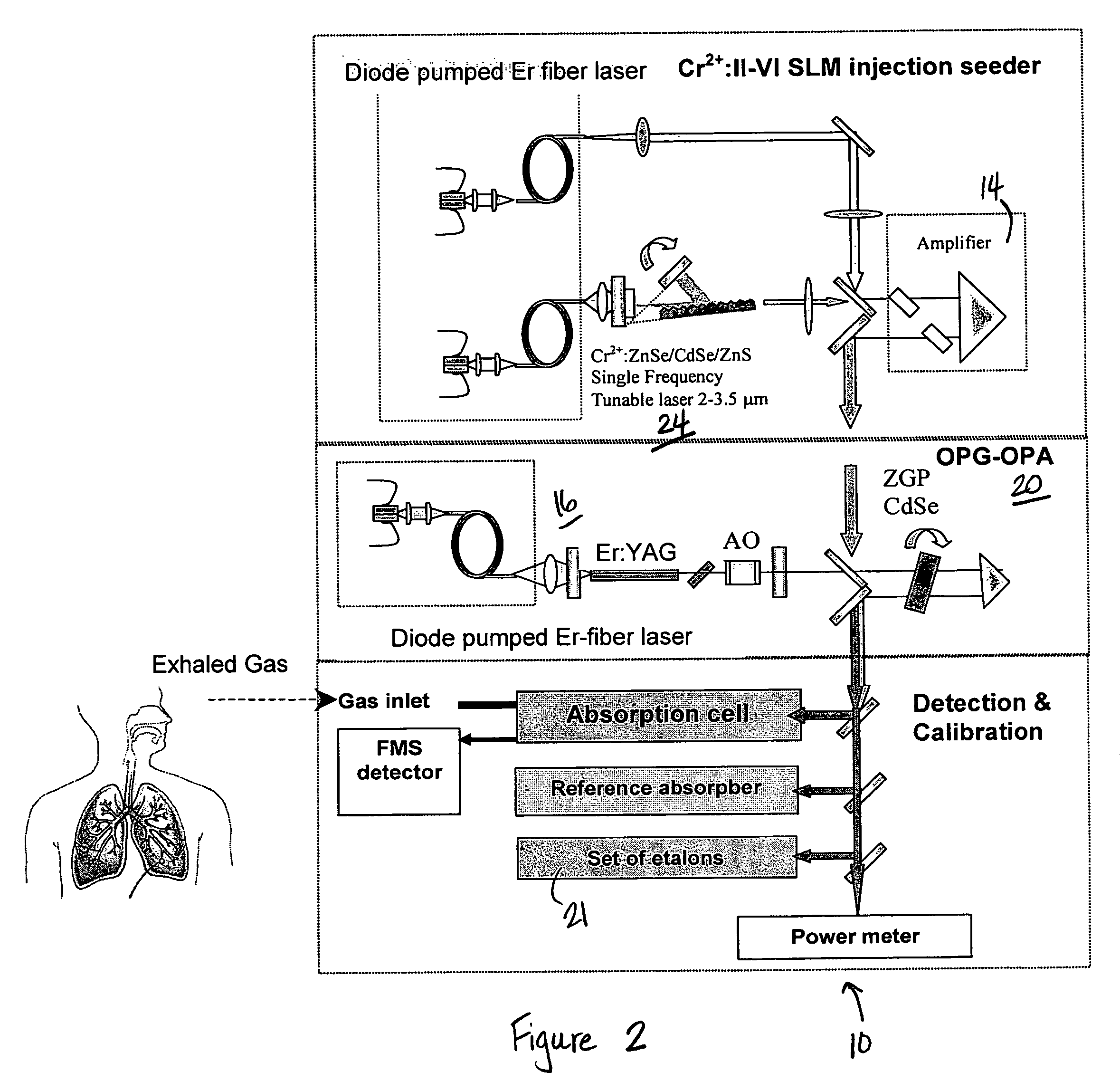

Mid-IR laser instrument for analyzing a gaseous sample and method for using the same

InactiveUS20070064748A1Wide tunabilityRapidly tuned SLM idlerPolycrystalline material growthDiffusion/dopingNoseMicrometer

An optical nose for detecting the presence of molecular contaminants in gaseous samples utilizes a tunable seed laser output in conjunction with a pulsed reference laser output to generate a mid-range IR laser output in the 2 to 20 micrometer range for use as a discriminating light source in a photo-acoustic gas analyzer.

Owner:UNIVERSITY OF ALABAMA

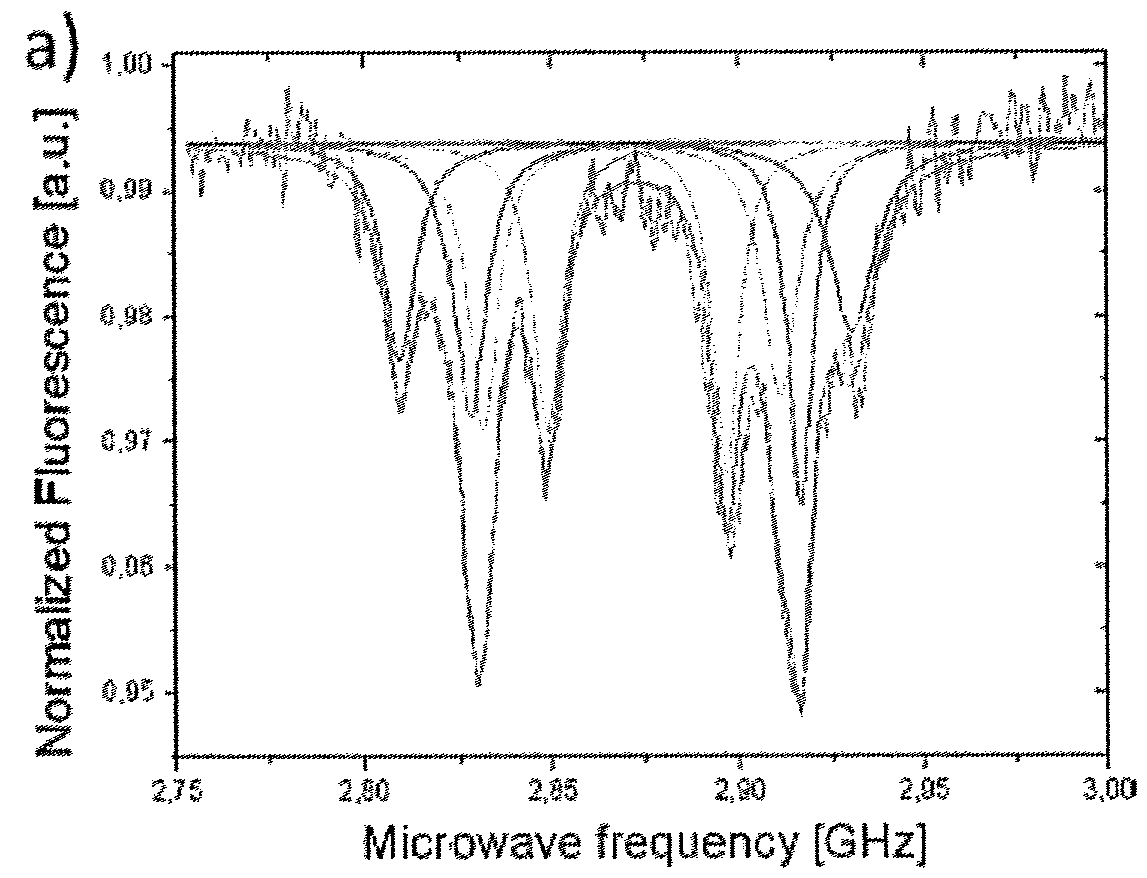

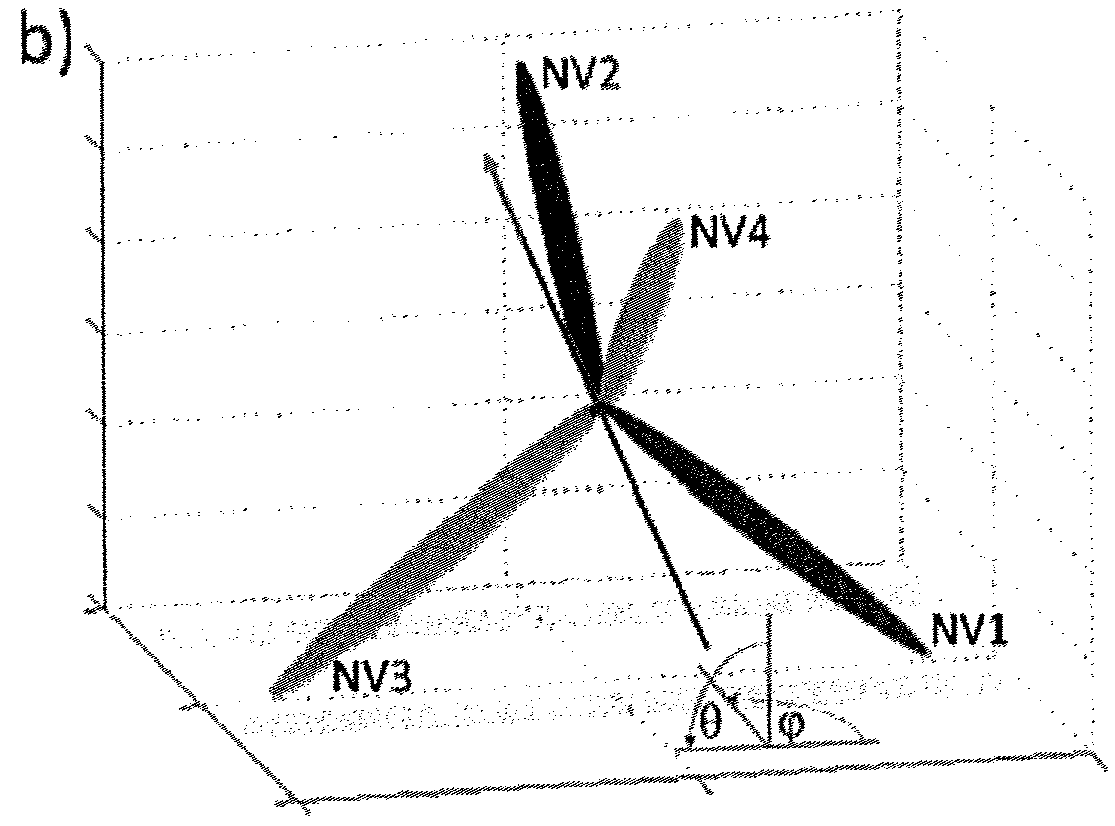

Diamond sensors, detectors, and quantum devices

ActiveUS8758509B2Improve excitation efficiencyIncrease the number ofUltra-high pressure processesNanoinformaticsBillionthSpins

A thin plate of synthetic single crystal diamond material, the thin plate of synthetic single crystal diamond material having: a thickness in a range 100 nm to 50 μιη; a concentration of quantum spin defects greater than 0.1 ppb (parts-per-billion); a concentration of point defects other than the quantum spin defects of below 200 ppm (parts-per-million); and wherein at least one major face of the thin plate of synthetic single crystal diamond material comprises surface termination species which have zero nuclear spin and / or zero electron spin.

Owner:ELEMENT SIX LTD

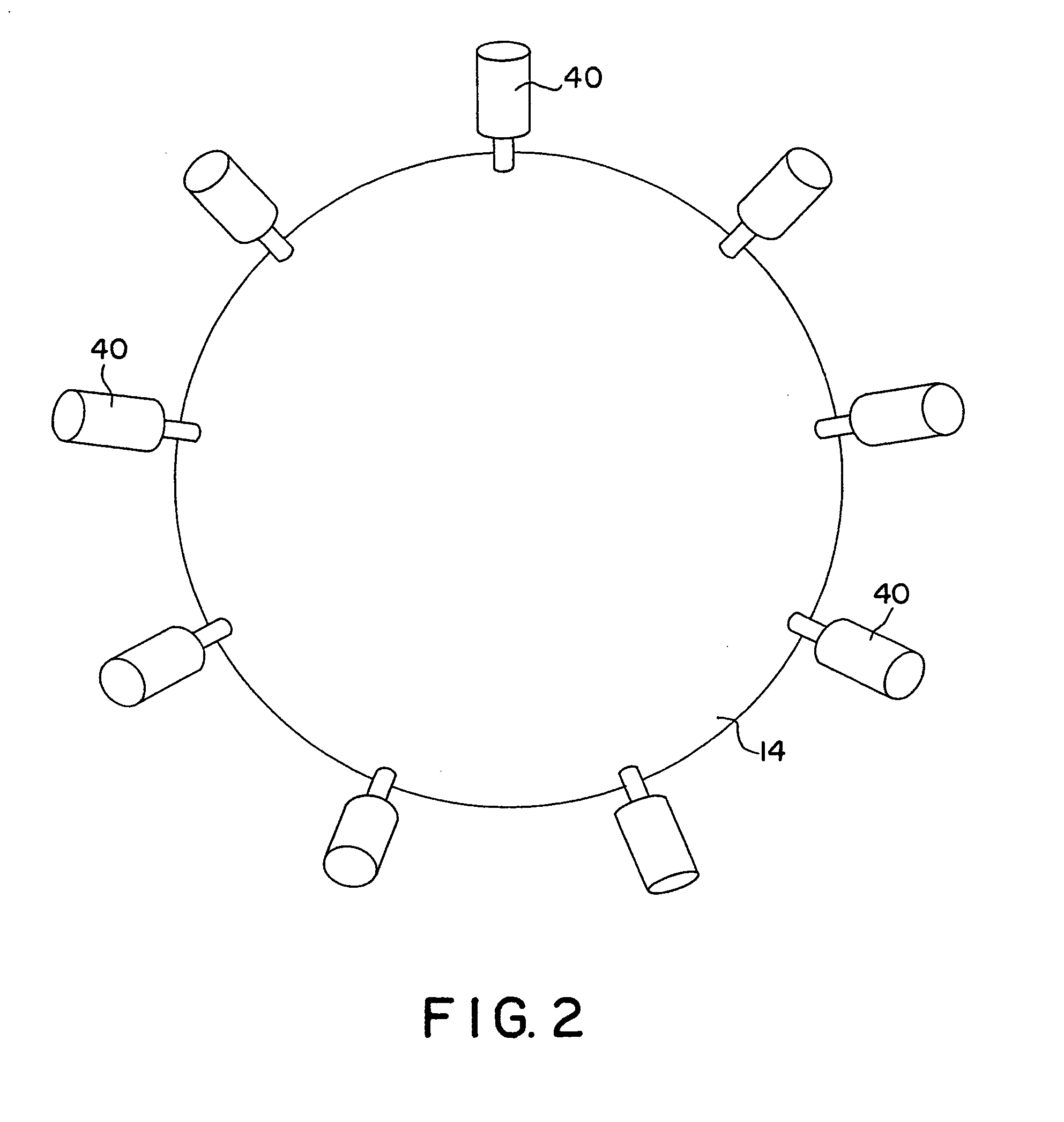

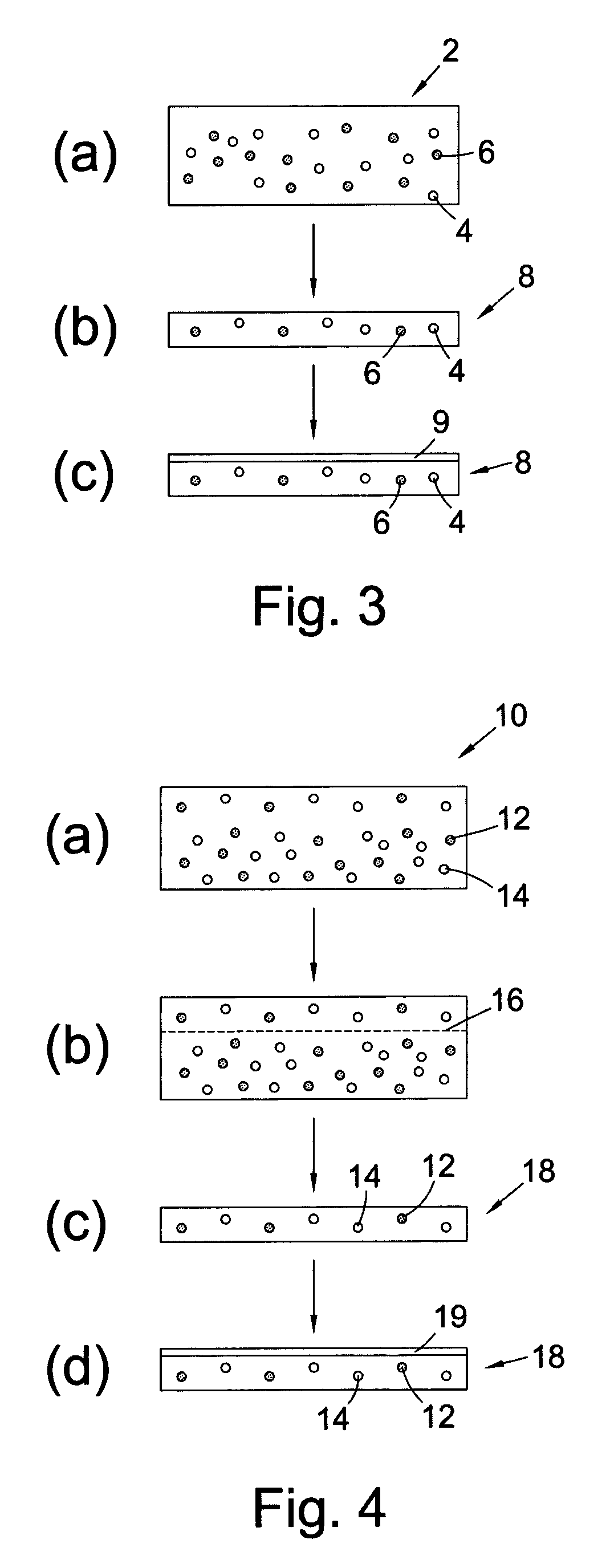

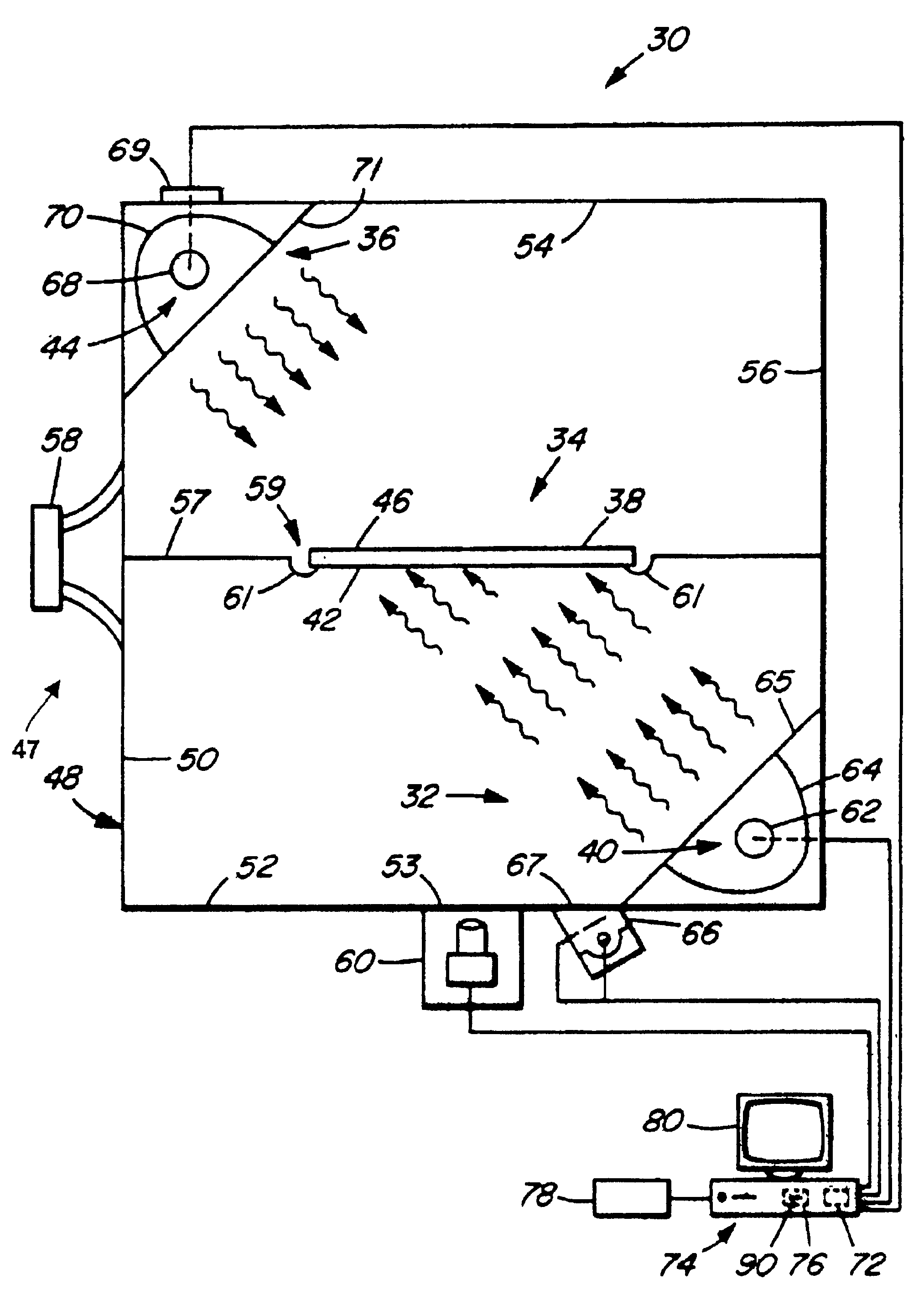

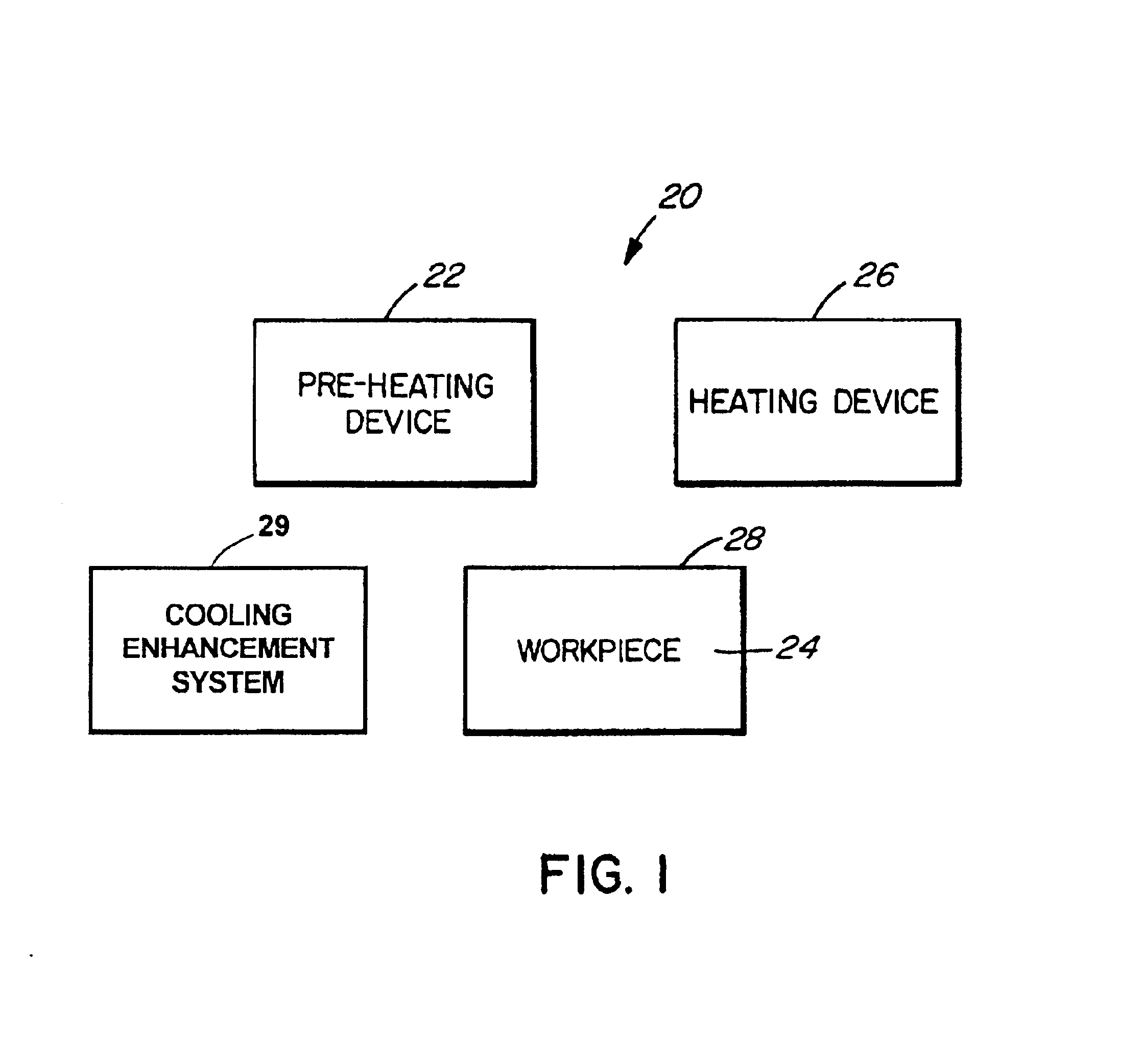

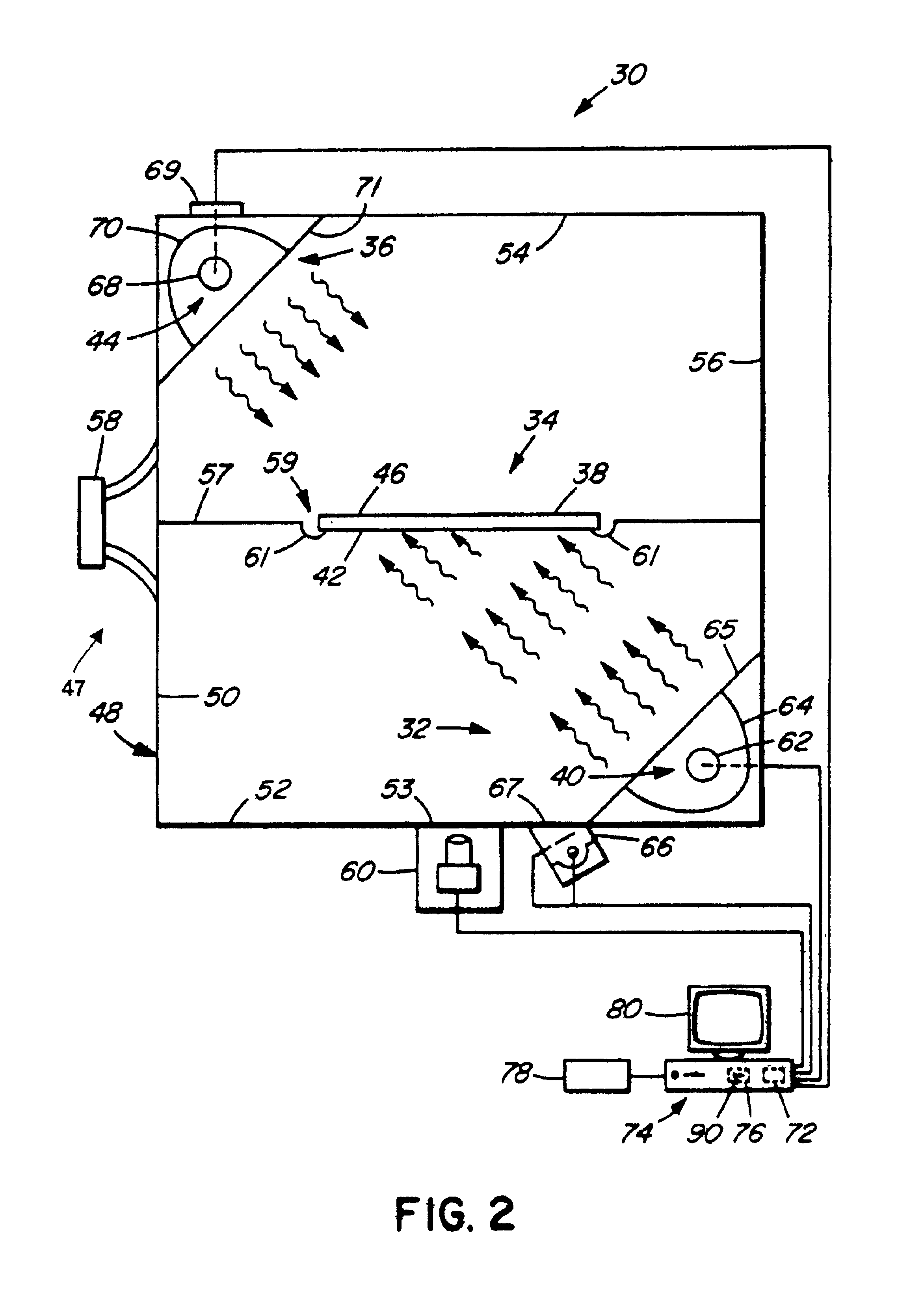

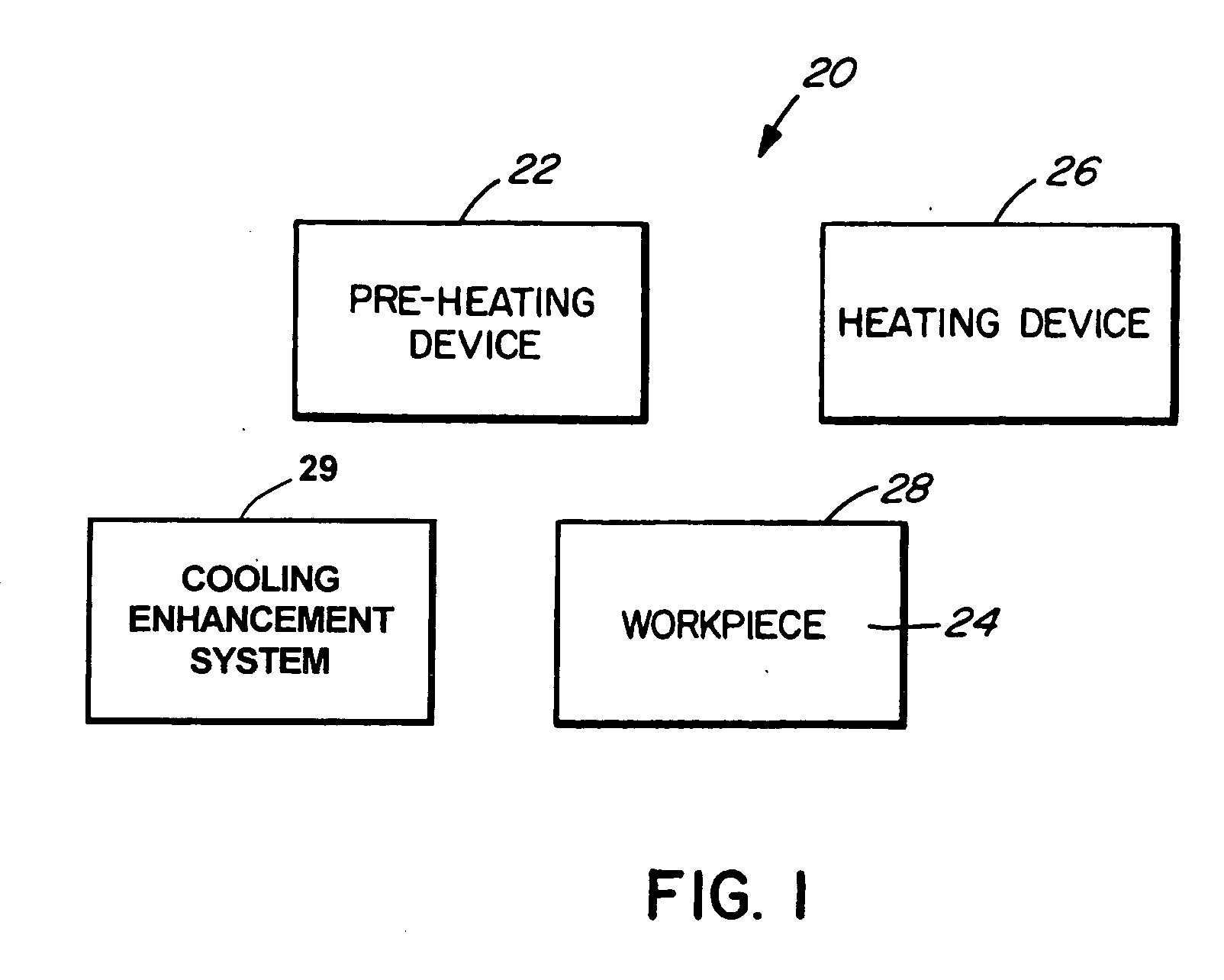

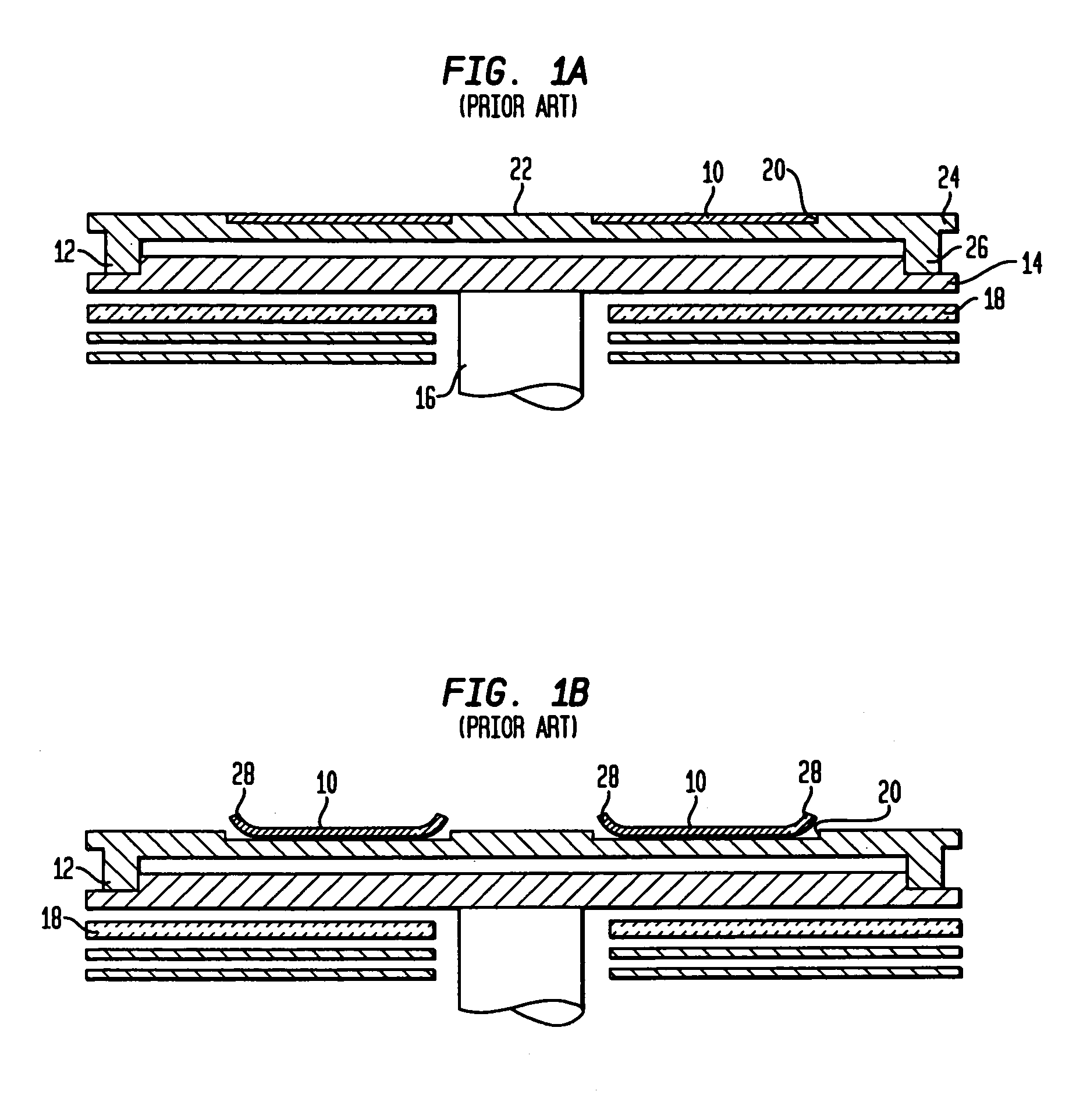

Heat-treating methods and systems

InactiveUS6941063B2Improve cooling effectWeakening rangeMechanical apparatusDrying solid materials with heatThermal radiationSemiconductor

A method involves pre-heating a workpiece to an intermediate temperature, heating a surface of the workpiece to a desired temperature greater than the intermediate temperature, and enhancing cooling of the workpiece. Enhancing cooling may involve absorbing radiation thermally emitted by the workpiece. An apparatus includes a first heating source for heating a first surface of a semiconductor wafer, a second heating source for heating a second surface of the semiconductor wafer, and a first cooled window disposed between the first heating source and the semiconductor wafer.

Owner:MATTSON TECHNOLOGY +1

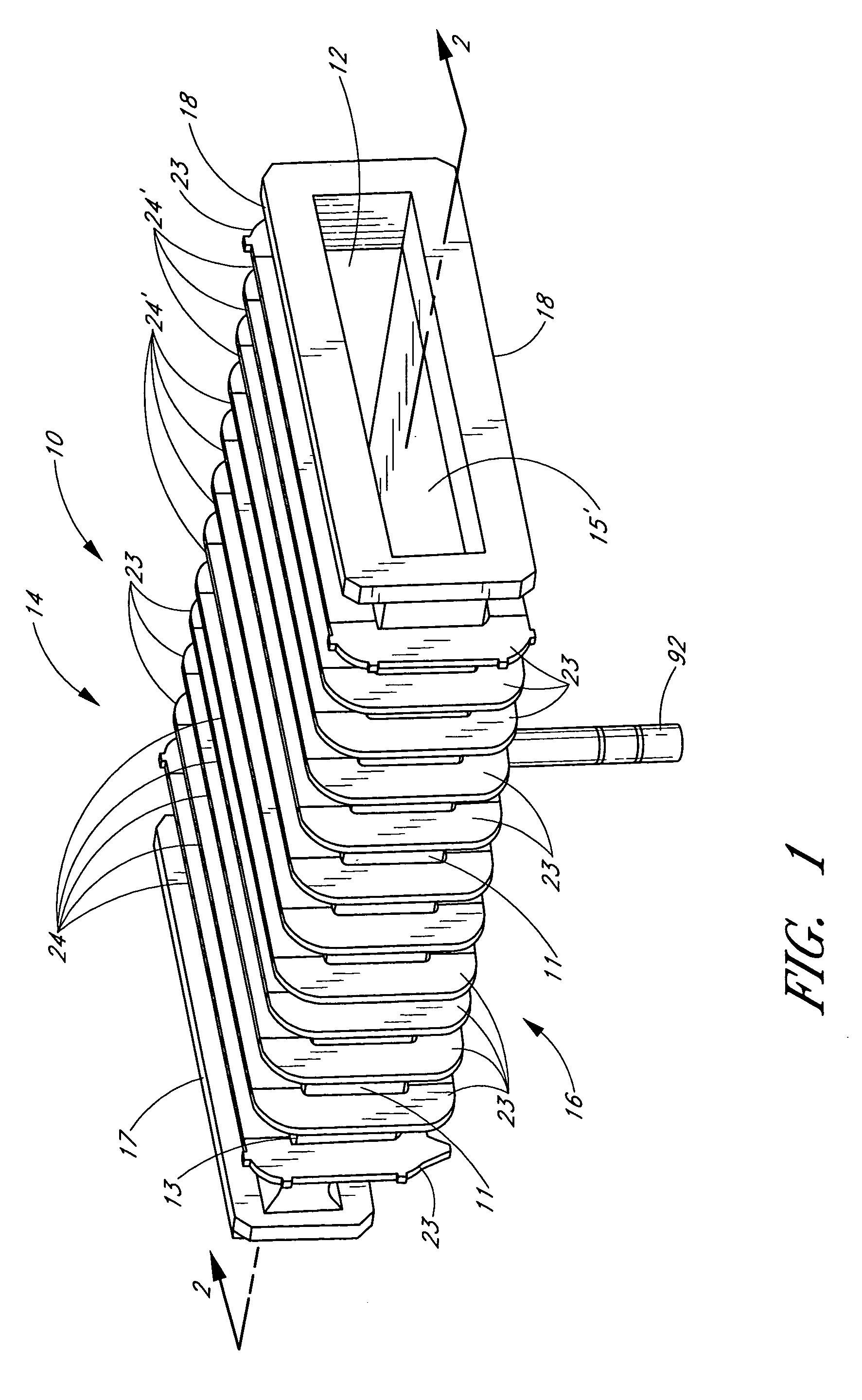

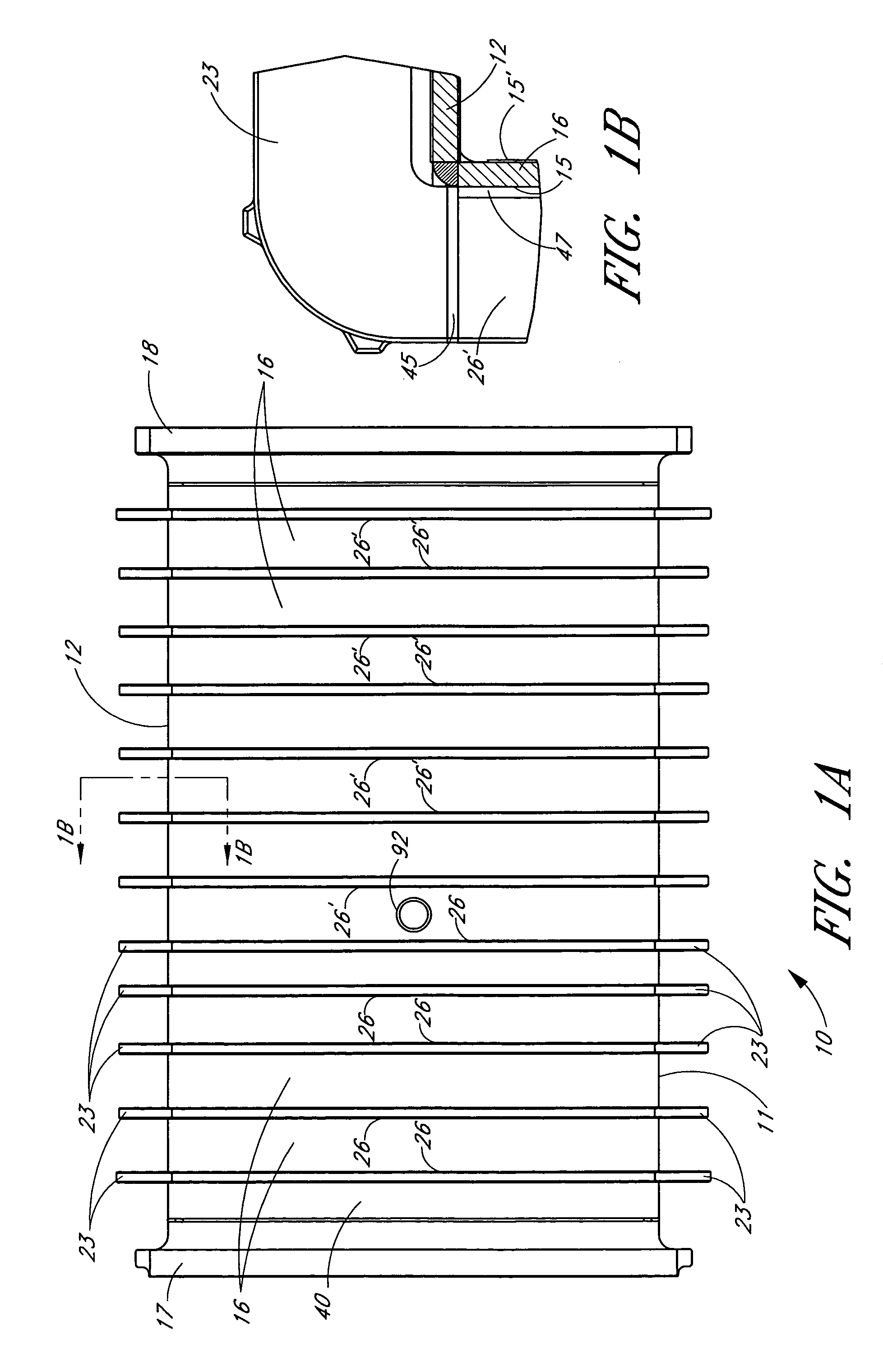

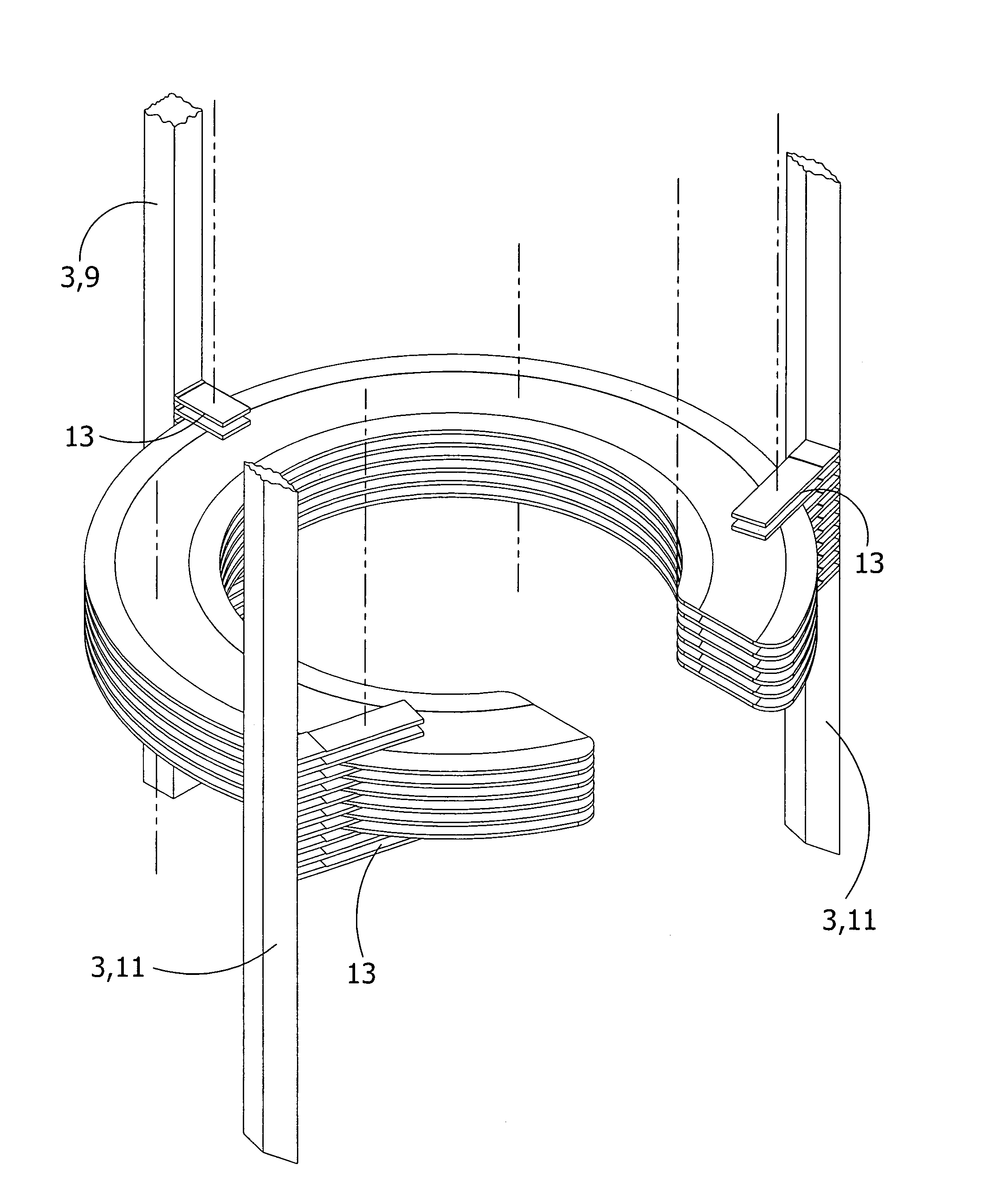

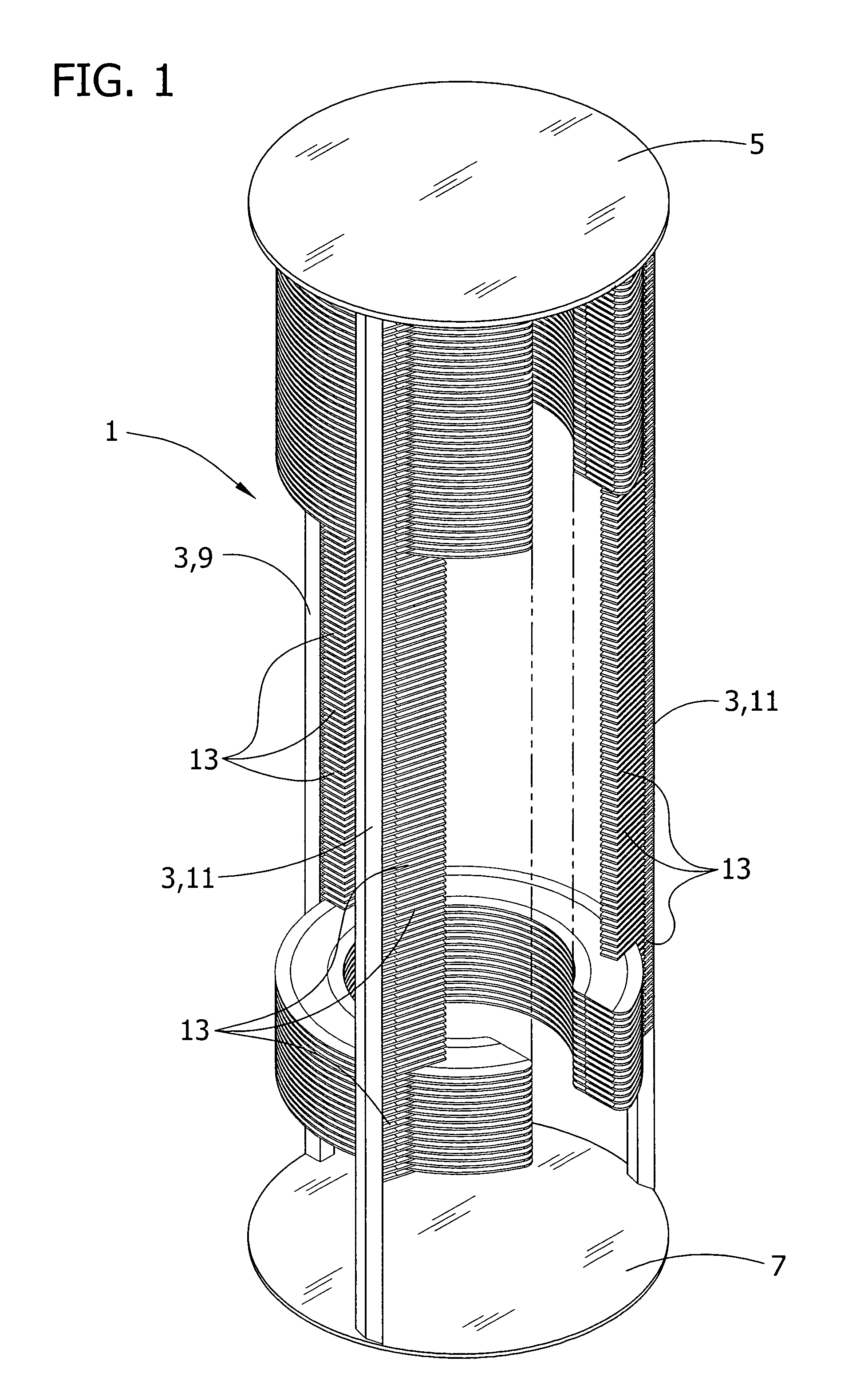

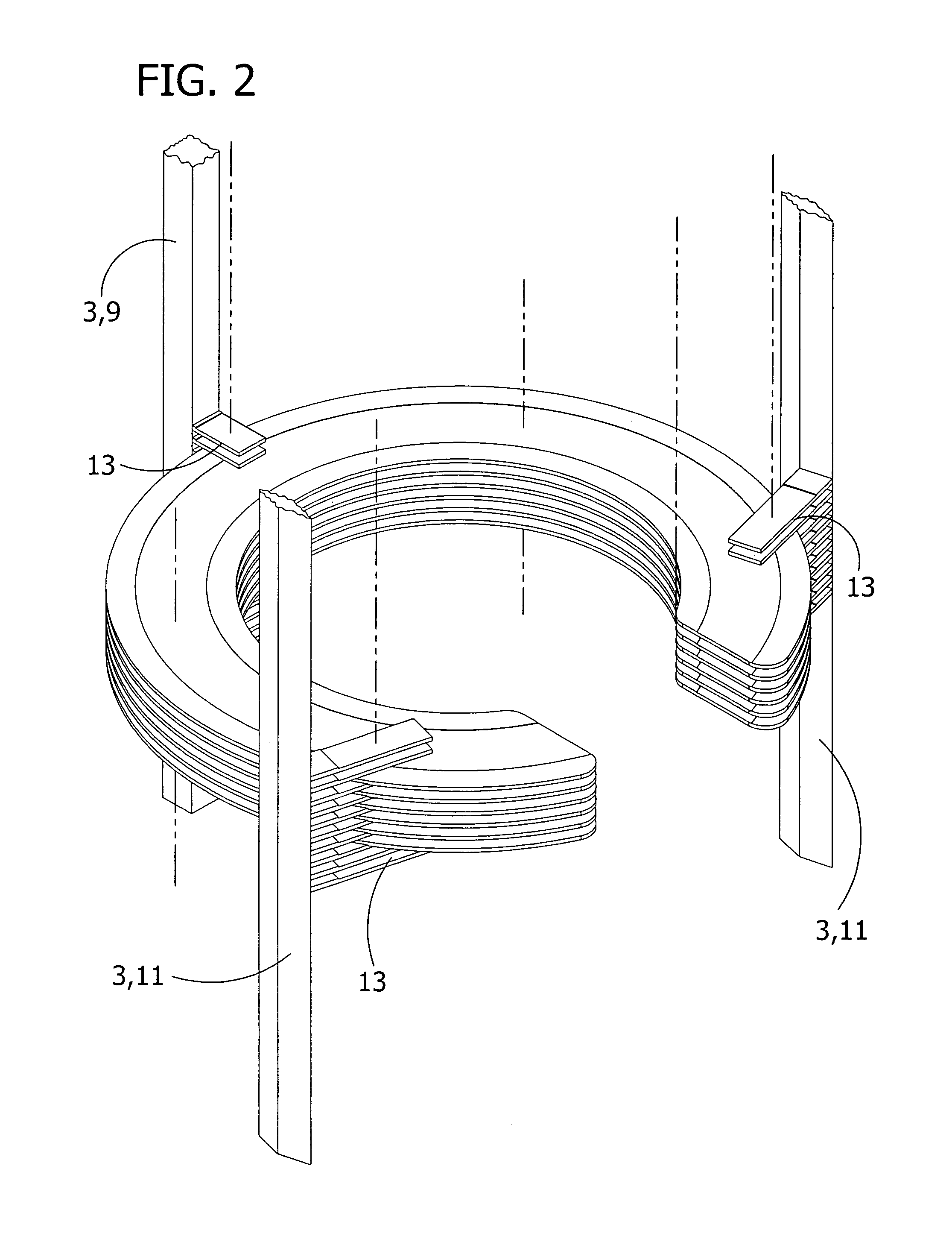

Semiconductor wafer boat for a vertical furnace

A wafer boat for use in heat treatment of semiconductor wafers in a vertical furnace comprises support rods extending generally vertically when the wafer boat is placed in the vertical furnace. Fingers are supported by and extend along vertical extent of the support rods. Wafer holder platforms are adapted to be supported by groups of fingers lying in generally different common horizontal planes. The fingers are adapted to underlie the wafer holder platforms and support the platforms at the support locations. The fingers and wafer holder platforms each have a respective first overall maximum thickness. The support location of at least one of the fingers and the wafer holder platforms have a second maximum thickness less than the first overall maximum thickness.

Owner:GLOBALWAFERS CO LTD

Heat-treating methods and systems

InactiveUS20050062388A1Improve cooling effectWeakening rangeMuffle furnacesDiffusion/dopingSemiconductorMaterials science

A method involves pre-heating a workpiece to an intermediate temperature, heating a surface of the workpiece to a desired temperature greater than the intermediate temperature, and enhancing cooling of the workpiece. Enhancing cooling may involve absorbing radiation thermally emitted by the workpiece. An apparatus includes a first heating source for heating a first surface of a semiconductor wafer, a second heating source for heating a second surface of the semiconductor wafer, and a first cooled window disposed between the first heating source and the semiconductor wafer.

Owner:MATTSON TECH CANADA

Diamond components for quantum imaging, sensing and information processing devices

ActiveUS20160348277A1Reduce surface damageLong spin coherence timePolycrystalline material growthDiffusion/dopingInformation processingSurface roughness

A single crystal CVD diamond component comprising: a surface, wherein at least a portion of said surface is formed of as-grown growth face single crystal CVD diamond material which has not been polished or etched and which has a surface roughness Ra of no more than 100 nm; and a layer of NV− defects, said layer of NV− defects being disposed within 1 μm of the surface, said layer of NV− defects having a thickness of no more than 500 nm, and said layer of NV− defects having a concentration of NV− defects of at least 105 NV− / cm2.

Owner:ELEMENT SIX TECH LTD

Diamond sensors, detectors, and quantum devices

ActiveUS9249526B2Minimizes strainShorten the timeQuantum computersPolycrystalline material growthElectron donorQuantum devices

A synthetic single crystal diamond material comprising: a first region comprising electron donor defects; a second region comprising quantum spin defects; and a third region between the first and second regions. The second and third regions have a lower concentration of electron donor defects than the first region. The first and second regions are sufficiently close to allow electrons to be donated from the first region to the second region, thus forming negatively charged quantum spin defects in the second and positively charged defects in the first region, and sufficiently far apart to reduce other coupling interactions between the first and second regions which would otherwise unduly reduce the decoherence time of the plurality of quantum spin defects and / or produce strain broaden of a spectral line width of the plurality of quantum spin defects in the second region.

Owner:ELEMENT SIX LTD

Mid-IR instrument for analyzing a gaseous sample and method for using the same

InactiveUS7606274B2Wide tunabilityRapidly tuned SLM idlerPolycrystalline material growthDiffusion/dopingNoseMicrometer

An optical nose for detecting the presence of molecular contaminants in gaseous samples utilizes a tunable seed laser output in conjunction with a pulsed reference laser output to generate a mid-range IR laser output in the 2 to 20 micrometer range for use as a discriminating light source in a photo-acoustic gas analyzer.

Owner:UNIVERSITY OF ALABAMA

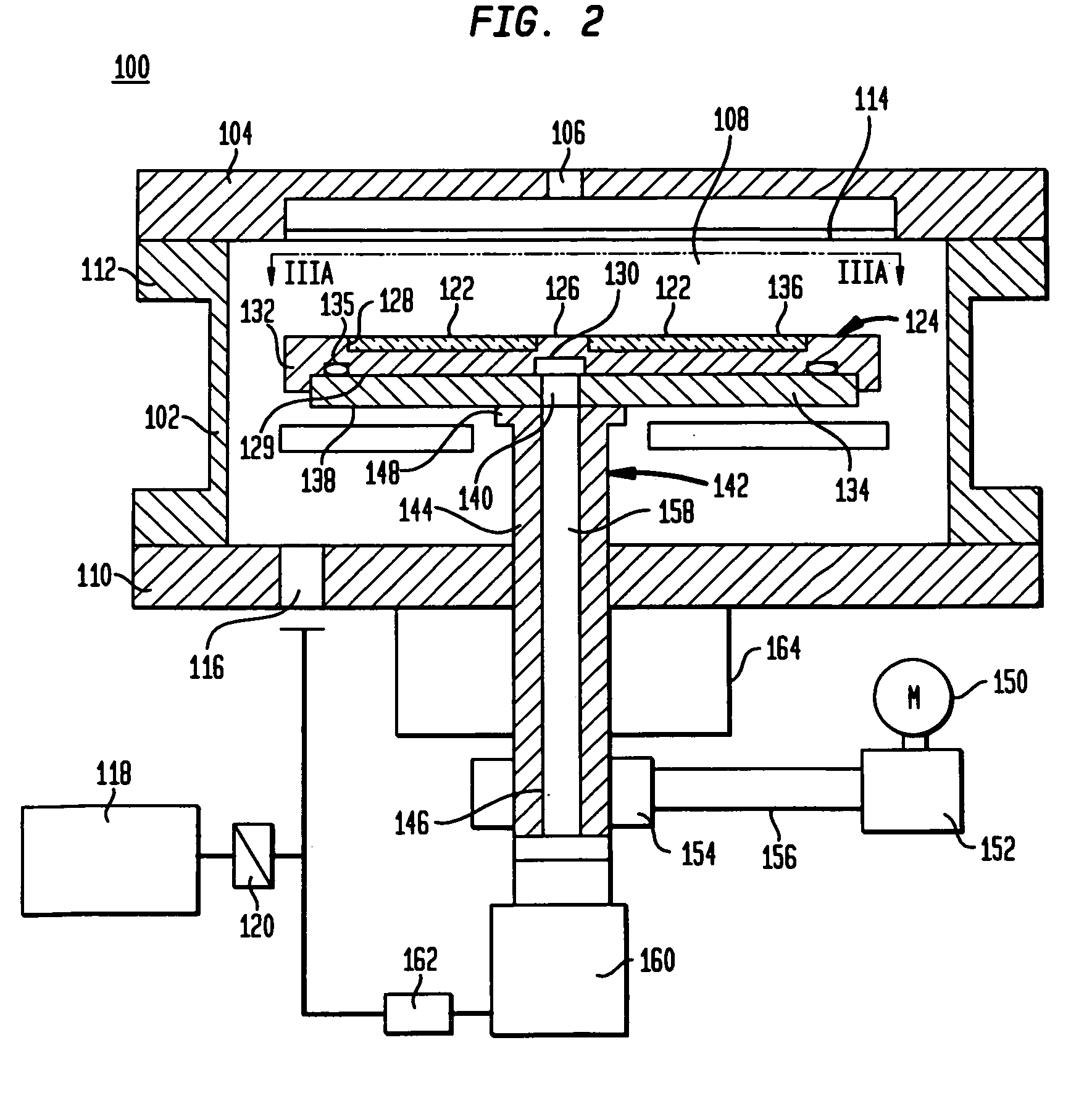

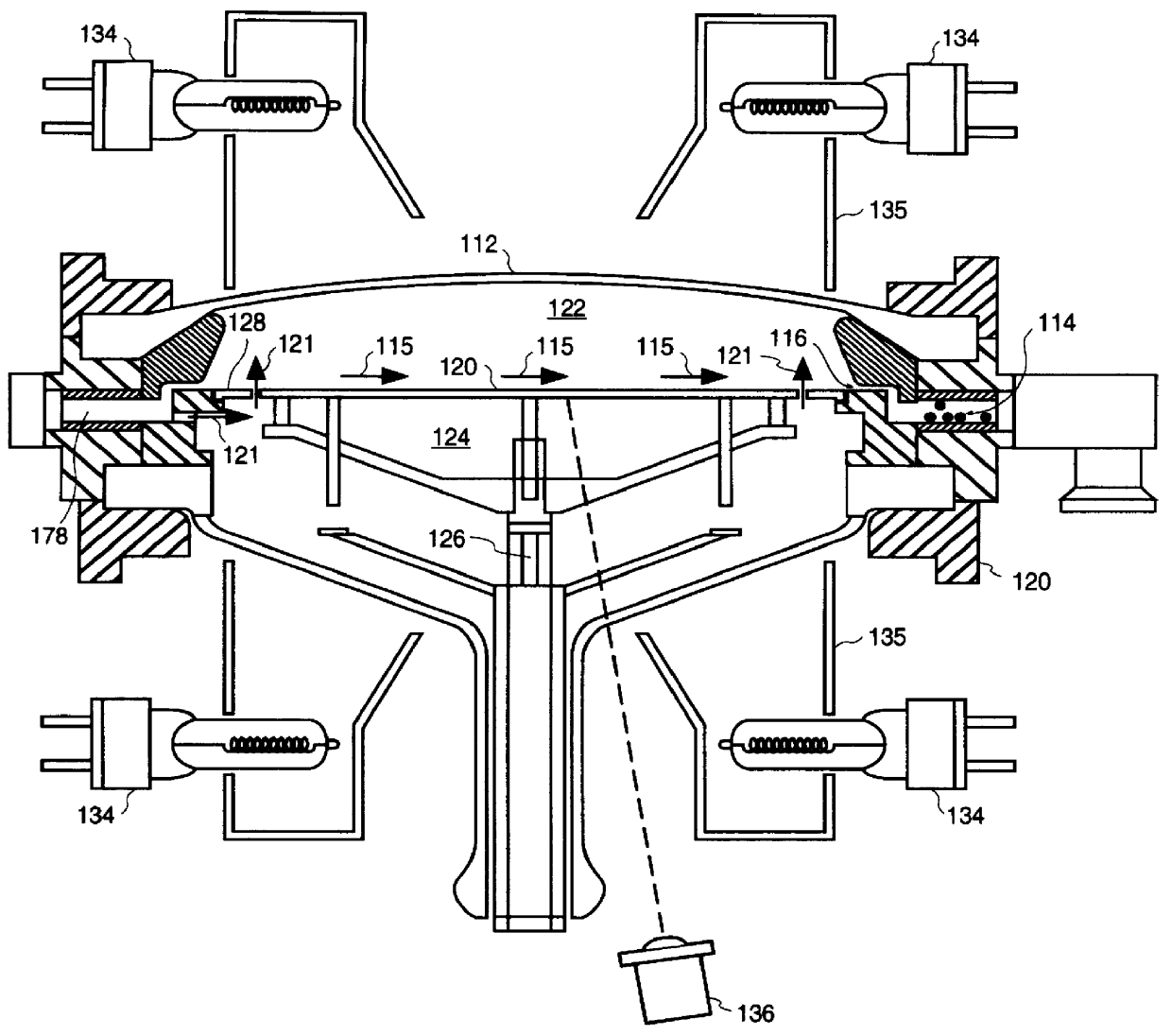

Heating configuration for use in thermal processing chambers

InactiveUS6970644B2Easy to control timeImprove temperature uniformityDrying solid materials with heatMuffle furnacesLight energyEngineering

An apparatus for heat treating semiconductor wafers is disclosed. The apparatus includes a heating device which contains an assembly linear lamps for emitting light energy onto a wafer. The linear lamps can be placed in various configurations. In accordance with the present invention, tuning devices which are used to adjust the overall irradiance distribution of the light energy sources are included in the heating device. The tuning devices can be, for instance, are lamps or lasers.

Owner:MATTSON TECHNOLOGY +1

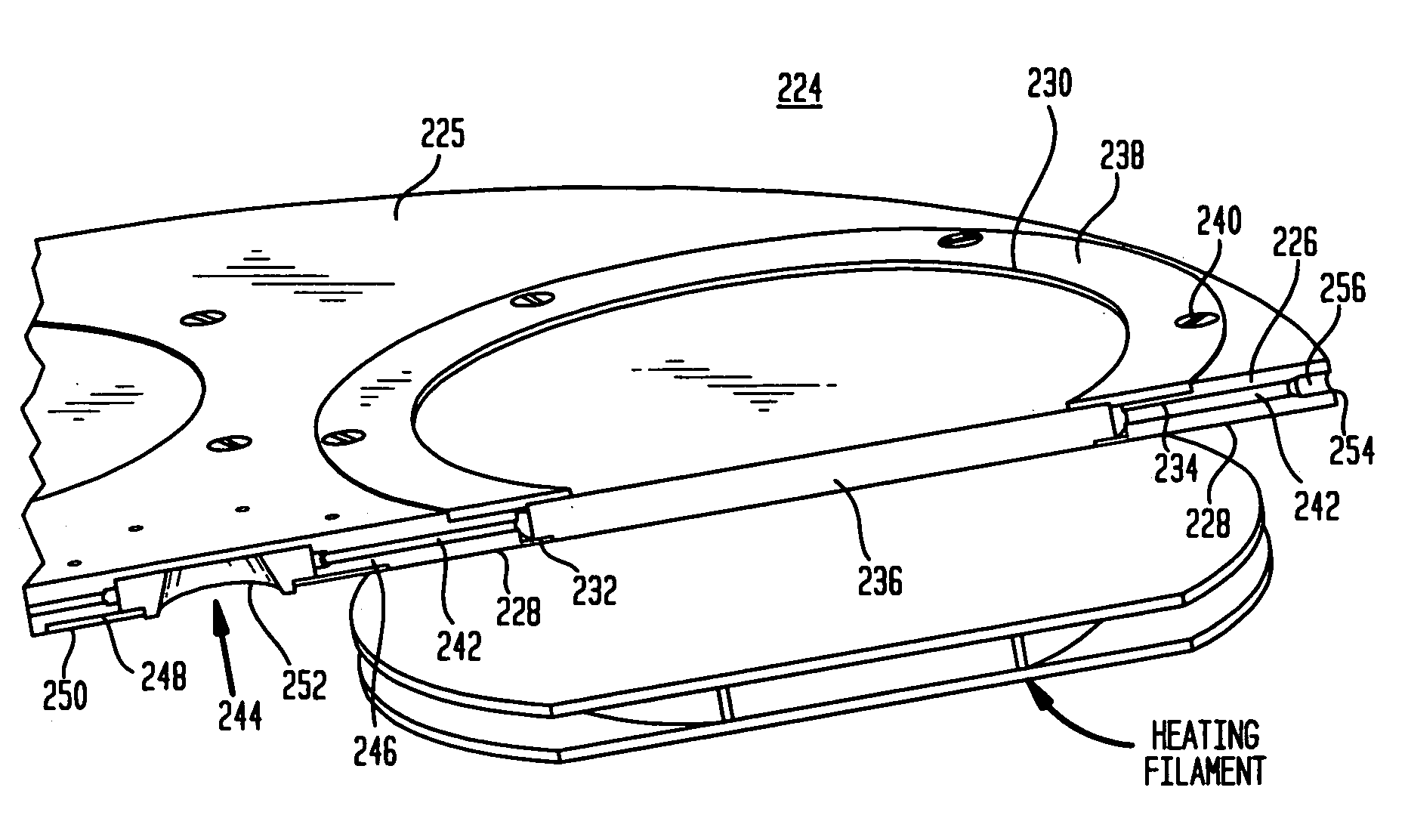

Wafer carrier for growing GaN wafers

InactiveUS7235139B2Avoid direct heat transferEliminate needLiquid surface applicatorsDiffusion/dopingEngineeringMechanical engineering

Owner:VEECO INSTR

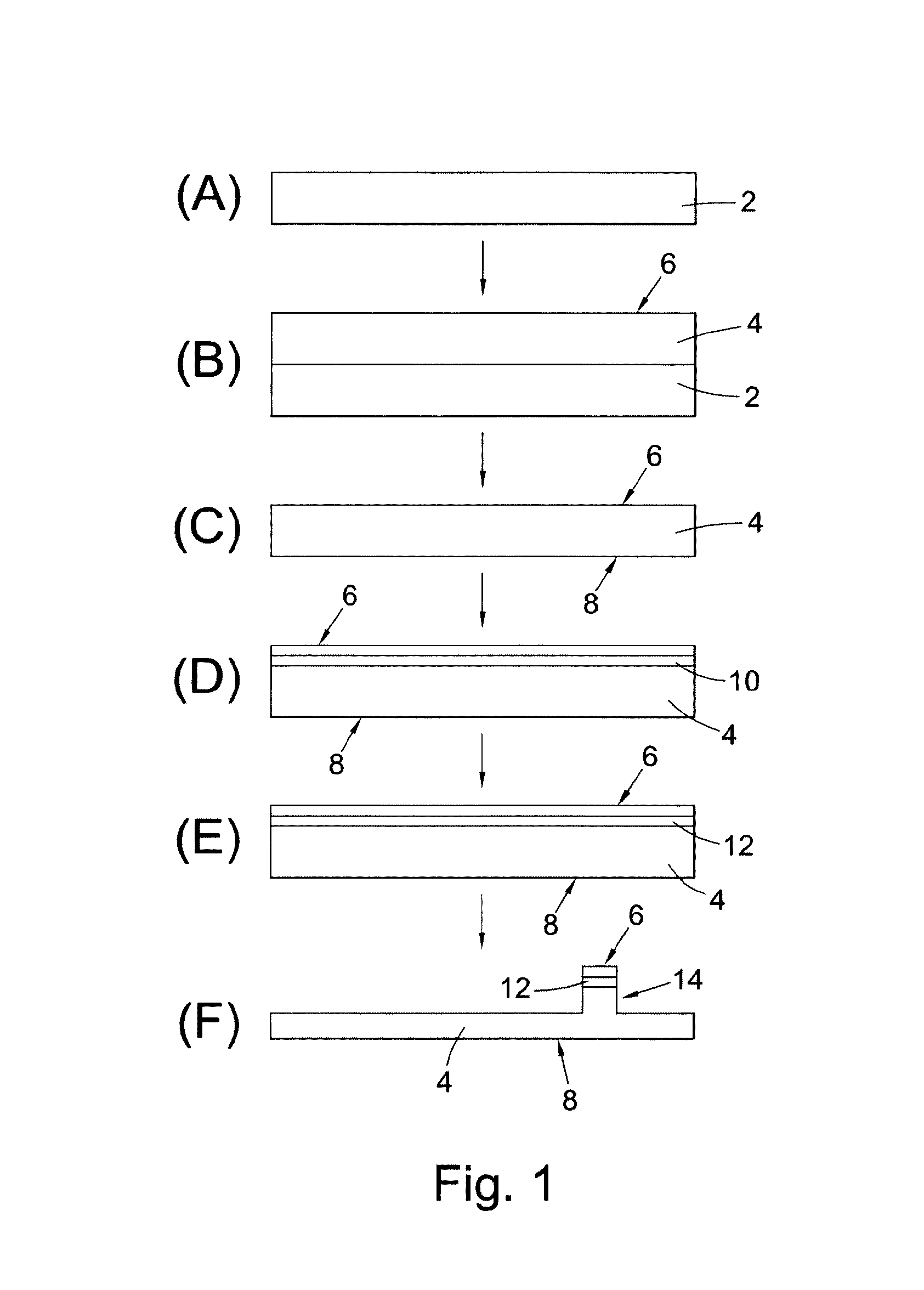

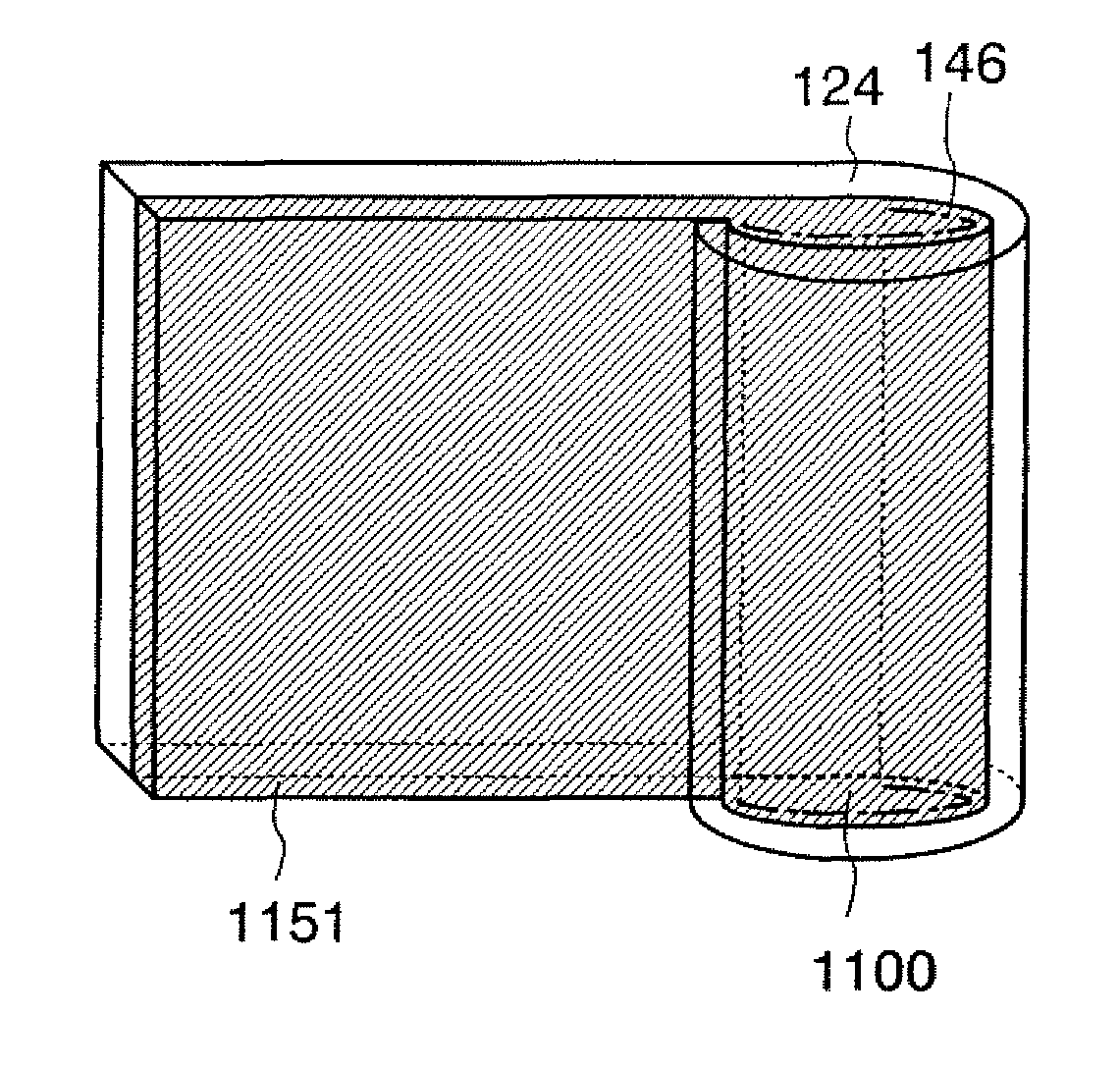

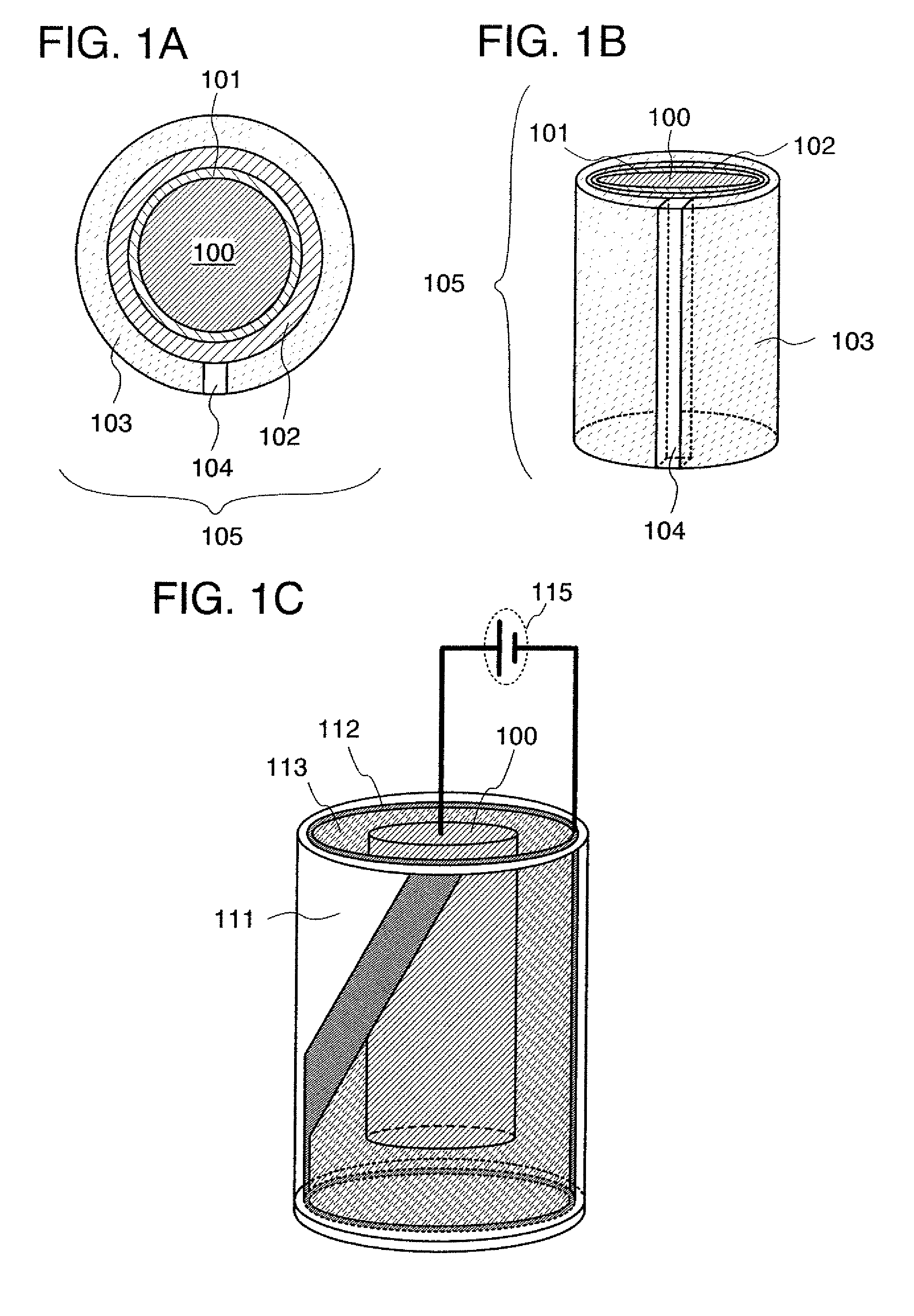

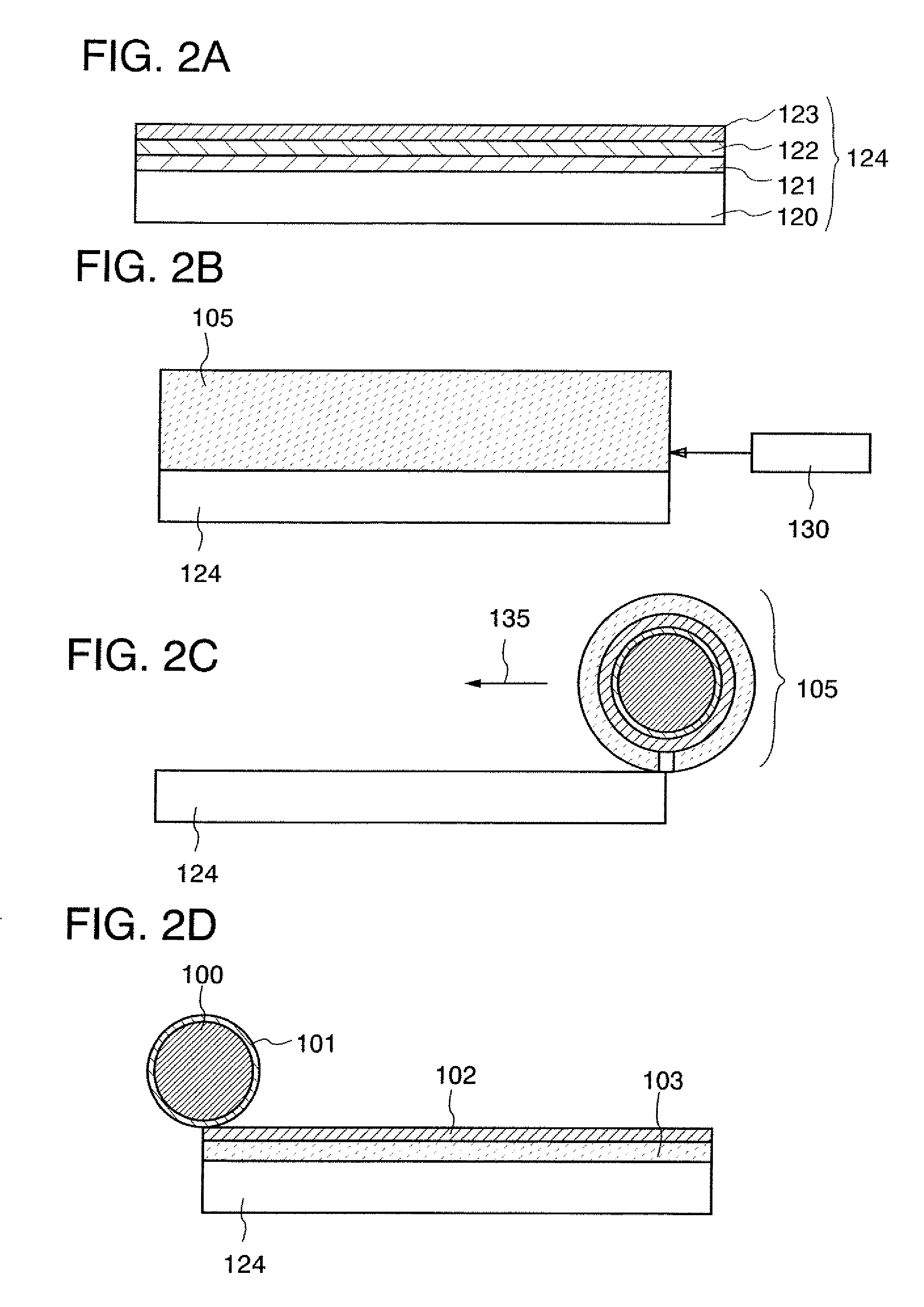

Formation method of single crystal semiconductor layer, formation method of crystalline semiconductor layer, formation method of polycrystalline layer, and method for manufacturing semiconductor device

InactiveUS7888242B2Increase the areaLittle changeAfter-treatment apparatusPolycrystalline material growthHydrogenPorous layer

A method for forming a single crystal semiconductor layer in which a first porous layer and a second porous layer are formed over a single crystal semiconductor ingot, a groove is formed in a part of the second porous layer and a single crystal semiconductor layer is formed over the second porous layer, the single crystal semiconductor ingot is attached onto a large insulating substrate, water jet is directed to the interface between the first porous layer and the second porous layer, and the single crystal semiconductor layer is attached to the large insulating substrate, or a method for forming a crystalline semiconductor layer in which a crystalline semiconductor ingot is irradiated with hydrogen ions to form a hydrogen ion irradiation region in the crystalline semiconductor ingot, the crystalline semiconductor ingot is rolled over the large insulating substrate while being heated, the crystalline semiconductor layer is separated from the hydrogen ion irradiation region, and the crystalline semiconductor layer is attached to the large insulating substrate.

Owner:SEMICON ENERGY LAB CO LTD

Method for heating exhaust gas in a substrate reactor

InactiveUS6153260ADiffusion/dopingSemiconductor/solid-state device manufacturingNuclear engineeringProduct gas

The present invention is a single wafer reactor having a vented lower liner for heating exhaust gas. The apparatus of the present invention includes a reaction chamber. A wafer support member which divides the chamber into an upper and lower portion is positioned within the chamber. A gas outlet for exhausting gas from the chamber has a vent to exhaust gas from the lower portion of the chamber and an exhaust passage opening to exhaust gas from the upper portion of the chamber. Heated inert purge gas is fed from the lower chamber portion through the vent at a rate so as to prevent the deposition gas from condensing in the exhaust passage.

Owner:APPLIED MATERIALS INC

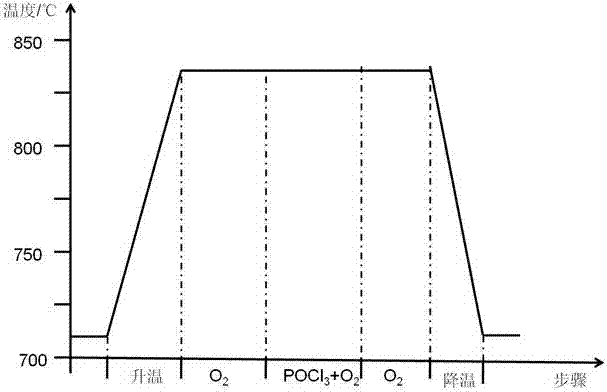

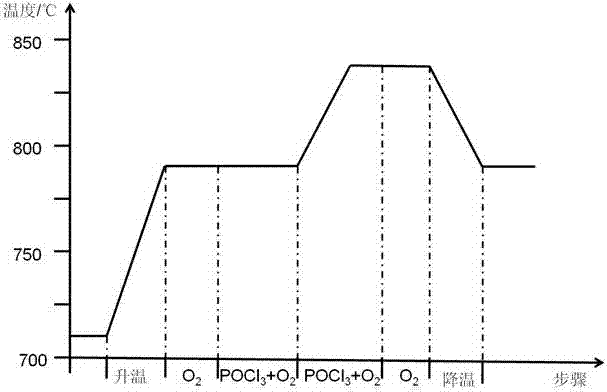

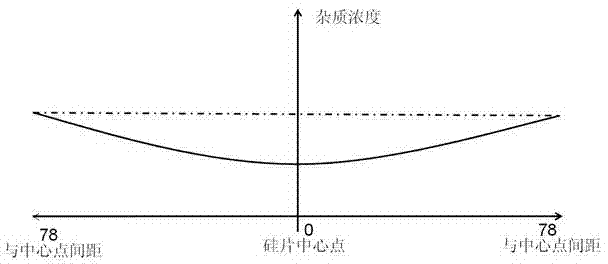

Spread method of polycrystalline silicon solar cell

InactiveCN102820383AImprove square resistance uniformityUniform concentration distributionFinal product manufactureDiffusion/dopingPre depositionSilicon chip

The invention relates to a spread method of a polycrystalline silicon solar cell. The spread method is characterized in that the spread method comprises the following processing steps of entering a boat, warming, oxidizing, spreading, redistributing, cooling and going out the boat, wherein the spreading step comprises low temperature pre-deposition and then high temperature spreading. Reaction between a phosphorus source and a silicon wafer cannot be completed under low temperature, so that the low temperature pre-deposition is carried out on low temperature source communication at a first step of spreading, the phosphorus source cannot spread (or conduct spreading with low rate) inside a silicon wafer, the phosphorus source only accumulates on the surface of the silicon wafer, and a phosphorus film with certain thickness is formed on the surface of the silicon wafer after source communication for certain time; and the high temperature spreading is carried out on high temperature source communication at a second step, phosphorus on the surface of an original silicon wafer is reacted with the silicon wafer and spreads to the inside of the silicon wafer, and spreading rates of the center point and the periphery of the silicon wafer are same. Therefore, spreading uniformity is good, concentration distribution of impurities on the surface of the silicon wafer and inside the silicon wafer body is even, sheet resistance uniformity is improved, and final photoelectric conversion efficiency of a cell sheet is improved accordingly.

Owner:JIANGYIN XINHUI SOLAR ENERGY

Method for preparing crystalline silicon solar cell selective emitter junction

ActiveCN101916799AHigh industrial applicabilityImprove uniformityFinal product manufactureDiffusion/dopingDiffusionOxygen

The invention discloses a method for preparing a crystalline silicon solar cell selective emitter junction. The method comprises the following steps of: growing a diffusion mask on a textured surface of a crystalline silicon wafer; etching and slotting an electrode gate line region; forming a heavily doped region at the electrode gate line region by using primary diffusion technology; and forminga lightly doped region at a non-electrode gate line region; the primary diffusion technology comprises the following steps of: (1) feeding a boat; (2) stabilizing a temperature; (3) performing high temperature diffusion: carrying phosphorus oxychloride into a diffusion furnace tube through nitrogen gas for diffusing; (4) performing high temperature propulsion: introducing the oxygen to perform diffusion and then redistributing; (5) stabilizing the temperature: reducing the temperature to 20 to 120 DEG C to stabilize the temperature in the diffusion furnace tube; (6) performing low temperaturepropulsion: introducing the oxygen to perform the diffusion and then redistributing; and (7) withdrawing the boat. By the method, square resistance of the heavily doped region can be controlled below40 ohms and the square resistance of the lightly doped region can be controlled over 50 ohms so as to realize the preparation of the crystalline silicon solar cell selective emitter junction.

Owner:CSI CELLS CO LTD +1