Patents

Literature

120 results about "Pre deposition" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A pre-arraignment deposition is the testimony that is presented at the pre-arraignment meeting that is held prior to a defendant's first appearance in court. A pre-arraignment meeting is where this deposition is delivered. The meeting is usually arranged by the Criminal Division Staff.

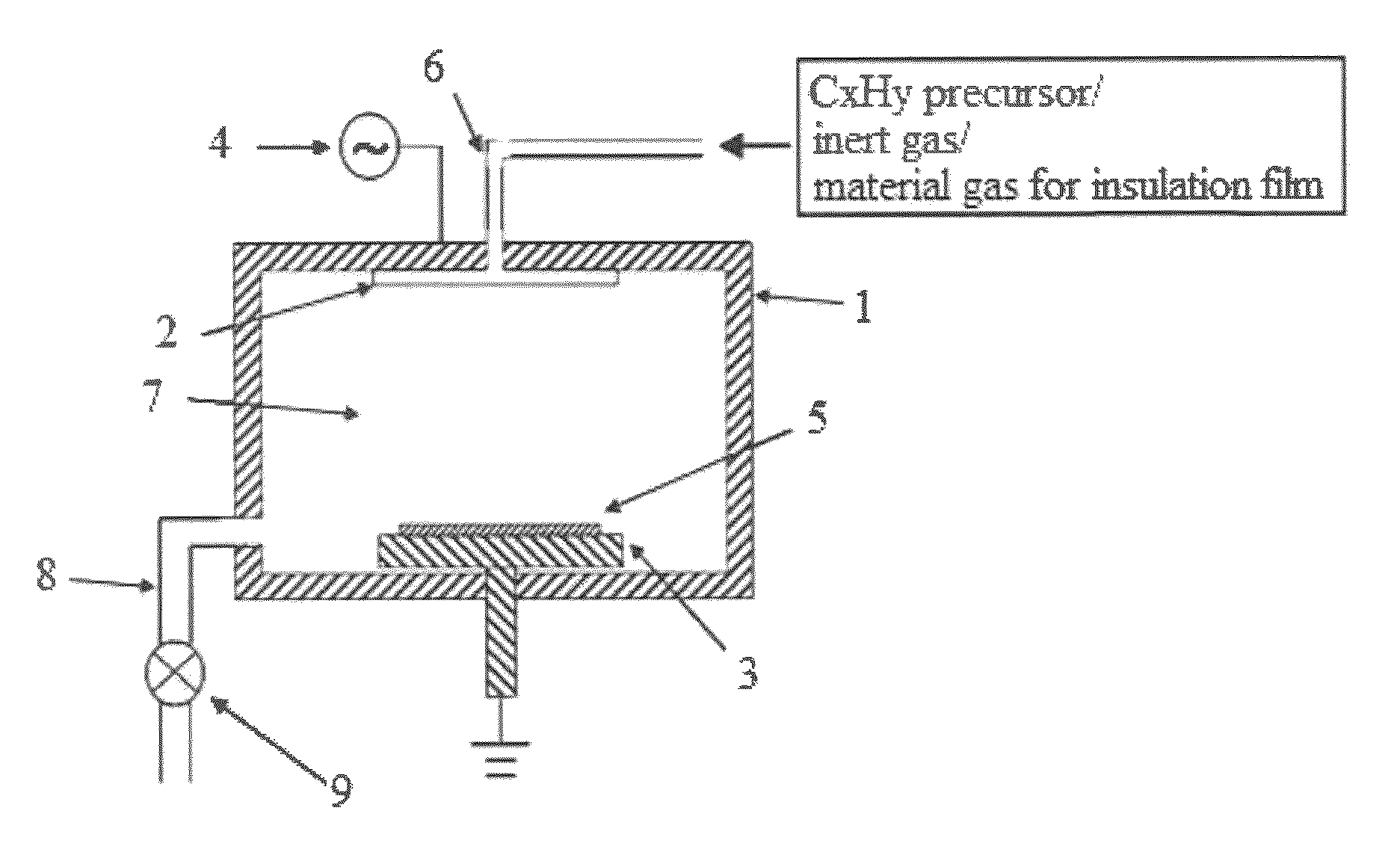

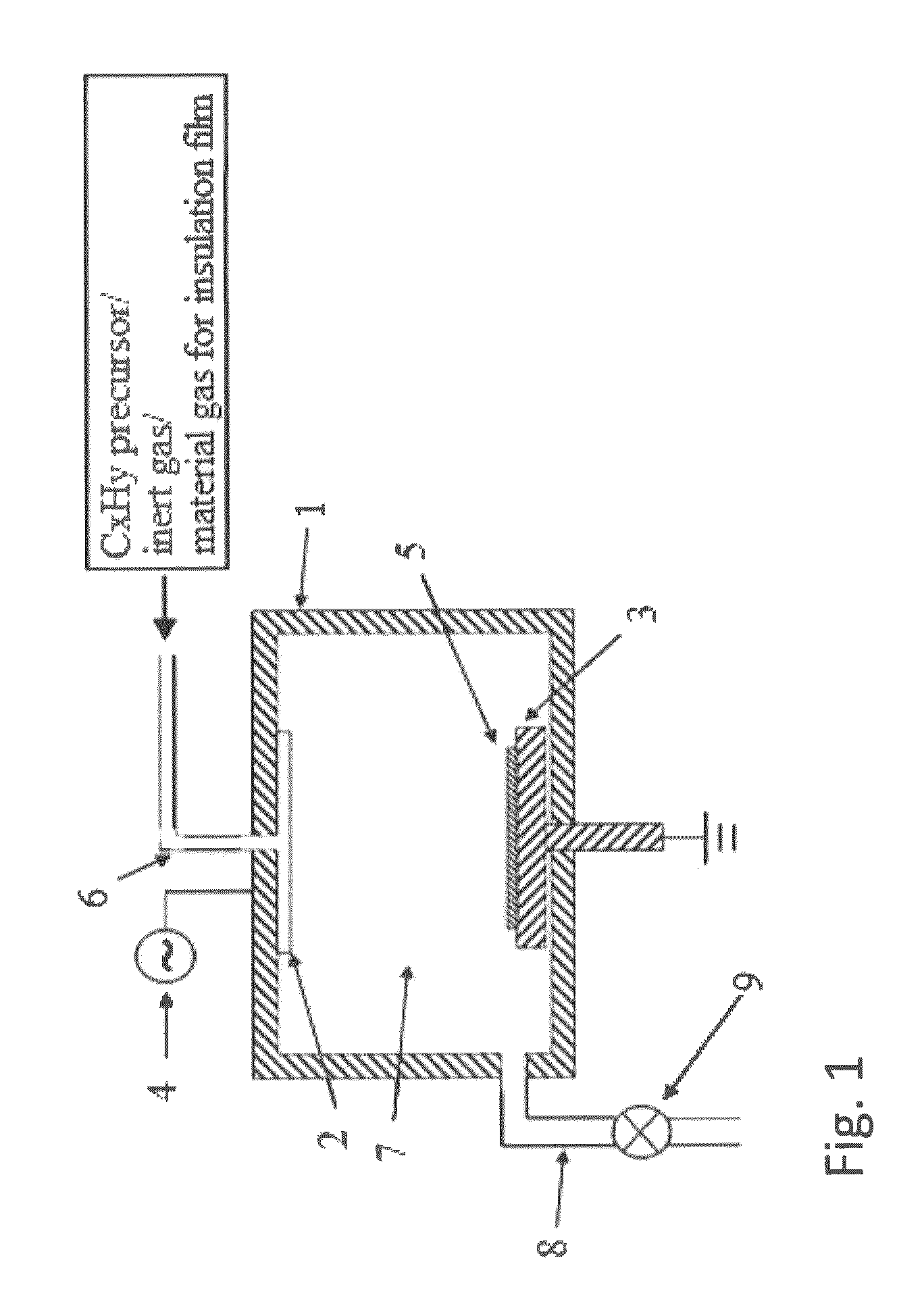

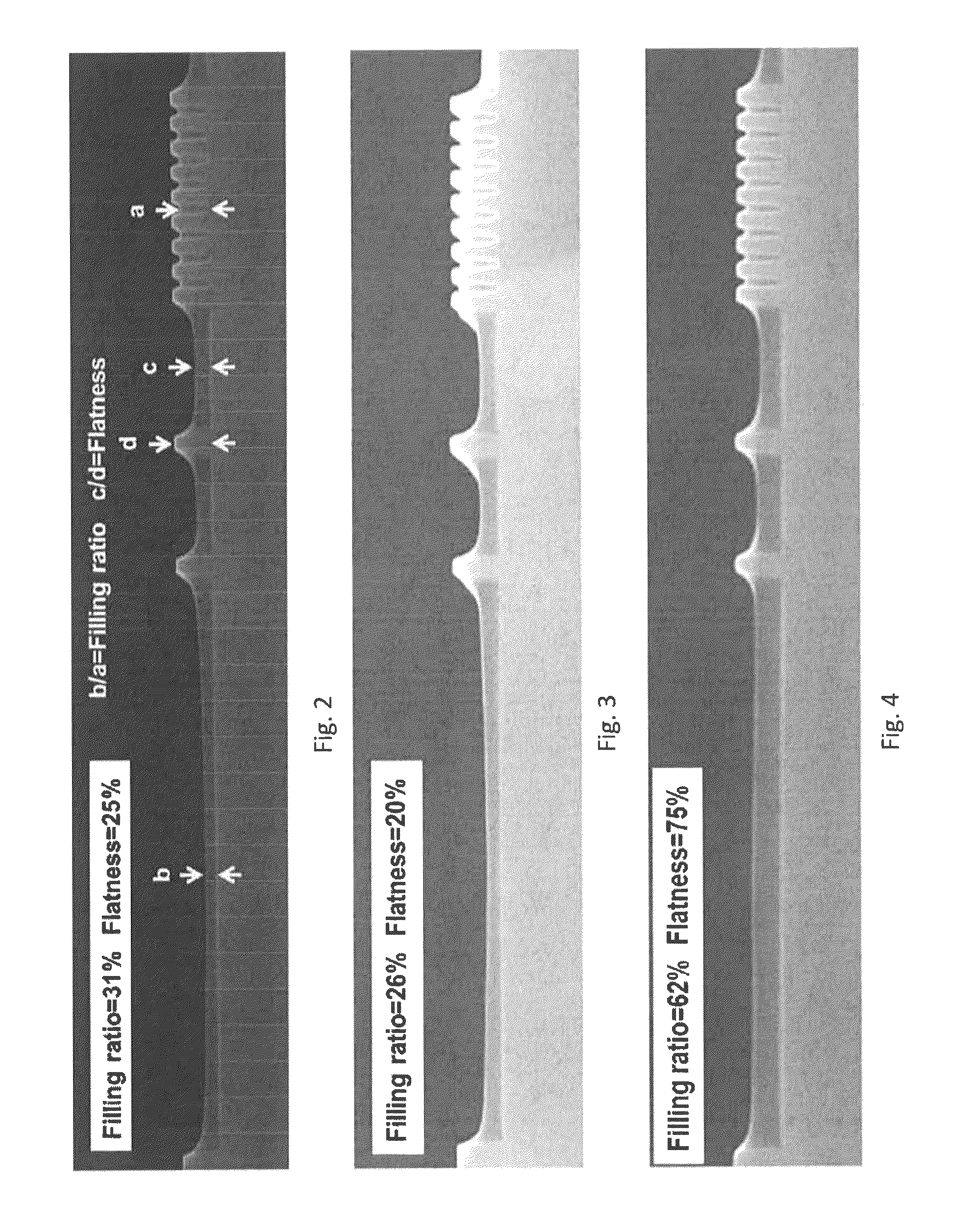

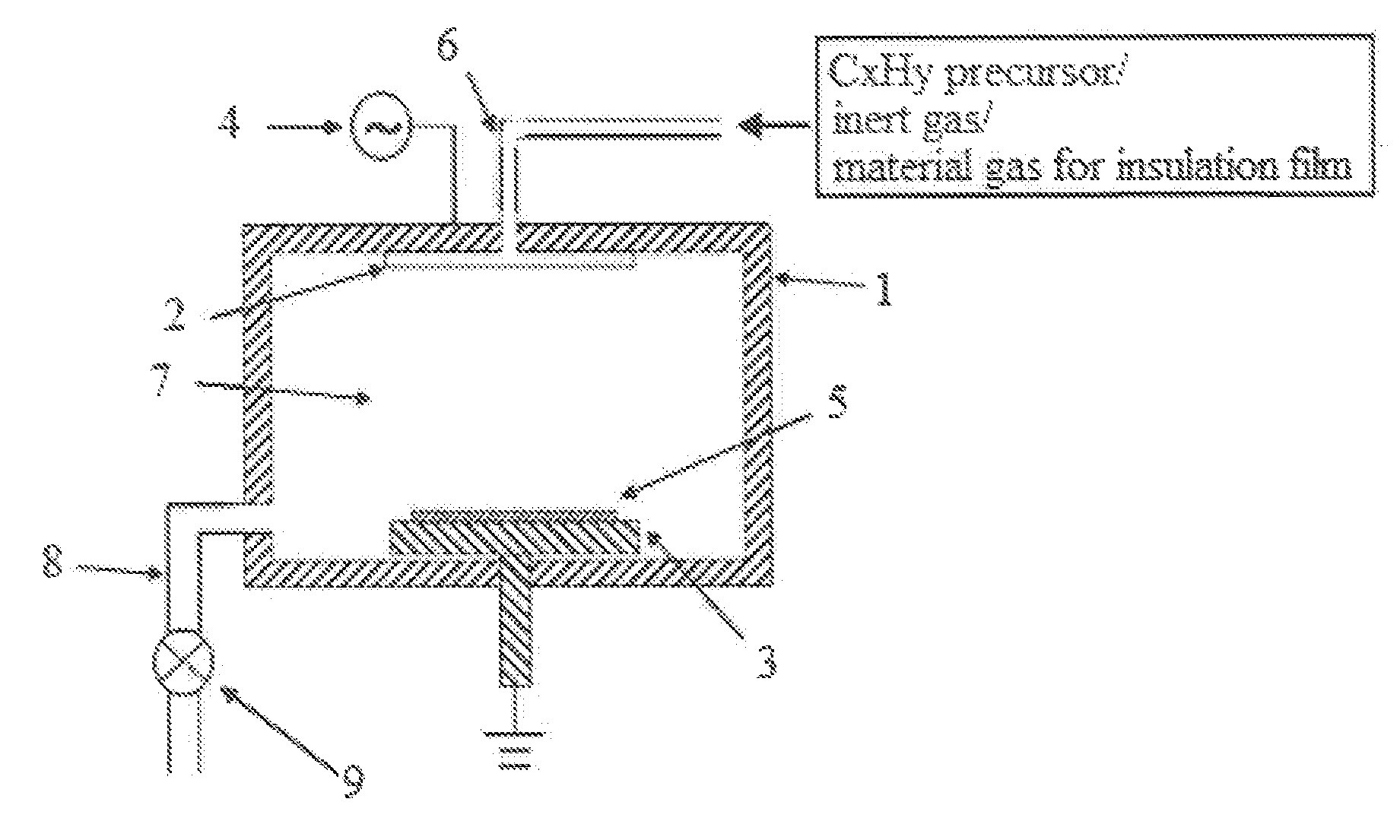

Method for filling recesses using pre-treatment with hydrocarbon-containing gas

ActiveUS9117657B2Improve flatnessHighly effectiveSemiconductor/solid-state device manufacturingChemical vapor deposition coatingPre treatmentPre deposition

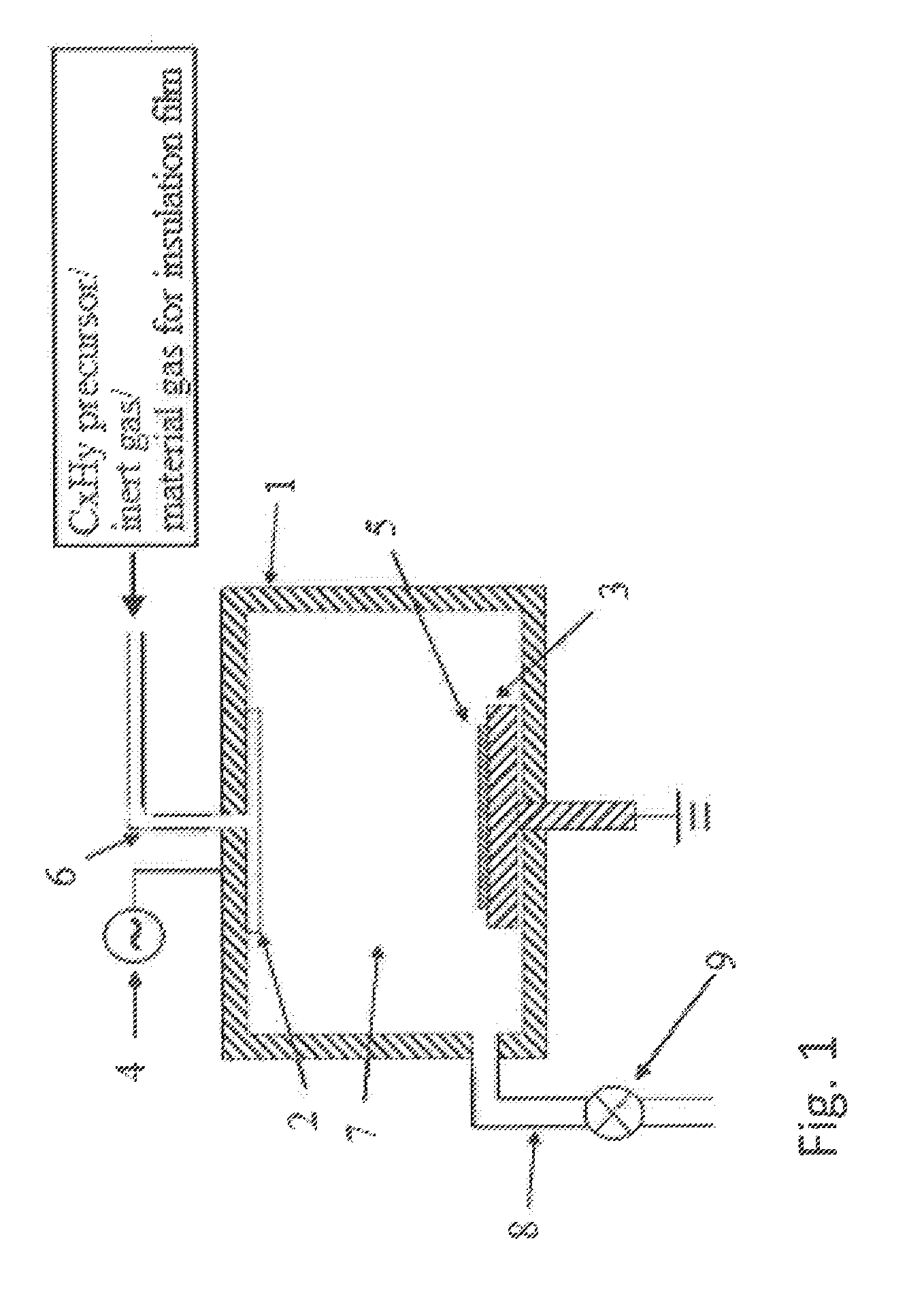

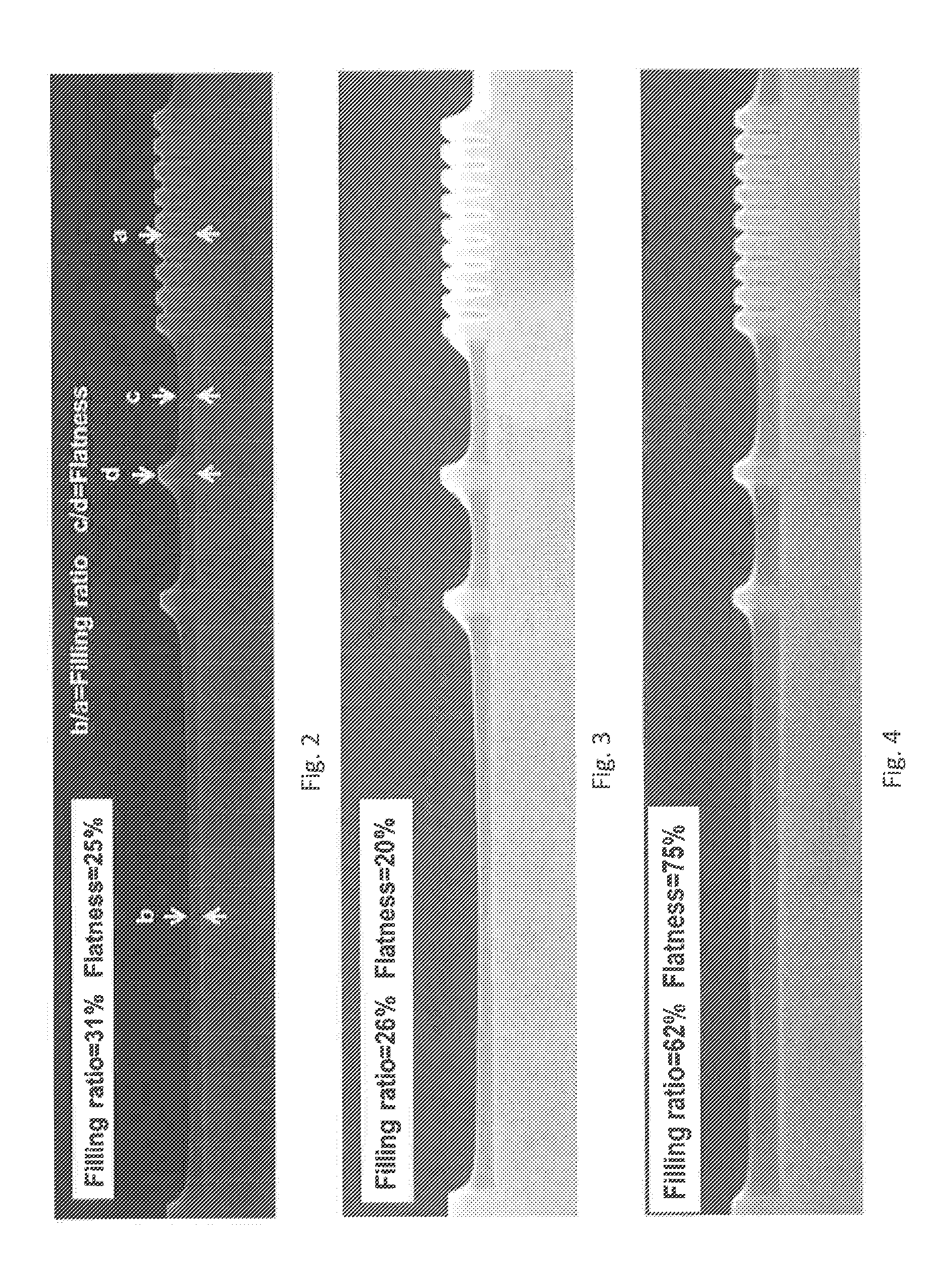

A method for filling recesses of a substrate with an insulation film includes: (i) exposing surfaces of the recesses of the substrate to a pre-deposition gas in a reactive state in a reaction space to treat the surfaces with reactive hydrocarbons generated from the pre-deposition gas without filling the recesses; and (ii) depositing a flowable insulation film using a process gas other than the pre-deposition gas on a surface of the substrate to fill the recesses treated in step (i) therewith by plasma reaction. The pre-deposition gas has at least one hydrocarbon unit in its molecule.

Owner:ASM IP HLDG BV

Method For Filling Recesses Using Pre-Treatment With Hydrocarbon-Containing Gas

ActiveUS20140363983A1Improve flatnessHighly effectiveSemiconductor/solid-state device manufacturingChemical vapor deposition coatingPre treatmentPlasma reaction

A method for filling recesses of a substrate with an insulation film includes: (i) exposing surfaces of the recesses of the substrate to a pre-deposition gas in a reactive state in a reaction space to treat the surfaces with reactive hydrocarbons generated from the pre-deposition gas without filling the recesses; and (ii) depositing a flowable insulation film using a process gas other than the pre-deposition gas on a surface of the substrate to fill the recesses treated in step (i) therewith by plasma reaction. The pre-deposition gas has at least one hydrocarbon unit in its molecule.

Owner:ASM IP HLDG BV

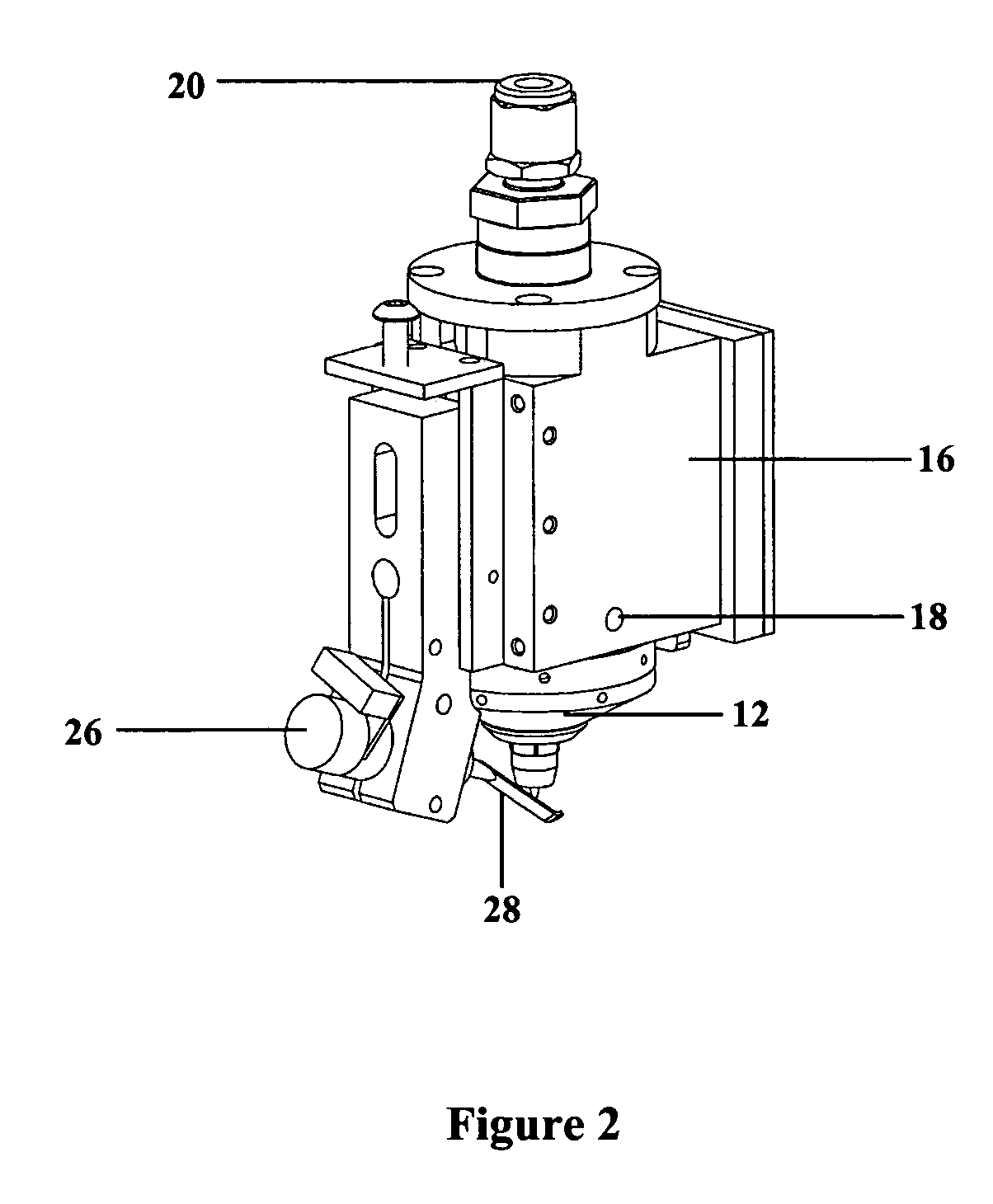

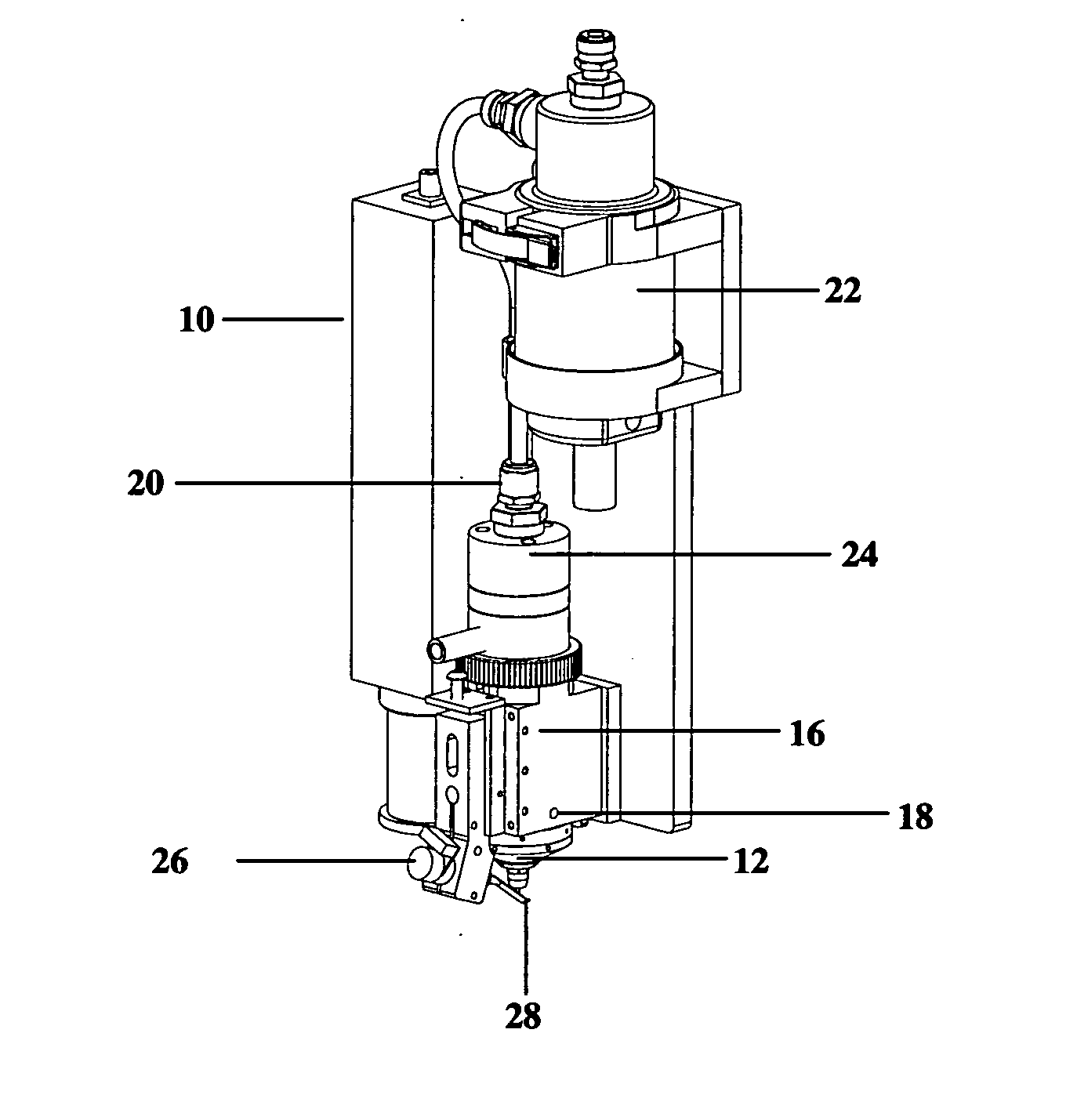

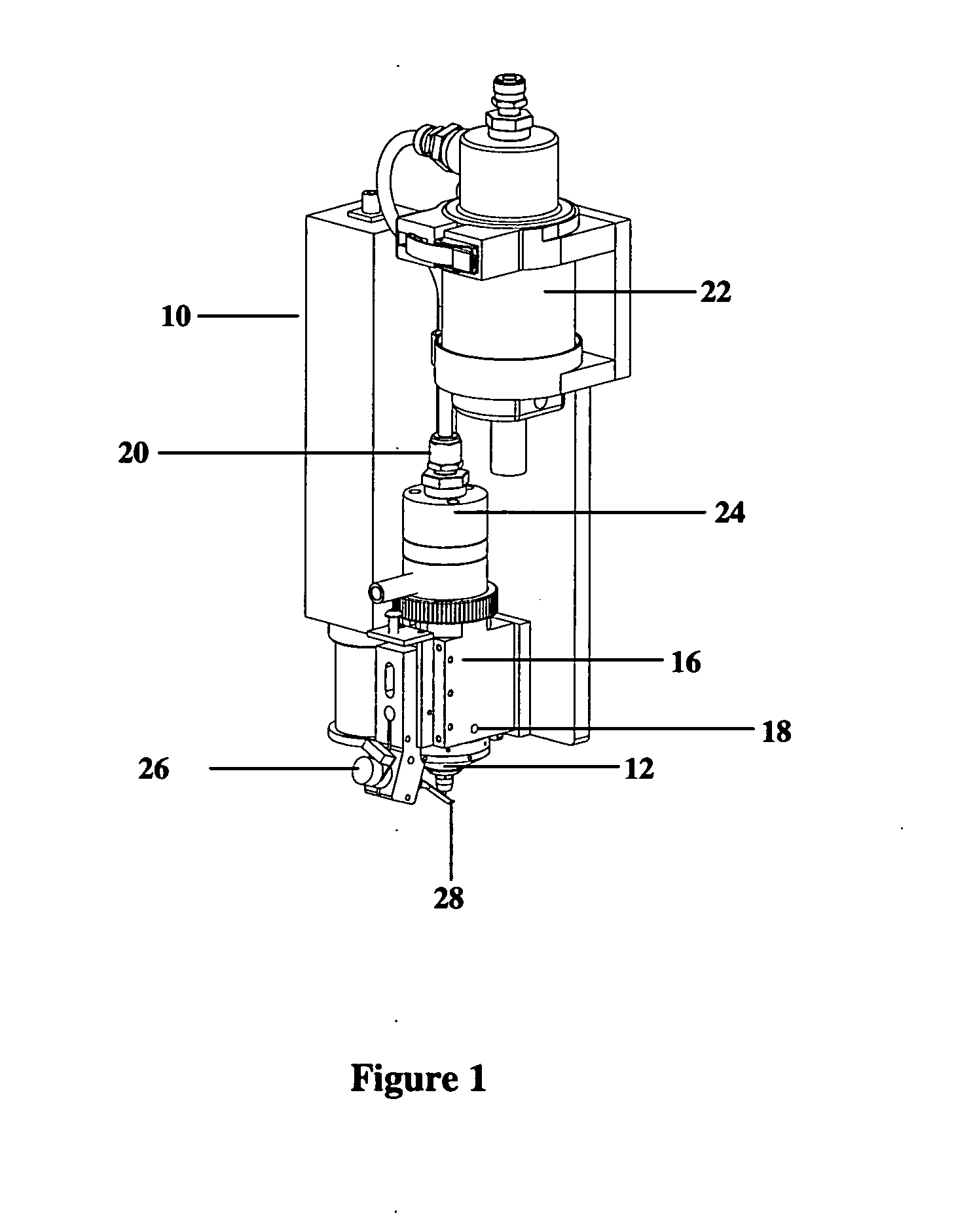

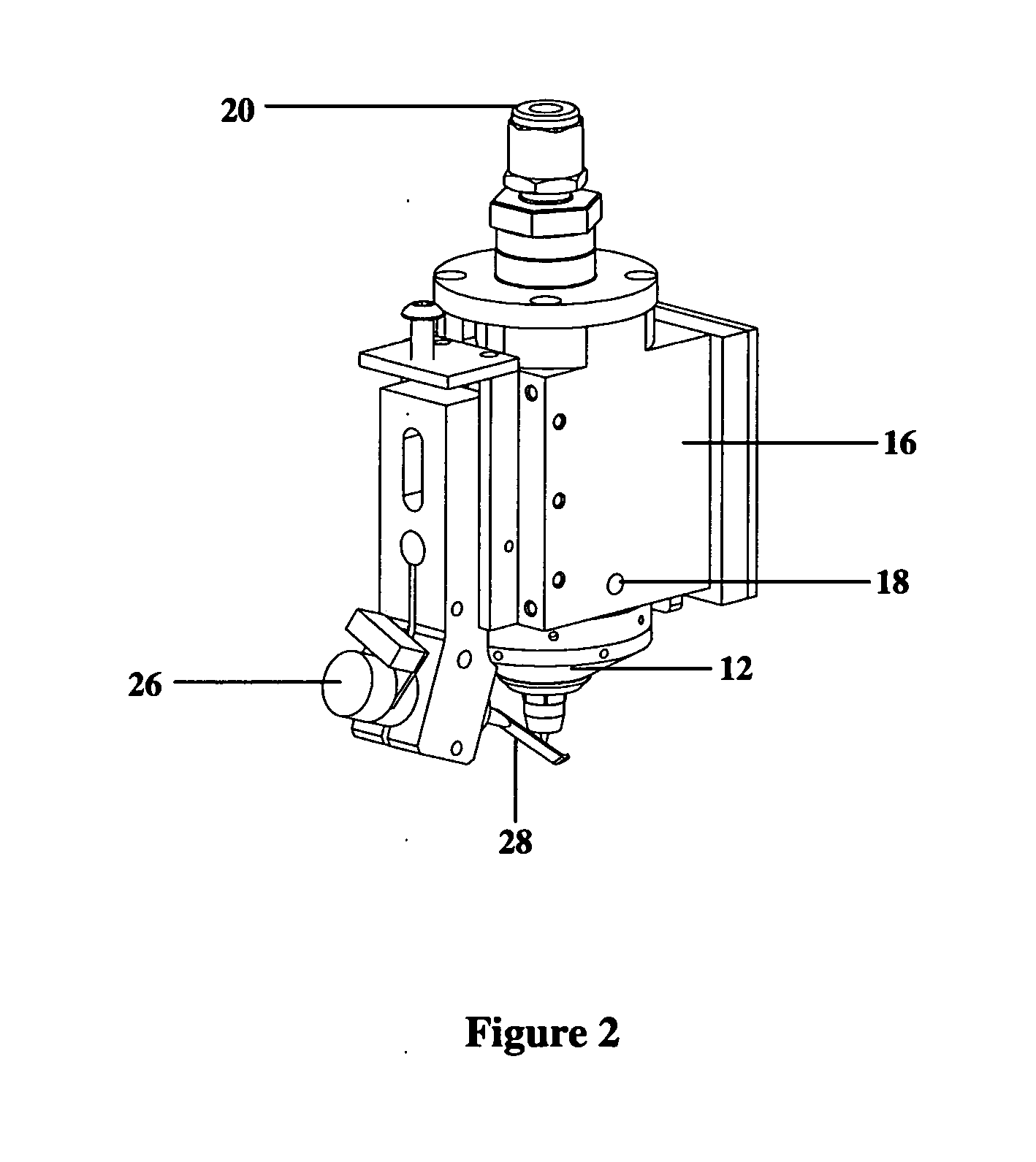

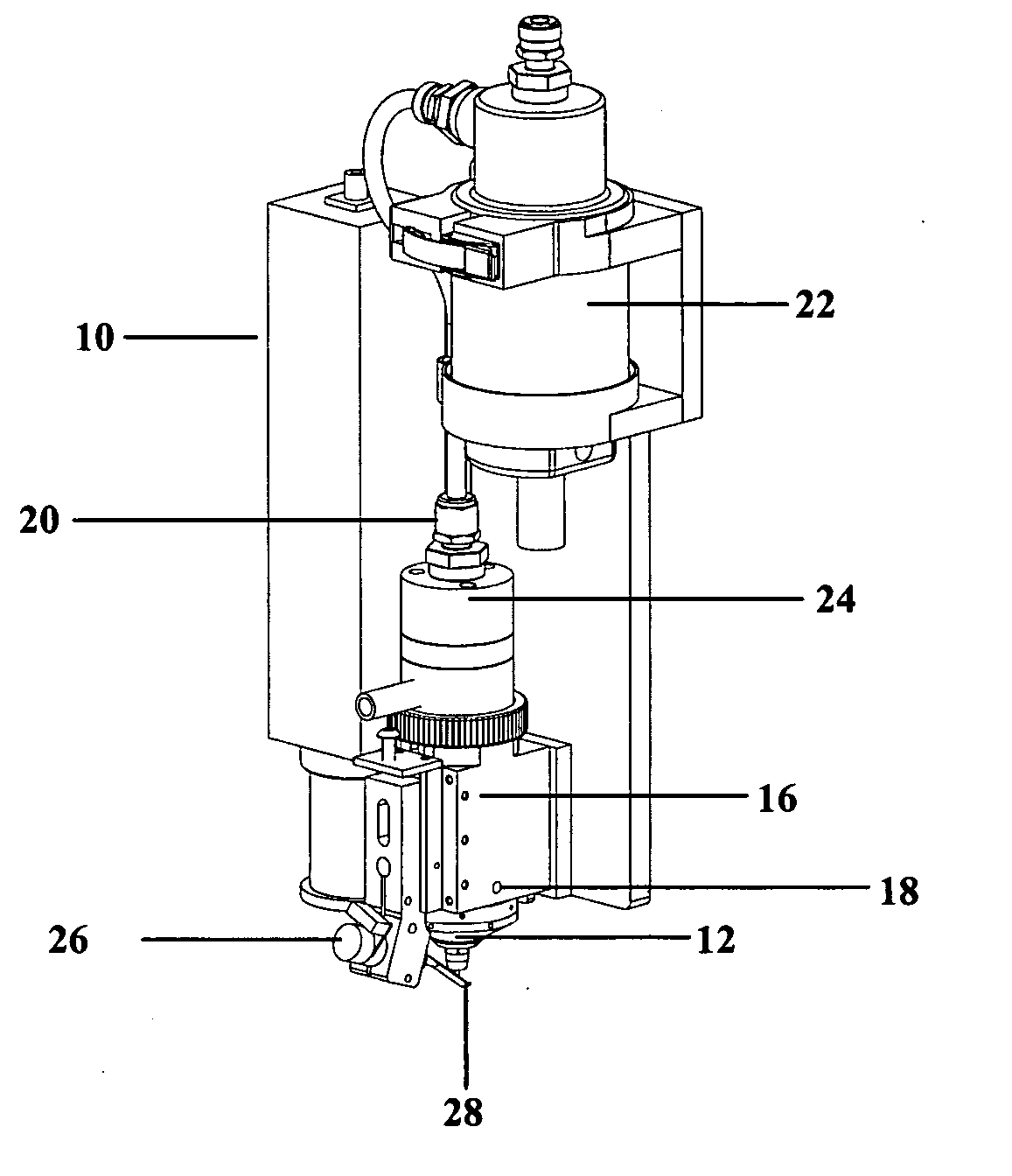

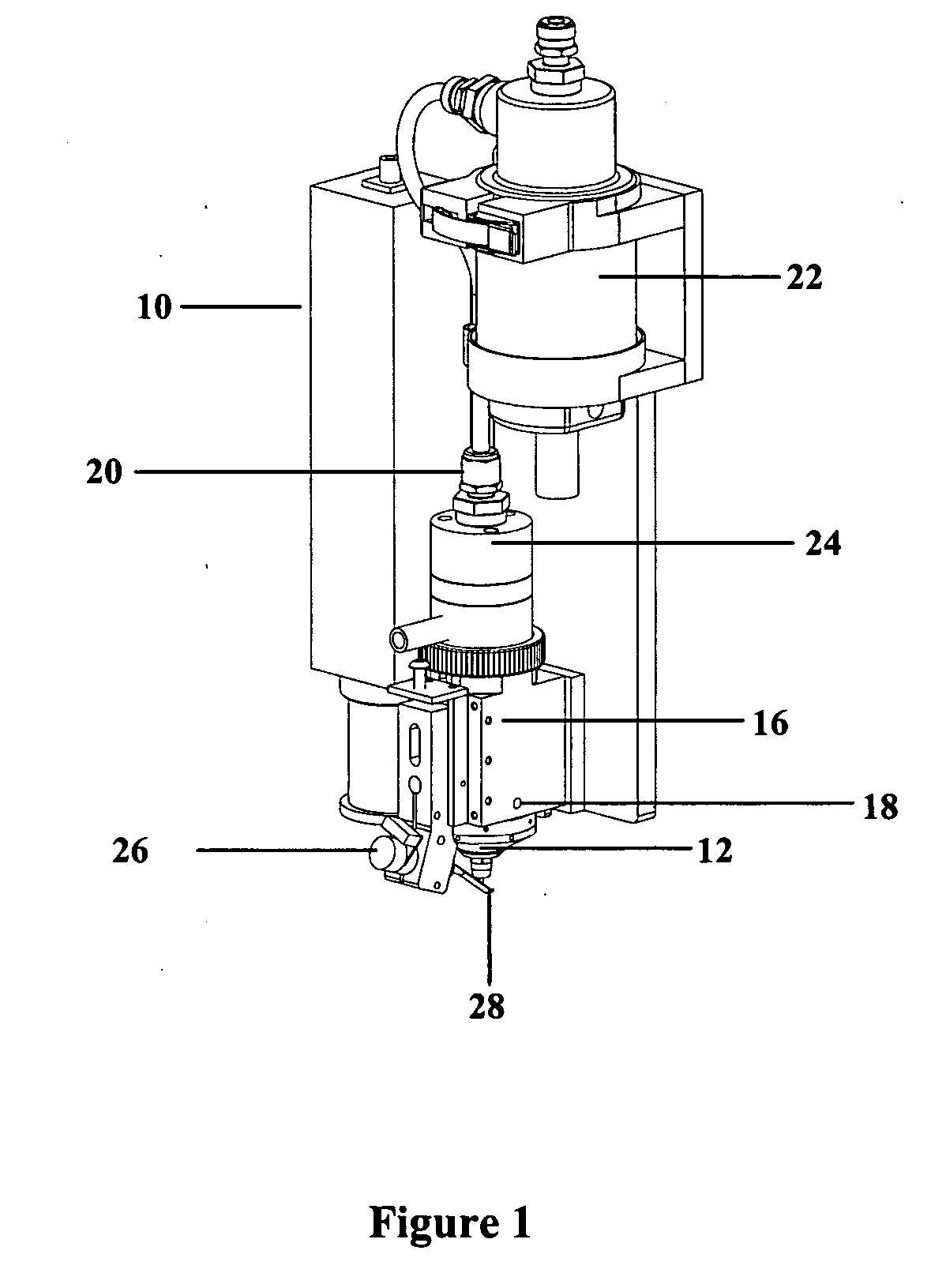

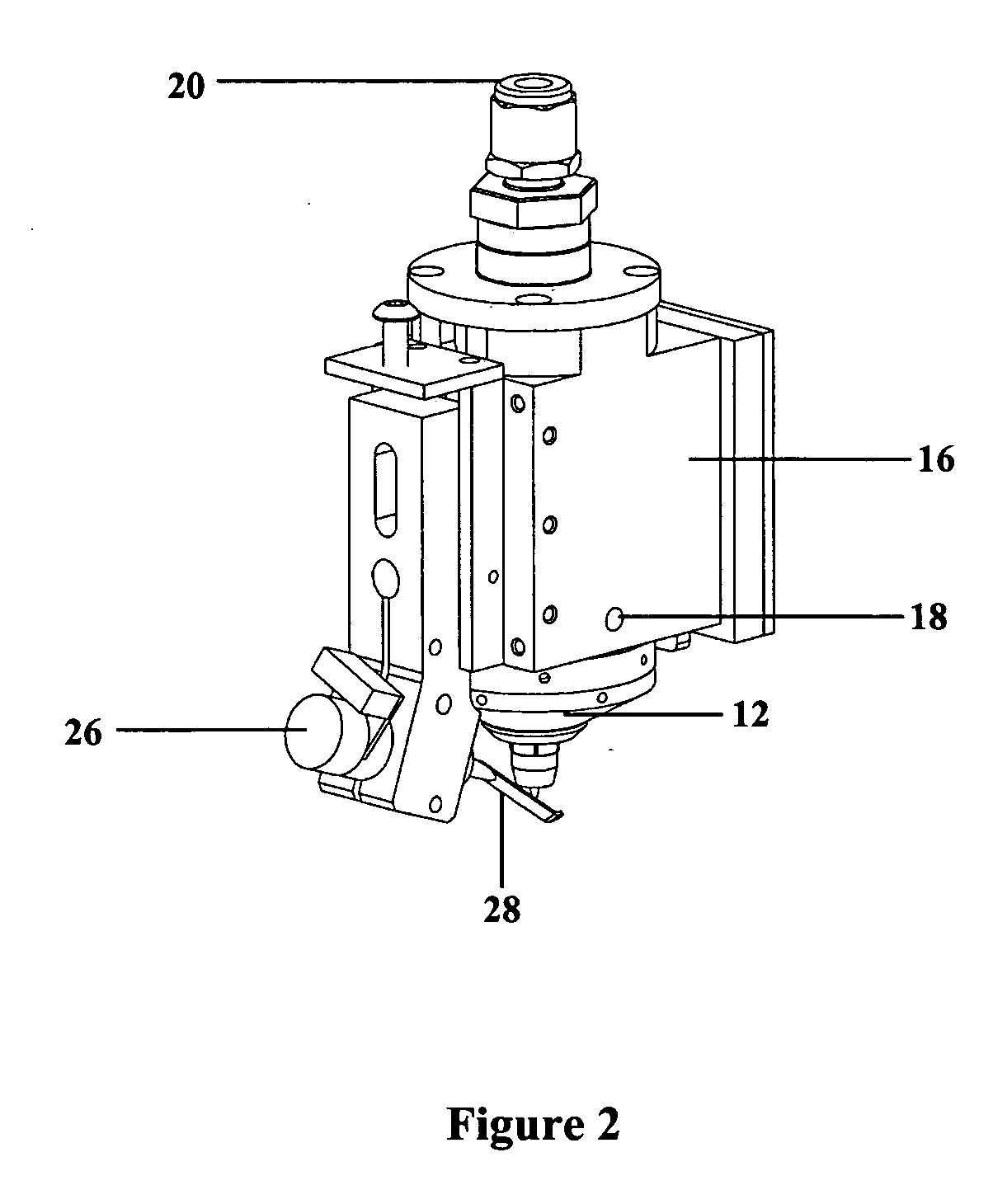

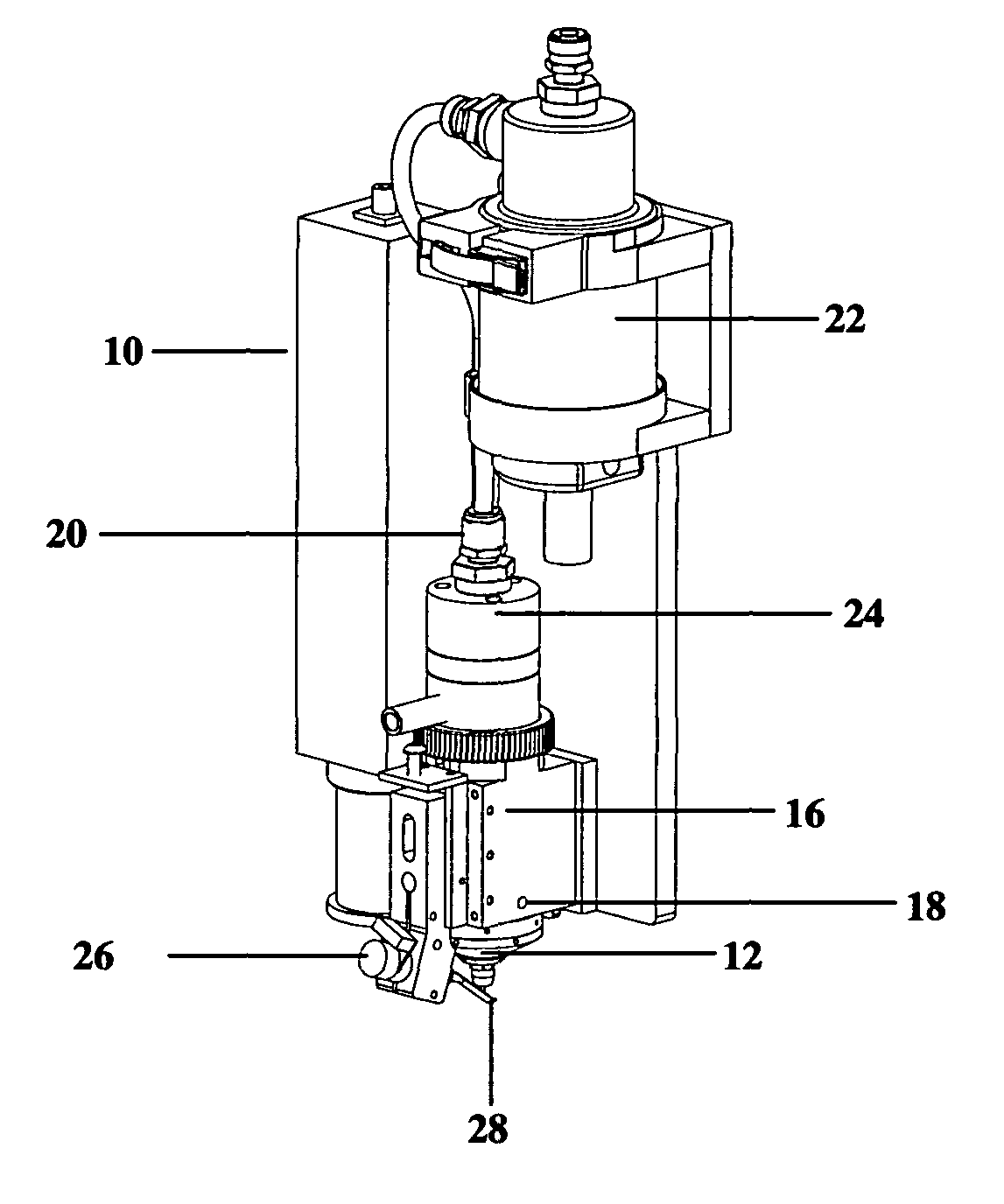

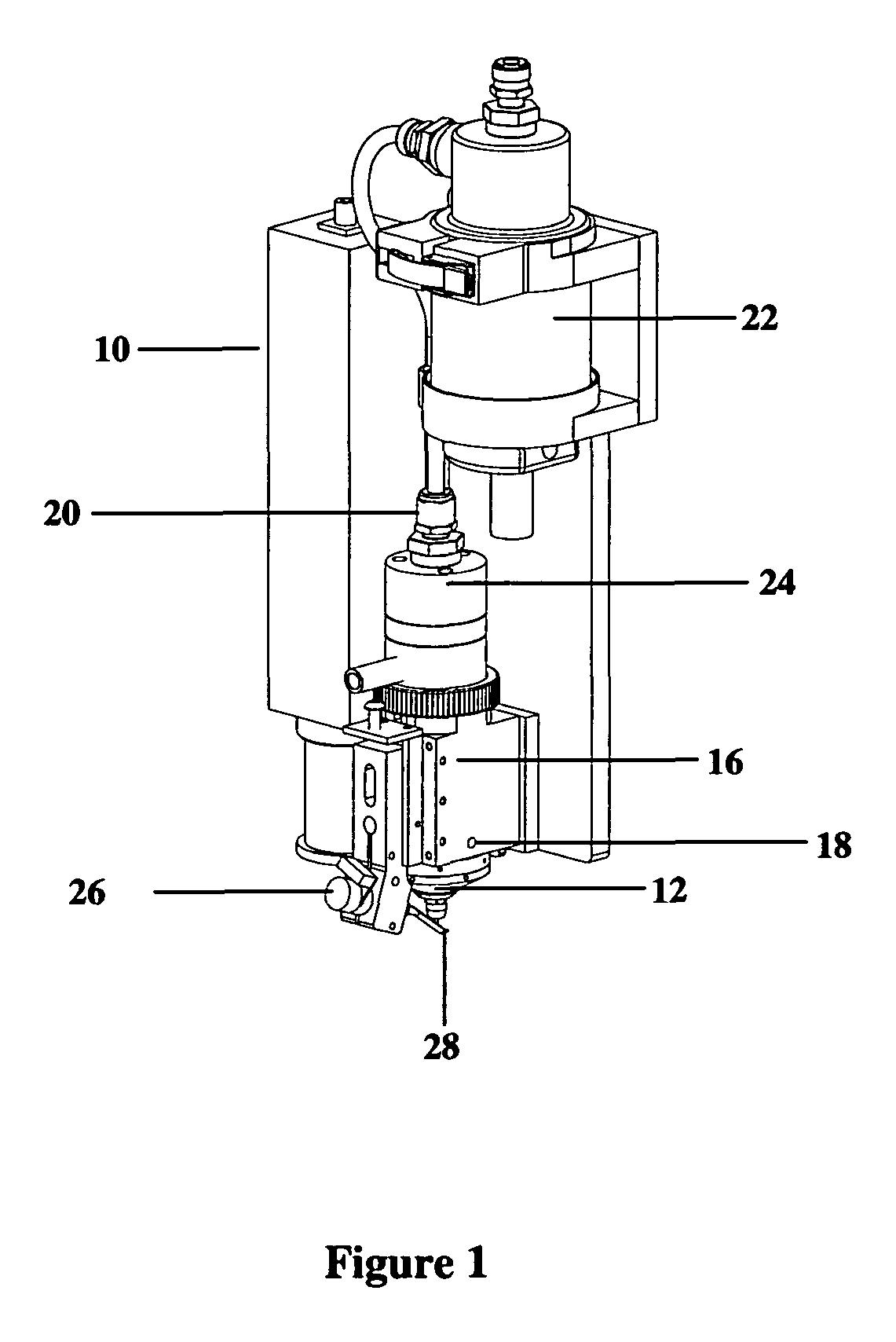

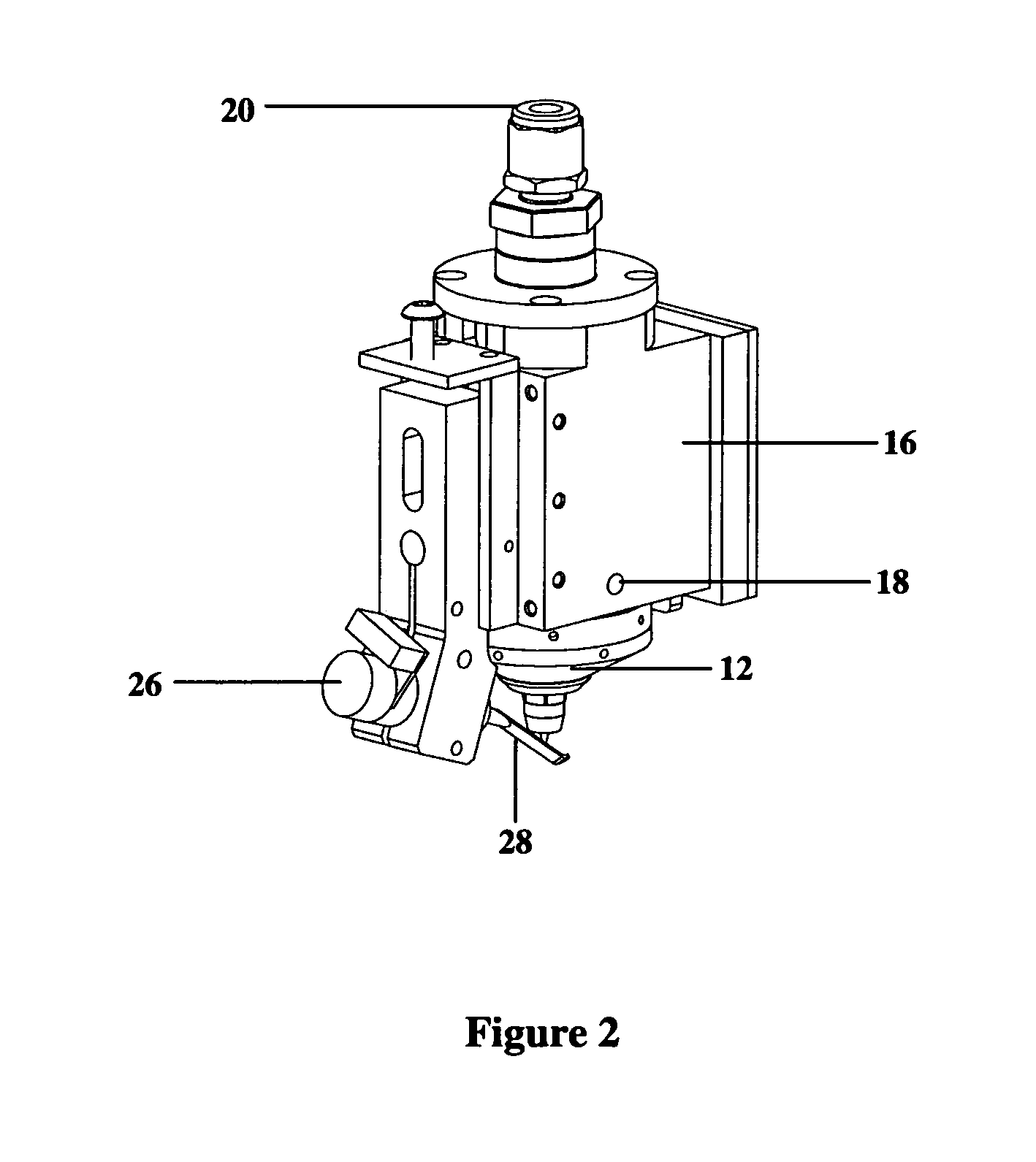

Laser processing for heat-sensitive mesoscale deposition

InactiveUS7294366B2Low damage thresholdElectric discharge heatingRadiation applicationsLaser processingHeat sensitive

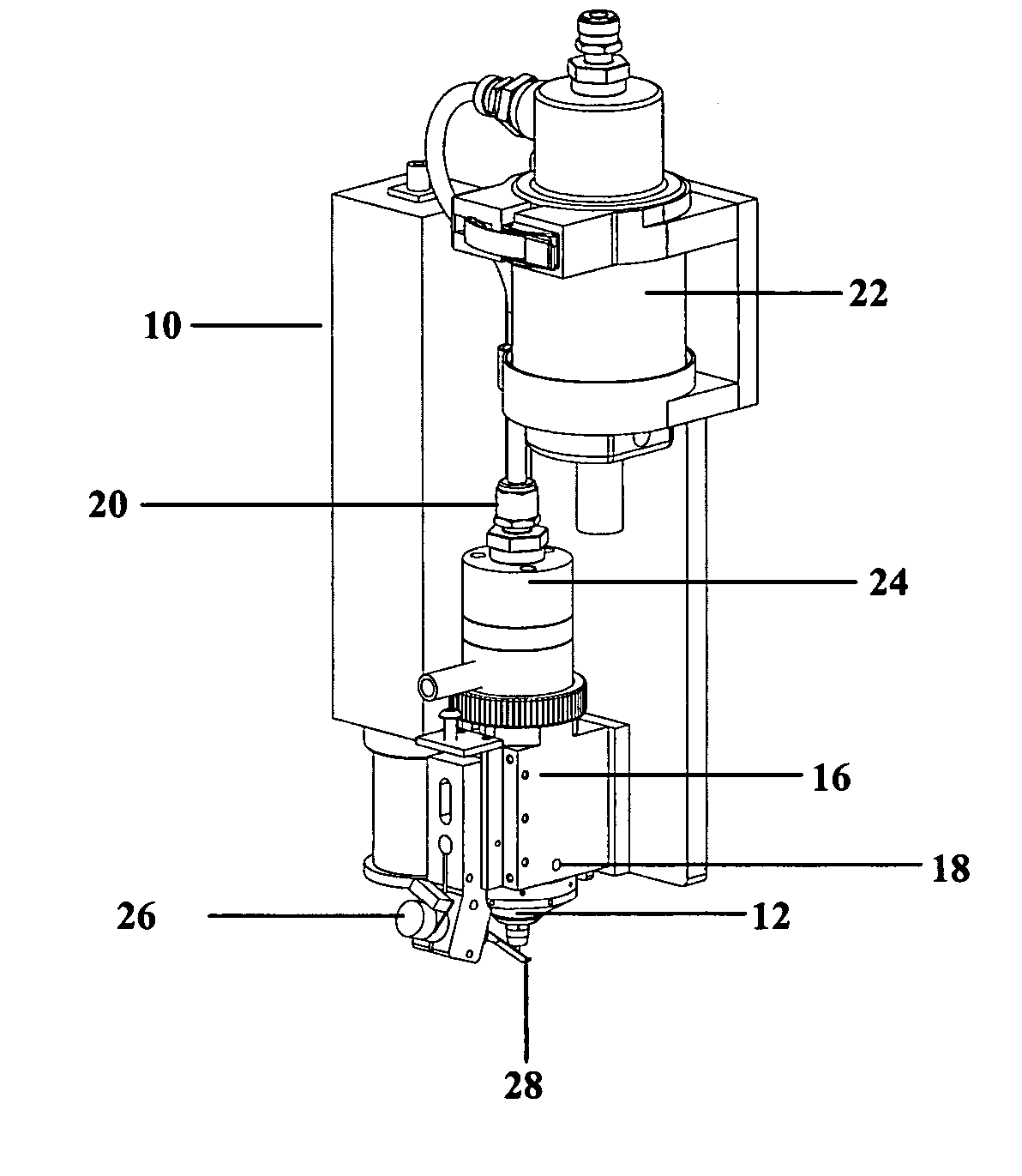

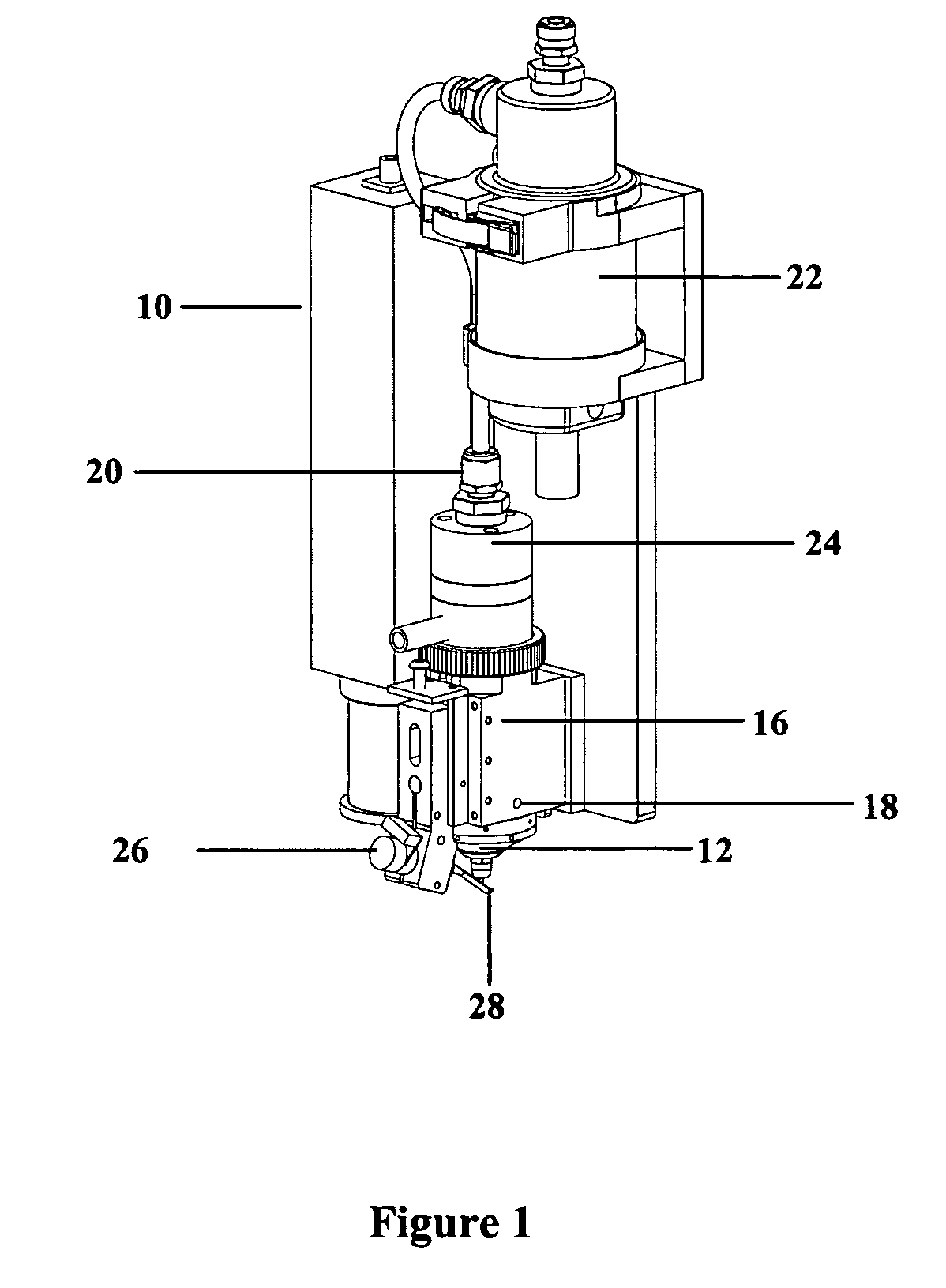

A method of depositing various materials onto heat-sensitive targets. Heat-sensitive targets are generally defined as targets that have thermal damage thresholds that are lower than the temperature required to process a deposited material. The invention uses precursor solutions and / or particle or colloidal suspensions, along with optional pre-deposition treatment and / or post-deposition treatment to lower the laser power required to drive the deposit to its final state. The present invention uses Maskless Mesoscale Material Deposition (M3D™) to perform direct deposition of material onto the target in a precise, highly localized fashion. Features with linewidths as small as 4 microns may be deposited, with little or no material waste. A laser is preferably used to heat the material to process it to obtain the desired state, for example by chemical decomposition, sintering, polymerization, and the like. This laser processing may be performed in an ambient environment with laser powers of less than 100 milliwatts.

Owner:OPTOMEC DESIGN CO

Laser processing for heat-sensitive mesoscale deposition of oxygen-sensitive materials

InactiveUS20070019028A1Damage to materialRadiation applicationsPretreated surfacesForming gasHeat sensitive

A method of depositing various materials onto heat-sensitive targets, particularly oxygen-sensitive materials. Heat-sensitive targets are generally defined as targets that have thermal damage thresholds that are lower than the temperature required to process a deposited material. The invention uses precursor solutions and / or particle or colloidal suspensions, along with optional pre-deposition treatment and / or post-deposition treatment to lower the laser power required to drive the deposit to its final state. The present invention uses Maskless Mesoscale Material Deposition (M3D™) to perform direct deposition of material onto the target in a precise, highly localized fashion. Features with linewidths as small as 4 microns may be deposited, with little or no material waste. A laser is preferably used to heat the material to process it to obtain the desired state, for example by chemical decomposition, sintering, polymerization, and the like. This laser processing may be performed in an ambient environment with laser powers of less than 100 milliwatts. Cover gases and / or forming gases may be used during thermal processing to change the material properties, for example by preventing oxidation.

Owner:OPTOMEC DESIGN CO

Laser processing for heat-sensitive mesoscale deposition

InactiveUS20050129383A1Low damage thresholdDamage to materialSolid-state devicesMetal-working apparatusLaser processingHeat sensitive

A method of depositing various materials onto heat-sensitive targets. Heat-sensitive targets are generally defined as targets that have thermal damage thresholds that are lower than the temperature required to process a deposited material. The invention uses precursor solutions and / or particle or colloidal suspensions, along with optional pre-deposition treatment and / or post-deposition treatment to lower the laser power required to drive the deposit to its final state. The present invention uses Maskless Mesoscale Material Deposition (M3D™) to perform direct deposition of material onto the target in a precise, highly localized fashion. Features with linewidths as small as 4 microns may be deposited, with little or no material waste. A laser is preferably used to heat the material to process it to obtain the desired state, for example by chemical decomposition, sintering, polymerization, and the like. This laser processing may be performed in an ambient environment with laser powers of less than 100 milliwatts.

Owner:OPTOMEC DESIGN CO

Laser processing for heat-sensitive mesoscale deposition of oxygen-sensitive materials

InactiveUS8110247B2Low damage thresholdRadiation applicationsPretreated surfacesForming gasLaser processing

Owner:OPTOMEC DESIGN CO

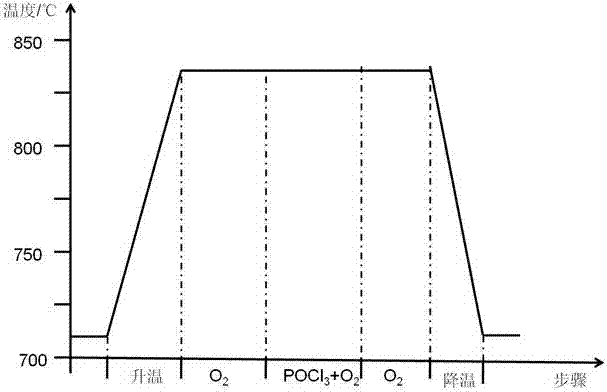

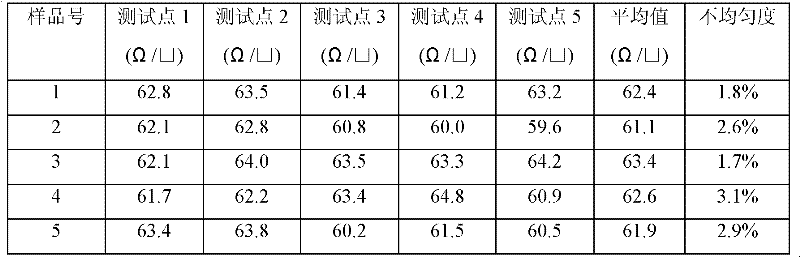

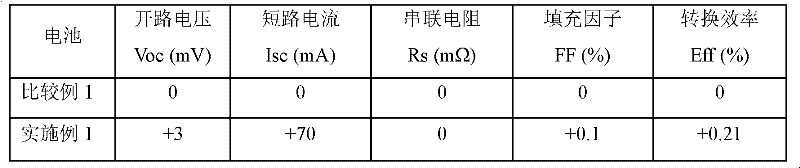

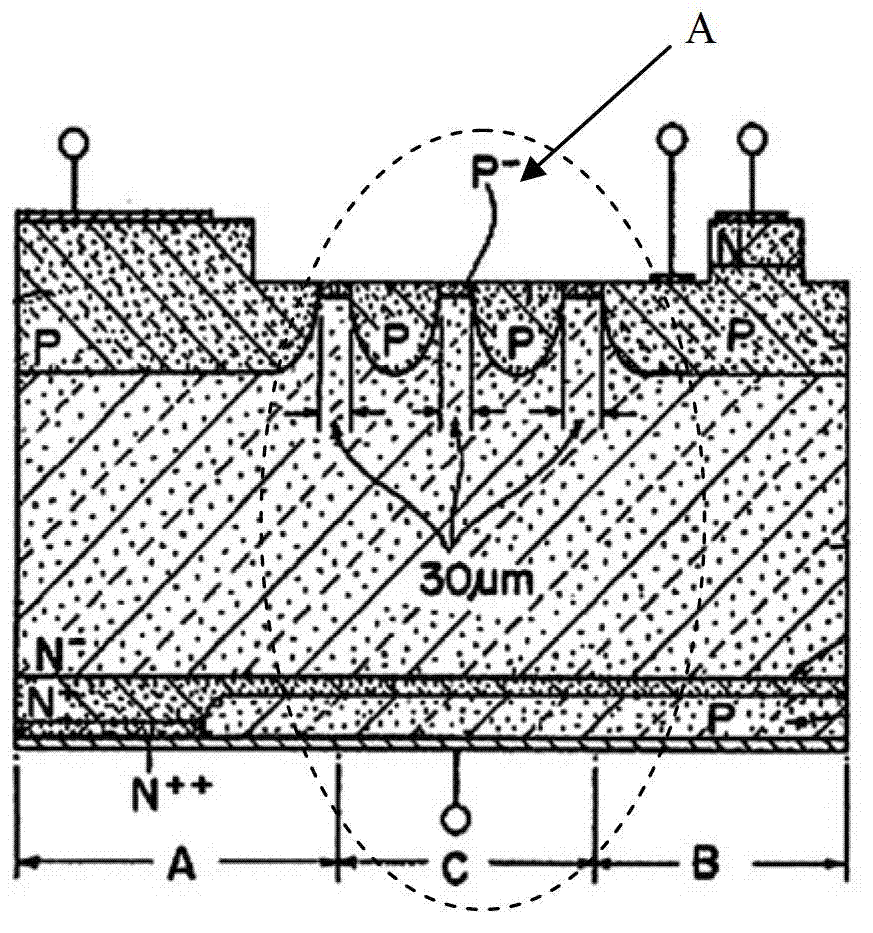

Spread method of polycrystalline silicon solar cell

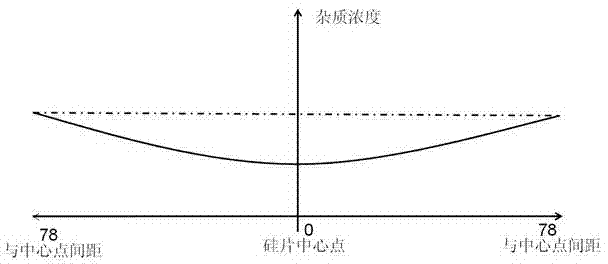

InactiveCN102820383AImprove square resistance uniformityUniform concentration distributionFinal product manufactureDiffusion/dopingPre depositionSilicon chip

The invention relates to a spread method of a polycrystalline silicon solar cell. The spread method is characterized in that the spread method comprises the following processing steps of entering a boat, warming, oxidizing, spreading, redistributing, cooling and going out the boat, wherein the spreading step comprises low temperature pre-deposition and then high temperature spreading. Reaction between a phosphorus source and a silicon wafer cannot be completed under low temperature, so that the low temperature pre-deposition is carried out on low temperature source communication at a first step of spreading, the phosphorus source cannot spread (or conduct spreading with low rate) inside a silicon wafer, the phosphorus source only accumulates on the surface of the silicon wafer, and a phosphorus film with certain thickness is formed on the surface of the silicon wafer after source communication for certain time; and the high temperature spreading is carried out on high temperature source communication at a second step, phosphorus on the surface of an original silicon wafer is reacted with the silicon wafer and spreads to the inside of the silicon wafer, and spreading rates of the center point and the periphery of the silicon wafer are same. Therefore, spreading uniformity is good, concentration distribution of impurities on the surface of the silicon wafer and inside the silicon wafer body is even, sheet resistance uniformity is improved, and final photoelectric conversion efficiency of a cell sheet is improved accordingly.

Owner:JIANGYIN XINHUI SOLAR ENERGY

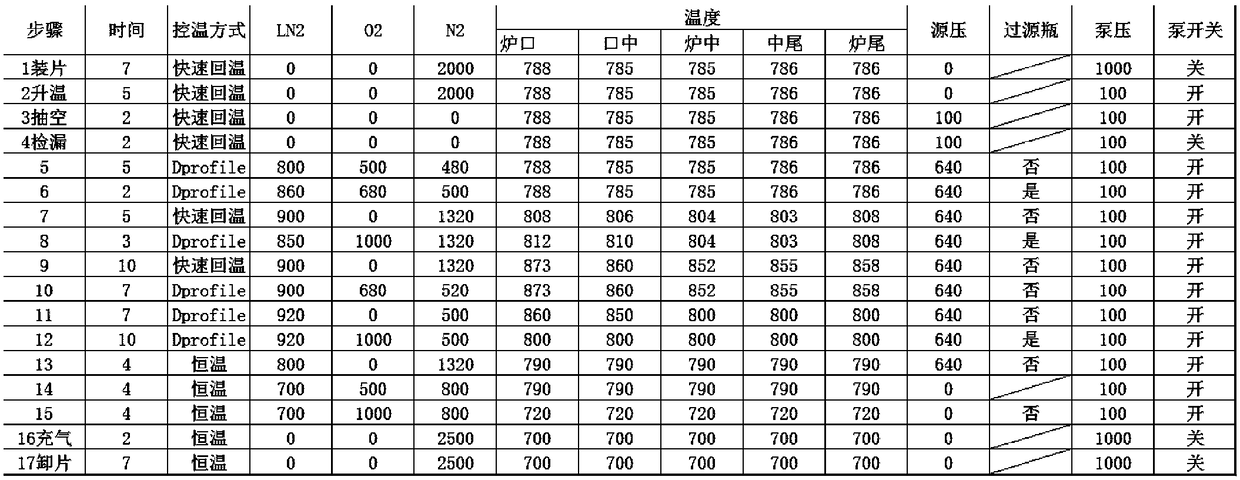

Phosphorus gettering process of silicon chip

InactiveCN101667605AImprove electrical performance parametersIncreased average life expectancyFinal product manufactureSemiconductor devicesEtchingSurface oxidation

The invention relates to a phosphorus gettering process of silicon chips in the manufacture of solar cells, which comprises the following steps: putting sueded silicon chips into a diffusion furnace for pre-deposition, removing a phosphorosilicate glass layer after diffusion, soaking the silicon chips through distributed processing in a hydrofluoric acid solution, and removing oxide layers from the surfaces of the silicon chips; then putting the silicon chips after washing into the diffusion furnace for secondary diffusion processing, taking the silicon chips out from the diffusion furnace after the processing of the secondary diffusion working procedure, cooling the silicon chips to room temperature, and measuring the square resistance of the silicon chips. The invention can effectively decrease heavily doped 'dead layers' and greatly prolong the average minority carrier lifetime of the silicon chips; after the processes including etching, PECVD, silk screen sintering and the like arefinished according to the normal process of a cell chip, the average transformation efficiency of the made cell chip is further improved, and the cell chip has better electrical performance parameters.

Owner:无锡尚品太阳能电力科技有限公司

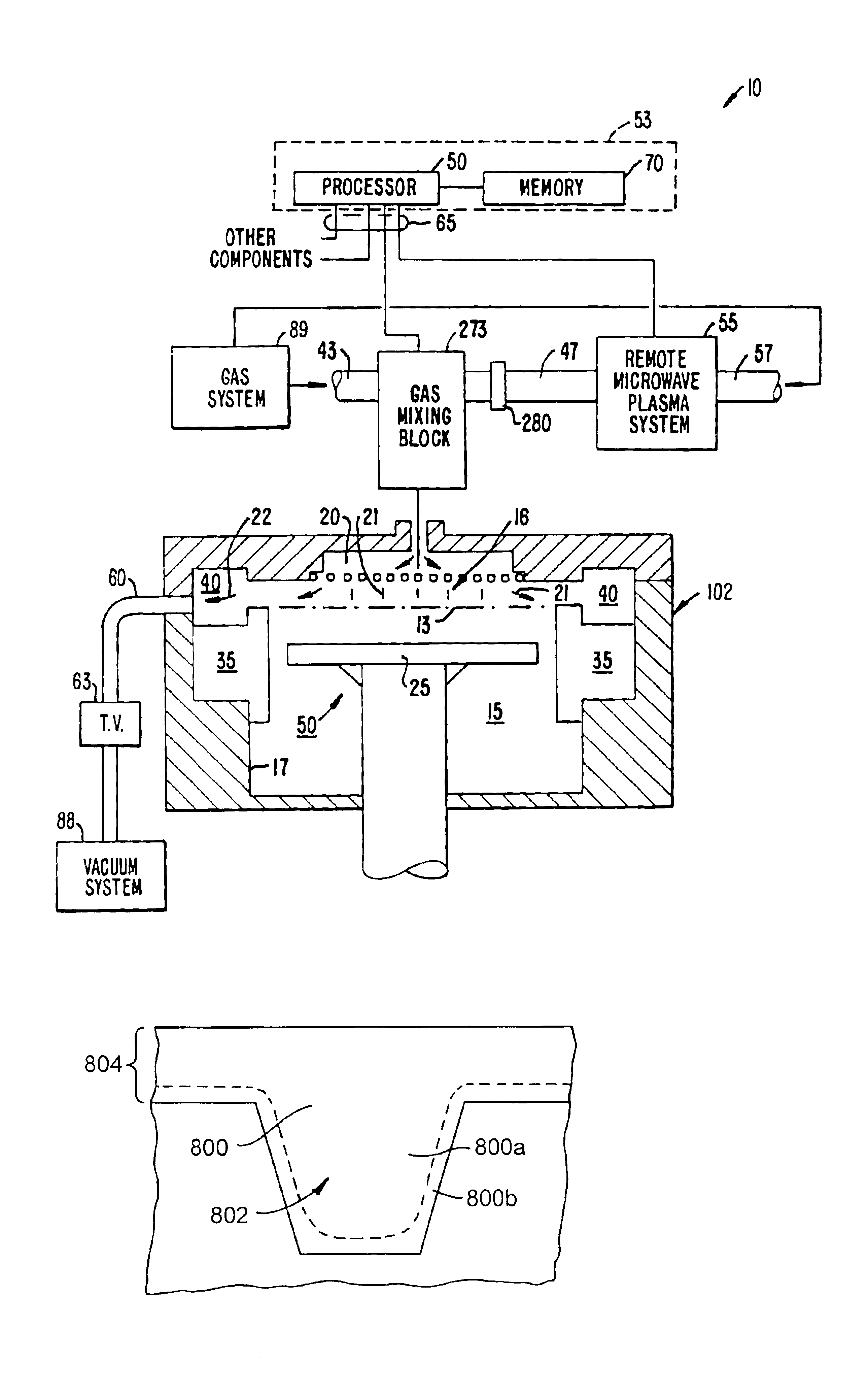

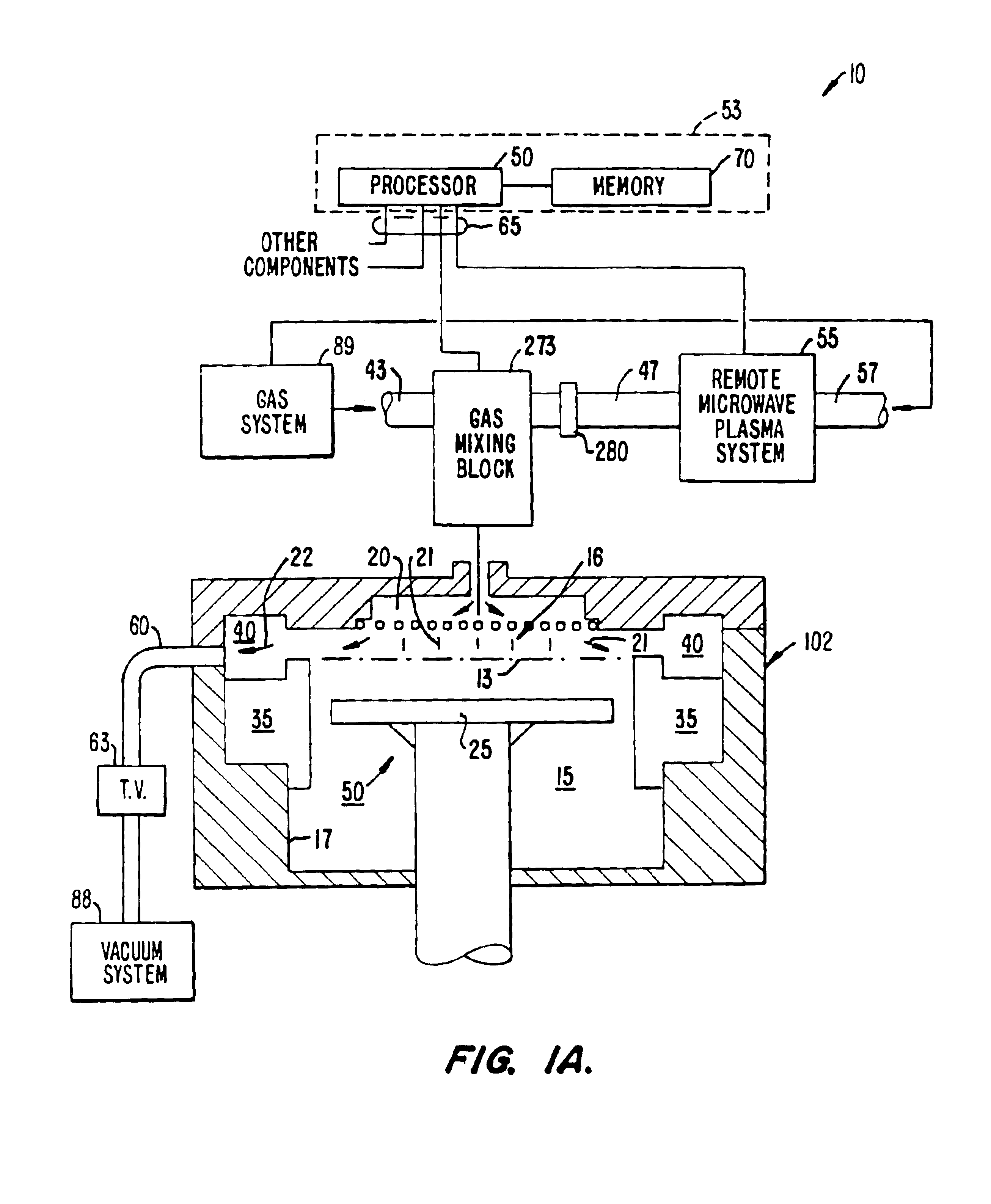

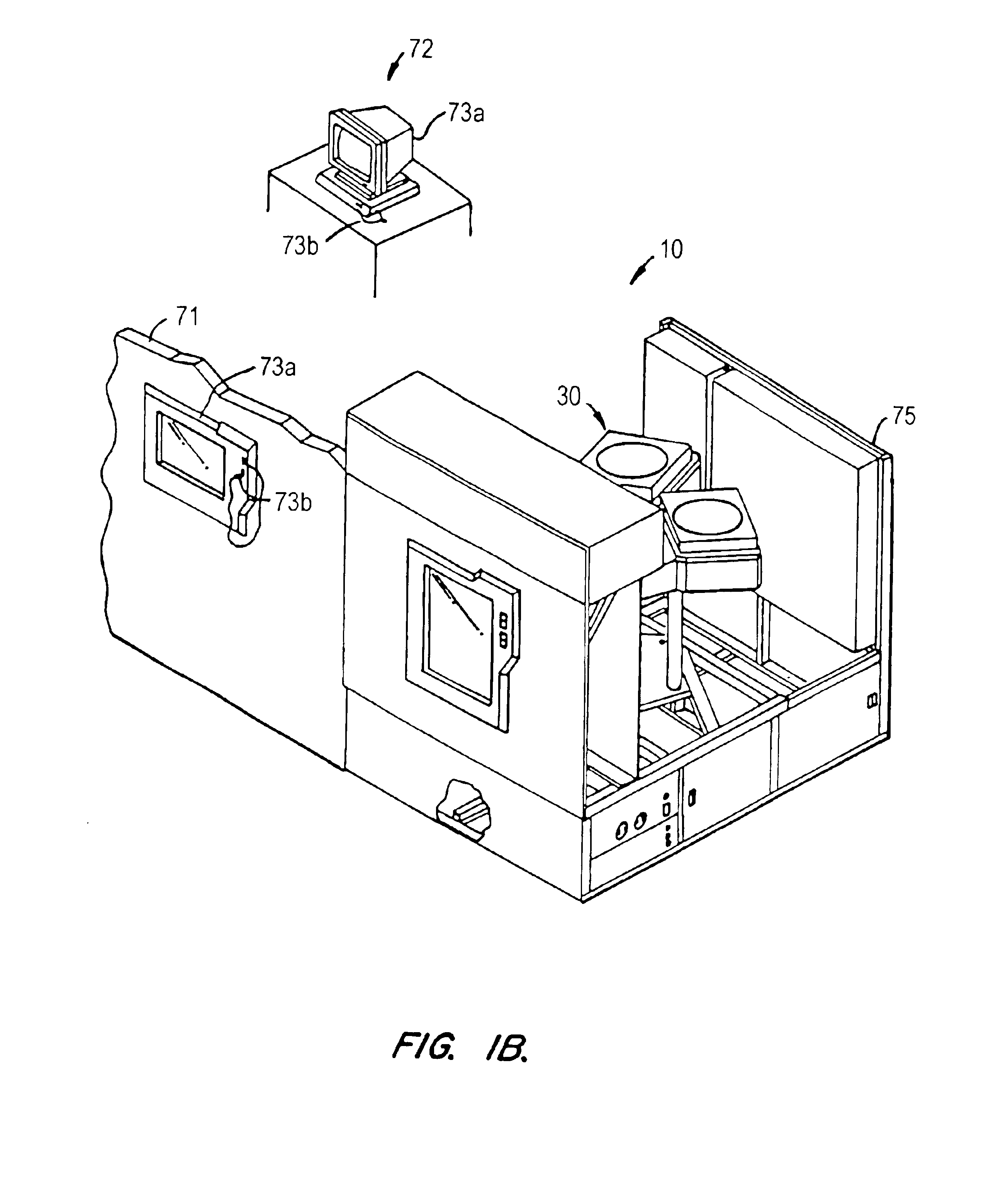

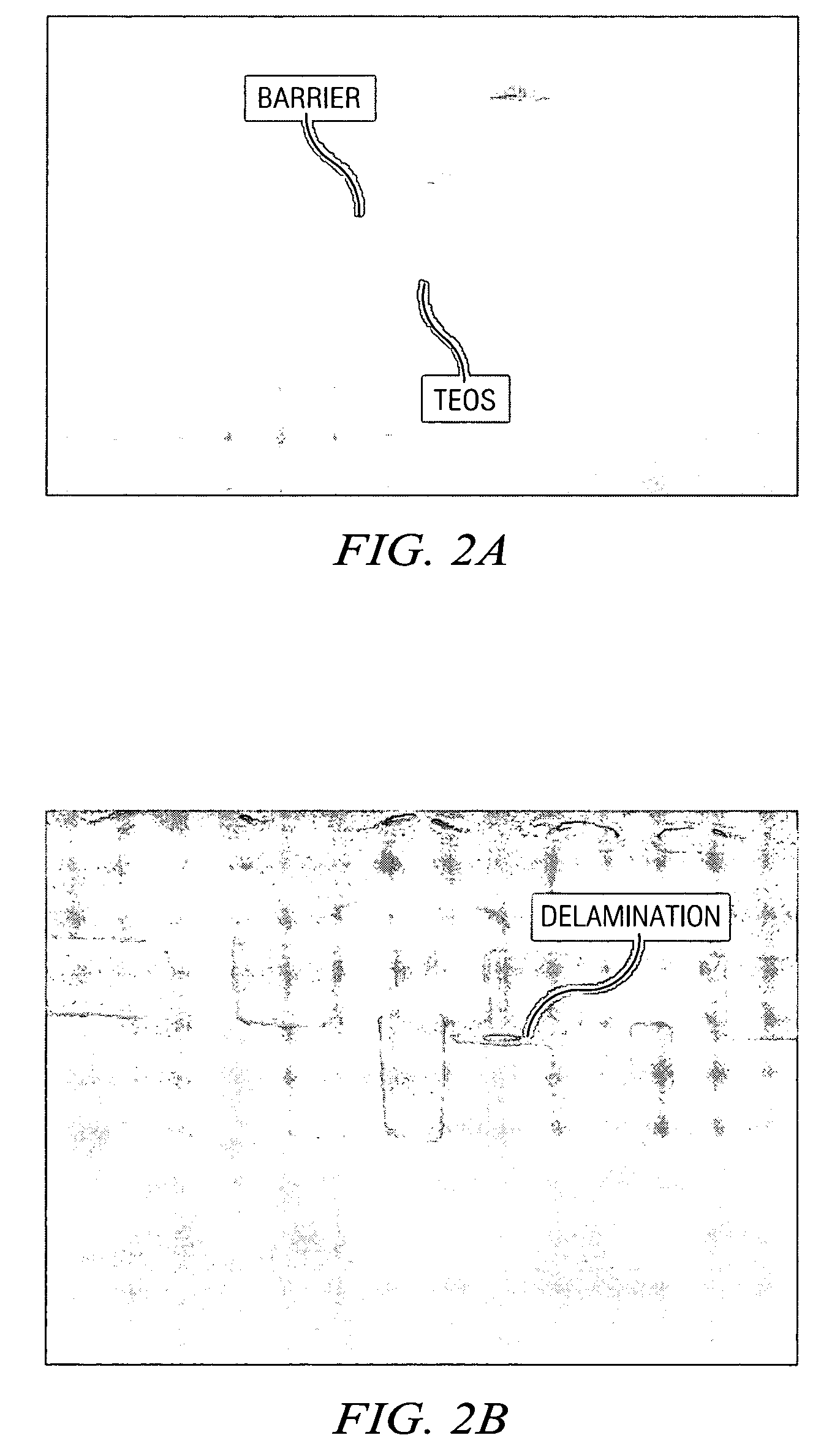

Method using TEOS ramp-up during TEOS/ozone CVD for improved gap-fill

InactiveUS6905940B2Excellent gap fillingImprove throughputSemiconductor/solid-state device manufacturingChemical vapor deposition coatingGas phaseSilicon oxide

Embodiments of the present invention provide methods, apparatuses, and devices related to chemical vapor deposition of silicon oxide. In one embodiment, a single-step deposition process is used to efficiently form a silicon oxide layer exhibiting high conformality and favorable gap-filling properties. During a pre-deposition gas flow stabilization phase and an initial deposition stage, a relatively low ratio of silicon-containing gas:oxidant deposition gas is flowed, resulting in formation of highly conformal silicon oxide at relatively slow rates. Over the course of the deposition process step, the ratio of silicon-containing gas:oxidant gas is increased, resulting in formation of less-conformal oxide material at relatively rapid rates during later stages of the deposition process step.

Owner:APPLIED MATERIALS INC

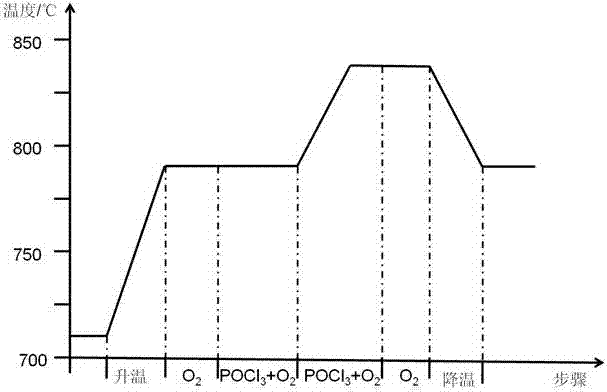

Three-step variable-temperature diffusion process for silicon cell

ActiveCN102383198AIncrease concentrationIncrease junction depthFinal product manufactureDiffusion/dopingFurnace temperatureOxygen

The invention relates to a three-step variable-temperature diffusion process for a silicon cell, which is realized by the following procedures: placing a silicon chip after etching into a boat, then rising the temperature to be 700-810 DEG C, and introducing large nitrogen, small nitrogen and oxygen to conduct low-temperature pre-deposition diffusion; subsequently rising the temperature to be 810-830 DEG C, and introducing large nitrogen to conduct knot thrusting; and then introducing large nitrogen, small nitrogen and oxygen, and rising the furnace temperature to be 830-870 DEG C to conduct secondary deposition diffusion. A multi-level PN knot structure formed after diffusion can ensure good ohmic contact with a metal gate wire on the one hand, and can have good blue response on the other hand; in addition, a PN knot formed by the method has great knot depth, and the possibility that the PN knot is burnt through, subjected to leakage of electricity and composited can be reduced.

Owner:REALFORCE POWER

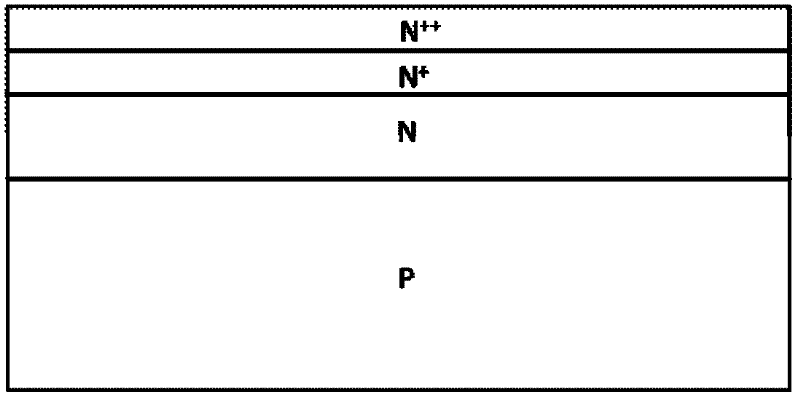

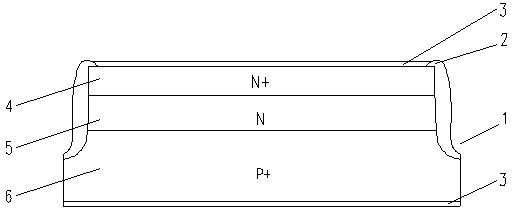

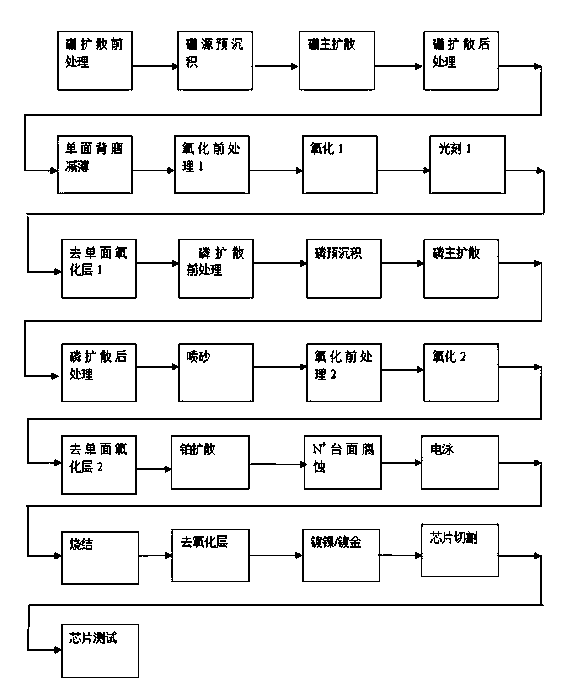

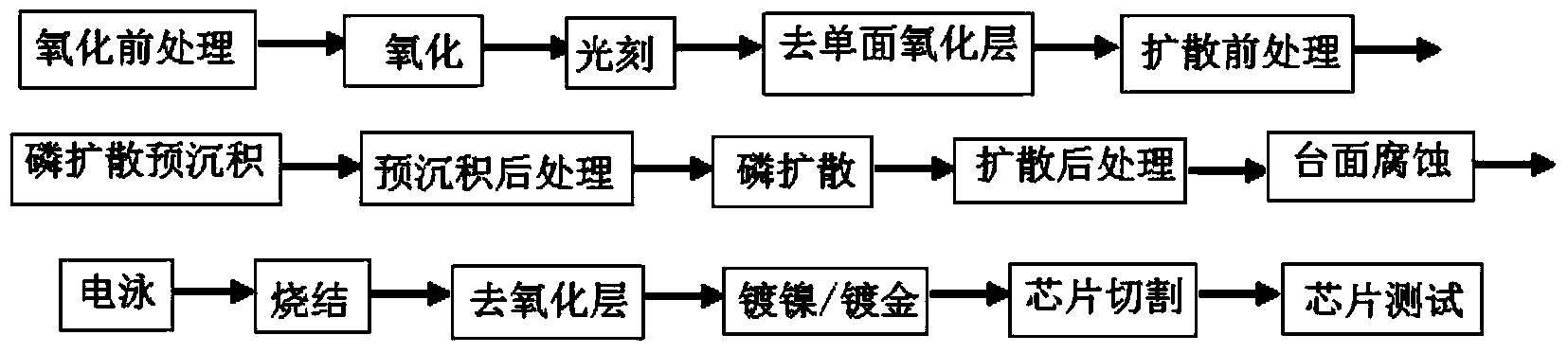

Fast recovery diode FRD chip and production process for same

ActiveCN104201102AImprove anti-surge performanceImprove flatnessSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingLayer removal

The invention relates to a fast recovery diode FRD chip and a production process for the same. The process comprises the following steps of: diffusion pre-treatment, boron source pre-deposition, boron source main diffusion, diffusion after-treatment, single-surface back grinding thinning, oxidation pre-treatment, oxidation, photoetching, single-surface oxide layer removal, phosphorus source pre-deposition, phosphorus diffusion, sand blasting, platinum diffusion, N + surface mesa etching, electrophoresis, sintering, oxide layer removal, nickel plating, gold plating and chip cutting, wherein the structure of the obtained chip is P+-N-N+ type. According to the process, the uniformity of the reverse recovery time of the fast recovery diode is improved and controllability is improved, meanwhile, voltage drop is reduced, leakage current is reduced, and voltage-proof stability is improved; the contradiction of mutual condition among the reverse voltage, the positive voltage, the reverse recovery time and the leakage current of the fast recovery diode is solved to enable the various parameters to achieve the optimal matching, thus improving the reliability and switching characteristic of the diode, and reducing power consumption. The fast recovery diode disclosed by the invention breaks through the technical bottleneck of the traditional fast recovery diodes.

Owner:SUZHOU QILAN POWER ELECTRONICS

Method for diffusing high sheet resistance of solar cells

ActiveCN102097524AReduce errorsImprove life expectancyFinal product manufactureSemiconductor devicesSurface concentrationSolar cell

The invention relates to a method for diffusing high sheet resistance of solar cells. The method is characterized by texturing the surface of a solar crystal silicon wafer, sending the silicon wafer to a diffusion furnace for high sheet resistance diffusion and then carrying out subsequent solar cell processes. The method has the following advantages: (1) superior sheet resistance uniformity can be still maintained when high sheet resistance is diffused; (2) through introducing TCA or TCE during pre-oxidation, oxidation can be sped up, the substrate fault number can be reduced and the minority carrier lifetime of the substrate silicon can be prolonged; (3) dead layers can be well avoided through oxide layers; and (4) surface concentration and junction depth topography of diffusion can be well controlled through low-temperature pre-deposition and high-temperature junction propelling forming.

Owner:TRINA SOLAR CO LTD

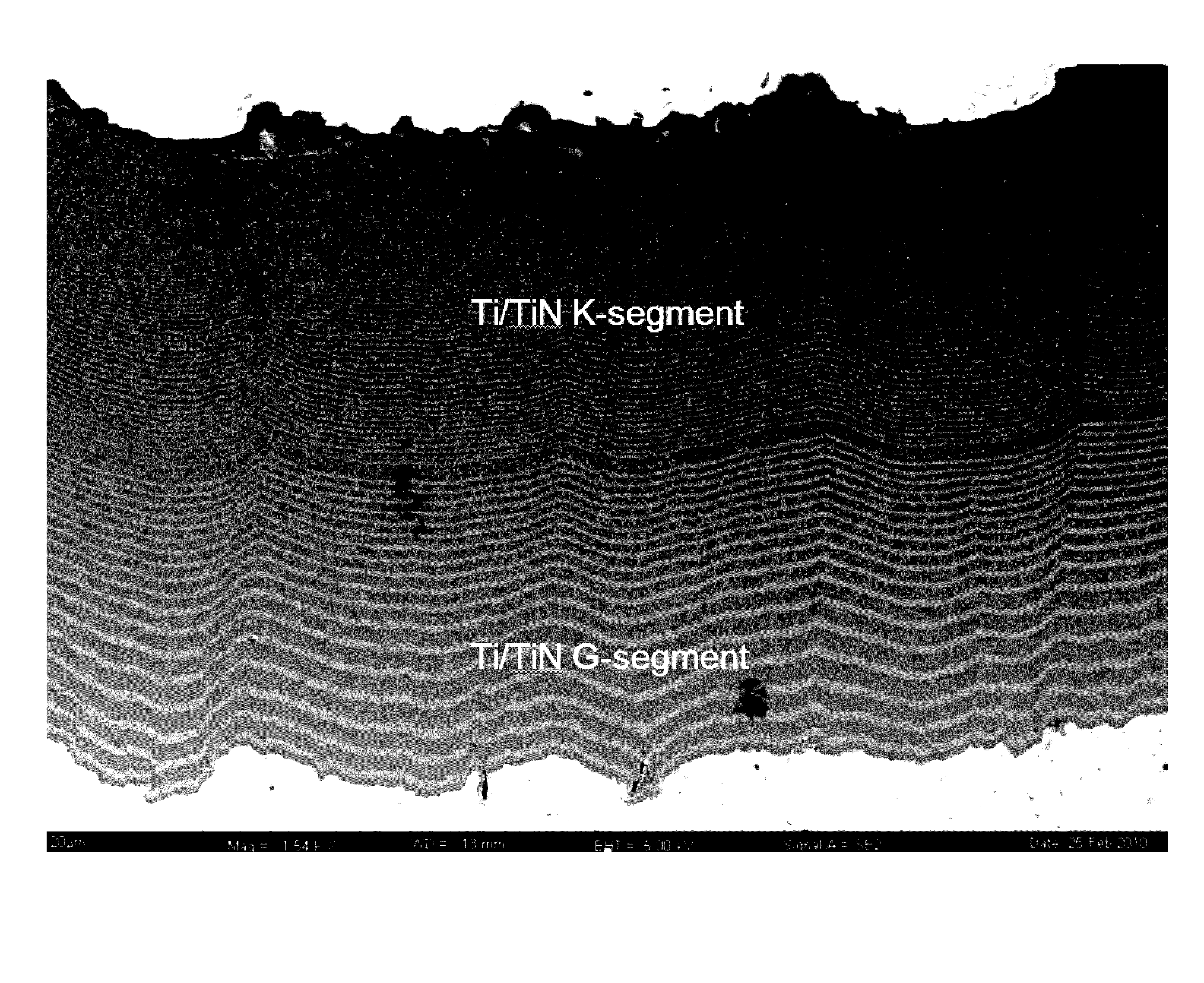

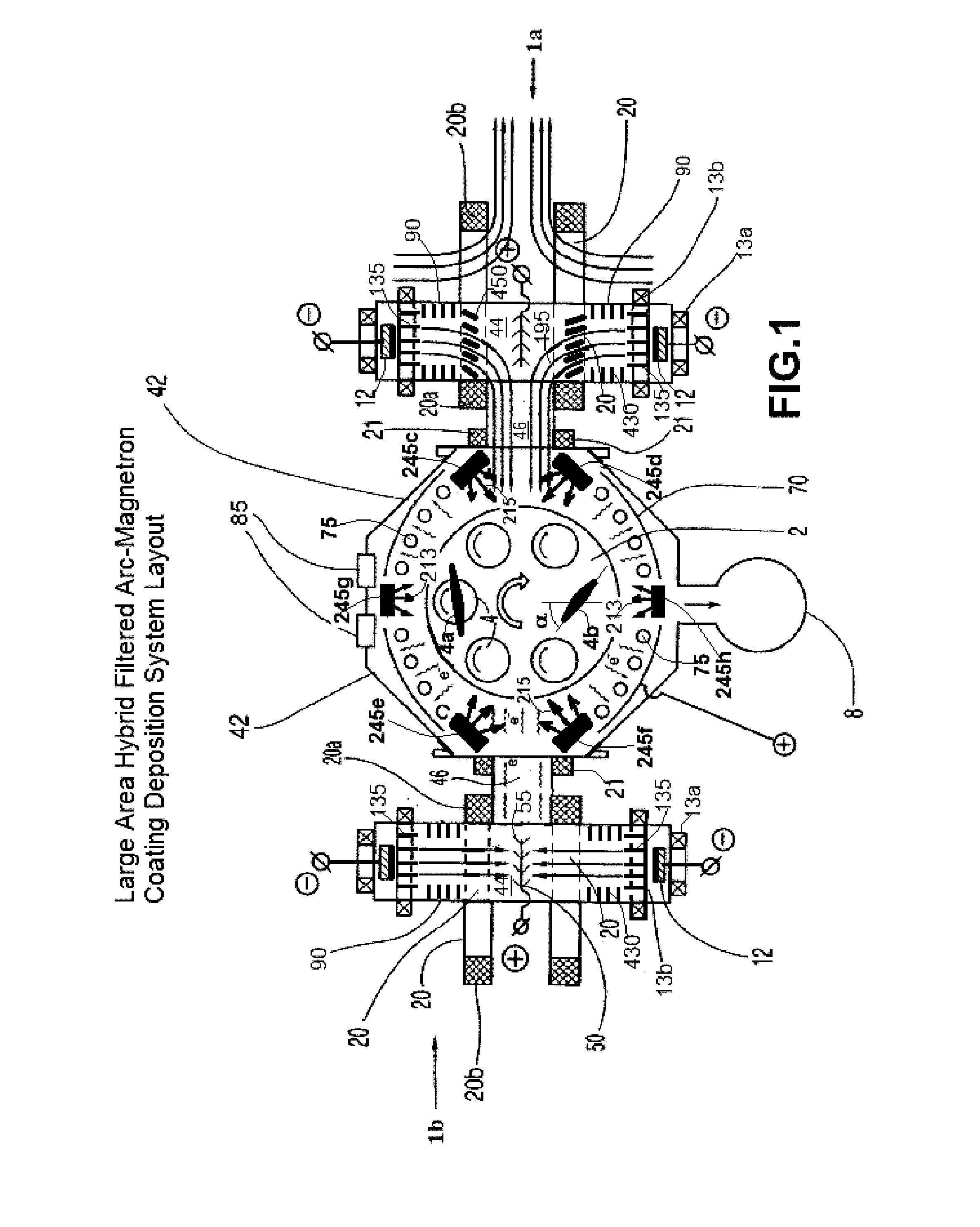

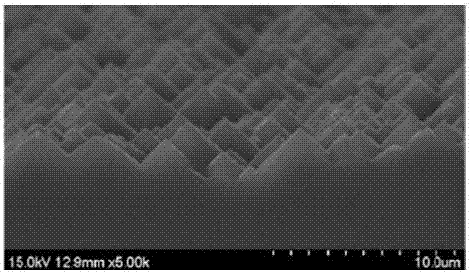

Erosion And Corrosion Resistant Protective Coatings For Turbomachinery

InactiveUS20170030204A1Increase flexibilityImprove reflectivityEngine manufactureBlade accessoriesCeramic coatingPlasma flow

An erosion and corrosion resistant protective coating for turbomachinery application includes at least one ceramic or metal-ceramic coating segment deposited on surface of a conductive metal substrate subjected to a pre-deposition treatment by at least blasting to provide the surface with texture. The erosion and corrosion resistant coating has a plurality of dome-like structures with dome width between in range from about 0.01 μm to about 30 μm. The at least one coating segment is formed by condensation of ion bombardment from a metal-gaseous plasma flow, wherein, at least during deposition of first micron of the coating segment, deposition rate of metal ions is at least 3 μm / hr and kinetic energy of deposited metal ions exceeds 5 eV.

Owner:NANO PROD ENG

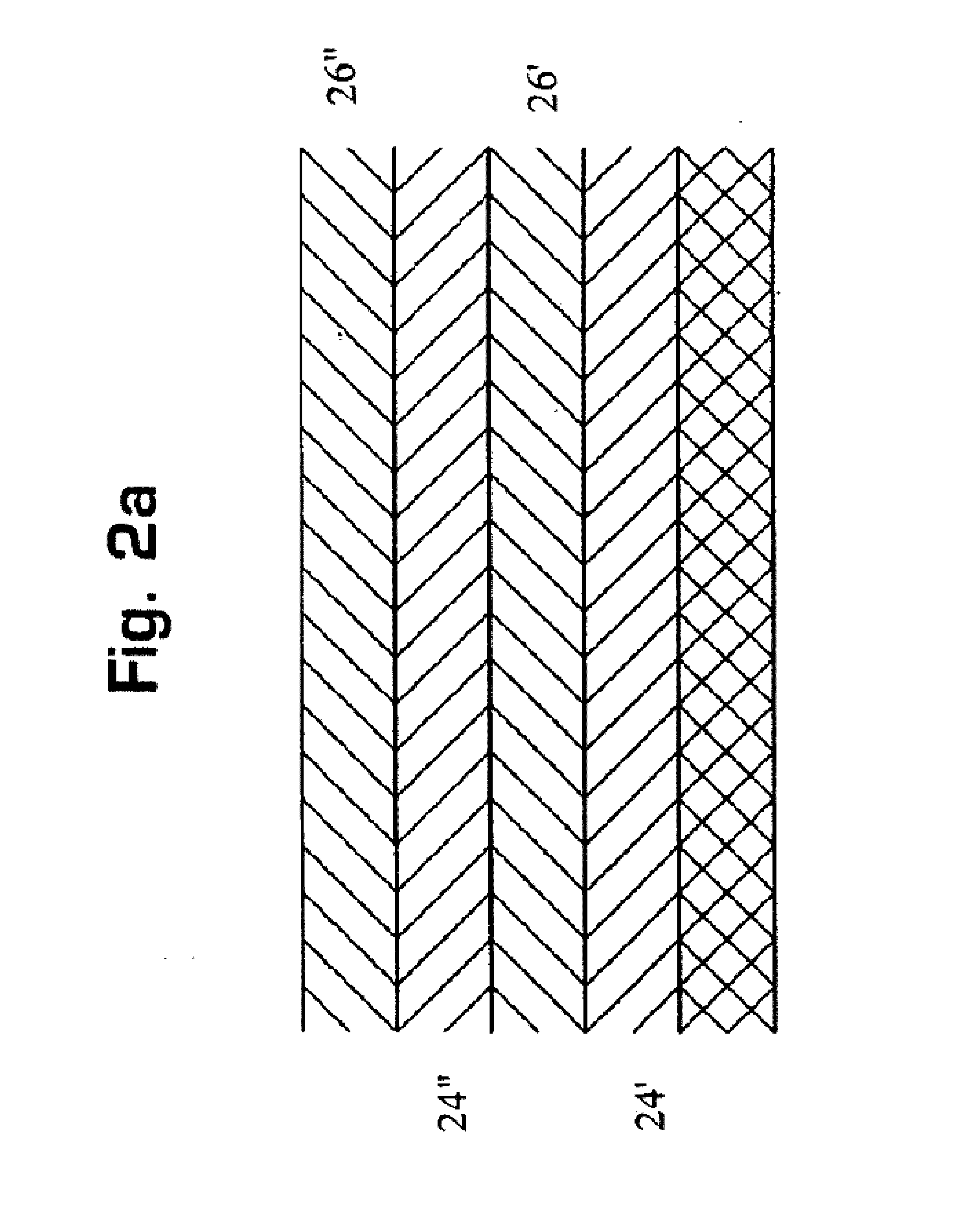

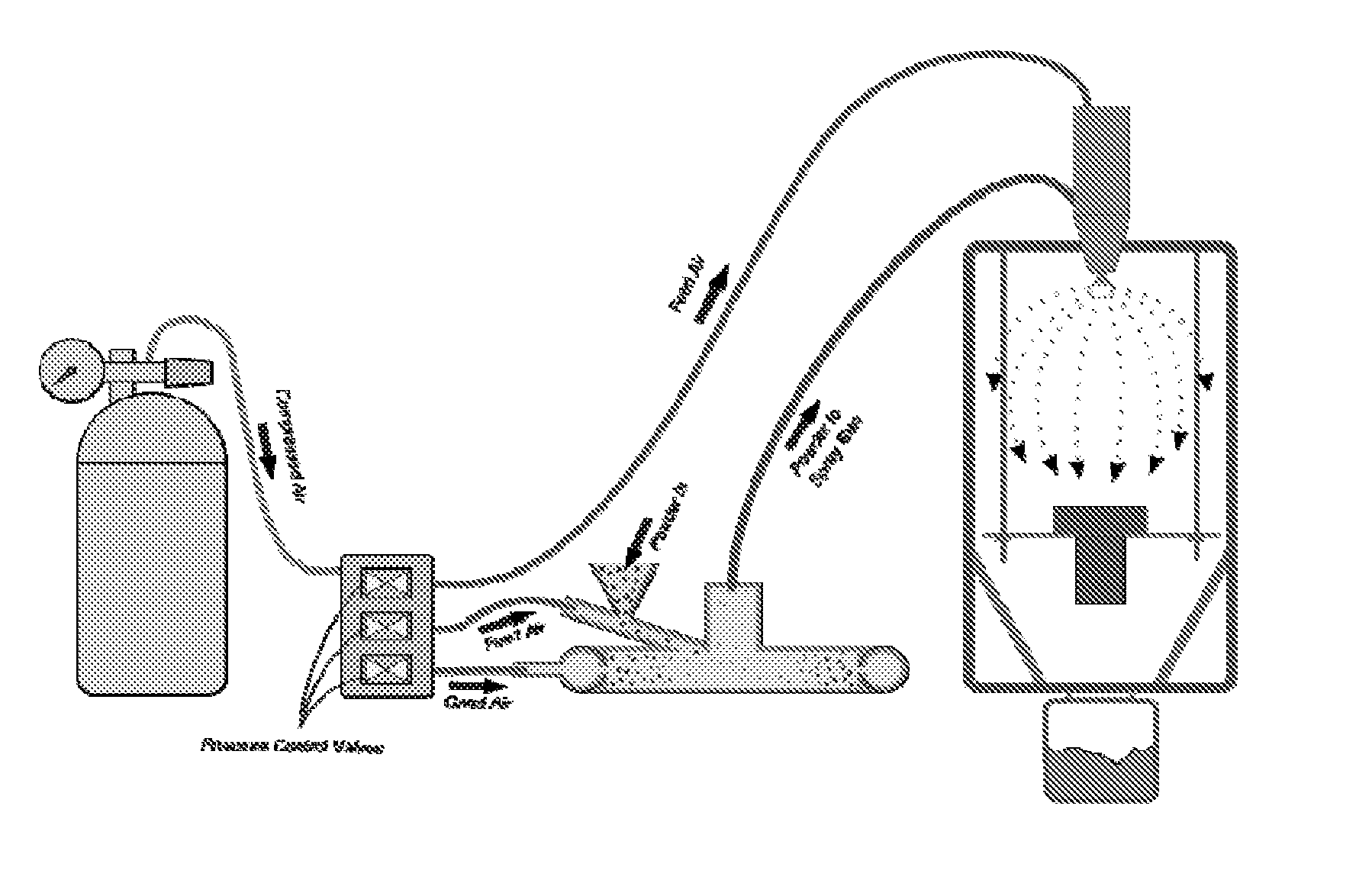

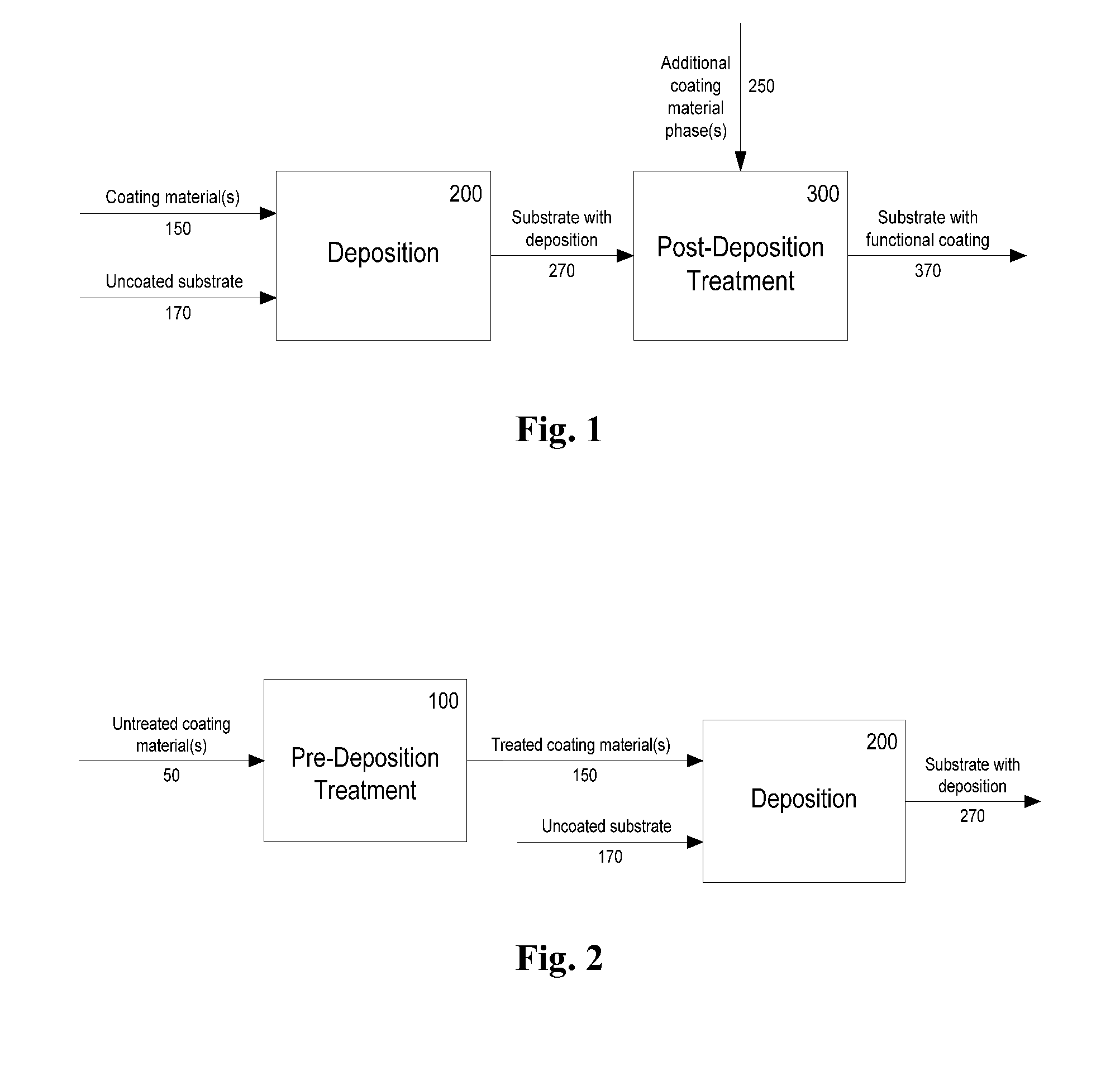

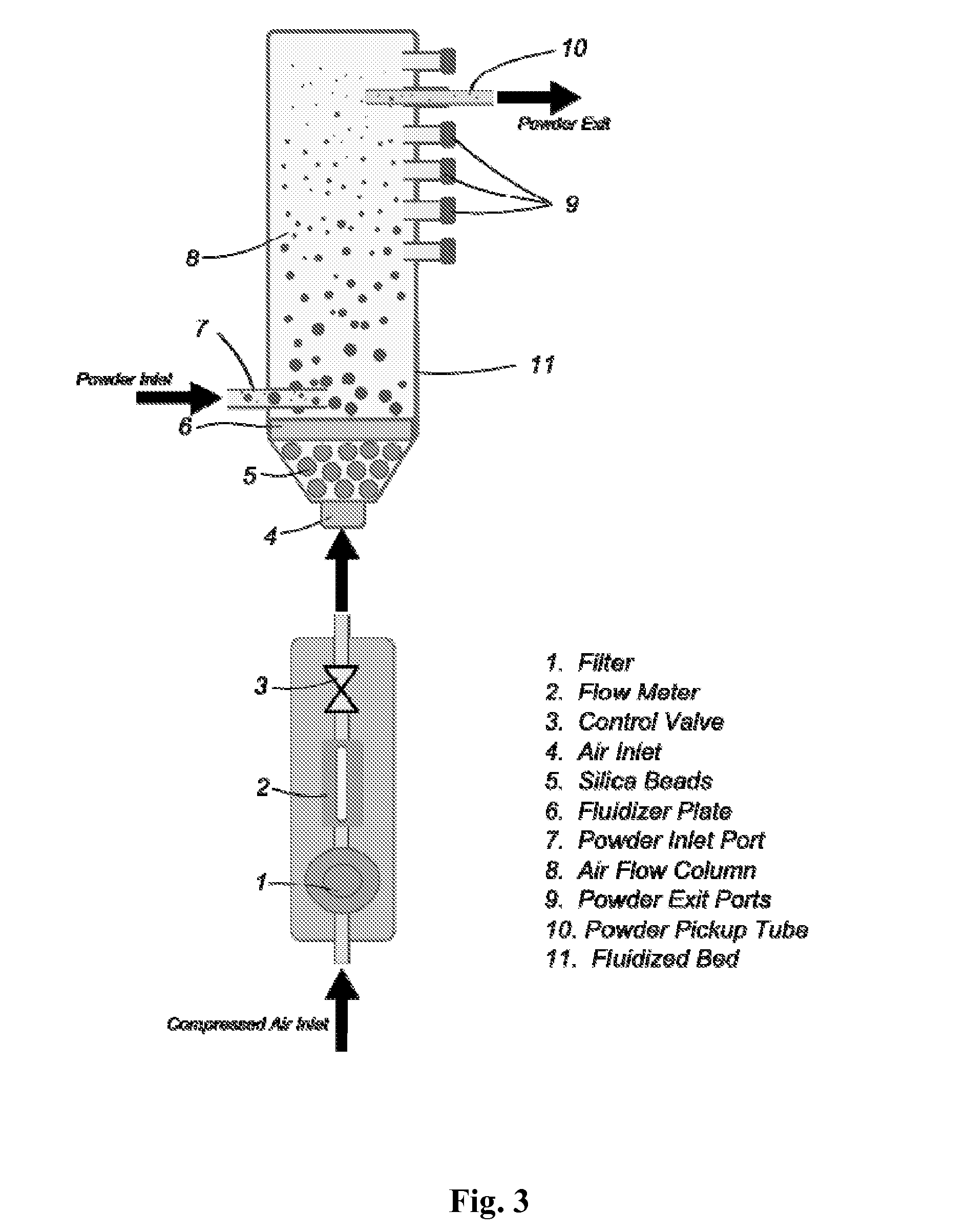

Methods and Apparatus for Making Coatings Using Electrostatic Spray

Methods for creating coatings composed of a single material or a composite of multiple materials, beginning with ESC to deposit the base layer and then using other methods for the binding step beyond CVI. Also, for certain materials and applications, some pre-processing or pre-treatment of the coating materials is necessary prior to deposition in order to achieve a satisfactory coating. This application discloses methods for pre-deposition treatment of materials prior to ESC deposition. It also discloses methods for post-processing that provide additional functionality or performance characteristics of the coating. Finally, this application discloses certain apparatus and equipment for accomplishing the methods described herein.

Owner:P&S GLOBAL HLDG LLC +1

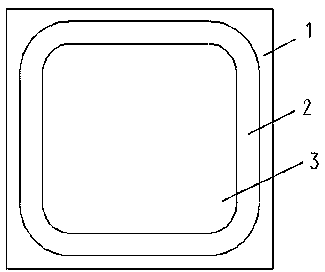

Texturing method of diamond wire slice polycrystalline black silicon

ActiveCN106935669AEnsure uniformityGuarantee stabilityAfter-treatment detailsFinal product manufactureNanostructurePre deposition

The invention discloses a texturing method of diamond wire slice polycrystalline black silicon. The texturing method comprises the following steps in turn: a silicon chip is arranged in a solution containing nitric acid and hydrofluoric acid to be preprocessed; the preprocessed silicon chip is arranged in a solution containing metal salt to perform pre-deposition of oxidized metal nanoparticles; the silicon chip after pre-deposition is arranged in a solution containing hydrofluoric acid and an oxidizing agent to perform deposition of the oxidized metal nanoparticles; the silicon chip after deposition is arranged in a solution containing hydrofluoric acid, the oxidizing agent and metal salt ions to perform longitudinal and transverse broaching corrosion; the silicon chip after broaching is arranged in an acid solution to remove the metal ions; and the silicon chip of which the metal ions are removed is arranged in an alkaline solution containing a texturing additive to perform modification of the nanostructure so as to form the final textured surface. The non-uniformity and the chromatic aberration of the appearance after texturing can be effectively avoided.

Owner:江苏福吉食品有限公司

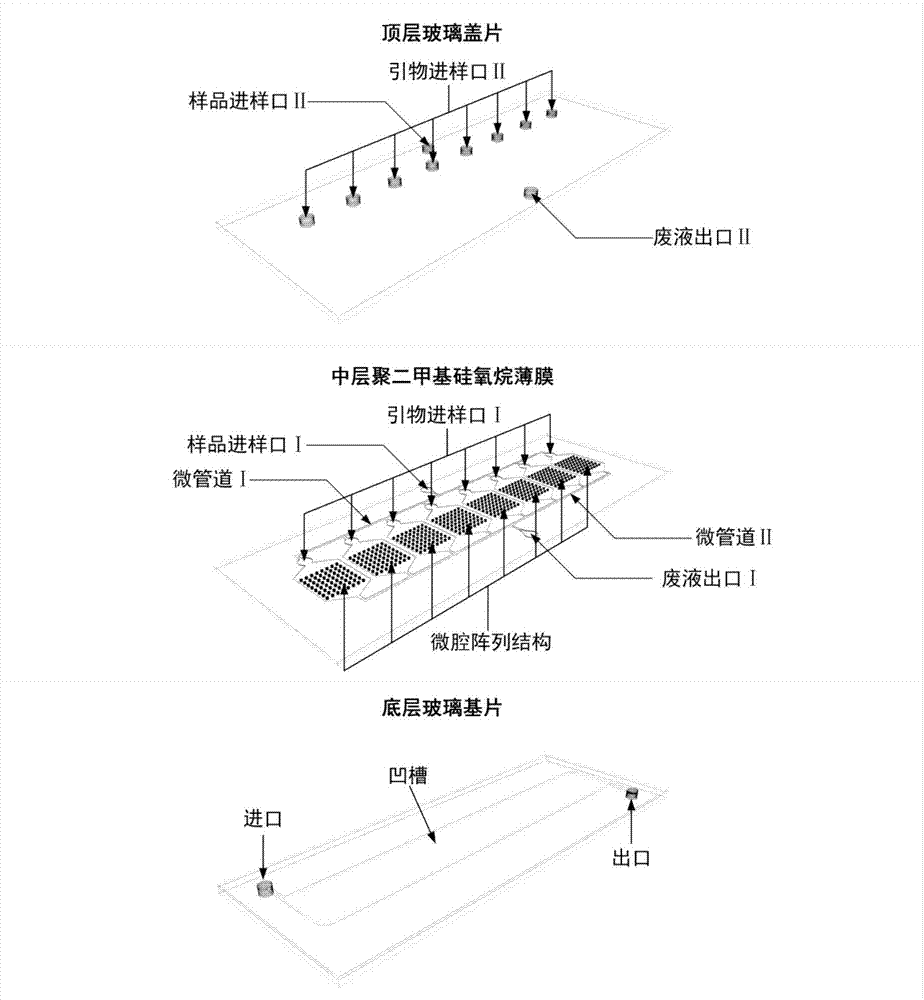

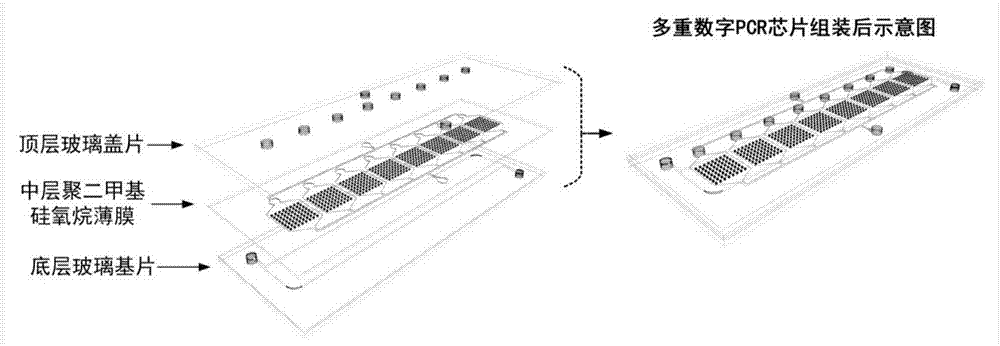

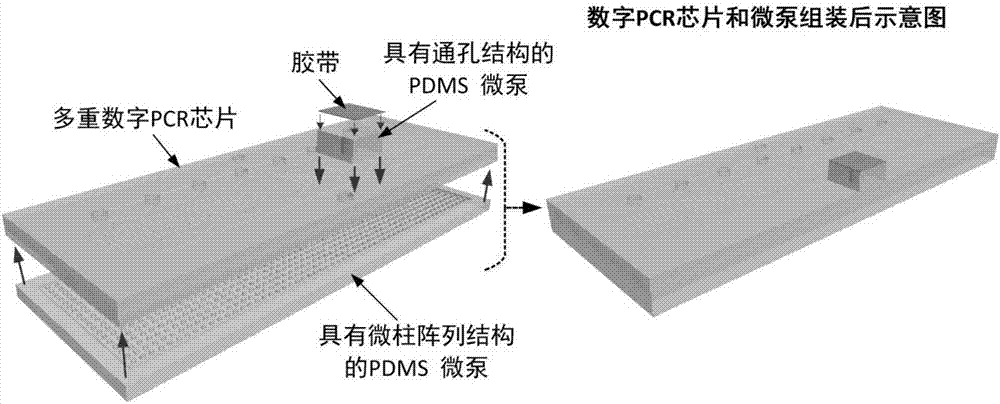

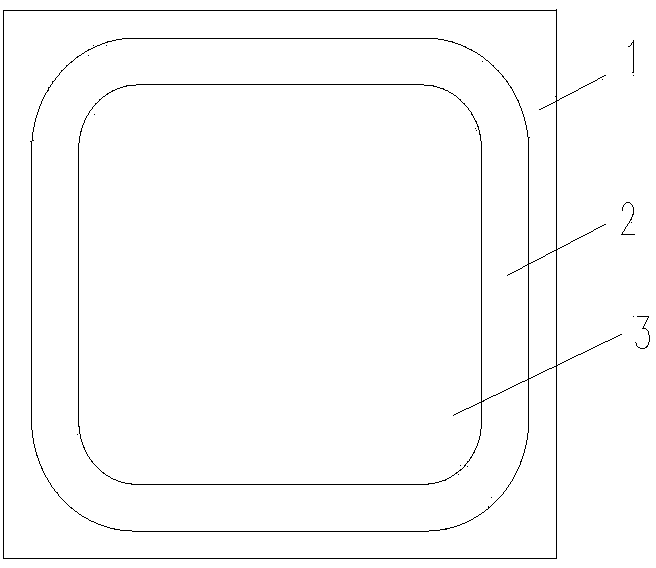

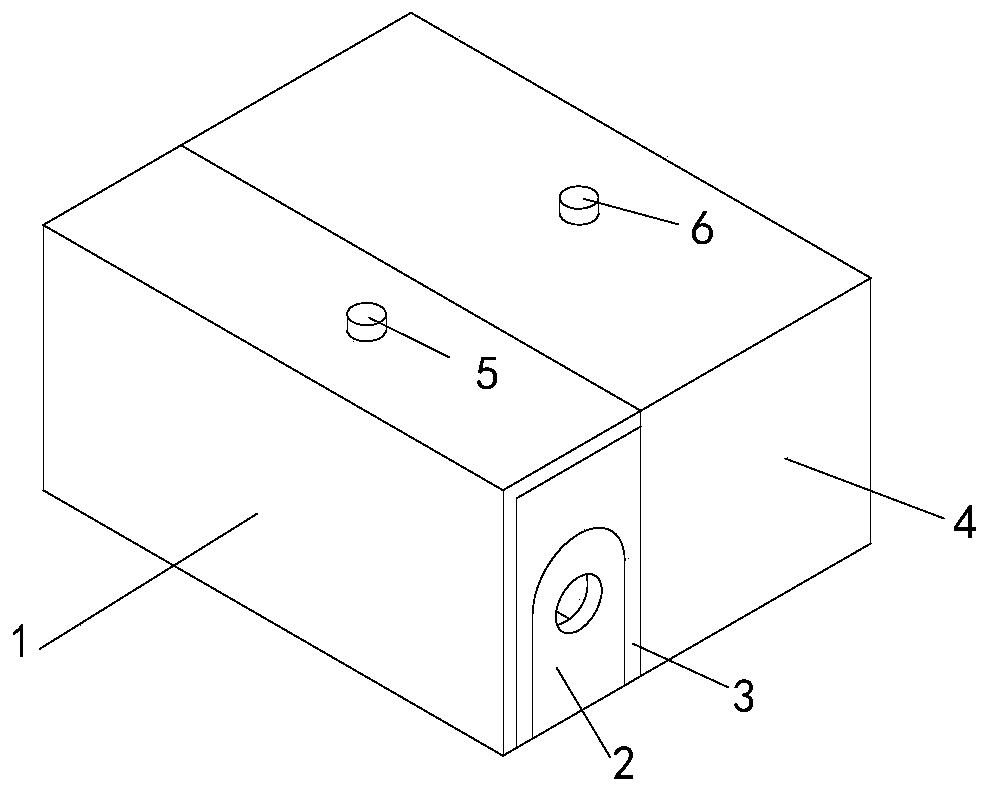

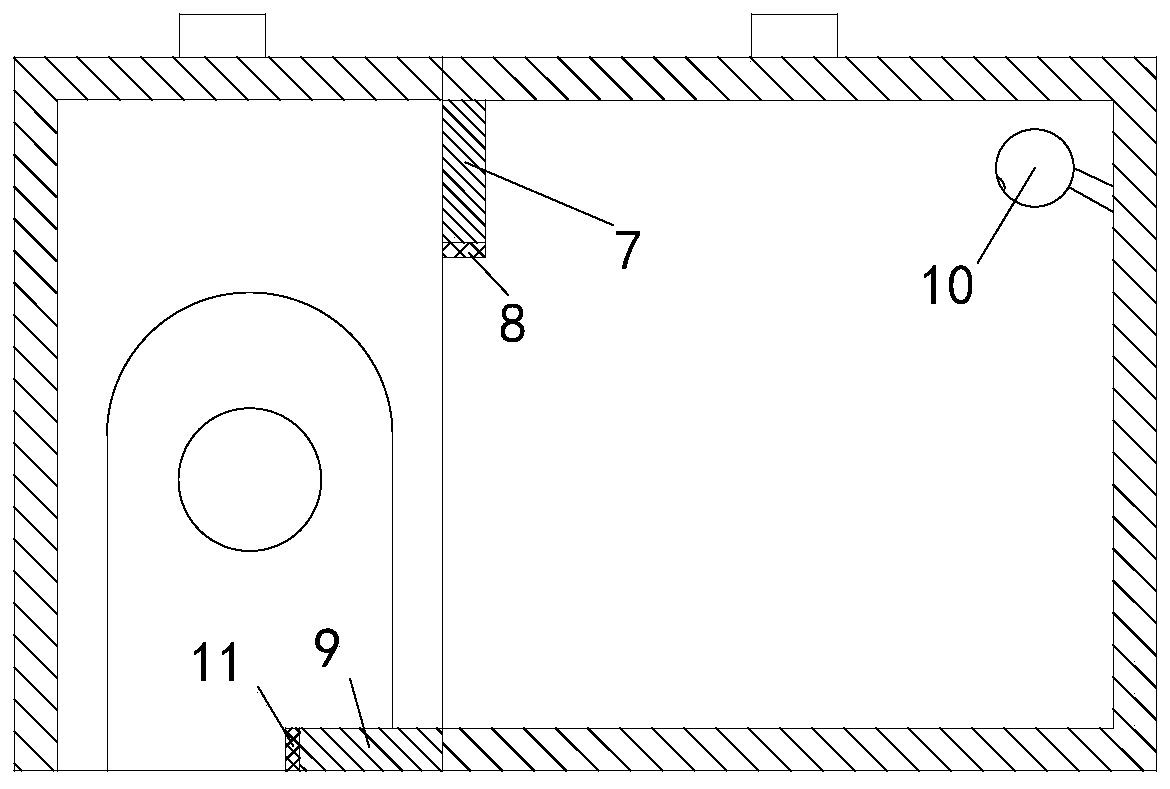

Multiple digital PCR chip and use method thereof

ActiveCN107262170ASimple and fast operationReduce complexityLaboratory glasswaresFluorescence/phosphorescencePcr chipEngineering

The invention relates to a multiple digital PCR chip and a use method thereof. The chip does not need to be driven by a precise micro-pump and be controlled by a complex micro-valve and does not need a complex macro-micro interface. The chip realizes simple, fast, low cost and large-scale autodecomposition and quantitative uniform distribution of samples. Compared with the existing commercial PCR chip, the chip greatly reduces the complexity and operating cost of the digital PCR system, simplifies the experimental operation and is free of professional training of an operator. The chip realizes the independence of each PCR reaction unit through microcavity arrays, is free of a surfactant and prevents the influence caused by an additive on the reaction system. Through integration of the isolated microcavity array zones and pre-deposition of primers corresponding to different specific target molecules in the microcavities in different zones, the chip can realize multiple detection through one step. The chip has the advantages of operation simpleness, low cost and strong multiple detection capacity and can promote development and wide application of the digital PCR technology.

Owner:CHONGQING UNIV

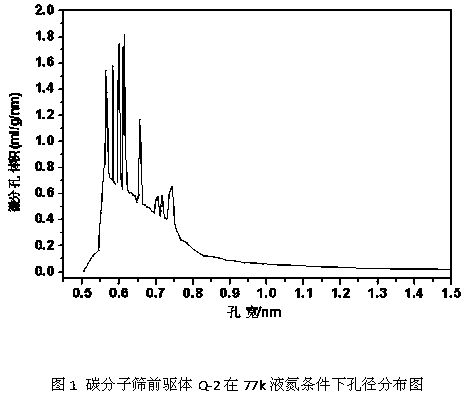

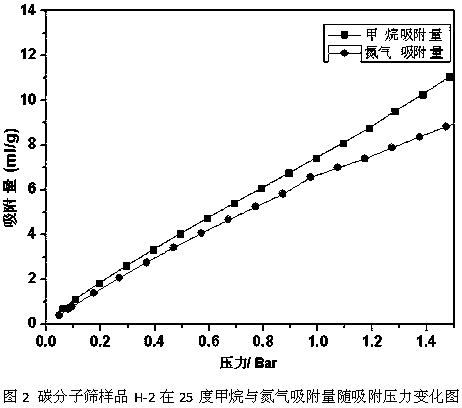

Preparation method of phenol-formaldehyde resin-based carbon molecular sieve for adsorbing and separating methane and nitrogen gas

ActiveCN109179369AReduce lossesReduce the amount of adsorptionNitrogen purification/separationCarbon preparation/purificationCarbonizationNitrogen gas

The invention discloses a preparation method of a phenol-formaldehyde resin-based carbon molecular sieve for adsorbing and separating methane and nitrogen gas. The preparation method mainly includes the following steps: (1) mixing phenol-formaldehyde resin waste, coal tar, water and a pore-forming agent in a certain proportion evenly, carrying out strip extrusion moulding and drying at low temperature; (2) carbonizing at high temperature under the protection of nitrogen gas to prepare a pre-deposition matrix with suitable pore size; and (3) directly introducing a methane depositing agent and depositing without cooling of the matrix, and adjusting the pore size of the matrix to prepare the carbon molecular sieve sample. The raw materials have low cost, carbonization and deposition are integrated in the preparation process, the energy loss is reduced, more energy is saved, the influence of heat on the pore size change of the matrix during carbonization cooling and deposition heating is reduced, and the pore size is relatively stable; the pore size of the matrix prepared by the method is small, the deposition time is reduced, and the sample after deposition has the adsorption capacityof nitrogen gas of 6.5-7.5 ml / g and the adsorption capacity of methane of 7-10 ml / g at 25 DEG C / 1 atmospheric pressure.

Owner:ZHENGZHOU MINERALS COMPOSITIVE UTILIZATION RES INST CHINESE GEOLOGICAL ACAD

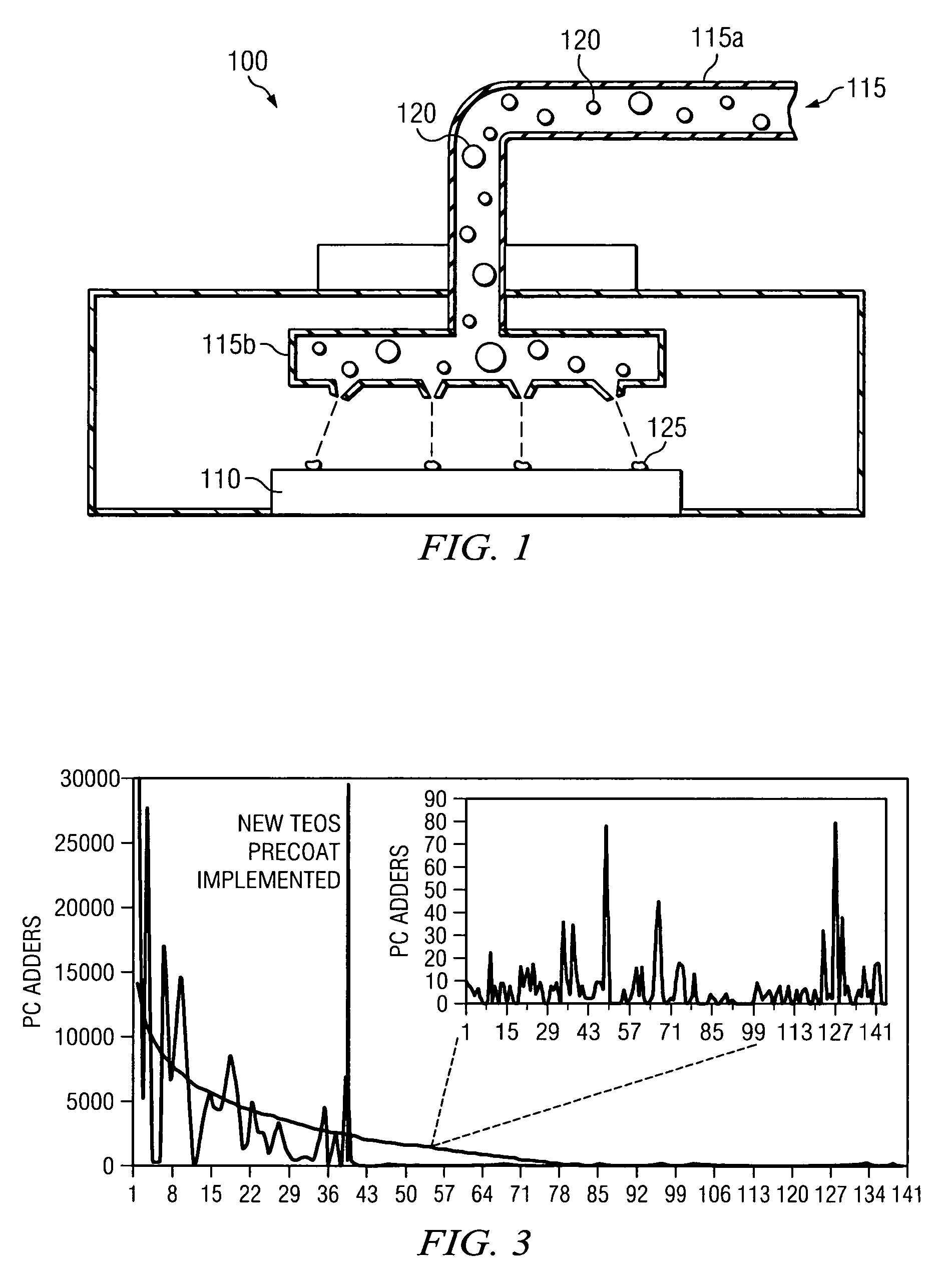

Method for conditioning a microelectronics device deposition chamber

ActiveUS7241690B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingEngineeringHigh pressure

The present invention provides, in one aspect, a method of conditioning a deposition chamber 100. An undercoat is placed on the walls of a deposition chamber 100 and a pre-deposition coat is deposited over the undercoat with a plasma gas mixture conducted at a high pressure and with high gas flow.

Owner:TEXAS INSTR INC

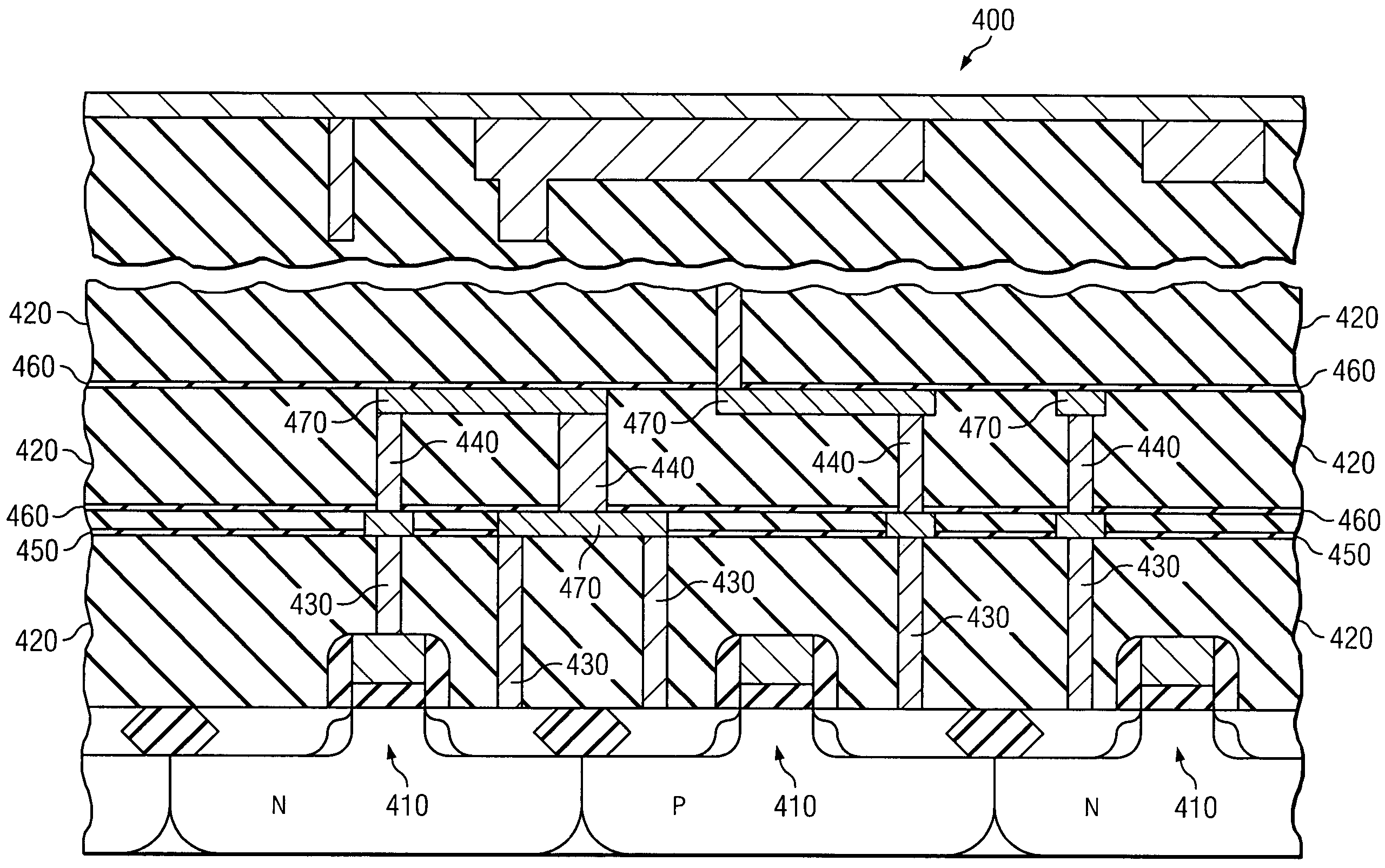

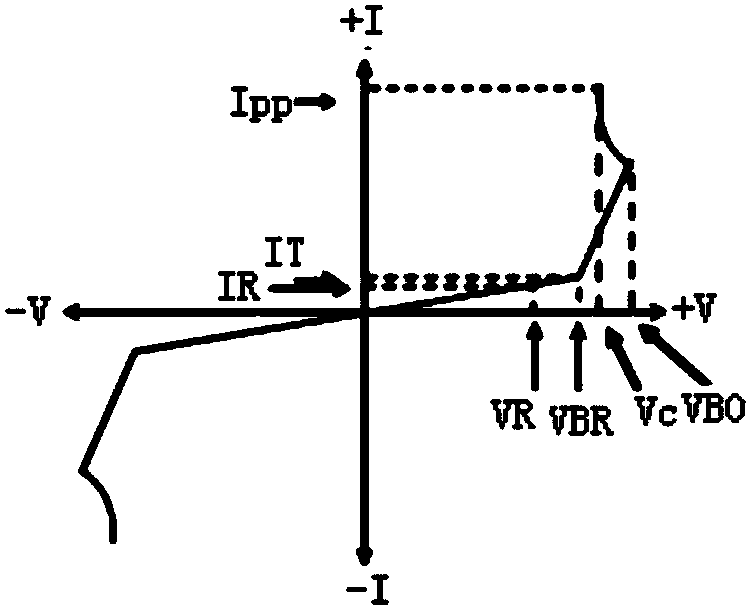

Manufacturing method of transient voltage suppressor chip having tunneling effect

InactiveCN103779205AVc value decreasesRealization of tunnel effectSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingElectrophoresis

The invention discloses a manufacturing method of a transient voltage suppressor chip having the tunneling effect. The method comprises the following steps: 1) treatment before oxidation; 2) oxidation; 3) photoetching; 4) single-sided oxide layer removal; 5) treatment before diffusion; 6) phosphorus diffusion pre-deposition; 7) treatment after pre-deposition; 8) phosphorus diffusion; 9) treatment after diffusion; 10) mesa etching; 11) electrophoresis; 12) sintering; 13) oxide layer removal; 14) nickel plating and gold plating; 15) and chip cutting. The manufacturing method disclosed in the invention can be used to realize the tunneling effect of the chip to reduce the chip Vc value, wherein the Ipp capability of the chip is greater than a same conventional chip.

Owner:上海瞬雷电子科技有限公司

Method for preparing low-carbon olefins by using oxygen-containing compounds

ActiveCN104672044AHigh yieldOptimize allocationHydrocarbon from oxygen organic compoundsEthylene productionNaphthaKerosene

The invention relates to a method for improving the yield of low-carbon olefins in a process for preparing low-carbon olefins by using oxygen-containing compounds. More specifically, the invention provides a method for preparing low-carbon olefins by using oxygen-containing compounds, which is implemented by taking a multistage dense phase fluidized bed containing k (k is greater than or equal to 1) secondary carbon pre-deposition areas and n secondary reaction areas and taking a multistage dense phase fluidized bed regenerator containing m (m is greater than or equal to 2) secondary regeneration areas as a main body apparatus, through implementing a process of recycling hydrocarbons with C4 or above obtained by a separating section or adding naphtha, gasoline, gas condensate, light diesel oil, hydrogenation tail oil or kerosene into a reaction area. The method mainly solves the problem that in the prior art, the uniformity of carbon deposition amount and carbon content of a catalyst is difficult to control, so that the yield of low-carbon olefins is low.

Owner:中科催化新技术(大连)股份有限公司

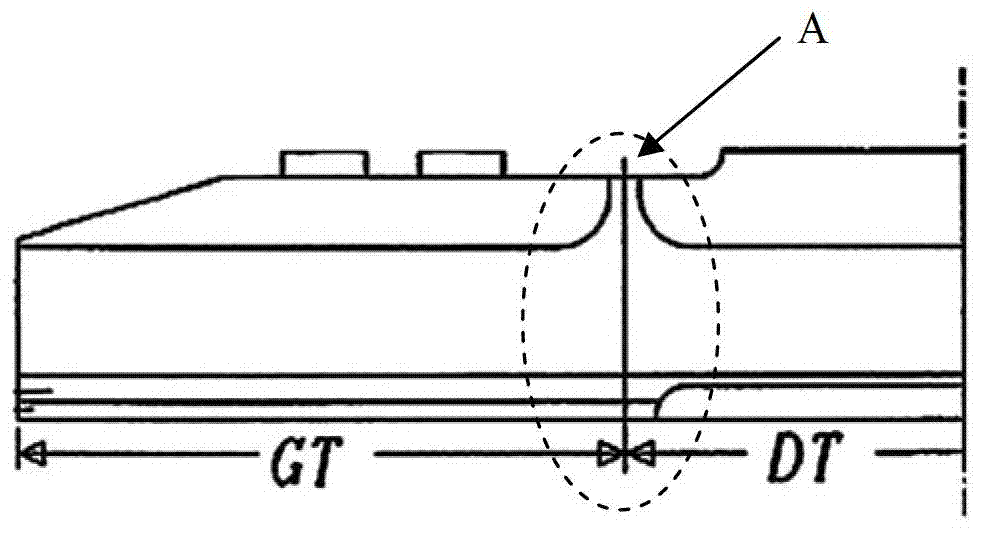

Manufacturing method of reverse-conducting integrated gate-commutated thyristor

ActiveCN102969245AIncrease the punch-through voltageDoes not affect vertical structureThyristorSemiconductor/solid-state device manufacturingImpurity dopingIntegrated gate-commutated thyristor

The invention discloses a manufacturing method of a reverse-conducting integrated gate-commutated thyristor. The method comprises the following steps: S100: lightly doping one side of an original N- substrate with a layer of N' impurity; S101, fabricating a P-type base region of a GCT (Gate Commuted Tryristor) and a P-type base region of an FRD (Fast Recovery Diode); S102, performing N' impurity doping on the other side of the N- substrate; S103, performing pre-deposition on a GCT cathode and an FRD cathode; S104, etching isolation trenches on the upper surface of an isolation region and a gate region of the GCT; S105, performing N+ propelling and passivation on the GCT cathode and the FRD cathode; S106, performing P+ doping on a GCT anode; and S107, fabricating electrodes. According to the invention, using the compensating effect of the impurity, under the condition that the P-type doping distribution of the isolation region is not changed, the effective width of the isolation region is increased, and the shortcomings existing in the prior art that the diffusion control precision is not high, and the process is complicated and not suitable for high pressure devices are overcome.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

Quick diffusion annealing method

InactiveCN106653598AImprove conversion efficiencyIncrease surface concentrationFinal product manufactureSemiconductor/solid-state device manufacturingP–n junctionPre deposition

The invention discloses a quick diffusion annealing method. A primary source introduction and pre-deposition process is carried out at below 800 DEG C. After deposition, aerobic heating advance is carried out, and the temperature can rise up to 840-880 DEG C. A PN node advanced at the moment is deep. Then, an aerobic cooling process is carried out, and the temperature drops to 810-850 DEG C. Secondary source introduction is carried out, which is a key step for quick annealing. After that, the furnace door is half-opened immediately, a large amount of nitrogen is introduced, and quick cooling and annealing are carried out. The lattice is repaired to a certain degree, but the phosphorus source still needs certain advance time. Thus, the furnace door is closed slowly, and the temperature goes back to a constant state. The beneficial effects of the method are as follows: through secondary source introduction, the surface concentration is increased, and the filling factor is improved; through lattice repair, thermal damage is reduced, the open-circuit voltage and short-circuit current are improved, and the conversion efficiency of cells is improved; and through quick cooling, the total process time is reduced, the process efficiency is improved, and the production capacity is increased.

Owner:HENGDIAN GRP DMEGC MAGNETICS CO LTD

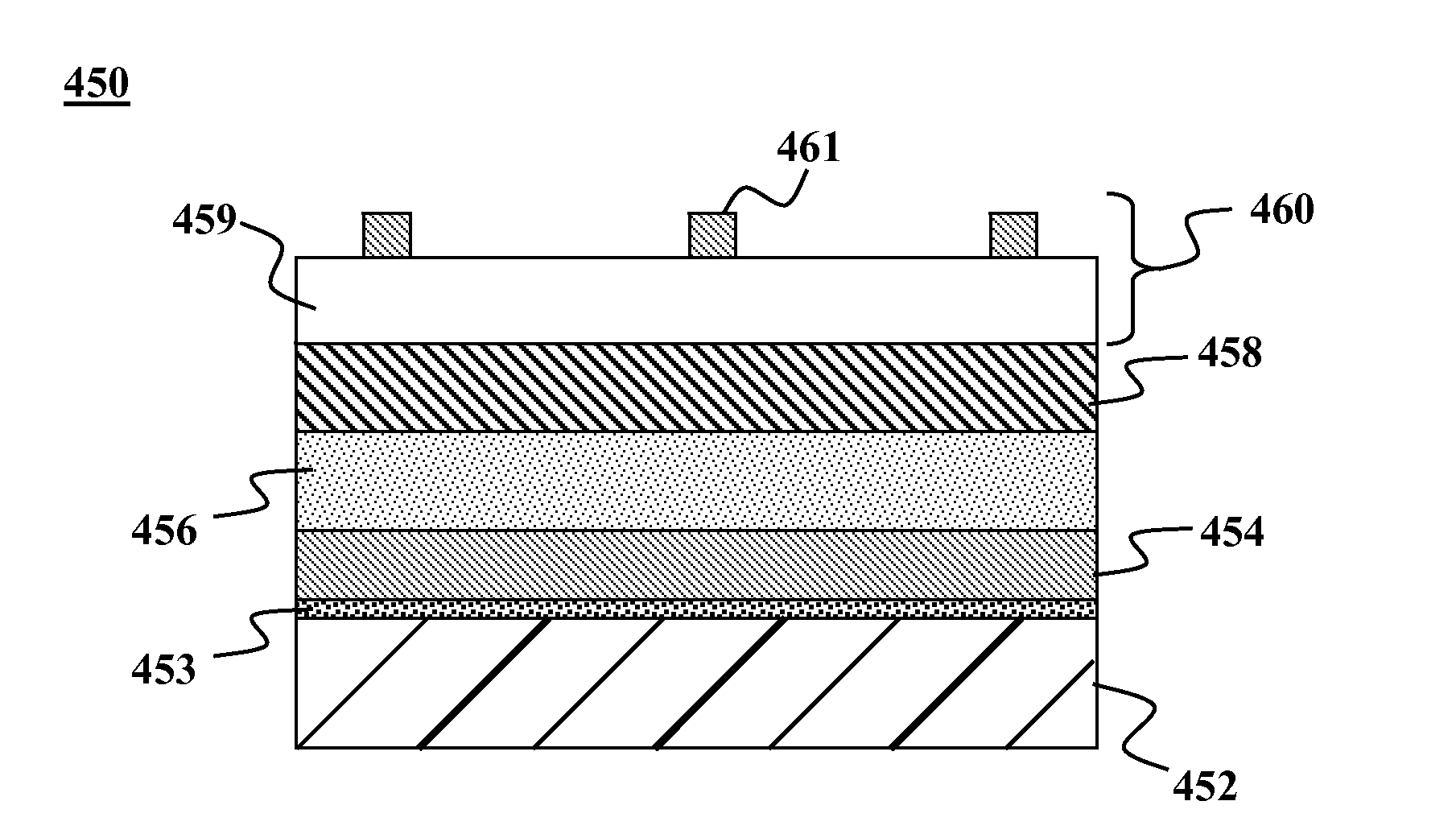

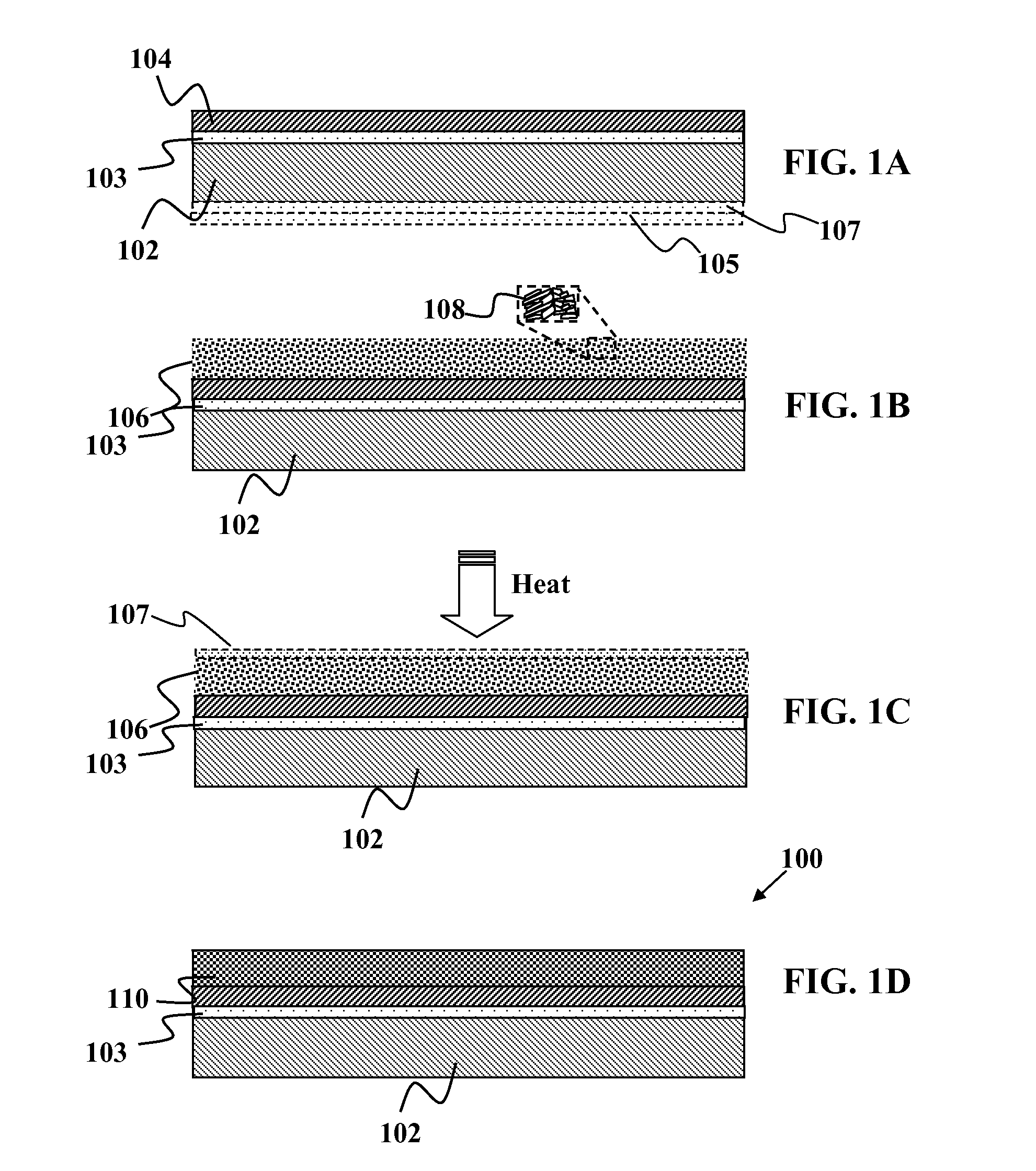

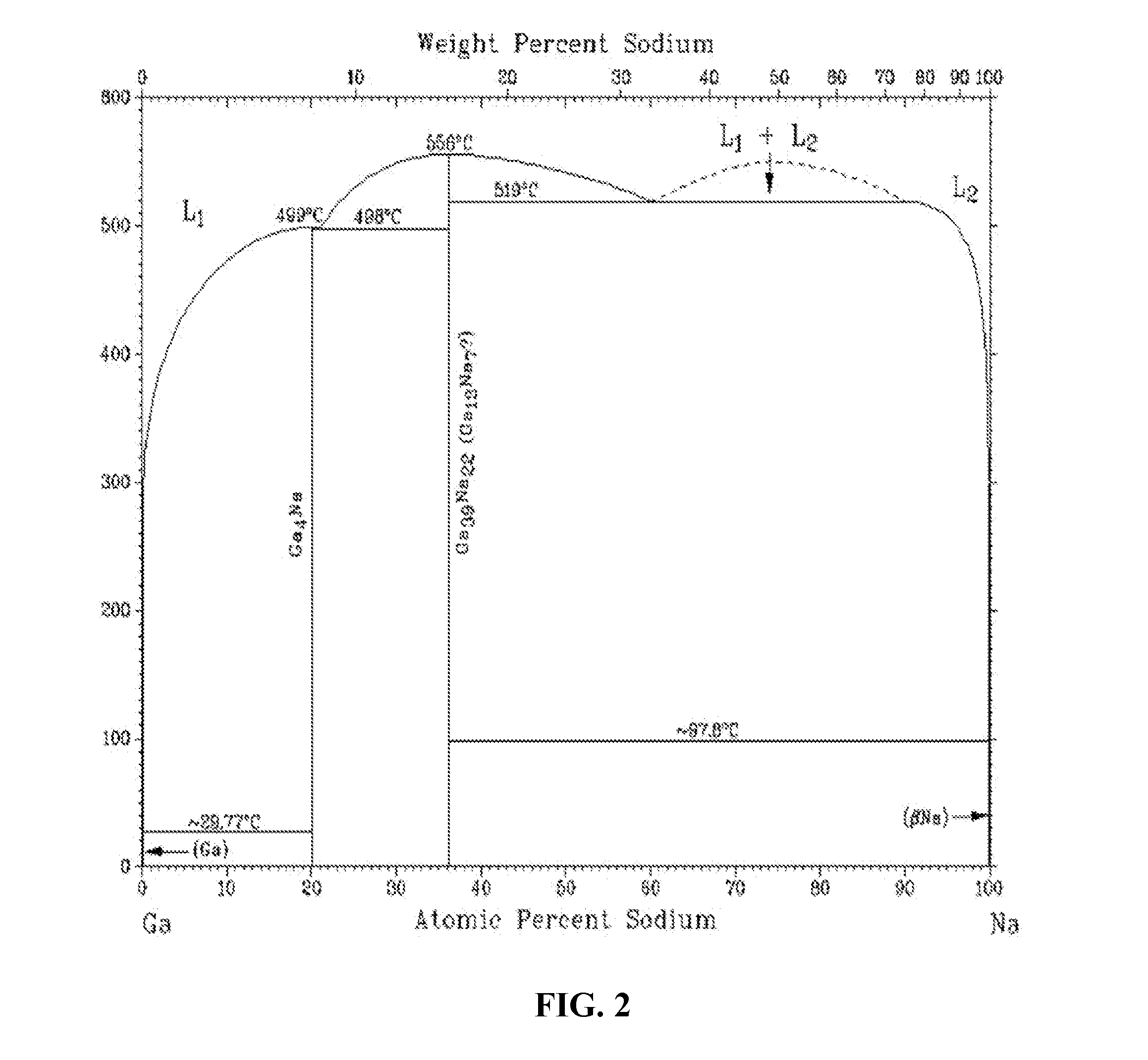

Thin-film devices formed from solid particles

InactiveUS20120171847A1Efficient and simplified creationPrevent leaching and phase separationSemiconductor/solid-state device manufacturingInksDevice formRoom temperature

Methods and devices are provided for forming thin-films from solid group IIIA-based particles. In one embodiment of the present invention, a method is described comprising of providing a first material comprising an alloy of a) a group IIIA-based material and b) at least one other material. The material may be included in an amount sufficient so that no liquid phase of the alloy is present within the first material in a temperature range between room temperature and a deposition or pre-deposition temperature higher than room temperature, wherein the group IIIA-based material is otherwise liquid in that temperature range. The other material may be a group IA material. A precursor material may be formulated comprising a) particles of the first material and b) particles containing at least one element from the group consisting of: group IB, IIIA, VIA element, alloys containing any of the foregoing elements, or combinations thereof.

Owner:PURDUE RES FOUND INC +1

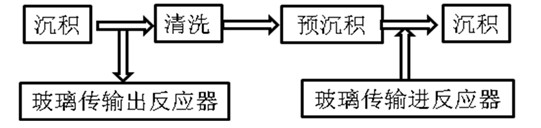

Preparation method for improving performance of industrial silicon thin-film cell component

InactiveCN102637780AImprove photoelectric conversion efficiencyReduce fluorine and sulfurFinal product manufactureSemiconductor devicesSilanesSilicon thin film

Owner:河北京碳能源有限公司

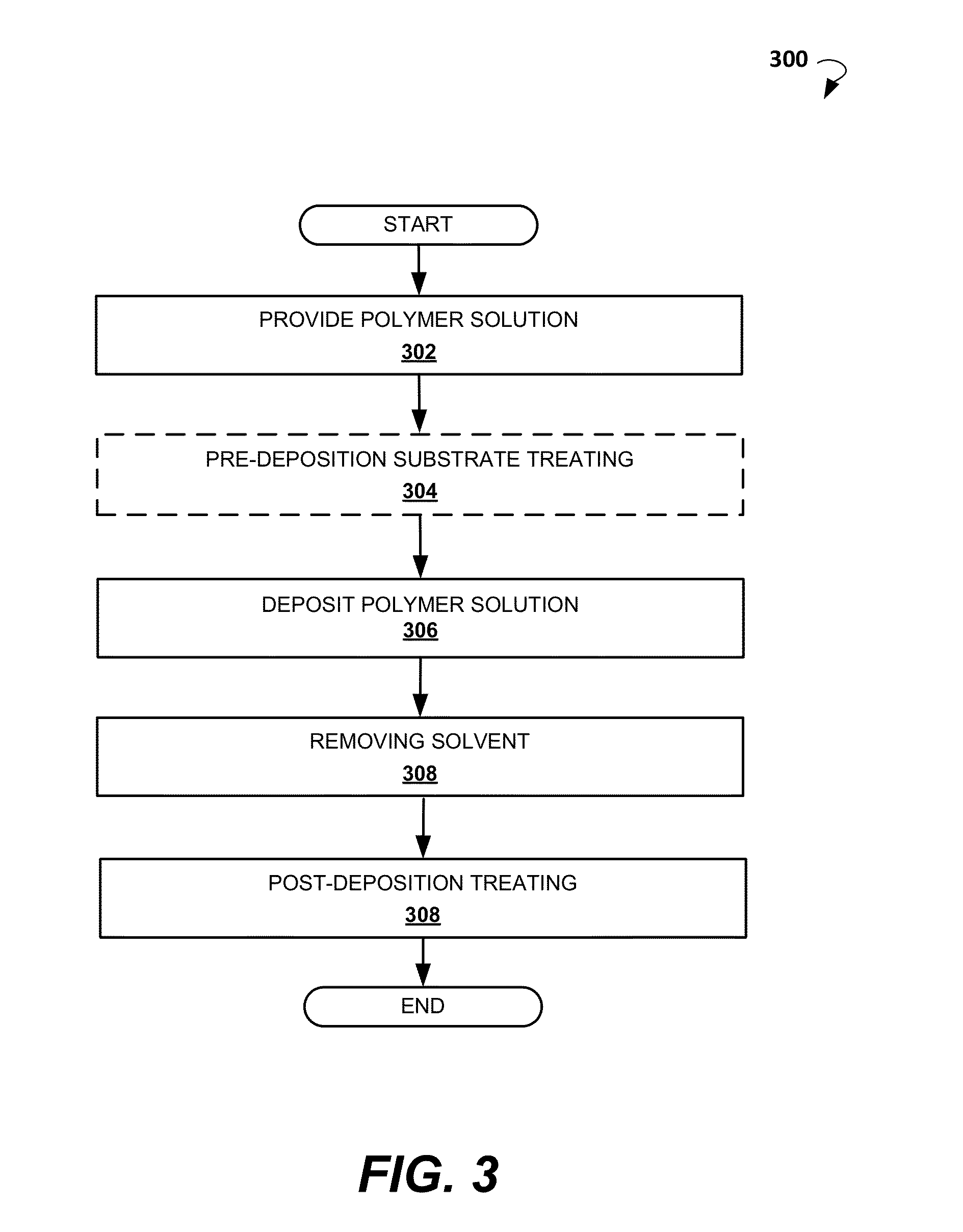

Depositing polymer solutions to form optical devices

ActiveUS20140322452A1Hindered phenolLiquid crystal compositionsMechanical vibrations separationSolubilityPolymer science

Provided are methods of depositing polymer solutions on substrates to form various optical elements. A polymer solution may include about 0.1%-0% by weight of a specific polymer having rigid rod-like molecules. The molecules may include various cores, spacers, and sides groups to ensure their solubility, viscosity, and cross-linking ability. The deposition techniques may include slot die, spray, molding, roll coating, and so forth. Pre-deposition techniques may be used to improve wettability and adhesion of substrates. Post-deposition techniques may include ultraviolet cross-linking, specific drying techniques, evaporation of solvent, treating with salt solutions, and shaping. The disclosed polymers and deposition processes may yield optical elements with high refractive index values, such as greater than 1.6. These optical elements may be used as +A plates, −C plates, or biaxial polymers and used as retarders in LCD active panels or as light collimators and light guides.

Owner:LIGHT POLYMERS HLDG

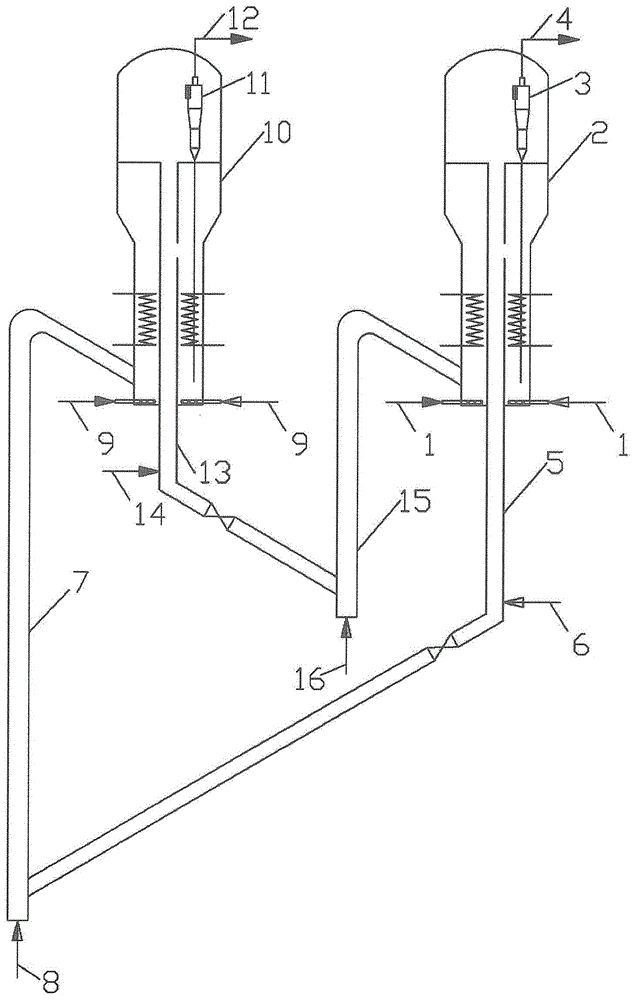

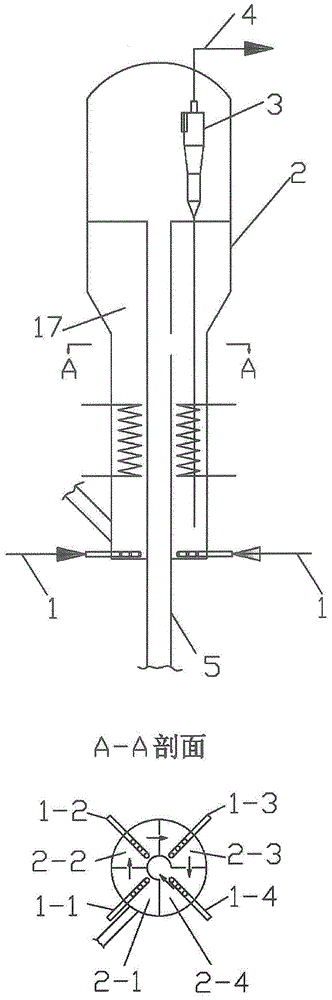

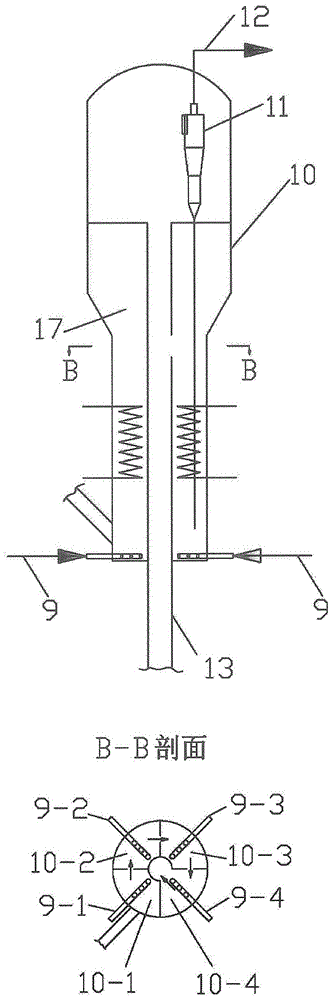

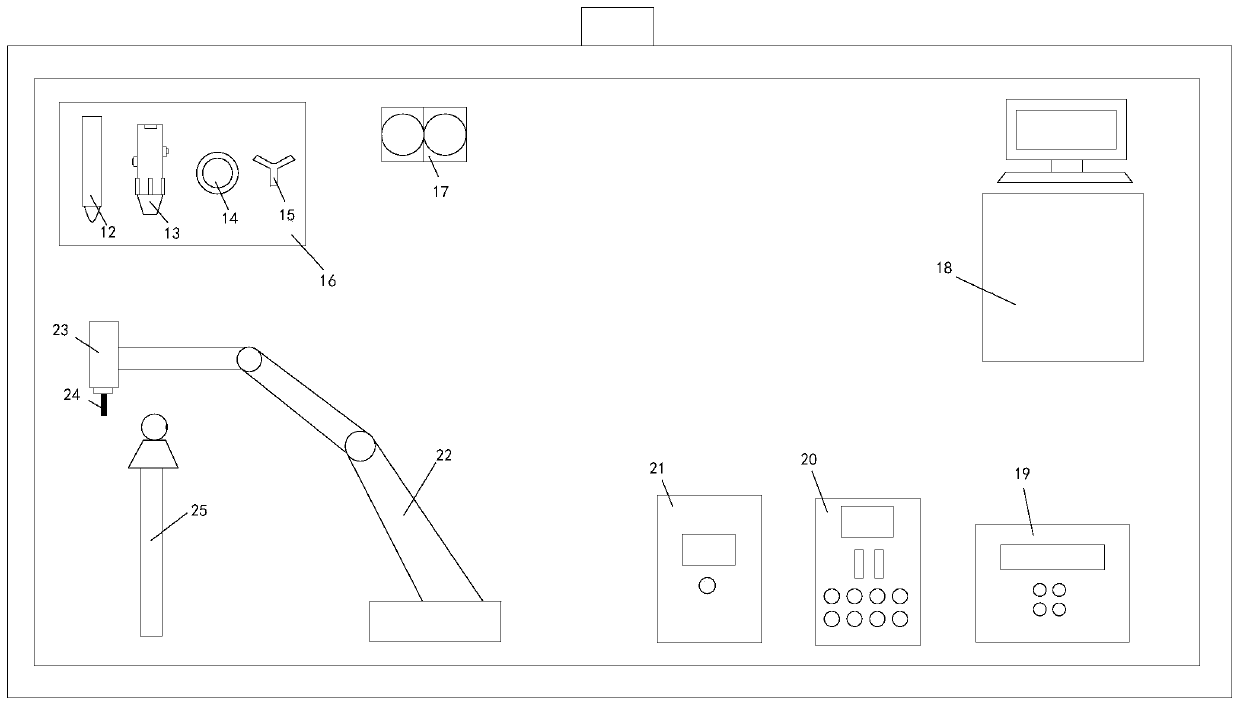

Composite milling material increasing and decreasing type in-situ repairing device and method for deepwater pipeline

PendingCN110539081AHigh densityHigh strengthAdditive manufacturing apparatusOther manufacturing equipments/toolsEngineeringHandling system

The invention discloses a composite milling material increasing and decreasing type in-situ repairing device for a deepwater pipeline. The device comprises a repair cabin, an equipment cabin, a cutterstorage, a local control system, a six-axis robot, a material increase repair system, a material decrease handling system and a monitoring system. According to the device, an underwater high-pressuredry method is utilized to carry out underwater metal additive manufacturing, so that repaired parts have fewer holes, fewer cracks, high density, high strength and good mechanical property. The plasma melting deposition and laser melting deposition combined material reduction manufacturing are adopted and meet repair work under various conditions; the problem of interface combination of a first layer of plasma melting deposition is solved in a laser pre-deposition mode, and the repair of dissimilar materials is realized; after the repair is finished, an anti-corrosion layer is subjected to laser melting deposition, thereby greatly improving the quality of the repaired parts.

Owner:SOUTH CHINA UNIV OF TECH

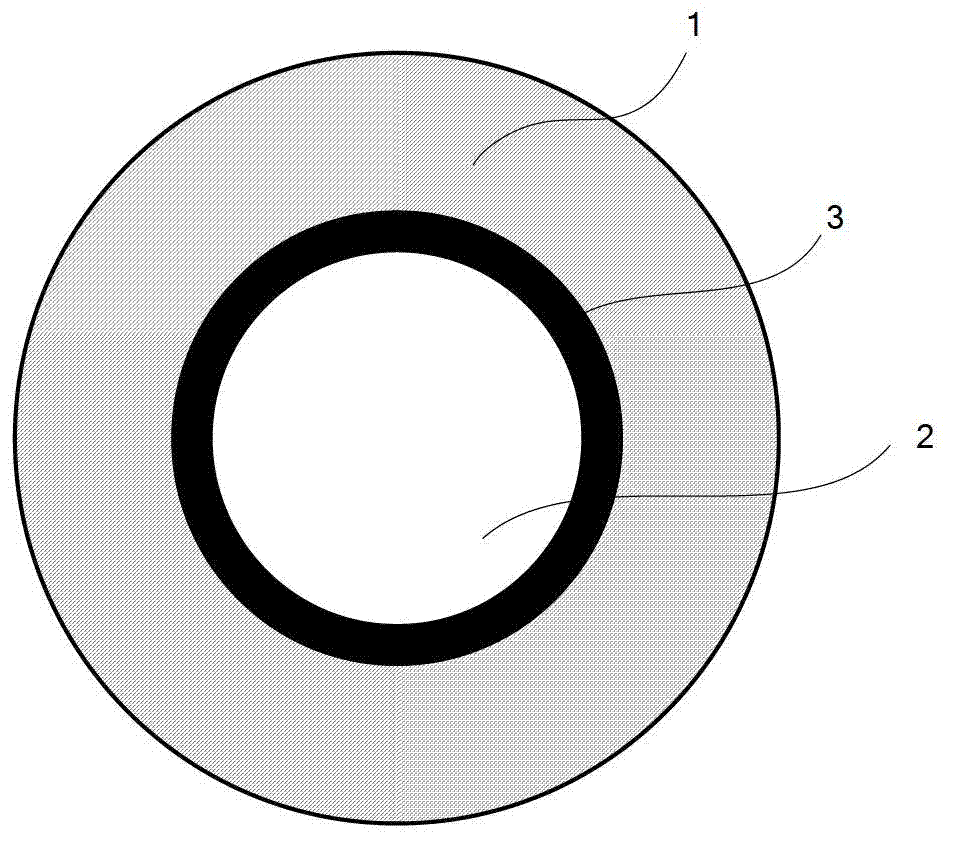

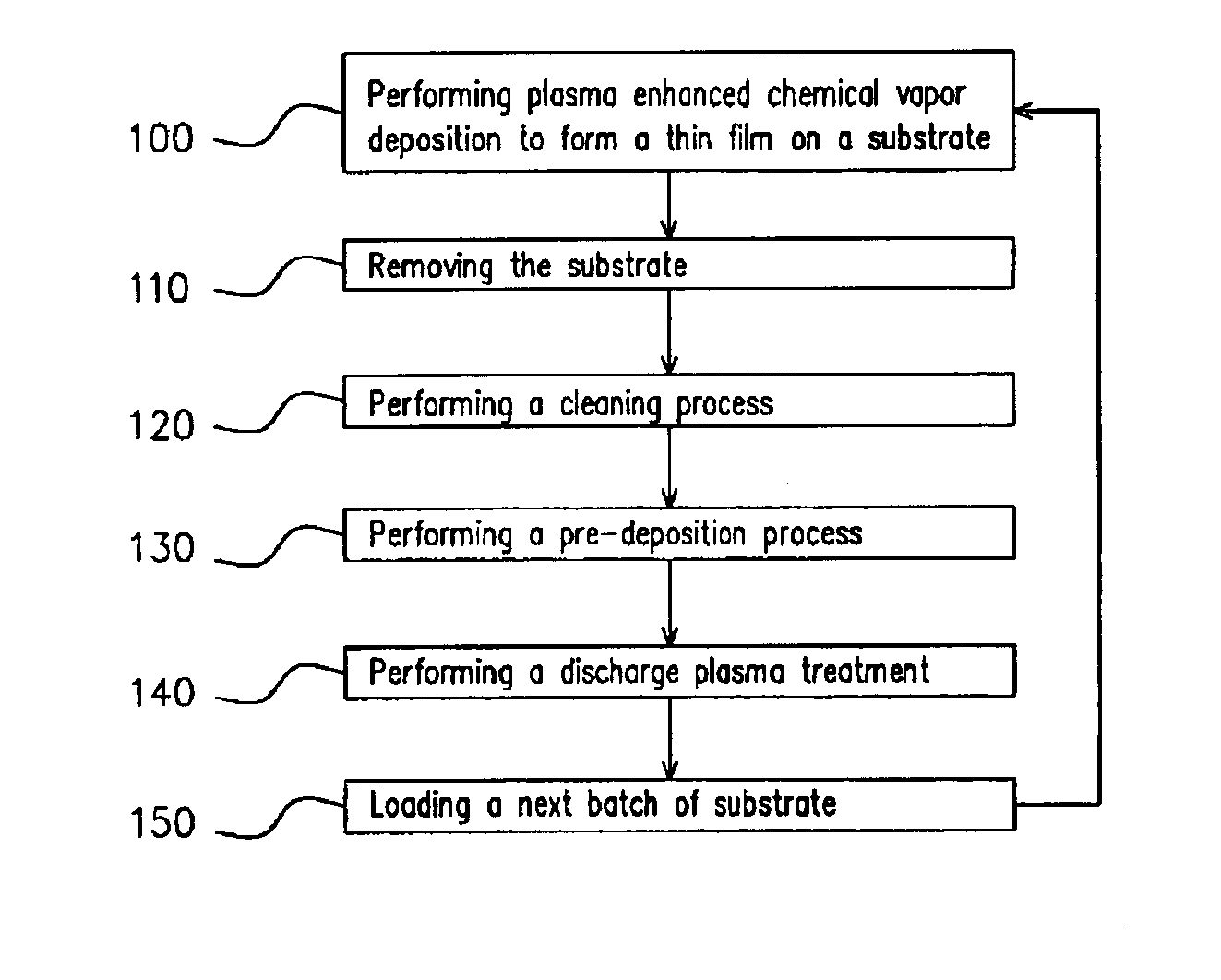

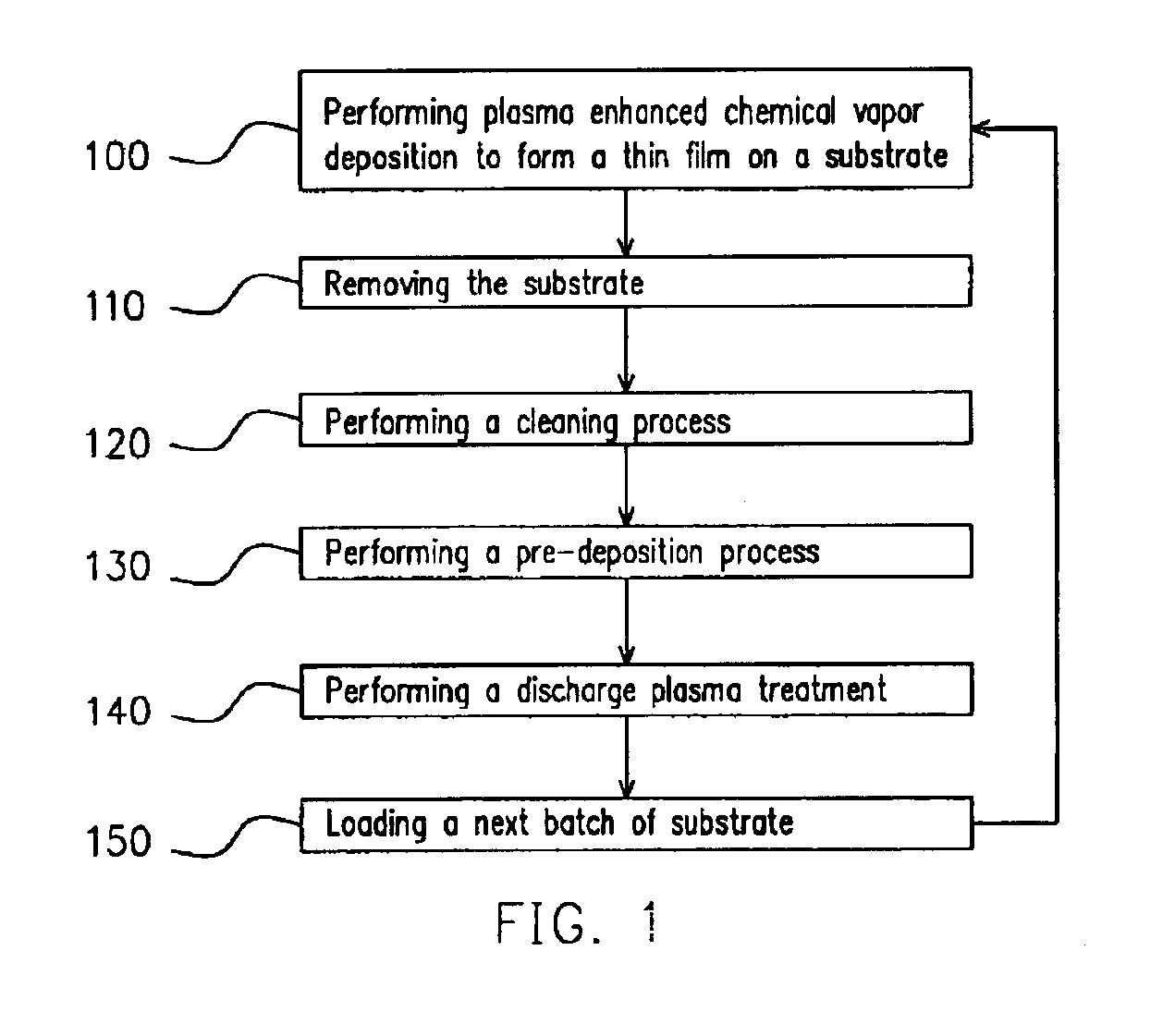

Method for depositing thin film using plasma chemical vapor deposition

InactiveUS6911233B2Enhanced vapor depositionIncrease costLiquid surface applicatorsElectrostatic cleaningChemical reactionPre deposition

A thin film deposition method using plasma enhanced chemical vapor deposition is described. In a plasma enhanced chemical vapor deposition chamber, plasma is used to enhance the chemical reaction to form a thin film on a substrate. The substrate is then removed, followed by passing a cleaning gas into the chamber to remove residues in the chamber. Before loading another batch of substrate in the chamber, a pre-deposition process is performed to isolate contaminants generated from the cleaning process. A discharge plasma treatment is then conducted to lower the amount of accumulated electrical charges.

Owner:INNOLUX CORP

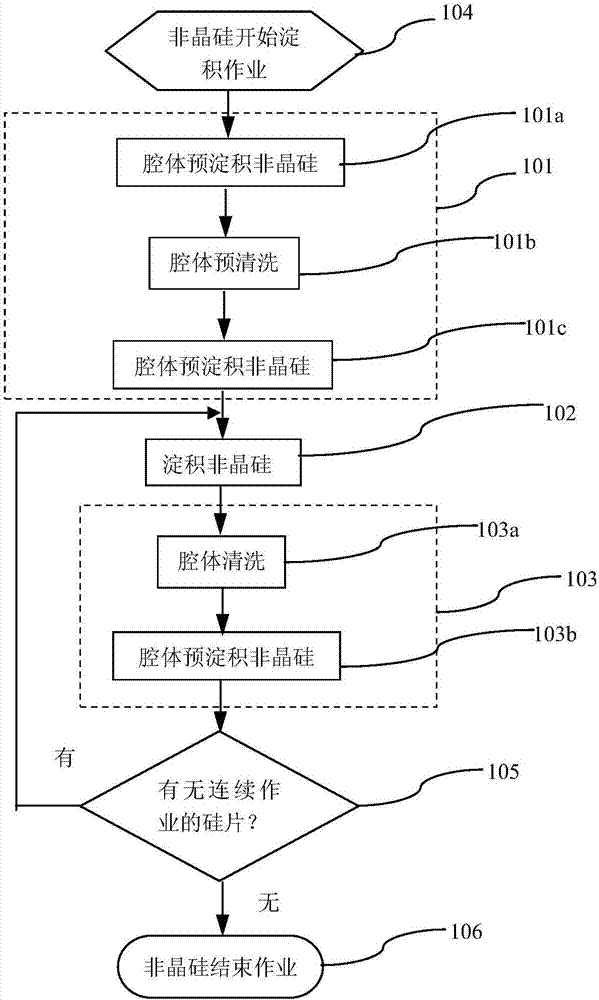

Method for depositing amorphous silicon membrane through PECVD (plasma enhanced chemical vapor deposition)

InactiveCN107083538APrevent peelingQuality improvementSemiconductor/solid-state device manufacturingChemical vapor deposition coatingMetallurgyAmorphous silicon

The invention discloses a method for depositing an amorphous silicon film by PECVD, which also includes a pretreatment step before the step of depositing the amorphous silicon film; the pretreatment step includes depositing a layer of intermediate The pre-deposition step of the dielectric layer; the adhesion and stress buffering capacity of the intermediate dielectric layer and the inner wall of the process chamber are greater than the adhesion and stress buffering capacity of the amorphous silicon film and the inner wall of the process chamber, and the intermediate dielectric layer and the amorphous silicon The adhesion and stress buffering capacity of the film are greater than the adhesion and stress buffering capacity of the amorphous silicon film and the inner wall of the process chamber, and the intermediate dielectric layer is used as a buffer layer between the inner wall of the process chamber and the amorphous silicon film on the inner wall and Prevent the amorphous silicon film on the inner wall of the process chamber from peeling off. The invention can reduce the generation of particles, improve the quality of the amorphous silicon film and improve the product yield.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Diffusion method for high-concentration phosphorosilicate glass and high square resistance

ActiveCN108389933AImprove conversion efficiencyReduce power-on timeFinal product manufactureSemiconductor/solid-state device manufacturingProduction lineHigh concentration

The invention discloses a diffusion method for high-concentration phosphorosilicate glass and high square resistance. The method comprises the steps of 1, first pre-deposition; 2, first heating; 3, second pre-deposition; 4, second heating; 5, propelling; 6, cooling; and 7, third pre-deposition. In the invention, a method of multi-step diffusion is adopted, the source introduction time is reduced,the source introduction flow is increased, fast heating and propelling improve the conventional diffusion method, and high square resistance with excellent uniformity is realized while obtaining PSG (Phosphorosilicate Glass) with high impurity concentration, so that the follow-up process is ensured to realize a more ideal SE structure, and finally the battery conversion efficiency is improved to the maximum extent. In addition, the diffusion method is extremely high in compatibility with the conventional production line, does not need to improve equipment or add new equipment and is excellentin practicability.

Owner:TONGWEI SOLAR ENERGY CHENGDU CO LID

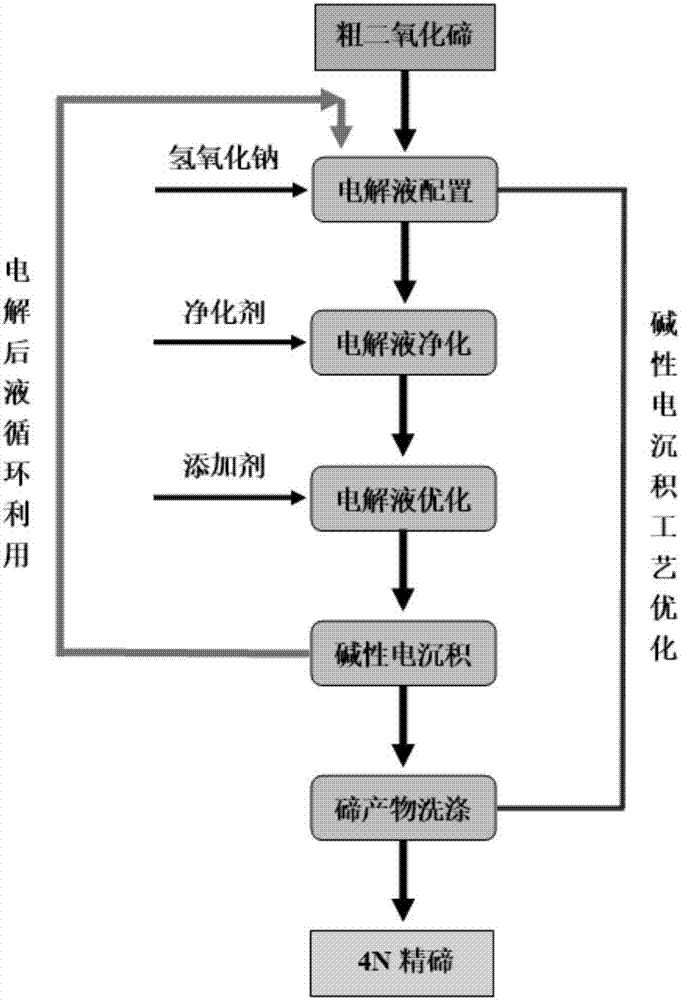

4N tellurium preparation method based on alkaline electro-deposition process

ActiveCN107475736AImprove compactnessHigh deposition current densityElectrolysis componentsElectrolysisTe element

The invention discloses a 4N tellurium preparation method based on an alkaline electro-deposition process. The method includes the following steps that a sodium hydroxide piece is added into ultrapure water at an indoor temperature, stirring and dissolving are conducted, and hot alkaline liquor is obtained; crude tellurium dioxide powder is added into the hot alkaline liquor for reacting, and electrolysis ex-liquid is obtained through preparation; a purifying agent is added so that the electrolysis ex-liquid can be purified and filtered, and an electrolyte is obtained through preparation; the electrolyte is cooled to the indoor temperature, an addition agent is added, the electrolyte is subjected to constant voltage pre-deposition treatment after stirring and dissolving are completed, and then constant current electro-deposition treatment is conducted so that electro-deposition product tellurium blocks and electrolysis post-liquid can be obtained; and after the tellurium blocks are stripped from a plate electrode, washing with the ultrapure water is performed for several times, and then drying is conducted so that 4N tellurium can be prepared. The preparation method disclosed by the invention has the advantages that the deposition electric current density is large, deposition efficiency is high, the preparation period is short, the tellurium product compactness is good, the electrolyte can be recycled, cost is low, the environment is friendly and industrialization is can be facilitated; and the 4N tellurium preparation method can be effectively applied to alkaline electro-deposition for preparing the 4N tellurium.

Owner:SICHUAN UNIV