Patents

Literature

79results about How to "Improve electrical performance parameters" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

High potential gradient zinc oxide pressure-sensitive resistor material and preparation process thereof

InactiveCN102515742AExtended service lifeReduce energy consumptionVaristor coresHigh energyElectric power system

The invention relates to a high potential gradient zinc oxide pressure-sensitive resistor material and a preparation process thereof. The high potential gradient zinc oxide pressure-sensitive resistor material with uniform particle sizes is obtained by weighing a main material ZnO, a doping oxide, and a product rare earth oxide obtained by carrying out thermal decomposition on a rare earth oxalate or / and carbonate or / and hydroxide according to proportions, carrying out high energy wet grinding, drying, presintering at 200-800DEG C, carrying out high energy dry grinding, and sintering at 800-1100DEG C. The preparation process of the invention has the advantages of simplicity, low cost, environmental protection and low energy consumption, and the prepared zinc oxide pressure-sensitive resistor material can be used for preparing high quality lightning arrester products for ultrahigh electric power systems.

Owner:INST OF PROCESS ENG CHINESE ACAD OF SCI

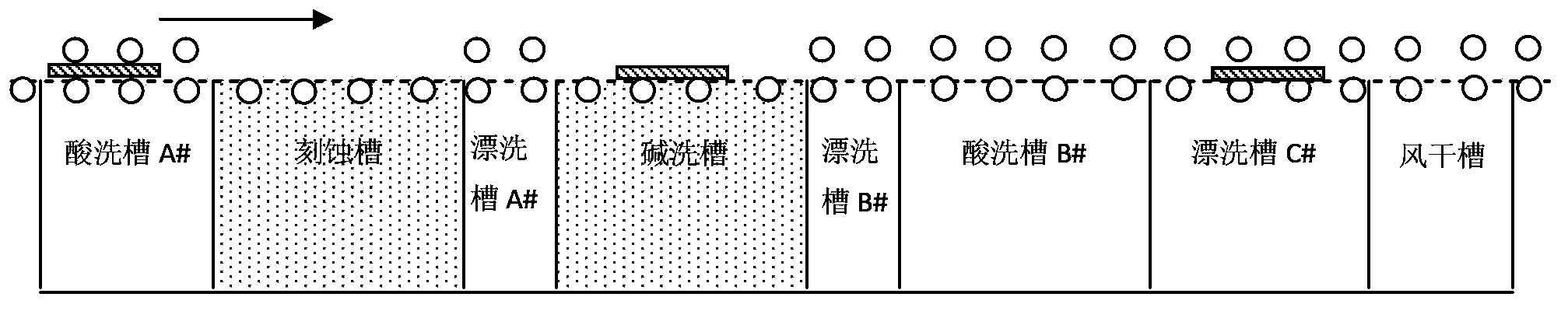

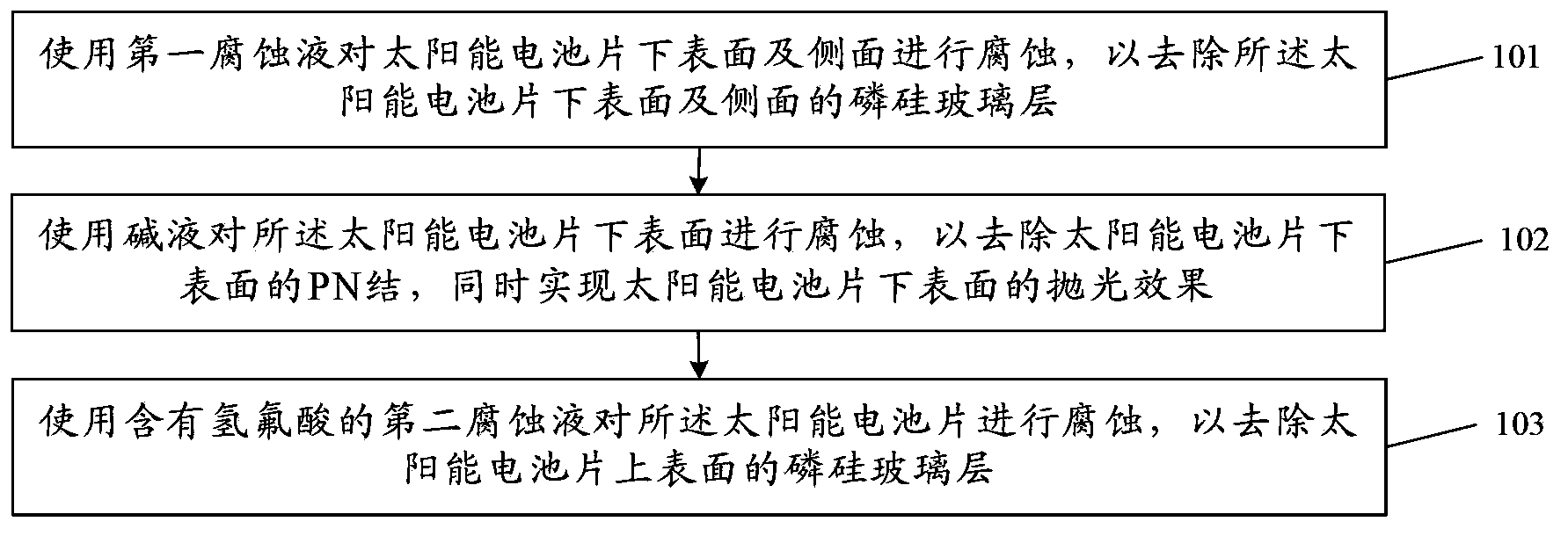

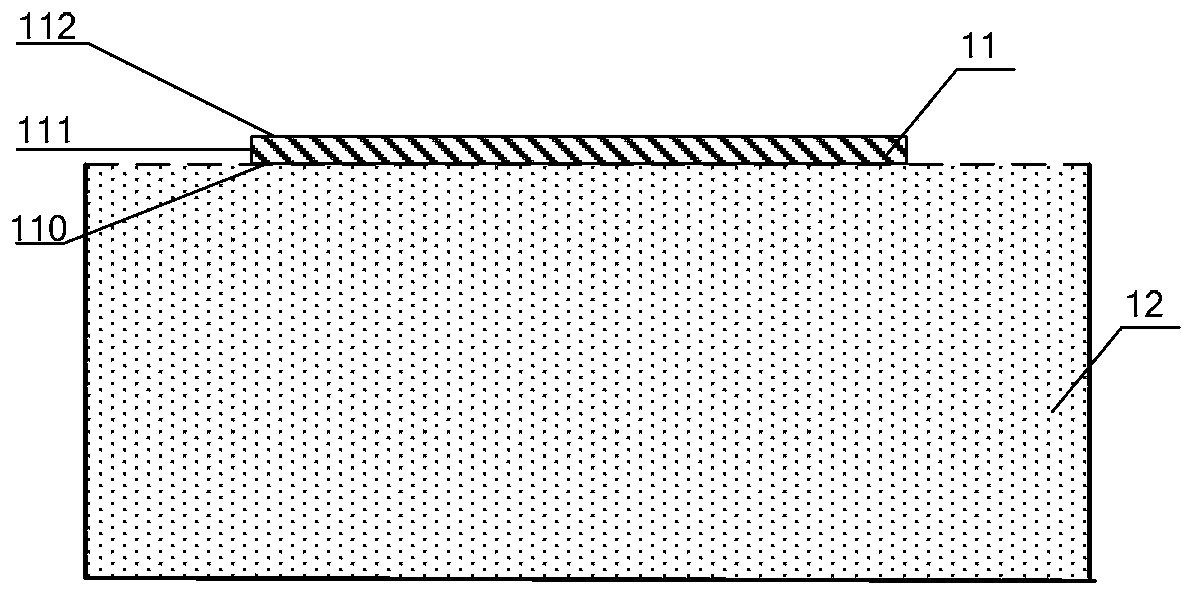

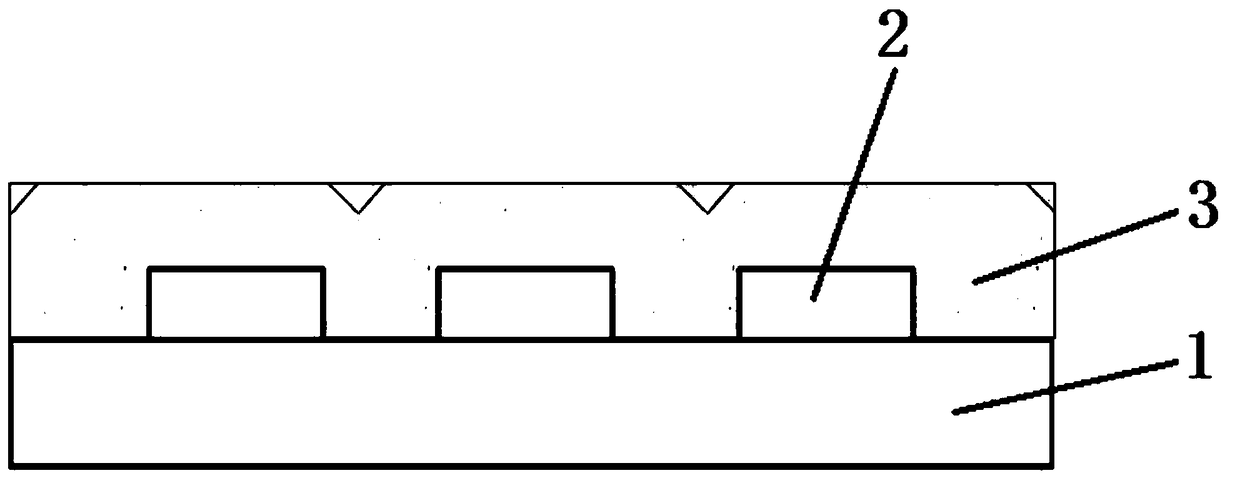

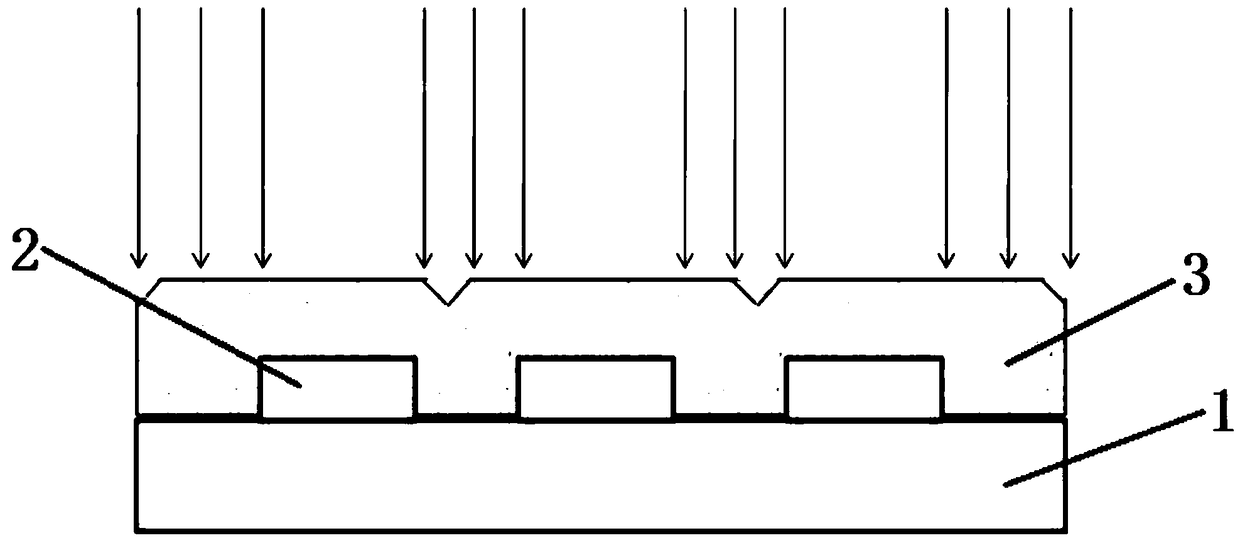

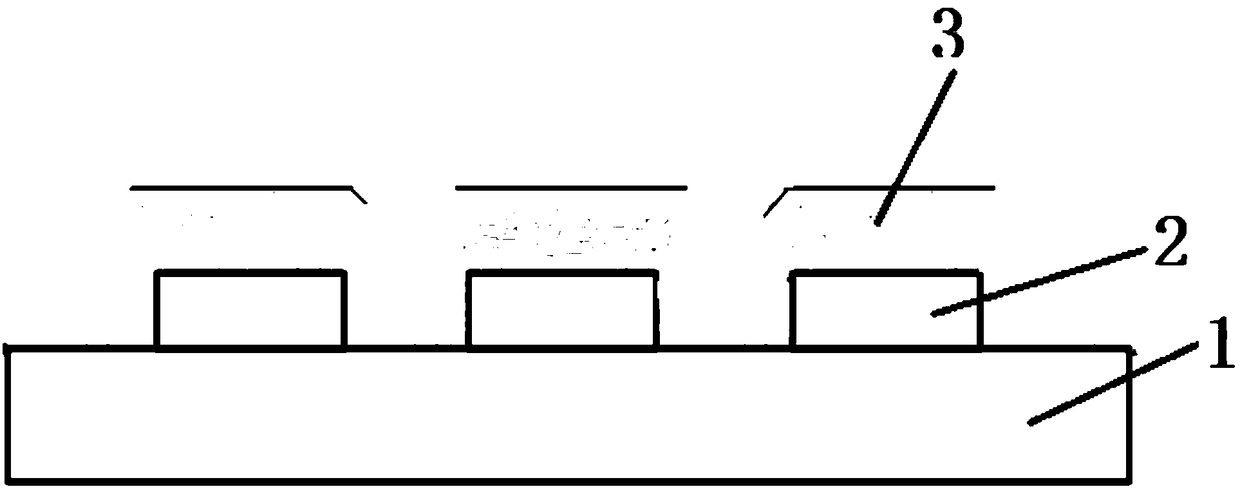

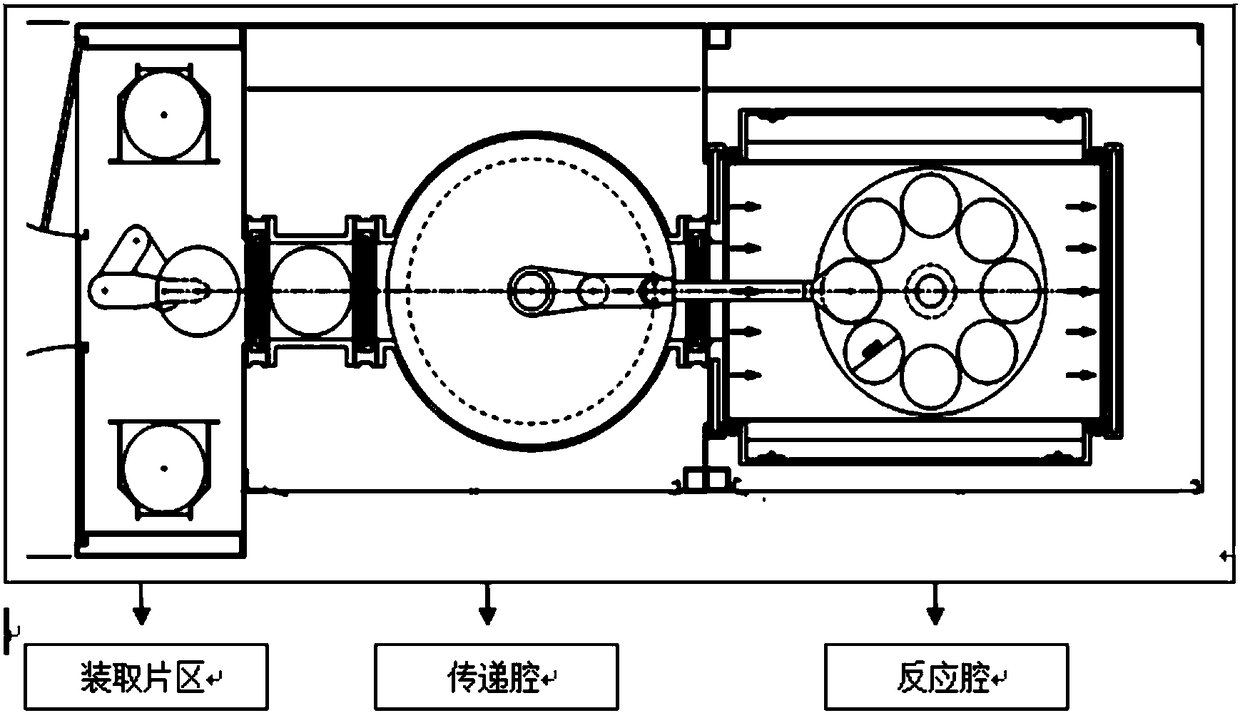

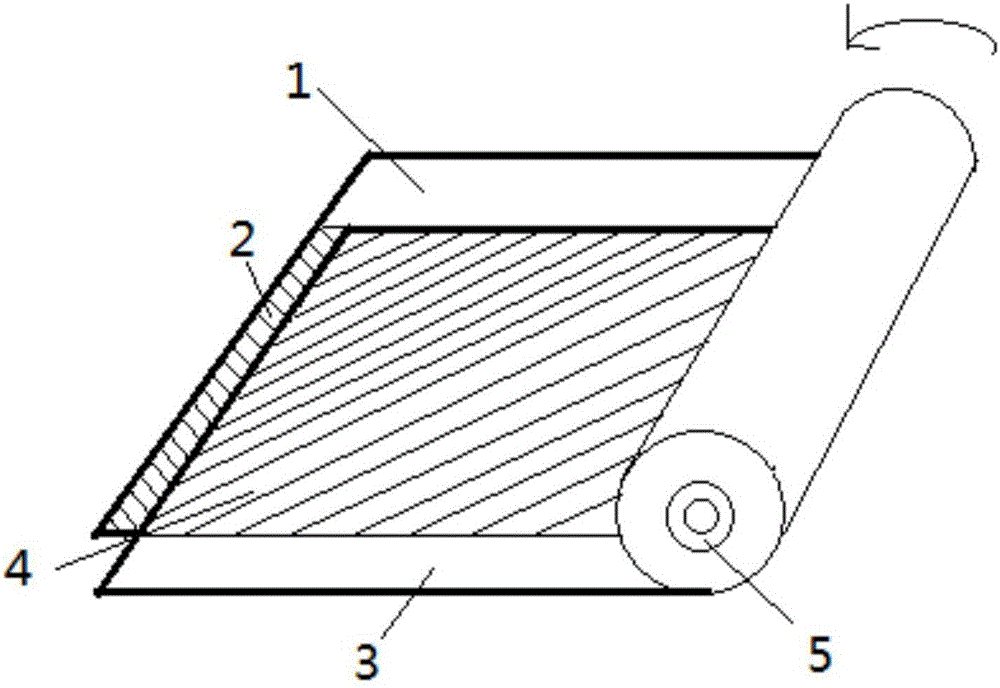

Wet etching process and equipment, and solar cell and manufacturing method thereof

InactiveCN104051564AThere is no problem of rising square resistanceReduce usageFinal product manufactureSemiconductor/solid-state device manufacturingHydrofluoric acidEtching

The invention, which relates to the technical field of the solar energy, discloses a wet etching process and equipment, and a solar cell and manufacturing method thereof. Therefore, problems of etching black line occurrence and square resistance increasing according to the existing wet etching process can be solved; and elimination of the phosphorosilicate glass layer and the back junction is realized and an objective of back polishing is achieved, thereby improving the conversion efficiency of the solar cell. The wet etching process comprises the following steps that: first corrosive liquid is used for carrying out corrosion on the lower surface and the side surface of a solar cell so as to remove the phosphorosilicate glass layer at the lower surface and the side surface of the solar cell, wherein the first corrosive liquid is a hydrofluoric acid solution; alkali liquor is used for carrying out corrosion on the lower surface of the solar cell so as to remove the PN junction at the lower surface of the solar cell and realize the polishing effect of the lower surface f the solar cell; and second corrosive liquid containing hydrofluoric acid is used for carrying out corrosion on the solar cell, thereby removing the phosphorosilicate glass layer at the upper surface of the solar cell.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

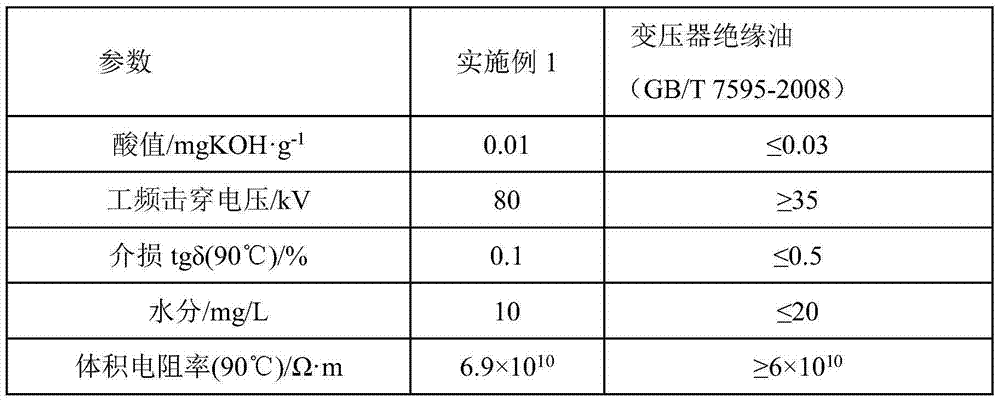

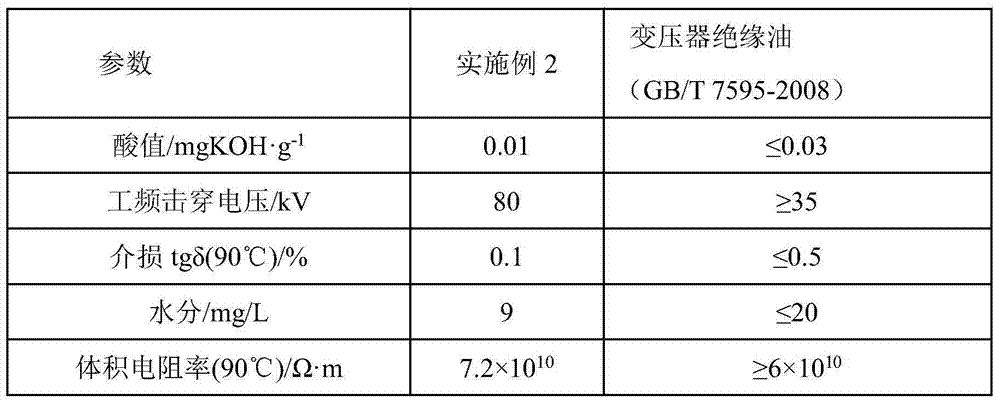

Vegetable insulating oil treating full-set process

ActiveCN104232302AImprove electrical performance parametersFatty-oils/fats refiningVegetable oilSlag

The invention discloses a vegetable insulating oil treating full-set process which includes the following steps: 1 conducting alkali refining, washing, decoloration and deodorization on vegetable oil; 2 filtering and dehydrating refined vegetable oil; 3 adsorbing the dehydrated vegetable oil, dehydrating the adsorbed vegetable oil and adding antioxidant into the oil. The step 3 includes (1) adding the oil subjected to vacuum dehydration into an adsorption container, utilizing argil as an adsorbent, adding 2-4% of argil, meanwhile heating the oil to enable the oil temperature to reach 45-70 DEG C, stirring the mixture for 2-4h with the rotating speed as 55-75 r / min and utilizing a slag extractor to conduct argil filtering treatment on the oil; (2) further filtering the vegetable oil, enabling the oil to pass through a filter screen and enter the vacuum dehydration process and repeating the step (2); (3) pumping the vegetable oil into a cooling stirring tank, conducting quick stirring at the speed of 30-60 r / min, adding an additive and maintaining the stirring speed for 3-5h. By means of the technical scheme, the obtained insulation oil reaches the standard for transformer oil, excellent vegetable insulation oil is obtained, and the oil can be greatly popularized in use.

Owner:CHONGQING UNIV

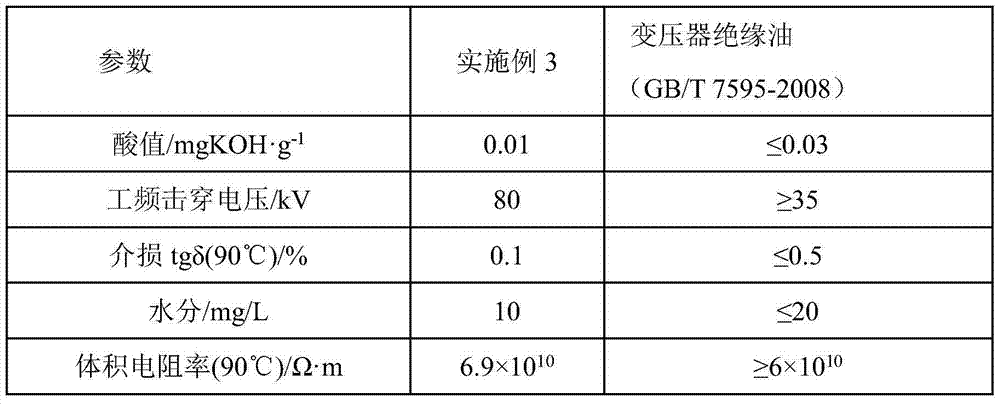

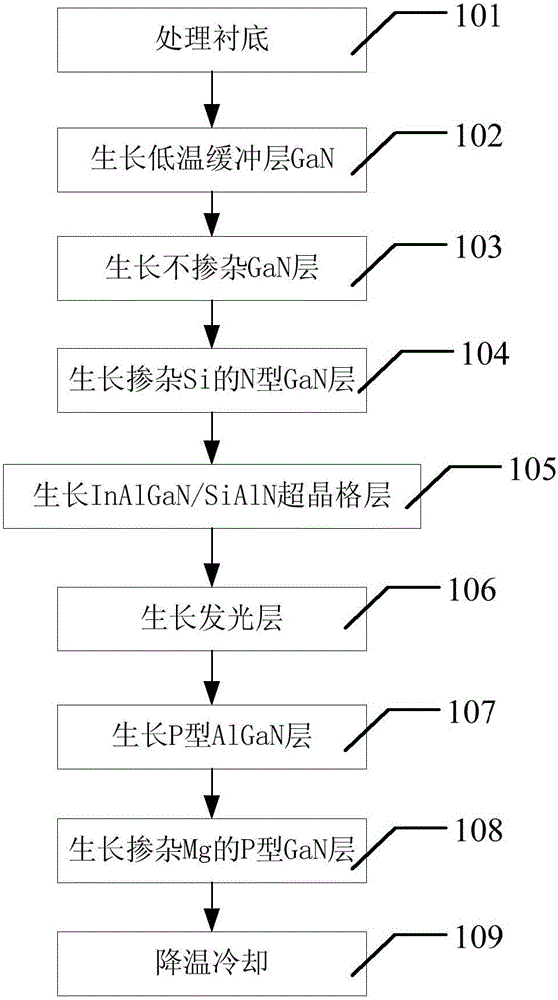

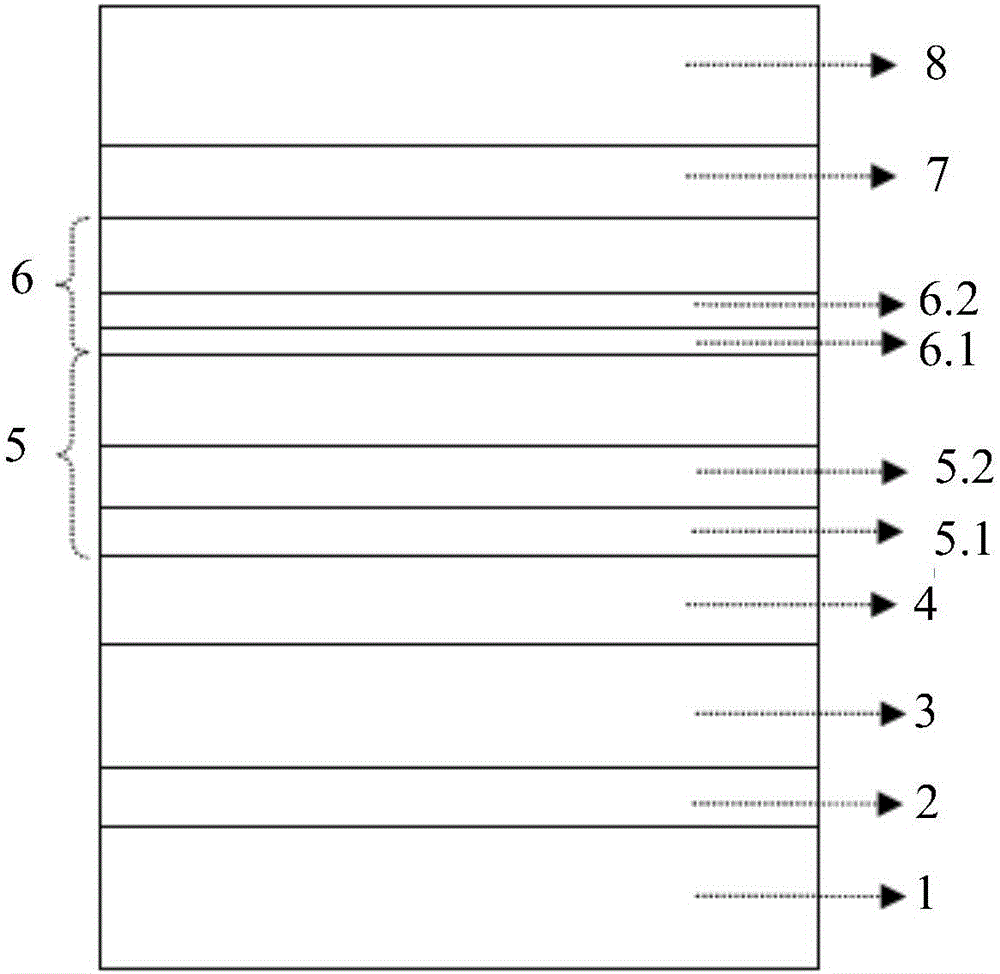

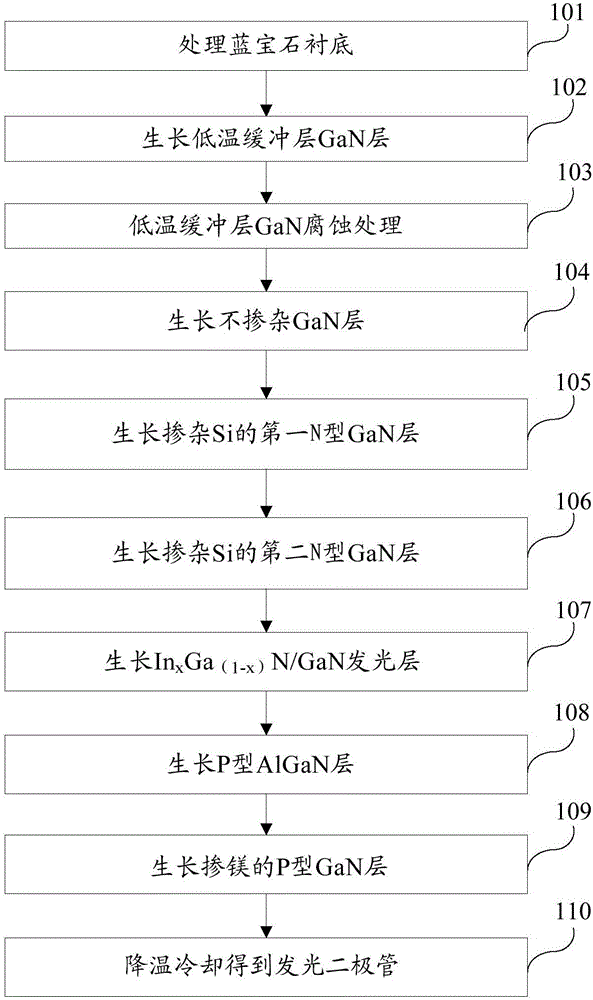

Epitaxial growing method of LED

ActiveCN105869999AHigh luminous intensityImprove electrical performance parametersSemiconductor/solid-state device manufacturingSemiconductor devicesLuminous intensityCurrent distribution

The invention discloses an epitaxial growing method of an LED. The method comprises the steps of processing a substrate, growing a low-temperature buffer layer GaN, growing an undoped GaN layer, growing an N-type GaN layer doped with Si, growing an InAlGaN / SiAlN superlattice layer, growing a luminous layer, growing a P-type AlGaN layer, growing a P-type GaN layer doped with Mg and conducting cooling. According to the technical scheme, the InAlGaN / SiAlN superlattice layer is introduced after growing of the N-type GaN layer doped with Si and before growing of the luminous layer, and due to the introduction of the InAlGaN / SiAlN superlattice layer, the N-layer current distribution of the LED is improved, and the luminous intensity of the LED is improved.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

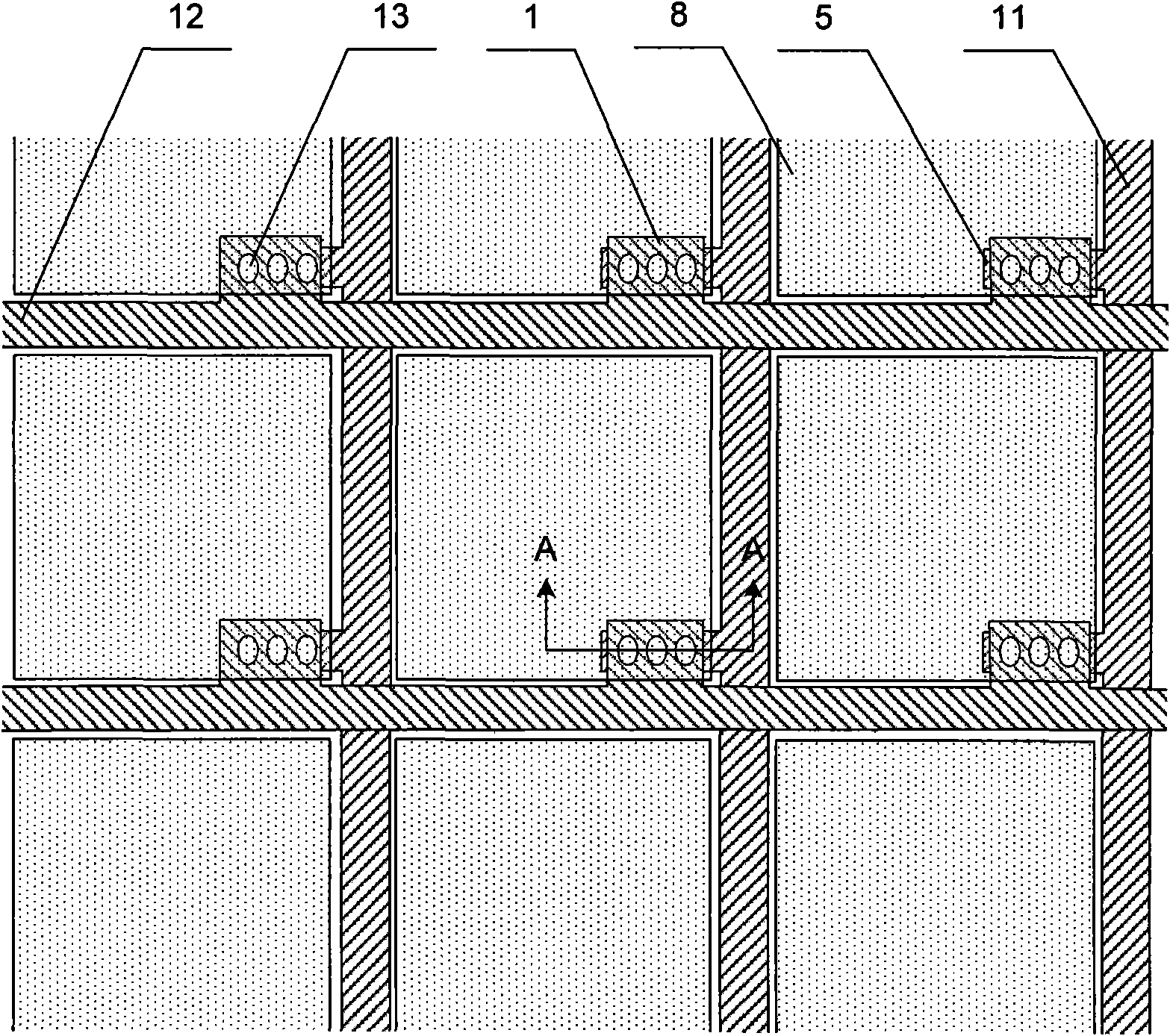

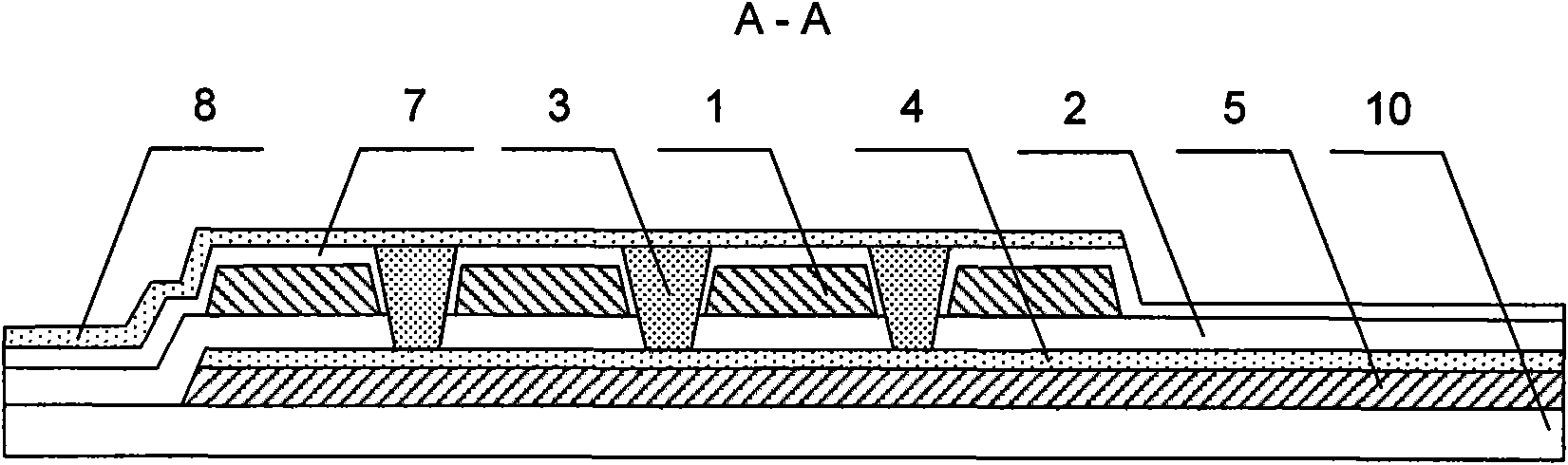

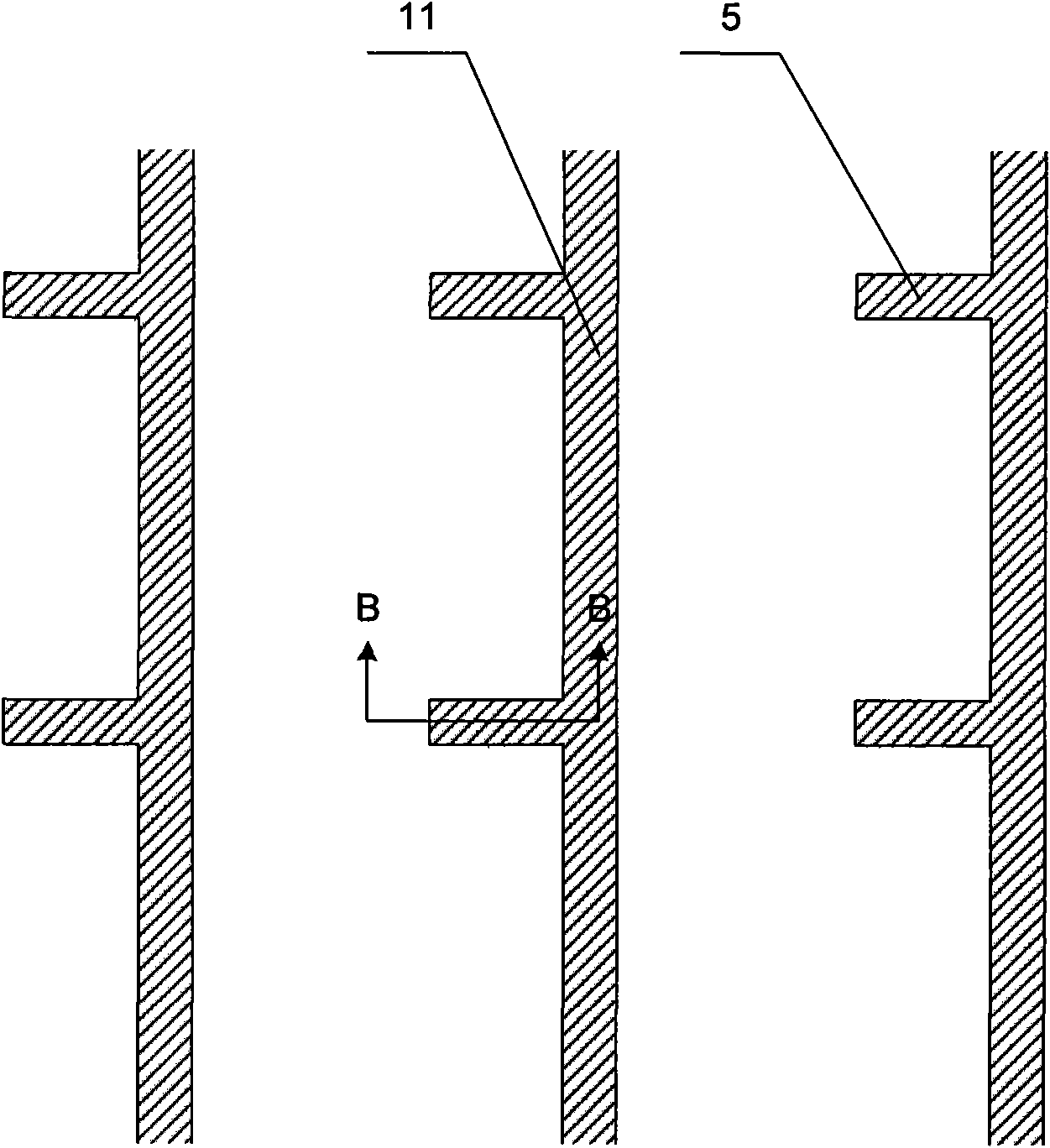

TFT-LCD array substrate and manufacturing method thereof

InactiveCN101620350AReduce electrical influenceExcellent electrical propertiesTransistorSolid-state devicesSpatial structureEngineering

The invention relates to a TFT-LCD array substrate and a manufacturing method thereof. The array substrate comprises a grid wire, a data wire, a pixel electrode and a thin film transistor. The array substrate is characterized in that the thin film transistor comprises a grid electrode connected with the grid wire and a source electrode connected with the data wire; at least one through hole is formed on the grid electrode or a through groove is formed on at least one side of the grid electrode; and a semiconductor layer which is connected with the pixel electrode and the source electrode respectively is filled in the through hole or the through groove. The array substrate changes a 'planar type' TFT structure which is universally adopted in the prior art, changes the planar structure into a spatial structure, and has the characteristics of simple and compact structure, good parameter property, simple manufacturing process and the like. The array substrate realizes the effect of increasing the starting current and has certain improvement on other electrical parameters, and the spatial structure of the array substrate reduces the planar size and increases the spatial utilization rate so as to increase the opening ratio.

Owner:BOE TECH GRP CO LTD +1

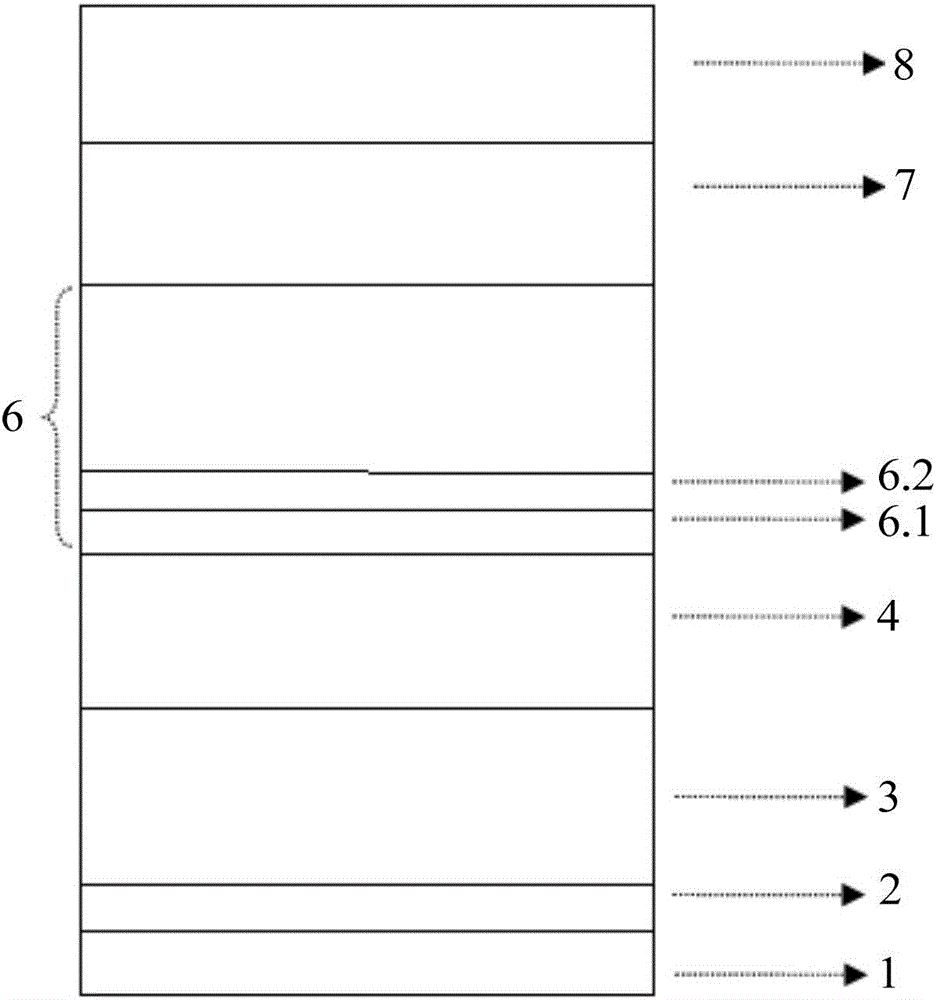

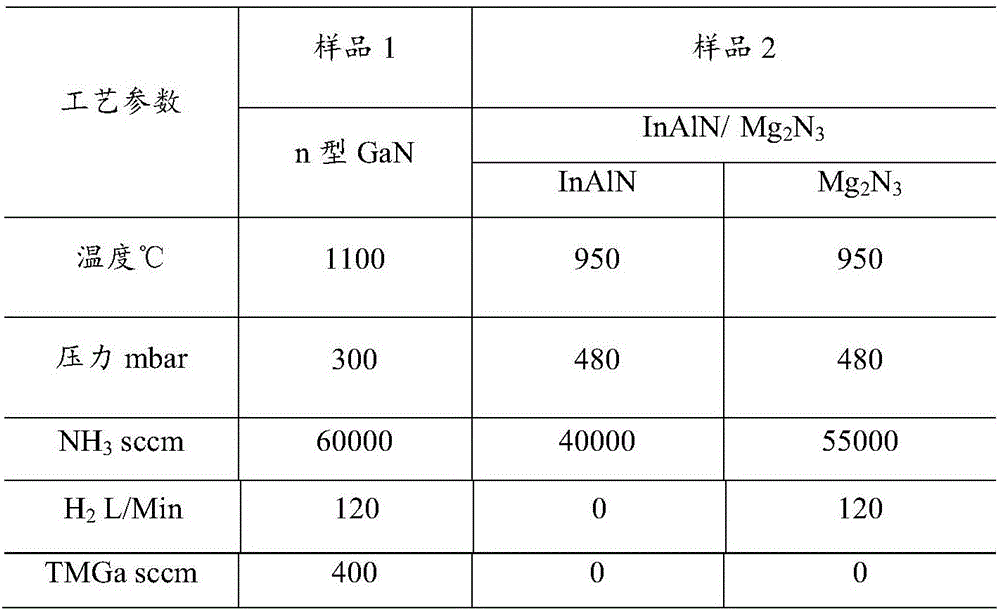

LED epitaxy superlattice growth method

ActiveCN106409999AEven distribution of currentImprove luminous efficiencySemiconductor devicesBiologySuperlattice

The present invention discloses a LED epitaxy superlattice growth method. The method comprises in order: processing a substrate, growing a low-temperature buffer layer GaN, growing an un-doping GaN layer, growing an N-type GaN layer doping Si, growing an InAlN / Mg2N3 superlattice layer, growing a luminescent layer, growing a P-type AlGaN layer, growing a P-type GaN layer doping Mg, and performing cooling. The InAlN / Mg2N3 superlattice layer is introduced after the growth of the N-type GaN layer doping Si and prior to the growth of the luminescent layer so as to extend the LED current, improve the LED luminous efficiency and allow the electrical parameters of the LED to be better.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

Manufacture method of high-efficiency cell with front emission junction and backside tunneling oxidation and passivation contact

InactiveCN106784128AReduce surface recombinationImprove electrical performance parametersFinal product manufactureSemiconductor devicesElectricitySurface concentration

The invention relates to a manufacture method of a high-efficiency cell with a front emission junction and backside tunneling oxidation and passivation contact. Texturing is carried out after removing a damage layer of a silicon chip, a B-doped P+ emission junction of a low surface concentration is formed, an ultrathin tunneling oxide layer SiO2 and a P-doped polysilicon layer are grown in the back side of the silicon chip after edge insulation and backside polishing, an alumina layer is deposited in the surface of the P+ emission junction, a hydrogenated amorphous silicon nitride passivation antireflection layer is grown in the front side of the silicon chip in a PECVD or magnetron sputtering method, a Ag / Al slurry is printed in the front side of the silicon chip, a full aluminum backfield Al-BSF structure is formed in the back side of the silicon chip, and a drying furnace is used to implement drying. Compared with the prior art, the ultrathin tunneling oxide SiO2 layer (<2nm) and the P-doped silicon layer are used to reduce metal-semiconductor surface combination in the backside greatly, and the manufacture method has the obvious advantage that electric performance parameters can be improved greatly on the basis that the method is compatible with a traditional cell manufacturing technology.

Owner:SHANGHAI SHENZHOU NEW ENERGY DEV

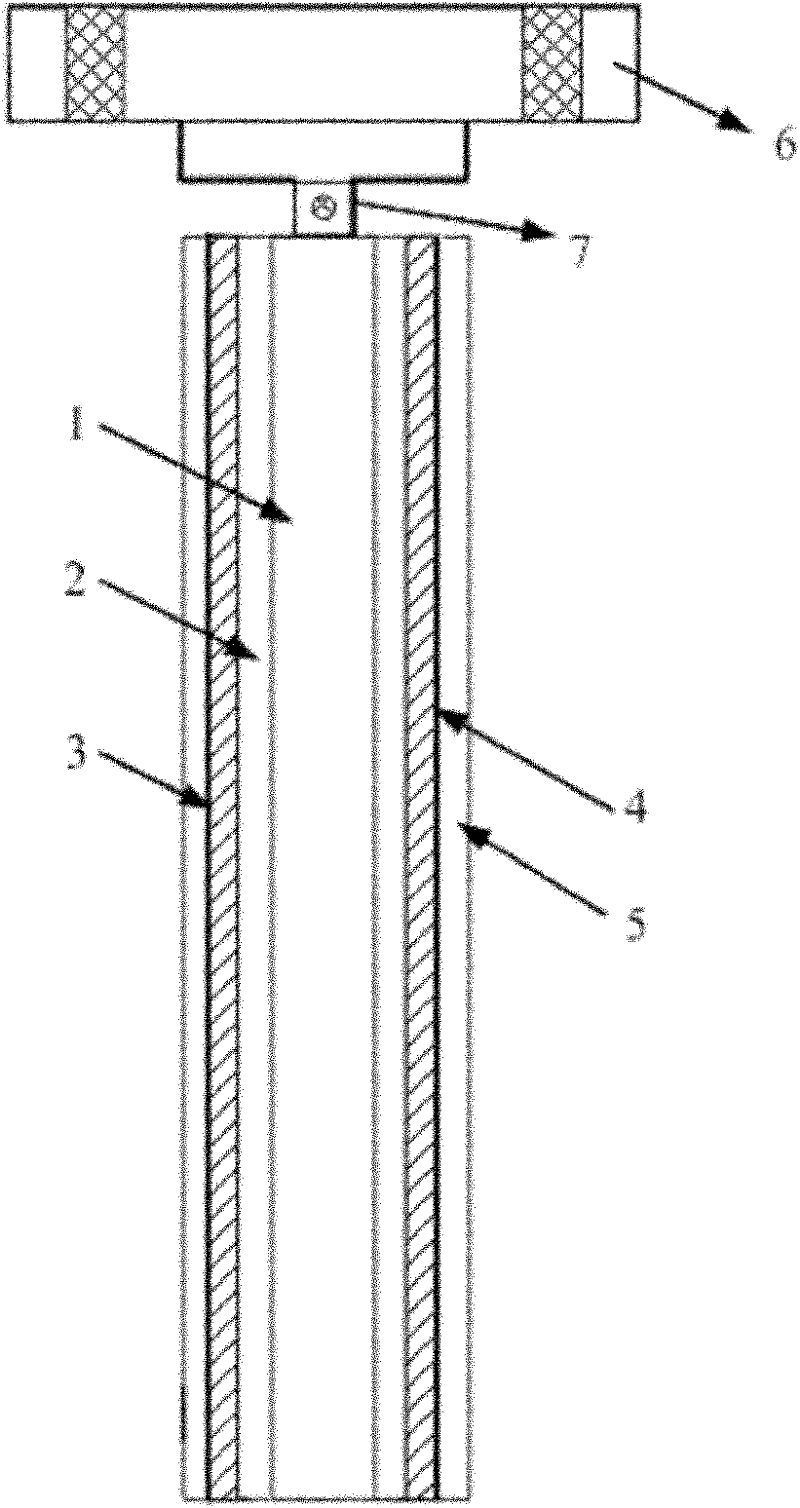

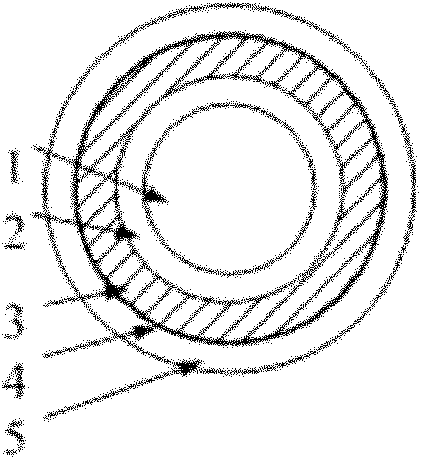

Low-temperature insulating structure of gas-cooled lead

ActiveCN102243908AExcellent electrical performance parametersReasonable electric and magnetic field distributionSuperconductors/hyperconductorsSuperconductor devicesLiquid nitrogen containerLightning impulse voltage

The invention belongs to the technical field of low-temperature and superconducting application and particularly relates to a low-temperature insulating structure of a gas-cooled lead. The structure provided by the invention comprises a vacuum flange and a three-layer insulating structure which is arranged on the outer surface of the gas-cooled lead, wherein the three-layer insulating structure comprises a lead inner protective layer, a low-temperature insulating layer and an outer protective layer which are sequentially arranged from interior to exterior; and the vacuum flange is connected with the gas-cooled lead which is arranged at the inner core of the three-layer insulating structure through bolts. The low-temperature insulating structure provided by the invention can stand a 5min power frequency voltage test of a more than 35kV voltage class, a thunder impulse voltage test, a partial discharge test, a 15min alternating current withstand voltage test, a direct current withstand voltage test and the like, has the advantages of excellent electric property parameters, reasonable electric field and magnetic field distribution, low heat leakage and integral vacuum tightness withstand voltage properties with a stainless steel liquid nitrogen container, and can be used for improving the stability of a system and greatly lowering the investment cost.

Owner:CHINA ELECTRIC POWER RES INST +1

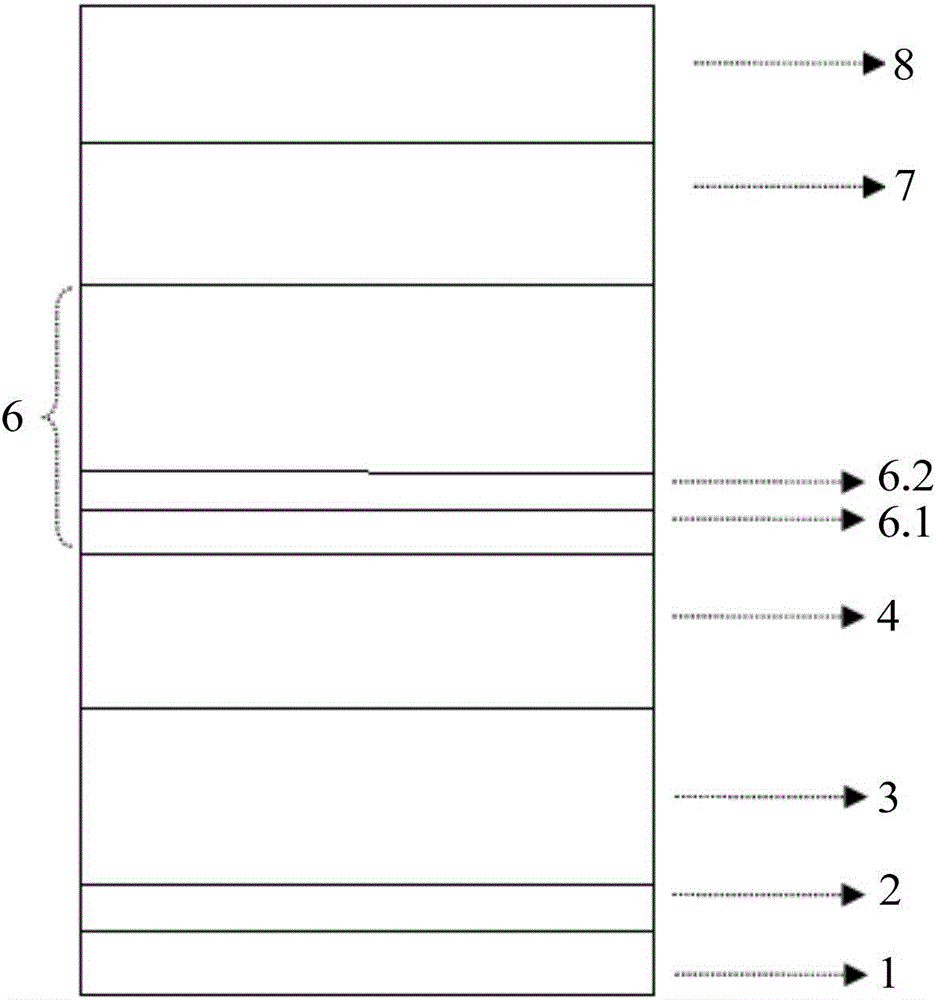

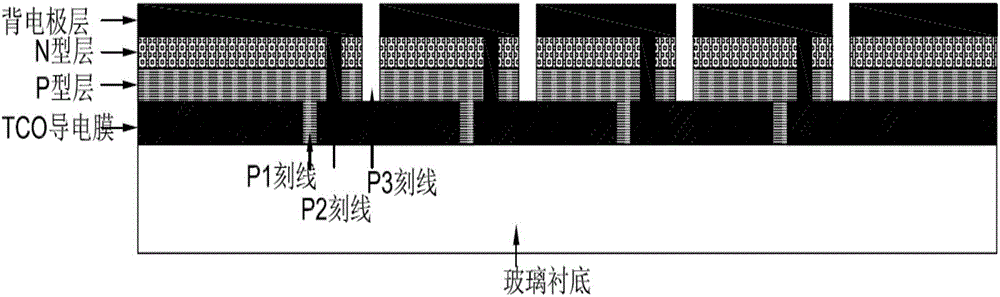

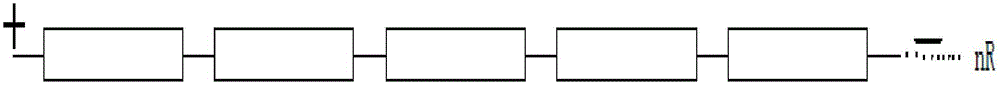

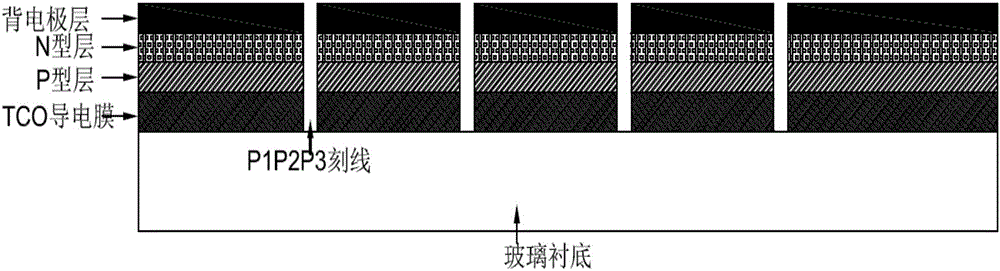

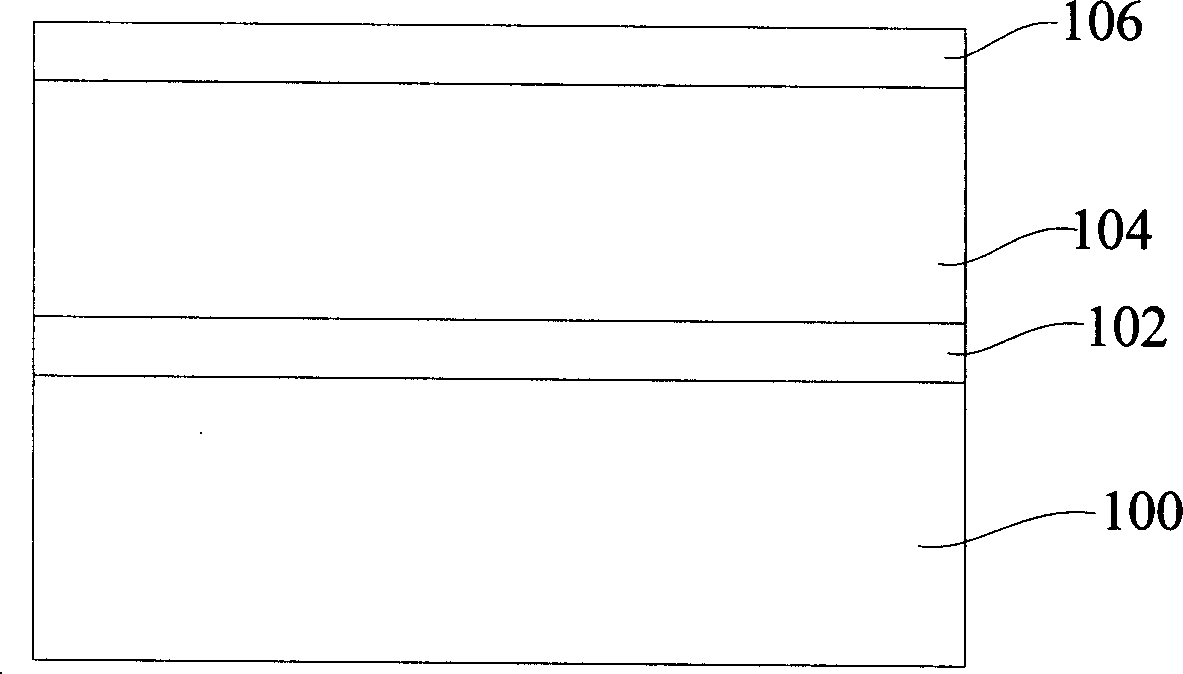

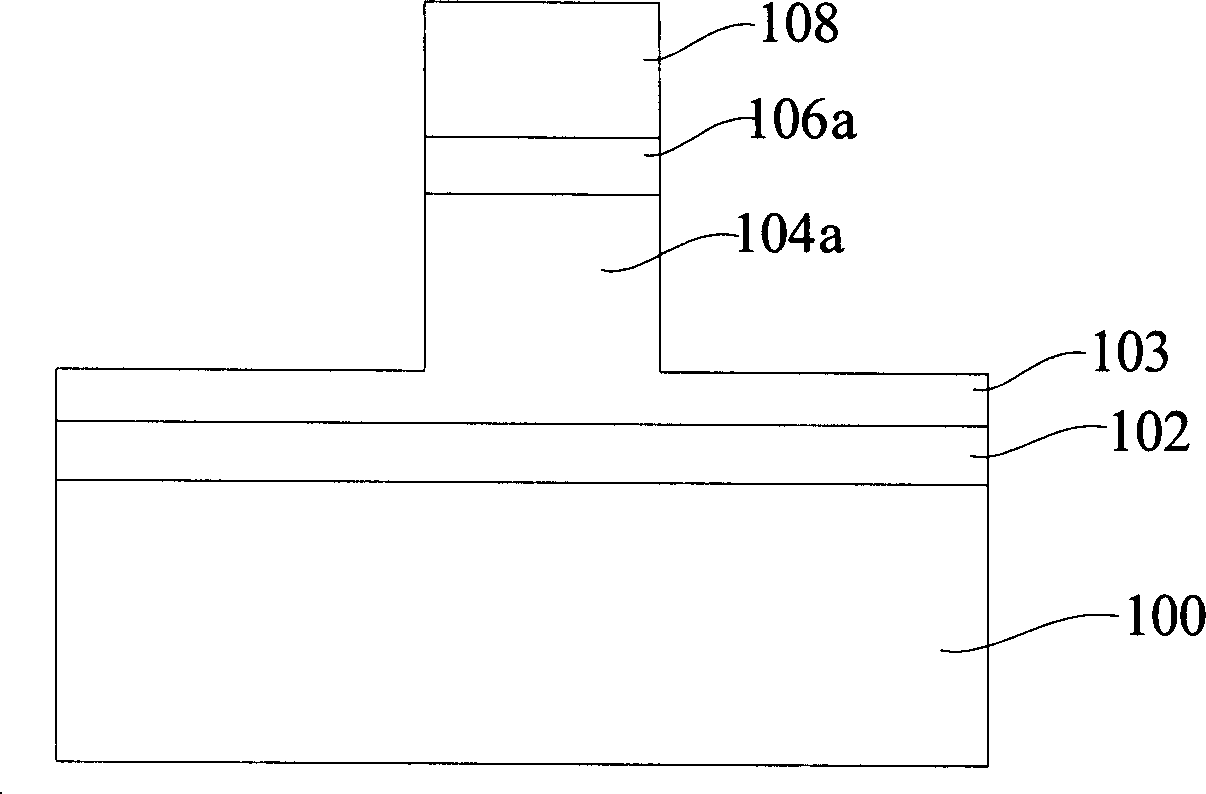

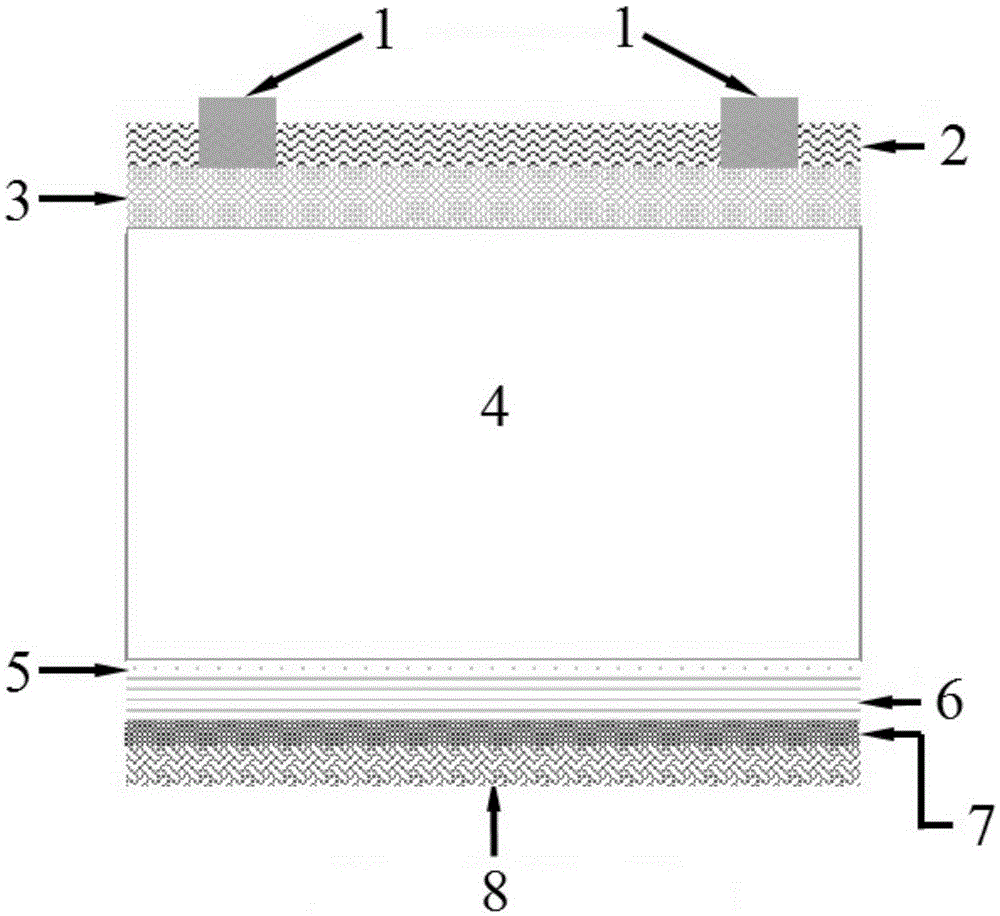

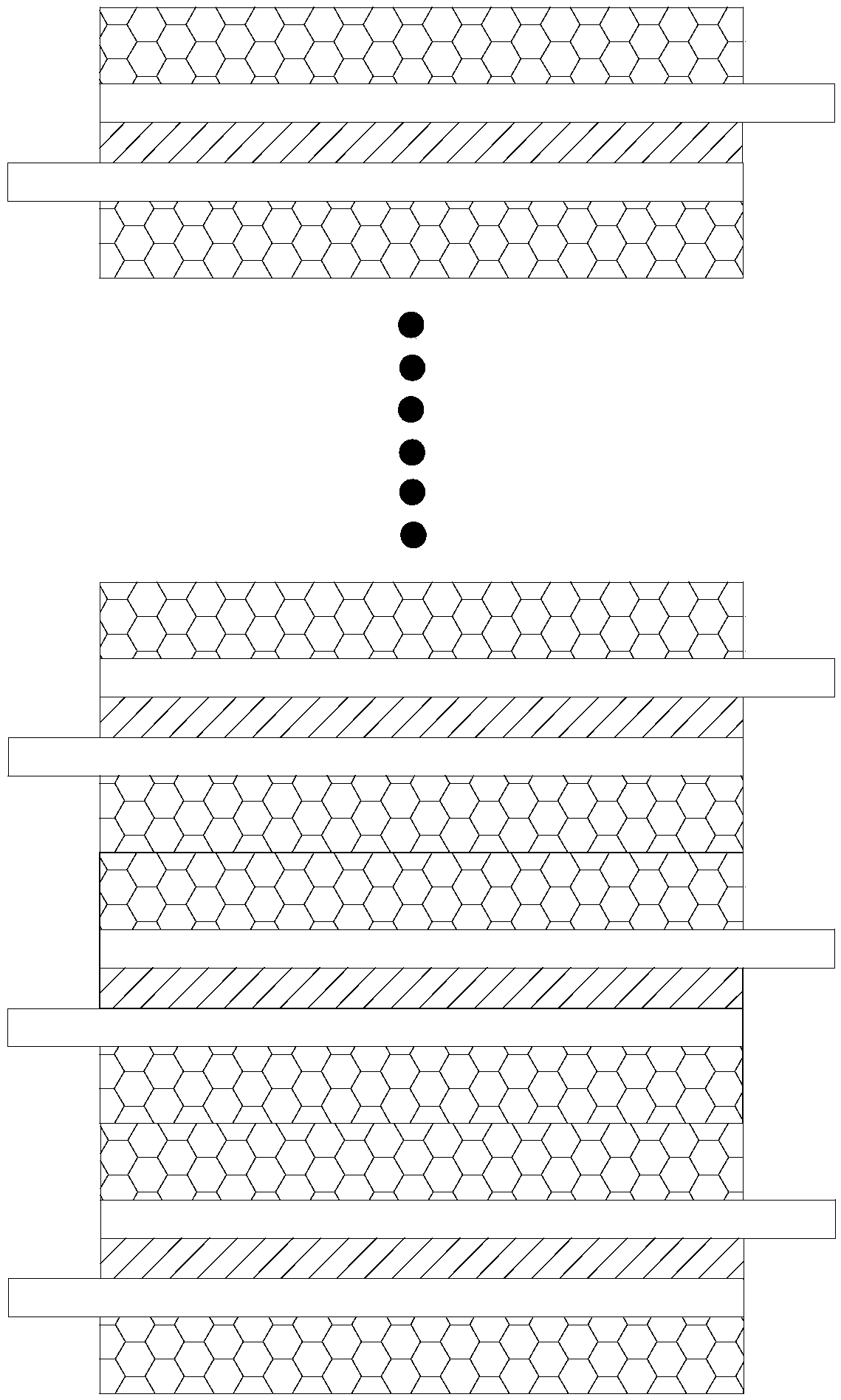

Preparation method of series-parallel thin film battery assembly

ActiveCN106098809AIncrease power generationLower internal resistanceFinal product manufactureSemiconductor/solid-state device manufacturingLaser etchingPower station

The invention discloses a preparation method of a series-parallel thin film battery assembly. The method is mainly characterized in that a piece of TCO conductive glass is equally divided into two parts, which are the same in area, through a laser etching line, wherein the two parts are a series conductive portion and a parallel conductive portion, the series conductive portion is used for carrying out laser scribing on series sub-batteries, the parallel conductive portion is used for carrying out laser scribing on parallel sub-batteries, the series sub-batteries and the parallel sub-batteries are respectively connected by using a drainage strip and a bus bar, and then the series conductive portion and the parallel conductive portion are connected so as to manufacture the required series-parallel thin film battery assembly. According to the preparation method disclosed by the invention, a defect that the film uniformity is poor after large-area film plating is considered, characteristics of a series circuit and a parallel circuit are combined, and problems brought about by film difference and series connection of the sub-batteries are solved. Optimization for electrical parameters is carried out in allusion to a characteristic of high voltage or high current in the electrical parameters of a thin film battery, thereby avoiding influences imposed on such factors as inverter model selection and power station design in power station construction in a later period.

Owner:ZHONGSHAN RUIKE NEW ENERGY CO LTD

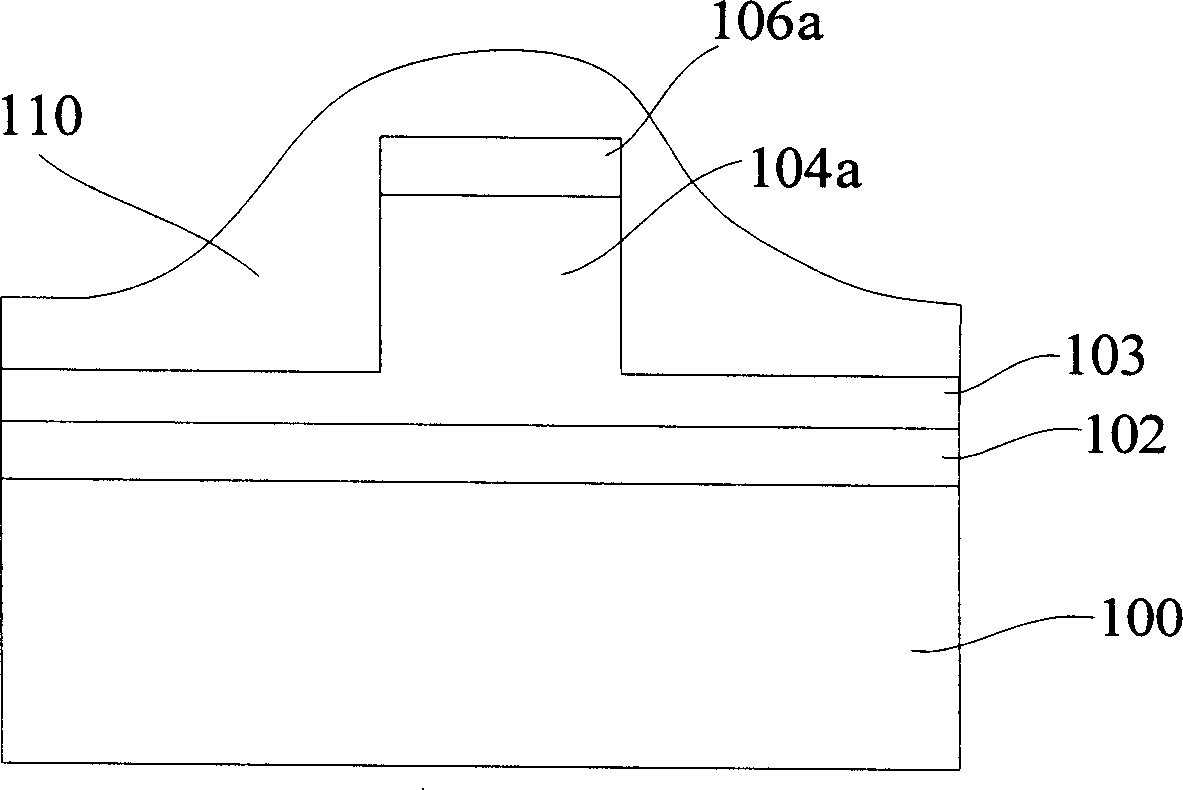

Grids and method of manufacture

InactiveCN101192522AImprove electrical performance parametersImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesResistElectrical conductor

The invention relates to a method for manufacturing a grid. The method includes the following steps: a fundus of a semiconductor is provided; a first dielectric layer is generated on the fundus of the semiconductor; at least one second dielectric layer is generated on the first dielectric layer; a groove is generated between the first dielectric layer and the second dielectric layer, and the bottom of the groove exposes the surface of the fundus; the second dielectric layer is removed; an conductive layer is generated both in the groove of the first dielectric layer and on the first dielectric layer; an optical resist layer is reelingly coated on the conductive layer, and a graphic presentation is carried out to generate a grid graph which is arranged above the groove of the first dielectric layer; the conductive layer and the first dielectric layer which are not covered by the grid graph are removed in a corrosion way. The method can control the generated linewidth on the bottom of the grid more accurately.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Back emitter junction back-surface tunnel oxidation and passivation contact efficient battery production method

InactiveCN106784129AReduce surface recombinationImprove electrical performance parametersFinal product manufacturePhotovoltaic energy generationSlurryEngineering

The invention relates to a back emitter junction back-surface tunnel oxidation and passivation contact efficient battery production method, comprising: removing the damage layer of a silicon wafer and making velvets; and then performing edge insulation and back polishing; growing an ultra-thin tunnel oxide layer SiO2 on the back of the silicon wafer; using the PECVD method or other CVD methods to grow a B-doped polysilicon layer on the ultra-thin tunnel oxide layer SiO2; depositing an aluminum oxide layer on the surface of the B-doped polysilicon layer; growing a hydrogenated amorphous silicon nitride passivation antireflective layer on the front surface of the silicon wafer; and finally, printing Ag slurry on the front surface of the silicon wafer to form an all-aluminum back-field A1-BSF structure at the back surface. Compared with the prior art, the method could replace the N type back emitter crystalline silicon battery back point contact mechanism through the utilization of an ultra-thin tunnel oxide layer SiO2 and a B-doped polysilicon layer. Such a composed layer could greatly reduce the composition of the back surface metal and the semiconductor surface.

Owner:SHANGHAI SHENZHOU NEW ENERGY DEV

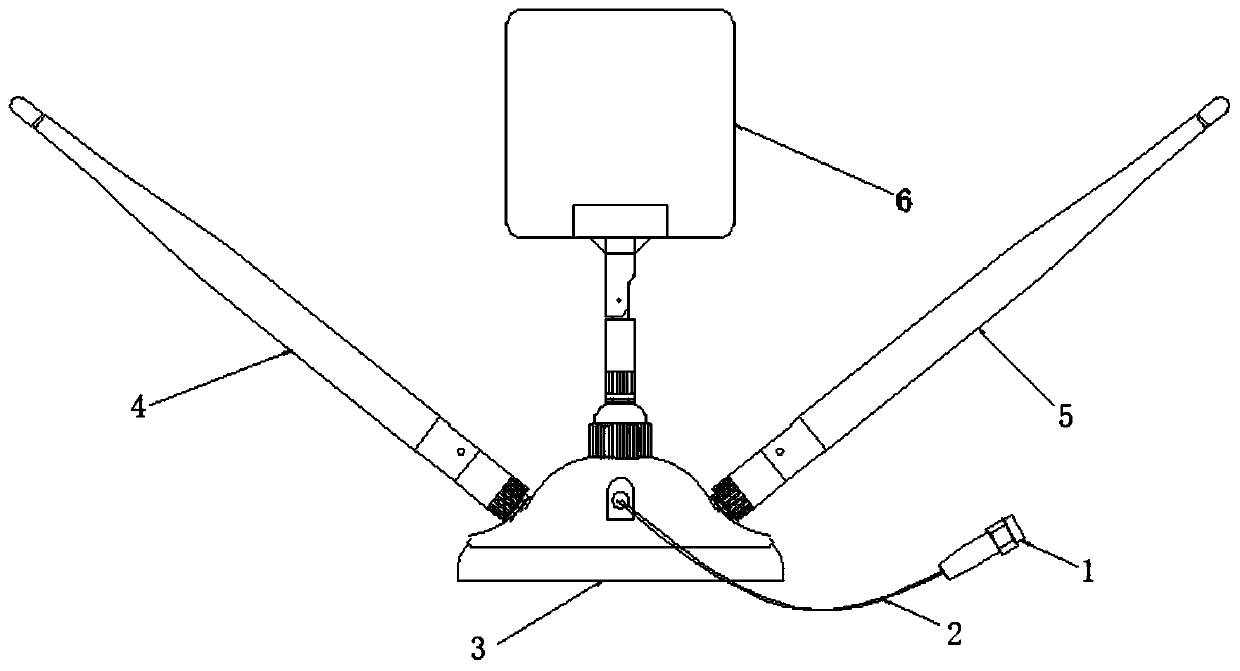

Terminal antenna used in wireless local area network

ActiveCN109728411AImprove electrical performance parametersHigh bandwidthSimultaneous aerial operationsAntenna supports/mountingsEngineeringComputer terminal

The invention discloses a terminal antenna used in a wireless local area network. The terminal antenna comprises a radio frequency connector, a feeding cable, a suction cup base, a 2.4G band antenna,a 5G band antenna and a combiner. The left side of the suction cup base is provided with a mounting screw and is fixedly installed with the 2.4G band antenna, the right side of the suction cup base isprovided with a mounting screw and is fixedly installed with the 5G band antenna, the top portion of the suction cup base is provided with a mounting screw and is fixedly installed with the combiner,the combiner is internally provided with a frequency division unit circuit board, the frequency division unit circuit board is provided with a 2.4G band feed connection, a 2.4G band grounding connection, a 5G band feed connection and a 5G band grounding connection, and the 2.4G band antenna and the 5G band antenna are welded and fixed with the output end of the frequency division unit circuit board through respective connection cables. The volume is small, the weight is light, the anti-interference ability is strong, the frequency band is wide, the gain is high, and the radiation performanceindex is good.

Owner:GUANGZHOU CREKING COMM TECH

Solar panel preparing method

ActiveCN102315309AImpurities are simpleSolve the problem of impuritiesFinal product manufacturePhotovoltaic energy generationOptoelectronicsSolar battery

The invention provides a solar panel preparing method, which comprises the steps of: a, preparing a-Si:H film on the surface of a silicon chip after texturing; b, treating the silicon chip containing the a-Si:H film on the surface obtained in the step a at 800 to 900 DEG C for 60 to 120 min; and c, carrying out corrosion treatment on the surface of the silicon chip treated through high temperature. The solar panel preparing method has the advantages that a layer of a-Si:H film is deposited on the back surface of the silicon chip after the texturing, the problems of many impurities and micro defects in the silicon chip can be perfectly solved, the electrochemical performance such as the service life, the photoelectric conversion efficiency and the like of solar panels is improved, in addition, good back side and body passivation effects can be realized, the current and voltage (I-V) character of solar batteries is improved, and simultaneously, the process is simple and is easy to implement.

Owner:BYD CO LTD

Method for improving thick metal layer LIFT OFF technology pattern abnormality

ActiveCN109461652AAvoid glue collapseReduce stressSemiconductor/solid-state device manufacturingEvaporationEngineering

The invention belongs to the technical field of a semiconductor integrated circuit technology, and relates to a method for improving thick metal layer LIFT OFF technology pattern abnormality, and specifically is photoresist coating-photoresist exposure-photoresist developing-thick metal layer deposition-blue film attachment, blue film stripping-photoresist stripping. According to a LIFT OFF technology provided by the invention, in a process of metal deposition, collapse of the photoresist is avoided through a low temperature technology, a multi-evaporation technology with slow-speed of revolution is used, and in combination with a blue film assistant stripping method, thickness of the photoresist is reduced, moreover, pattern abnormality caused by collapse of a relatively thick metal layer(more than 3 microns) on the photoresist and cracks of the photoresist is avoided, and consequently, the thick layer LIFT OFF technology is realized.

Owner:WUXI ZHONGWEI JINGYUAN ELECTRONIC CO LTD

Preparation method of epitaxial wafer for 8-inch high-power IGBT component

ActiveCN108417483AImprove controllabilityImprove consistencySemiconductor/solid-state device manufacturingSemiconductor devicesHigh resistanceControllability

The invention discloses a preparation method of an epitaxial wafer for an 8-inch high-power IGBT component. The method includes following steps: preparing a substrate: selecting an 8-inch substrate with a p-doped middle resistance, wherein the resistivity is 3-25 ohm*cm, and a back-sealing structure is in a polycrystalline (Poly) back-sealing mode; HCl polishing: selecting the HCl flow of 1-2 L / min at the temperature lower than 1080 DEG C with the polishing time of 2 minutes, and performing purging with high-flow H2 for 3 minutes after completion of polishing; and epitaxial growth: selecting at least three layers of epitaxial process conditions, wherein a silicon source employs ultra-high-purity trichlorosilane, the epitaxial growth of each layer employs the same growth temperature and growth rate, an epitaxial layer with flat resistivity is grown on a first layer, an intermediate transition layer is grown on an intermediate layer through introduction of a doping source with a variabledoping flow, and a high-resistance epitaxial layer is grown on a final layer. According to the method, the growth of the epitaxial layer of each layer employs the same growth rate and growth temperature so that the controllability of epitaxial parameters of products in a batch production process is facilitated.

Owner:NANJING GUOSHENG ELECTRONICS

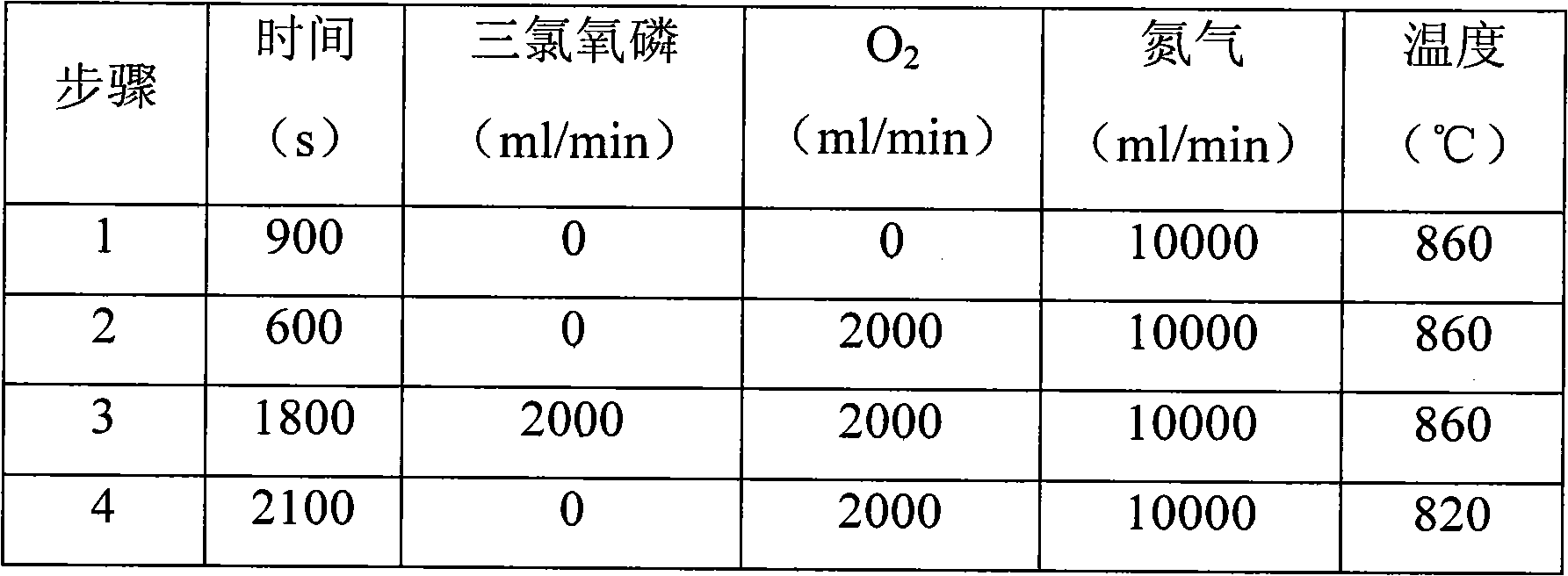

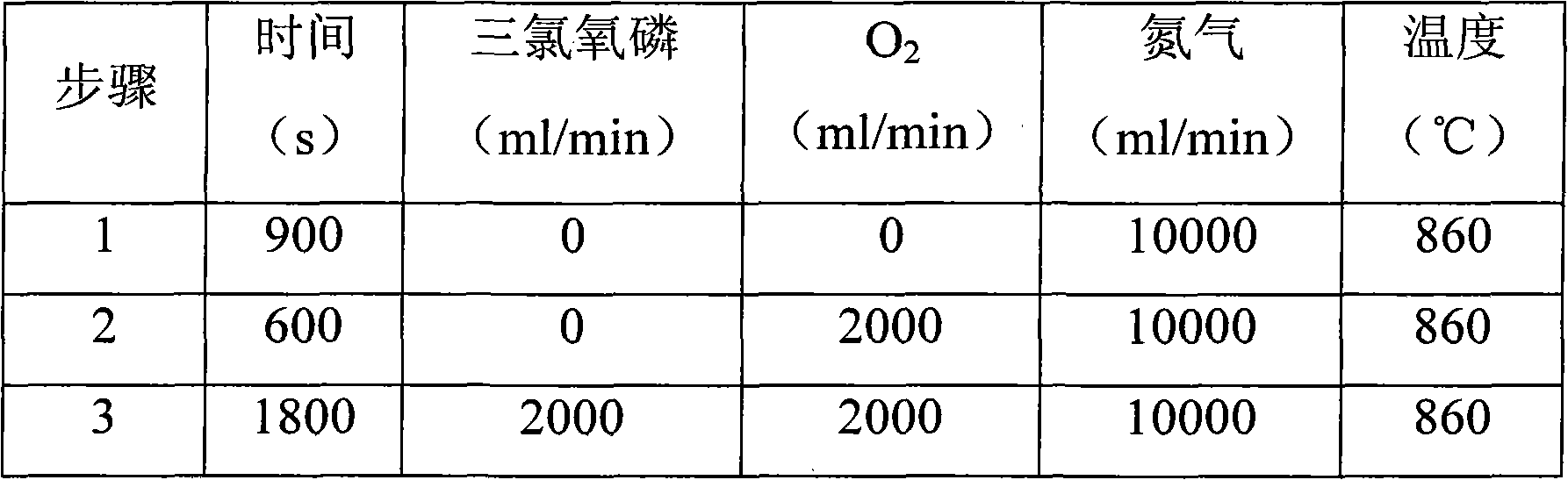

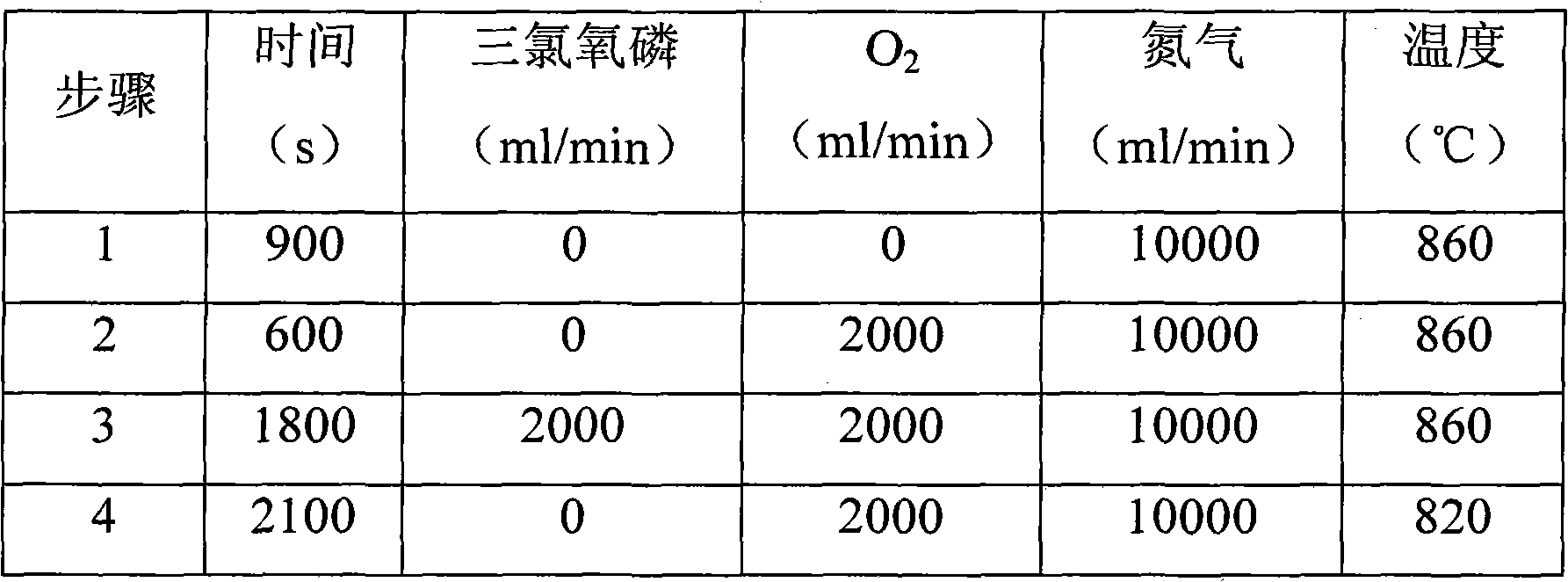

Phosphorus gettering process of silicon chip

InactiveCN101667605BImprove electrical performance parametersIncreased average life expectancyFinal product manufactureSemiconductor devicesEtchingSurface oxidation

The invention relates to a phosphorus gettering process of silicon chips in the manufacture of solar cells, which comprises the following steps: putting sueded silicon chips into a diffusion furnace for pre-deposition, removing a phosphorosilicate glass layer after diffusion, soaking the silicon chips through distributed processing in a hydrofluoric acid solution, and removing oxide layers from the surfaces of the silicon chips; then putting the silicon chips after washing into the diffusion furnace for secondary diffusion processing, taking the silicon chips out from the diffusion furnace after the processing of the secondary diffusion working procedure, cooling the silicon chips to room temperature, and measuring the square resistance of the silicon chips. The invention can effectively decrease heavily doped 'dead layers' and greatly prolong the average minority carrier lifetime of the silicon chips; after the processes including etching, PECVD, silk screen sintering and the like are finished according to the normal process of a cell chip, the average transformation efficiency of the made cell chip is further improved, and the cell chip has better electrical performance parameters.

Owner:无锡尚品太阳能电力科技有限公司

Ohmic contact electrode, HEMT device and preparation method

InactiveCN109712877AImprove contact uniformityReduce the formation temperatureSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactOptoelectronics

The invention provides an ohmic contact electrode, an HEMT device and a preparation method, and the preparation method comprises the following steps: S1, defining a source-drain ohmic contact window by photoetching; S2, etching an ohmic contact area of AlGaN to a certain thickness; S3, sequentially depositing metal layers in the source-drain region; S4, carrying out alloy annealing treatment by adopting a microwave radiation process after degumming and stripping to form the ohmic contact electrode provided by the invention. According to the preparation method of the ohmic contact electrode, the deposited metal layer is processed in a microwave annealing mode, the formation temperature of the GaN ohmic contact resistor can be reduced, the ohmic contact uniformity is improved, and the electrical parameters and the working reliability of a GaN power device are improved.

Owner:ZHANGJIAGANG EVER POWER SEMICON

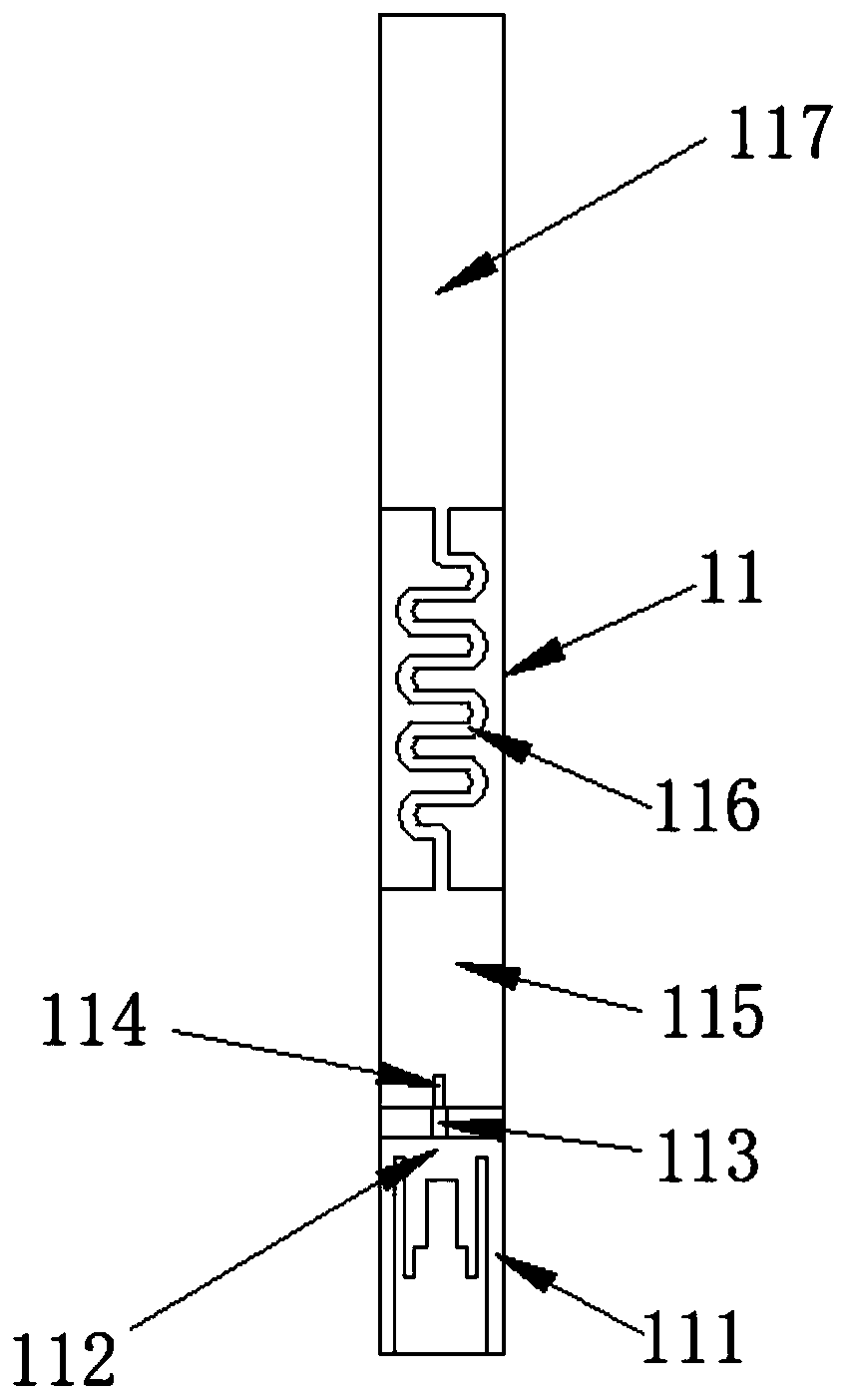

High-vacuum surface-mounted miniature tuning fork quartz crystal resonator and manufacturing method thereof

PendingCN111917395AGood sealing performanceIncrease vacuumImpedence networksSeam weldingQuartz crystal resonator

The invention relates to a high-vacuum surface-mounted miniature tuning fork quartz crystal resonator and a manufacturing method thereof. The resonator comprises a ceramic base, a miniature tuning fork wafer and a metal cover plate; the ceramic base is formed by sequentially superposing a ceramic bottom plate, a ceramic backing plate, a ceramic ring plate and a kovar alloy ring from bottom to top,wherein the bottom of the ceramic bottom plate is provided with a metal pad, and a left protruding bonding pad and a right protruding bonding pad are arranged on the ceramic backing plate. The resonator is manufactured through a high-vacuum baking degassing process, a sealing nitrogen parallel seam welding process and a high-vacuum laser spot welding process. The manufacturing method is simple and rapid, and the manufactured resonator is reliable in quality, long in service life and excellent in electrical performance.

Owner:HUBEI TKD ELECTRONICS TECH

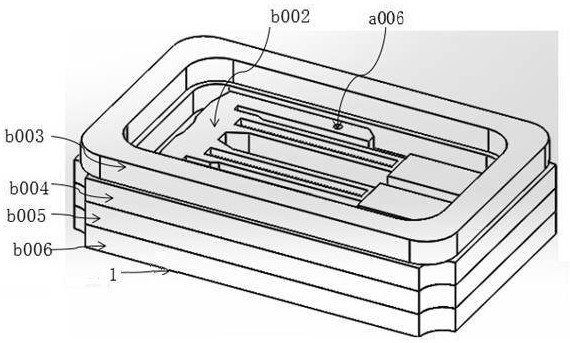

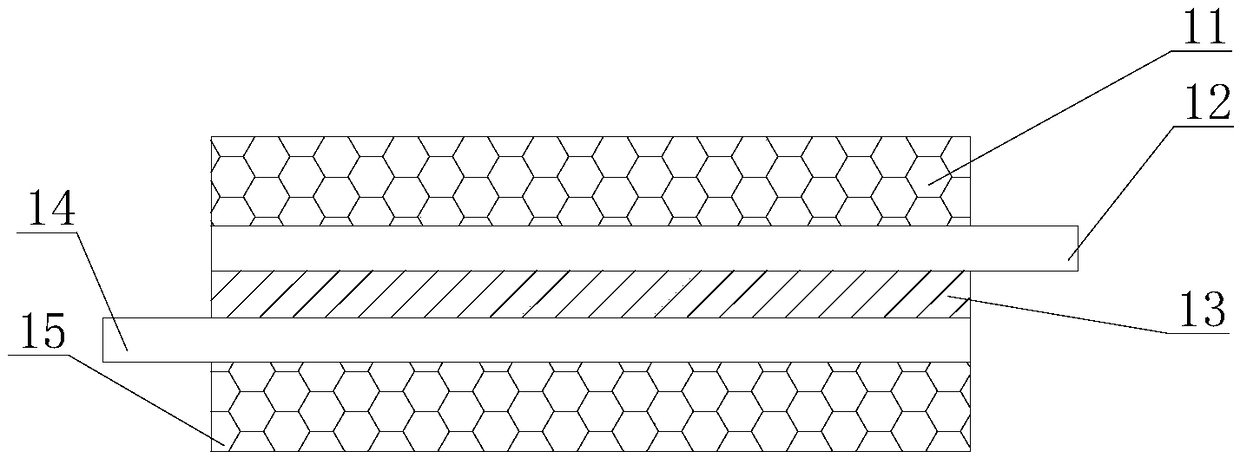

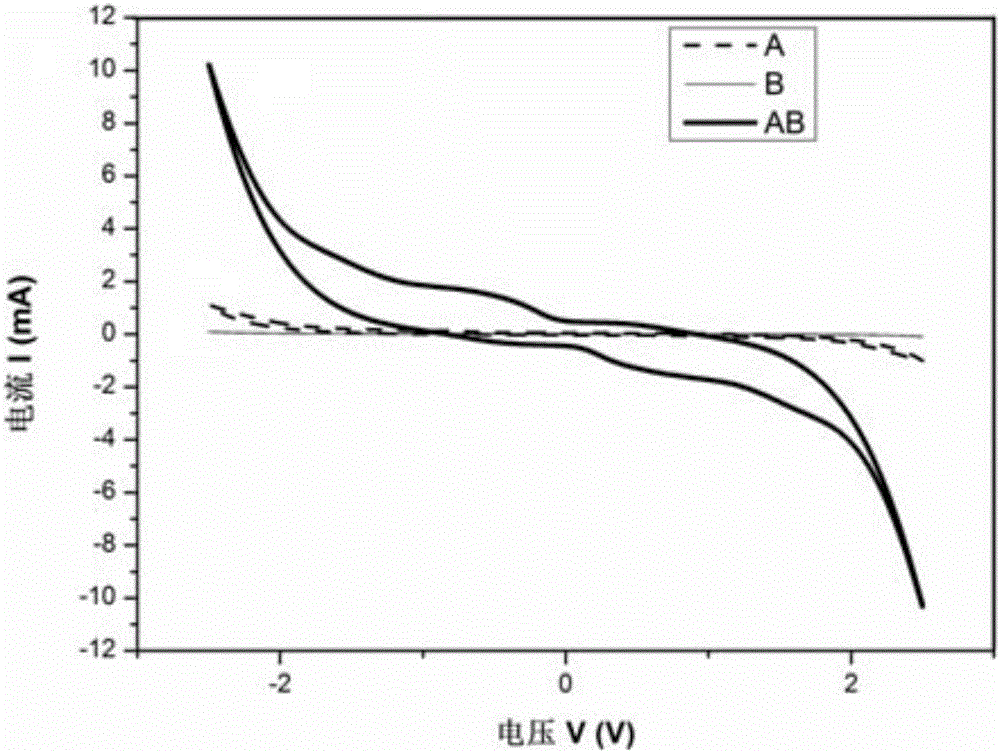

A kind of sheet laminated all-solid-state supercapacitor and preparation method thereof

ActiveCN106847521BImprove electrical performance parametersImprove mobilityMultiple hybrid/EDL capacitorsHybrid/EDL manufactureEpoxySupercapacitor

The invention relates to a sheet-shaped laminated full-solid super capacitor and a preparing method. The sheet-shaped laminated full-solid super capacitor comprises a full-solid super capacitor core and a housing, the top side of the housing is provided with a rectangular blind hole, the inner side wall of the rectangular blind hole is coated with conductive silver pulp, the upper surface of the housing is also provided with the conductive silver pulp, the full-solid super capacitor core is arranged in the rectangular blind hole in a clamped mode, the upper surface of the full-solid super capacitor core is provided with an encapsulating layer, and conductive silver pulp at the two sides of the top side of the housing is connected to an electrode lead. The preparing method of the sheet-shaped laminated full-solid super capacitor comprises the steps of 1, preparing the full-solid super capacitor core, 2, upwards folding and pressing aluminum foils at the two sides of the full-solid super capacitor core to cover the side face, 3, coating the conductive silver pulp, 4, welding the electrode lead, 5, putting the full-solid super capacitor core into the rectangular blind hole; 6, adding epoxy resin into the rectangular blind core to form an epoxy resin encapsulating layer, so that the sheet-shaped laminated full-solid super capacitor is obtained after being cured.

Owner:胡英 +1

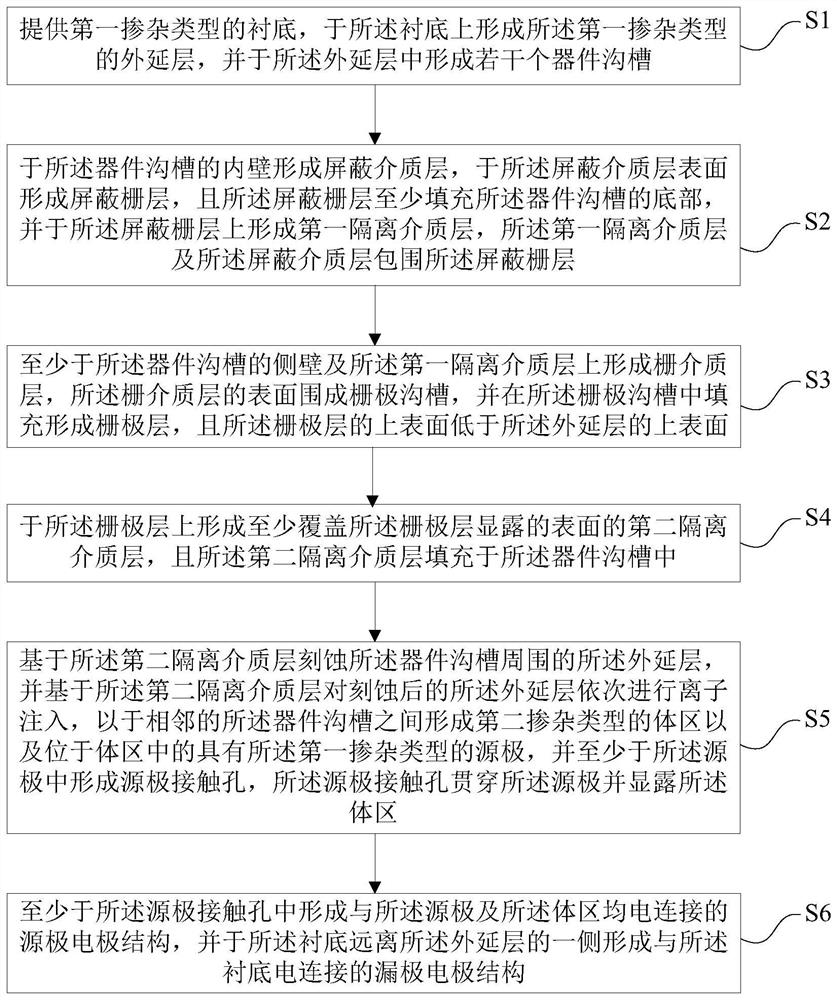

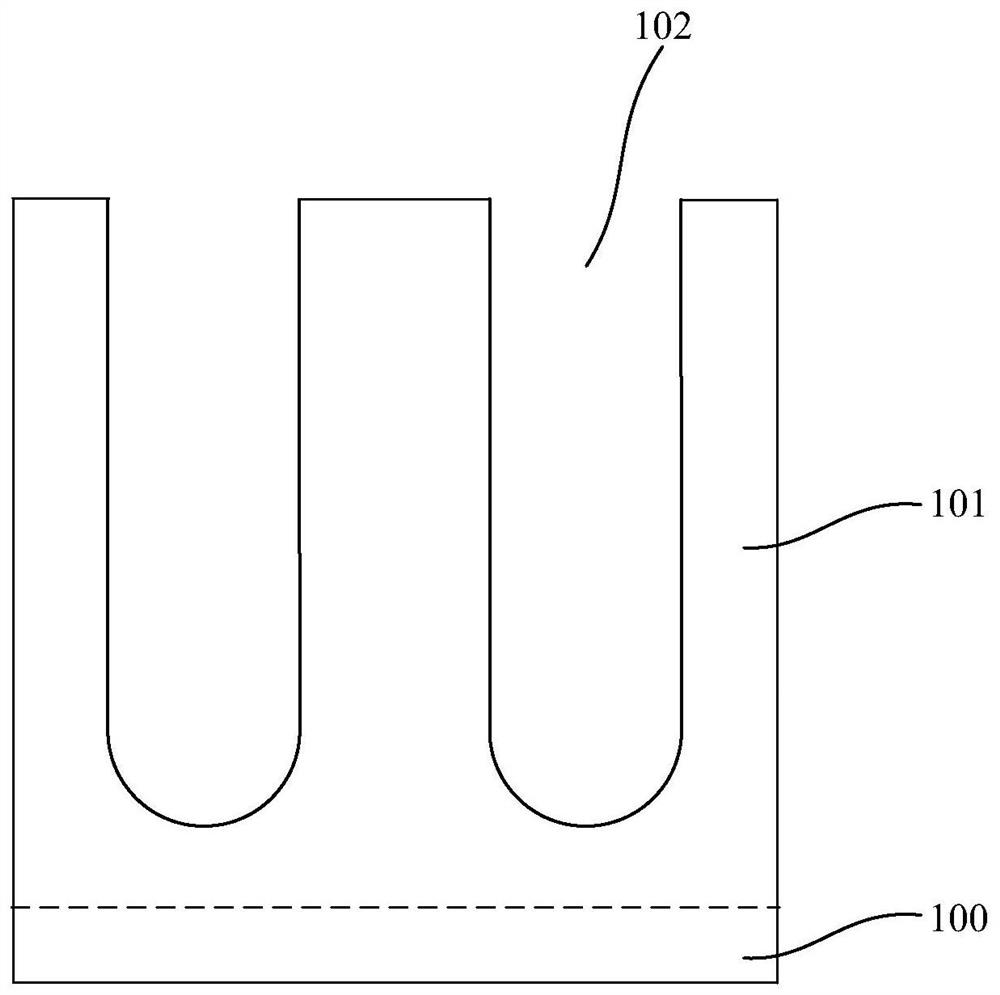

Groove type field effect transistor structure and preparation method thereof

ActiveCN112864018ALower channel resistanceReduced characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

Owner:CHINA RESOURCES MICROELECTRONICS (CHONGQING) CO LTD

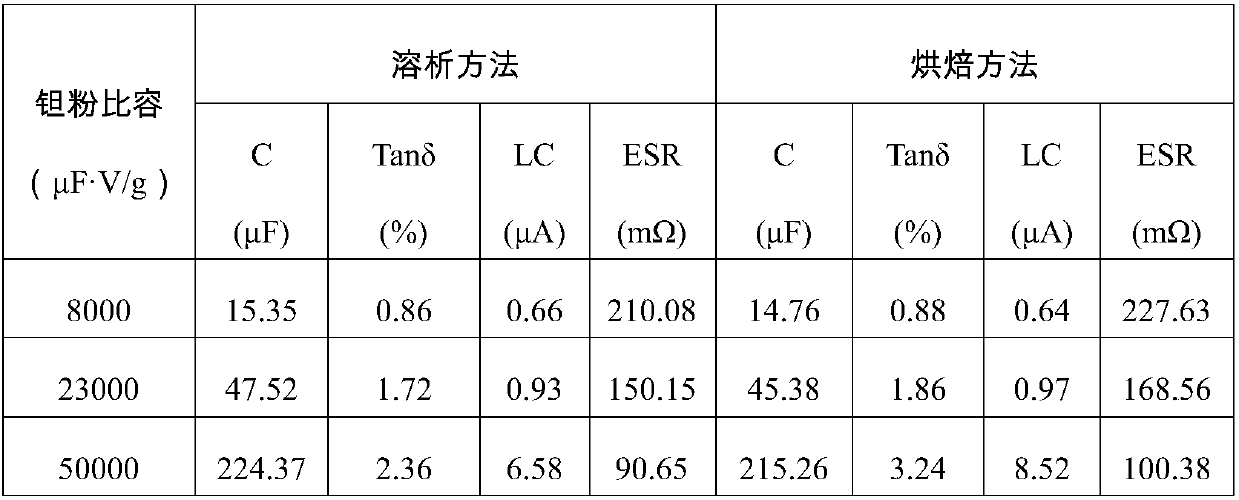

Method for removing adhesive in anode block of solid electrolytic capacitor

ActiveCN107680809AClean removalImprove electrical performance parametersSolid electrolytic capacitorsElectrolytic capacitor manufacturePorosityElectrolysis

The invention belongs to the technical field of manufacturing of electrolytic capacitors, and particularly discloses a method for removing an adhesive in an anode block of a solid electrolytic capacitor. Treatment is carried out through the following 11 steps of dissolving, spaying, drying, compression, reciprocating sifting, first elution, standing, second elution, third elution, boiling and drying in all, so that the adhesive and a solvent can be removed clean without a residue, improvement of electric performance parameters of the capacitor is facilitated, meanwhile, fine powder particles blocked in micropores and powder particles adhered to the surface of an anode blank are also burst through, the capacity extraction rate of the capacitor is improved, and the probability of crystallization when an anode is formed is reduced. According to the method, increase of the content of impurities of carbon and oxygen in the tantalum blank is effectively suppressed, the porosity in the tantalum blank is improved and the stability and the reliability of the tantalum electrolytic capacitor are improved.

Owner:CHINA ZHENHUA GRP XINYUN ELECTRONICS COMP ANDDEV CO LTD

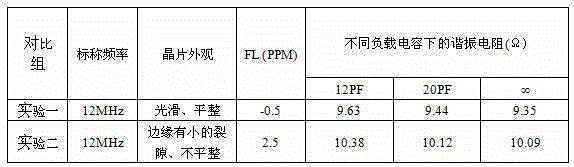

Processing method for manufacturing crystal base plate of quartz-crystal resonator

ActiveCN105141271AImprove electrical performance parametersReduce spreadImpedence networksQuartz crystal resonatorElectricity

The invention discloses a processing method for manufacturing a crystal base plate of a quartz-crystal resonator. The processing method comprises steps of using chemical solvent to process and erode the crystal base plate according to preset size of erosion area and erosion time, thereby achieving that thickness of a designated area of the crystal base plate is changed according to preset design and form, and achieving the edge chamfering effects of chemical erosion; and then manufacturing the crystal resonator. The chemical solvent is hydrogen fluoride NH4HF2 solution. Segmentation and partition erosion can be used in the method, and the method is characterized by low cost, short time, controllable surface damage and less loss. As a novel quartz-crystal processing technology and method, electrical performance parameters of the resonator can be improved. The processing method is characterized in that performance parameters of materials can be changed; the specific mode of the thickness or rigidity of the designed crystal plate is changed; energy trapping performance of the crystal resonator is achieved; and quite small shearing vibration on the edge of the crystal plate are ensured, thereby reducing diffusion of energy towards outside and achieving the objective to enhance shearing vibration.

Owner:JIANGSU HAIFENG ELECTRONICS

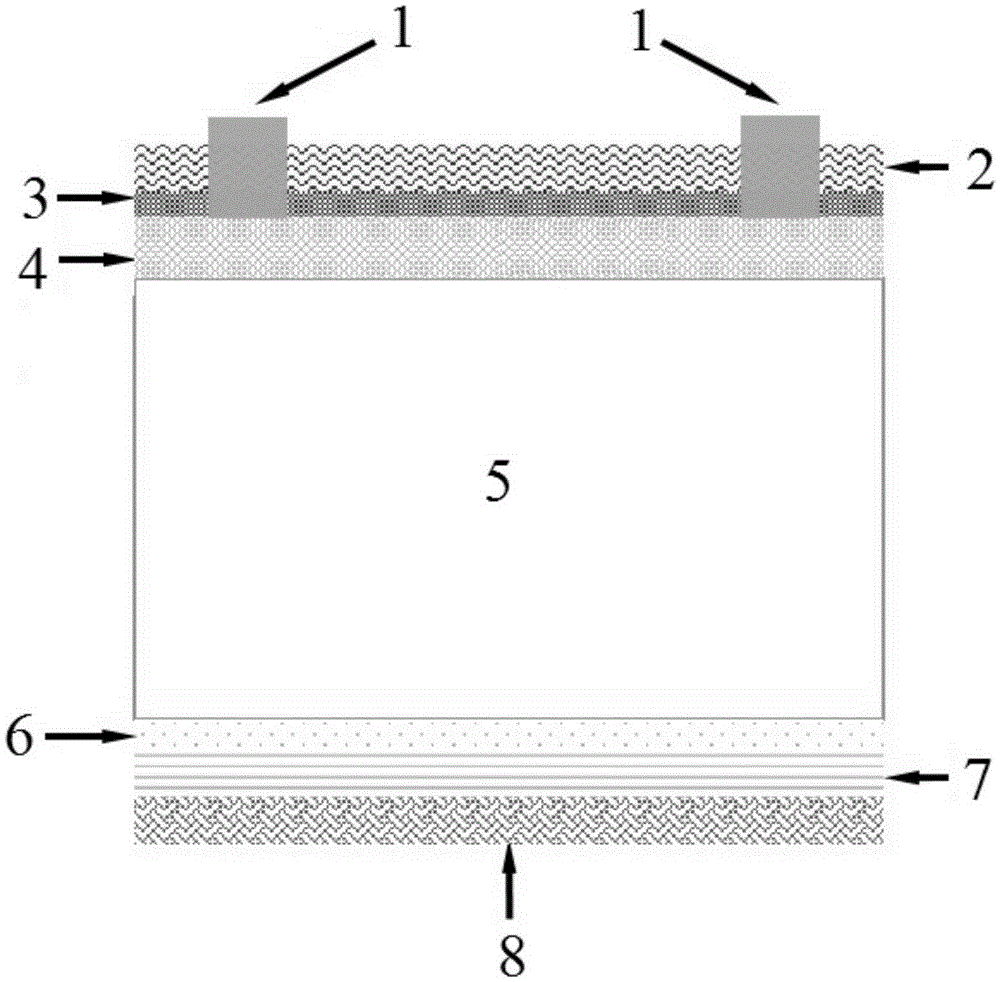

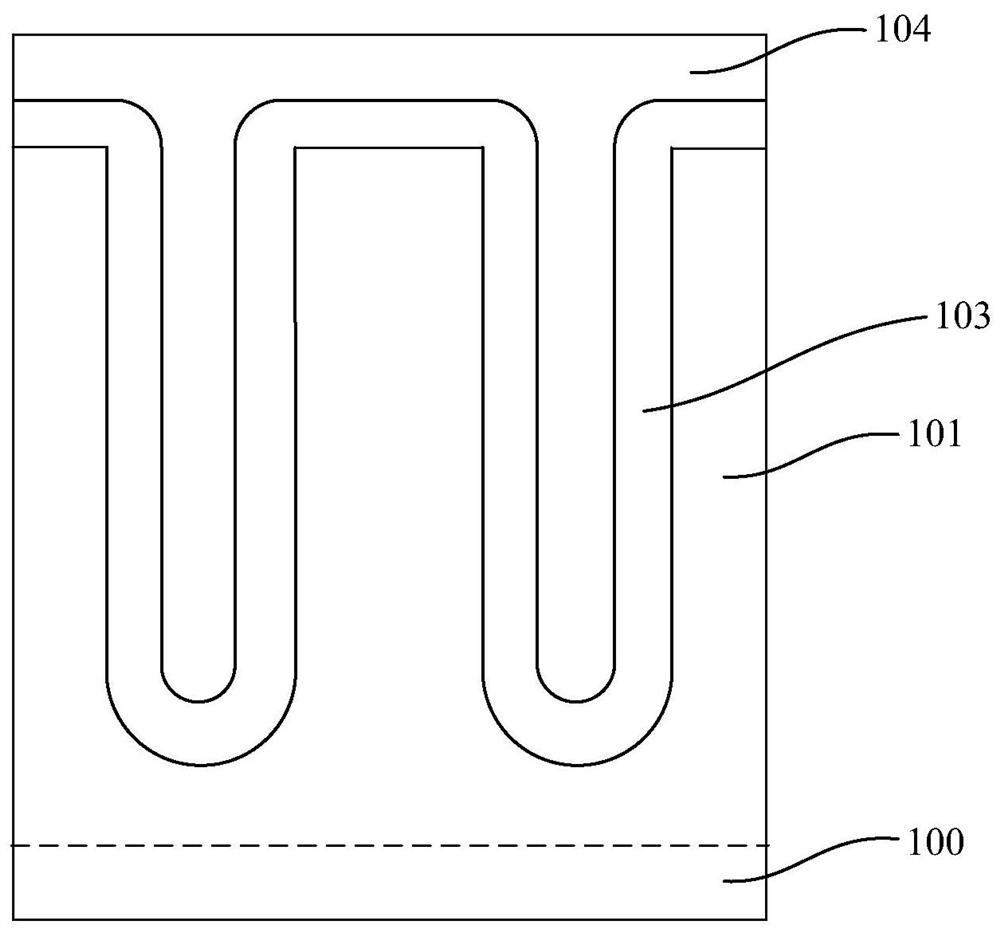

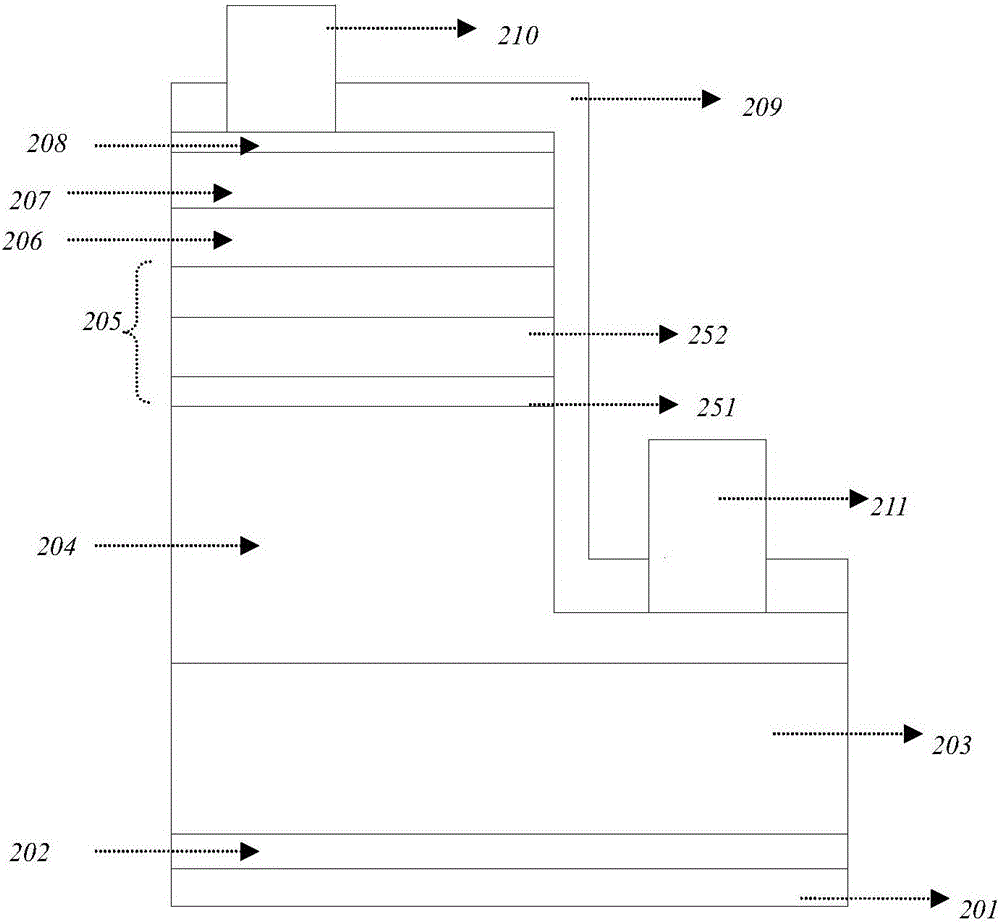

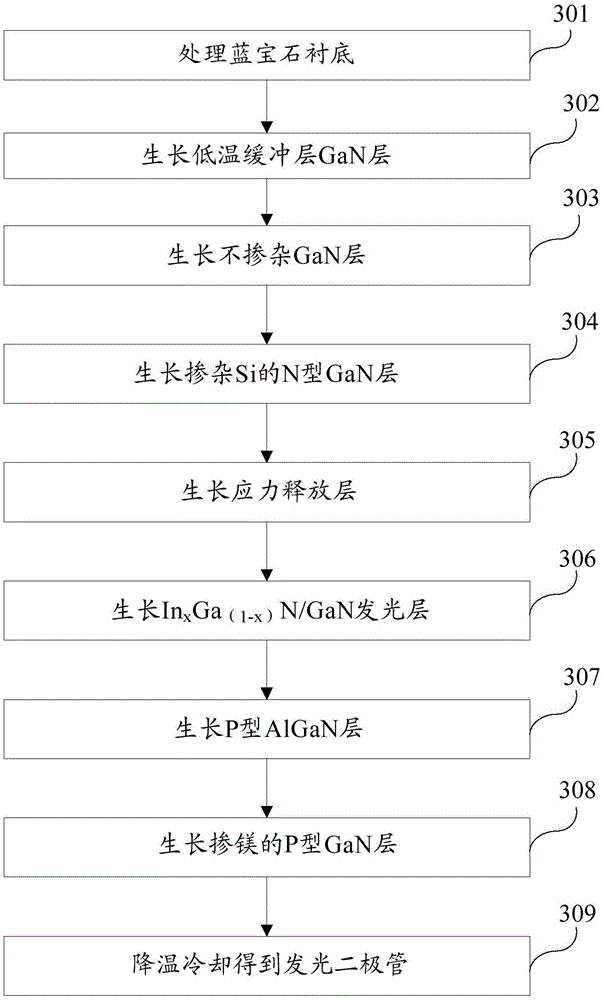

Epitaxial growth method for improving quality of LED

The invention discloses an epitaxial growth method for improving quality of an LED. The epitaxial growth method comprises the steps of processing a sapphire substrate, growing low temperature GaN buffer layers, growing undoped GaN layers, growing Si-doped N-type GaN layers, growing stress release layers, growing InxGa(1-x)N / GaN light-emitting layers, growing P-type AlGaN layers, growing Mg-doped P-type GaN layers, and cooling to obtain the LED; the epitaxial growth method for improving the quality of the LED solves the problem that the stress in the light-emitting layer is too large which leads to low luminous efficiency.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

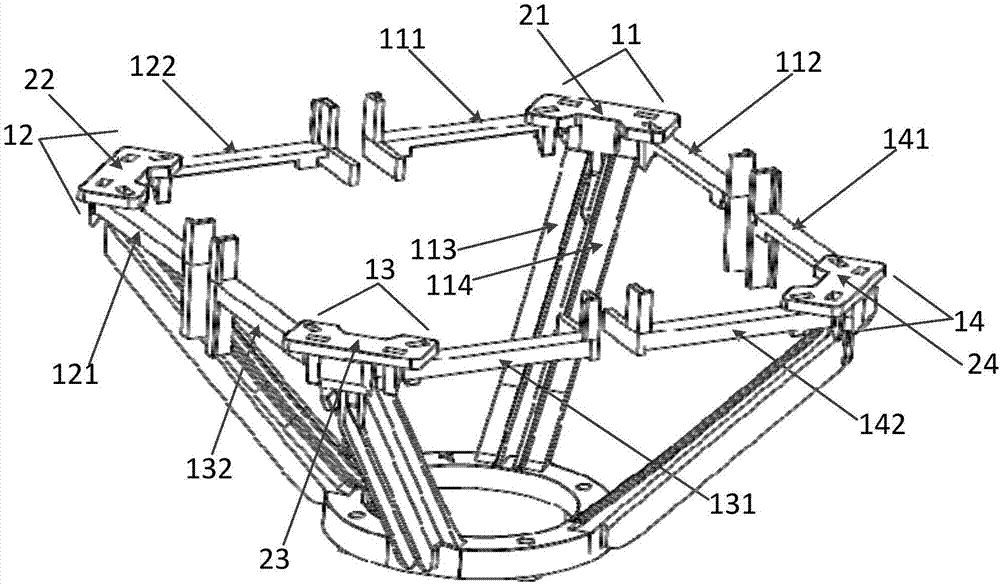

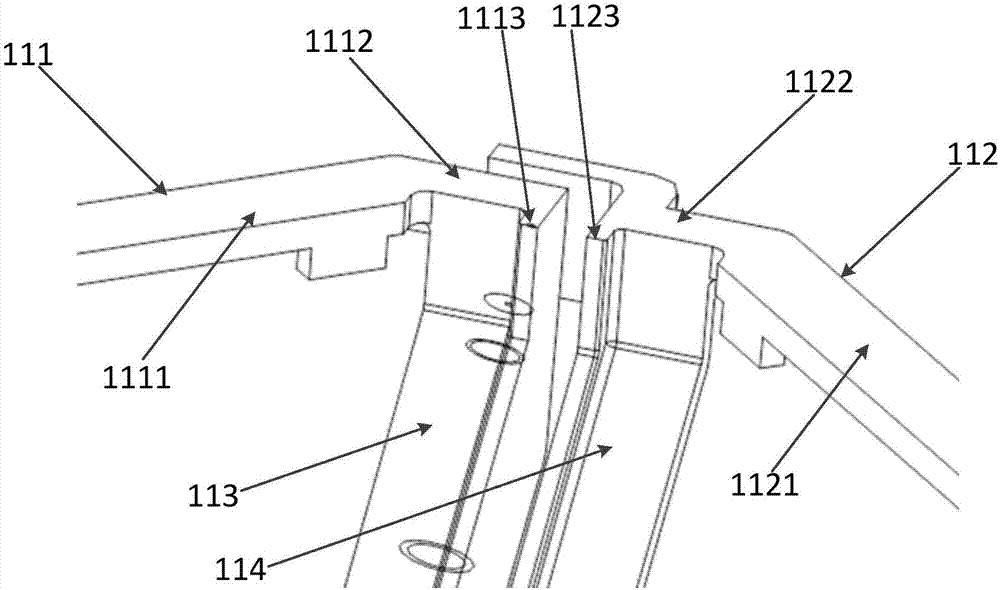

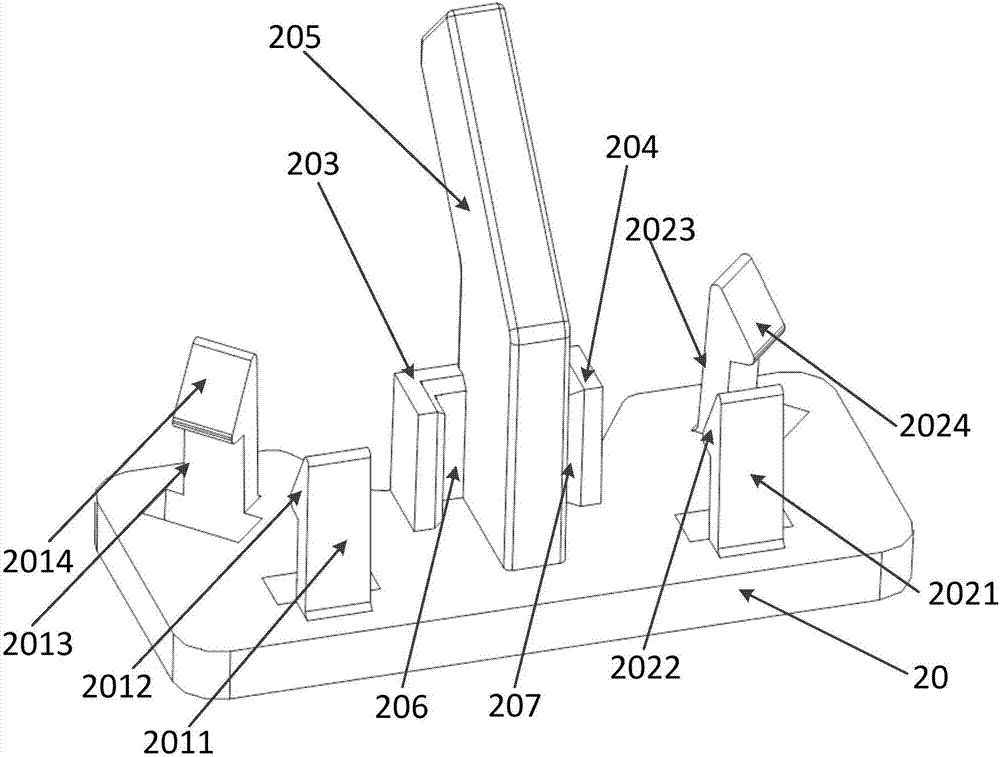

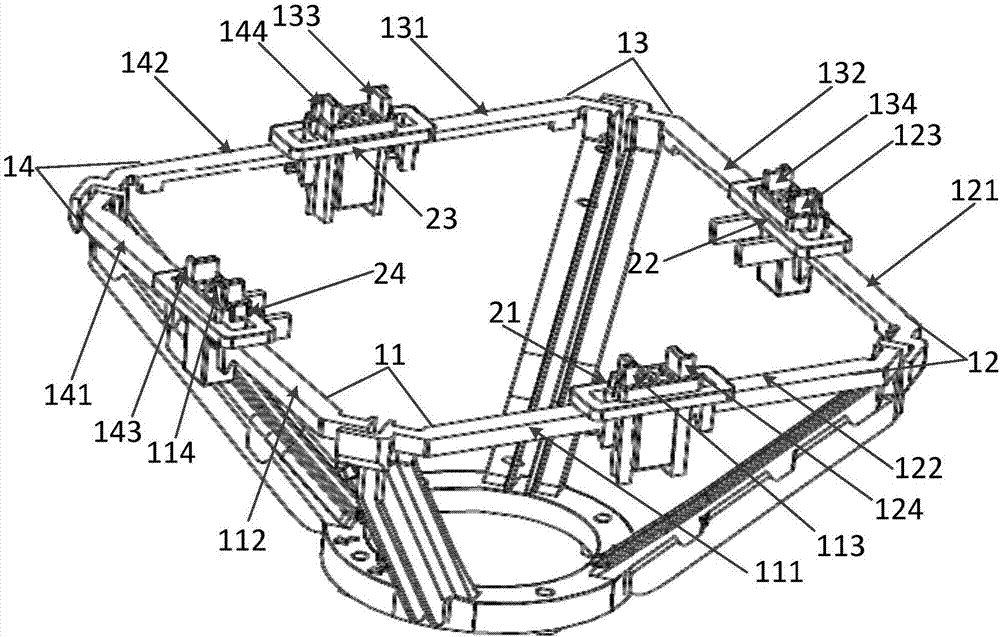

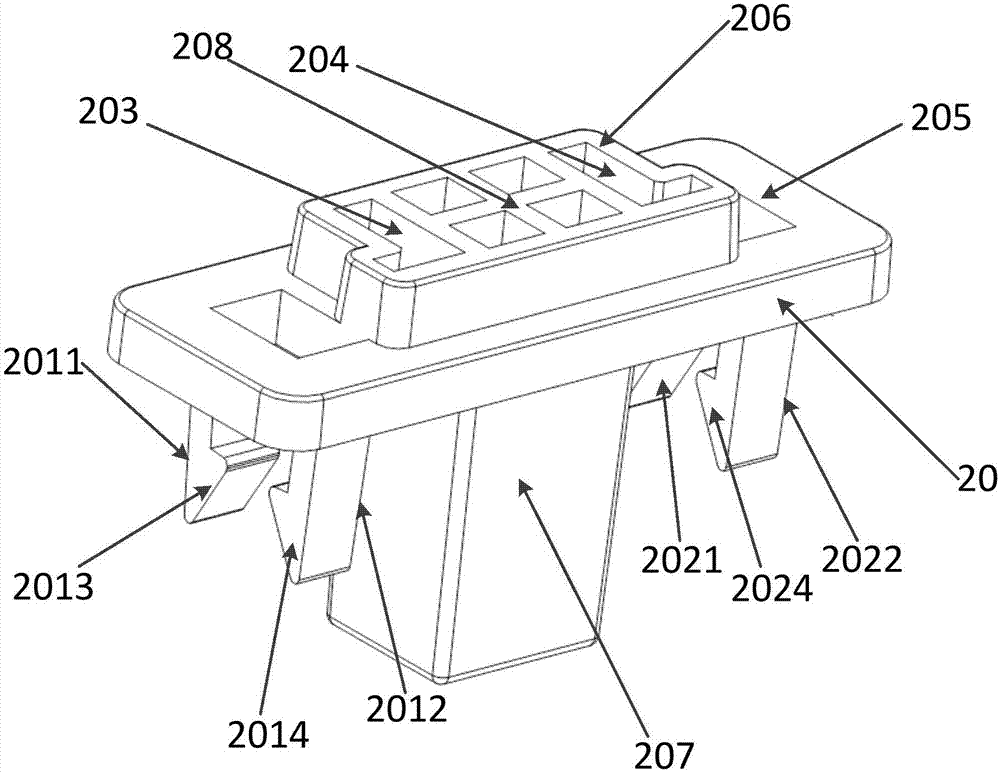

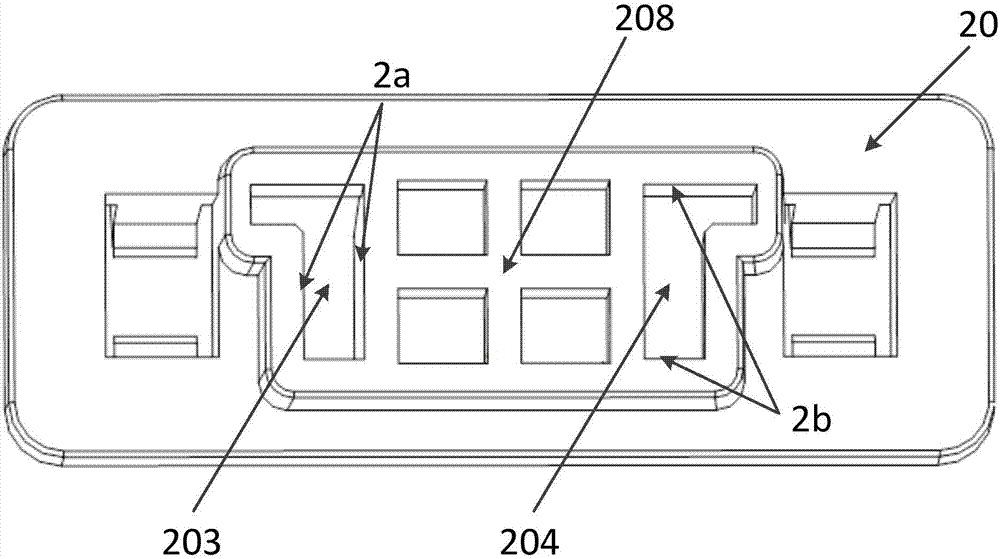

Radiation unit positioning clamp and low-frequency radiation unit

InactiveCN107516757AEasy to fixImprove electrical performance parametersAntenna supports/mountingsRadiating elements structural formsDipoleFastener

The invention discloses a radiation unit positioning clamp for connecting a first radiation arm and a second radiation arm in each dipole. The radiation unit positioning clamp comprises a base; the base is provided with a first inverted fastener and a third inverted fastener for being clamped and fixed on the first radiation arm; the base is also provided with a second inverted fastener and a fourth inverted fastener for being clamped and fixed on the second radiation arm; the base is also provided with a boss; the boss is provided with positioning grooves correspondingly matched with a first clamping part and a second clamping part; and the boss is clamped and fixed on the first radiation arm and the second radiation arm through match between the positioning grooves and the first clamping part and the second clamping part. By adopting the radiation unit positioning clamp provided by the embodiment of the invention, shape and position offset of the radiation arm can be effectively corrected from multiple directions, and reliable fixing and deformation correction roles are played for the radiation unit.

Owner:GCI SCI & TECH

Radiating element positioning clamp and low-frequency radiating element

InactiveCN107453033ASolve the lack of rigidityEffective correction of deformationRadiating elements structural formsAntennas earthing switches associationEngineeringRadiating element

The invention discloses a radiating element positioning clamp, which is used for connecting adjacent first radiating arm and second radiating arm which are located in different dipoles. The radiating element positioning clamp comprises a substrate, wherein the substrate is provided for a first undercut part and a second undercut part used for being clamped and fixed on the first radiating arm; the substrate is also provided with a third undercut part and a fourth undercut part used for being clamped and fixed on the second radiating arm; a first positioning through hole and a second positioning through hole are also arranged in the substrate, wherein the first positioning through hole is correspondingly matched with a first loading section and the second positioning through hole is correspondingly matched with a second loading section; and the substrate coats the first positioning through hole and the second positioning through hole therein. By adopting the radiating element positioning clamp disclosed by the embodiment of the invention, the shapes and the position deviations of the radiating arms of the radiating element can be effectively corrected from multiple directions, and reliable fixing and deformation correcting functions can be provided for the radiating element.

Owner:GCI SCI & TECH

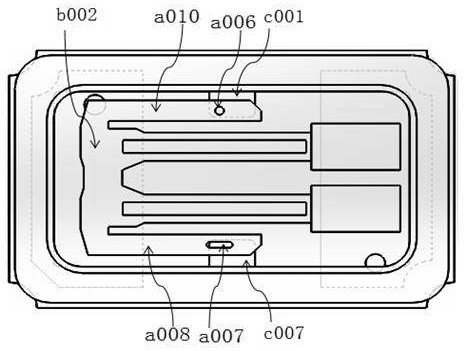

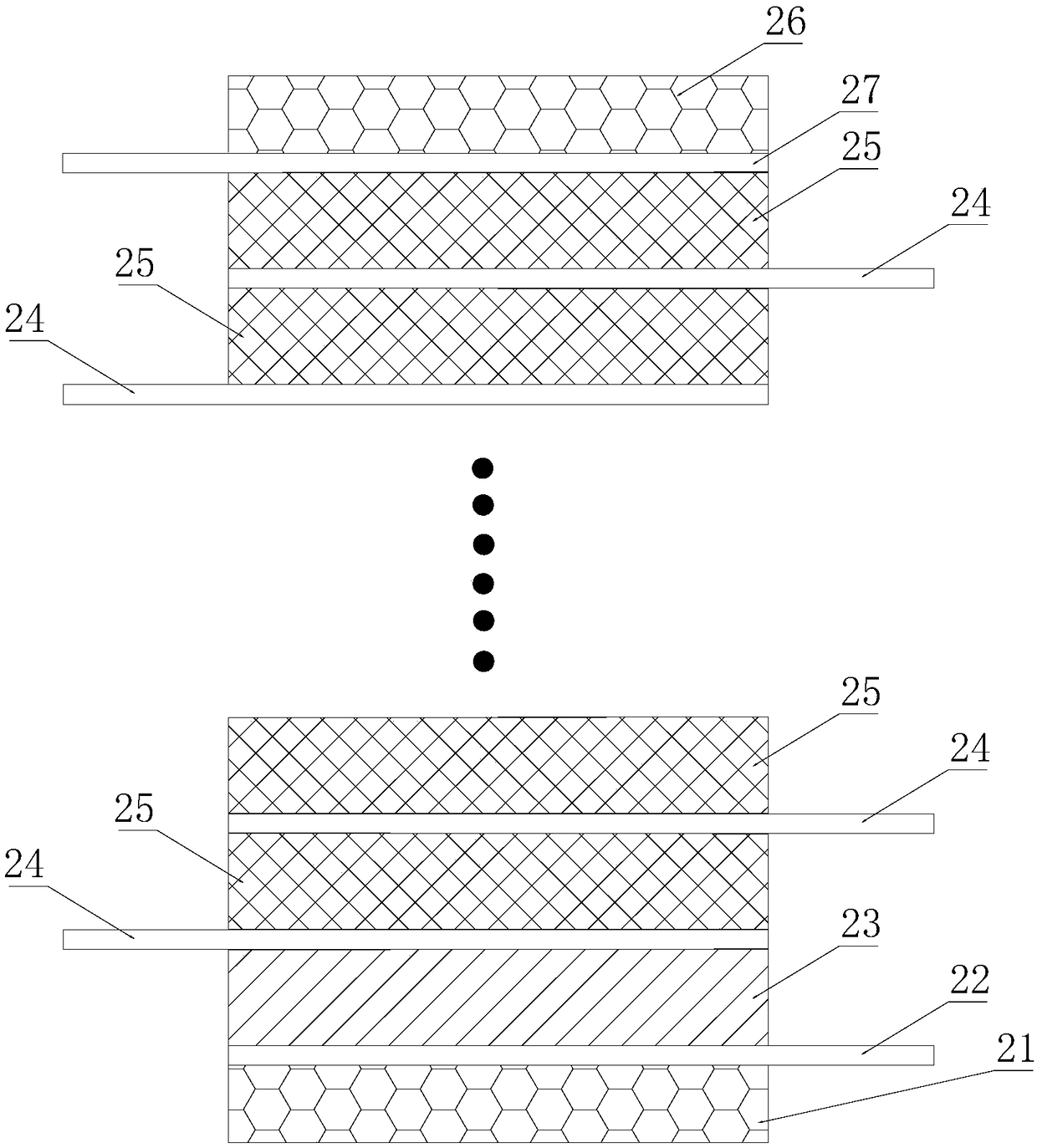

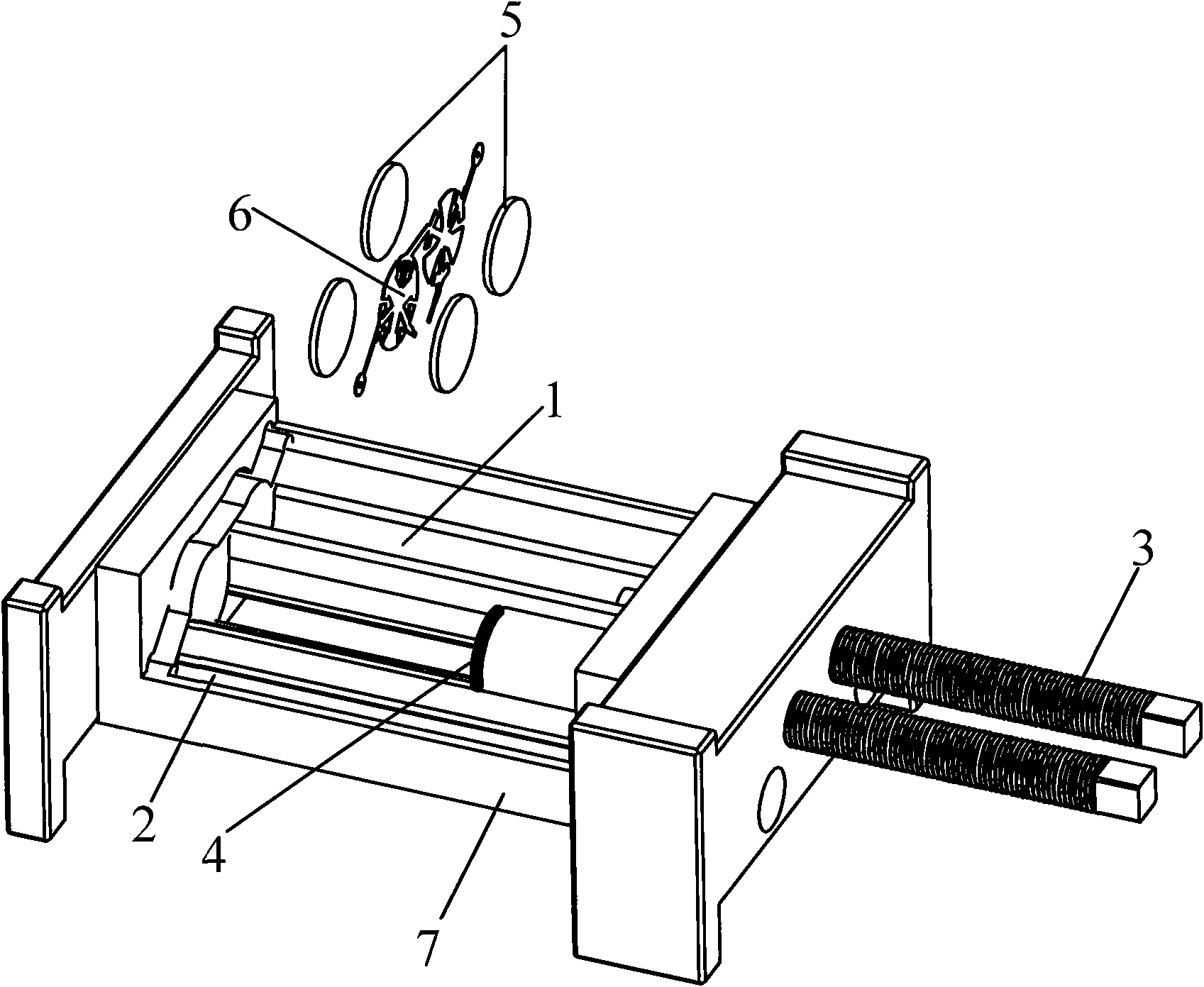

Winding type all-solid-state super capacitor and preparation method thereof

ActiveCN106783223AImprove electrical performance parametersOvercome the shortcomings of rigidity that cannot be coiledHybrid cases/housings/encapsulationsHybrid/EDL manufactureDielectricAll solid state

The invention relates to a winding type all-solid-state super capacitor and a preparation method thereof. The winding type all-solid-state super capacitor comprises bottom layer metal foil, a bottom layer metal foil coating, top layer metal foil, a top layer metal foil coating, a winding central spindle, a shell, a conductive silver paste coating, an electrode outgoing line and adhesive tape; the bottom layer metal foil, the bottom layer metal foil coating, the top layer metal foil, the top layer metal foil coating, the winding central spindle and the adhesive tape compose a winding type super capacitor core. The preparation method of the winding type all-solid-state super capacitor comprises the steps: 1, preparing dielectric / electrolyte composite powder; 2, preparing composite powder / organic adhesive paste; 3, preparing the top layer metal foil coating; 4, preparing the bottom layer metal foil coating; 5, aligning the center of the bottom layer metal foil coating and the center of the top layer metal foil coating and leaving a margin at different sides, and preparing the winding type super capacitor core after being winded on the winding central spindle, wrapped and fixed with the adhesive tape; 6 putting the winding type super capacitor core into the shell and then packaging and drying to finish the preparation.

Owner:胡英 +1

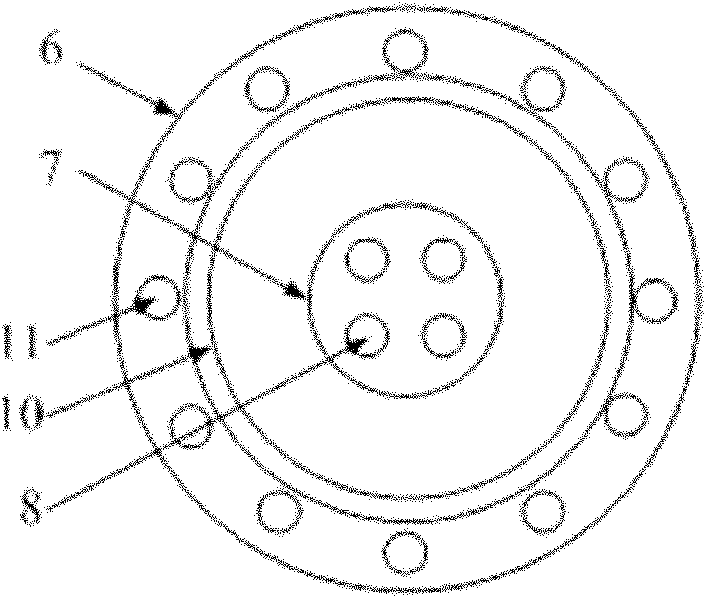

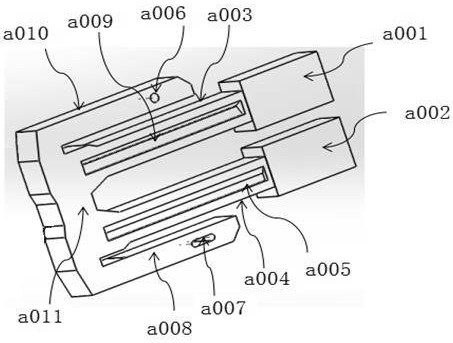

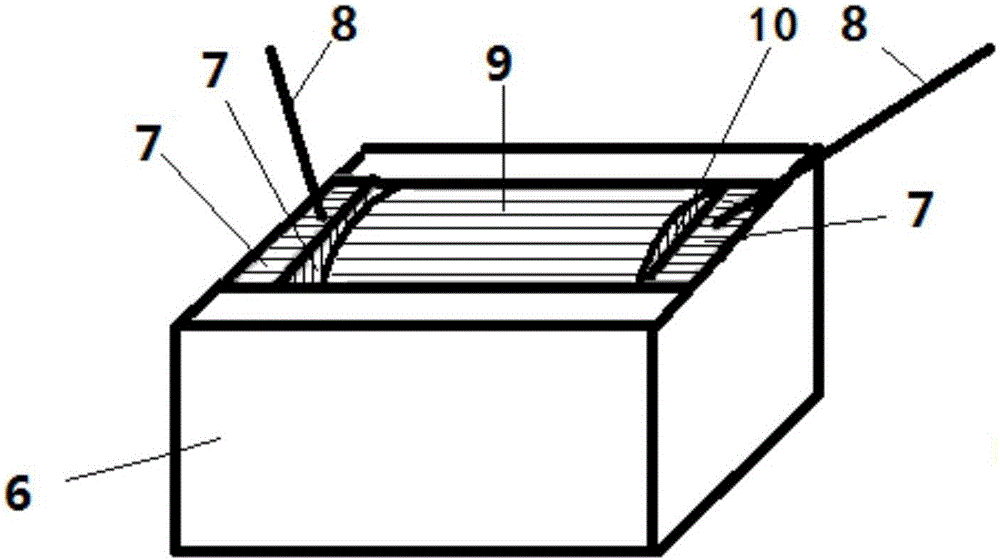

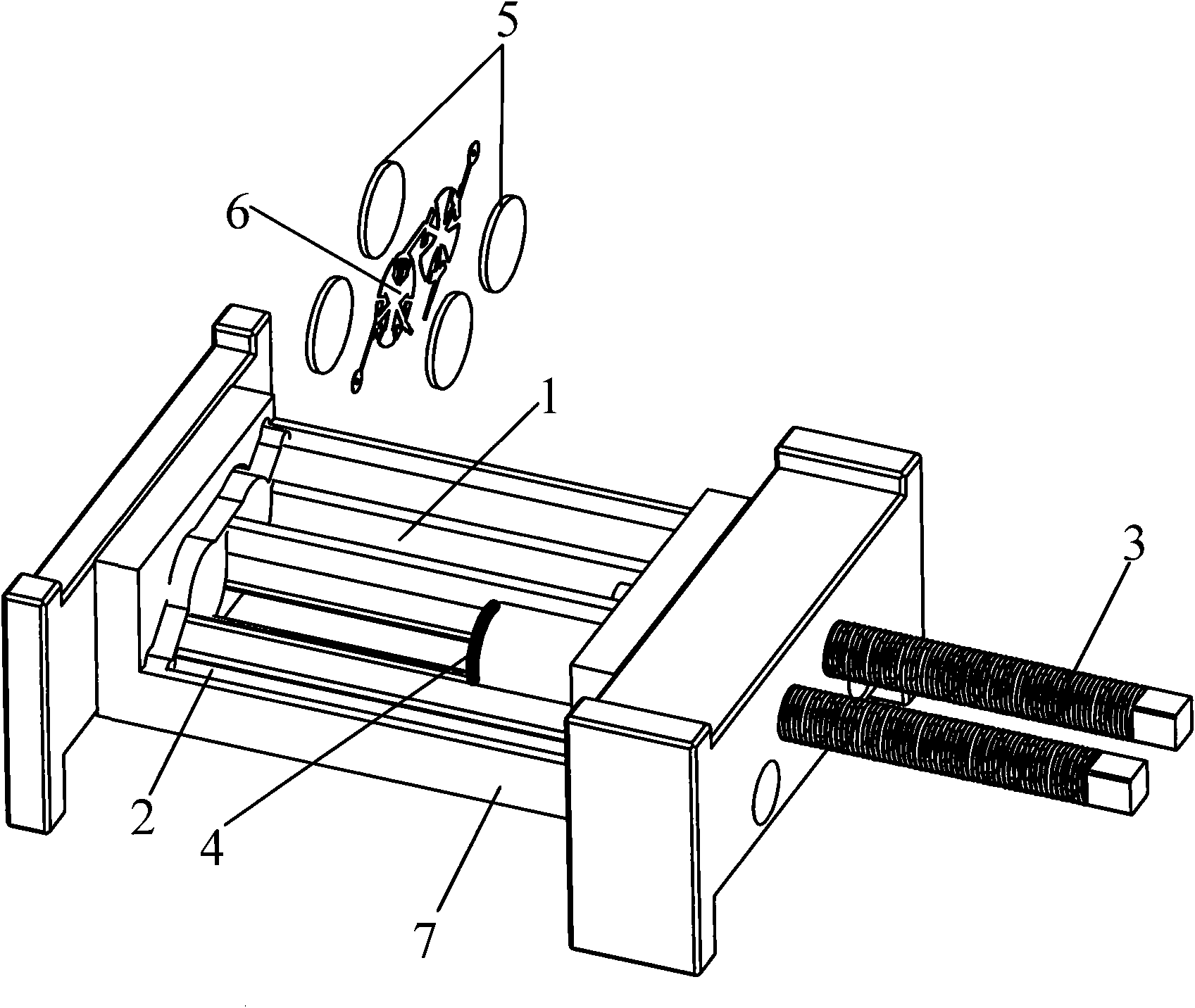

Assembling device of microwave isolator

InactiveCN101777689AImprove electrical performance parametersImprove alignment accuracyWaveguide type devicesIsolatorElectrical conductor

The invention provides an assembling device of a microwave isolator. The assembling device comprises a workbench and pressing mechanisms. The assembling device is characterized in that side plates are arranged on the front and back ends of the workbench, the workbench is supported by the front and back side plates, a central great-circle guide slot is arranged in the central part of the workbench transversely, auxiliary small-circle guide slots are arranged on the left and right sides of the central great-circle guide slot transversely, screwed holes are arranged on the front or back side plate transversely, and the pressing mechanisms penetrate through the transverse screwed holes of the side plate to form a screw transmission pair which can move along the direction of the central great-circle guide slot. The centring, positioning and fastening of a central conductor and a microwave ferrite are realized, and the electric performance parameters of the microwave isolator are increased. Dozens of central conductors and microwave ferrite components can be bound once so that the centring accuracy and positioning accuracy of the microwave isolator are increased significantly, the one-time pass rate is greatly improved, the assembly time is significantly shortened, the cost is reduced, the consistency of the production is greatly improved, and the assembling device is in particular applicable to the mass production of microwave isolators.

Owner:SDP TELECOM SUZHOU

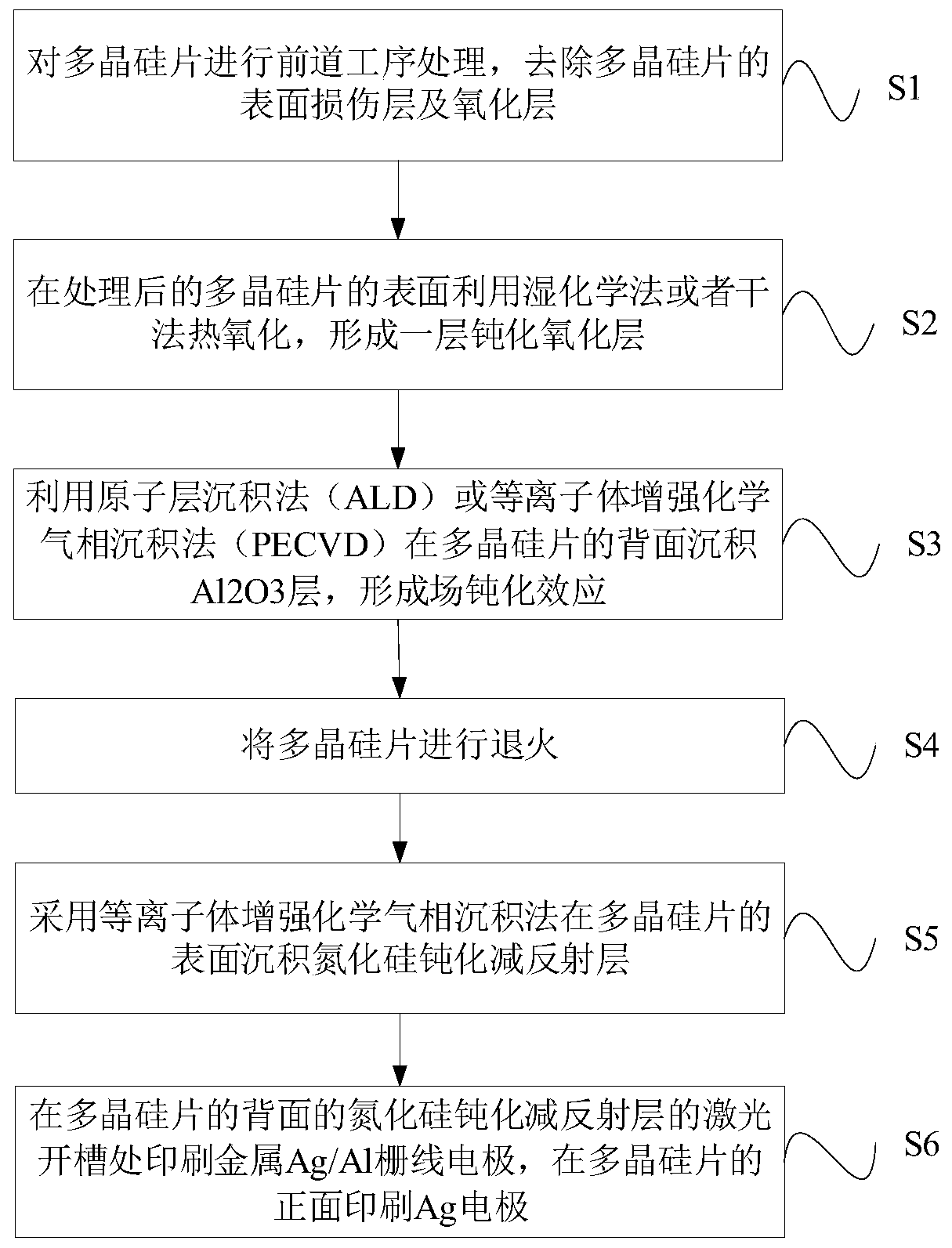

P-type polysilicon double-sided solar cell making method

InactiveCN110311017ASimple structureImprove performanceFinal product manufacturePhotovoltaic energy generationRefractive indexLight reflection

The invention provides a P-type polysilicon double-sided solar cell making method. Through front-end production processing on a polysilicon wafer, a surface damage layer and an oxide layer of the polysilicon wafer are removed; a wet chemical method or a dry method is used for thermal oxidation on the surface of the processed polysilicon wafer, and a passivation oxide layer is formed; an Al2O3 layer is deposited on the back surface of the polysilicon wafer to form field passivation effects; the polysilicon wafer is annealed; a plasma enhanced chemical vapor deposition method is adopted to deposit a silicon nitride passivation anti-reflection layer on the surface of the polysilicon wafer; and a metal Ag / Al gate electrode is printed on a laser groove of the silicon nitride passivation anti-reflection layer on the back surface of the polysilicon wafer, an Ag electrode is printed on the front surface of the polysilicon wafer, and good contact is ensured to be formed between the electrode and the silicon wafer. A plurality of silicon nitride stacks with different refractive indexes are adopted to passivate the front surface and the back surface, the passivation effects are enhanced, light reflection on the front and back surfaces is reduced, and the electrical performance parameters of the polysilicon solar cell are greatly improved.

Owner:SHANGHAI SHENZHOU NEW ENERGY DEV

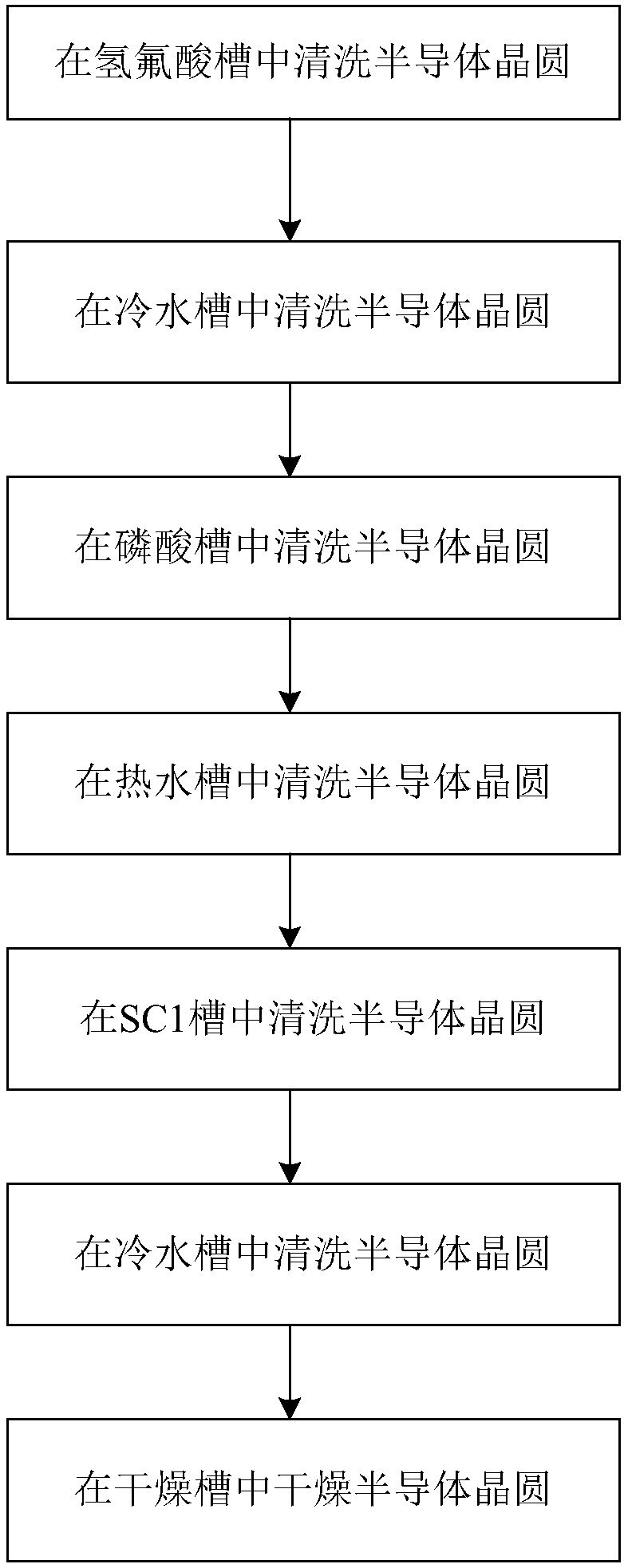

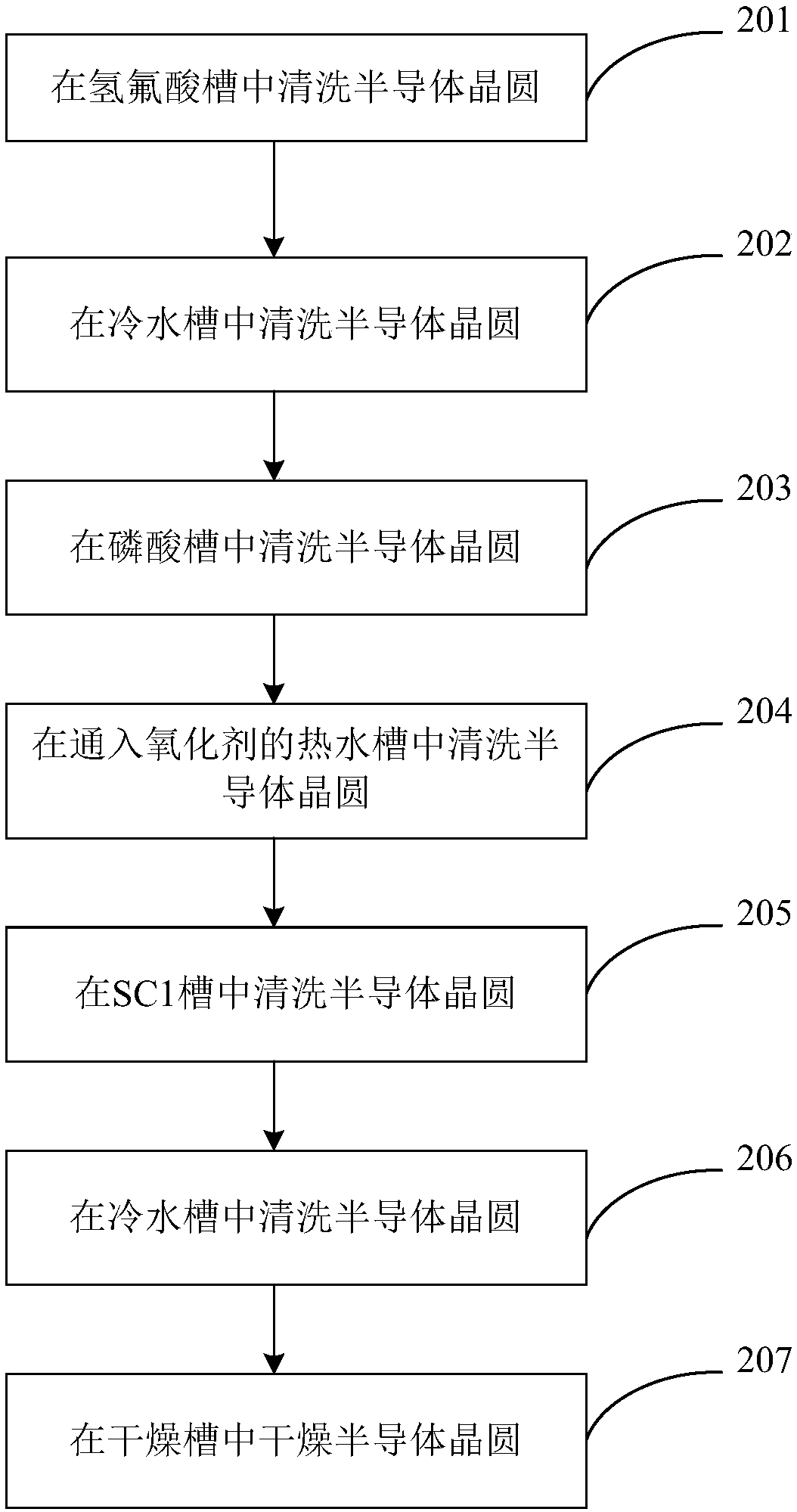

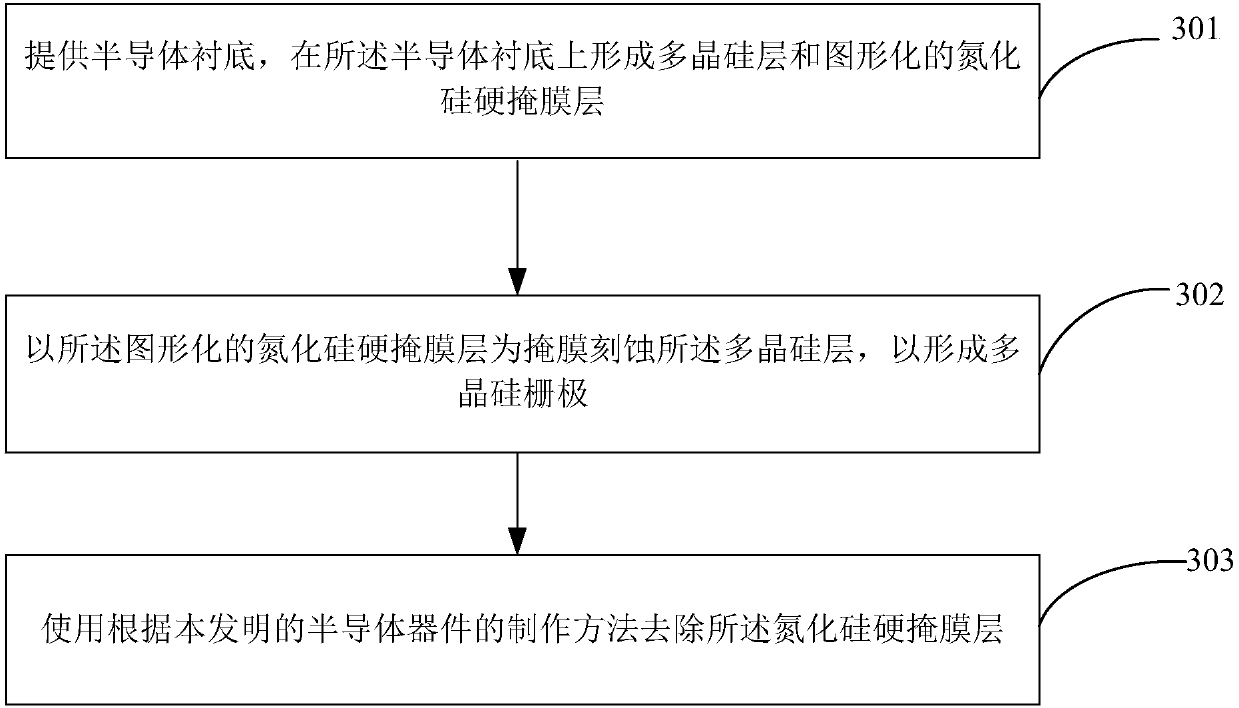

Semiconductor device, method for manufacturing same, and electronic device

InactiveCN109830436AAvoid corrosionAvoid increased roughnessSemiconductor/solid-state device manufacturingSidewall roughnessPhosphoric acid

The present invention provides a semiconductor device, a method for manufacturing the same, and an electronic device. The method comprises cleaning a semiconductor wafer in a phosphoric acid tank to remove a silicon nitride hard mask layer; and cleaning the semiconductor wafer in a hot water tank filled with an oxidant to remove phosphoric acid residues on the semiconductor wafer. The manufacturing method can solve the problem that a polycrystalline silicon gate corrodes in a silicon nitride removal process after the polycrystalline silicon etching so as to result in an increase in the sidewall roughness of the polycrystalline silicon gate and a decrease in the characteristic dimension (CD) of the polycrystalline silicon gate, thereby improving the electrical parameters and yield of the products. The semiconductor device and the electronic device have similar advantages.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

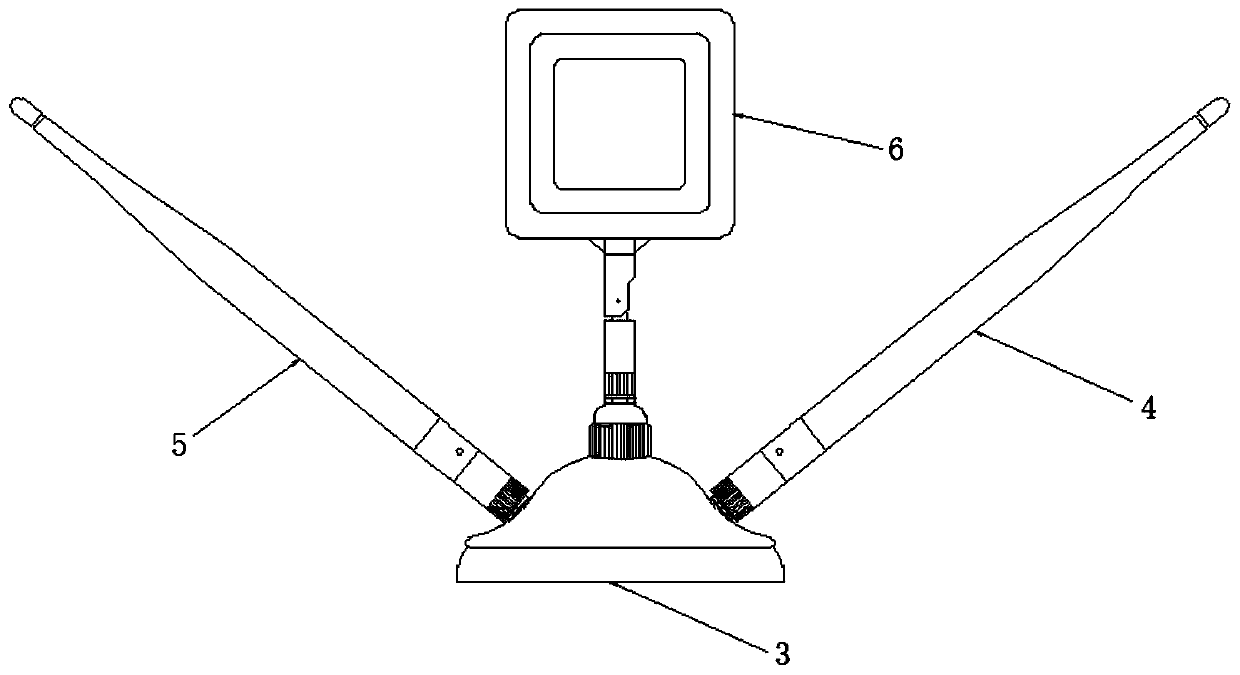

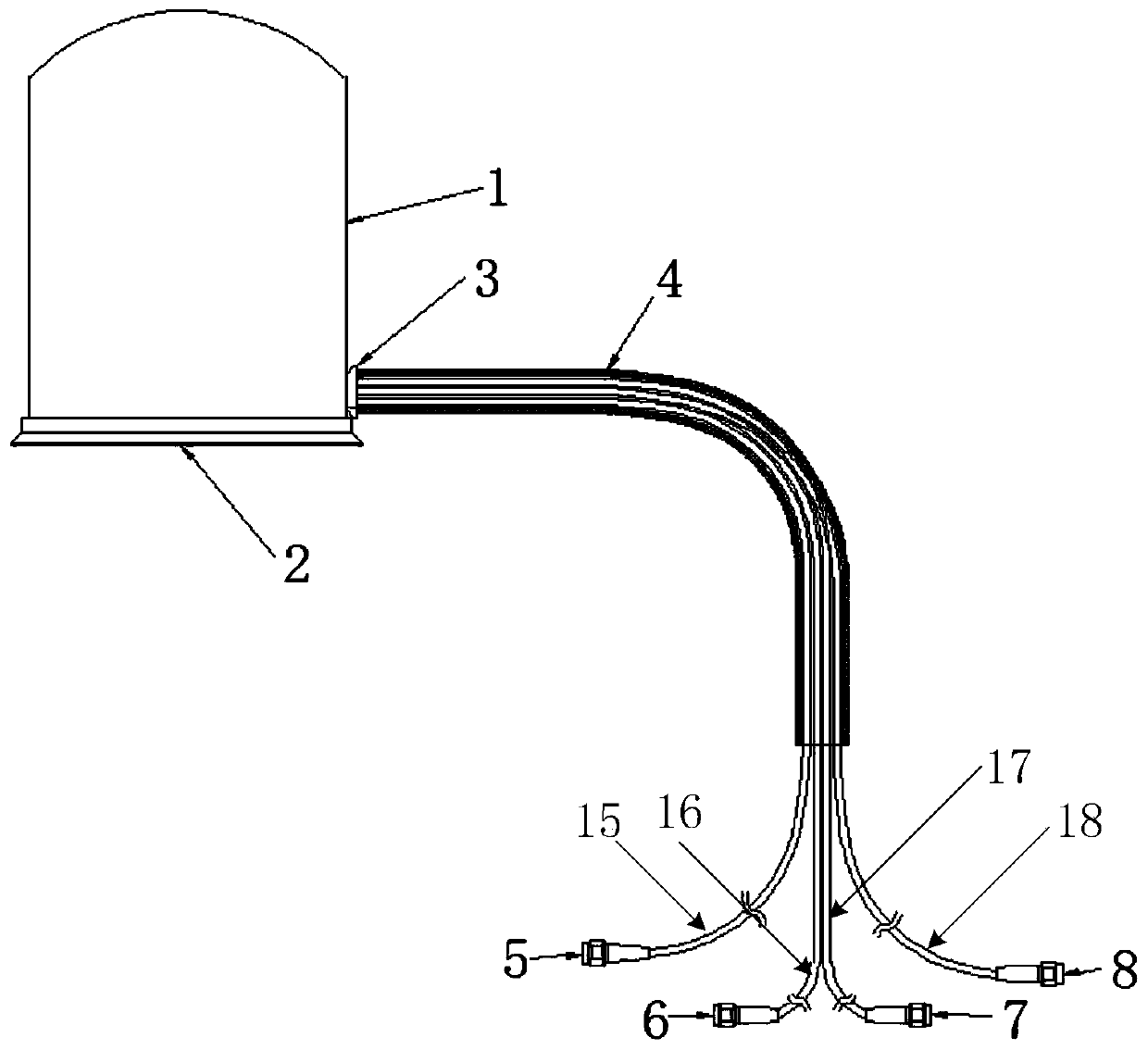

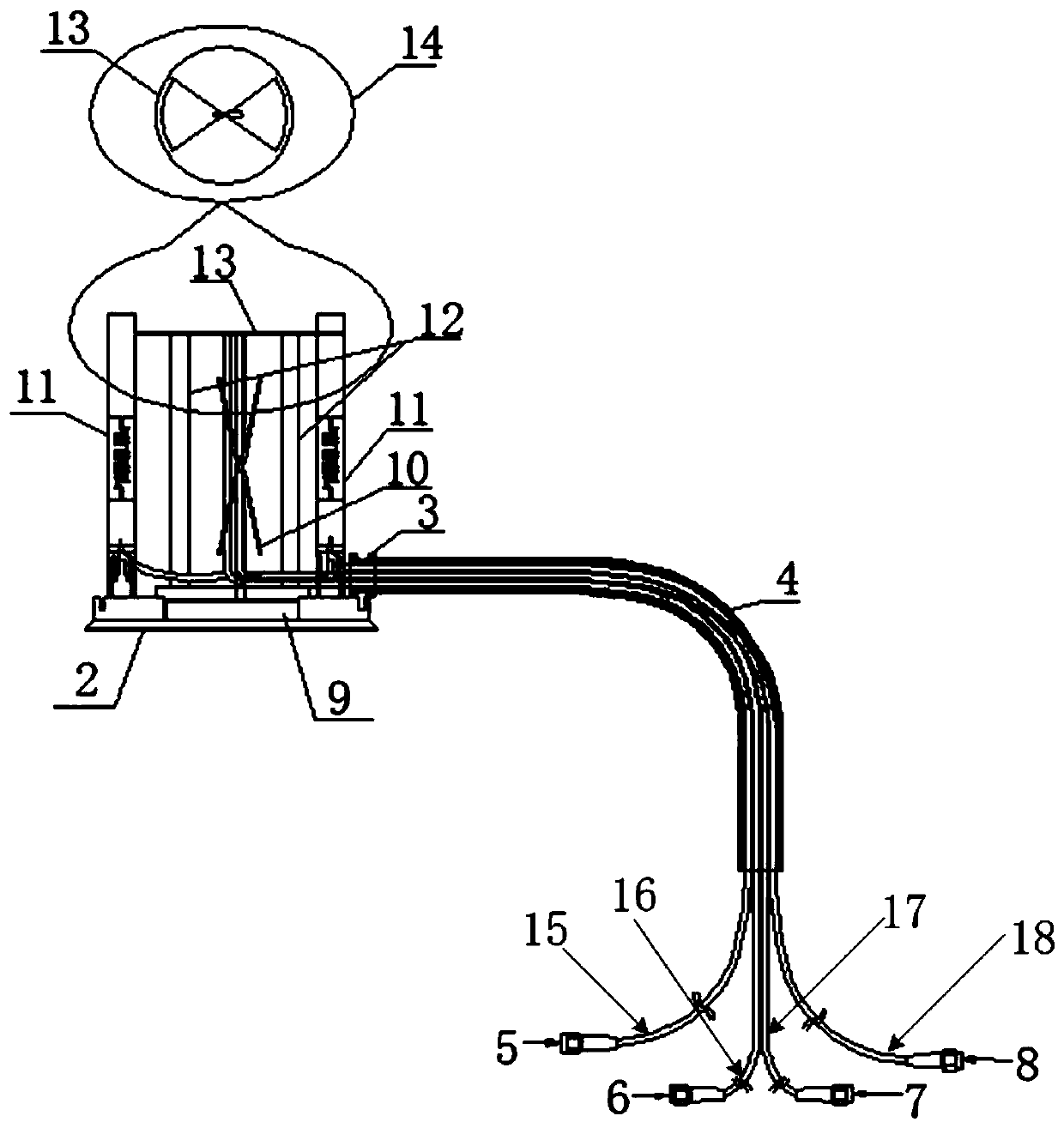

Four-port suction cup combined antenna

ActiveCN109728424AImprove electrical performance parametersHigh radiation area utilizationSimultaneous aerial operationsRadiating elements structural formsTransceiverPerformance index

The invention discloses a four-port suction cup combined antenna. The four-port suction cup combined antenna comprises an antenna cover, a bottom cover, a retaining sleeve, a cable protector, a firstport feeding cable, a second port feeding cable, a third port feeding cable and a fourth port feeding cable. A 3G band circuit board is fixedly installed at the middle portion of the internal portionof the antenna cover, ABS support columns are respectively installed at two sides of the 3G band circuit board, one WlAN frequency circuit board is fixedly installed at the outer side of each supportcolumn, one GPS frequency circuit board is fixedly installed at the upper end of the 3G band circuit board, the GPS frequency circuit boards are fixed on a round plastic board, the two ends of the round plastic board are respectively fixedly matched with the upper end of the corresponding WlAN frequency circuit boards. The four-port suction cup combined antenna is simple in structure and small insize, can provide a good radiation performance index, and can be matched with the connection end in a transceiver device.

Owner:GUANGZHOU CREKING COMM TECH