Manufacture method of high-efficiency cell with front emission junction and backside tunneling oxidation and passivation contact

A technology of tunnel oxidation and manufacturing method, which is applied in the manufacture of circuits, electrical components, final products, etc., can solve the problems that the electrical performance is not greatly improved, achieve easy compatibility, improve open circuit voltage and conversion efficiency, and have strong process feasibility Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

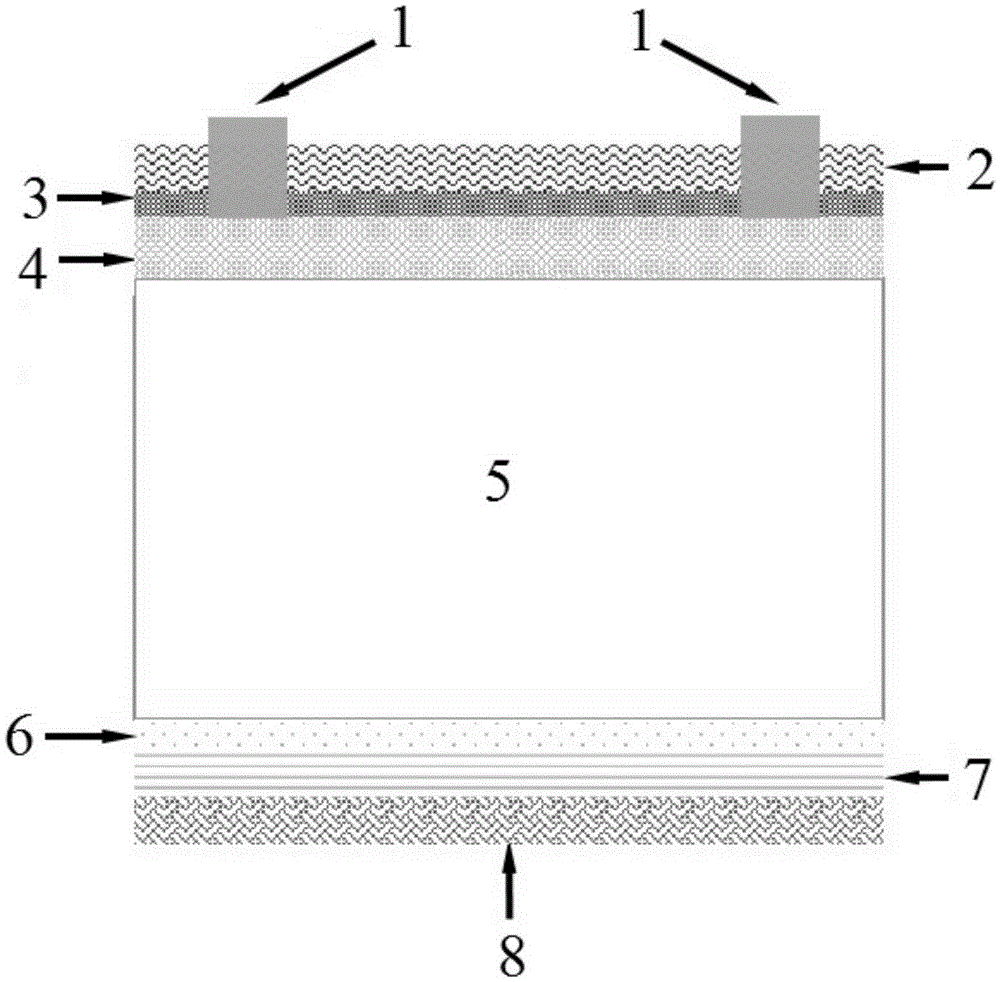

Image

Examples

Embodiment 1

[0023] A method for making a high-efficiency cell with an oxidation passivation contact on the back side of the front emitter junction adopts the following steps:

[0024] (1) Using the silicon chip in KOH alkali solution and H 2 o 2 Remove the damaged layer in the solution, then use tetramethylammonium hydroxide and isopropanol to form a mixed solution to texture the silicon wafer, and form a pyramid texture with 1 μm on both sides;

[0025] (2) In the boron source high-temperature diffusion furnace tube, the temperature is controlled at 850 ° C for 40 minutes, and then the temperature is controlled at 800 ° C to pass oxygen into the junction to form a low surface concentration B-doped P + launch junction;

[0026] (3) Use HF solution to remove borosilicate glass BSG layer, and use HNO 3 Mixed solution with HF for side insulation and back polishing;

[0027] (4) Using wet chemical method to grow an ultra-thin tunnel oxide layer SiO on the back of the silicon wafer 2 , it...

Embodiment 2

[0033] A method for making a high-efficiency cell with an oxidation passivation contact on the back side of the front emitter junction adopts the following steps:

[0034] (1) Using the silicon chip in NaOH alkali solution and H 2 o 2 Remove the damaged layer in the solution, then use tetramethylammonium hydroxide and isopropanol to form a mixed solution to texture the silicon wafer, and form a pyramid texture with 2 μm on both sides;

[0035] (2) In the boron source high-temperature diffusion furnace tube, the temperature is controlled at 900°C for 30 minutes, and then the temperature is controlled at 850°C to pass oxygen into the junction to form a low surface concentration B-doped P + launch junction;

[0036] (3) Use HF solution to remove borosilicate glass BSG layer, and use HNO 3 Mixed solution with HF for side insulation and back polishing;

[0037] (4) Using wet chemical method to grow an ultra-thin tunnel oxide layer SiO on the back of the silicon wafer 2 , its t...

Embodiment 3

[0042] A method for making a high-efficiency cell with an oxidation passivation contact on the back side of the front emitter junction adopts the following steps:

[0043] (1) Using the silicon chip in NaOH alkali solution and H 2 o 2 Remove the damaged layer in the solution, then use tetramethylammonium hydroxide and isopropanol to form a mixed solution to texture the silicon wafer, and form a pyramid texture with 4 μm on both sides;

[0044] (2) In the boron source high-temperature diffusion furnace tube, the temperature is controlled at 1000 ° C for 20 minutes, and then the temperature is controlled at 900 ° C to pass oxygen into the junction to form a low surface concentration B-doped P + launch junction;

[0045] (3) Use HF solution to remove borosilicate glass BSG layer, and use HNO 3 Mixed solution with HF for side insulation and back polishing;

[0046] (4) Using wet chemical method to grow an ultra-thin tunnel oxide layer SiO on the back of the silicon wafer 2 , ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More