Silicon-on-insulator laterally diffused metal oxide semiconductor (SOI LDMOS) device containing composite drift region

A drift region and device technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problem of increasing the on-state voltage drop

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] In order to make the purpose, content, and advantages of the present invention clearer, the implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings.

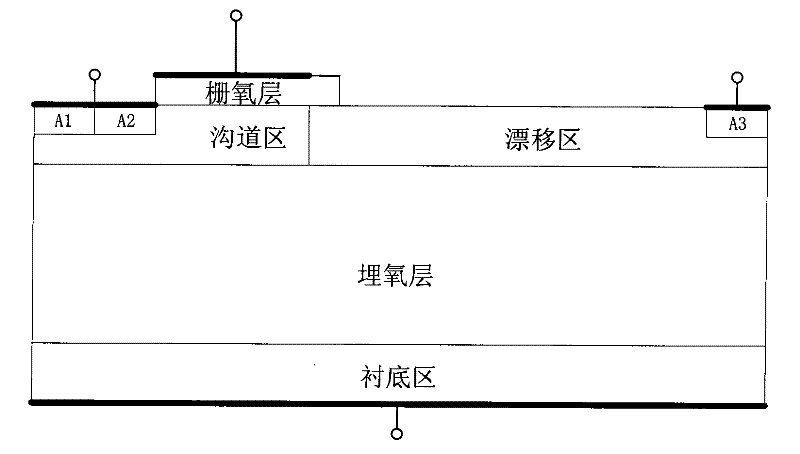

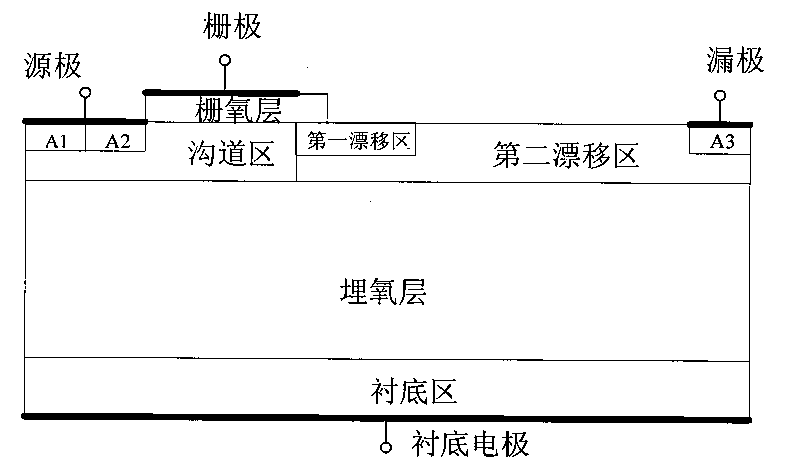

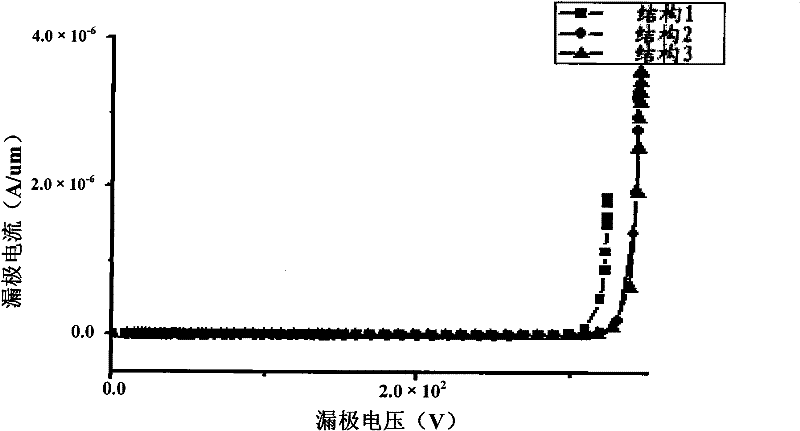

[0020] Such as figure 2 As shown, the SOI LDMOS device containing the composite drift region according to the embodiment of the present invention sequentially includes a gate oxide layer, a top silicon layer, a buried oxide layer and a bottom silicon layer (ie figure 2 The substrate region in), wherein the top layer silicon includes a channel region and a composite drift region, and the composite drift region includes a first drift region and a second drift region, wherein the thickness of the first drift region is smaller than the thickness of the top layer silicon .

[0021] The channel region is a P channel region (that is, a P-type doped channel region), and correspondingly, the second drift region is an N-type drift region (that is, an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More