Process method of soi LDMOS device preparation

A process method and device technology, applied in the field of semiconductor process manufacturing, can solve the problems of difficult dielectric isolation, low SOI withstand voltage, unfavorable device heat dissipation, etc., and achieve the effects of simple process steps, guaranteed isolation, and simple operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

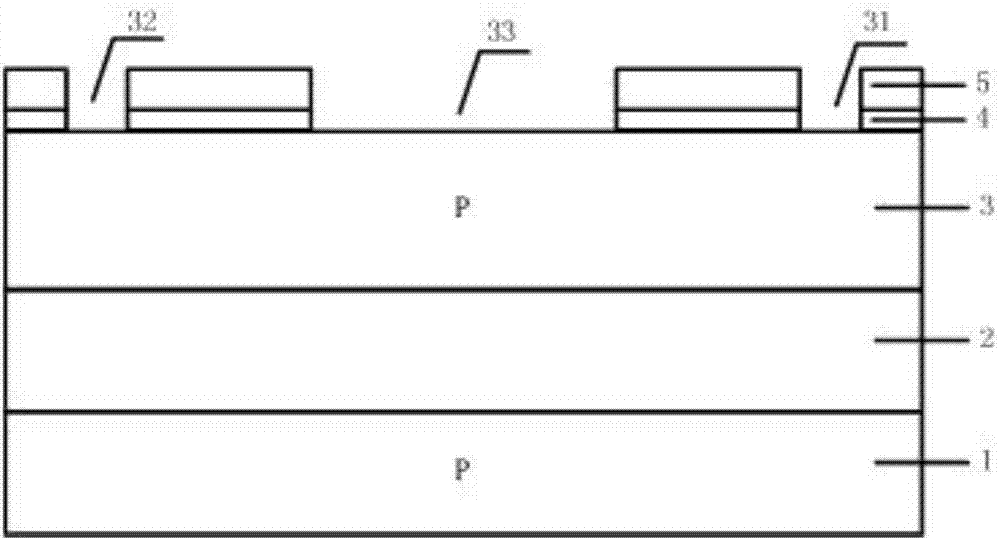

[0044] The present invention is described in further detail now in conjunction with accompanying drawing. These drawings are all simplified schematic diagrams, which only illustrate the basic structure of the present invention in a schematic manner, so they only show the configurations related to the present invention.

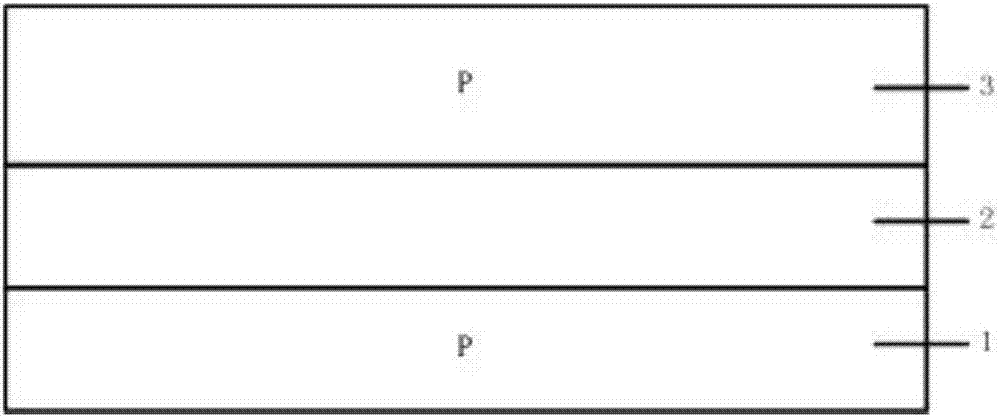

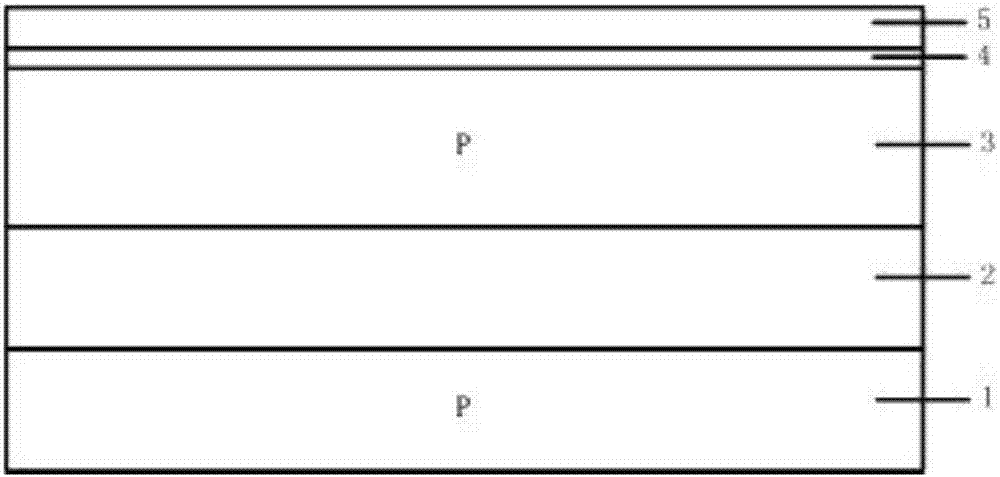

[0045] In an embodiment of a process method for preparing an SOI LDMOS device according to the present invention, the SOI LDMOS device is prepared on the basis of an SOI process base, and the process base includes a silicon substrate 1, a BOX buried Oxygen layer 2 and top silicon film 3. Wherein the resistivity of the top silicon film 3 is 10-40Ω•cm, and the thickness is greater than 1.5µm. Described processing method comprises the steps:

[0046] 1) if figure 1 As shown, a P-type well is implanted in the top silicon film, and the P-well implantation dose is 1e12-1e14cm -2 , to increase the P-type well content in the top silicon film. Step 1) is to prepa...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More