Integrated double longitudinal channel SOI LDMOS (silicon on insulator laterally double diffusion metal oxide semiconductor) device unit

A vertical and device technology, applied in the field of microelectronics, can solve the problems that are not conducive to improving the reliability of devices and systems, saving energy and protecting the environment, low working efficiency of devices, large on-state resistance of devices, etc., to achieve extended conductive current path, Effect of reducing on-state resistance and on-state voltage drop and eliminating peak electric field

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

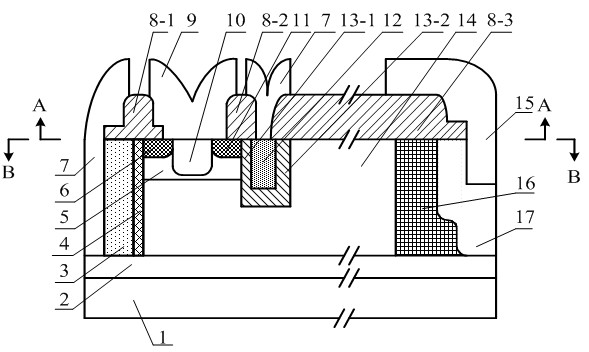

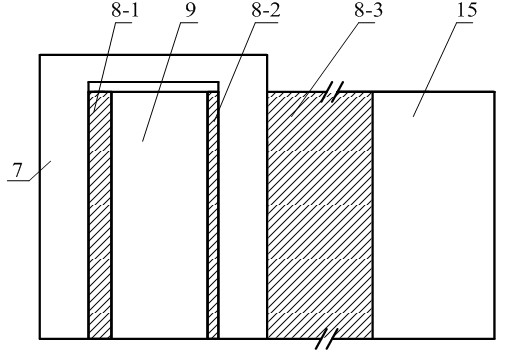

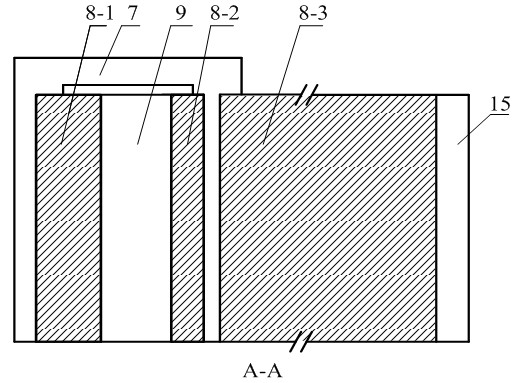

[0012] Such as figure 1 , 2 , 3 and 4, an integrated vertical double-channel SOI nLDMOS device unit includes a semiconductor substrate (1), covered with a buried oxide layer (2) on the semiconductor substrate (1), and a buried oxide layer (2) A lightly doped drift region (14) is arranged on it. One side of the lightly doped drift region (14) is set as a same-type heavily doped semiconductor region as a buffer zone (16) for LDMOS, and the other side is set with an N-type heavily doped first low-resistance polysilicon gate (3) A vertical gate oxide layer (4) is arranged between the first low-resistance polysilicon gate (3) and the lightly doped drift region (14).

[0013] A well region (5) and a groove oxygen region are arranged on the top of the lightly doped drift region (14), the well region (5) is an anisotropic heavily doped semiconductor region, the groove oxygen region is an oxide layer, and one part of the well region (5) One side is arranged adjacent to the vertical ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More