High-reliability silicon on insulator (SOI) laterally diffused metal oxide semiconductor (LDMOS) power element

A power device, a reliable technology, applied in the field of high-reliability SOI LDMOS power devices, can solve the problems of poor reliability and other problems, achieve the effect of raising the maintenance voltage, enhancing the reliability of the device, and expanding the electrical safe working area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

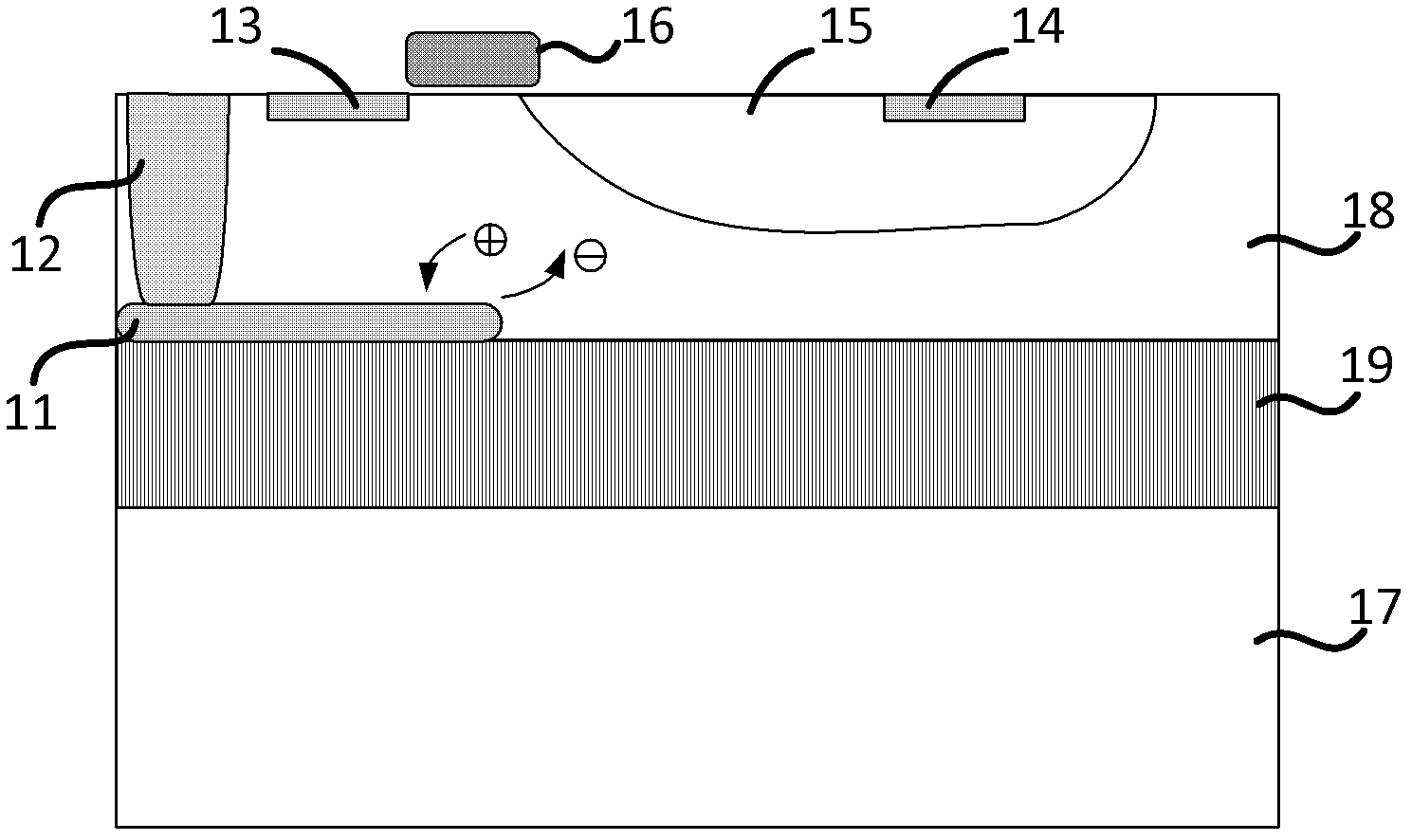

[0029] The highly reliable SOI LDMOS power device provided by the present invention, such as figure 1 As shown, in the figure, 19 is a buried oxide layer, and the material is silicon dioxide; 18 is a top silicon layer, in which an SOI device is fabricated; 17 is a bottom silicon layer, which is completely isolated from the top silicon layer 18 by the buried oxide layer 19 ; 16 is the SOI LDMOS gate, the material is polysilicon implanted with high concentration; 15 is the drift region; 13 is the source implantation region to form the device source, 14 is the drain implantation region to form the device drain; 11 is the buried layer, this embodiment Among them, its scope is a part of the device working area, and the depth is close to the buried oxide layer 19 above the buried oxide layer 19; 12 is a high-concentration contact implantation region, and its function is to connect the surface of the buried layer 11 and the top silicon layer 18, so that the buried layer The potential...

Embodiment 2

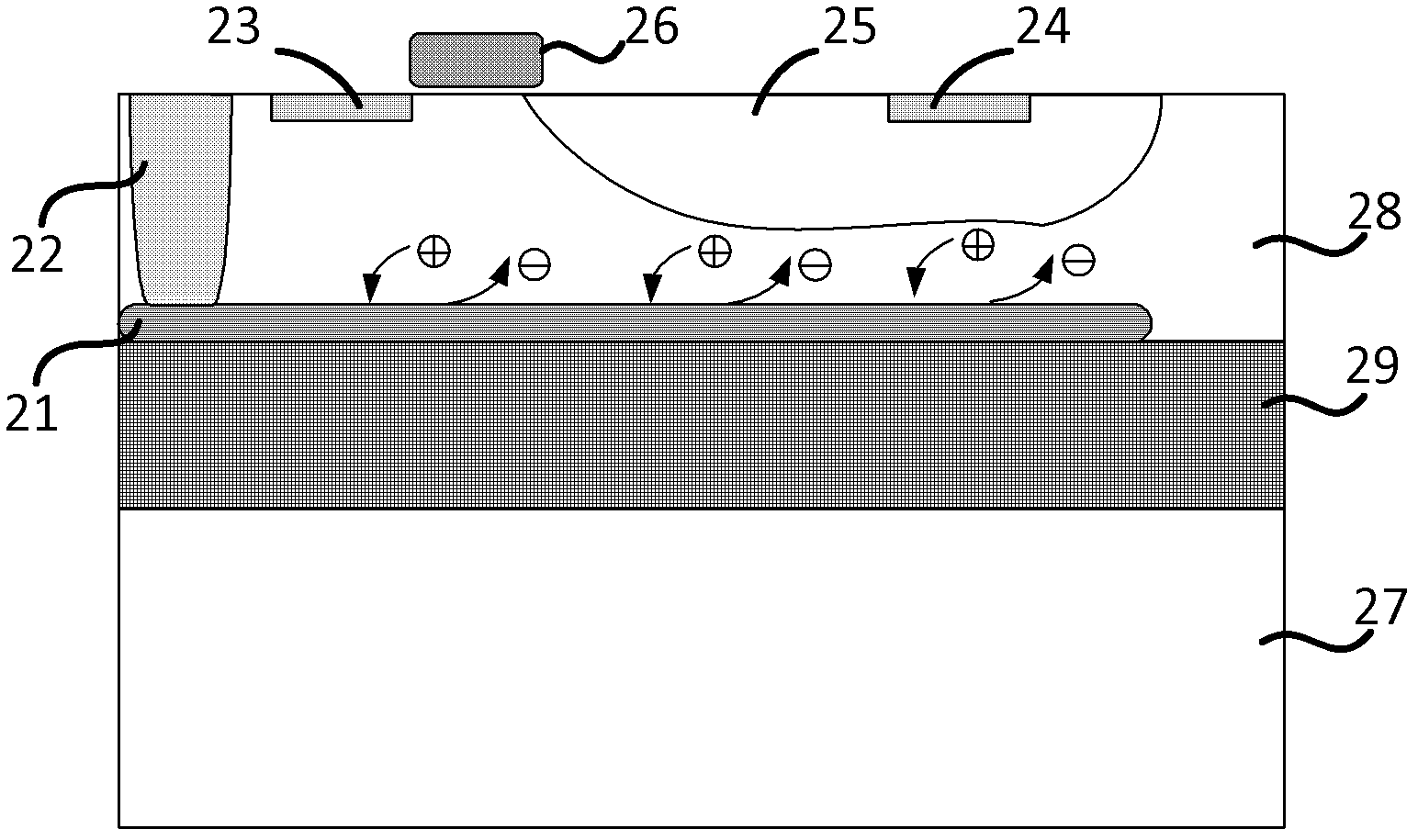

[0031] Such as figure 2 As shown, it is a schematic cross-sectional view of an SOI LDMOS power device structure in which the buried oxide layer is next to the buried oxide layer and the entire working area is buried in the embodiment of the present invention. In the figure, 29 is a buried oxide layer, and the material is silicon dioxide; 28 is a top silicon layer, in which an SOI device is fabricated; 27 is a bottom silicon layer, which is completely isolated from the top silicon layer 28 by a buried oxide layer 29; 26 is SOI LDMOS gate, the material is polysilicon implanted with high concentration; 25 is a drift region; 23 is a source implantation region to form a device source, 24 is a drain implantation region to form a device drain; 21 is a buried layer, and its range in this embodiment is the entire working area of the device, and the depth is close to the buried oxide layer 29 on the buried oxide layer 29; It can be controlled, and the carriers are absorbed during th...

Embodiment 3

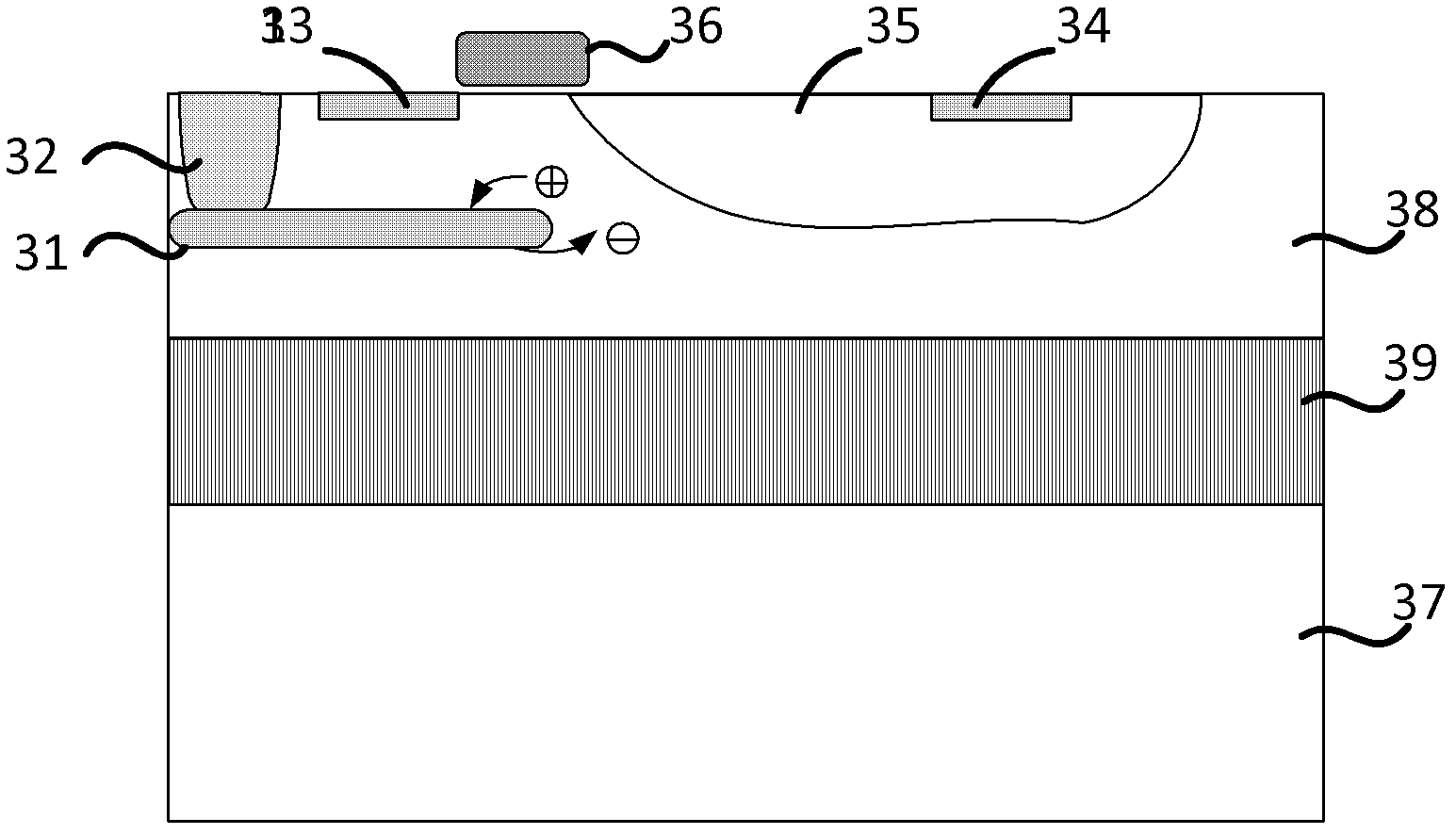

[0033] Such as image 3 As shown, it is a schematic cross-sectional view of an SOI LDMOS power device structure in which a buried layer is buried between a buried oxide layer and a device surface according to an embodiment of the present invention. 39 is a buried oxide layer, the material is silicon dioxide; 38 is a top silicon layer, in which an SOI device is fabricated; 37 is a bottom silicon layer, which is completely isolated from the top silicon layer 38 by a buried oxide layer 39; 36 is an SOI LDMOS gate , the material is high-concentration implanted polysilicon; 35 is the drift region; 33 is the source implantation region to form the device source, 34 is the drain implantation region to form the device drain; 31 is the buried layer, and its scope is the working of the device in this embodiment Part of the area, the depth is the position between the buried oxide layer 39 and the surface of the top silicon layer 38; 32 is a high-concentration contact implantation region, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More