Fabrication method of anti-esd integrated soi LDMOS device unit

A manufacturing method and device technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of increasing system volume, weight and cost, SOILDMOS devices without integrated anti-ESD structure and function, device failure, etc., to achieve Excellent electrical and thermal properties, excellent integrated anti-ESD self-protection effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

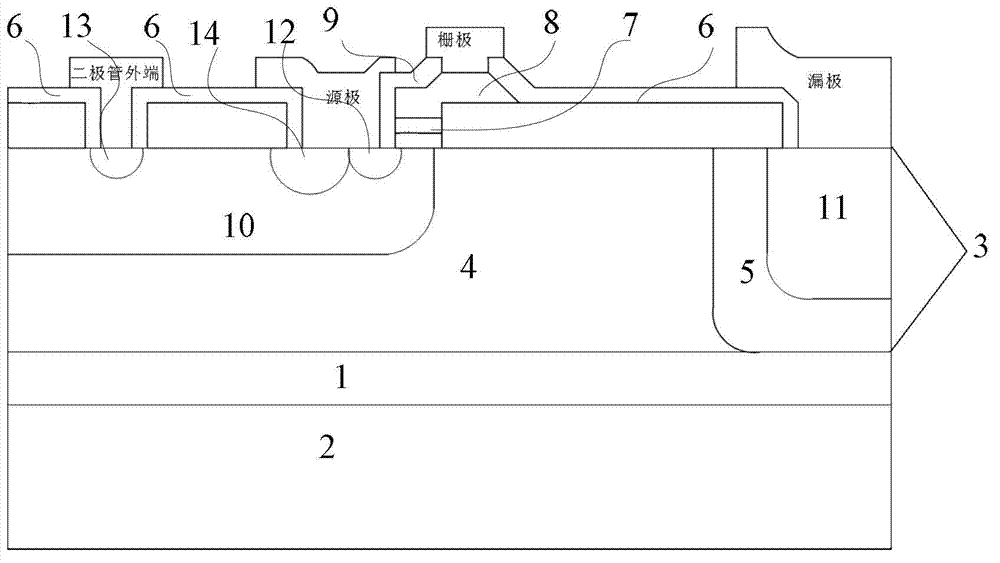

[0030] Such as figure 1 and figure 2 Shown, the fabrication method of anti-ESD integrated SOI LDMOS device unit comprises the following steps:

[0031] Step (1) select the silicon wafer of the first conductivity type, a buried insulating layer 1 is formed at a certain depth below the surface of one side of the silicon wafer, and the buried insulating layer 1 completely isolates the silicon wafer into two semiconductor regions, The thick one of the two semiconductor regions is used as the substrate 2, and the thin one has the second conductivity type and a certain doping concentration distribution, and is used as the top layer silicon film 3 for making devices and circuits; wherein, the top layer silicon film 3 is greater than 50 The area of % is used as the drift zone 4 of making device;

[0032] The certain depth mentioned is determined according to the actual situation.

[0033] Step (2) Carry out the first oxidation on the upper surface of the exposed top layer silico...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More