Super structure based on vertical gate SOI CMOS device and manufacturing method thereof

A fabrication method and vertical gate technology, applied in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., can solve the problems of reducing source-drain breakdown voltage, reducing device gain, increasing power consumption, etc., and achieving the optimization of electric field distribution , The effect of improving the breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

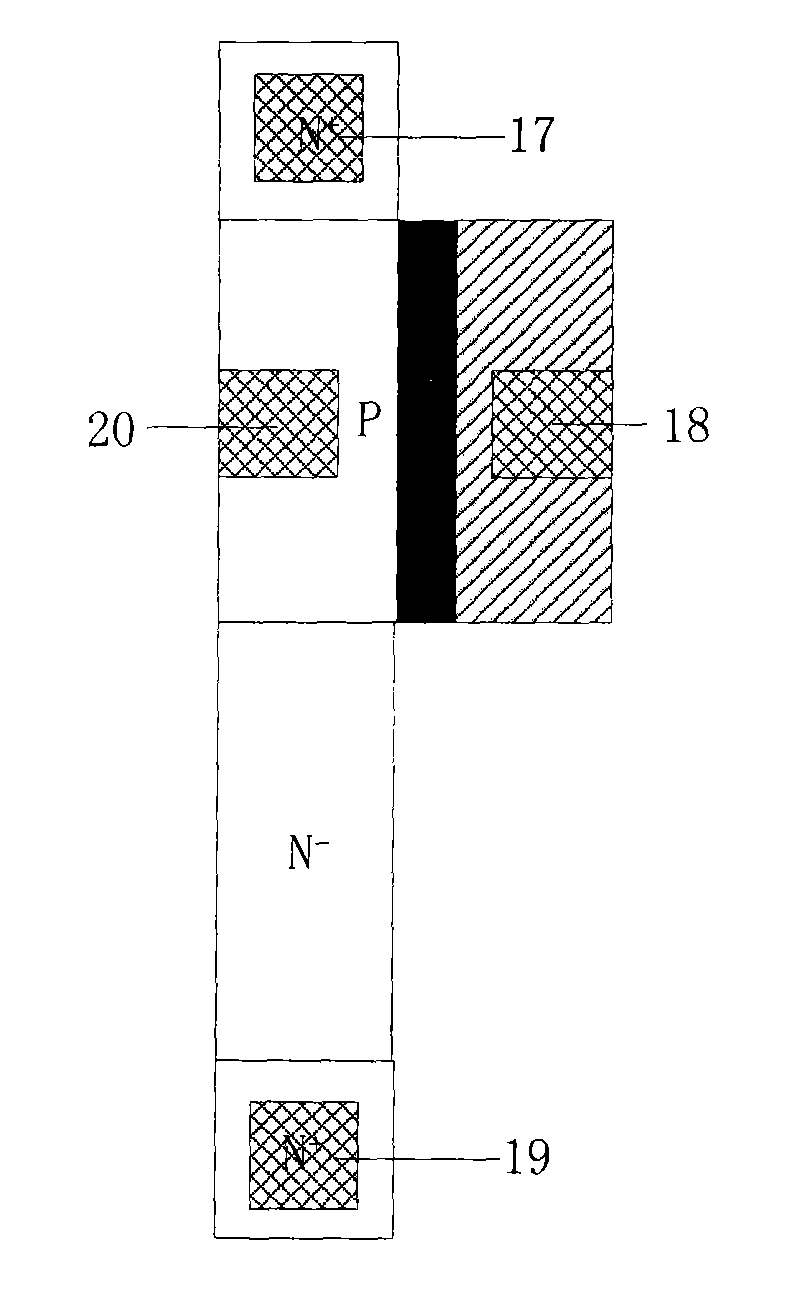

[0050] This embodiment provides a super junction structure based on a vertical gate SOI CMOS device, including an SOI substrate, and a gate region, a source region, a channel region, and a drain region grown on the SOI substrate, and the channel region and the drain region A drift region with pn column regions arranged up and down is arranged between the regions, and the doping type of the lower column region in the drift region is consistent with that of the drain region.

[0051] The SOI substrate includes a silicon substrate layer grown from bottom to top, a buried oxide layer, and a single crystal silicon top layer. The super junction structure of the vertical gate SOI CMOS device includes a vertical gate SOI NMOS super junction structure and a vertical gate SOIPMOS super junction structure, the gate area is divided into an NMOS gate area and a PMOS gate area, and the source area is divided into an NMOS source area and a PMOS source area region, the channel region is divid...

Embodiment 2

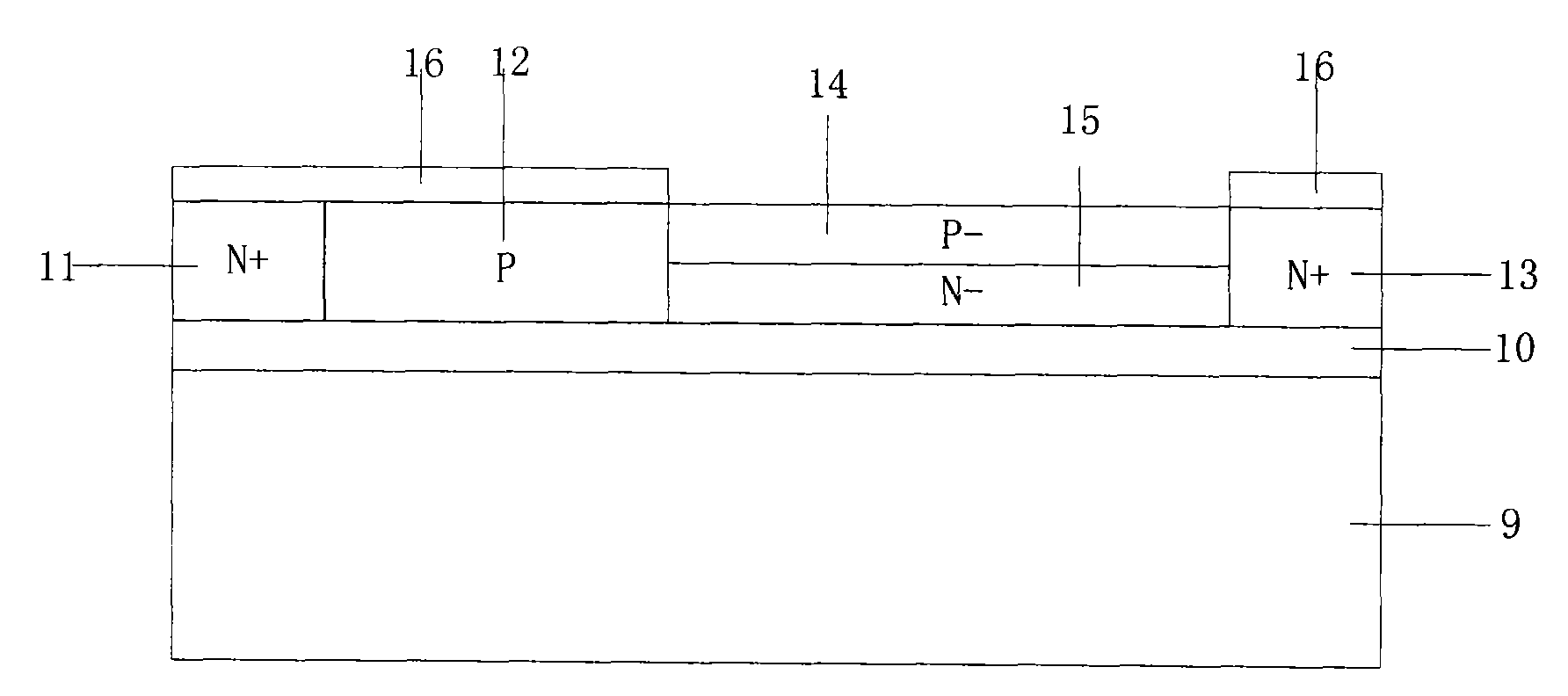

[0067] Such as figure 2 , 3 As shown, this embodiment provides a super junction structure based on a vertical gate SOI NMOS device, including an SOI substrate, and an NMOS source region 11, an NMOS channel region 12, and an NMOS drain region 13 grown on the SOI substrate. Between the NMOS channel region 12 and the NMOS drain region 13 there is a drift region with pn junctions arranged up and down, and the doping type of the junction region below is consistent with that of the NMOS drain region 13 . In the NMOS super junction structure, the upper junction region is the n-pillar region 14 , and the lower junction region is the p-pillar region 15 .

[0068] The SOI substrate includes a silicon substrate layer 9 grown from bottom to top, a buried oxide layer 10, and a single crystal silicon top layer. An NMOS vertical gate region is grown on one side of the NMOS channel region 12 , and an NMOS gate oxide layer is grown between the NMOS vertical gate region and the NMOS channel ...

Embodiment 3

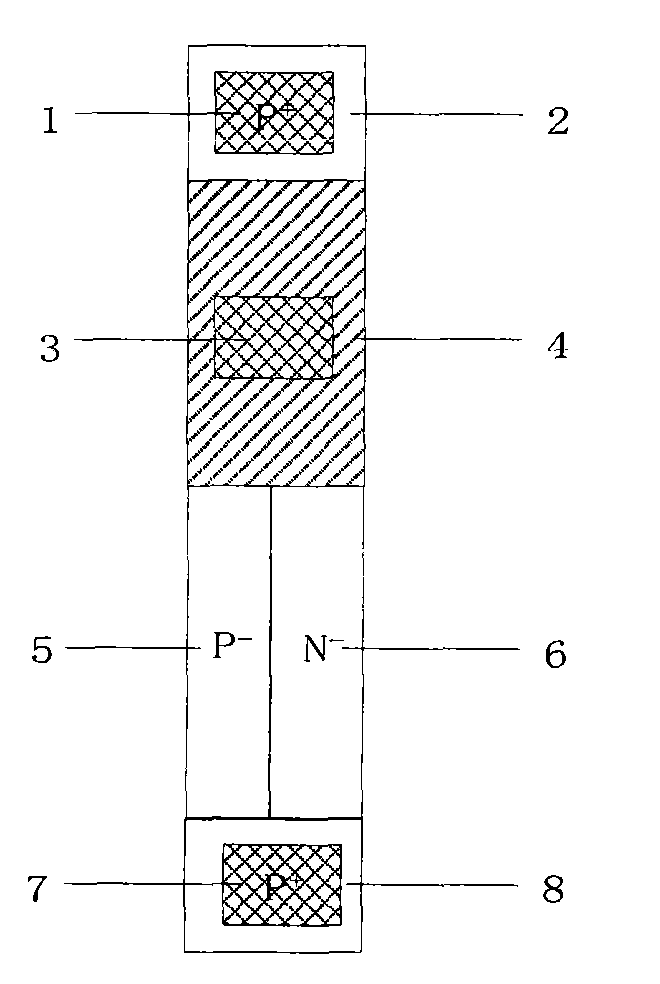

[0071] Such as Figure 4 , 5 As shown, this embodiment provides a super junction structure based on a vertical gate SOI PMOS device, including an SOI substrate, and a PMOS source region 21, a PMOS channel region 22, and a PMOS drain region 23 grown on the SOI substrate. Between the PMOS channel region 22 and the PMOS drain region 23 there is a drift region with pn junctions arranged up and down, and the doping type of the junction region below is consistent with that of the PMOS drain region 23 . In the PMOS superjunction structure, the upper junction region of the drift region is the p-pillar region 24 , and the lower junction region is the n-pillar region 25 .

[0072] The SOI substrate includes a silicon substrate layer 9 grown from bottom to top, a buried oxide layer 10, and a single crystal silicon top layer. A PMOS vertical gate region is grown on one side of the PMOS channel region 22 , and a PMOS gate oxide layer is grown between the PMOS vertical gate region and the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More