Patents

Literature

46results about How to "Realize the process is simple" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Graphene heating ink, preparation method and application thereof

InactiveCN108610736AHigh electrothermal conversion efficiencyImprove the normal emissivity of far-infrared raysInksCross-linkEmissivity

The invention discloses a graphene heating ink, a preparation method and application thereof. The graphene heating ink comprises the following raw materials by mass percent: 5-15% of carbon black, 10-25% of graphite, 0.1-5% of graphene powder, 0.1-8% of carbon nanotube powder, 25-40% of an adhesive, 1-5% of an assistant, and the balance a mixed solvent. Through combination of dotted carbon black,linear carbon nanotubes and planar graphene, a mutually cross-linked stable structure can be formed inside the ink, and the safety is high. Through improvement of the preparation process and the ink formula components, blistering does not occur easily in the stirring process, and the ink has good adhesion during printing, the electro-thermal conversion efficiency of the heating ink is remarkably improved, the far infrared normal emissivity of an electrothermal film is significantly enhanced, the service life of the electrothermal film is greatly increased, and the power change of 100,000h aging test is less than 2.6%. Also, the implementation process adopted by the invention is simple, efficient and practical.

Owner:山东暖匠智能电子科技有限公司

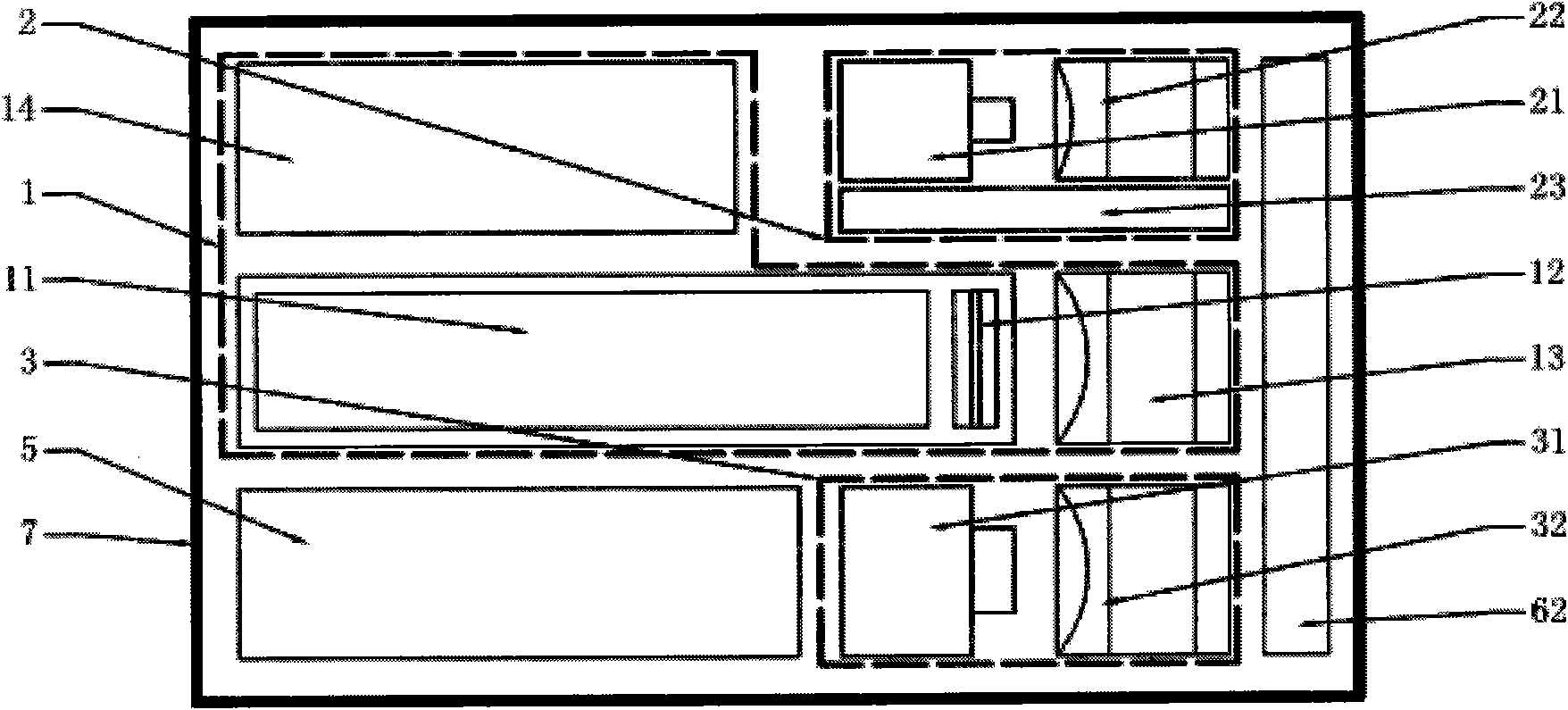

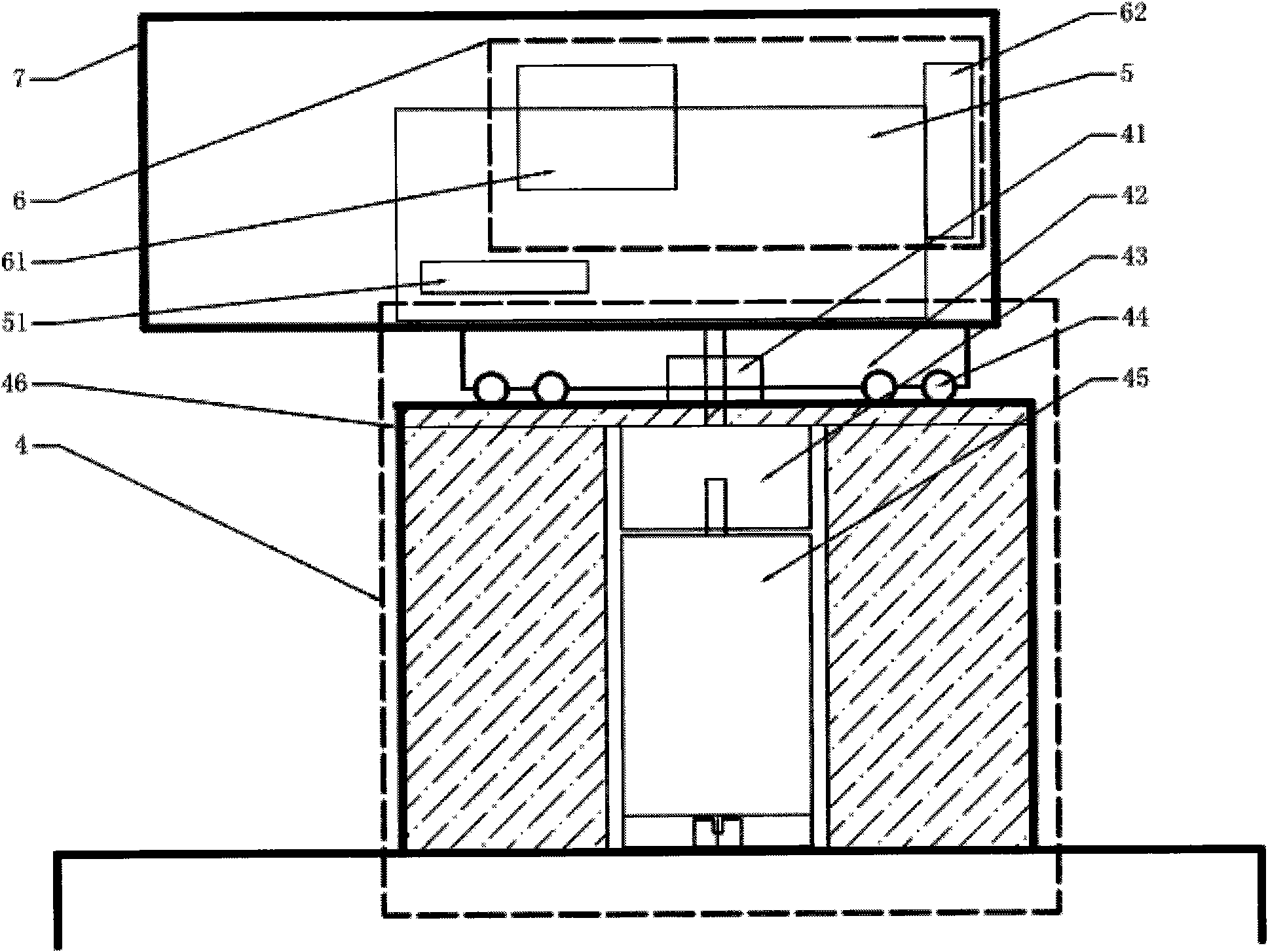

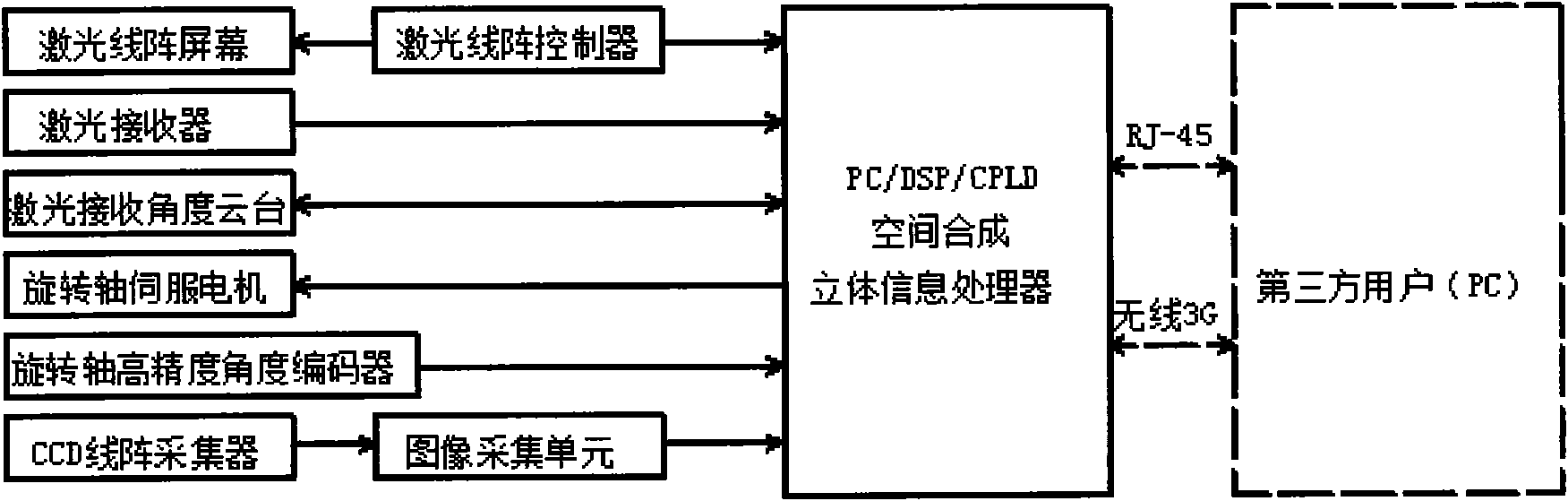

Rotary laser visual linear array space identification and positioning system

InactiveCN101852607AImprove environmental adaptabilityReduce the impactOptical rangefindersPhotogrammetry/videogrammetryThird partyColor image

The invention relates to a rotary laser visual linear array space identification and positioning system, which belongs to the field of mode identification and artificial intelligence. The system comprises a laser linear array emission module, a holder laser-receiving module, a CCD linear array acquisition module, a principal-axis rotation module, a three-dimensional information processor and an auxiliary module. The laser linear array is used for ranging, the CCD linear array is used for acquiring colors, the high-subdivision principal-axis rotation module is used for carrying out 360-degree rotary scanning to acquire high-precision three-dimensional position data and two-dimensional color images, the three-dimensional information processor is used for synthesizing the three-dimensional position and color data (X, Y, Z, RGB) of all the pixel points in the rotating space, and the synthesized data can be directly used for mixing identification and intelligence applications, or can be outputted to a third-party user via RJ45 or wireless 3G. The system is characterized by high precision, wide scanning range, high environment adaptability, wide application range, simple implementation technique and the like.

Owner:崔一 +1

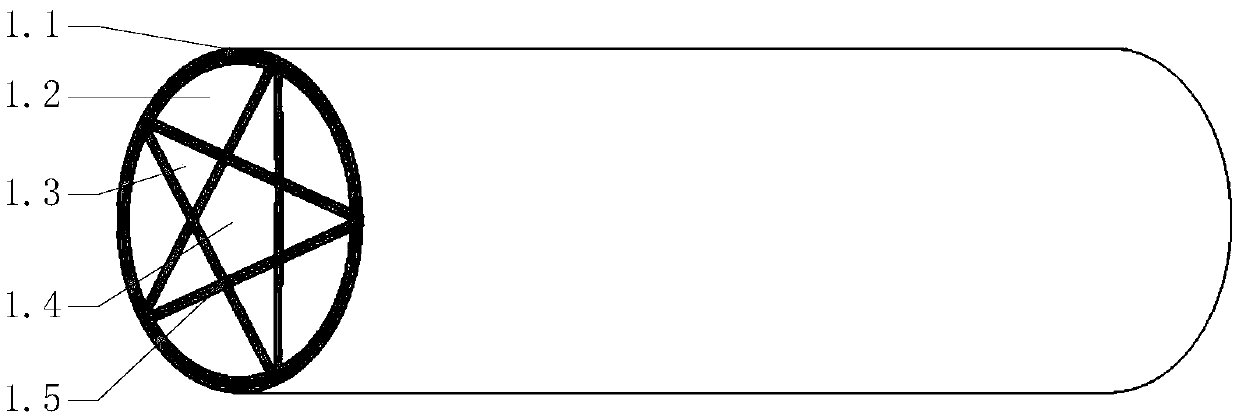

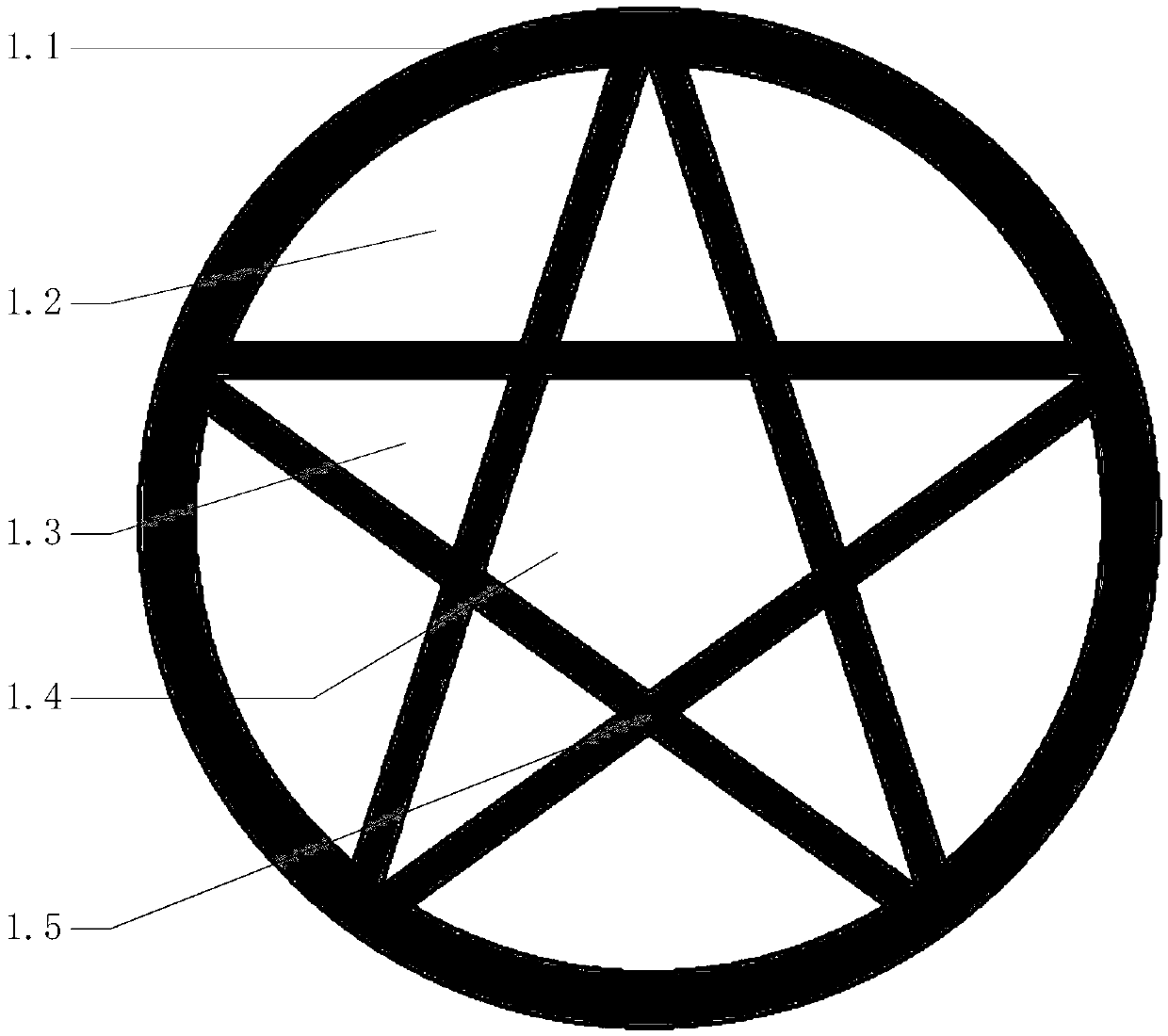

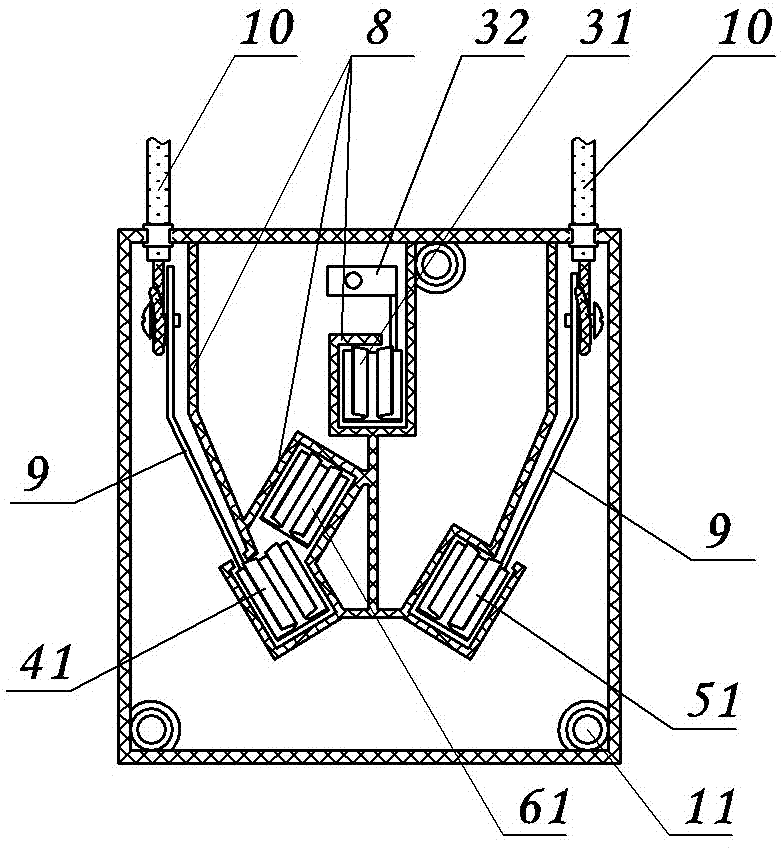

Method for manufacturing terahertz waveguide preform by means of 3D printing technology

InactiveCN105500719AImprove the structural design dimensionVast worldAdditive manufacturing apparatusOptical waveguide light guideAcute angle3d printer

The invention provides a method for manufacturing a terahertz waveguide preform of an acute angle structure by means of a 3D printing technology. The method comprises the steps that firstly, computer cartographic software is adopted for drawing a stereo structure of the terahertz waveguide preform, then, and printing is performed by means of a 3D printer piece by piece to form the terahertz waveguide preform. The method is applicable to a majority of terahertz waveguide materials including metal or polymer and composite metamaterials thereof. Terahertz waveguide (shown in the figure) of various special-shaped cross-section structures of the acute-angle structure such as a triangle and a pentagram, the structural design freedom degree is increased, embedding of high-melting metal wires is facilitated, and the longitudinal structure of the waveguide can also be changed. The method is simple, convenient to implement and low in cost, the cross-section structures of the manufactured waveguide are abundant, the performance is excellent, and the method is applicable to large-scale industrial production and laboratory investigation, exploration and application.

Owner:BEIJING JIAOTONG UNIV

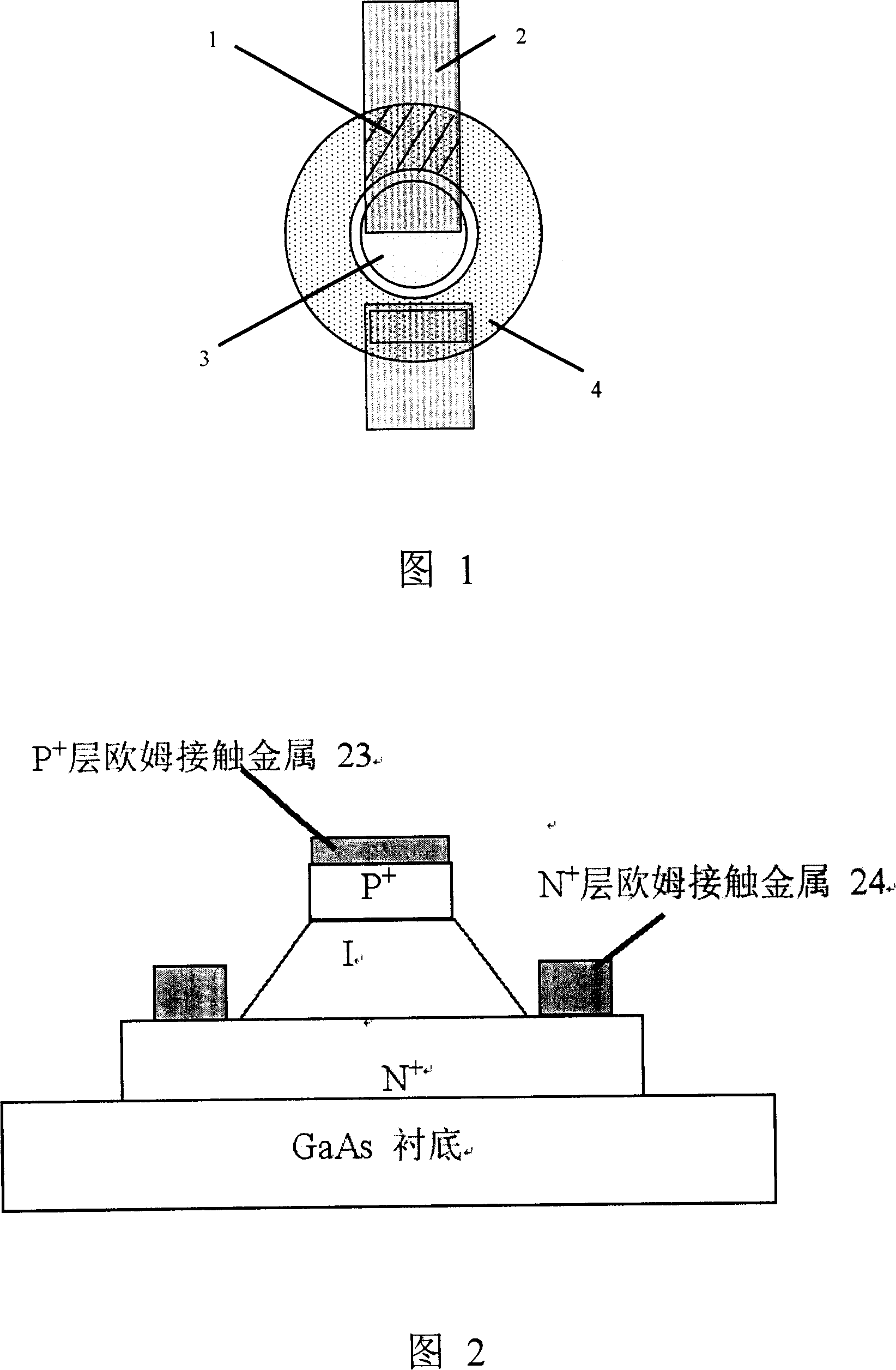

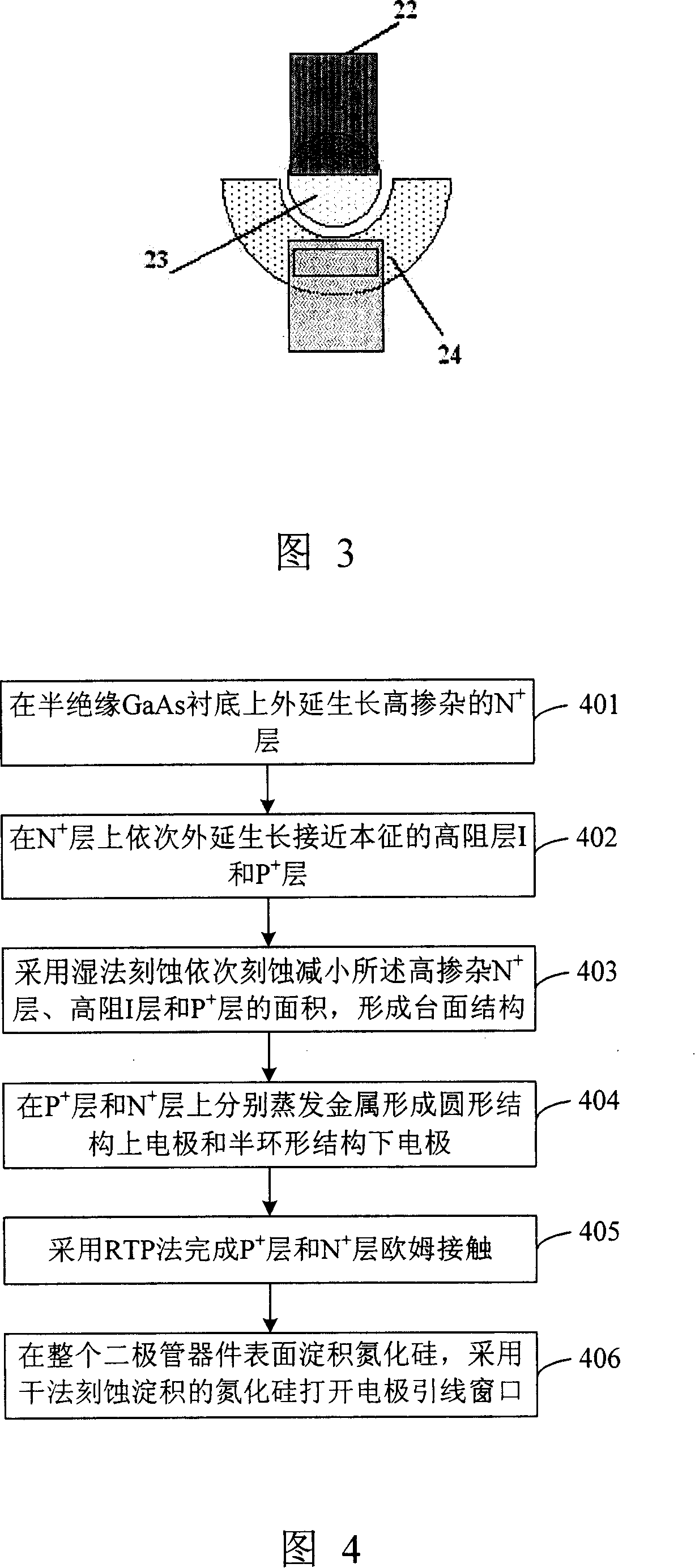

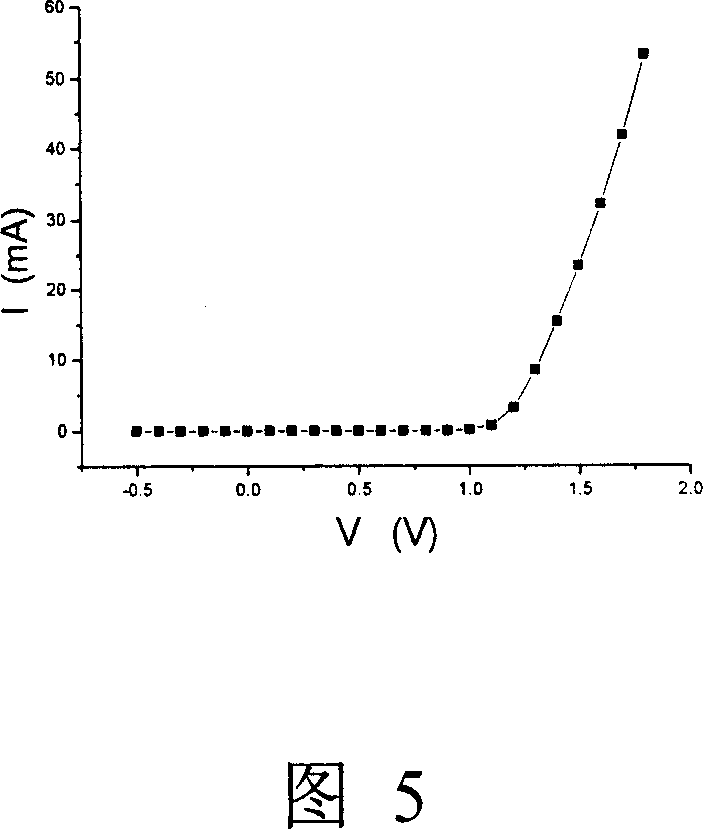

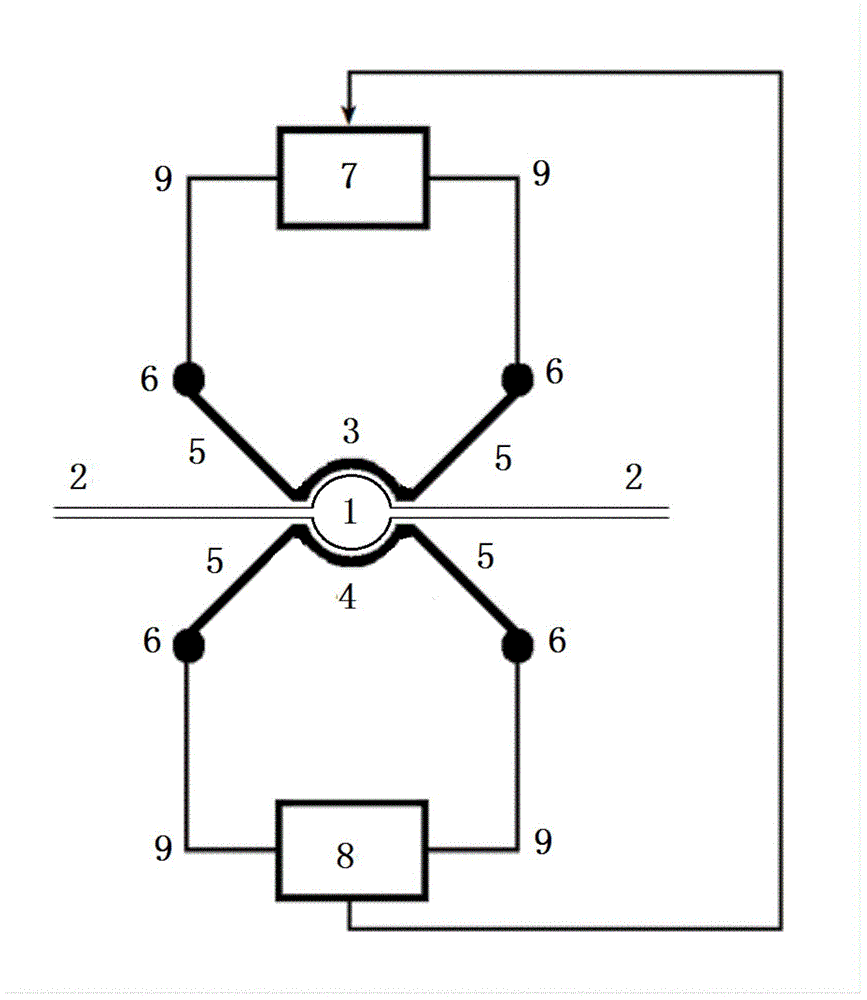

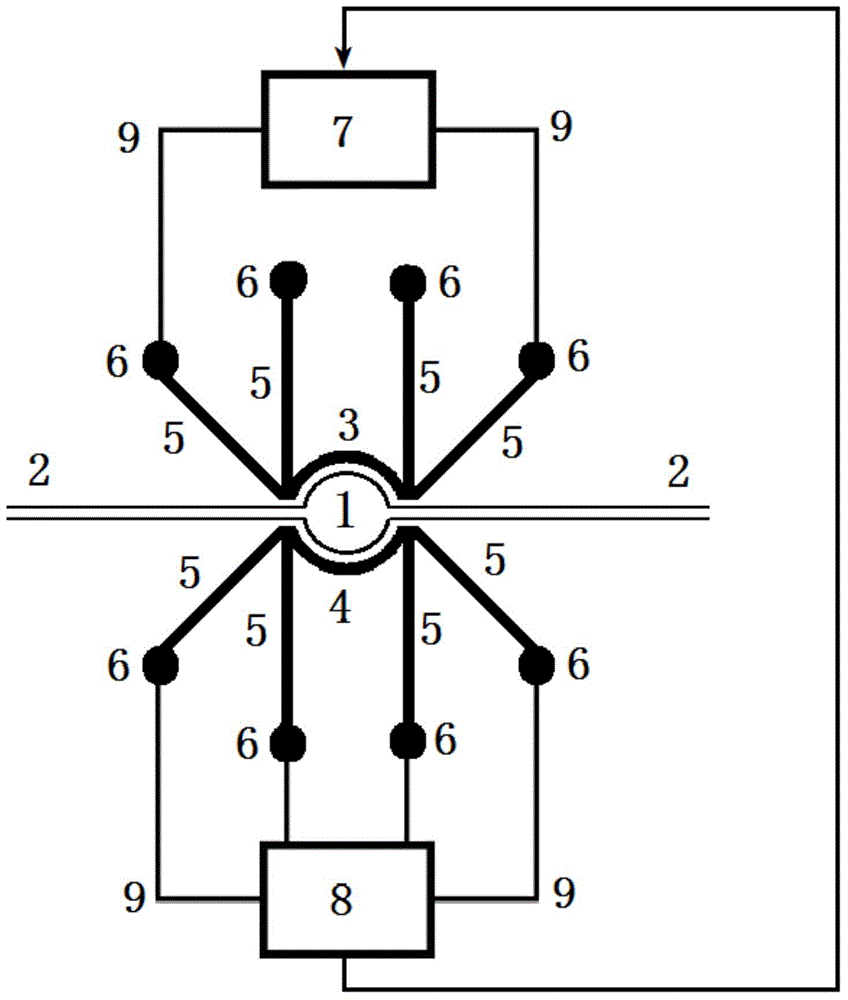

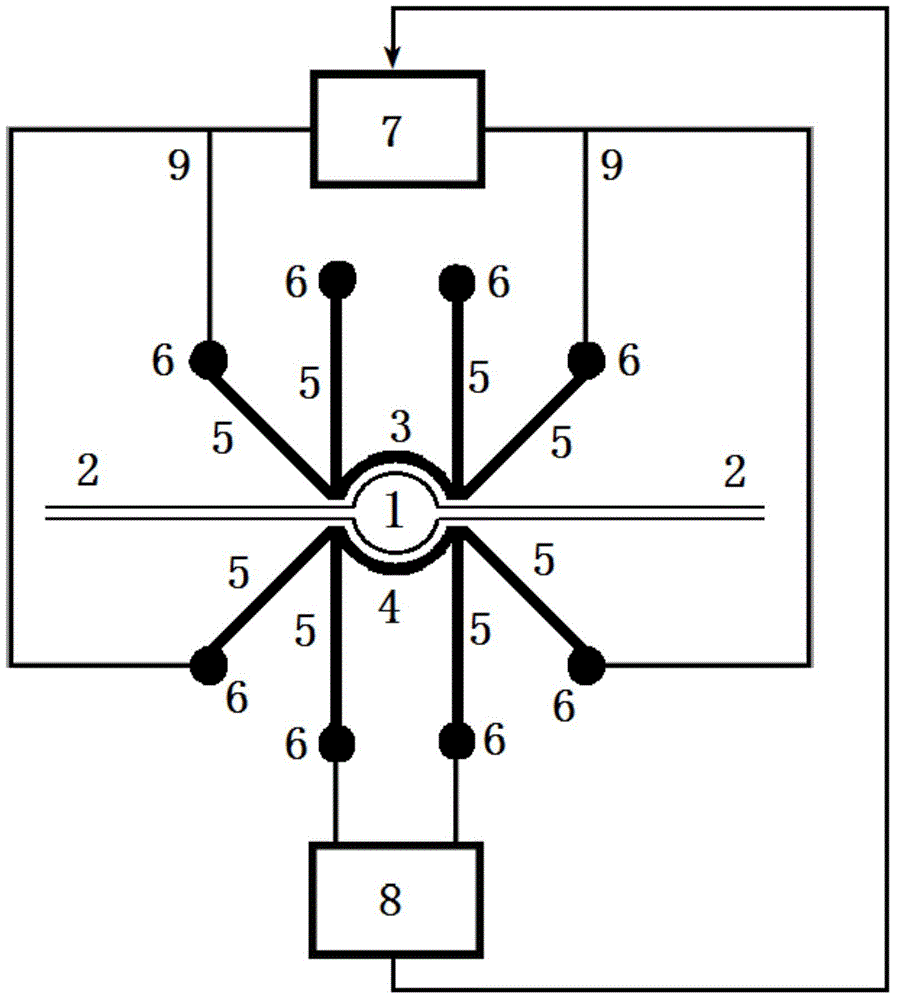

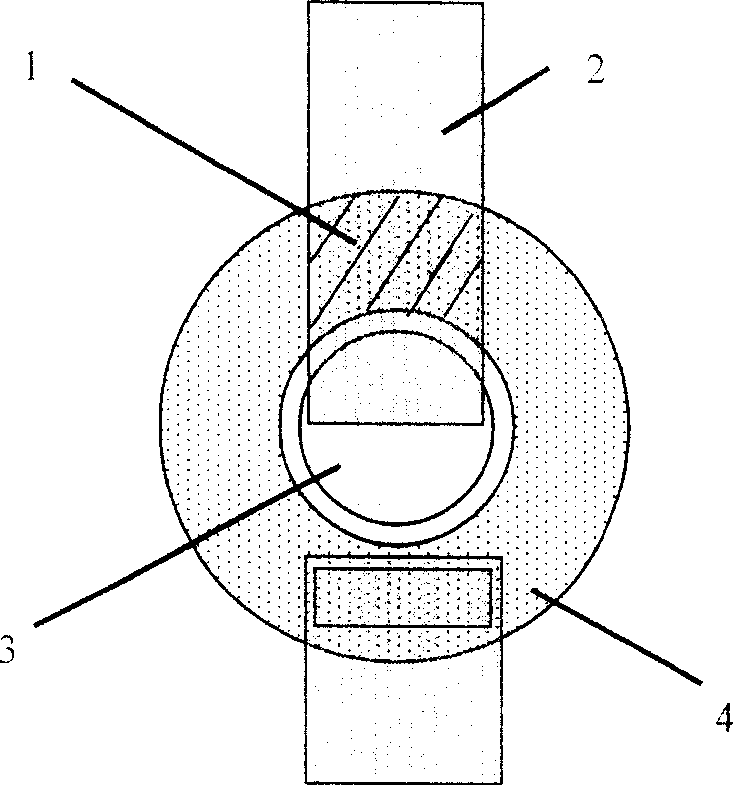

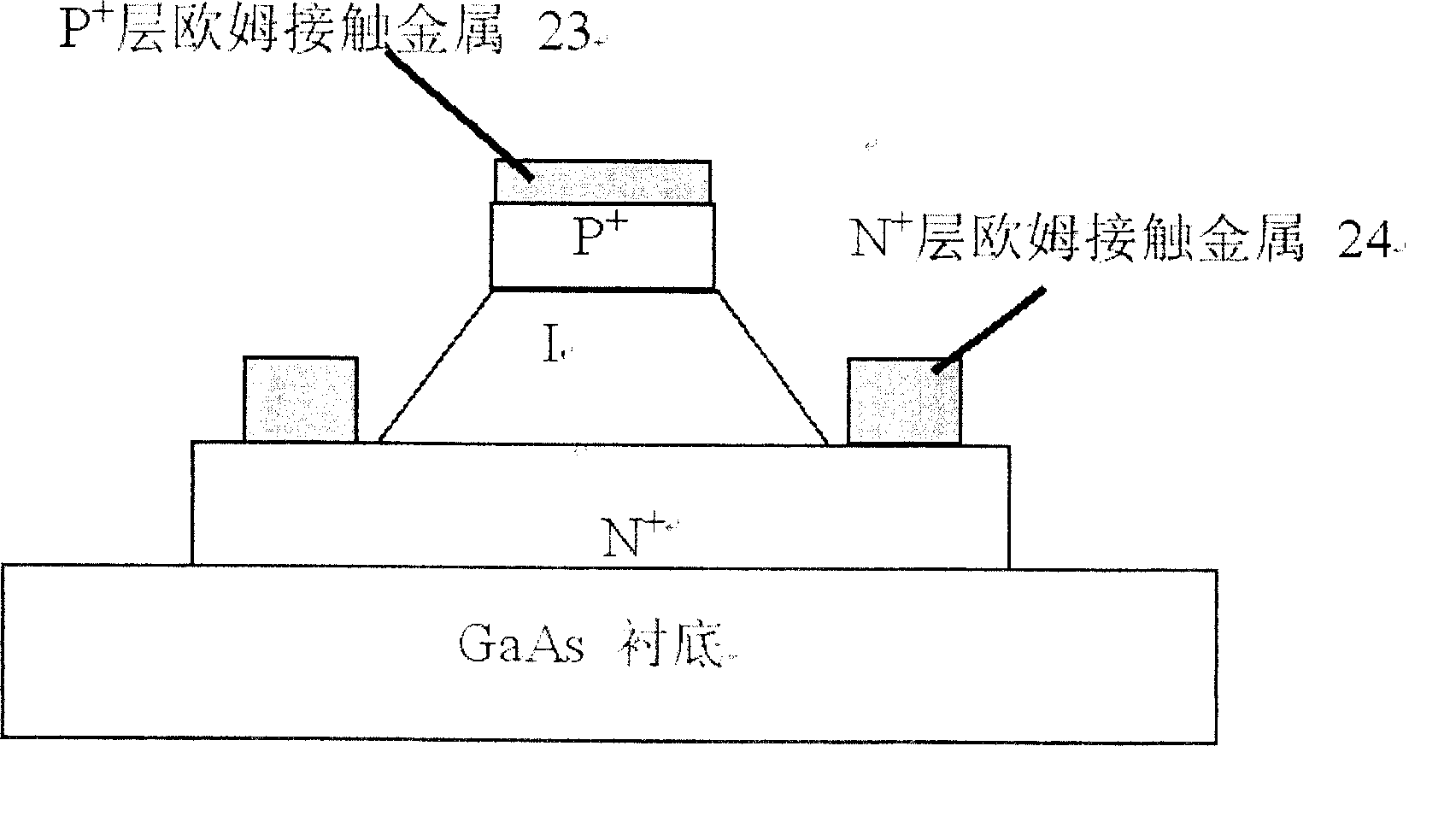

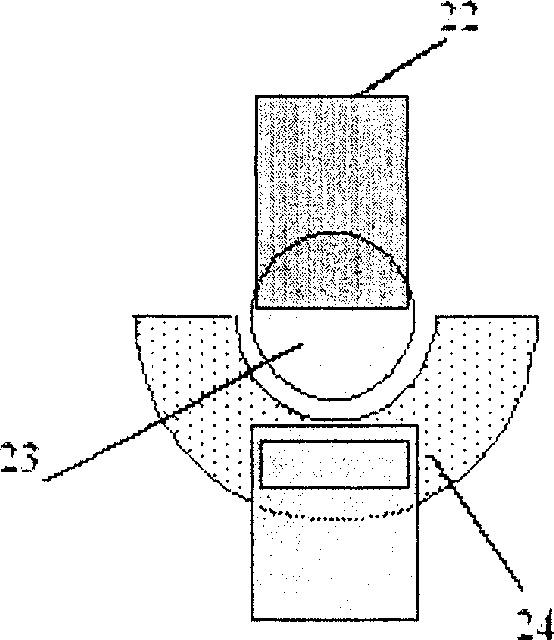

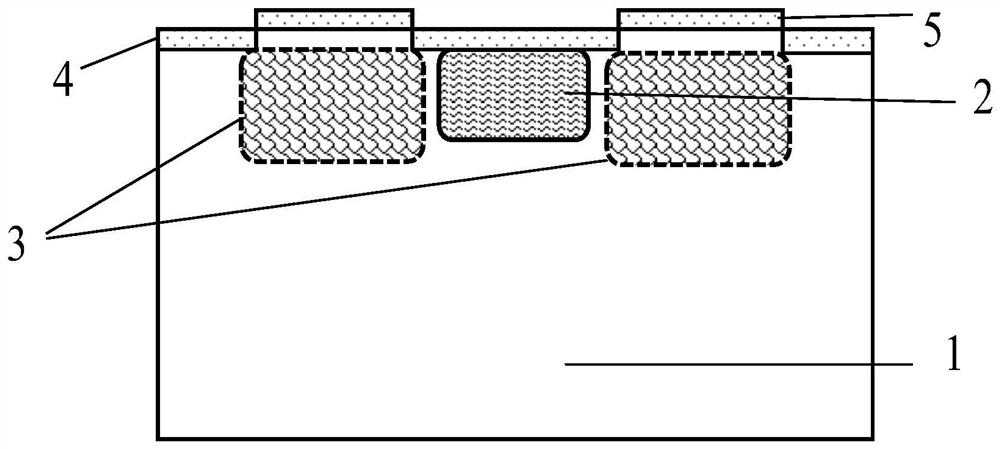

Gallium arsenide PIN diode and preparation method thereof

ActiveCN101140955AReduce parasitic capacitanceRealize the process is simpleSemiconductor/solid-state device manufacturingSemiconductor devicesMaterials scienceAir bridge

The invention discloses a GaAs PIN diode, which comprises: a semi-insulating GaAs underlay for supporting the whole GaAs diode; a high doped layer N growing in extension on the semi-insulating GaAs underlay, resistive formations I and P close to eigen growing in extension in turn on the high doped layer N; By wet process and etching, the areas of the said high doped layer N, resistive formations I and P reduced in turn to form a mesa structure; a top electrode of the round structure formed by metal evaporator on layer P; a semi-orbicular bottom electrode formed by metal evaporator on layer N. The invention also discloses a manufacturing method of GaAs PIN diode. The invention efficiently lowers the parasitic capacitance of the PIN diode without increasing the difficulty of the process and simultaneously greatly shortens the microstrip line connected with the top electrode. The spurious inductance brought by the invention can be greatly reduced or even omitted without using the air-bridge process. The invention has the advantages of easy making, better high frequency characteristic, which is easy to realize the single scale integration.

Owner:北京中科微投资管理有限责任公司

Semi-conductor adhesive and preparation method thereof

ActiveCN101210162AImprove reliabilityUniform electric fieldNon-macromolecular adhesive additivesEpoxy resin adhesivesWater bathsLow temperature curing

The invention relates to a semiconductor adhesive used for electric apparatuses, which contains, by weight percentage, an adhesive material 55 to 65% which contains an epoxy adhesive 79 to 81%, a curing agent 7 to 9% and a toughening agent 11 to 13%; a packing material 31 to 41% which contains graphite 58 to 62% and kaolin 38 to 42%; and a low-temperature curing agent 2 to 4%. The epoxy adhesive is heated to fluid by a 50-60-DEG C oven; the fluidic epoxy adhesive is added into a beaker and then in a constant-temperature water bath at 50-60 DEG C; the curing agent, the toughening agent and a diluting agent are sequentially added into the beaker while stirring until stirring uniformly; and the packing material is added and stirred uniformly. The invention solves the technical problems of the prior arts such as poor shielding reliability and poor safety. The invention has the advantages of simple implementation process and high production efficiency, and can be used for electrostatic shielding or for formation of semiconductor layer.

Owner:XIAN XIDIAN TRANSFORMER

Micro heater

The invention provides a micro heater, which belongs to the field of micro-electro-mechanical system. The micro heater includes a reaction chamber, a sample micro channel leading to the reaction chamber, and at least two circular-arc micro channels having the same radian. The reaction chamber is surrounded by the at least two circular-arc micro channels having the same radian. The at least two circular-arc micro channels are not directly contacted to each other and to the reaction chamber. Compared with the existing heating method by a metal film which is formed on a chip substrate material, the micro heater in embodiments of the invention is easy to produce and low in cost, and can be used in on-chip cell culture, on-chip protein thermal focusing, on-chip polymerase chain reaction (PCR), and the like.

Owner:TECHNICAL INST OF PHYSICS & CHEMISTRY - CHINESE ACAD OF SCI

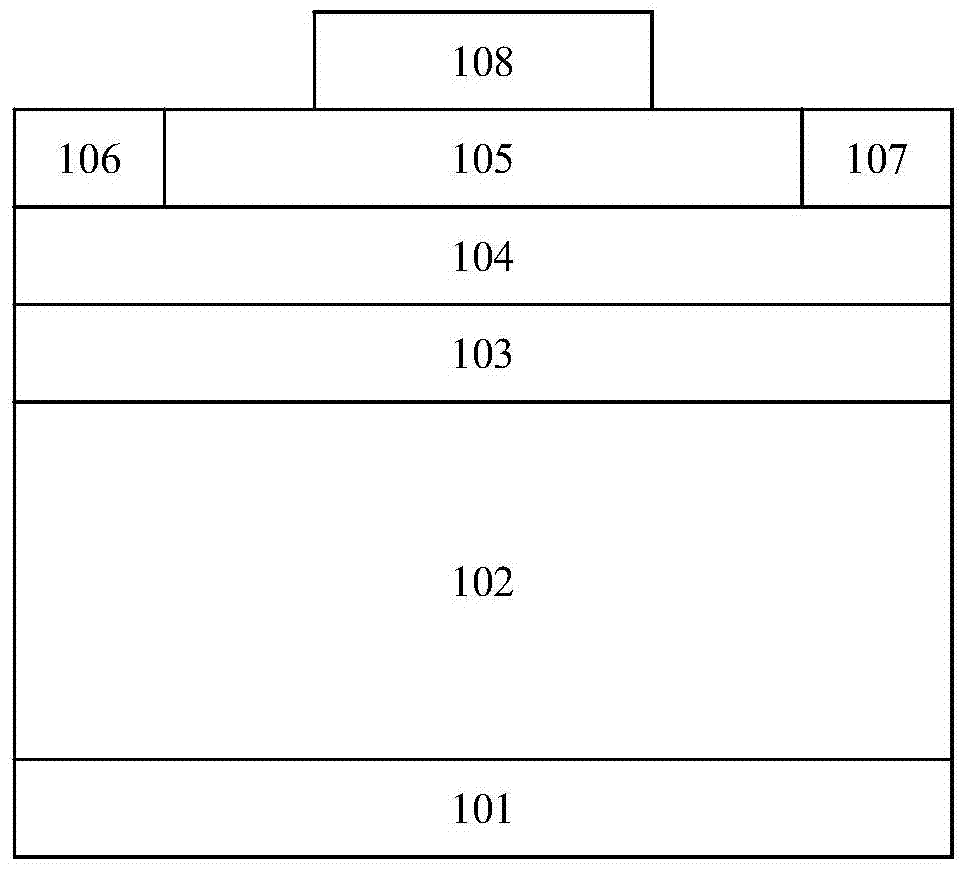

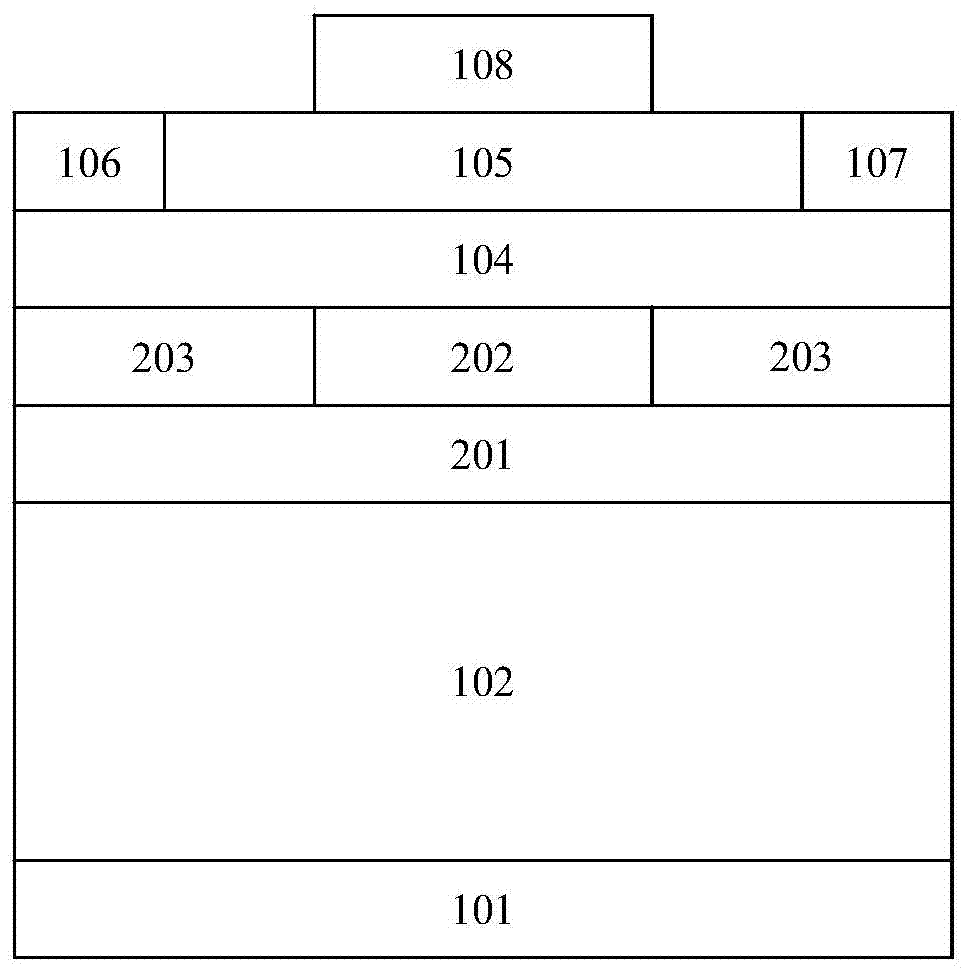

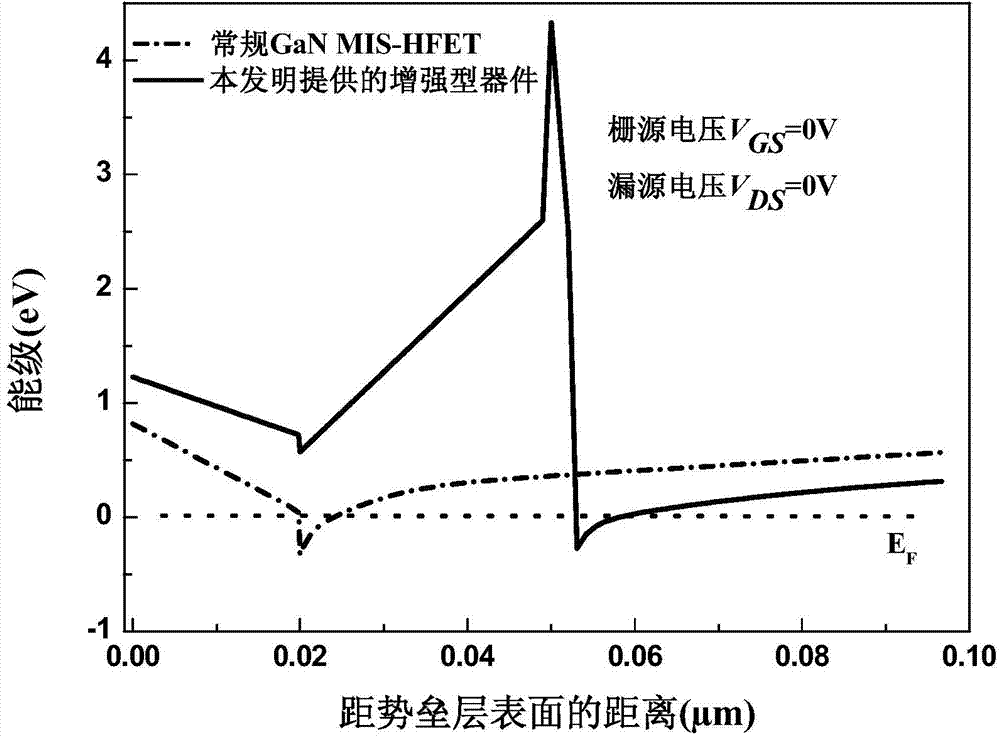

Gallium-nitride-based enhancement type heterojunction field effect transistor with composite channel layer

The invention relates to the technology of semiconductors, and provides a gallium-nitride-based enhancement type heterojunction field effect transistor with a composite channel layer. The problem that an existing gallium-nitride-based heterojunction field effect transistor is a depletion type component, but there is no relatively reliable enhancement type component is solved. According to the technical scheme, compared with an existing GaN MIS-HFET component, an aluminum nitride back barrier layer is arranged between an aluminum indium gallium nitrogen buffer layer and the channel layer of the gallium-nitride-based enhancement type heterojunction field effect transistor with the composite channel layer, and the channel layer is composite. The gallium-nitride-based enhancement type heterojunction field effect transistor with the composite channel layer has the advantages that reliability is improved, and repeatability is high.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

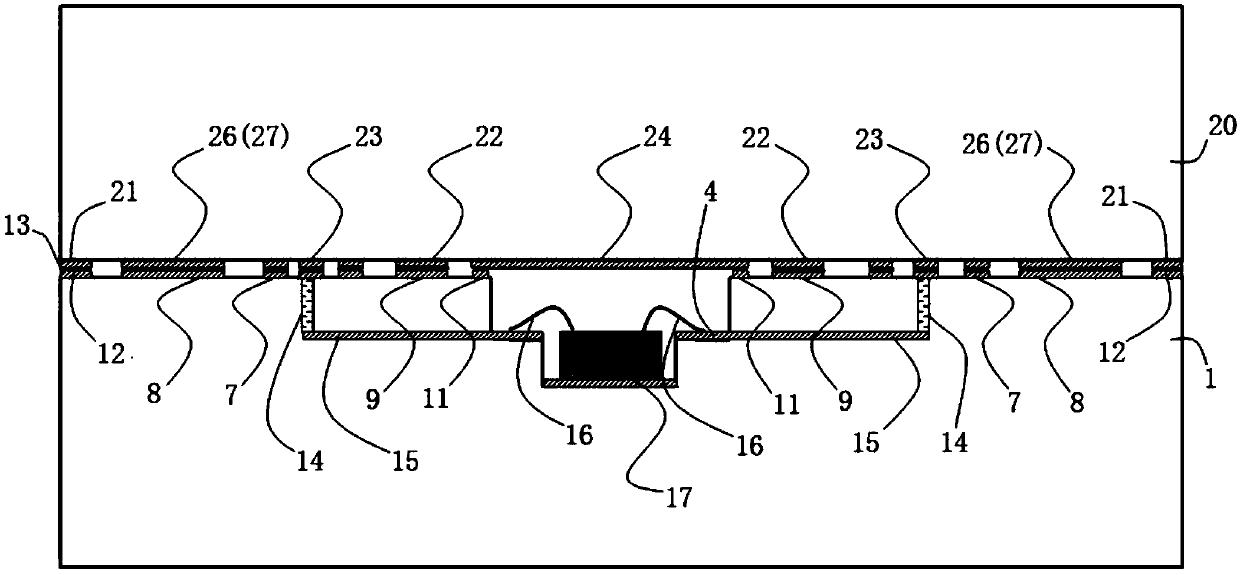

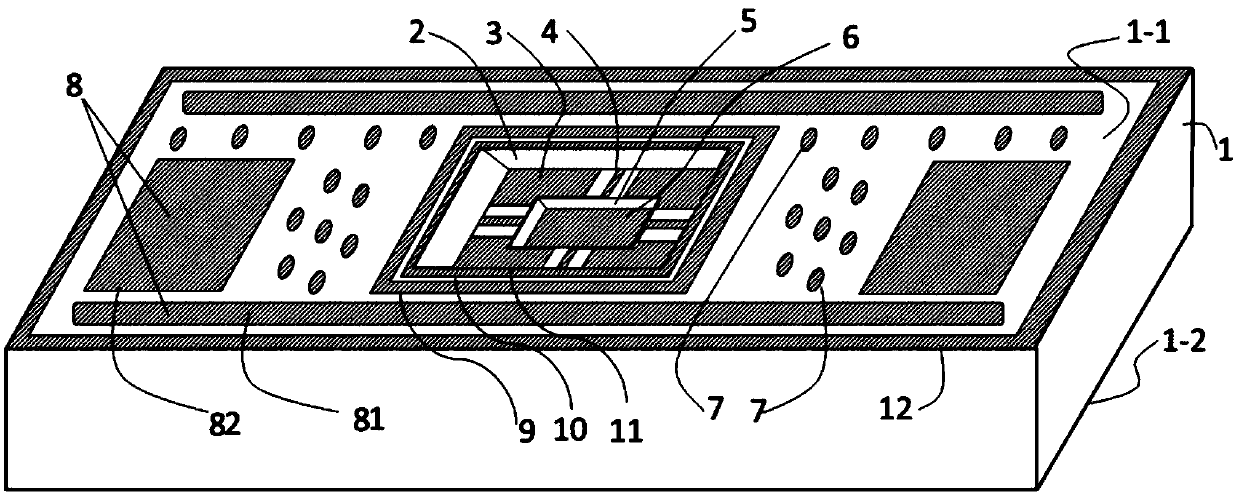

A LTCC substrate three-dimensional stacking structure and a hermetic packaging method thereof

ActiveCN109103165ASimple structureEasy to solveSemiconductor/solid-state device detailsSolid-state devicesHigh densityWeld seam

A LTCC substrate three-dimensional stacking structure and a hermetic packaging method thereof are disclosed. The three-dimensional stacking structure comprises components, first and second LTCC substrates, first, second, third, fourth, fifth and sixth metal film layer, and first and second pads. The hermetic packaging method comprises the following steps of: processing a substrate with a ceramic dummy layer on a stacked assembly surface by a conventional LTCC proces; grinding and leveling the surface of the assembly surface; fabricating metallized pads for solder welding on the assembly surface by a post-firing process; prefusing the solder in the welding area and performing cleaning; assembling the components on the substrate; aligning the stacking assembling surfaces of the substrates with assembled components and performing heating to realize sol bonding; cleaning the weld seam and supplementing the solder; testing the airtightness of the stacked LTCC substrates, and welding the substrates until the substrates are qualified if the airtightness is not up to the standard. The invention can realize the vertical interconnection between the local hermetic package of the substrate and the substrate including the high-frequency signal, and provides a simple and reliable solution for the high-density integration.

Owner:SOUTHWEST CHINA RES INST OF ELECTRONICS EQUIP

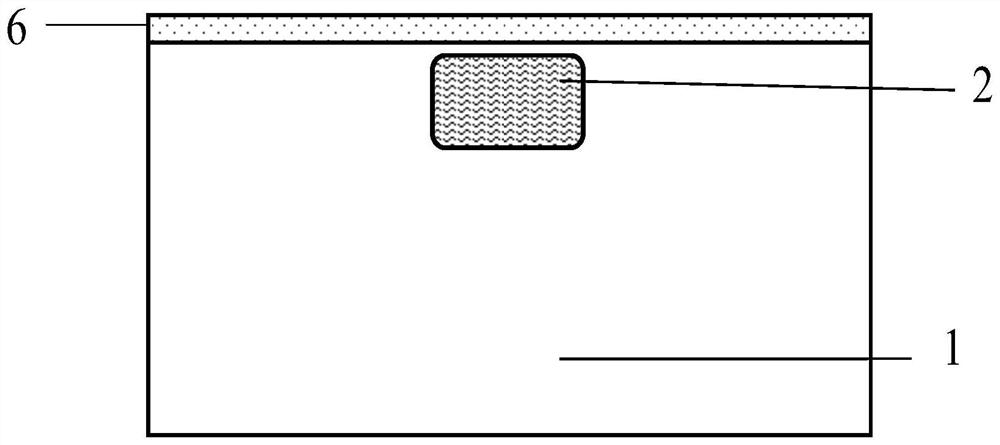

Dielectric filter and 5G communication equipment

PendingCN109860966ADoes not affect mechanical strengthRealize the process is simpleResonatorsResonant cavityDielectric resonator antenna

The invention discloses a dielectric filter. The dielectric filter comprises at least three dielectric resonators in successive connection; each dielectric resonator comprises a body composed of a solid-state dielectric material and a conductive layer covered on a body surface; a groove structure covered with the conductive layer is arranged on the body surface of at least one dielectric resonators except the dielectric resonators at the head and end locations, thereby realizing the capacitive cross-coupling; the groove structure and the located dielectric resonator commonly form a secondary-mode resonant cavity. The invention further discloses a 5G communication device. Compared with the prior art, the cross-coupling with negative polarity can be conveniently realized, the mechanical strength of the filter cannot be reduced, the preparation process is simple, and the mass production is convenient.

Owner:PIVOTONE COMM TECH

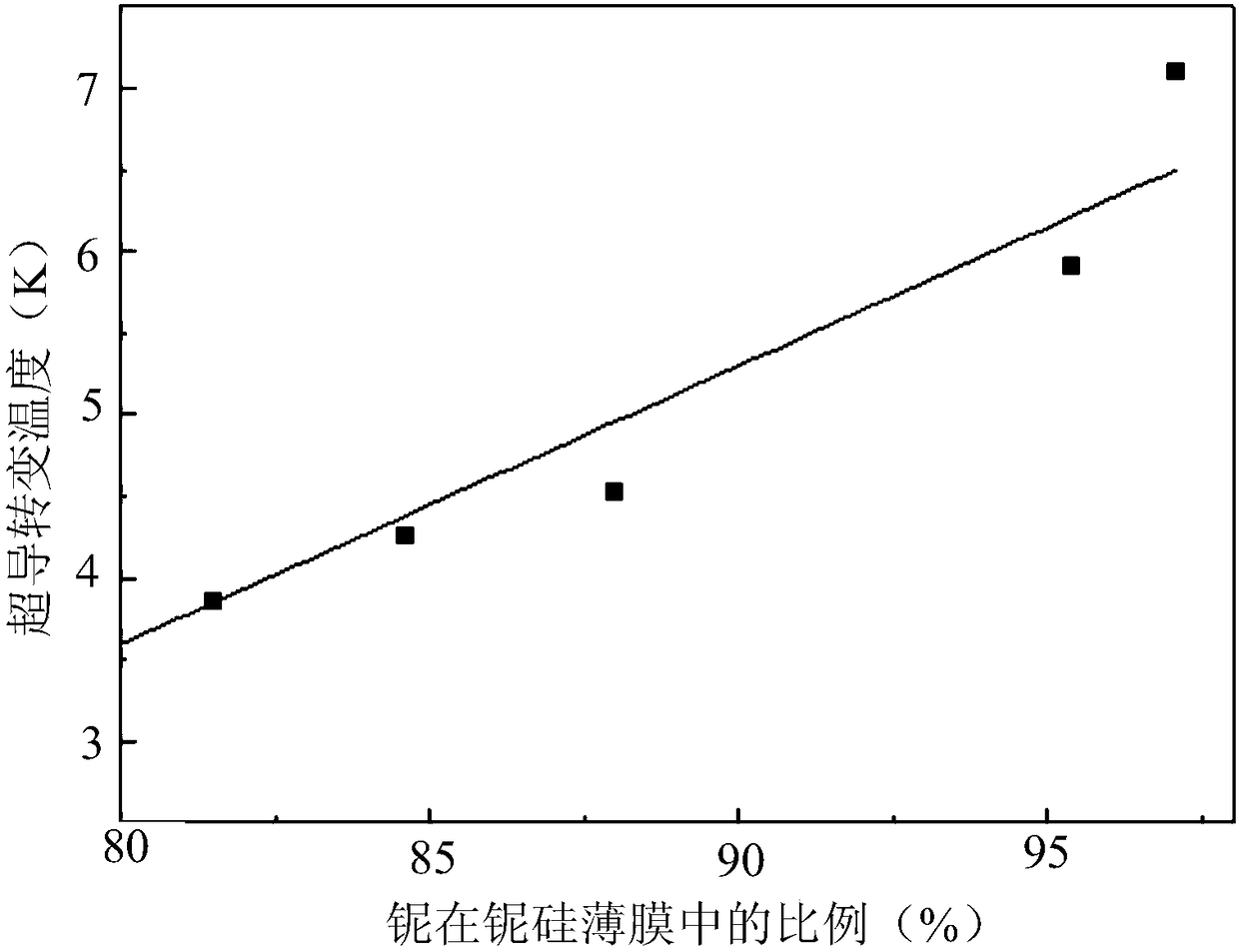

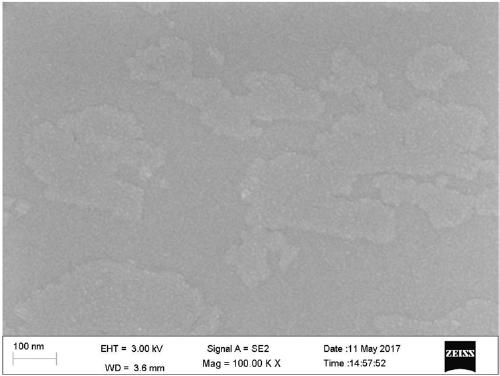

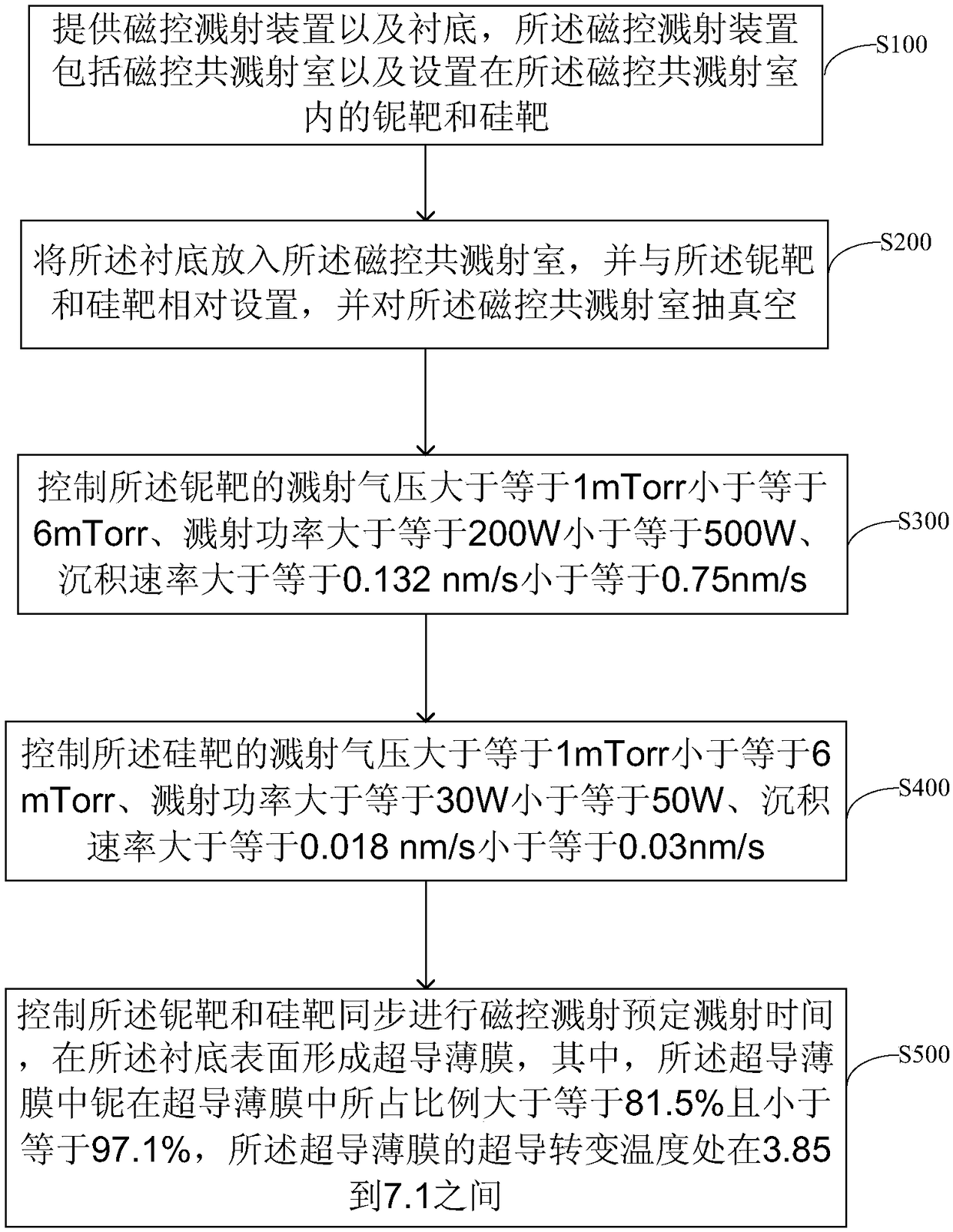

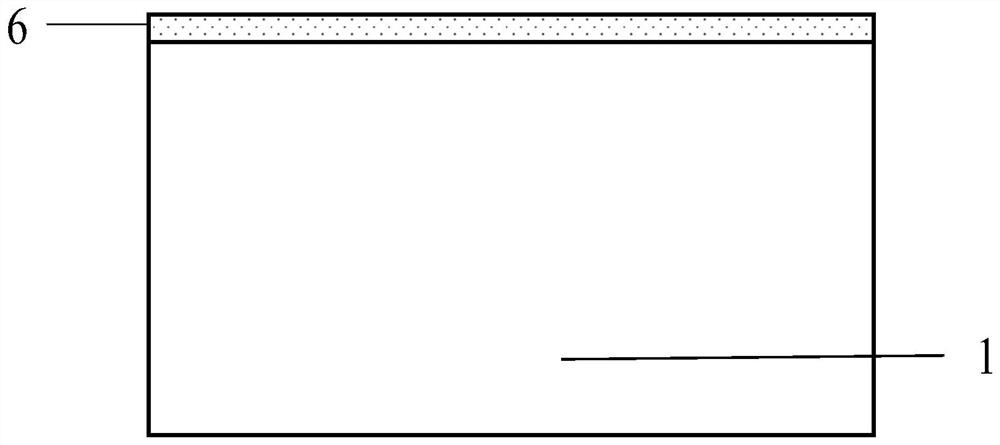

Superconducting film, preparation method thereof, superconducting quantum interference device and inductive superconducting edge detector

ActiveCN109285942ARealize the process is simpleEasy to processVacuum evaporation coatingSputtering coatingNiobiumSuperconducting transition temperature

The invention relates to a superconducting film. The components of the superconducting film includes niobium and silicon, wherein the proportion of niobium in the superconducting film is greater thanor equal to 81.5% and less than or equal to 97.1%, and the superconducting transition temperature of the superconducting film ranges from 3.85K to 7.1K. The superconducting film provided by the invention can realize the change of the superconducting transition temperature only by controlling the proportion of niobium, thereby being simple in implementation process, and being easy to process and prepare.

Owner:NAT INST OF METROLOGY CHINA

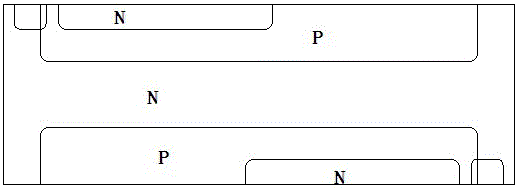

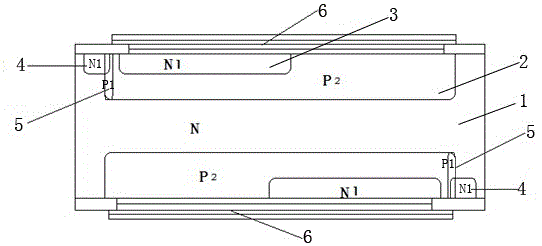

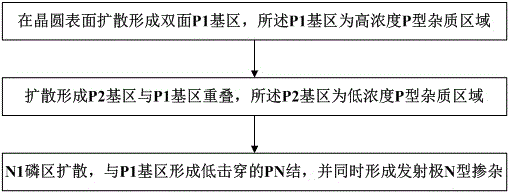

Low-capacitance and low-voltage semiconductor overvoltage protection device

InactiveCN105720108AReduce parasitic junction capacitanceAchieving Low Capacitance Design GoalsThyristorSemiconductor/solid-state device manufacturingCapacitanceHigh concentration

The invention discloses a low-capacity and low-voltage semiconductor overvoltage protection device. The chip layer includes an N-type substrate, and a P2 base region, an N-type region and an emitter N-type doped region are diffused symmetrically above and below the N-type substrate. A P1 base region is diffused in the emitter N-type doped region and the P2 base region, and the P1 and P2 are P-type variable doped base regions. The base area diffusion is divided into two parts to achieve variable doping base area, the P1 base area is a high-concentration P-type doping diffusion, and the P2 base area is a low-concentration P-type doping diffusion, so that the area of high-concentration regions on both sides of the PN junction It is greatly reduced to ensure the low-voltage and over-voltage protection functions, and at the same time, the parasitic junction capacitance of the PN junction is greatly reduced, and the design goal of low capacitance is realized. The process is simple and the cost is low.

Owner:KUNSHAN HAIXIN ELECTRONICS CO LTD

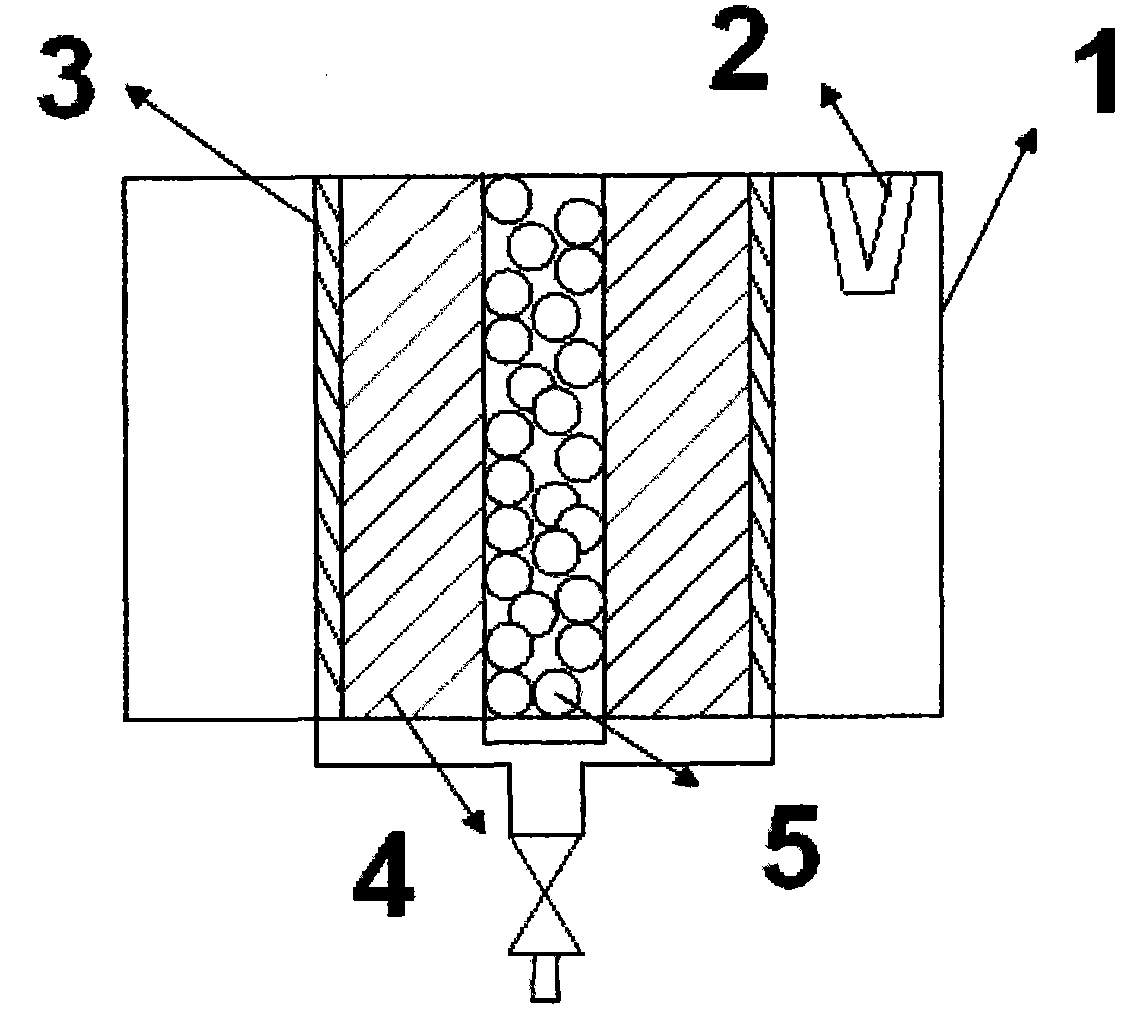

Novel green water purifier

InactiveCN102234164ARealize the process is simpleEasy to operateWater/sewage treatment by irradiationEnergy based wastewater treatmentFiltrationWater flow

A novel green water purifier comprises an outer cylinder, an inner cylinder, a cylinder core, an inlet and an outlet, wherein the inner cylinder is disposed inside the outer cylinder, the inner cylinder core is arranged inside the inner cylinder, the top and the bottom of the inner cylinder are connected with those of the outer cylinder respectively, the upper portion of the outer cylinder is provided with the inlet, the outlet is disposed at the central of the outer cylinder bottom, an outlet of the inner cylinder core communicates with the outlet of the outer cylinder and a filter screen is mounted between the two outlets. The green water purifier is characterized in that the outer cylinder is made from a transparent light transmission material; the outer wall of the inner cylinder is coated with a nonwoven filter blanket processed by nanometer cuprous oxide; the inner cylinder material is active carbon; the filter core is made from porous silica; and the inlet and outlet are both provided with filter screens. The product provided by the invention has a good photocatalytic activity, can be used for filtration, sterilization, deodorization, and decolorization of water, and is green and environment-friendly.

Owner:上海图和环保材料科技有限公司

Sapphire loading microwave cavity for miniature hydrogen atomic clock

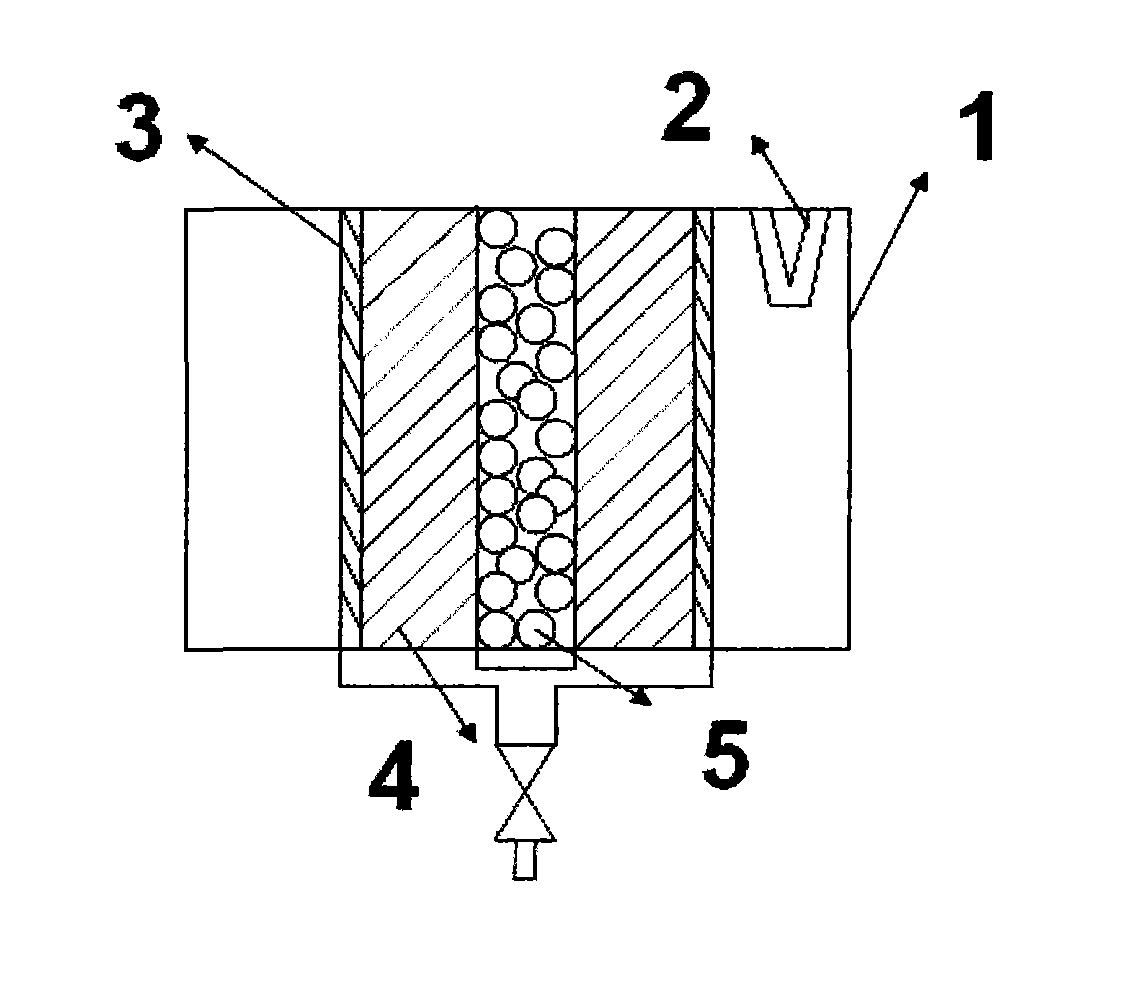

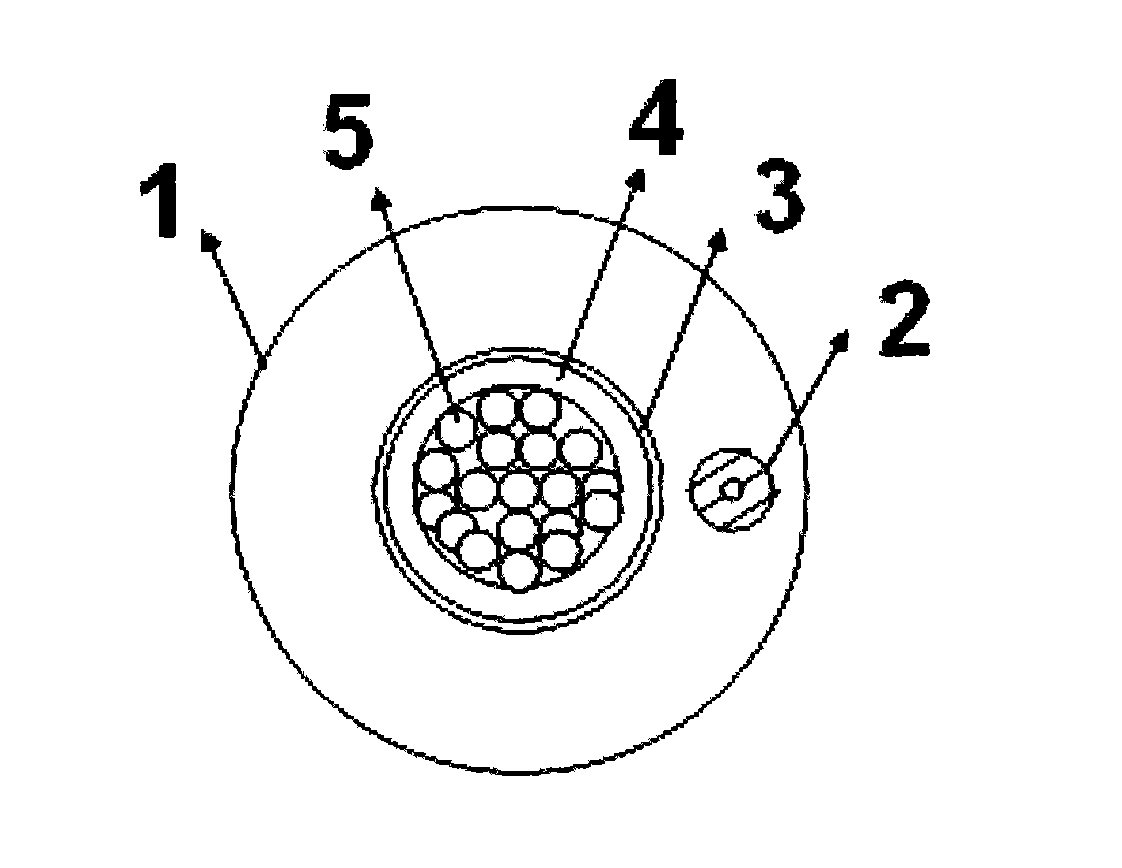

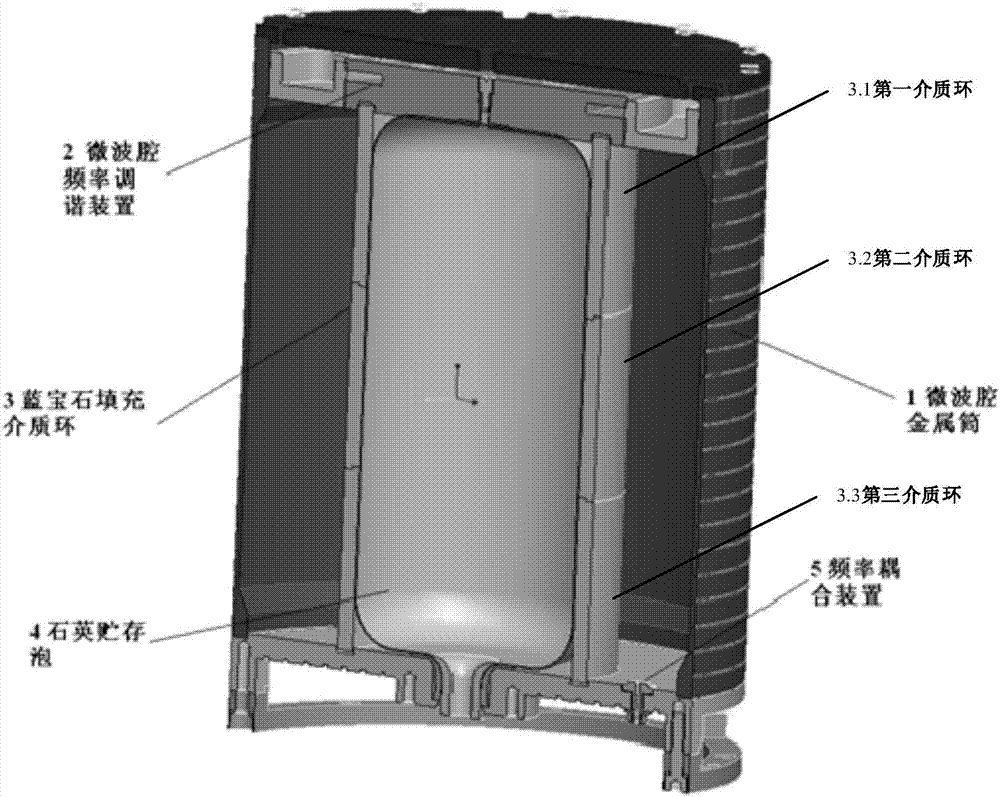

ActiveCN107229213AGuaranteed miniaturizationImprove reliabilityPulse automatic controlApparatus using atomic clocksMicrowave cavityHydrogen

The invention discloses a sapphire loading microwave cavity for a miniature hydrogen atomic clock; the sapphire loading microwave cavity comprises a microwave cavity barrel, sapphire filling medium and a hydrogen atom storage bulb, wherein the sapphire filling medium is arranged in the microwave cavity barrel and includes a first medium ring, a second medium ring and a third medium ring stack-connected in wedge form, and the hydrogen atom storage bulb is arranged in a space formed by the first medium ring, the second medium ring and the third medium ring. Loading and storage are separated for the sapphire microwave cavity with reliability, index performance improvement and cost control considered; the three wedged sapphire stacked medium rings are used as a loading material for the microwave cavity, and the sapphire loading microwave cavity with high reliability and performance is provided. At the premise that the dimensional size of the whole cavity is equal to that of the traditional schemes, inner filling size is increased greatly, miniaturization of the atomic clock is guaranteed, and machine performance and machine environmental adaptability are also improved.

Owner:BEIJING INST OF RADIO METROLOGY & MEASUREMENT

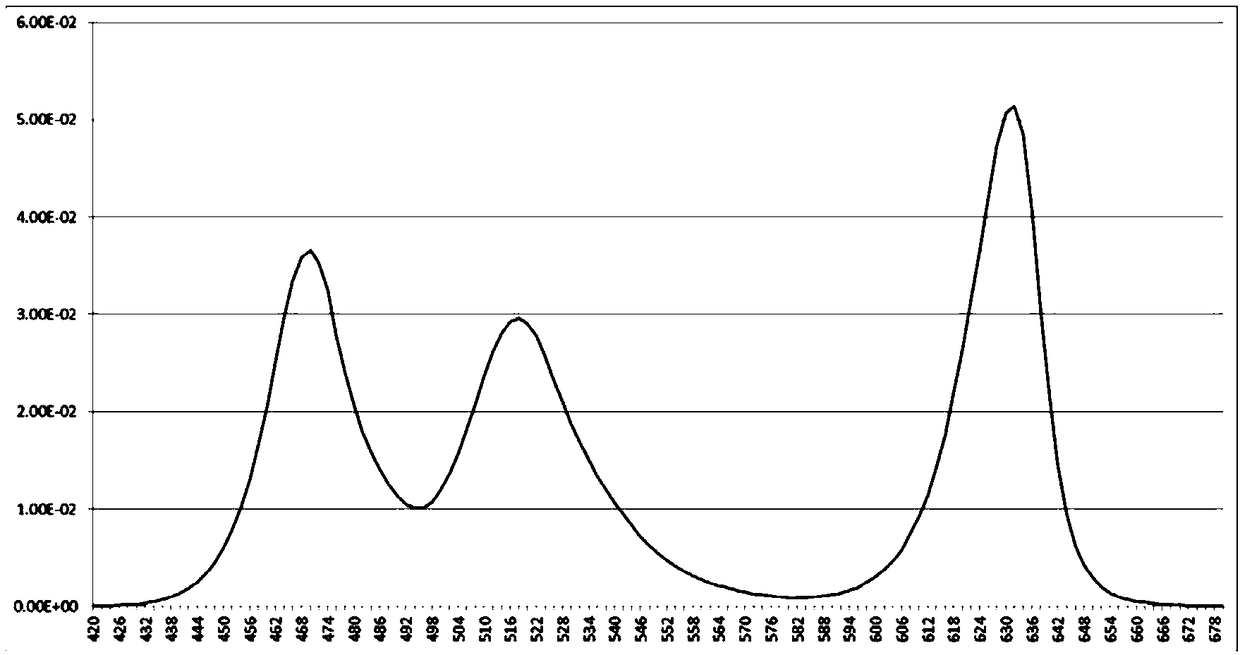

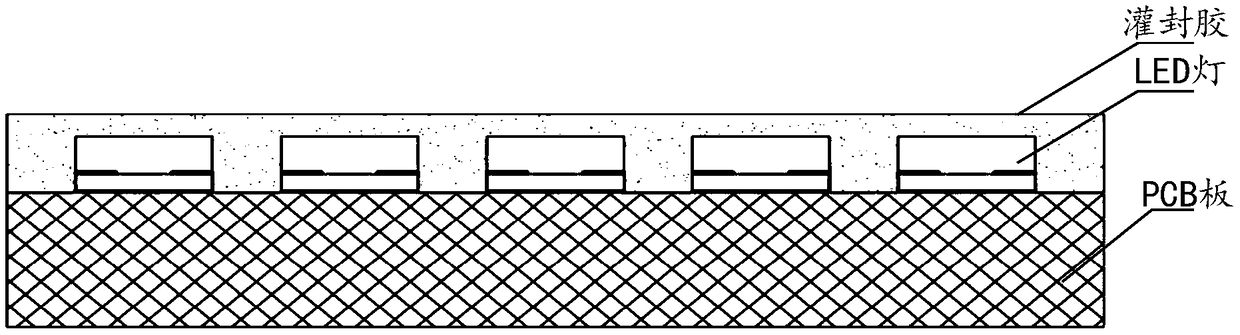

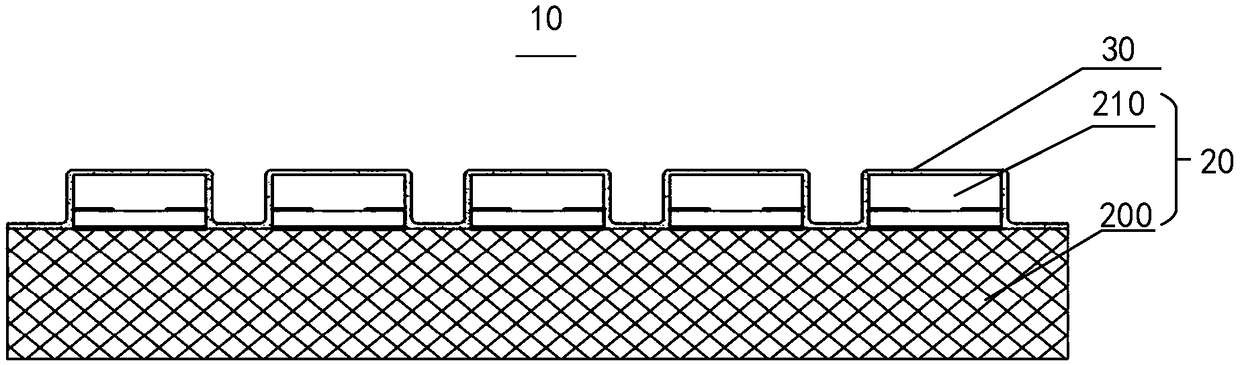

Anti-blue-ray printing ink, display device and manufacturing method of display device

InactiveCN108641473ARealize the process is simpleEasy maintenanceInksIdentification meansDisplay deviceEngineering

The invention provides an anti-blue-ray printing ink, a display device and a manufacturing method of the display device, and relates to the technical field of displayers. The display device comprisesa display screen and an anti-blue-ray printing ink layer formed through the anti-blue-ray printing ink, wherein the anti-blue-ray printing ink layer is manufactured on a light-emitting surface of thedisplay screen. According to the anti-blue-ray printing ink, the display device and the manufacturing method of the display device provided by the invention, the blue ray hazard during the LED (Light-emitting Diode) display screen use process can be effectively reduced, the manufacturing process is simple, the treatment consistency is good, and the display screen can be protected.

Owner:GUANGDONG VTRON TECH CO LTD

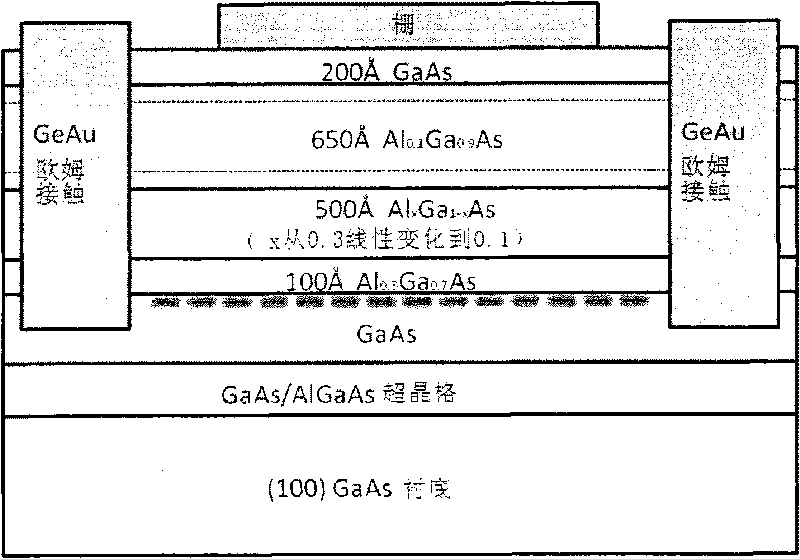

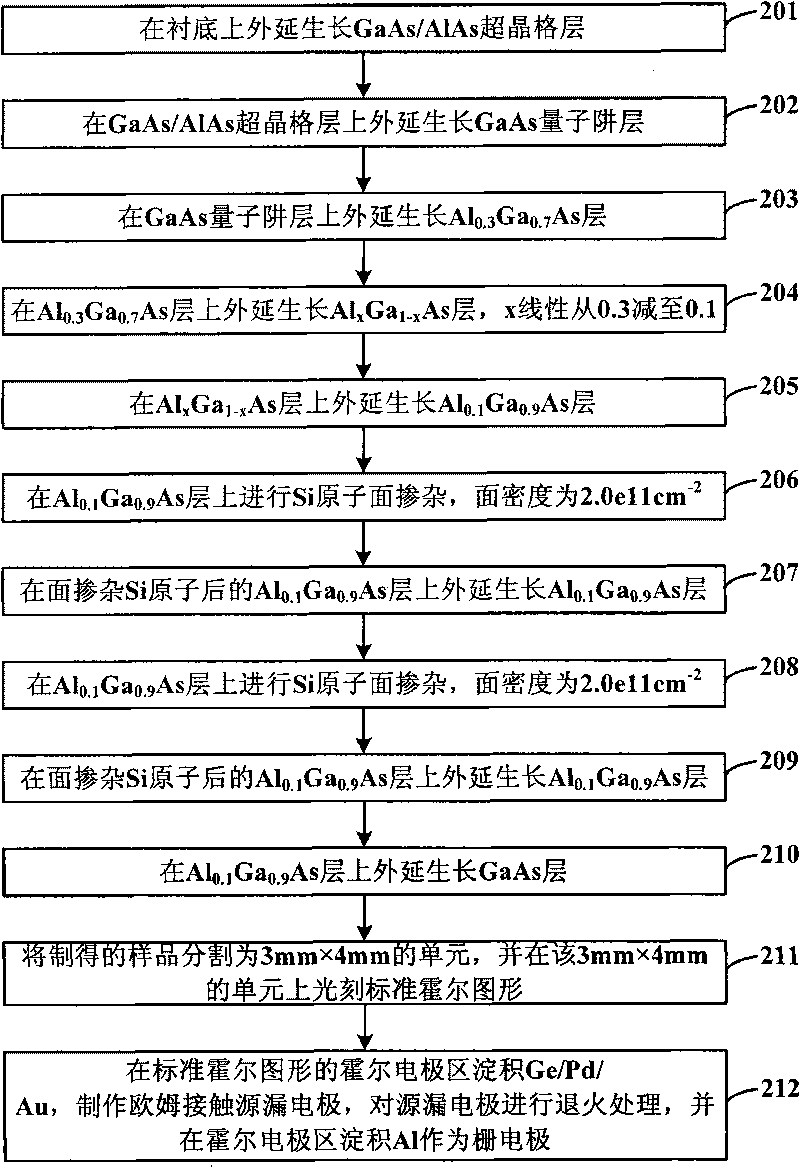

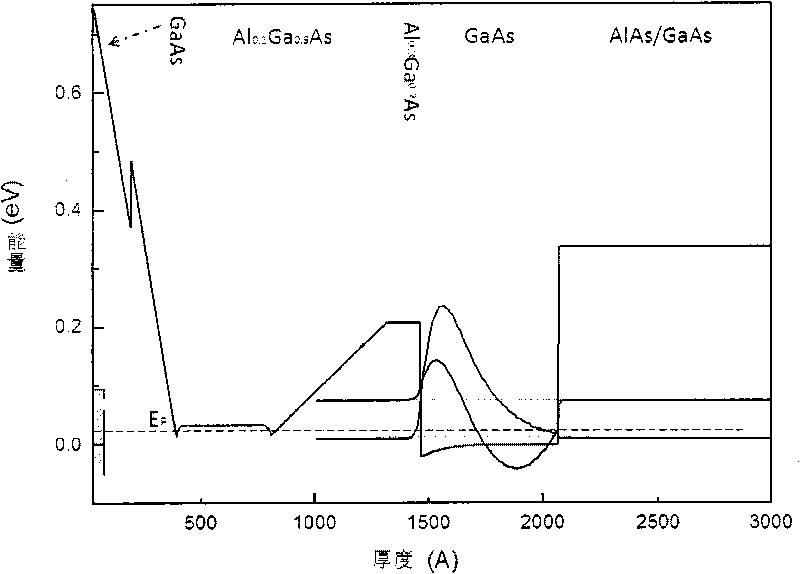

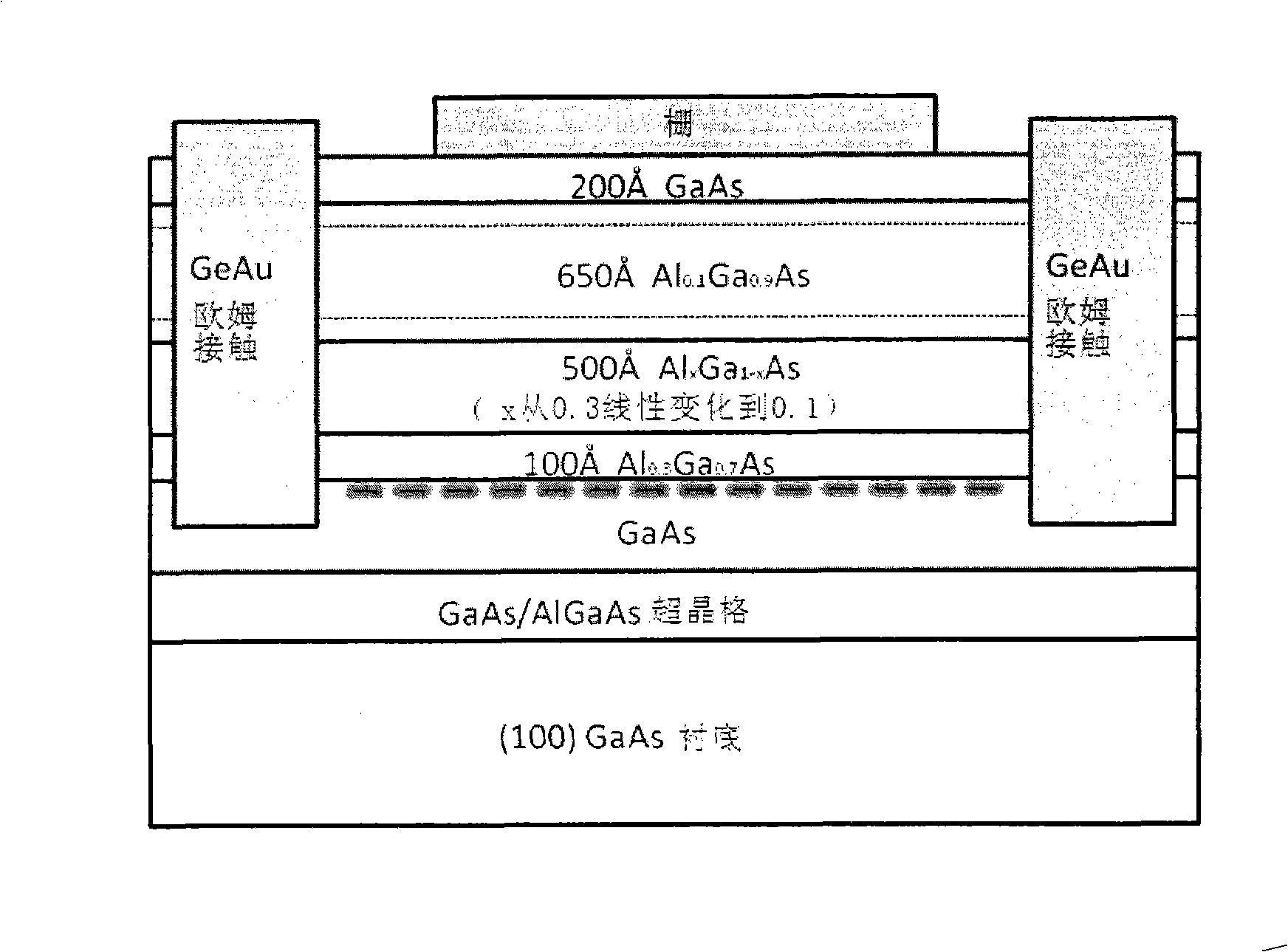

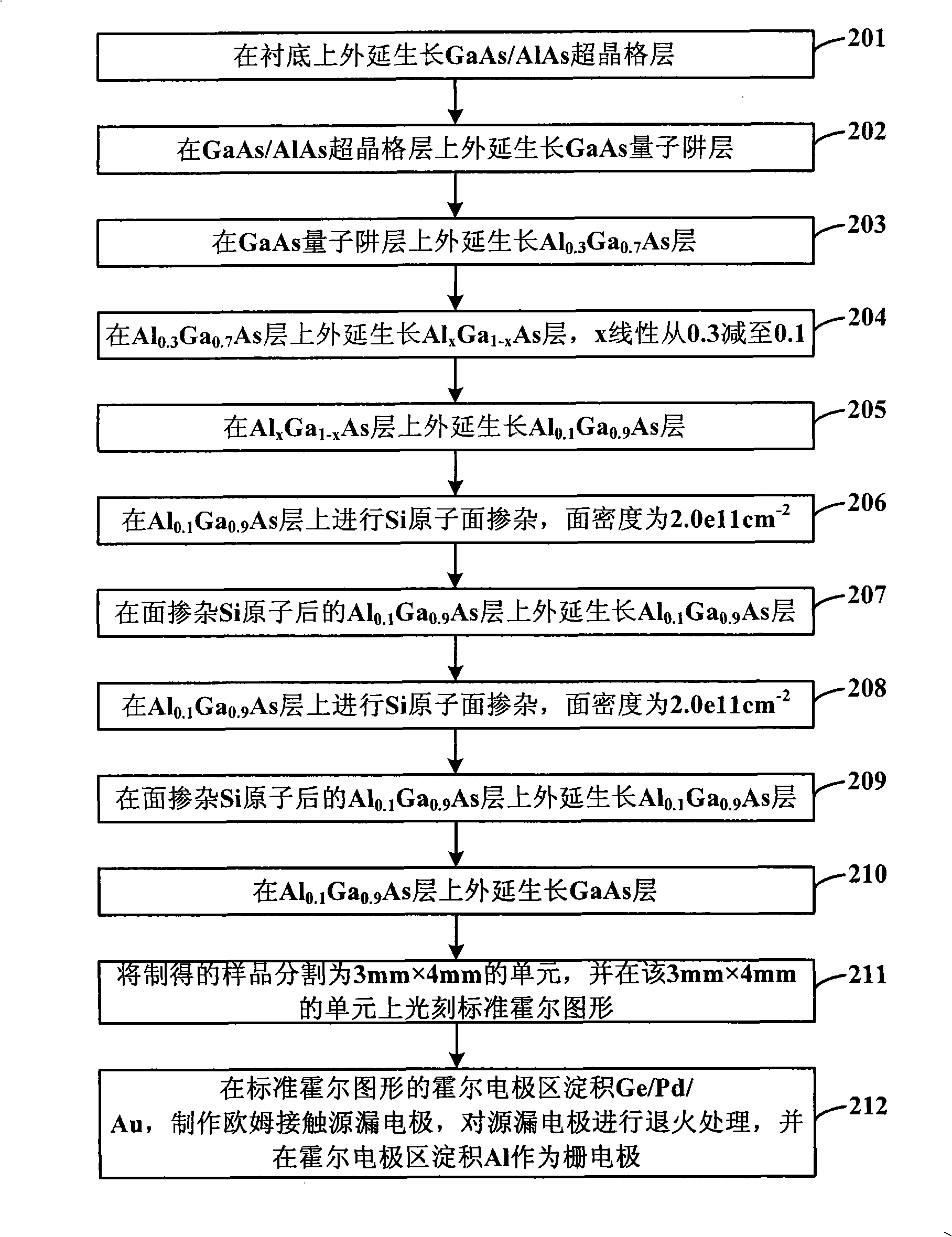

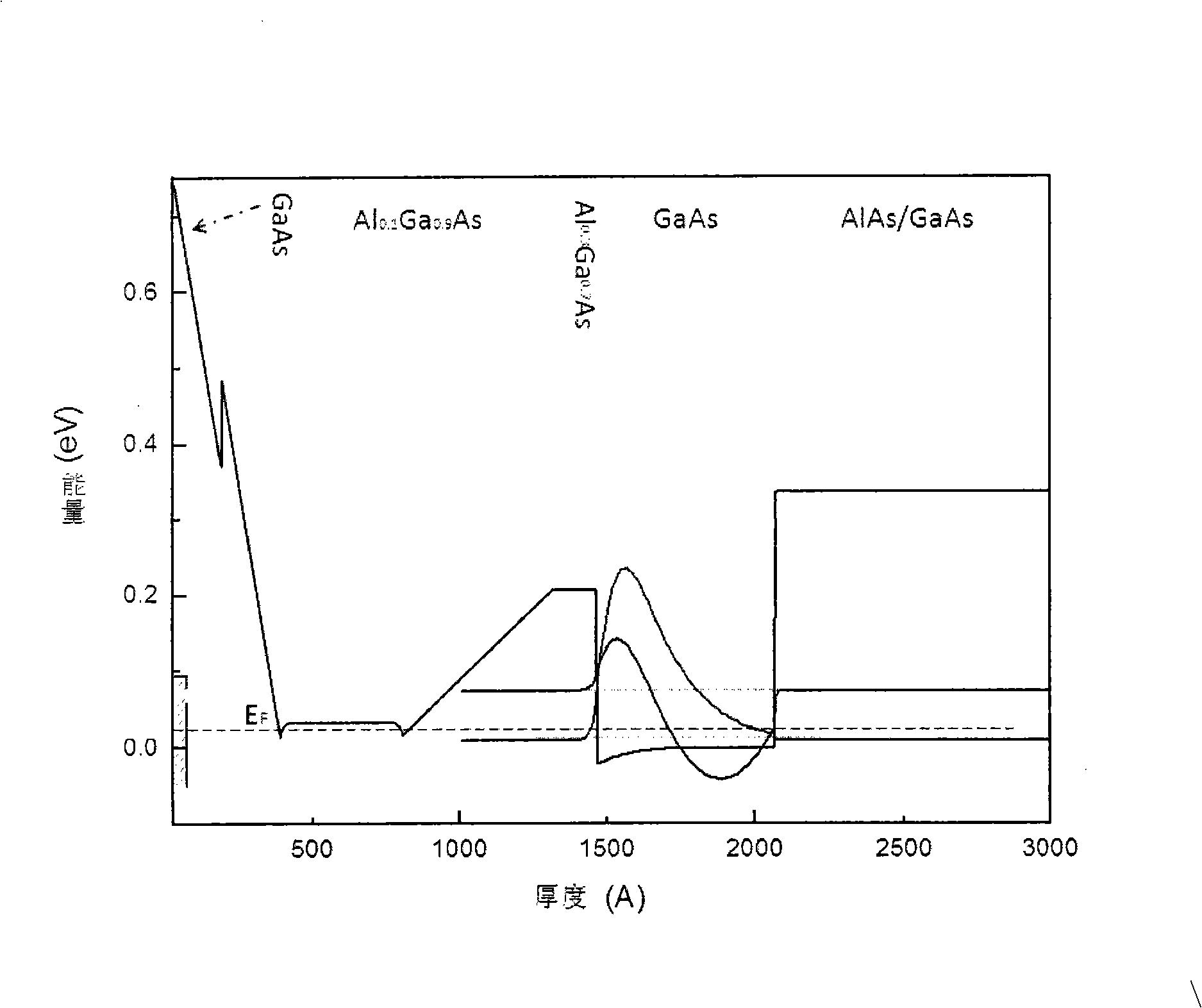

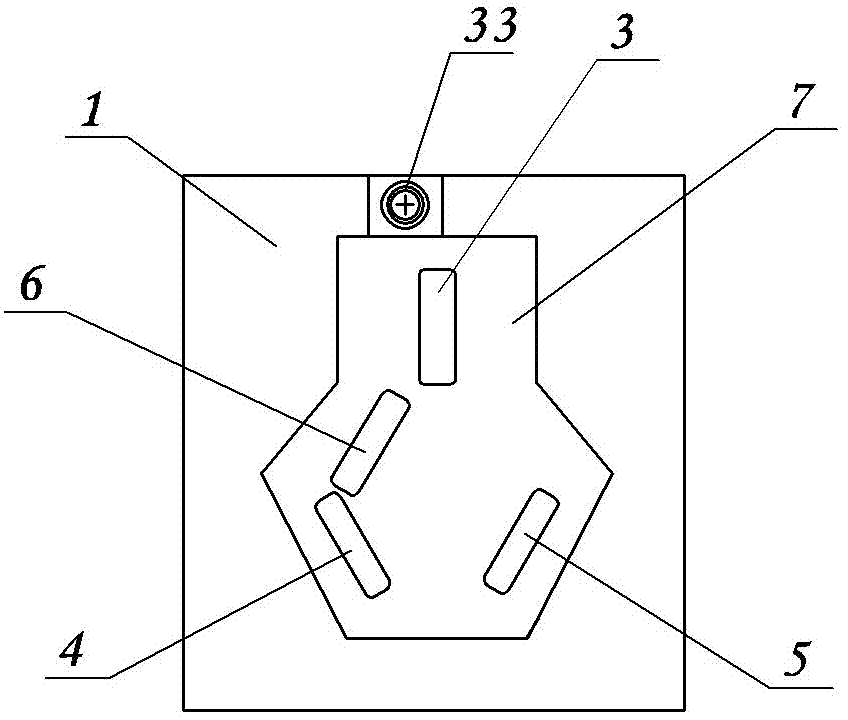

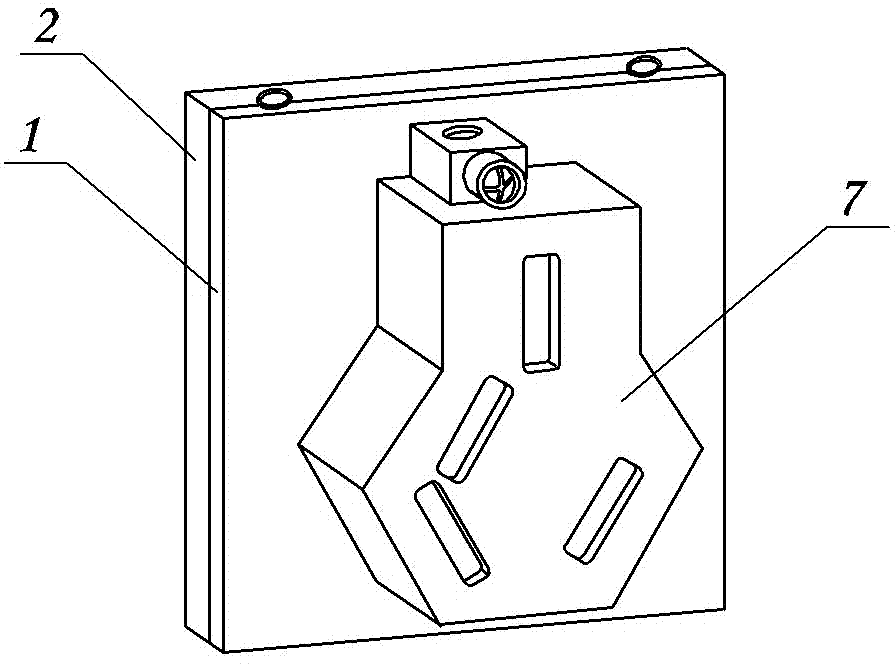

Reinforced transistor structure with high electron mobility and fabrication method thereof

InactiveCN101764152ASimple structureRealize the process is simpleSemiconductor/solid-state device manufacturingSemiconductor devicesElectron mobilityModulation doping

The invention relates to the technical field of semiconductor devices, in particular to a modulation-doped reinforced transistor structure with high electron mobility. The reinforced transistor structure consists of a substrate, a GaAs / AlAs superlattice layer, a GaAs quantum well layer, an Al0.3Ga0.7As layer, an AlxGa1-xAs layer (x is linearly reduced from 0.3 to 0.1), an Al0.1Ga0.9As layer, a GaAs layer, source and drain electrodes and a gate electrode sequentially from the bottom up. The invention also discloses a fabrication method for the reinforced transistor structure. By utilizing the invention, the power consumption of an HEMT device is reduced, the fabrication technique is simplified, and the fabrication cost is reduced.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

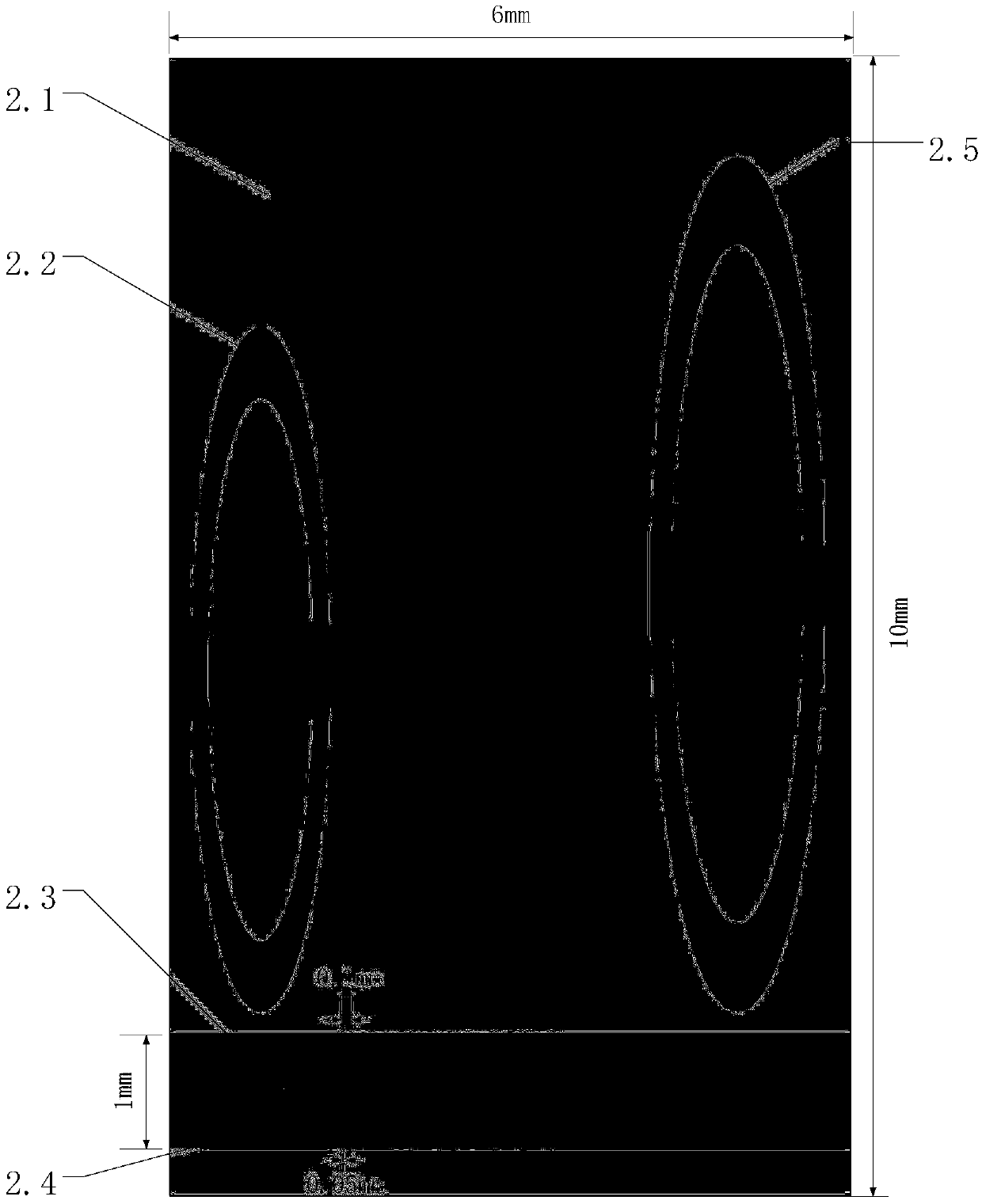

Gallium arsenide PIN diode and preparation method thereof

ActiveCN100485971CReduce parasitic capacitanceRealize the process is simpleSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsAir bridge

The invention discloses a GaAs PIN diode, which comprises: a semi-insulating GaAs underlay for supporting the whole GaAs diode; a high doped layer N growing in extension on the semi-insulating GaAs underlay, resistive formations I and P close to eigen growing in extension in turn on the high doped layer N; By wet process and etching, the areas of the said high doped layer N, resistive formations I and P reduced in turn to form a mesa structure; a top electrode of the round structure formed by metal evaporator on layer P; a semi-orbicular bottom electrode formed by metal evaporator on layer N. The invention also discloses a manufacturing method of GaAs PIN diode. The invention efficiently lowers the parasitic capacitance of the PIN diode without increasing the difficulty of the process and simultaneously greatly shortens the microstrip line connected with the top electrode. The spurious inductance brought by the invention can be greatly reduced or even omitted without using the air-bridge process. The invention has the advantages of easy making, better high frequency characteristic, which is easy to realize the single scale integration.

Owner:北京中科微投资管理有限责任公司

Functional fertilizer capable of improving soil structure and preparing method thereof

InactiveCN106083378AWide range of raw materialsRealize the process is simpleAlkali orthophosphate fertiliserAmmonium orthophosphate fertilisersCellulosePotassium

The invention discloses a functional fertilizer capable of improving the soil structure. The functional fertilizer is prepared from, by mass, 85-98% of water-soluble fertilizer and 2-15% of water-retaining agent. The water-retaining agent is the combination of one or two of potassium polyacrylate, carboxymethylcellulose and hydroxy propyl cellulose and polyacrylamide. The functional fertilizer can achieve fertilizer and water retaining as well as soil loosening, and can improve soil hardening caused by long-term chemical fertilizer application in agricultural practice in China to a certain degree; the functional fertilizer also meets the urgent demand of western drought areas of China for water retaining.

Owner:SHENYANG AGRI UNIV

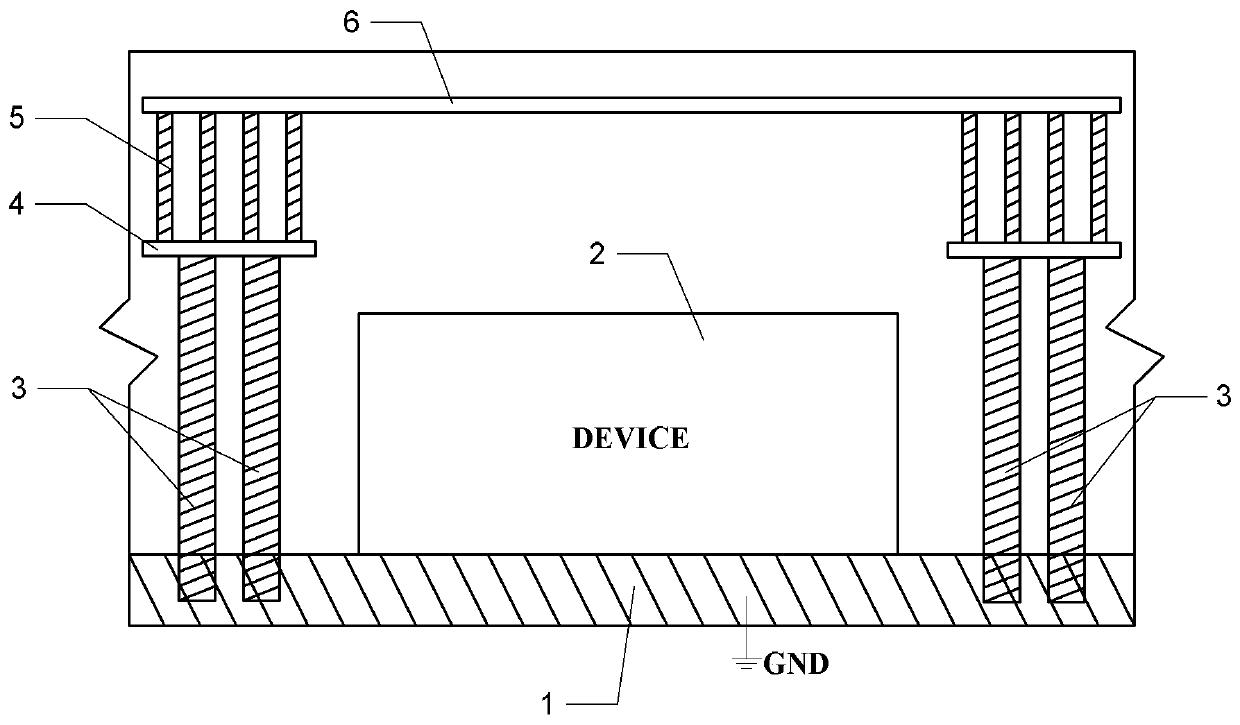

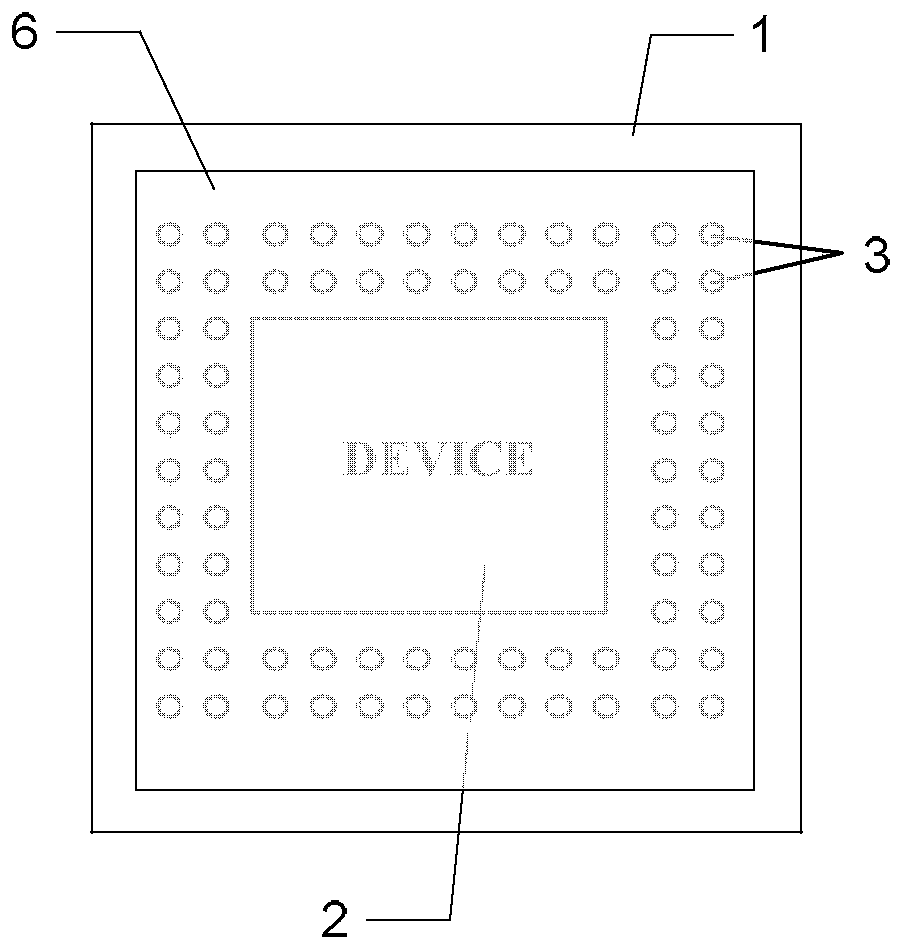

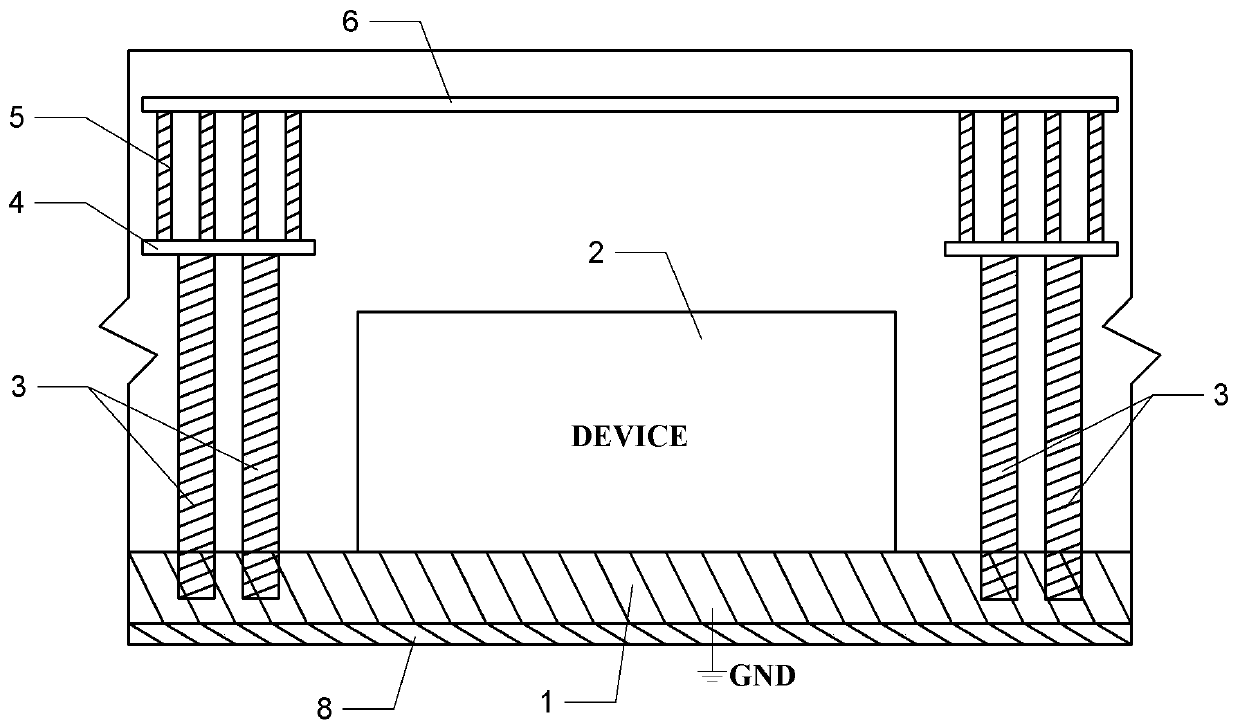

Bare core with electromagnetic shielding structure

InactiveCN111048488ARealize the process is simpleSimple processSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorEngineering

The invention discloses a bare core with an electromagnetic shielding structure, belongs to the technical field of integrated circuits, and aims to solve the problems of complex process and high costof a common electromagnetic shielding structure of an integrated circuit. The scheme of the invention is as follows: an integrated circuit device DEVICE is built on a P-type substrate; a plurality oflayers of deep silicon through holes DSV are tightly and orderly built around the integrated circuit device DEVICE, the deep silicon through holes DSV are filled with high-conductivity conductors, thebottom ends of the deep silicon through holes DSV penetrate through the active layer of the P-type substrate, and the top ends of the deep silicon through holes DSV are connected with a middle metallayer which is physically grounded; one or more middle metal layers are connected to the top metal layer, and the middle metal layers and the top metal layer are connected through multiple rows of parallel metal layer through holes via; any two middle metal layers are connected through a plurality of rows of parallel metal layer through holes via; and the top metal layer is located right above theintegrated circuit device DEVICE.

Owner:QIANDU TONGCHIP XIAMEN MICROELECTRONICS TECH CO LTD

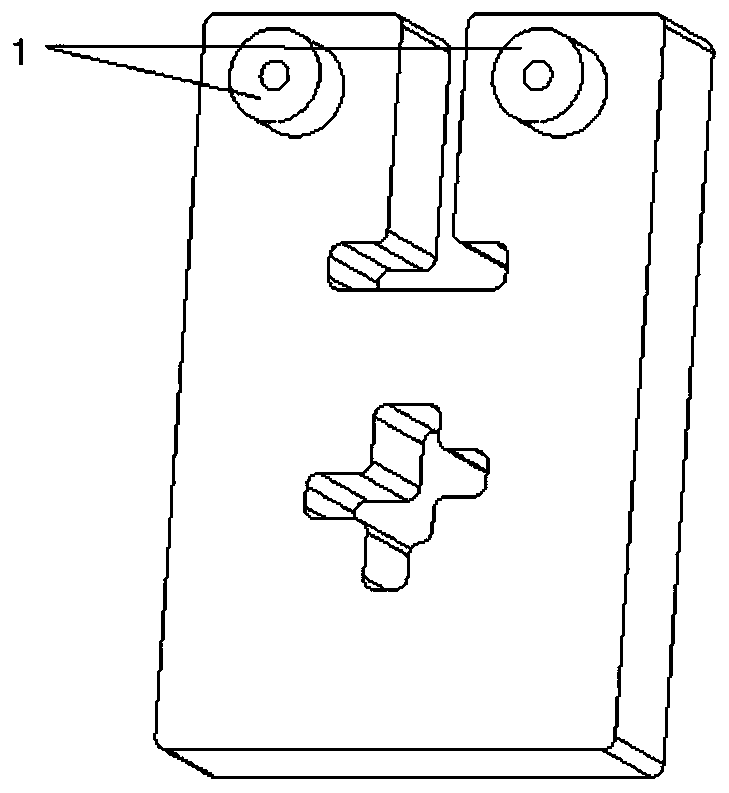

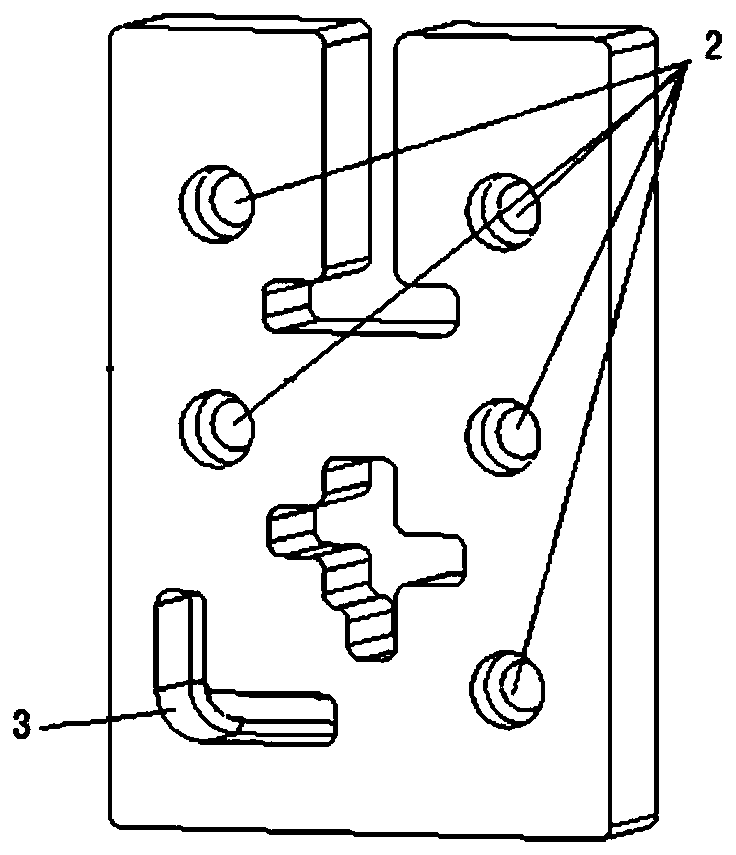

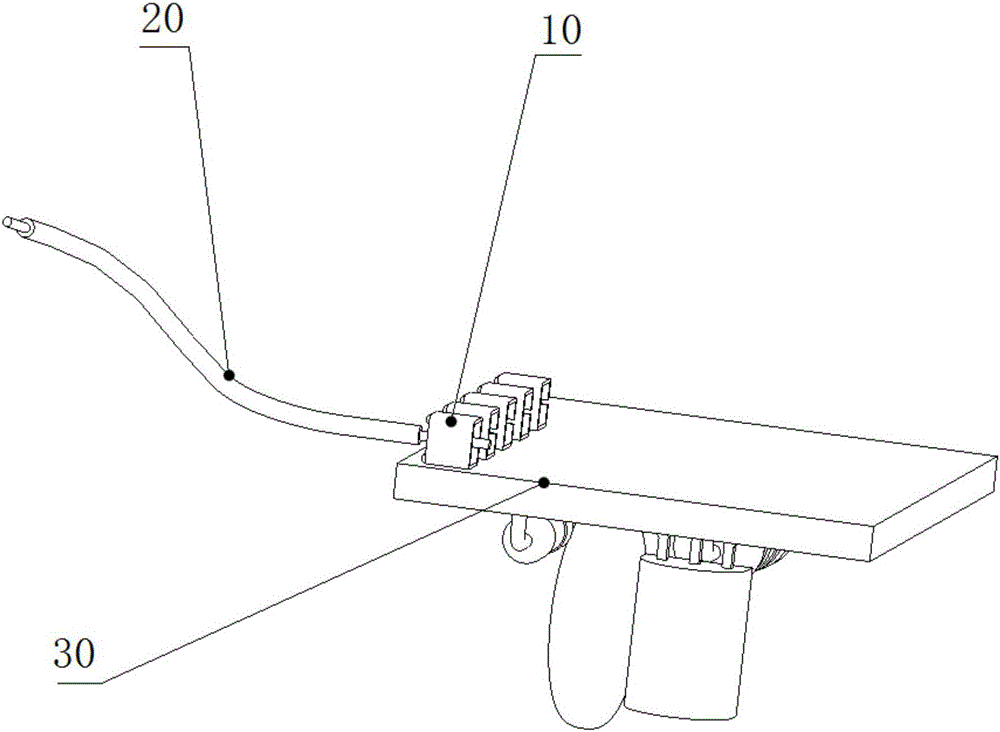

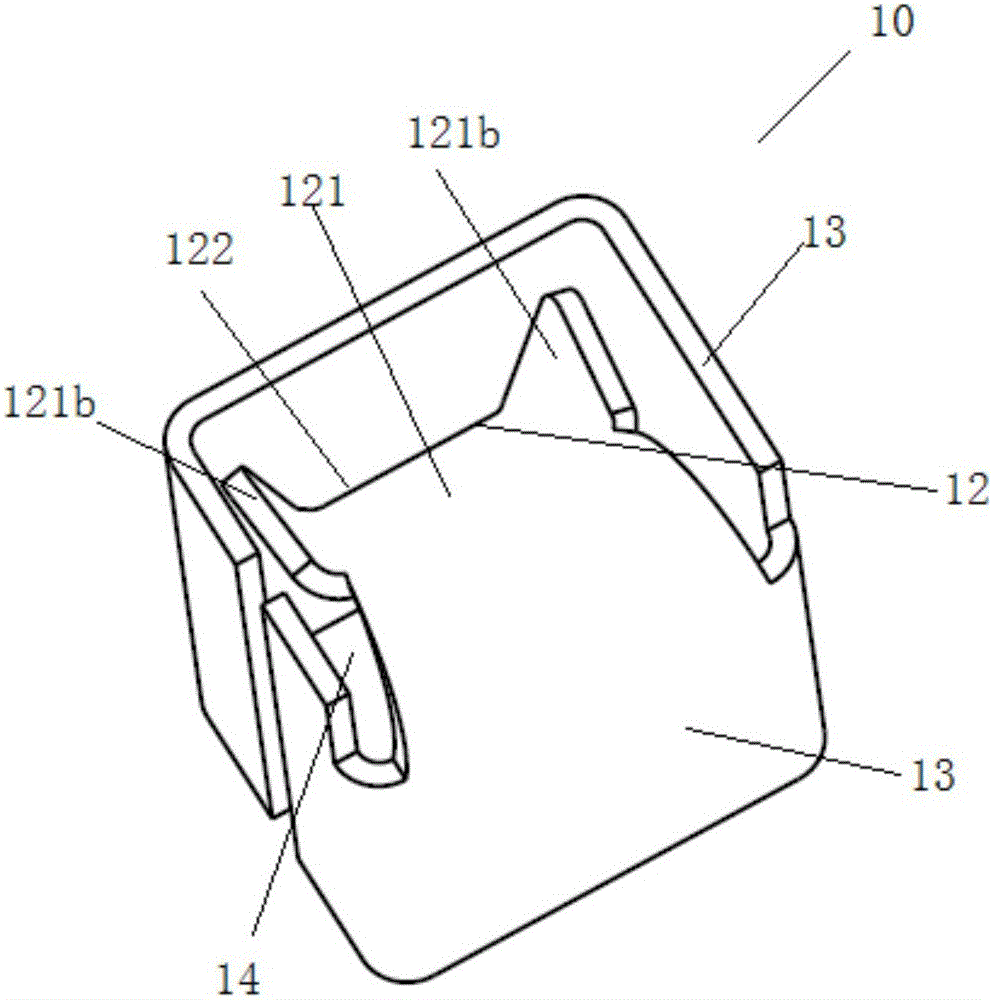

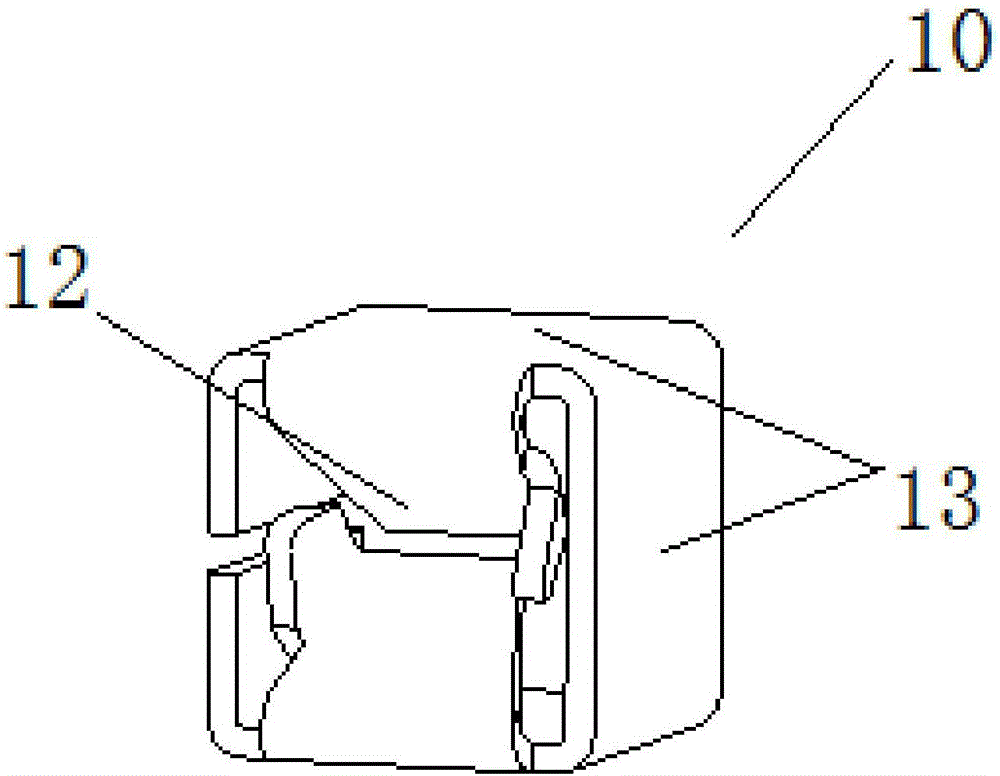

Plug-in assembly

InactiveCN105024224AReduce volumeHighly integratedCoupling device detailsTwo-part coupling devicesEngineeringConductive materials

The invention discloses a plug-in assembly, which comprises a lead (20) and a plug-in female head (10) formed by a conductive material, wherein the plug-in female head (10) is provided with an elastic clamping slot provided for the lead (20) to insert, the elastic clamping slot (12) is extruded by the lead (20) when the lead (20) is inserted so as to generate elastic deformation, and the elastic clamping slot (12),which is extruded and generates the elastic deformation, clamps the lead (20) by using an elastic restoring force.

Owner:DELIXI ELECTRIC

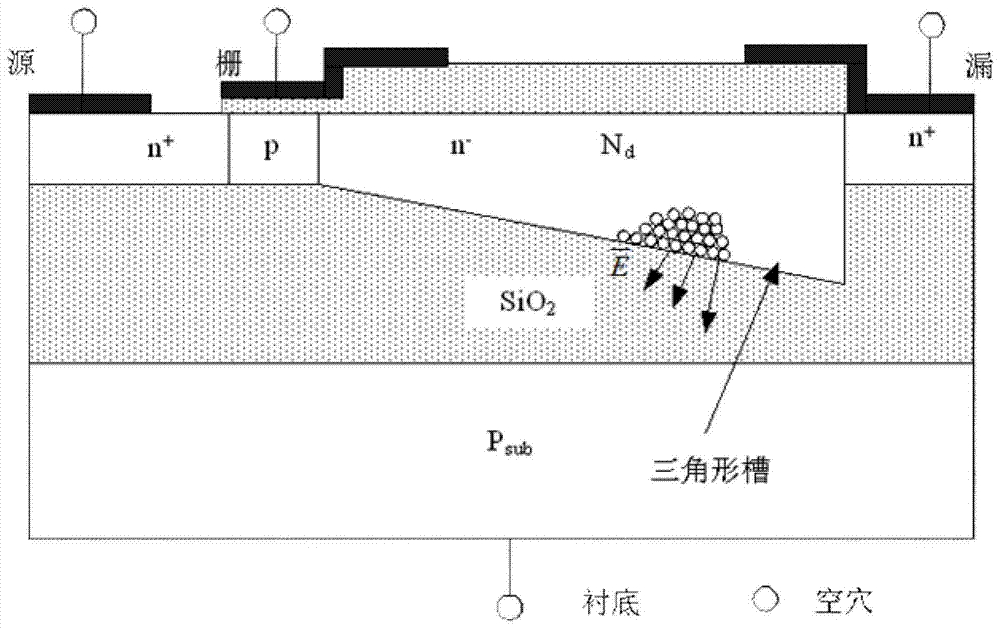

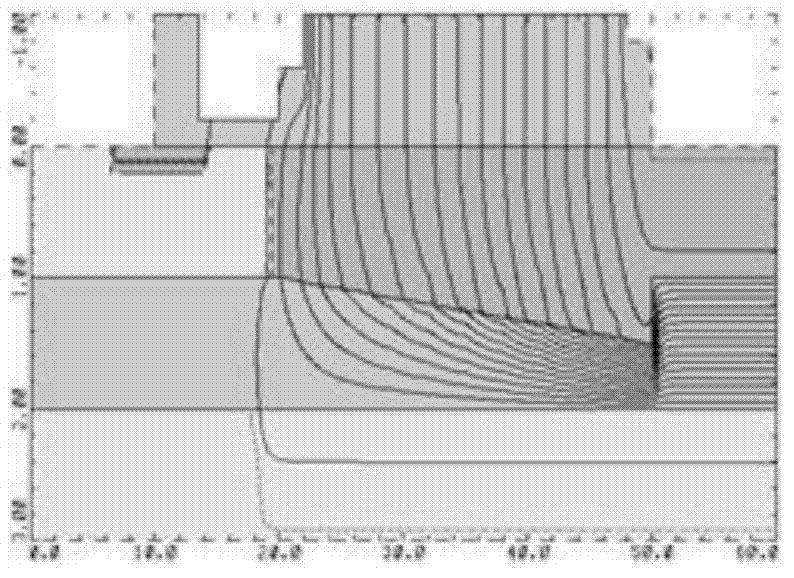

SOI-LDMOS (silicon-on-insulator laterally diffused metal oxide semiconductor) high-tension power device with triangular trench

InactiveCN104241388AImprove vertical pressure resistanceRealize the process is simpleSemiconductor devicesHigh densityEngineering

The invention discloses an SOI-LDMOS (silicon-on-insulator laterally diffused metal oxide semiconductor) high-tension power device with a triangular trench and aims to solve the problems that voltage of a drain of the prior SOI-LDMOS device is induced out of an electronic inversion layer from beneath a buried oxide layer, an equipotential line is prevented from penetrating the buried oxide layer, and early breakdown occurs to a silicon layer, and breakdown voltage withstanding is difficult to increase. The SOI-LDMOS high-tension power device is mainly characterized in that the triangular trench is etched in a buried oxide layer under a drift area; a buried oxide slope exists under the drift area and is capable of constraining positively charged holes, high-density positive charge is produced, and breakdown voltage withstanding of the device is greatly increased through the high-density positive charge; thickness of the drift area linearly increases from a source to a drain, according to the principle of RESURF (reduced surface field), a transverse electric field is uniformized owing to modulation, lateral voltage withstanding can be improved, and rejection ratio on resistance can be increased fast.

Owner:XIHUA UNIV

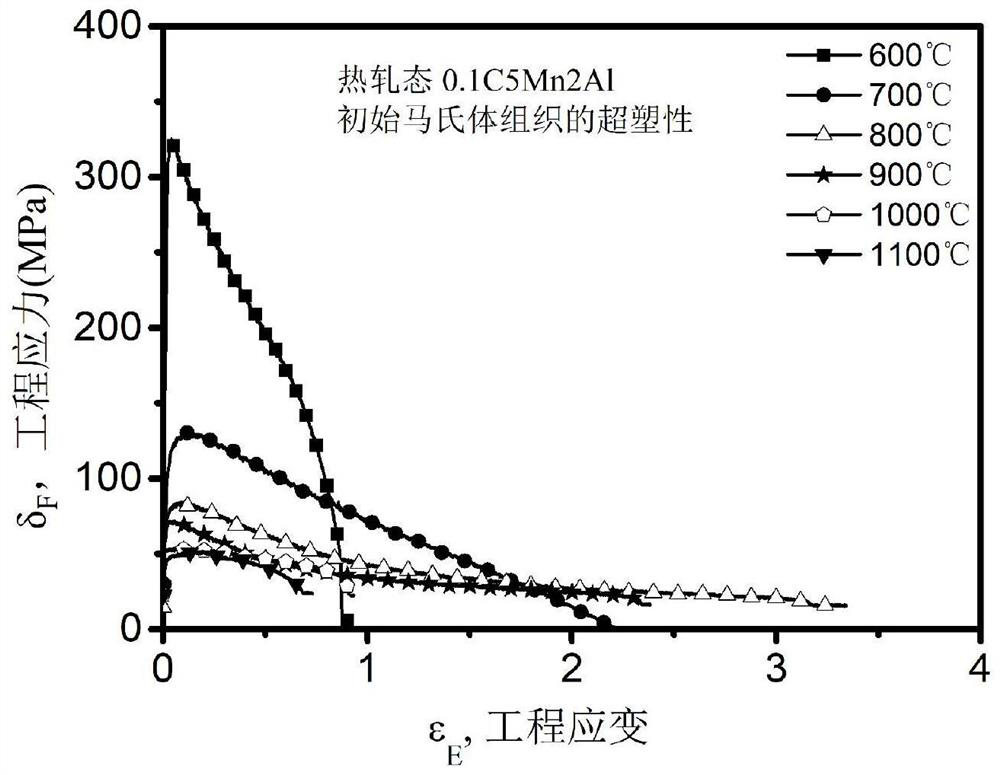

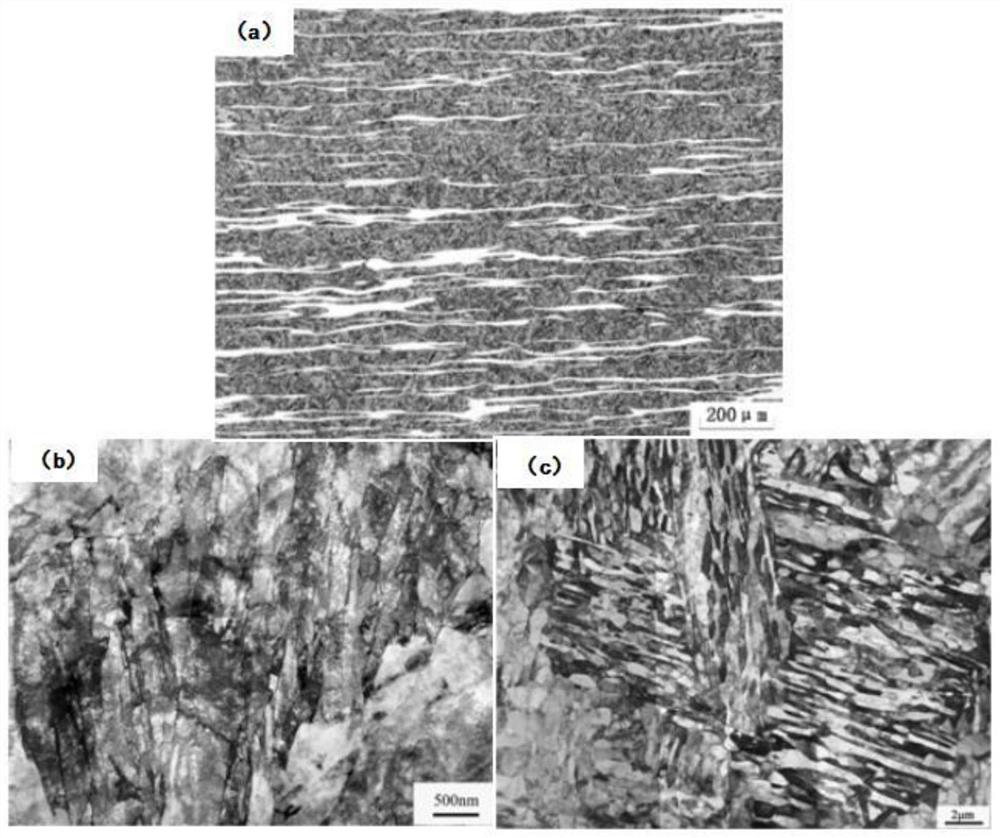

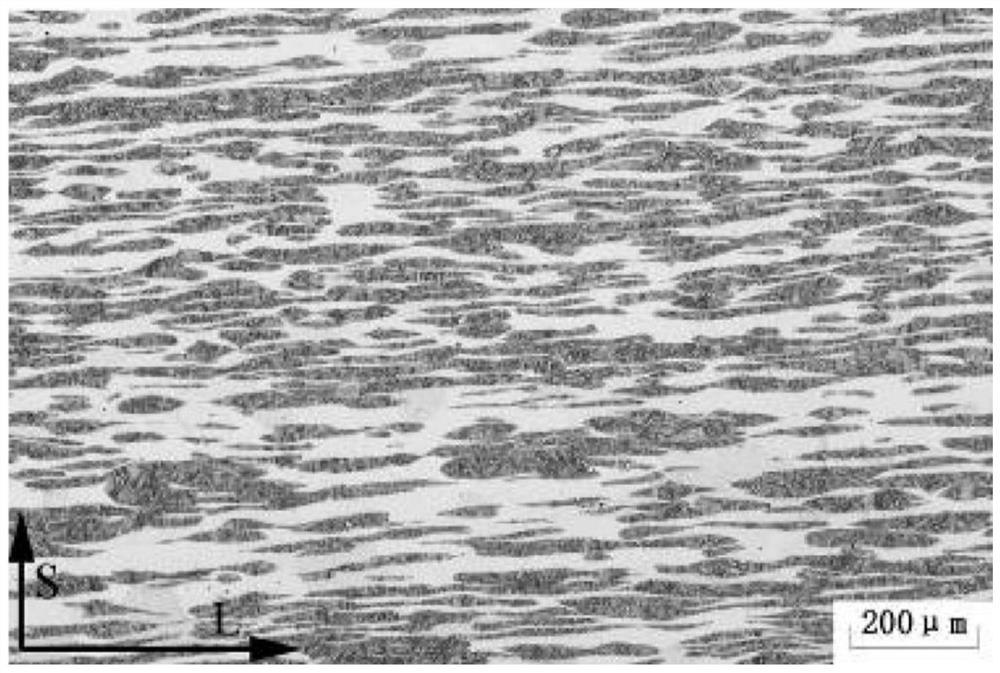

Low-carbon low-alloy steel superplastic material and preparation method thereof

PendingCN113832320ARealize the process is simpleImprove manufacturing efficiencyMetallurgySmelting process

The invention provides a low-carbon low-alloy steel superplastic material and a preparation method thereof. The preparation method comprises the following steps of: step 1, smelting low-carbon low-alloy steel, and producing a cast ingot by die casting or producing a continuous casting billet by continuous casting in the smelting process; step 2, rolling and forming the cast ingot or the continuous casting blank, and conducting cooling to obtain a lamellar or lath-shaped tissue blank; and step 3, annealing the rolled and formed blank, and quickly stretching the blank at a high temperature to enable the elongation to reach 100% or above, and achieving the superplasticity of the low-carbon low-alloy steel. For the low-carbon low-alloy steel superplastic material and the preparation method disclosed by the invention, the maximum strain rate of the implemented superplastic process is 10 <-2 > / s and is increased by 102 orders of magnitude compared with that of an existing superplastic process, so that the production and manufacturing efficiency of large complex parts can be greatly improved, the production cost is saved, and welding application is greatly lowered.

Owner:CENT IRON & STEEL RES INST

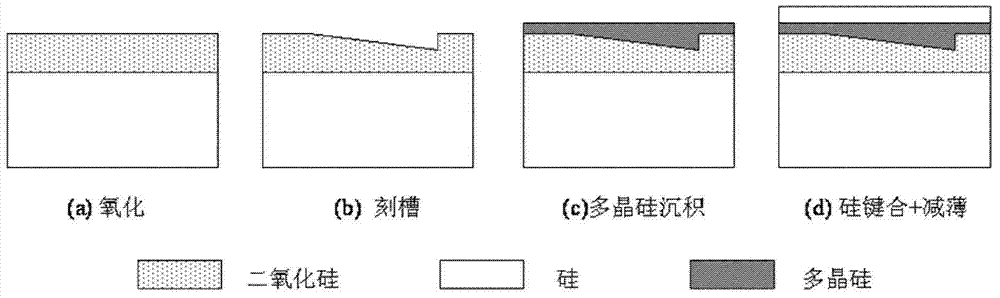

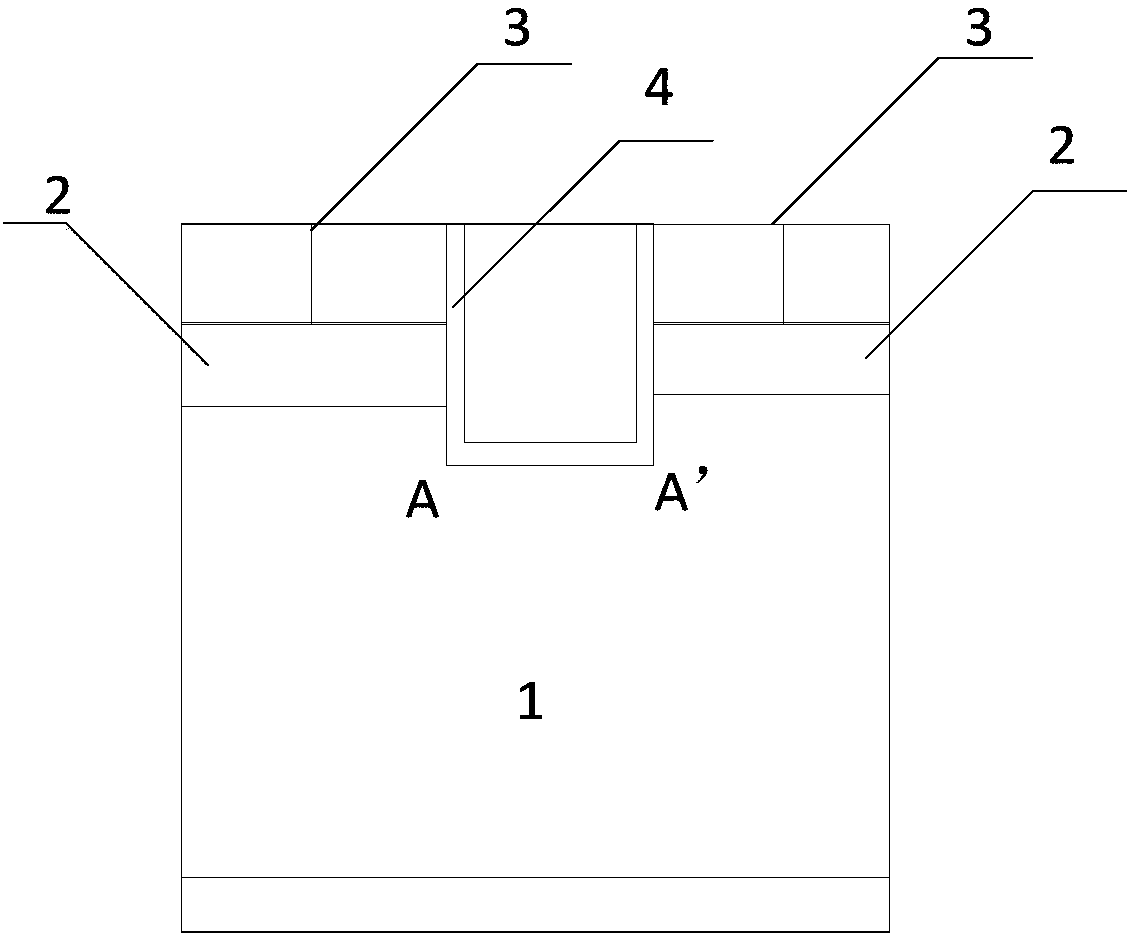

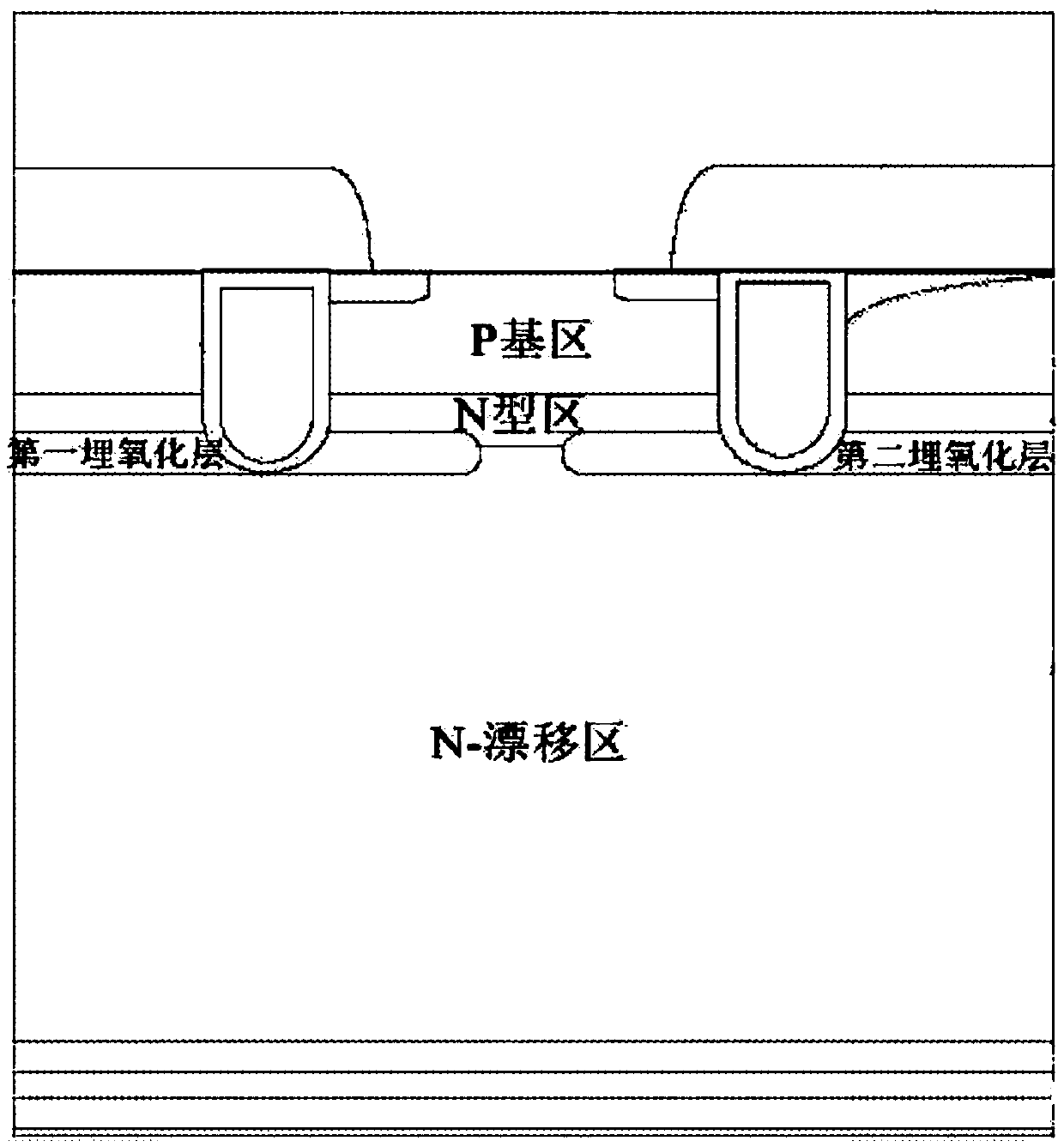

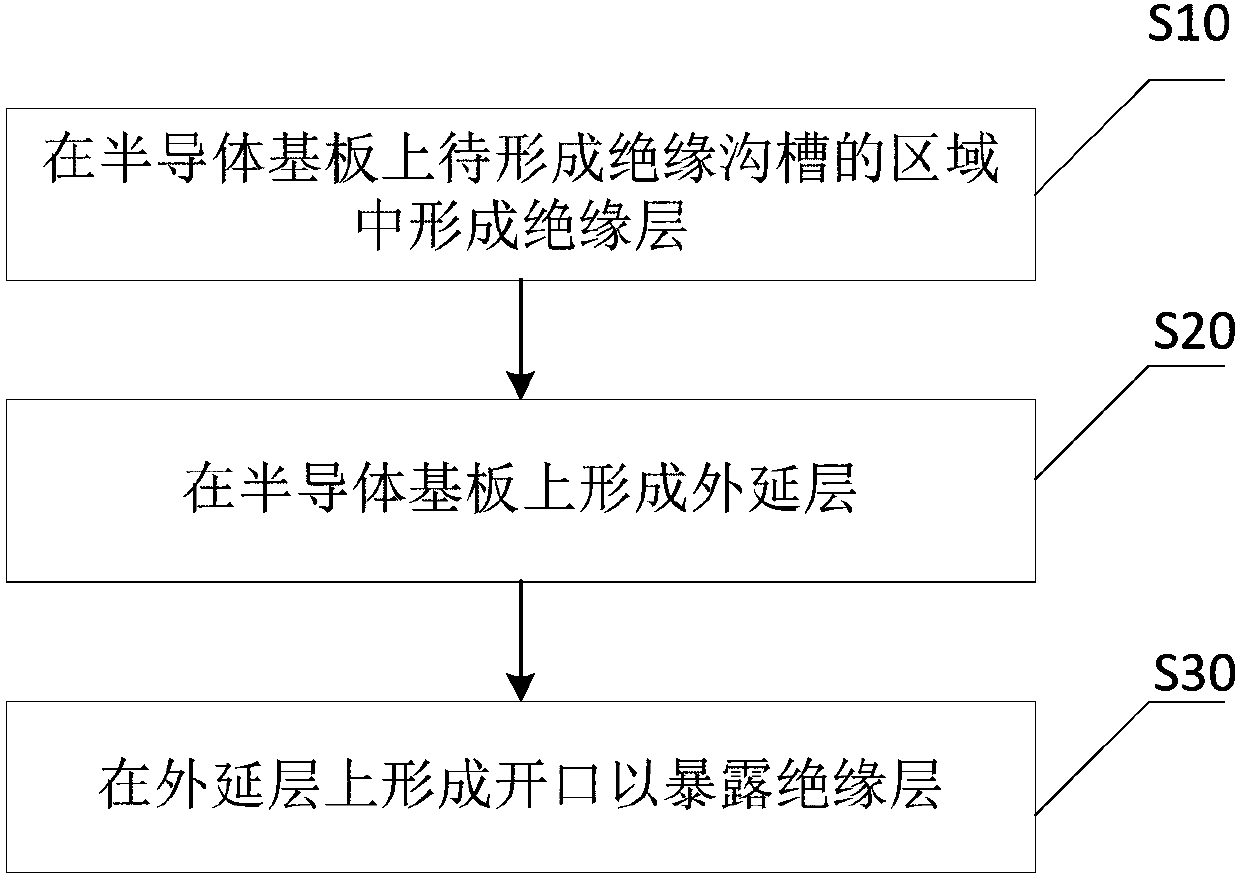

Method for forming insulating groove in substrate and semiconductor device

InactiveCN107658260AControl thicknessImprove distributionSemiconductor/solid-state device manufacturingPower semiconductor deviceDevice type

The invention provides a method for forming an insulating groove in a substrate and a semiconductor device. The method comprises the steps as follows: an insulating layer is formed in the region, in which an insulating groove is to be formed, on the surface of a substrate, wherein the insulating layer can be taken as the bottom of the insulating groove, the specific thickness can be correspondingly adjusted according to the device type and the operating requirements, forming of the insulating layer on the surface of the substrate is relatively easy to implement, and the thickness and the region range are relatively easy to control; an epitaxial layer is formed on the substrate, and the structure of the epitaxial layer can be determined according to the type of the semiconductor device; andan opening is formed in the epitaxial layer to expose the insulating layer, thereby forming the insulating groove. Compared with the prior art, the method has the advantages that control on the thickness of the bottom of the insulating layer at the bottom of the groove and improvement of electric field distribution can be implemented, additional equipment or process is not needed for implementation, and the implementation procedure and the implementation process are simple.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +2

A kind of semiconductor glue and preparation method thereof

ActiveCN101210162BImprove reliabilityUniform electric fieldNon-macromolecular adhesive additivesEpoxy resin adhesivesWater bathsEpoxy

The invention relates to a semiconductor glue used in electrical products, which contains 55-65% of glue, 79-81% of epoxy glue, 7-9% of curing agent, and 11-13% of toughening agent by weight percentage. %; filler 31-41%, including graphite 58-62%, kaolin 38-42%; low temperature curing agent 2-4%. Heat the epoxy glue into a fluid in an oven at 50-60°C; take the liquid epoxy glue in a beaker, and place it in a constant temperature water bath at 50-60°C; while stirring, add curing agent, toughening agent and thinner in sequence until stirring Evenly; add the filling and stir well. The invention solves the technical problem of poor reliability and safety of shielding in the background technology. The invention has simple process and high production efficiency, and can be used for electrostatic shielding or forming semiconductor layers.

Owner:XIAN XIDIAN TRANSFORMER

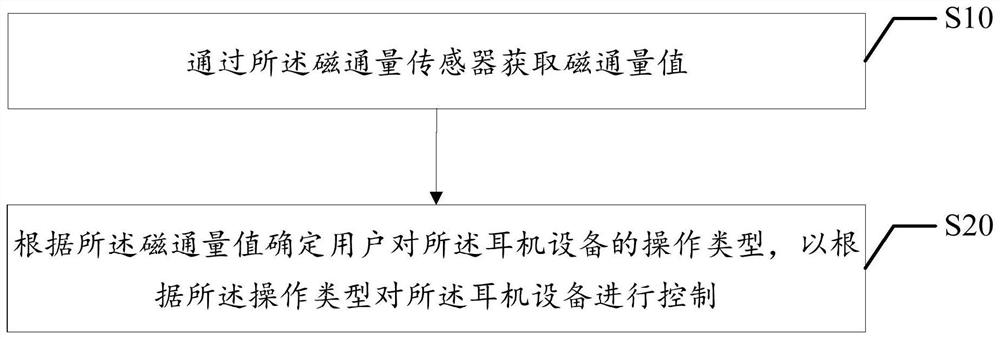

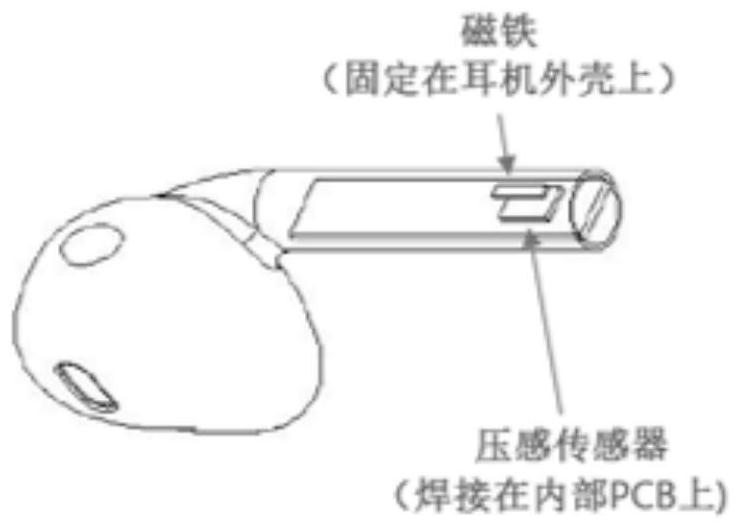

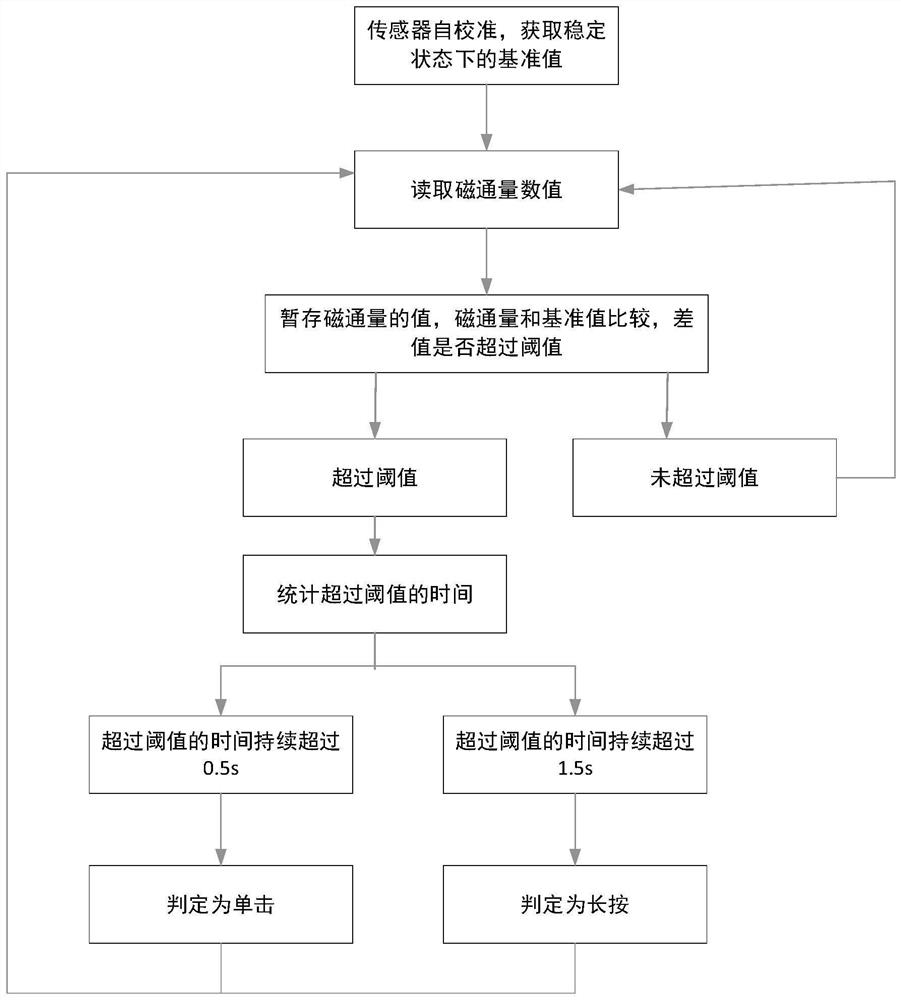

Earphone control method and device, earphone equipment and storage medium

ActiveCN114501220AEasy to operateRealize the process is simpleEarpiece/earphone mechanical/electrical switchesMagnitude/direction of magnetic fieldsHeadphonesMagnetic flux

The invention discloses an earphone control method and device, earphone equipment and a storage medium, the earphone control method is applied to the earphone equipment, the earphone equipment is internally provided with a magnet and a magnetic flux sensor, the distance between the magnet and the magnetic flux sensor can be changed by pressing the earphone equipment, and the method comprises the following steps: acquiring a magnetic flux value through the magnetic flux sensor; and determining an operation type of the user on the earphone equipment according to the magnetic flux value, and controlling the earphone equipment according to the operation type. Compared with a control method adopting a traditional key, the novel earphone equipment control method has the advantages that the implementation process adopting the magnetic flux sensor and the magnet is simpler, and the operation of pressing the earphone equipment by a user is more convenient.

Owner:GOERTEK INC

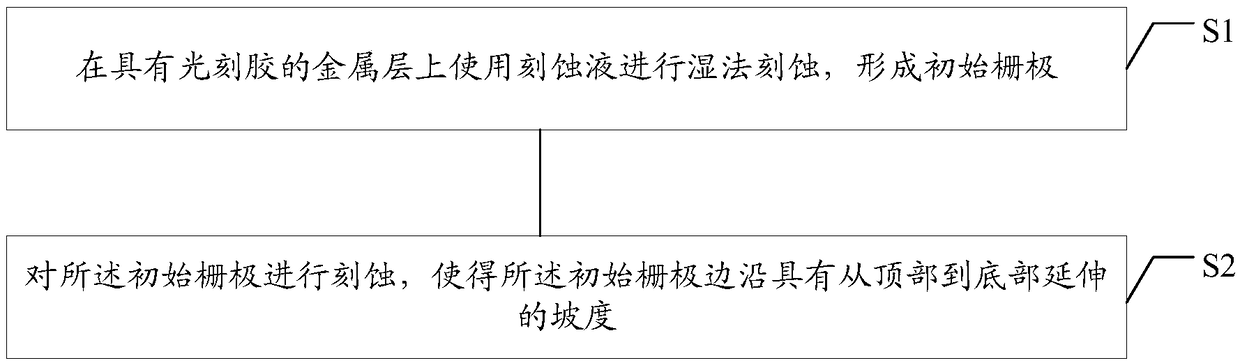

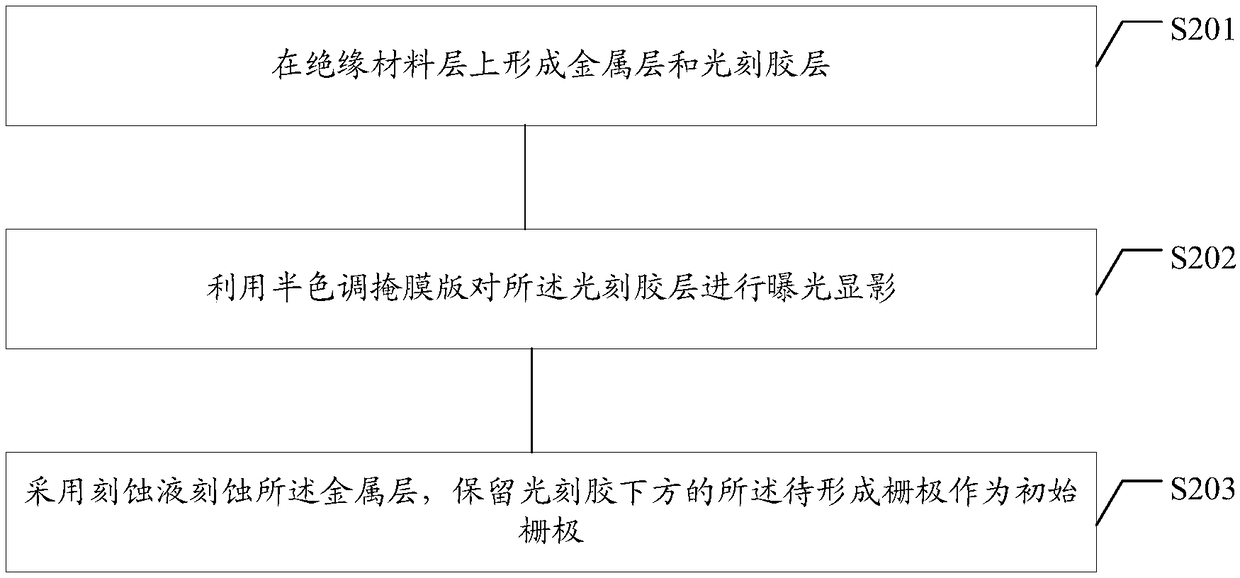

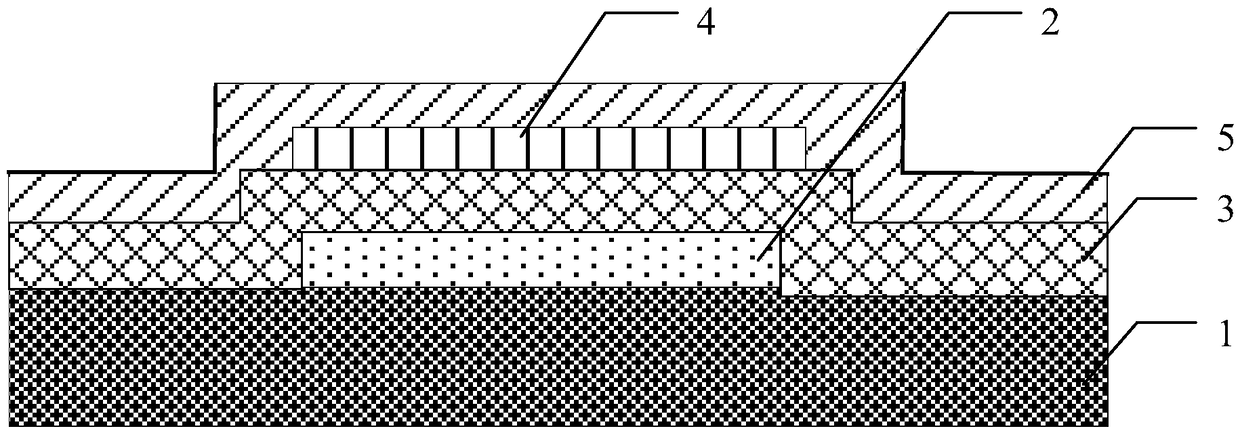

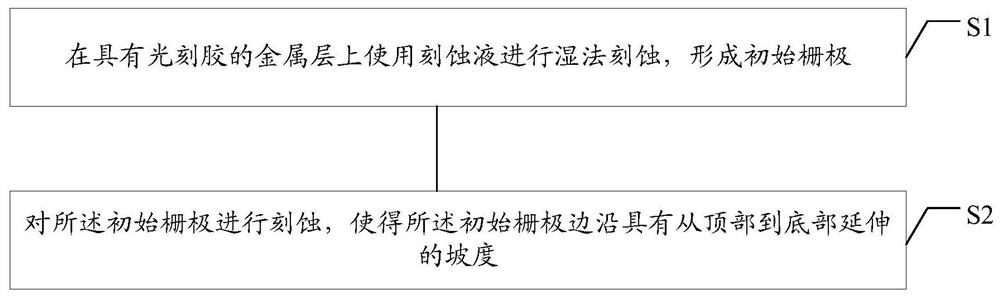

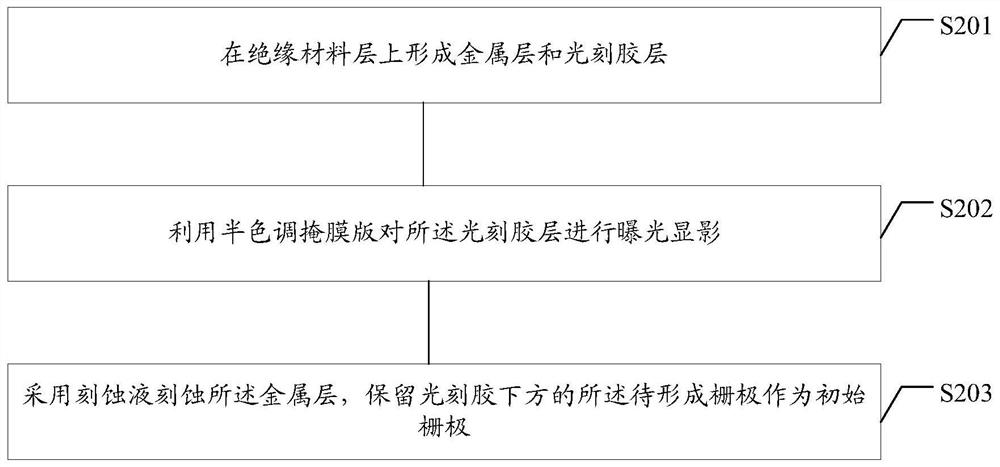

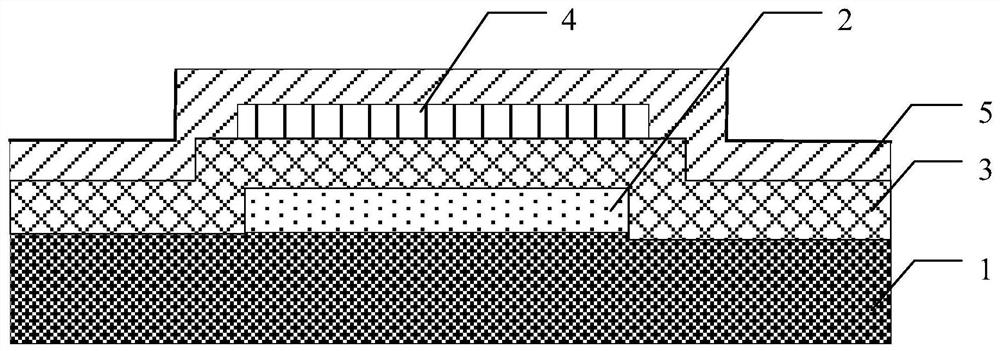

Fabrication method of array substrate, array substrate, and display device

ActiveCN109166823AReduce breakageReduce voidsSemiconductor/solid-state device manufacturingEtchingSlope angle

The invention relates to the technical field of display, and provides a manufacturing method of an array substrate. The method comprises the following steps: forming an initial gate, wherein, the edgeof the initial gate has a slope; A preset thick bottom etching is performed on a slope surface of the initial gate edge and a partial plane extending inwardly of the slope surface, thereby reducing aslope angle of the initial gate slope surface. The present disclosure reduces the slope angle of the initial gate edge slope surface by performing a preset thick bottom etching on the slope surface of the initial gate edge and a portion of the plane in which the slope surface extends inwardly, thereby reducing the probability of a fracture or void occurring between the initial gate and the interlayer insulating layer.

Owner:HEFEI XINSHENG OPTOELECTRONICS TECH CO LTD +1

Manufacturing method of array substrate, array substrate and display device

ActiveCN109166823BReduce breakageReduce voidsSemiconductor/solid-state device manufacturingEtchingDisplay device

The invention relates to the technical field of display, and provides a manufacturing method of an array substrate. The method comprises the following steps: forming an initial gate, wherein, the edgeof the initial gate has a slope; A preset thick bottom etching is performed on a slope surface of the initial gate edge and a partial plane extending inwardly of the slope surface, thereby reducing aslope angle of the initial gate slope surface. The present disclosure reduces the slope angle of the initial gate edge slope surface by performing a preset thick bottom etching on the slope surface of the initial gate edge and a portion of the plane in which the slope surface extends inwardly, thereby reducing the probability of a fracture or void occurring between the initial gate and the interlayer insulating layer.

Owner:HEFEI XINSHENG OPTOELECTRONICS TECH CO LTD +1

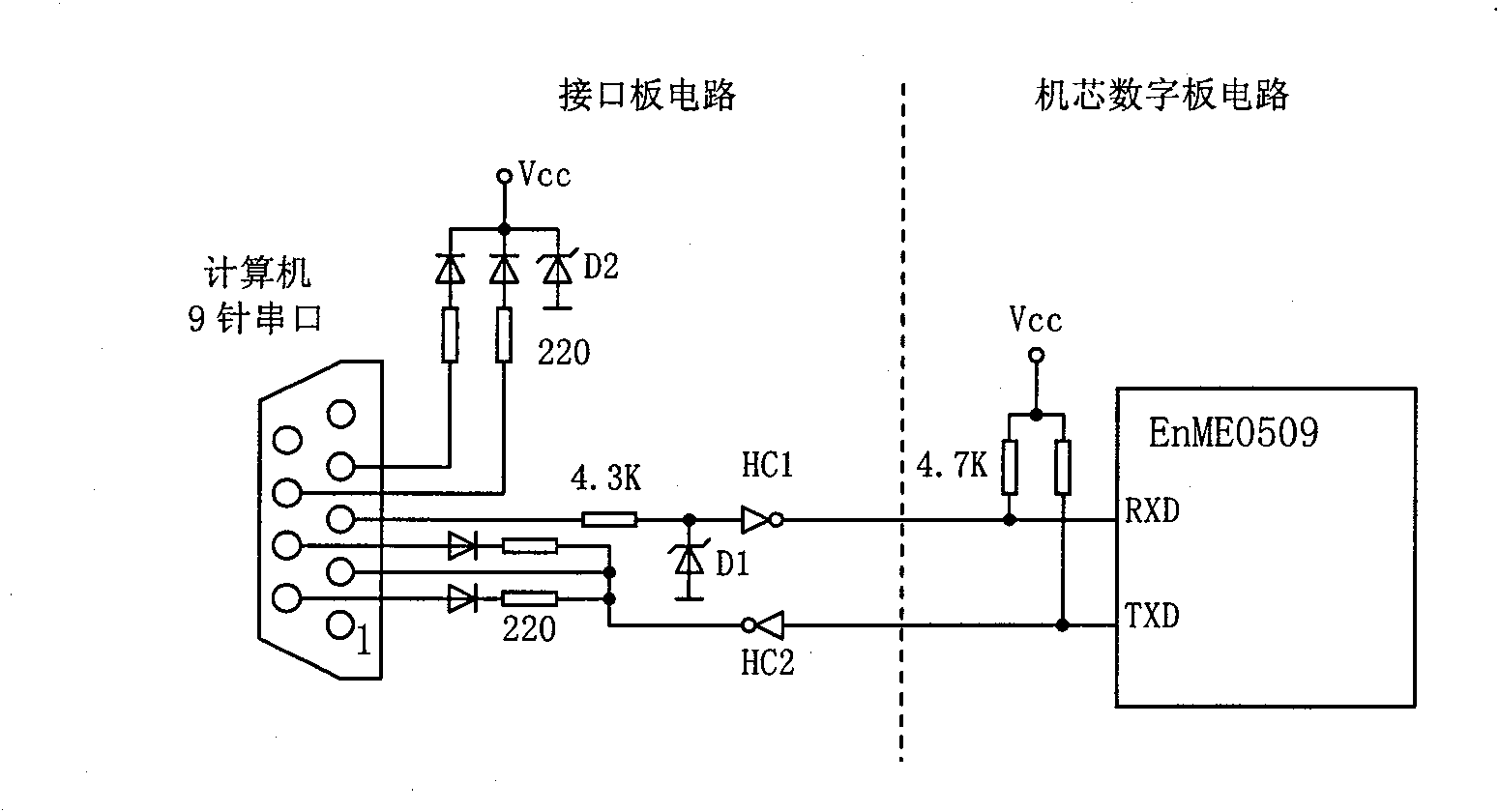

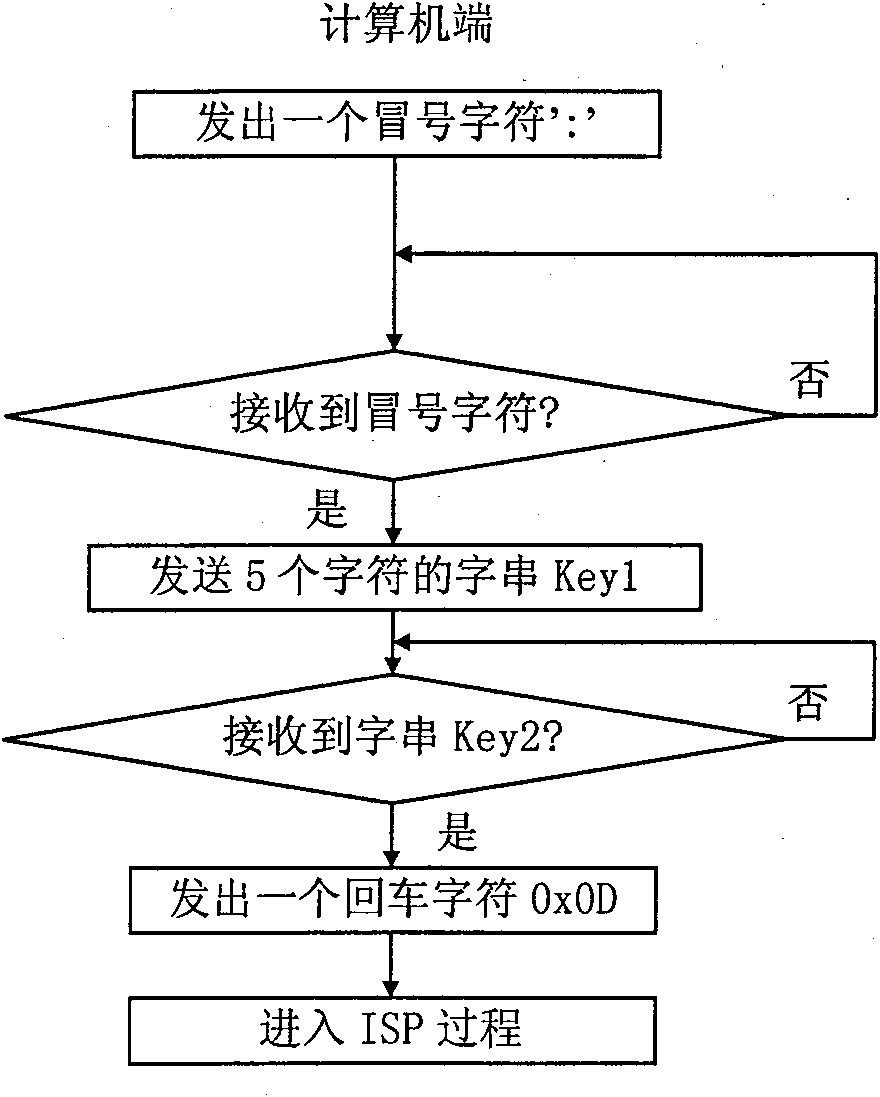

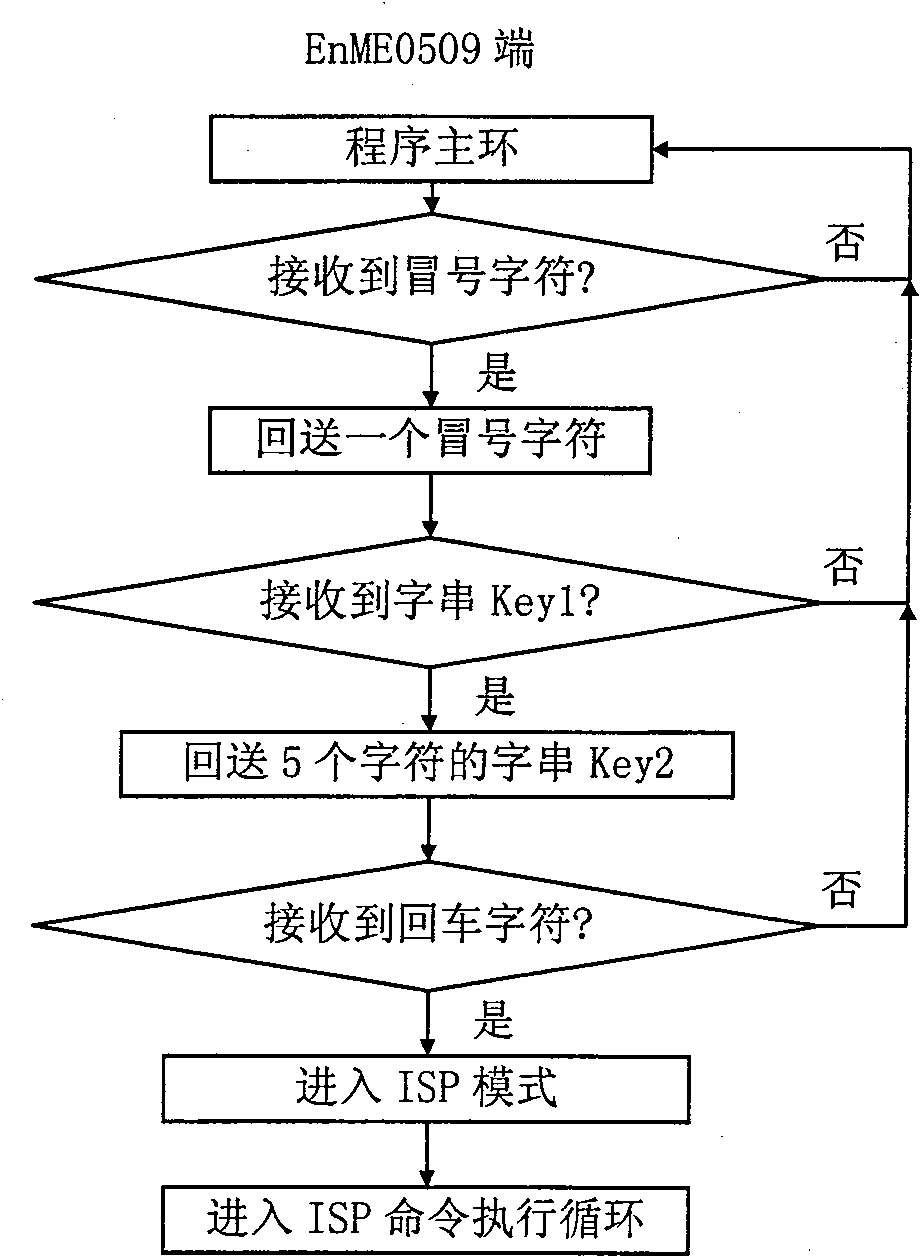

Circuit device for repeating on-line programming and implement method

InactiveCN100583961COnline programming is convenientRealize simple structureTelevision system detailsColor television detailsGeneral purpose computerData transmission

The invention is used in TV circuit board. The apparatus thereof comprises: an interface board circuit and a TV control chip. Said interface board circuit is used for connecting 9-pin serial port of a computer to the I / O pins of TV control chip, and comprises a level conversion circuit used for converting the level of 9-pin serial port to the level desired by the TV control chip. On said computer there is an on-line updating programming program installed for updating the TV control chip on-line.

Owner:SHENZHEN SKYWORTH RGB ELECTRONICS CO LTD

Reinforced transistor structure with high electron mobility and fabrication method thereof

InactiveCN101764152BSimple structureRealize the process is simpleSemiconductor/solid-state device manufacturingSemiconductor devicesHigh electronElectron mobility

The invention relates to the technical field of semiconductor devices, in particular to a modulation-doped reinforced transistor structure with high electron mobility. The reinforced transistor structure consists of a substrate, a GaAs / AlAs superlattice layer, a GaAs quantum well layer, an Al0.3Ga0.7As layer, an AlxGa1-xAs layer (x is linearly reduced from 0.3 to 0.1), an Al0.1Ga0.9As layer, a GaAs layer, source and drain electrodes and a gate electrode sequentially from the bottom up. The invention also discloses a fabrication method for the reinforced transistor structure. By utilizing the invention, the power consumption of an HEMT device is reduced, the fabrication technique is simplified, and the fabrication cost is reduced.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Multifunctional socket structure

InactiveCN103151663BCompact structureImprove securityCoupling contact membersCouplings bases/casesEngineeringGround line

Owner:冯立勋

Substrate electric leakage isolation structure of conventional tunneling field effect transistor, and process method

PendingCN111785770AGood leakage isolation effectReduce distanceSemiconductor/solid-state device manufacturingDiodeEngineeringElectronics

The invention provides a substrate electric leakage isolation structure of a conventional tunneling field effect transistor, and a process method, and belongs to the technical field of micro-nano electronics. The structure comprises a P-type substrate, wherein an active region is arranged on the P-type substrate, shallow groove isolation is arranged outside the active region, the active region issurrounded by NWELLs, a PWELL is arranged between every two adjacent NWELLs, and the width of the PWELL between every two adjacent NWELLs is equal to or slightly smaller than the distance between every two NWELLs. According to the invention, after PWELL injection is introduced, the reverse PN junction realized by the PWELL with small width and the NWELL has a good electric leakage isolation effect, so that by using the structure provided by the invention, the electric leakage of the substrate can be effectively isolated, the distance between the TFET devices during integration can be reduced,and the optimization of the circuit area is brought.

Owner:PEKING UNIV