Method for forming insulating groove in substrate and semiconductor device

A technology of insulating trenches and semiconductors, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, circuits, etc., and can solve the problems of increasing the manufacturing cost of semiconductor devices with insulating trenches, high manufacturing costs, and complicated processes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

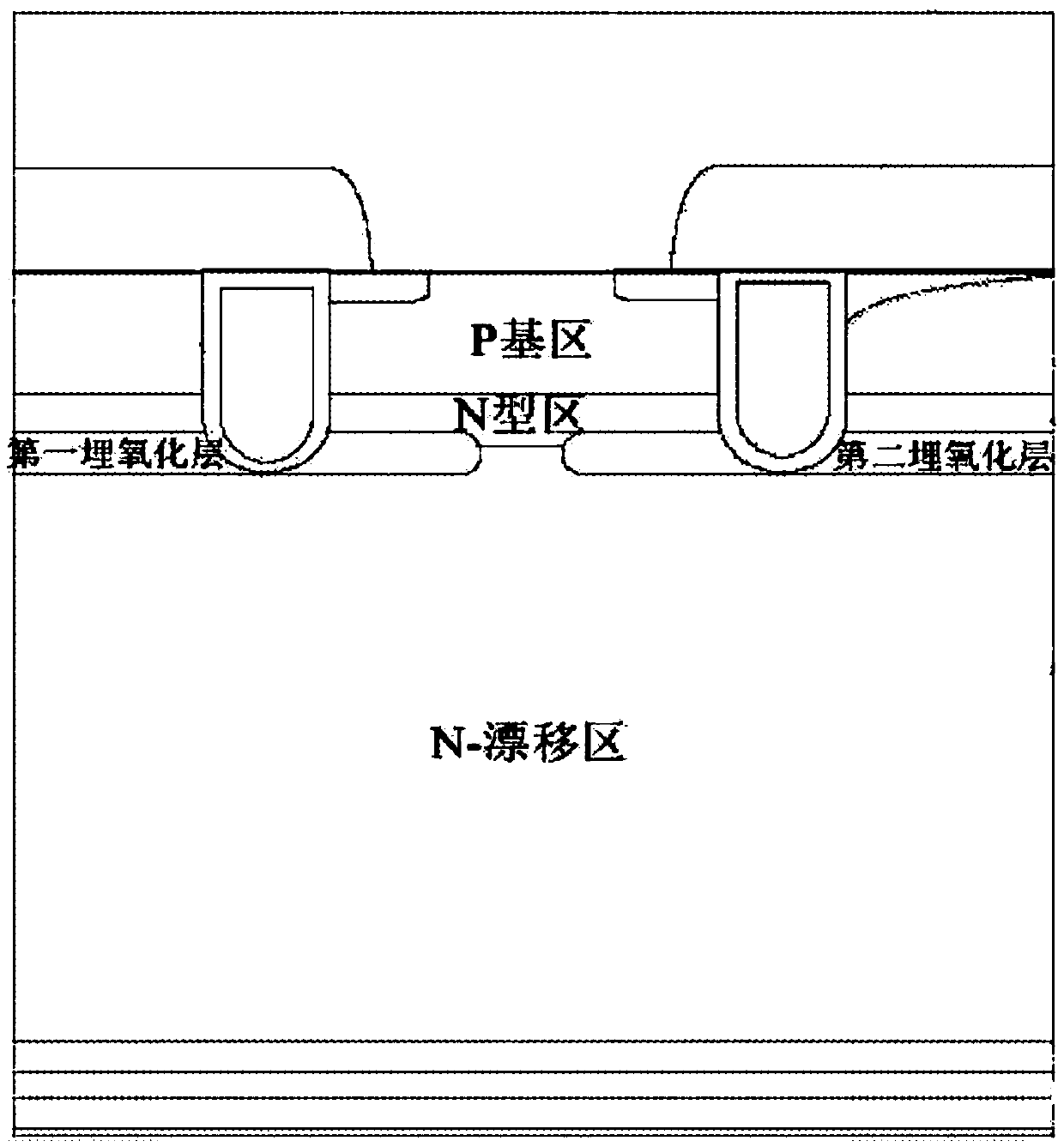

[0028] The technical solutions of the present invention will be clearly and completely described below in conjunction with the accompanying drawings. Apparently, the described embodiments are some of the embodiments of the present invention, but not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention. In addition, the terms "first", "second", etc. are used for descriptive purposes only, and should not be construed as indicating or implying relative importance.

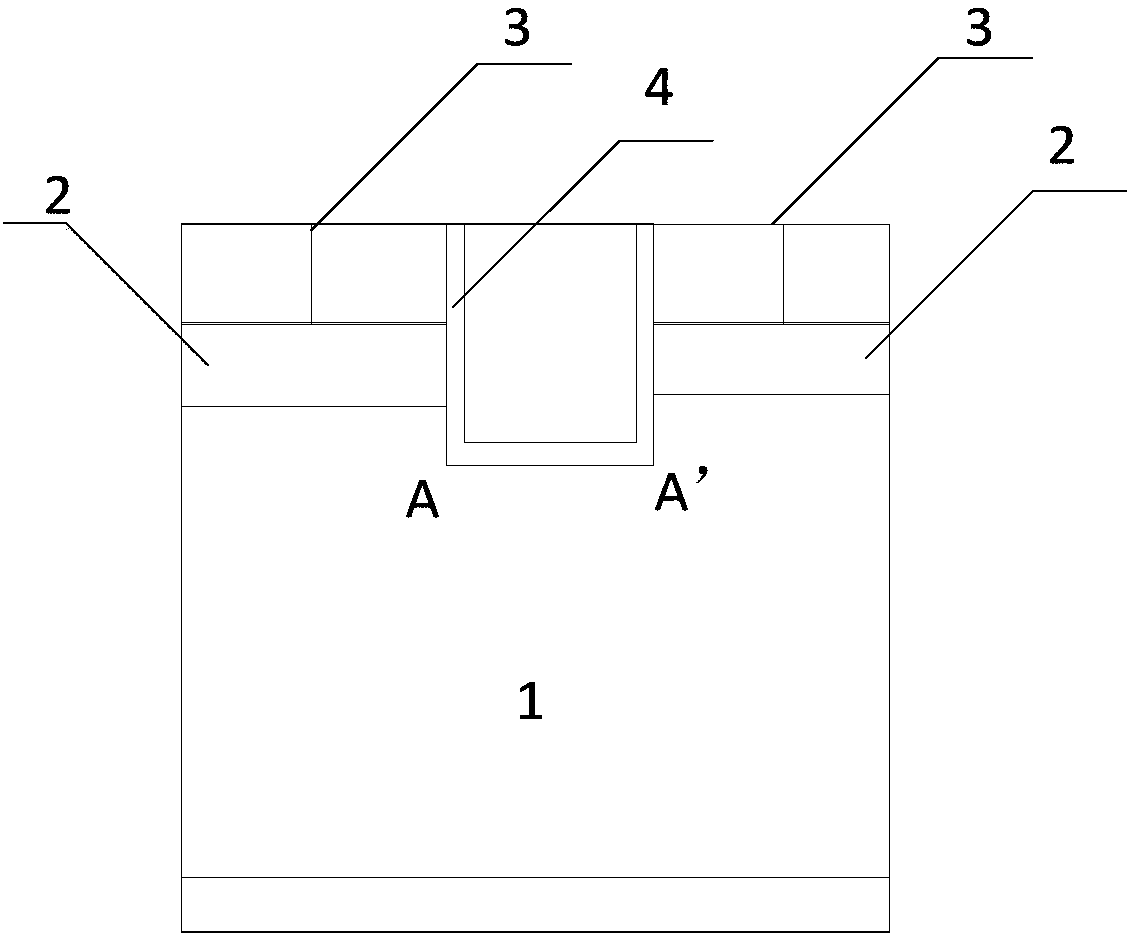

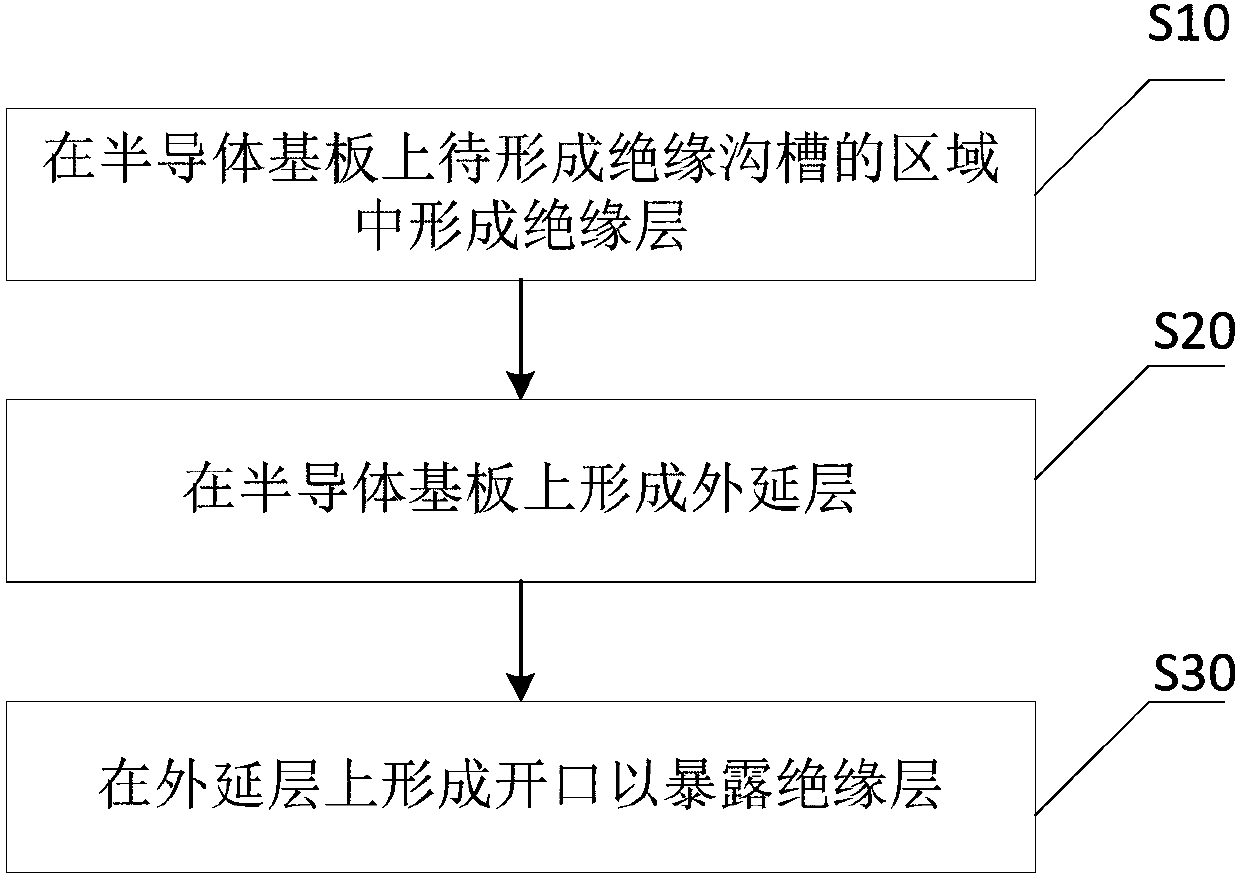

[0029] An embodiment of the present invention provides a method for forming an insulating trench on a substrate, such as image 3 As shown, the method includes:

[0030] S10 . Form an insulating layer 20 in a region on the substrate 10 where the insulating trench 40 is to be formed. In a specific embodiment, the substrate 10 may be a silicon substra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More