Patents

Literature

331results about How to "Uniformly formed" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

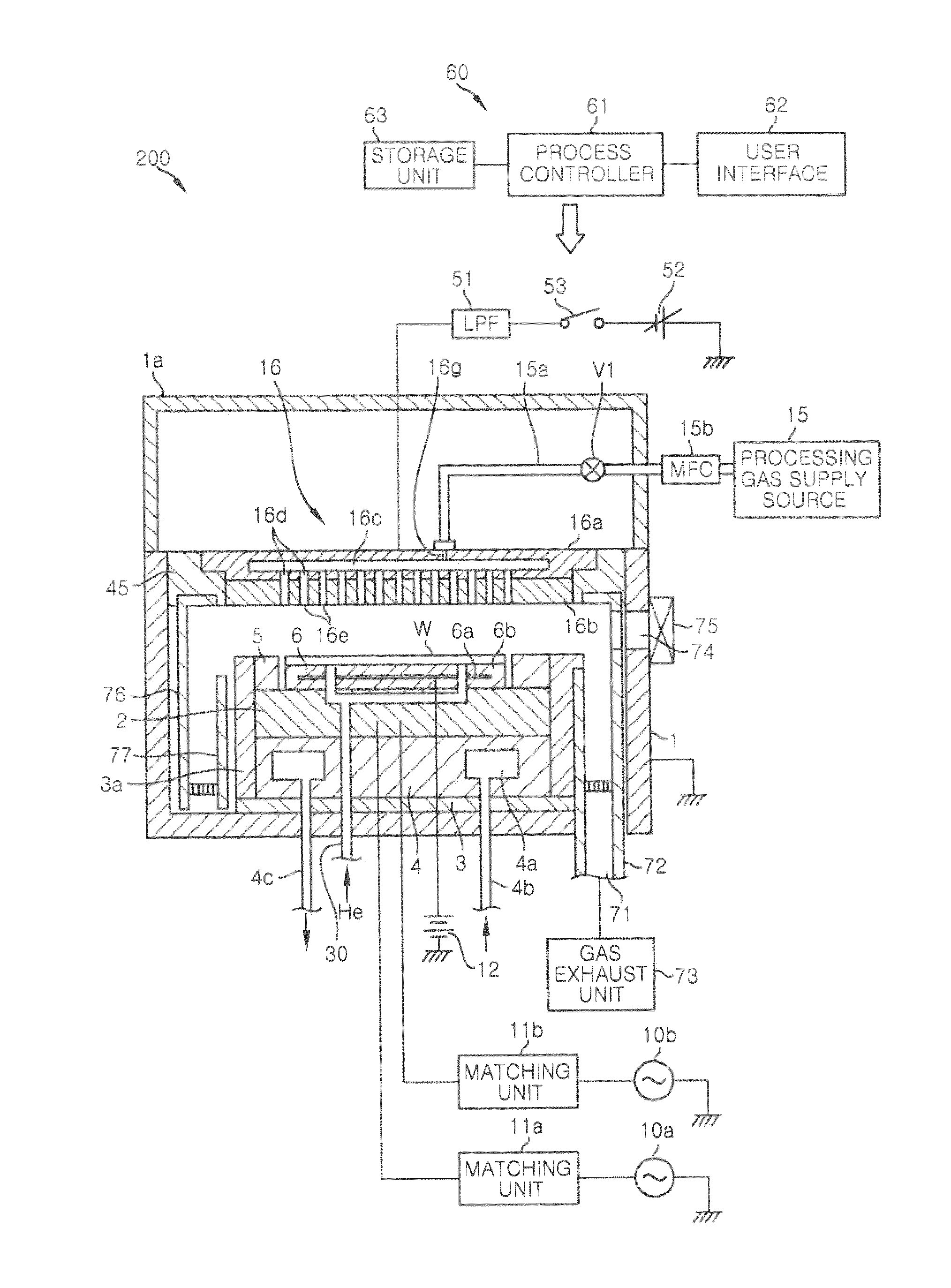

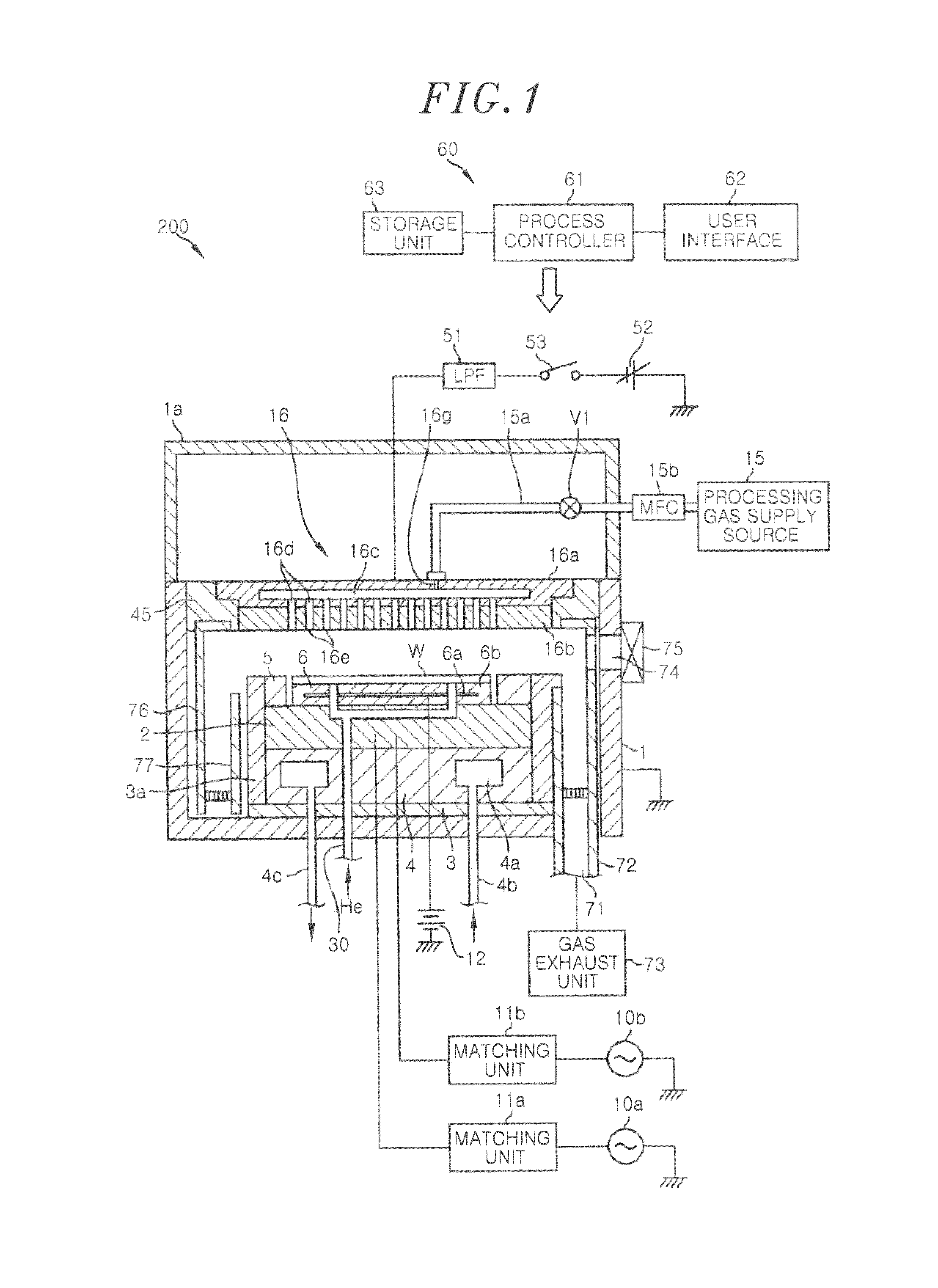

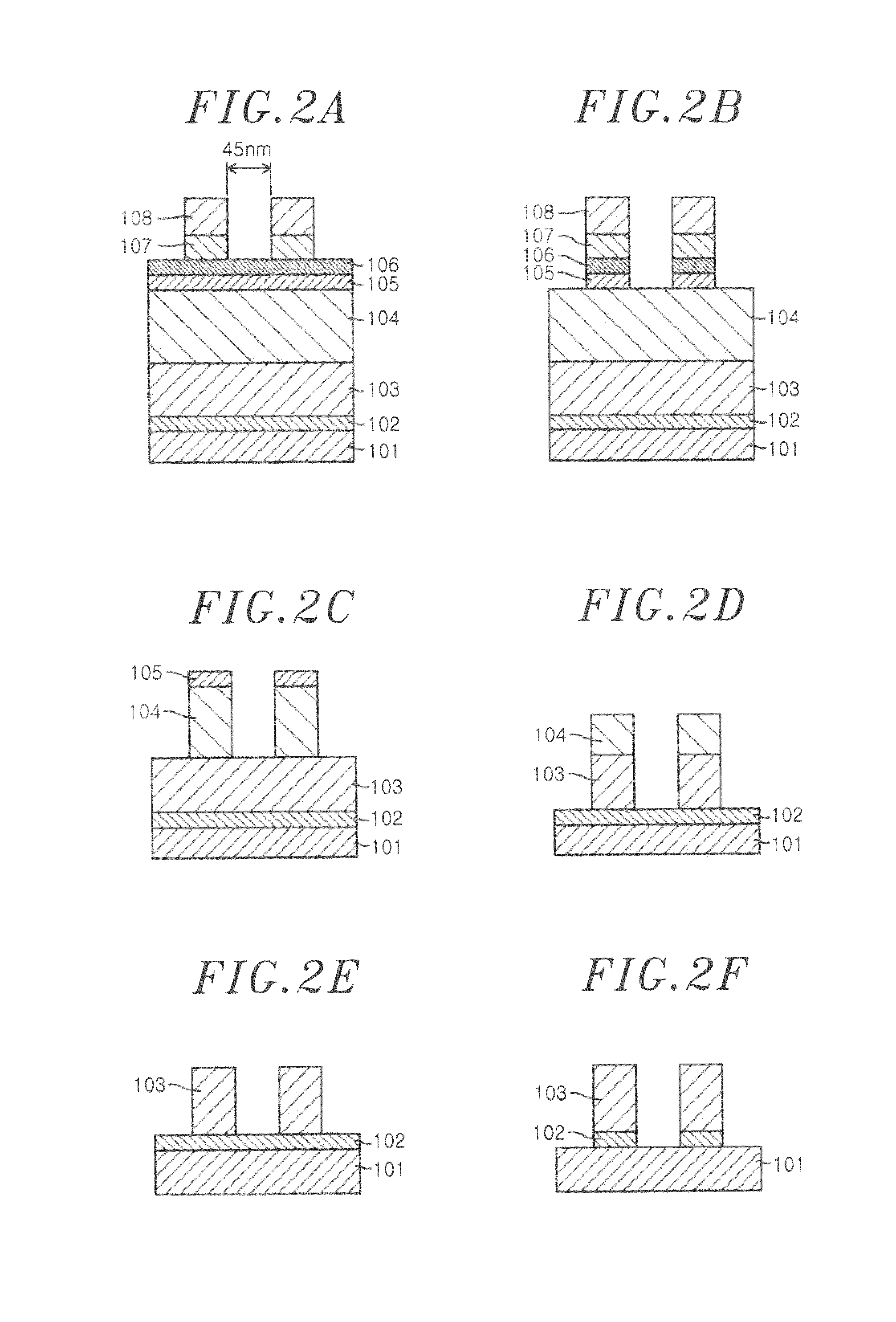

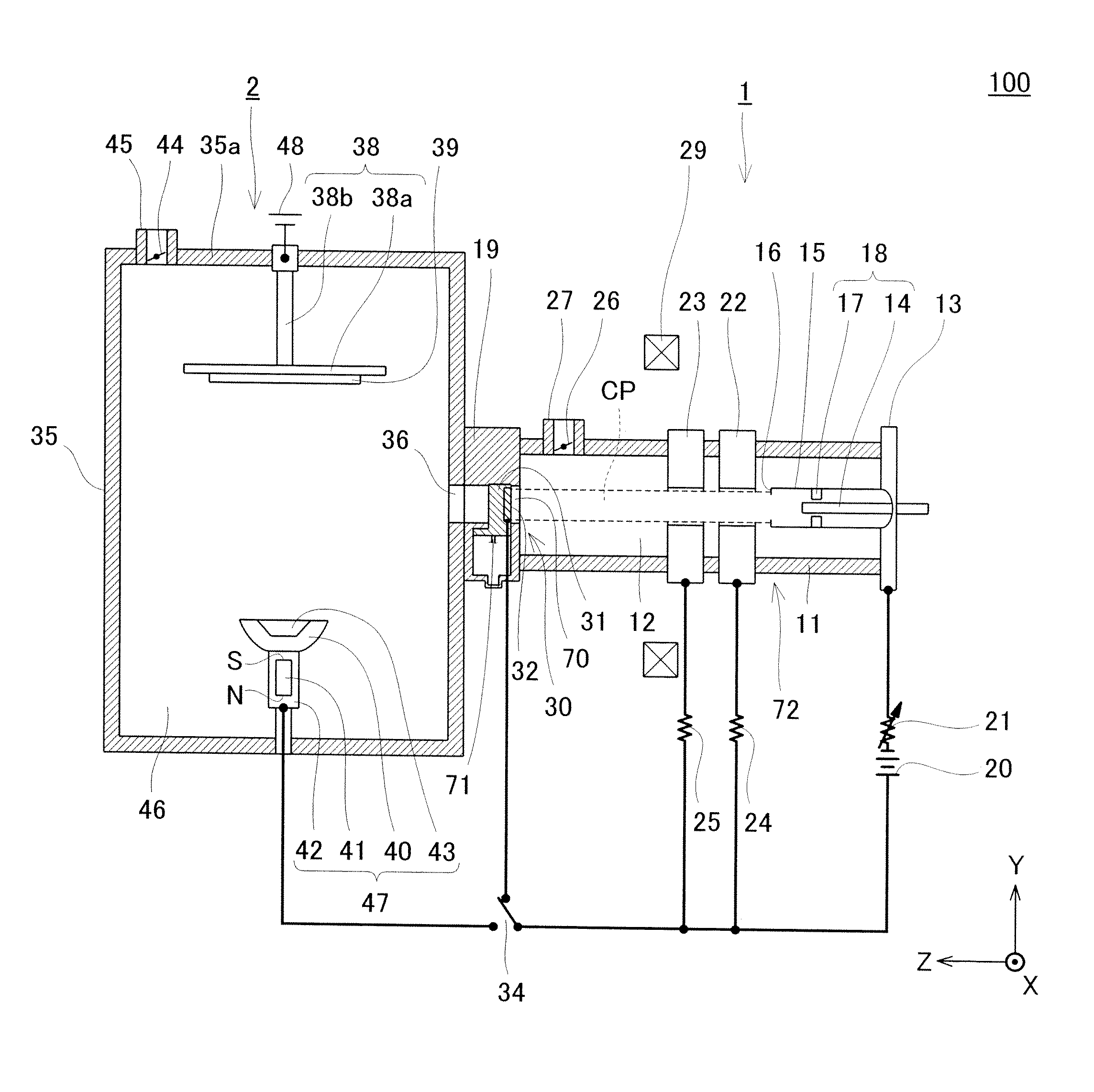

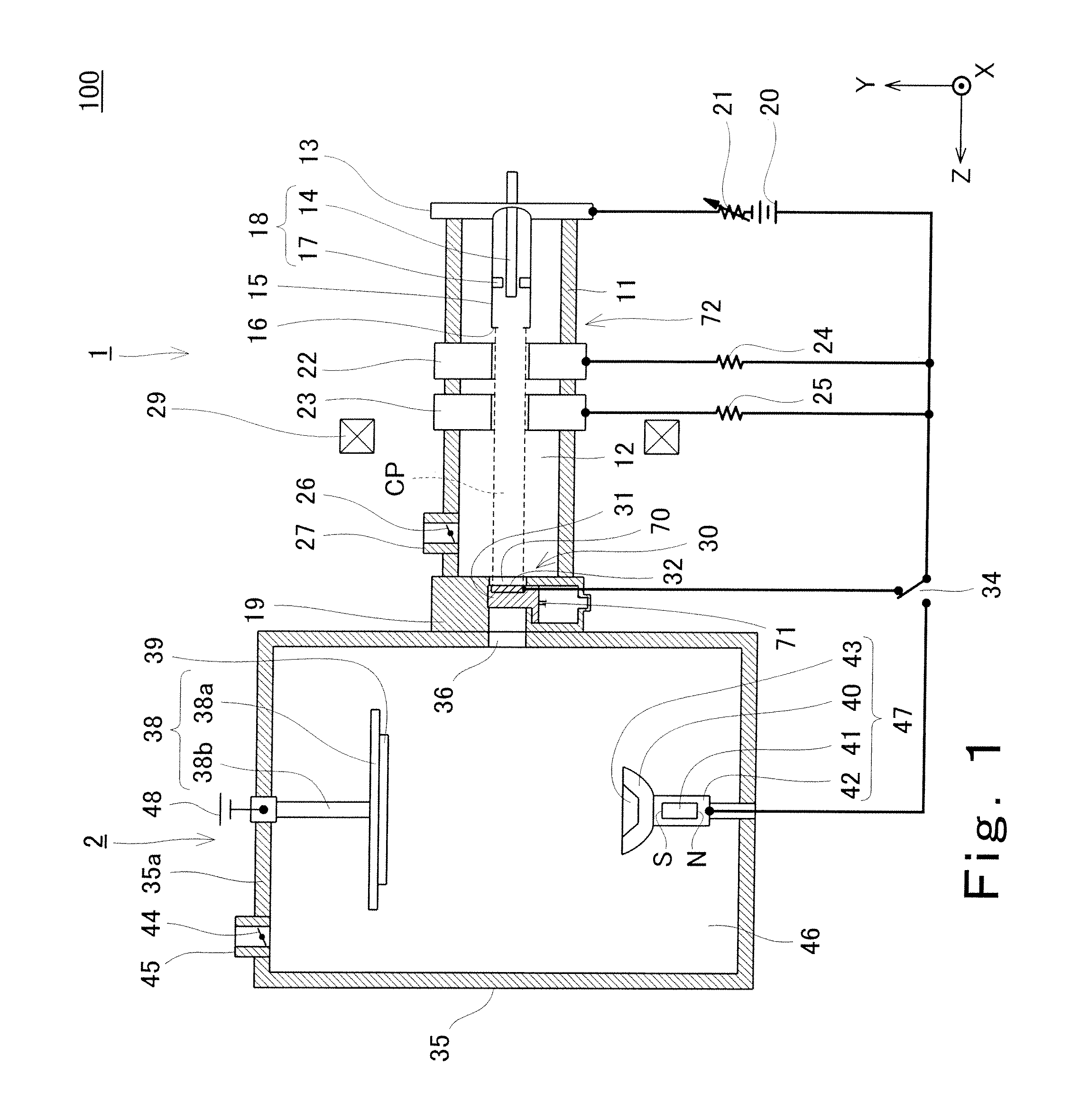

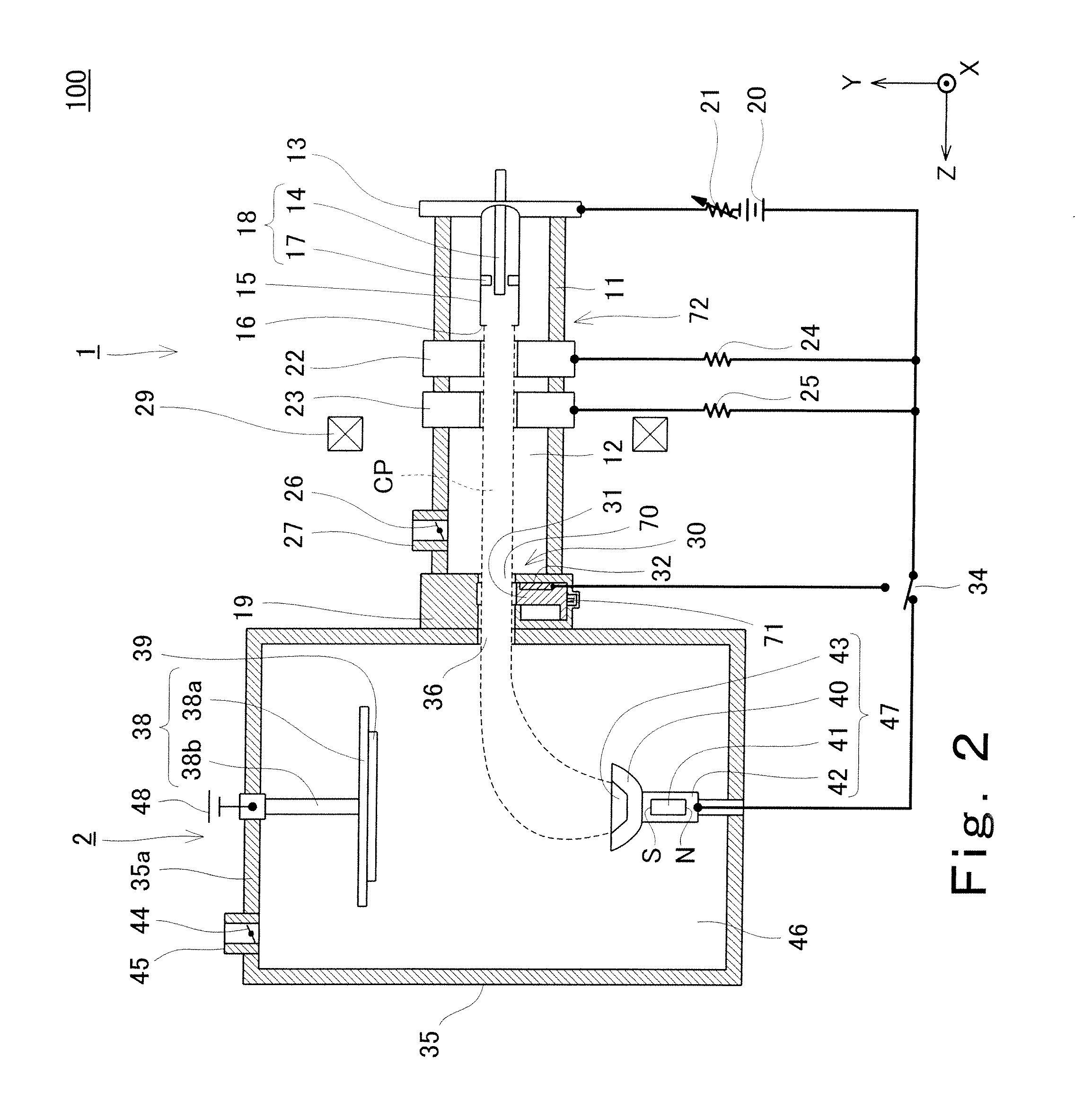

Semiconductor device manufacturing method and plasma etching apparatus

ActiveUS8491805B2Improve accuracyHigh selectivityElectric discharge tubesDecorative surface effectsEngineeringSemiconductor

Owner:TOKYO ELECTRON LTD

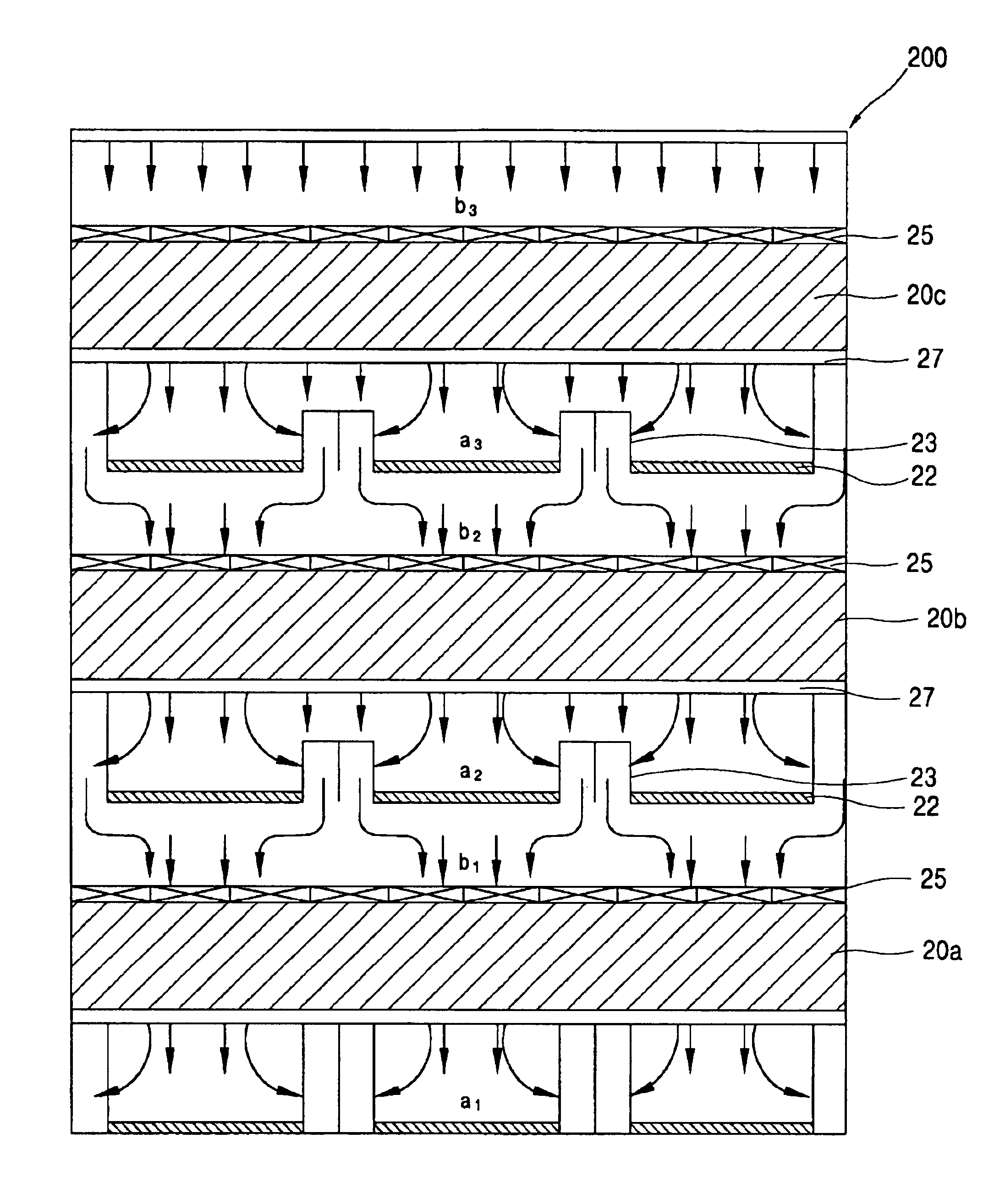

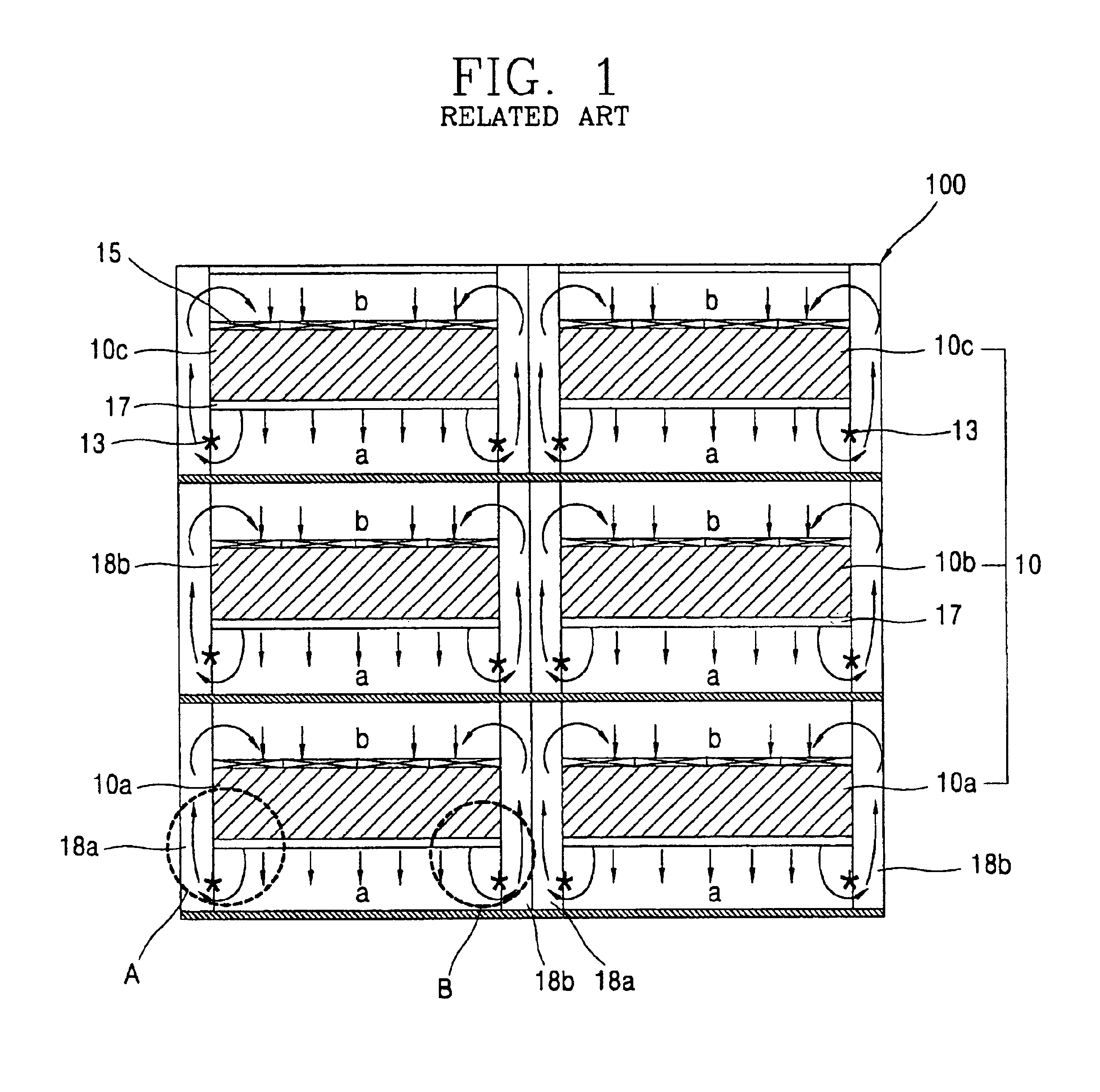

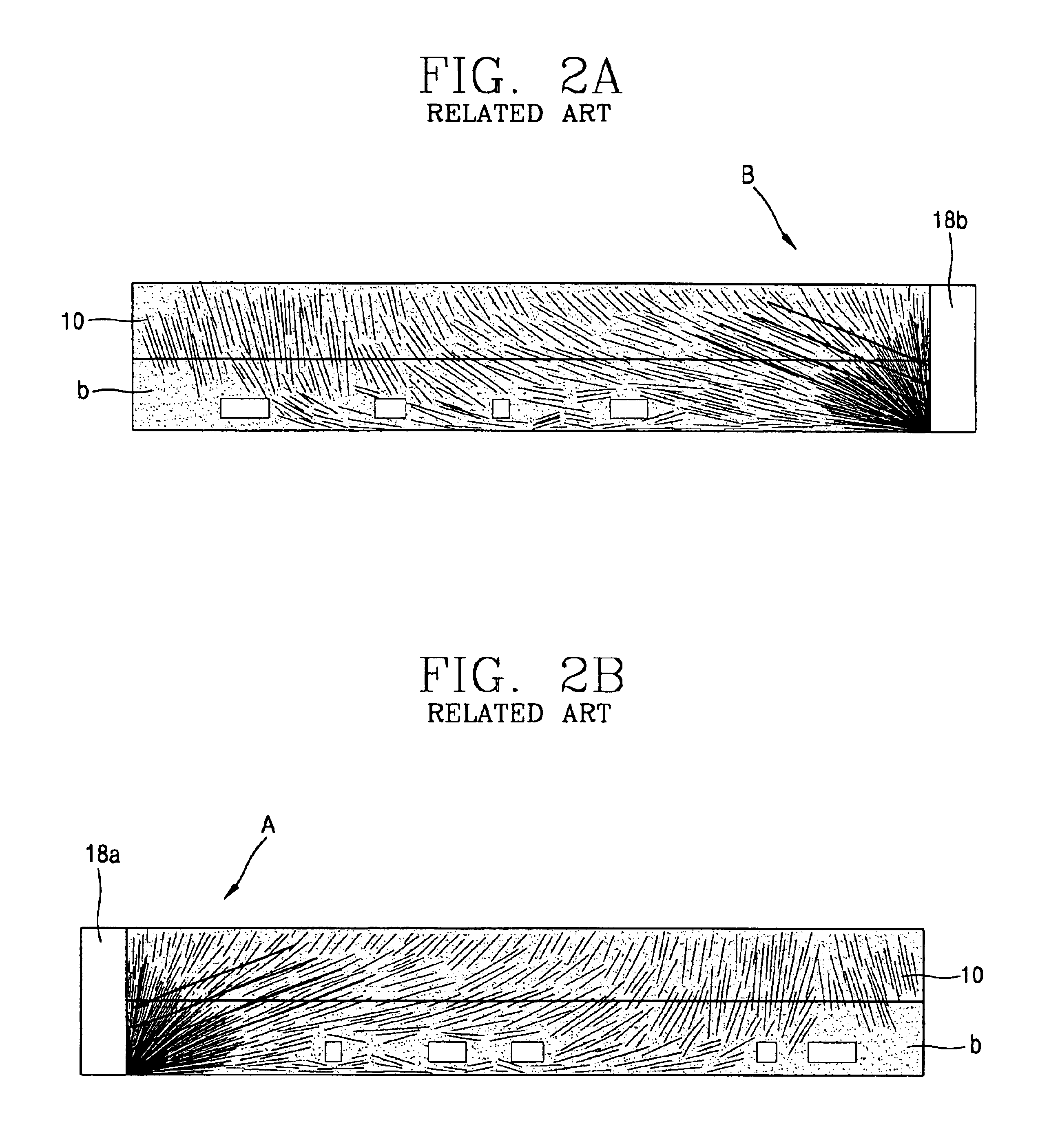

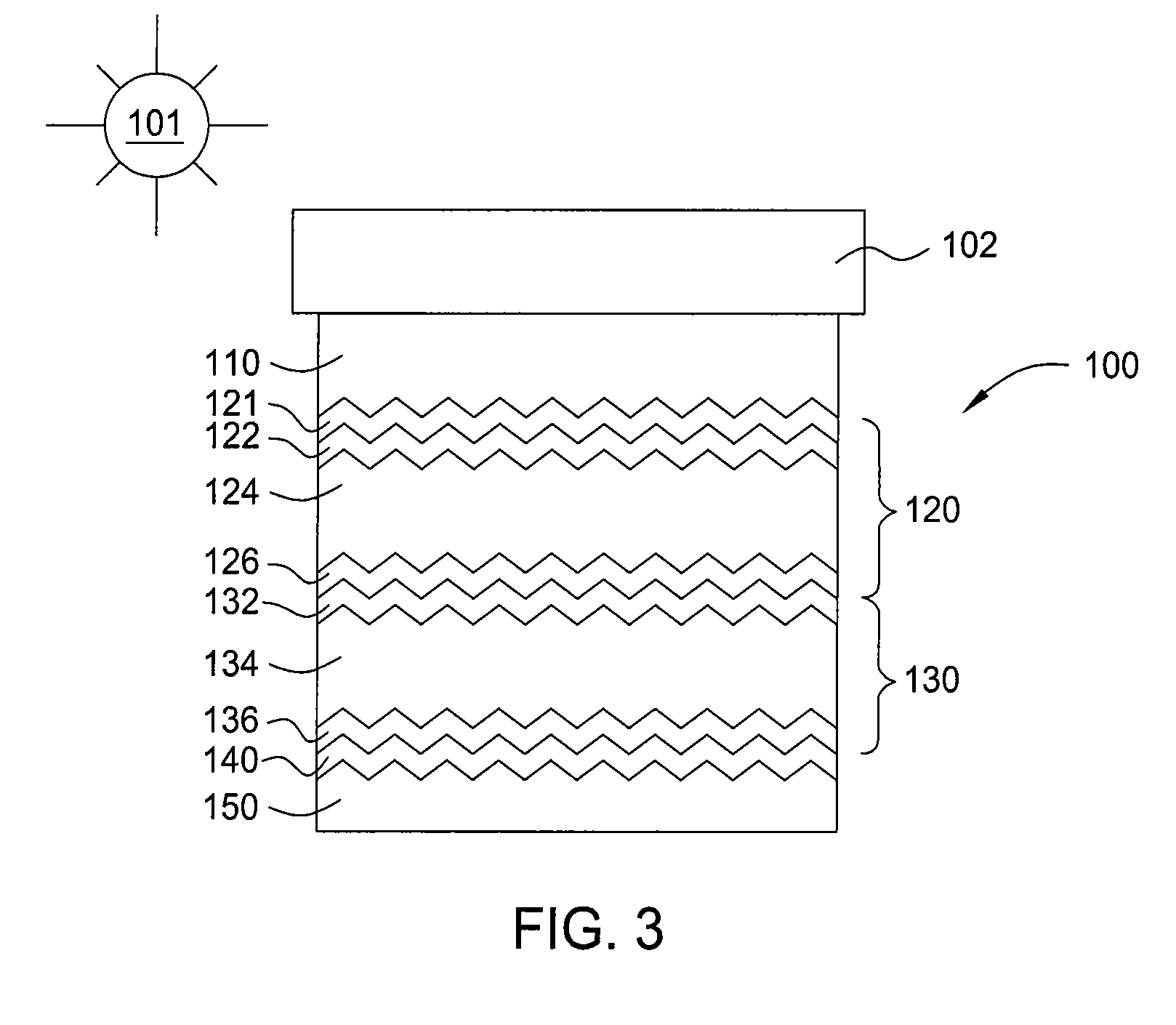

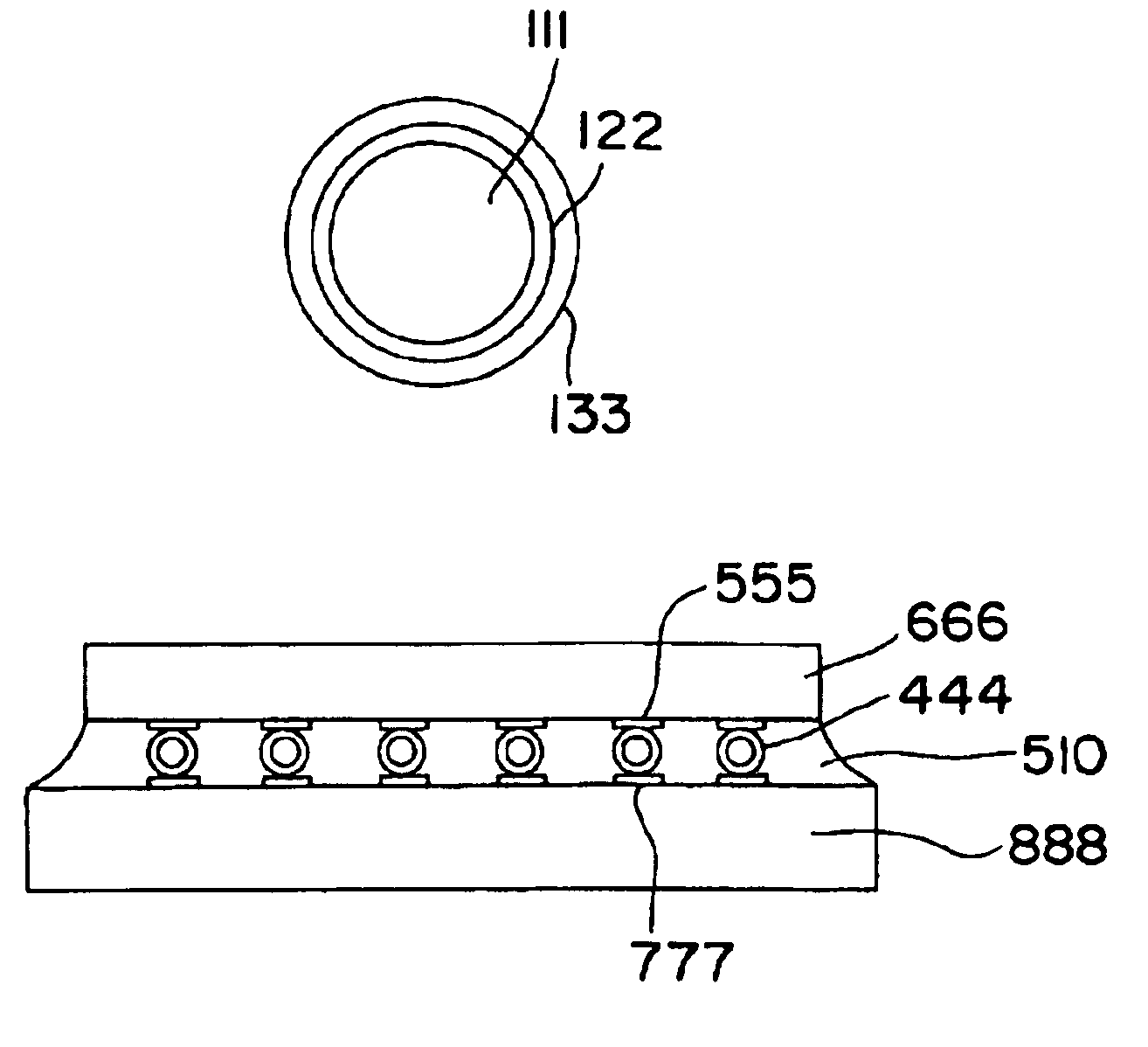

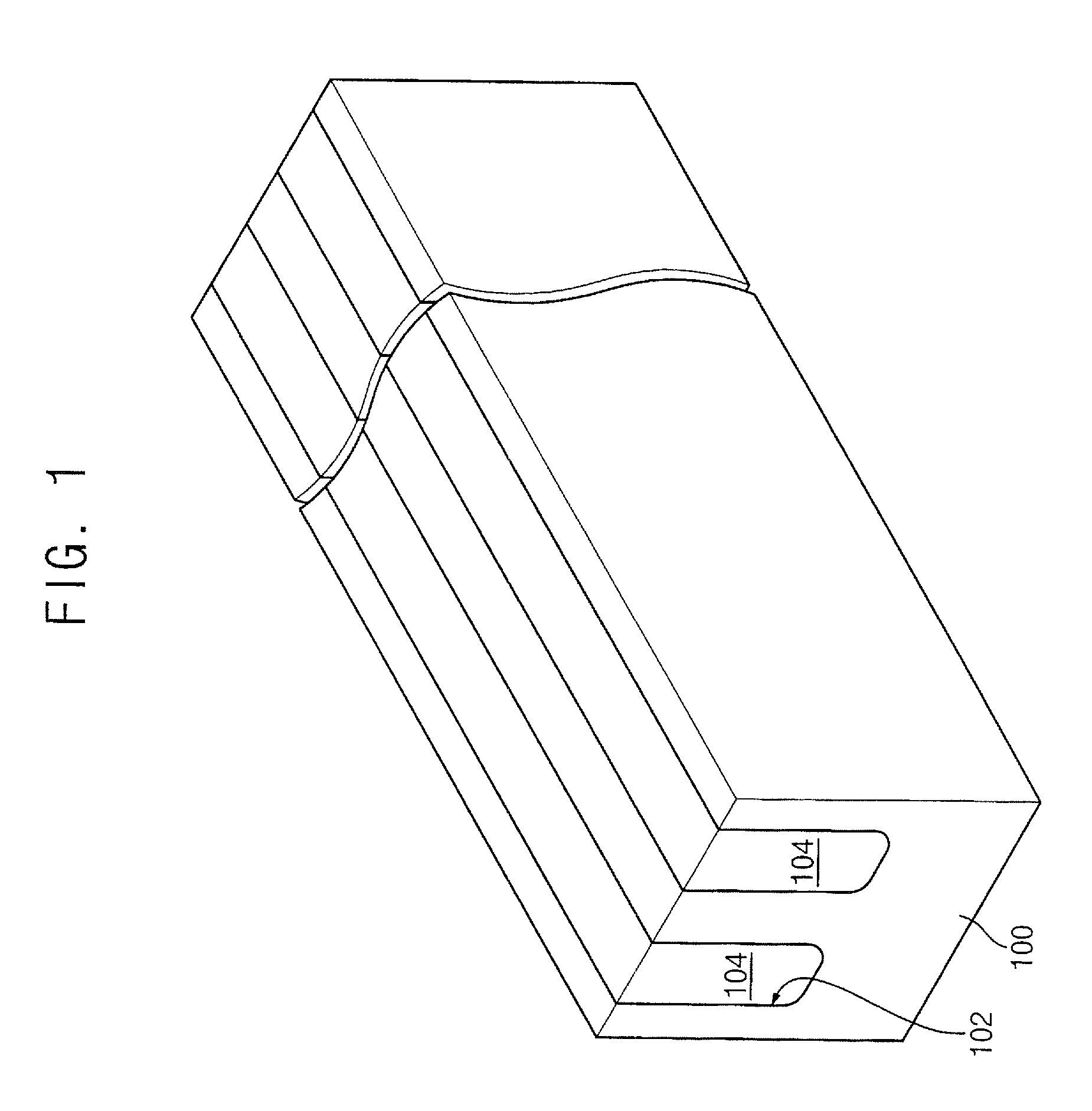

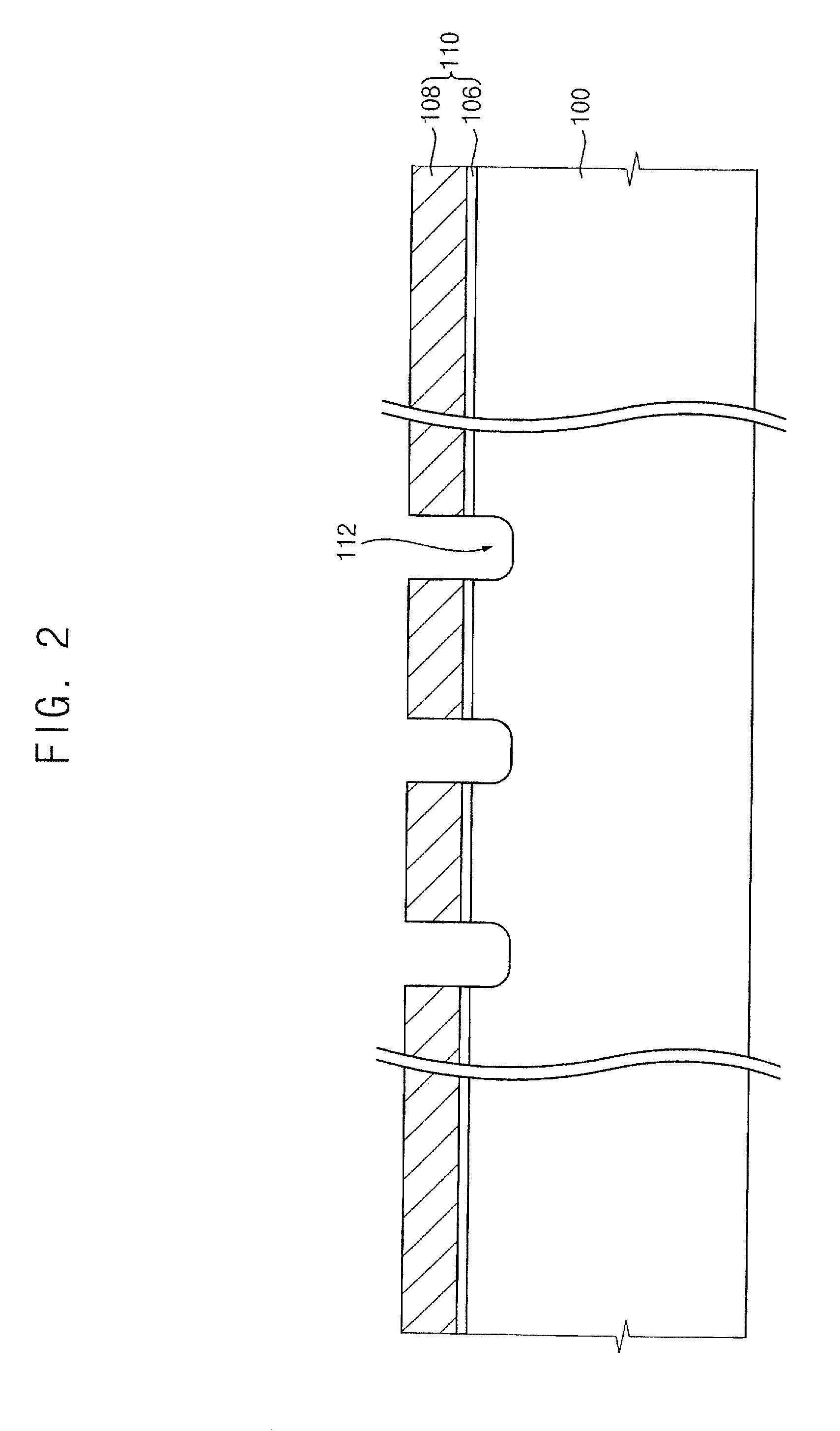

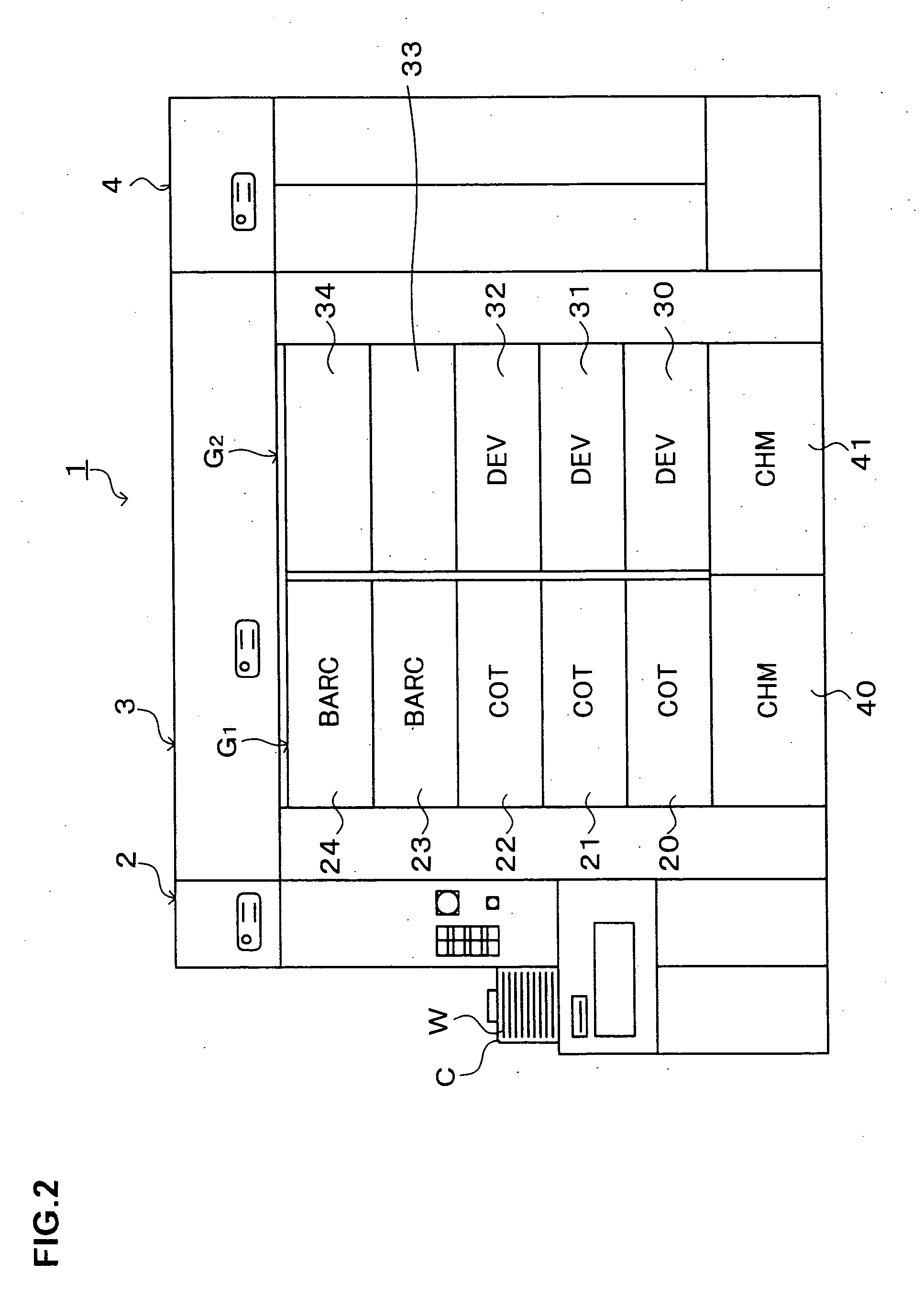

Clean room system

InactiveUS6955595B2Increase the use of spaceUniformly formedMechanical apparatusLighting and heating apparatusEngineering

A clean room system is provided. The clean room includes a plurality of multi-level clean rooms and an air passage. The plurality of multi-level clean rooms has at least a lower clean room and an upper clean room above the lower clean room. The air passage permits air flow between the upper clean room and the lower clean room and smooths the air flow.

Owner:LG DISPLAY CO LTD

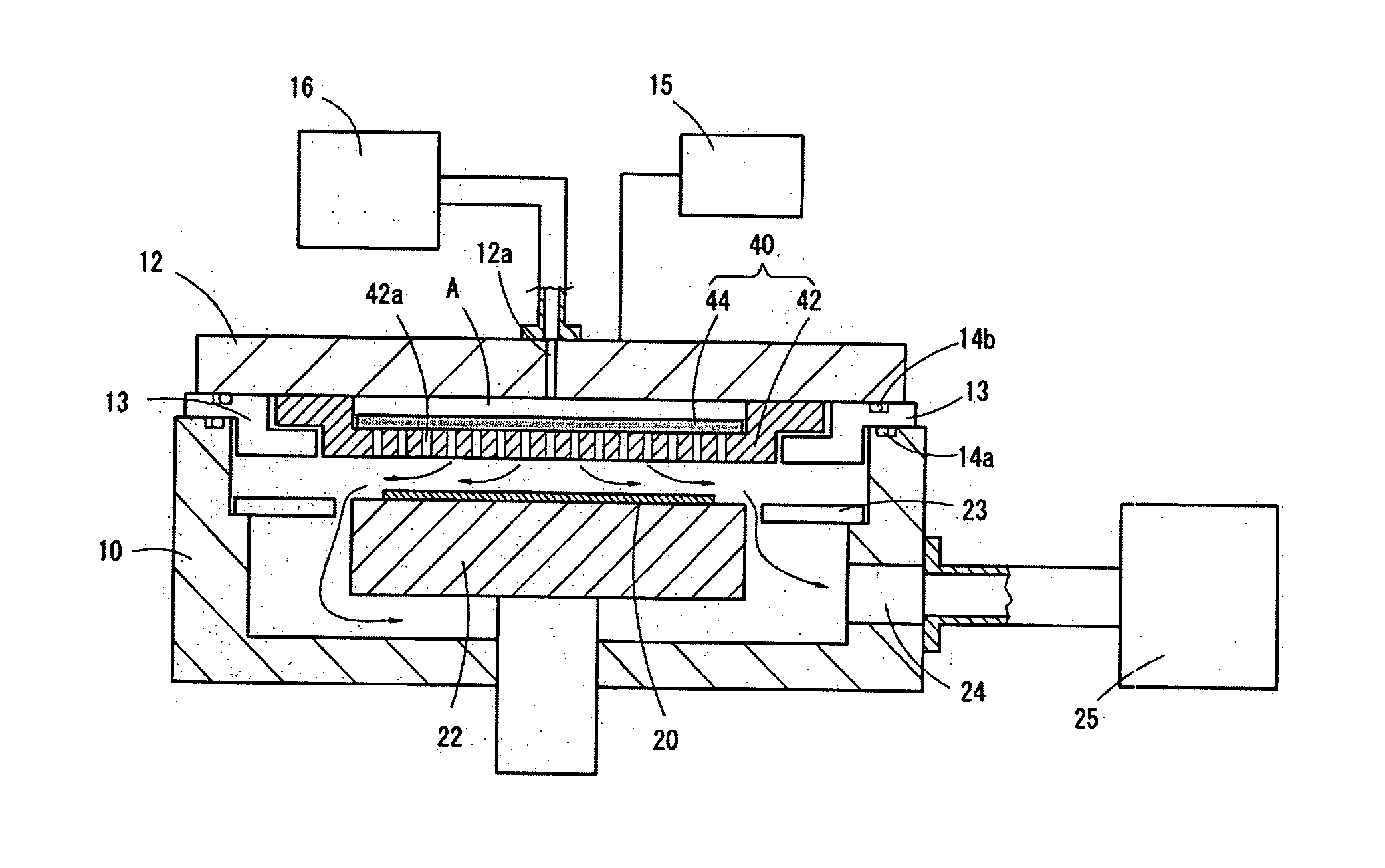

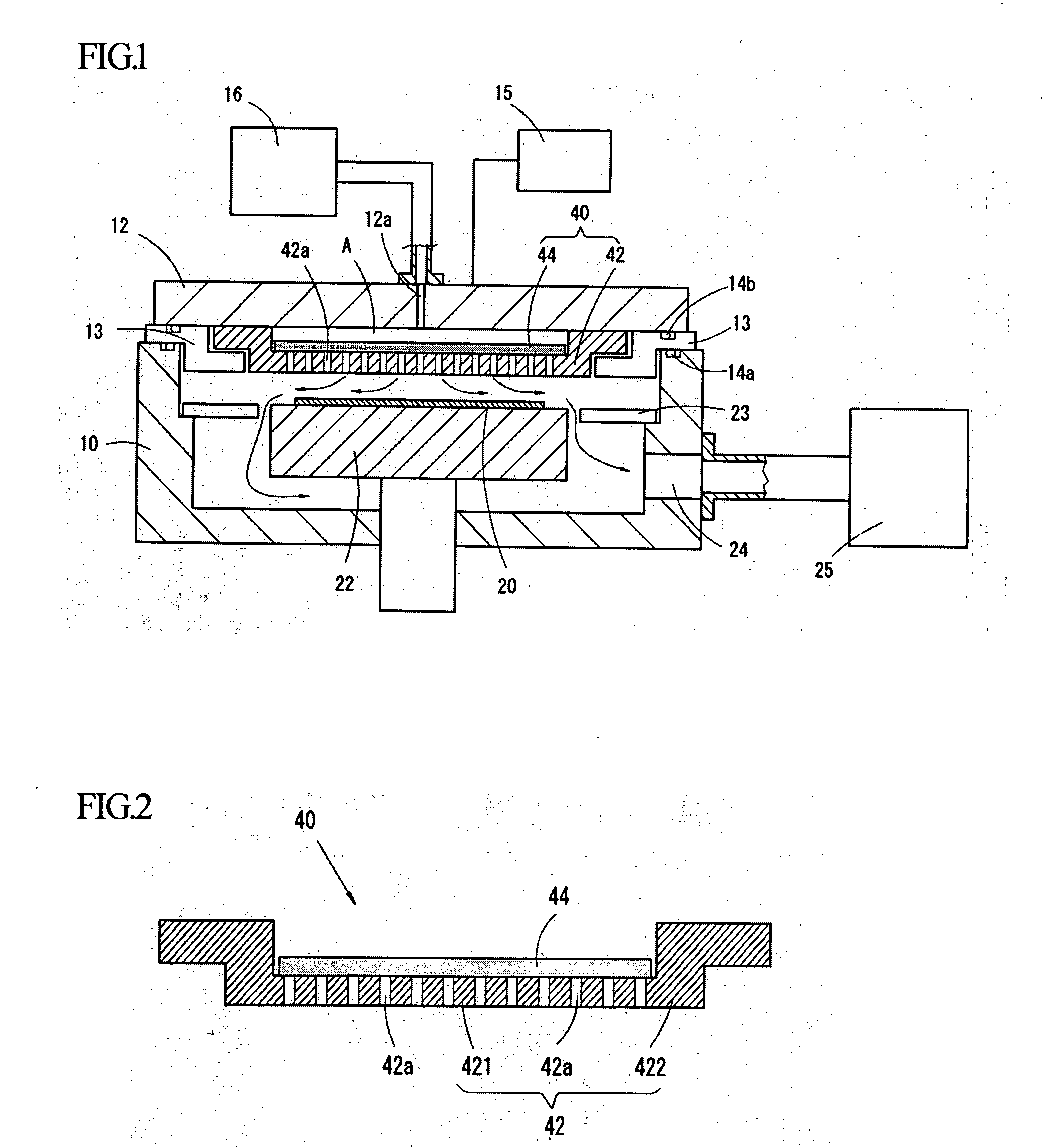

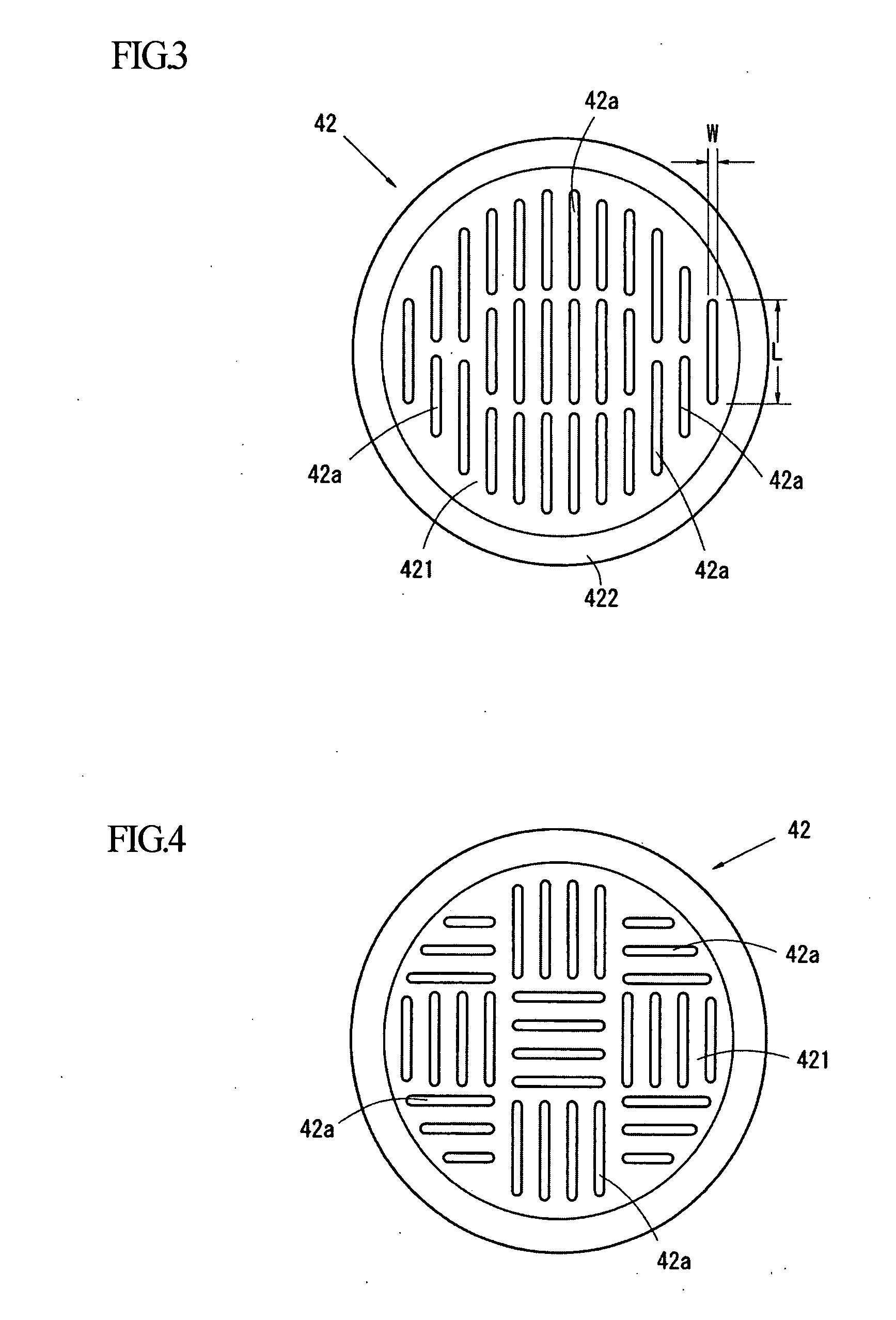

Shower head and cvd apparatus using the same

InactiveUS20080196666A1Efficient dissociationImprove efficiencyElectric discharge tubesChemical vapor deposition coatingEngineeringMechanical engineering

The showerhead for a CVD apparatus can be easily produced and is capable of forming a film efficiently. The showerhead comprises: a shower plate being made of a metal; and a porous plate contacting a rear face of the shower plate. A plurality of gas diffusion holes are formed in a plate section of the shower plate, which faces a workpiece, and penetrate the plate section in the thickness direction, and the porous plate covers all of the gas diffusion holes.

Owner:ORBOTECH LT SOLAR

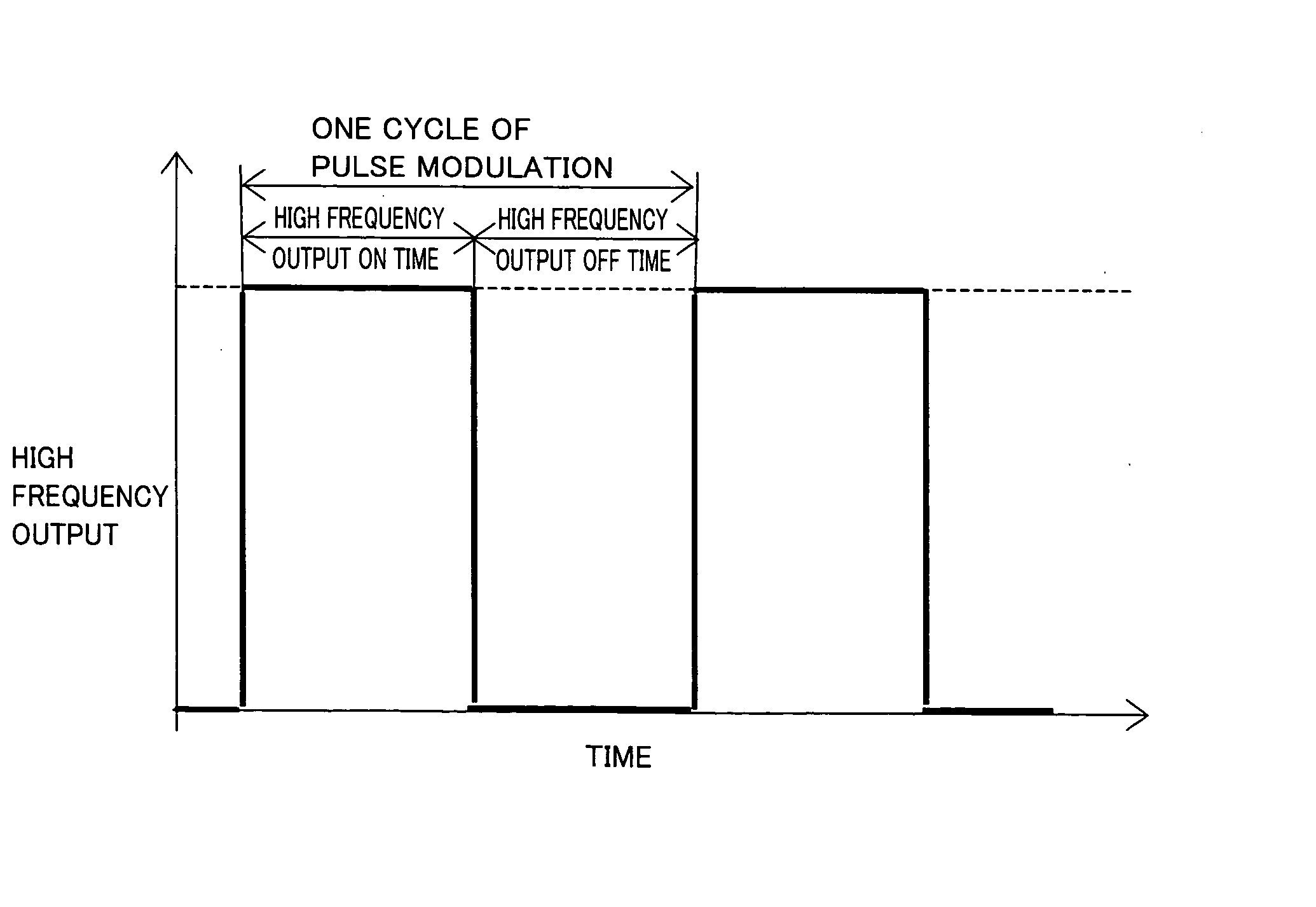

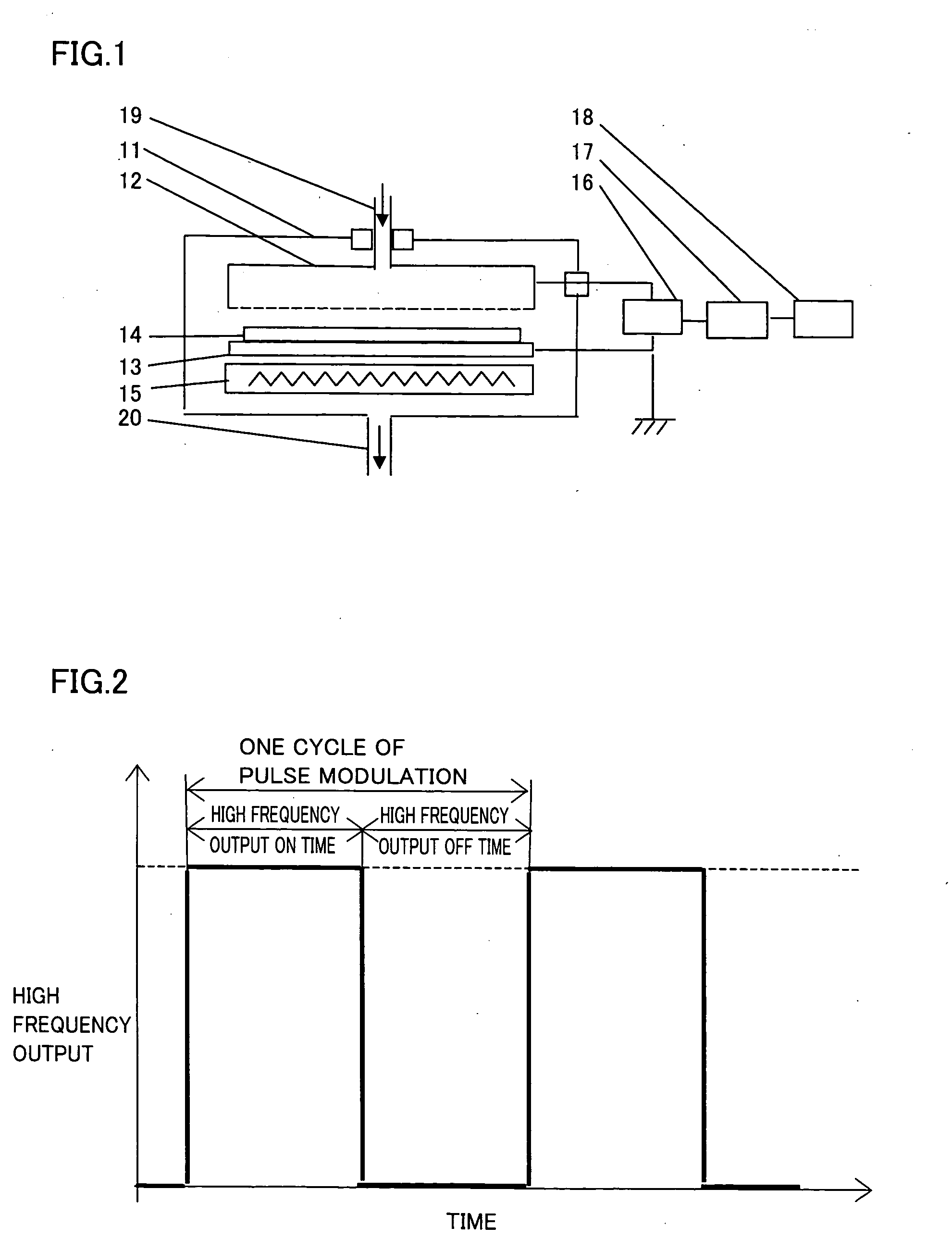

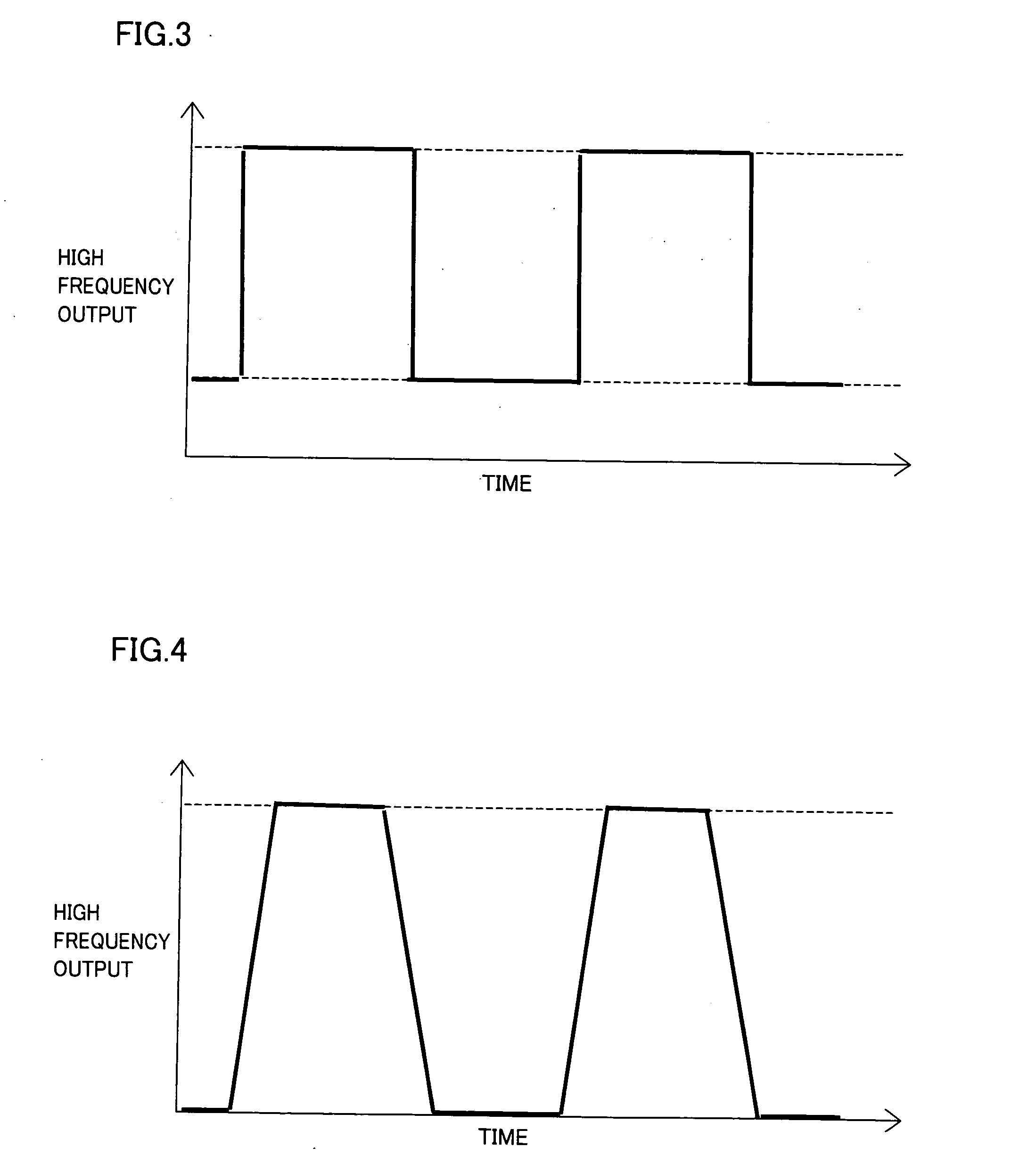

Manufacturing method of silicon thin film solar cell

InactiveUS20050022864A1Lower performance requirementsIncrease currentFinal product manufactureSemiconductor/solid-state device manufacturingHigh frequency powerSilicon thin film

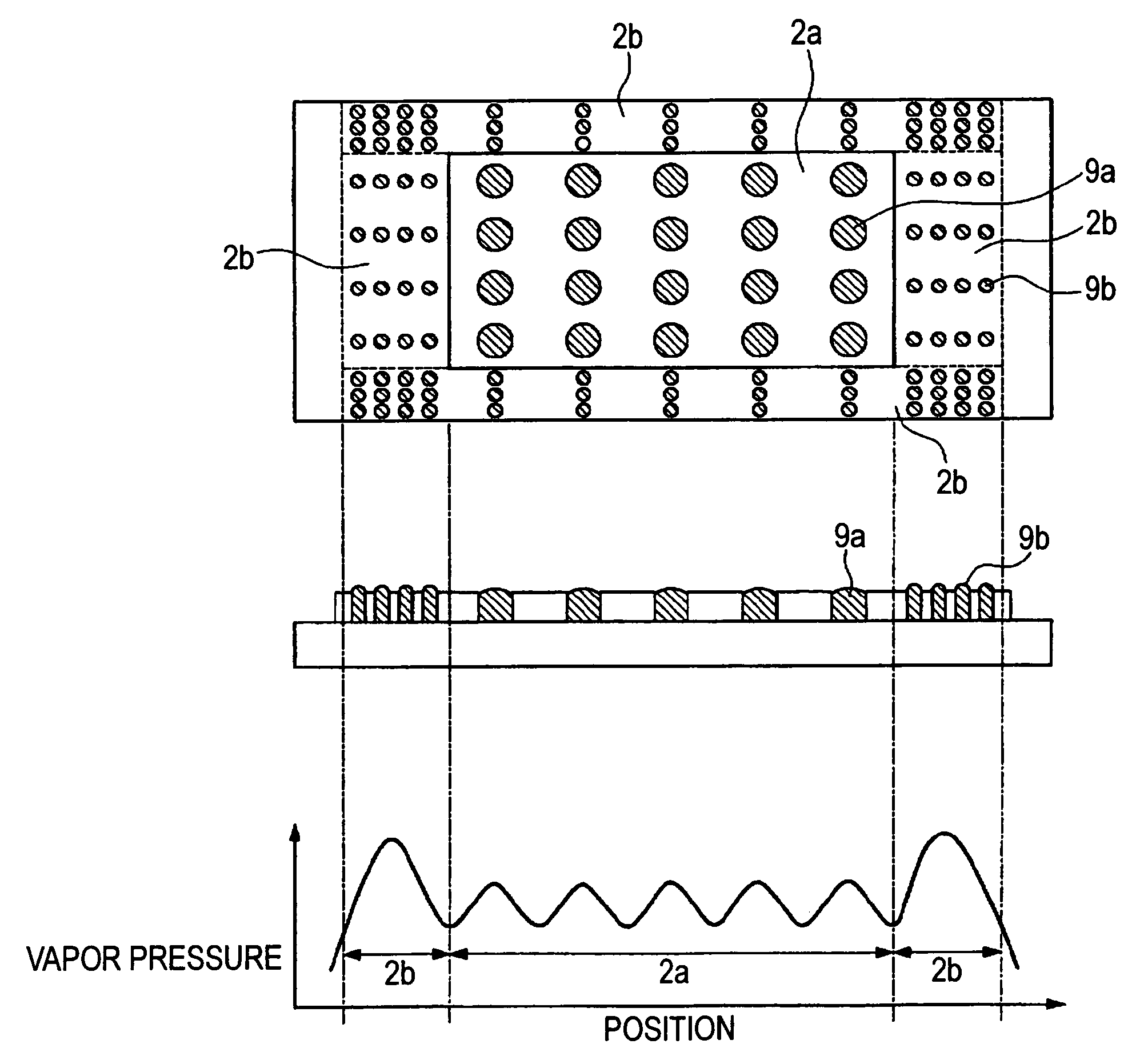

To uniformly form a silicon thin film for a solar cell, having an i layer formed with crystalline silicon, on a substrate of a large area to provide a high power solar cell, in a manufacturing method of a silicon thin film solar cell, a silicon thin film, having a structure such that an i layer is sandwiched between a p layer and an n layer, is formed on a substrate with a high frequency plasma CVD method, wherein i layer is formed with crystalline silicon using plasma with pulse-modulated high frequency power, one cycle of pulse modulation includes an ON state for outputting high frequency power and an OFF state for not outputting, an output waveform is modulated to be rectangular, a time of the ON state is 1-100 microseconds, and a time of the OFF state is 5 microseconds or longer.

Owner:SHARP KK

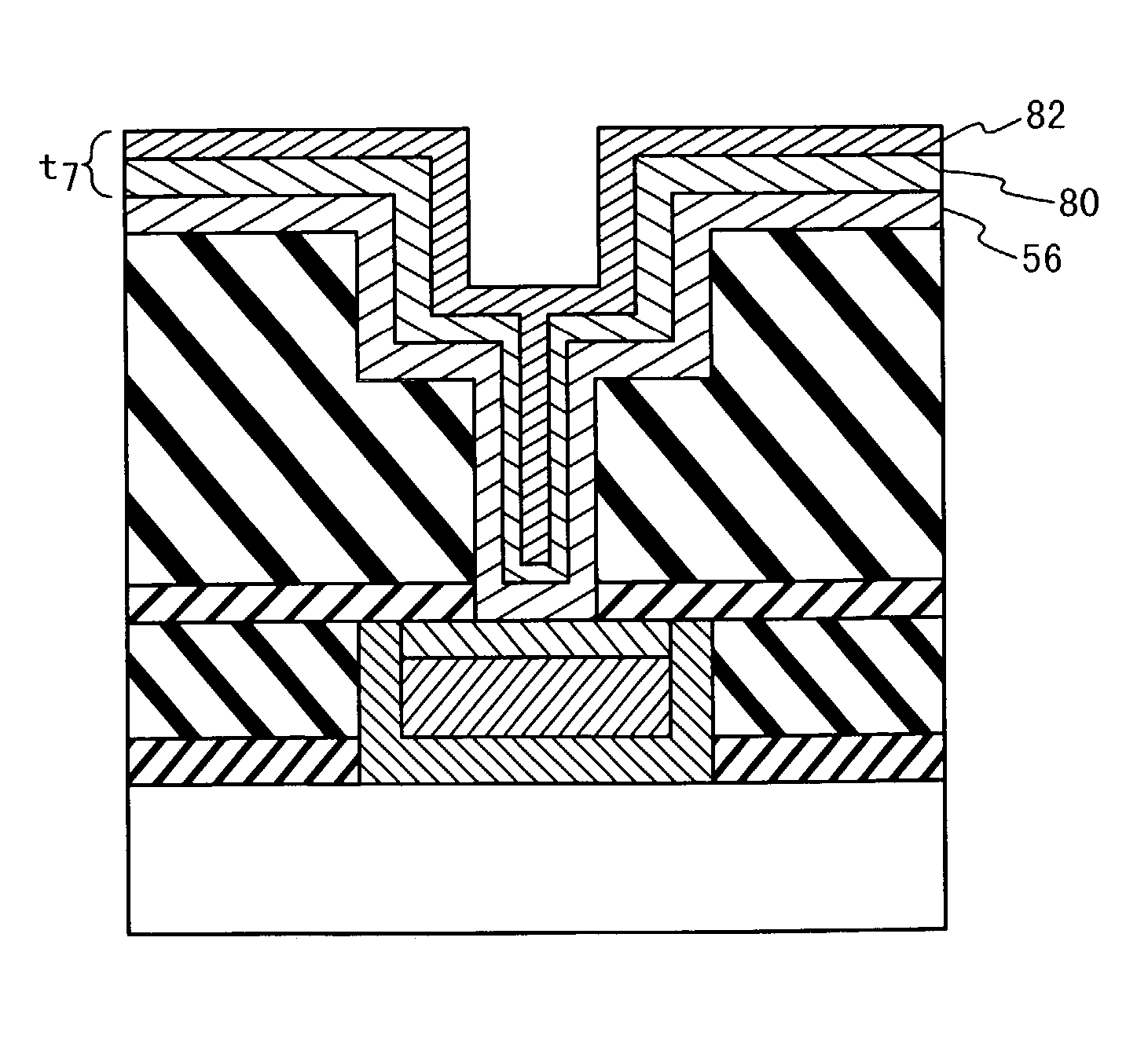

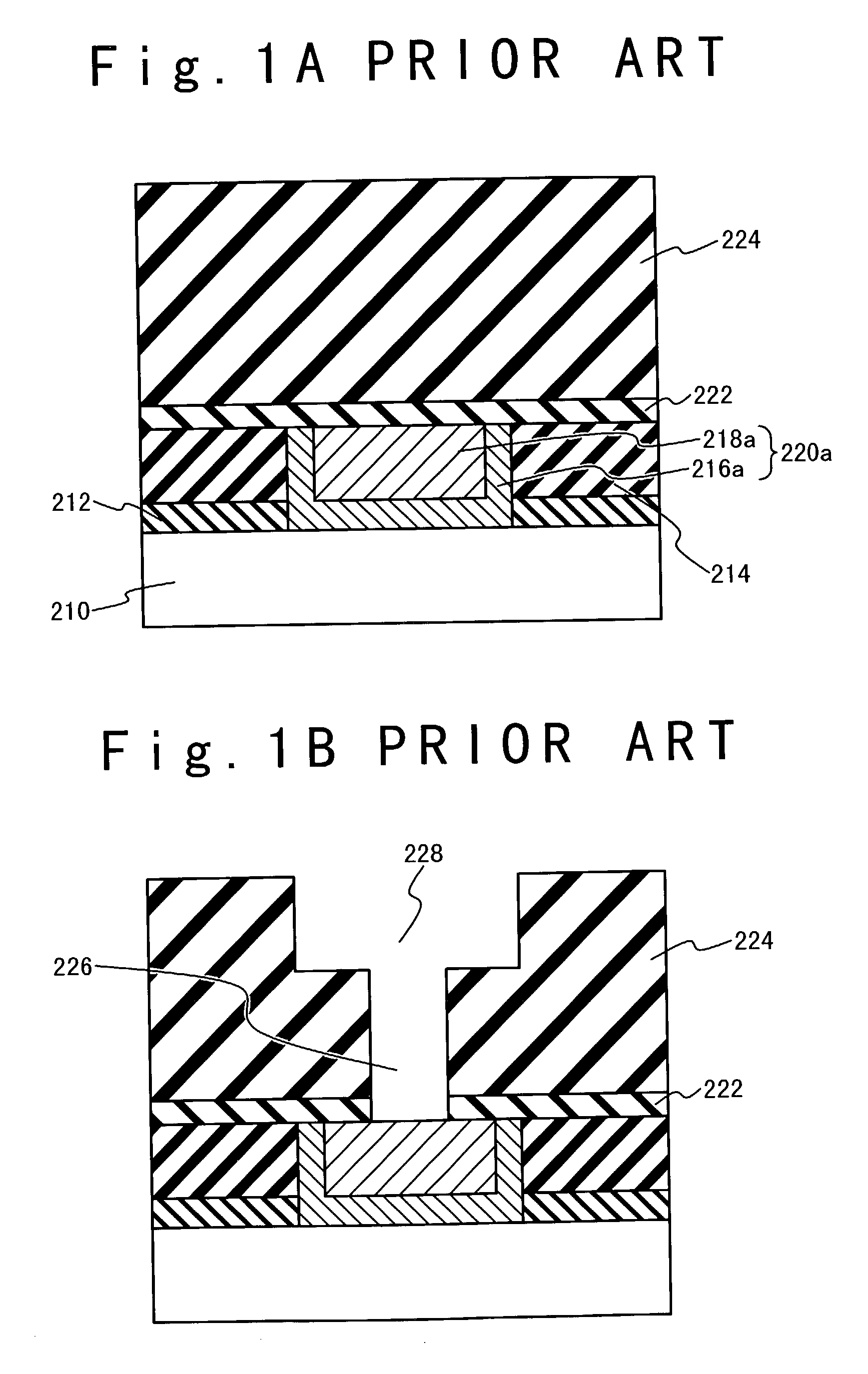

Semiconductor device and manufacturing method for the same

ActiveUS20030173671A1Improve production yieldImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

In a method of manufacturing a semiconductor device, a first wiring line composed of a copper containing metal film is formed on or above a semiconductor substrate. A first interlayer insulating film is formed on a whole surface of the semiconductor substrate to cover the first wiring line. The first interlayer insulating film is selectively removed to form a connection hole reaching the first wiring line. A barrier metal film is formed to cover an inner surface of the connection hole and then a copper containing metal film is formed to fill the connection hole. The copper containing metal film formed outside the connection hole is removed. A second interlayer insulating film is formed on a whole surface of the semiconductor substrate to cover the copper containing metal film formed in the connection hole. The second interlayer insulating film is selectively removed to form a wiring line groove such that the copper containing metal film formed in the connection hole is exposed at a bottom. A barrier metal film is formed to cover an inside of the wiring line groove and then a copper containing metal film is formed to fill the wiring line groove. Then, the copper containing metal film outside the wiring line groove is removed to form a second wiring line.

Owner:TESSERA ADVANCED TECH

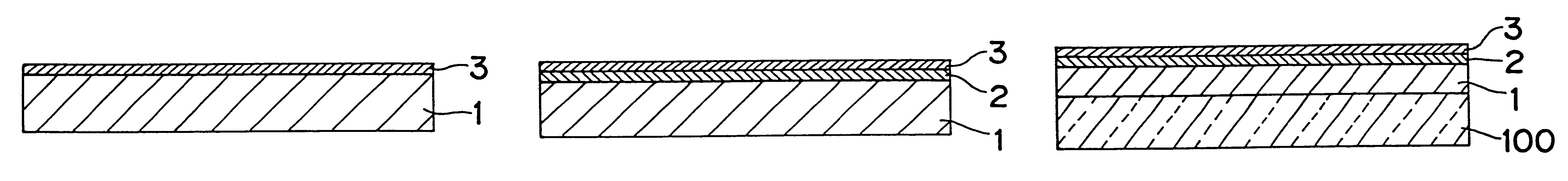

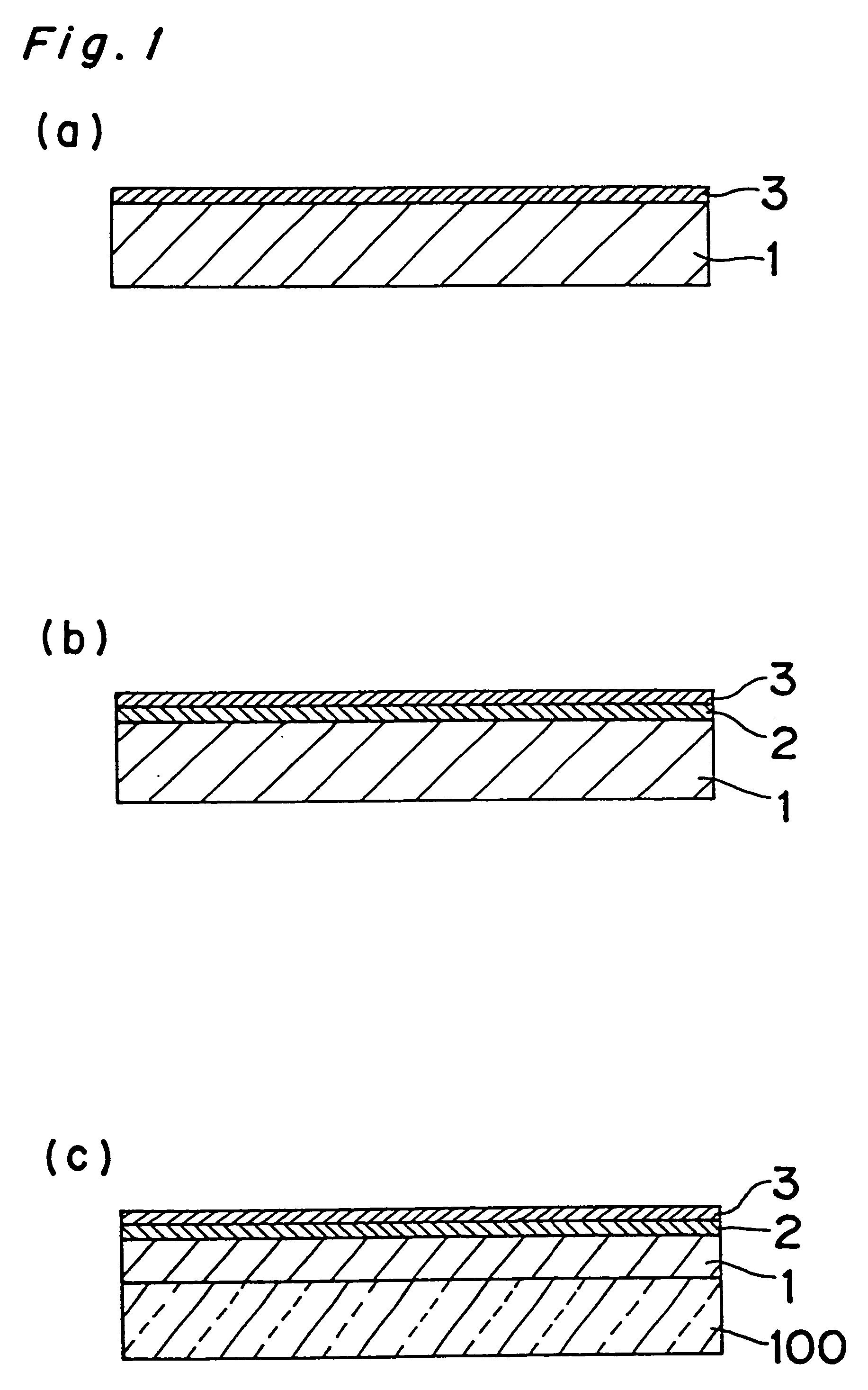

Aerogel substrate and method for preparing the same

InactiveUS6740416B1Uniformly formedLiquid surface applicatorsSolid-state devicesHydrophilizationInter layer

An aerogel substrate useful for an electrically conductive substrate, a heat insulating substrate, an optical waveguide substrate, a substrate for a light emitting device or a light emitting device is provided.The aerogel substrate is characterized by comprising a functional layer and an aerogel layer, and an intermediate layer formed between the functional layer and the aerogel layer to allow the functional layer to be formed uniformly thereon. The intermediate layer is formed on at least one surface of the aerogel layer by a gas phase method, by the Langmuir-Blodgett method or by adsorption of an inorganic layered compound; or formed by a hydrophilicizing treatment of at least one surface of the aerogel layer followed by coating and drying an aqueous coating fluid, by an annealing treatment of at least one surface of the aerogel layer, or by a hydrophilicizing treatment of at least one surface of the aerogel layer.

Owner:MATSUSHITA ELECTRIC WORKS LTD

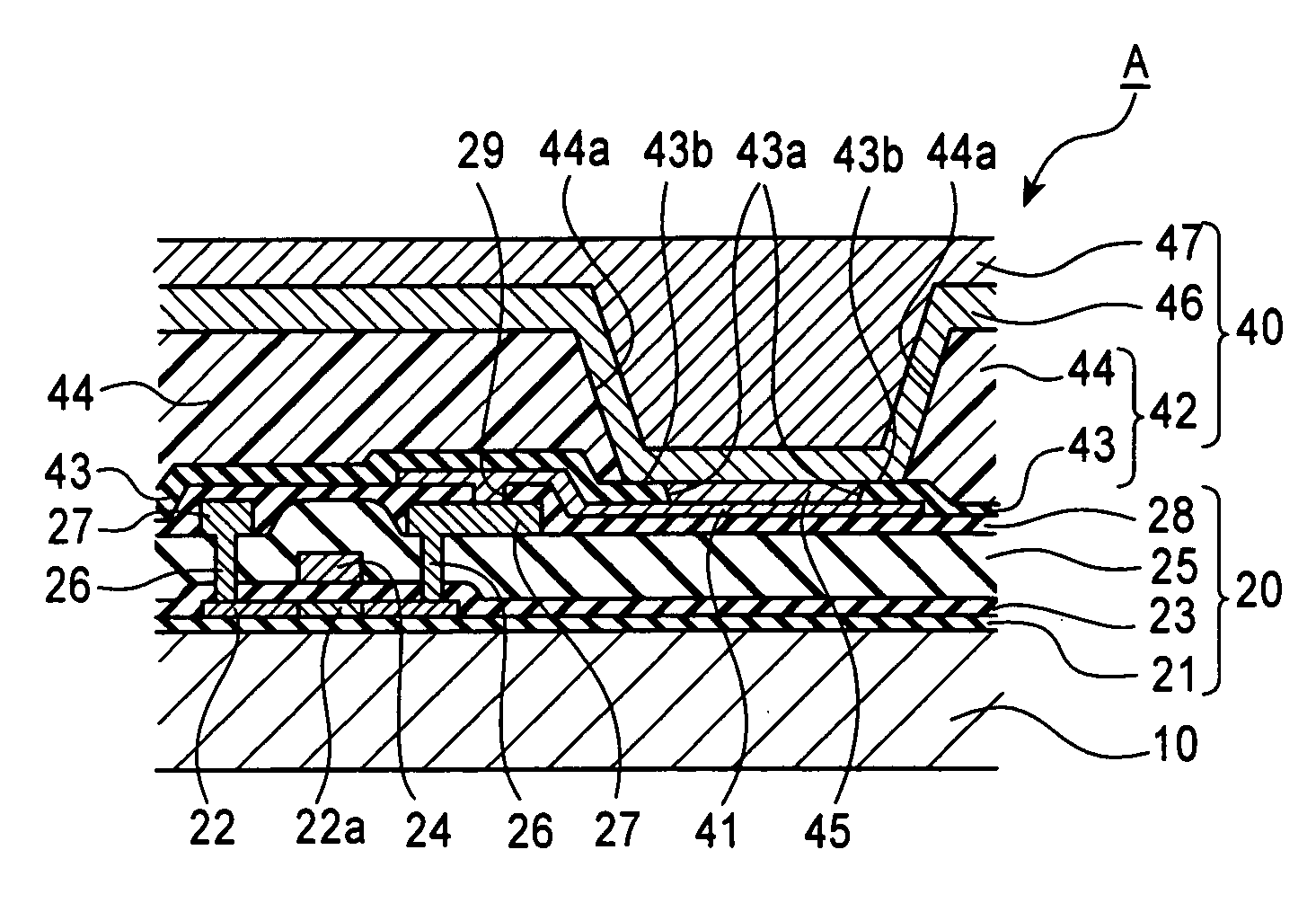

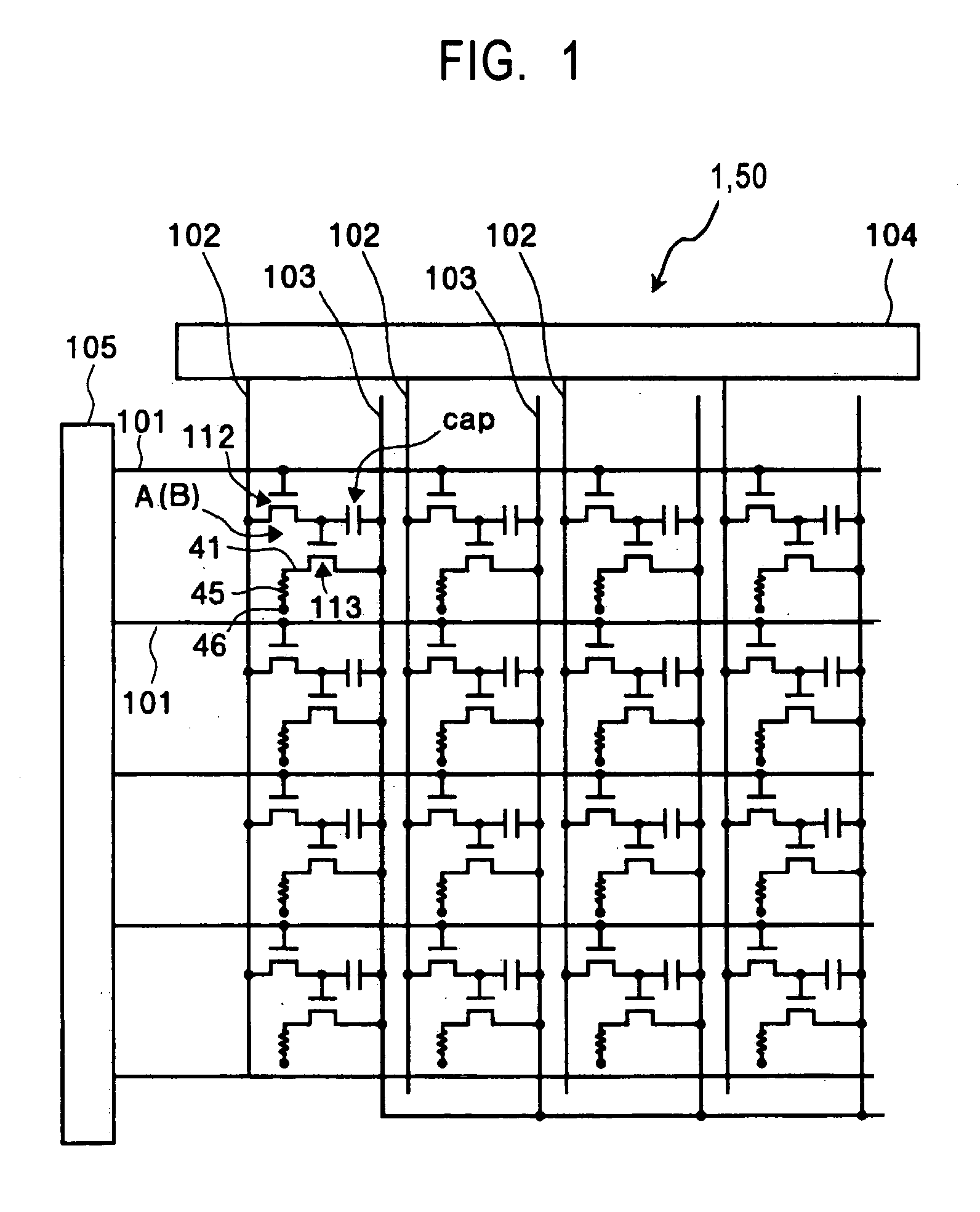

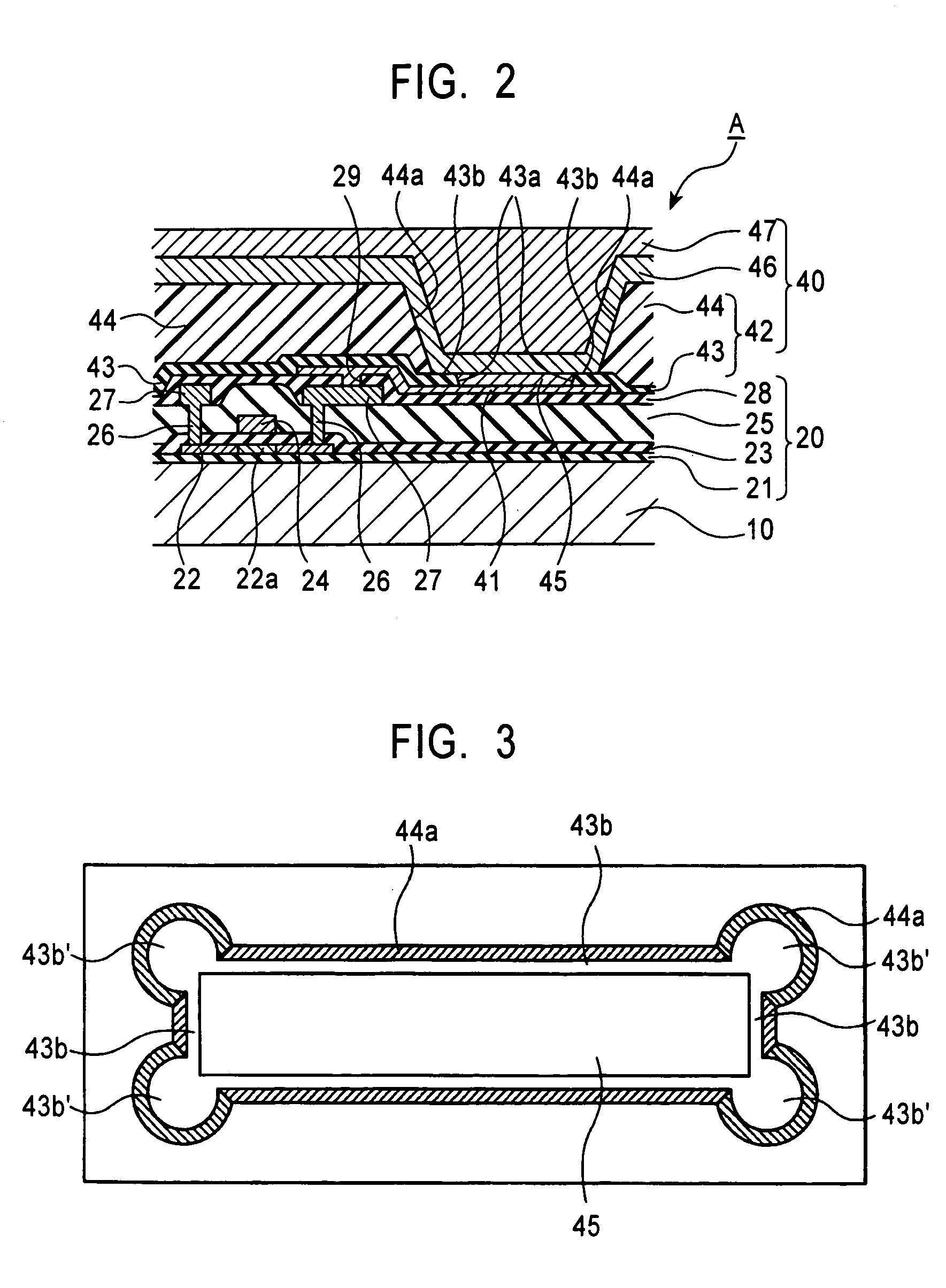

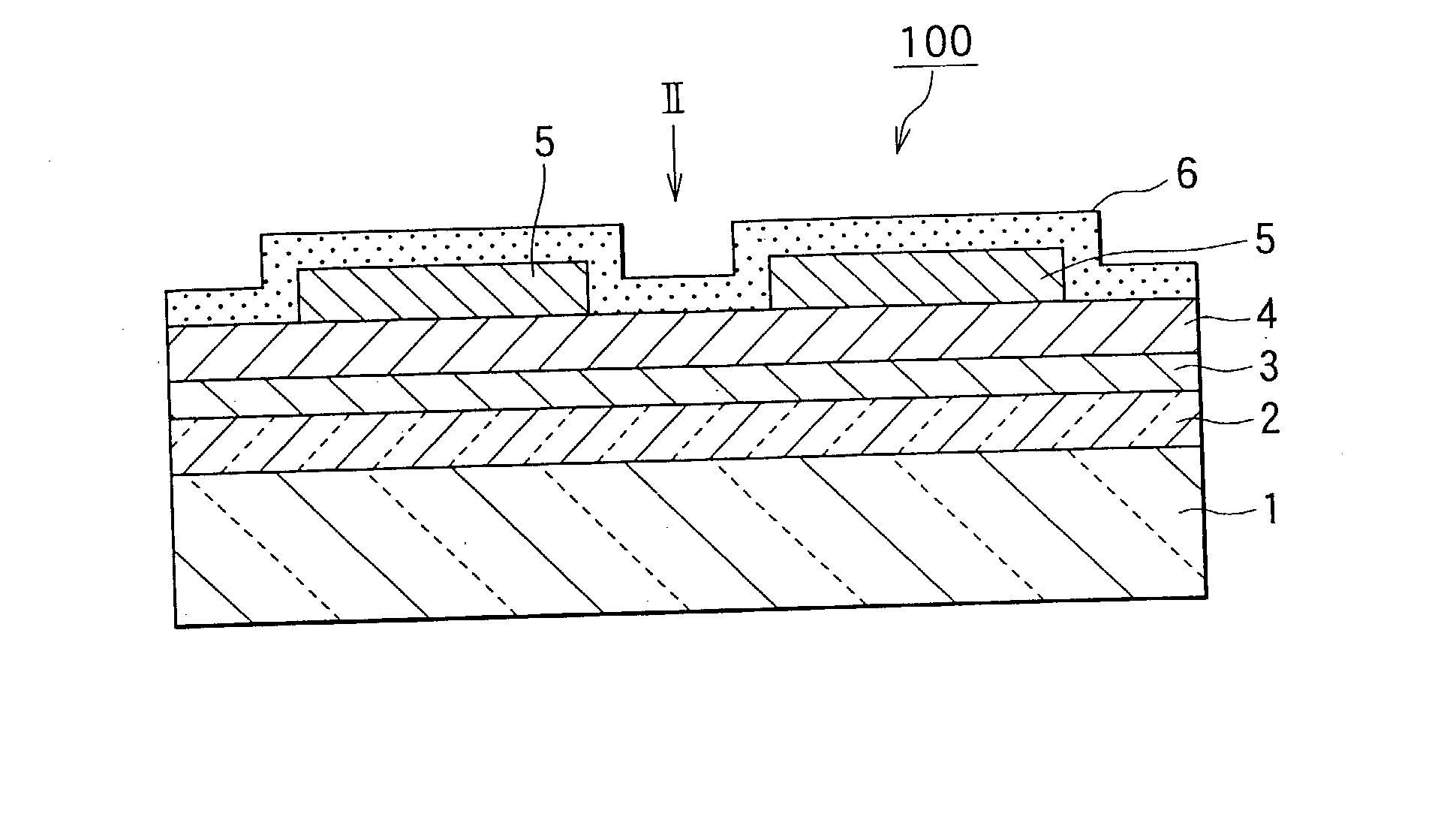

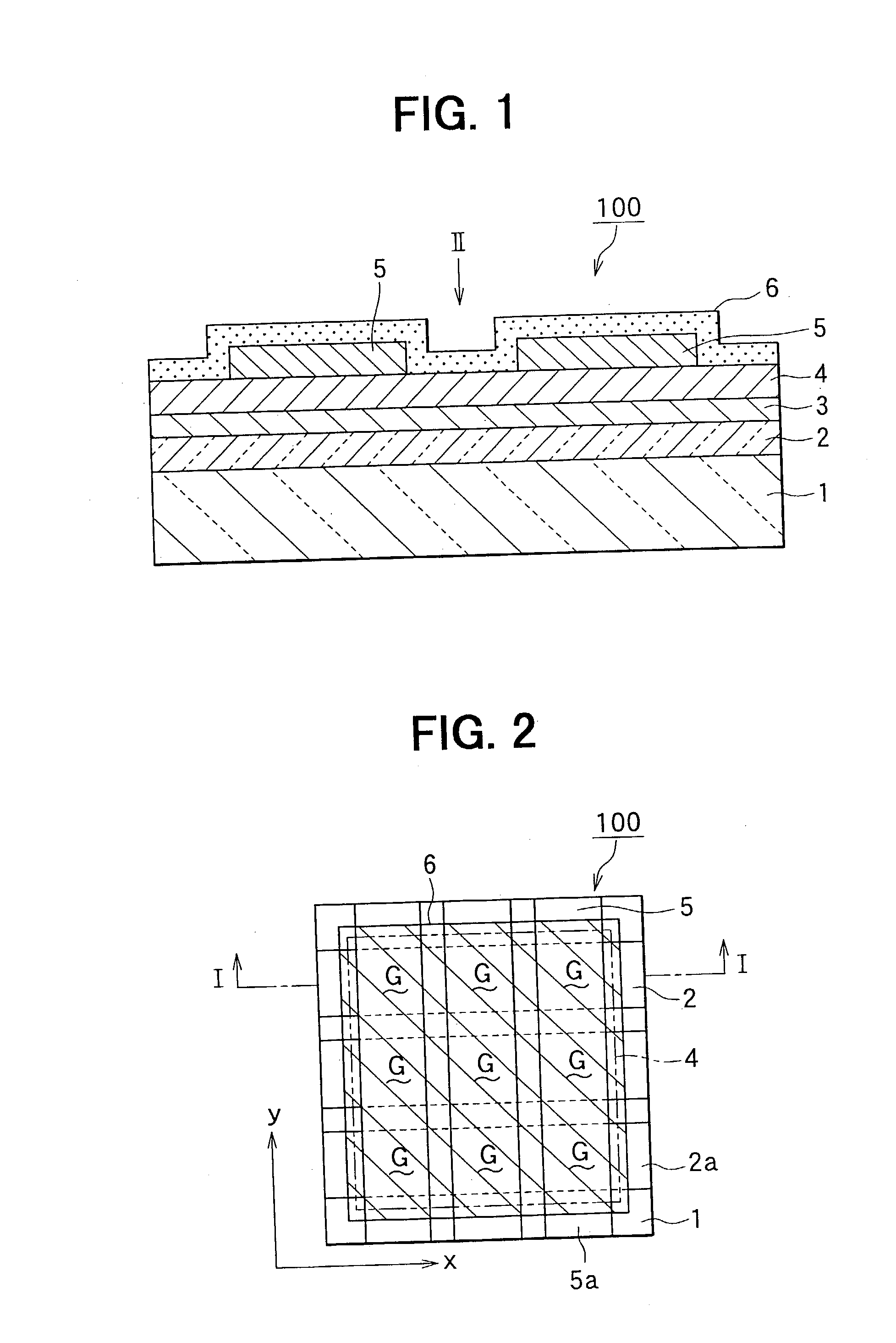

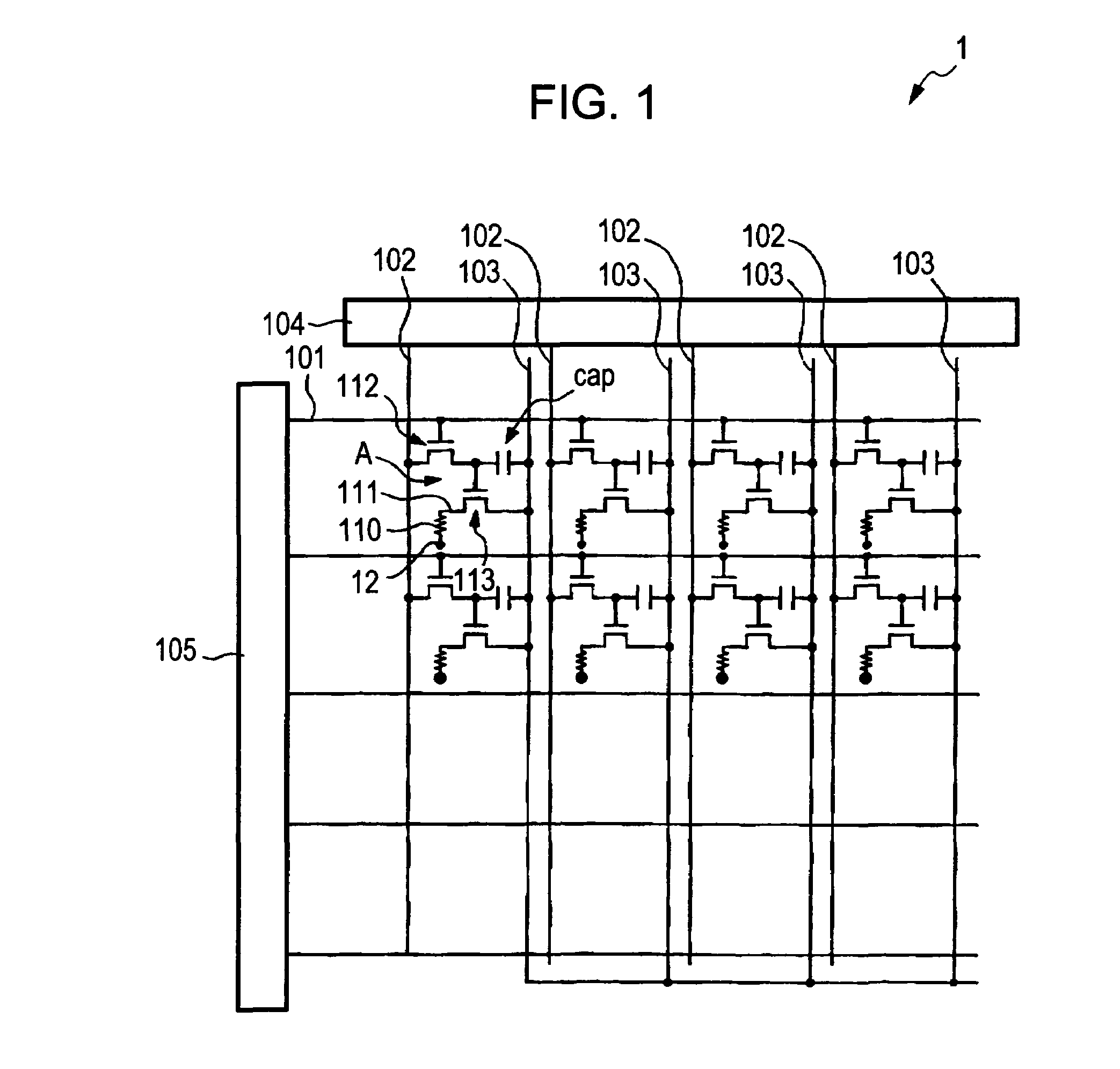

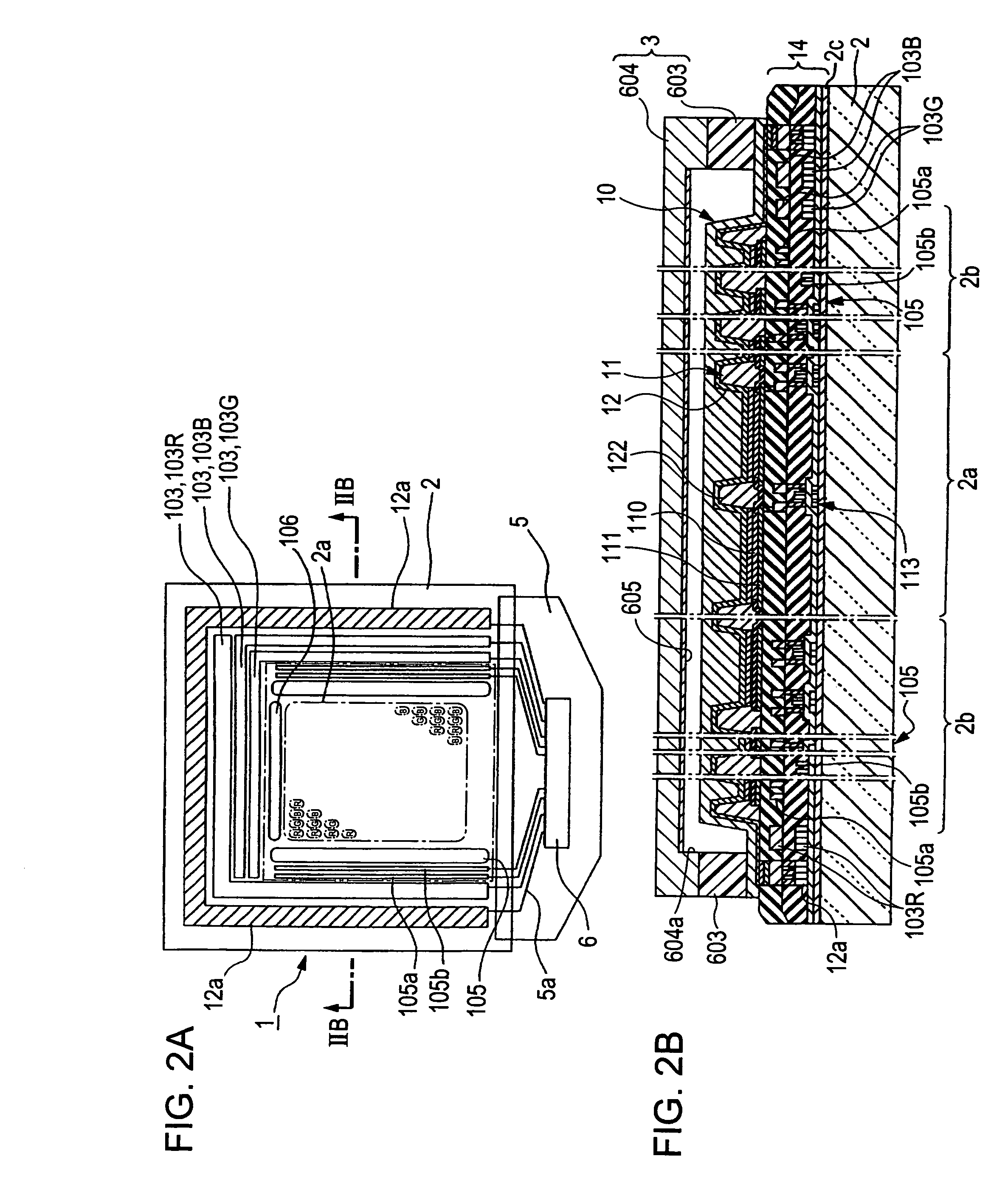

Electro-optic device, semiconductor device, electro-optic device substrate, manufacturing methods thereof, and electronic apparatus

ActiveUS20050116632A1Uniform thicknessQuality improvementDischarge tube luminescnet screensFinal product manufactureEngineeringSemiconductor

A pixel structure is provided in which a functional thin film having a uniform thickness can be formed in a pixel region, and an electro-optic device is obtained having superior uniformity of light brightness by the use of the above pixel structure. The functional thin film is formed on a thin film-forming surface surrounded by a partition for defining the pixel region. In this step, since the partition described above is formed of a first partition having a lyophilic surface and a second partition which is provided thereon and which has a lyophobic surface, and the first partition has parts which are not covered with the second partition, a liquid material for forming the functional thin film, which is filled inside the partition, can be formed into a film having a uniform thickness after drying due to the interaction between the lyophilic and the lyophobic properties.

Owner:SEIKO EPSON CORP

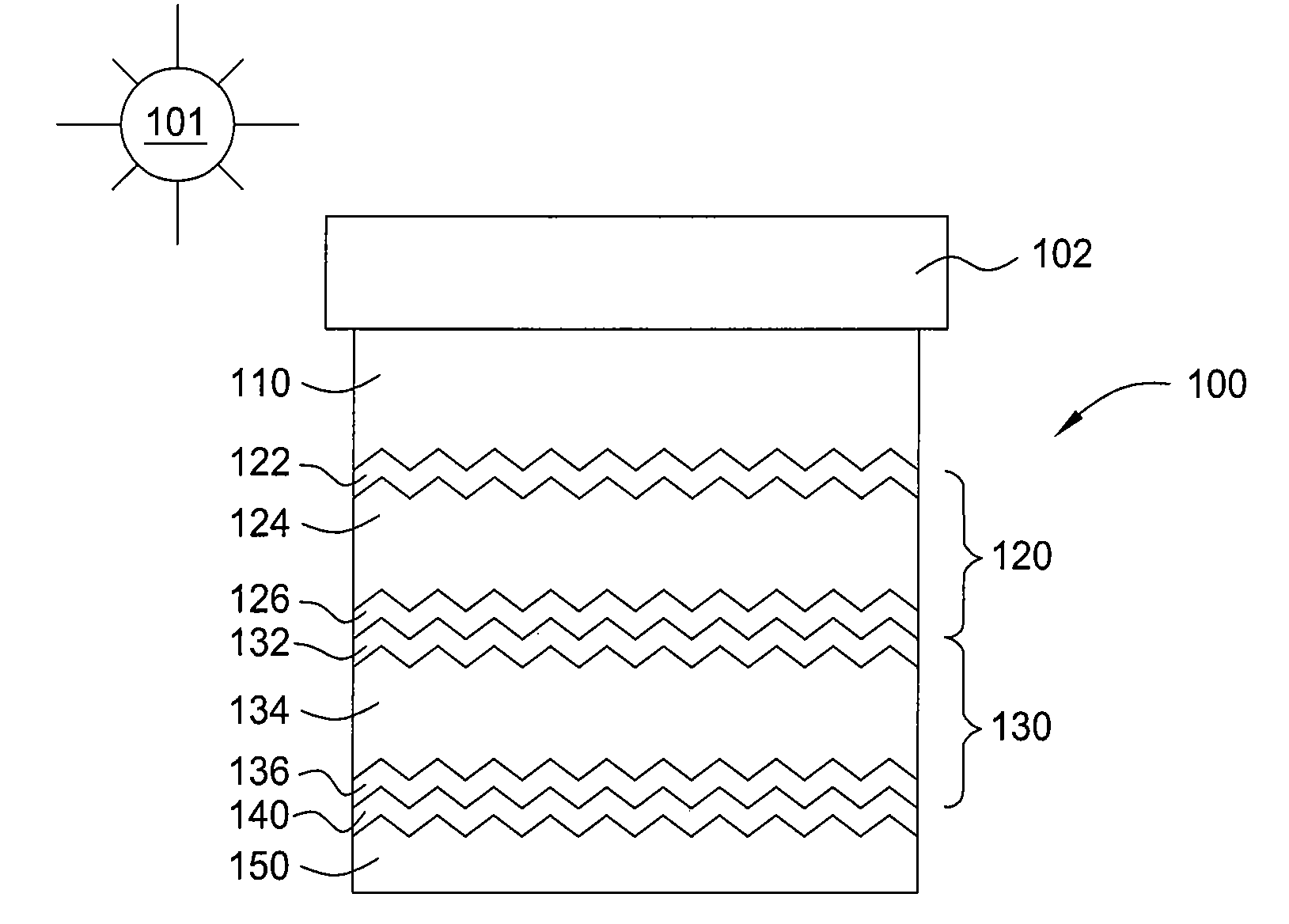

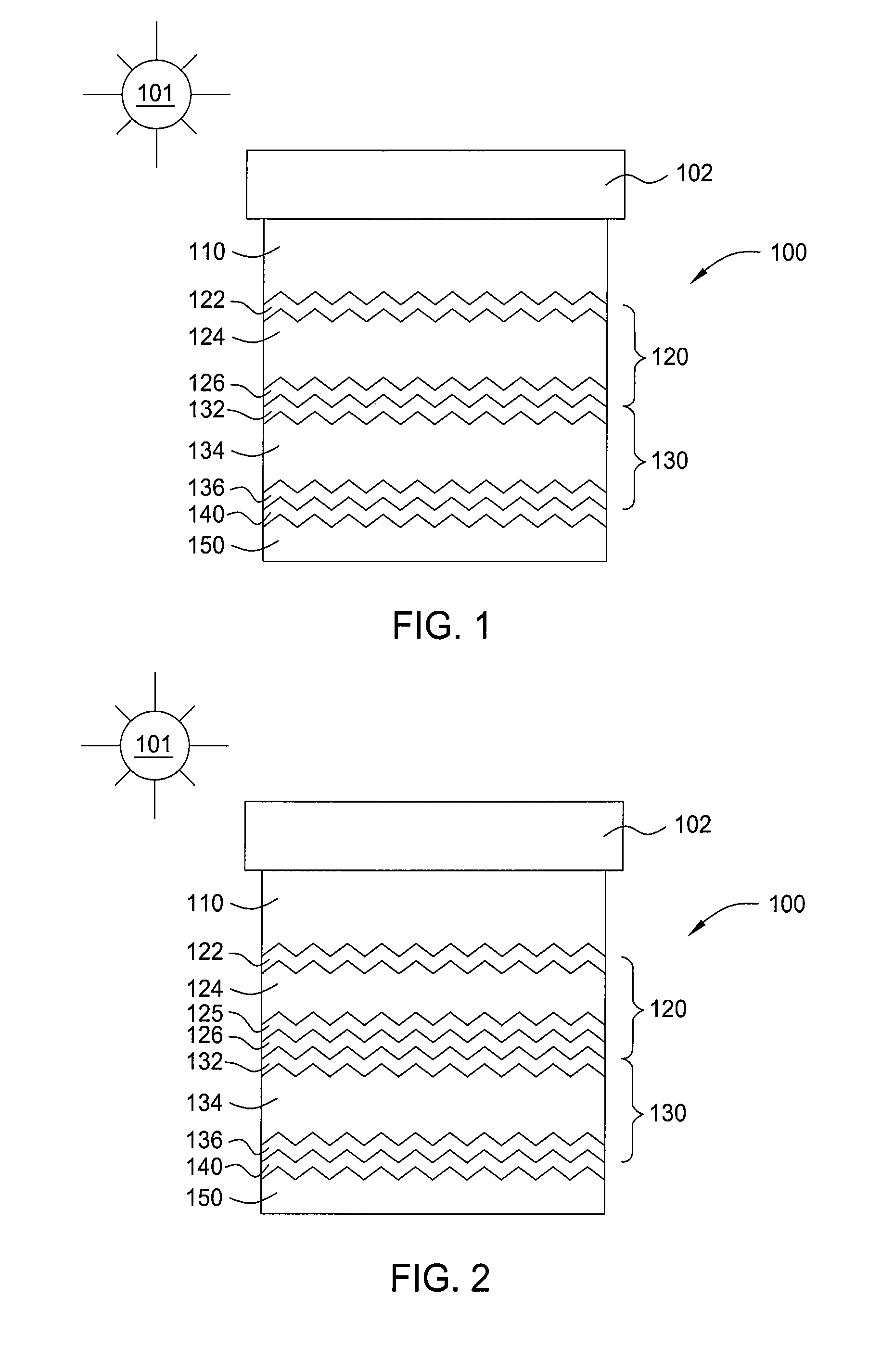

Multi-junction solar cells and methods and apparatuses for forming the same

InactiveUS20090020154A1Uniformly formedFinal product manufactureSemiconductor/solid-state device manufacturingAmorphous siliconSilicon solar cell

Embodiments of the present invention generally relate to solar cells and methods and apparatuses for forming the same. More particularly, embodiments of the present invention relate to thin film multi-junction solar cells and methods and apparatuses for forming the same. Embodiments of the present invention also include an improved thin film silicon solar cell, and methods and apparatus for forming the same, where one or more of the layers in the solar cell comprises at least one amorphous silicon layer that has improved electrical characteristics and mechanical properties, and is capable of being deposited at rates many times faster than conventional amorphous silicon deposition processes.

Owner:APPLIED MATERIALS INC

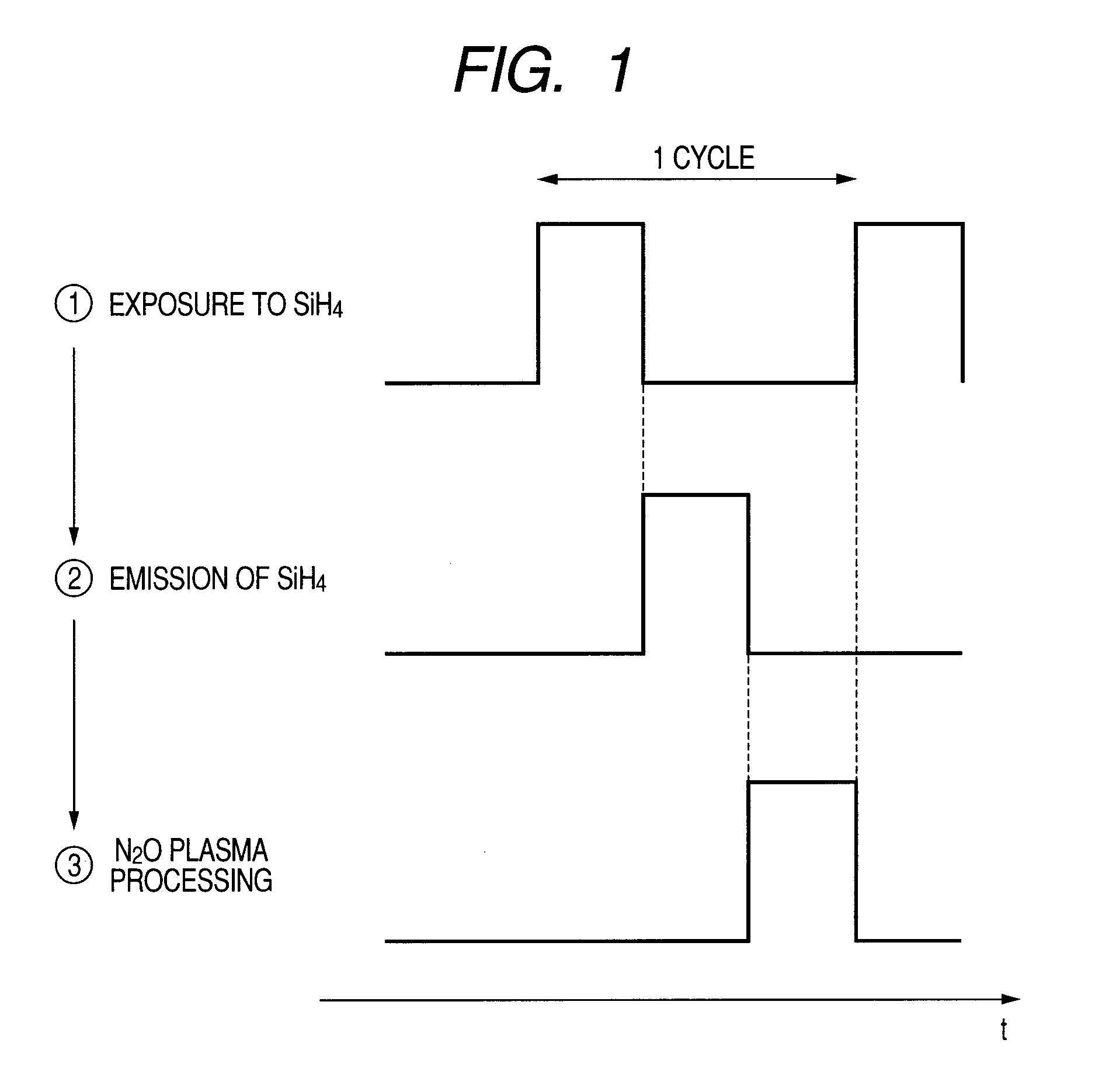

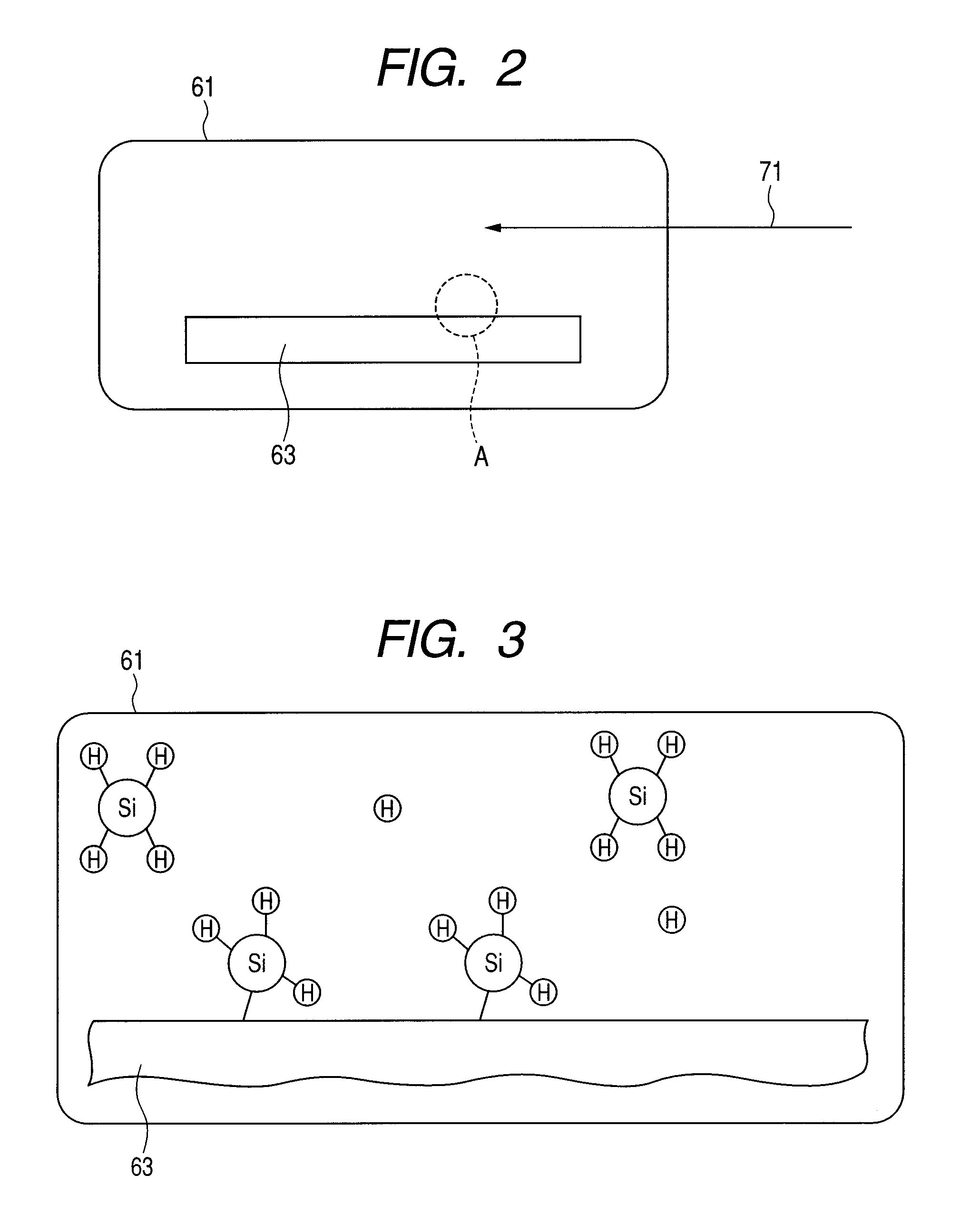

Manufacturing method of semiconductor device

InactiveUS20110003445A1Good and thin silicon oxide filmUniformly formedSolid-state devicesSemiconductor/solid-state device manufacturingSilicon oxideNitrous oxide

A manufacturing method of a semiconductor device is provided which can uniformly form a good and thin silicon oxide film or the like at a relatively low temperature. In step 1, a semiconductor substrate is exposed to monosilane (SiH4). Then, in step 2, the remaining monosilane (SiH4) is emitted. In step 3, the semiconductor substrate is exposed to nitrous oxide plasma. A desired silicon oxide film is formed by repeating one cycle including steps 1 to 3 until a necessary thickness of the film is obtained.

Owner:RENESAS ELECTRONICS CORP

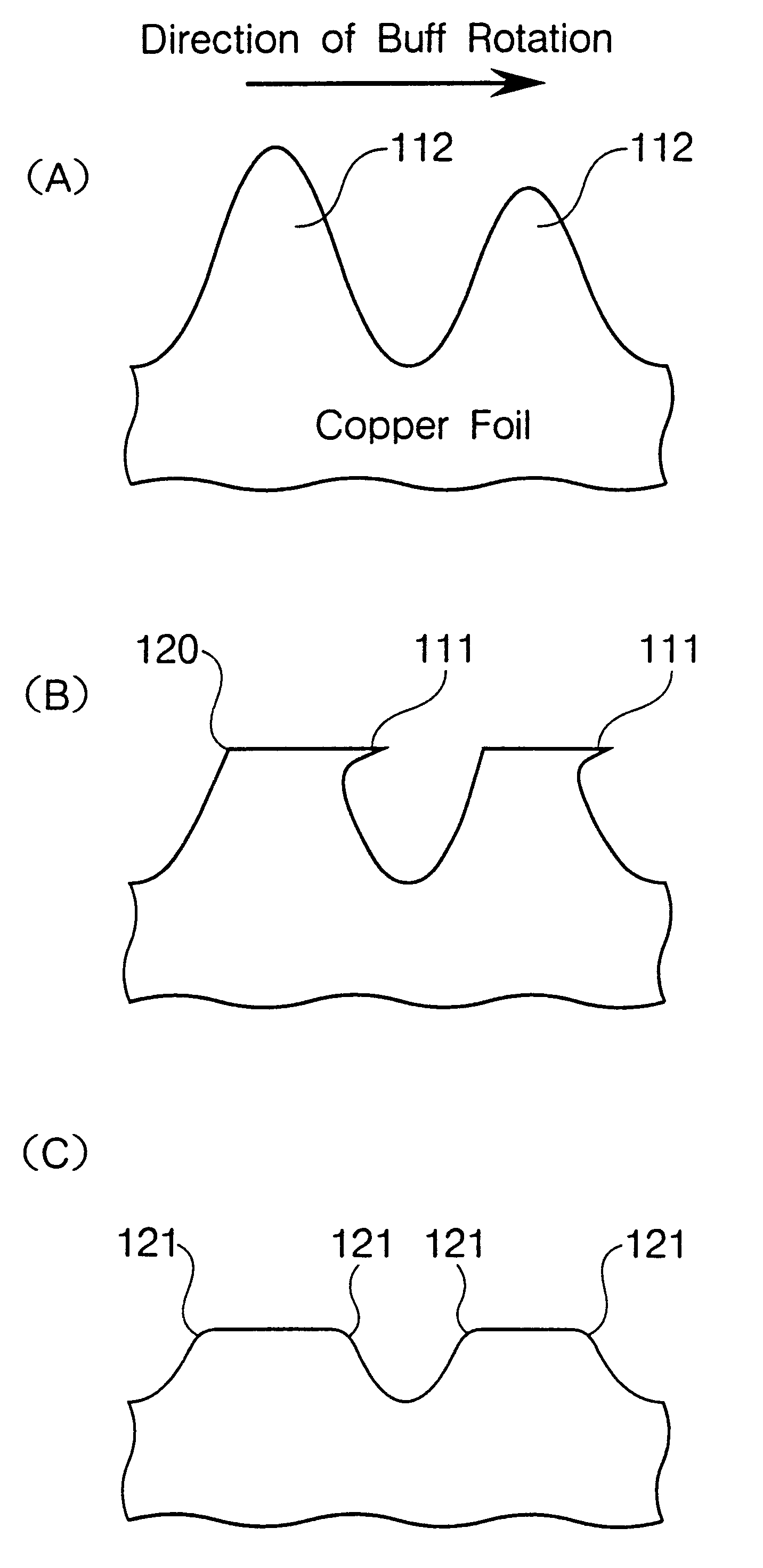

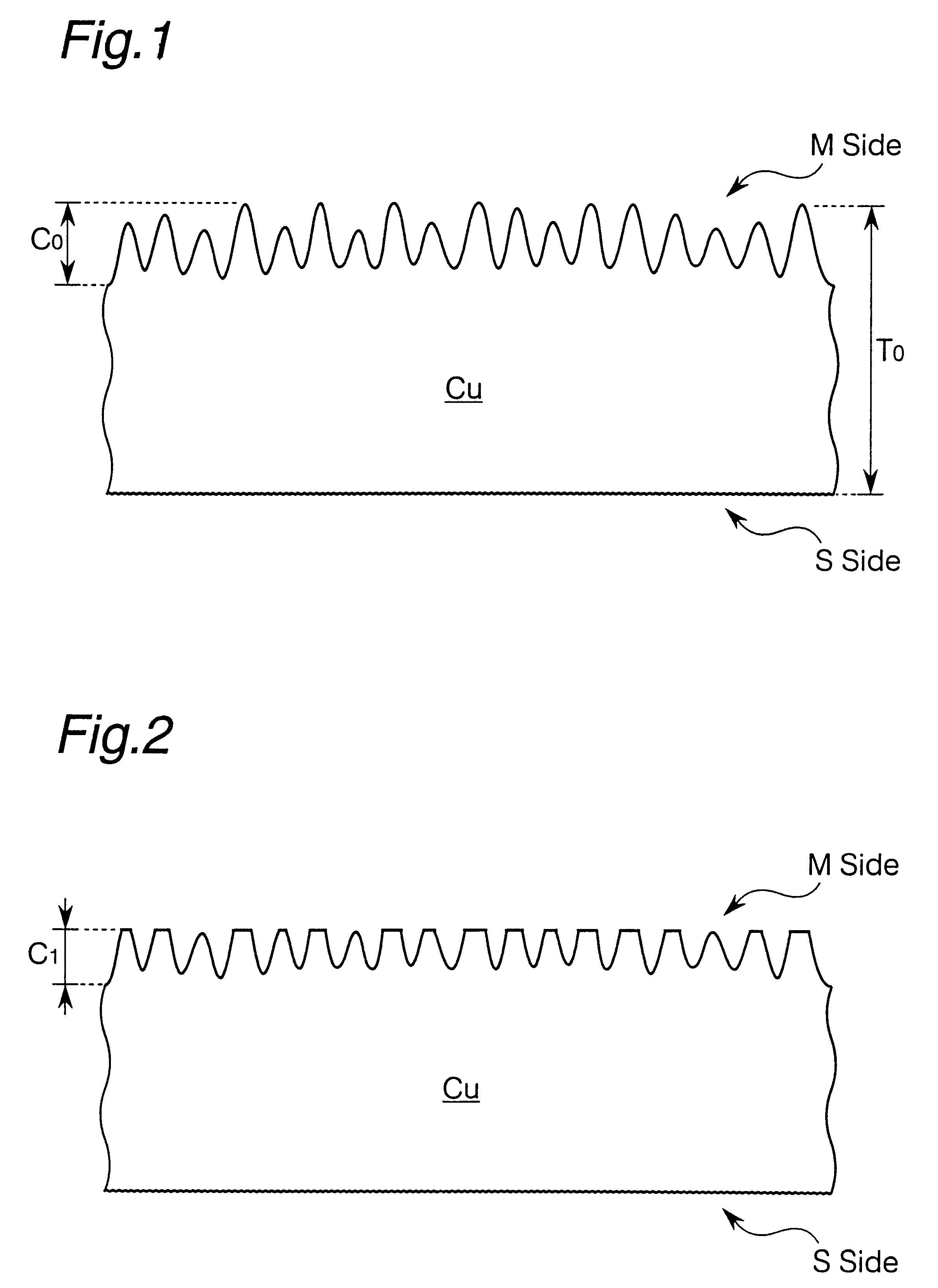

Electrodeposited copper foil with its surface prepared, process for producing the same and use thereof

InactiveUS6475638B1Eliminate deformationHigh peel strengthInsulating substrate metal adhesion improvementLapping machinesSurface roughnessCopper foil

A process for producing an electrodeposited copper foil with its surface prepared, comprising the steps of: subjecting an electrodeposited copper foil having a shiny side and a matte side whose average surface roughness (Rz) is in the range of 2.5 to 10 mum to at least one mechanical polishing so that the average surface roughness (Rz) of the matte side becomes in the range of 1.5 to 3.0 mum; and subjecting the matte side having undergone the mechanical polishing to a selective chemical polishing so that the average surface roughness (Rz) of the matte side becomes in the range of 0.8 to 2.5 mum. The invention further provides an electrodeposited copper foil with its surface prepared, produced by the above process, and still further provides PWBs and a multilayer laminate of PWBs, produced with the use of the above electrodeposited copper foil with its surface prepared. The mechanical polishing followed by chemical polishing of the matte side enables obtaining an electrodeposited copper foil with its surface prepared, the matte side of which exhibits excellent properties, and hence enables obtaining PWBs and a multilayer PWBs which have excellent properties.

Owner:MITSUI MINING & SMELTING CO LTD

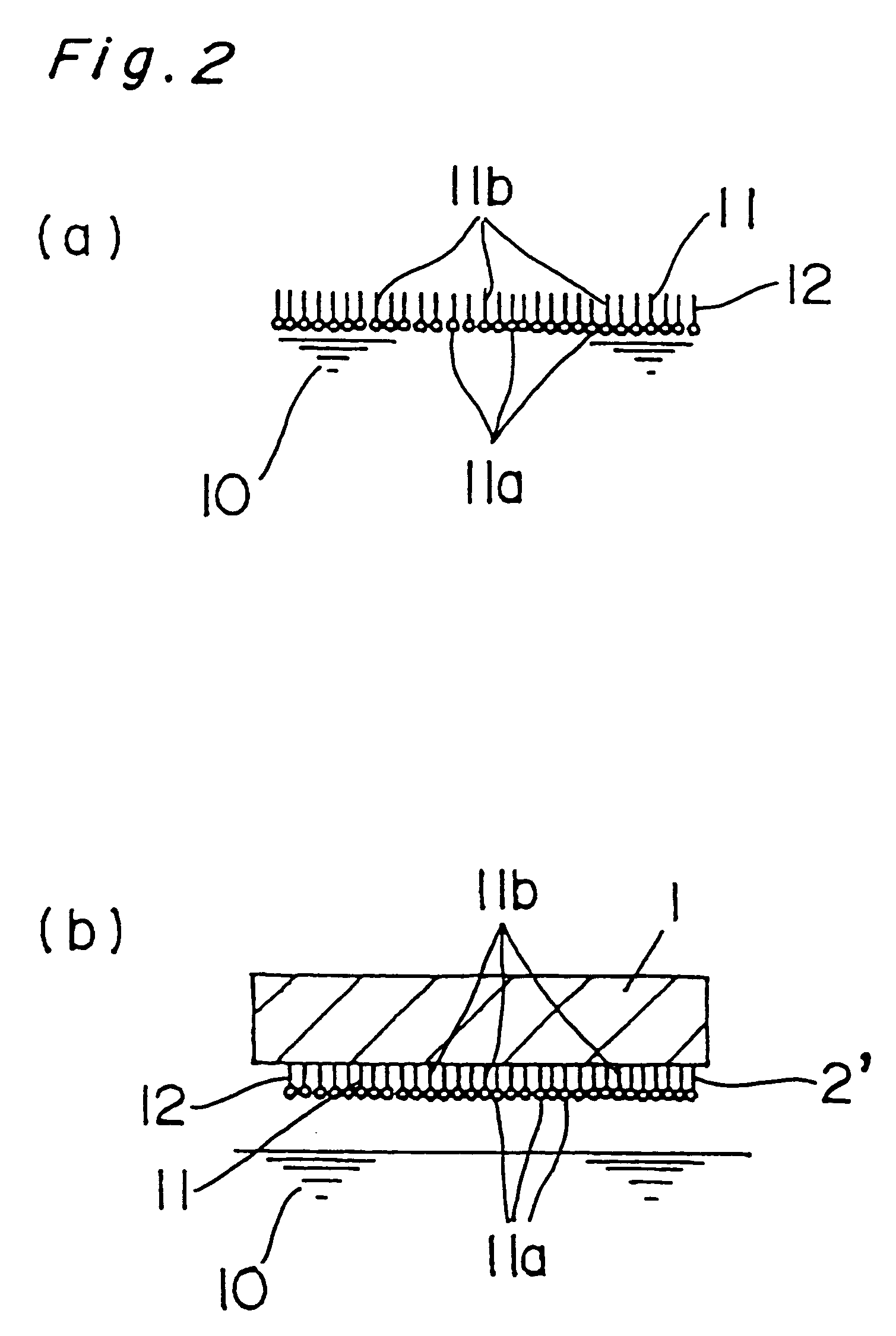

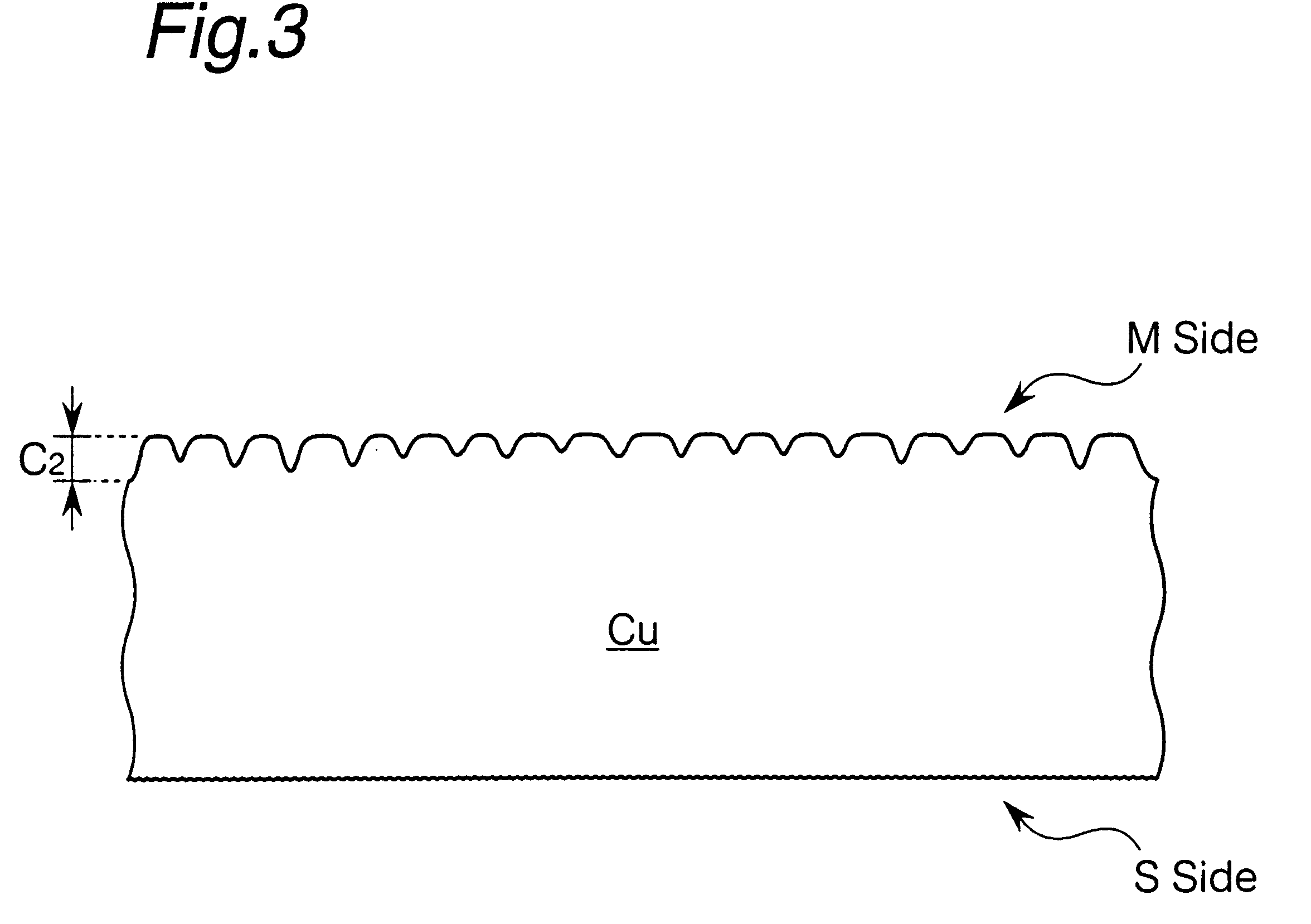

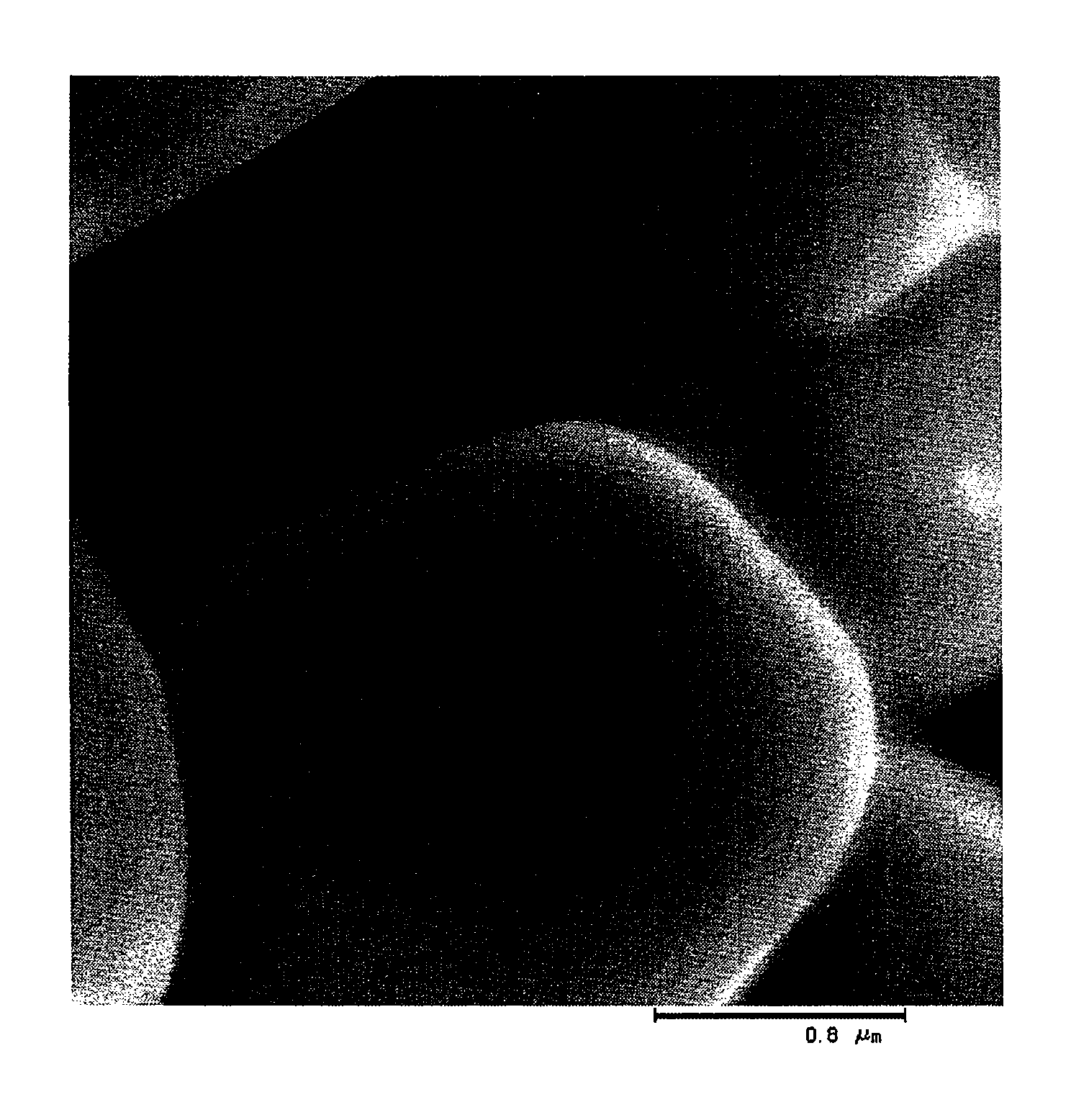

Conductive particles and method and device for manufacturing the same, anisotropic conductive adhesive and conductive connection structure, and electronic circuit components and method of manufacturing the same

InactiveUS6906427B2Efficient executionInhibit aggregationElectrolysis componentsSemiconductor/solid-state device detailsAnisotropic conductive adhesiveElectrical connection

An electrical connection is formed by using a double laminated conductive fine particle provided with a conductive metal layer on the surface of a spherical elastic base particle by electroless plating and electroplating and a layer of a low-melting-point metal on the surface of the conductive metal layer and wherein the conductive metal layer comprises a plurality of metal layers.

Owner:SEKISUI CHEM CO LTD

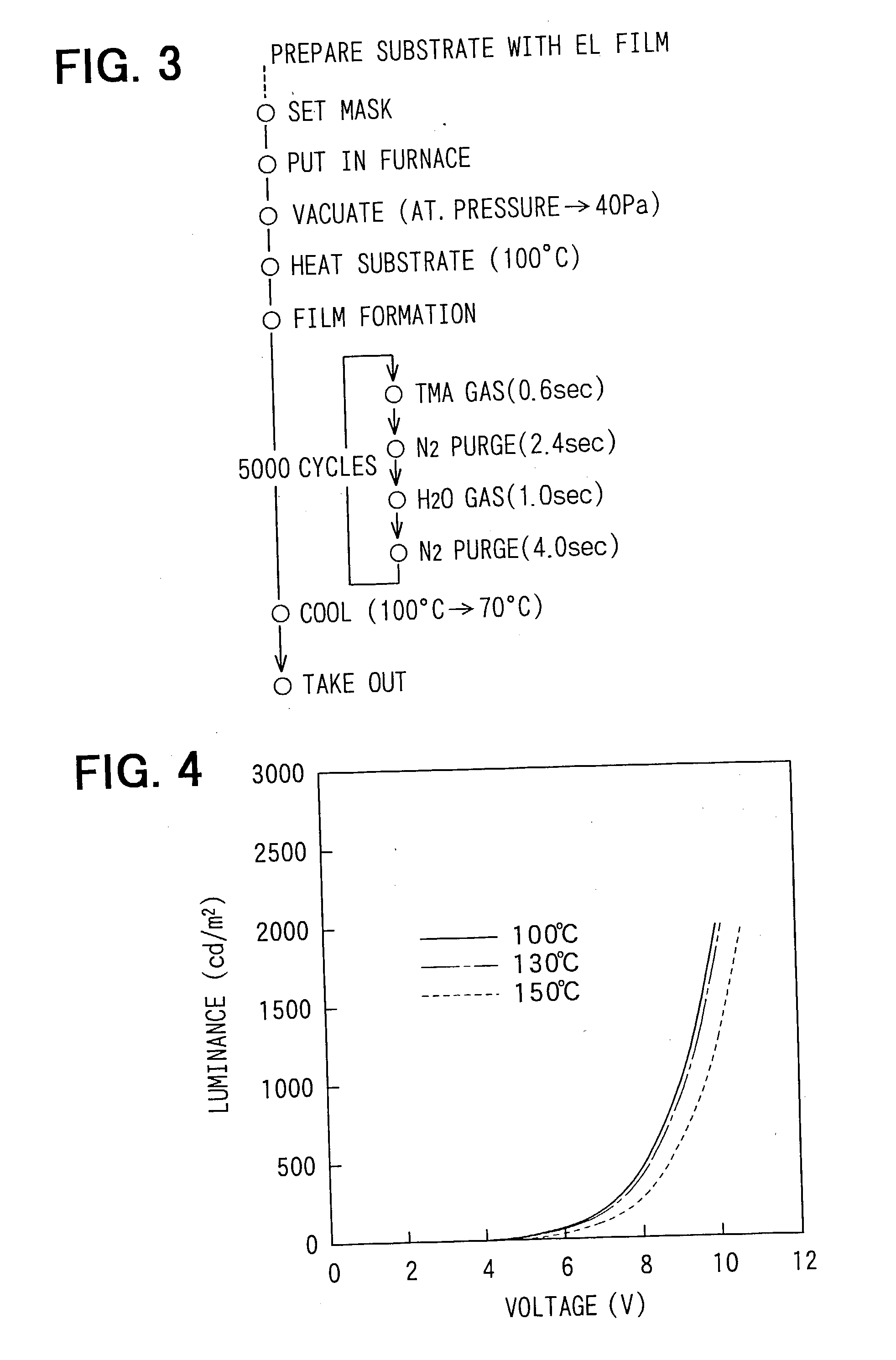

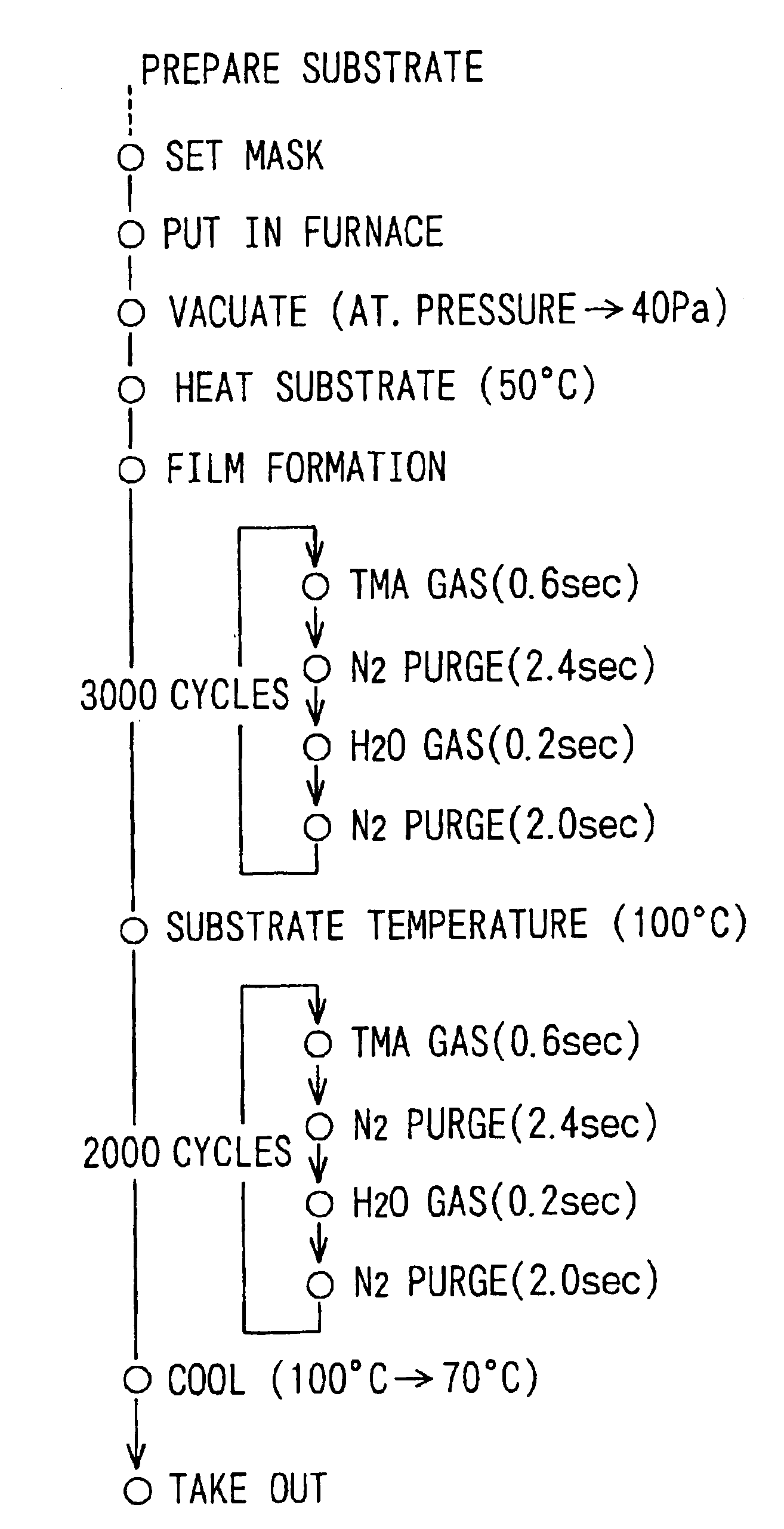

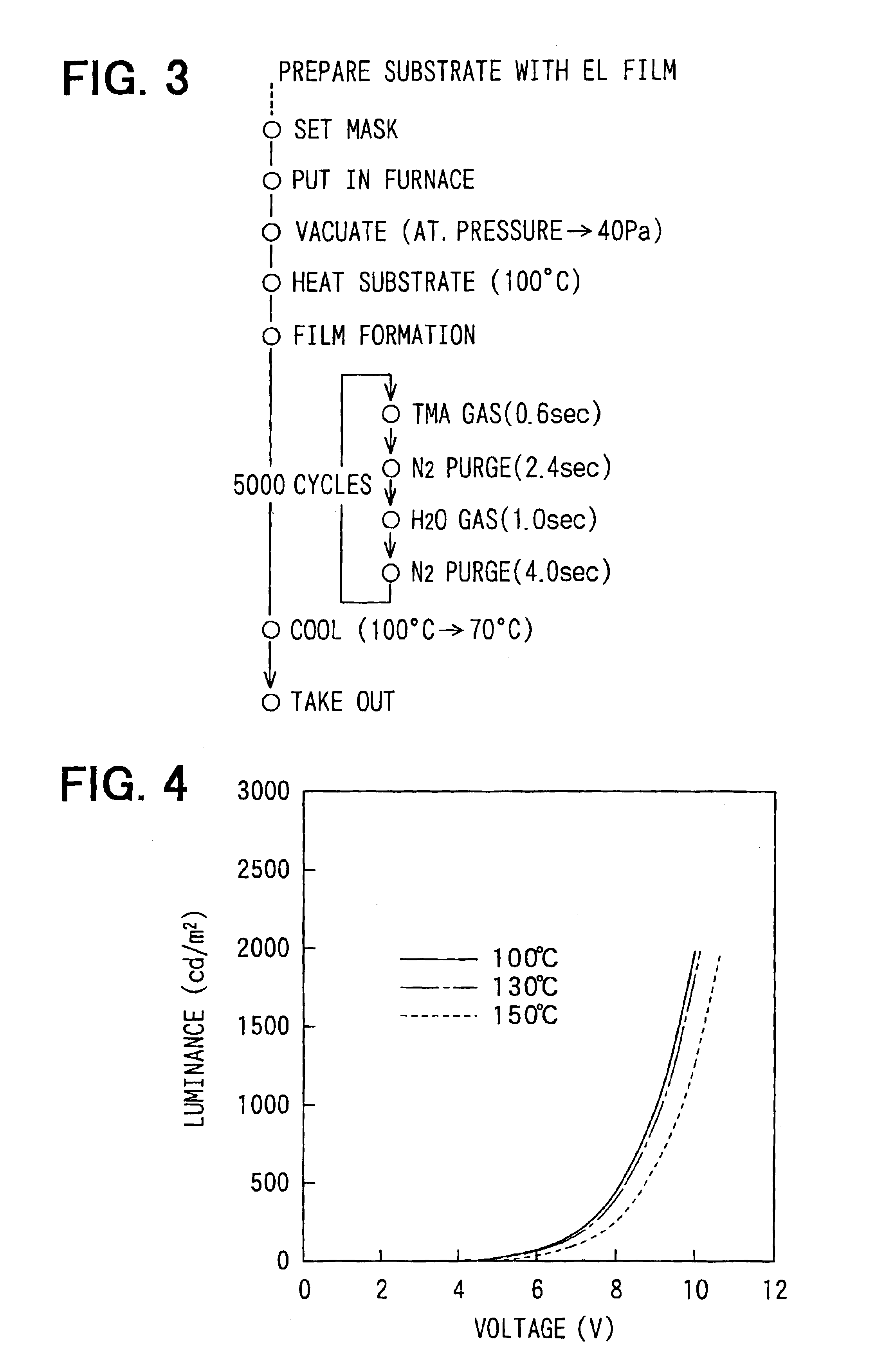

Method for manufacturing organic EL device with protective layer

InactiveUS20030129298A1Expand coverageImprove moisture resistanceDischarge tube luminescnet screensElectroluminescent light sourcesEngineeringGlass transition

An organic EL device has a structure in which an anode, a hole transporting layer, an organic luminescent layer, and a cathode are disposed on a glass substrate in this order. The organic EL device further has a protective layer covering an outer surface of the structure to protect it from an external environment. The protective layer is formed by an ALE method at a temperature lower than glass transition temperatures materials constituting the hole transporting layer and the organic luminescent layer.

Owner:DENSO CORP

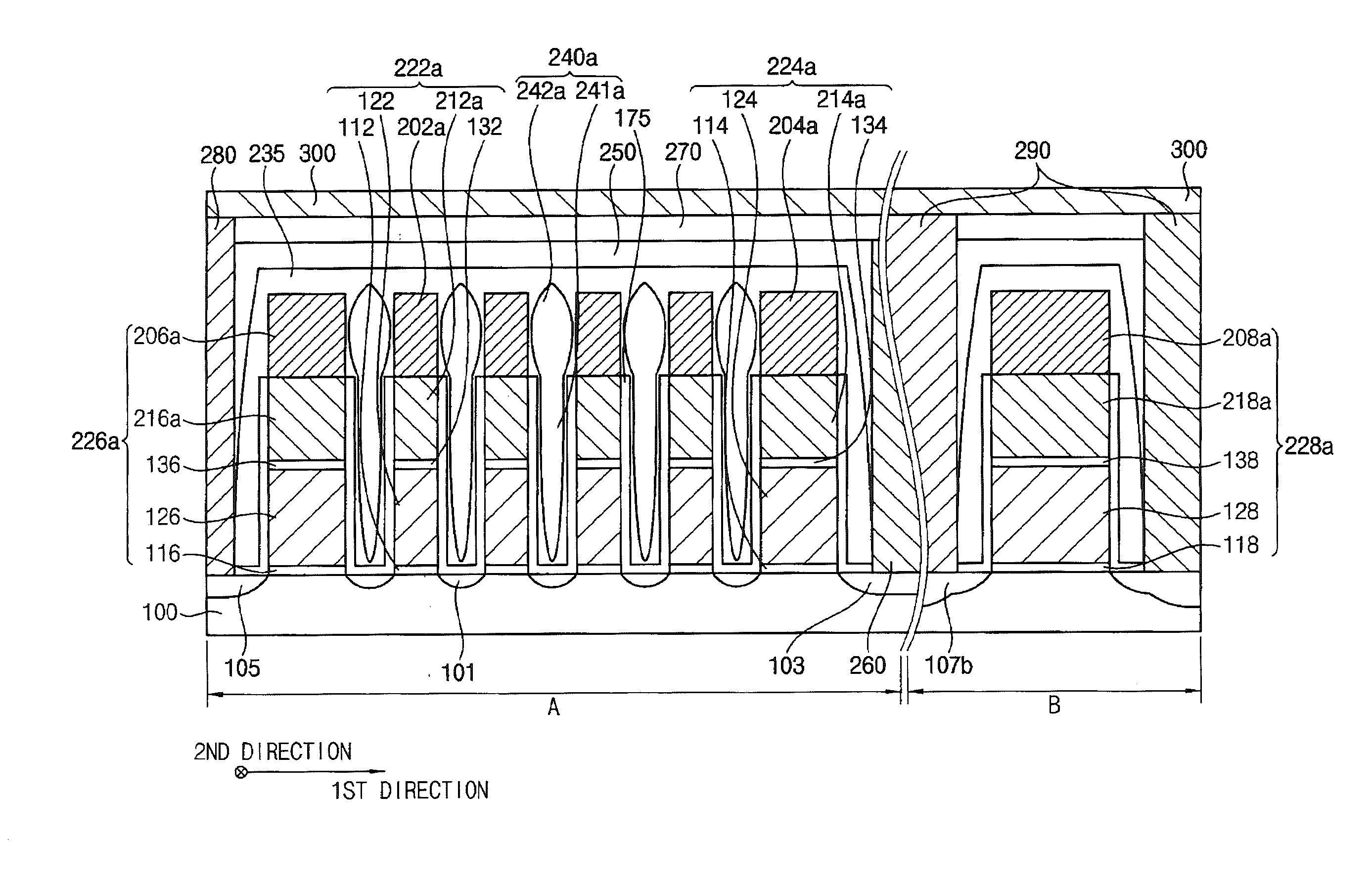

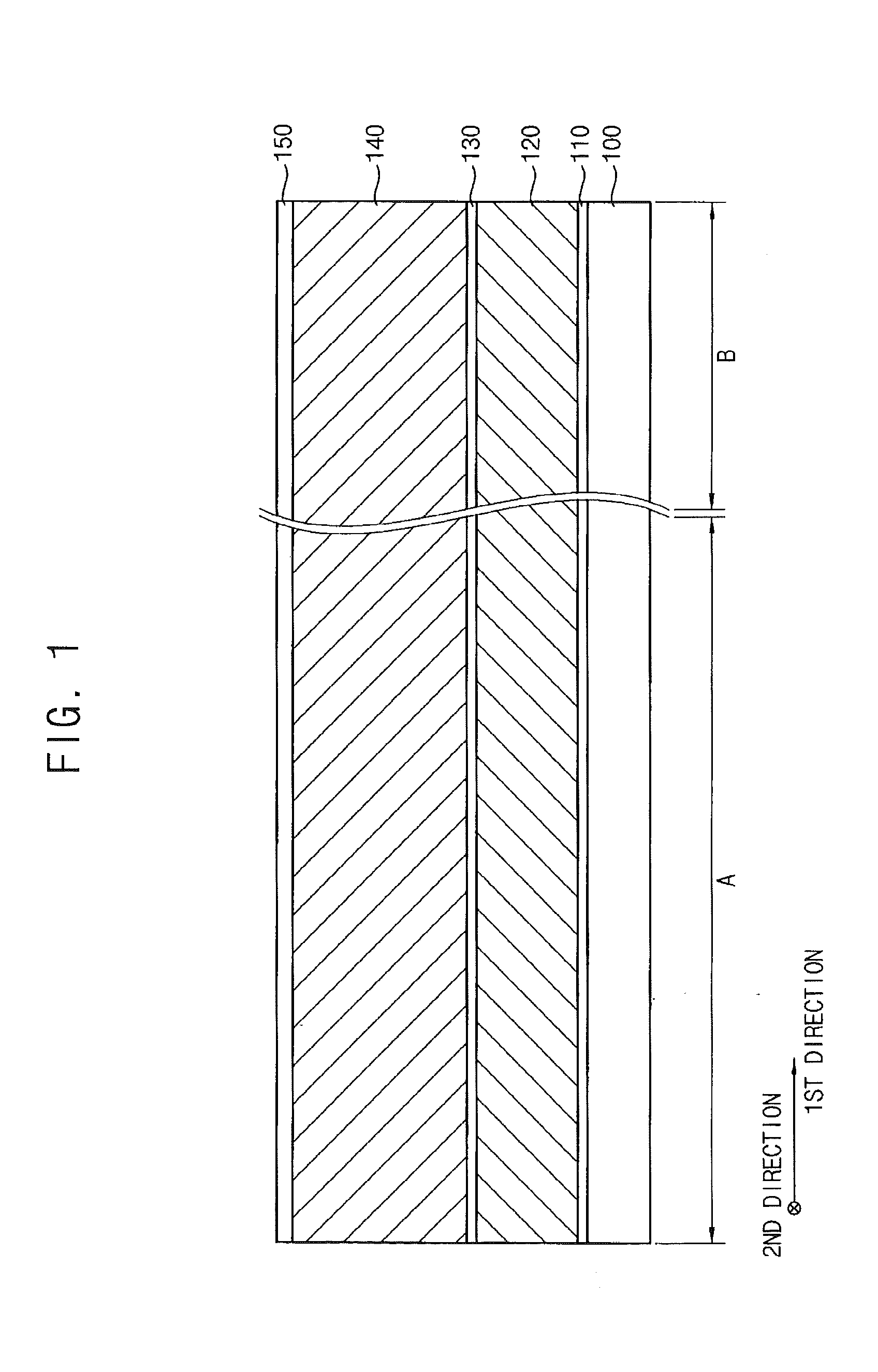

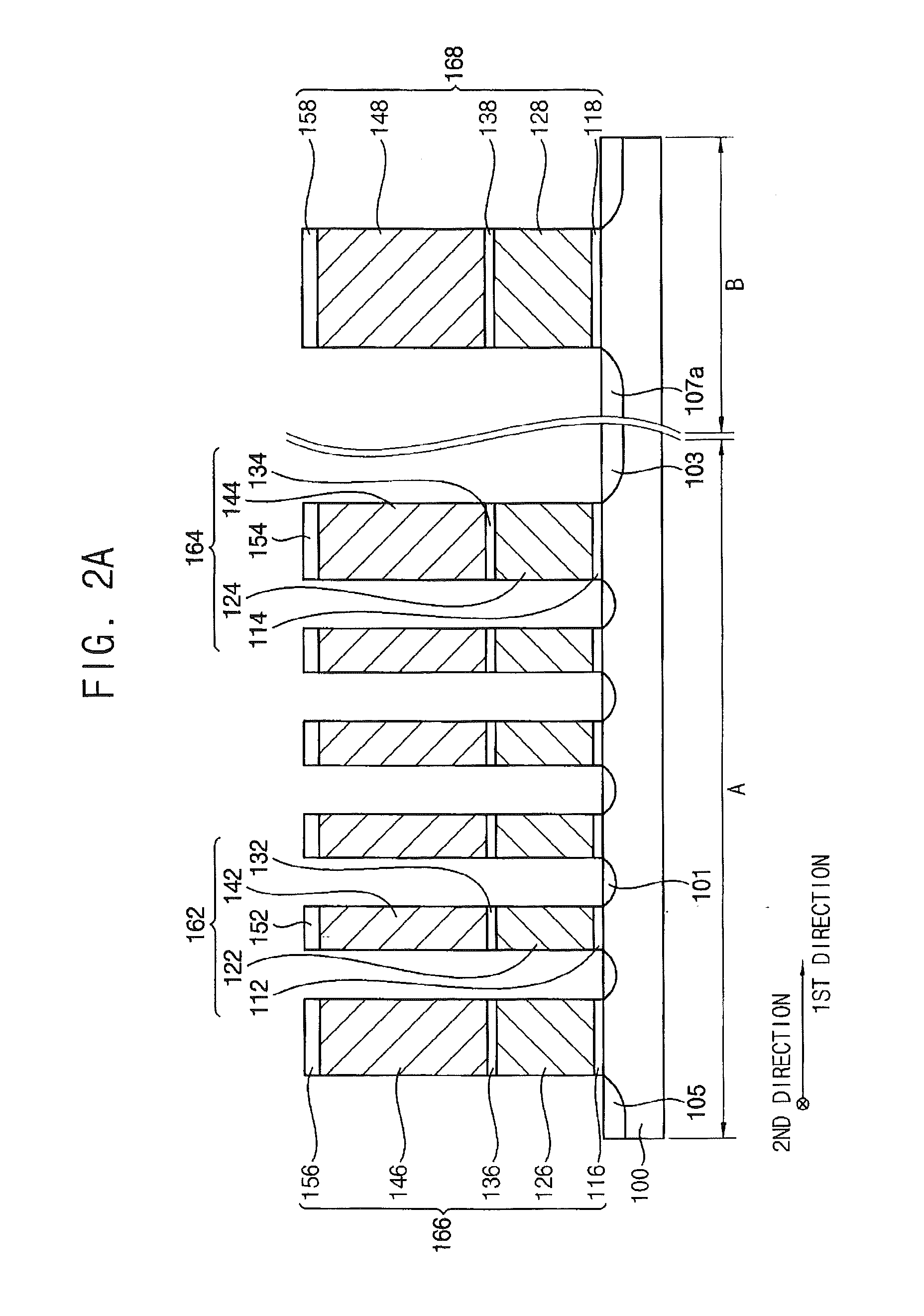

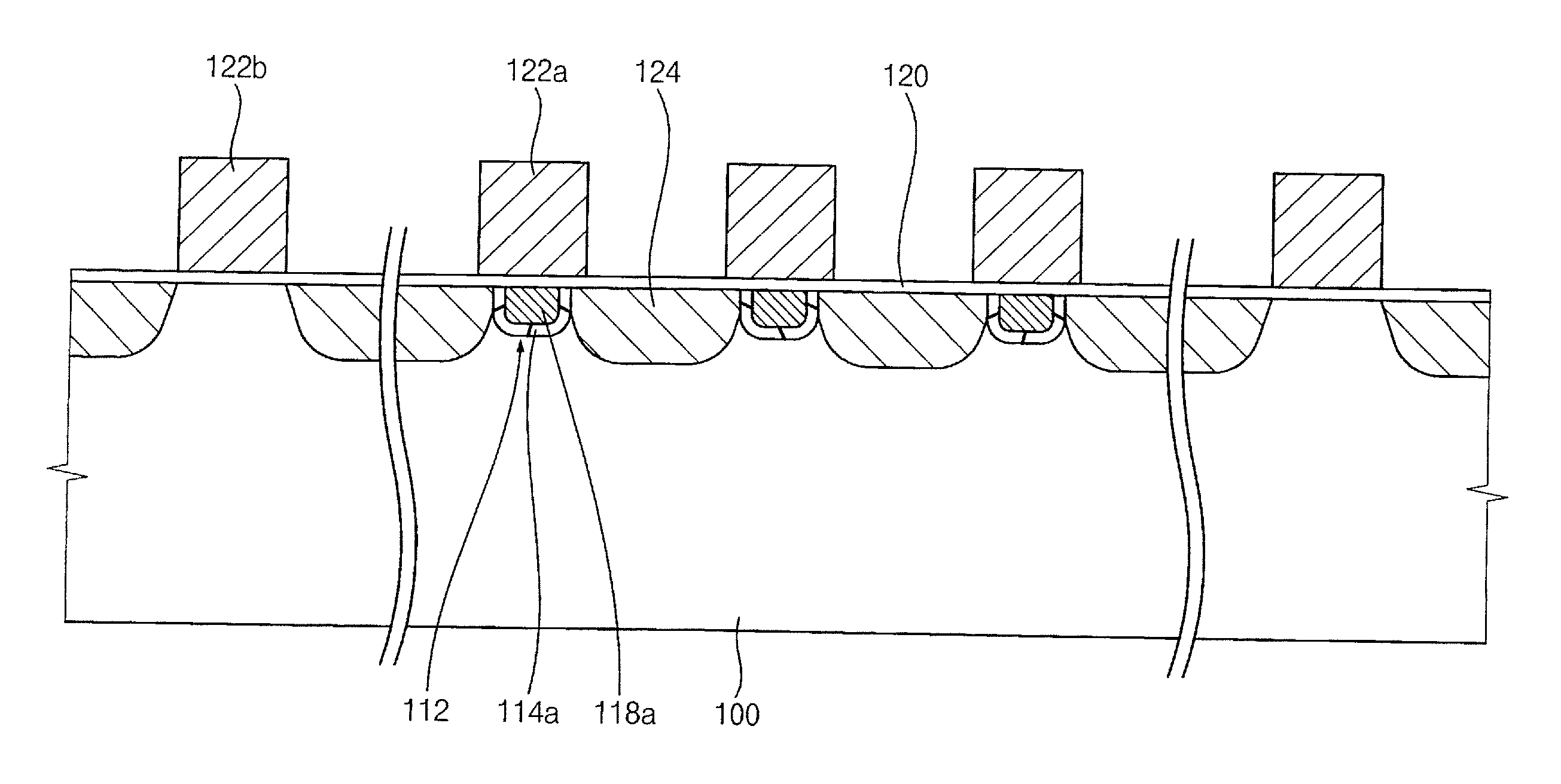

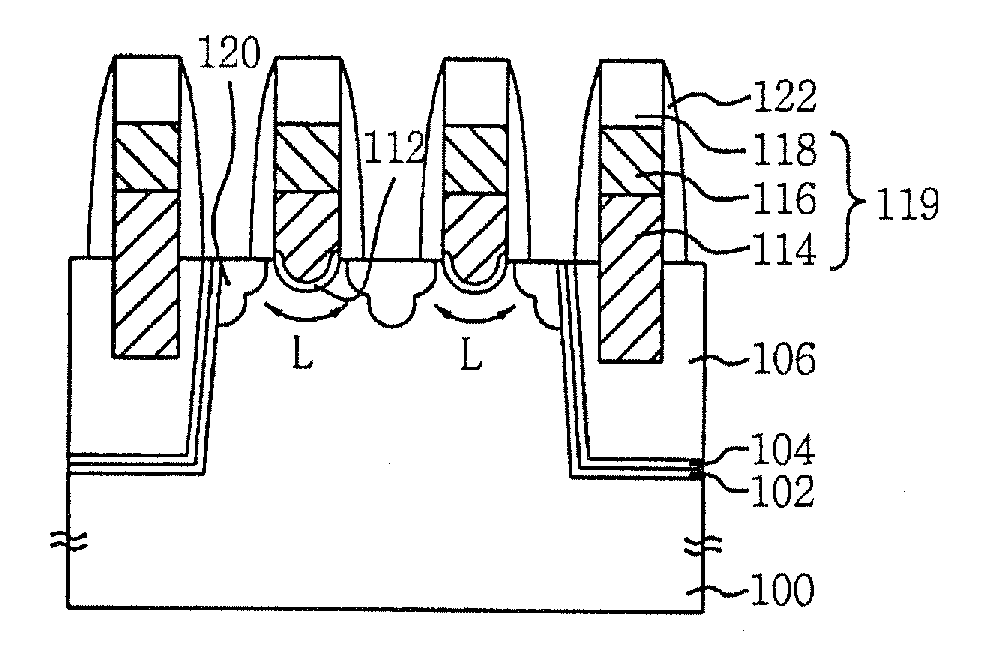

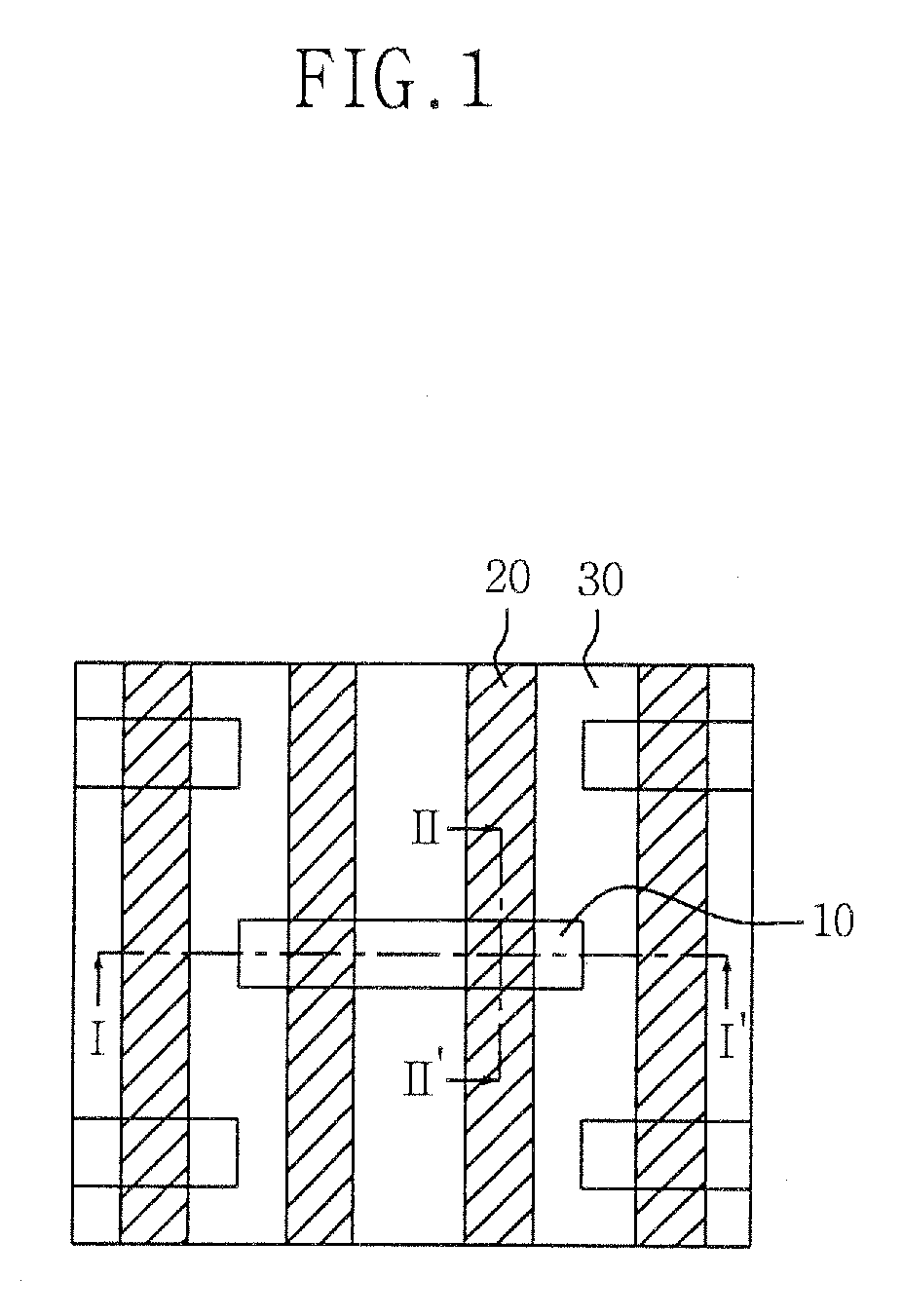

Semiconductor devices

InactiveUS20120007165A1Lower resistanceReduce parasitic capacitanceTransistorSolid-state devicesInsulation layerDevice material

A semiconductor device includes a substrate, a plurality of gate structures, a first insulating interlayer pattern, and a second insulation layer pattern. The substrate has an active region and a field region, each of the active region and the field region extends in a first direction, and the active region and the field region are alternately and repeatedly arranged in a second direction substantially perpendicular to the first direction. The gate structures are spaced apart from each other in the first direction, each of the gate structures extends in the second direction. The first insulation layer pattern is formed on a portion of a sidewall of each gate structure. The second insulation layer pattern covers the gate structures and the first insulation layer pattern, and has an air tunnel between the gate structures, the air tunnel extending in the second direction.

Owner:SAMSUNG ELECTRONICS CO LTD

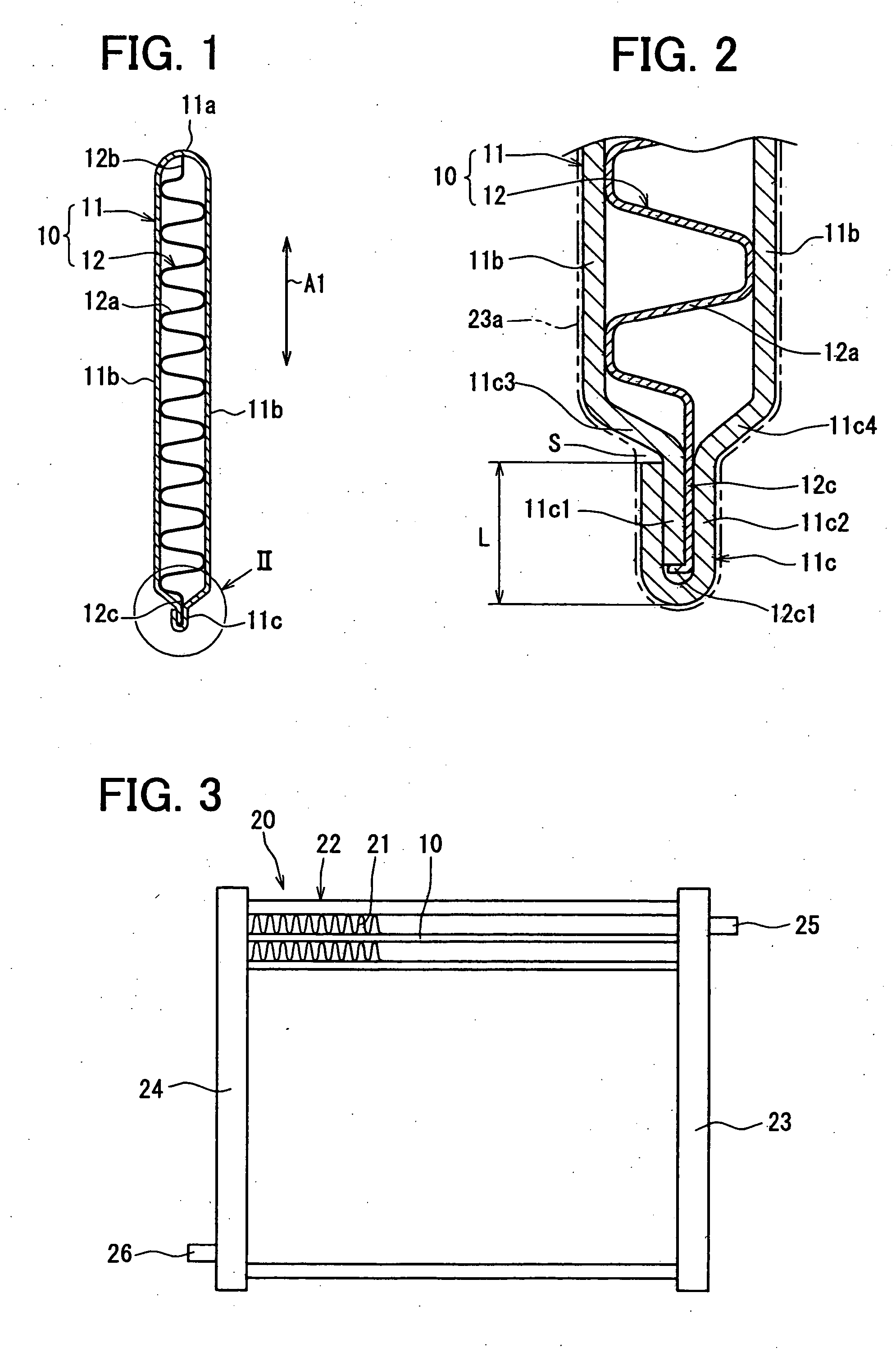

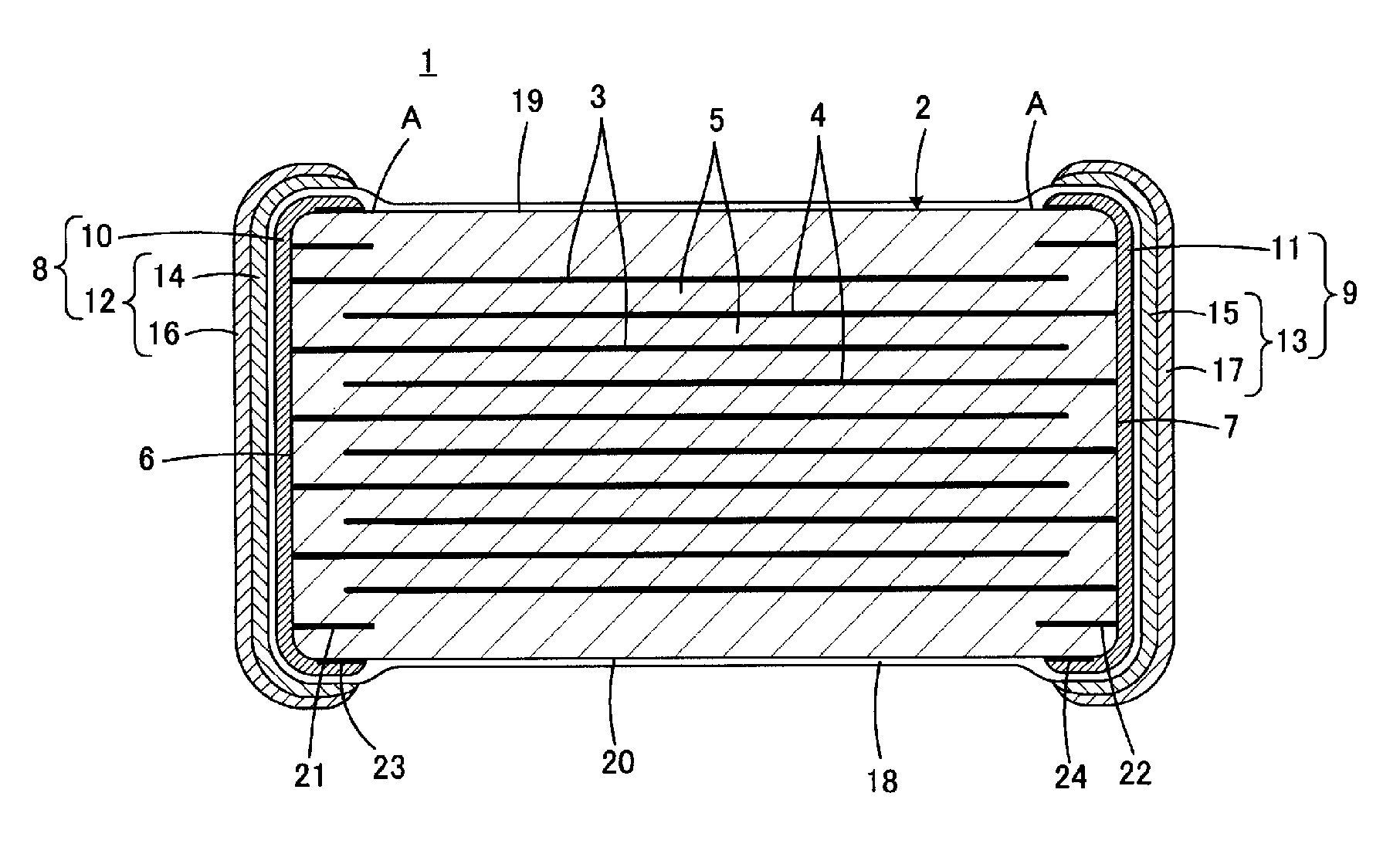

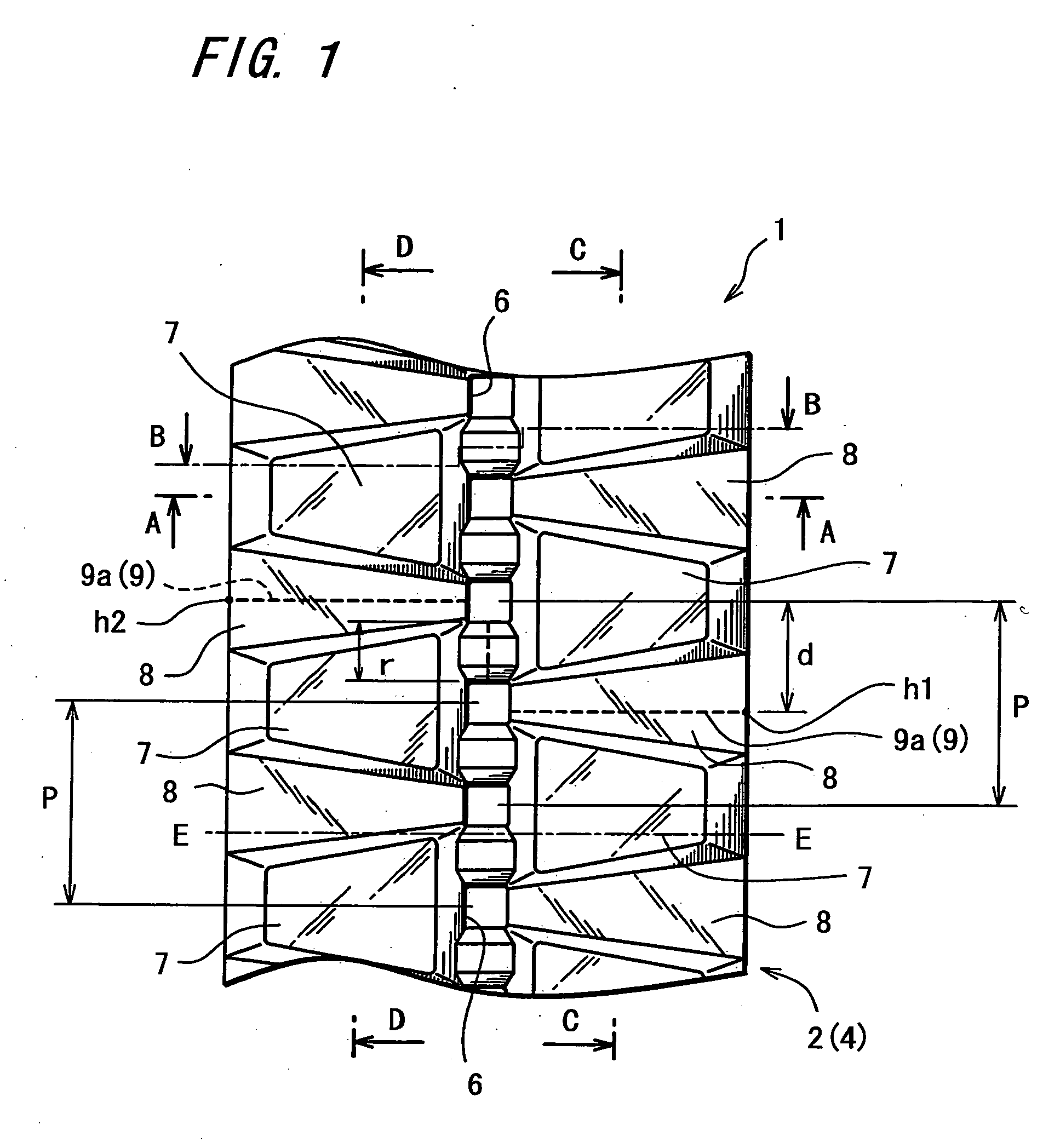

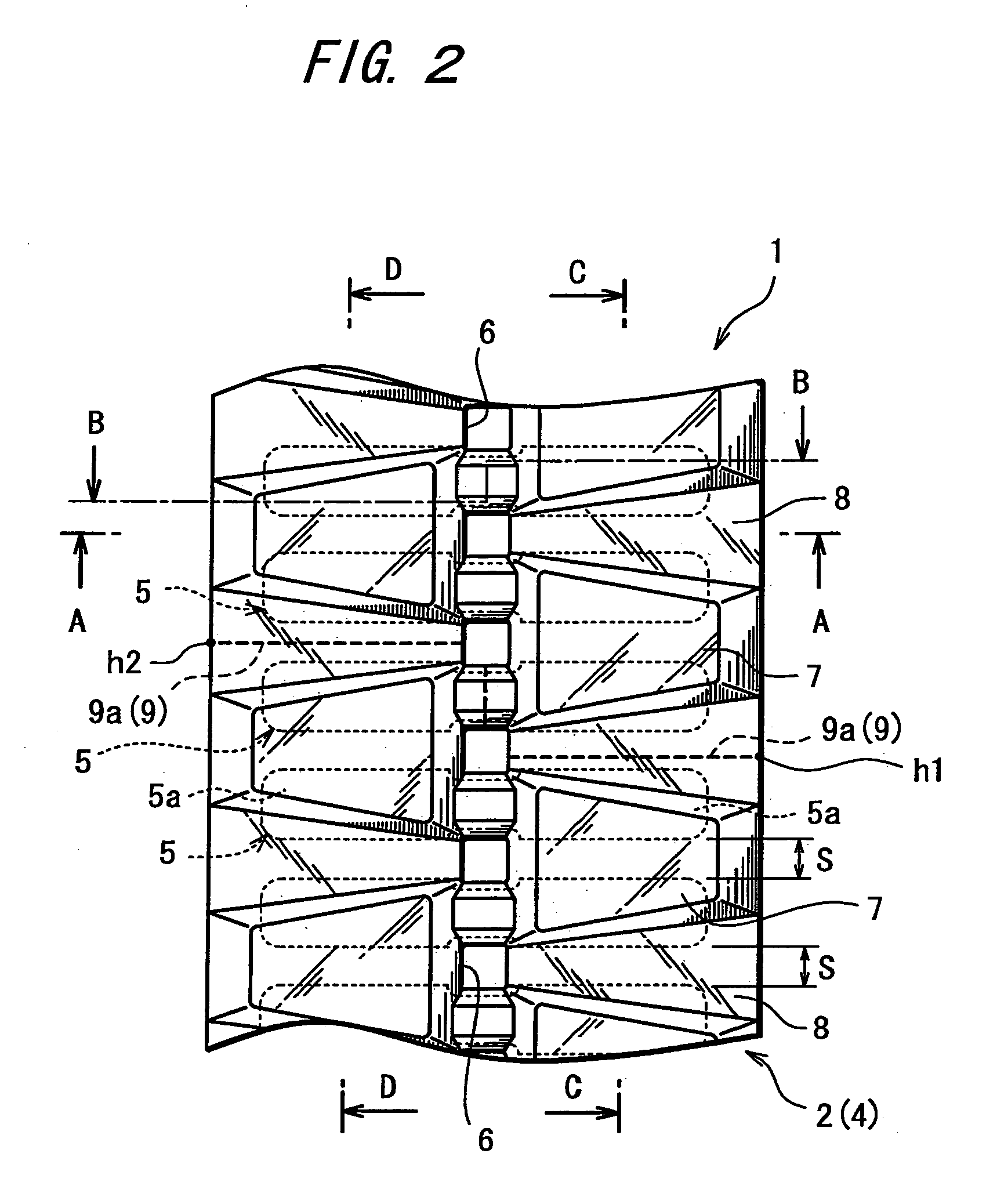

Tube for heat exchanger and method of manufacturing the same

InactiveUS20070095514A1Joining qualityUniformly formedReinforcing meansEvaporators/condensersEngineeringHeat exchanger

A tube for a heat exchanger has a tube member and a fin inserted in the tube member. The tube member has a first wall having a first end portion and a second wall having a second end portion. The second end portion of the second wall is folded over the first end portion of the first wall. Also, an end of the fin is held between the first end portion and the second end portion of the tube member. Further, the end of the fin has a bent portion at an end of the first end portion within the folded second end portion. The bent portion of the fin is engaged with the first end portion of the tube member for positioning the fin with respect to the tube member.

Owner:DENSO CORP

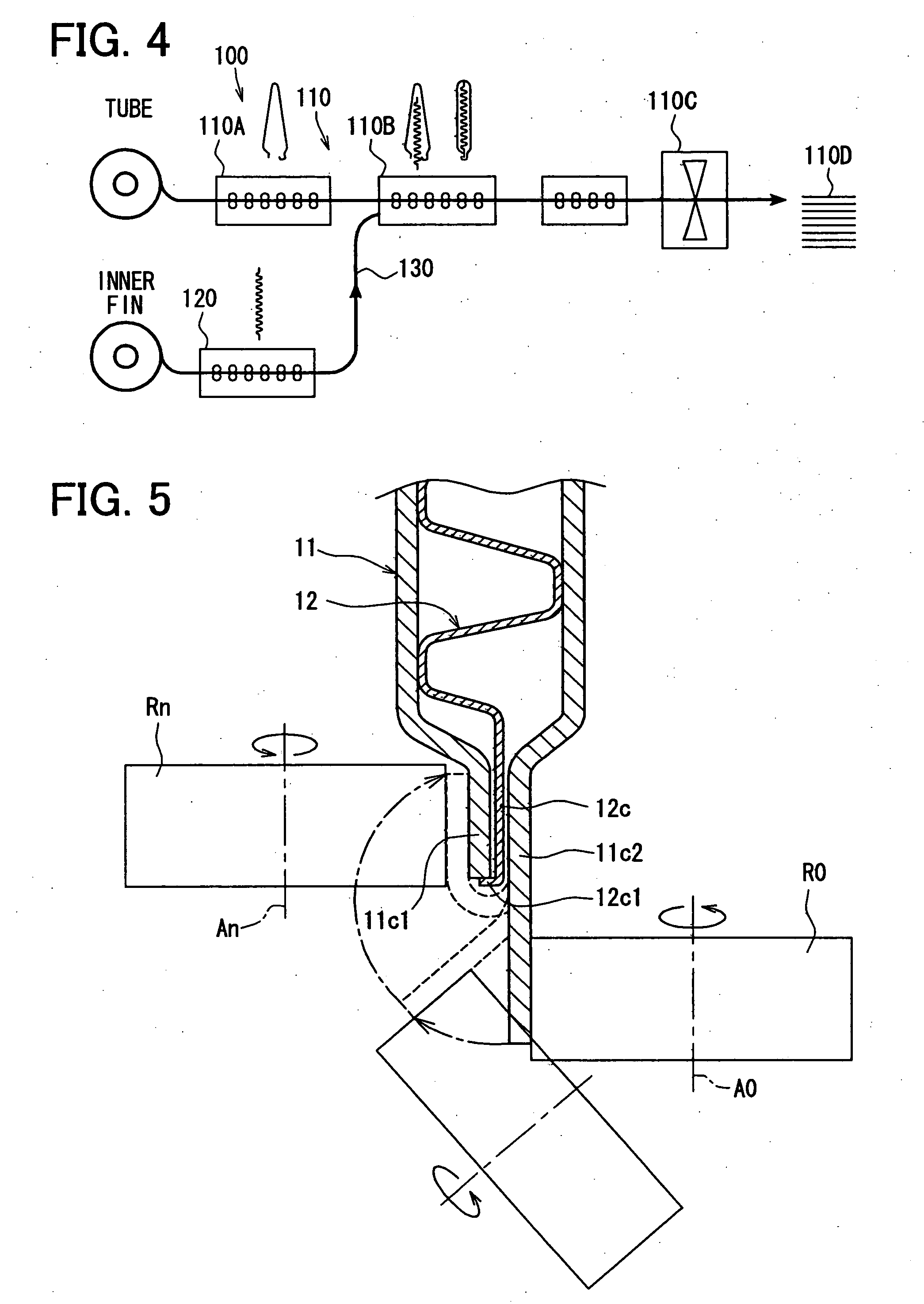

Laminated electronic component and manufacturing method therefor

ActiveUS20100290172A1Reliability be ensureImprove mount propertyFixed capacitor electrodesFixed capacitor dielectricBiomedical engineeringElectronic component

A method for manufacturing a laminated electronic component includes the steps of preparing a component main body having a laminated structure, the component main body including a plurality of internal electrodes formed therein, and each of the internal electrodes being partially exposed on an external surface of the component main body, and forming an external terminal electrode on the external surface of the component main body such that the external terminal electrode is electrically connected to the internal electrodes. The step of forming the external terminal electrode includes the steps of forming a first plating layer on exposed surfaces of the internal electrodes of the component main body, applying a water repellant at least on a surface of the first plating layer and on a section in the external surface of the component main body at which an end edge of the first plating layer is located, and then forming a second plating layer on the first plating layer having the water repellant applied thereon.

Owner:MURATA MFG CO LTD

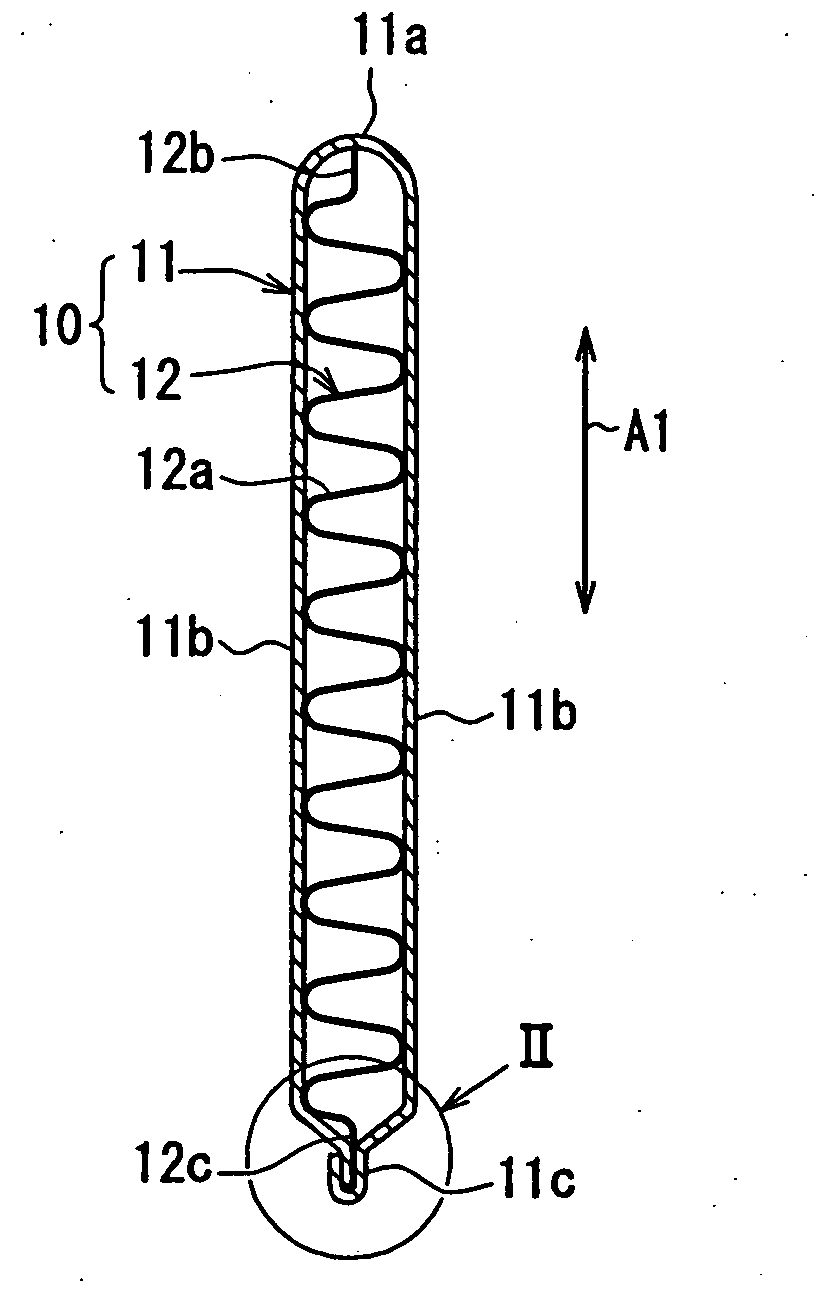

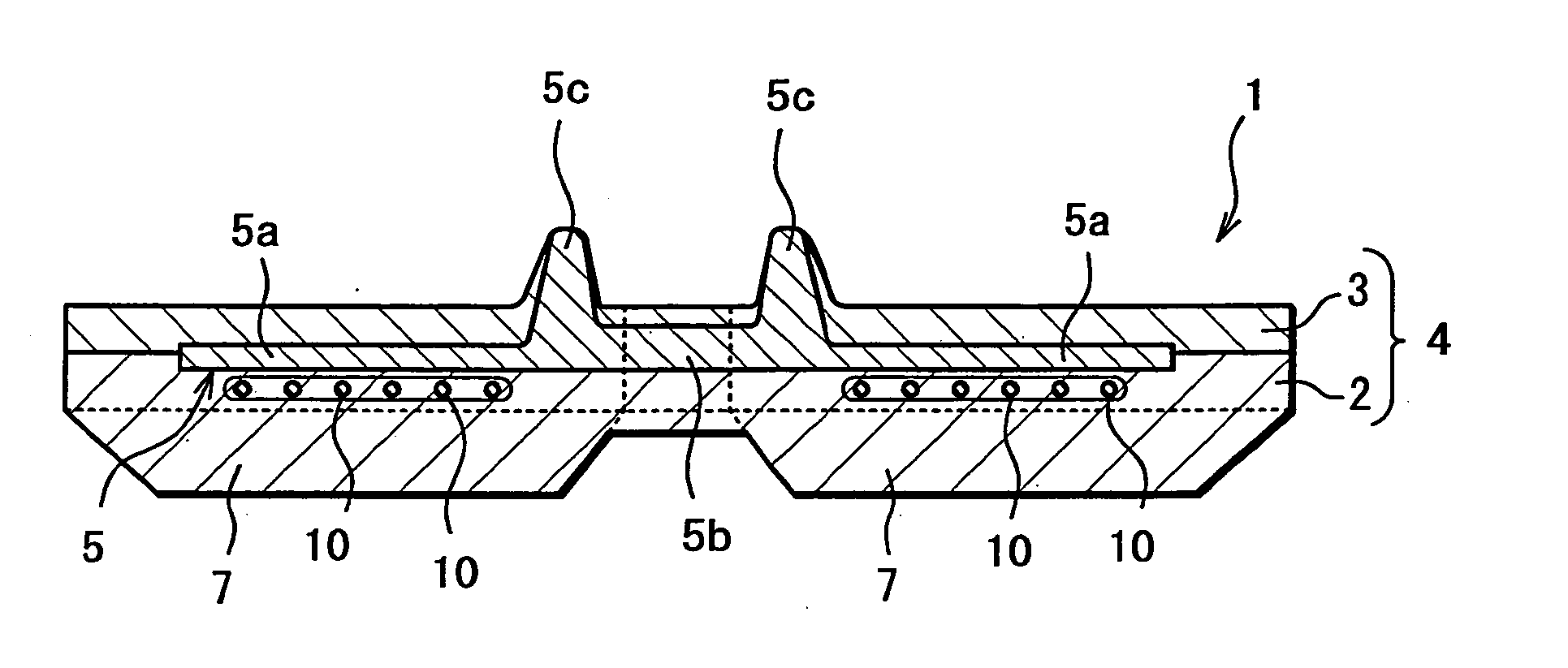

Rubber crawler

InactiveUS20050168069A1Small thicknessImprove joint strengthDriving beltsAlighting gearElastic componentEngineering

Owner:SUMITOMO RUBBER IND LTD

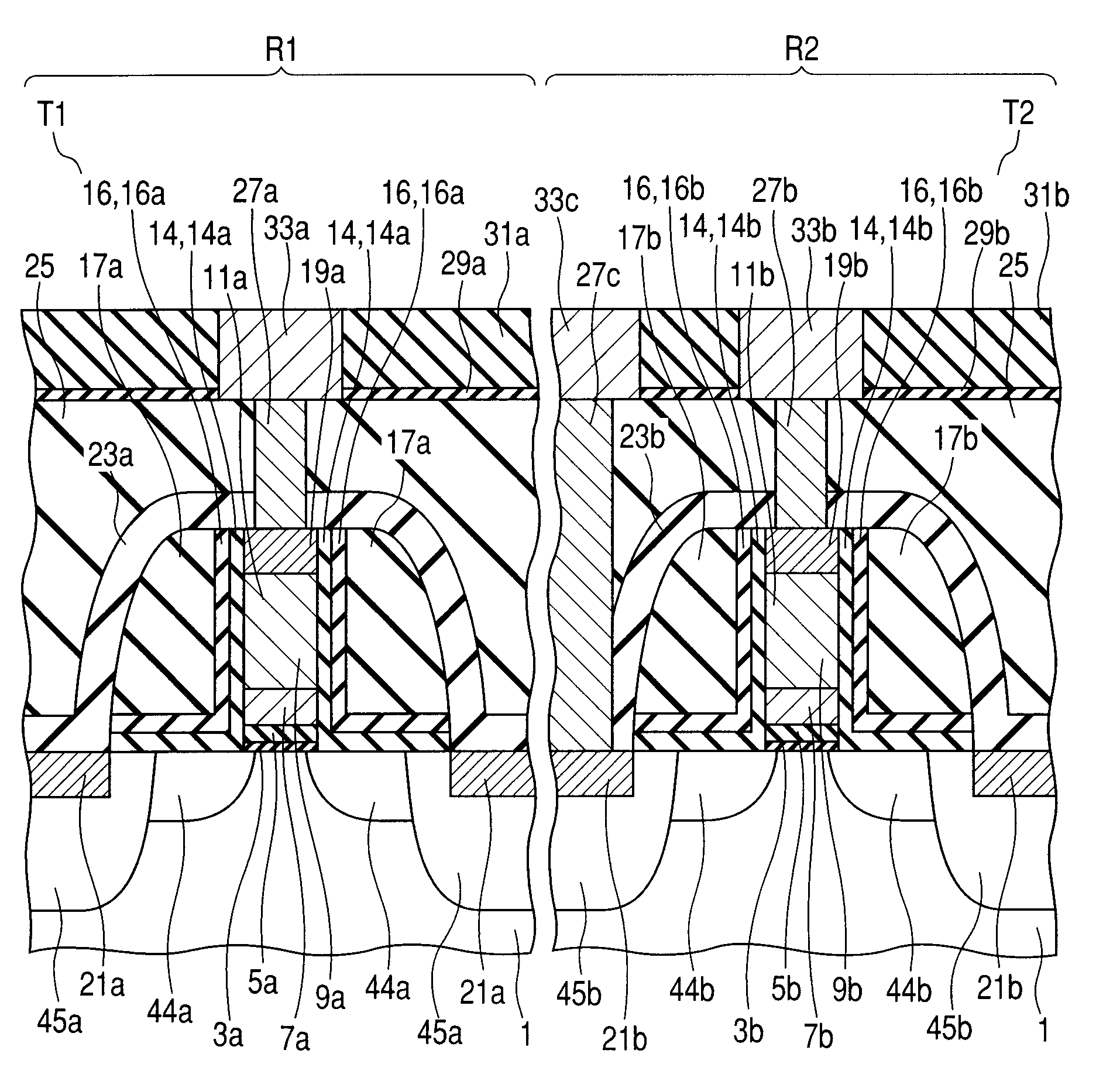

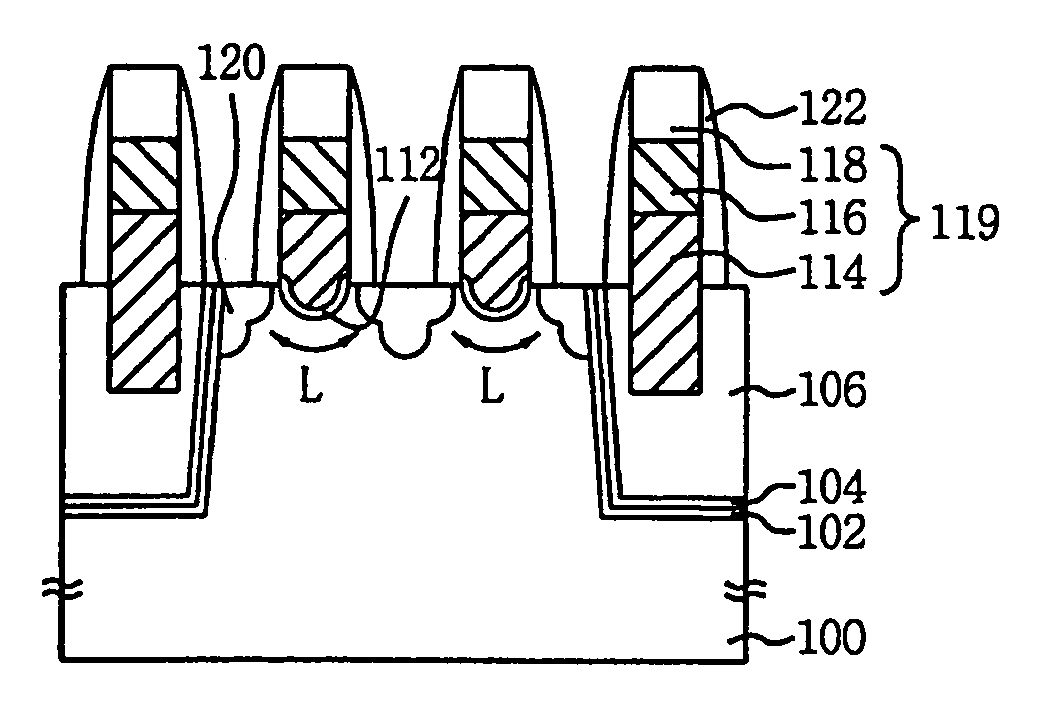

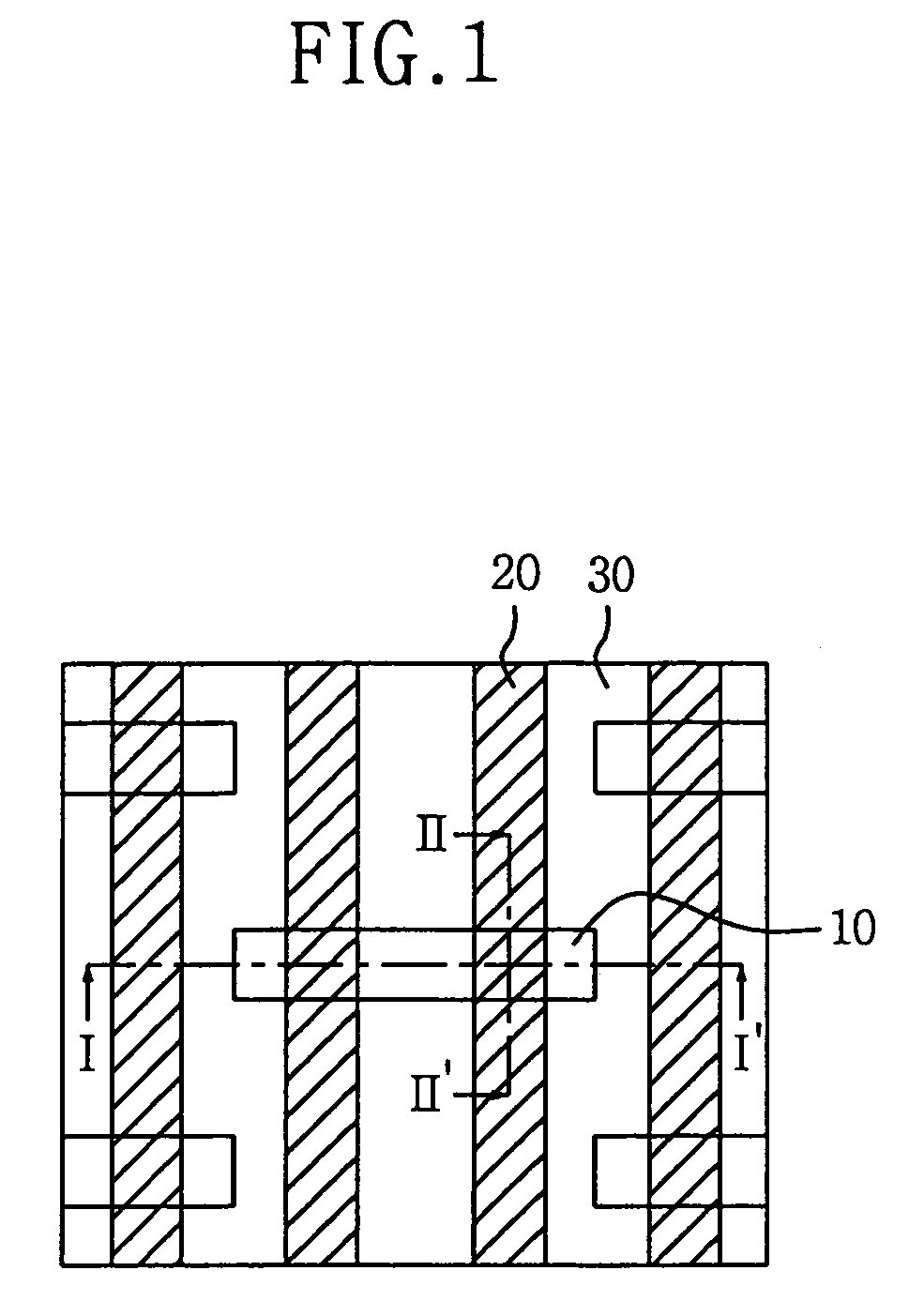

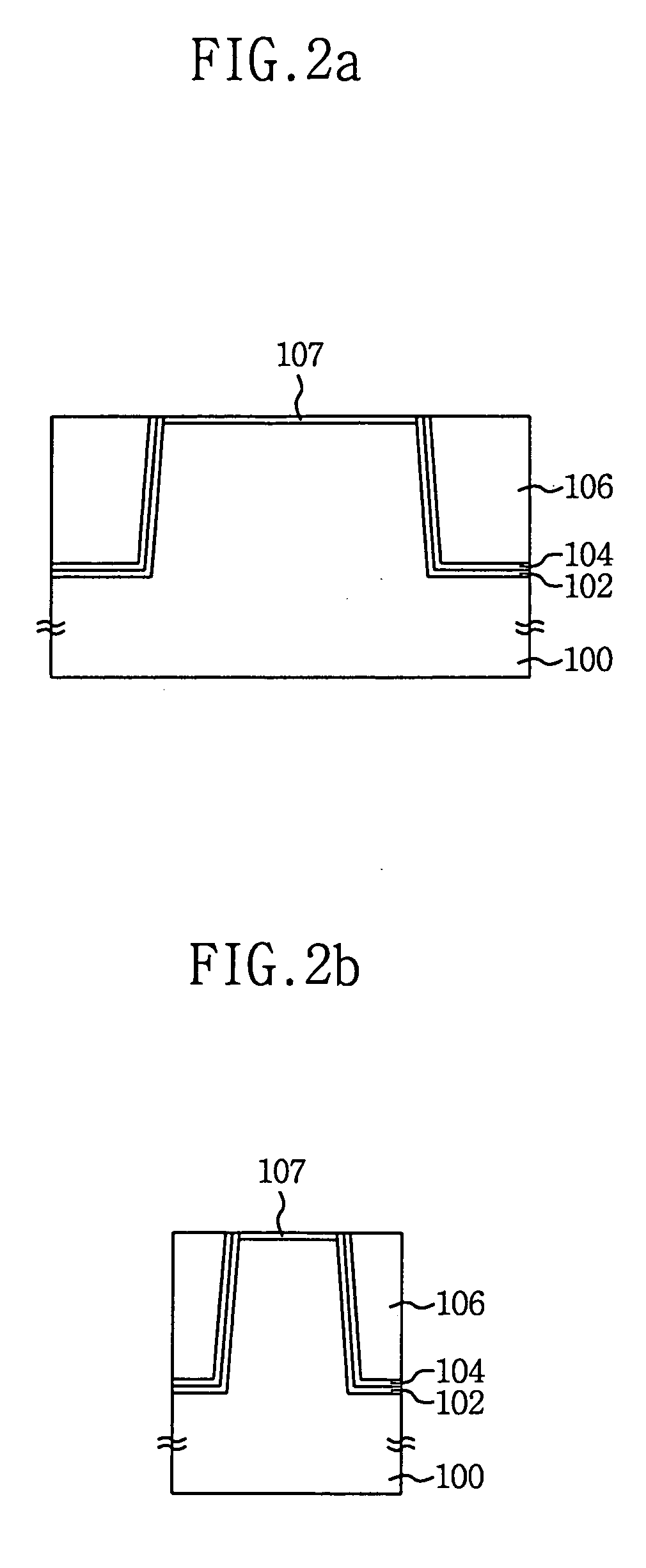

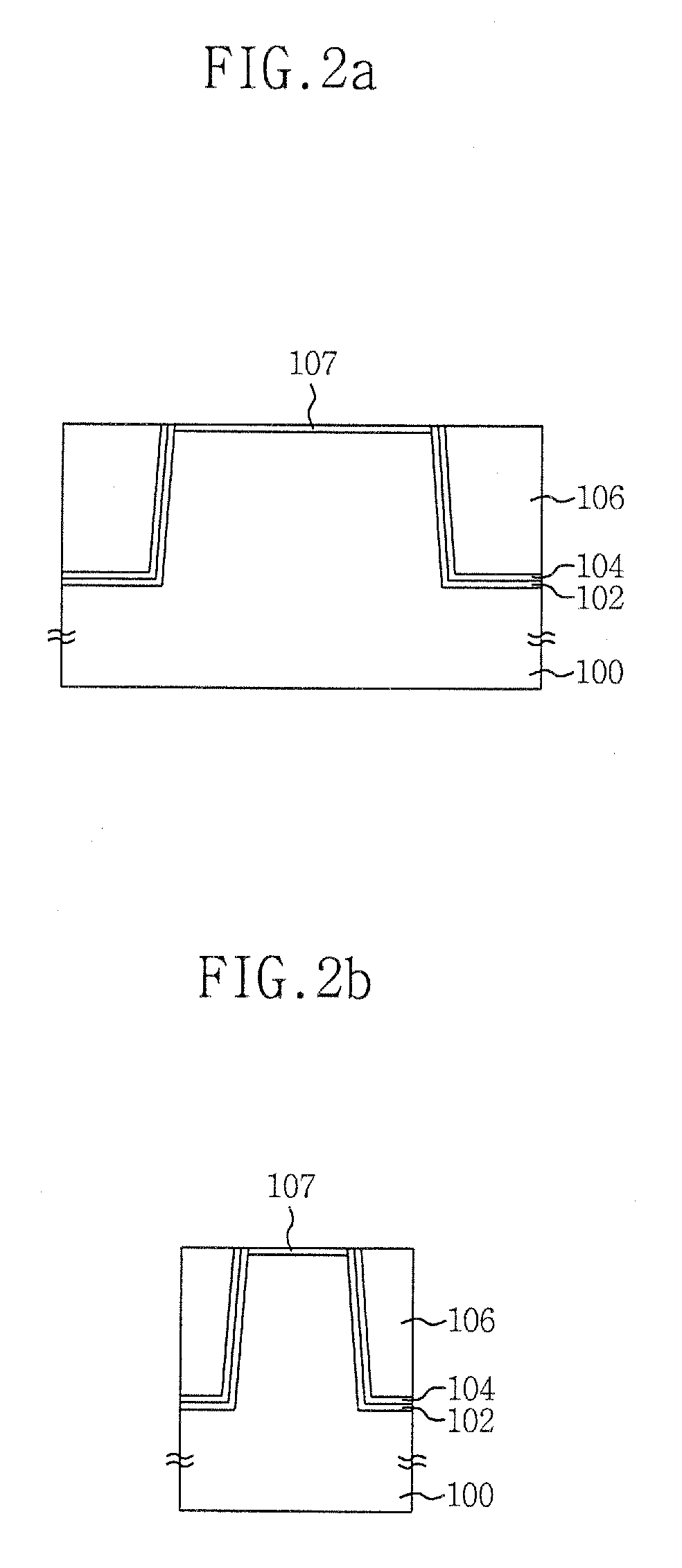

Fin FET and method of fabricating same

ActiveUS7217623B2Improving swing characteristicReducing electric fieldTransistorSolid-state devicesInsulation layerEngineering

A fin field effect transistor (fin FET) is formed using a bulk silicon substrate and sufficiently guarantees a top channel length formed under a gate, by forming a recess having a predetermined depth in a fin active region and then by forming the gate in an upper part of the recess. A device isolation film is formed to define a non-active region and a fin active region in a predetermined region of the substrate. In a portion of the device isolation film a first recess is formed, and in a portion of the fin active region a second recess having a depth shallower than the first recess is formed. A gate insulation layer is formed within the second recess, and a gate is formed in an upper part of the second recess. A source / drain region is formed in the fin active region of both sides of a gate electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

Methods of manufacturing non-volatile memory devices by implanting metal ions into grain boundaries of variable resistance layers, and related devices

ActiveUS20080203377A1Easy to operateUniformly formedDispersed particle filtrationSolid-state devicesElectrical resistance and conductanceGrain boundary

Integrated circuit nonvolatile memory devices are manufactured by forming a variable resistance layer on an integrated circuit substrate. The variable resistance layer includes grains that define grain boundaries between the grains. Conductive filaments are formed along at least some of the grain boundaries. Electrodes are formed on the variable resistance layer. The conductive filaments may be formed by implanting conductive ions into at least some of the grain boundaries. Moreover, the variable resistance layer may be a variable resistance oxide of a metal, and the conductive filaments may be the metal. Related devices are also disclosed.

Owner:SAMSUNG ELECTRONICS CO LTD

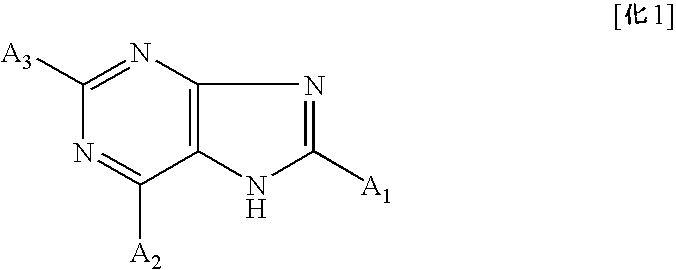

Positive electrode forming material, component thereof, method for producing the same and rechargeable lithium-ion battery

ActiveUS20100075229A1Improve conductivityGood dispersionMaterial nanotechnologyNon-metal conductorsCarbon fibersCarbon nanofiber

Disclosed is a positive electrode forming material for a positive electrode of a battery, the material including particles of a positive electrode active material and fine carbon fibers adhering to surfaces of particles of the positive electrode active material in a shape of a network. The positive electrode active material is preferably fine particles having an average particle diameter of 0.03 to 40 μm. Each of the fine carbon fibers is preferably carbon nanofiber having an average fiber diameter of 1 to 100 nm and an aspect ratio of 5 or greater. The carbon nanofiber is surface-oxidized. The positive electrode forming material includes a binder. The content of the fine carbon fibers is 0.5 to 15 parts by mass and the content of the binder is 0.5 to 10 parts by mass with respect to 100 parts by mass of the positive electrode active material.

Owner:MITSUBISHI MATERIALS ELECTRONICS CHEM CO LTD +1

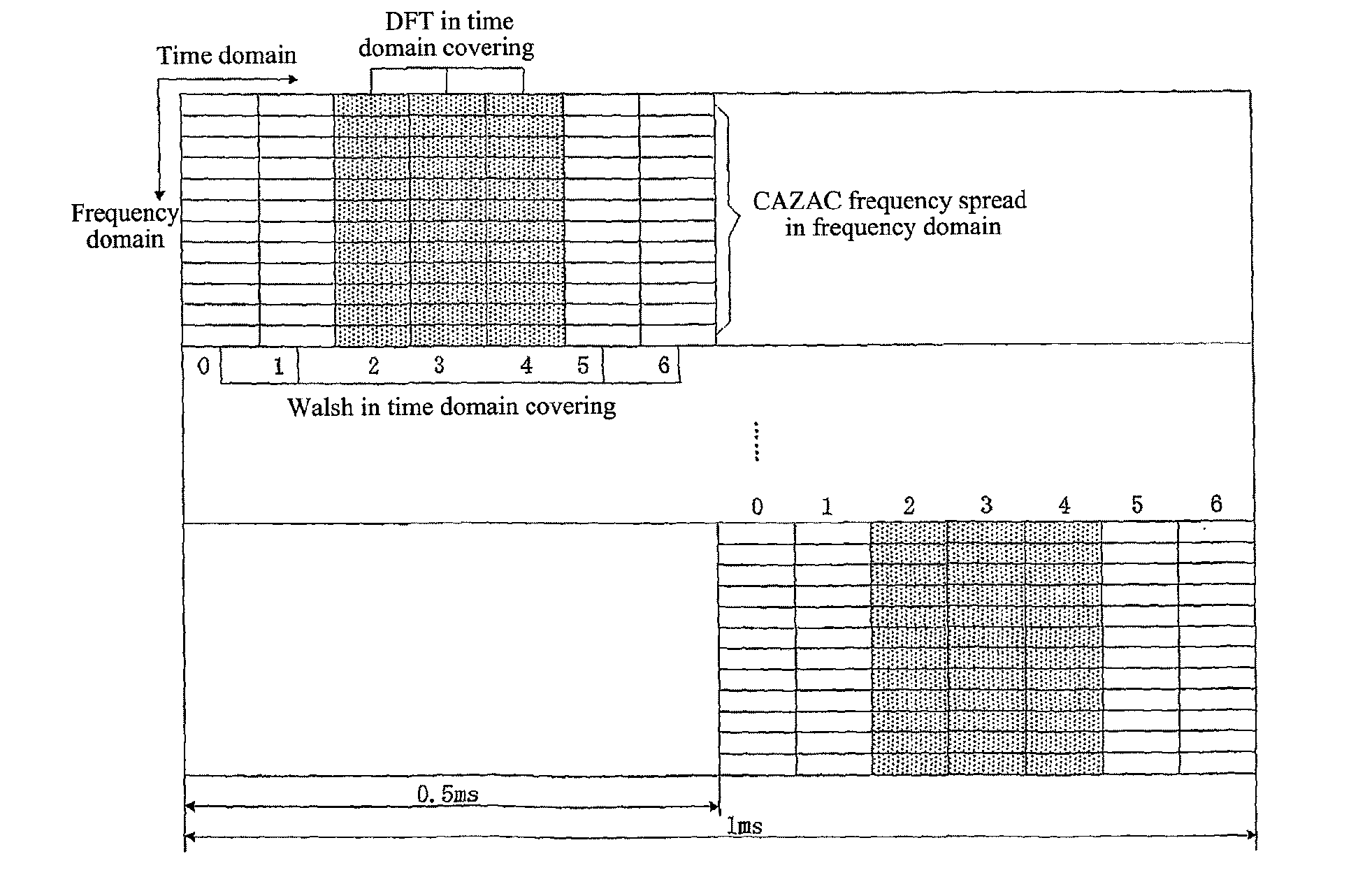

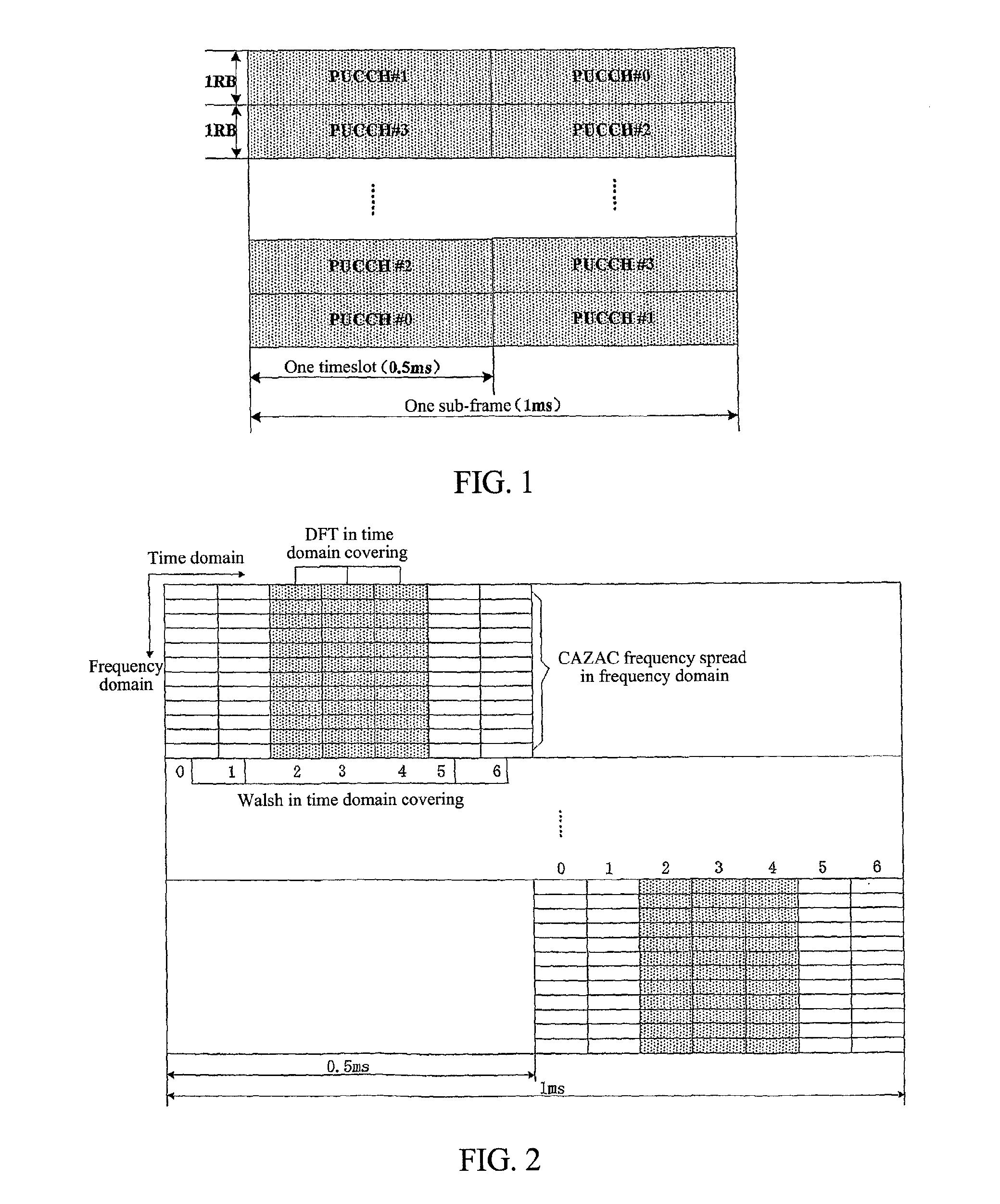

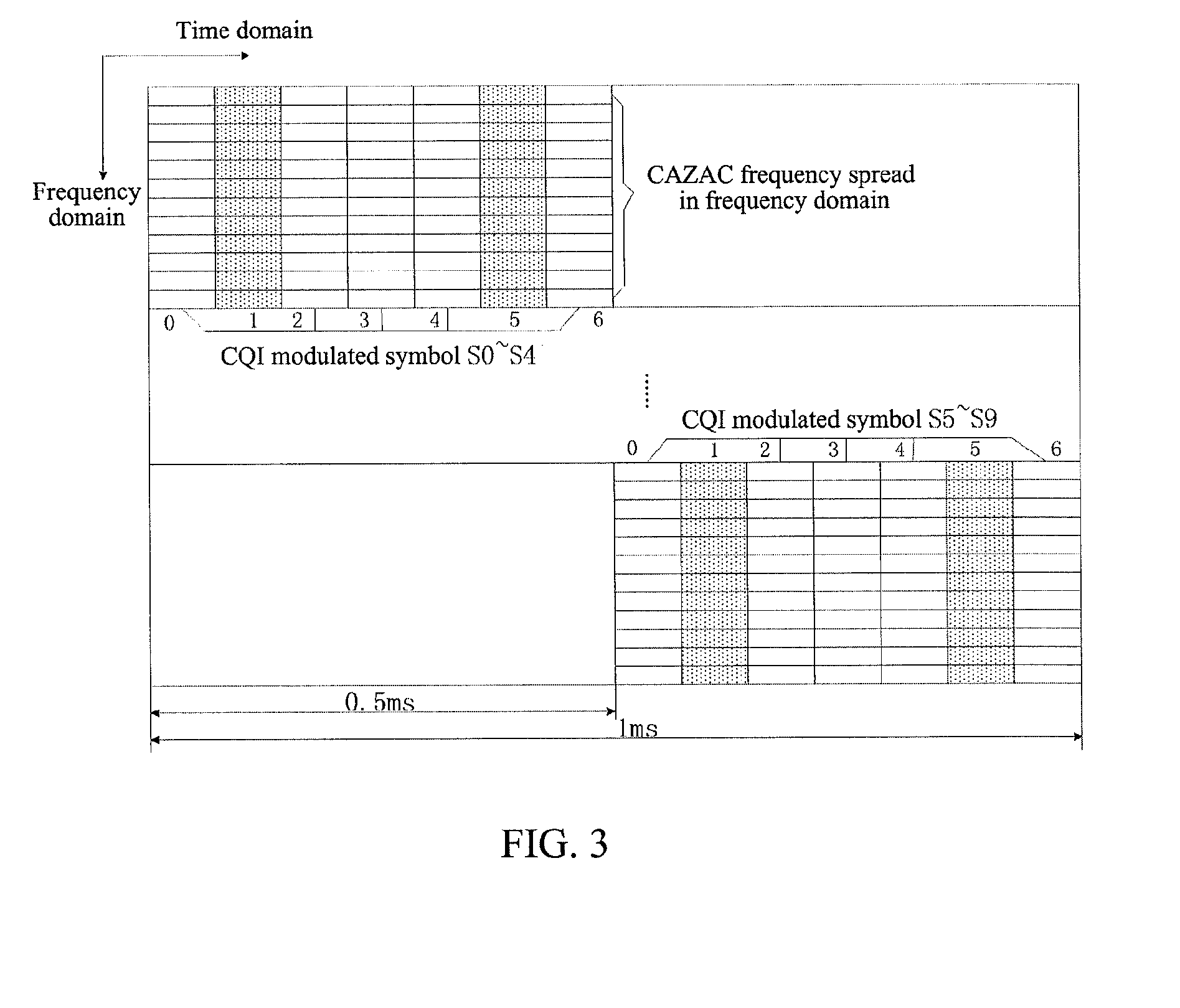

Method for interference randomization of physical uplink control channel

ActiveUS20110032926A1Easy to implementImprove performanceTransmission path divisionCriteria allocationTelecommunicationsControl channel

A method for interference randomization of physical uplink control channel (PUCCH), which is used in long term evolution (LTE) system, when multiple terminals multiplex PUCCH to transmit uplink control signallings, the difference of index of control channel resource used by any two terminals in the first timeslot of PUCCH is different from the difference of index of control channel resource used by the two terminals in the second timeslot of PUCCH. The invention can realize interference randomization between UEs that multiplex the same PUCCH.

Owner:ZTE CORP

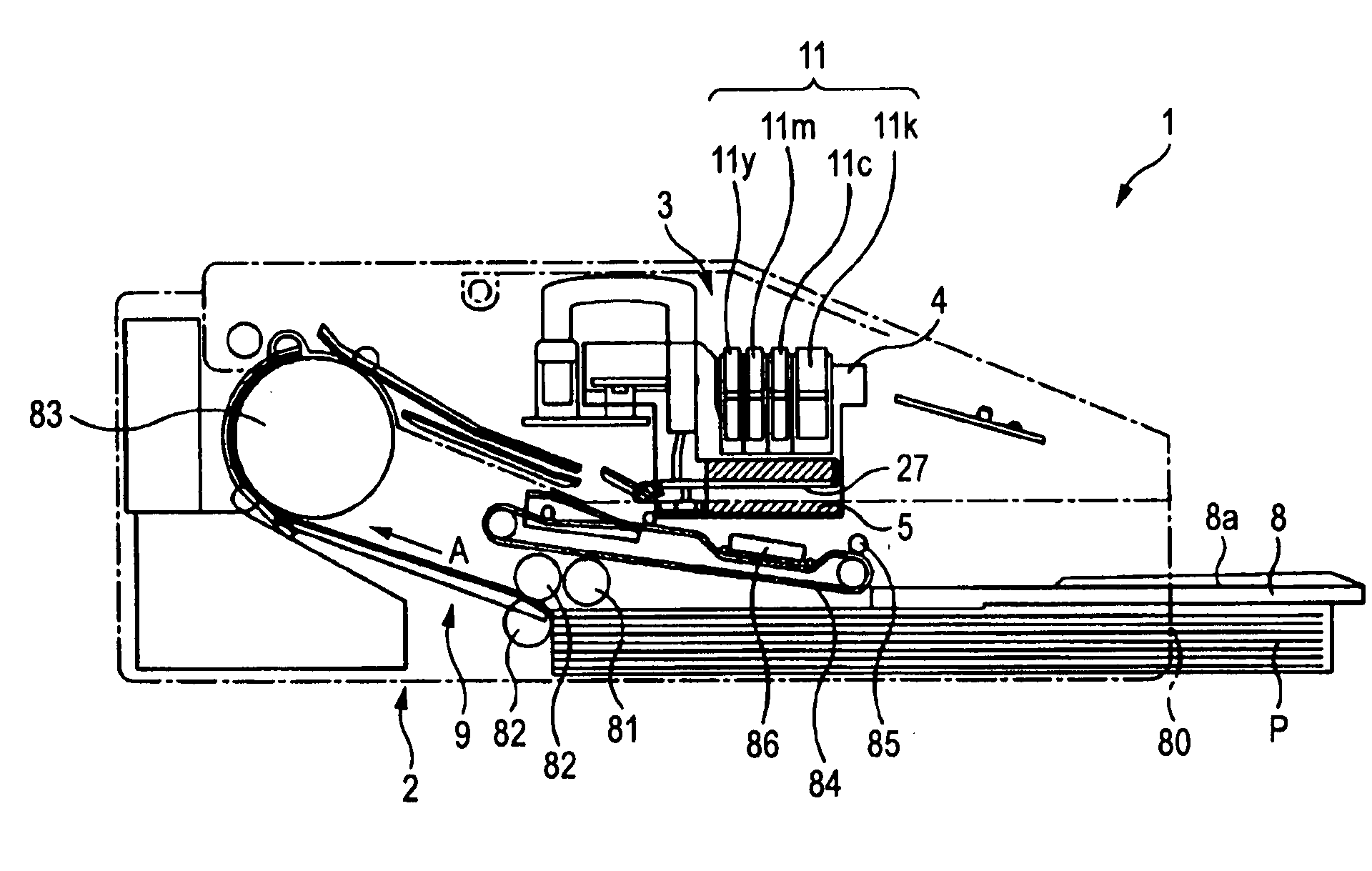

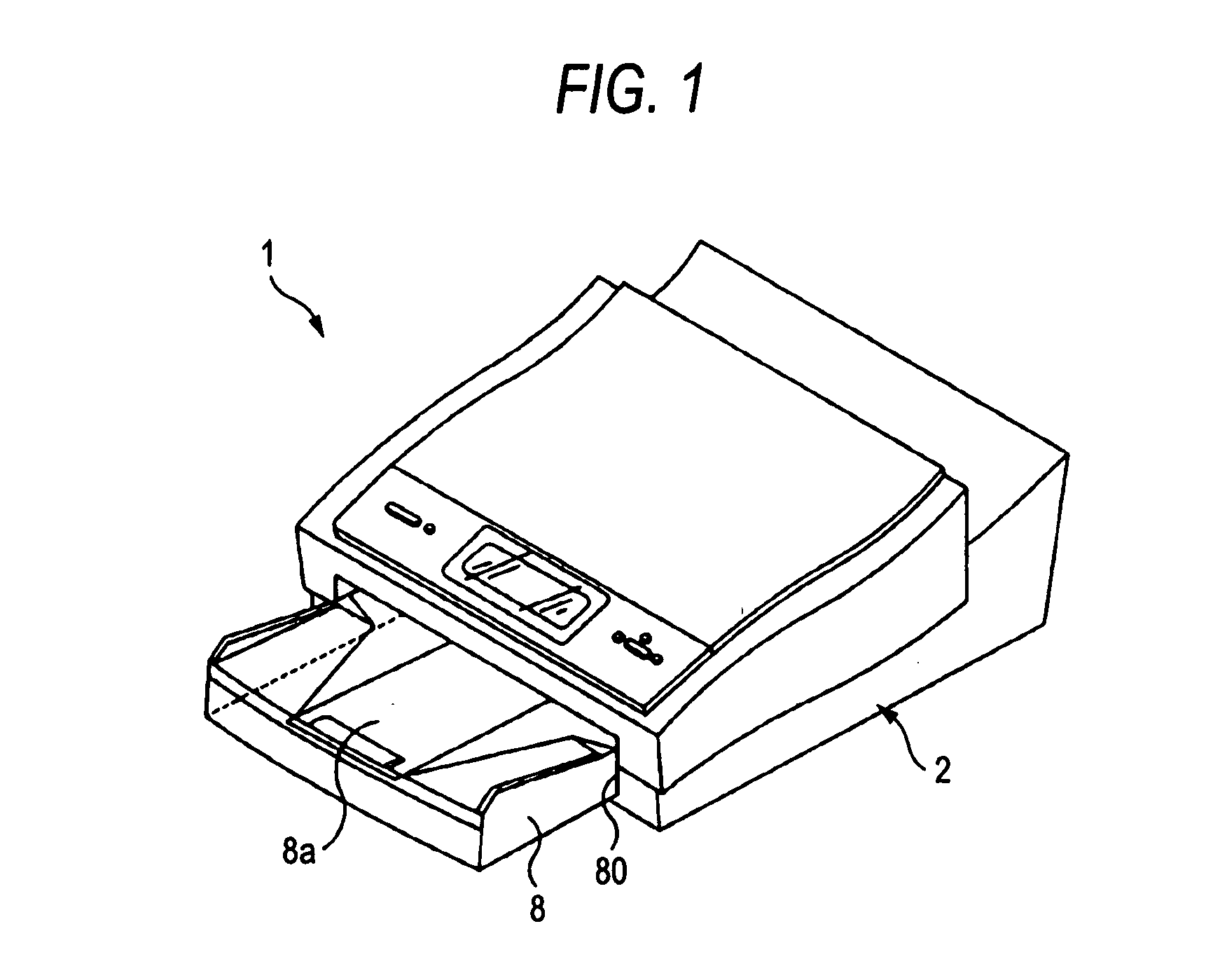

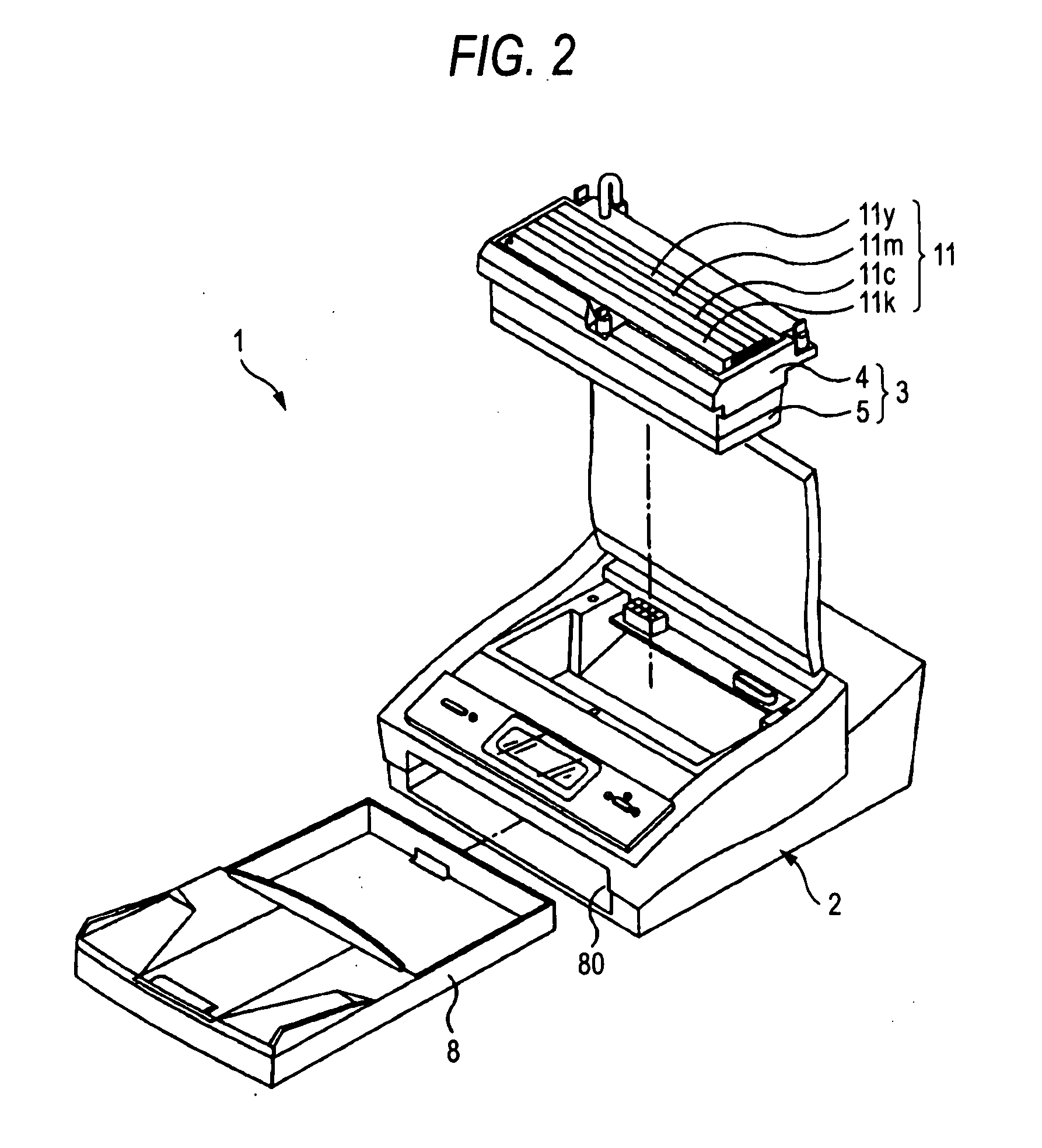

Cleaning blade, method fabricating cleaning blade, and cleaning apparatus for liquid discharge head

A cleaning blade which wipes a liquid discharge area by being moved relatively with respect to the liquid discharge area of a liquid discharge head having the liquid discharge area in which liquid discharge nozzles are arranged to discharge a liquid is disclosed. The cleaning blade includes: a supporting plate which has an adhesive agent layer on its front surface; and a wipe part which is slid and contacted with the liquid discharge area, the wipe part formed in which an elastic part formed of a synthetic resin is formed in one piece on the adhesive agent layer, and a tip end thereof is cut in a predetermined shape.

Owner:SONY CORP

Method of manufacturing color filter substrate, method of manufacturing electro-optical device, electro-optical device, and electronic apparatus

InactiveUS7459177B2Uniform film thicknessA large amountDomestic cooling apparatusLighting and heating apparatusEngineeringSolvent

The color filter substrate has a functional region which includes a plurality of colored layers and which functions as a color filter selectively transmitting predetermined color light components and a non-functional region other than the functional region. The method includes discharging, onto a substrate, a liquid material, in which coloring materials constituting the colored layers are dissolved or dispersed into a solvent, with a liquid droplet discharge method. In the discharging of the liquid material, the liquid material is discharged onto the functional region and the liquid material or the solvent is discharged onto the non-functional region. The amount of the solvent discharged onto the non-functional region per unit area is larger than the amount of the solvent discharged onto the functional region per unit area.

Owner:KATEEVA

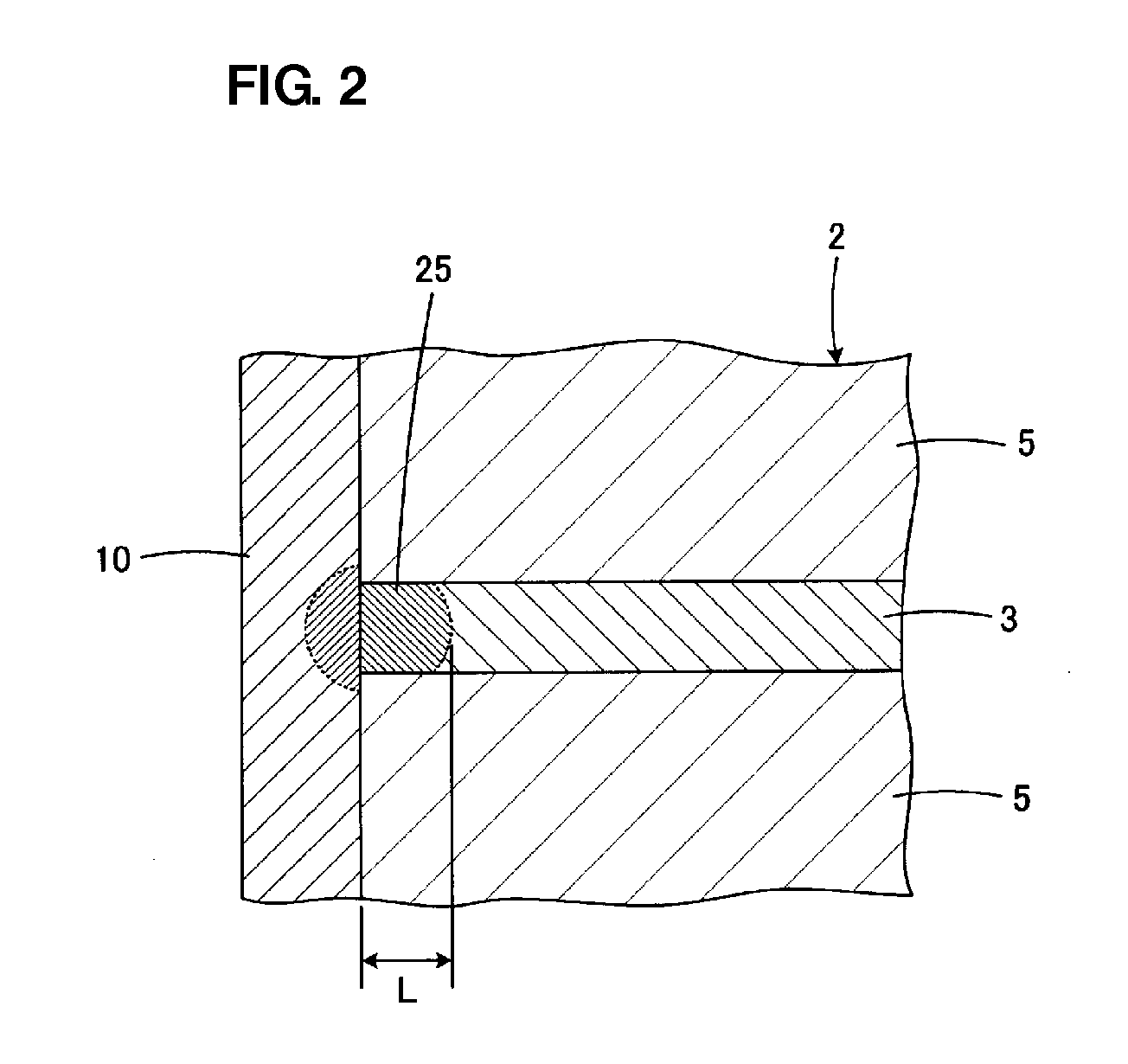

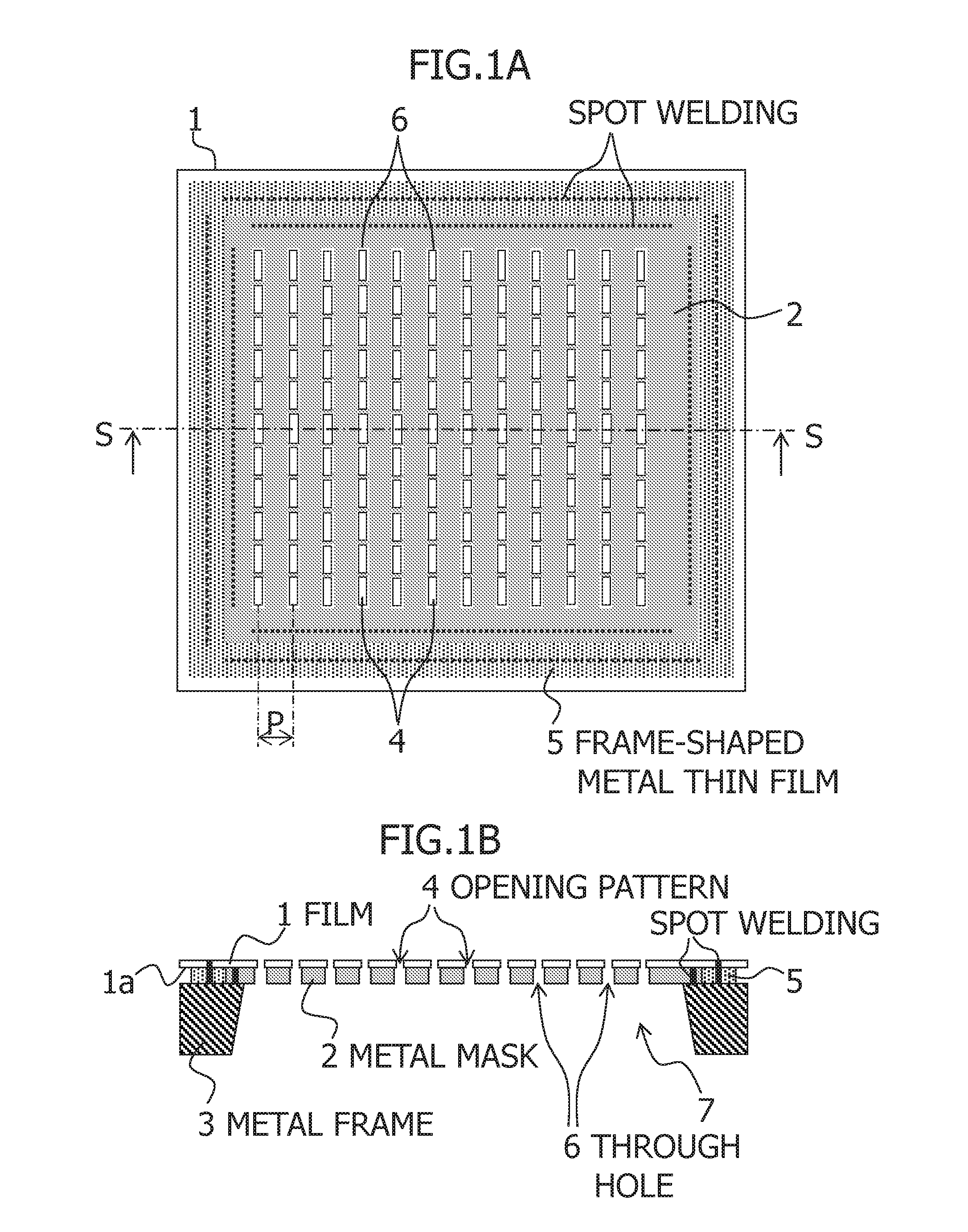

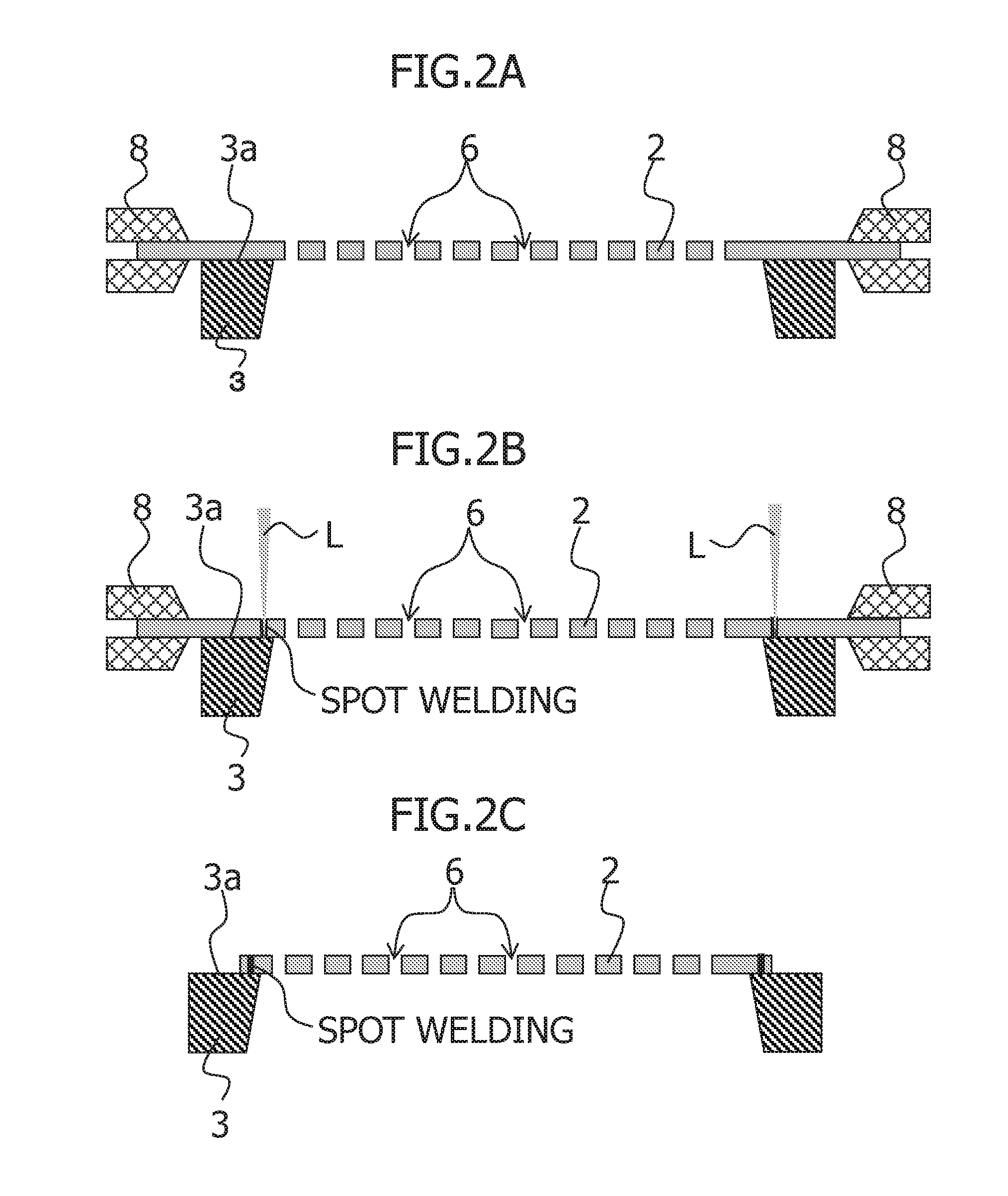

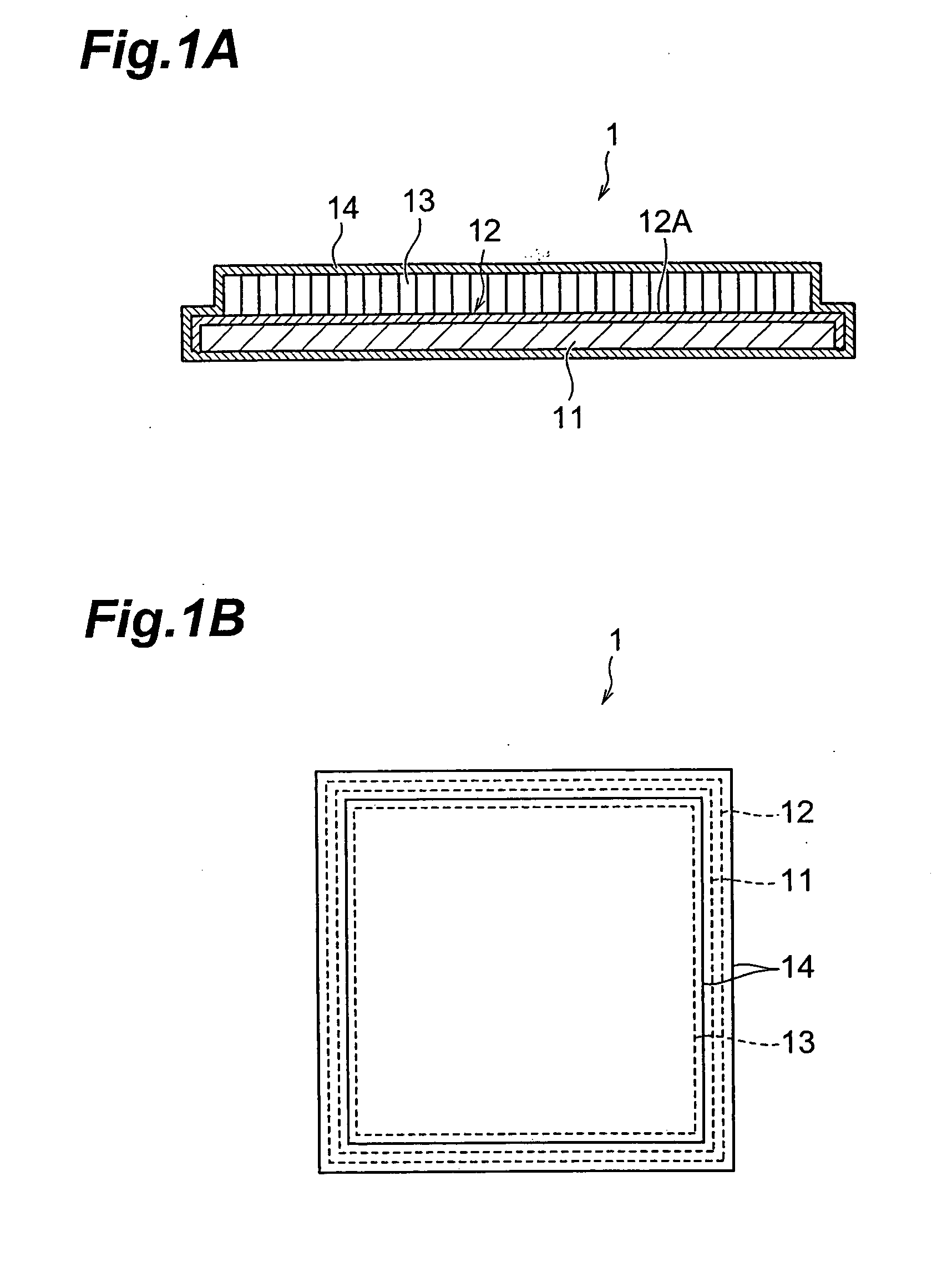

Deposition mask and method for producing deposition mask

ActiveUS20160115580A1High positioning accuracyReduce positional deviationVacuum evaporation coatingSputtering coatingEngineeringSpot welding

A deposition mask is provided. The deposition mask including: a resin film 1 in which penetrating opening patterns 4 are formed and a frame-shaped metal thin film 5 having an opening is provided on one face 1a of the film 1; a metal mask 2 provided at a position corresponding to the opening of the metal thin film 5 on one face 1a side of the film 1, the metal mask 2 being separated from and independent of the film 1, the metal mask 2 being provided with through holes 6; and a metal frame 3 positioned on one face 1a side of the film 1, the metal frame 3 supporting the film 1 and the metal mask 2 by spot-welding a portion of the metal thin film 5 and an edge region of the metal mask 2 to one end face 3a.

Owner:V TECH CO LTD

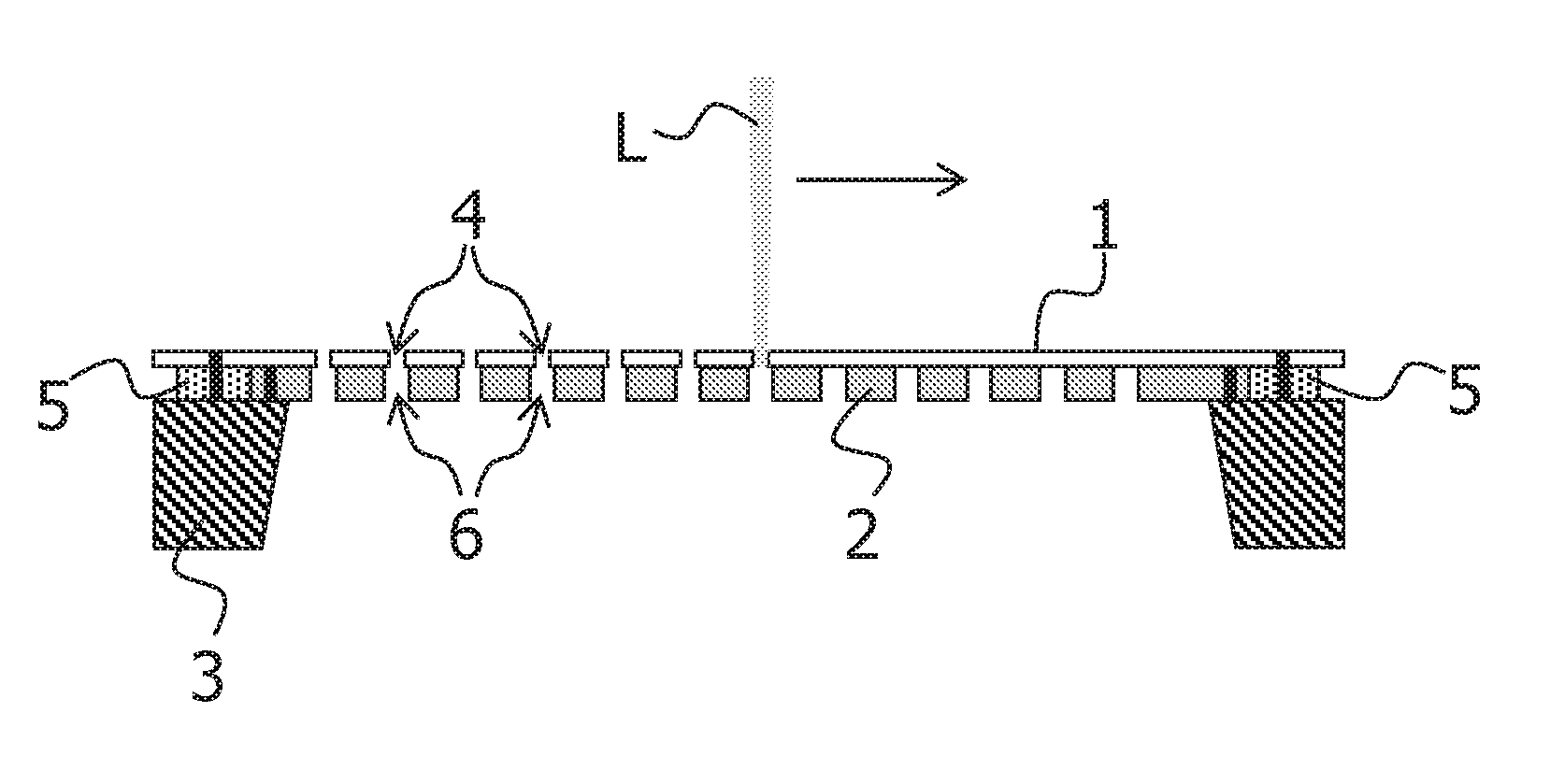

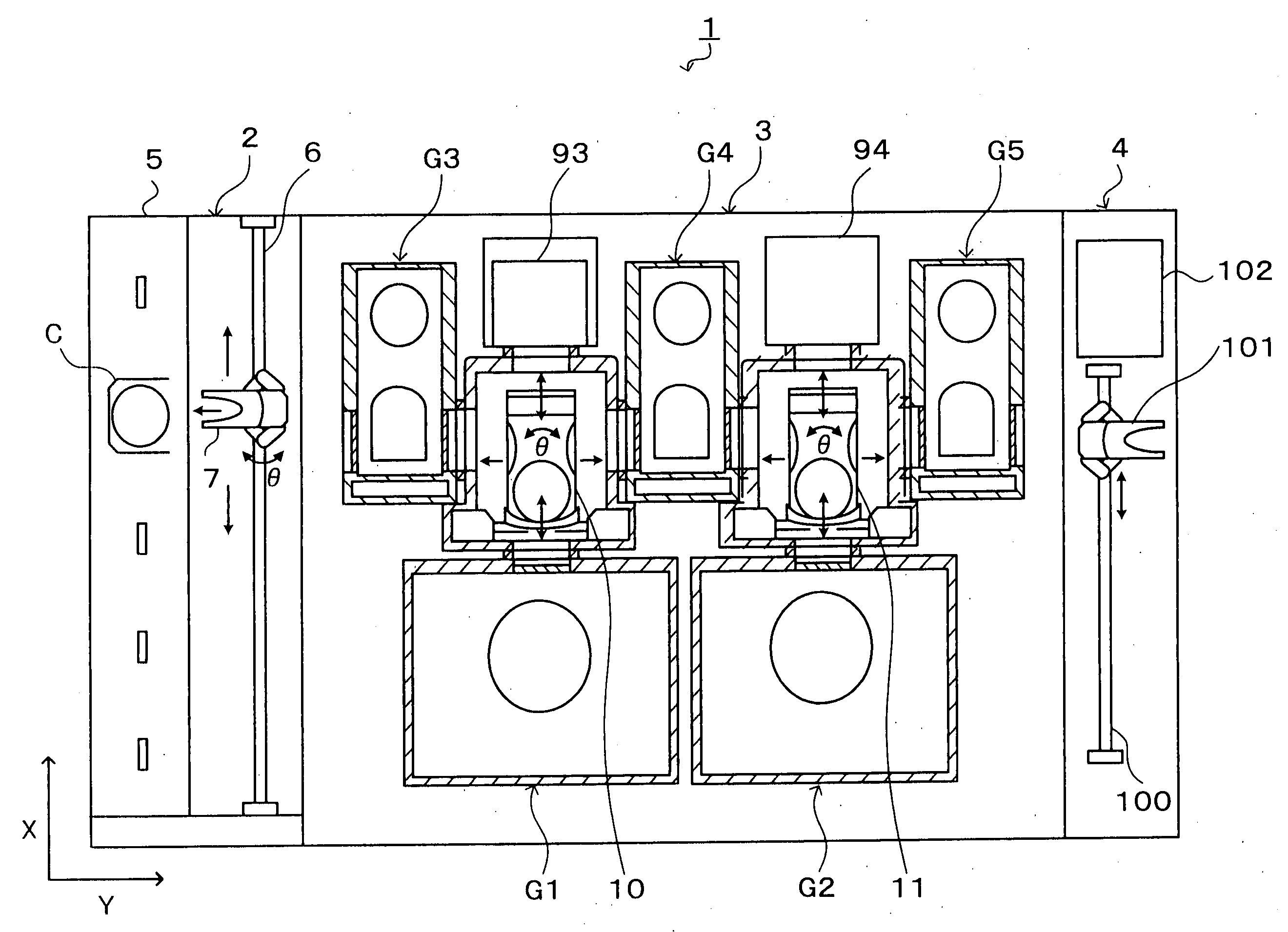

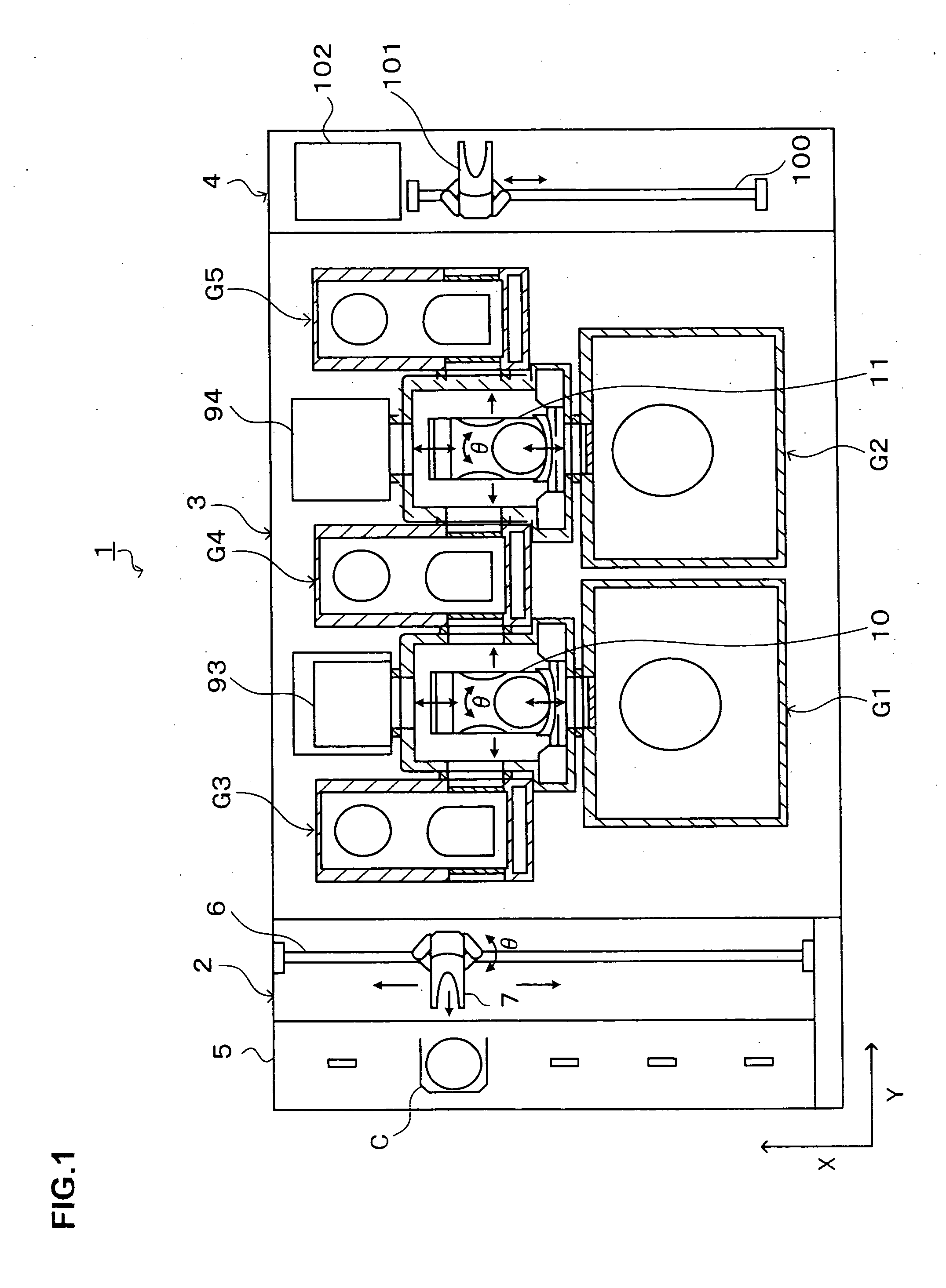

Substrate Treatment Method and Substrate Treatment Apparatus

An object of the present invention is to uniformly form a fine resist pattern with a desired dimension within a plane of a substrate. In a solvent vapor supply unit, a solvent vapor discharge nozzle is provided which can discharge a solvent vapor for swelling a resist pattern while moving above the front surface of a wafer. The wafer for which developing treatment has been finished and on which a resist pattern has been formed is carried into the solvent vapor supply unit, and the solvent vapor discharge nozzle is moved above the front surface of the wafer, so that the solvent vapor discharge nozzle supplies the solvent vapor onto the front surface of the wafer. This uniformly supplies a predetermined amount of solvent vapor to the resist pattern on the front surface of the wafer. As a result, the solvent vapor causes the resist pattern to evenly swell by a predetermined dimension, so that a resist pattern with a desired dimension is finally uniformly formed within the plane of the wafer.

Owner:TOKYO ELECTRON LTD

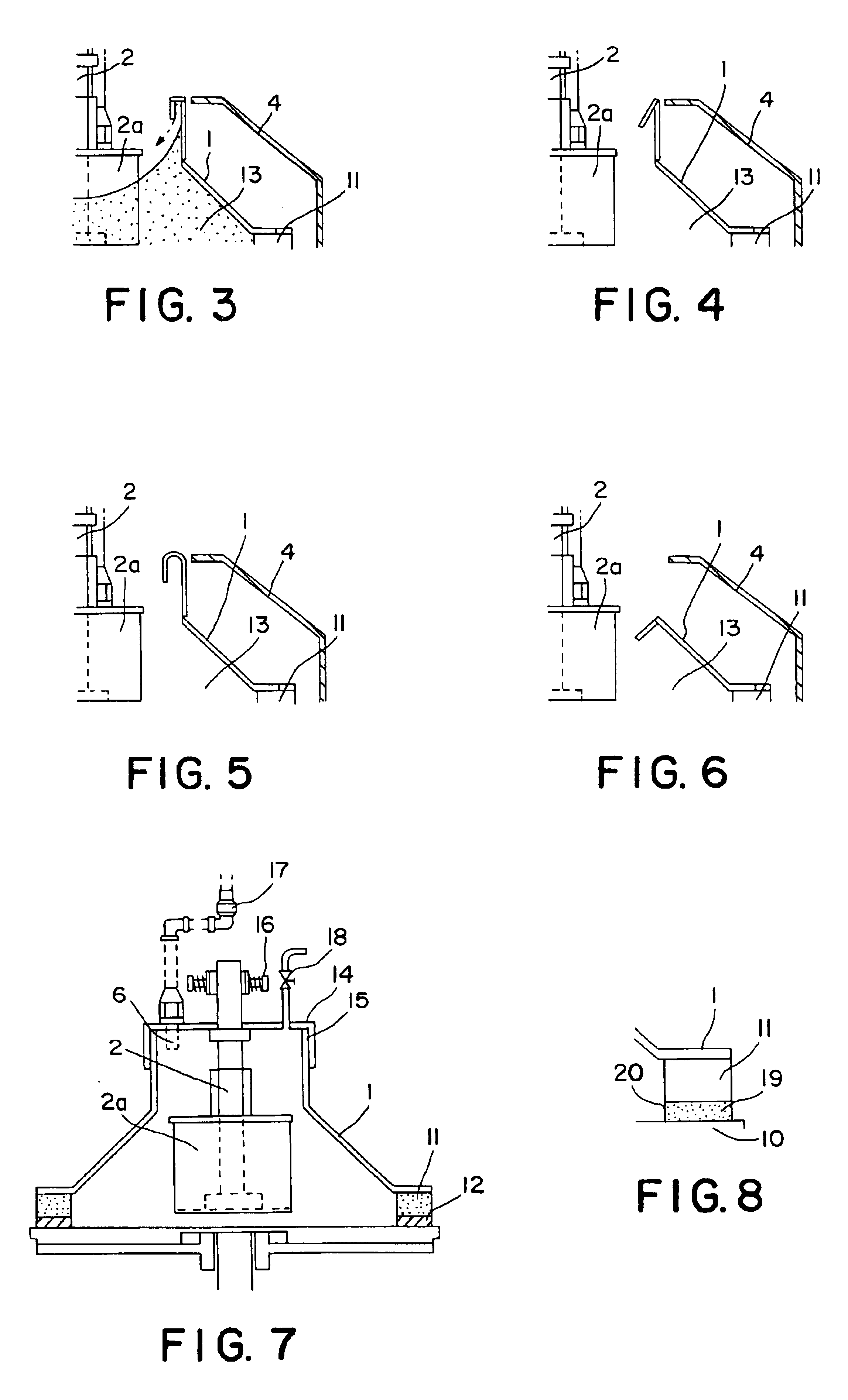

Method for manufacturing organic EL device with protective layer

InactiveUS6933002B2Expand coverageImprove moisture resistanceElectroluminescent light sourcesSolid-state devicesVitrificationEngineering

An organic EL device has a structure in which an anode, a hole transporting layer, an organic luminescent layer, and a cathode are disposed on a glass substrate in this order. The organic EL device further has a protective layer covering an outer surface of the structure to protect it from an external environment. The protective layer is formed by an ALE method at a temperature lower than glass transition temperatures materials constituting the hole transporting layer and the organic luminescent layer.

Owner:DENSO CORP

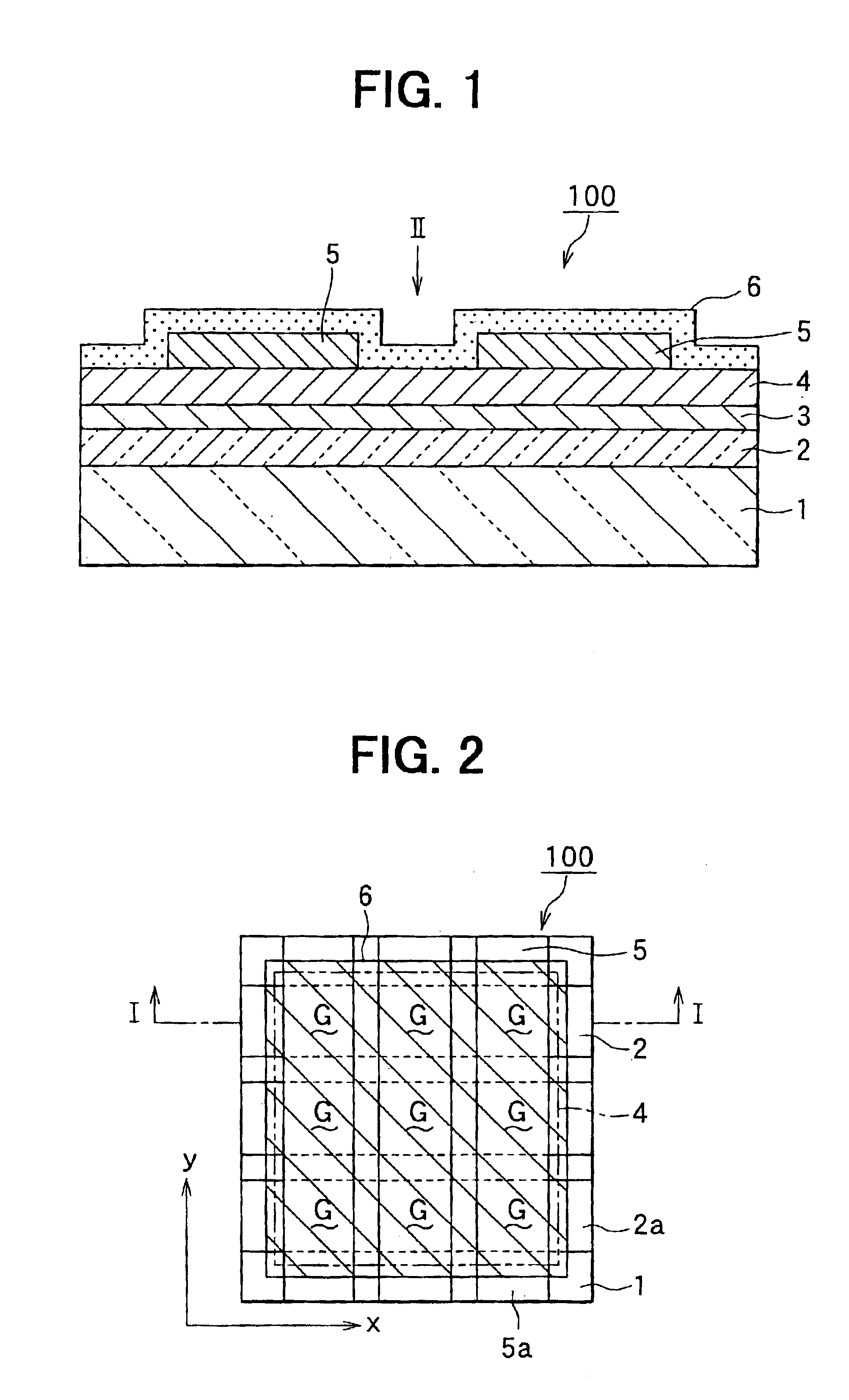

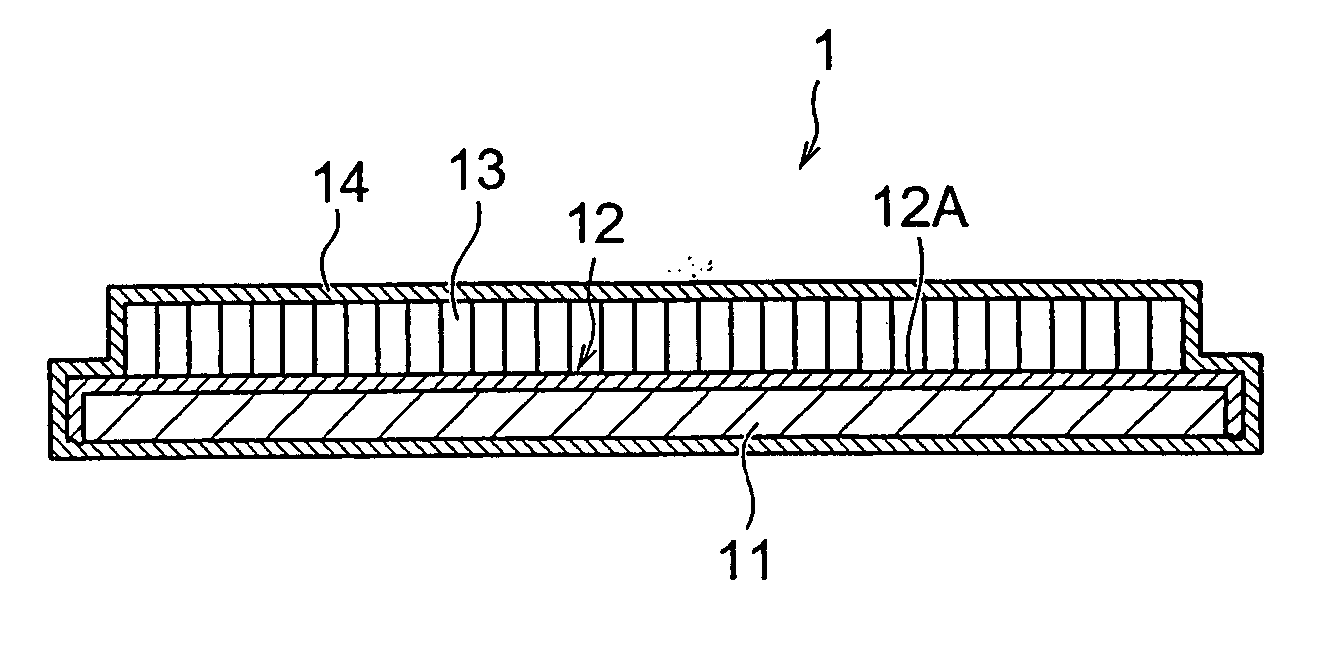

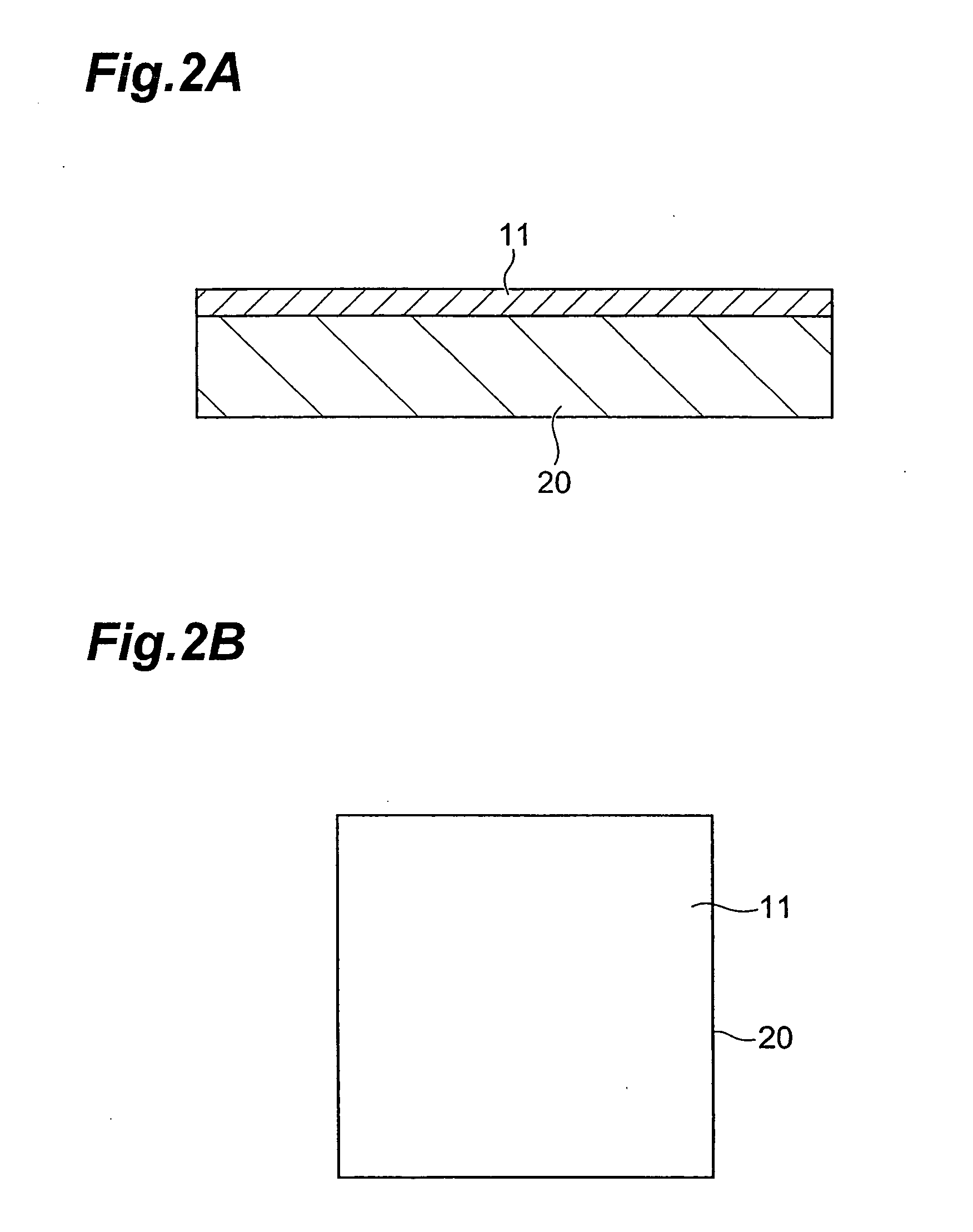

Scintillator panel and method of manufacturing radiation image sensor

InactiveUS20060263521A1Increase the area ratioSlimming down of the substrateAdhesivesChemical vapor deposition coatingOrganic filmOptoelectronics

An auxiliary substrate 20 is overlapped onto a thin substrate 11, and substrate 11 and auxiliary substrate 20 are covered with an organic film 12. Thereafter, a scintillator 13 is formed on a scintillator forming portion 12A of organic film 12 that corresponds to substrate 11. Here, since thickness is added to substrate 11 by auxiliary substrate 20, the warping of substrate 11 is prevented and scintillator 13 is formed uniformly.

Owner:HAMAMATSU PHOTONICS KK

Plasma Gun and Plasma Gun Deposition System Including the Same

InactiveUS20110011734A1Unity of formAvoid depositionCellsElectric discharge tubesExhaust valveEngineering

Owner:SHIN MEIWA IND CO LTD

Fin FET and method of fabricating same

ActiveUS20070176245A1Improving swing characteristicReducing electric fieldTransistorSolid-state devicesInsulation layerSilicon

A fin field effect transistor (fin FET) is formed using a bulk silicon substrate and sufficiently guarantees a top channel length formed under a gate, by forming a recess having a predetermined depth in a fin active region and then by forming the gate in an upper part of the recess. A device isolation film is formed to define a non-active region and a fin active region in a predetermined region of the substrate. In a portion of the device isolation film a first recess is formed, and in a portion of the fin active region a second recess having a depth shallower than the first recess is formed. A gate insulation layer is formed within the second recess, and a gate is formed in an upper part of the second recess. A source / drain region is formed in the fin active region of both sides of a gate electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

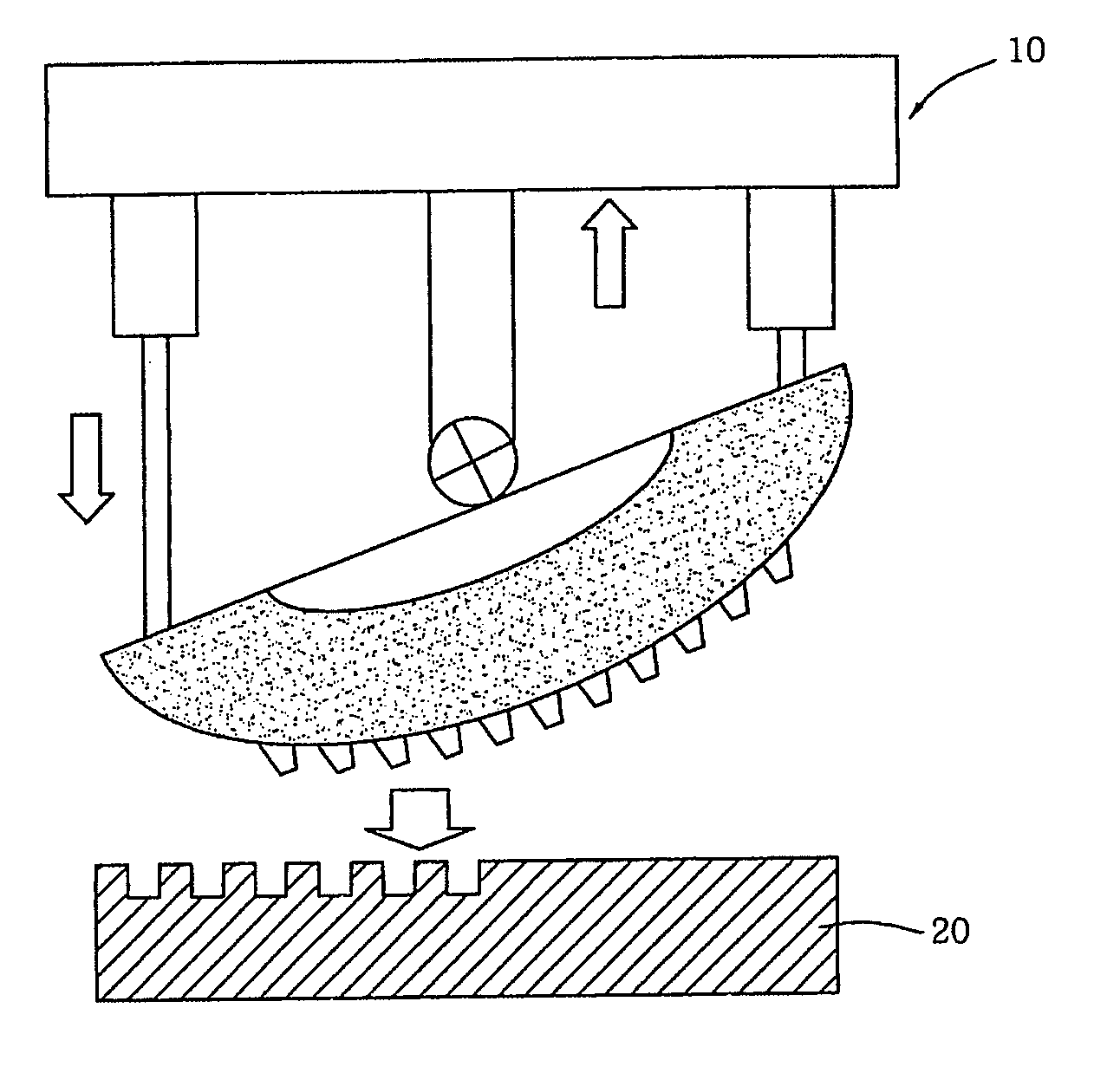

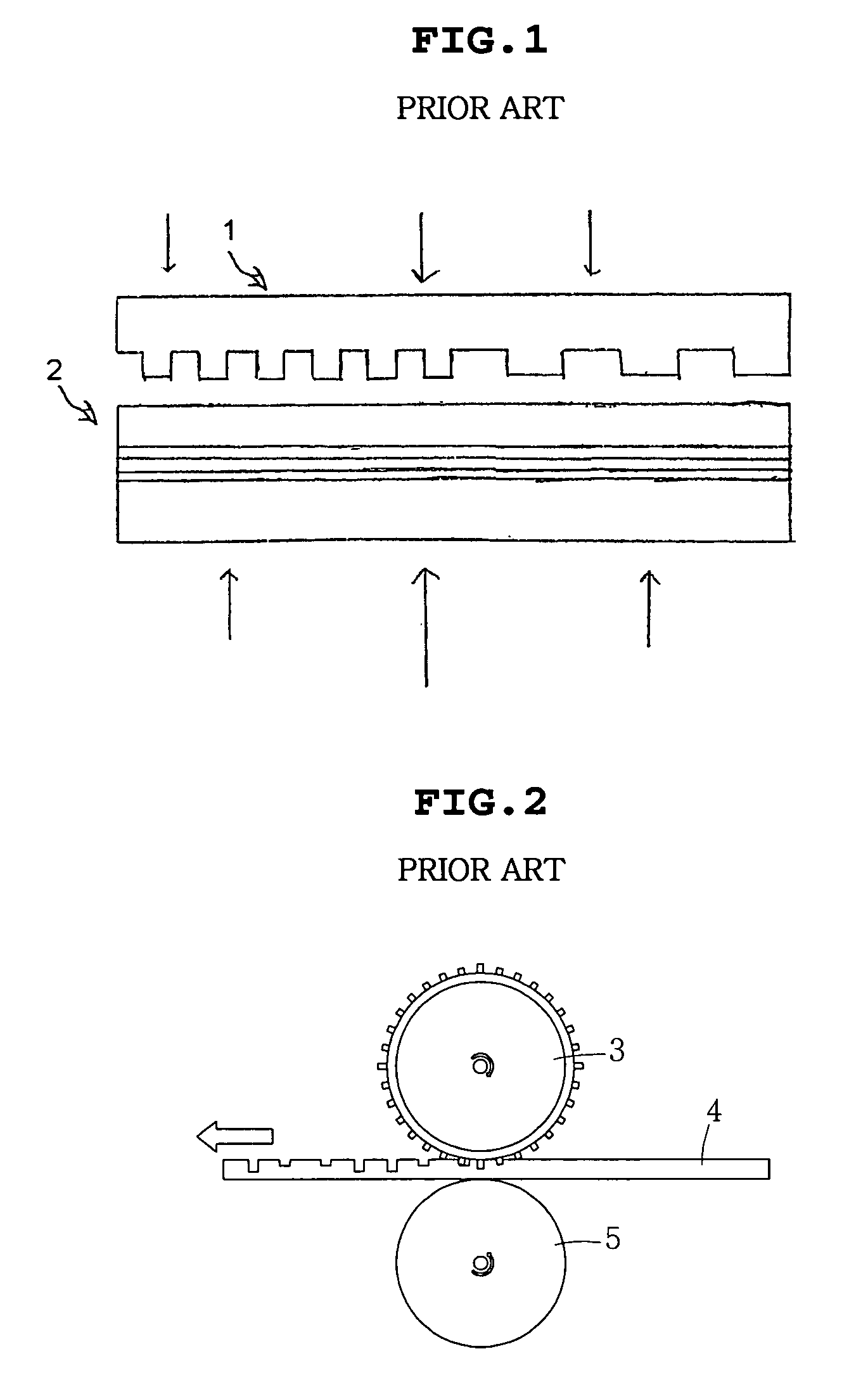

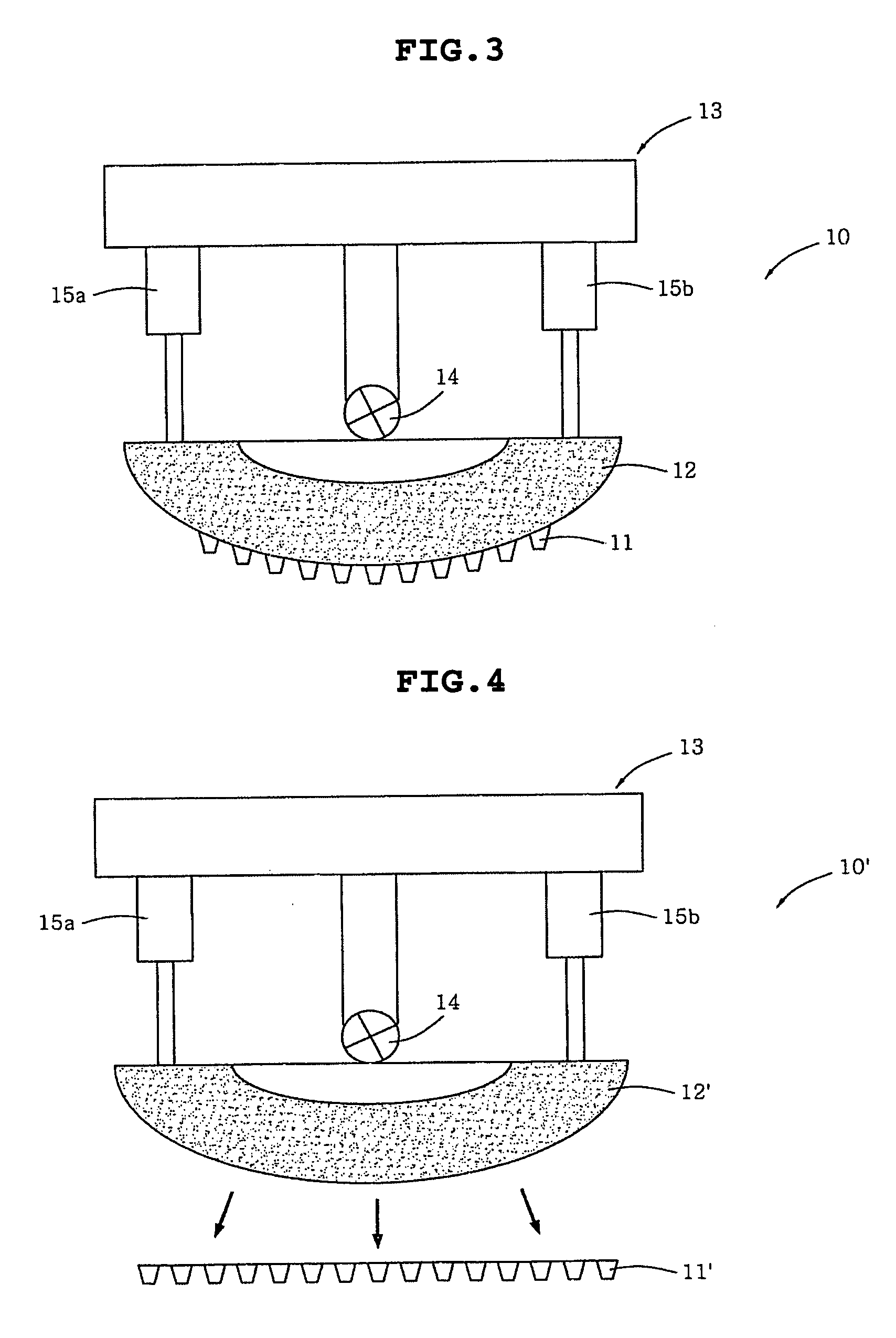

Imprinting apparatus, system and method

The present invention relates to an imprinting apparatus, system and method. Specifically, the present invention relates to an imprinting apparatus, system and method, which can be applied to a large substrate, in which a substrate is aligned, imprinted through sequential pressurization by the imprinting apparatus to form a circuit pattern on the substrate and easily released from the imprinting apparatus.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

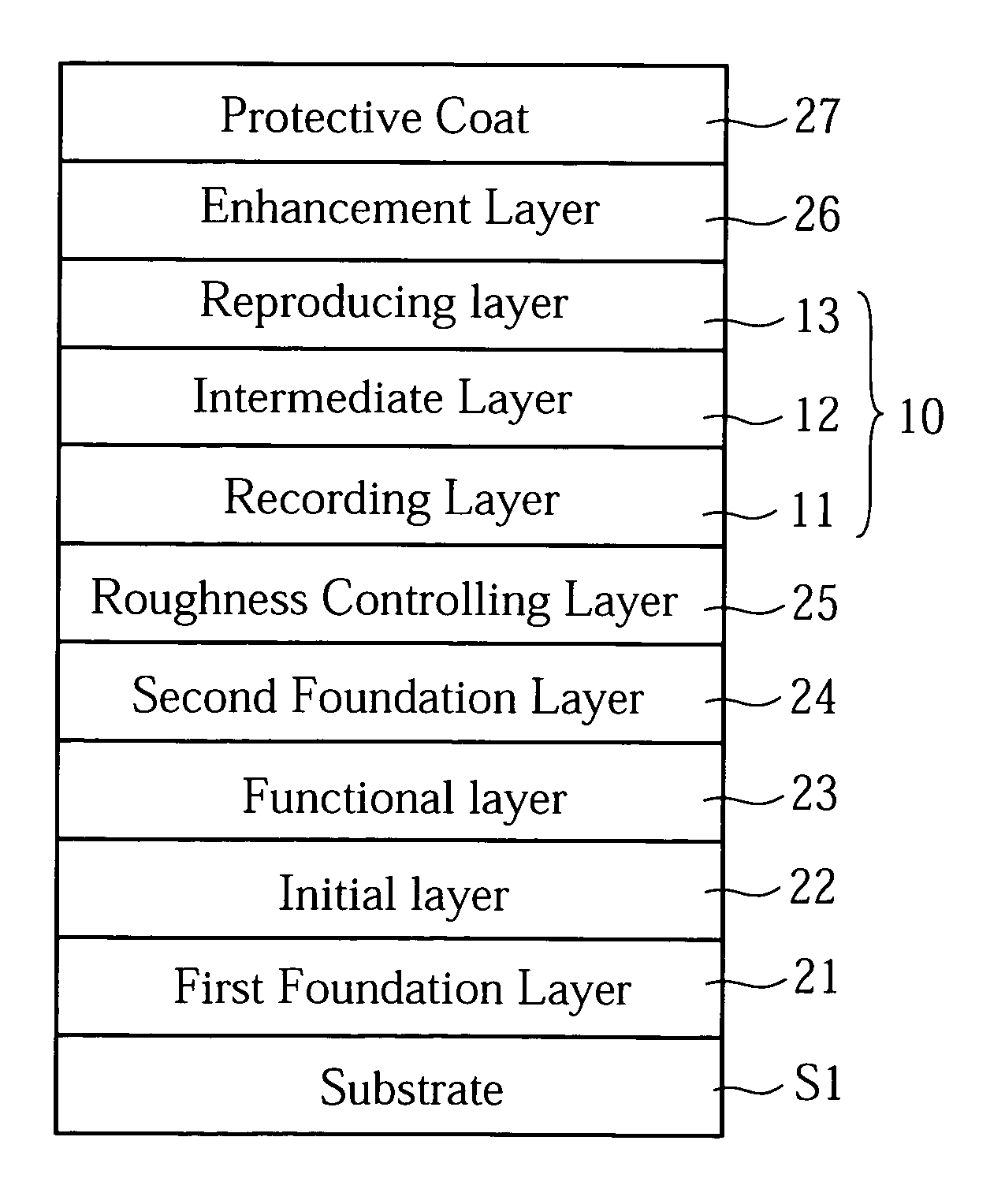

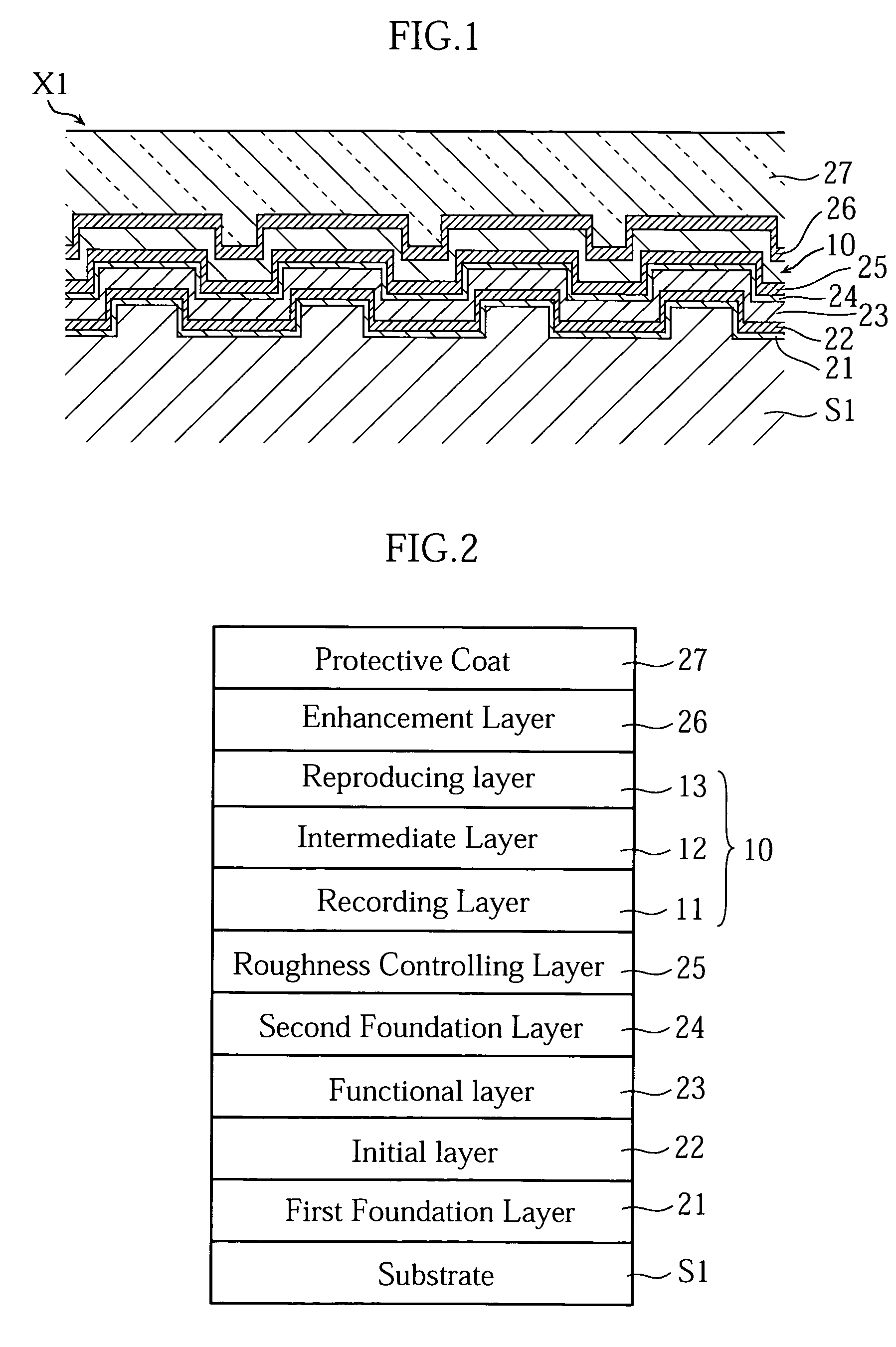

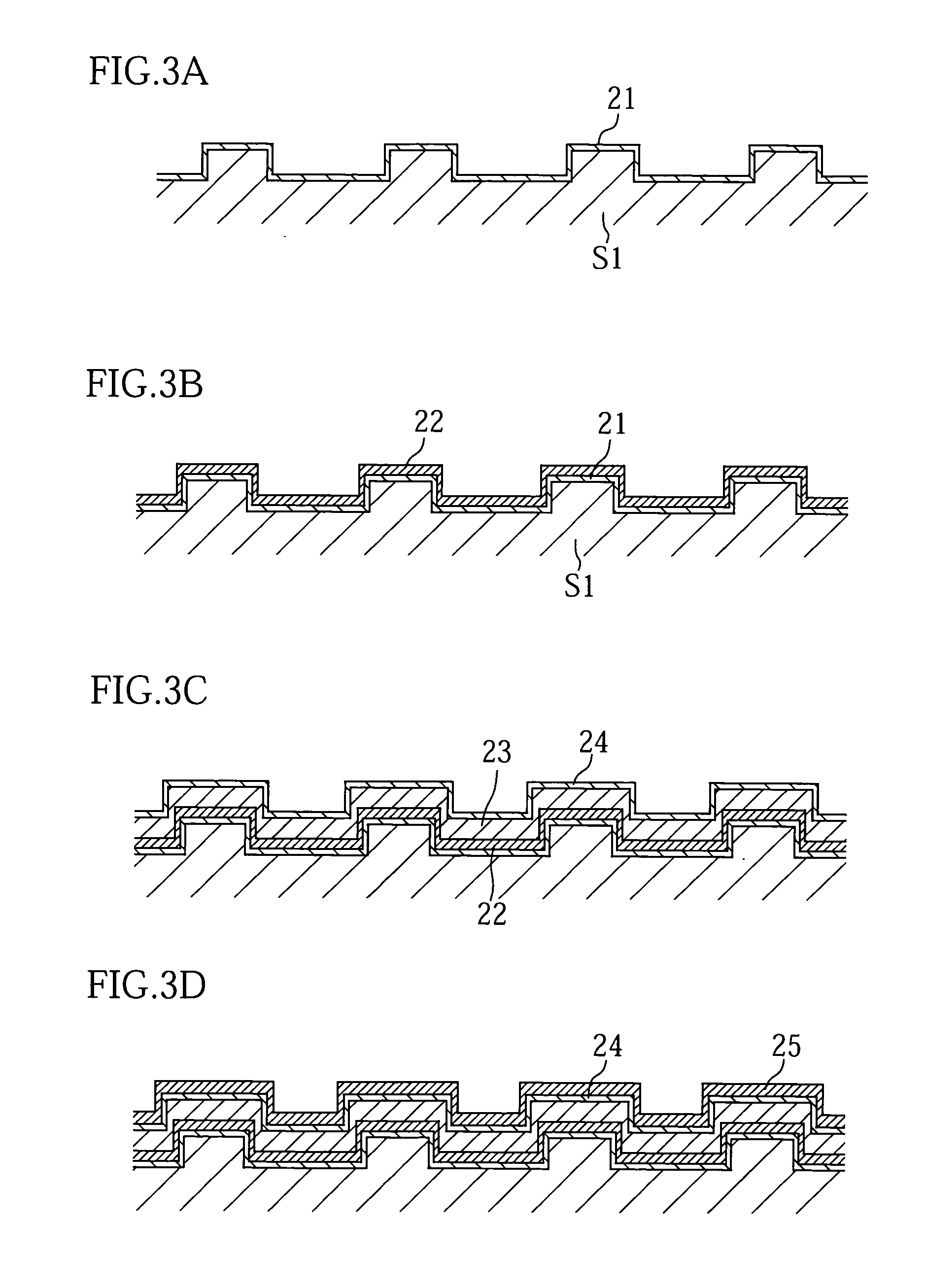

Recording medium and method of making the same

InactiveUS20050068855A1Improve recording densitySmall surface tensionDifferent record carrier formsBase layers for recording layersEngineeringRecording layer

A recording medium includes a substrate, a recording layer provided with perpendicular magnetic anisotropy for recording of information, a foundation layer disposed between the substrate and the recording layer, an initial layer which is greater in surface tension than the foundation layer and held in contact with a recoding-layer-side surface of the foundation layer, and a functional layer held in contact with a recoding-layer-side surface of the initial layer.

Owner:FUJITSU LTD