Patents

Literature

192 results about "Heterojunction field effect transistor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

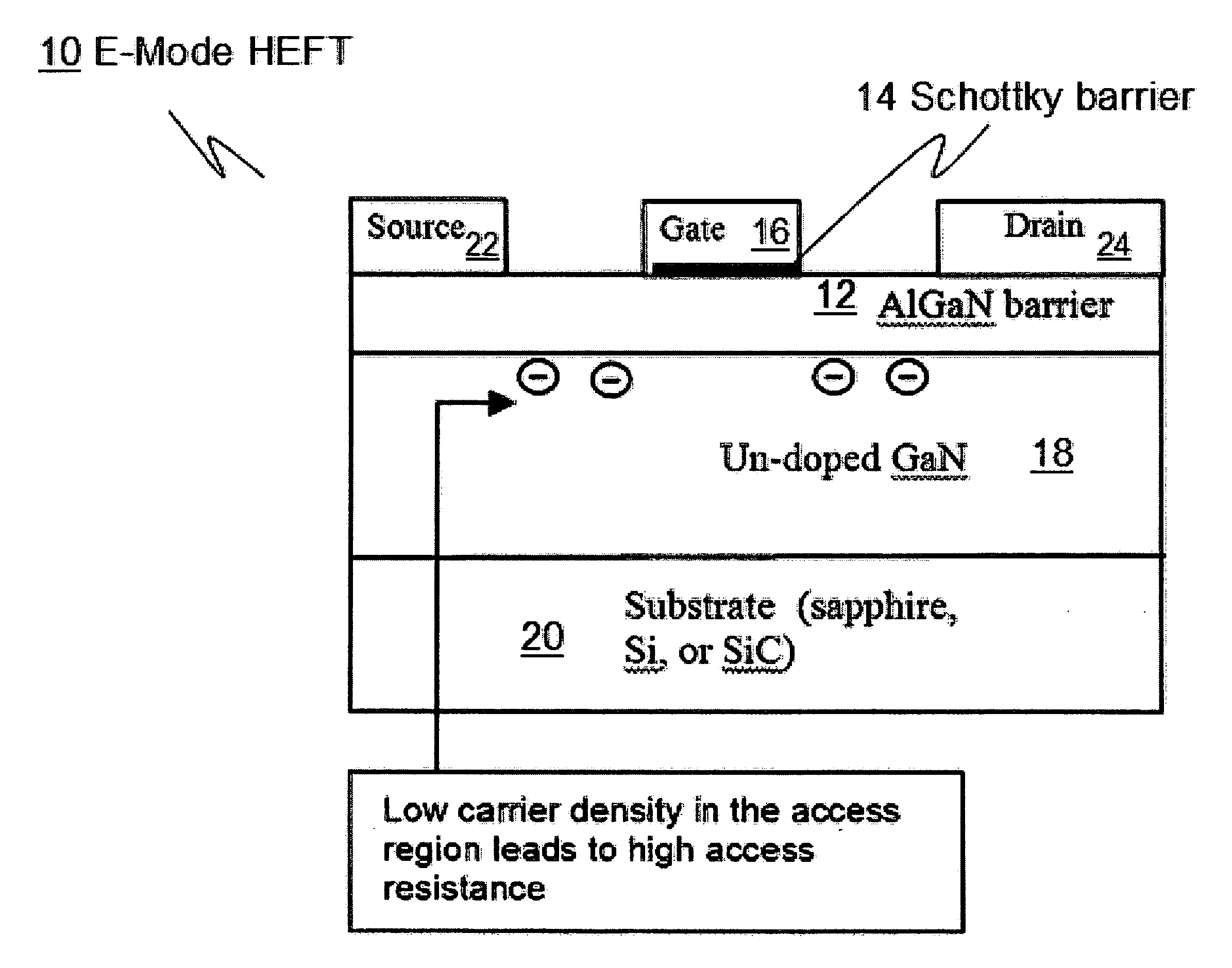

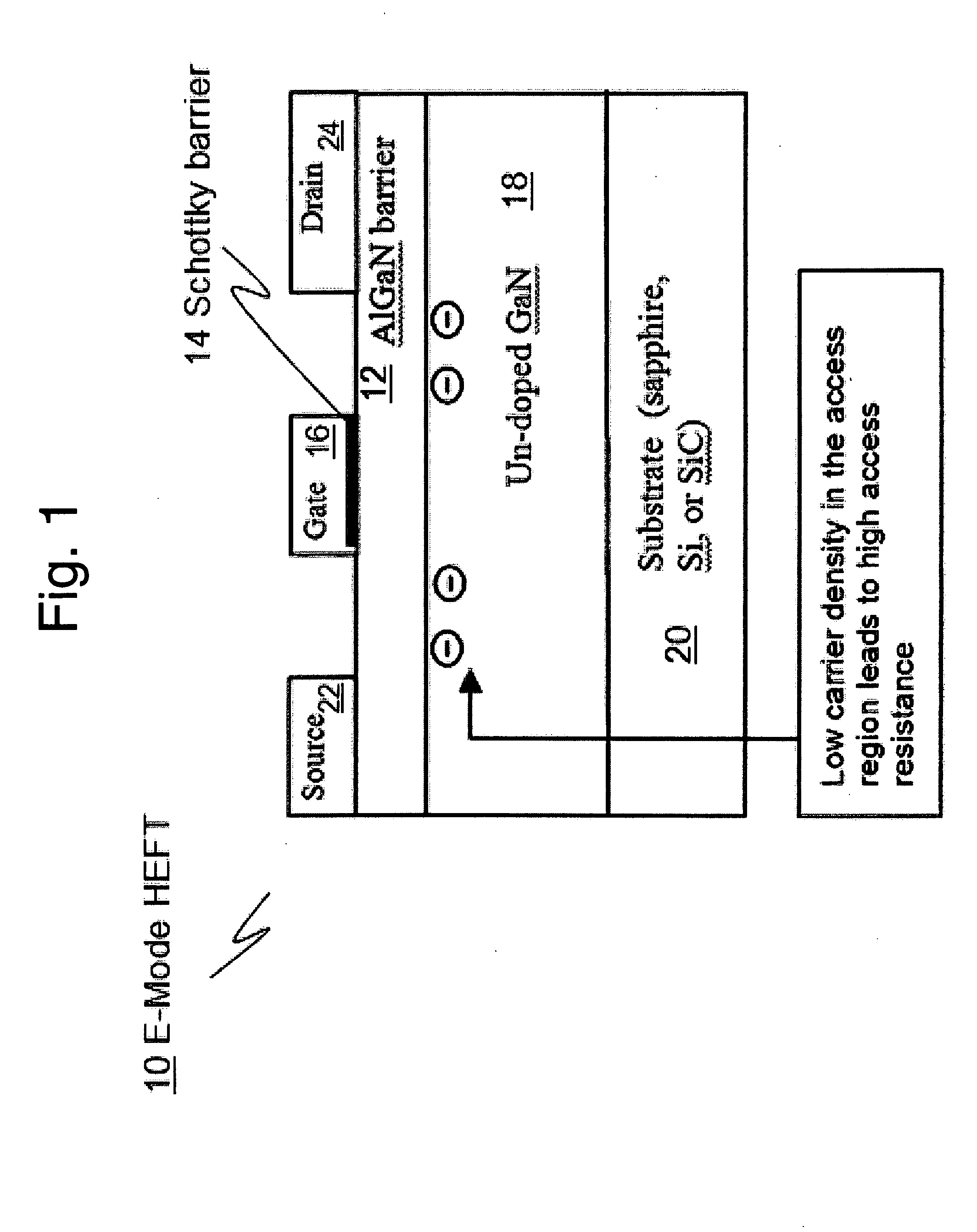

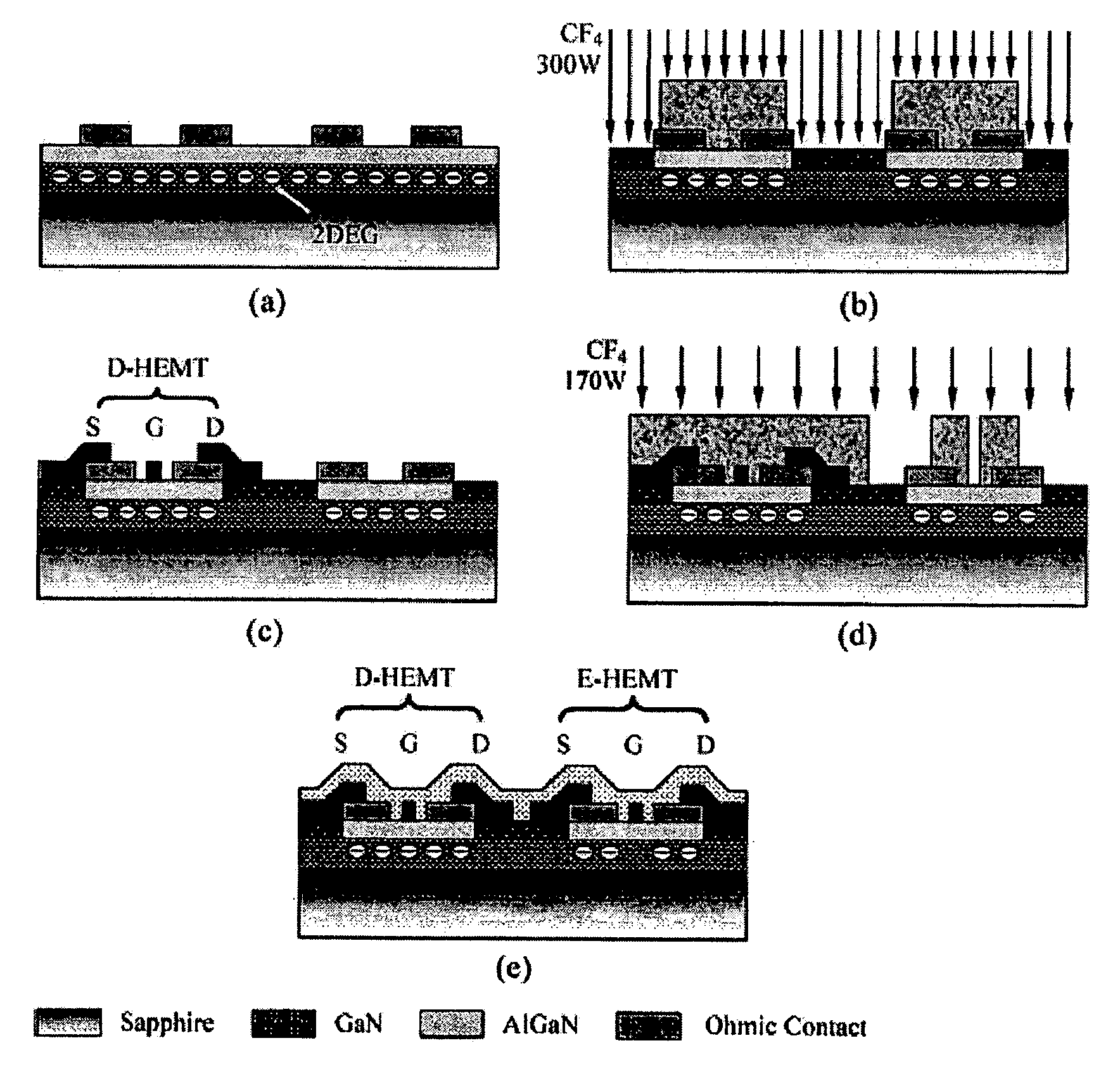

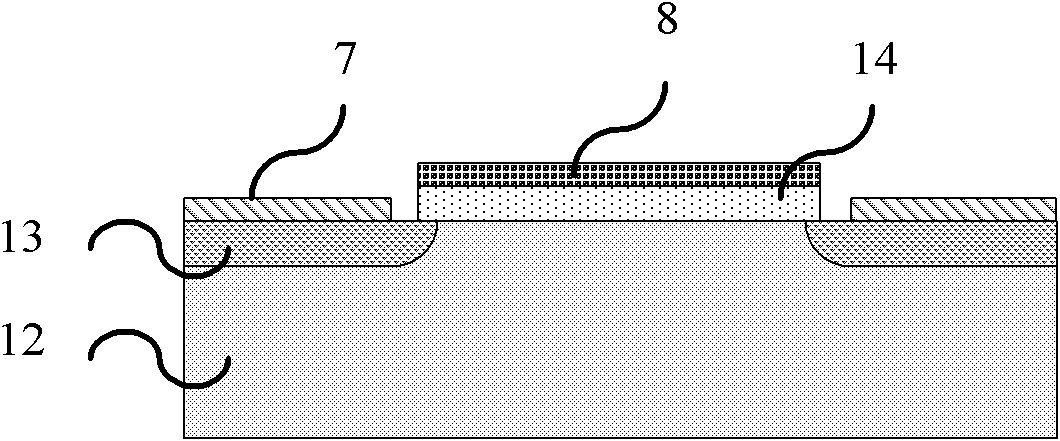

Monolithic Integration of Enhancement- and Depletion-mode AlGaN/GaN HFETs

ActiveUS20070228416A1Wide bandgapHigh breakdown fieldTransistorSolid-state devicesHeterojunctionEtching

A method for and devices utilizing monolithic integration of enhancement-mode and depletion-mode AlGaN / GaN heterojunction field-effect transistors (HFETs) is disclosed. Source and drain ohmic contacts of HFETs are first defined. Gate electrodes of the depletion-mode HFETs are then defined. Gate electrodes of the enhancement-mode HFETs are then defined using fluoride-based plasma treatment and high temperature post-gate annealing of the sample. Device isolation is achieved by either mesa etching or fluoride-based plasma treatment. This method provides a complete planar process for GaN-based integrated circuits favored in high-density and high-speed applications.

Owner:THE HONG KONG UNIV OF SCI & TECH

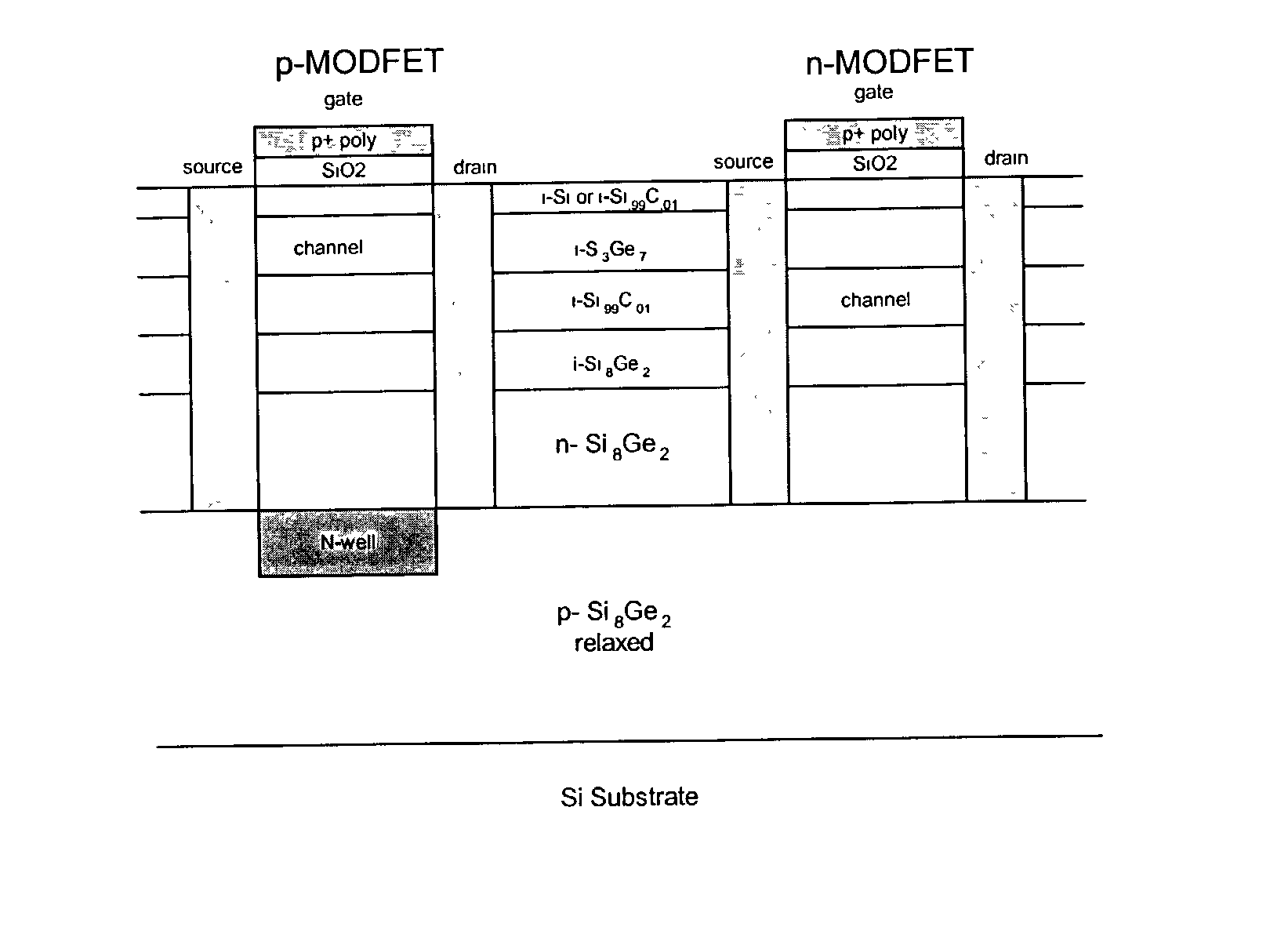

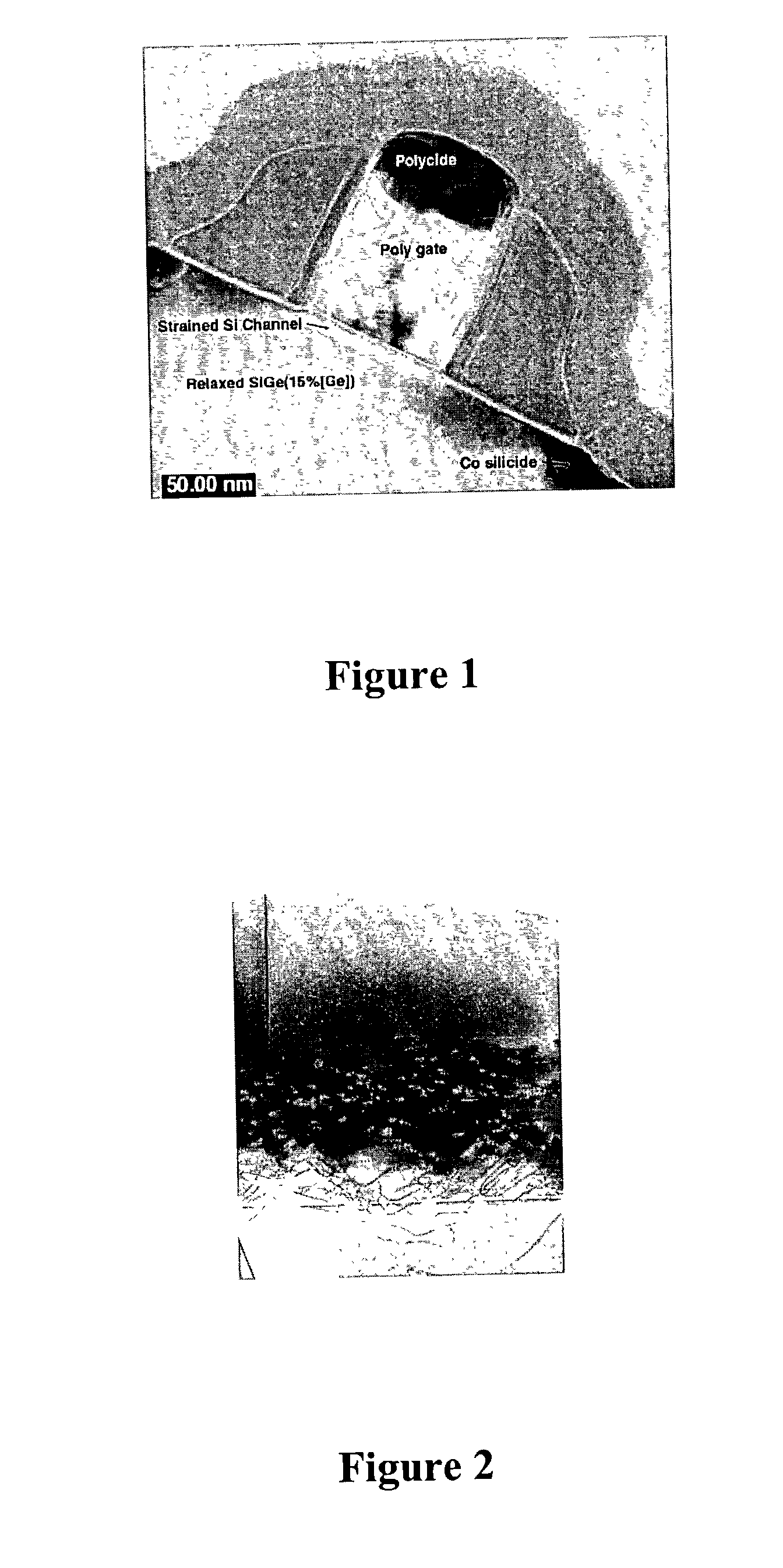

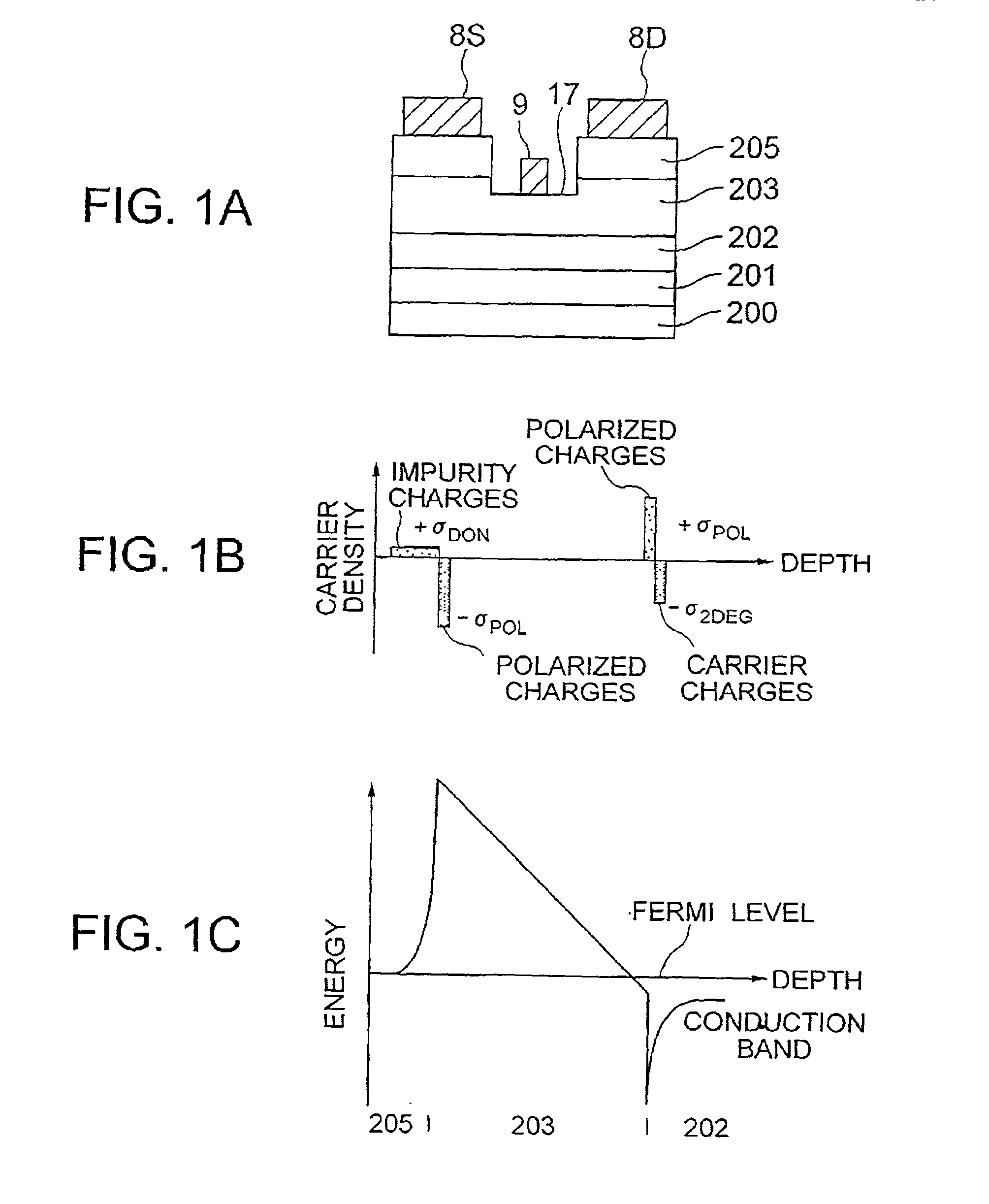

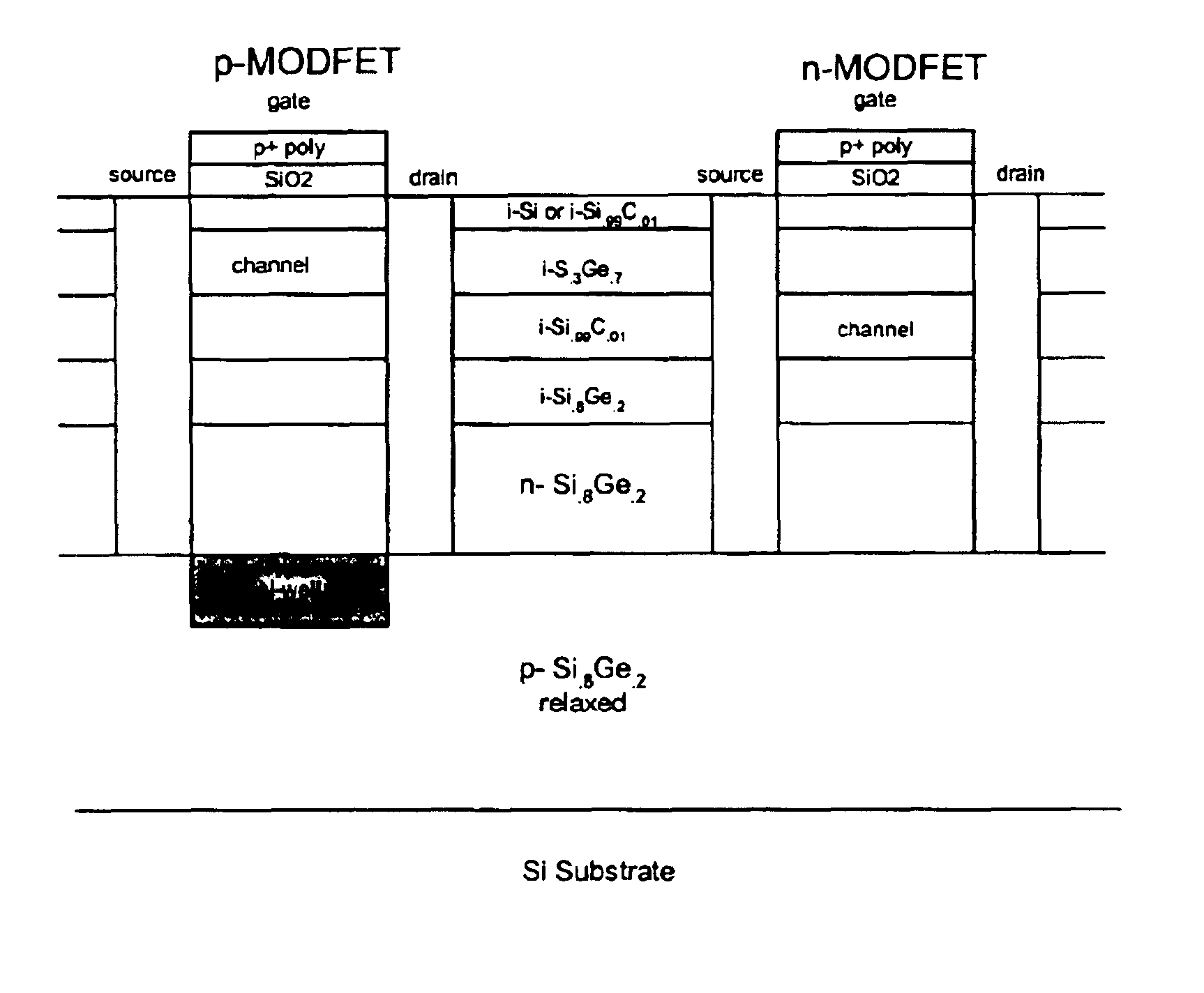

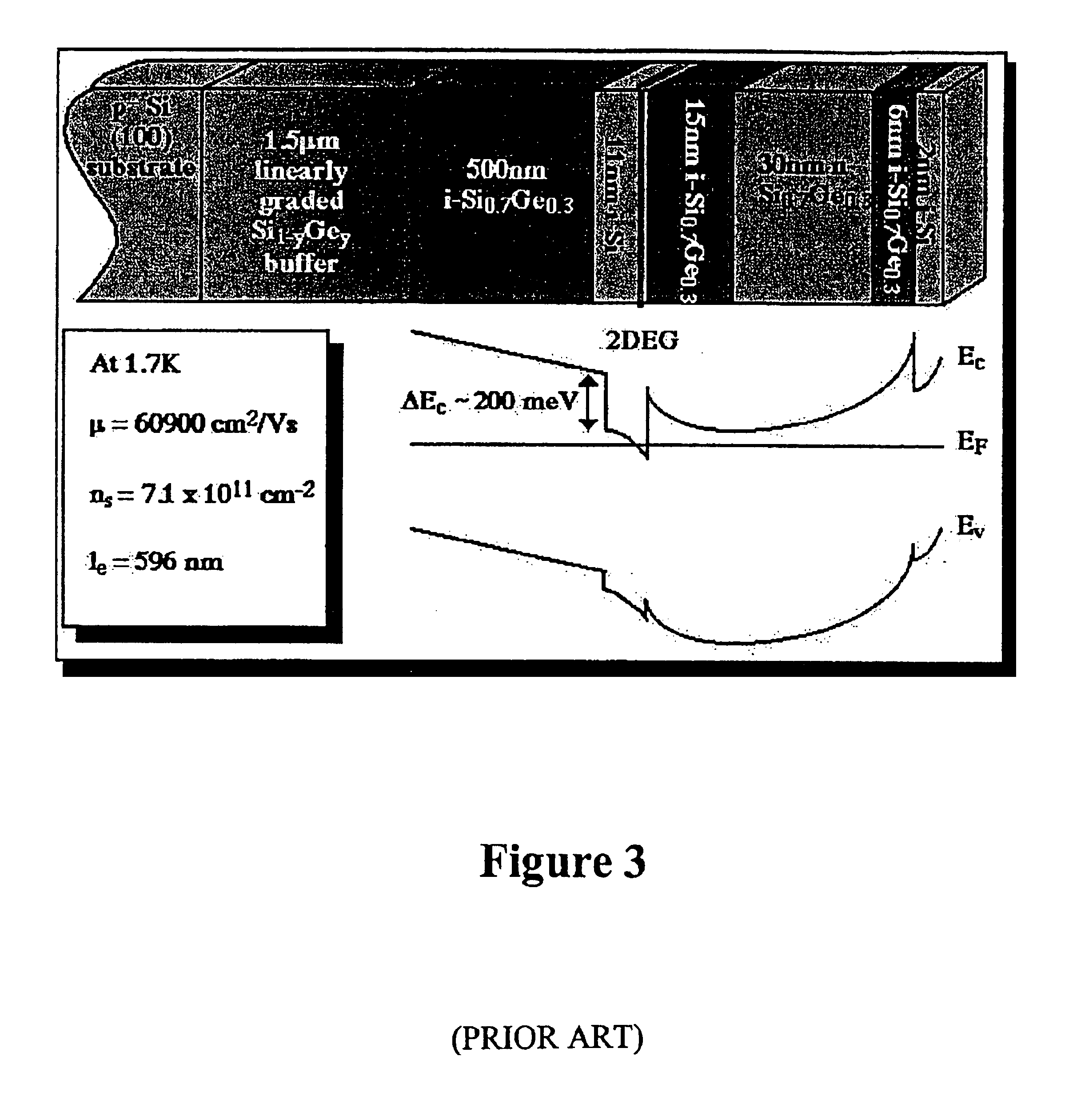

Heterojunction field effect transistors using silicon-germanium and silicon-carbon alloys

InactiveUS20040007715A1Without of performanceWithout strainTransistorSolid-state devicesHeterojunctionSemiconductor

Semiconductor devices, e.g., heterojunction field effect transistors, fabricated with silicon-germnanium buffer layer and silicon-carbon channel layer structures. The invention provides a method of reducing threading defect density via reducing germanium content in a SiGe relaxed buffer layer on which a strained silicon channel layer is formed, by forming the strained silicon channel layer of a silicon-carbon alloy, e.g., containing less than about 1.5 atomic % C substitutionally incorporated in the Si lattice of the alloy.

Owner:INTERNATIONAL RECTIFIER COEP

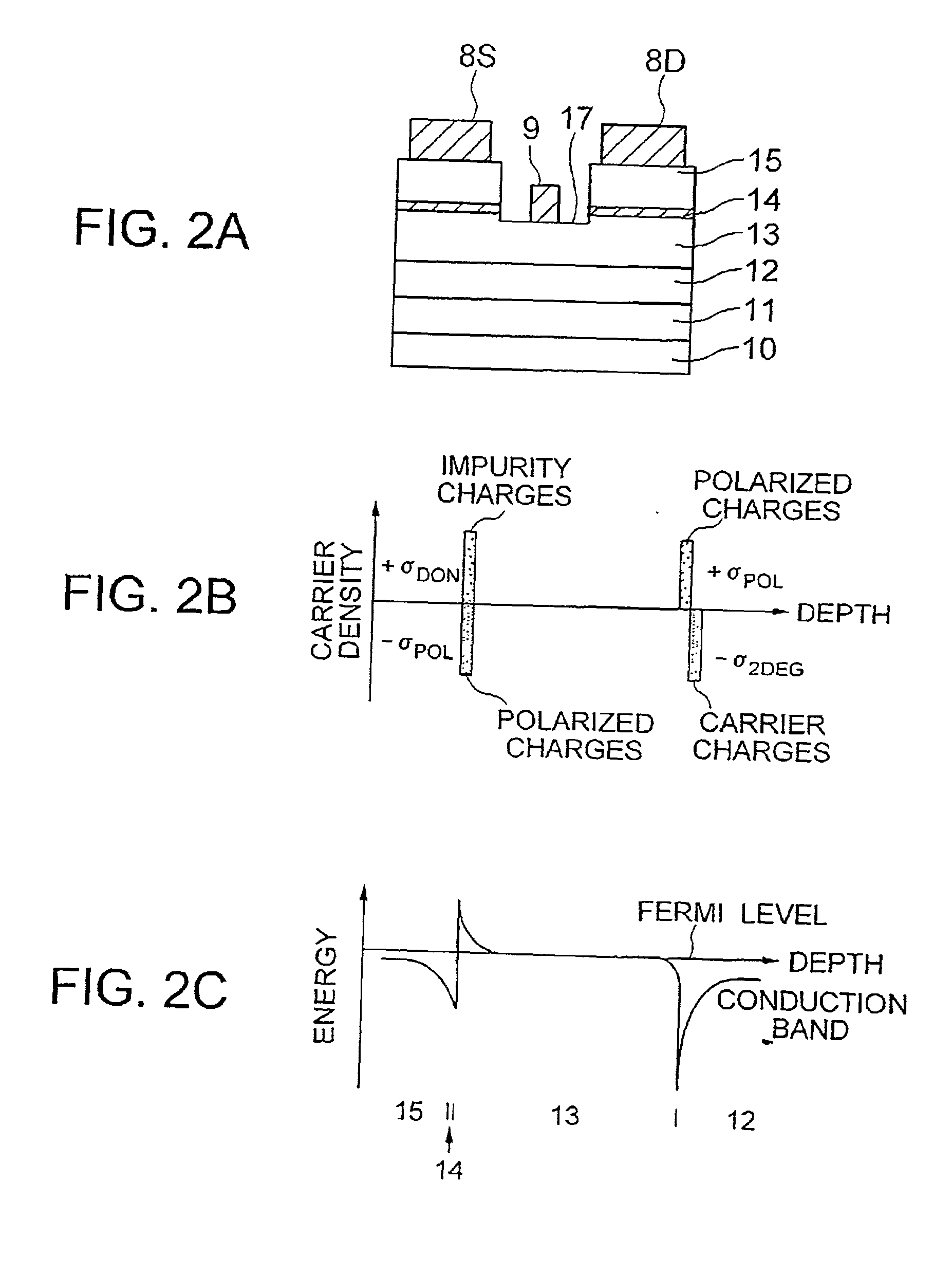

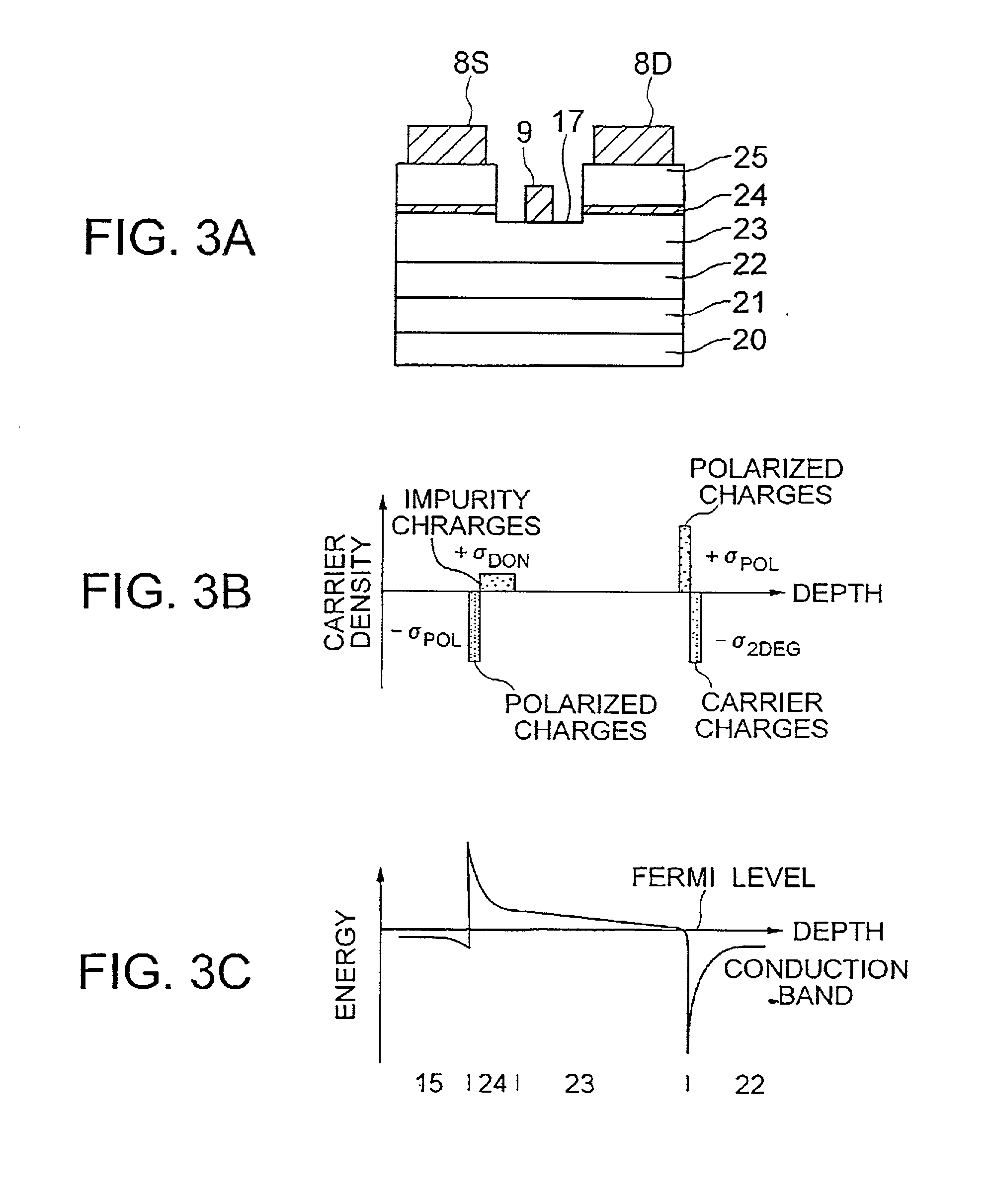

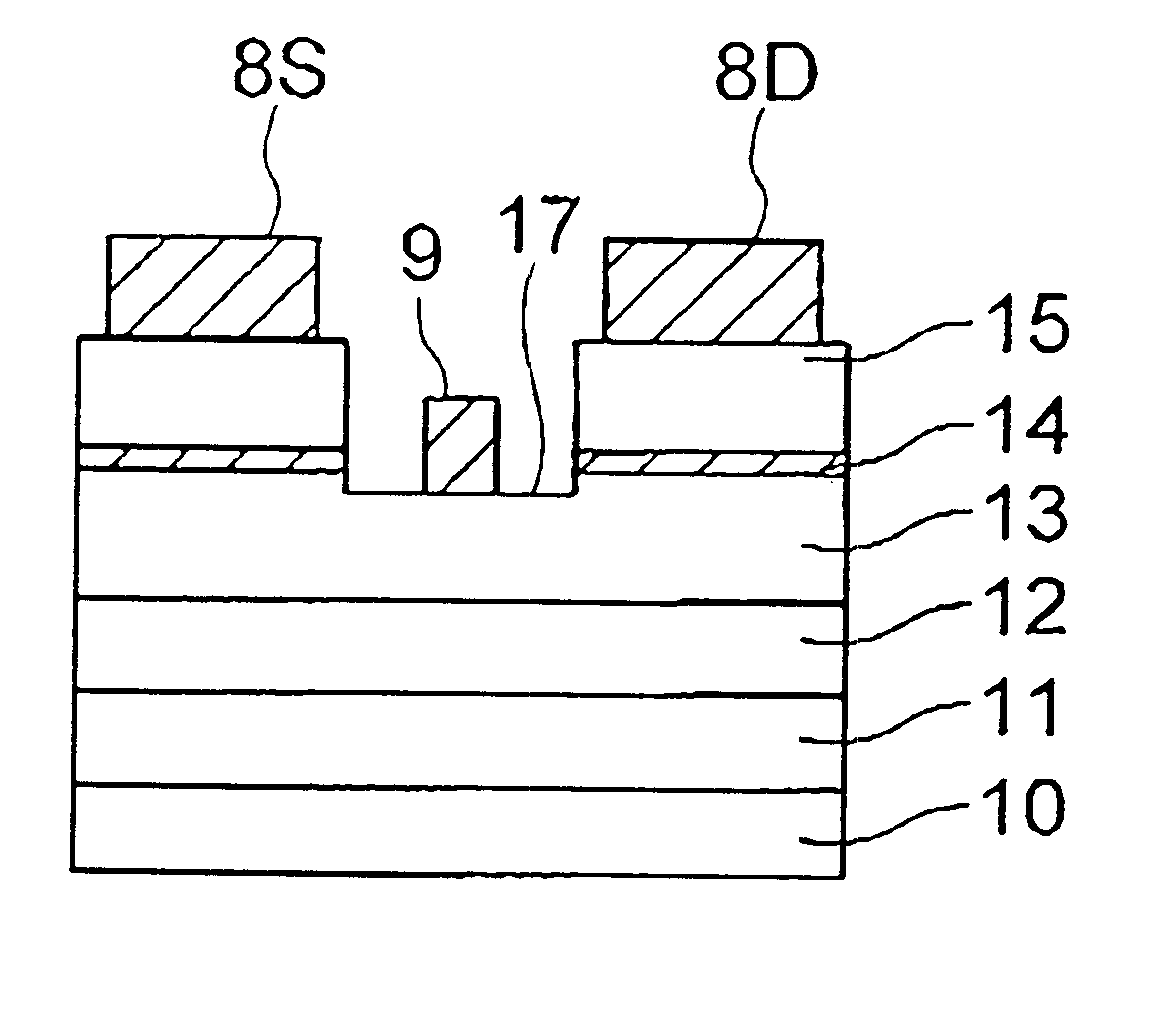

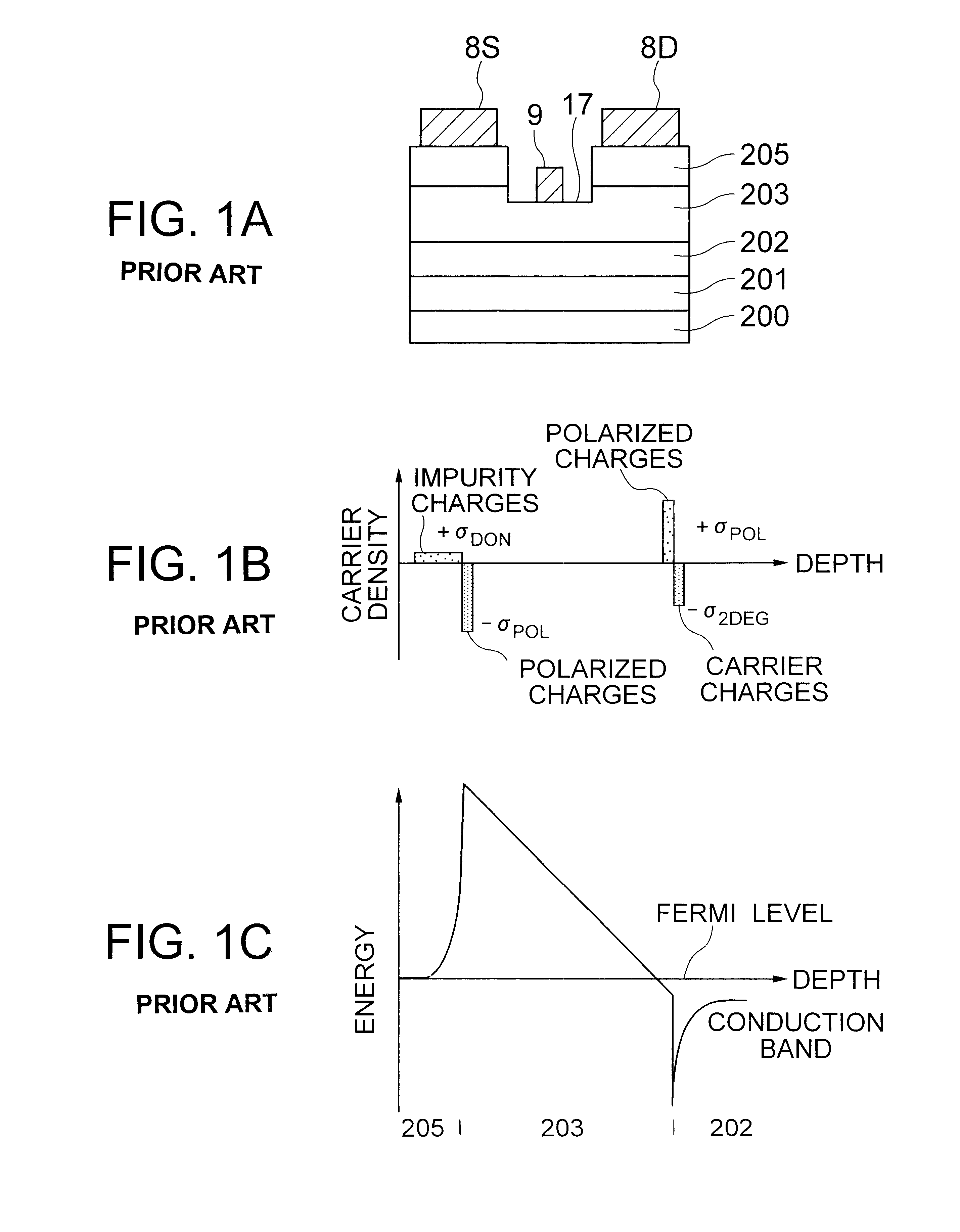

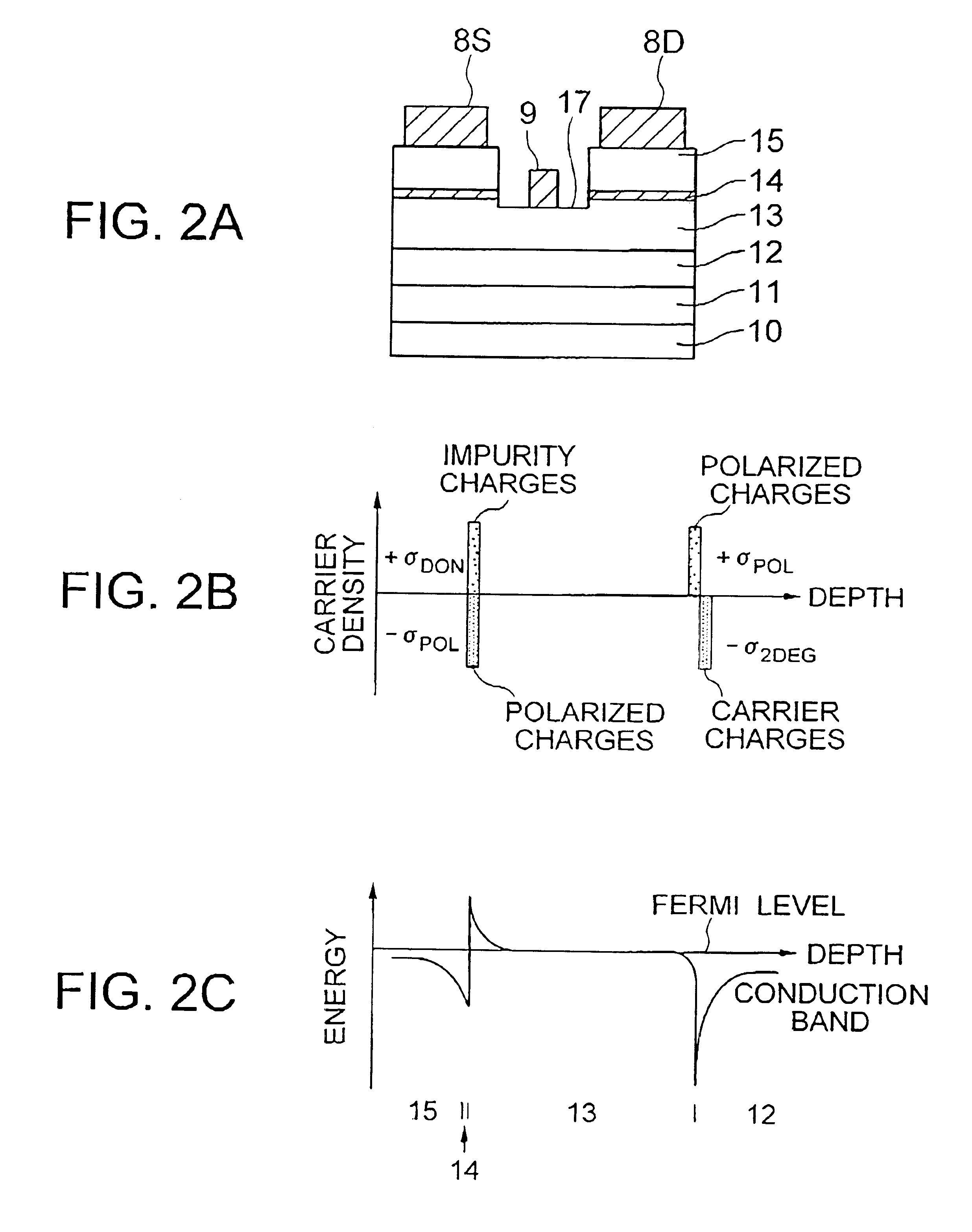

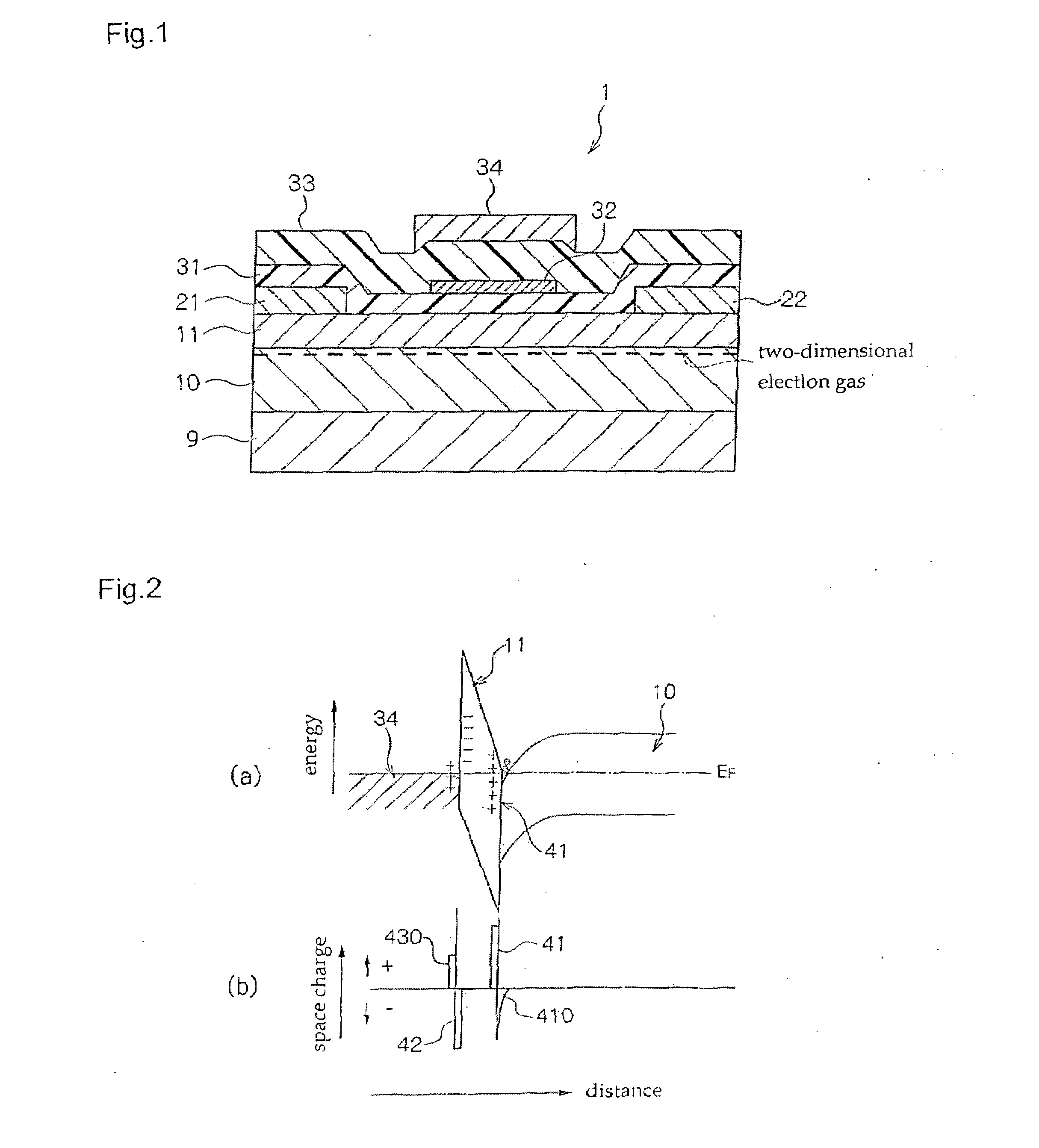

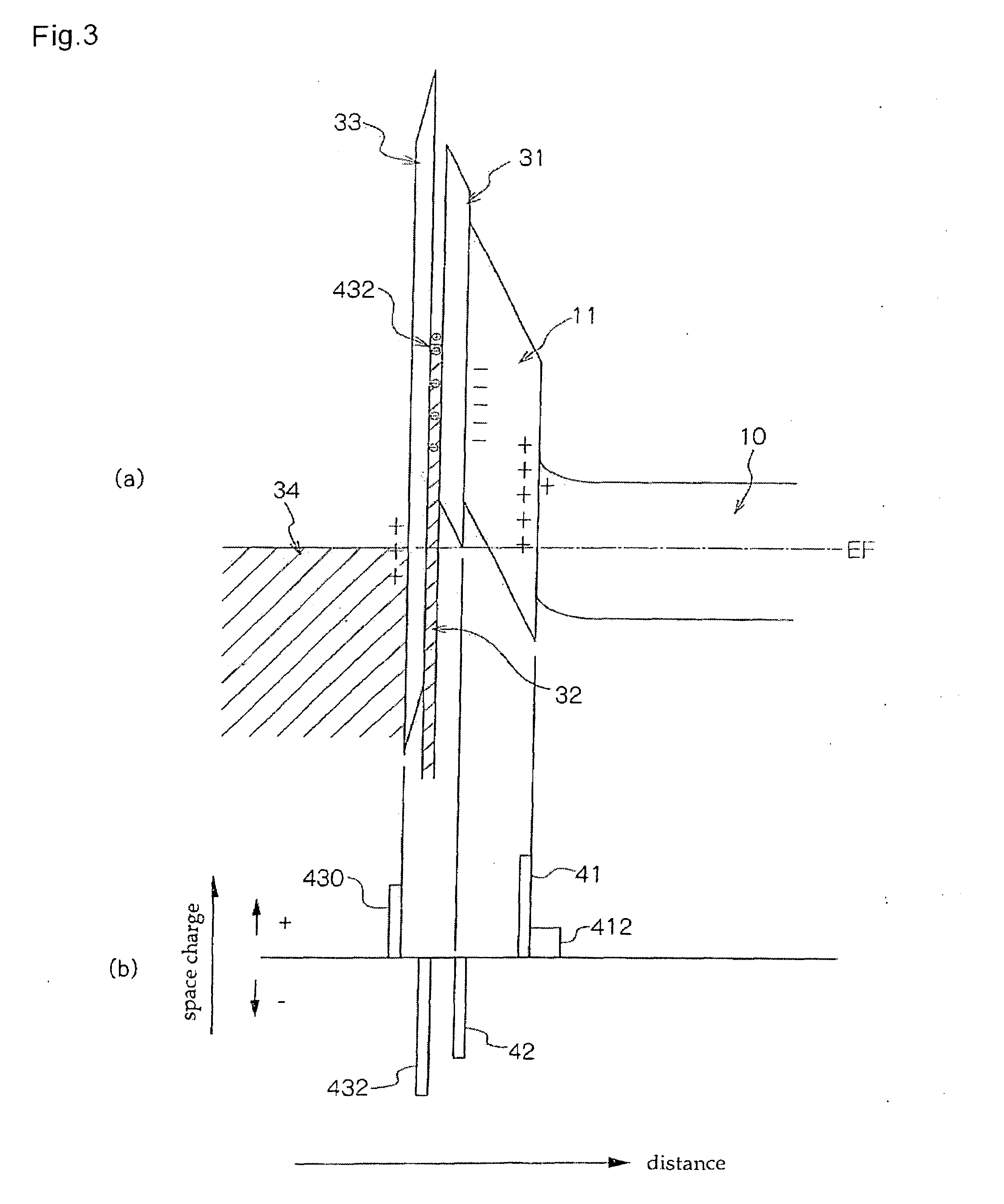

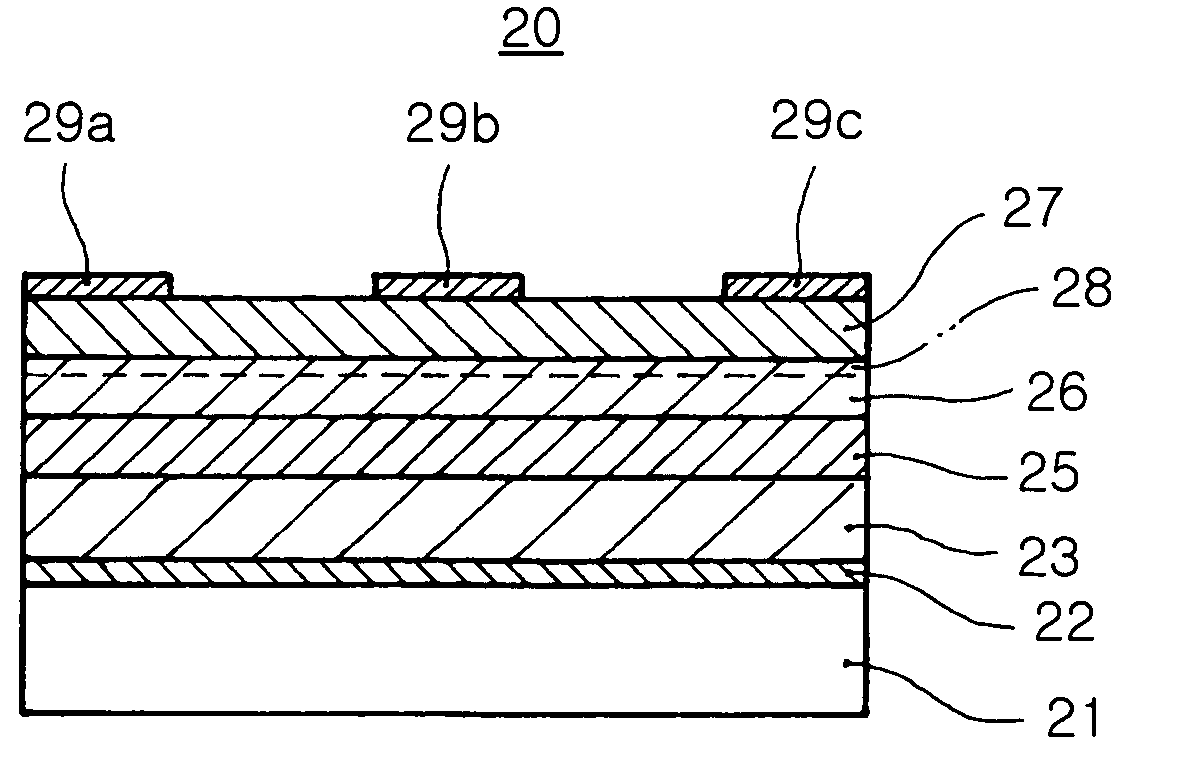

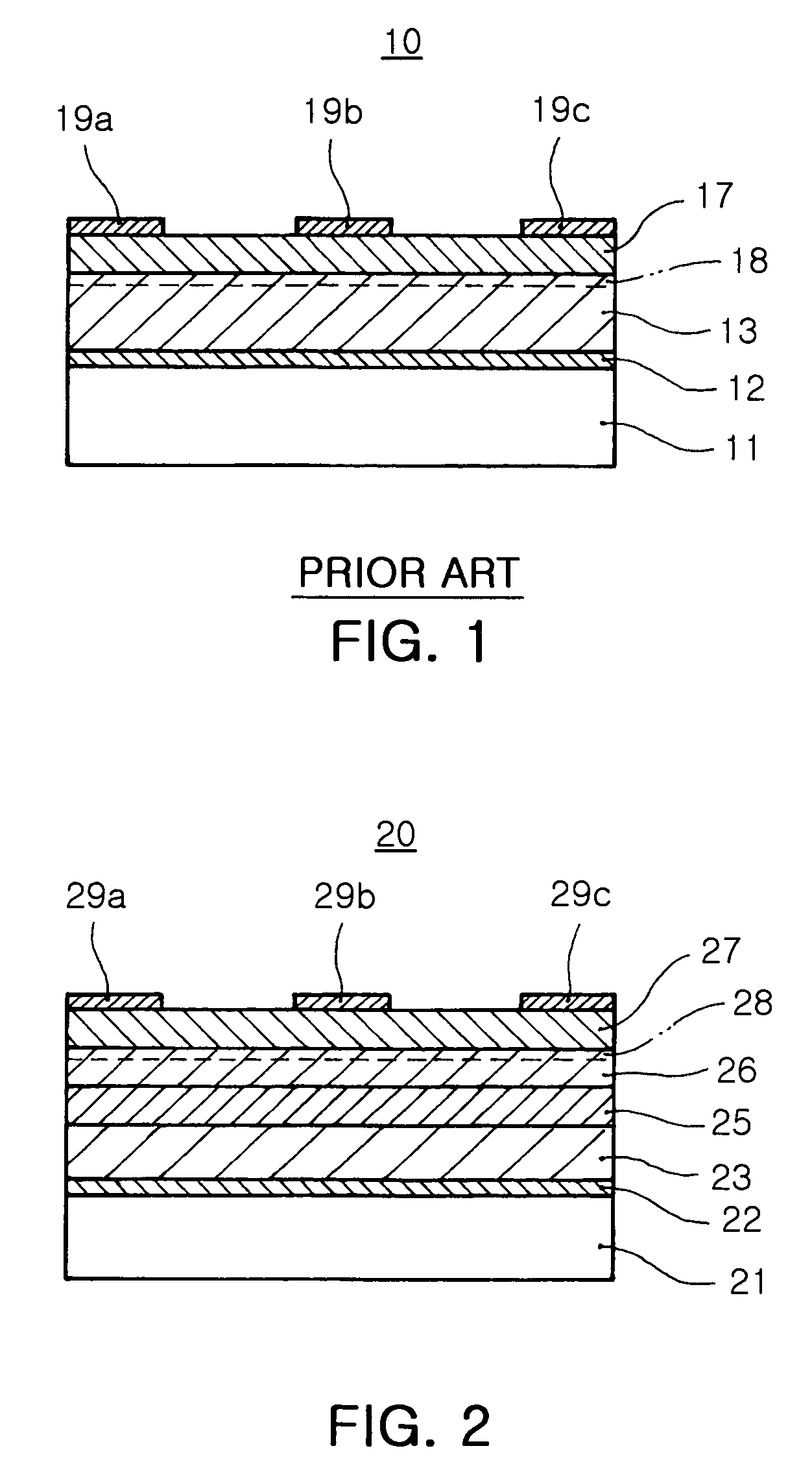

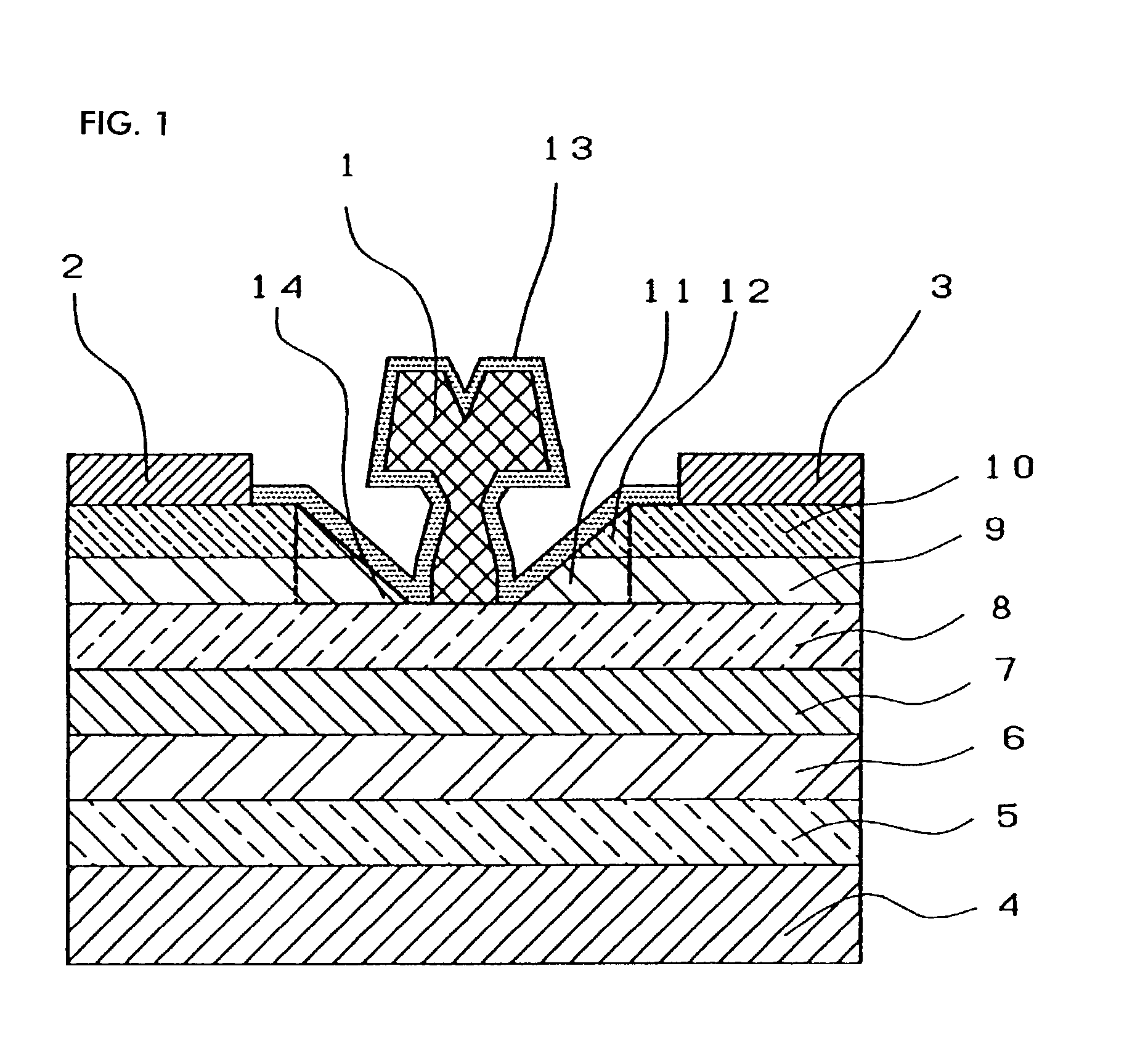

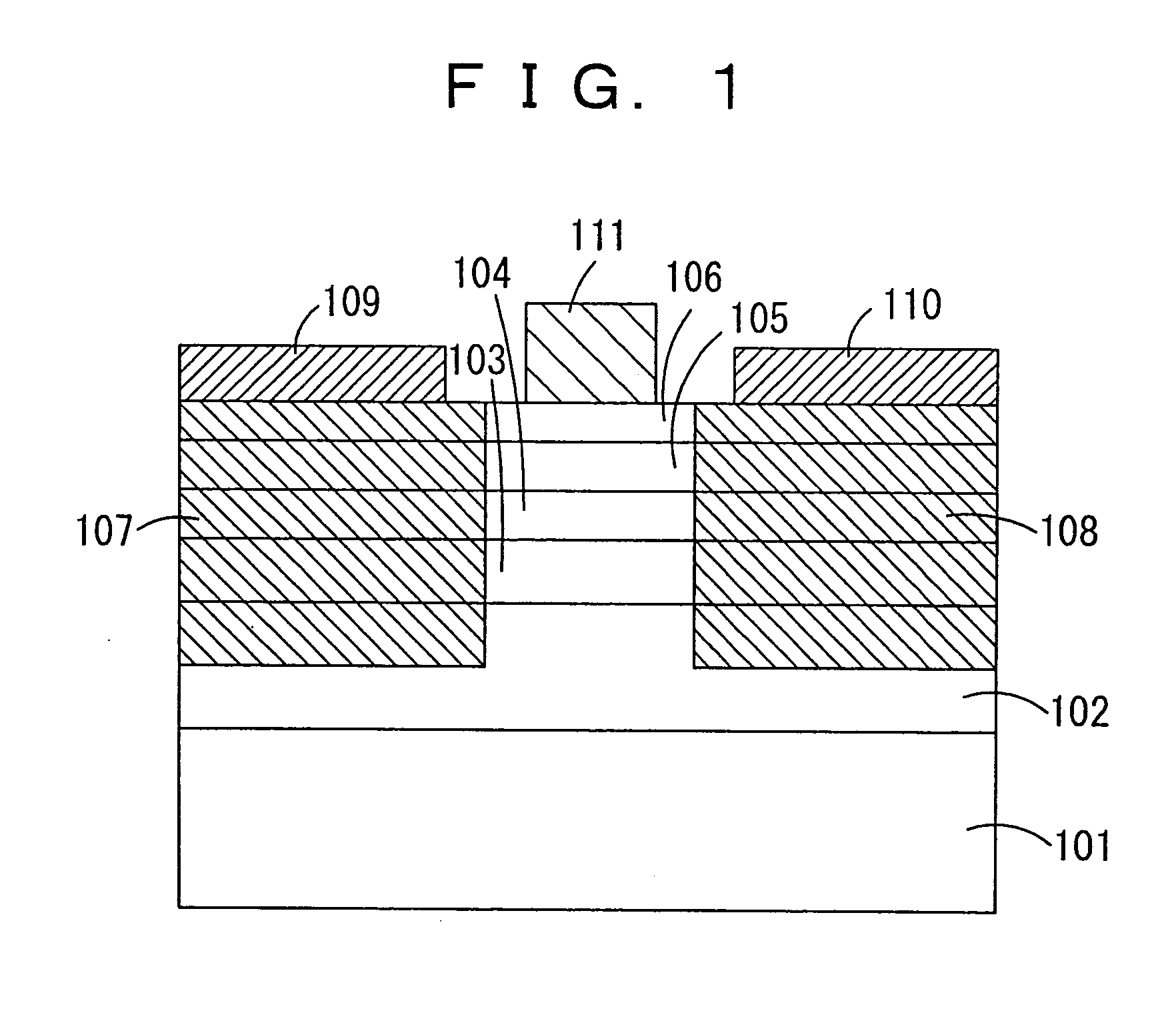

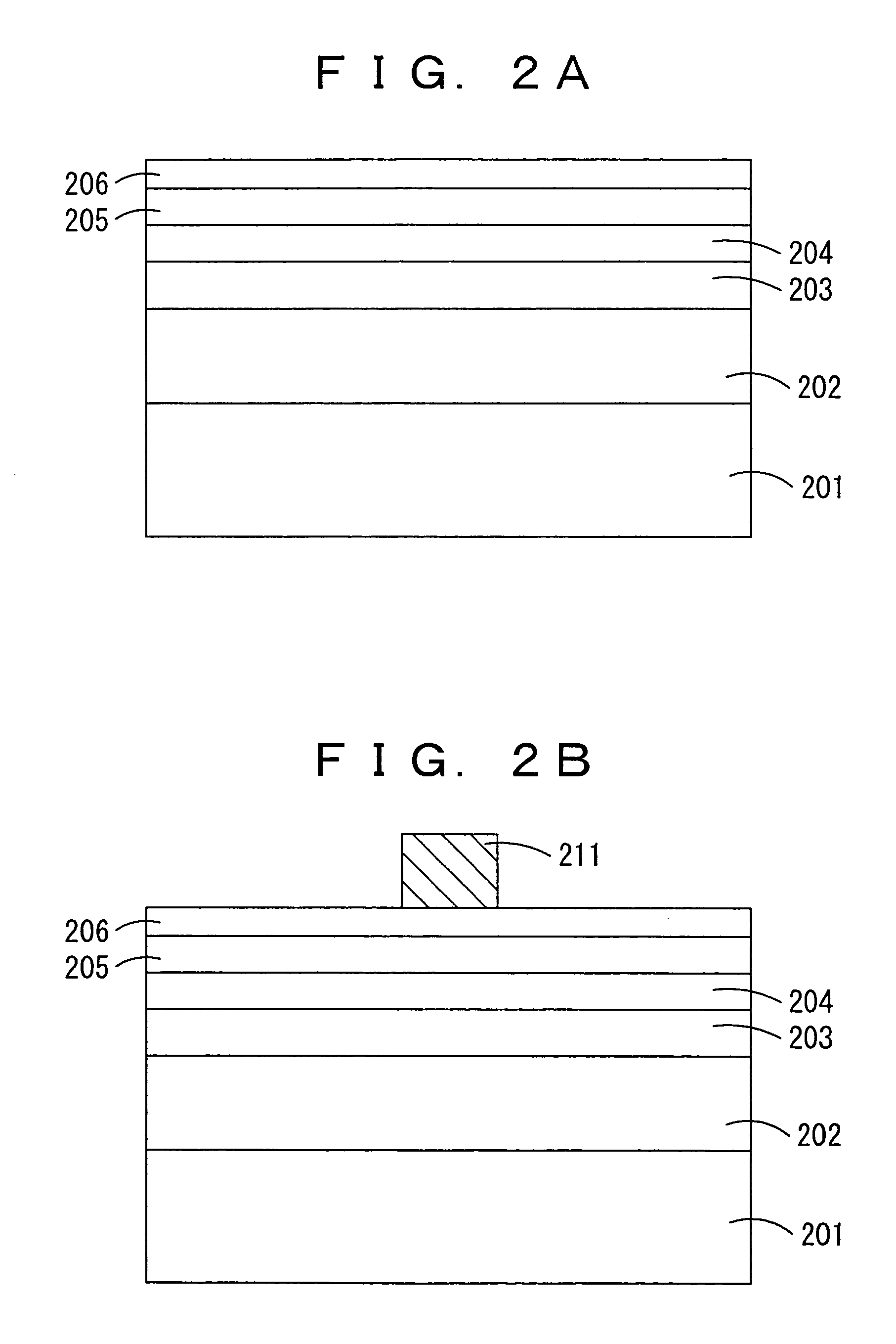

Hetero-junction field effect transistor having an intermediate layer

InactiveUS20010040247A1Solid-state devicesSemiconductor/solid-state device manufacturingImpurityElectron

A hetero-junction FET has an intermediate layer including n-type-impurity doped layer between an electron supply layer and an n-type cap layer. The intermediate layer cancels the polarized negative charge generated between the electron supply layer and the n-type cap layer by ionized positive charge, thereby reducing the barrier against the electrons and source / drain resistance.

Owner:RENESAS ELECTRONICS CORP

Hetero-junction field effect transistor having an intermediate layer

InactiveUS6552373B2Solid-state devicesSemiconductor/solid-state device manufacturingElectronImpurity

A hetero-junction FET has an intermediate layer including n-type-impurity doped layer between an electron supply layer and an n-type cap layer. The intermediate layer cancels the polarized negative charge generated between the electron supply layer and the n-type cap layer by ionized positive charge, thereby reducing the barrier against the electrons and source / drain resistance.

Owner:RENESAS ELECTRONICS CORP

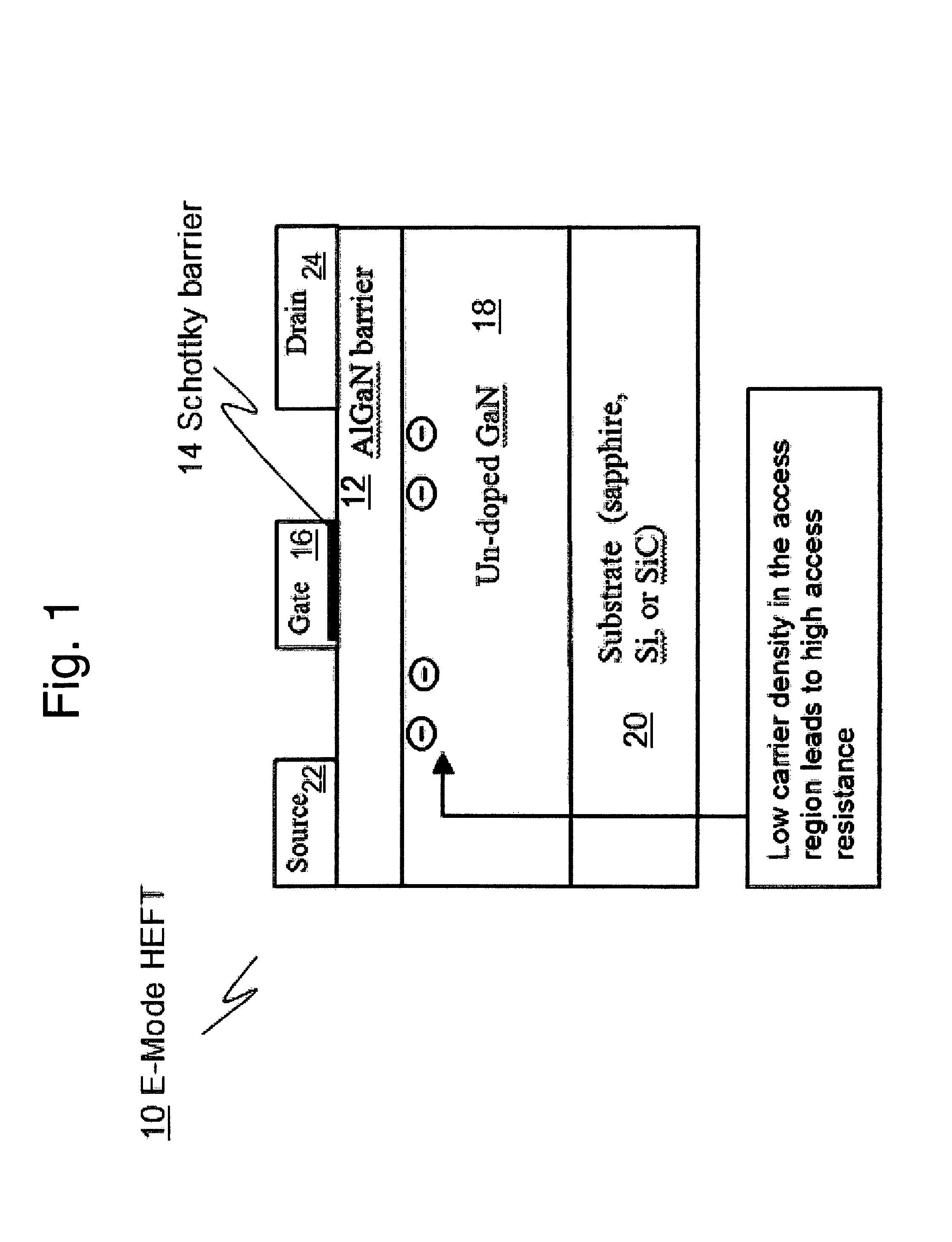

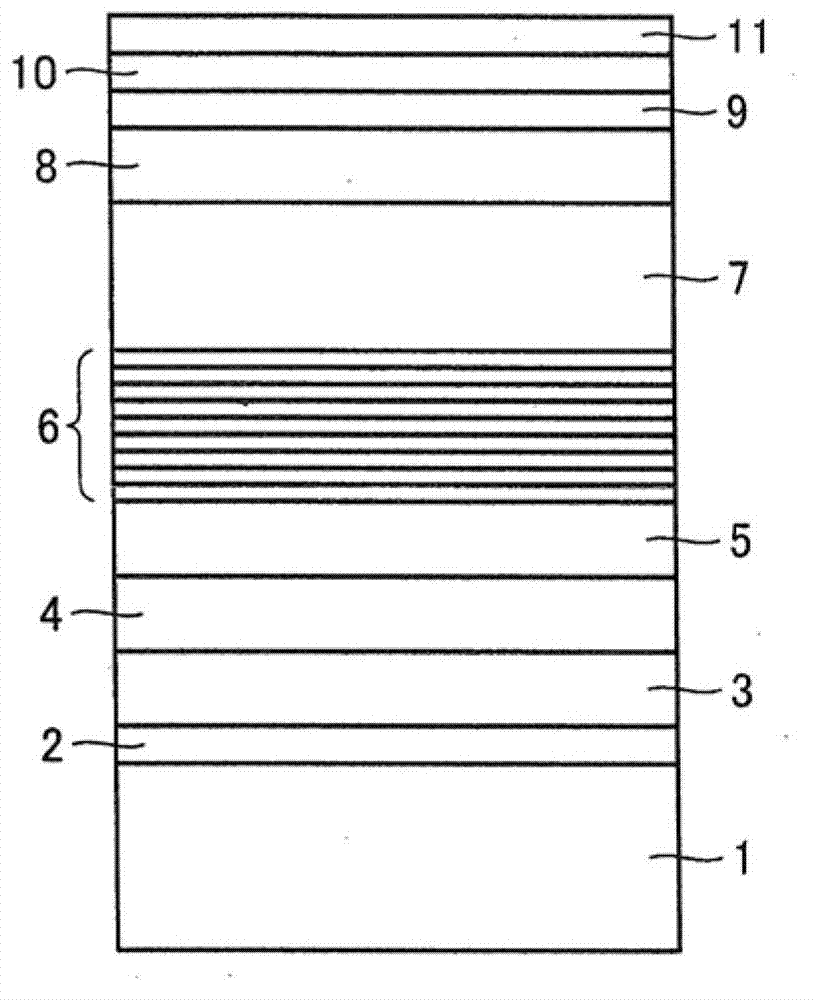

Semiconductor electronic devices and methods

InactiveUS20050006639A1Semiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionEngineering

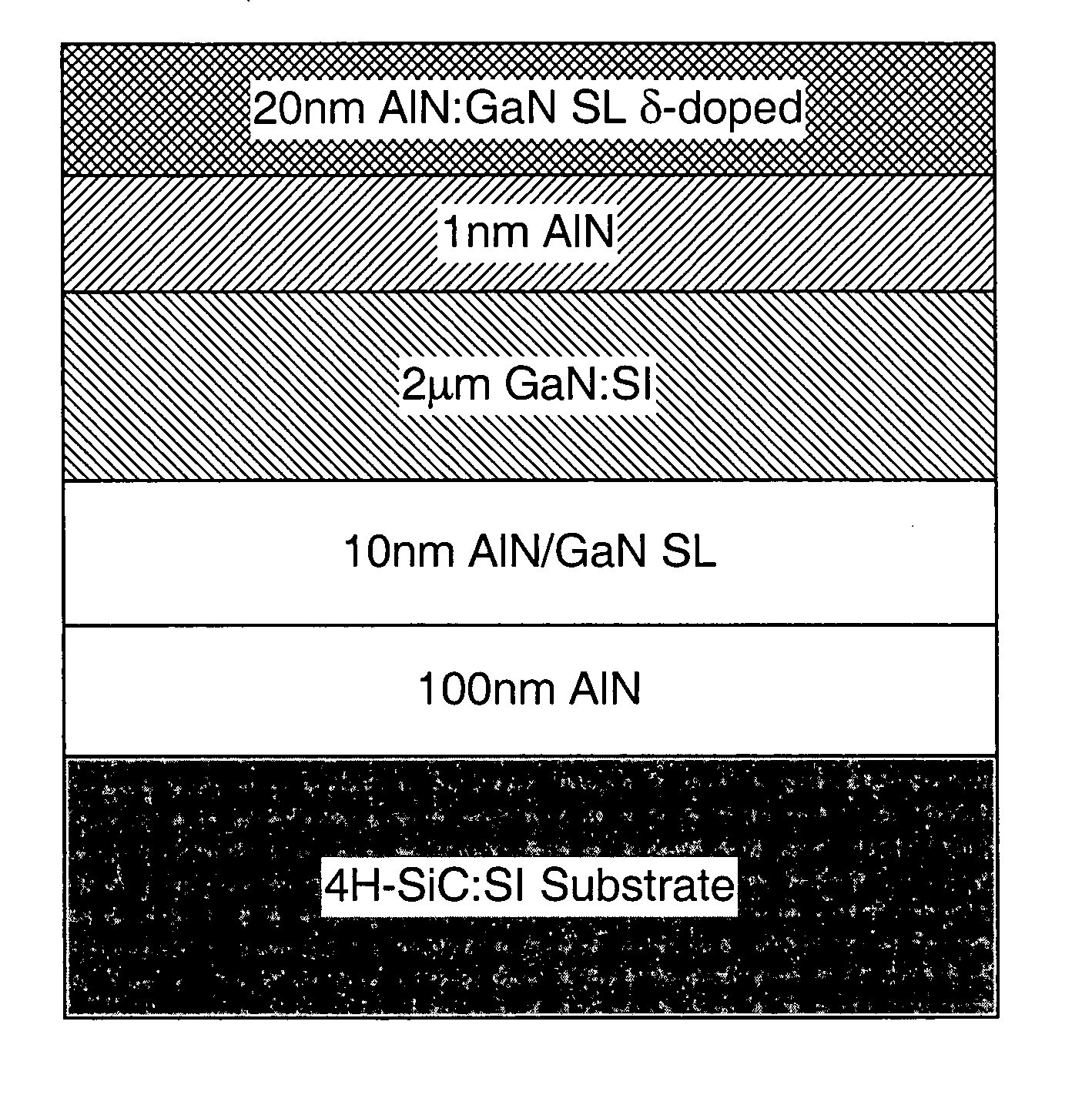

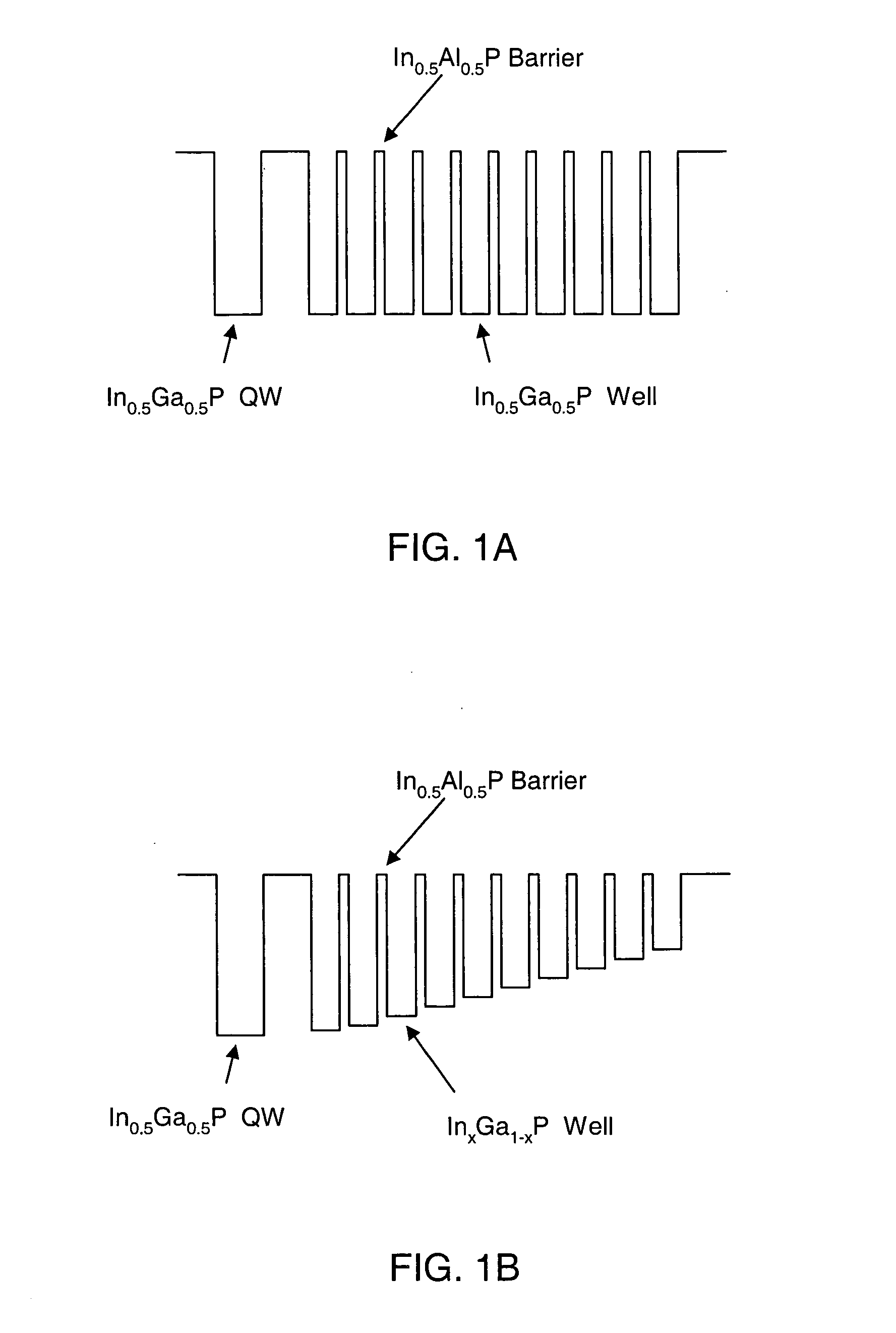

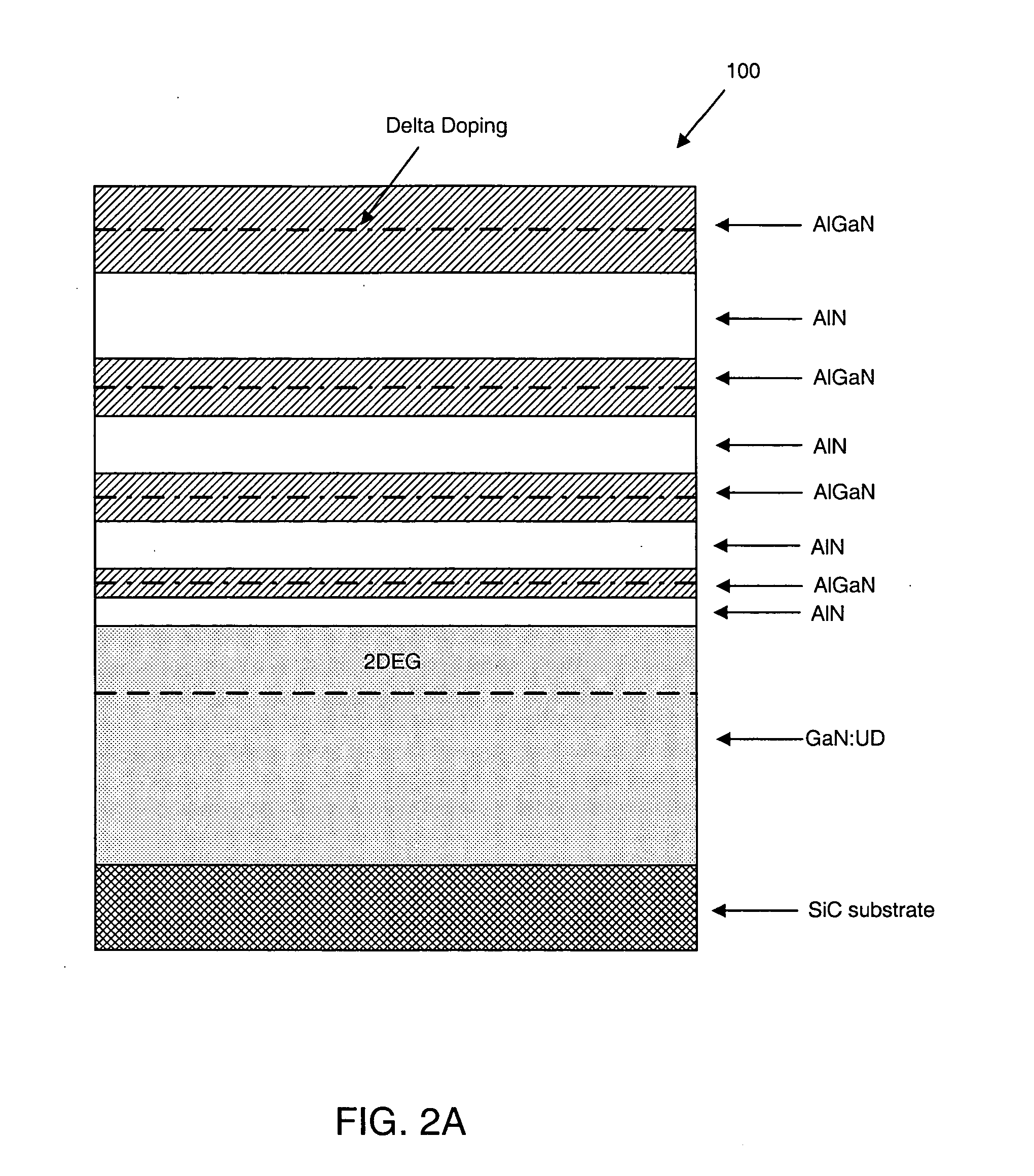

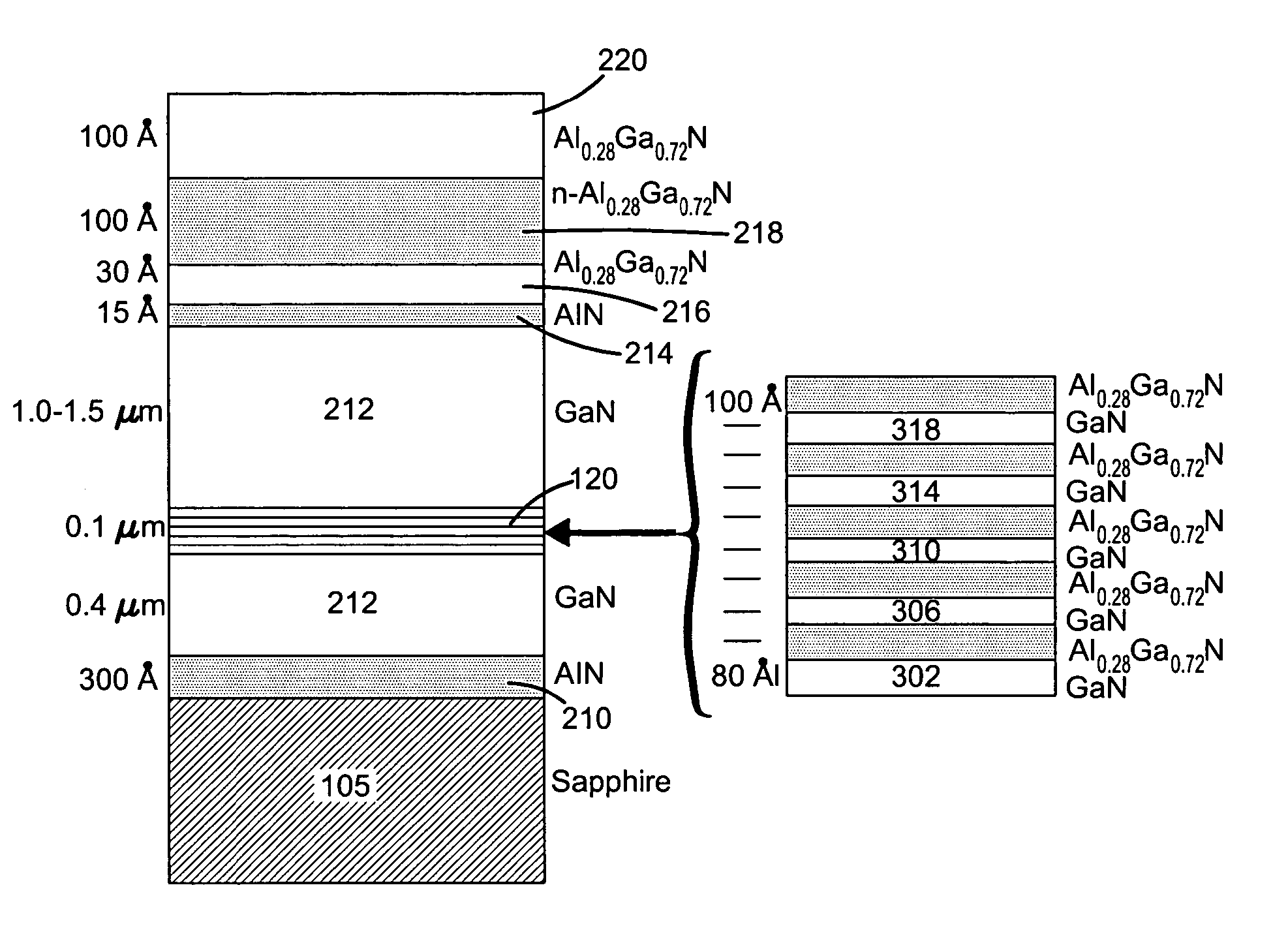

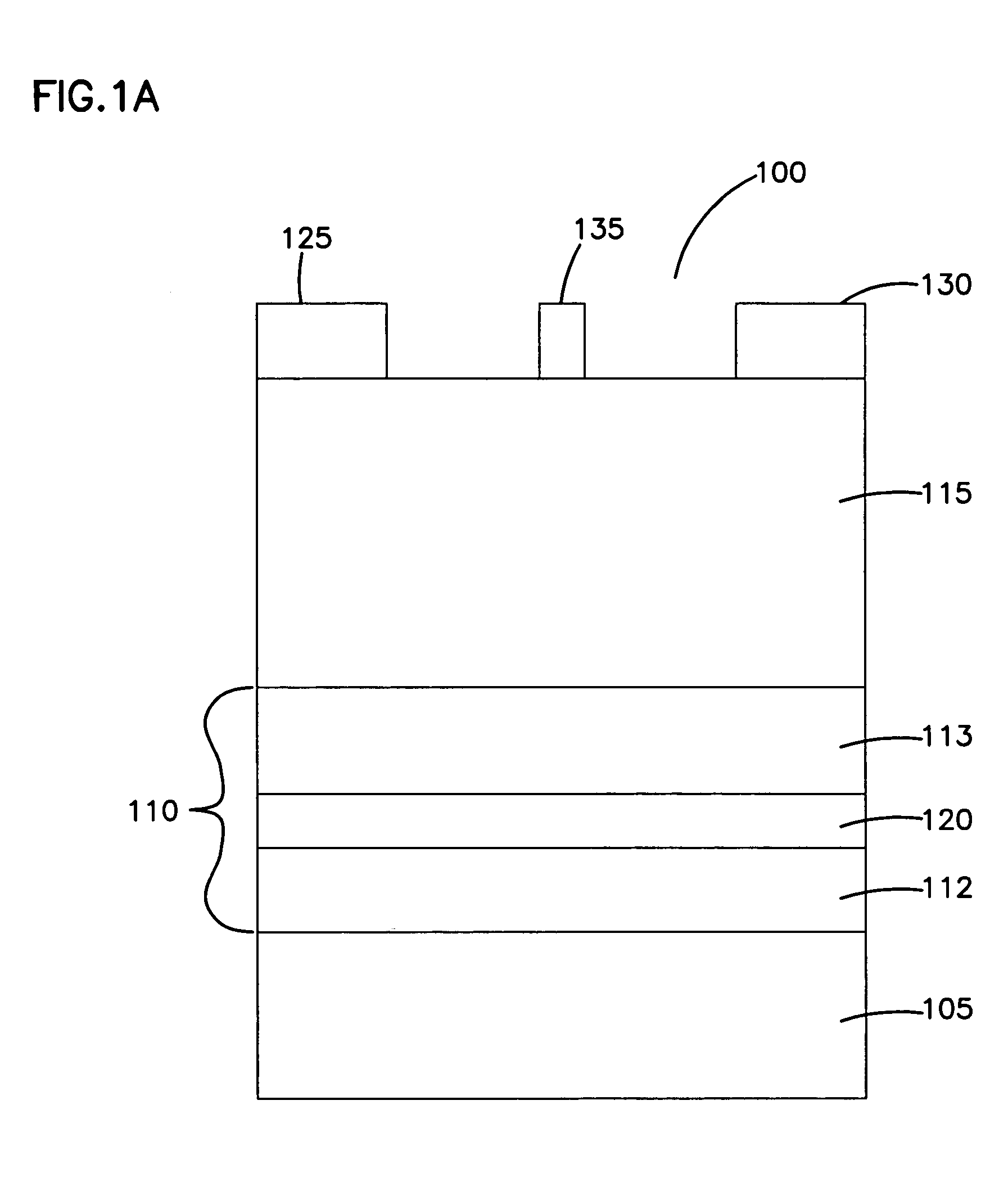

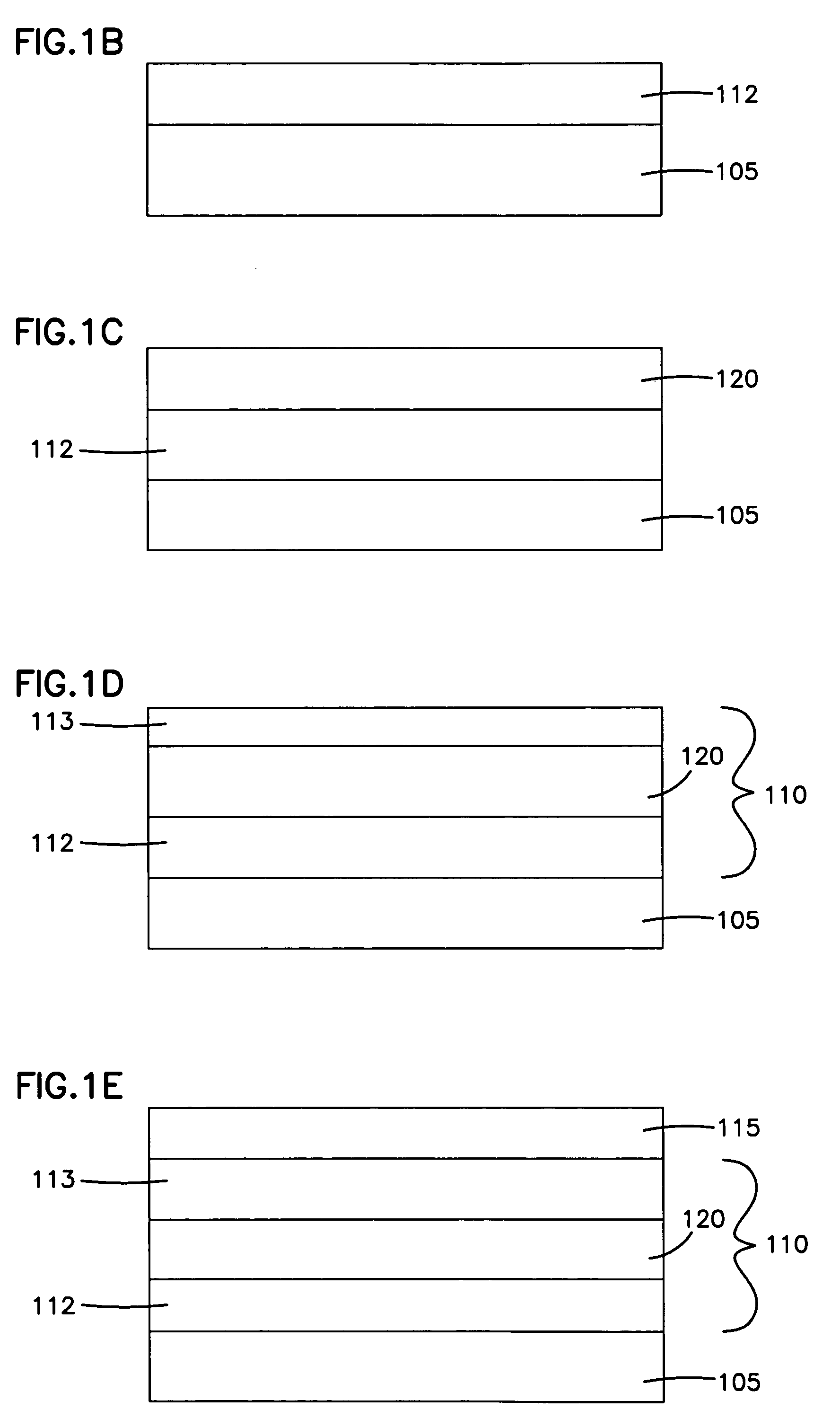

Embodiments disclosed herein include electronic device designs based upon electronic properties of Group III-N materials and quantum-mechanical effects of specialized heterostructures. Such electronic device designs may include, for example, heterojunction field-effect transistors (HFETs) and high-electron-mobility transistors (HEMTs). The design concepts permit high power, high-frequency, and high-temperature operation of advanced electronic circuits, including devices for radar, collision-avoidance systems, and wireless communications. Designs disclosed may include one or more AlN layers and / or one or more SMASH superlattice barriers combined with one or more n-type delta-doped regions. Alternately, in certain embodiments, one or more AlN layers and one or more SMASH superlattice barriers may be combined without the n-type delta-doped regions.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

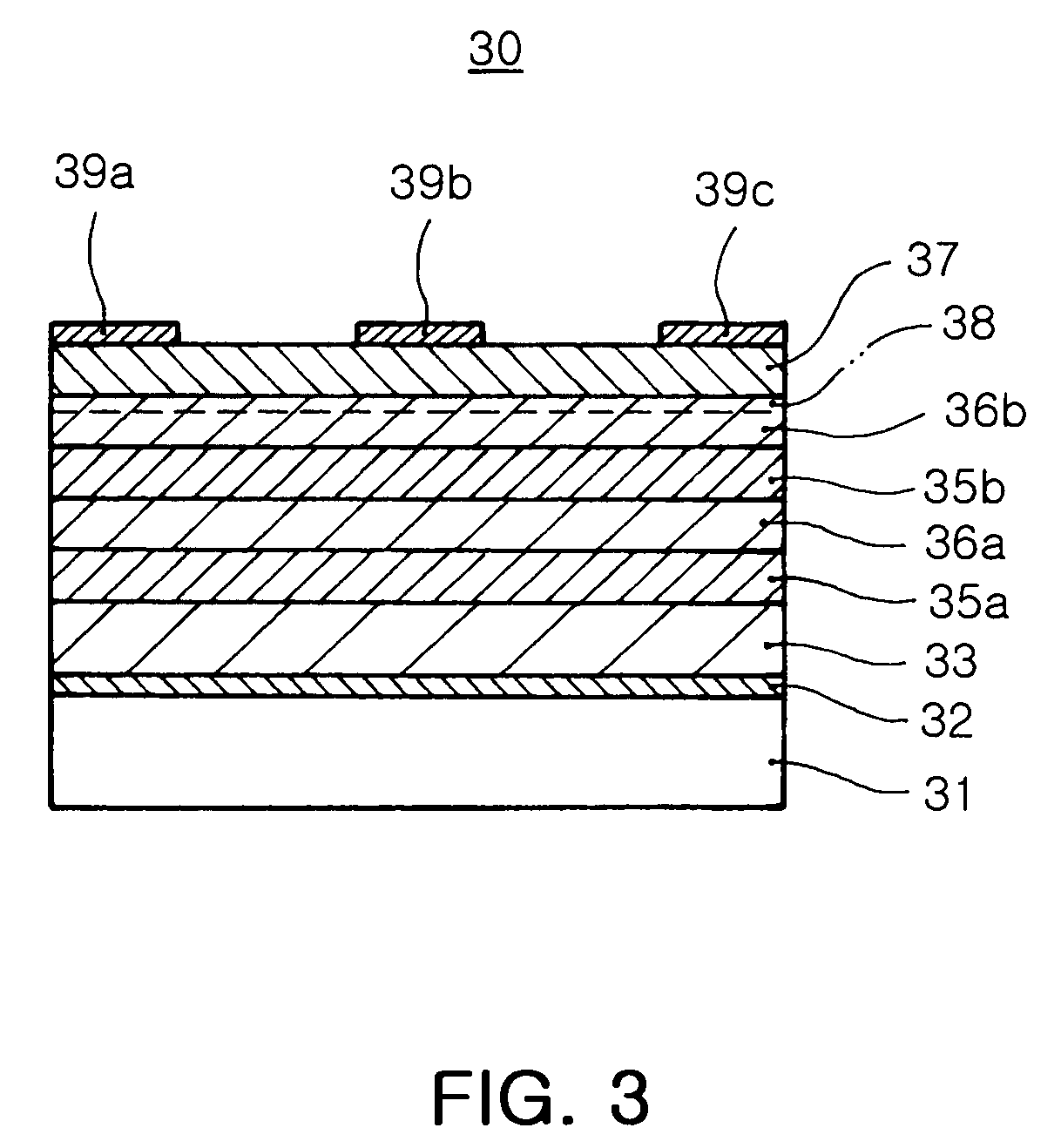

Super lattice modification of overlying transistor

ActiveUS7112830B2Reduce surface roughnessReduces surface mobilitySemiconductor/solid-state device manufacturingBulk negative resistance effect devicesHeterojunctionHeterojunction field effect transistor

The invention provides a device having a substrate, a buffer region positioned upon the substrate, wherein the buffer region has an upper buffer region and a lower buffer region, a heterojunction region positioned upon the buffer region, and a superlattice positioned between the lower buffer region and the upper buffer region, wherein the device is configured to function as a heterojunction field effect transistor.

Owner:INFINEON TECH AMERICAS CORP

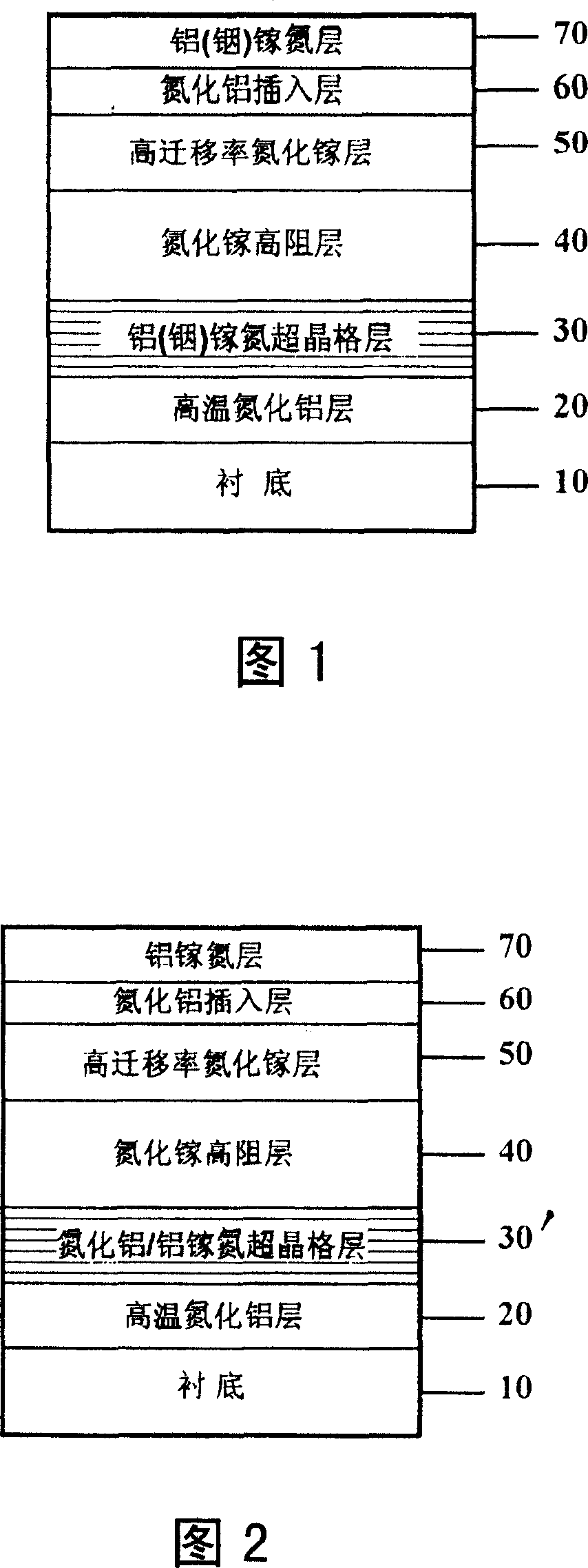

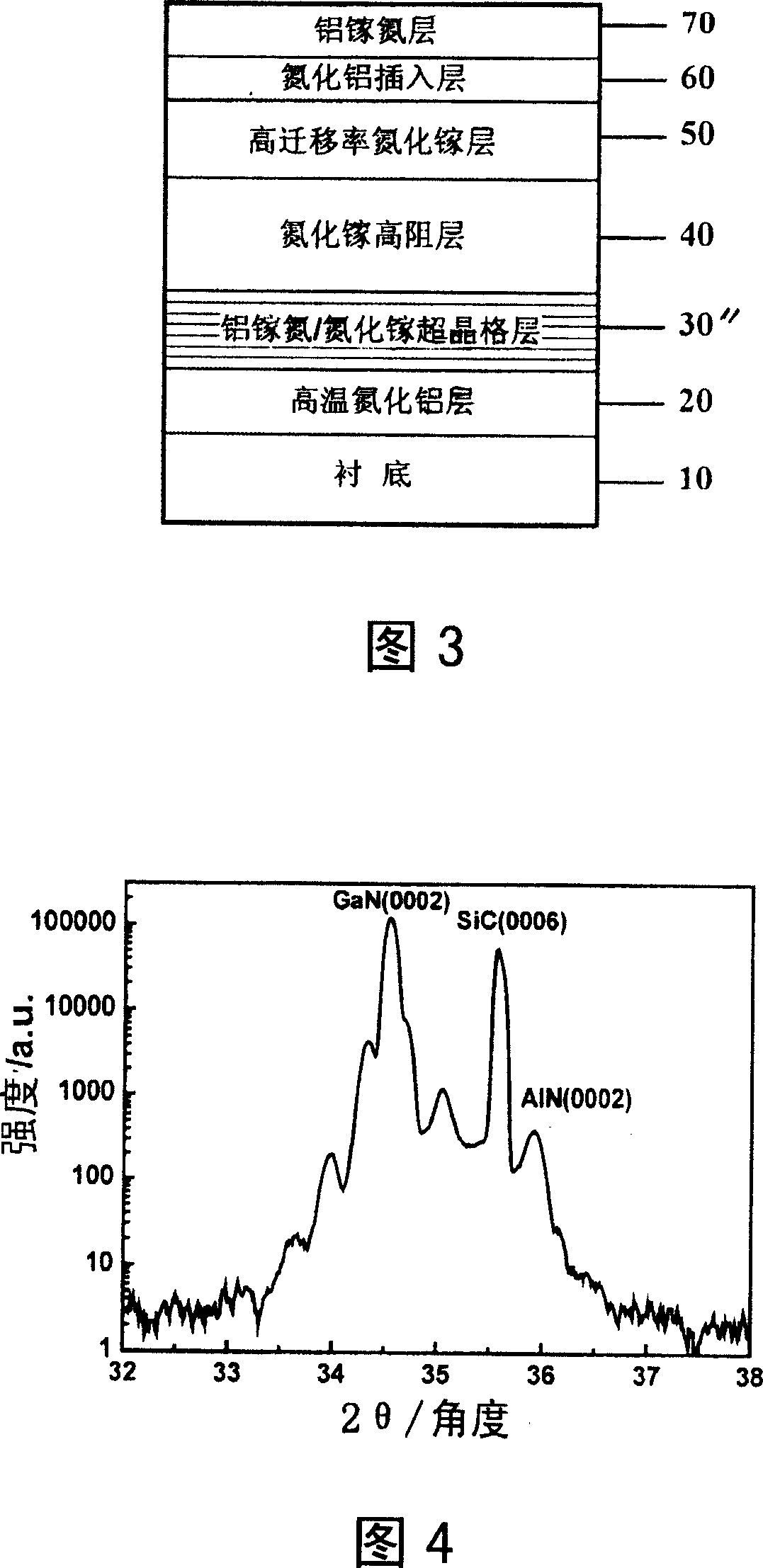

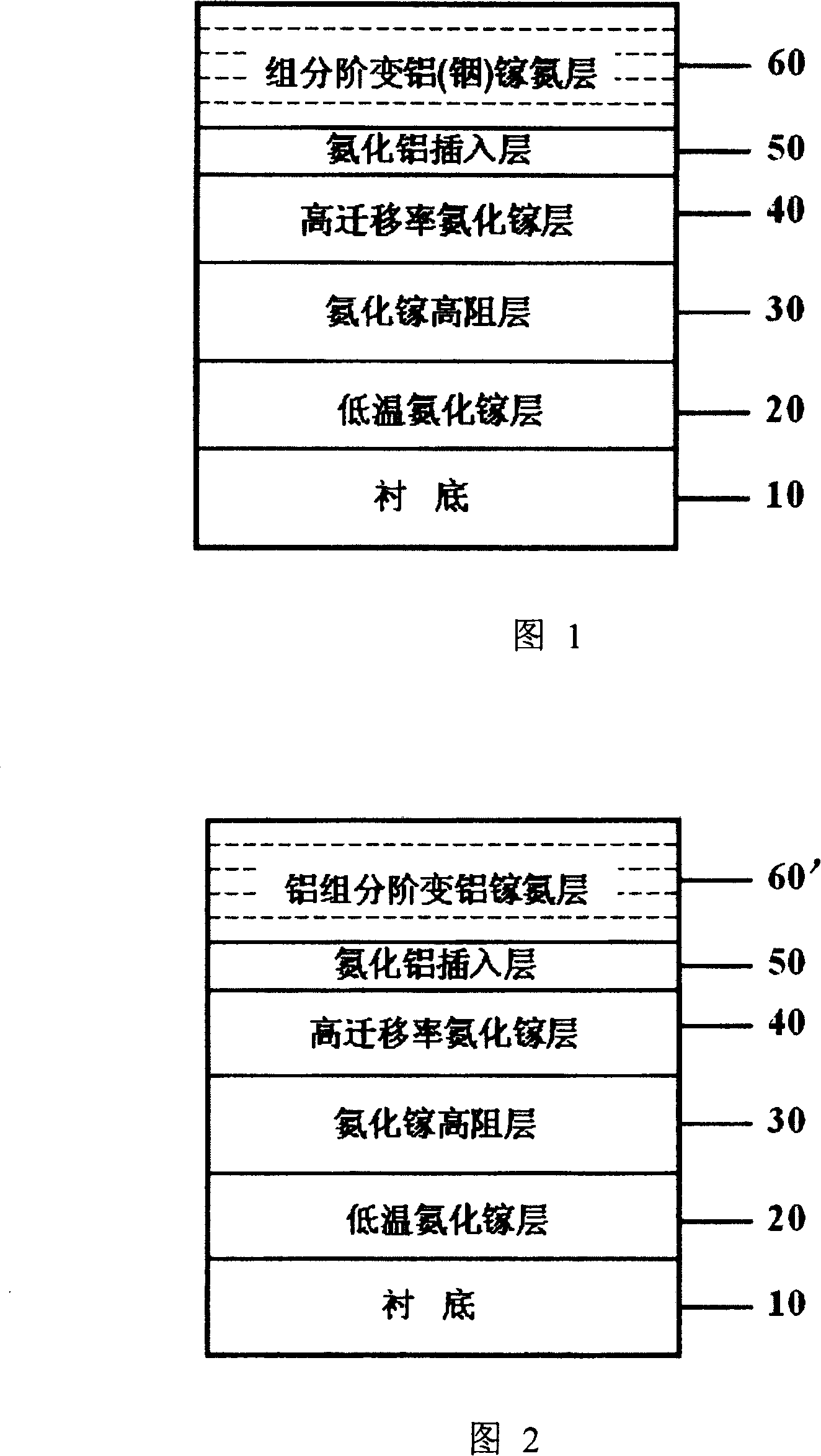

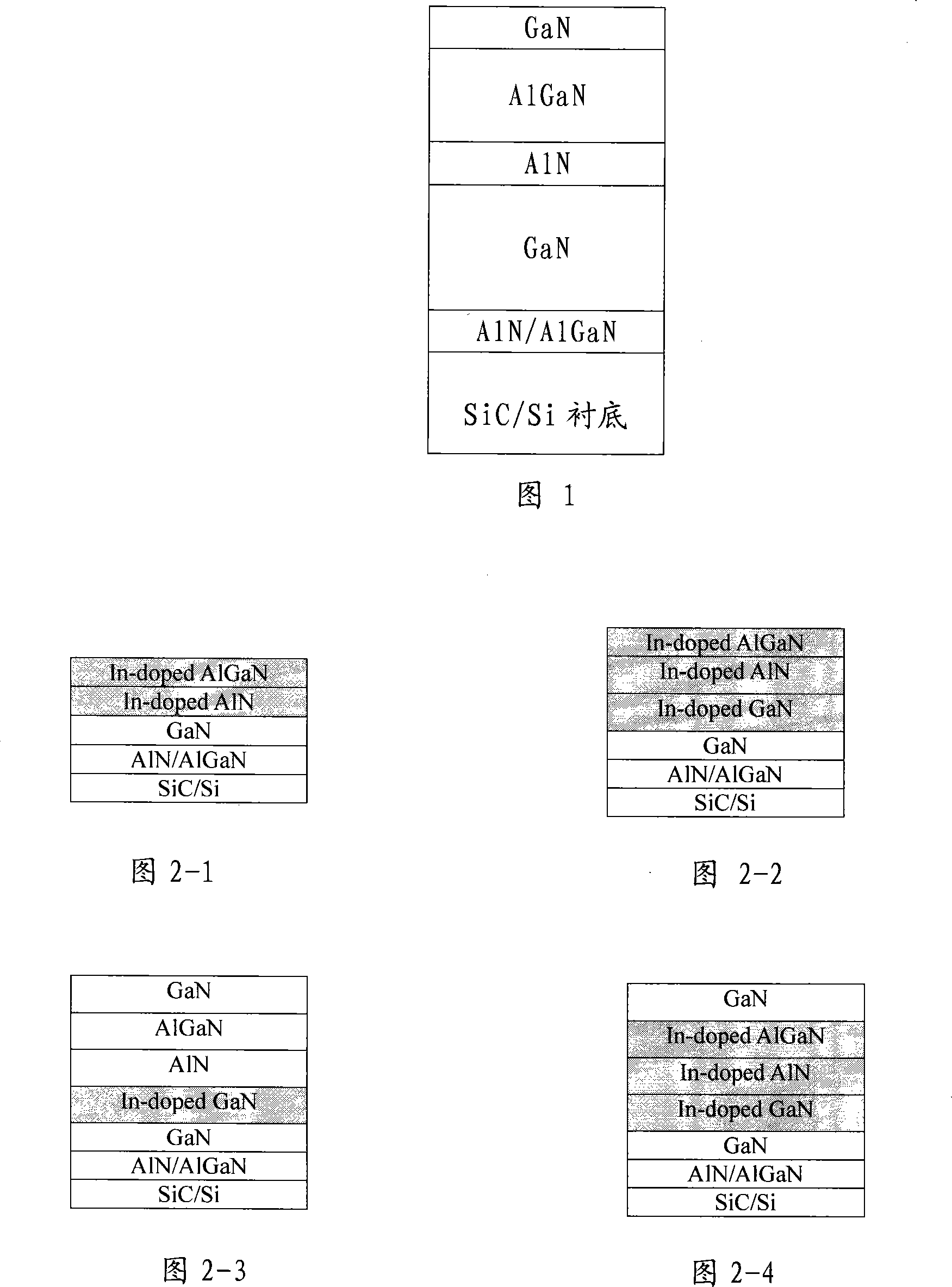

Wideband gap gallium nitride radical heterojunction field effect transistor structure and method for making

InactiveCN101136432AStress reliefImprove crystal qualitySemiconductor/solid-state device manufacturingSemiconductor devicesResistIndium

This invention relates to a wide band-gap GaN-base heterojunction field effect transistor structure including: a substrate, a high temperature AlN nucleating layer on the substrate, an AlInGaN supper lattice buffer layer processed on the nucleating layer, a non-intentional or intentional doped GaN high resist layer processed on the buffer layer, a non-intentional doped high transfer rate GaN layer processed on the high resist layer and an AlN insertion layer set on the high transfer rate GaN layer and a non-intentional doped or n-type doped AlInGaN layer set on the AlN insertion layer.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Monolithic integration of enhancement- and depletion-mode AlGaN/GaN HFETs

A method for and devices utilizing monolithic integration of enhancement-mode and depletion-mode AlGaN / GaN heterojunction field-effect transistors (HFETs) is disclosed. Source and drain ohmic contacts of HFETs are first defined. Gate electrodes of the depletion-mode HFETs are then defined. Gate electrodes of the enhancement-mode HFETs are then defined using fluoride-based plasma treatment and high temperature post-gate annealing of the sample. Device isolation is achieved by either mesa etching or fluoride-based plasma treatment. This method provides a complete planar process for GaN-based integrated circuits favored in high-density and high-speed applications.

Owner:THE HONG KONG UNIV OF SCI & TECH

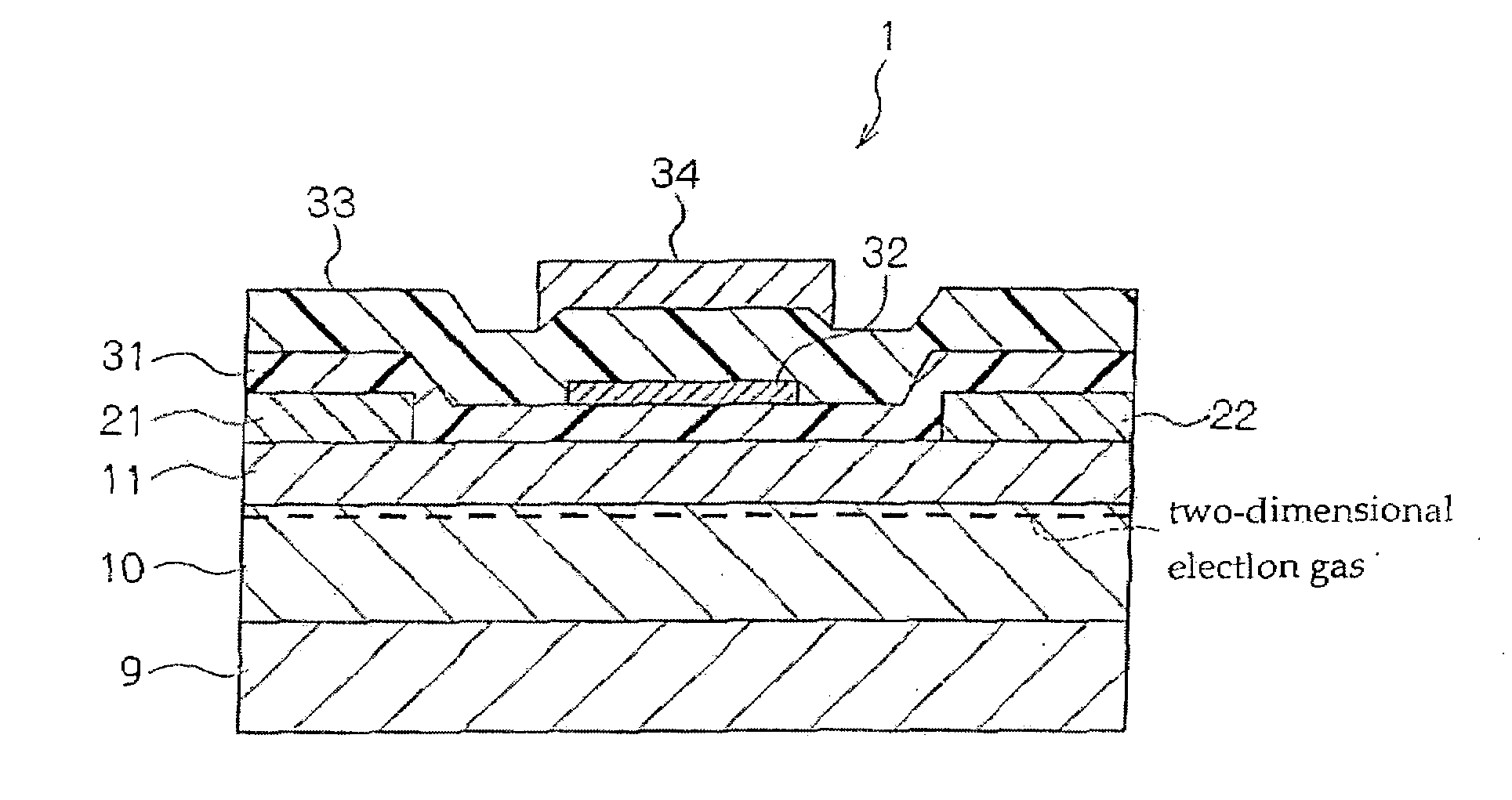

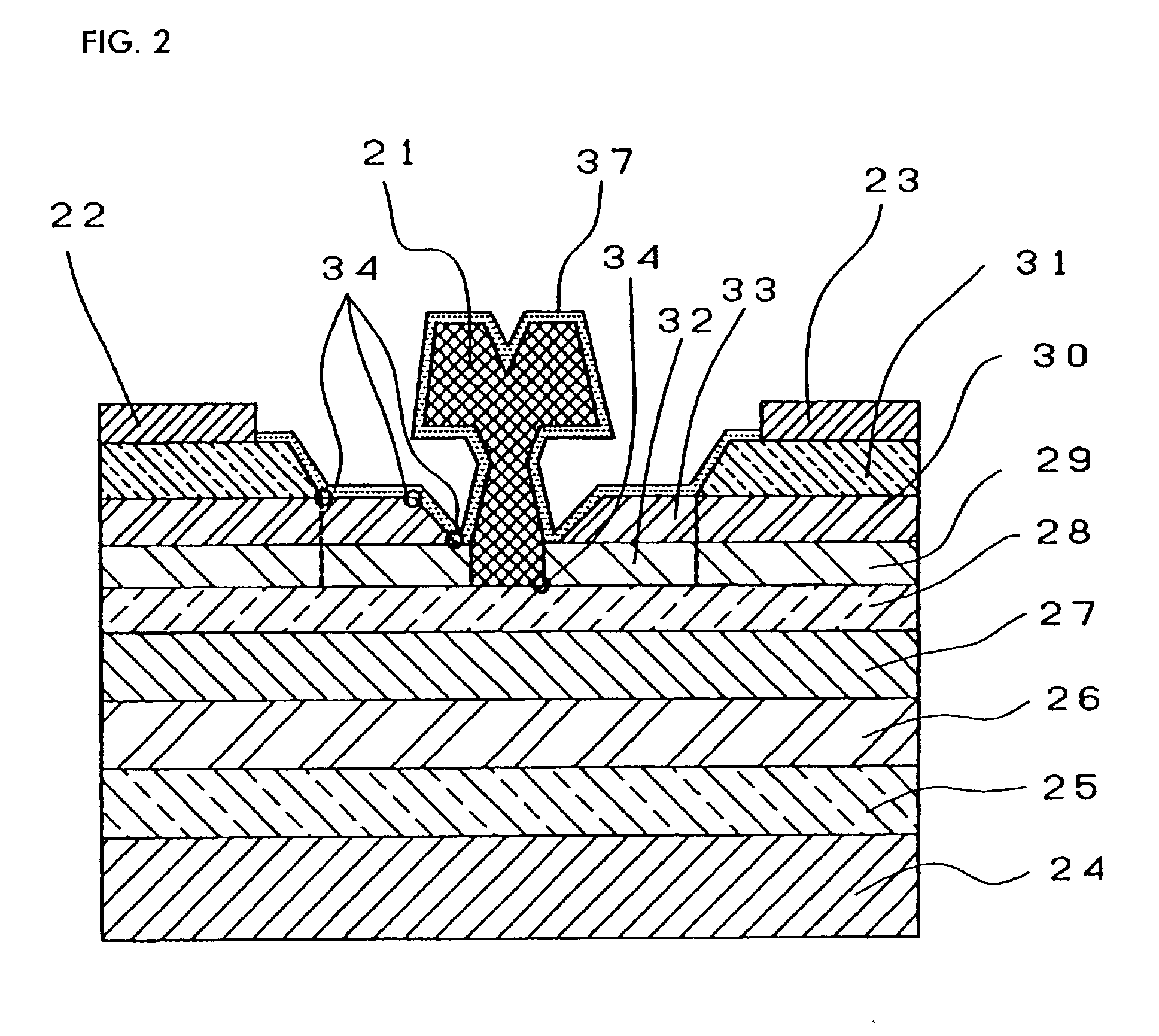

Nitride semiconductor heterojunction field effect transistor

InactiveUS20080135880A1Suppress fluctuationsEasy to controlSemiconductor devicesDrain currentGate voltage

In the nitride semiconductor heterojunction field effect transistor of the present invention, the floating gate layer (32), as the third layer, is formed between the control gate electrode (34) and the AlGaN layer (11), and the potential for the electrons in the AlGaN layer (11), which is substantially neighboring the floating gate layer (32), is able to be substantially high, and then the channel is able to be depleted. Hence, no current can be flowed through the channel (no drain current) at the time of no gate voltage, as so-called stable normally-off operation can be obtained.

Owner:FURUKAWA ELECTRIC CO LTD +1

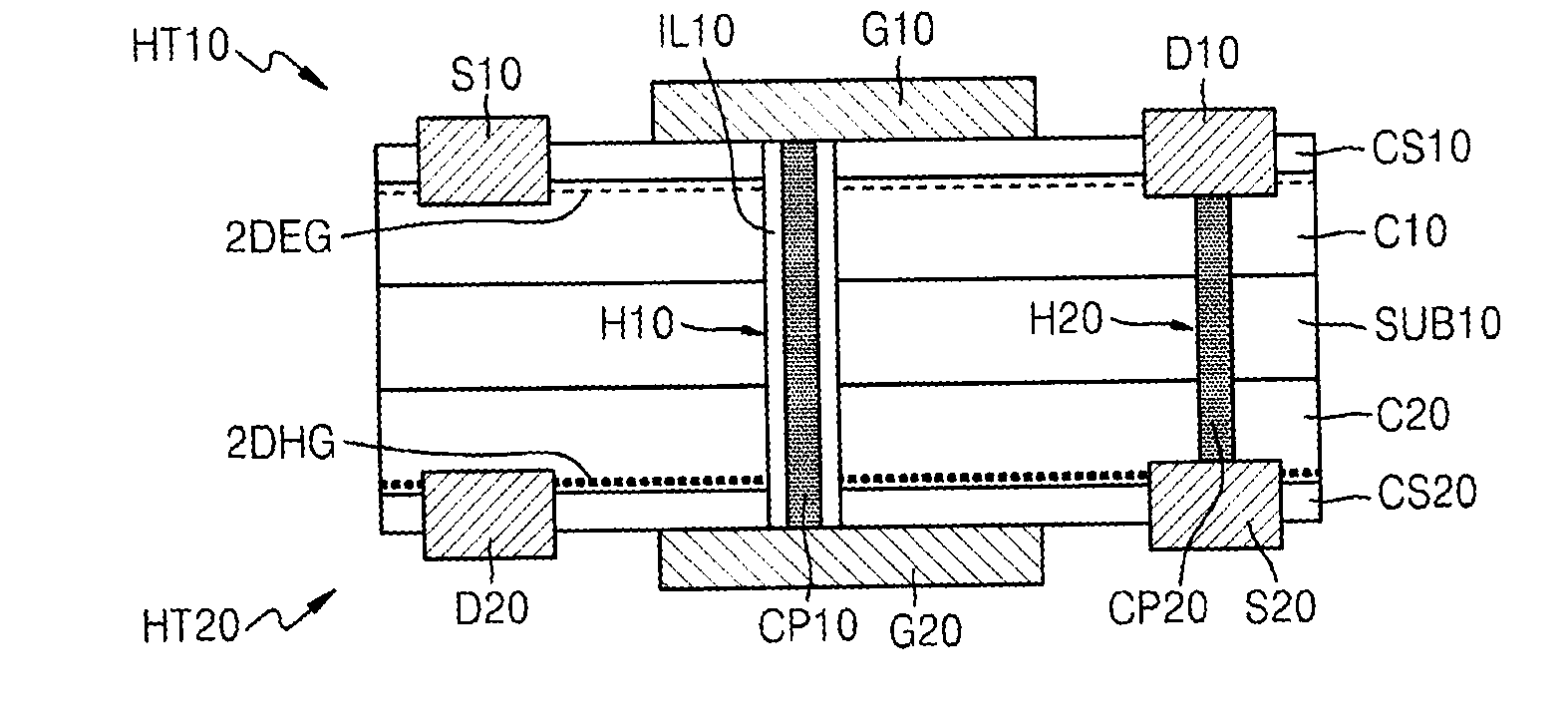

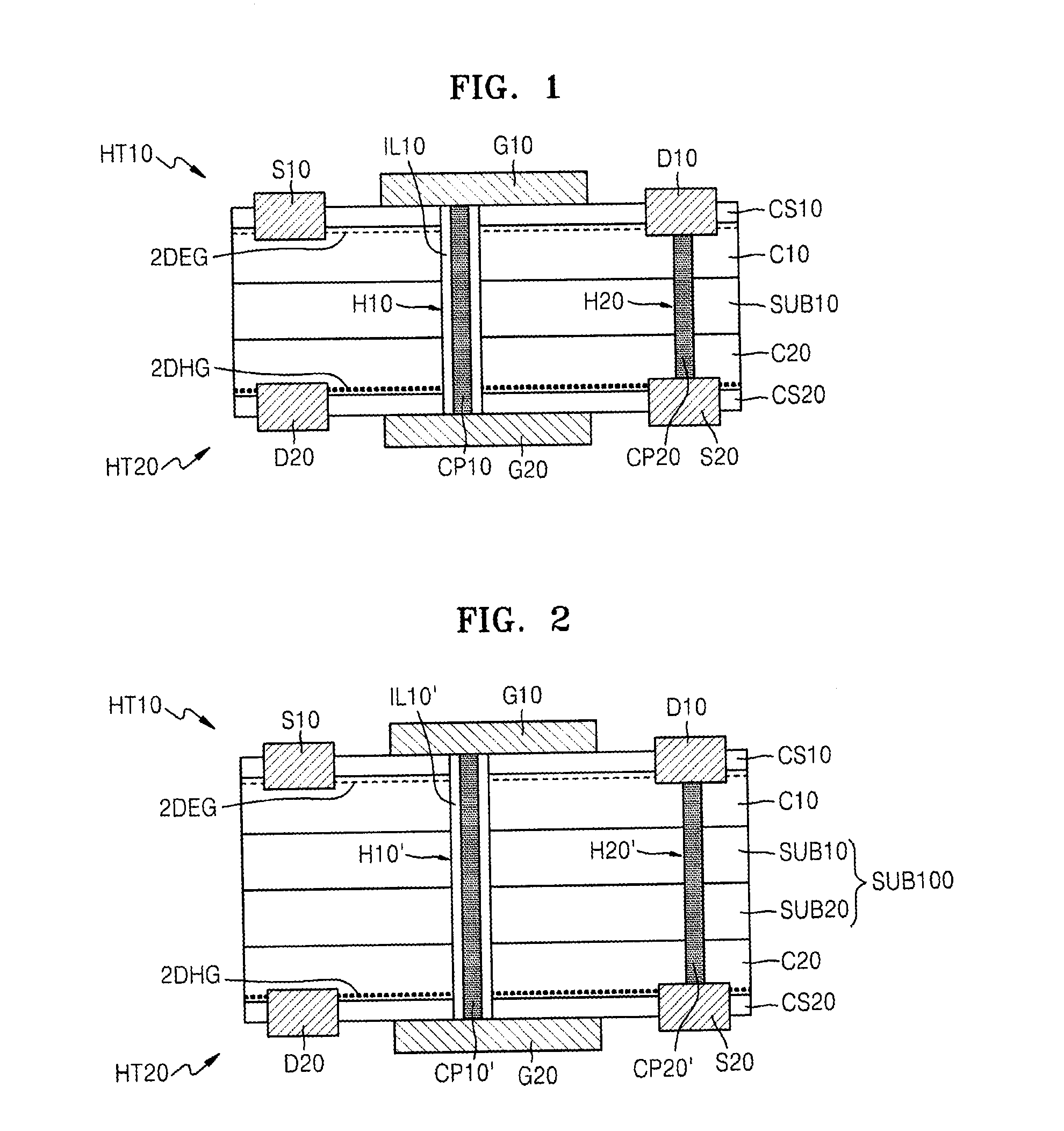

Semiconductor devices and methods of manufacturing the same

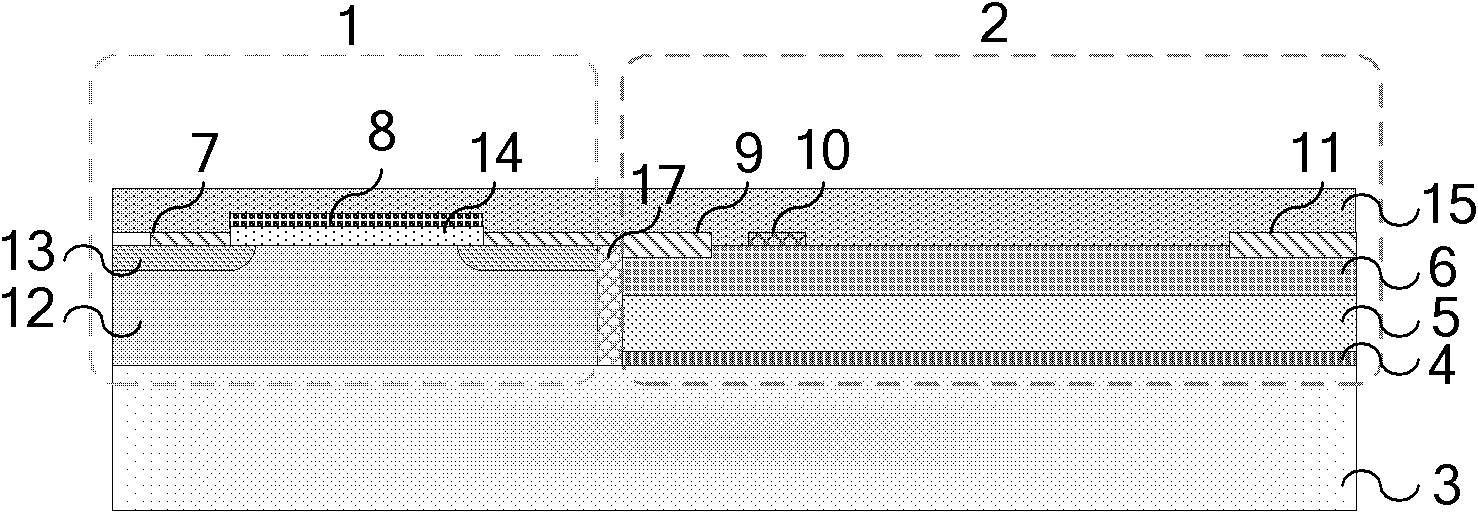

ActiveUS20140091366A1Improve comprehensive applicabilityIncreasing practicabilityTransistorSolid-state devicesDevice materialHigh electron

Example embodiments relate to semiconductor devices and / or methods of manufacturing the same. According to example embodiments, a semiconductor device may include a first heterojunction field effect transistor (HFET) on a first surface of a substrate, and a second HFET. A second surface of the substrate may be on the second HFET. The second HFET may have different properties (characteristics) than the first HFET. One of the first and second HFETs may be of an n type, while the other thereof may be of a p type. The first and second HFETs may be high-electron-mobility transistors (HEMTs). One of the first and second HFETs may have normally-on properties, while the other thereof may have normally-off properties.

Owner:SAMSUNG ELECTRONICS CO LTD

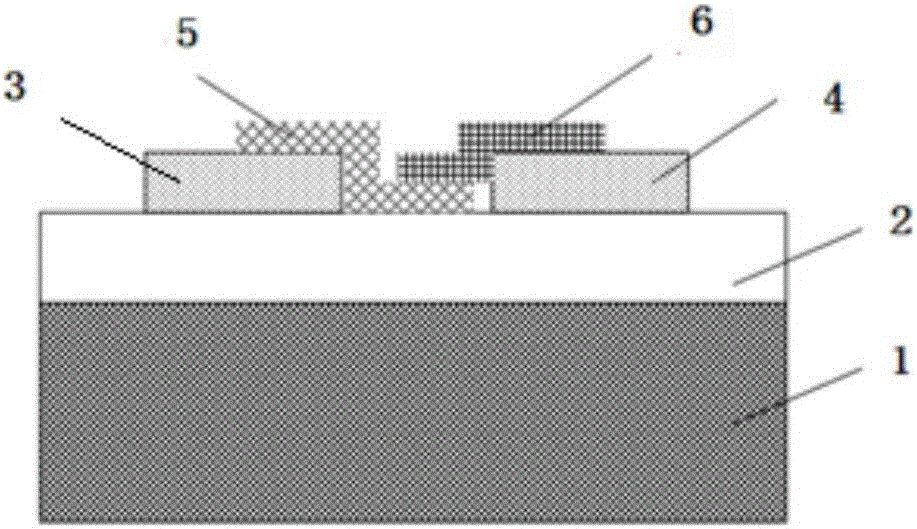

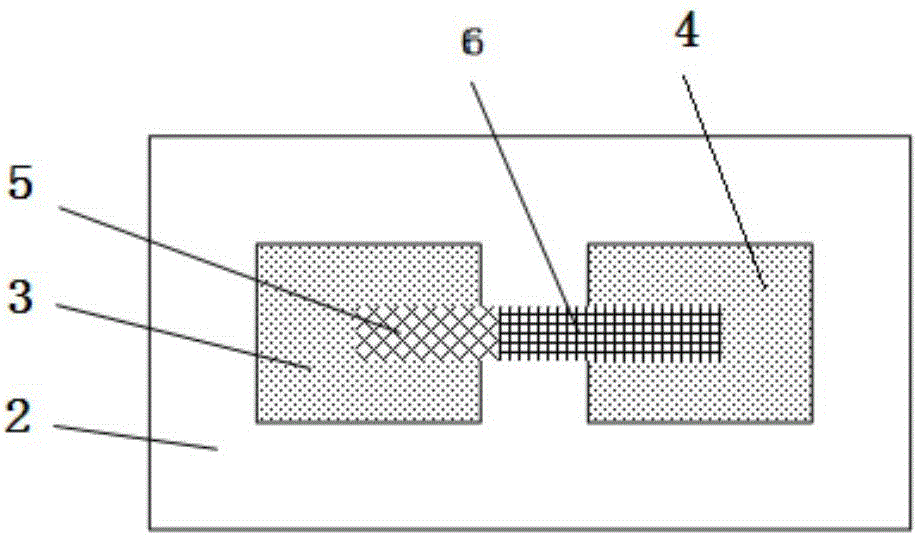

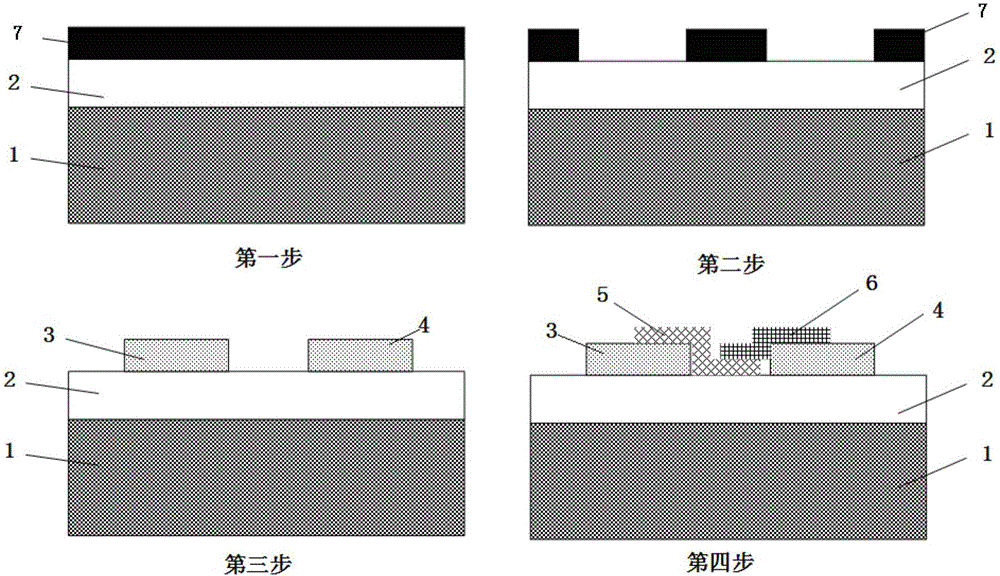

Two-dimensional material heterojunction field effect transistor, preparation method thereof and transistor array device

ActiveCN106206710AImprove output characteristicsLow costSemiconductor/solid-state device manufacturingSemiconductor devicesTransistor arrayOhmic contact

The invention provides a two-dimensional material heterojunction field effect transistor, a preparation method thereof and a transistor array device. The transistor comprises a conductive substrate, an insulating dielectric layer, a source electrode, a drain electrode, a first two-dimensional material layer and a second two-dimensional material layer, wherein the insulating dielectric layer is arranged on the conductive substrate; the source electrode and the drain electrode are arranged at two ends of the insulating dielectric layer respectively and a channel region is arranged between the source electrode and the drain electrode; the first two-dimensional material layer is arranged on the source electrode and the channel region connected with the source electrode; the second two-dimensional material layer is arranged on the drain electrode and one part of first two-dimensional material layer on the channel region; the first two-dimensional material layer is different from the second two-dimensional material layer in material; the first two-dimensional material layer, the second two-dimensional material layer, the source electrode and the drain electrode can form ohmic contact. The transistor provided by the invention has good properties of output characteristics and the like and is low in cost. The preparation method of the transistor provided by the invention is high in substrate utilization rate and high in preparation efficiency; the damage of metal evaporation to a two-dimensional material can be avoided; and the array device can also be prepared.

Owner:科睿唯安(佛山)新能源科技有限公司

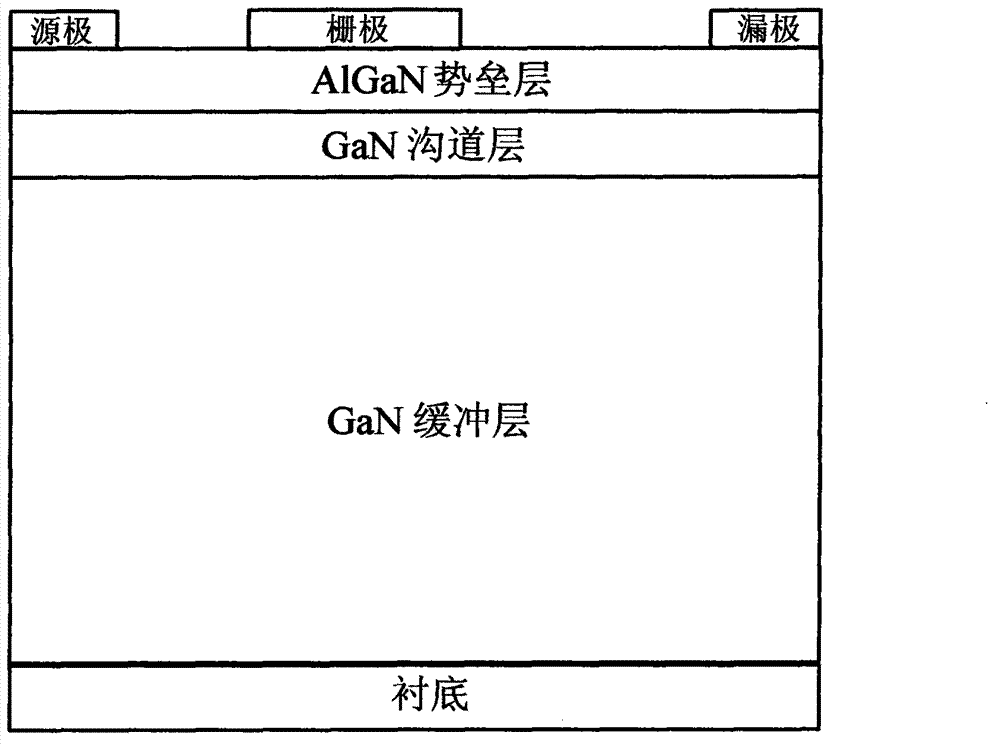

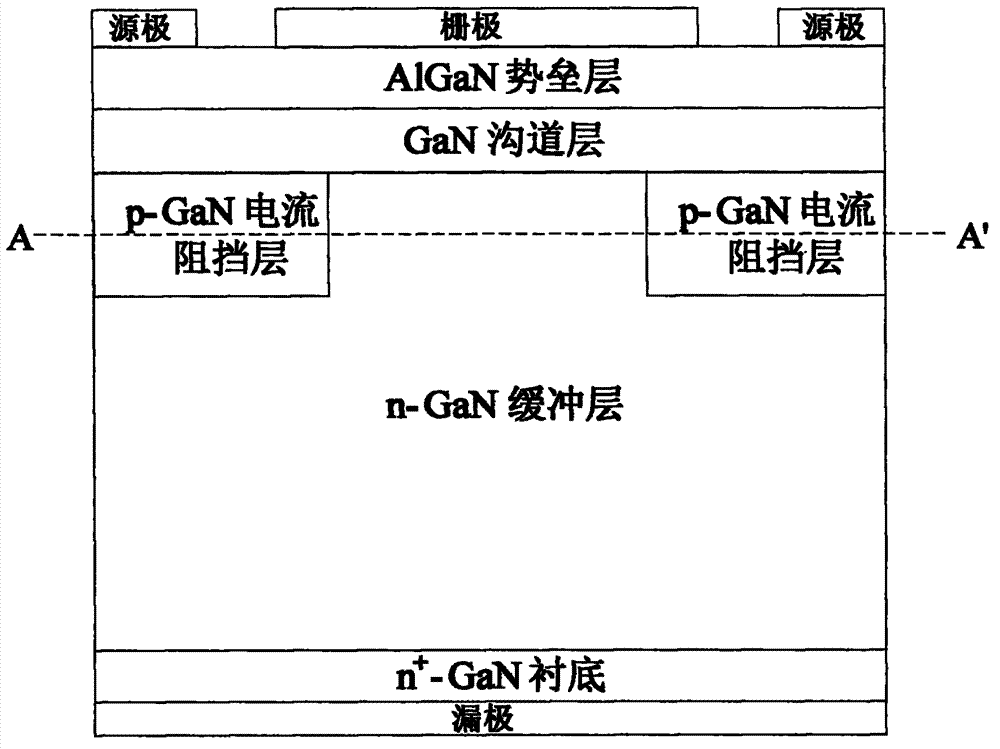

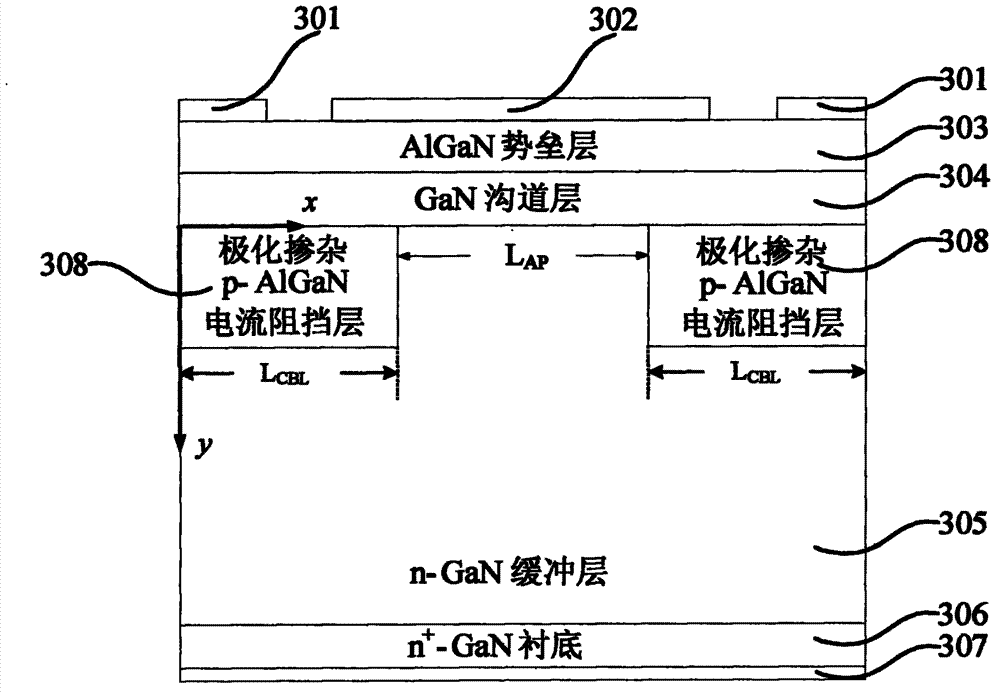

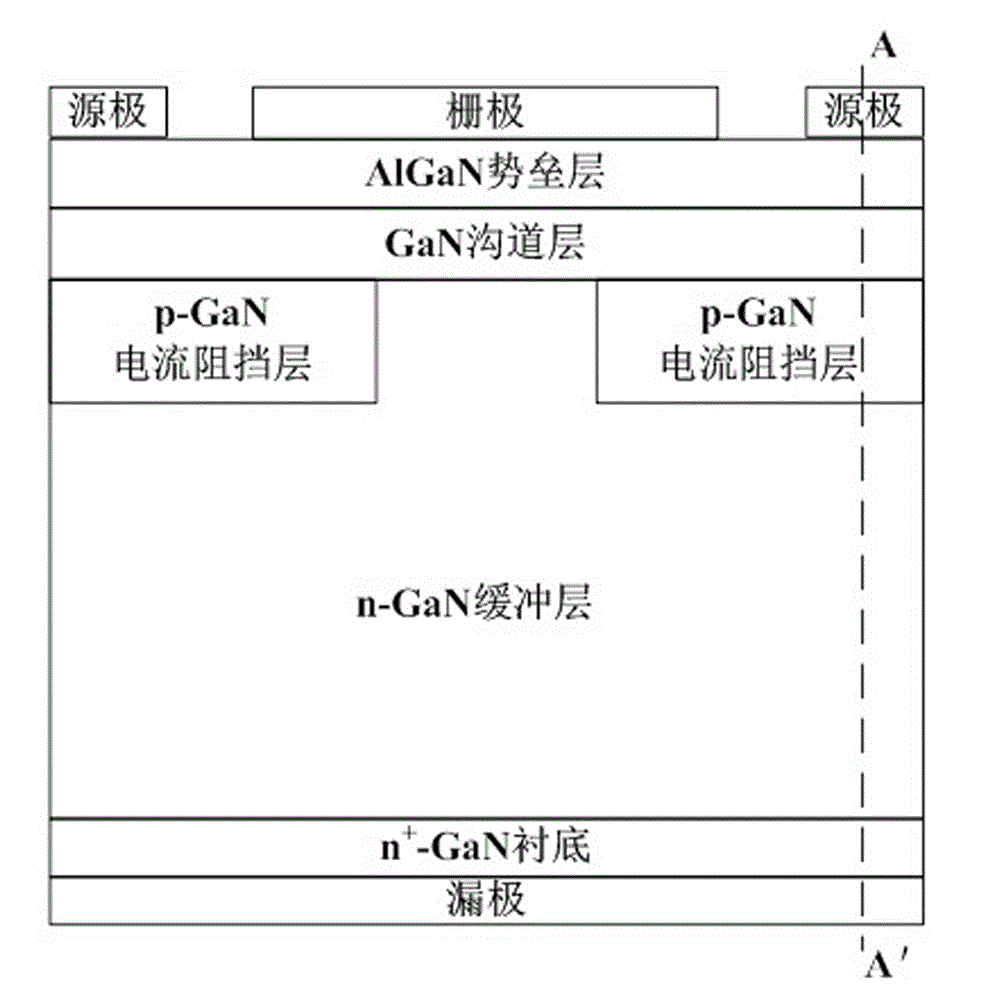

Vertical gallium nitride based nitride heterojunction field effect transistor with polarized doped current barrier layer

InactiveCN103035706AImprove thermal stabilityHigh activation rateSemiconductor devicesOhmic contactGallium nitride

The invention provides a vertical gallium nitride based nitride heterojunction field effect transistor with a polarized doped current barrier layer, which sequentially and mainly comprises a drain electrode, an n<+>-GaN substrate, an n-GaN buffer layer, a GaN channel layer, an AlGaN barrier layer, a source electrode on the AlGaN barrier layer and a grid electrode on the AlGaN barrier layer from bottom to top, wherein the source electrode and the drain electrode are both in ohmic contact, the grid electrode is in Schottky contact, the vertical gallium nitride based nitride heterojunction field effect transistor further comprises the polarized doped p-AlGaN current barrier layer between the n-GaN buffer layer and the GaN channel layer, and an Al component in the current barrier layer increases gradually in the y direction. According to the vertical gallium nitride based nitride heterojunction field effect transistor with the polarized doped current barrier layer, a polarized electric field, produced by the gradual change of the Al component in the current barrier layer, increases the activation rate of p-type impurities and the hole concentration of the current barrier layer, so that the breakdown voltage of an element is increased.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Nitride based hetero-junction field effect transistor

InactiveUS20060049426A1Excellent electrical propertiesHigh crystallinitySolid-state devicesSemiconductor devicesHigh resistanceHeterojunction field effect transistor

A nitride based hetero-junction field effect transistor comprises a high resistance nitride semiconductor layer formed on a substrate, an Al-doped GaN layer formed on the high resistance nitride semiconductor layer and having an Al content of 0.1˜1%, an undoped GaN layer formed on the Al-doped GaN layer, and an AlGaN layer formed on the undoped GaN layer such that a two-dimensional electron gas (2DEG) layer is formed at an interface of the undoped GaN layer. With the Al-doped GaN layer and the undoped GaN layer grown on the high resistance GaN layer having low crystallinity, crystallinity of the GaN layer is enhanced, and thus electrical characteristics of DC and RE of an HEET device are remarkably improved due to enhanced carrier mobility.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

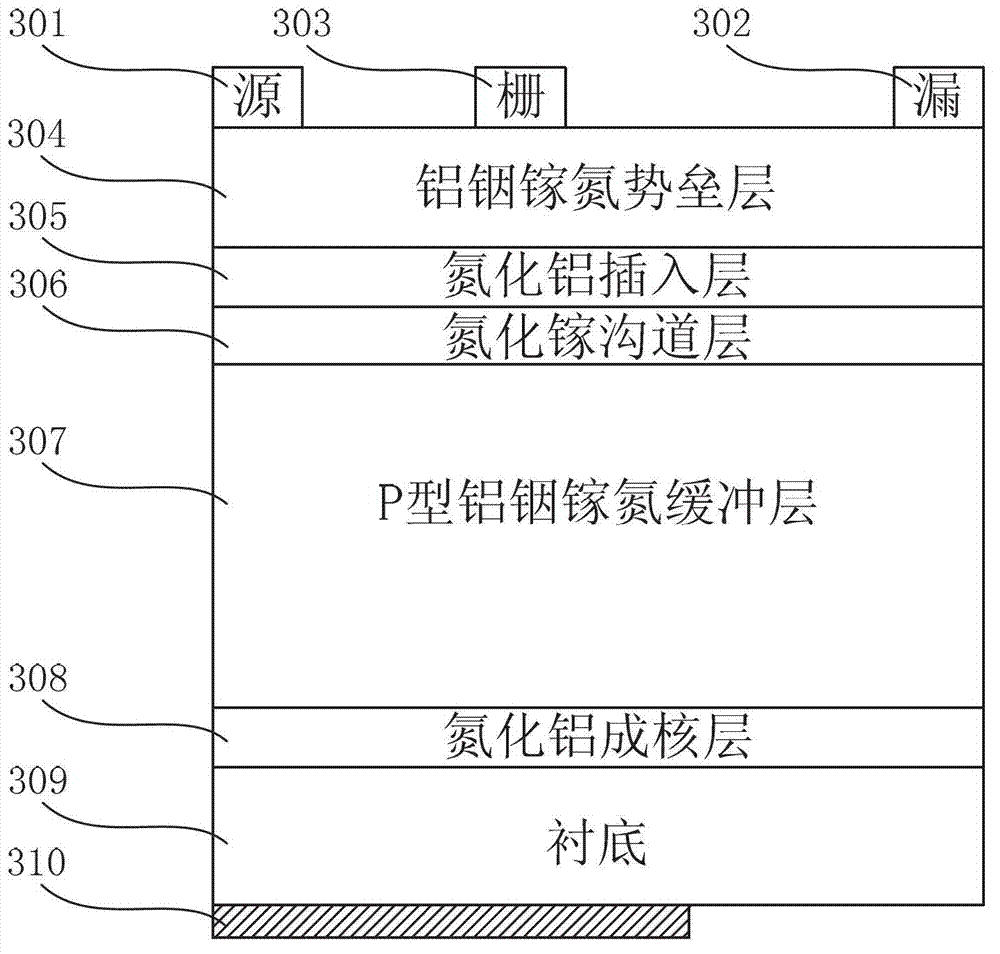

Gallium nitride-based hetero-junction field effect transistor with back electrode structure

ActiveCN102820325AImprove breakdown voltageSuppress leakage currentSemiconductor devicesIndiumOhmic contact

The invention discloses a gallium nitride-based hetero-junction field effect transistor with a back electrode structure. The gallium nitride-based hetero-junction field effect transistor mainly consists of a substrate, an aluminum nitride nucleating layer, a P-type aluminum-indium-gallium-nitrogen buffering layer, a gallium nitride channel layer, an aluminum nitride inserting layer and an aluminum-indium-gallium-nitrogen barrier layer in sequence from bottom to top; a source electrode, a drain electrode and a gate electrode are formed on the barrier layer; the source electrode and the drain electrode form ohmic contact with the barrier layer; the gate electrode and the barrier layer are in Schottky contact; and the gallium nitride-based hetero-junction field effect transistor further comprises the back electrode in contact with the substrate. The back electrode in the gallium nitride-based hetero-junction field effect transistor provided by the invention modulates potential distribution of a device buffering layer, so as to increase potential difference between the two-dimensional electron gas channel and the P-type aluminum-indium-gallium-nitrogen buffering layer. Therefore, two-dimensional electron gas in the channel and the P-type impurities in the buffering layer are entirely consumed, so that the electric field distribution of the device channel is more uniform, and the breakdown voltage of the device is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

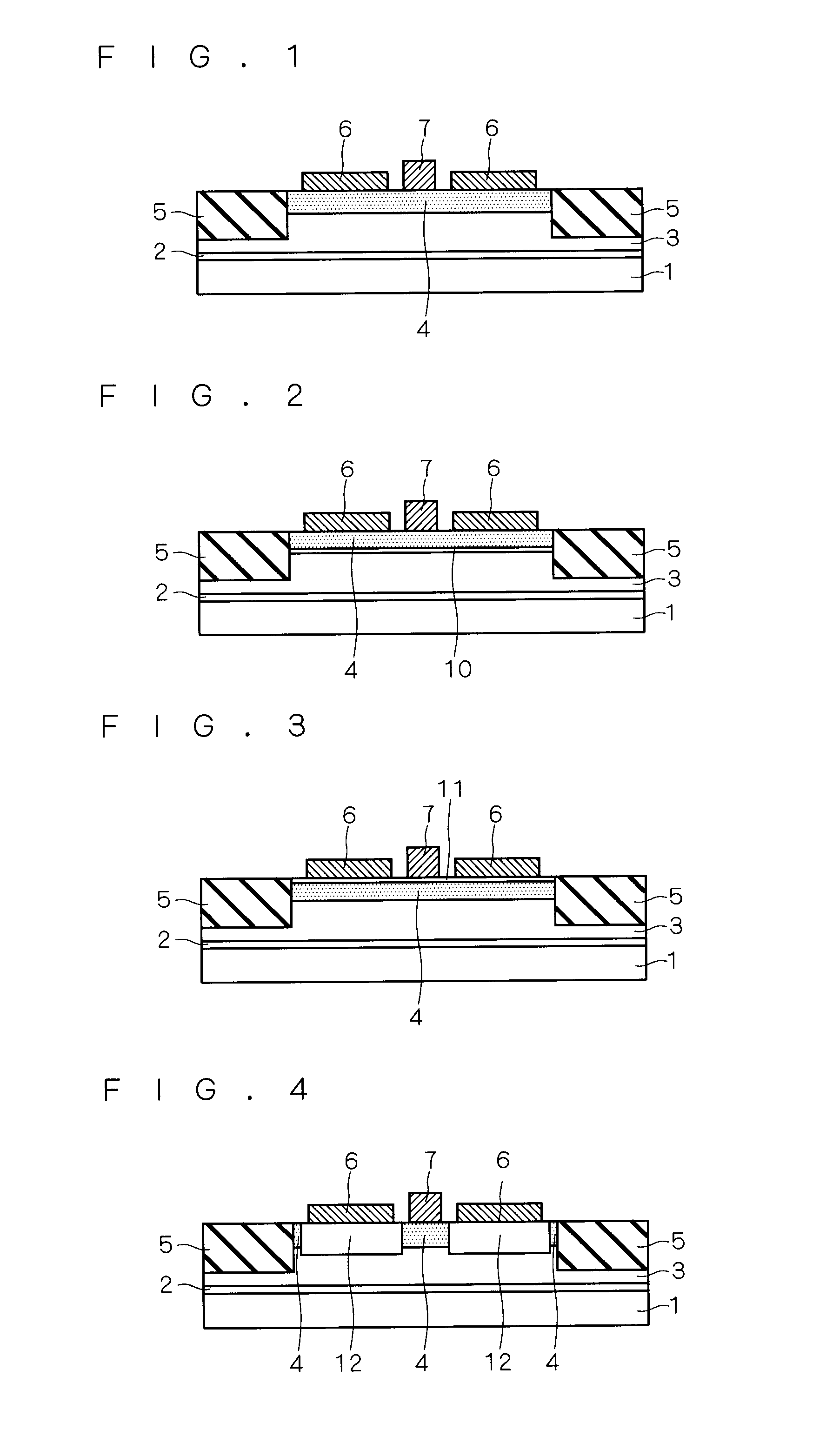

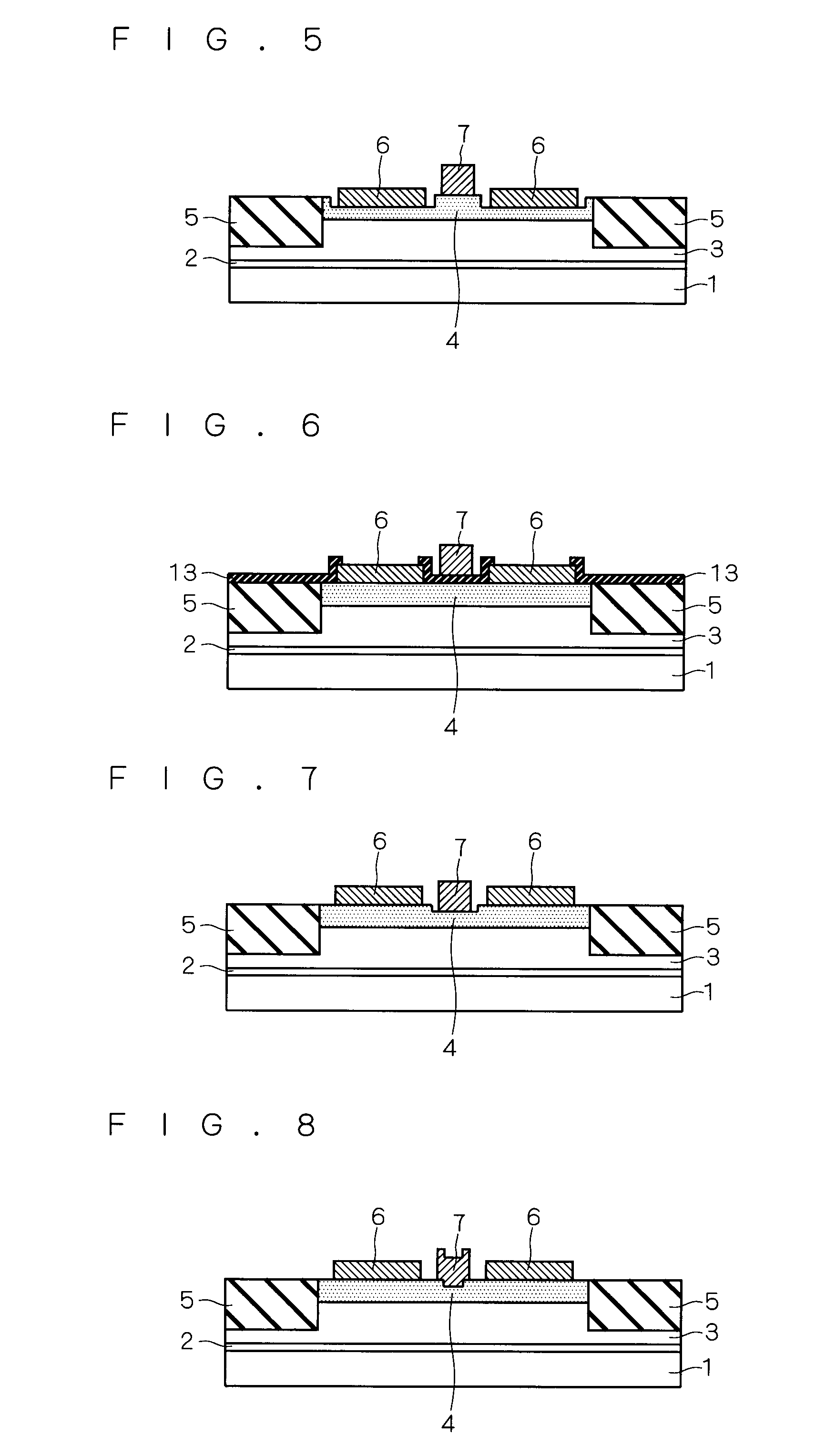

Semiconductor device and manufacturing method of the same

InactiveUS20080237639A1Increase productionImprove breakdown voltageSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialSemiconductor

The objective of the present invention is to provide a semiconductor device of a hetero-junction field effect transistor that is capable of obtaining a high output and a high breakdown voltage and a manufacturing method of the same.The present invention is a semiconductor device of a hetero-junction field effect transistor provided with an AlxGa1-xN channel layer with a composition ratio of Al being x (0<x<1) formed on a substrate, an AlyGa1-yN barrier layer with a composition of Al being y (0<y≦1) formed on the channel layer, and source / drain electrodes and a gate electrode formed on the barrier layer, wherein the composition ratio y is larger than the composition ratio x.

Owner:MITSUBISHI ELECTRIC CORP

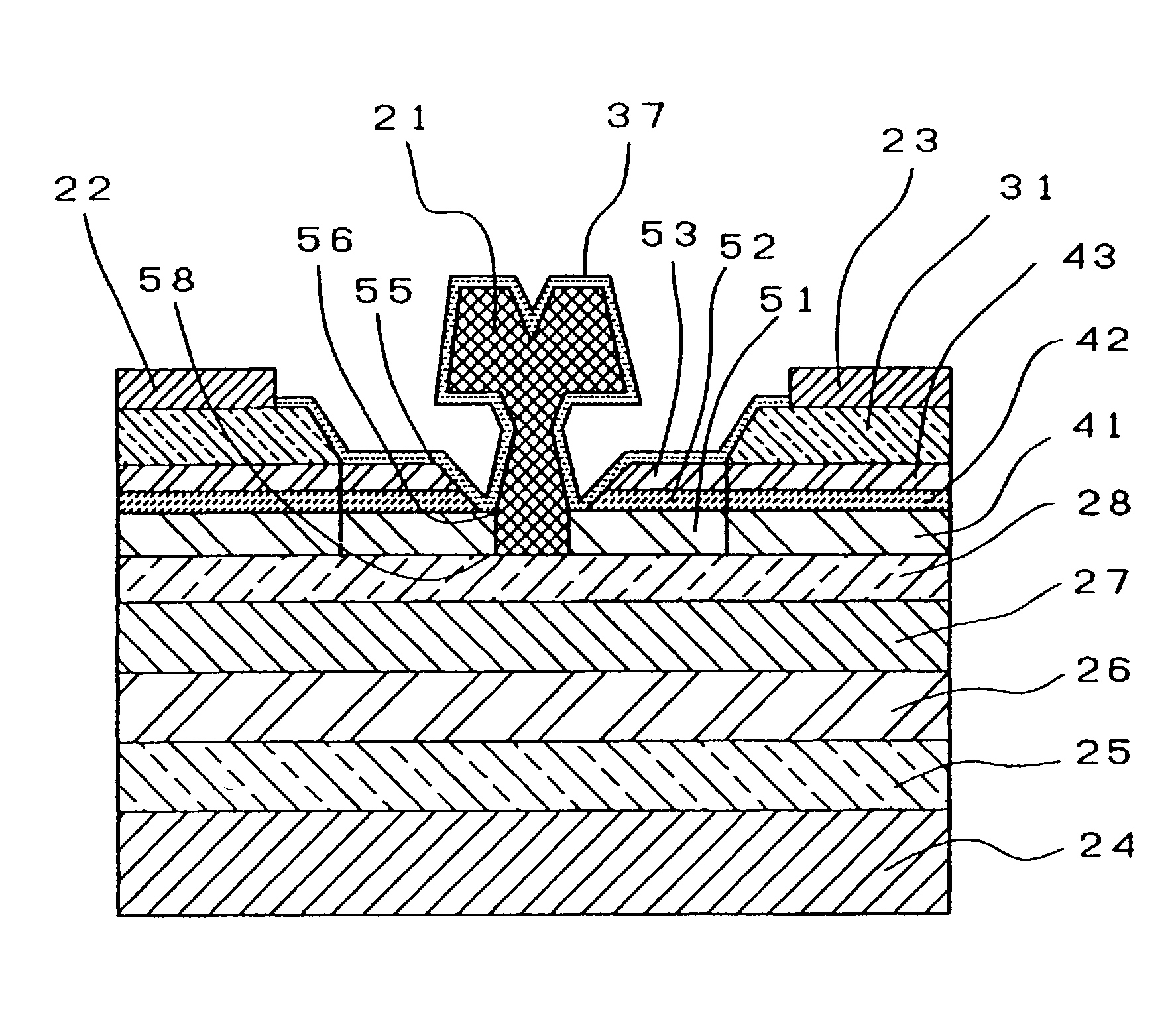

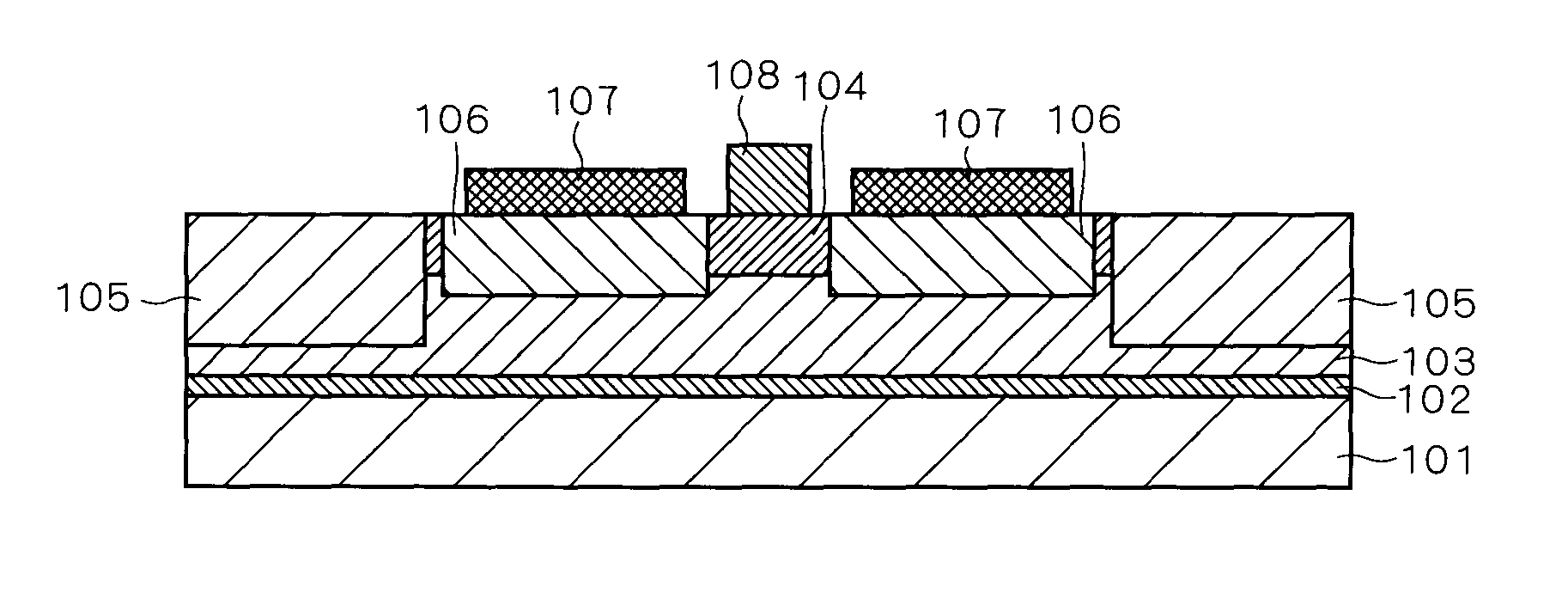

Heterojunction field effect transistor

InactiveUS7012286B2High voltage durabilitySmall series resistanceTransistorSemiconductor/solid-state device manufacturingElectrical resistance and conductanceMicrowave

A heterojunction field effect transistor operative from the micro wave band to the millimeter wave band has a gate recess structure formed in a manner such that its eye-empty areas have a significant effect on the voltage durability of the transistor. The eye-empty areas extend from a gate electrode to a source electrode as well as to a drain electrode and are formed by at least two material layers having different impurity concentrations, thereby making it possible to obtain an improved heterojunction field effect transistor having a reduced series resistance and an increased voltage durability.

Owner:MURATA MFG CO LTD

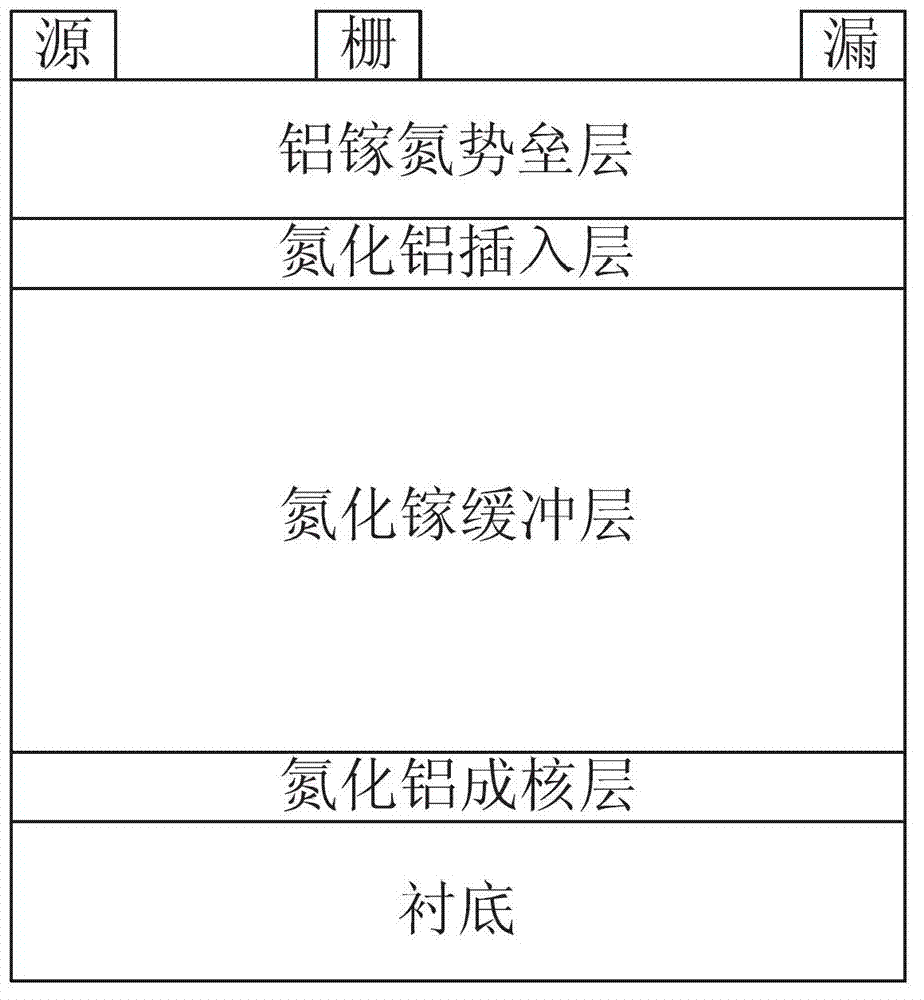

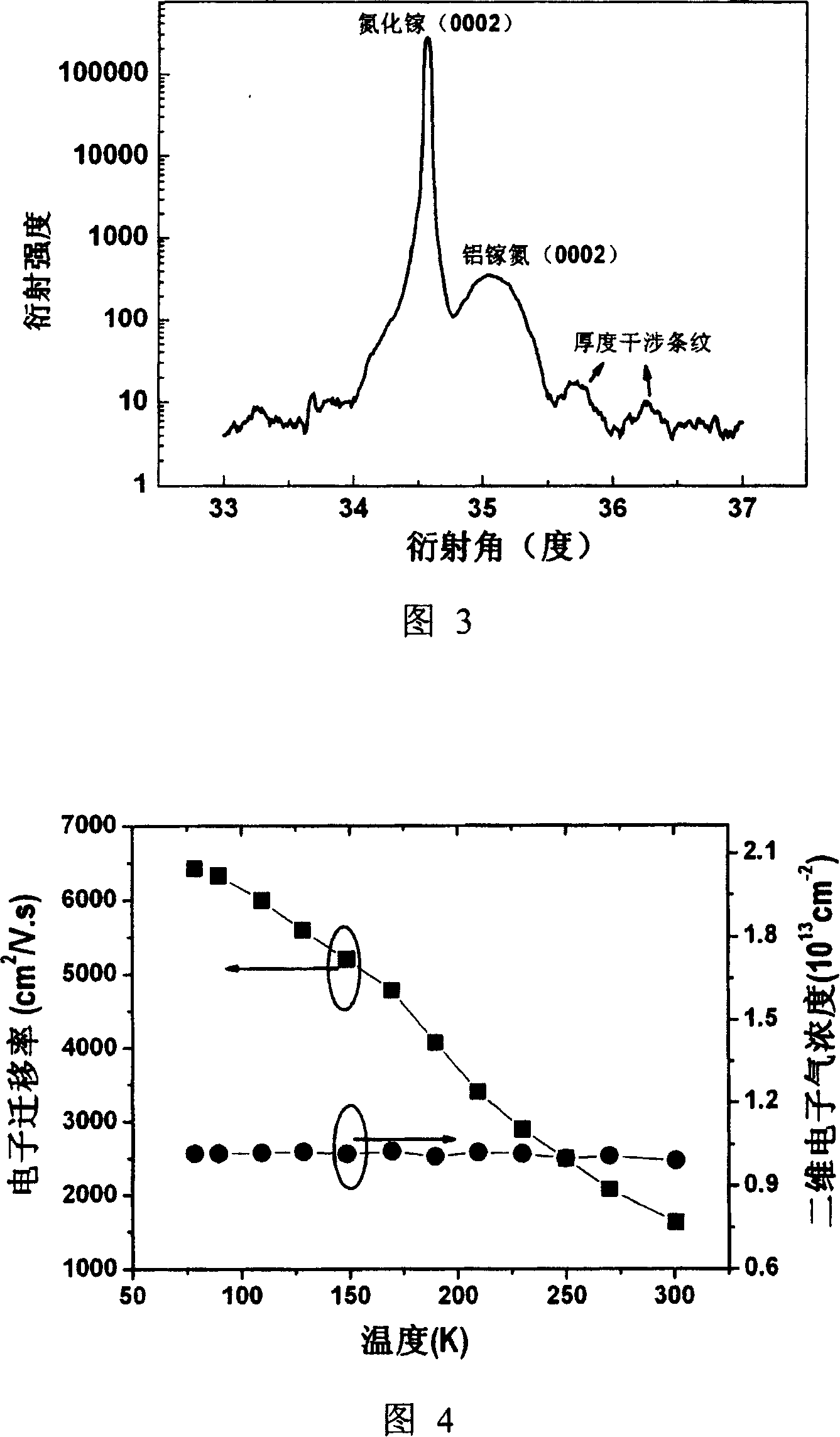

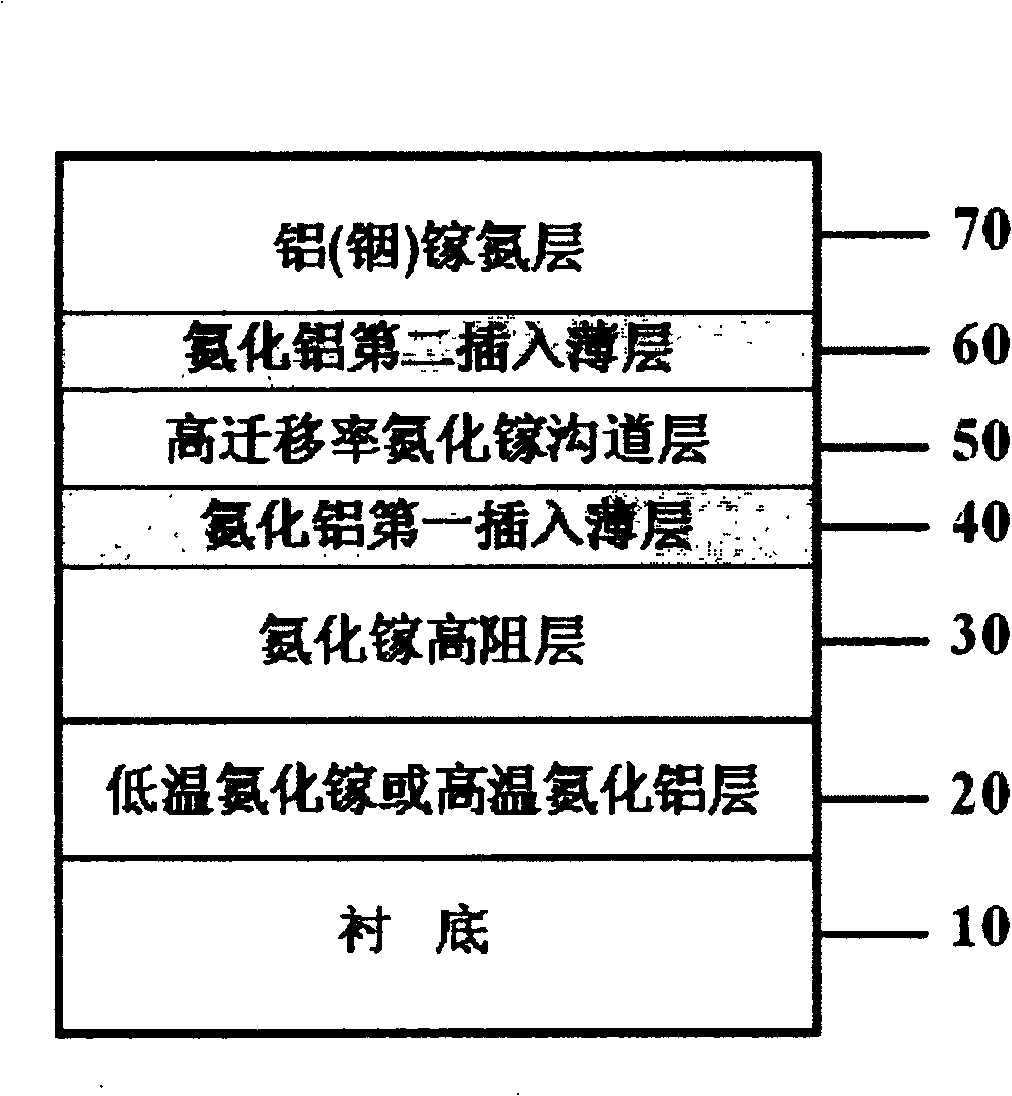

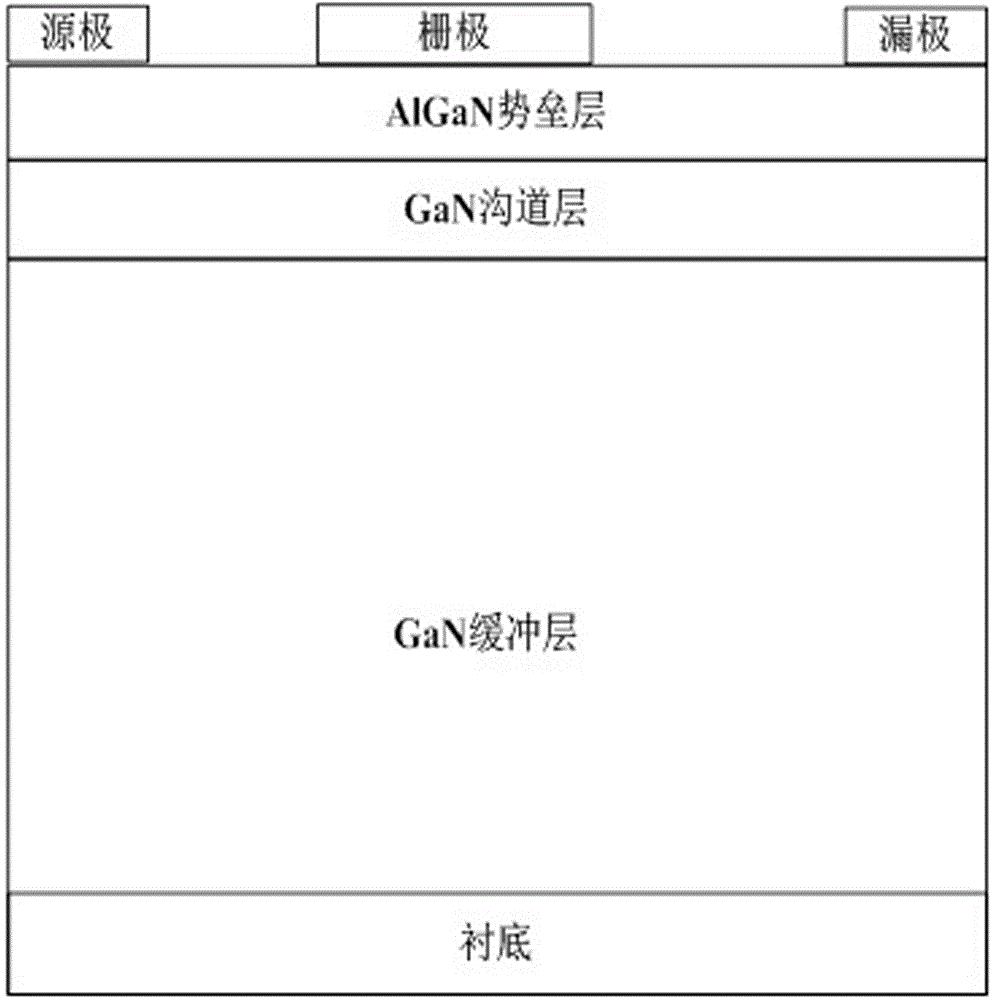

Gallium nitride radical heterojunction field effect transistor structure and method for making the same

InactiveCN101140947AImprove crystal qualityReduce defect densitySemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideHeterojunction field effect transistor

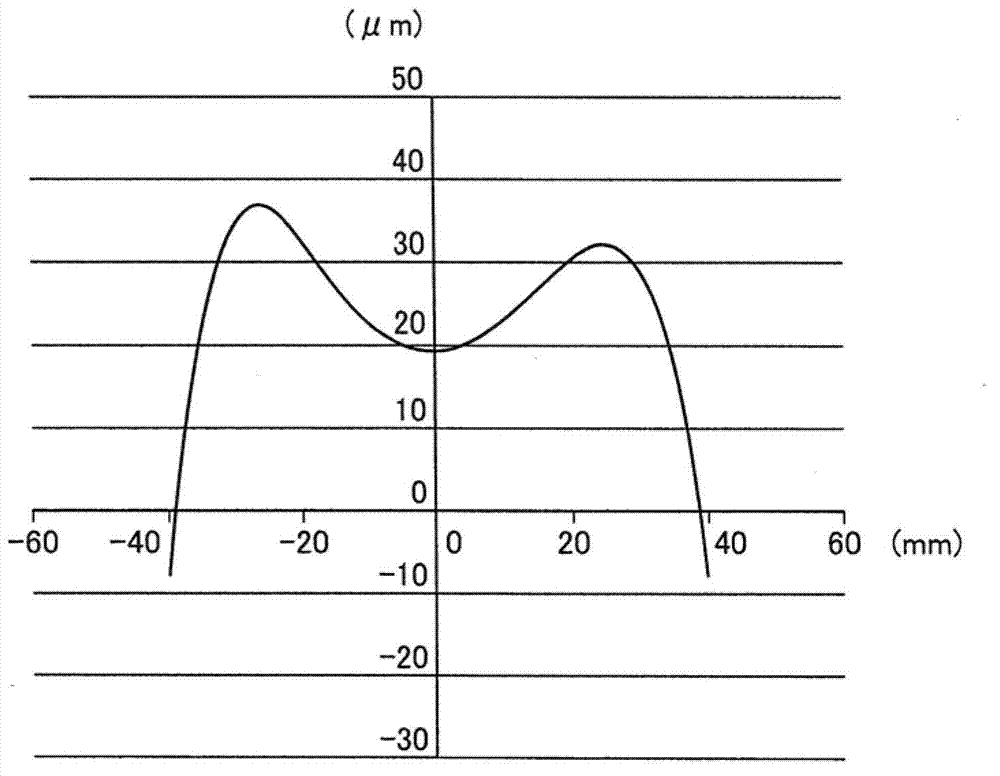

The invention is a GaN-based HFET structure, which comprises an underlay, a low-temperature GaN nucleating layer which is set on the underlay; a resistive formation doped or unintended doped with GaN, which is made on the upside of the low-temperature GaN nucleating layer; an unintended doped high mobility GaN layer, which is set on the upside of the resistive formation unintended doped with GaN; an aluminum nitride interposed layer, which is made on the unintended doped high mobility GaN layer; a component step change AlxInyGazN layer unintended doped or doped in type N, which is set on the aluminum nitride interposed layer.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

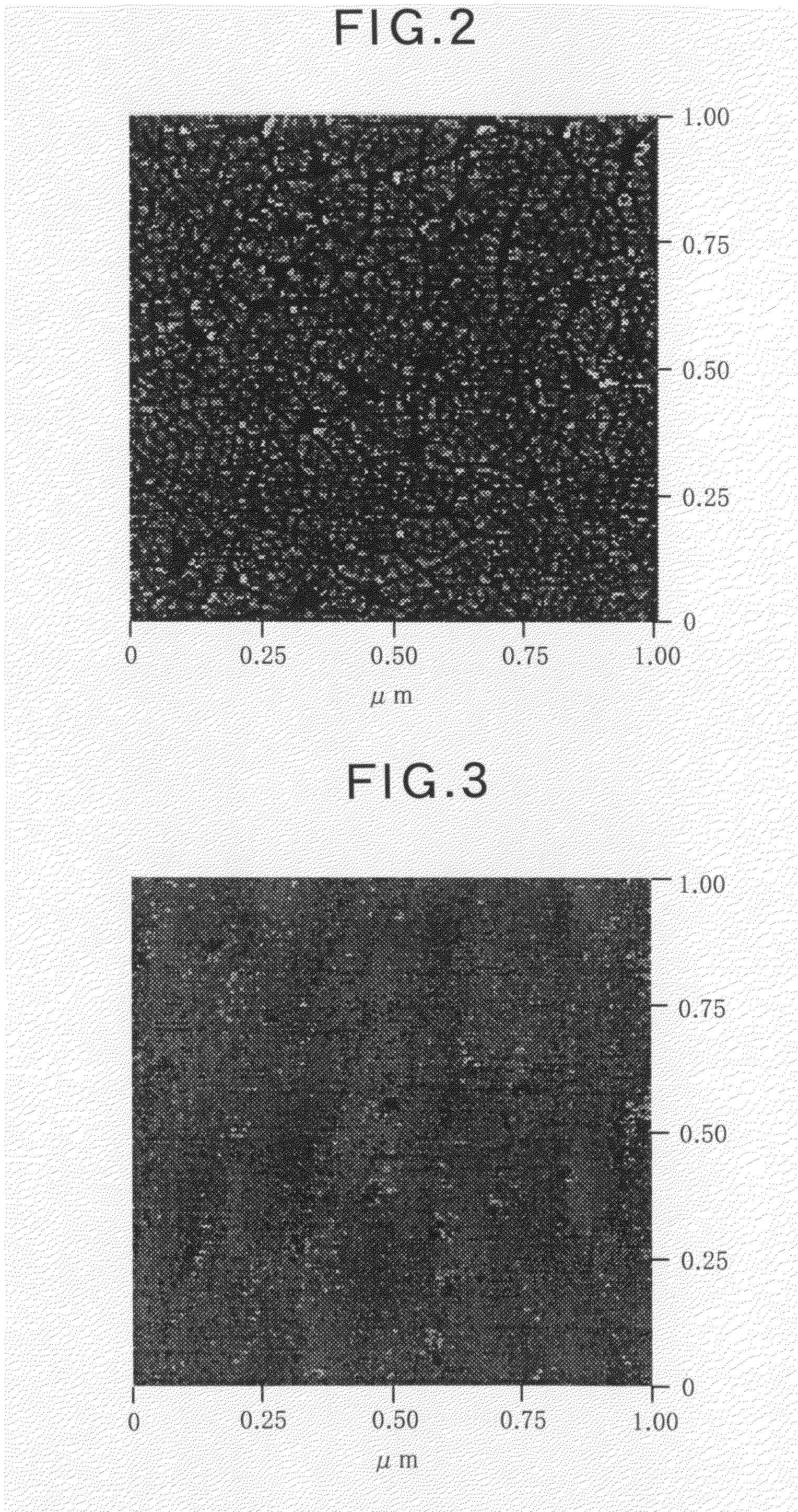

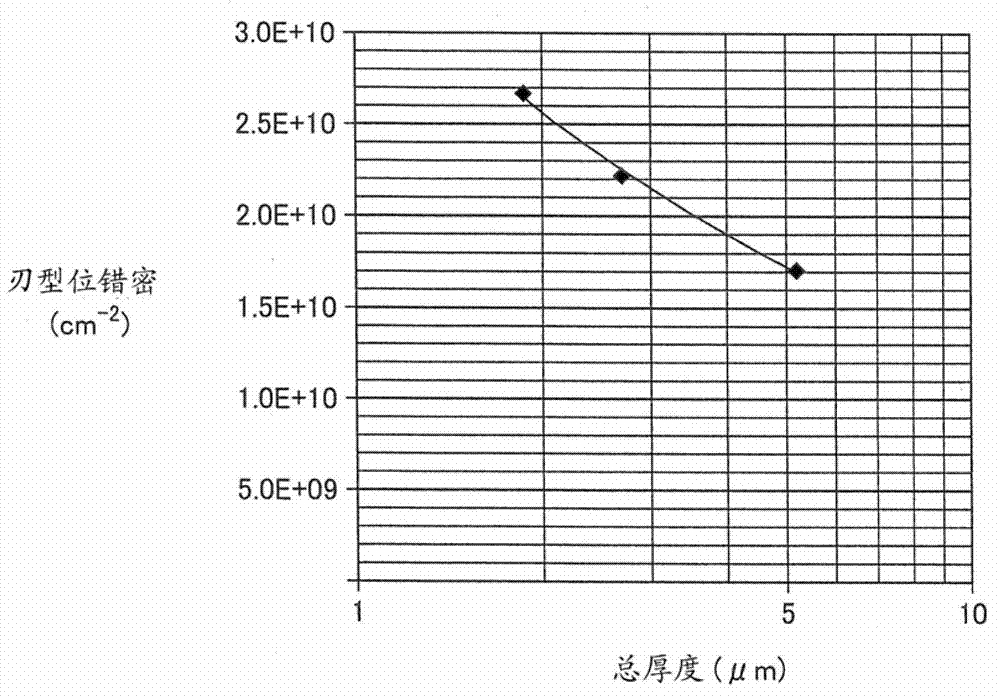

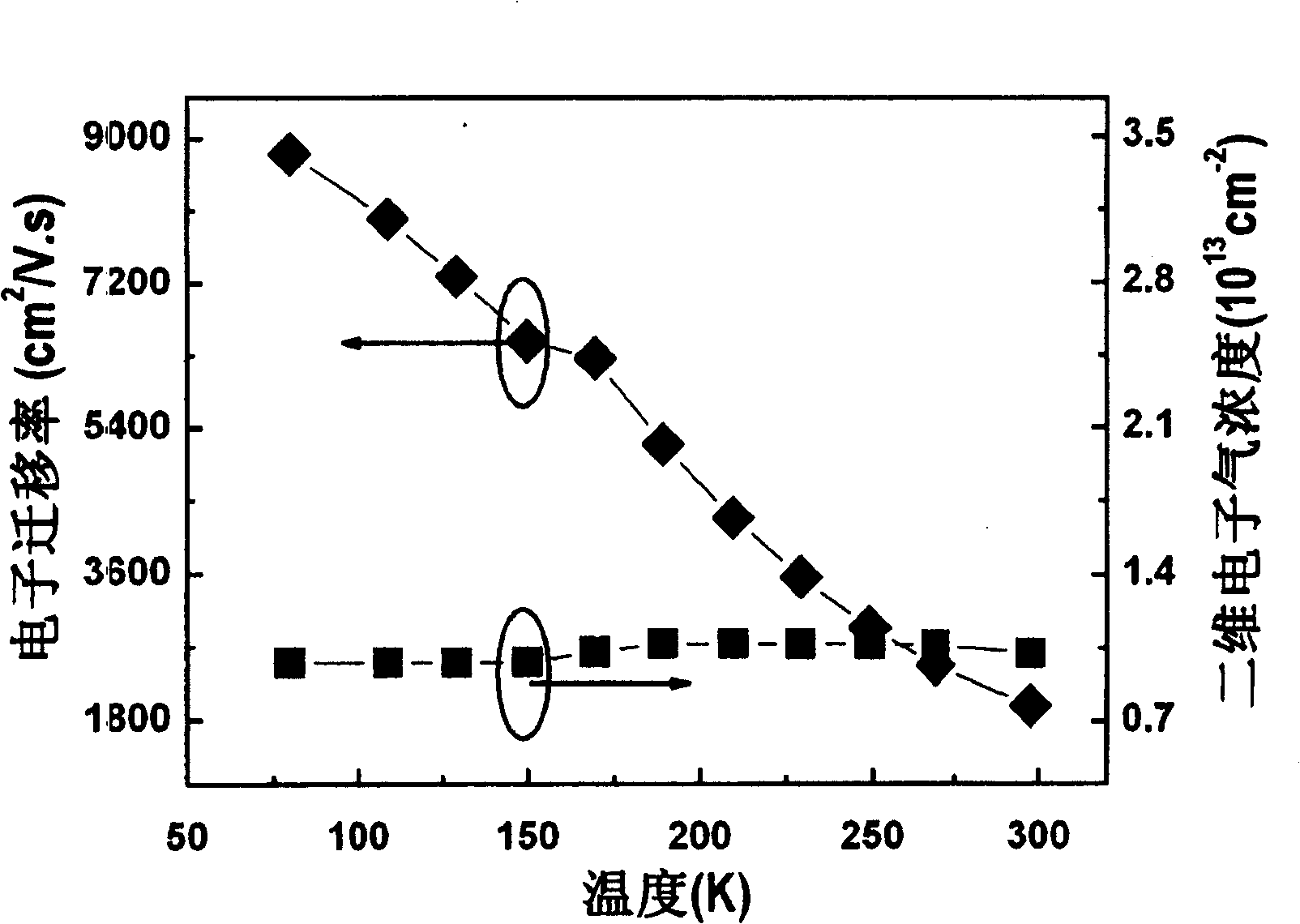

Method for improving gallium nitride based transistor material and device performance using indium doping

ActiveCN101114594AFree diffusionIncrease the diffusion distanceSemiconductor/solid-state device manufacturingGas phaseSingle crystal

The invention discloses a method of increasing the properties of the gallium nitride-based transistor material and device with indium doping and applies in the field of making gallium nitride-based HEMT or HFET materials and devices. The method and process is to form the gallium nitride-based high electron mobility transistor or heterostructure field effect transistor materials on SiC or Si single crystal substrate grown by metal-organic chemical vapor deposition epitaxial growth system. After the AlN or AlGaN nucleating layer and the GaN buffer layer are grown on the SiC or Si single crystal substrate, a GaN channel layer, an AlN insert layer, an AlGaN barrier layer and a GaN capped layer are grown, and trimethyl indium is added in the growth atmosphere to do epitaxial growth with indium doping. The dislocation of the material or device made by the method of the invention is reduced greatly. The invention improves the interfacial smoothness, increases the electron mobility of the material, increases the growth window, ensures the material grow easier, improves the current collapse of the device, reduces the leakage current and increases transconductance and gain and increases the output power of microwave power devices.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

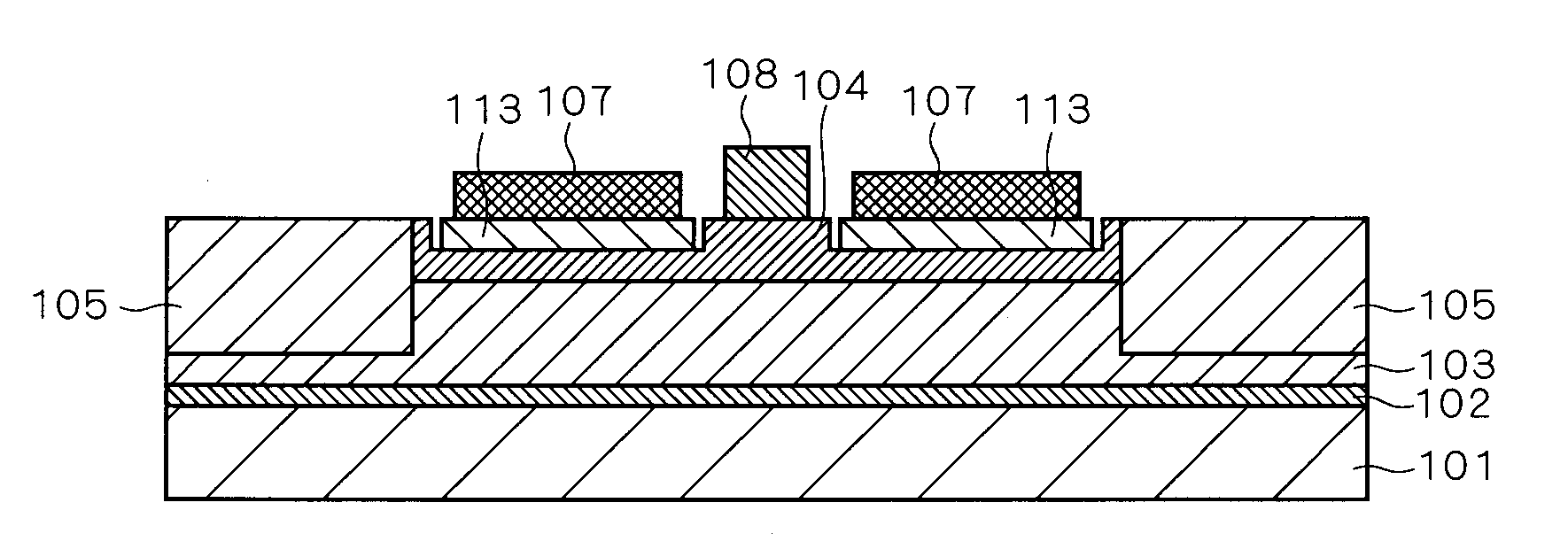

Heterojunction field effect transistor and manufacturing method thereof

InactiveUS20040079965A1Improve performanceLittle deteriorationSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionCharge carrier

In a heterojunction FET in which source and drain areas are formed by carrying out high temperature annealing process after carrying out ion implantation in areas to be formed into source and drain areas, conventionally, the N-type carrier supply layer and the N-type active layer are doped with Si. In place of doping with Si, doping with Se or Te is adopted. Thereby, in high temperature annealing process for activating the ion implanted areas, which serves as source and drain areas, unlike the Si donor, inactivation of donor due to reaction with F-atoms occurs scarcely with respect to the diffusion of F-atoms on the surface of the epitaxial substrate, which adhered during the process. Further, since the Se and Te are impurities from VI-family, when the Se or Te occupies any grid position of atoms from III-family or V-family, the Se or Te serves as the donor. Accordingly, a high performance heterojunction FET of little deterioration of the FET characteristics can be obtained.

Owner:PANASONIC CORP

Heterojunction field effect transistor and manufacturing method thereof

InactiveUS20090045439A1Semiconductor/solid-state device manufacturingSemiconductor devicesElectronCondensed matter physics

A heterojunction field effect transistor includes a laminated body. The laminated body includes a channel layer of GaN, an electron supply layer of AlN or AlxGa1-xN (0.6≦x<1) formed on the channel layer, and a cap layer of GaN formed on the electron supply layer.

Owner:OKI ELECTRIC IND CO LTD

Heterojunction field effect transistor based on channel array structure

InactiveCN102201442AMeet the needs of practical applicationsSemiconductor devicesElectrical conductorHeterojunction field effect transistor

The invention relates to a heterojunction field effect transistor based on a channel array structure. The heterojunction field effect transistor comprises a heterojunction which comprises a first semiconductor layer and a second semiconductor layer which are stacked from top to bottom; a two-dimensional electron gas is formed on the interface of the first semiconductor layer and the second semiconductor layer; a source electrode, a drain electrode and a grid electrode are arranged on the first semiconductor layer; the grid electrode is arranged between the source electrode and the drain electrode; and more than one channels are formed in the heterojunction under the grid electrode, and two ends of the channel respectively point to the source electrode and the drain electrode. In the invention, the structural design based on the channel array is adopted, and an annular gate structure is formed by covering a gate metal on the top part of the channel and the side walls on two sides, so that the capability of modulating the channel is strengthened. The heterojunction field effect transistor is suitable for all semiconductor electron devices working based on the two-dimensional electron gas on the heterojunction node interface, and various requirements of practical application can be met simultaneously.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

Gallium-nitride-based heterostructure field effect transistor with composite barrier layers

ActiveCN104201202ASuppression of short channel effectsImprove pressure resistanceSemiconductor devicesGallium nitrideDrift velocity

The invention discloses a gallium-nitride-based heterostructure field effect transistor with composite barrier layers. The composite barrier layers are formed by AlInGaN material with different polarization intensities. When the AlInGaN composite barrier layer with low polarization intensity is located at a grid drain terminal, the density of two-dimensional electron gas (2DEG) of the channel below the barrier layer is smaller than that of the 2DEG at other positions of the channel drain terminal, an LDD structure is formed, and the electric field distribution of the channel is modulated to increase voltage endurance capability; when the AlInGaN composite barrier layer with low polarization intensity is located right below a grid, a below-grid gallium nitride (GaN) channel guide strip bottom is distributed in a stepped manner, the drift speed of a below-grid channel carrier is increased due to barrier descending, electric field peak is generated between AlInGaN composite barrier layer with two different elemental components, and more potential is distributed at the grid drain terminal instead of the whole grid to restrain drain induced barrier lowering (DIBL).

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

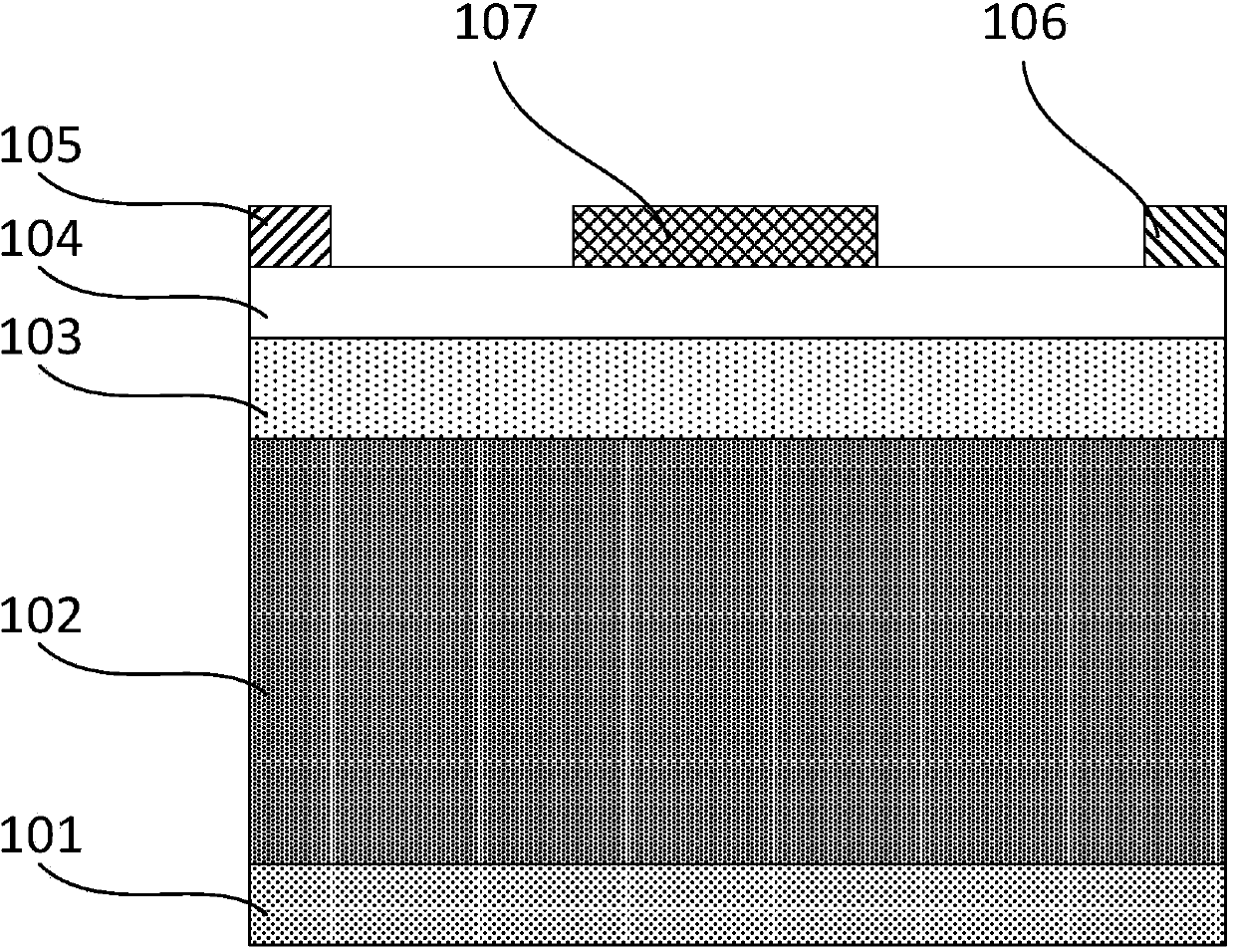

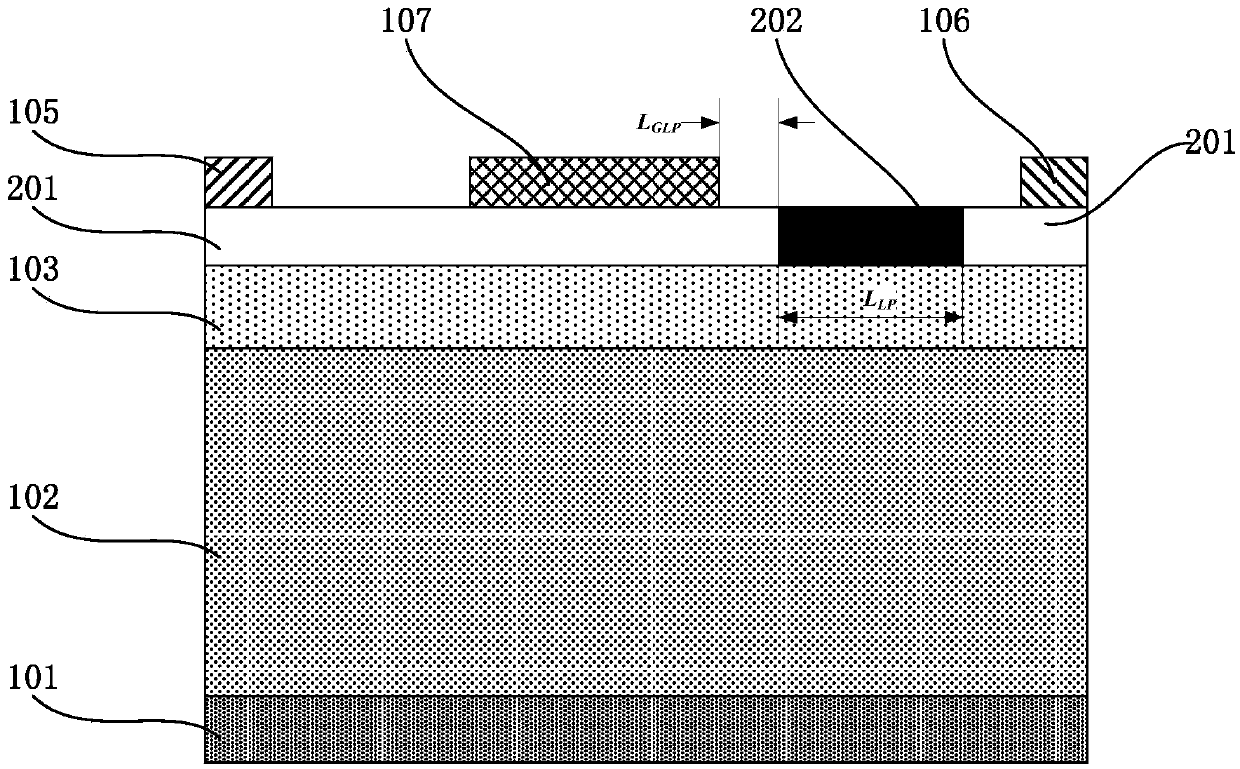

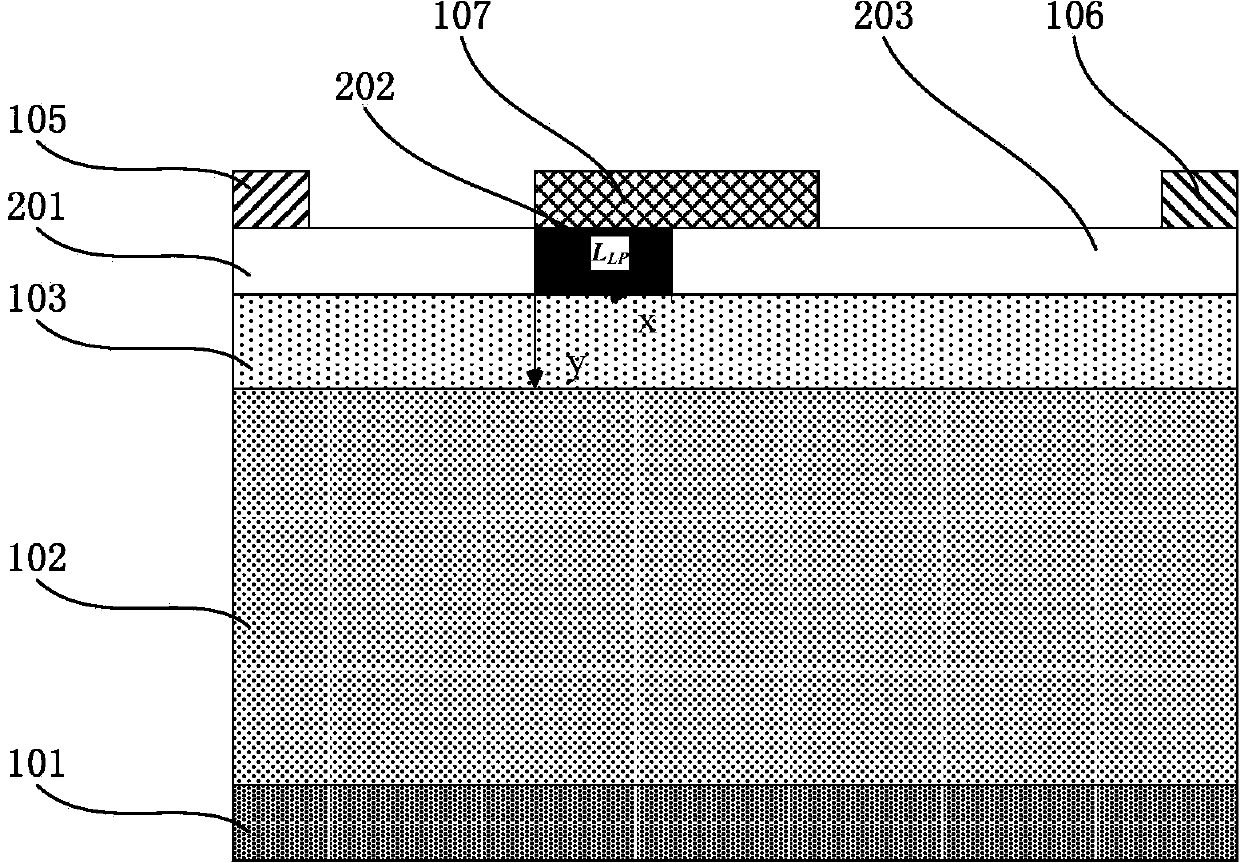

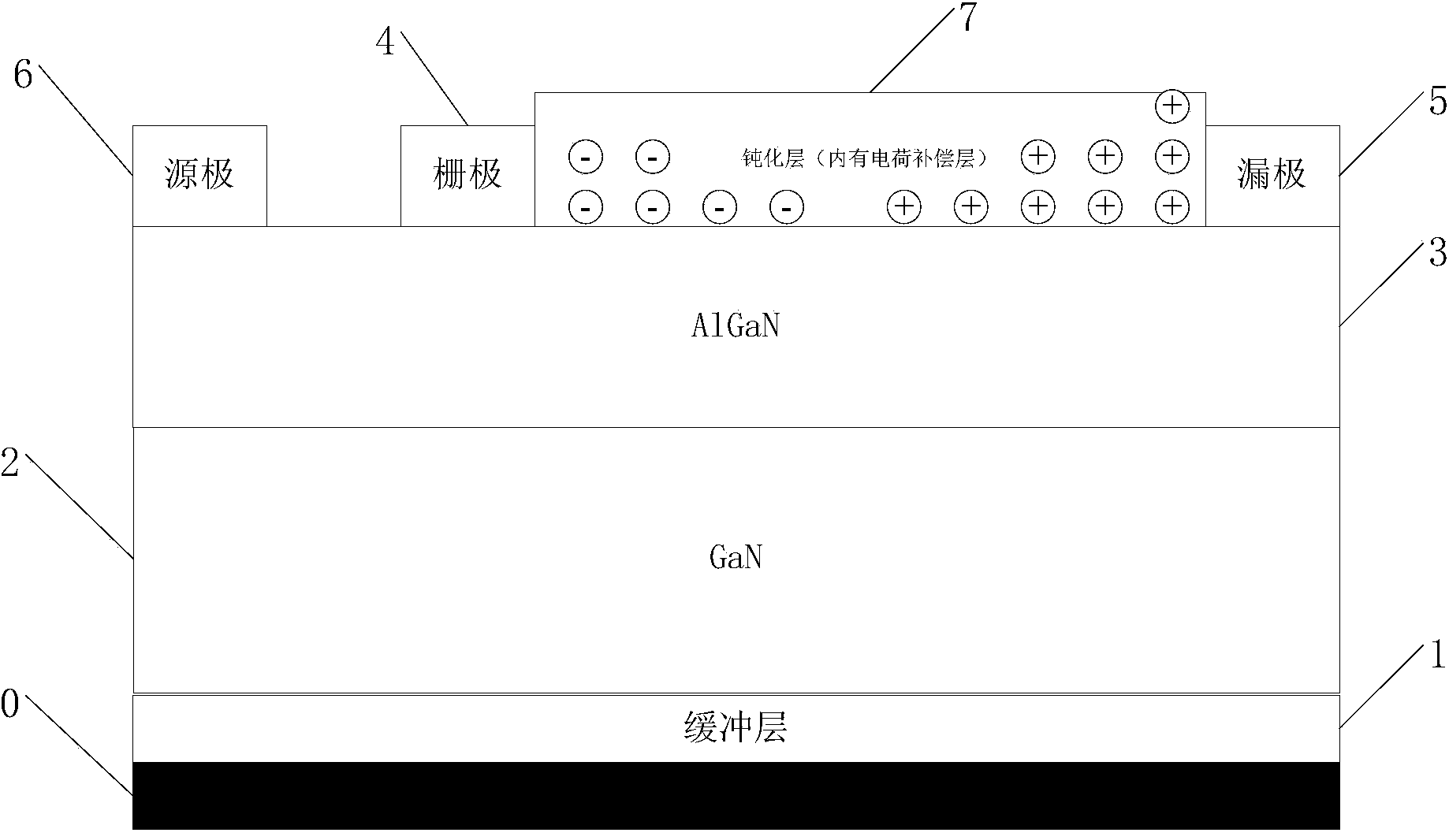

AlGaN/GaN heterojunction field effect transistor

ActiveCN104009076ADoes not affect junction polarization effectsHigh electric field reductionSemiconductor devicesElectric field modulationHeterojunction

The invention discloses a novel AlGaN / GaN high-electronic-mobility transistor with the passivation layer charge compensation function. According to the novel crystal structure, charges are injected into a surface passivation layer between the grid electrode and the drainage electrode of the transistor, so that a charge compensation layer is formed, the charges exist on the surface of the transistor, surface electric fields are re-distributed through the electric field modulation effect on the premise that the AlGaN / GaN heterojunction polarization effect is not affected, a new electric field peak is generated, in this way, high electric fields on the edge of the grid electrode and at the drainage end are lowered, the surface electric fields tend to be even, and compared with a traditional structure, the breakdown voltage and the reliability of devices are improved remarkably; in addition, due to the fact that the charge compensation layer has the charge compensation function, the carrier concentrations of channels are re-distributed, the on resistance of the devices is reduced, and the output current is increased.

Owner:XIDIAN UNIV

Heterojunction field effect transistors using silicon-germanium and silicon-carbon alloys

InactiveUS6936869B2Without of performanceWithout strainTransistorSolid-state devicesHeterojunctionSemiconductor

Semiconductor devices, e.g., heterojunction field effect transistors, fabricated with silicon-germnanium buffer layer and silicon-carbon channel layer structures. The invention provides a method of reducing threading defect density via reducing germanium content in a SiGe relaxed buffer layer on which a strained silicon channel layer is formed, by forming the strained silicon channel layer of a silicon-carbon alloy, e.g., containing less than about 1.5 atomic % C substitutionally incorporated in the Si lattice of the alloy.

Owner:INTERNATIONAL RECTIFIER COEP

Epitaxial wafer including nitride-based semiconductor layers

InactiveCN102891174AReduce dislocation densitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor packageNitride

Owner:SHARP KK

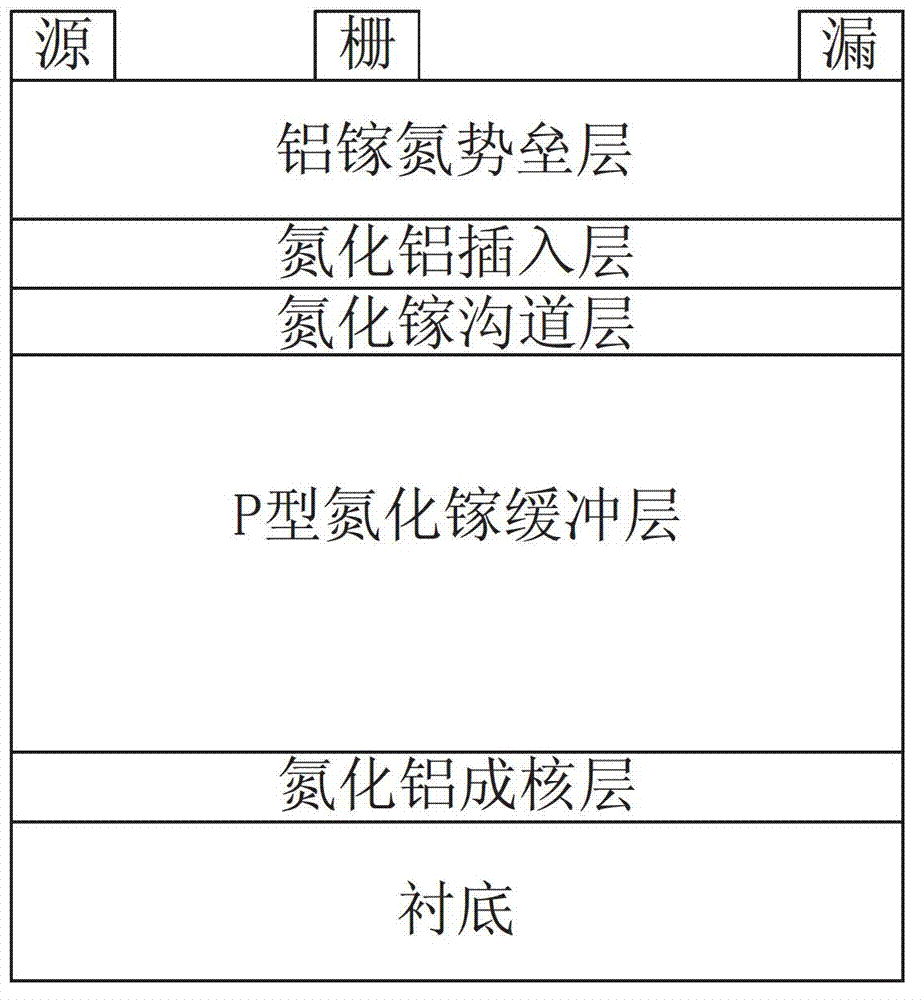

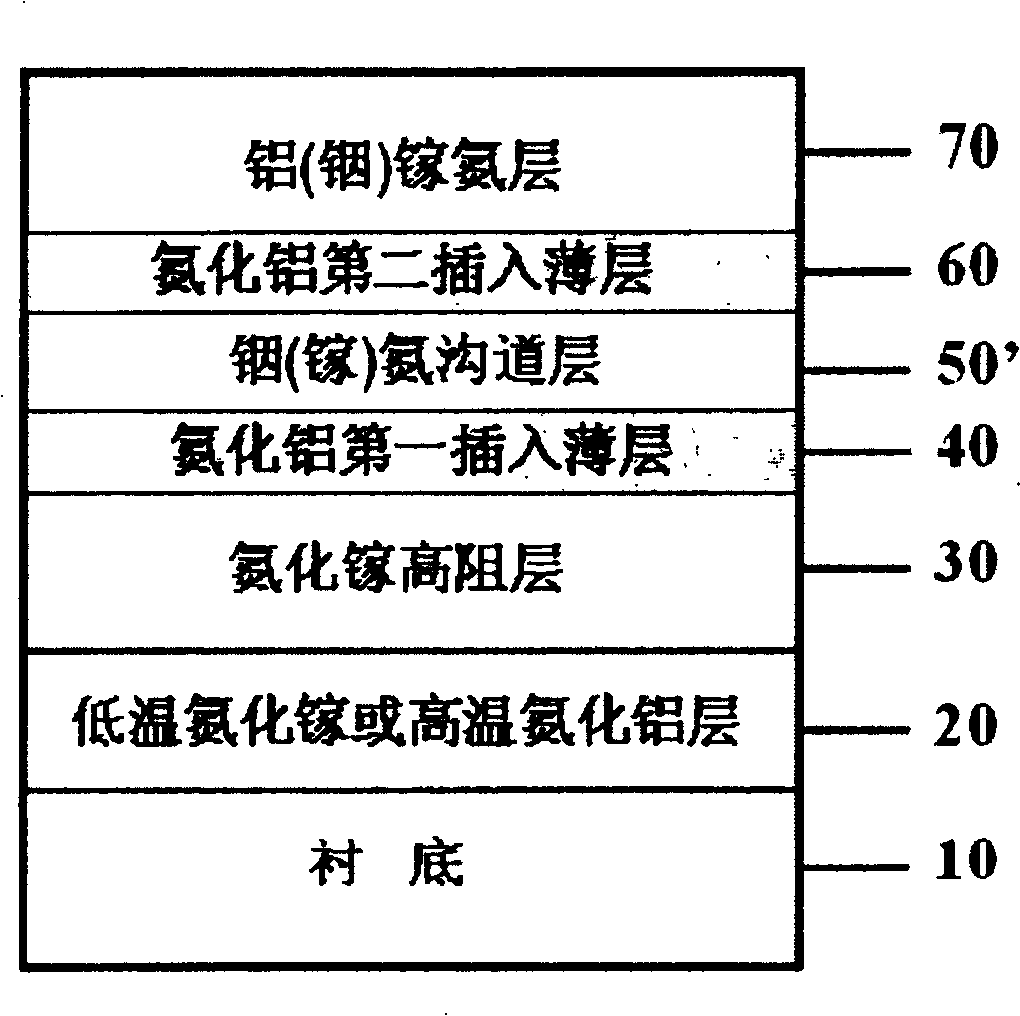

GaN dual heterogeneity node field effect transistor structure and its making method

InactiveCN101266999ARaise the barrier heightImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerGallium nitride

A gallium nitride-based double heterojunction field effect transistor structure comprises a substrate, a low temperature gallium nitride layer or high temperature aluminum nitride layer formed on the substrate; a high insulation layer with unintentional-doped or doped gallium nitride; the high insulation layer with unintentional-doped or doped gallium nitride is formed on a low temperature gallium nucleation layer or a high temperature gallium nitride nucleation layer; a first aluminum nitride inserting layer, the first aluminum nitride inserting layer is formed on the high insulation layer with unintentional-doped or doped gallium nitride; a unintentional-doped gallium nitride channel layer, the unintentional-doped gallium nitride channel layer is formed on the first aluminum nitride inserting layer; a second aluminum nitride inserting layer, the second aluminum nitride inserting layer is formed on the unintentional-doped gallium nitride channel layer, an unintentional-doped or n-type doped AlxInyGazN layer, the unintentional-doped or n-type doped AlxInyGazN layer is formed on the second aluminum nitride inserting layer.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

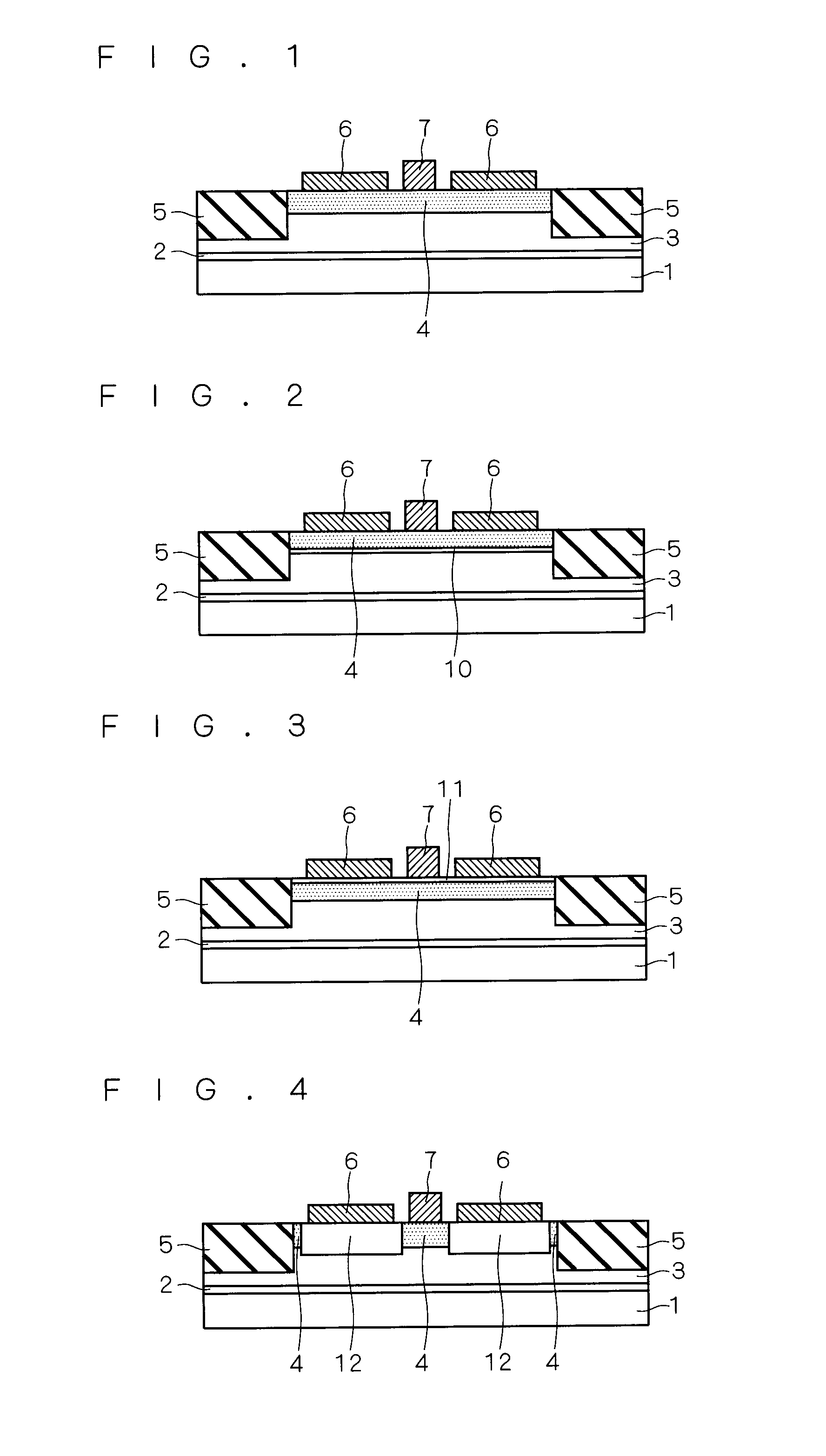

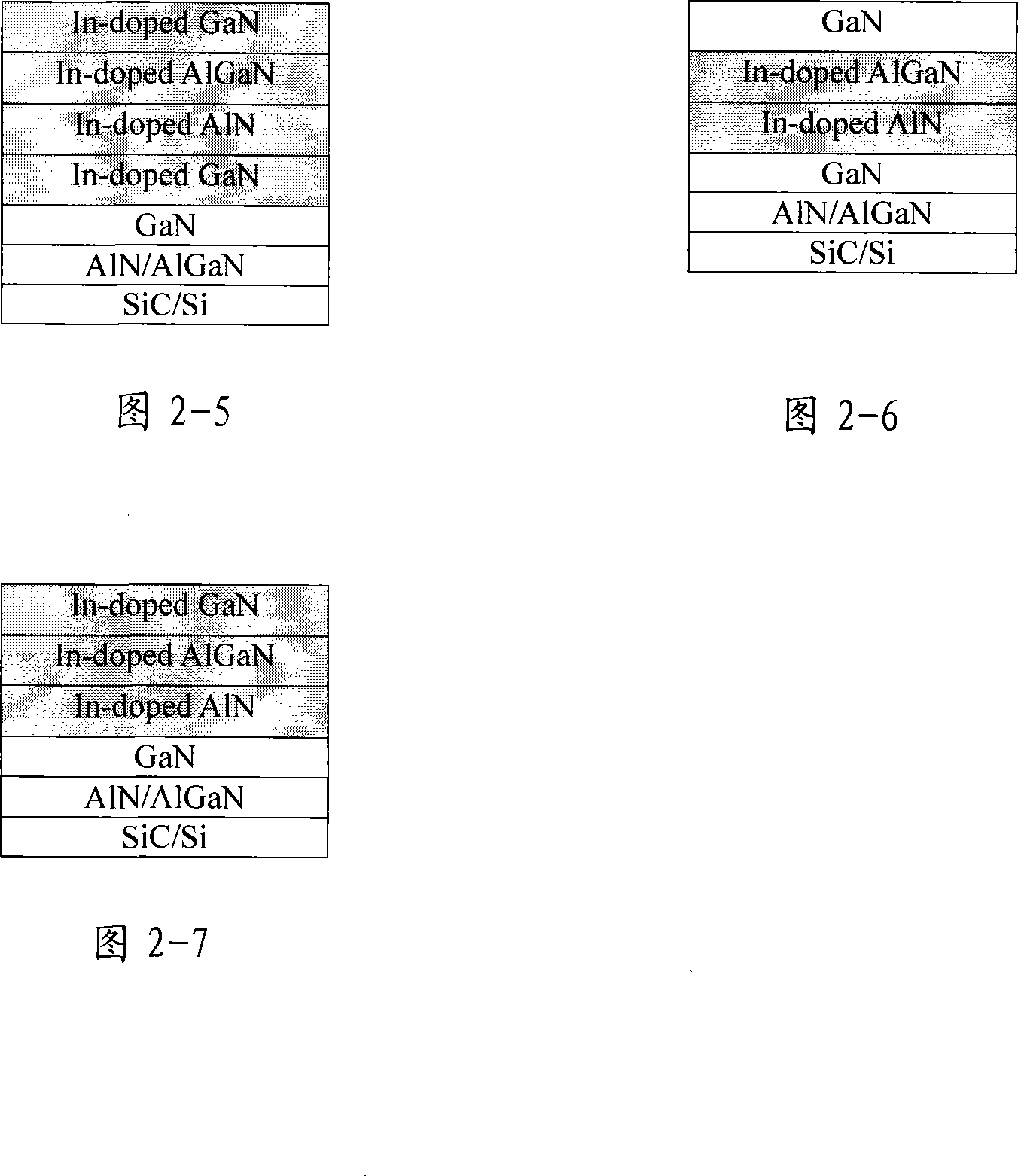

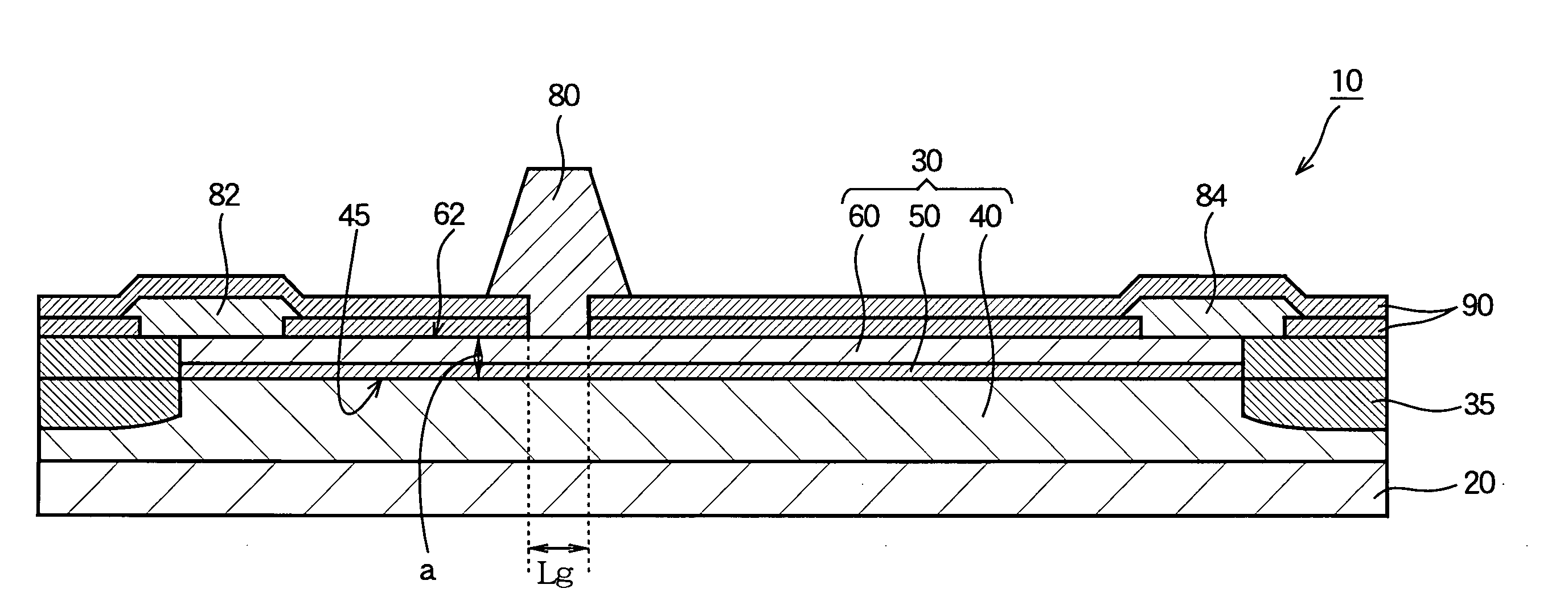

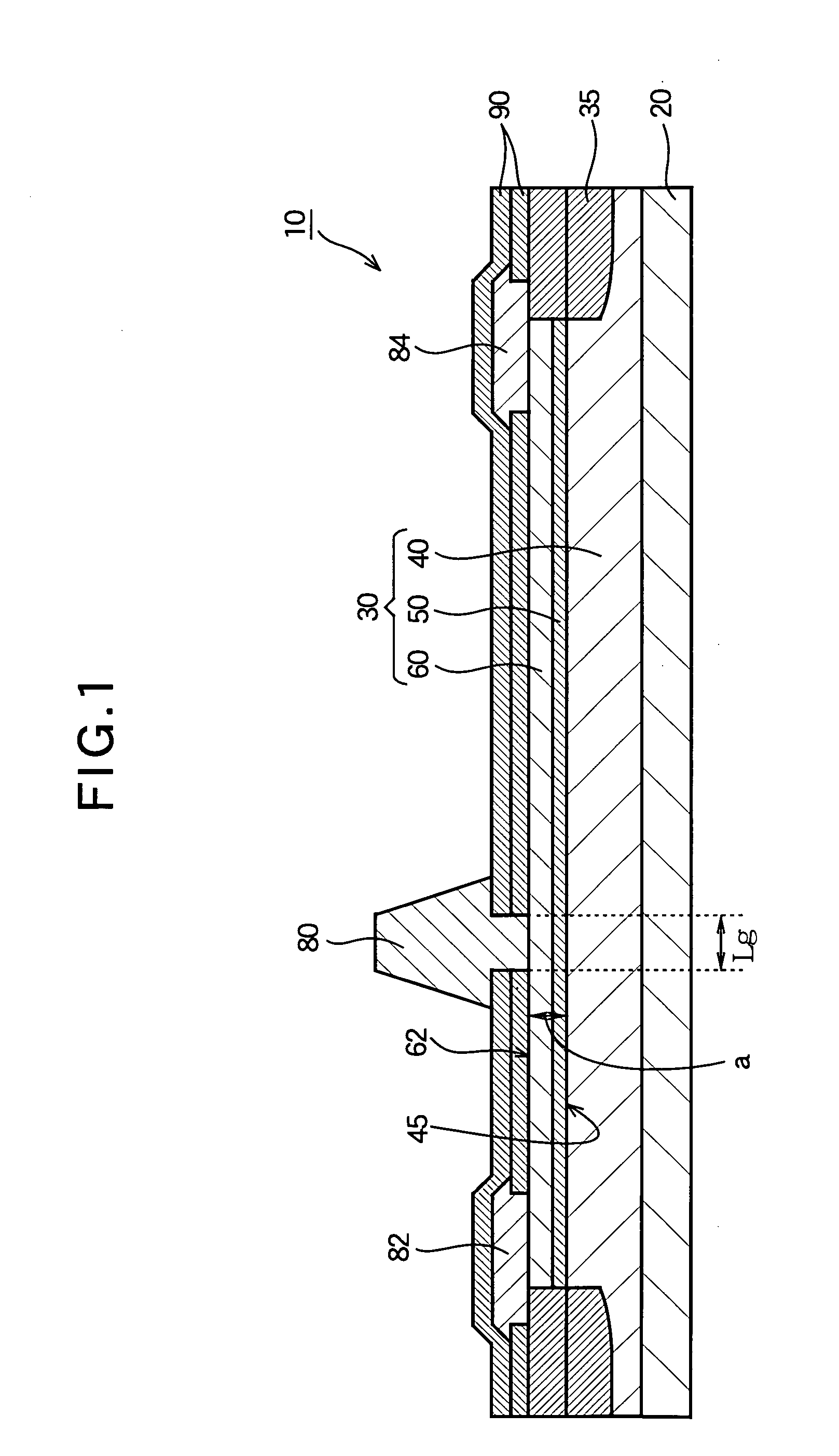

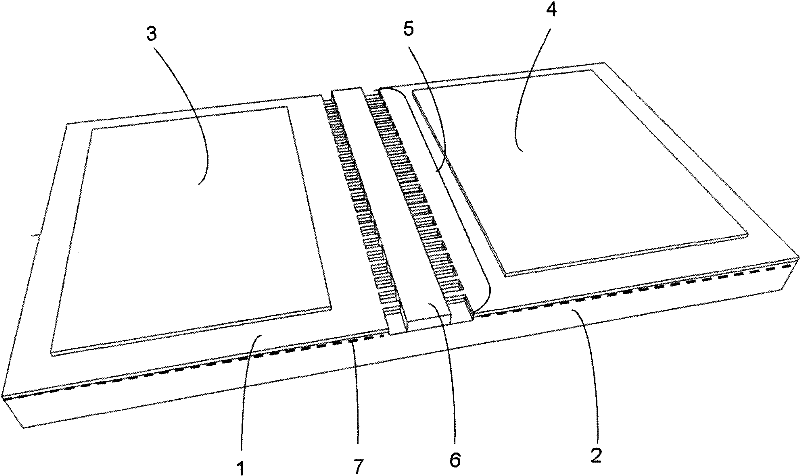

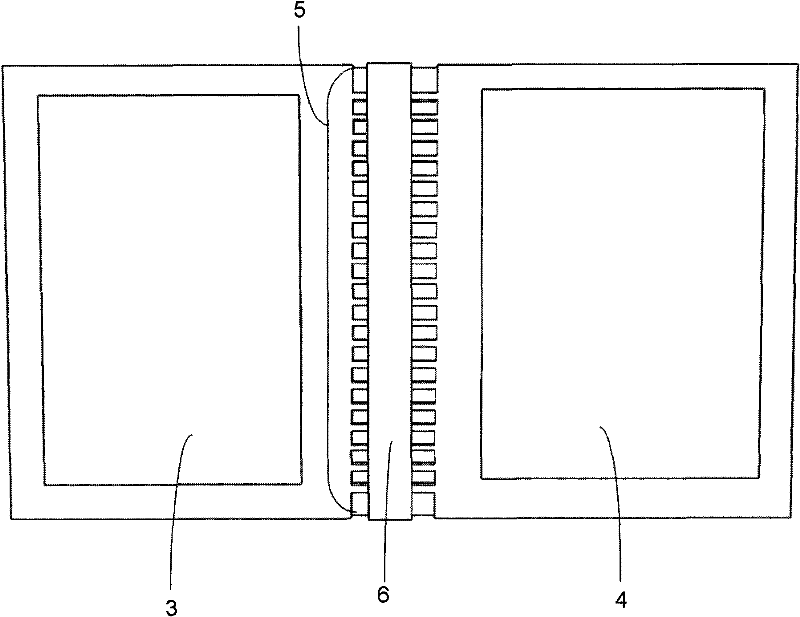

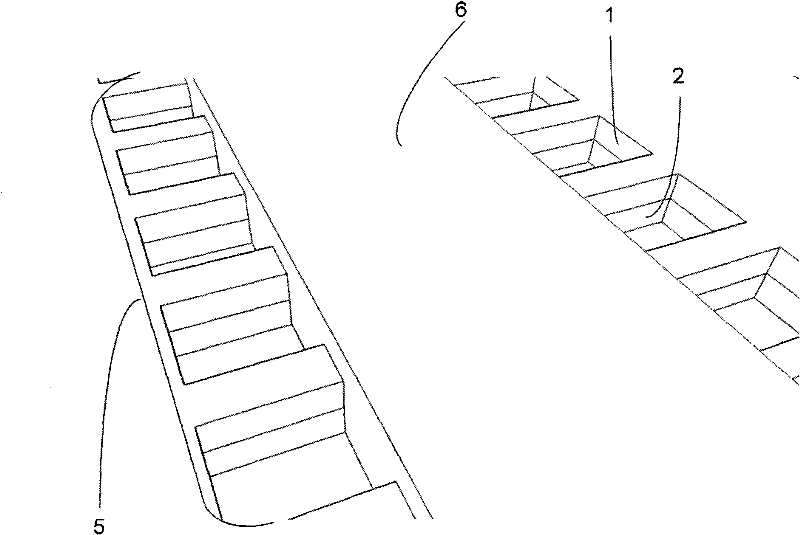

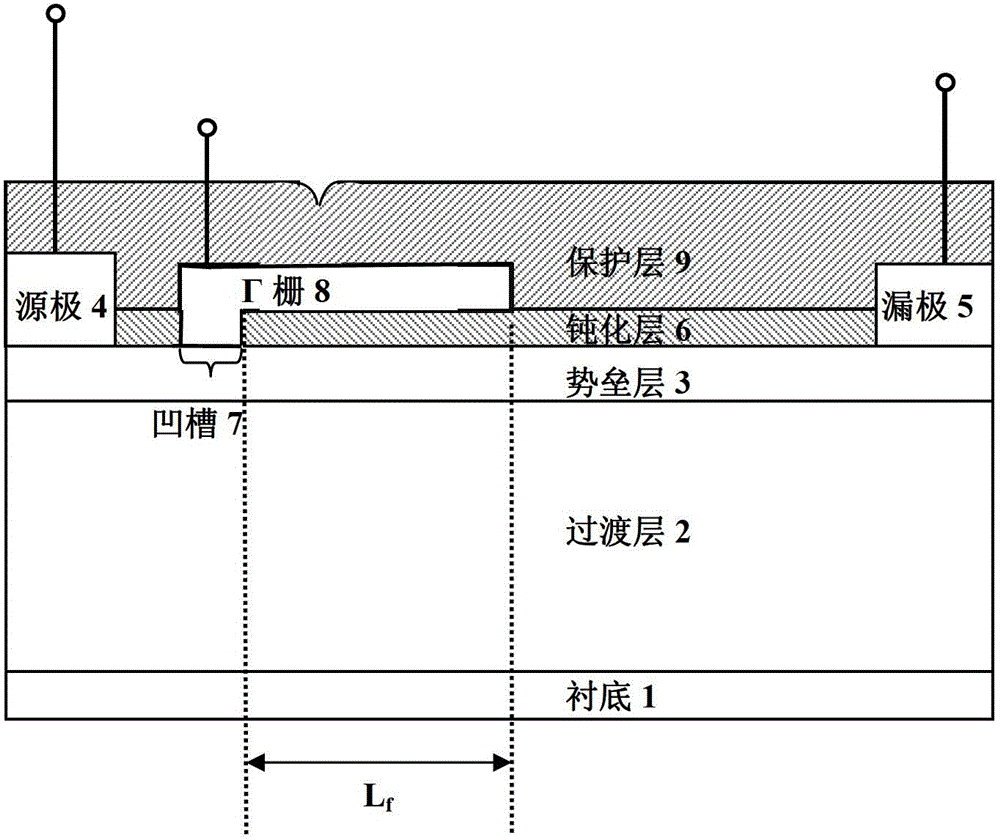

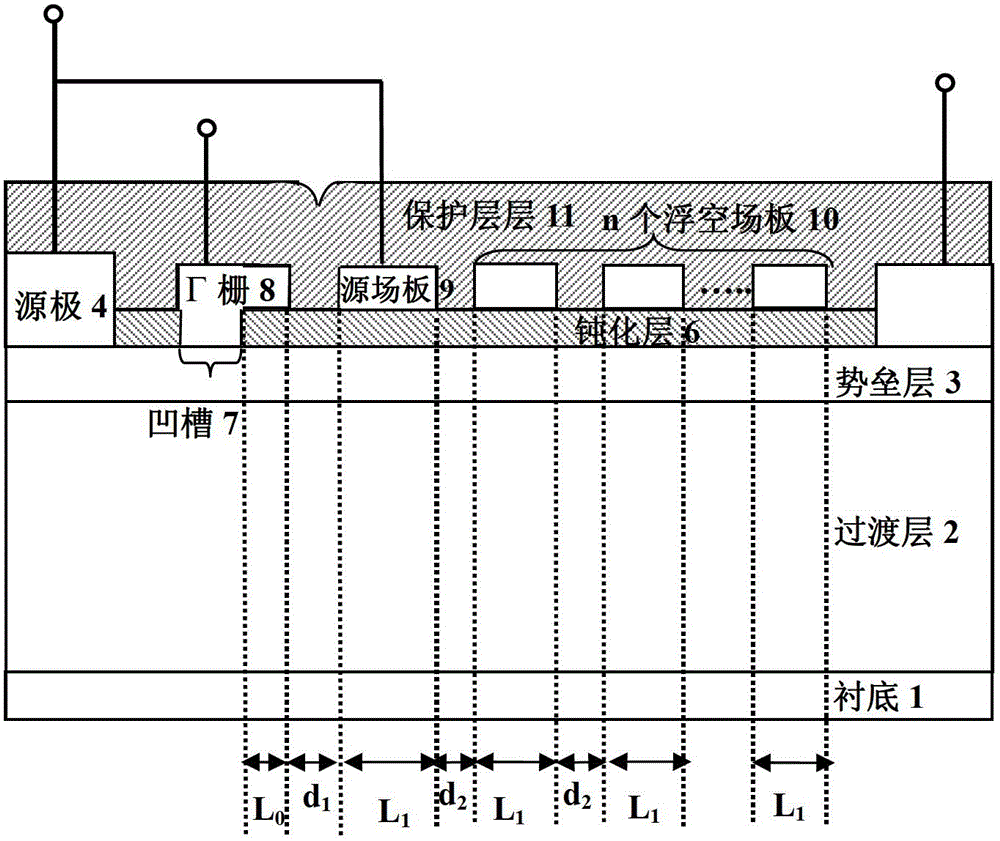

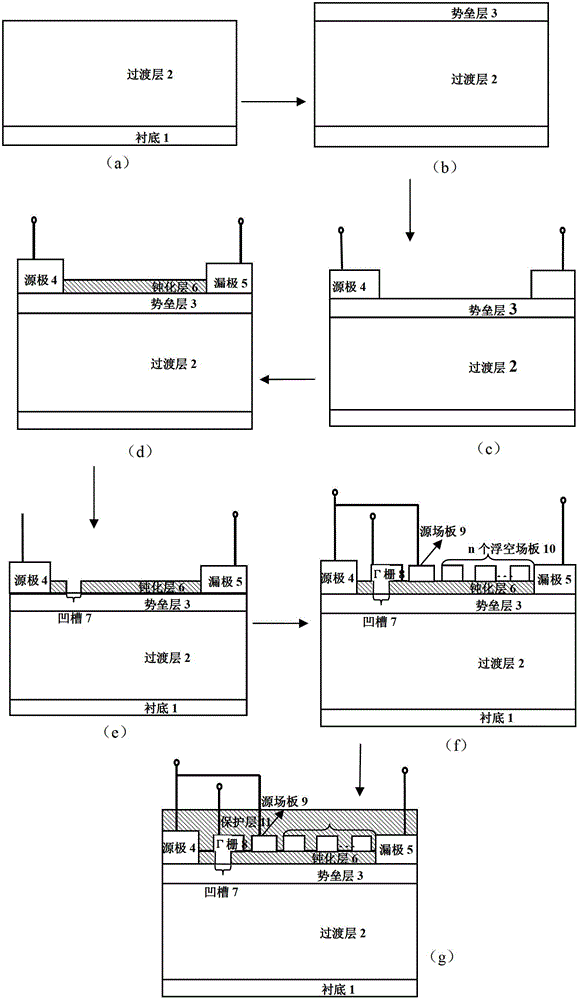

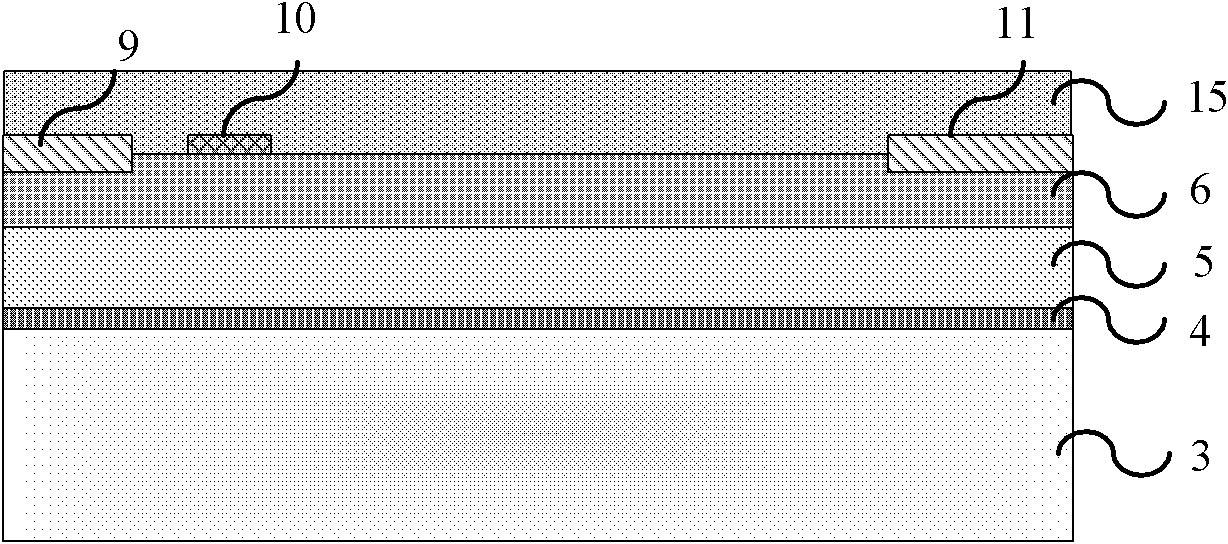

Source-field-plate heterojunction field-effect transistor and manufacturing method thereof

InactiveCN102881722AImprove breakdown characteristicsIncrease the length of the high-resistance depletion regionSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceSource field

The invention discloses a source-field-plate heterojunction field-effect transistor and a manufacturing method, and mainly solves the problems of low breakdown voltage and low power gain in the conventional field-plate technology. The source-field-plate heterojunction field-effect transistor comprises a substrate (1), a transition layer (2), a potential barrier layer (3), a source electrode (4), a drain electrode (5), a passivating layer (6), a Gamma-shaped grid (8) and a protective layer (11), wherein the passivating layer (6) is provided with a groove (7); a part of the Gamma-shaped grid (8) is positioned in the groove (7), and the other part of the Gamma-shaped grid (8) is positioned at the upper part of the passivating layer (6); the passivating layer (6) between the Gamma-shaped grid (8) and the drain electrode (5) is provided with a source field plate (9) and n floating metal field plates (10); the source field plate (9) is connected with the source electrode (4); the floating metal field plates are same in length, and the distances among the field plates are same; and the Gamma-shaped grid (8), the source field plate (9) and the n floating metal field plates (10) are manufactured by using a same metal deposition process so as to form the source-field-plate heterojunction field-effect transistor. The source-field-plate heterojunction field-effect transistor and the method have the advantages of high breakdown voltage, little grid-drain feedback capacitance, high power grain and simpleness for process, and is applicable to high-frequency and large-power III-V compound microwave power devices.

Owner:XIDIAN UNIV

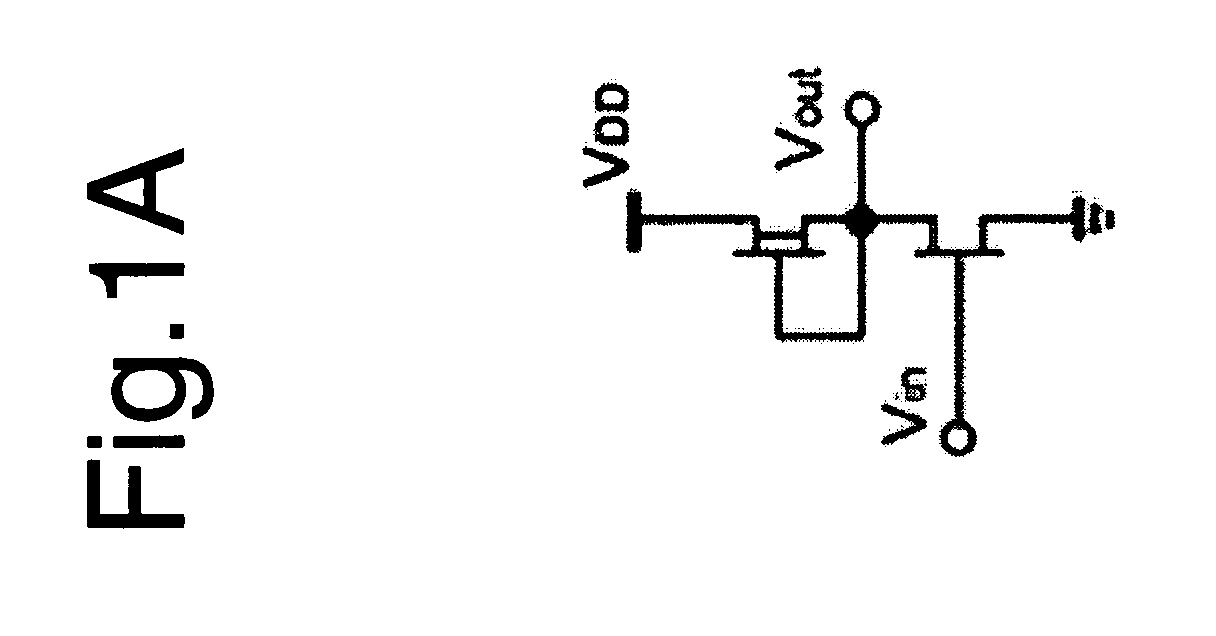

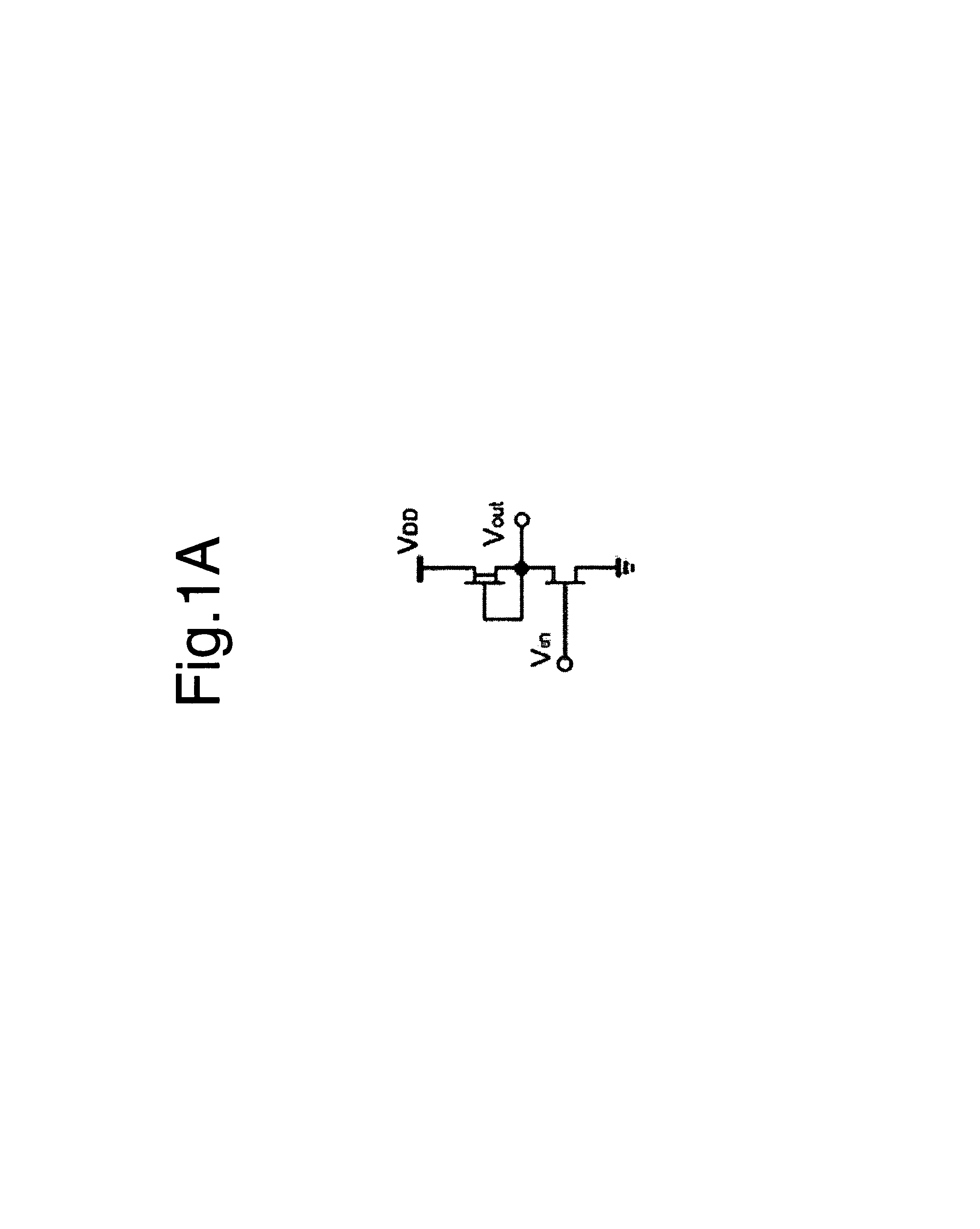

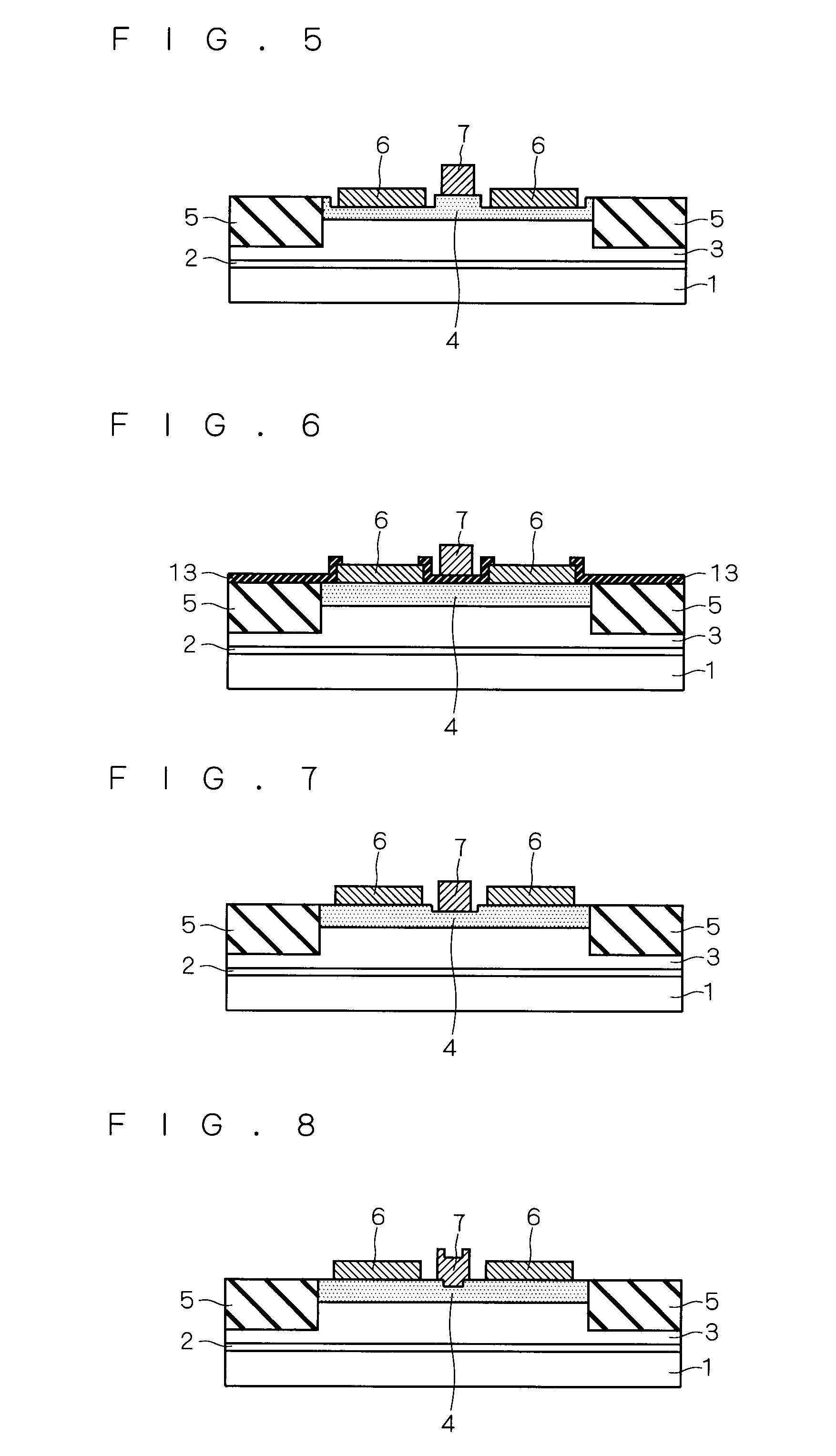

Enhanced GaN heterojunction field effect transistor based on metal oxide semiconductor (MOS) control

InactiveCN102194819ALower on-resistanceWith high withstand voltageTransistorPower semiconductor deviceLow voltage

The invention provides an enhanced GaN heterojunction field effect transistor based on metal oxide semiconductor (MOS) control and belongs to the technical field of power semiconductor devices. The enhanced GaN heterojunction field effect transistor comprises a monolithic integrated low-voltage MOS tube and a depletion mode GaN heterojunction field effect transistor, wherein the drain of the MOS tube is connected with the source of the depletion mode GaN heterojunction field effect transistor; the grid of the MOS tube and the grid of the depletion mode GaN heterojunction field effect transistor are connected with each other or the grid of the GaN heterojunction field effect transistor is connected with the source of the MOS tube; and the MOS tube and the depletion mode GaN heterojunction field effect transistor are isolated from each other by using a medium isolation slot. In the enhanced GaN heterojunction field effect transistor based on MOS control, transformation from the depletion mode GaN heterojunction field effect transistor to the enhanced GaN heterojunction field effect transistor is realized by controlling an on / off state of the low-voltage MOS tube connected in series with the depletion mode GaN heterojunction field effect transistor; the enhanced GaN heterojunction field effect transistor has the normally off characteristic of the low-voltage MOS tube and the advantages of high-voltage resistance, low-conductivity resistance and the like of the depletion mode GaN heterojunction field effect transistor, has good frequency characteristic and high output power and density, and is applicable to the high-frequency and high-power fields.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Nitride semiconductor heterojunction field effect transistor having wide band gap barrier layer that includes high concentration impurity region

InactiveUS8035130B2Increase productionLower resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationDevice material

The objective of the present invention is to provide a semiconductor device of a hetero-junction field effect transistor that is capable of obtaining a high output and a high breakdown voltage and a manufacturing method of the same. The present invention is a semiconductor device of a hetero-junction field effect transistor provided with an AlxGa1-xN channel layer with a composition ratio of Al being x (0<x<1) formed on a substrate, an AlyGa1-yN barrier layer with a composition of Al being y (0<y≦1) formed on the channel layer, and source / drain electrodes and a gate electrode formed on the barrier layer, wherein the composition ratio y is larger than the composition ratio x.

Owner:MITSUBISHI ELECTRIC CORP

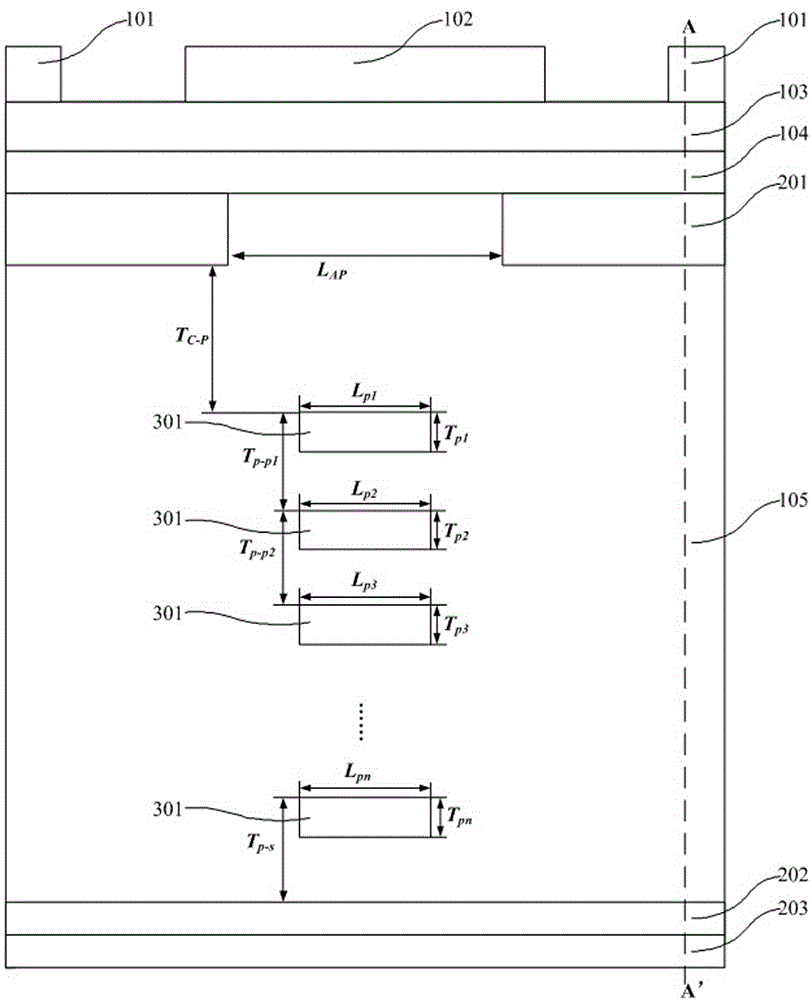

Vertical GaN heterojunction field-effect transistor with P type GaN island

ActiveCN104167442AIncrease the electric field strengthHigh compressive strengthSemiconductor devicesBlocking layerHeterojunction field effect transistor

The invention discloses a vertical GaN heterojunction field-effect transistor with a P type GaN island. The field-effect transistor comprises an AlGaN barrier layer, wherein a source electrode and a grid electrode are arranged on the AlGaN barrier layer, and a GaN channel layer, a p-GaN current blocking layer, an n-GaN buffer layer, an n+-GaN substrate and a drain electrode are arranged under the AlGaN barrier layer in sequence. A hole with the caliber of LAP is formed in the center of the p-GaN current blocking layer and nested to the n-GaN buffer layer, the p-GaN island is arranged in the n-GaN buffer layer, and the p-GaN island is located between the p-GaN current blocking layer and the n+-GaN substrate. In the GaNPI-VHFET, by using the p-GaN island layer, extra p type impurities are introduced into the n-GaN buffer layer, and the n-GaN buffer layer area is exhausted in the off state, so that the buffer area is equivalent to an intrinsic region during voltage resistance. Therefore, the problem that the vertical electric field intensity is continuously decreased when current moves far away from an interface of the p-GaN current blocking layer and the n-GaN buffer layer is solved to increase breakdown voltage of a device. Meanwhile, leaked current of the drain electrode is also decreased in the off state.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA