Two-dimensional material heterojunction field effect transistor, preparation method thereof and transistor array device

A heterojunction field effect, two-dimensional material technology, applied in the field of microelectronics, can solve the problems affecting transistor performance, two-dimensional material damage, low substrate utilization, etc., to avoid damage, low cost, good output characteristics and Effects of Transfer Features

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

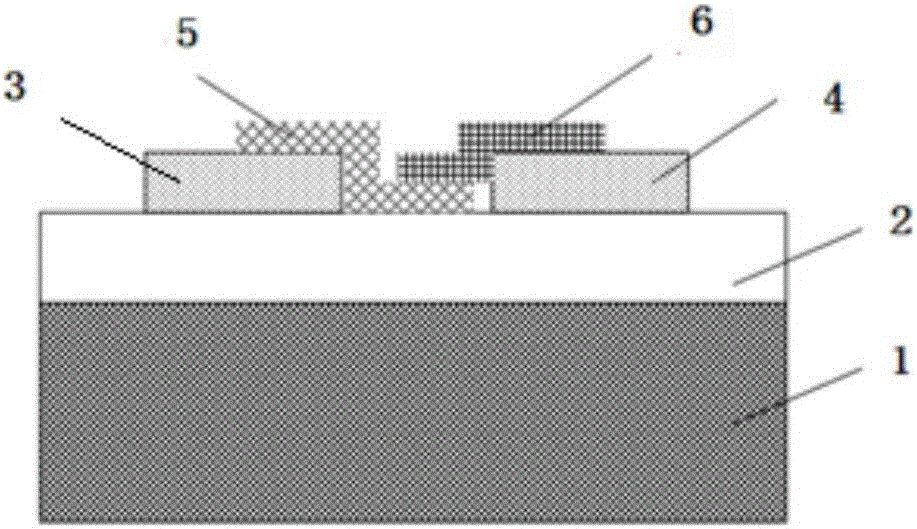

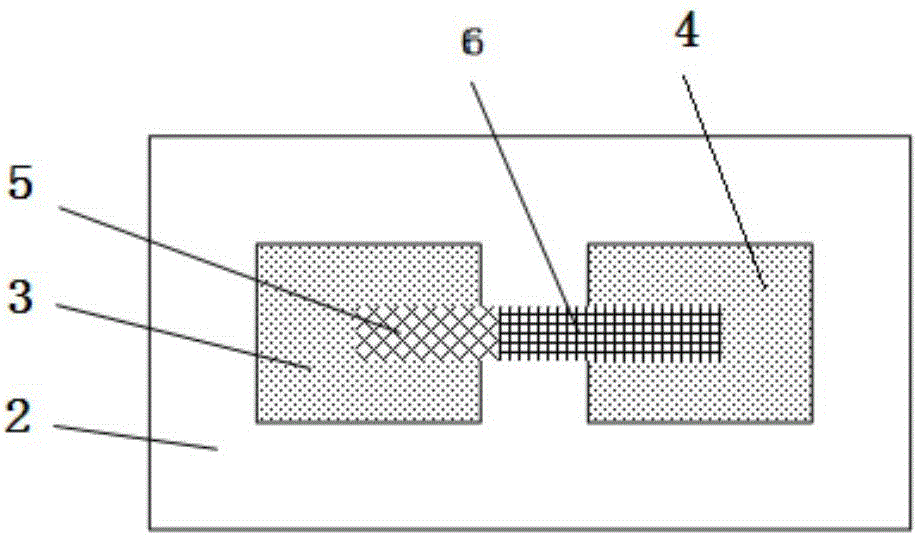

[0057] Correspondingly, the present invention provides a method for preparing a two-dimensional heterojunction field effect transistor, comprising the following steps:

[0058] 1) setting an insulating medium layer on the conductive substrate, and then spin-coating the photoresist on the insulating medium layer;

[0059] 2) making an electrode pattern mask on the insulating dielectric layer by photolithography and development;

[0060] 3) Evaporating metal on the electrode pattern mask, then removing the photoresist on the insulating dielectric layer, forming a source electrode and a drain electrode at both ends thereof, between the source electrode and the drain electrode is the channel area;

[0061] 4) disposing a first two-dimensional material on the source electrode and the channel region connected thereto to form a first two-dimensional material layer, and then disposing a second two-dimensional material different from the first two-dimensional material on the source el...

Embodiment 1

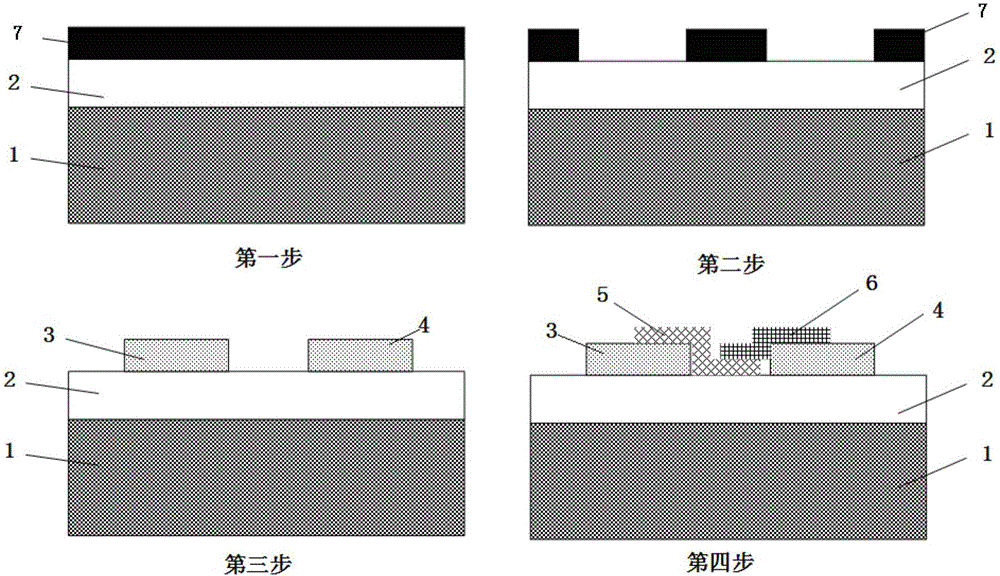

[0076] Such as image 3 As shown, a method for preparing a two-dimensional material heterojunction field effect transistor comprises the following steps:

[0077] In the first step, a thermal oxidation method is used on the n-type conductive Si substrate 1 to obtain SiO with a thickness of 300nm 2 Insulation medium layer 2;

[0078] The 601 positive photoresist 7 was spin-coated on the insulating dielectric layer 2, the spin-coating time was 40 s, and the spin-coating speed was 4000 rpm.

[0079] In the second step, an electrode pattern mask is fabricated on the insulating dielectric layer 2 through photolithography and development; wherein, the photolithography time is 7s; the developer used is polyimide, and the development time is 35s.

[0080] In the third step, on the electrode pattern mask, utilize an electron beam evaporation evaporation deposition machine to successively evaporate (cavity vacuum degree is 10 -4 Pa, the coating rate is 0.1mm / s) a Ni layer with a thic...

Embodiment 2

[0086] This embodiment adopts the same transistor structure and fabrication process as in Embodiment 1, wherein the second two-dimensional material (MoSe 2 ) is replaced by the p-type second two-dimensional material (WSe 2 ), thus forming a MoS 2 / WSe 2 pn heterojunction field effect transistor, the physical picture is as follows Figure 8 as shown, Figure 8 is the MoS provided by Example 2 of the present invention 2 / WSe 2 Pn heterojunction field effect transistor physical map.

[0087] Using a probe station and a dual-channel SourceMeter, the MoS 2 / WSe 2 pn heterojunction field effect transistor for performance testing. See results Figure 9 with Figure 10 , Figure 9 is the MoS provided by Example 2 of the present invention 2 / WSe 2 I-V characteristic curve of pn heterojunction field effect transistor, Figure 10 is the MoS provided by Example 2 of the present invention 2 / WSe 2 Transfer curves of a pn heterojunction field effect transistor. from Figur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More