Gallium-nitride-based heterostructure field effect transistor with composite barrier layers

A heterojunction field effect and composite barrier technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of device output current drop, reaction speed drop, current collapse effect, etc., to increase drift speed and improve endurance The effect of pressure and simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

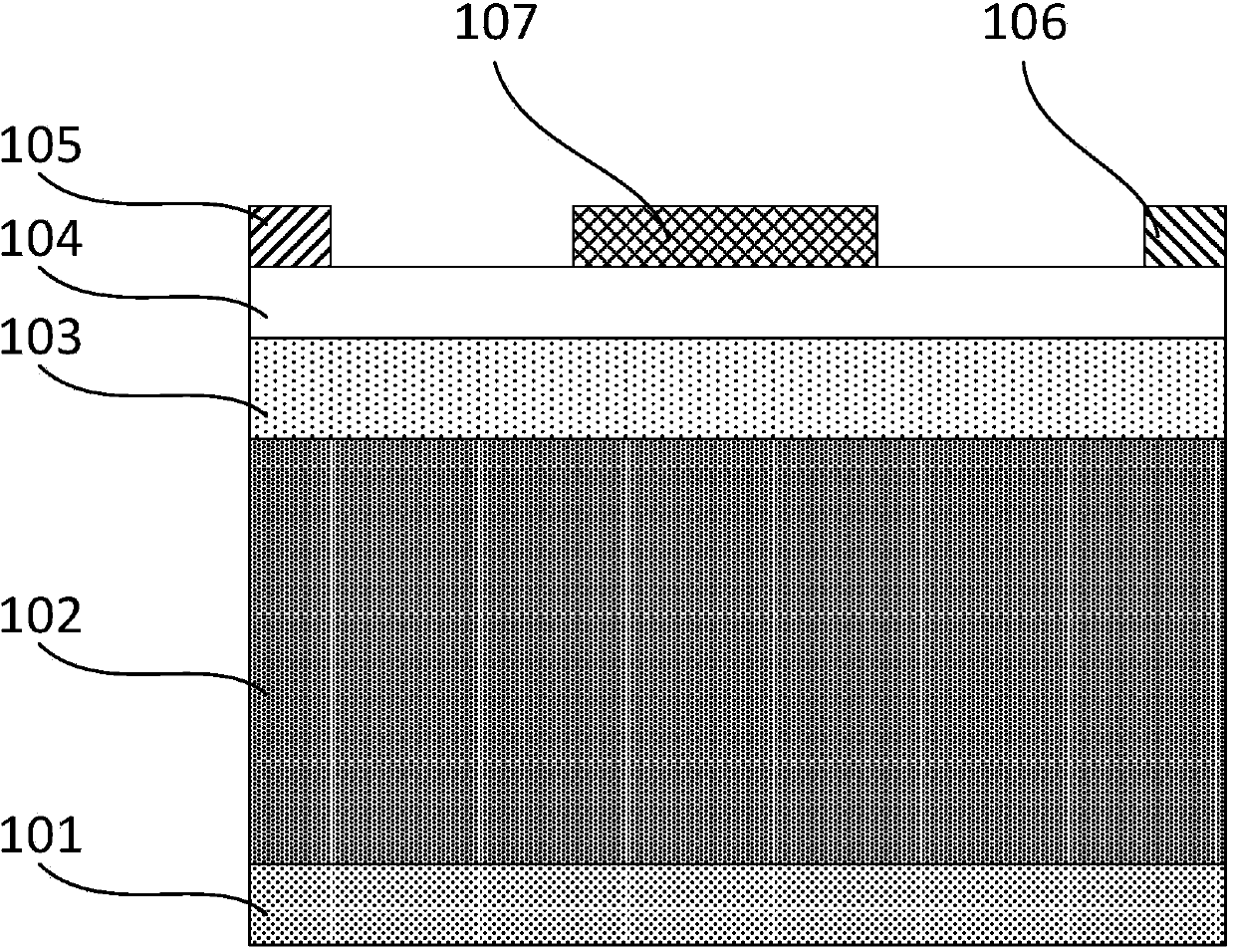

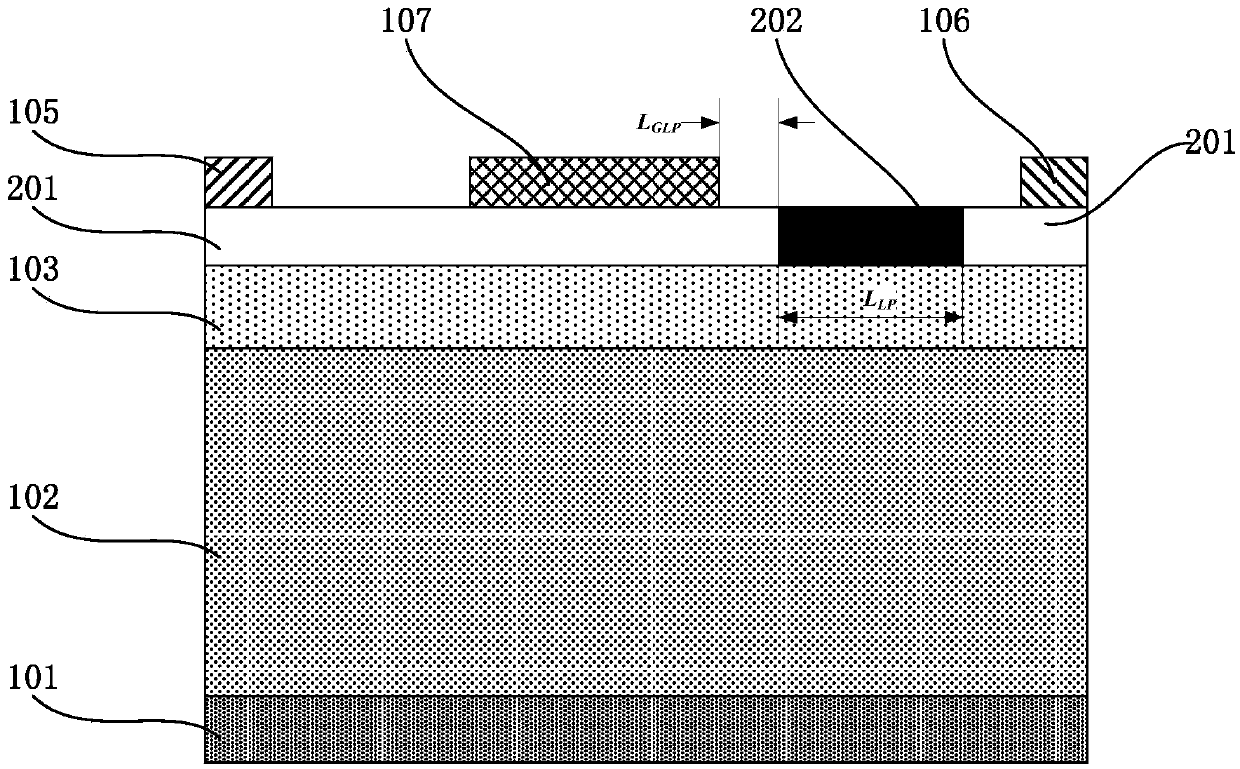

Embodiment 1

[0037] This example is used as a power device. like figure 2 As shown, the GaN HEMT of this example includes a substrate 101, a gallium nitride buffer layer 102 disposed on the substrate 101, a gallium nitride channel layer 103 disposed on the gallium nitride buffer layer 102, a source 105, a drain Pole 106 and gate 107; It is characterized in that, a compound barrier layer is arranged on the upper layer of the gallium nitride channel layer 103, and the source electrode 105 and the drain electrode 106 are located at both ends of the upper surface of the compound barrier layer and are connected to the compound potential The barrier layer forms an ohmic contact, and the grid 107 is located in the middle of the upper surface of the composite barrier layer and forms a Schottky contact with the composite barrier layer; the composite barrier layer is composed of a high polarization barrier layer 201 and a low pole The two ends of the low polarization barrier layer 202 are connecte...

Embodiment 2

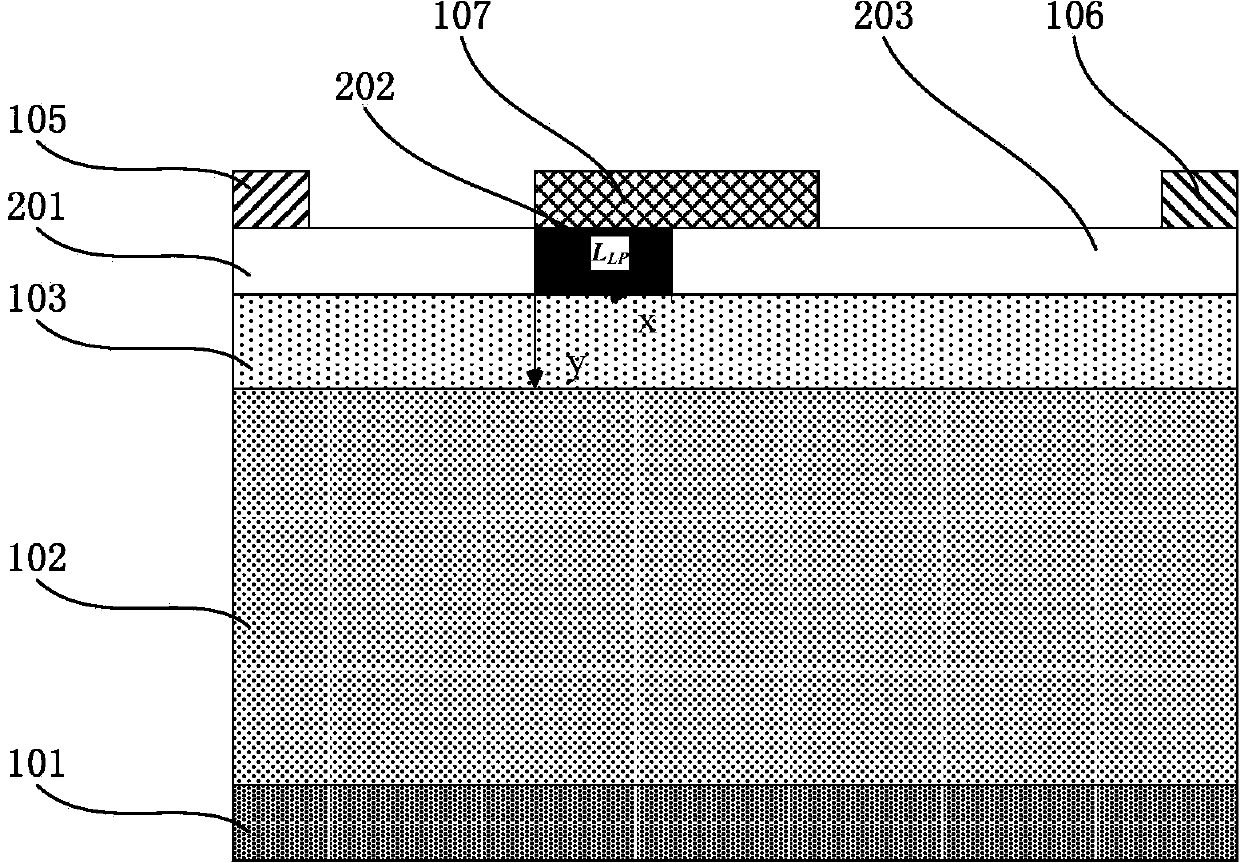

[0047] This example is used as a microwave device. like image 3 As shown, the GaN HEMT structure of this example differs from Embodiment 1 in that the low polarization barrier layer 202 in the composite barrier layer is located in the area directly below the gate, the left edge is aligned with the source end of the gate, and the right edge is not beyond the gate drain terminal. The main process steps of the GaN HEMT provided in this embodiment are as follows: First, a gallium nitride (GaN) buffer layer 102 and a gallium nitride (GaN) channel layer 103 are sequentially grown on the substrate by MOCVD, and then grown by selective growth technology Growing a high-polarization barrier layer 201 and a low-polarization barrier layer 202 with different polarization strengths to form a composite barrier layer; finally, forming a source electrode 105 and a drain electrode 106 in ohmic contact with the composite barrier layer , and a gate 107 in Schottky contact with the barrier laye...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More