Patents

Literature

53 results about "Heterostructure field effect transistors" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Enhancement-Mode III-N Devices, Circuits, and Methods

ActiveUS20070278518A1High breakdown fieldHigh Power Handling CapabilitySemiconductor devicesPhotoresistIon implantation

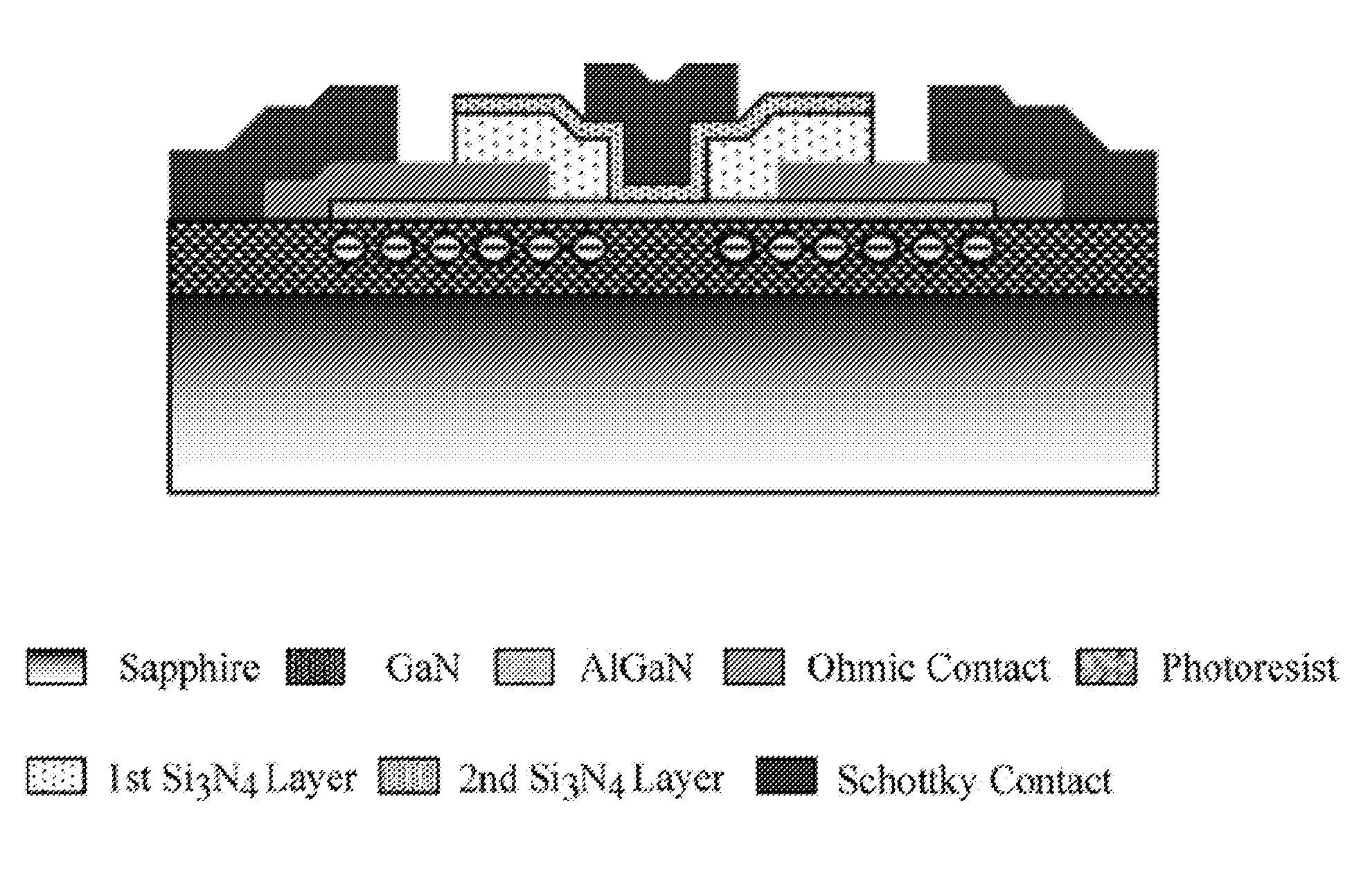

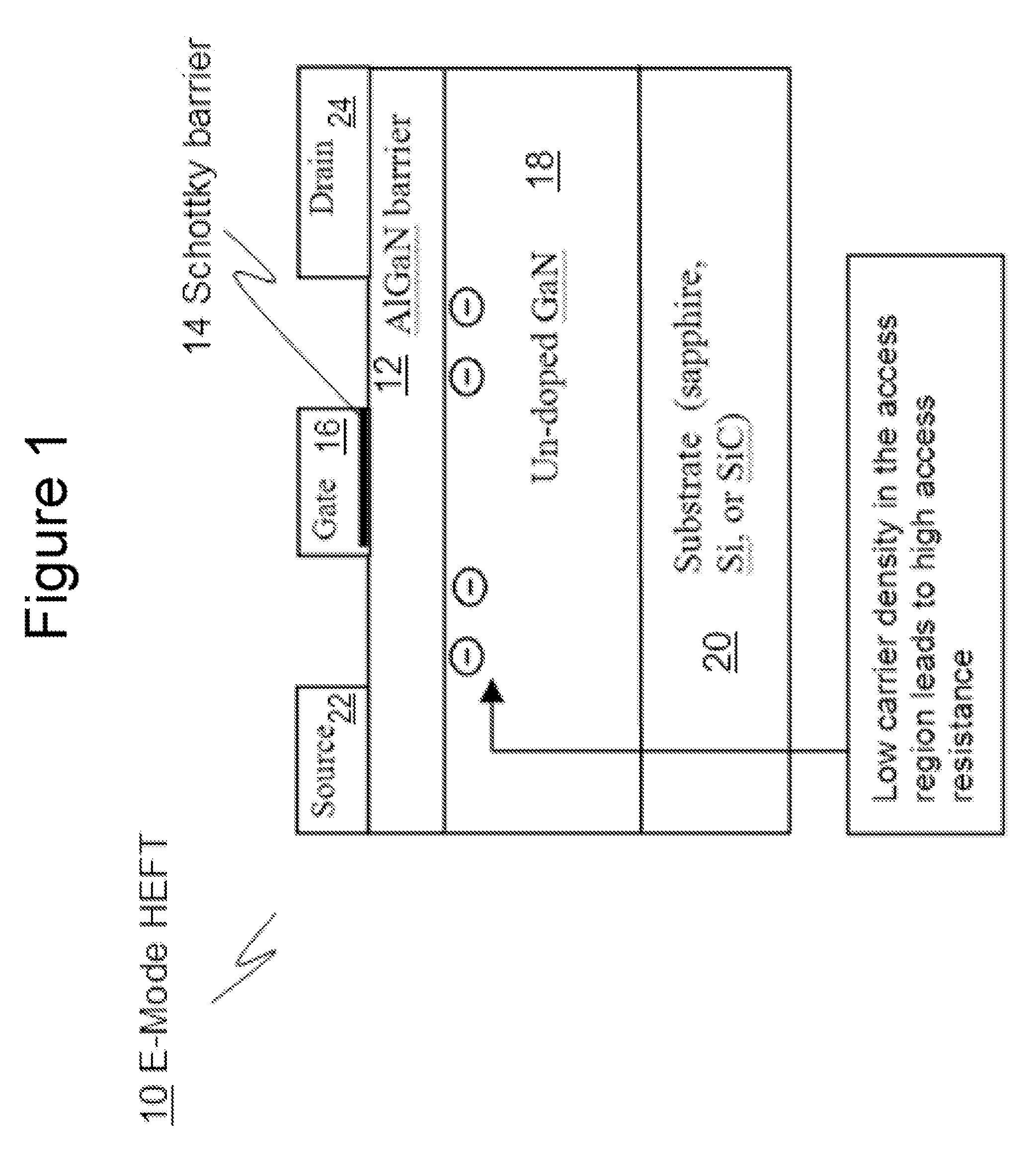

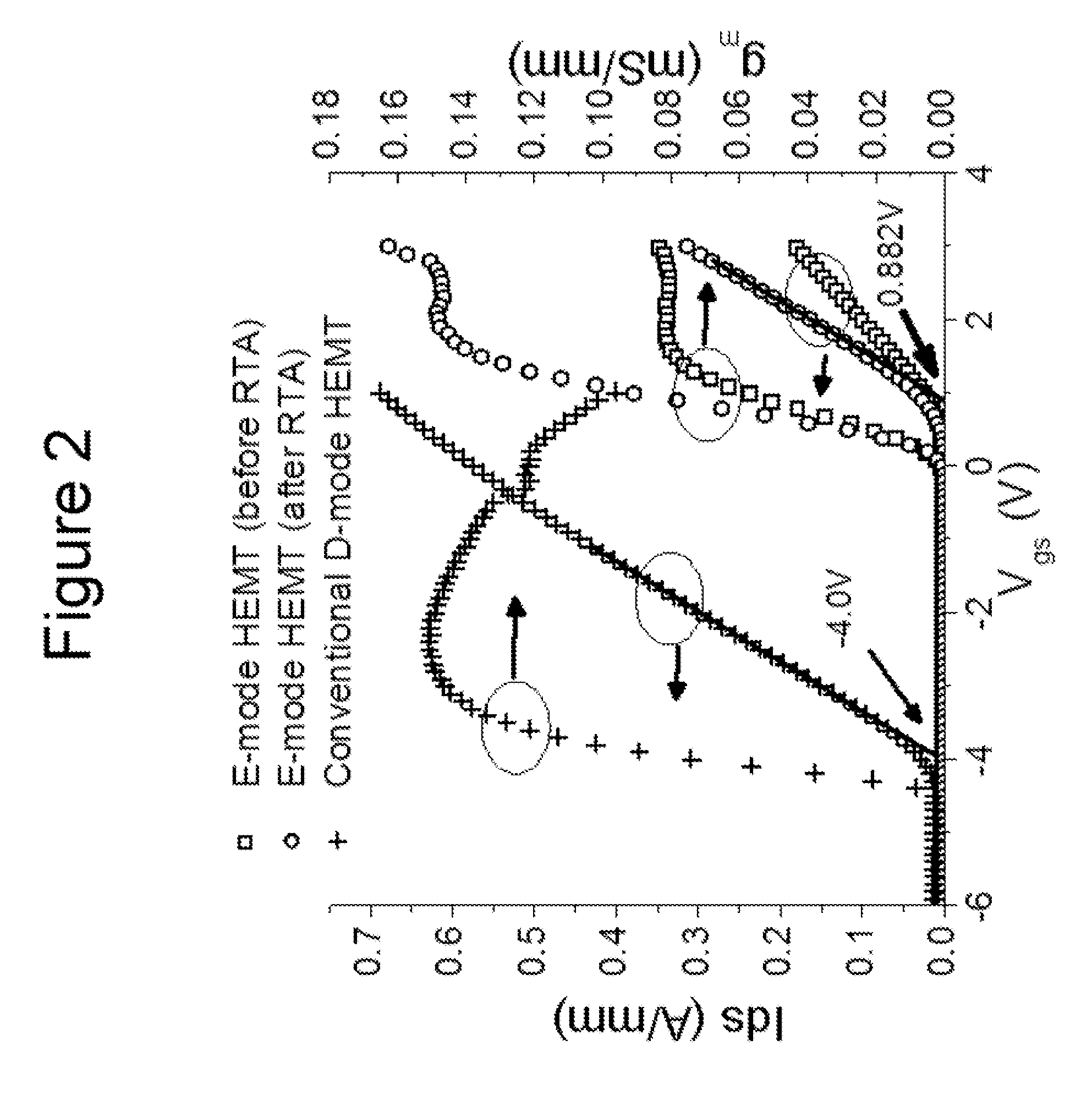

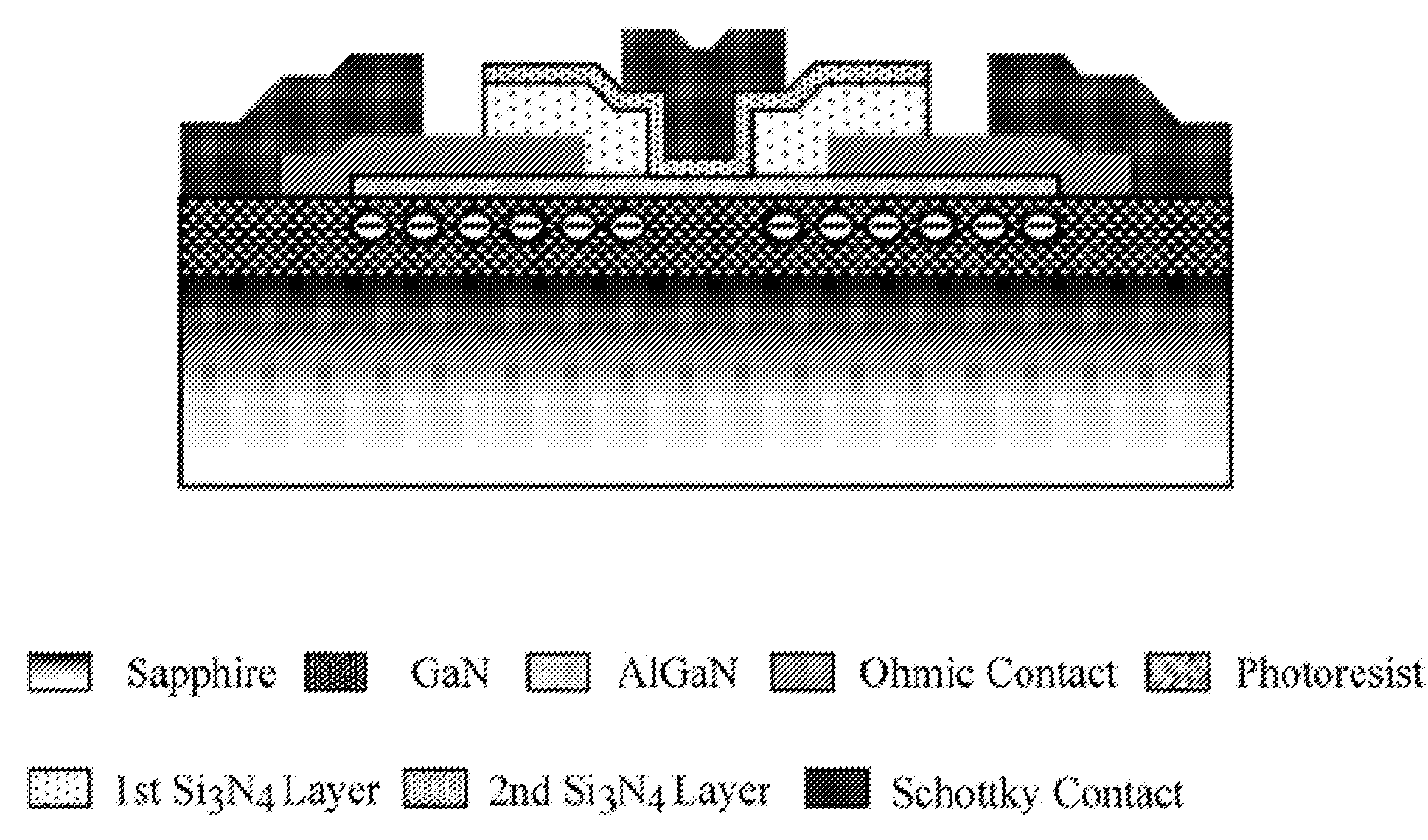

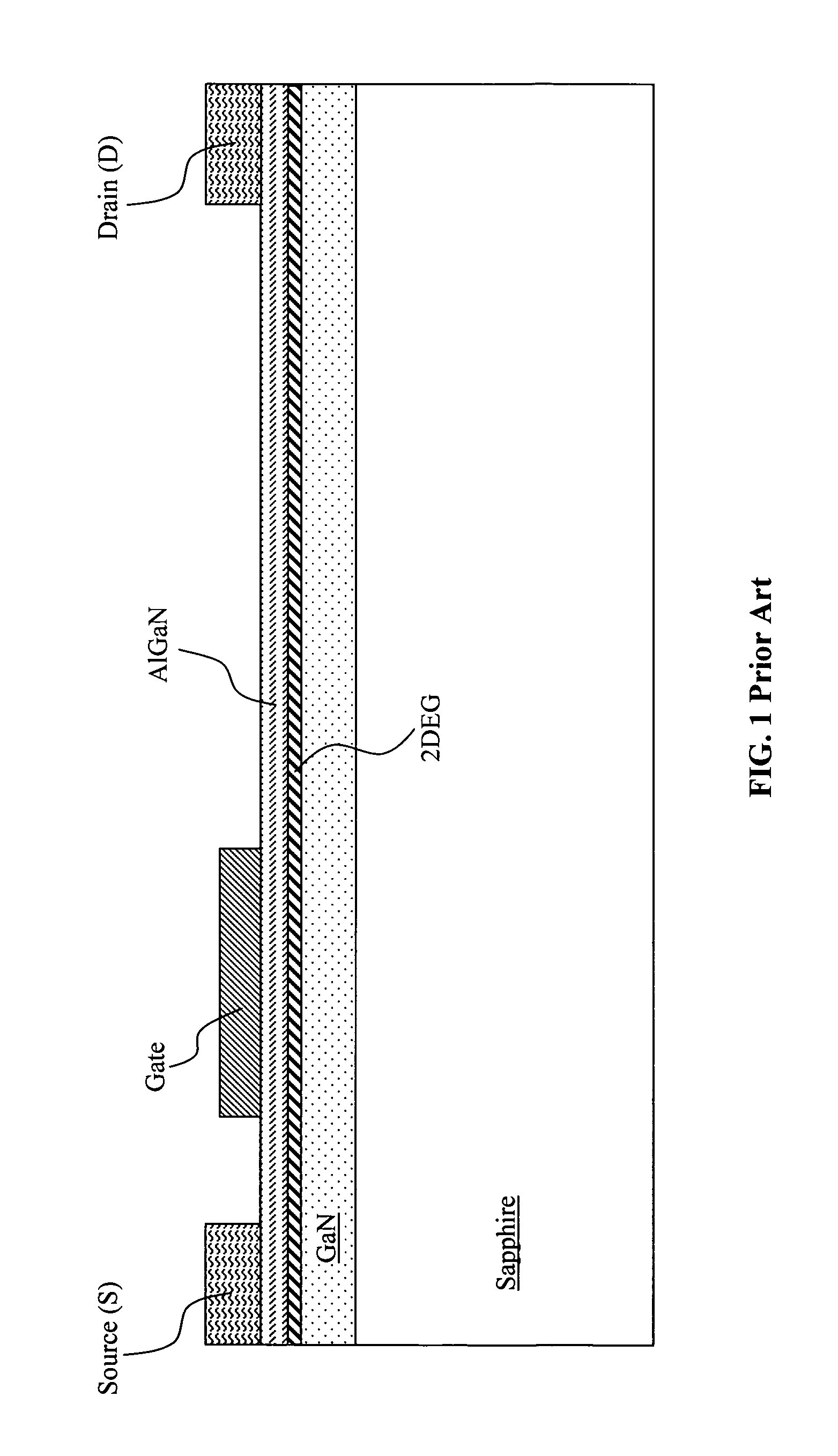

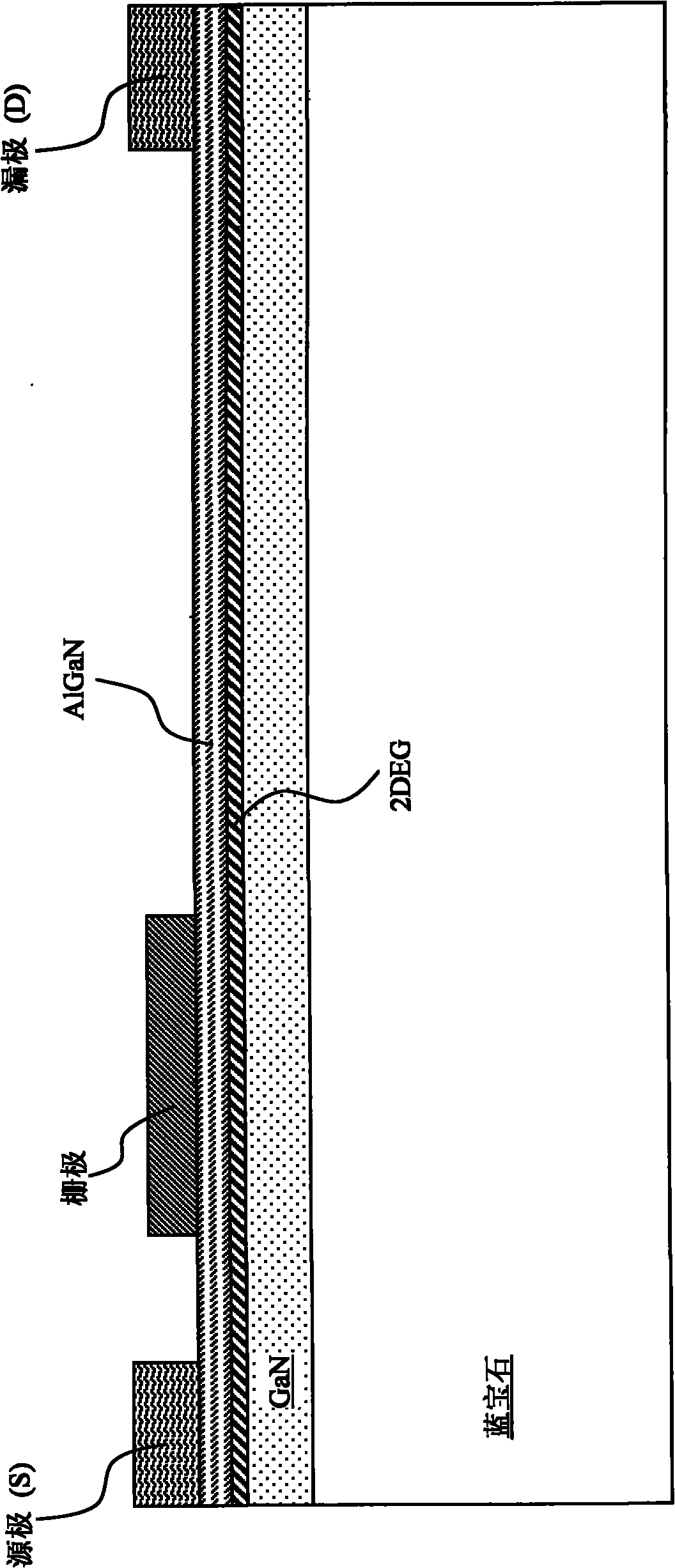

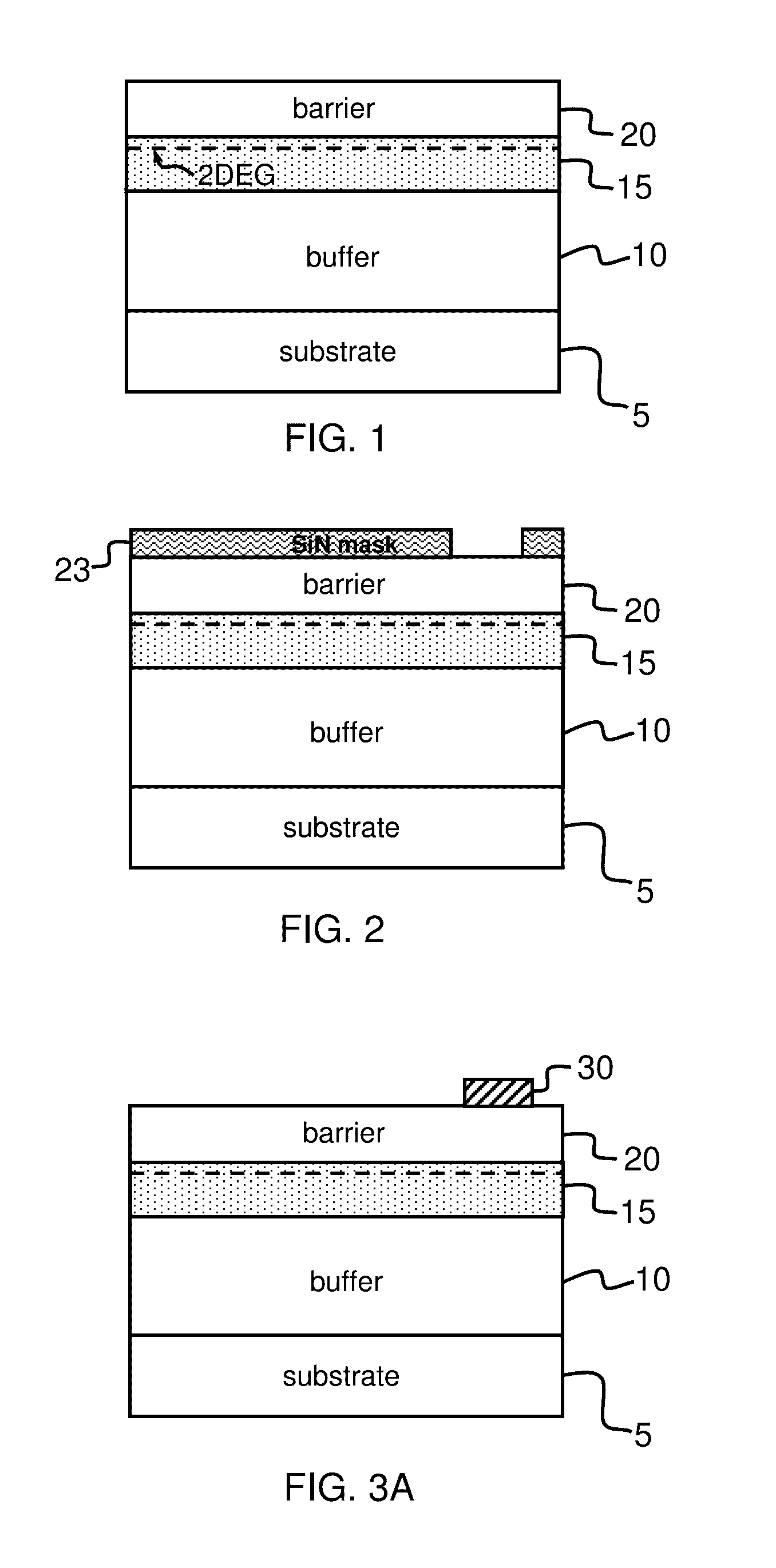

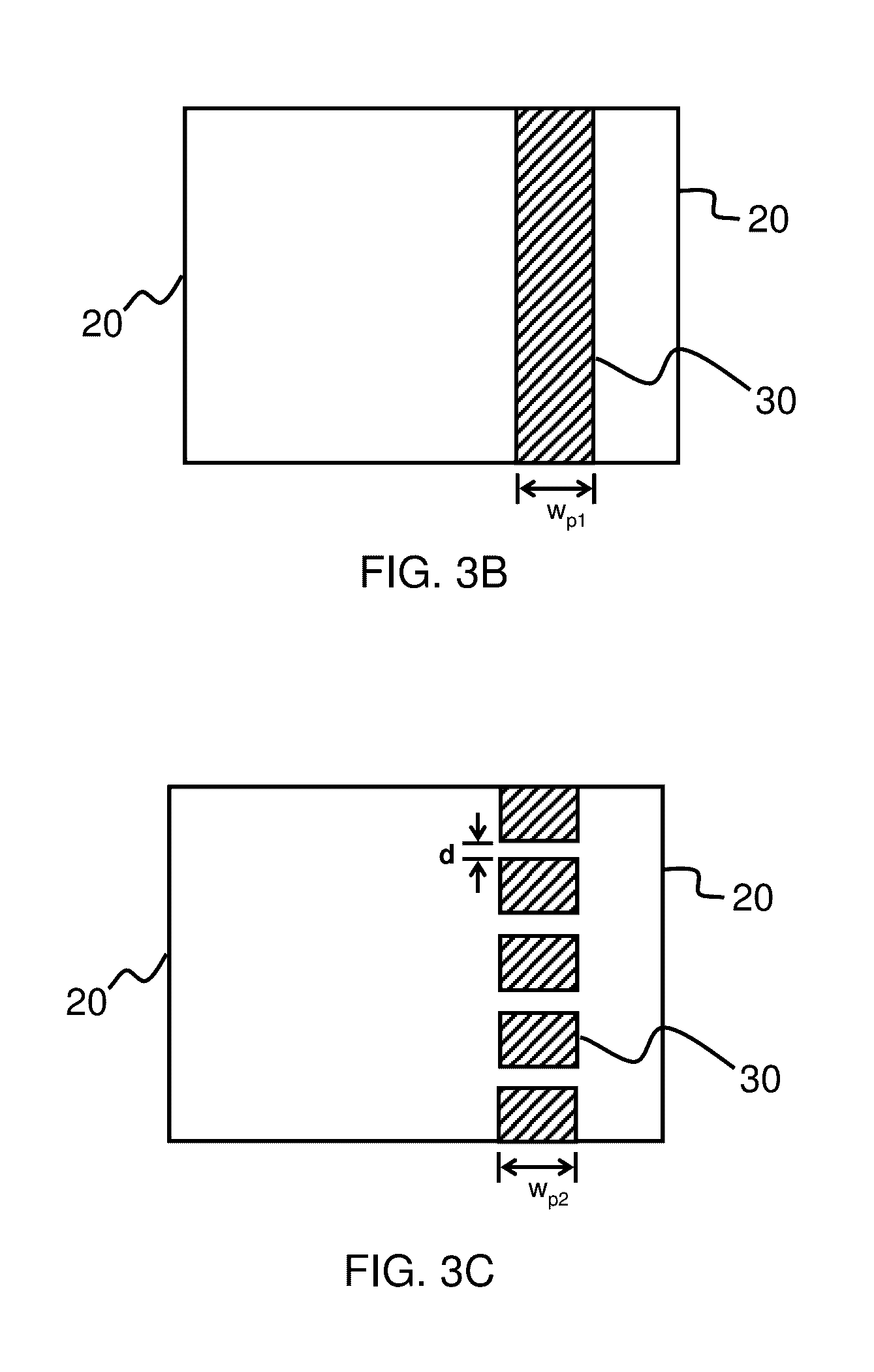

A method of fabricating AlGaN / GaN enhancement-mode heterostructure field-effect transistors (HFET) using fluorine-based plasma immersion or ion implantation. The method includes: 1) generating gate patterns; 2) exposing the AlGaN / GaN heterostructure in the gate region to fluorine-based plasma treatment with photoresist as the treatment mask in a self-aligned manner; 3) depositing the gate metal to the plasma treated AlGaN / GaN heterostructure surface; 4) lifting off the metal except the gate electrode; and 5) high temperature post-gate annealing of the sample. This method can be used to shift the threshold voltage of a HFET toward a more positive value, and ultimately convert a depletion-mode HFET to an enhancement-mode HFET (E-HFET).

Owner:THE HONG KONG UNIV OF SCI & TECH

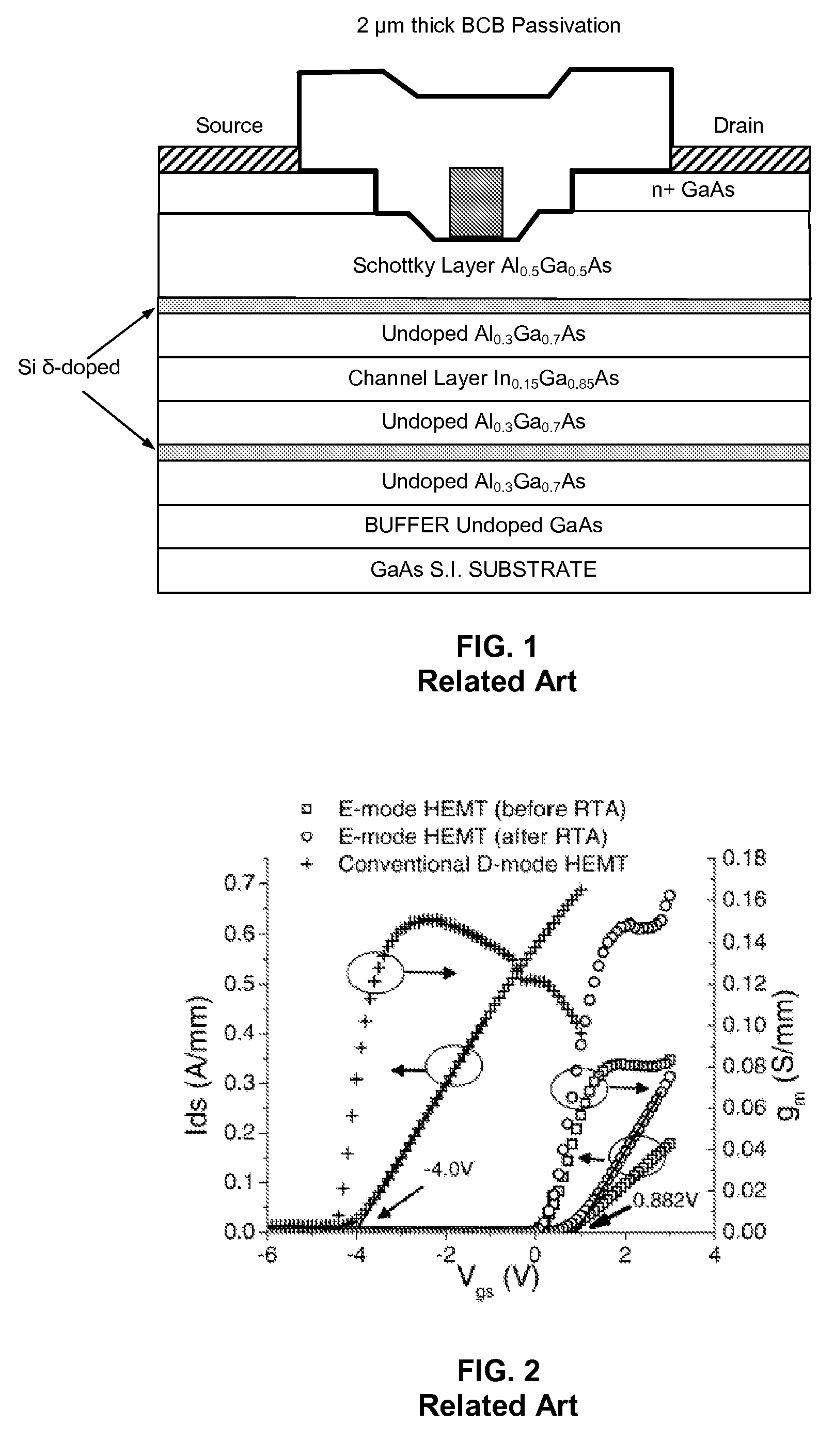

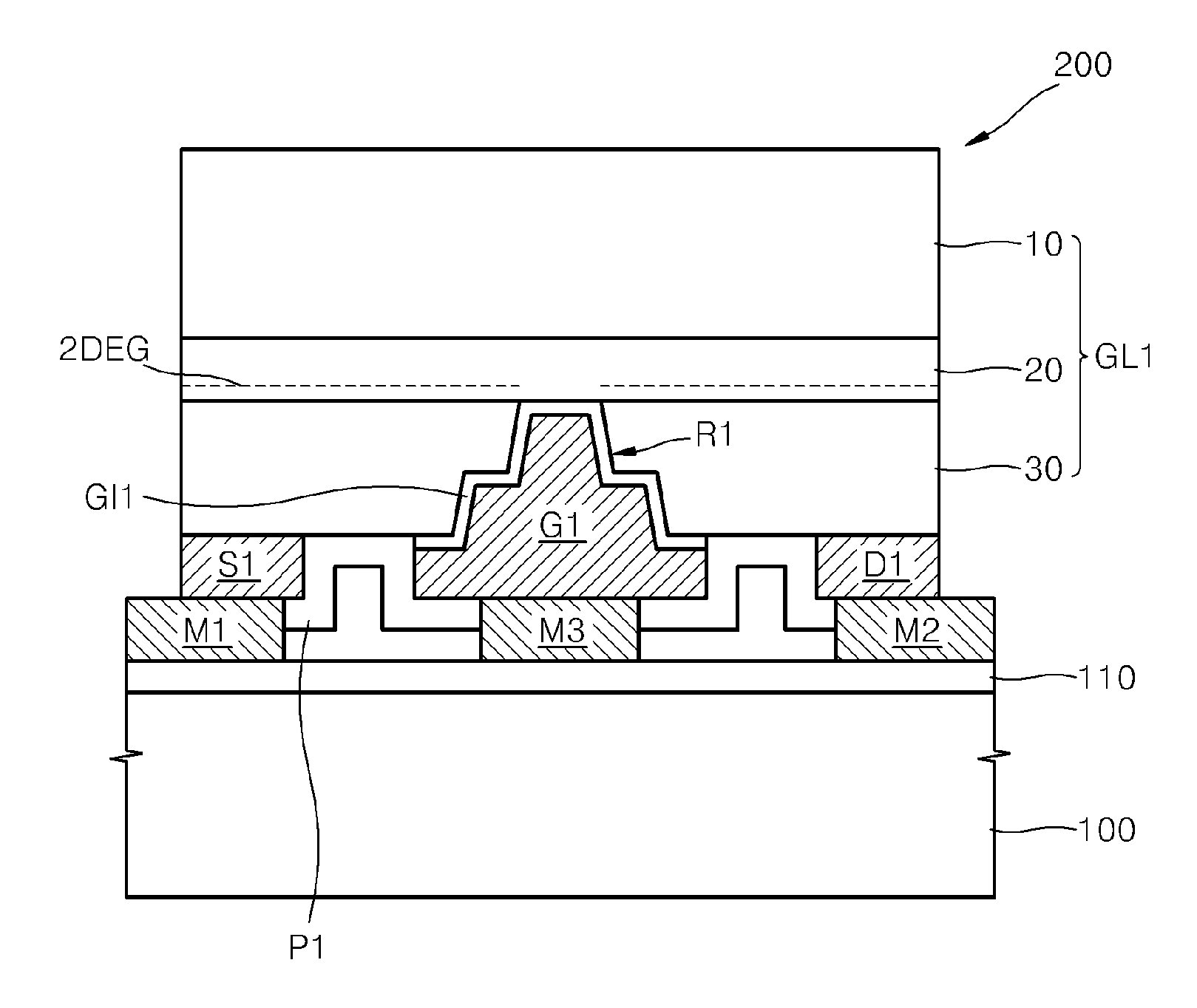

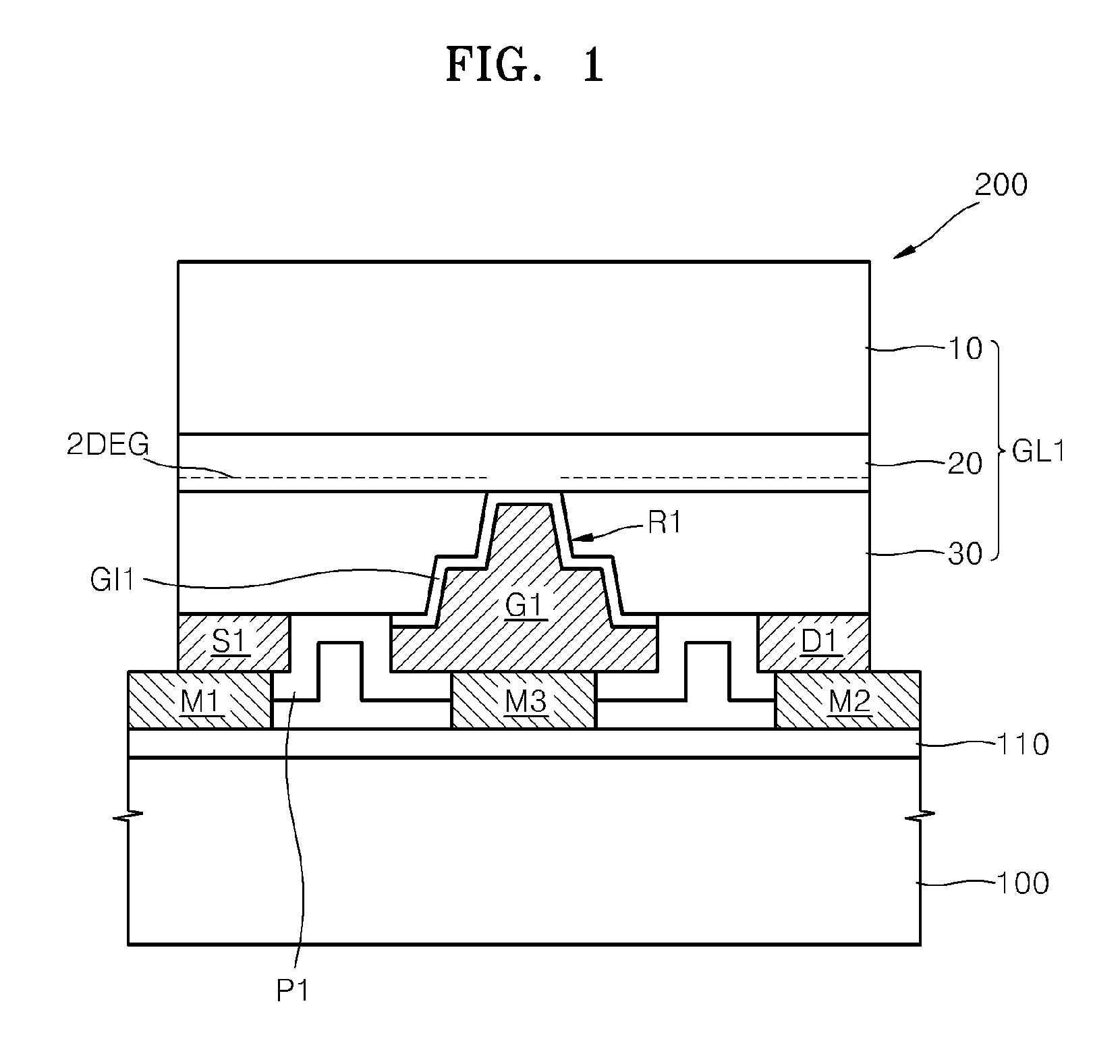

Enhancement mode insulated gate heterostructure field-effect transistor

ActiveUS20080203430A1Enhancement mode operationAccurate control of threshold voltageSemiconductor devicesCharge carrierGate current

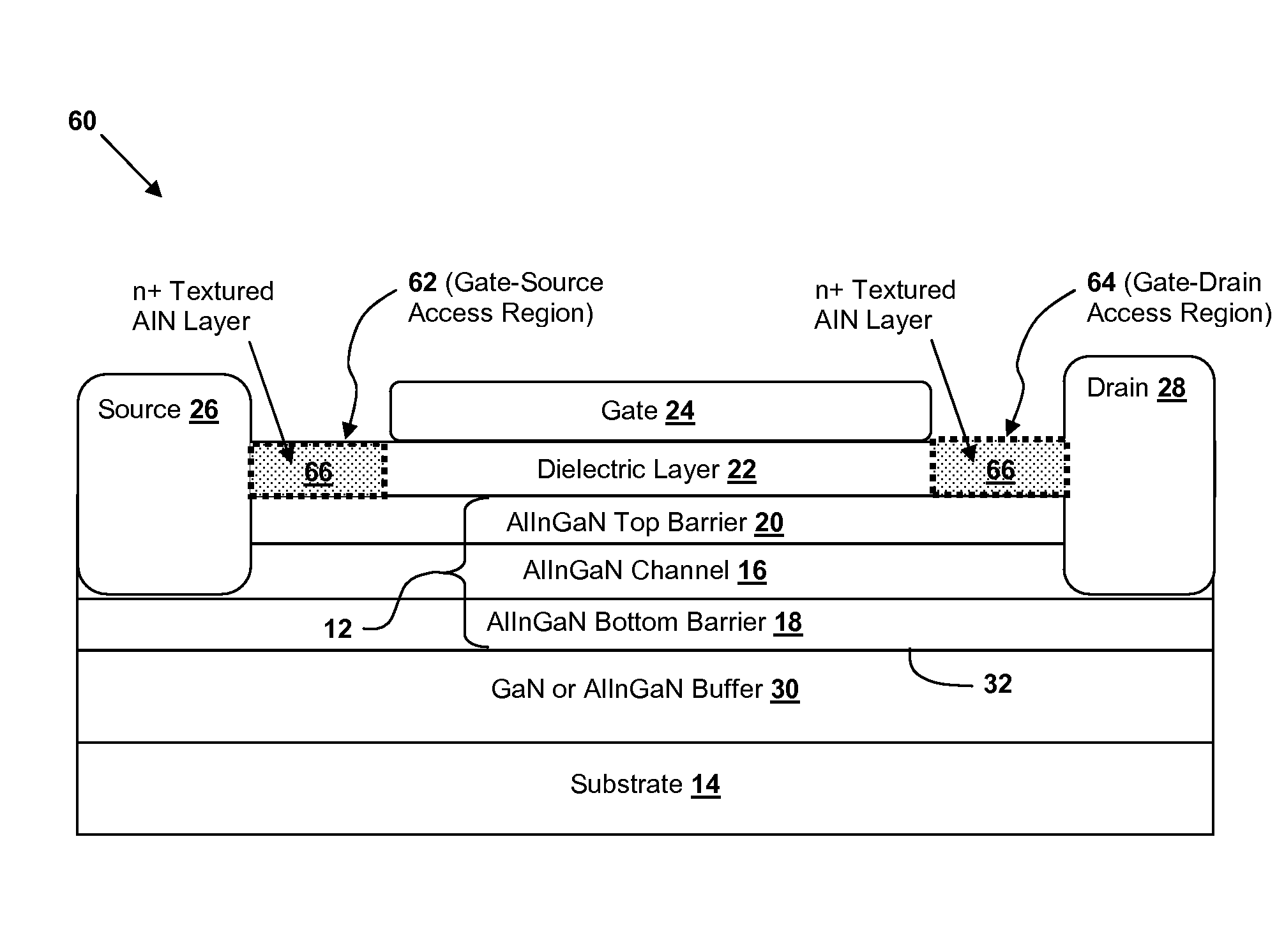

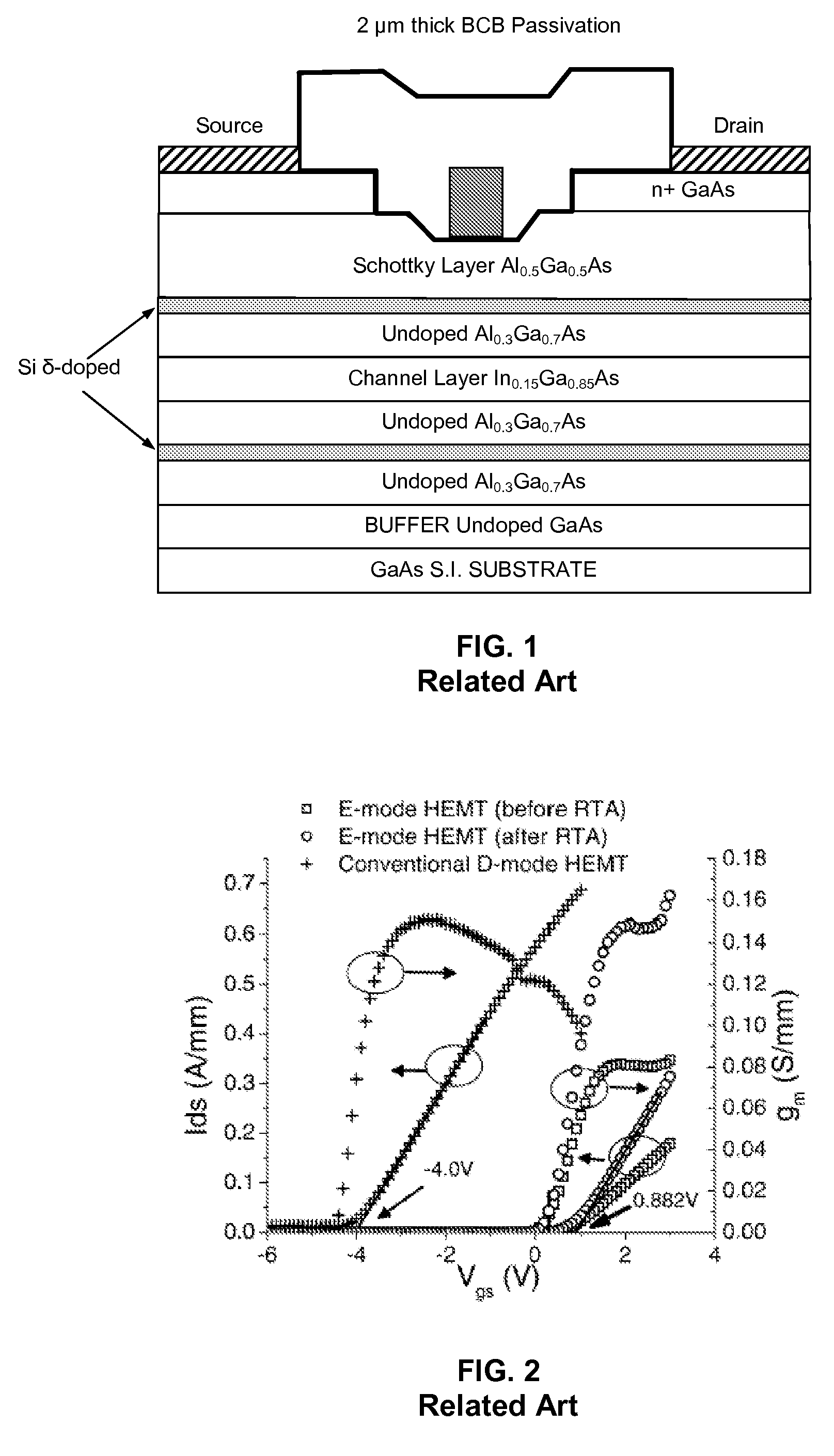

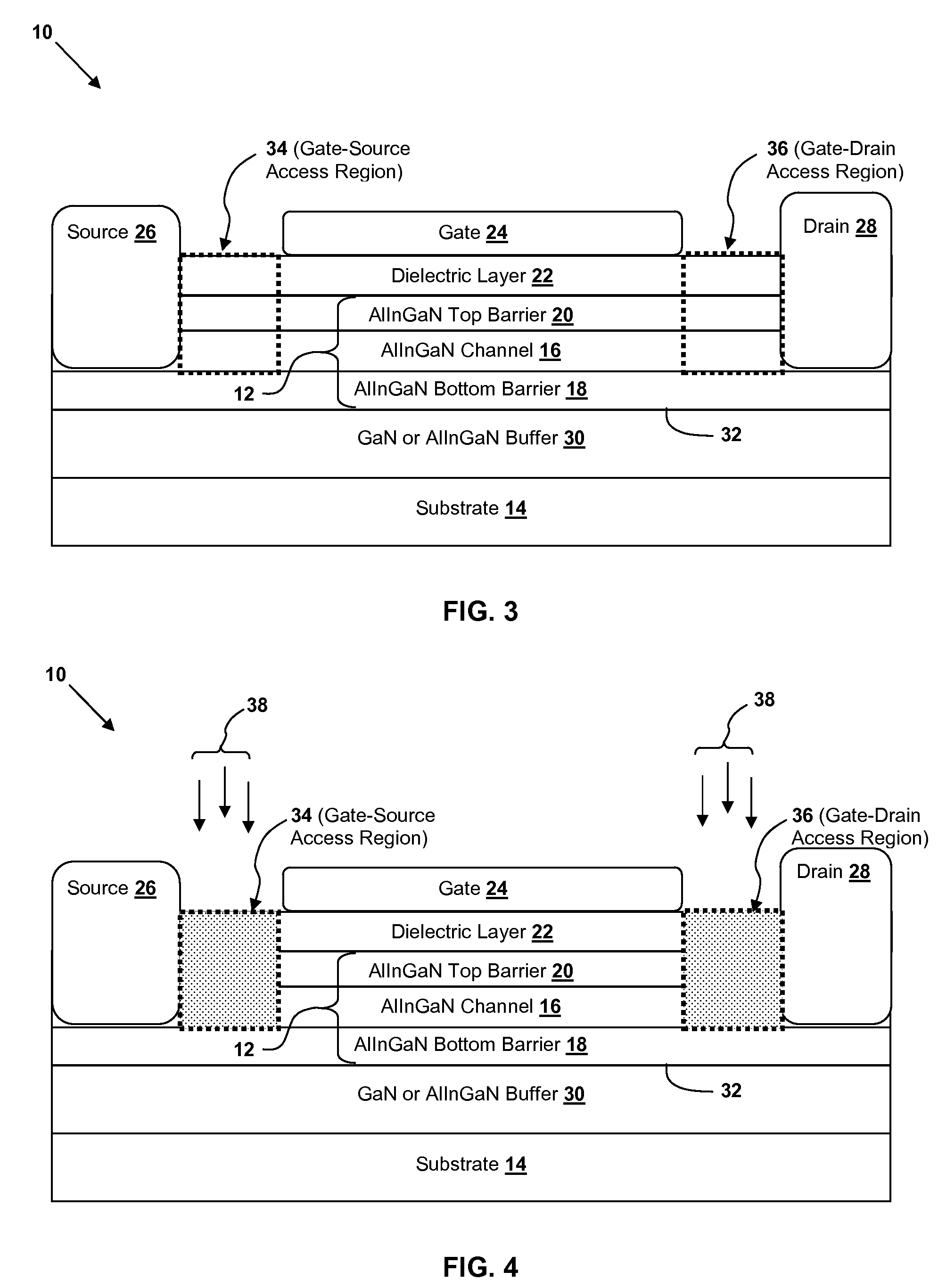

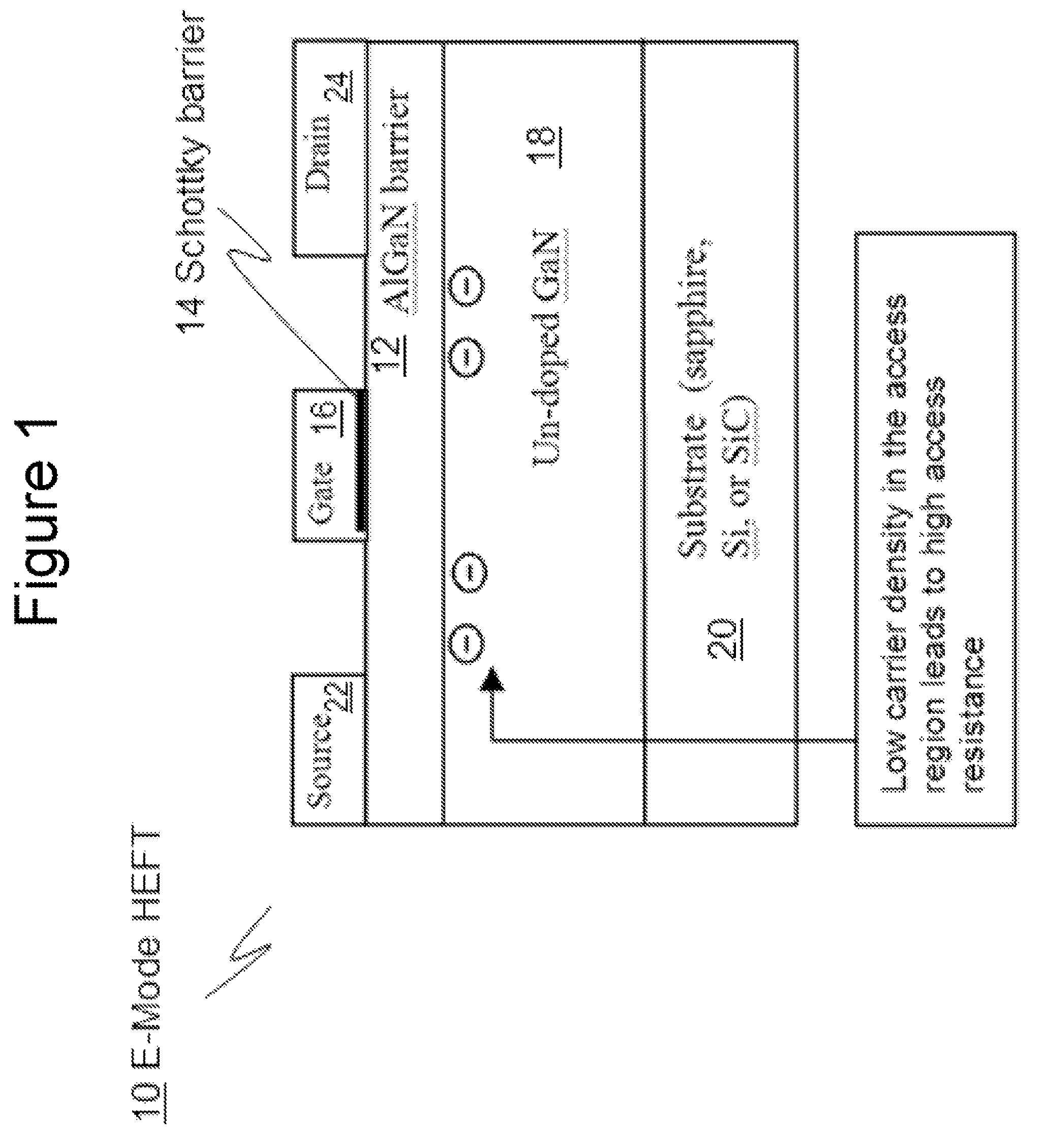

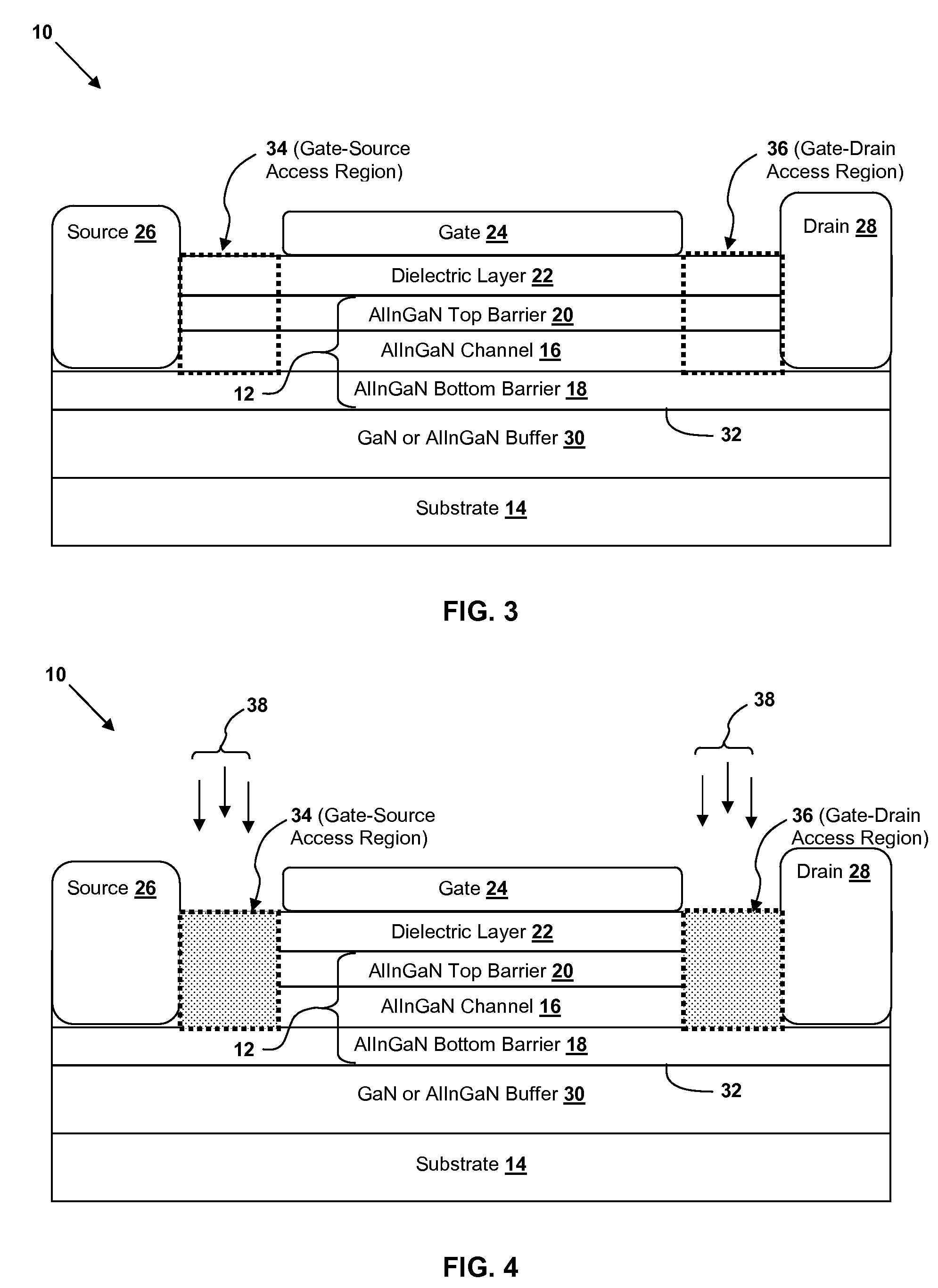

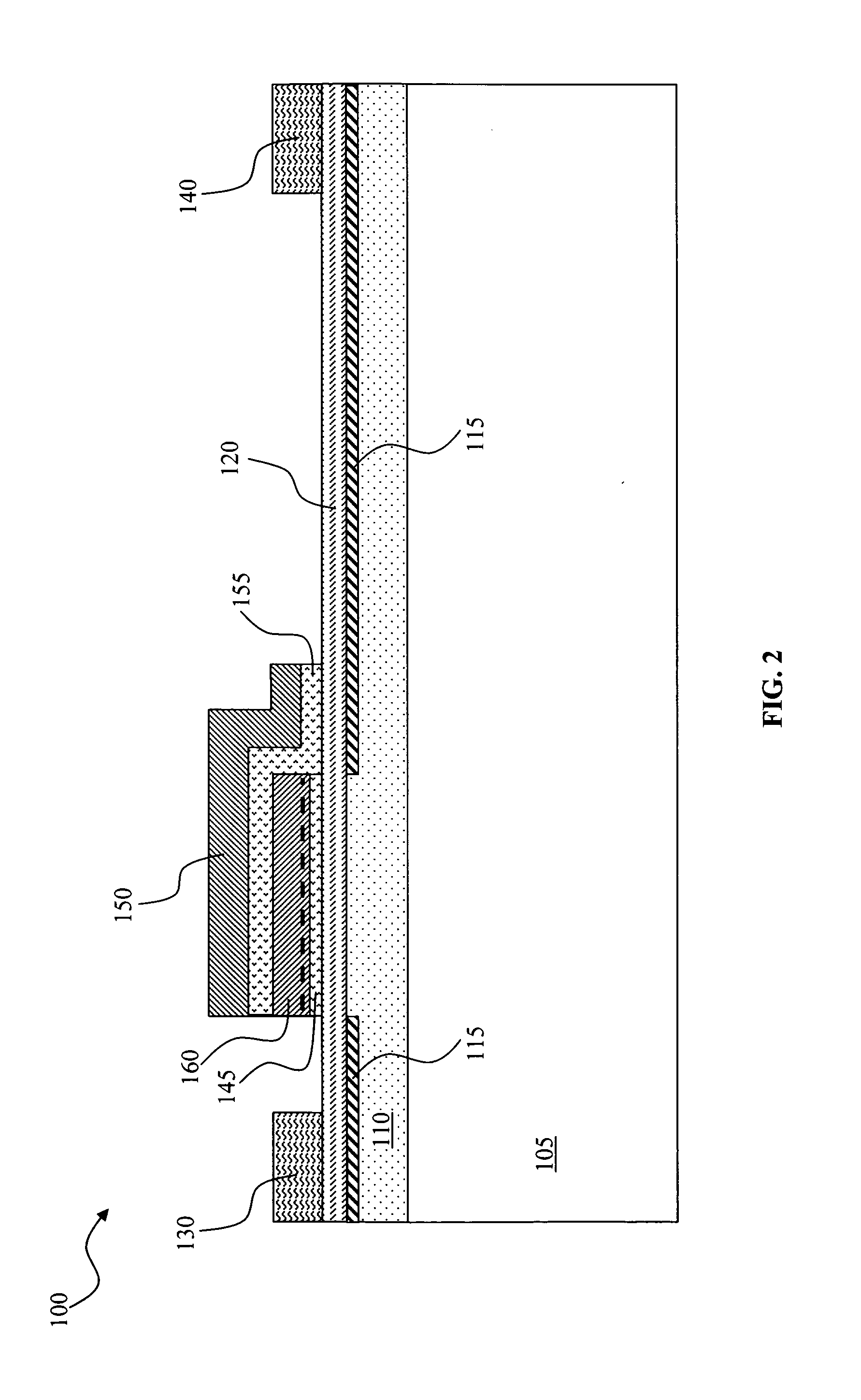

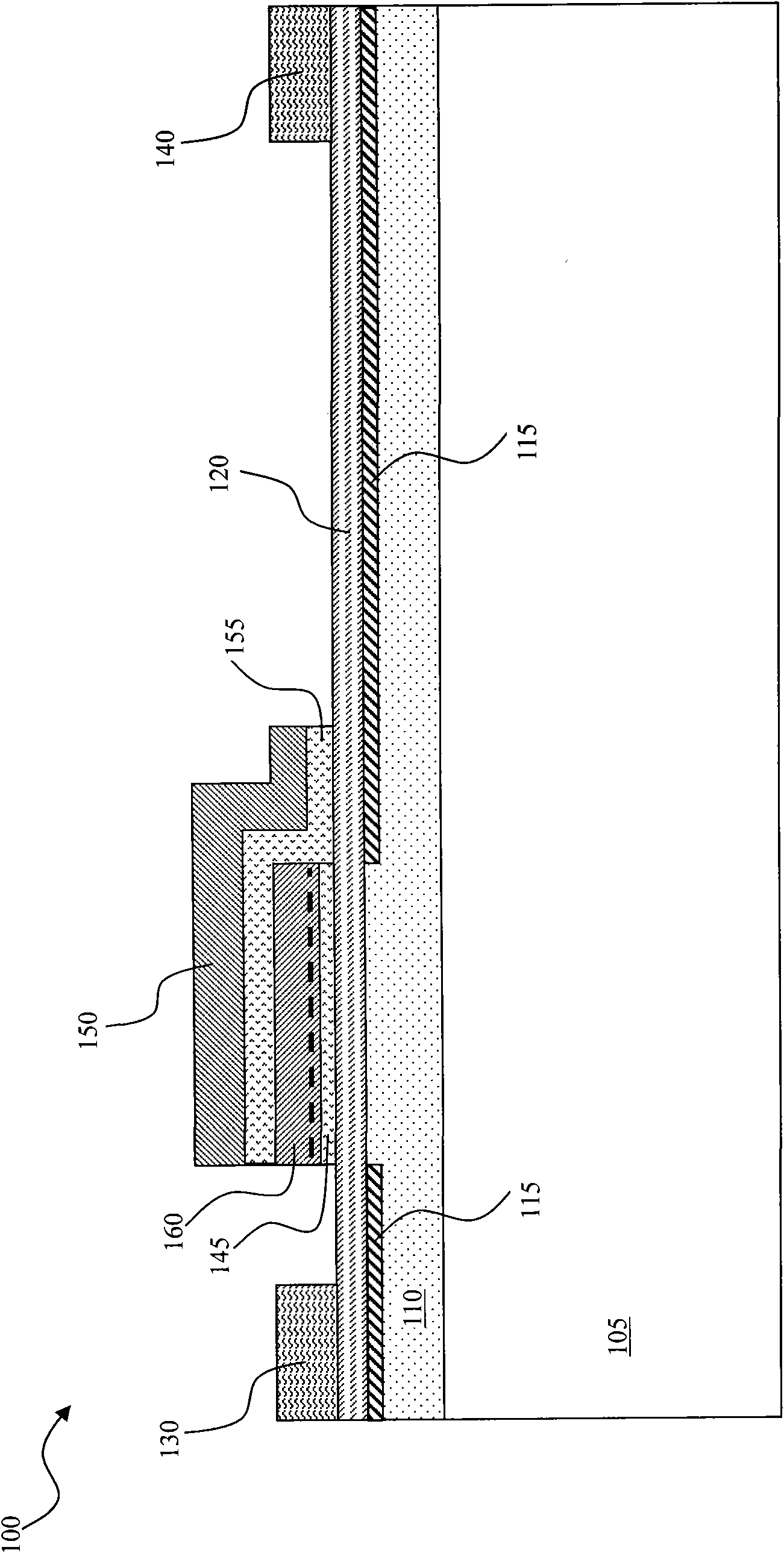

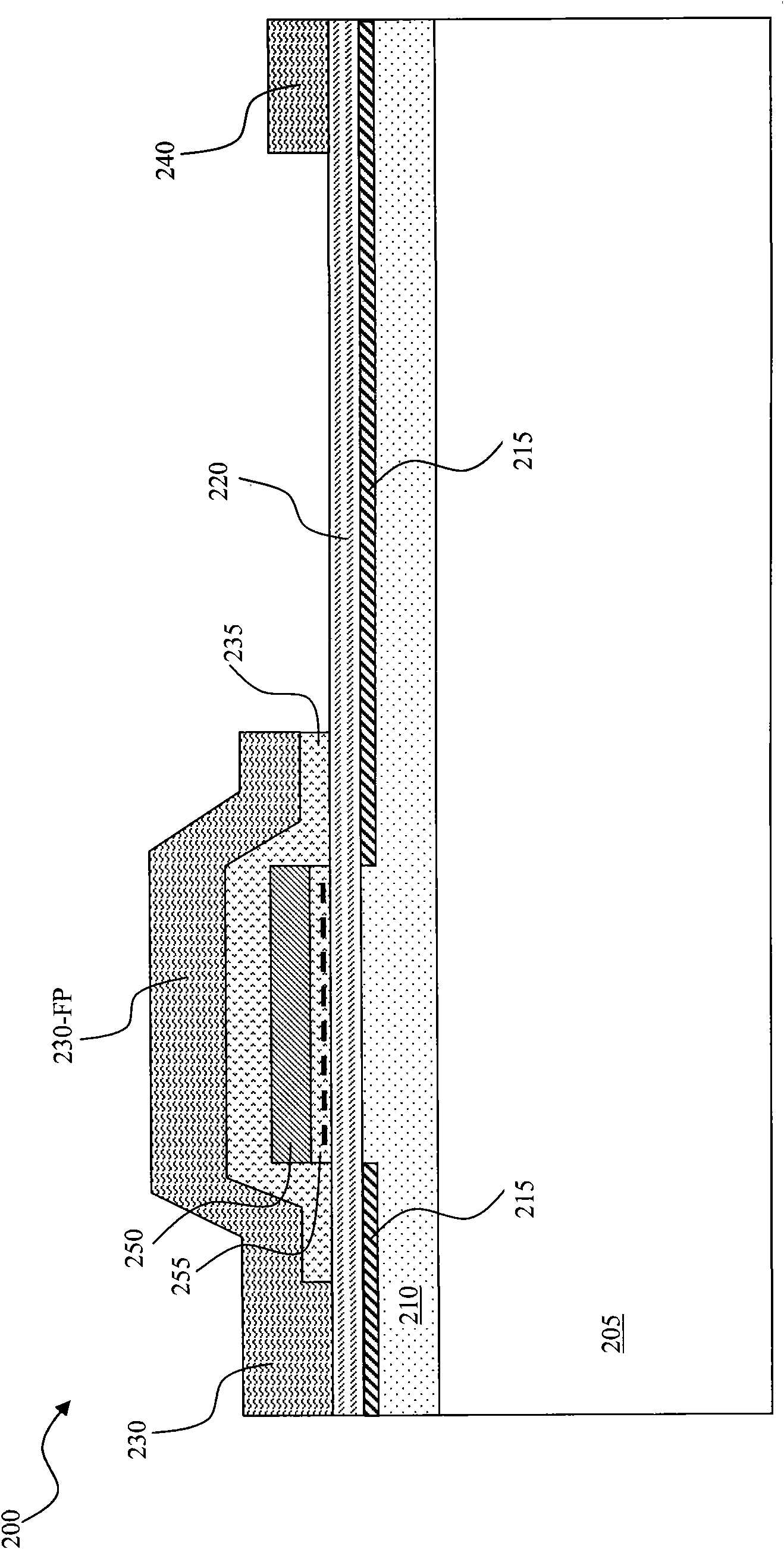

Aspects of the present invention provide an enhancement mode (E-mode) insulated gate (IG) double heterostructure field-effect transistor (DHFET) having low power consumption at zero gate bias, low gate currents, and / or high reliability. An E-mode HFET in accordance with an embodiment of the invention includes: top and bottom barrier layers; and a channel layer sandwiched between the bottom and the top barrier layers, wherein the bottom and top barrier layers have a larger bandgap than the channel layer, and wherein polarization charges of the bottom barrier layer deplete the channel layer and polarization charges of the top barrier layer induce carriers in the channel layer; and wherein a total polarization charge in the bottom barrier layer is larger than a total polarization charge in the top barrier layer such that the channel layer is substantially depleted at zero gate bias.

Owner:SENSOR ELECTRONICS TECH

Enhancement-mode III-N devices, circuits, and methods

ActiveUS7932539B2High breakdown fieldHigh Power Handling CapabilitySemiconductor devicesResistPhotoresist

A method of fabricating AlGaN / GaN enhancement-mode heterostructure field-effect transistors (HFET) using fluorine-based plasma immersion or ion implantation. The method includes: 1) generating gate patterns; 2) exposing the AlGaN / GaN heterostructure in the gate region to fluorine-based plasma treatment with photoresist as the treatment mask in a self-aligned manner; 3) depositing the gate metal to the plasma treated AlGaN / GaN heterostructure surface; 4) lifting off the metal except the gate electrode; and 5) high temperature post-gate annealing of the sample. This method can be used to shift the threshold voltage of a HFET toward a more positive value, and ultimately convert a depletion-mode HFET to an enhancement-mode HFET (E-HFET).

Owner:THE HONG KONG UNIV OF SCI & TECH

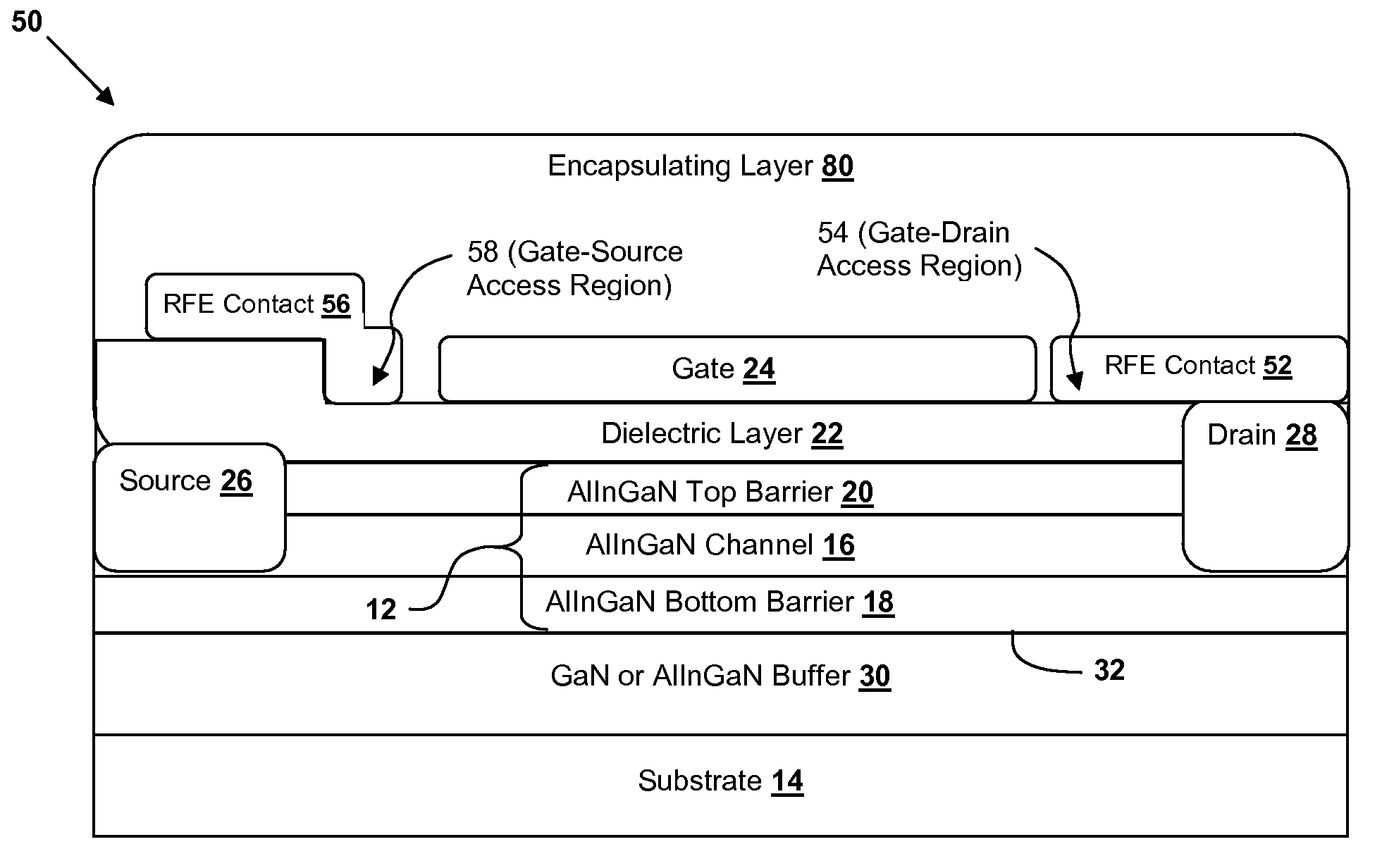

Enhancement mode insulated gate heterostructure field-effect transistor with electrically isolated RF-enhanced source contact

Aspects of the present invention provide an enhancement mode (E-mode) insulated gate (IG) double heterostructure field-effect transistor (DHFET) having low power consumption at zero gate bias, low gate currents, and / or high reliability. An E-mode HFET in accordance with an embodiment of the invention includes: top and bottom barrier layers; and a channel layer sandwiched between the bottom and the top barrier layers, wherein the bottom and top barrier layers have a larger bandgap than the channel layer, and wherein polarization charges of the bottom barrier layer deplete the channel layer and polarization charges of the top barrier layer induce carriers in the channel layer; and wherein a total polarization charge in the bottom barrier layer is larger than a total polarization charge in the top barrier layer such that the channel layer is substantially depleted at zero gate bias.

Owner:SENSOR ELECTRONICS TECH

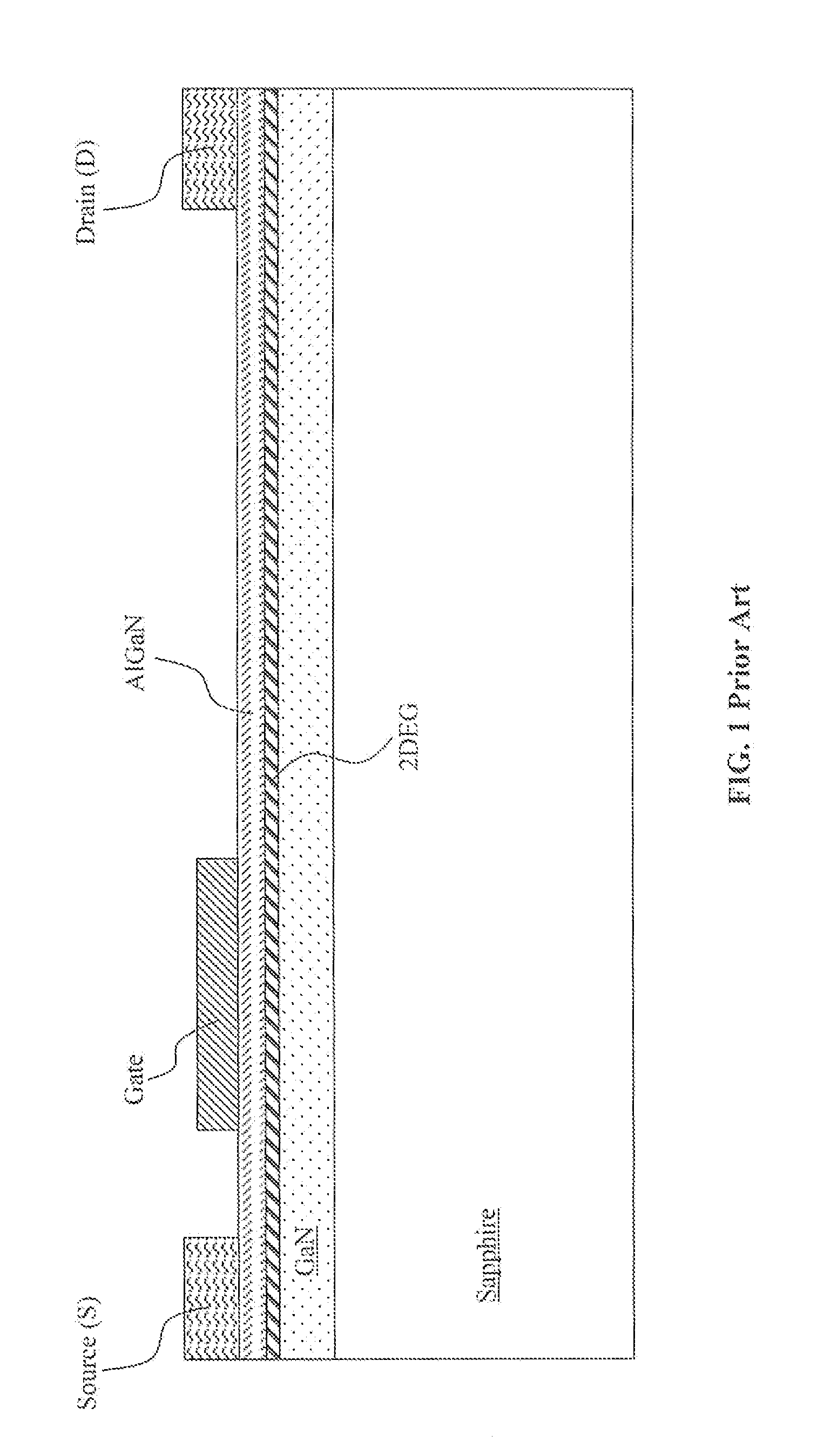

High electron mobility devices

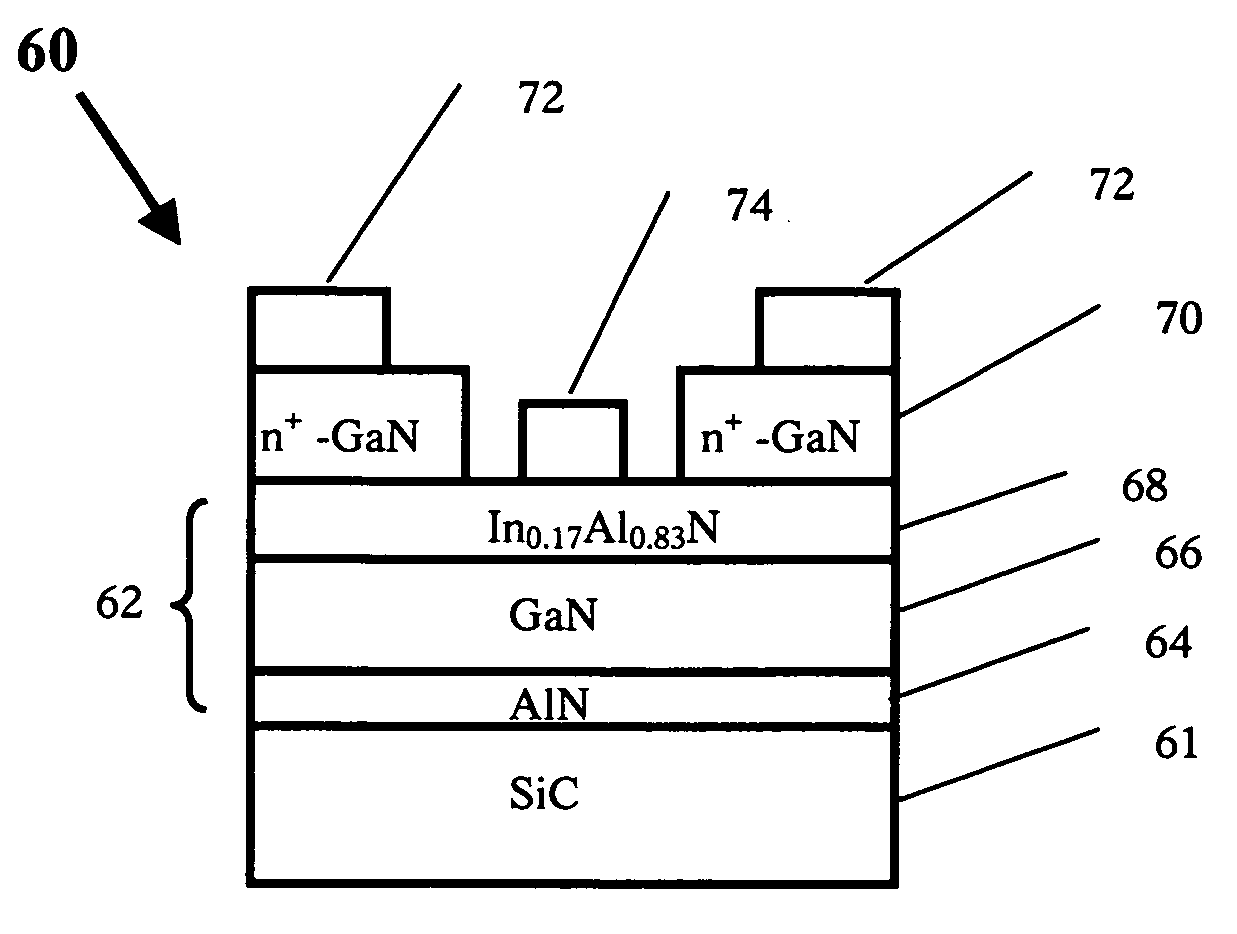

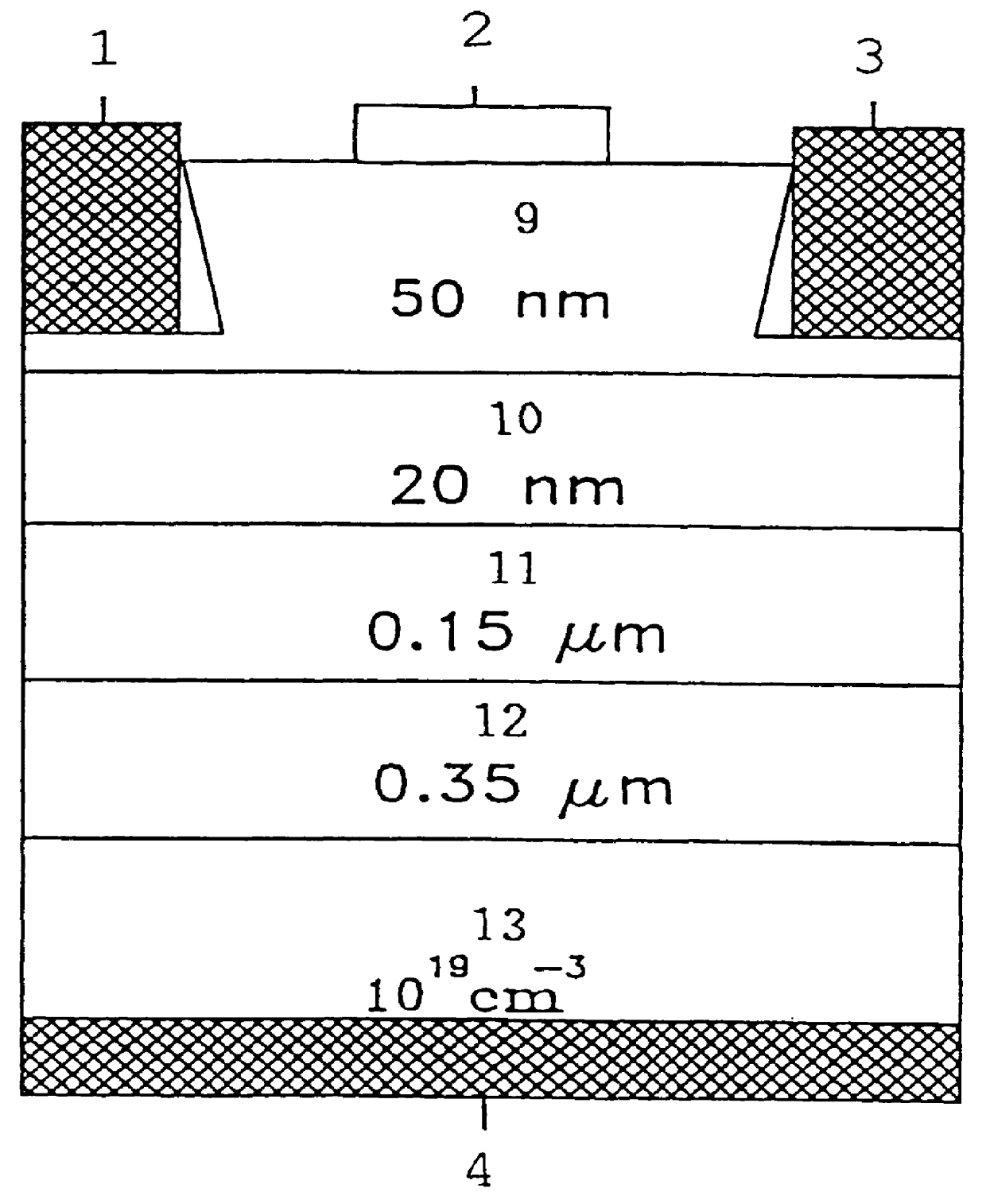

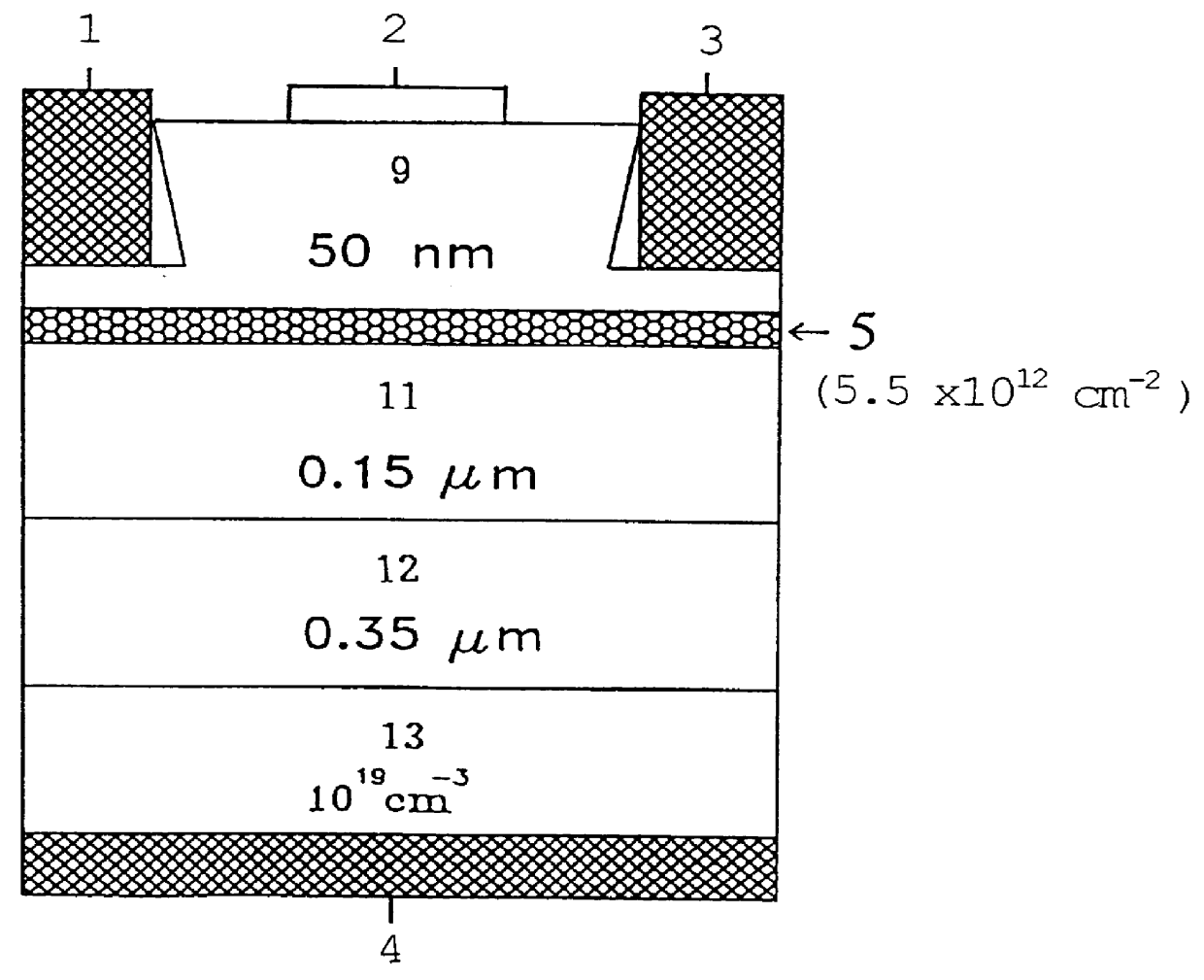

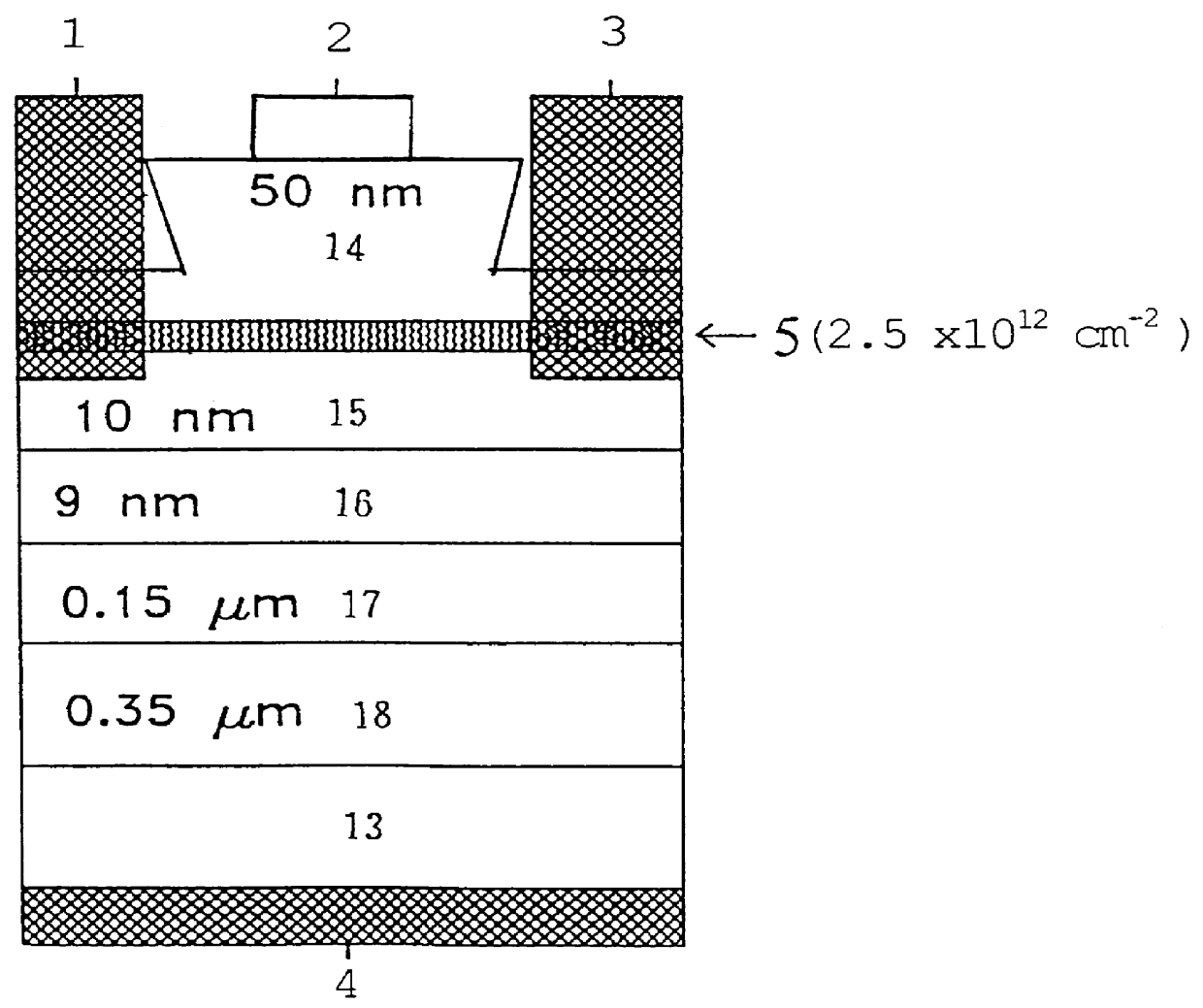

InactiveUS20060163594A1High currentPower capacitySemiconductor devicesLow noiseSatellite broadcasting

The present invention is directed to high frequency, high power or low noise devices such as low noise amplifiers, amplifiers operating at frequencies in the range of 1 GHz up to 400 GHz, radars, portable phones, satellite broadcasting or communication systems, or other devices and systems that use high electron mobility transistors, also called hetero-structure field-effect transistors. A high electron mobility transistor (HEMT) includes a substrate, a quantum well structure and electrodes. The high electron mobility transistor has a polarization-induced charge of high density. Preferably, the quantum well structure includes an AlN buffer layer, an un-doped GaN layer, and an un-doped InAlN layer.

Owner:KUZMIK JAN

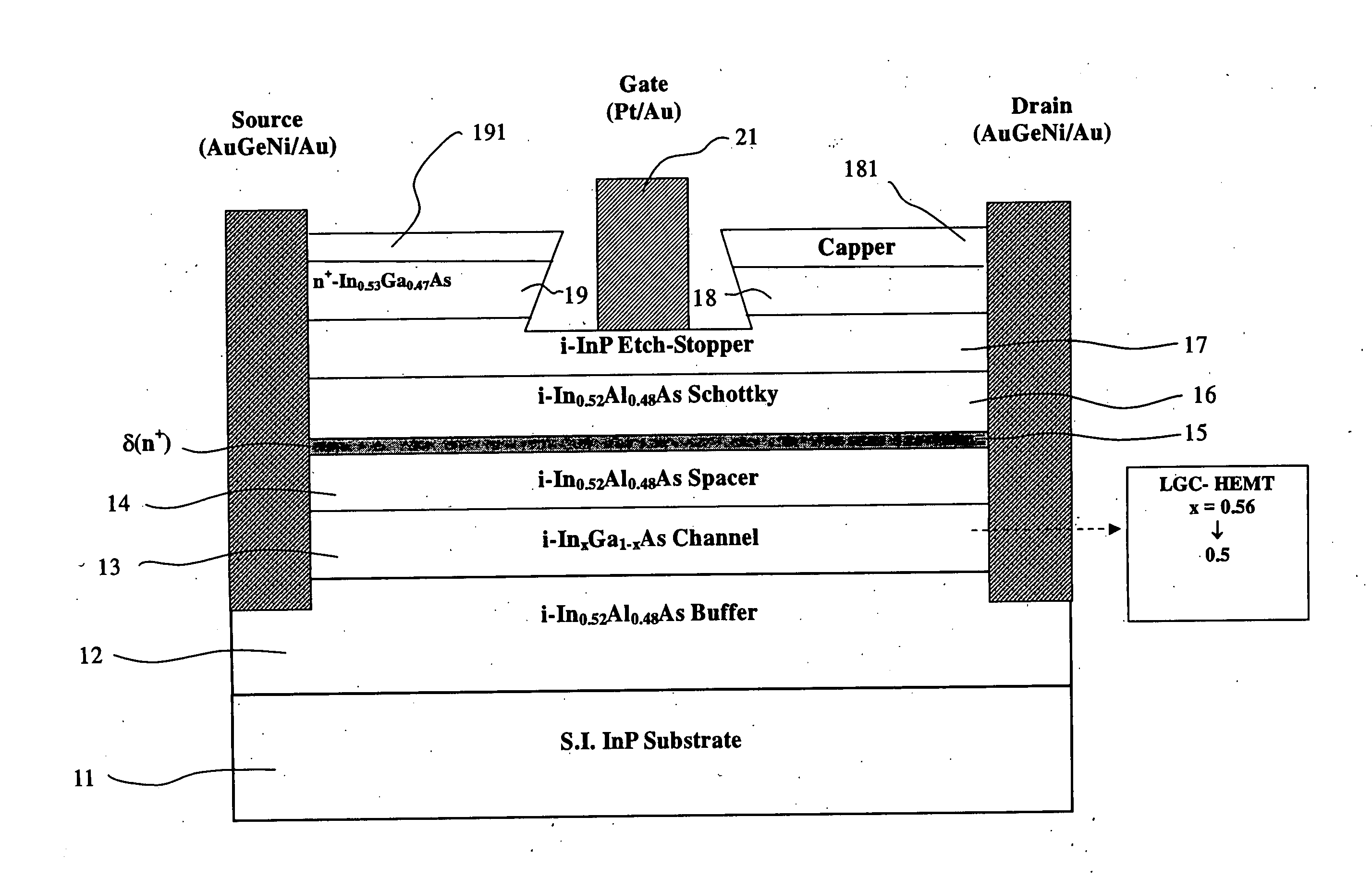

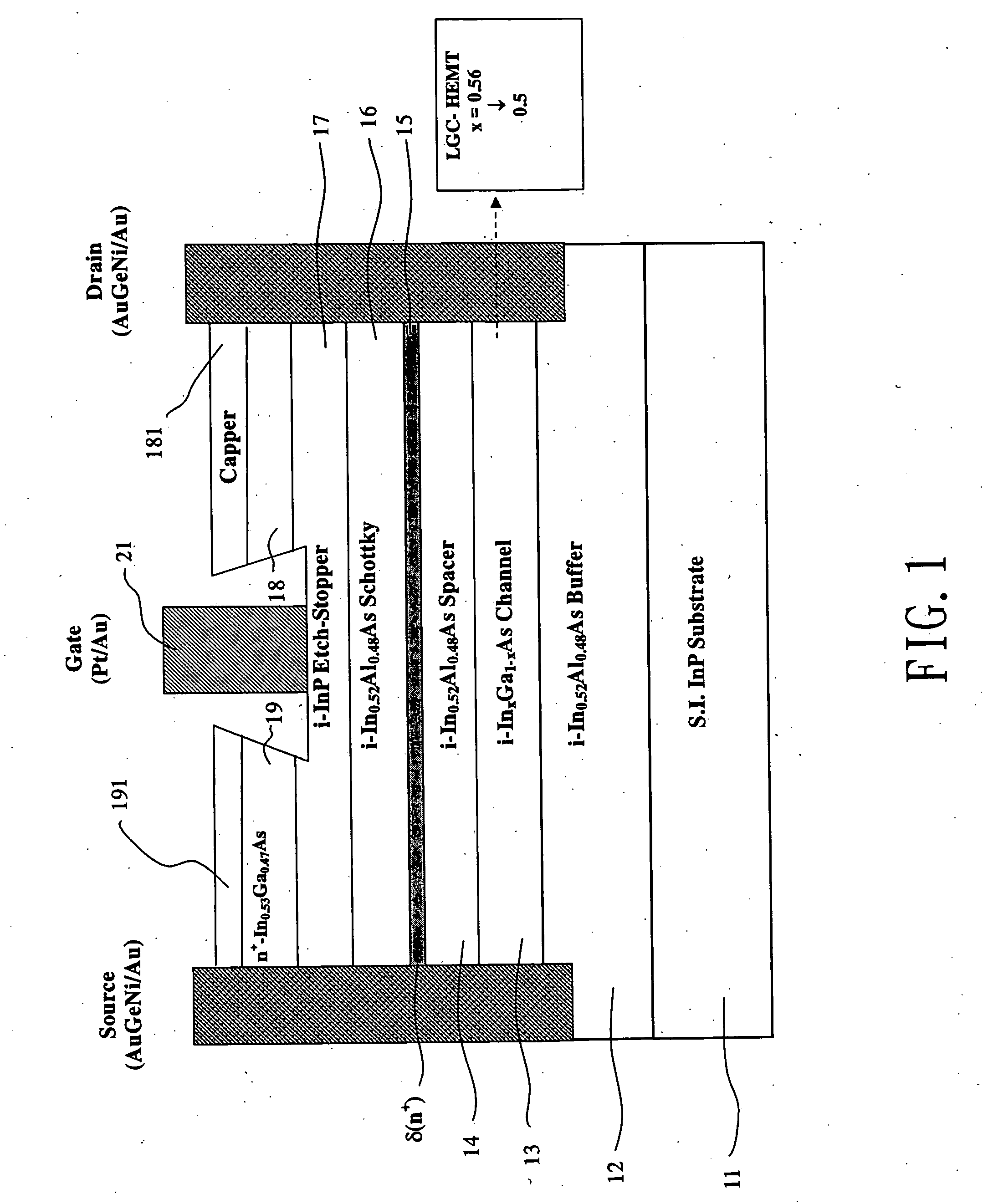

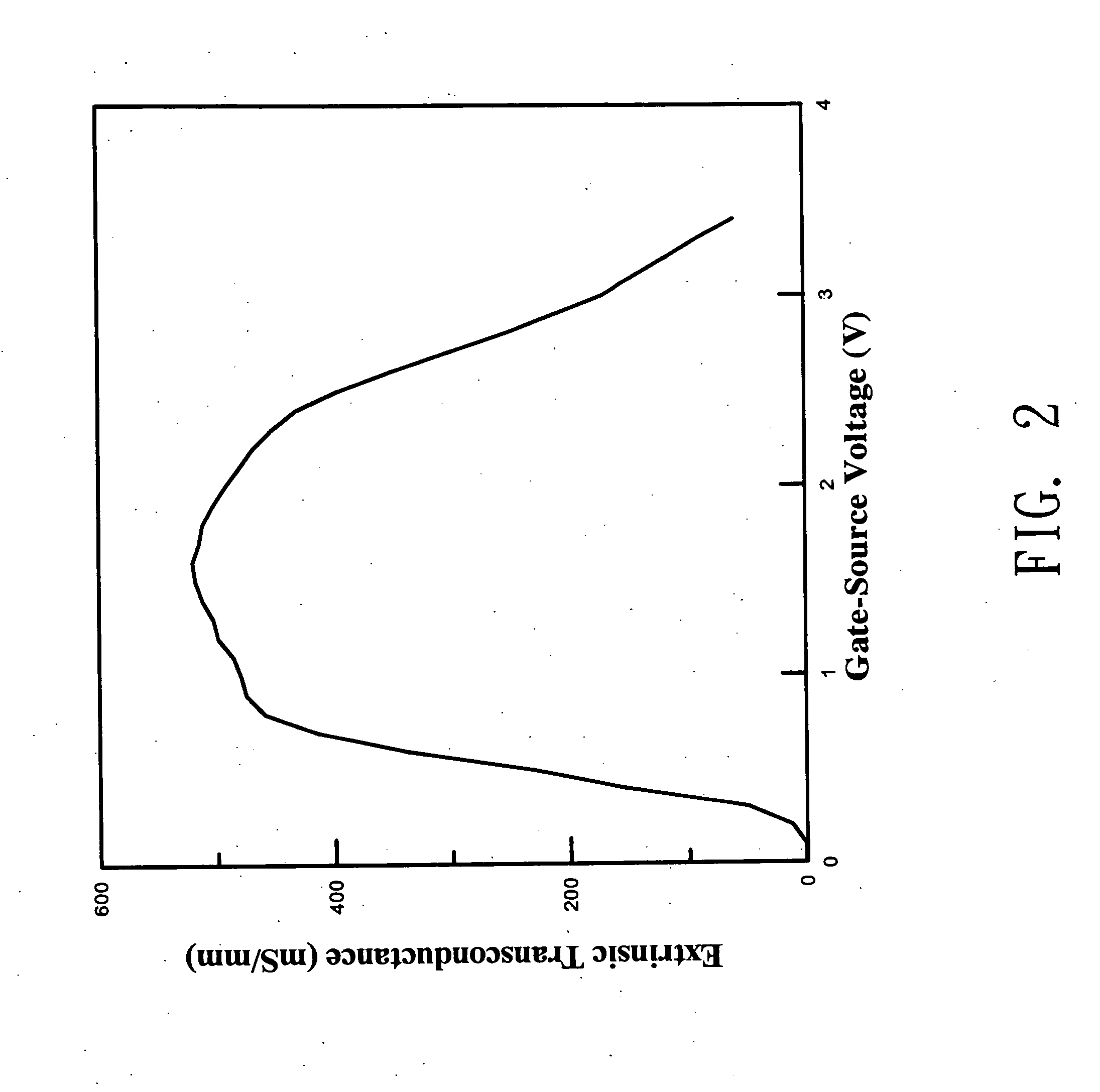

High linear enhancement-mode heterostructure field-effect transistor

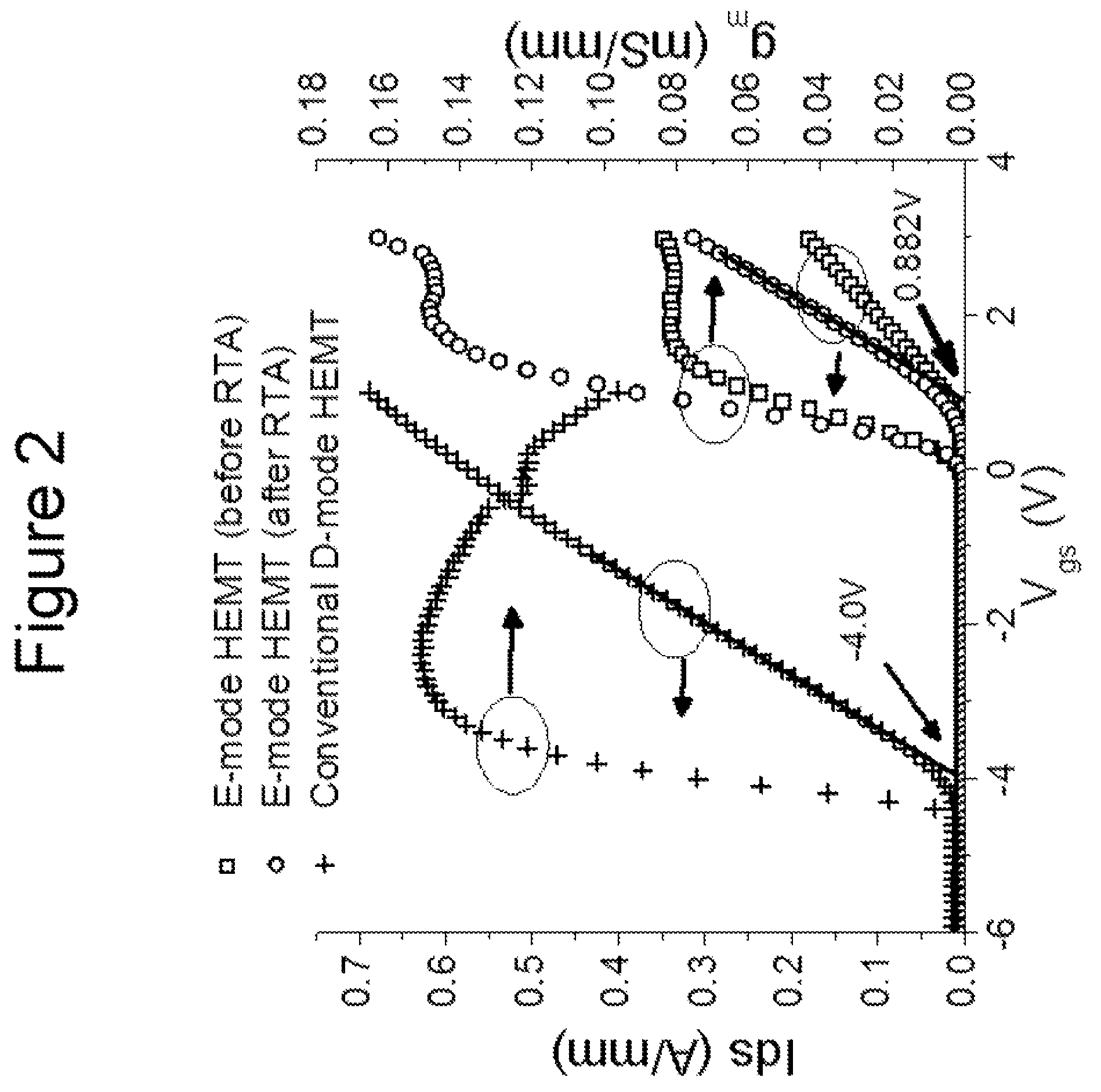

InactiveUS20070200142A1Increase rangeHigh linear E-mode heterostructure FETSemiconductor devicesPush pullLinear amplification

Owner:FENG CHIA UNIVERSITY

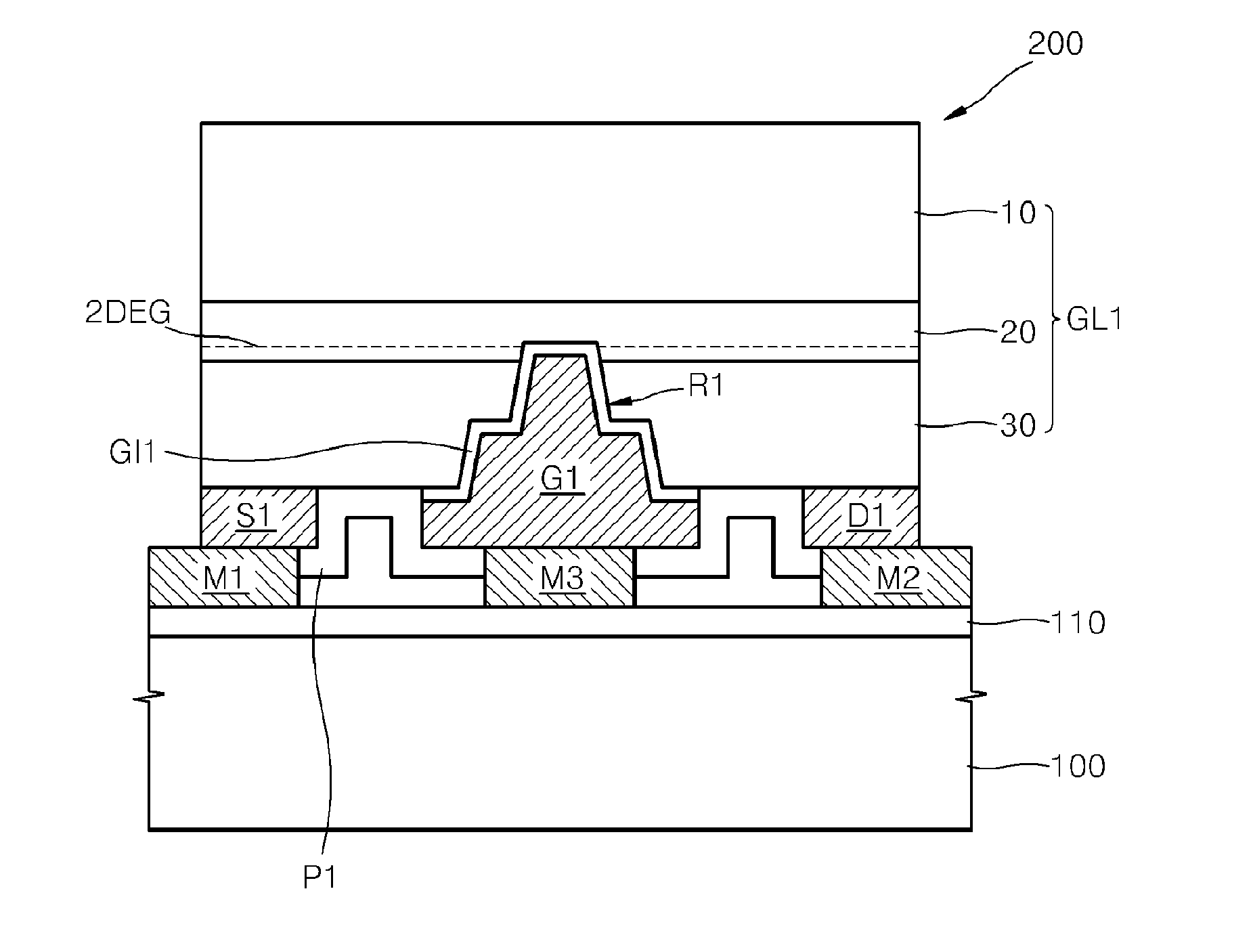

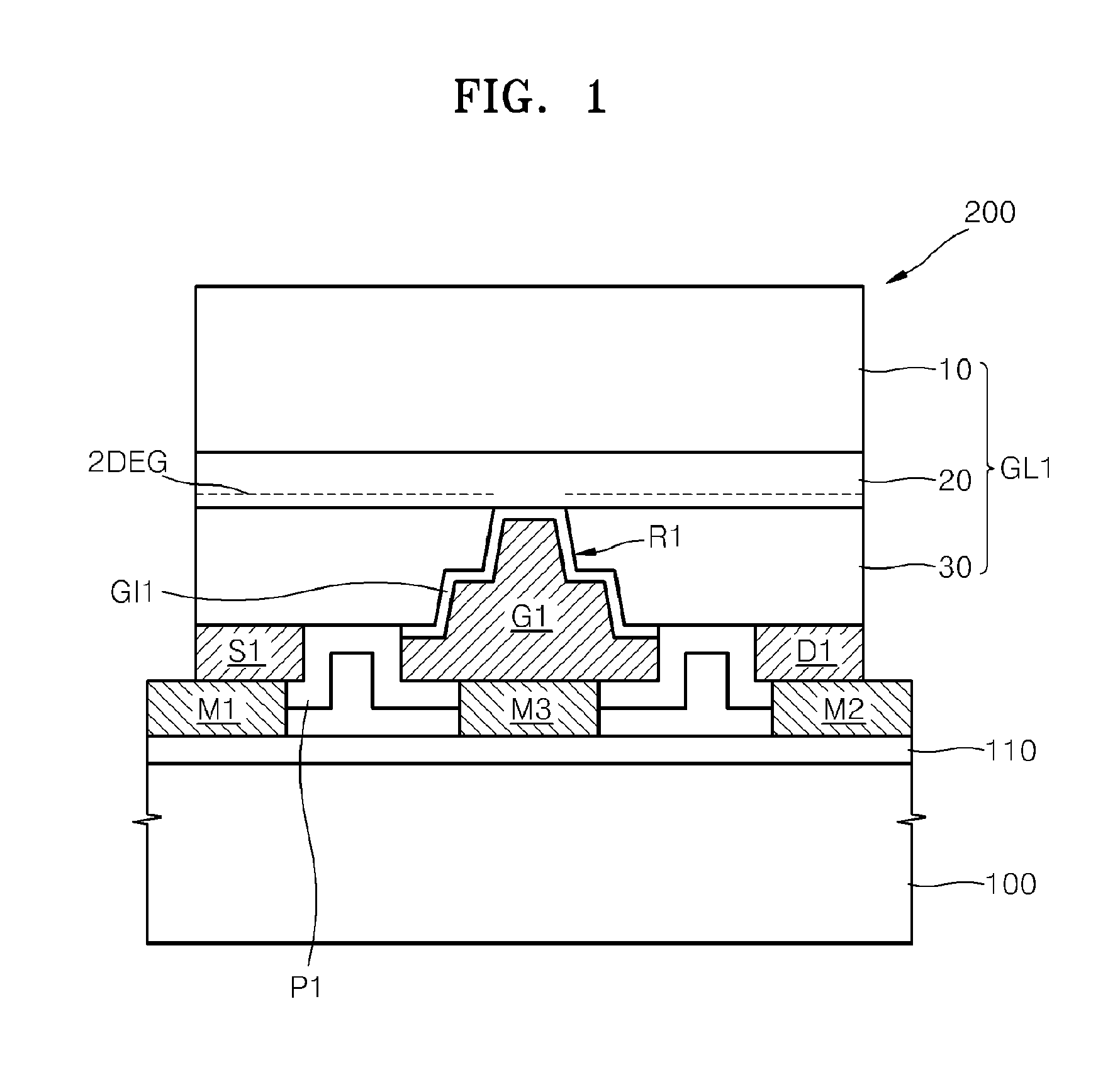

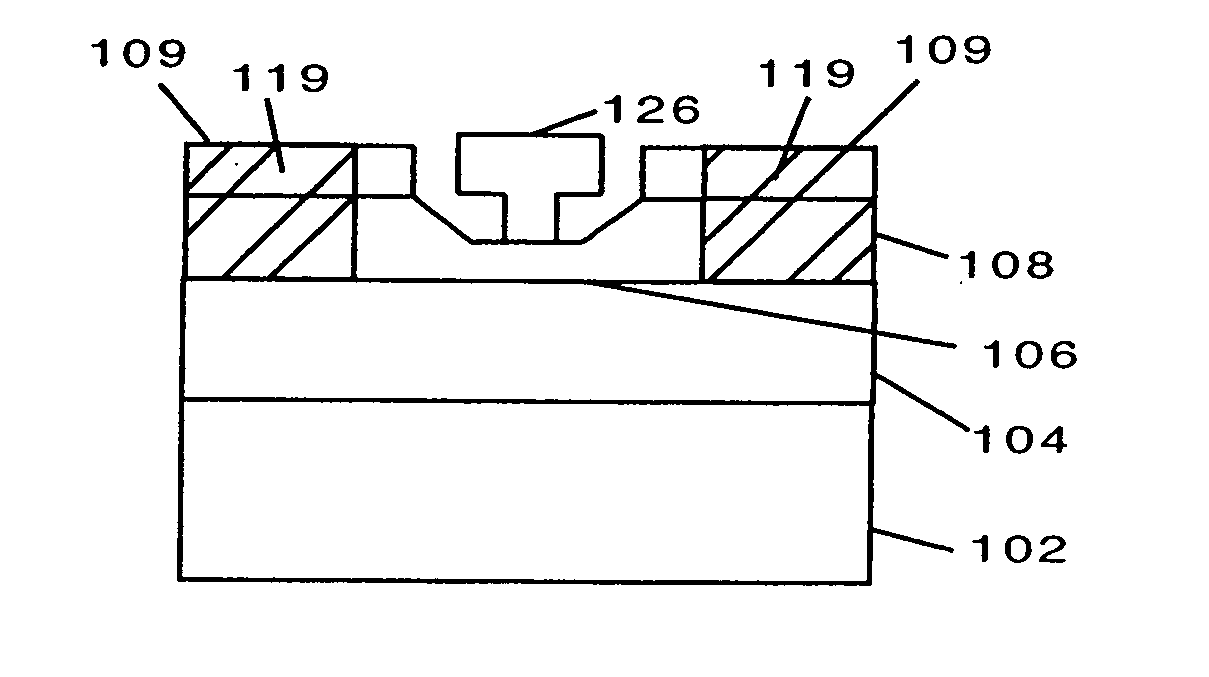

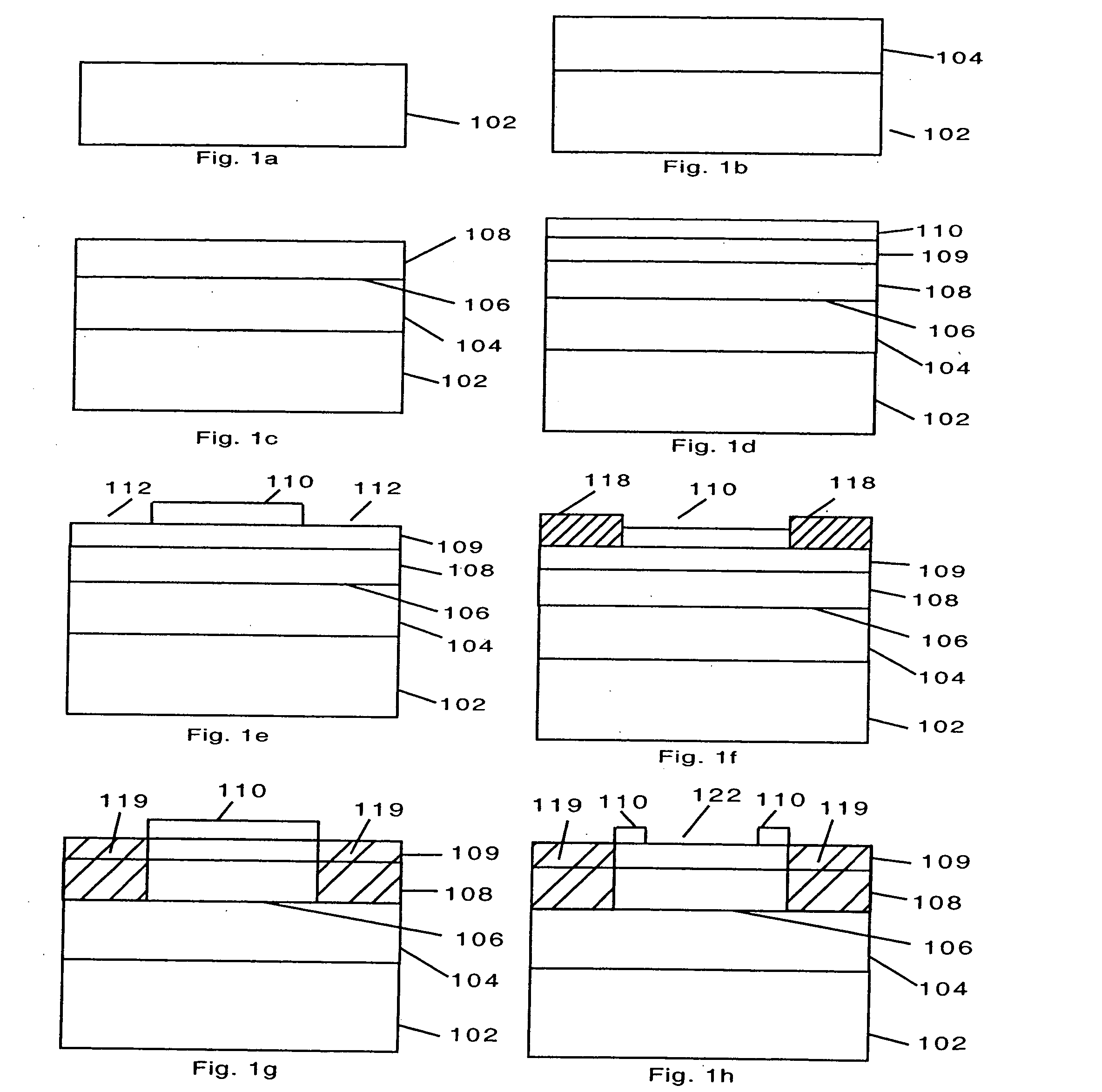

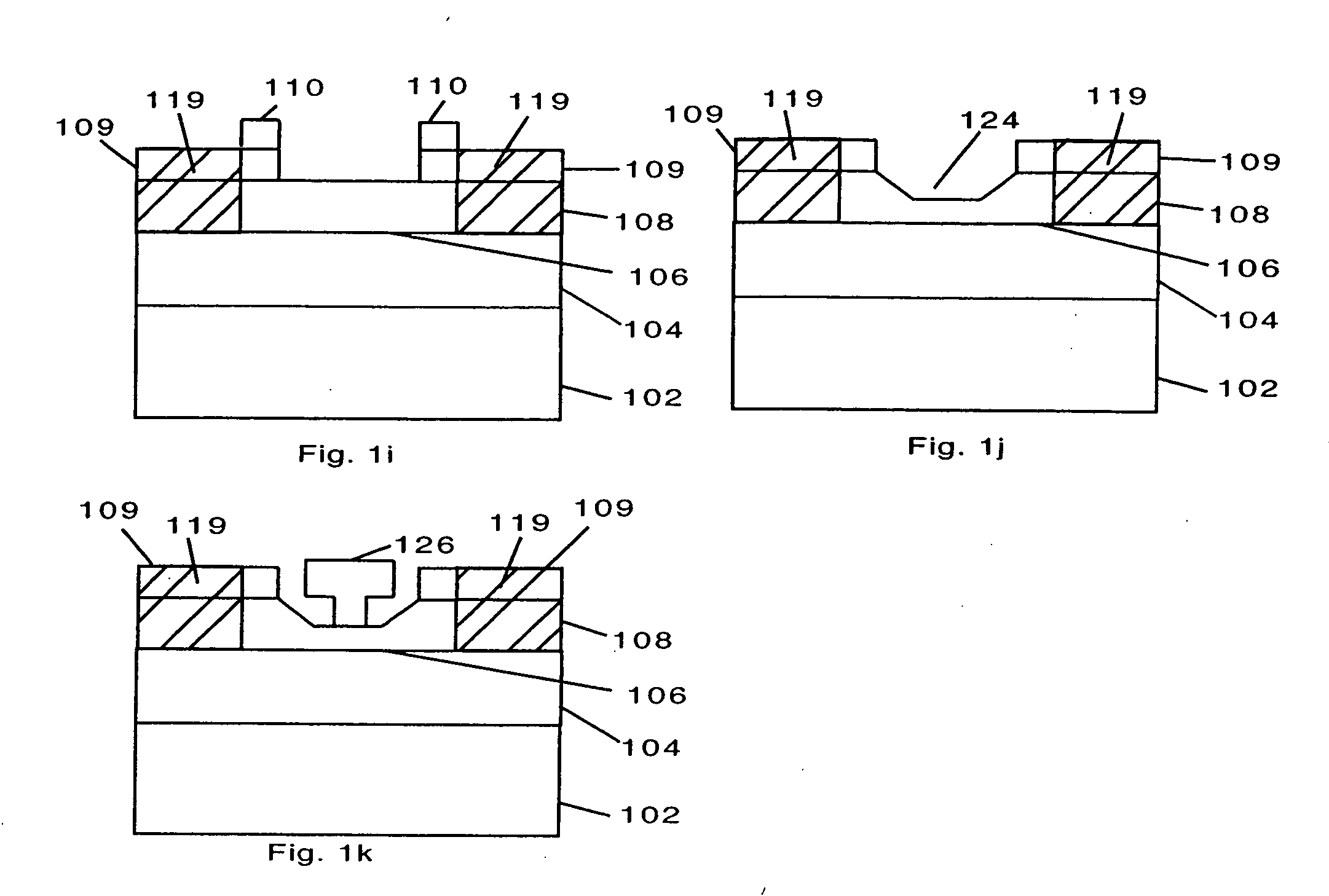

Gallium nitride based semiconductor devices and methods of manufacturing the same

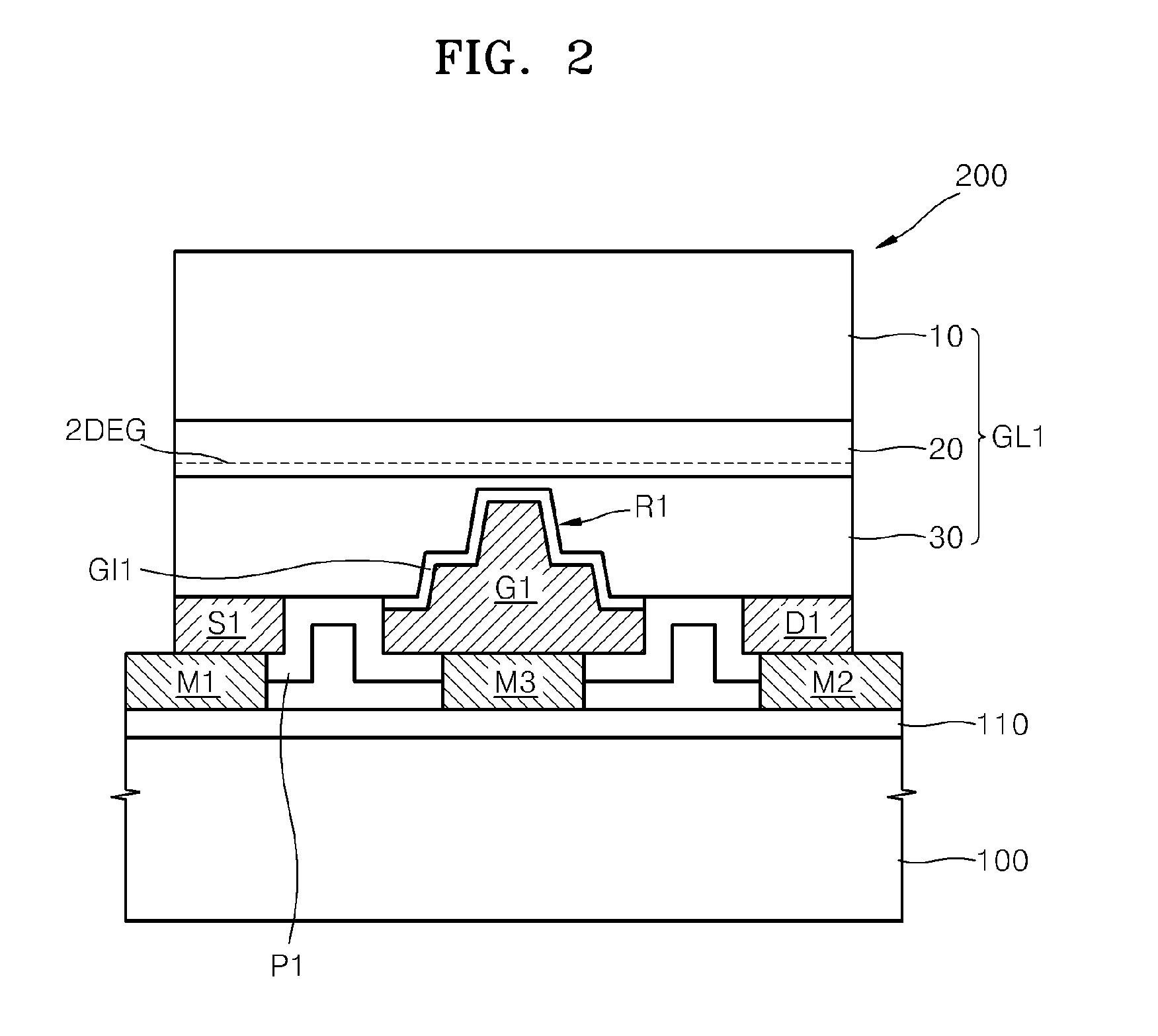

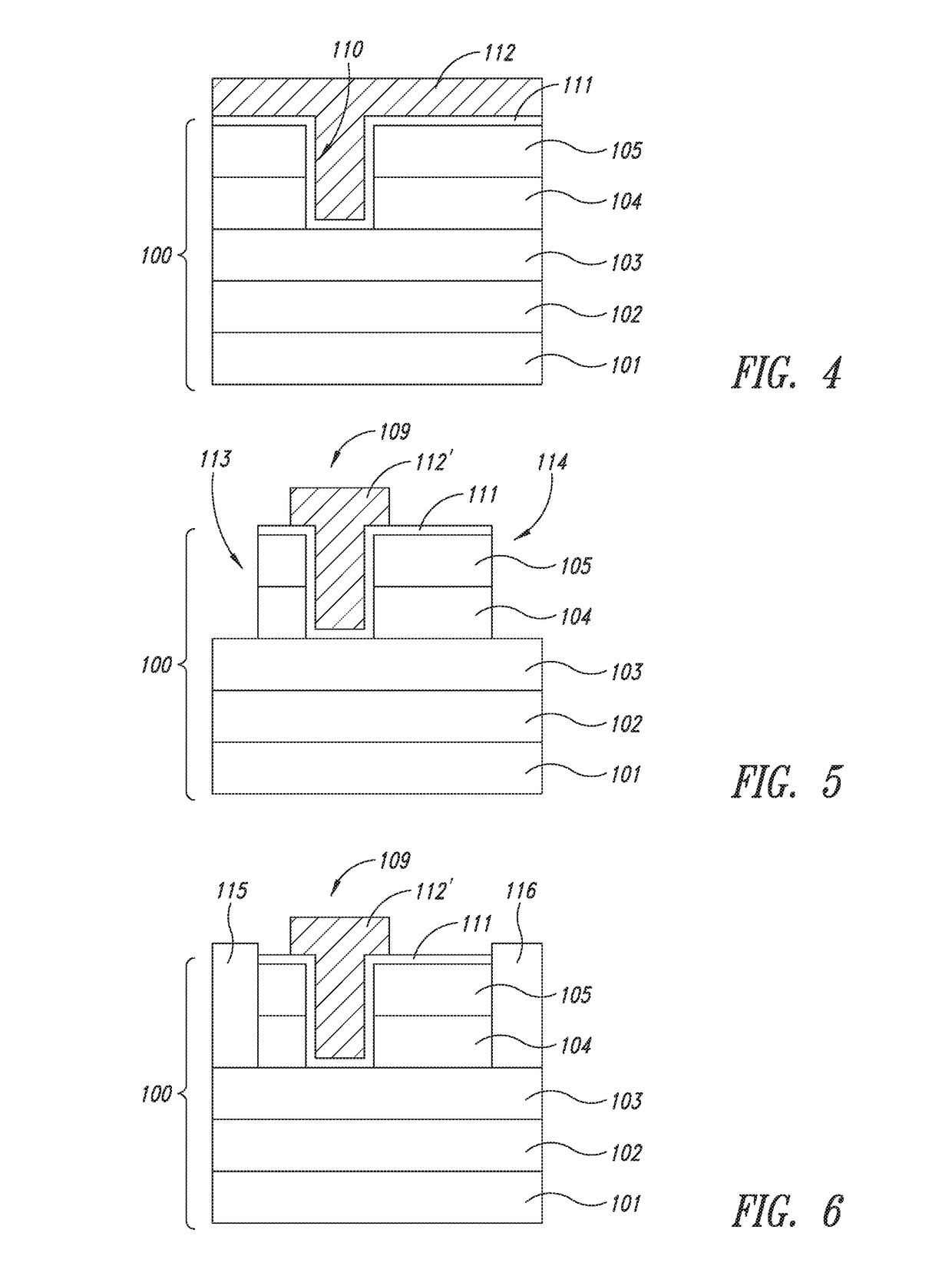

InactiveUS20120061727A1Good heat dissipationImprove withstand voltage characteristicsSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

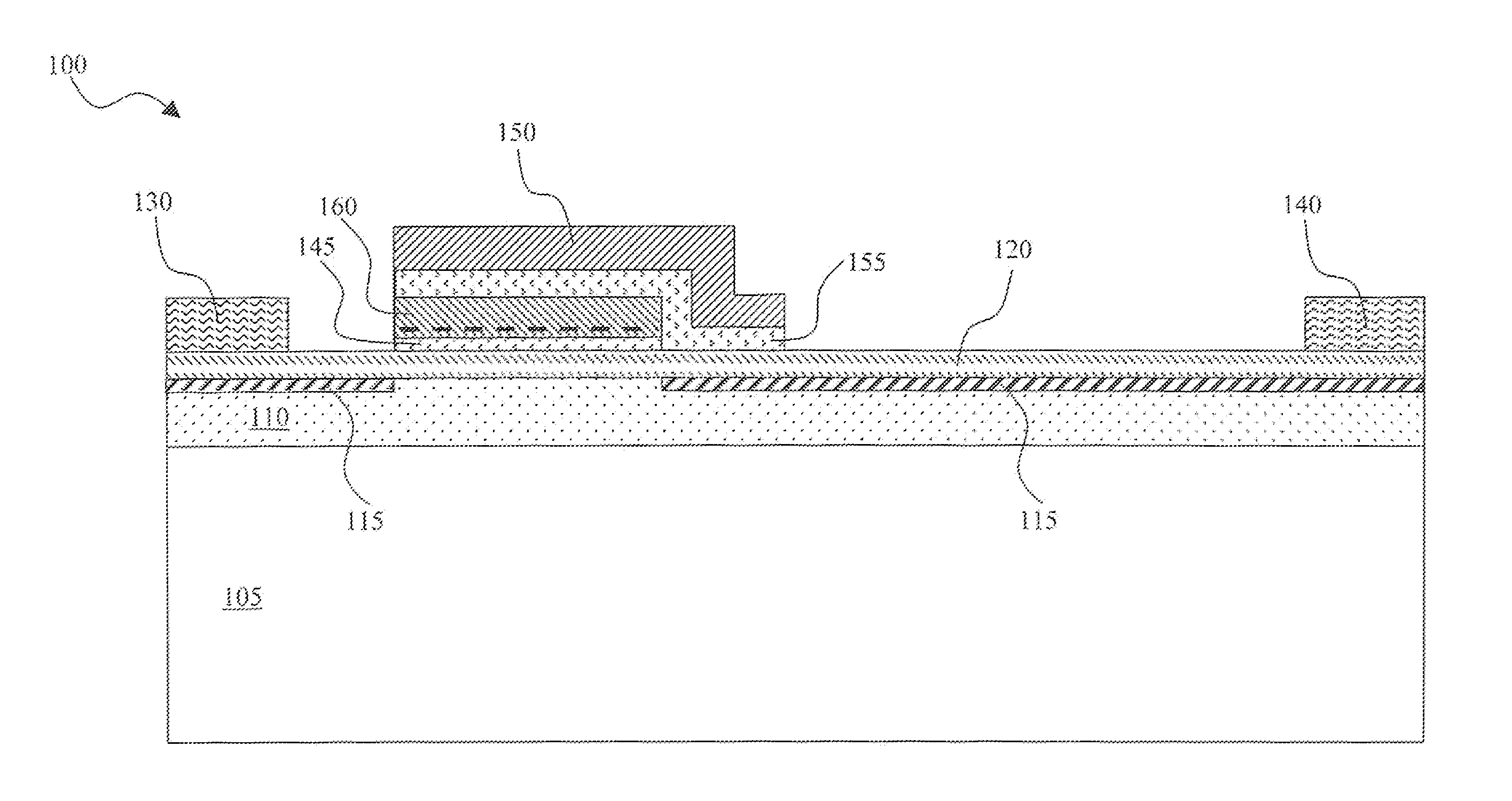

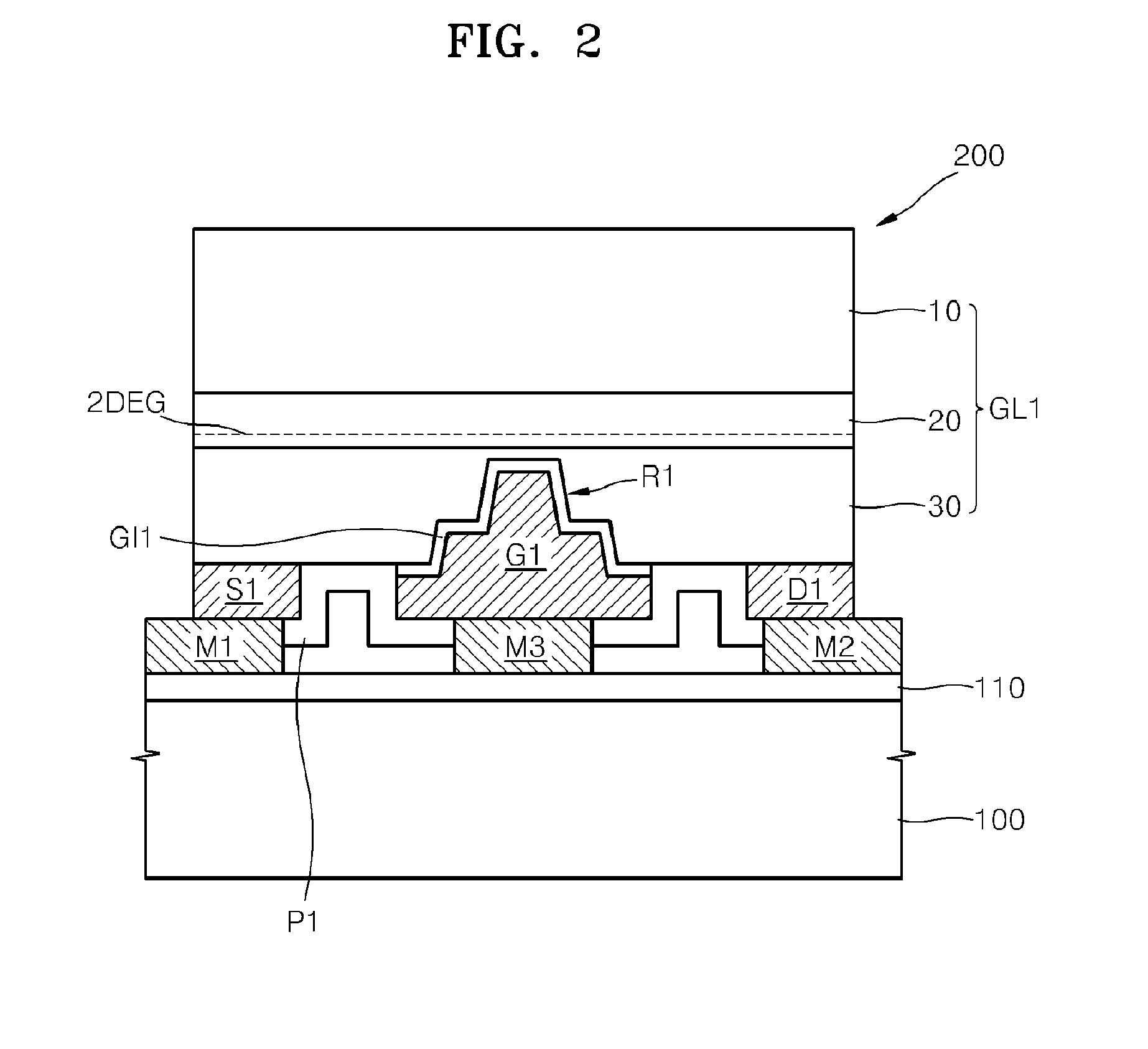

Gallium nitride (GaN) based semiconductor devices and methods of manufacturing the same. The GaN-based semiconductor device may include a heterostructure field effect transistor (HFET) or a Schottky diode, arranged on a heat dissipation substrate. The HFET device may include a GaN-based multi-layer having a recess region; a gate arranged in the recess region; and a source and a drain that are arranged on portions of the GaN-based multi-layer at two opposite sides of the gate (or the recess region). The gate, the source, and the drain may be attached to the heat dissipation substrate. The recess region may have a double recess structure. While such a GaN-based semiconductor device is being manufactured, a wafer bonding process and a laser lift-off process may be used.

Owner:SAMSUNG ELECTRONICS CO LTD

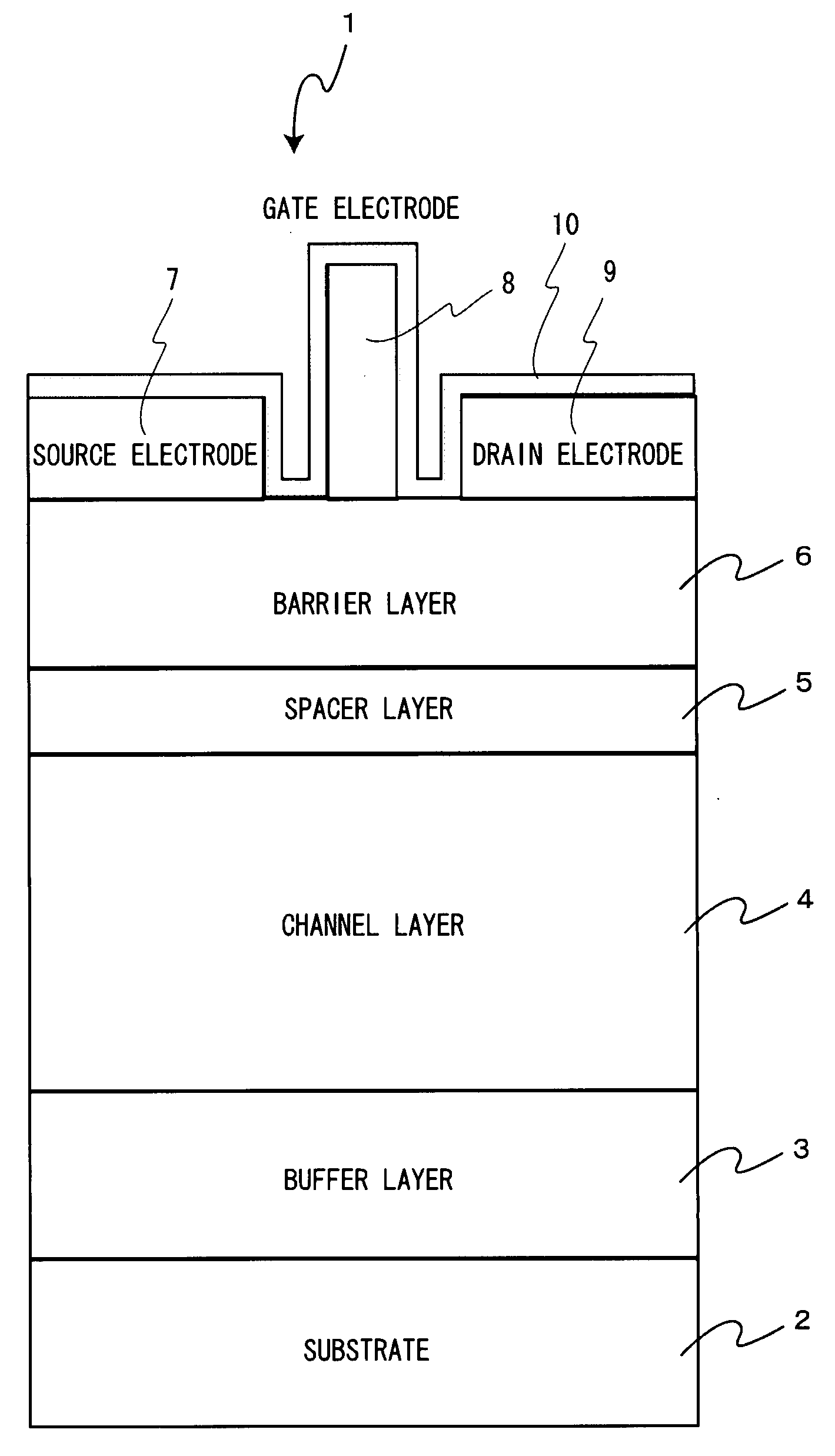

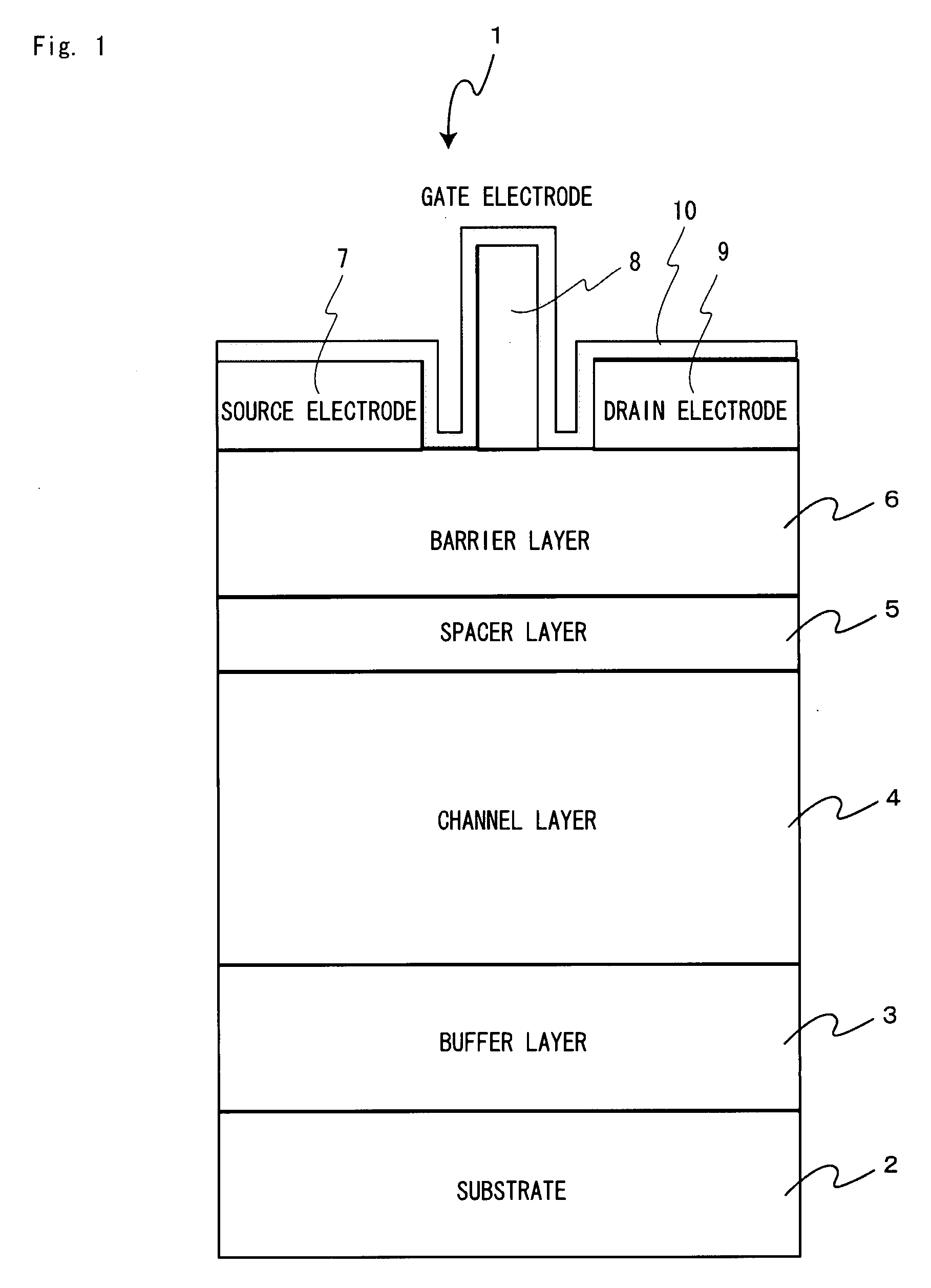

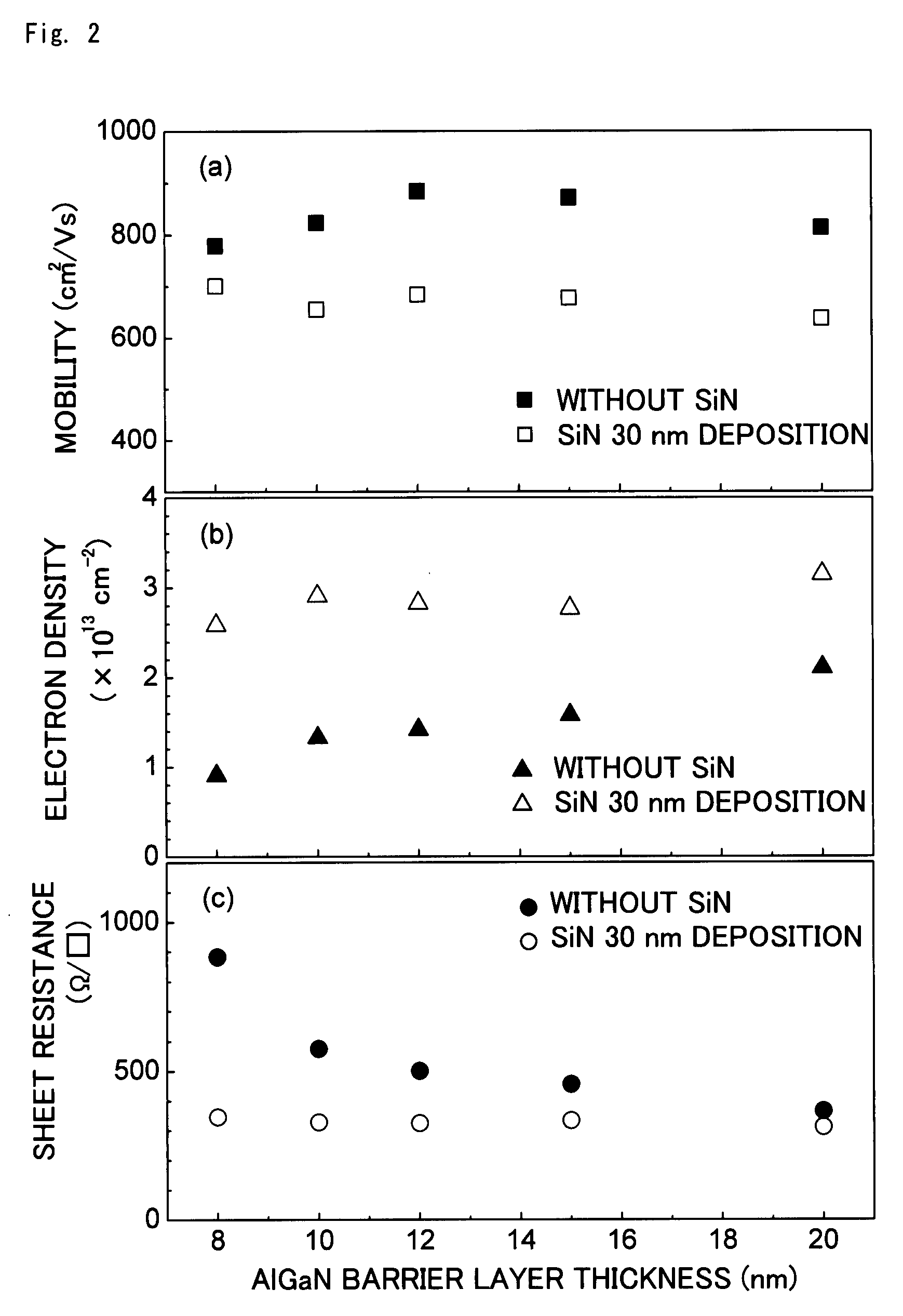

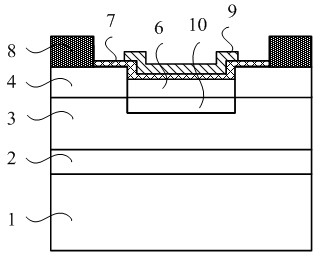

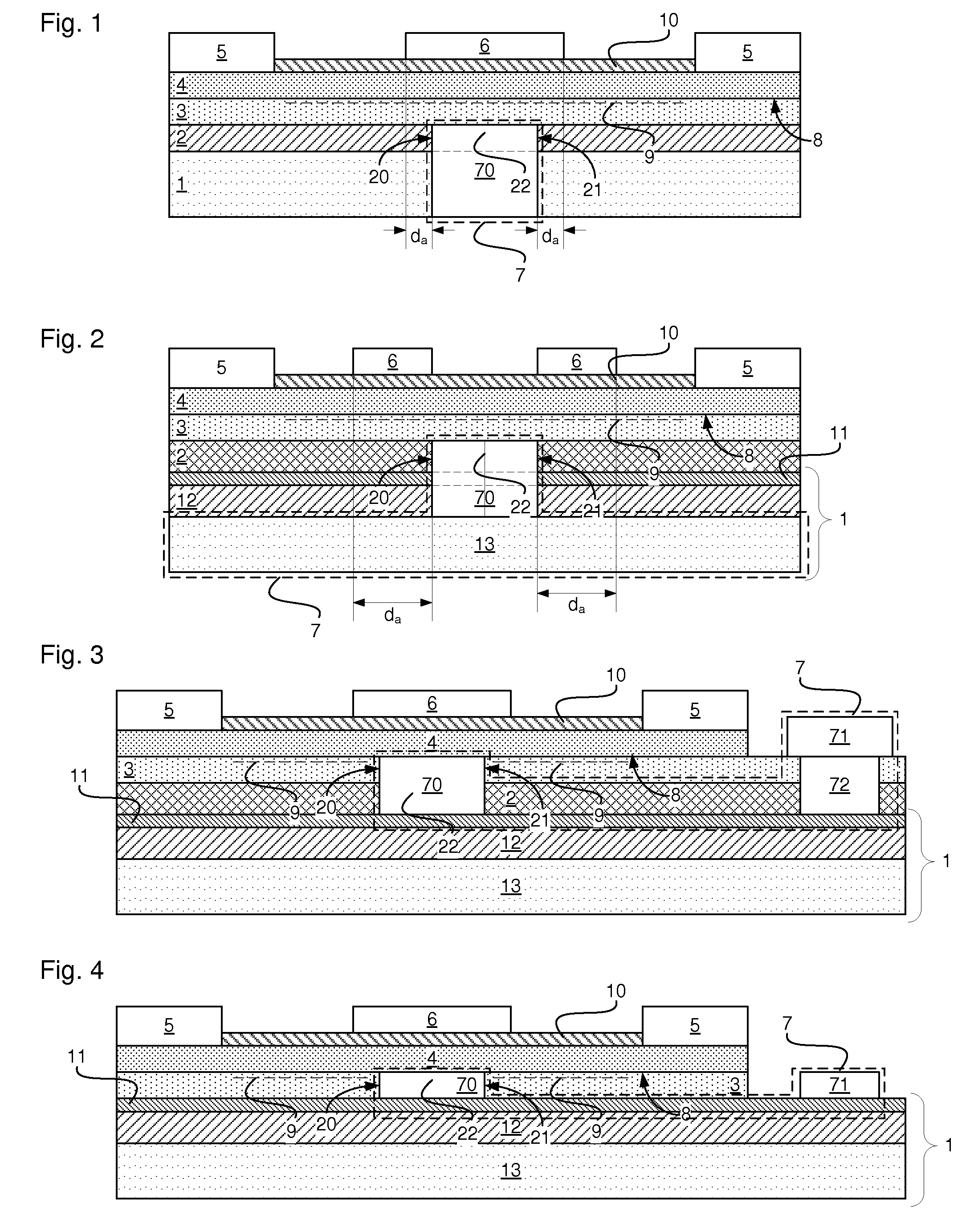

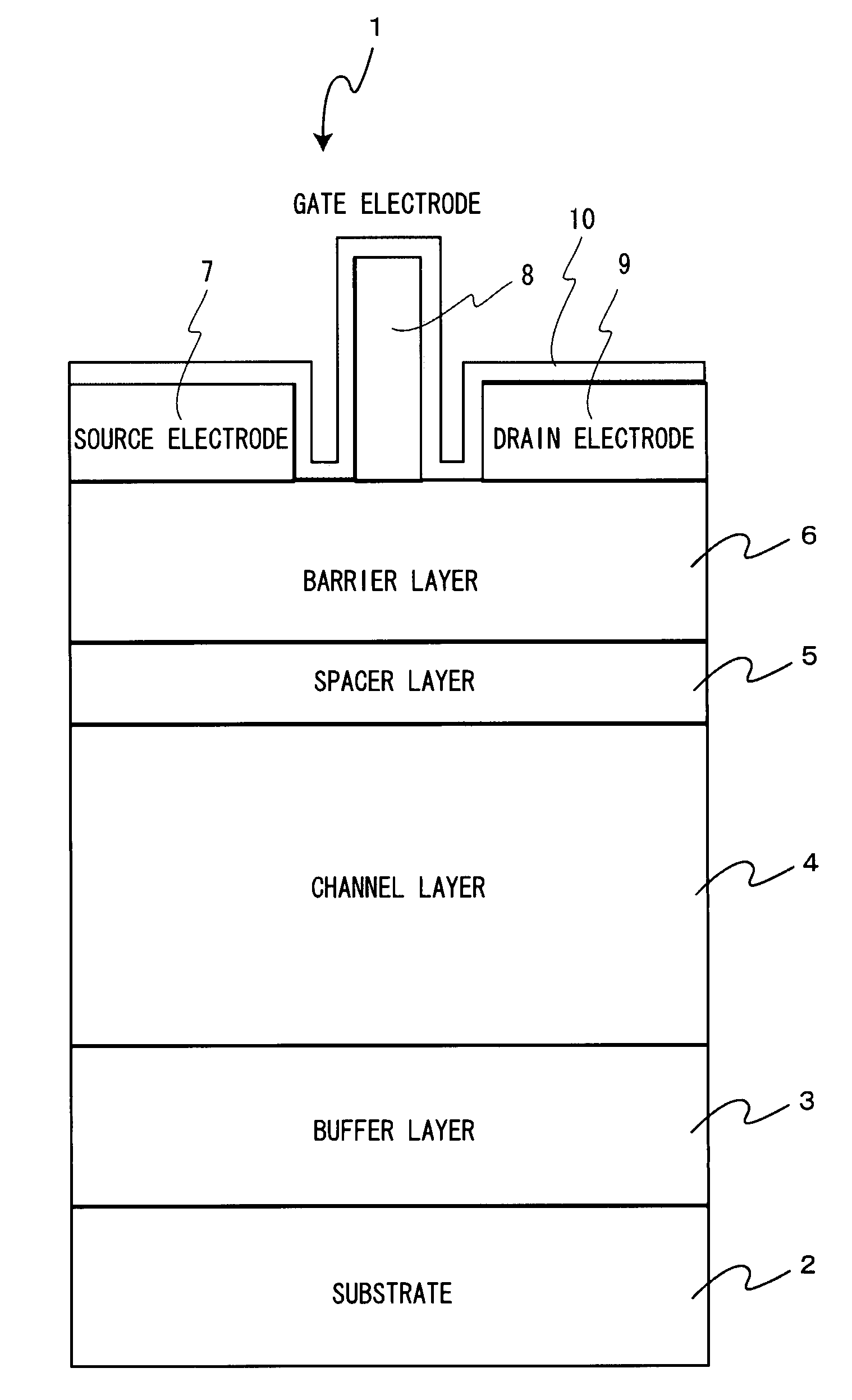

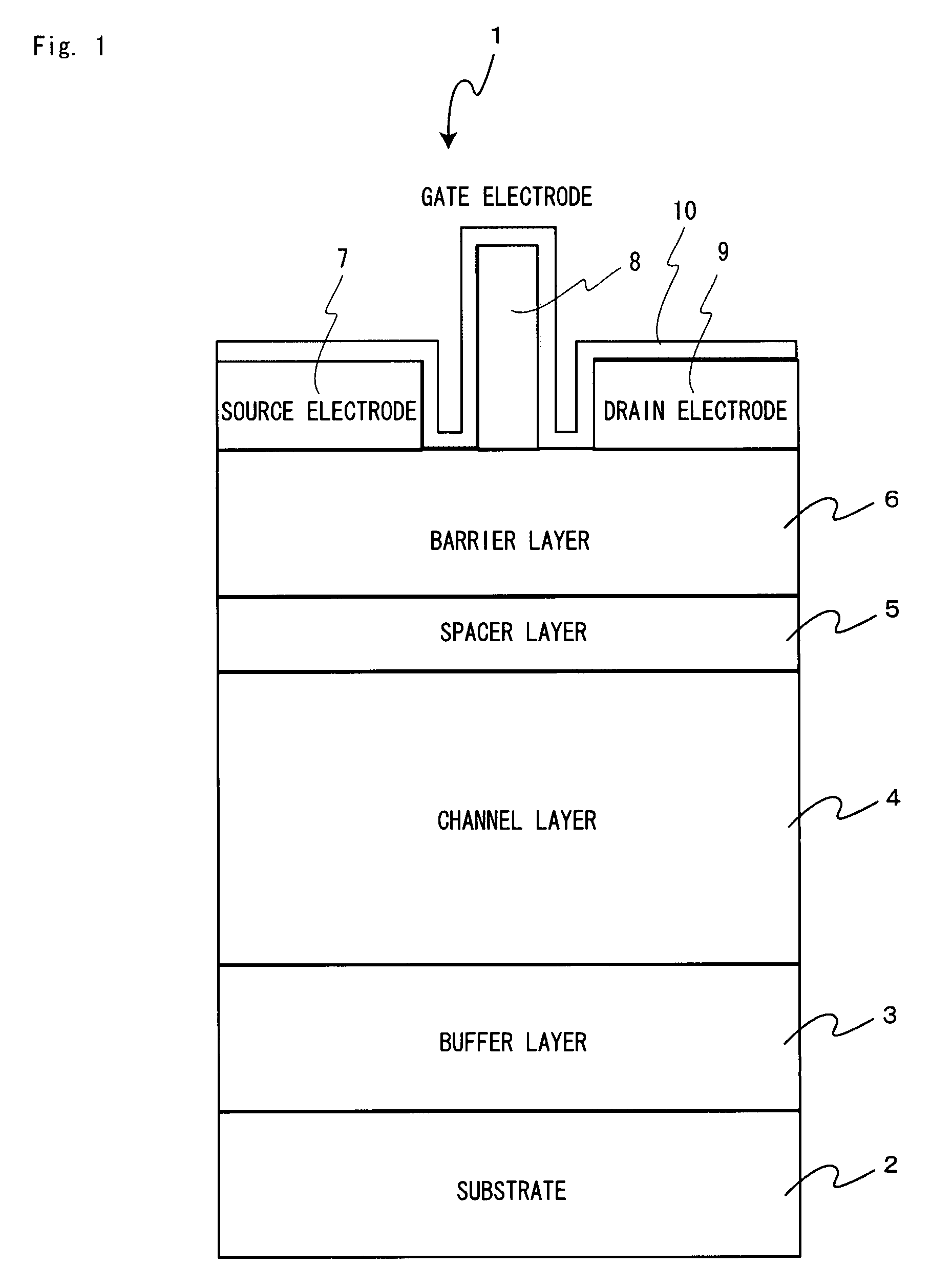

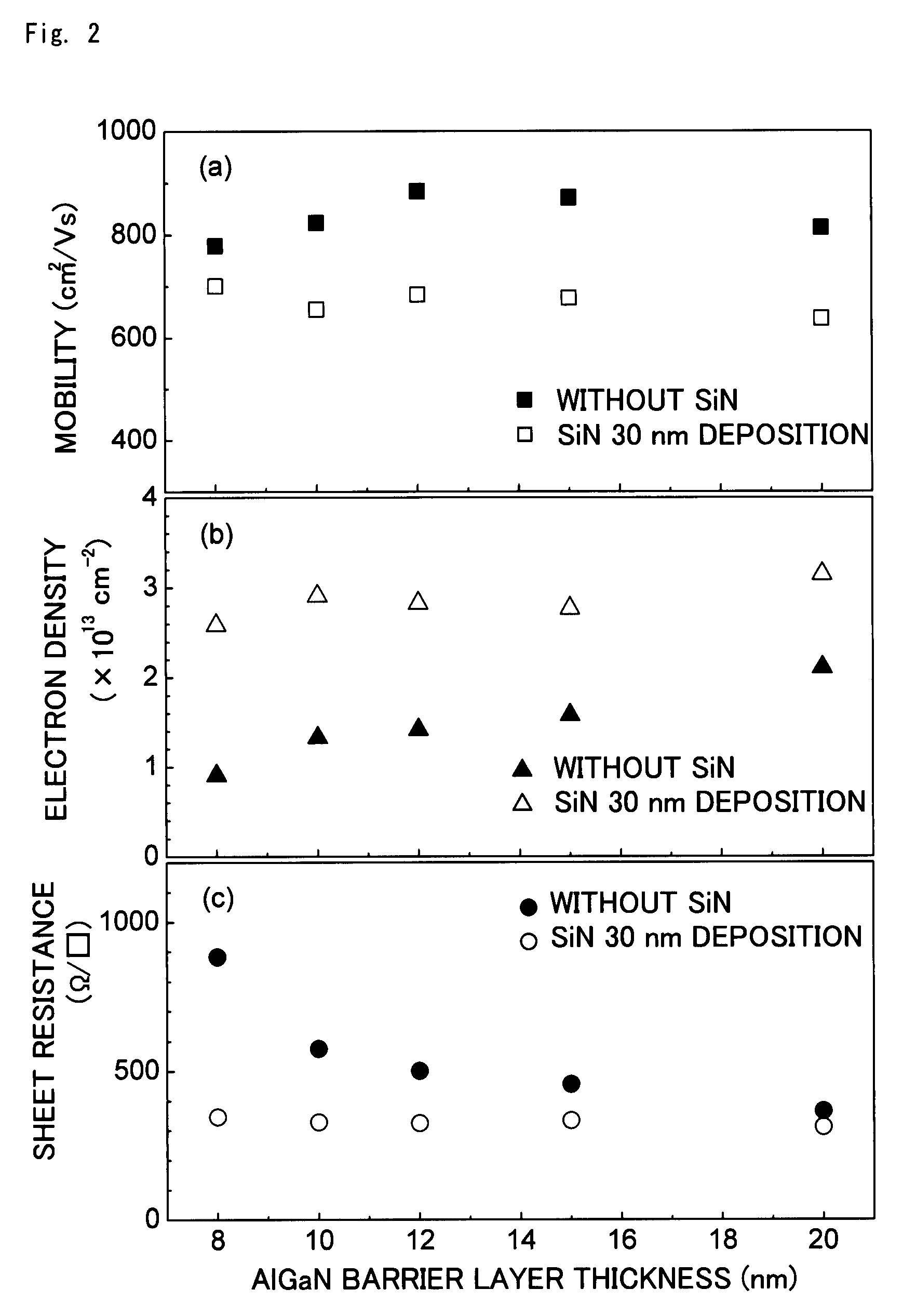

Gan-Based Field Effect Transistor and Production Method Therefor

InactiveUS20070295990A1Low mobilitySmall dispersionSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringBreakdown voltage

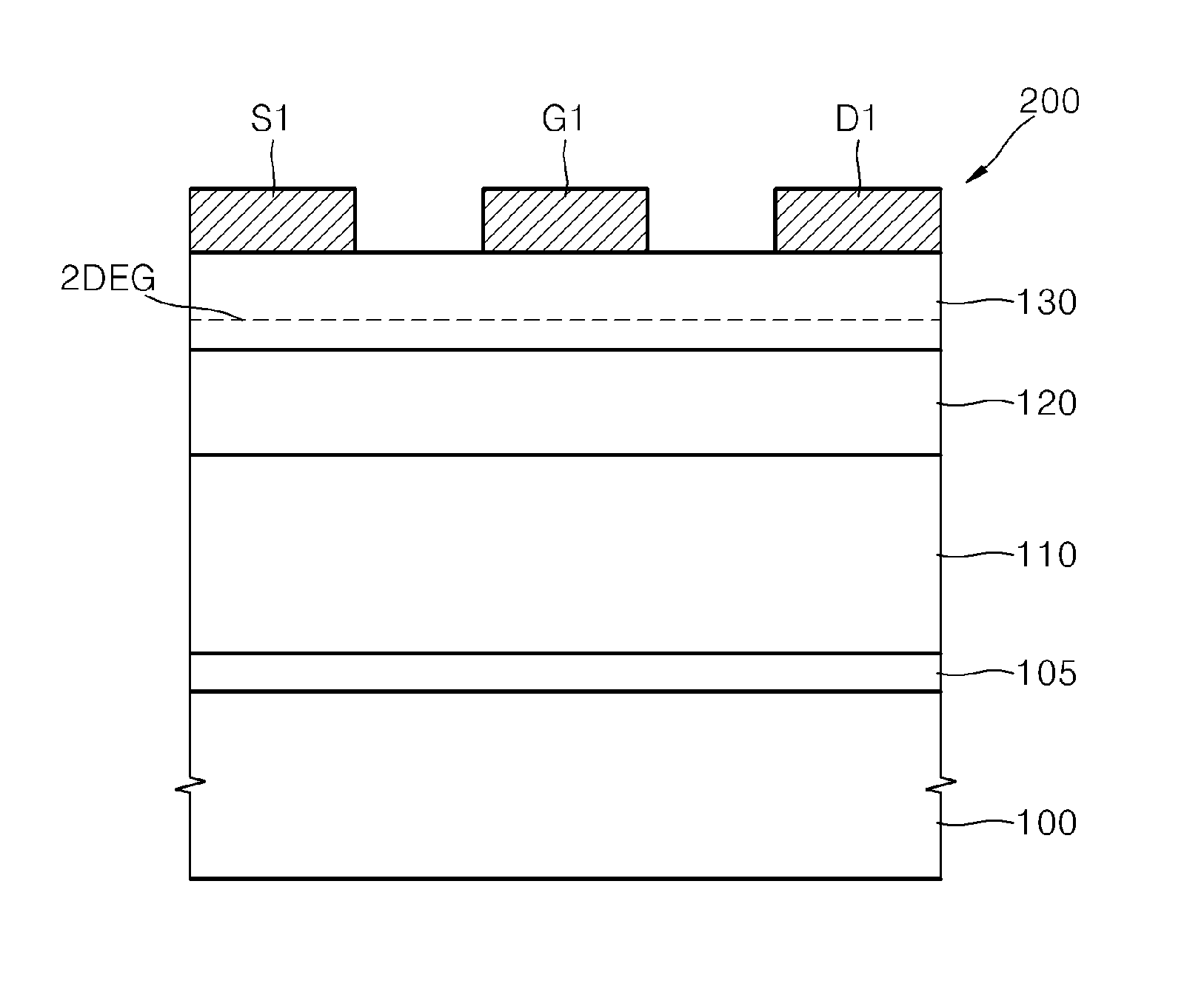

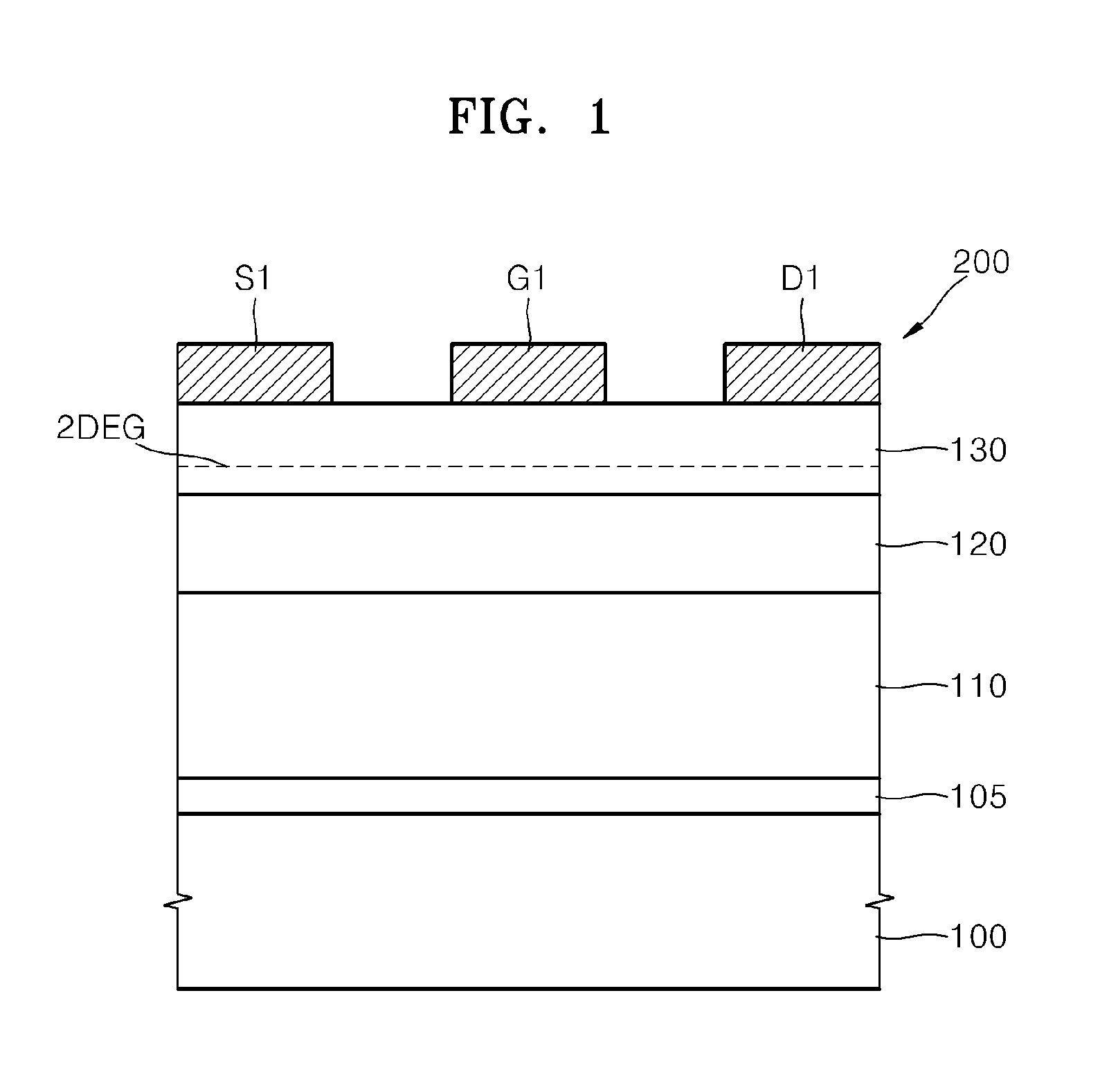

A GaN-based heterostructure field effect transistor capable of accomplishing higher output, higher breakdown voltage, higher speed, higher frequency, and the like. A heterostructure field effect transistor including a channel layer (4) of GaN and a barrier layer (6) of AlGaN, wherein the surface of a transistor element has an insulating film (10).

Owner:NAT INST OF INFORMATION & COMM TECH

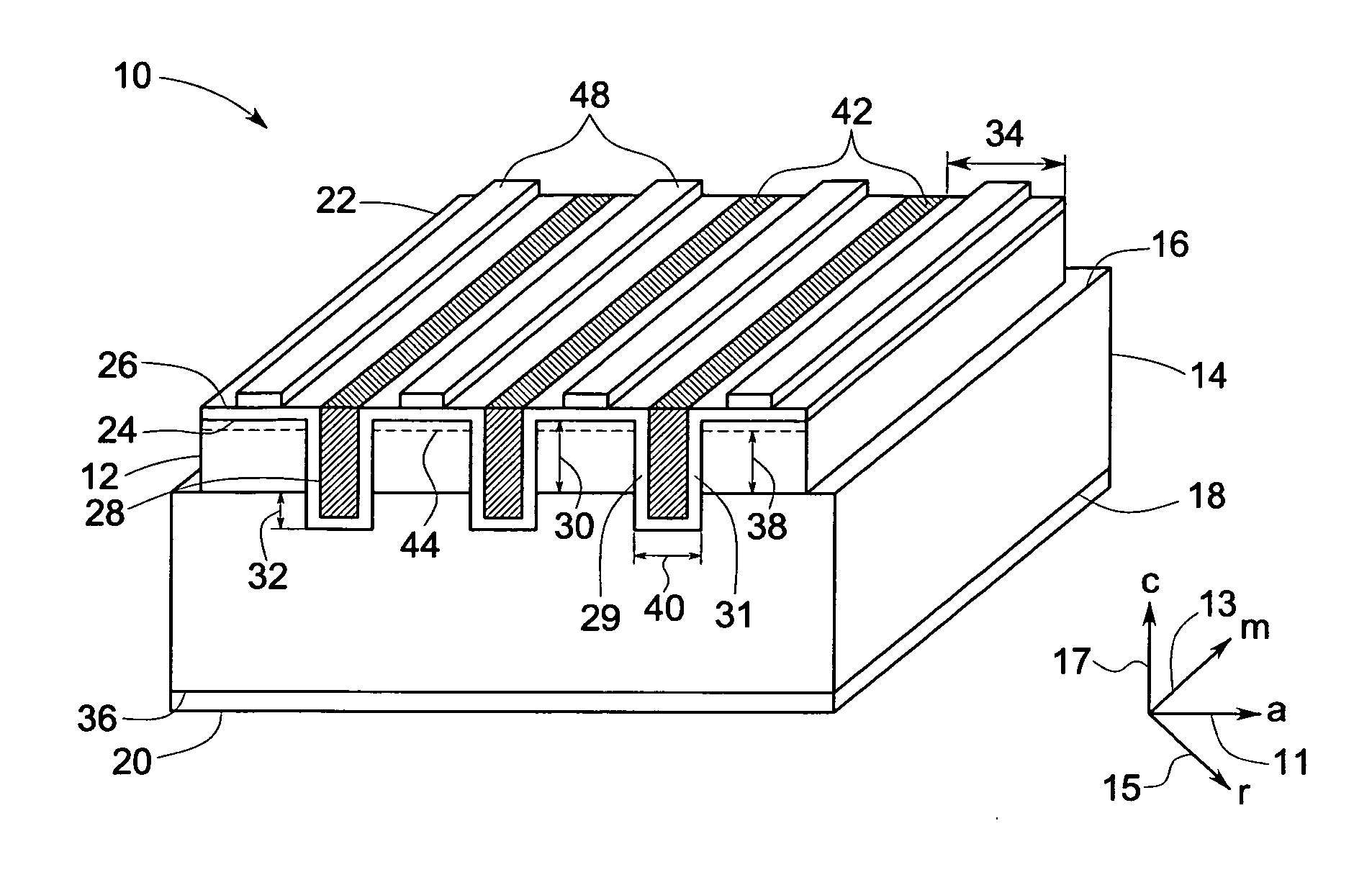

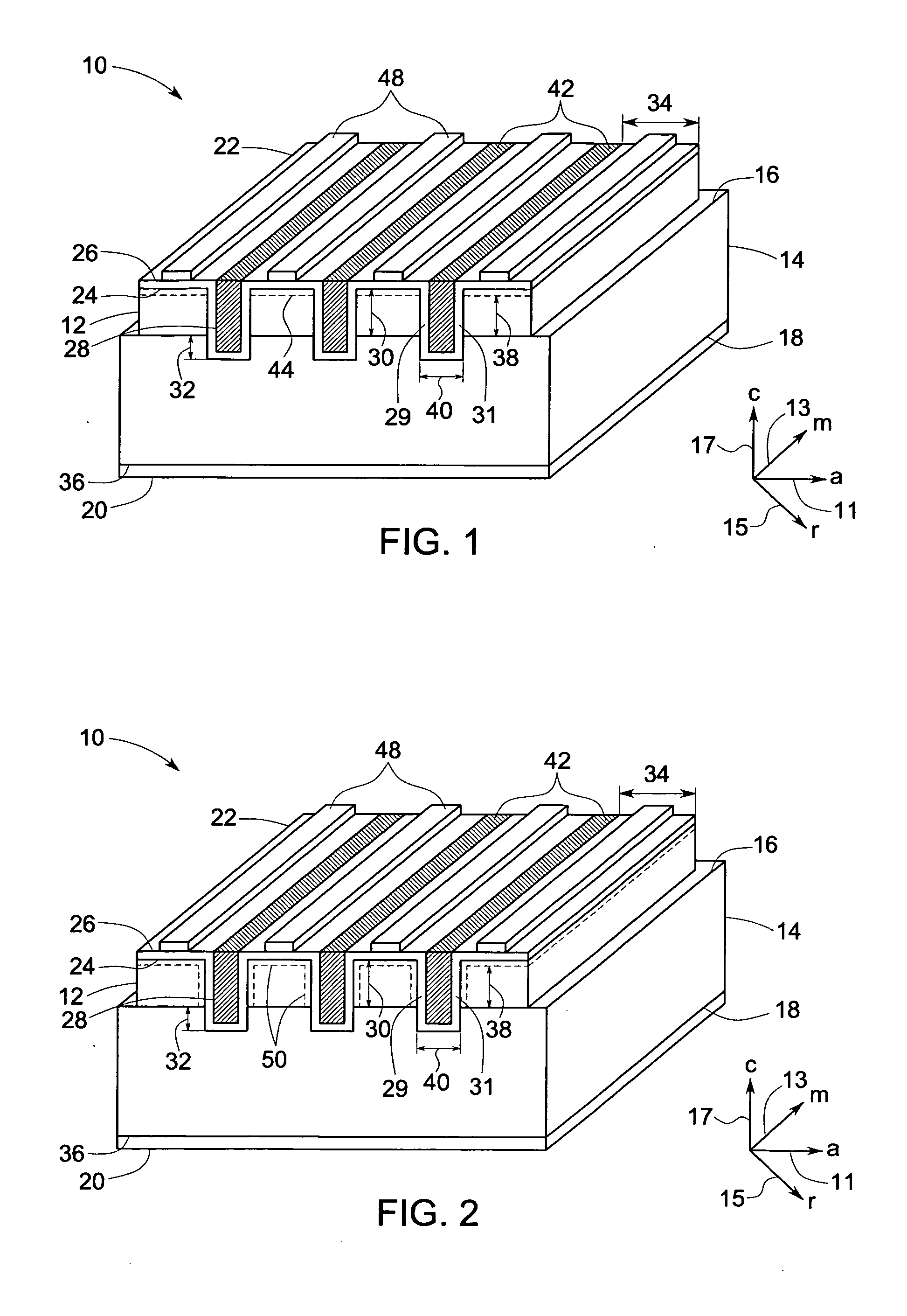

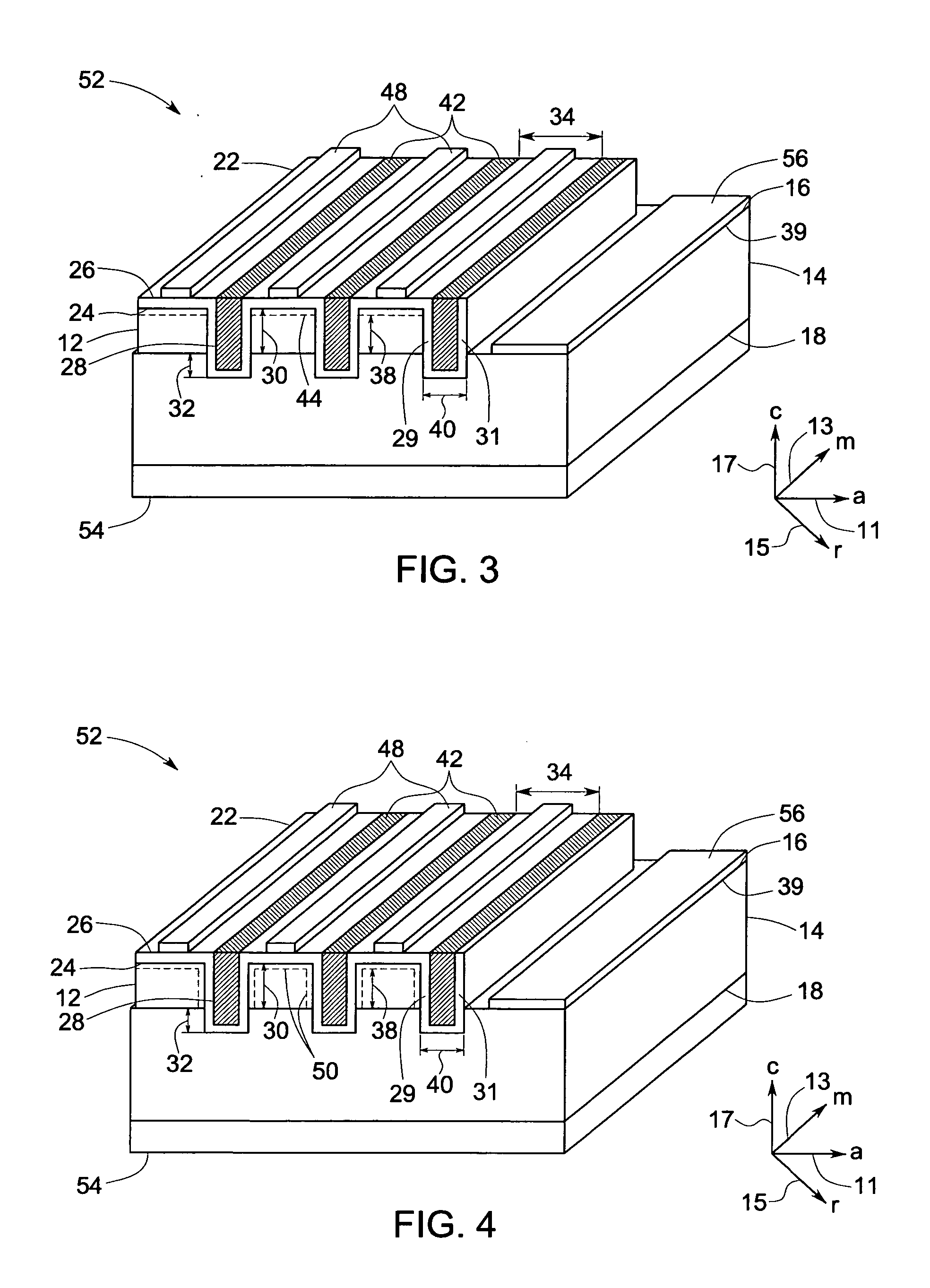

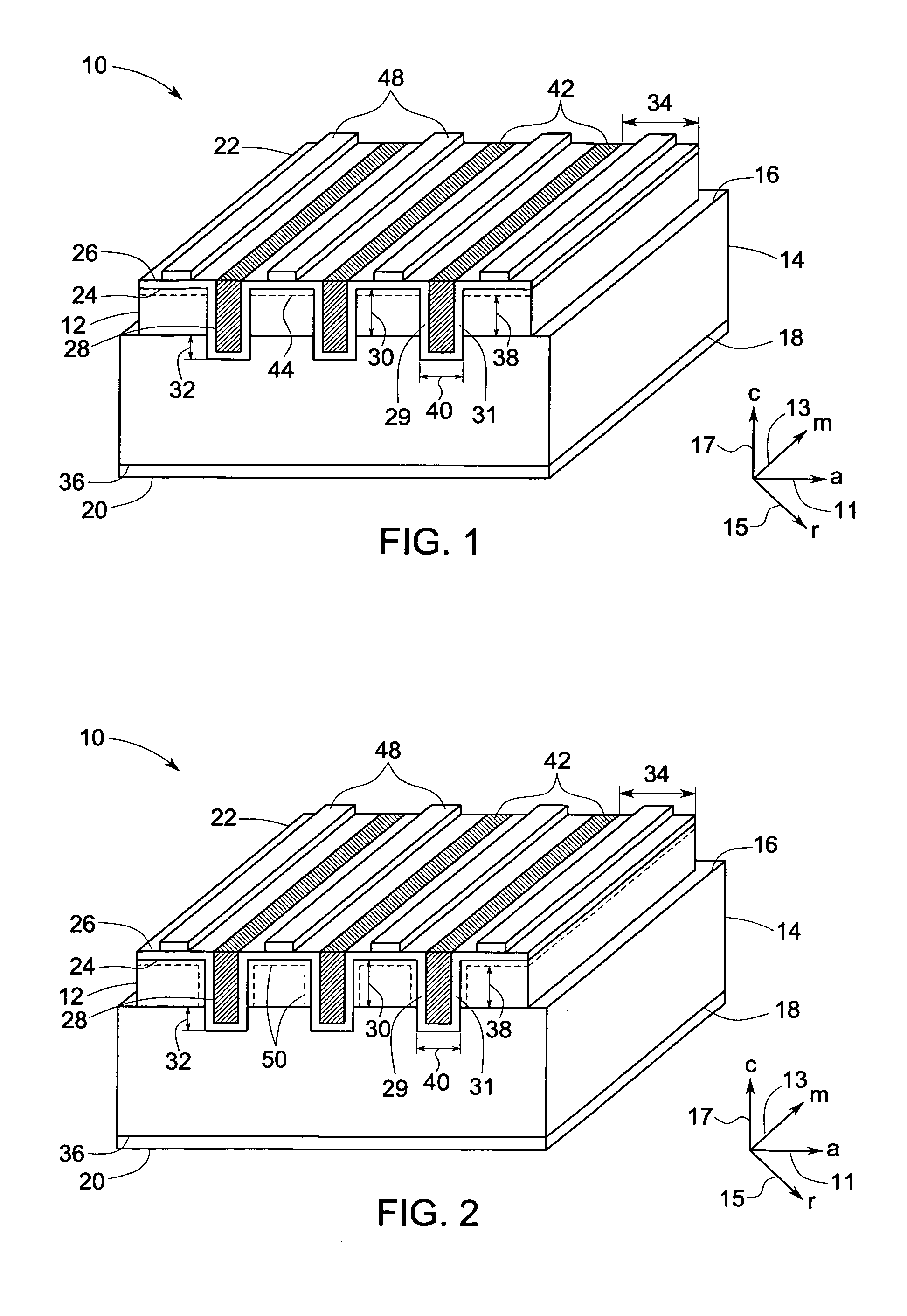

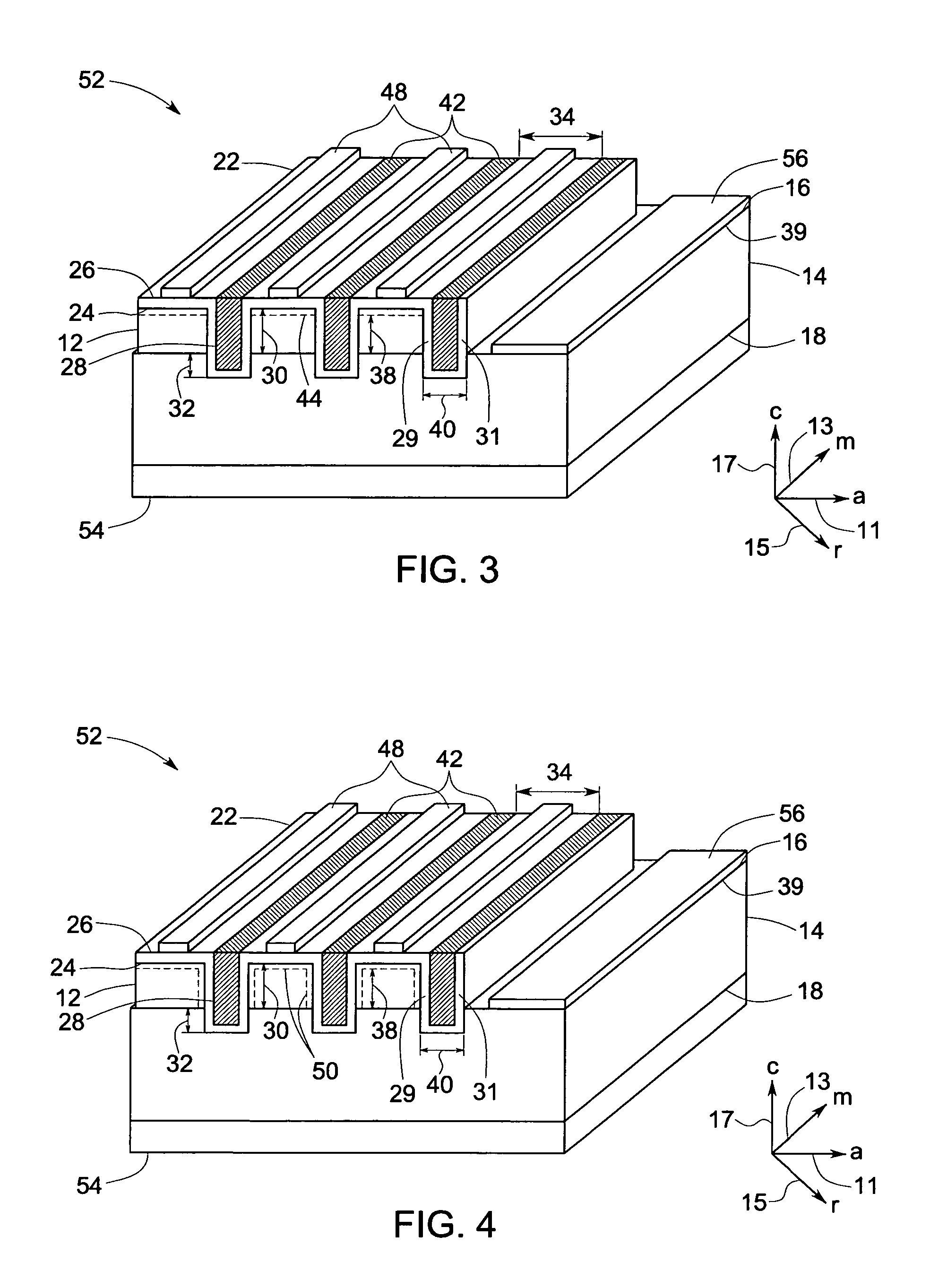

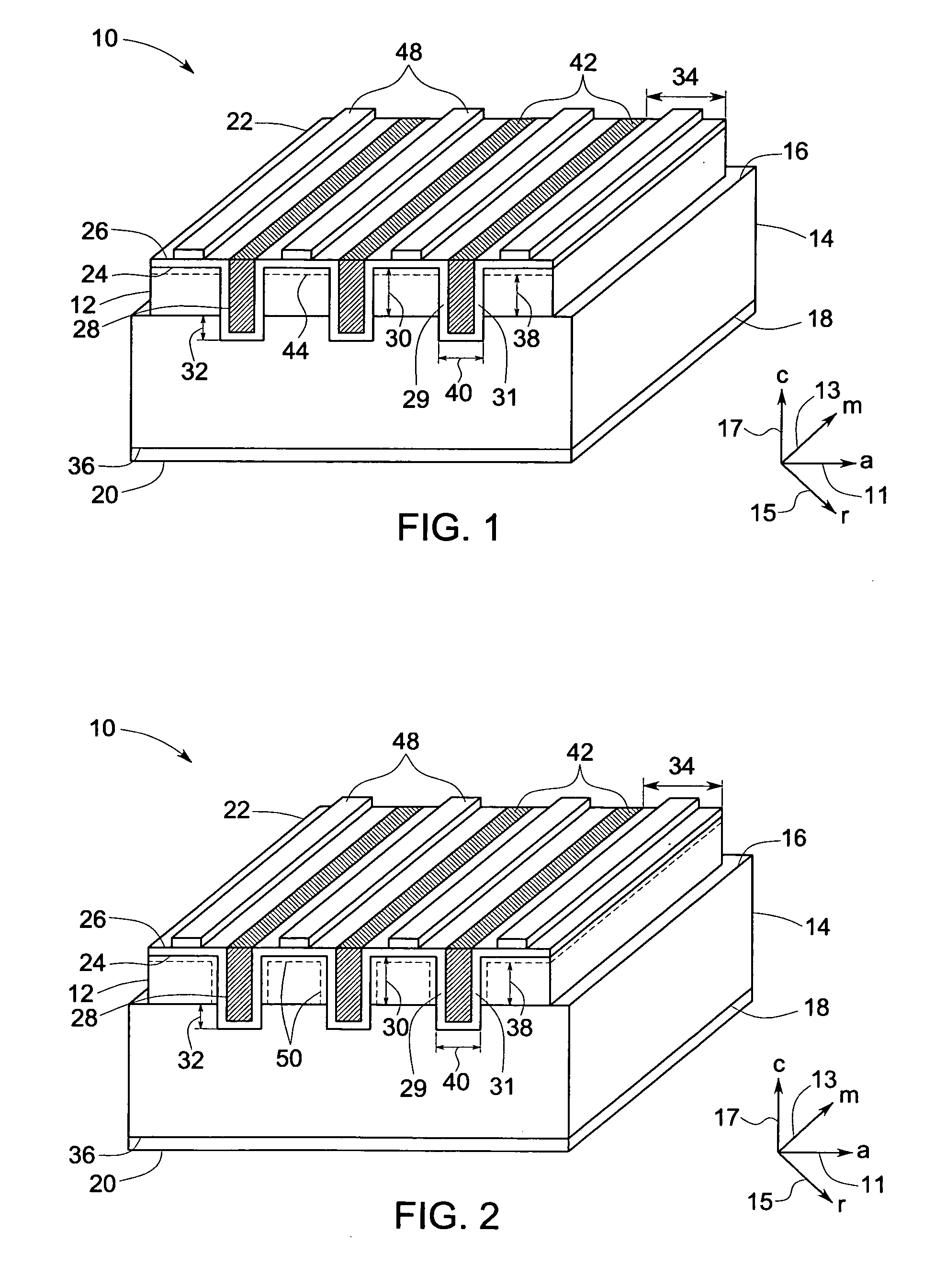

Vertical heterostructure field effect transistor and associated method

A vertical heterostructure field effect transistor including a first layer having a first material, and the first material having a hexagonal crystal lattice structure defining a first bandgap and one or more non-polar planes is provided. The transistor further includes a second layer that is adjacent to the first layer having a second material. Further, the second layer has a first surface and a second surface, and a portion of the second layer first surface is coupled to the surface of the first layer to form a two dimensional charge gas and to define a first region. The second material may have a second bandgap that is different than the first bandgap. Furthermore, the transistor may include a conductive layer that is disposed in the trench and is interposed between the first region and a second region that is not in electrical communication with the first region if no electrical potential is applied to the conductive layer, and an electrical potential applied to the conductive layer allows electrical communication from the first region to the second region.

Owner:GENERAL ELECTRIC CO

Normally off gallium nitride field effect transistors (FET)

ActiveUS20110103148A1The process is simple and convenientImproved device configurationTransistorRead-only memoriesElectrical conductorInsulation layer

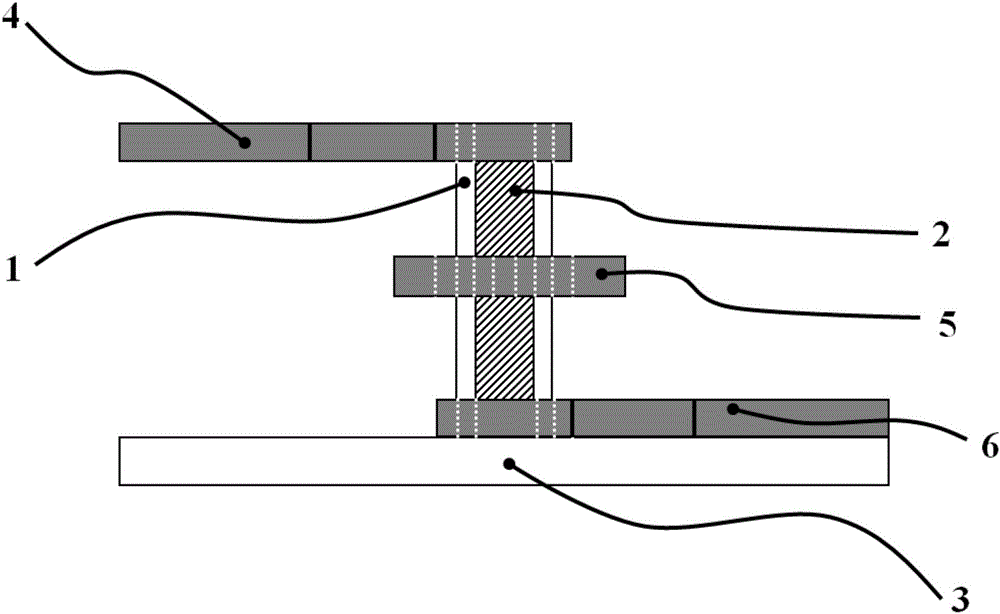

A heterostructure field effect transistor (HFET) gallium nitride (GaN) semiconductor power device comprises a hetero-junction structure comprises a first semiconductor layer interfacing a second semiconductor layer of two different band gaps thus generating an interface layer as a two-dimensional electron gas (2DEG) layer. The power device further comprises a source electrode and a drain electrode disposed on two opposite sides of a gate electrode disposed on top of the hetero-junction structure for controlling a current flow between the source and drain electrodes in the 2DEG layer. The power device further includes a floating gate located between the gate electrode and hetero-junction structure, wherein the gate electrode is insulated from the floating gate with an insulation layer and wherein the floating gate is disposed above and padded with a thin insulation layer from the hetero-junction structure and wherein the floating gate is charged for continuously applying a voltage to the 2DEG layer to pinch off the current flowing in the 2DEG layer between the source and drain electrodes whereby the HFET semiconductor power device is a normally off device.

Owner:ALPHA & OMEGA SEMICON INC

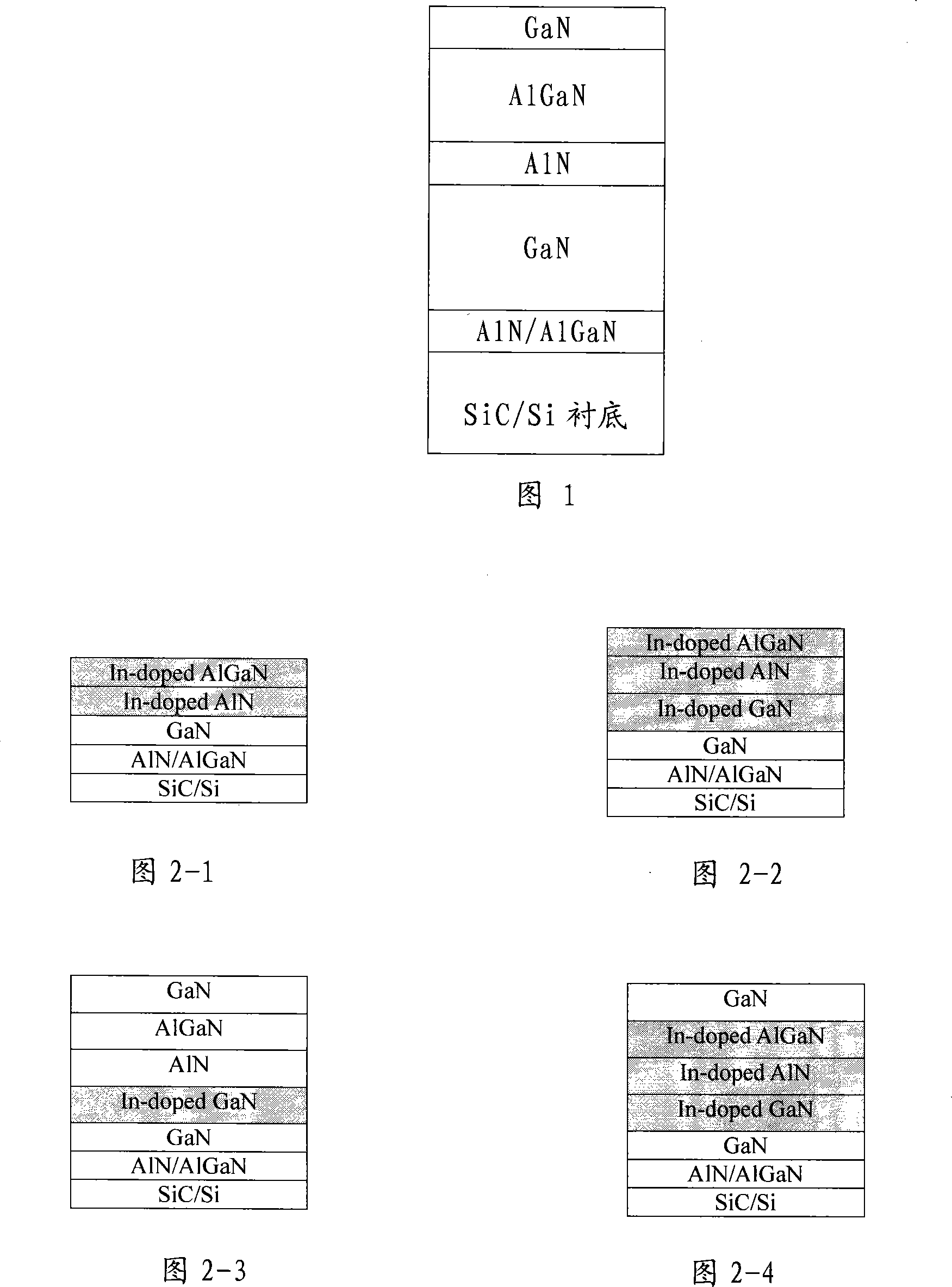

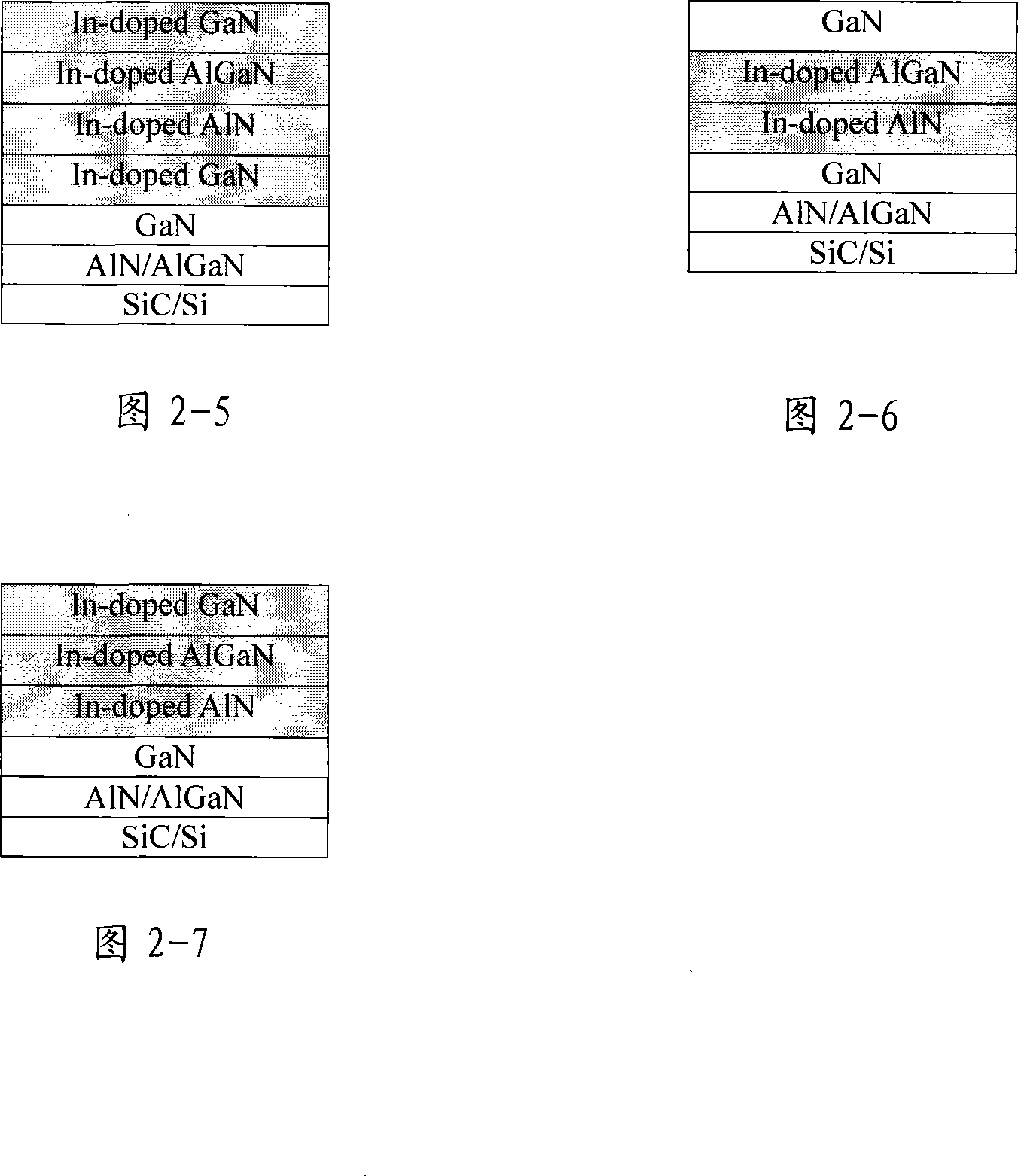

Method for improving gallium nitride based transistor material and device performance using indium doping

ActiveCN101114594AFree diffusionIncrease the diffusion distanceSemiconductor/solid-state device manufacturingGas phaseSingle crystal

The invention discloses a method of increasing the properties of the gallium nitride-based transistor material and device with indium doping and applies in the field of making gallium nitride-based HEMT or HFET materials and devices. The method and process is to form the gallium nitride-based high electron mobility transistor or heterostructure field effect transistor materials on SiC or Si single crystal substrate grown by metal-organic chemical vapor deposition epitaxial growth system. After the AlN or AlGaN nucleating layer and the GaN buffer layer are grown on the SiC or Si single crystal substrate, a GaN channel layer, an AlN insert layer, an AlGaN barrier layer and a GaN capped layer are grown, and trimethyl indium is added in the growth atmosphere to do epitaxial growth with indium doping. The dislocation of the material or device made by the method of the invention is reduced greatly. The invention improves the interfacial smoothness, increases the electron mobility of the material, increases the growth window, ensures the material grow easier, improves the current collapse of the device, reduces the leakage current and increases transconductance and gain and increases the output power of microwave power devices.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

Normally off gallium nitride field effect transistors (fet)

ActiveCN102074576ASolve problemsAddress limitationsTransistorSemiconductor/solid-state device manufacturingElectrical conductorInsulation layer

A heterostructure field effect transistor (HFET) gallium nitride (GaN) semiconductor power device comprises a hetero-junction structure comprises a first semiconductor layer interfacing a second semiconductor layer of two different band gaps thus generating an interface layer as a two-dimensional electron gas (2DEG) layer. The power device further comprises a source electrode and a drain electrode disposed on two opposite sides of a gate electrode disposed on top of the hetero-junction structure for controlling a current flow between the source and drain electrodes in the 2DEG layer. The power device further includes a floating gate located between the gate electrode and hetero-junction structure, wherein the gate electrode is insulated from the floating gate with an insulation layer and wherein the floating gate is disposed above and padded with a thin insulation layer from the hetero-junction structure and wherein the floating gate is charged for continuously applying a voltage to the 2DEG layer to pinch off the current flowing in the 2DEG layer between the source and drain electrodes whereby the HFET semiconductor power device is a normally off device.

Owner:ALPHA & OMEGA SEMICON INT LP

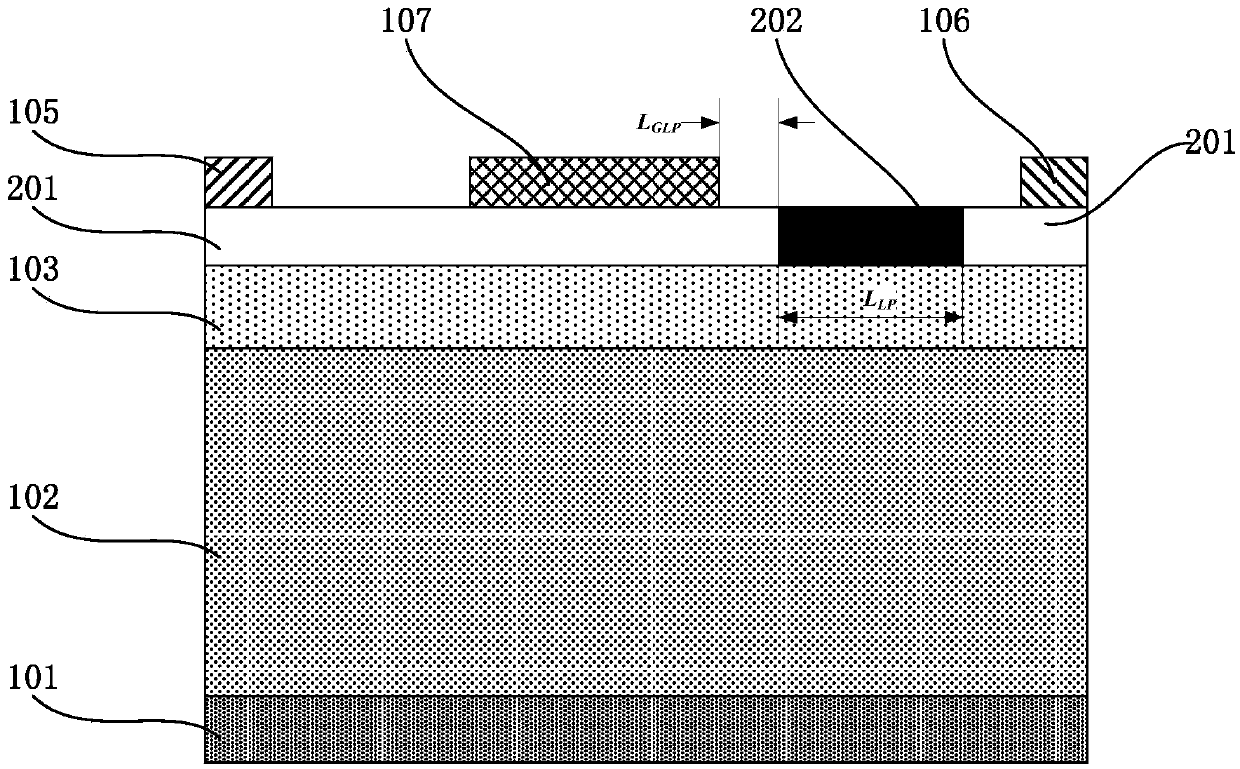

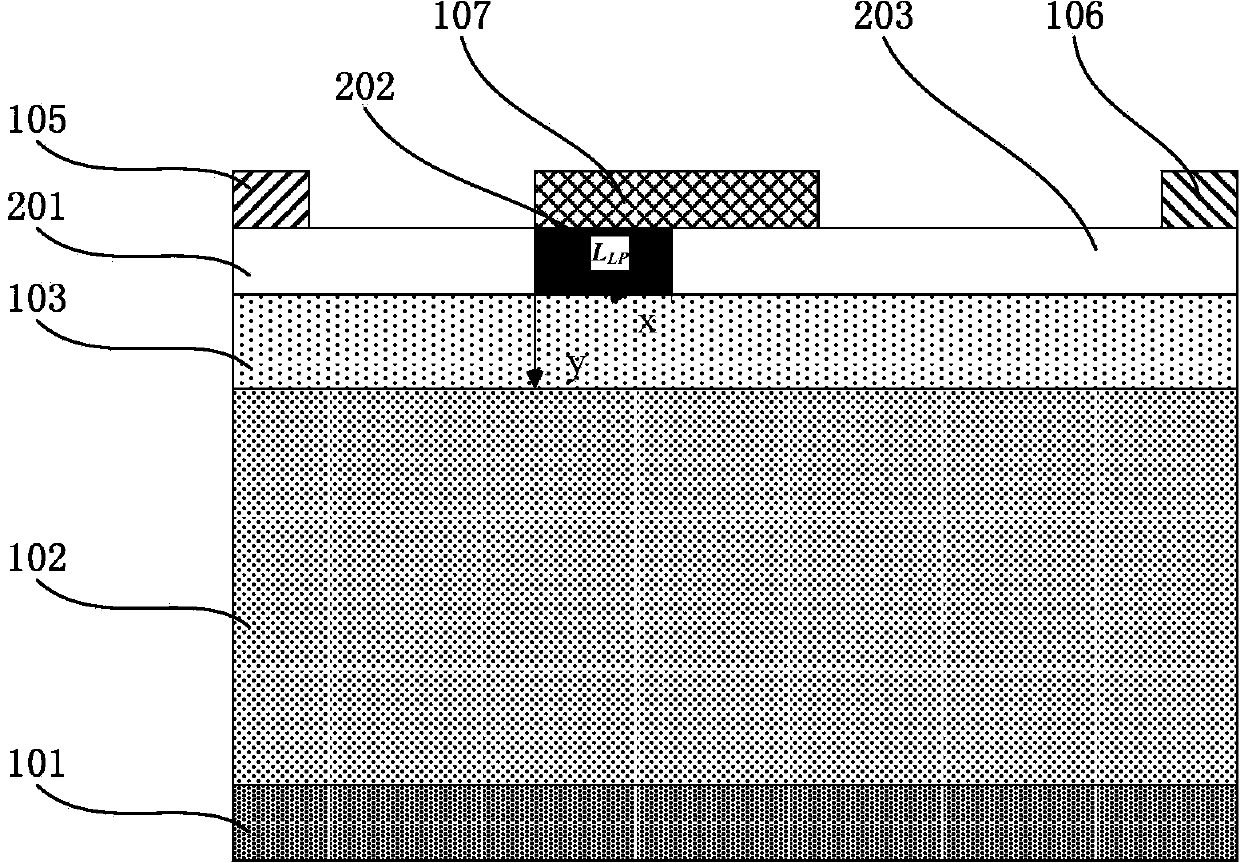

Gallium-nitride-based heterostructure field effect transistor with composite barrier layers

ActiveCN104201202ASuppression of short channel effectsImprove pressure resistanceSemiconductor devicesGallium nitrideDrift velocity

The invention discloses a gallium-nitride-based heterostructure field effect transistor with composite barrier layers. The composite barrier layers are formed by AlInGaN material with different polarization intensities. When the AlInGaN composite barrier layer with low polarization intensity is located at a grid drain terminal, the density of two-dimensional electron gas (2DEG) of the channel below the barrier layer is smaller than that of the 2DEG at other positions of the channel drain terminal, an LDD structure is formed, and the electric field distribution of the channel is modulated to increase voltage endurance capability; when the AlInGaN composite barrier layer with low polarization intensity is located right below a grid, a below-grid gallium nitride (GaN) channel guide strip bottom is distributed in a stepped manner, the drift speed of a below-grid channel carrier is increased due to barrier descending, electric field peak is generated between AlInGaN composite barrier layer with two different elemental components, and more potential is distributed at the grid drain terminal instead of the whole grid to restrain drain induced barrier lowering (DIBL).

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

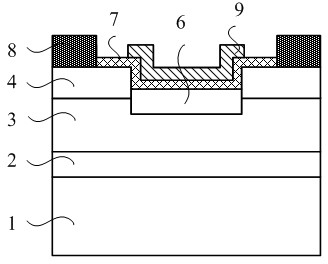

High-threshold voltage gallium nitride (GaN) enhancement metal oxide semiconductor heterostructure field effect transistor (MOSHFET) device and manufacturing method

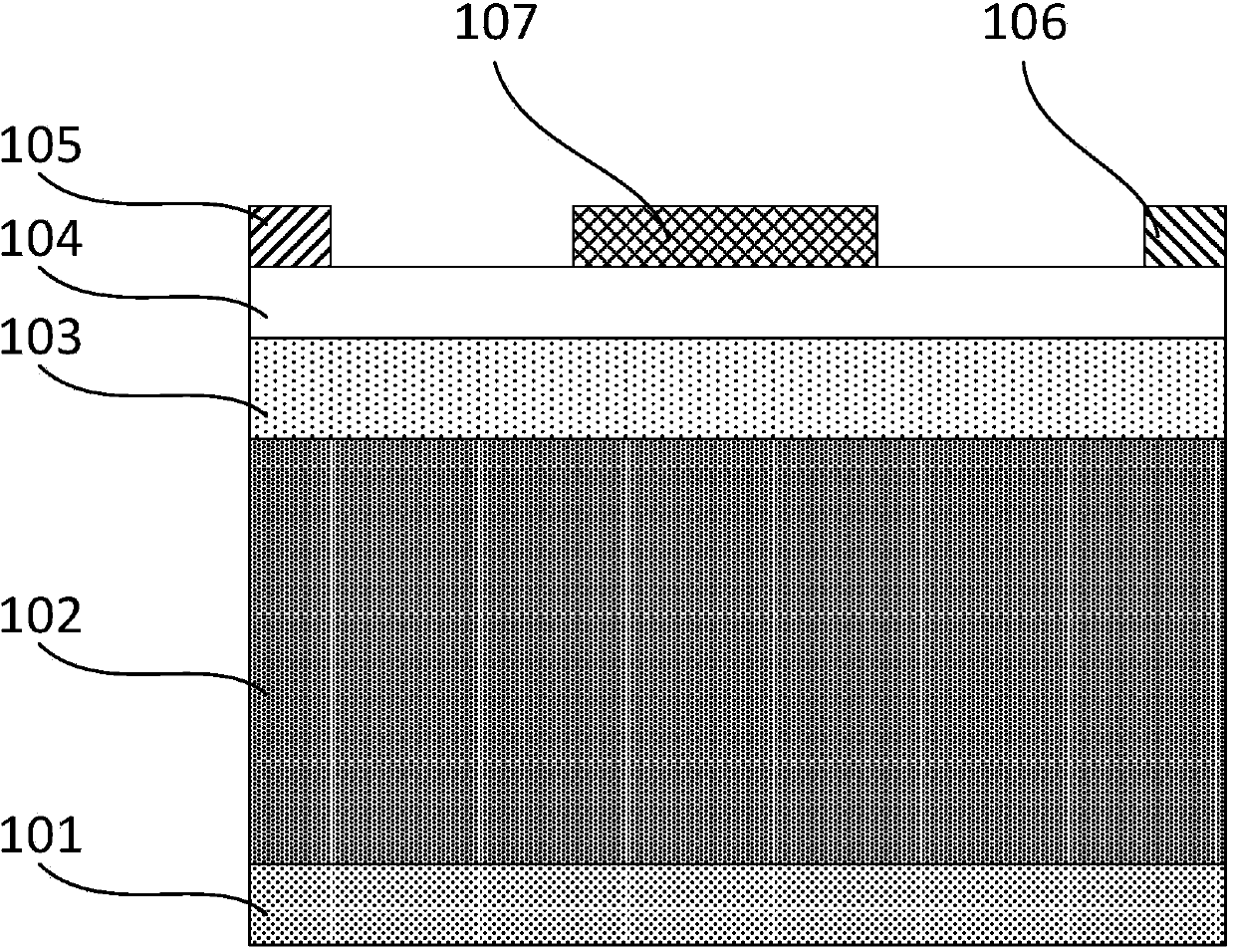

ActiveCN102386223ALower on-resistanceRaise the threshold voltageSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactGallium nitride

The invention discloses a high-threshold voltage gallium nitride (GaN) enhancement metal oxide semiconductor heterostructure field effect transistor (MOSHFET) device and a manufacturing method. The device comprises a substrate (1) and an epitaxial layer grown on the substrate (1), and is characterized in that: the epitaxial layer comprises a stress buffer layer (2), a GaN layer (3) and a heterostructure barrier layer (4) sequentially upwards from the bottom; the heterostructure barrier layer (4) is etched to the GaN layer (4) to form a groove in a gate region; a p-type GaN layer (6) is selectively grown on the groove; an insulated dielectric layer (7) is deposited on the surfaces of the p-type GaN layer (6) and the heterostructure barrier layer (4) and etched in source and drain regions on the surface of the heterostructure barrier layer (4); a gate metal (9) is evaporated in the gate region; and an ohmic contact metal (8) is evaporated on the source and drain regions. The device provided by the invention has a simple structure, is simple in manufacturing process and high in stability, and can effectively increase a forward threshold voltage and simultaneously repair crystal lattices damaged by plasma treatment.

Owner:SUN YAT SEN UNIV

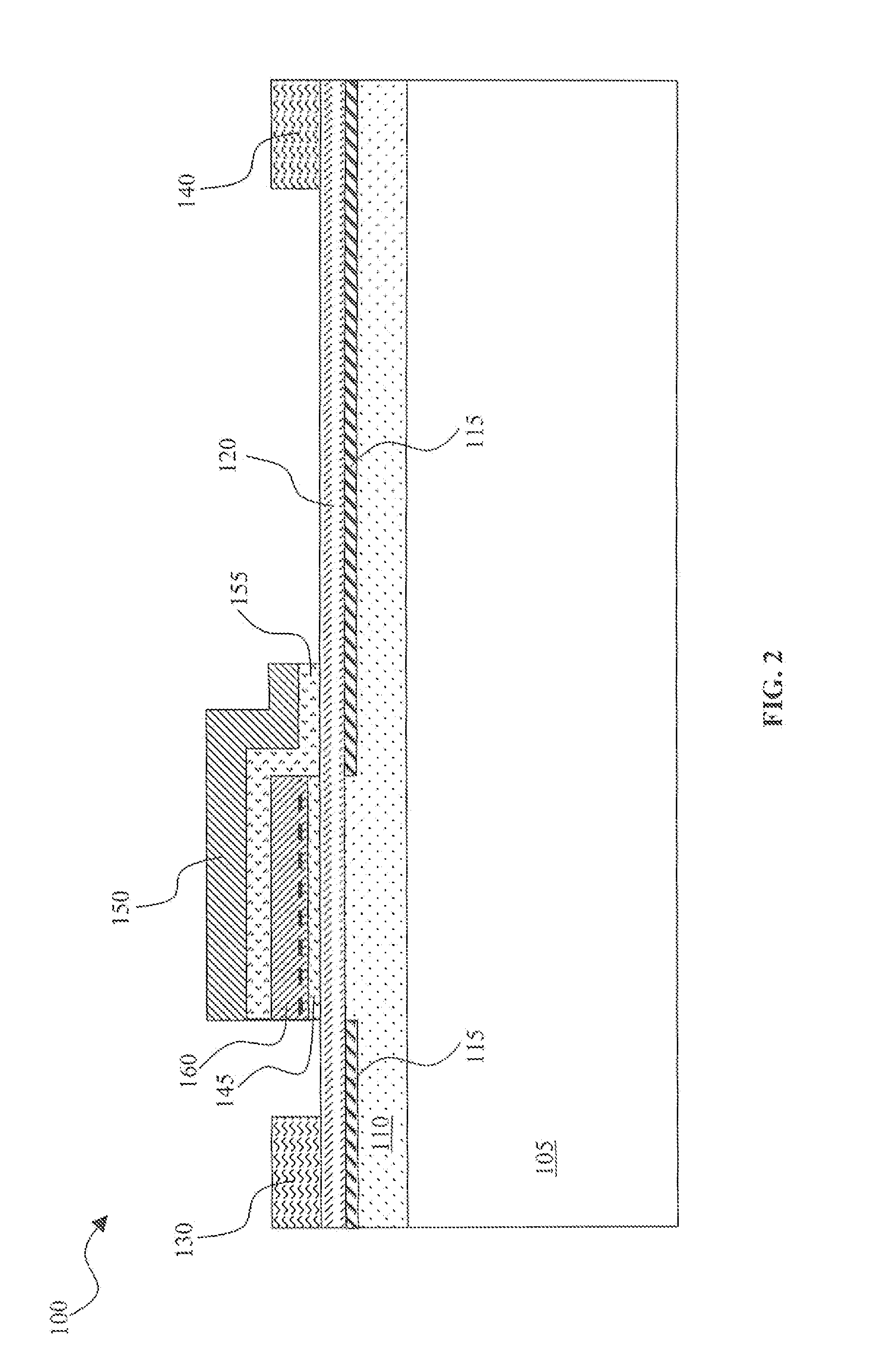

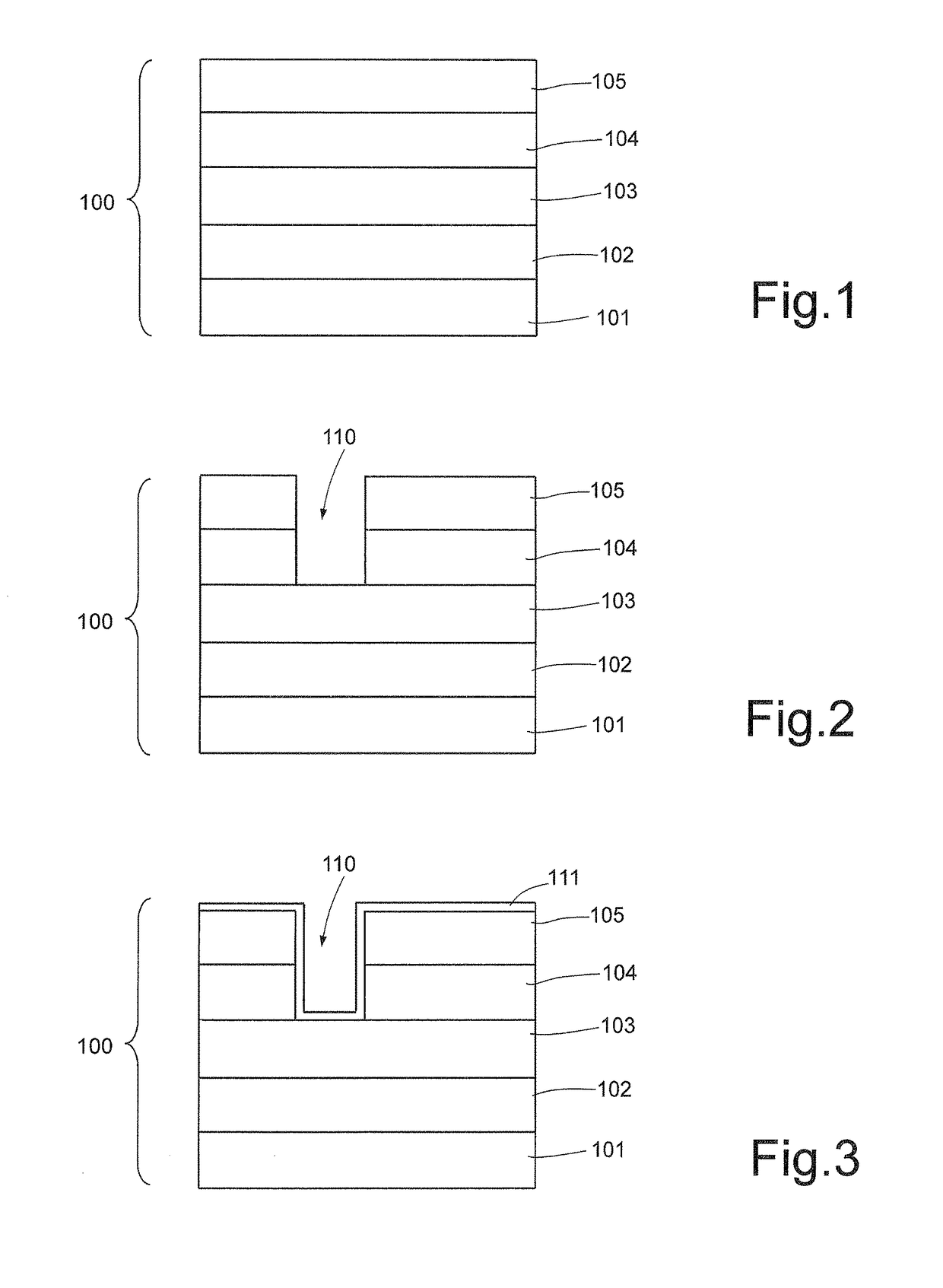

Gallium nitride based semiconductor devices and methods of manufacturing the same

ActiveUS20120061680A1Improve cooling effectImprove operating characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialWafer bonding

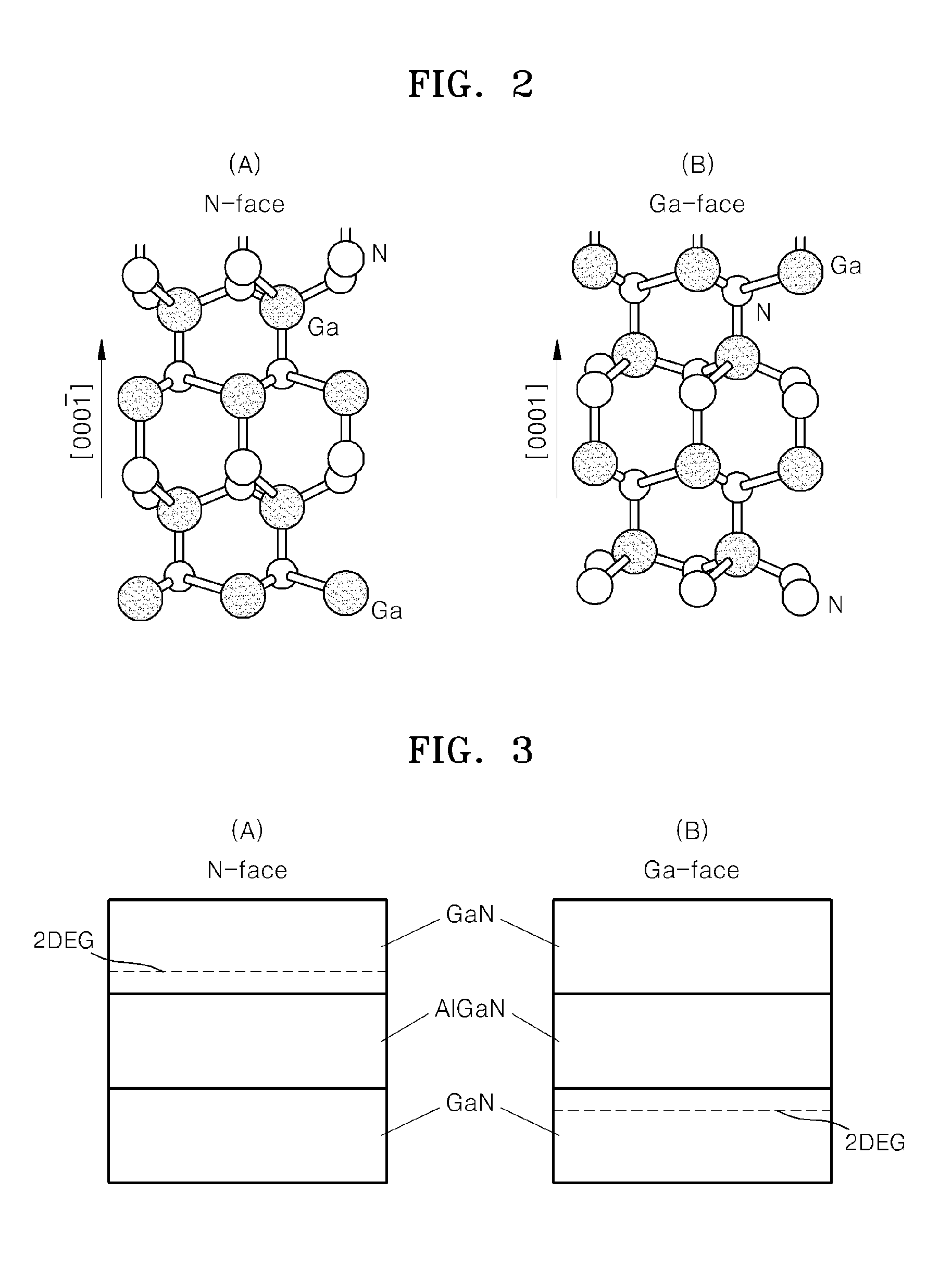

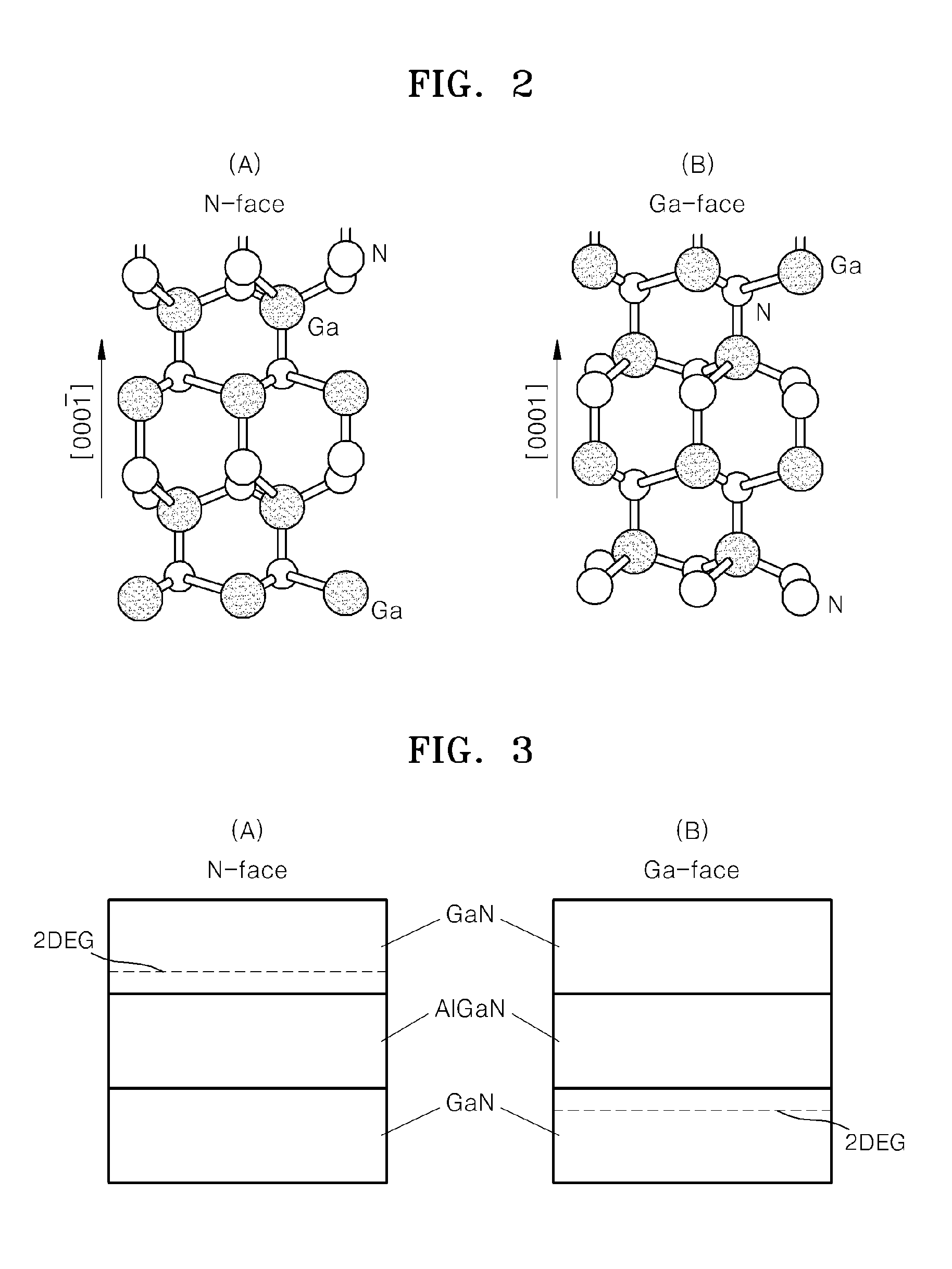

Gallium nitride (GaN) based semiconductor devices and methods of manufacturing the same. The GaN-based semiconductor device may include a heat dissipation substrate (that is, a thermal conductive substrate); a GaN-based multi-layer arranged on the heat dissipation substrate and having N-face polarity; and a heterostructure field effect transistor (HFET) or a Schottky electrode arranged on the GaN-based multi-layer. The HFET device may include a gate having a double recess structure. While such a GaN-based semiconductor device is being manufactured, a wafer bonding process and a laser lift-off process may be used.

Owner:SAMSUNG ELECTRONICS CO LTD

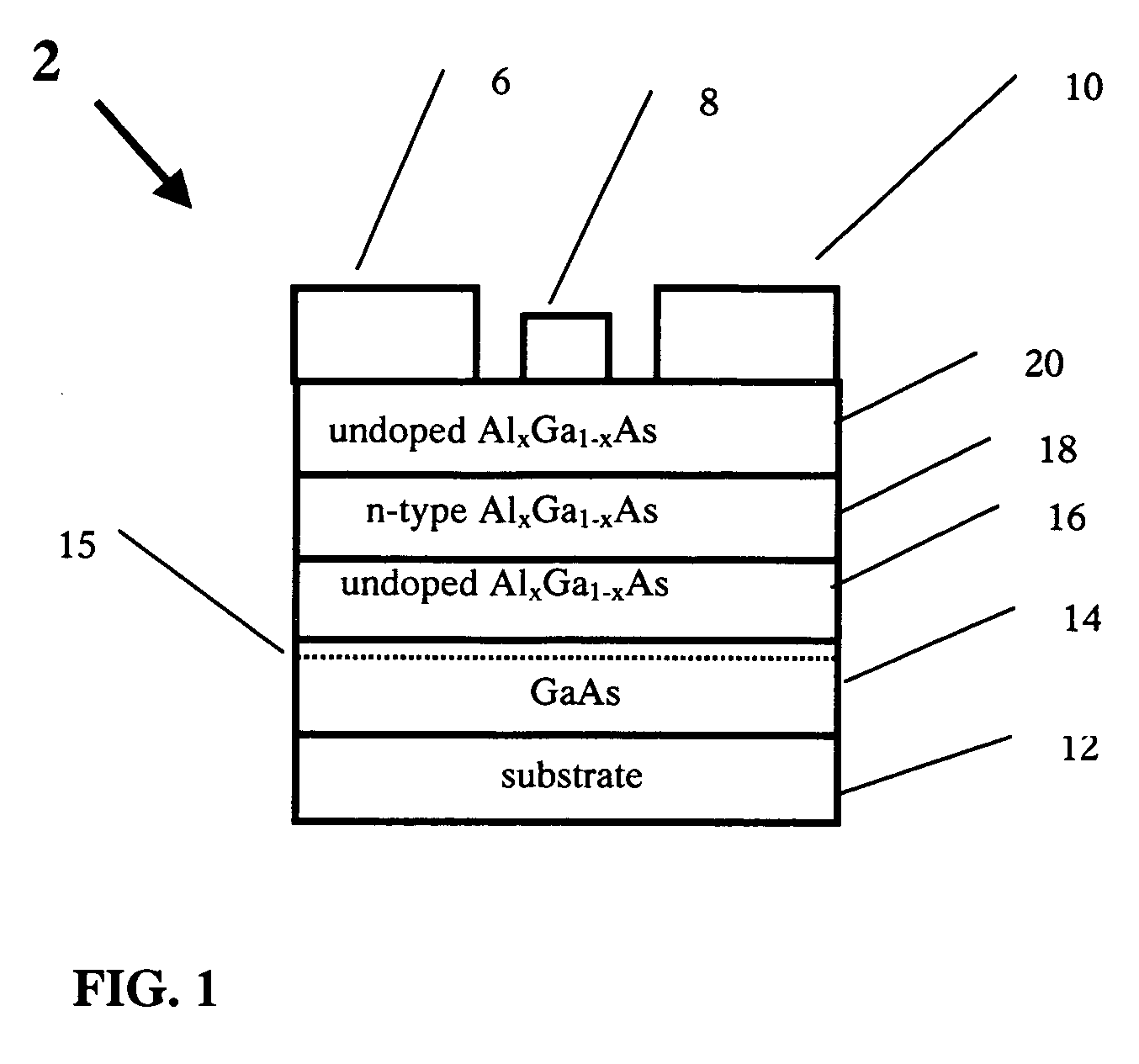

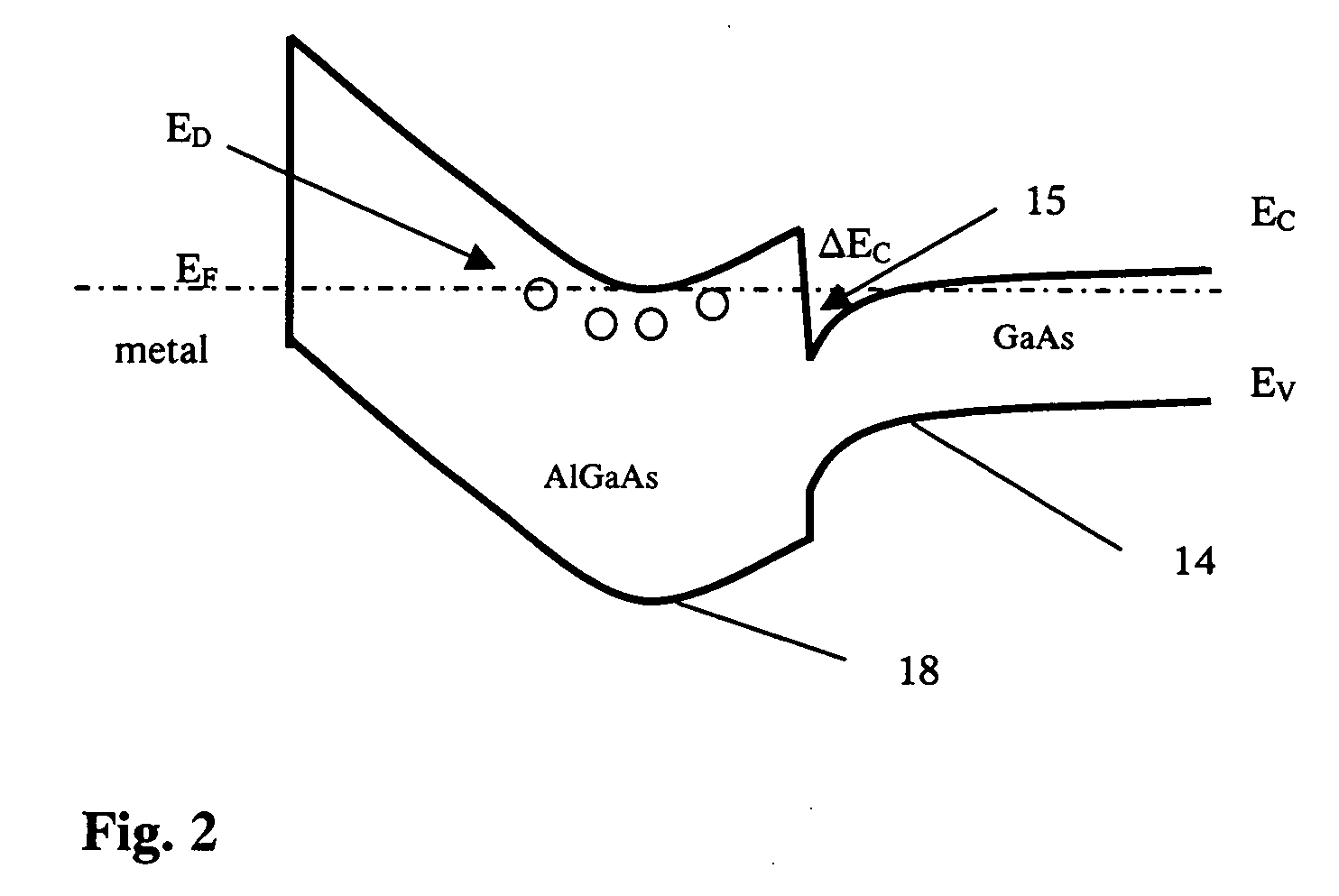

Multiple-function GaAs transistors with very strong negative differential resistance phenomena

Disclosed in this invention is a new four-terminal type and multiple delta-doped transistors with multiple functions grown by low-pressure metalorganic chemical vapor deposition (LP-MOCVD). All the epilayers are grown on n+-GaAs substrates. The real-space transfer transistors (RST), the collector is located under the substrate, reveal very strong negative differential resistance phenomena. The RST structure using an InGaAs channel manifests superior characteristics of a very high peak-to-valley current ratio up to 430,000 at room temperature, a peak current as high as 100 mA, very sharp charge injection, and a valley current as broad as 5.5V. Meanwhile, high performance heterostructure field effect transistors can be implemented on the same wafer by further evaporating a gate between source and drain electrodes. In order to significantly reduce leakage current, an ohmic recession is made at the source and drain. These new multiple-functions device may be used in high-speed, low-noise, and / or high power microwave oscillators and amplifiers.

Owner:NAT SCI COUNCIL

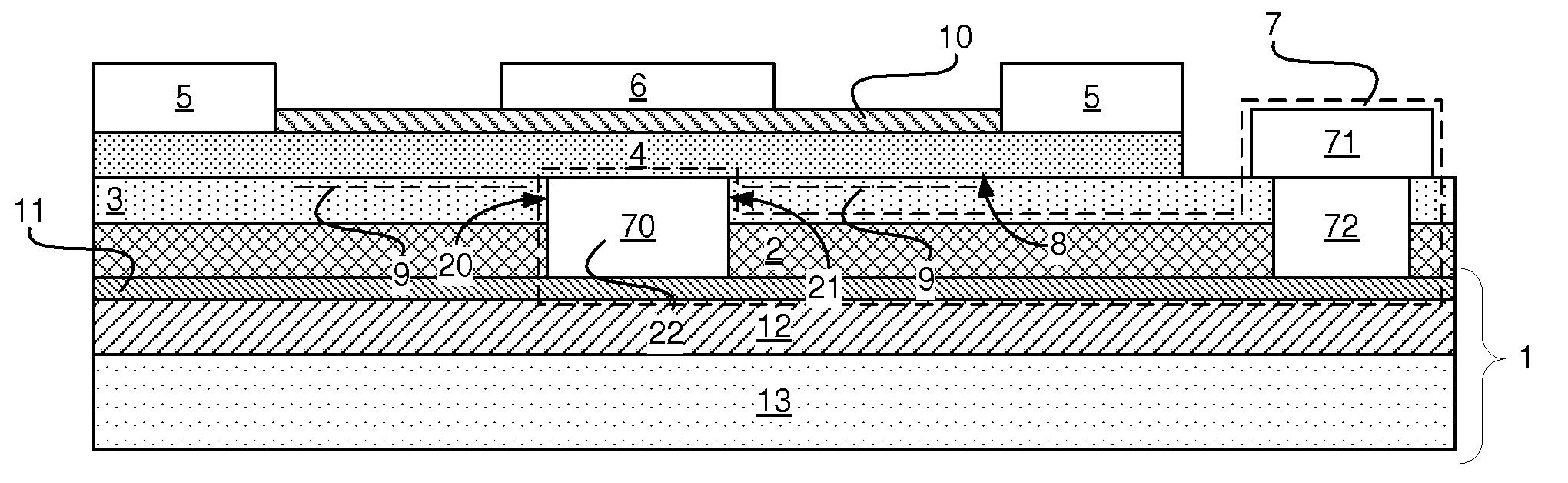

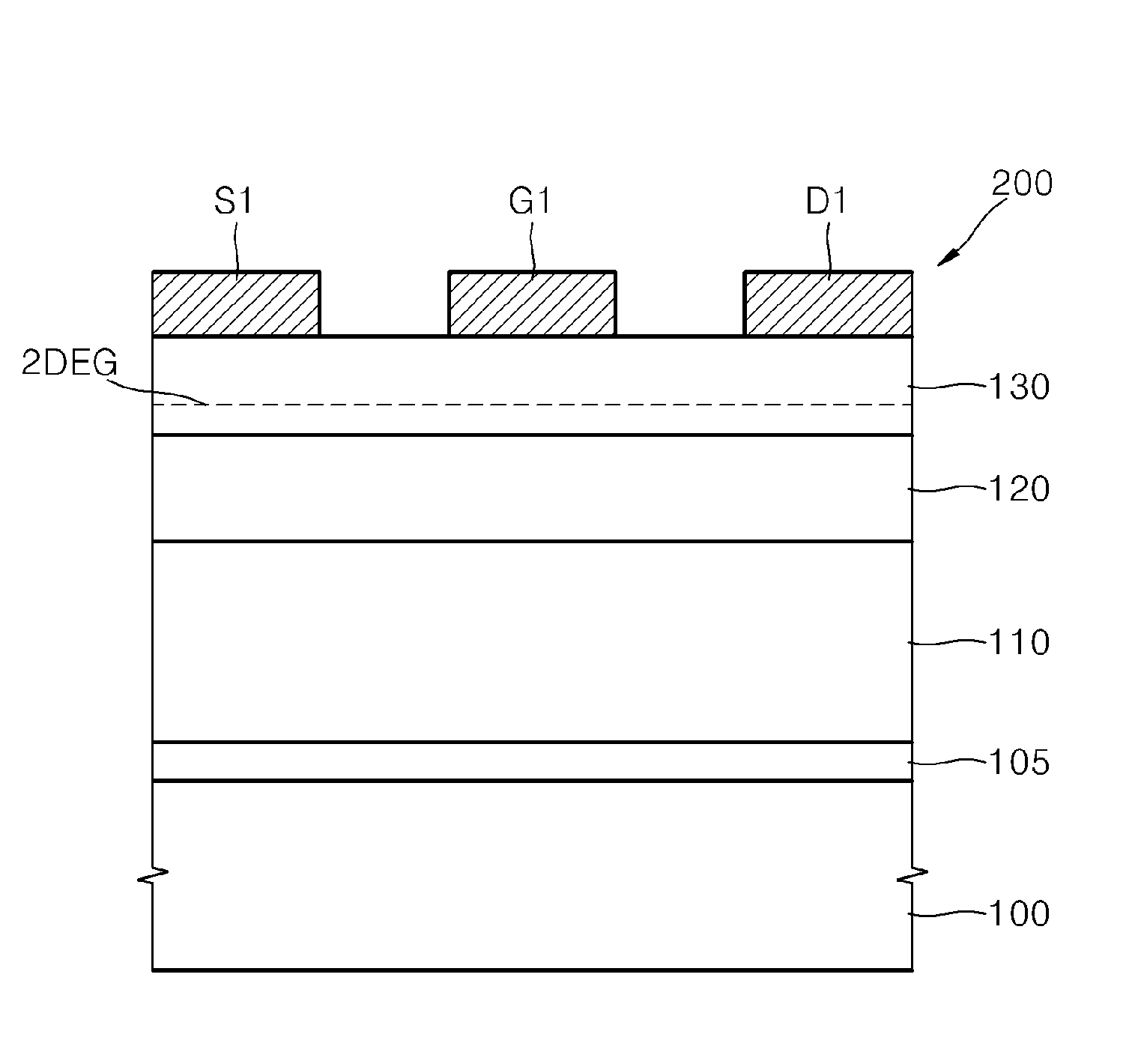

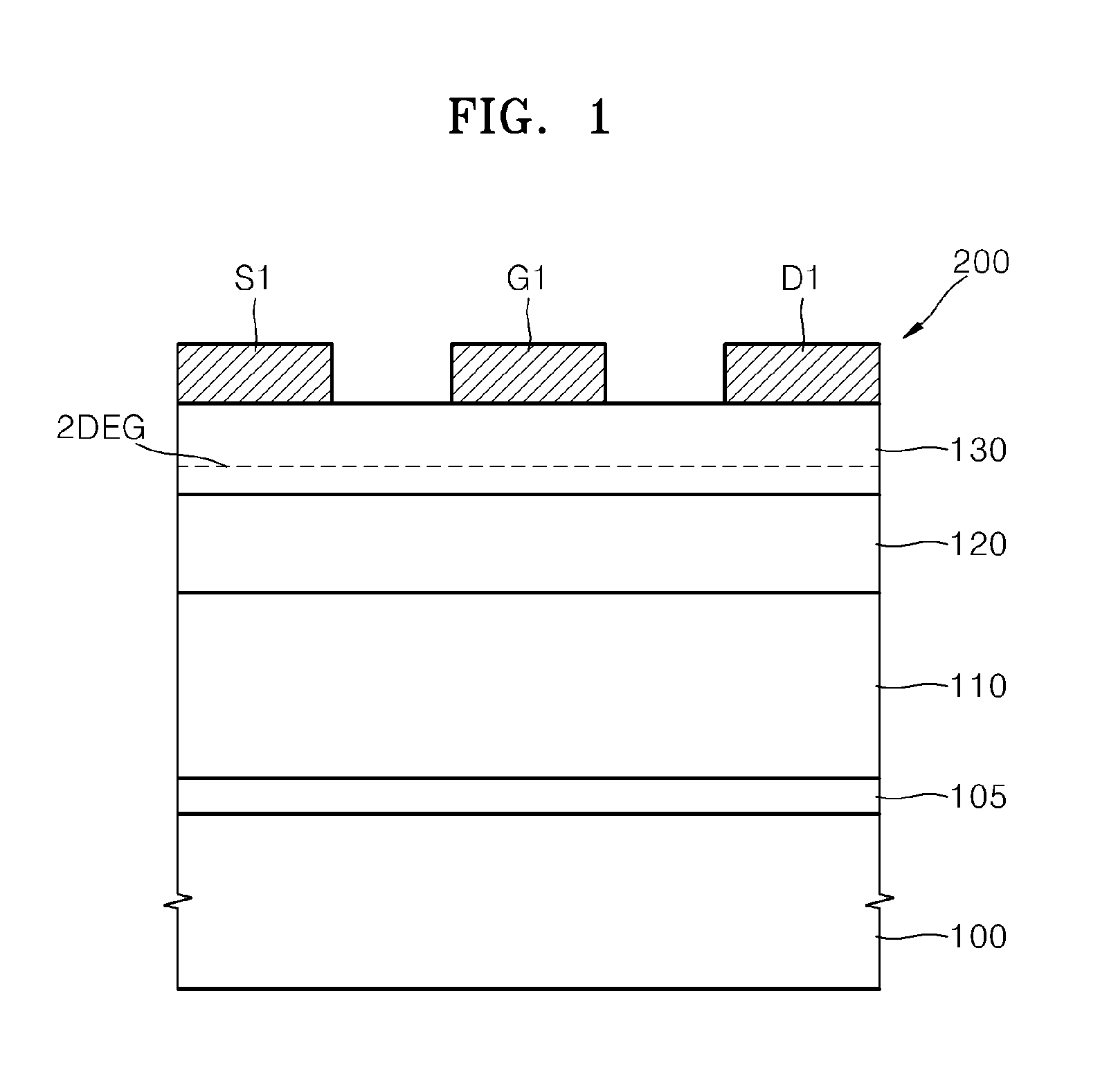

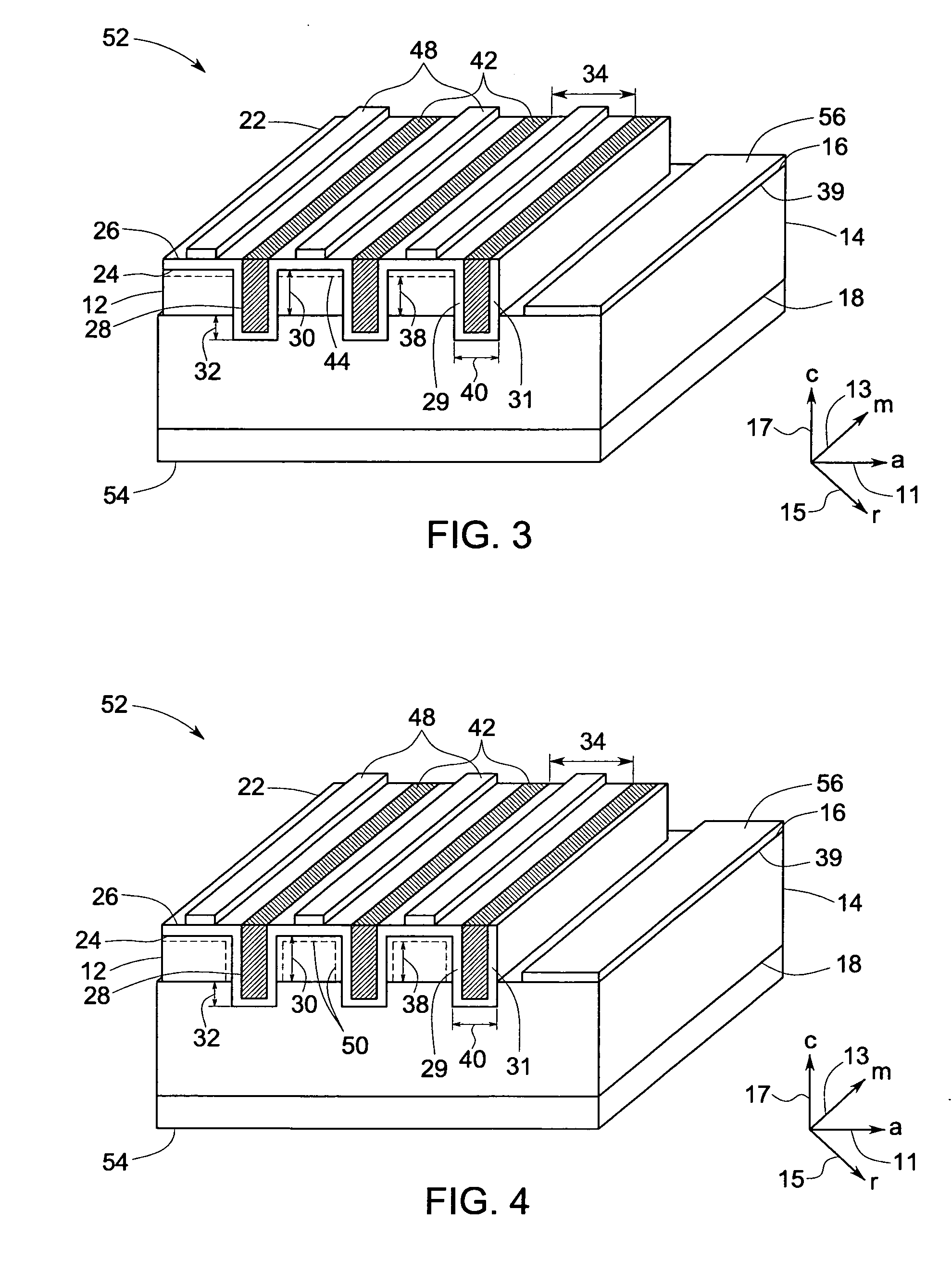

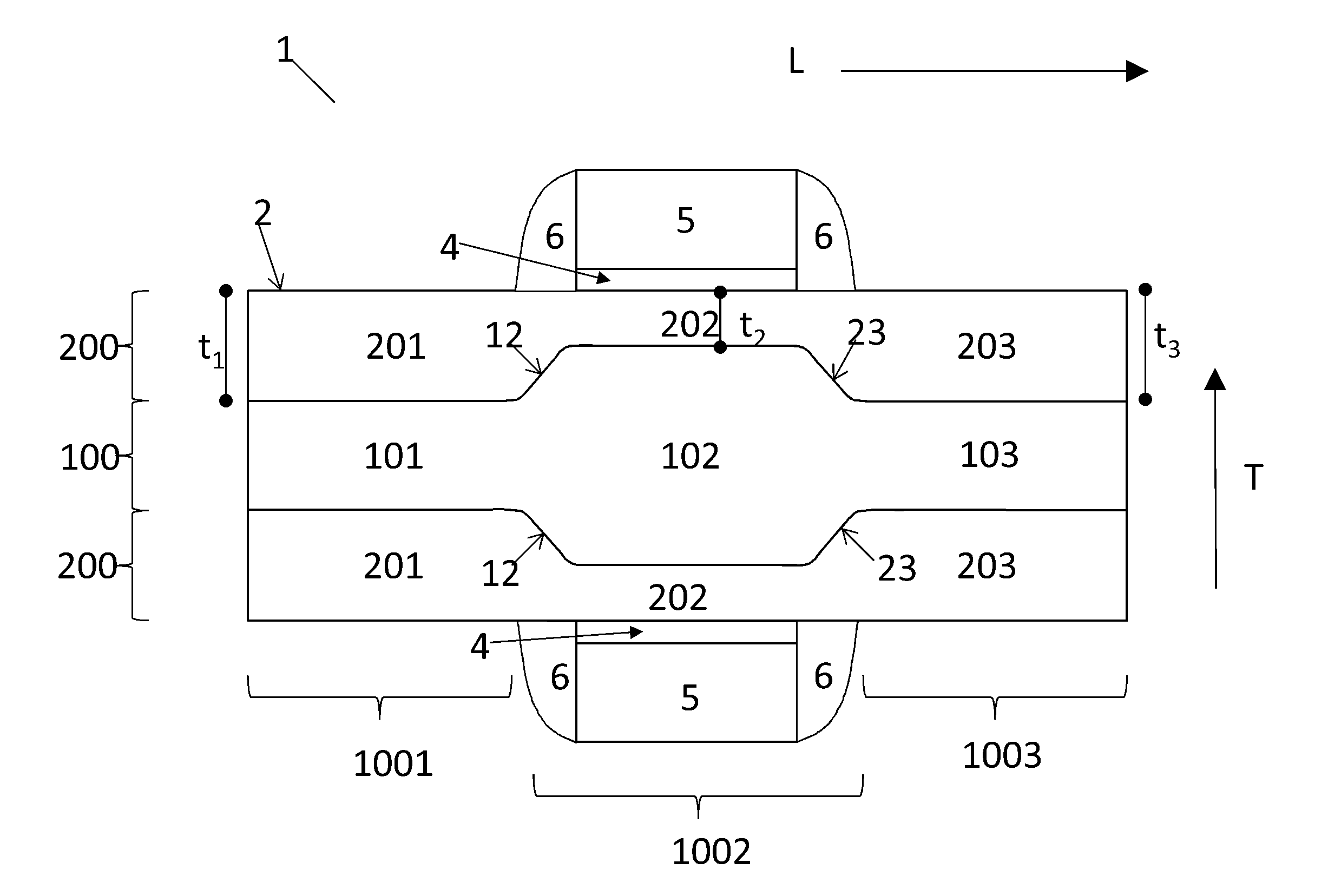

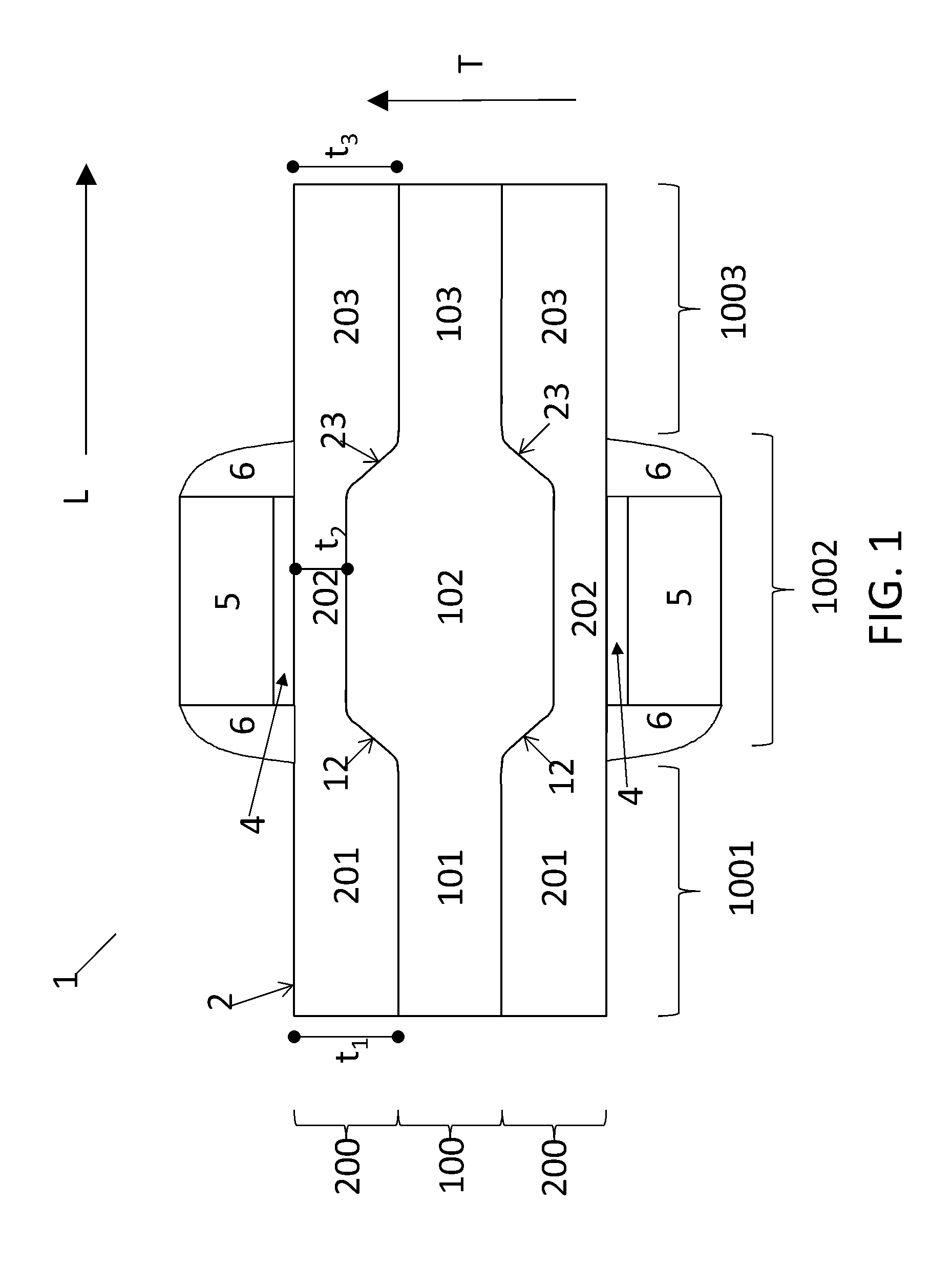

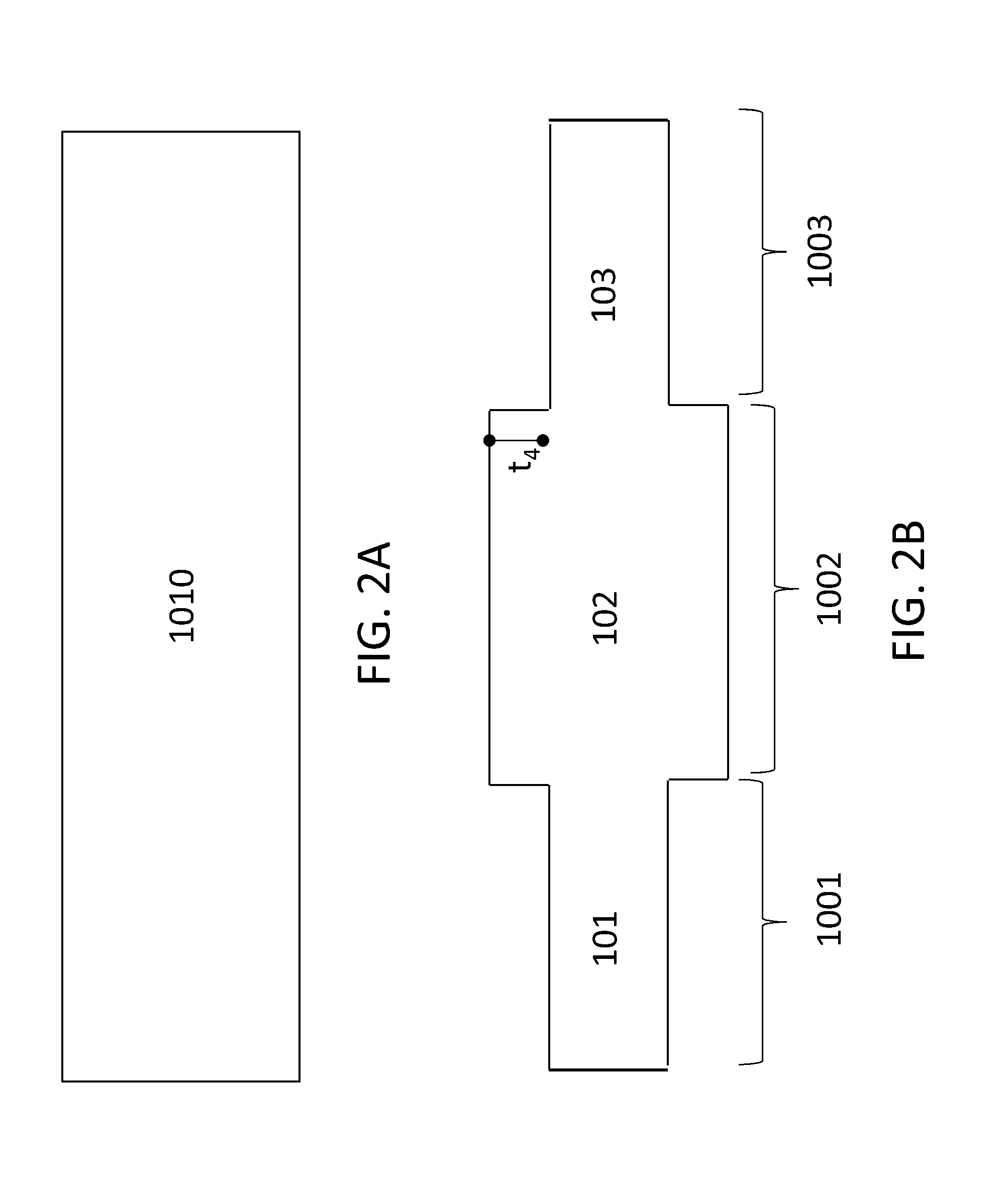

Hetero-structure field effect transistor, integrated circuit including a hetero-structure field effect transistor and method for manufacturing a hetero-structure field effect transistor

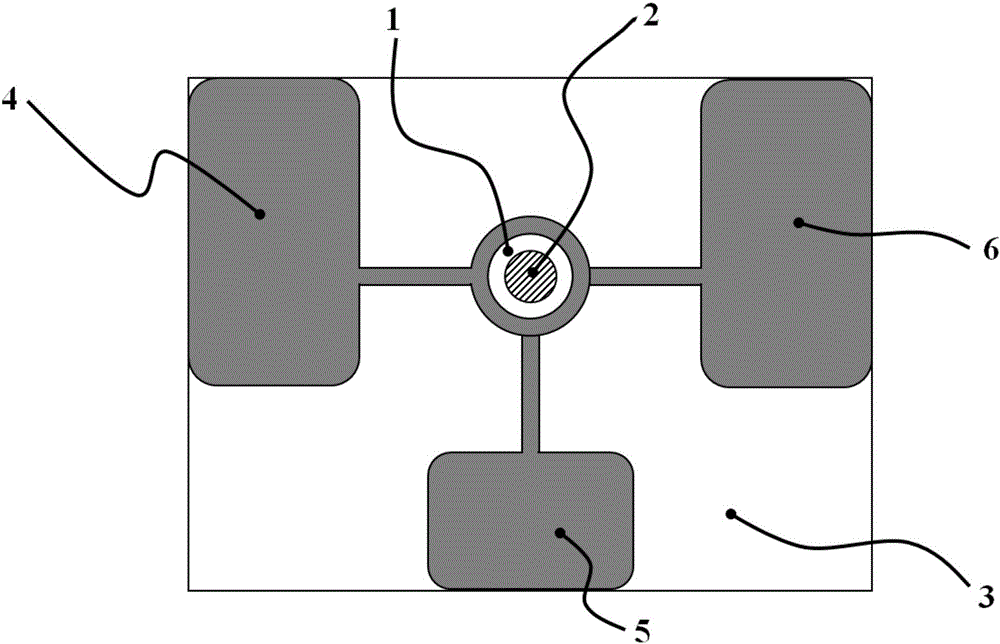

ActiveUS20100187569A1TransistorSemiconductor/solid-state device manufacturingSemiconductor materialsElectrical connection

A hetero-structure field effect transistor (HFET). The HFET may include a first contact and a second contact and a hetero-junction structure. The hetero-junction structure may include a first layer made from a first semiconductor material and a second layer made from a second semiconductor material. An interface at which the first layer and the second layer are in contact with each other may be provided, along which a two dimensional electron gas (2DEG) is formed in a part of the first layer directly adjacent to the interface, for propagating of electrical signals from the first contact to the second contact or vice versa. The transistor may further include a gate structure for controlling a conductance of the channel; a substrate layer made from a substrate semiconductor material, and a dielectric layer separating the first layer from the substrate layer. The second contact may include an electrical connection between the substrate layer and the first layer. The electrical connection may include a passage through the dielectric layer filled with an electrically conducting material which is electrically connected to the first layer.

Owner:NXP USA INC

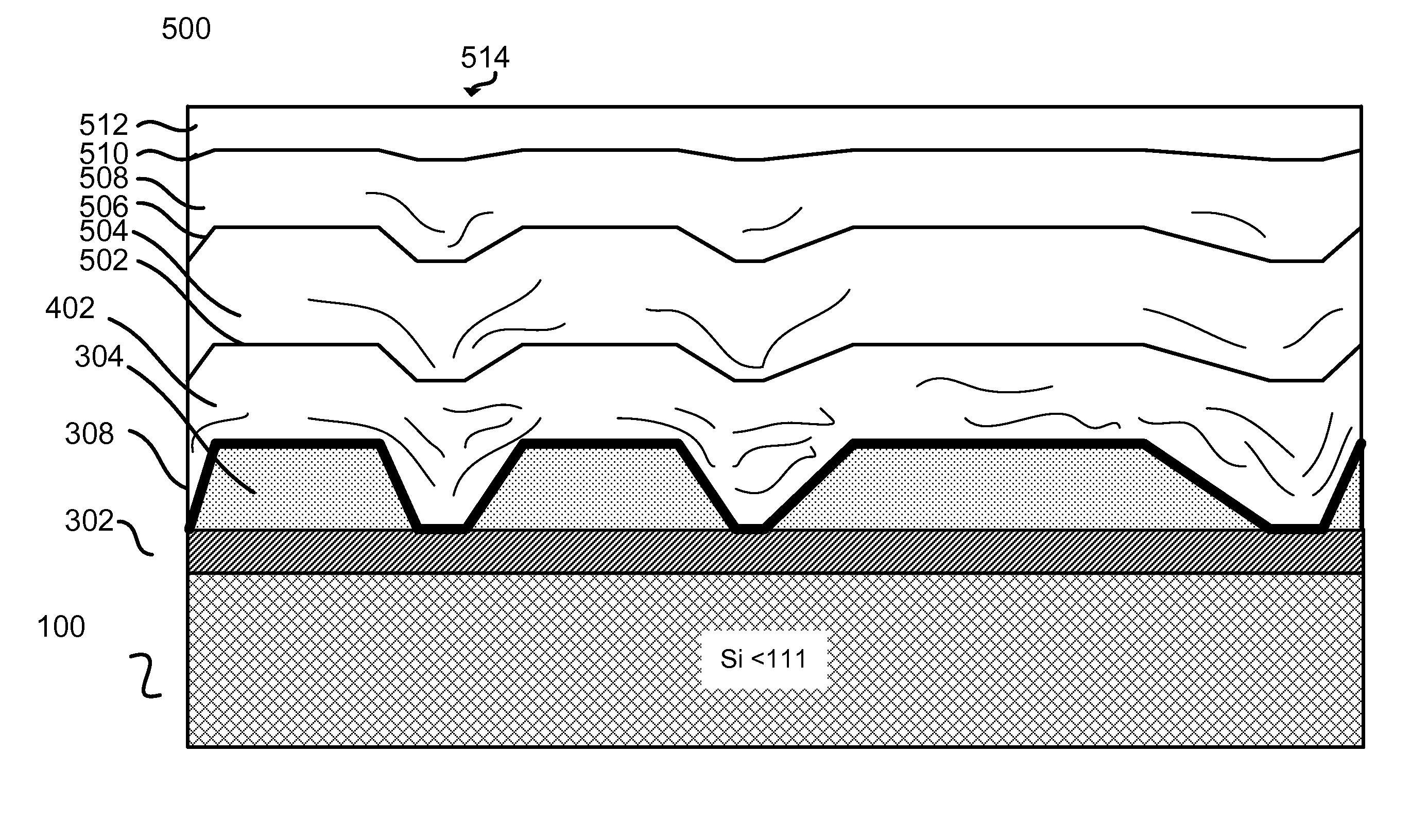

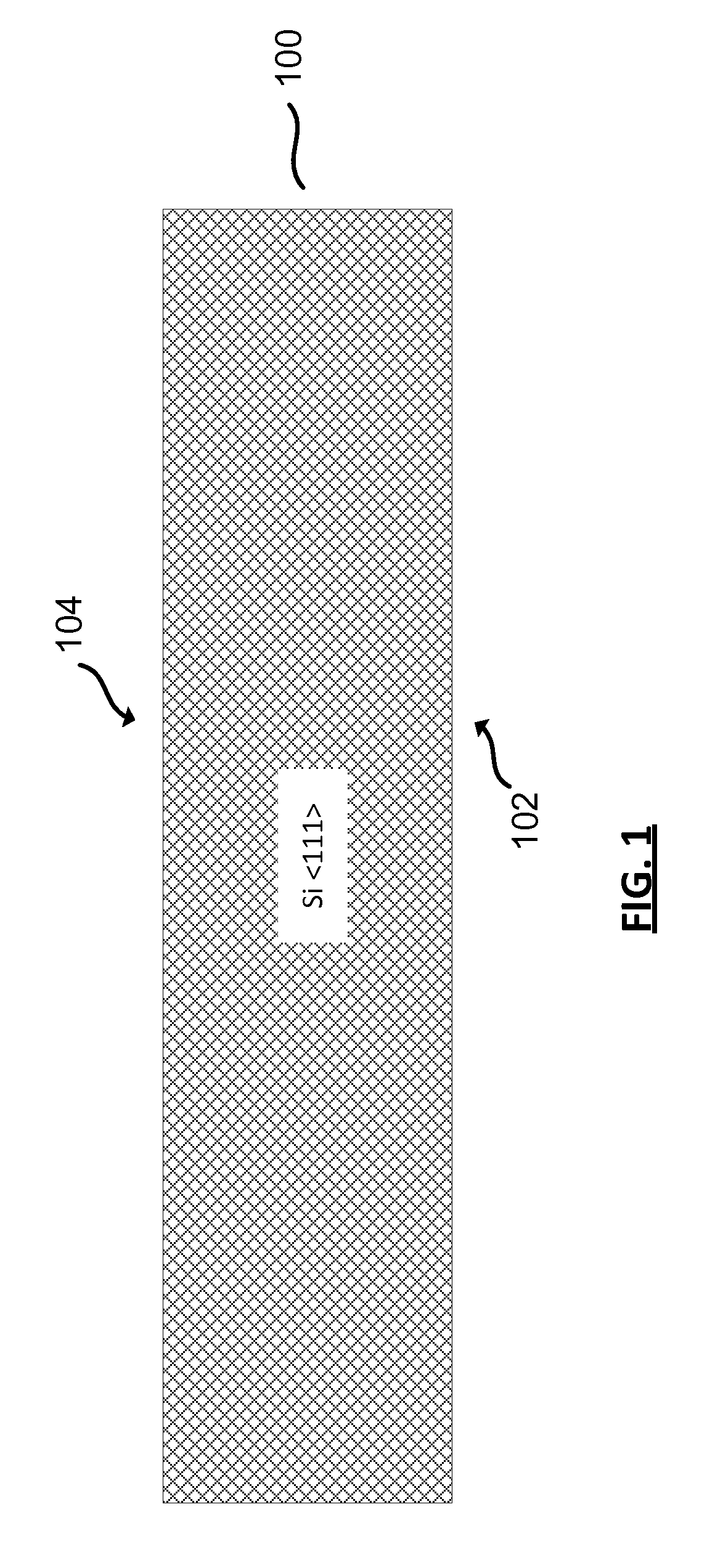

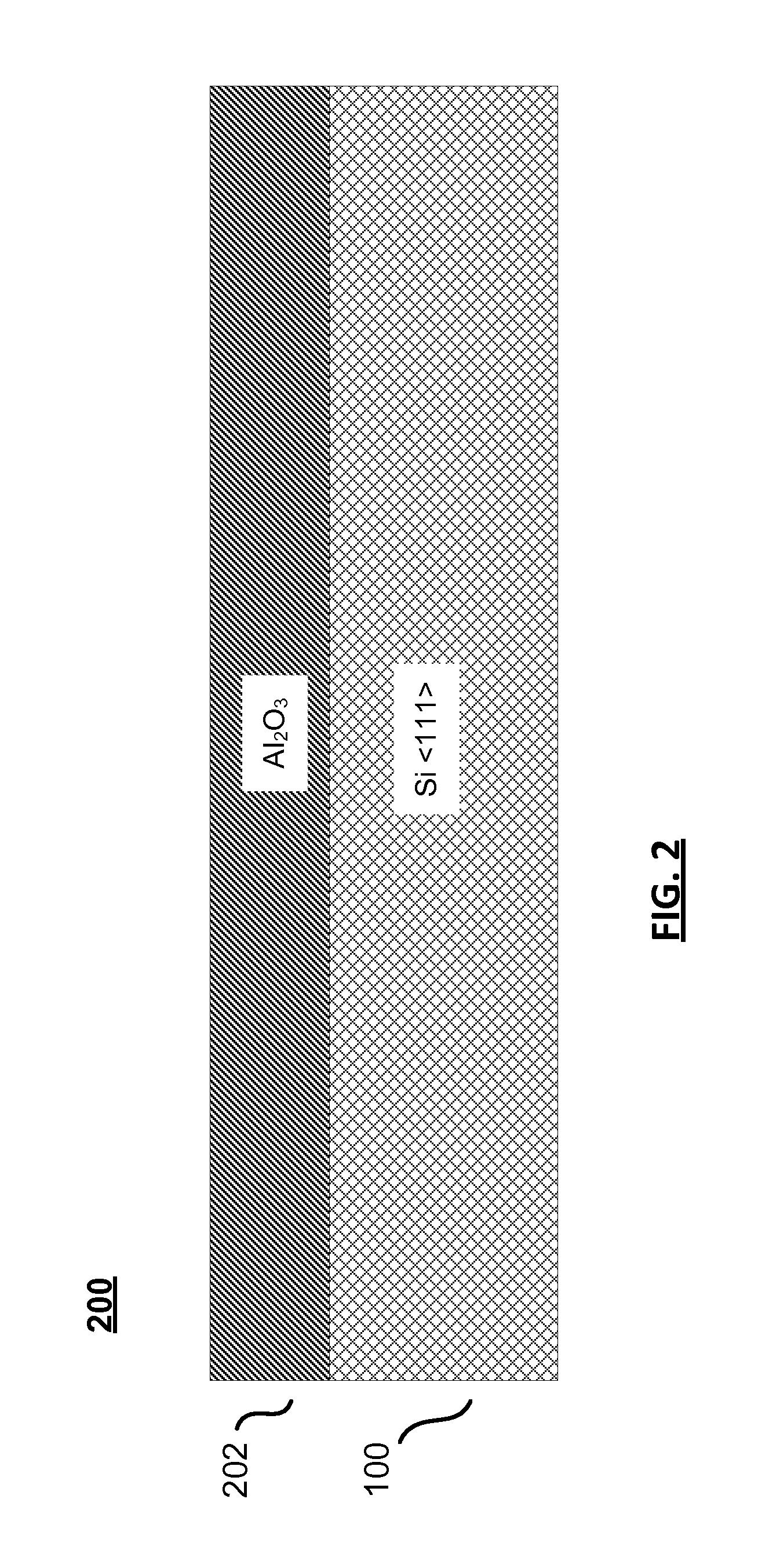

High quality GaN high-voltage HFETS on silicon

Substrates of GaN over silicon suitable for forming electronics devices such as heterostructure field effect transistors (HFETs), and methods of making the substrates, are disclosed. Voids in a crystalline Al2O3 film on a top surface of a silicon wafer are formed. The top surface of the silicon wafer is along the <111> silicon crystal orientation. A plurality of laminate layers is deposited over the voids and the Al2O3 film. Each laminate layer includes an AlN film and a GaN film. A transistor or other device may be formed in the top GaN film.

Owner:POWER INTEGRATIONS INC

Heterostructure field-effect transistor

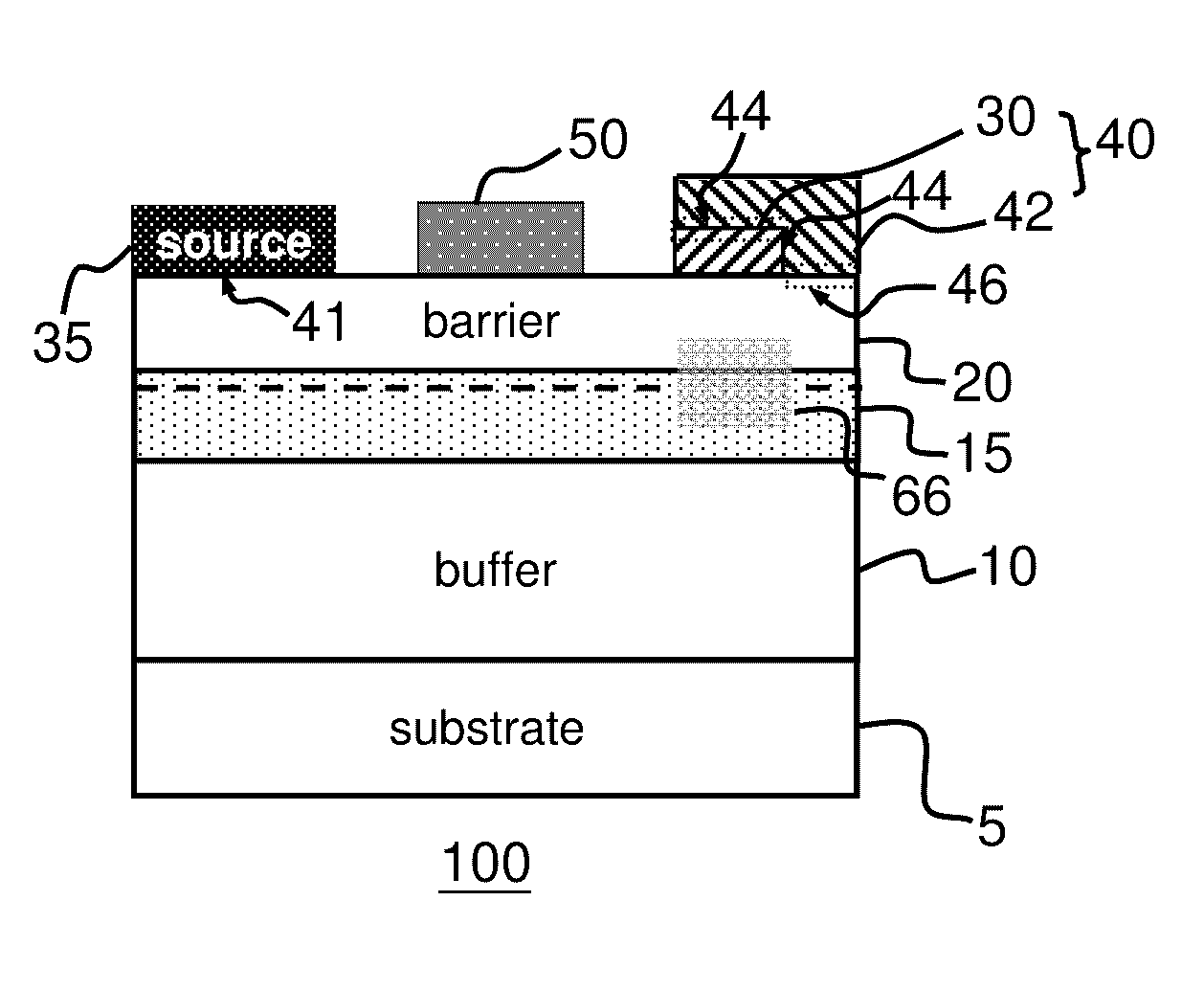

ActiveUS9577048B1Low costGood blocking performanceSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactEngineering

Heterostructure field-effect transistor (HFET) having a channel layer, a barrier layer disposed on the channel layer, and a gate, source and drain electrodes disposed on the barrier layer, respectively, and corresponding fabrication methods are disclosed. The drain electrode includes a p-type semiconductor patterned structure and a raised drain section, the drain electrode includes a Schottky contact and an ohmic contact, the Schottky contact is formed between a top surface together with a side surface of p-type semiconductor patterned structure and a bottom surface together with a side surface of raised drain section, the ohmic contact is formed between another surface of raised drain section and barrier layer, the raised drain section partially surrounding the p-type semiconductor patterned structure, and a bandgap of the channel layer is less than a bandgap of the barrier layer.

Owner:EPISTAR CORP

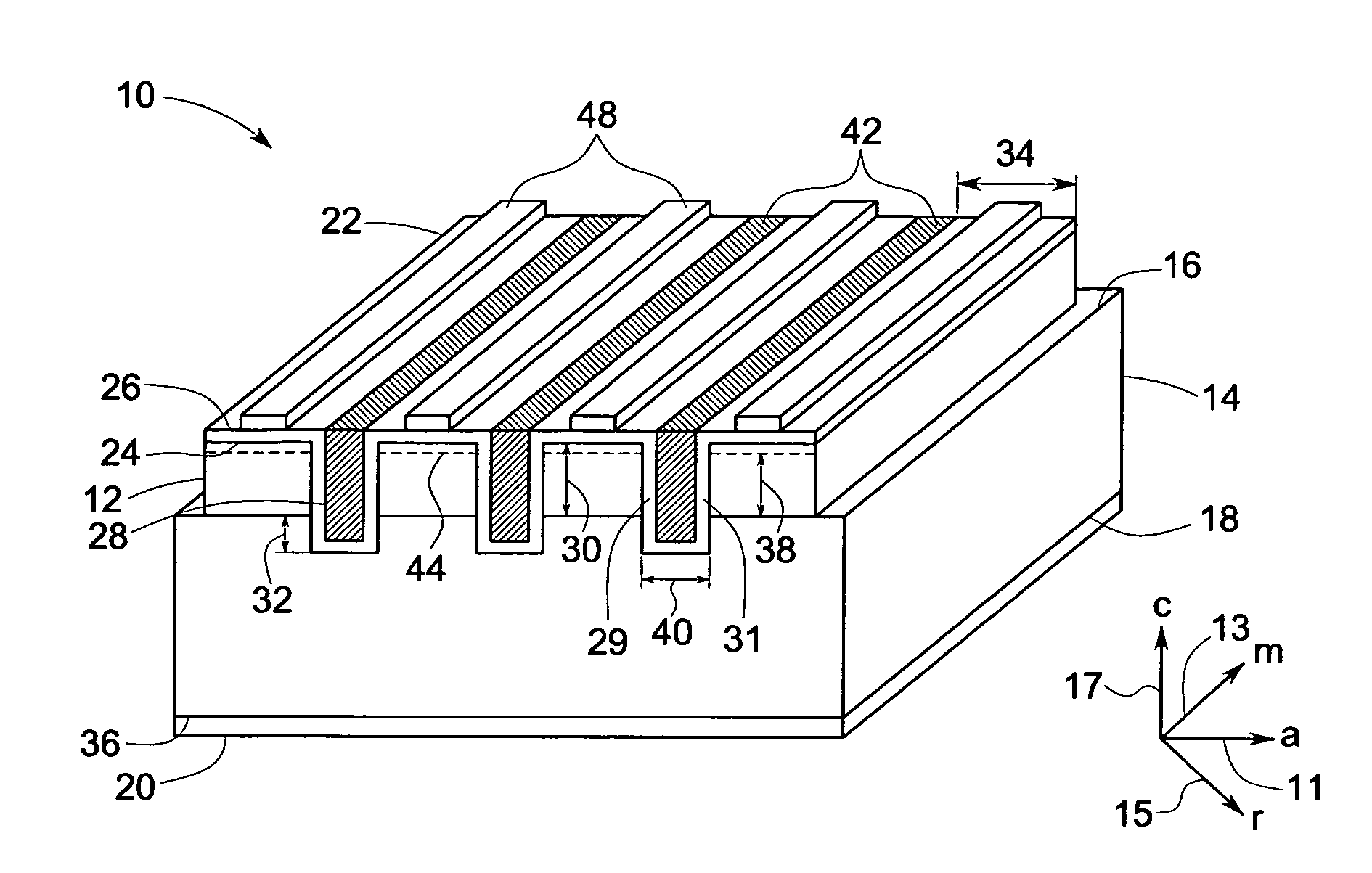

Vertical heterostructure field effect transistor and associated method

A vertical heterostructure field effect transistor including a first layer having a first material, and the first material having a hexagonal crystal lattice structure defining a first bandgap and one or more non-polar planes is provided. The transistor further includes a second layer that is adjacent to the first layer having a second material. Further, the second layer has a first surface and a second surface, and a portion of the second layer first surface is coupled to the surface of the first layer to form a two dimensional charge gas and to define a first region. The second material may have a second bandgap that is different than the first bandgap. Furthermore, the transistor may include a conductive layer that is disposed in the trench and is interposed between the first region and a second region that is not in electrical communication with the first region if no electrical potential is applied to the conductive layer, and an electrical potential applied to the conductive layer allows electrical communication from the first region to the second region.

Owner:GENERAL ELECTRIC CO

Gallium nitride based semiconductor devices and methods of manufacturing the same

ActiveUS8698162B2Improve cooling effectImprove operating characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceElectrical polarity

Gallium nitride (GaN) based semiconductor devices and methods of manufacturing the same. The GaN-based semiconductor device may include a heat dissipation substrate (that is, a thermal conductive substrate); a GaN-based multi-layer arranged on the heat dissipation substrate and having N-face polarity; and a heterostructure field effect transistor (HFET) or a Schottky electrode arranged on the GaN-based multi-layer. The HFET device may include a gate having a double recess structure. While such a GaN-based semiconductor device is being manufactured, a wafer bonding process and a laser lift-off process may be used.

Owner:SAMSUNG ELECTRONICS CO LTD

Normally off gallium nitride field effect transistors (FET)

ActiveUS20140175451A1The process is simple and convenientImproved device configurationTransistorSemiconductor/solid-state device manufacturingElectrical conductorInsulation layer

A heterostructure field effect transistor (HFET) gallium nitride (GaN) semiconductor power device comprises a hetero-junction structure comprises a first semiconductor layer interfacing it second semiconductor layer of two different band gaps thus generating an interface layer as a two-dimensional electron gas (2DEG) layer. The power device further comprises a source electrode and a drain electrode disposed on two opposite sides of a gate electrode disposed on top of the hetero-junction structure for controlling a current flow between the source and drain electrodes in the 2DEG layer. The power device further includes a floating gate located between the gate electrode an hetero-junction structure, wherein the gate electrode is insulated from the floating gate with an insulation layer and wherein the floating gate is disposed above and padded with a thin insulation layer from the hetero-junction structure and wherein the floating gate is charged for continuously applying a voltage to the 2DEG layer to pinch off the current flowing in the 2DEG layer between the source and drain electrodes whereby the HFET semiconductor power device is a normally off device.

Owner:ALPHA & OMEGA SEMICON INC

Vertical channel heterostructure field-effect transistor and preparation method thereof

InactiveCN106684143ARealize full angle surroundImprove gate control abilitySemiconductor/solid-state device manufacturingSemiconductor devicesVertical channelSemiconductor

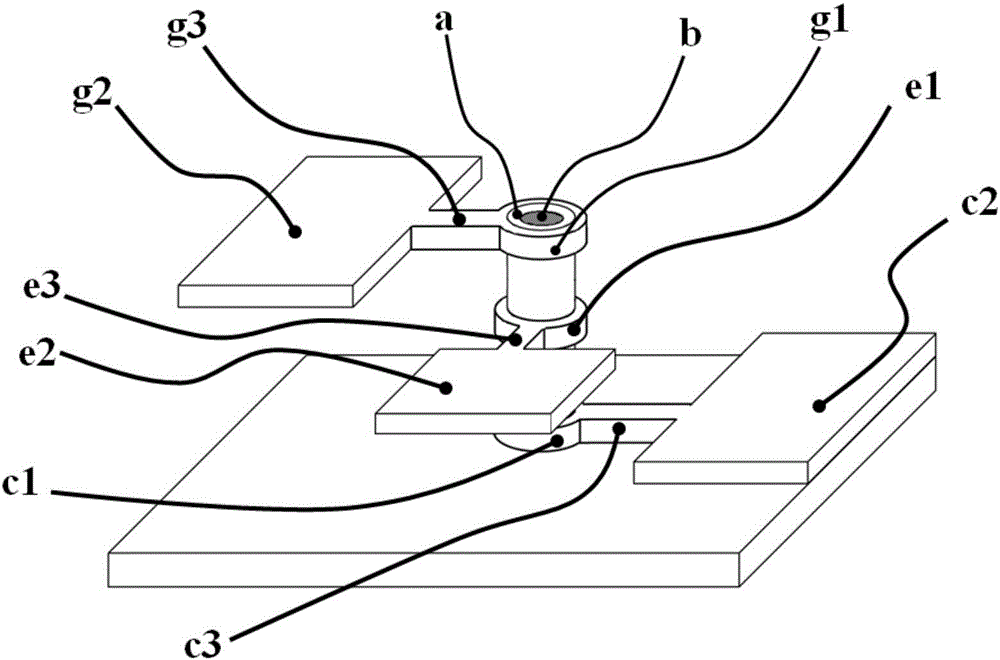

The invention discloses a vertical channel heterostructure field-effect transistor (VC-HFET) and a preparation method thereof. The heterostructure field-effect transistor comprises a source electrode, a drain electrode, a grid electrode and at least one heterostructure channel, wherein the axis of the heterostructure channel is fundamentally vertical to a selected plane; the heterostructure channel is positioned in a heterostructure; the heterostructure comprises a second semiconductor and a first semiconductor arranged around the second semiconductor, the energy gap of the first semiconductor is greater than that of the second semiconductor, and two-dimensional electron gas or two-dimensional hole gas is formed in the heterostructure channel; the source electrode is electrically connected with the drain electrode through the two-dimensional electron gas or the two-dimensional hole gas; and the grid electrode is distributed between the source electrode and the drain electrode. The heterostructure field-effect transistor disclosed by the invention has the advantages of being good in grid-control capacity, high in work efficiency, low in process difficulty, easy to manufacture, high in rate of finished products and the like.

Owner:HANGZHOU DIANZI UNIV

Heterostructure field effect transistor and associated method

A device including a first layer having a first material, and the first material having a hexagonal crystal lattice structure defining a first bandgap and one or more non-polar planes is provided. The device further includes a second layer that is adjacent to the first layer having a second material. The second material may have a second bandgap that is different than the first bandgap. The second layer may have a first surface and a second surface, and a portion of the second layer first surface may be coupled to a surface of the first layer to form a two dimensional charge gas and to define a first region. Further, the device includes a conductive layer that is interposed between the first region and a second region that is spaced from the first region, where the device is normally-off if no electrical potential is applied to the conductive layer, and an electrical potential applied to the conductive layer allows electrical communication from the first region to the second region.

Owner:GENERAL ELECTRIC CO

Methods of manufacturing the gallium nitride based semiconductor devices

InactiveUS20140021512A1Good heat dissipationImprove withstand voltage characteristicsSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

Owner:SAMSUNG ELECTRONICS CO LTD

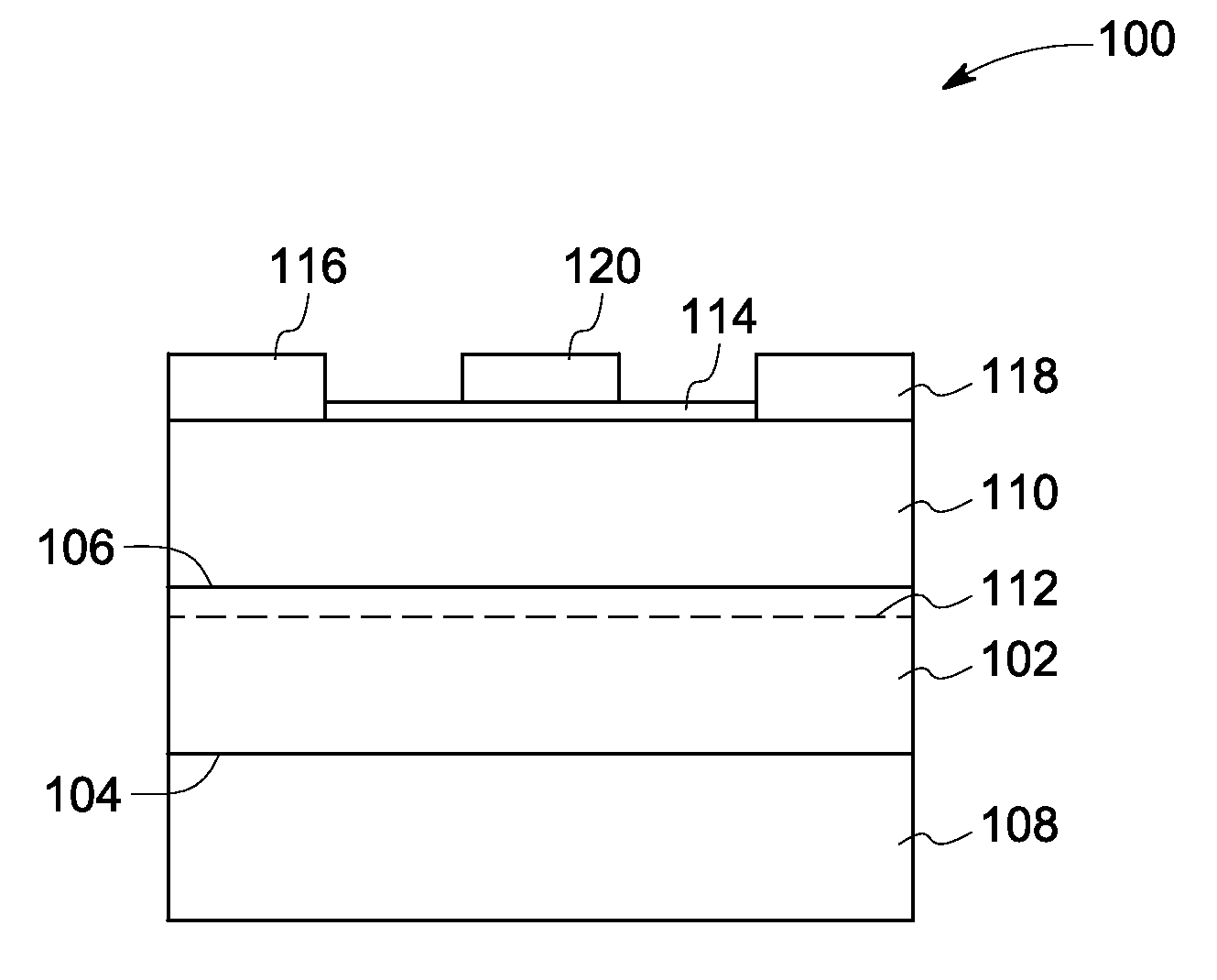

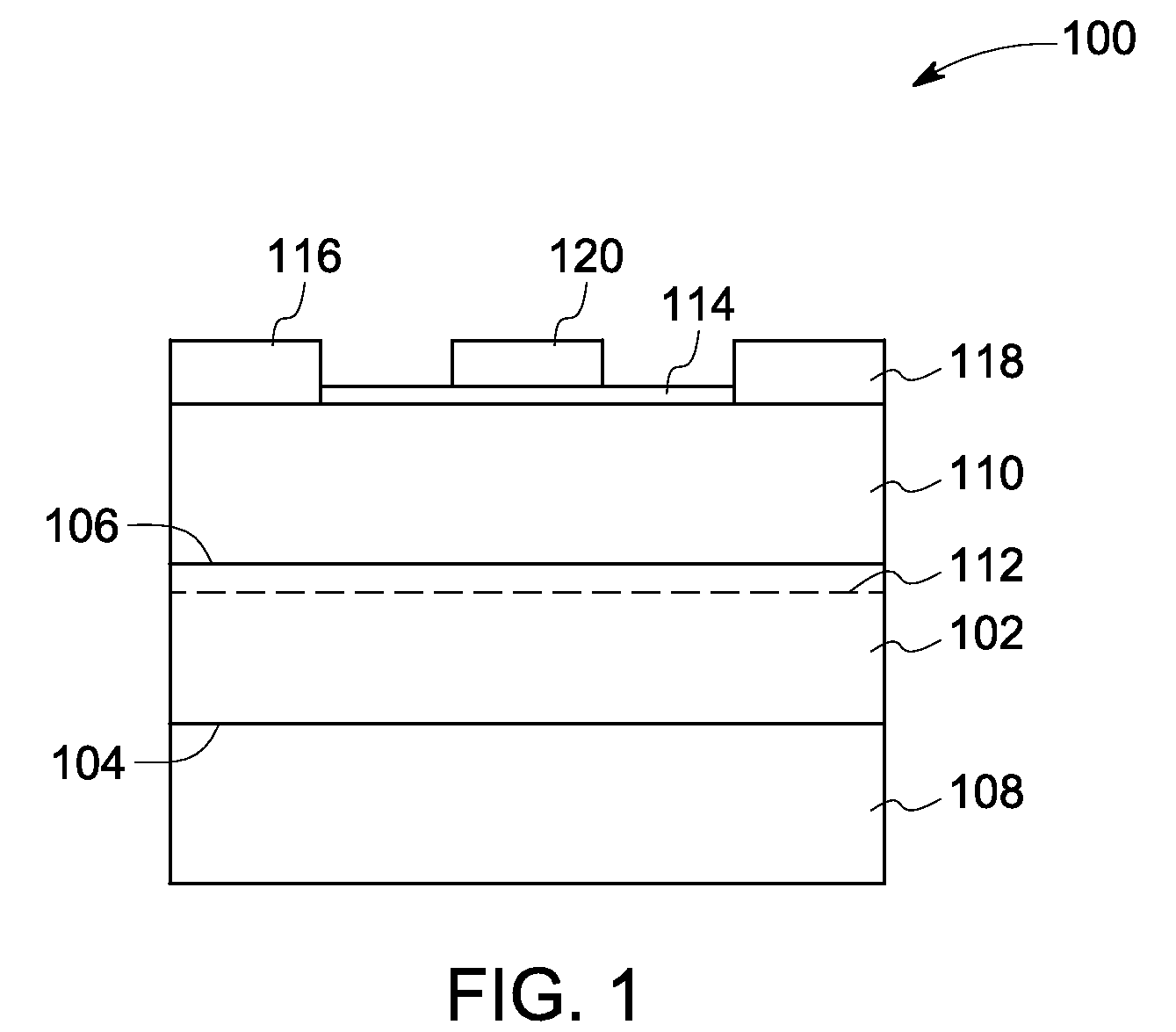

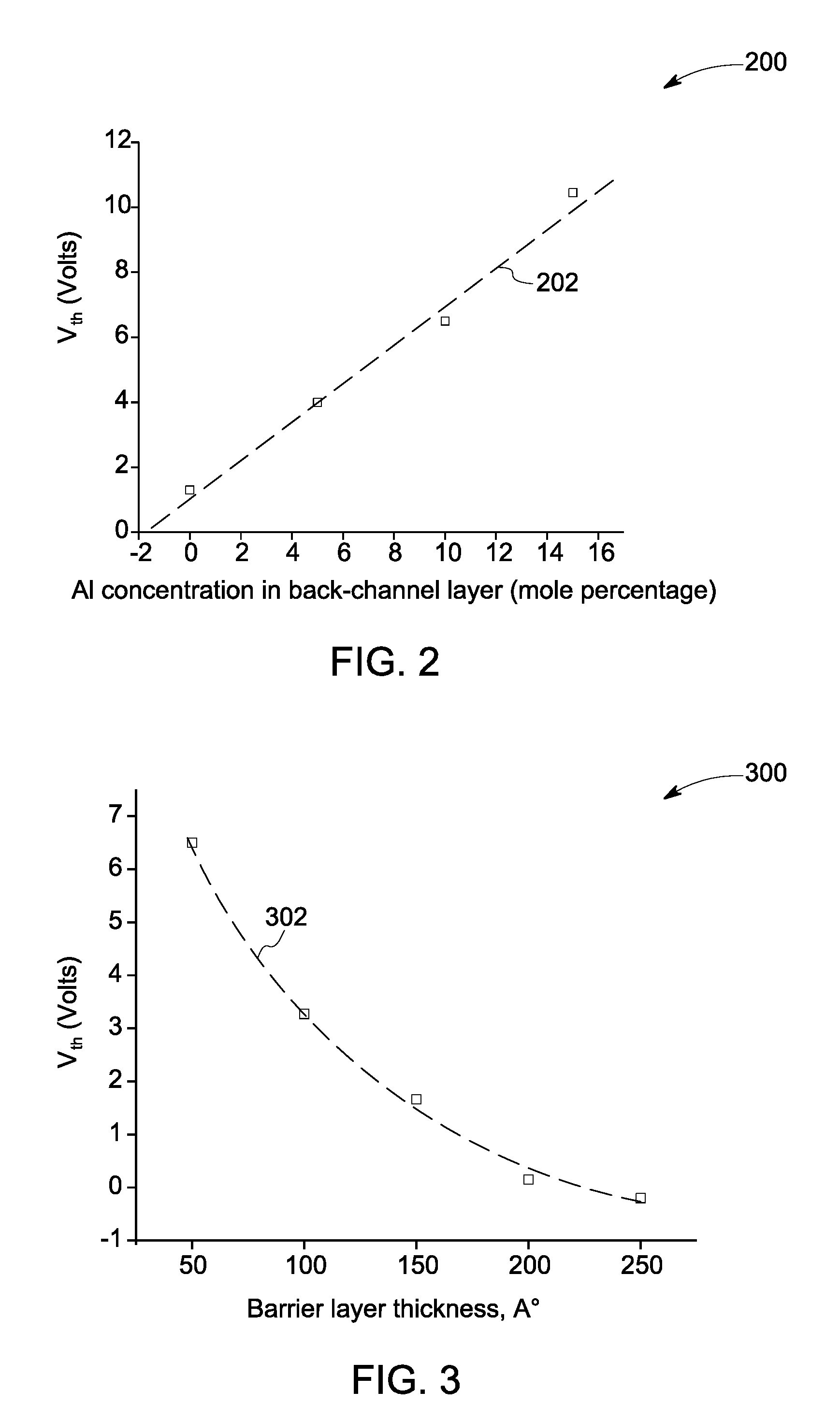

Heterostructure device and associated method

A heterostructure device or article includes a carrier transport layer, a back channel layer and a barrier layer. The carrier transport layer has a first surface and a second surface opposing to the first surface. The back channel layer is secured to the first surface of the carrier transport layer and the barrier layer is secured to the second surface of the carrier transport layer. Each of the carrier transport layer, the back channel layer and the barrier layer comprises an aluminum gallium nitride alloy. The article further includes a 2D electron gas at an interface of the second surface of the carrier transport layer and a surface of the barrier layer. The 2D electron gas is defined by a bandgap differential at an interface, which allows for electron mobility. A system includes a heterostructure field effect transistor that includes the article.

Owner:GENERAL ELECTRIC CO

Method for fabricating a non-planar nitride-based heterostructure field effect transistor

ActiveUS20050194602A1Prevent oxidationAvoid damageSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsSolvent

A method for fabricating a non-planar heterostructure field effect transistor using group III-nitride materials with consistent repeatable results is disclosed. The method provides a substrate on which at least one layer of semiconductor material is deposited. An AlN layer is deposited on the at least one layer of semiconductor material. A portion of the AlN layer is removed using a solvent to create a non-planar region with consistent and repeatable results. The at least one layer beneath the AlN layer is insoluble in the solvent and therefore acts as an etch stop, preventing any damage to the at least one layer beneath the AlN layer. Furthermore, should the AlN layer incur any surface damage as a result of the reactive ion etching, the damage will be removed when exposed to the solvent to create the non-planar region.

Owner:HRL LAB

Gan-based field effect transistor and production method therefor

InactiveUS7547911B2Semiconductor/solid-state device manufacturingInterconnection systemsEngineeringBreakdown voltage

A GaN-based heterostructure field effect transistor capable of accomplishing higher output, higher breakdown voltage, higher speed, higher frequency, and the like. A heterostructure field effect transistor including a channel layer (4) of GaN and a barrier layer (6) of AlGaN, wherein the surface of a transistor element has an insulating film (10).

Owner:NAT INST OF INFORMATION & COMM TECH

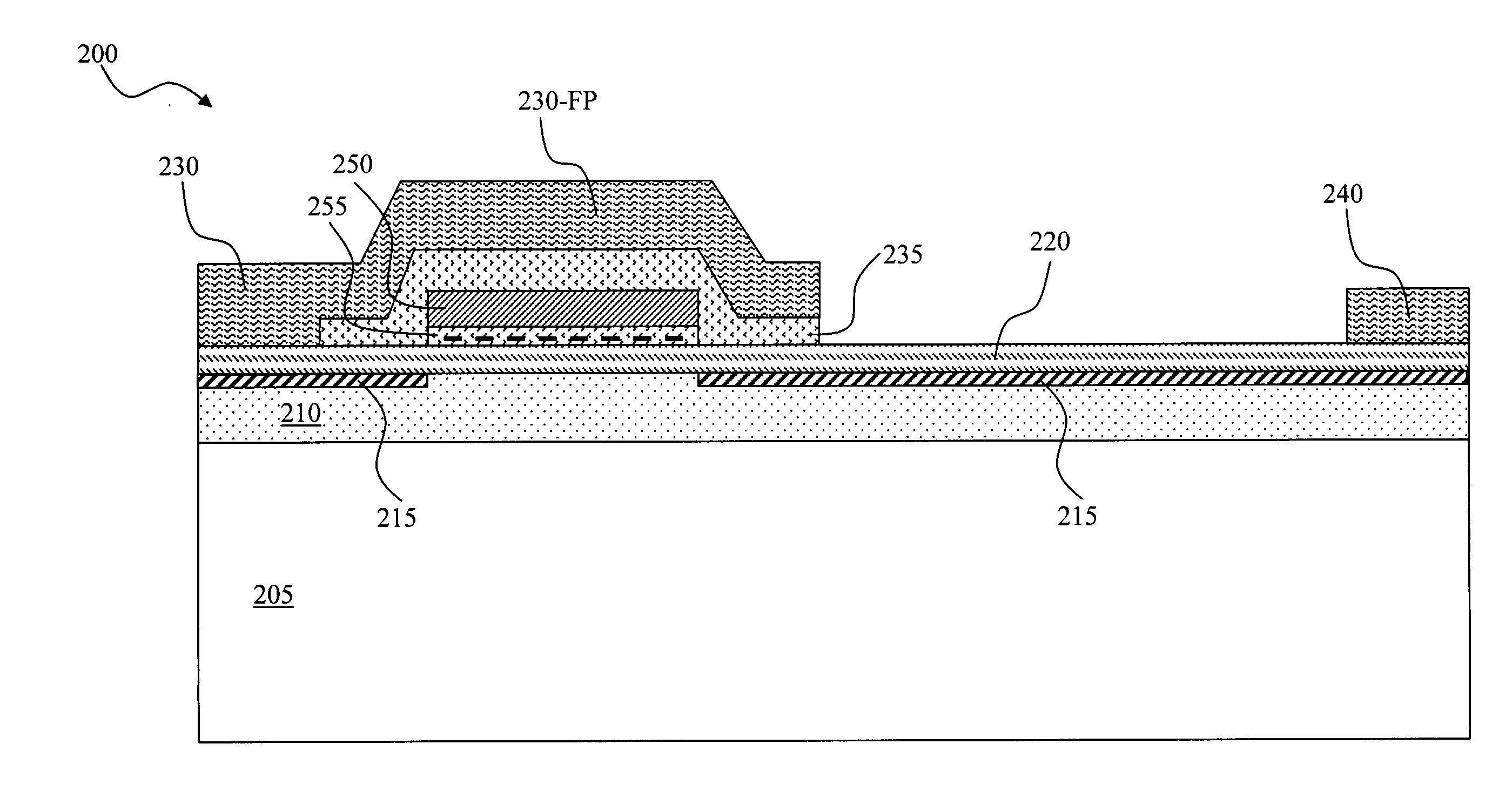

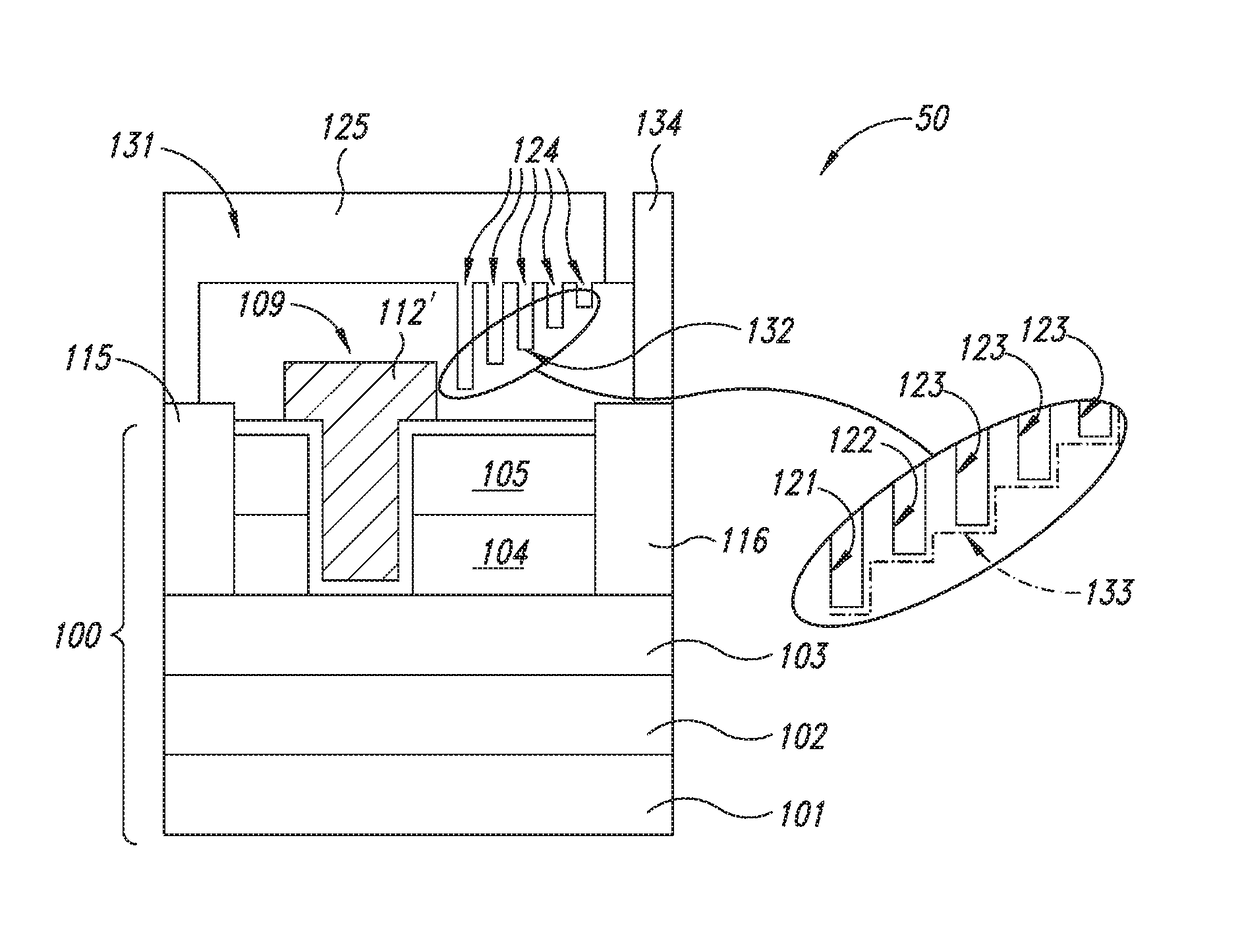

High-power and high-frequency heterostructure field-effect transistor

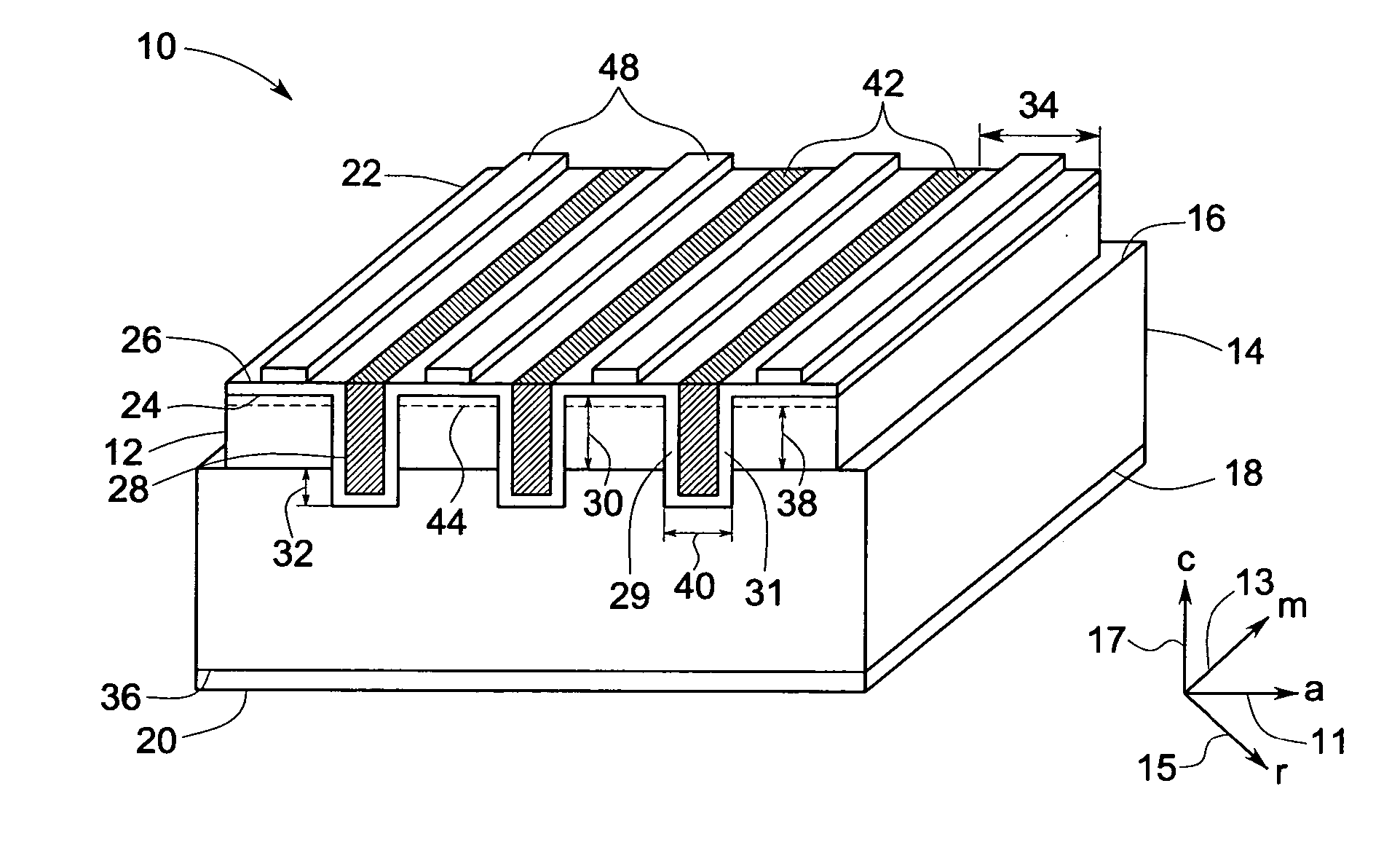

ActiveUS10050136B2Semiconductor/solid-state device manufacturingSemiconductor devicesConductive materialsDielectric layer

In an HEMT device, a gate region is formed in a wafer having a channel layer, a barrier layer, and a passivation layer, overlying each other. Drain and source electrodes are formed in the wafer, on different sides of the gate region. A dielectric layer is formed over the gate region and over the passivation layer. Selective portions of the dielectric layer are removed by a plurality of etches so as to form one or more cavities between the gate region and the drain electrode. The one or more cavities have a plurality of steps at an increasing distance from the wafer moving from the gate region to the drain electrode. The cavity is then filled with conductive material to form a field plate coupled to the source electrode, extending over the gate region, and having a surface facing the wafer and having a plurality of steps.

Owner:STMICROELECTRONICS SRL

Semiconductor heterostructure field effect transistor and method for making thereof

ActiveUS9093516B2Intrinsic electrostatics is enhancedEasy to controlSemiconductor devicesSemiconductor heterostructuresEngineering

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)