Patents

Literature

104results about How to "High density integration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

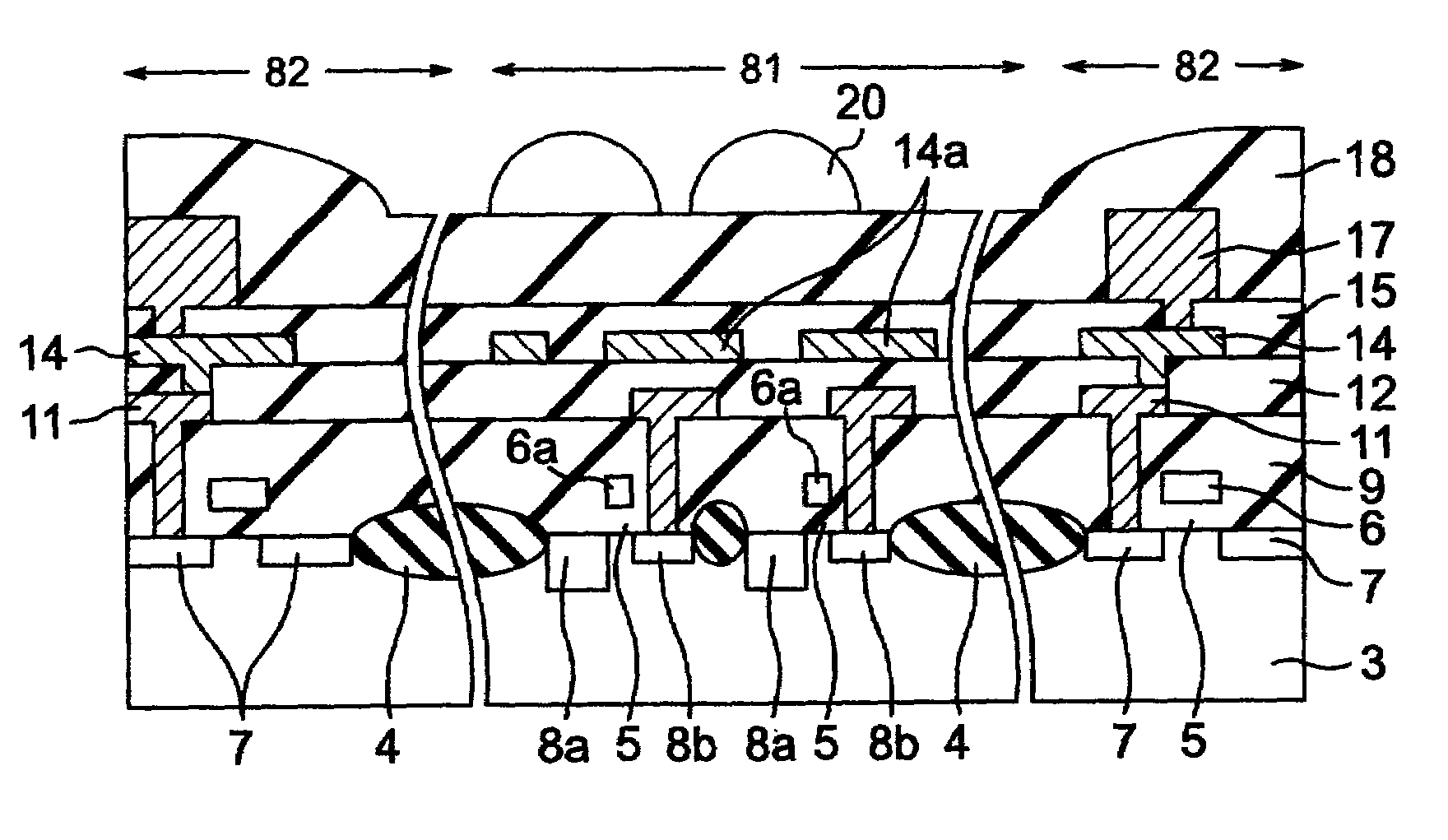

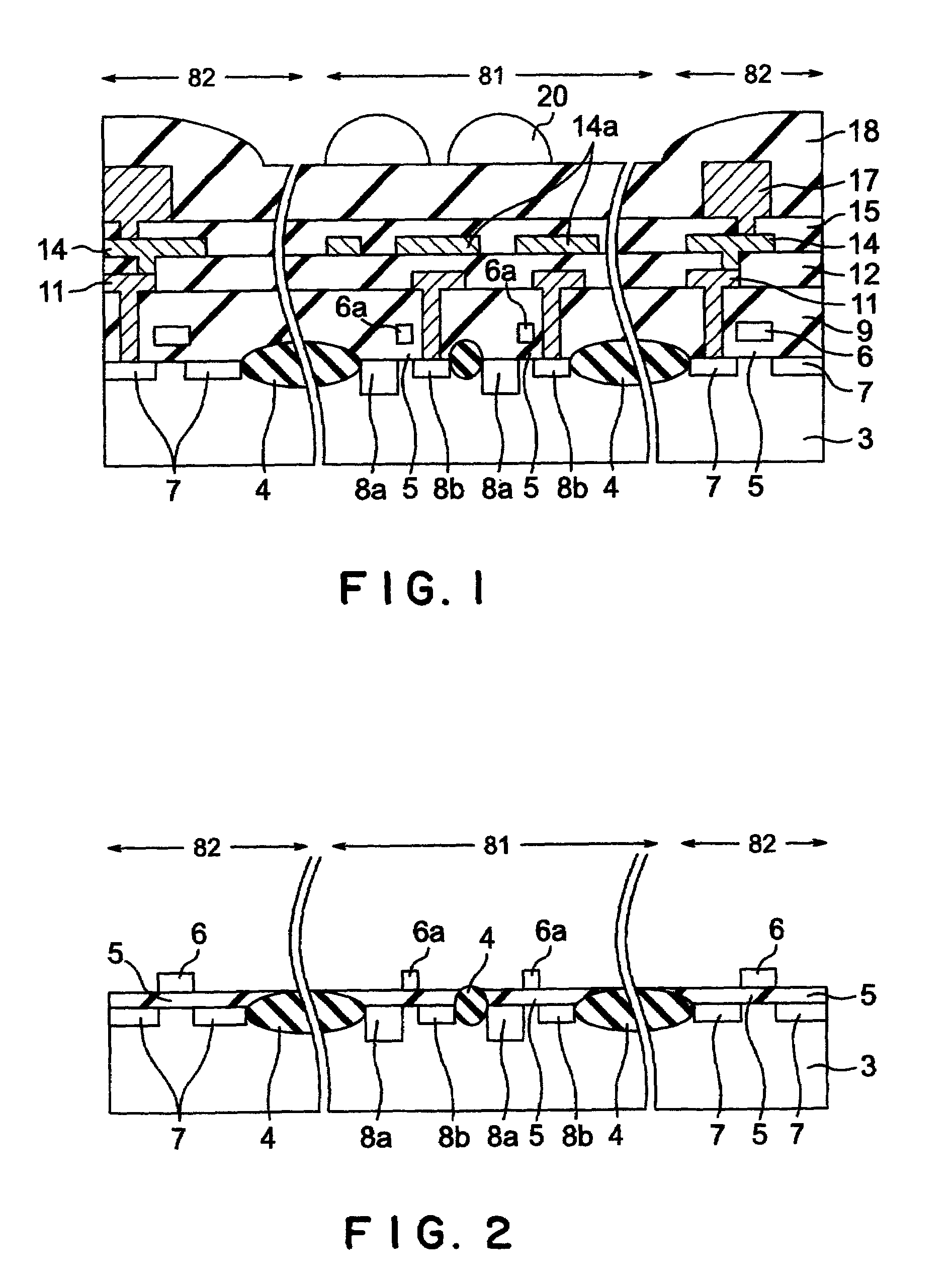

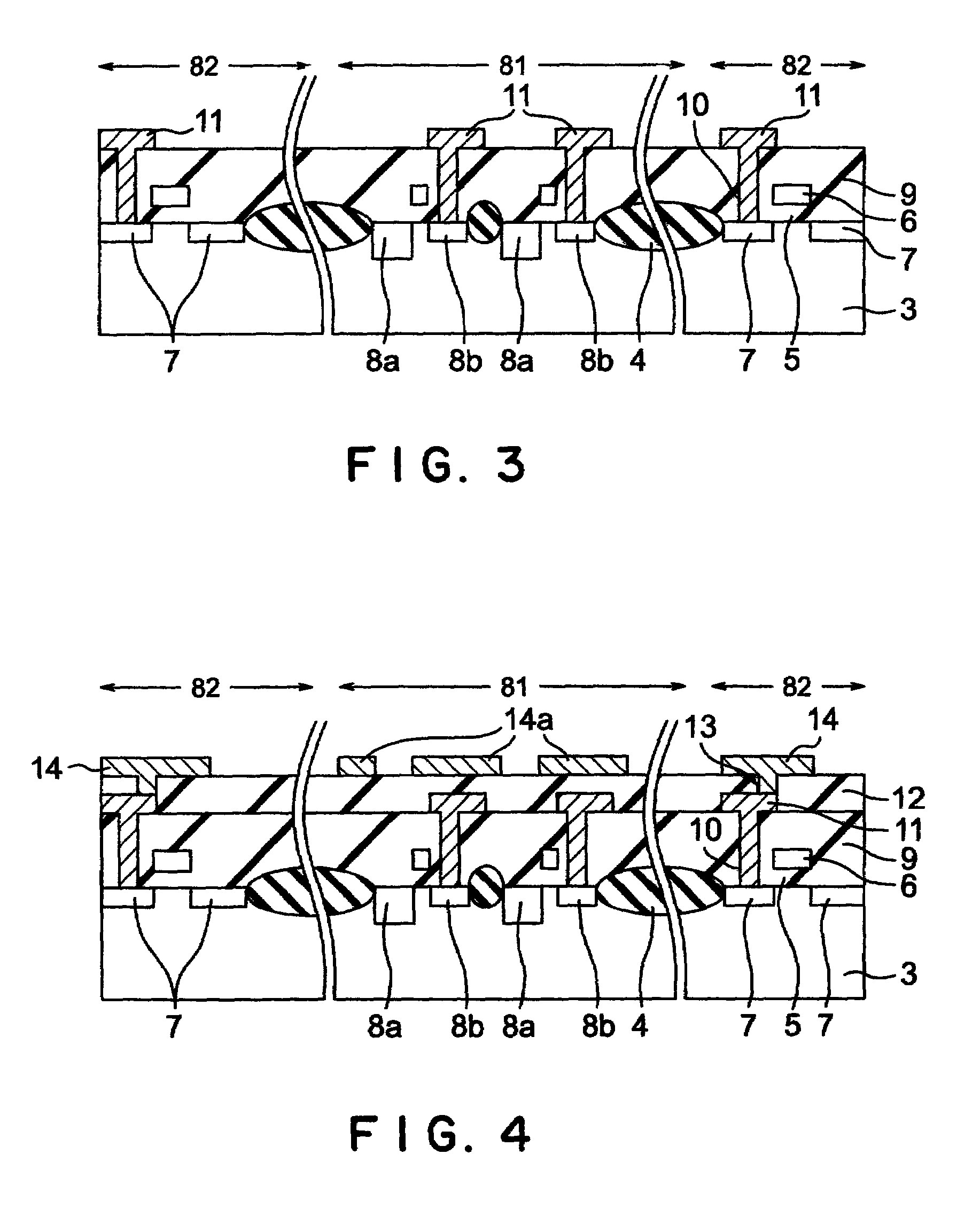

Display device

InactiveUS6853371B2Reduce signal linesLess spaceCathode-ray tube indicatorsNon-linear opticsHigh densityDisplay device

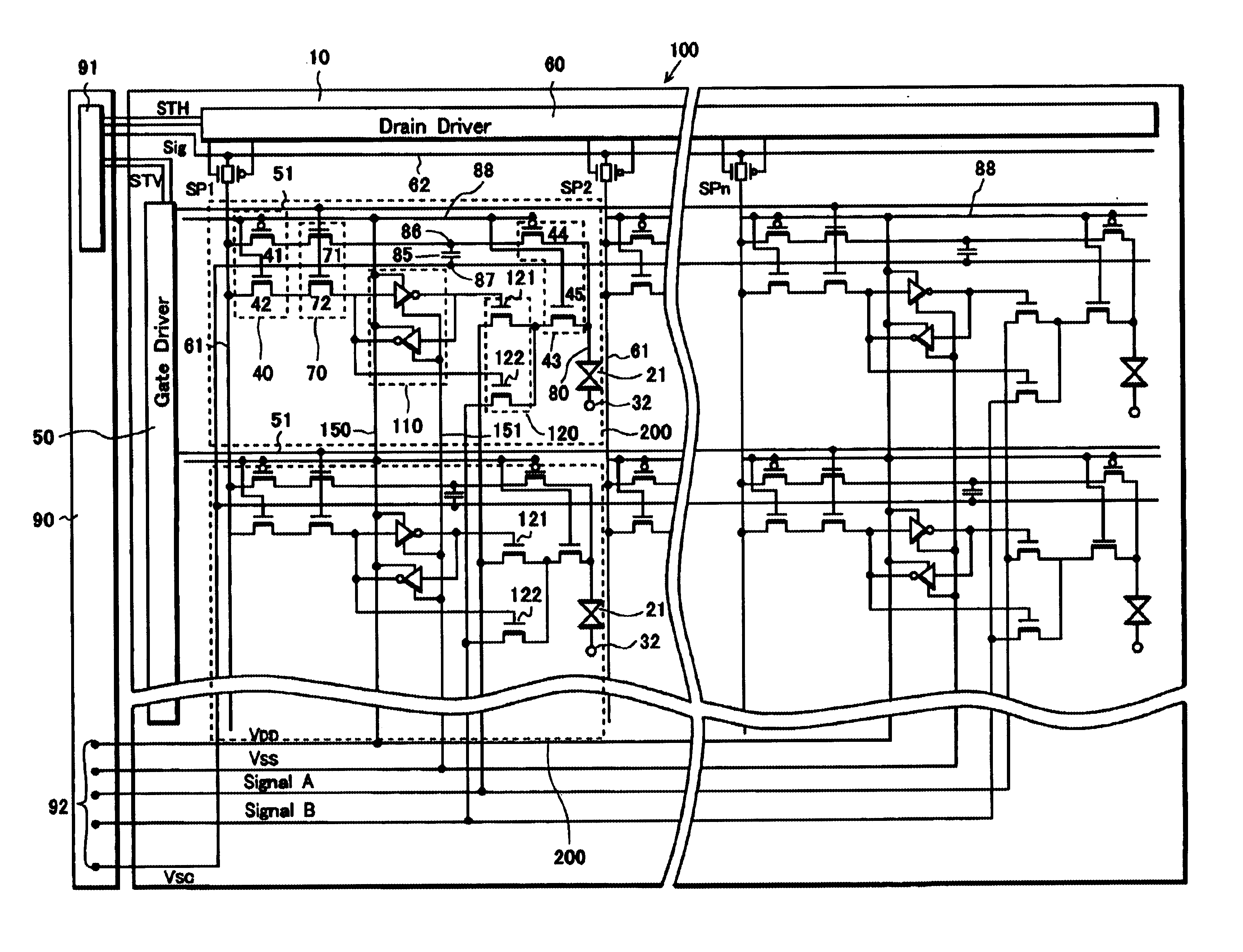

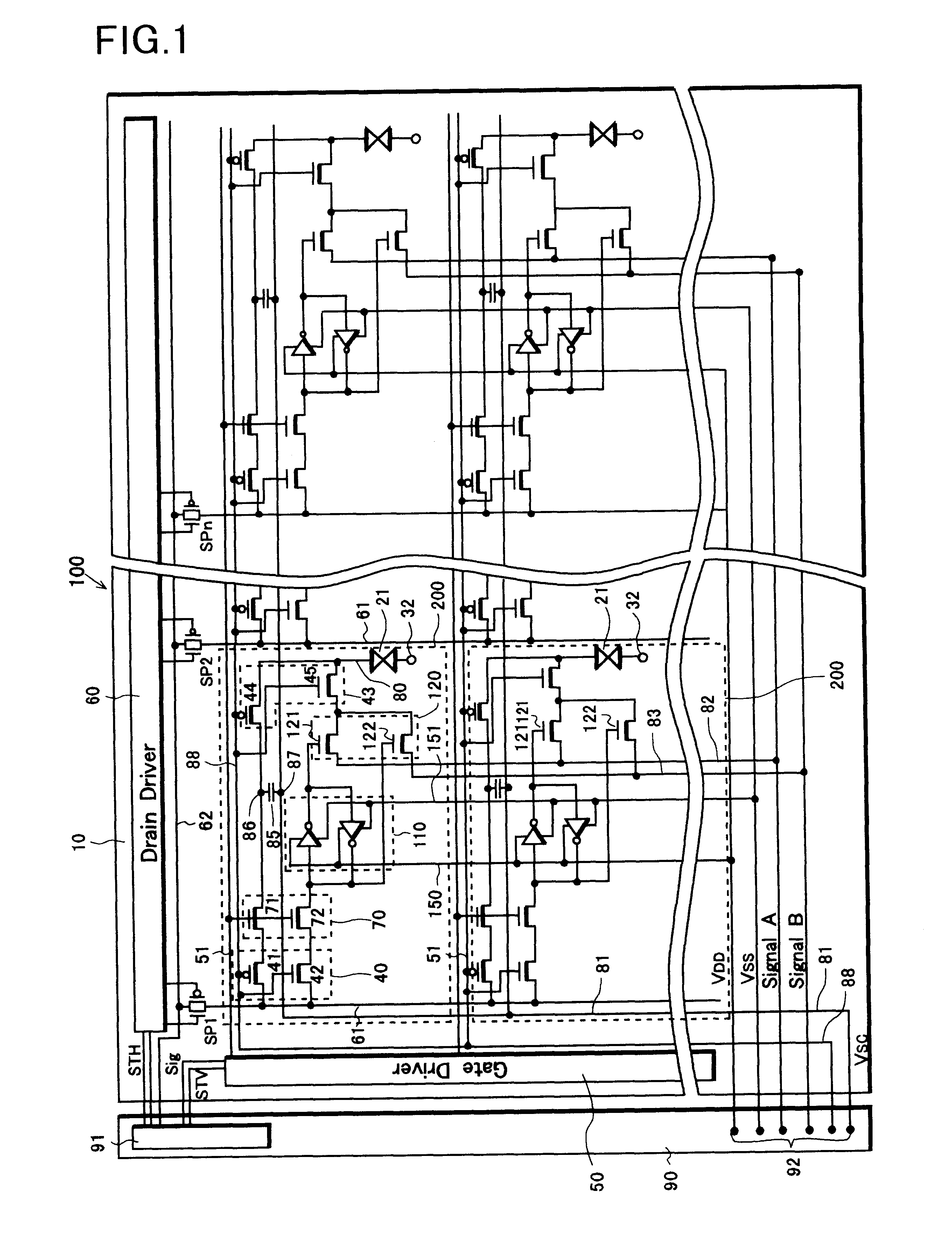

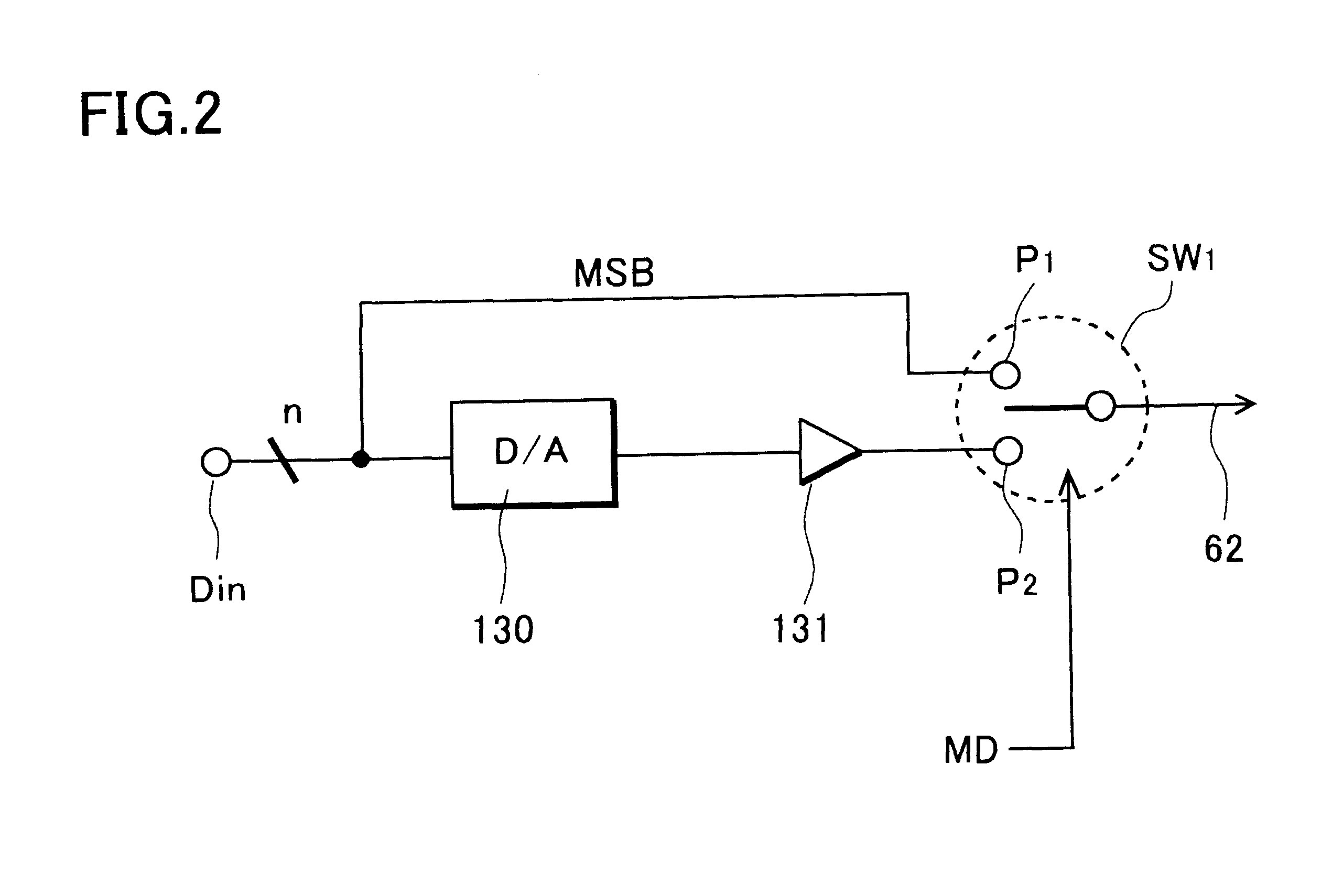

Within one pixel element 200, two display circuits corresponding to the analog display mode and the digital display mode are disposed such that they are adjacent to each other. One of these two display circuits can be selected through the circuit selection circuits 40 or 43. Since the high voltage power line 150 of the retaining circuit 110, which is used under the digital display mode, also performs as the signal selection line 88, it is possible to have the high density integration of the pixel element 200. Also, the bias voltage Vsc supplied through the selection storage capacitor line 81 is same as the signal A. Therefore, the storage capacitor line 81 is connected to the drain of the TFT 122 of the signal selection circuit 120 so that the signal line 82 for supplying the signal A can be omitted. Thus, the high-density integration of the pixel element 200 can be achieved.

Owner:SANYO ELECTRIC CO LTD

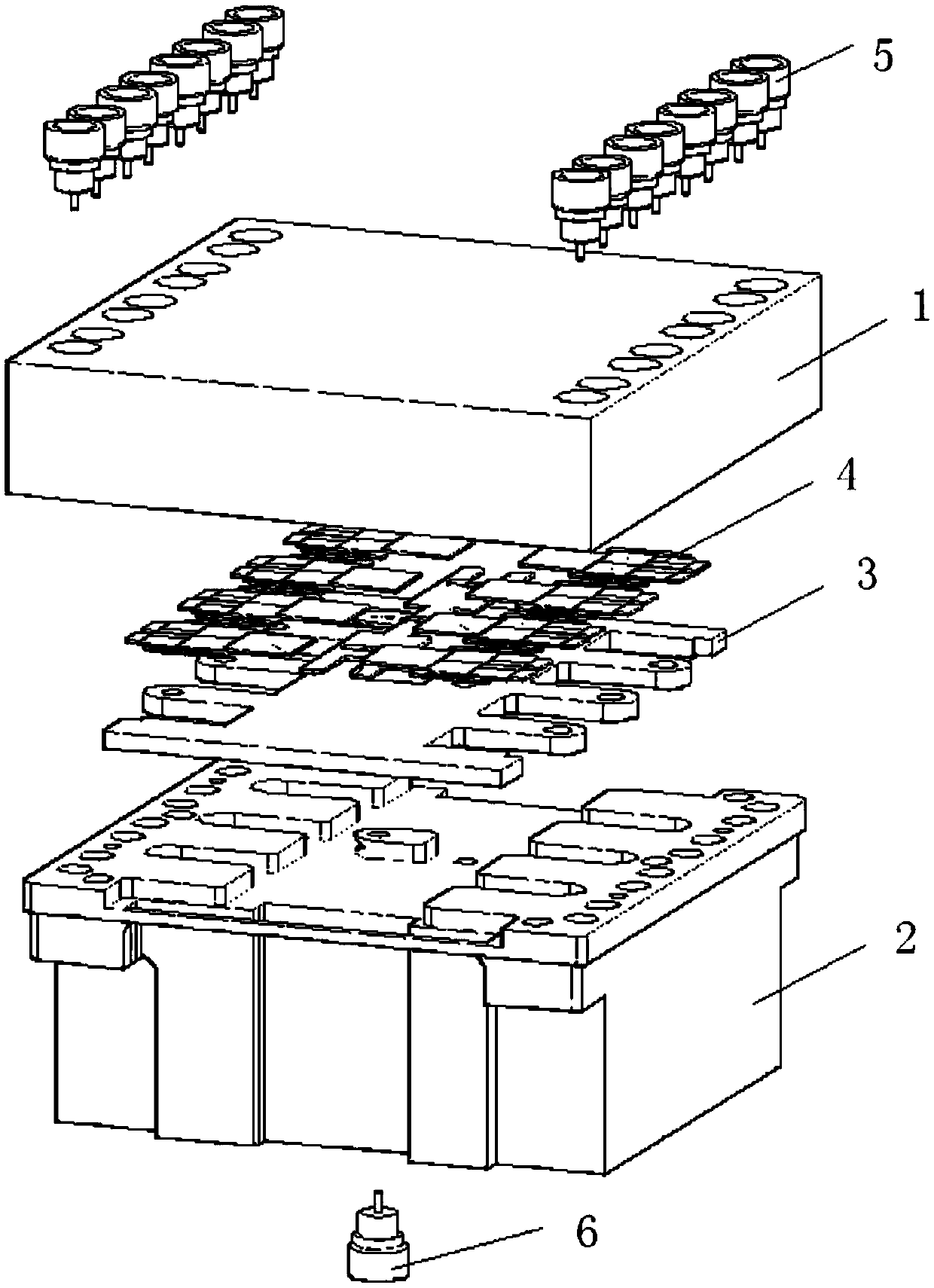

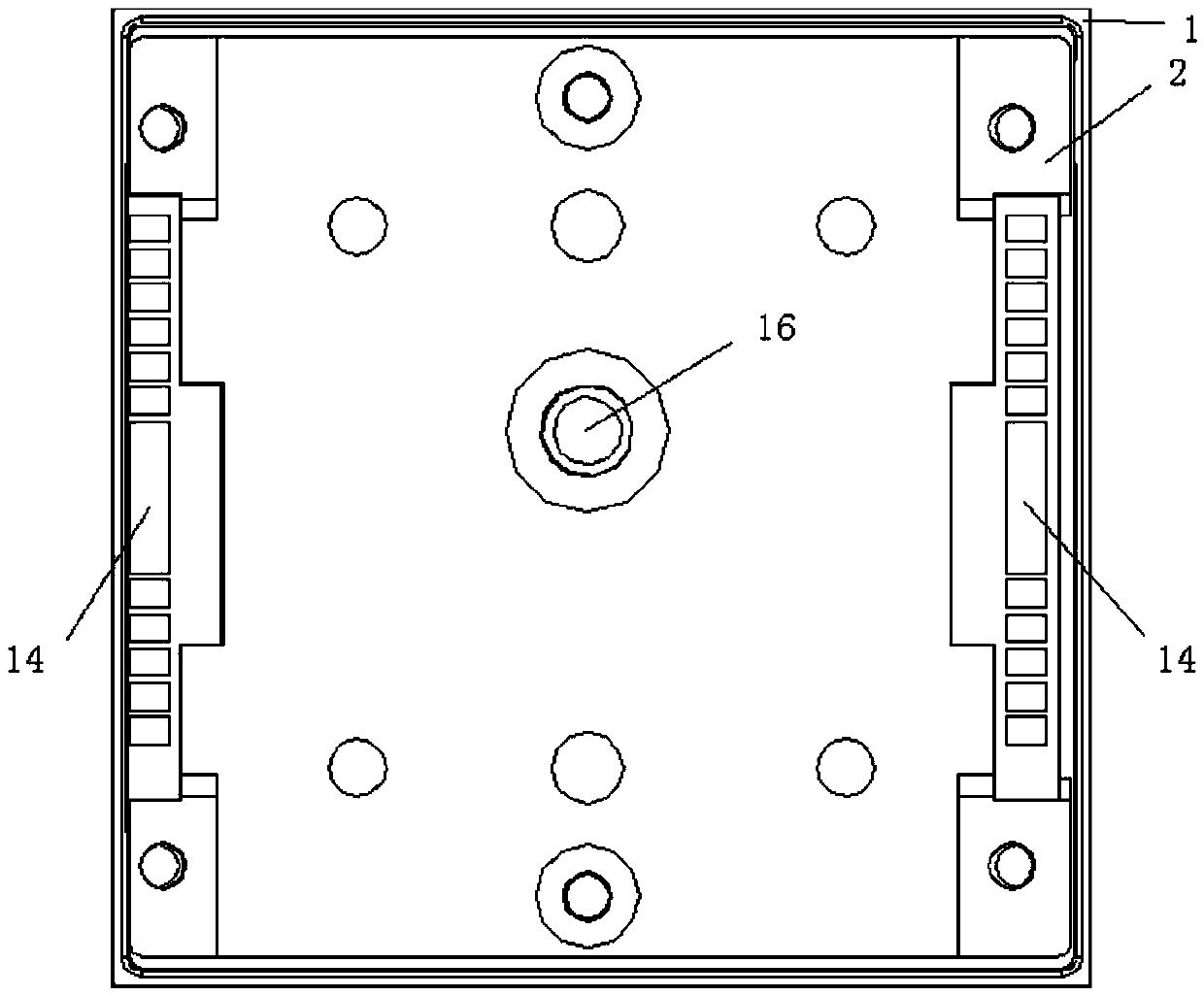

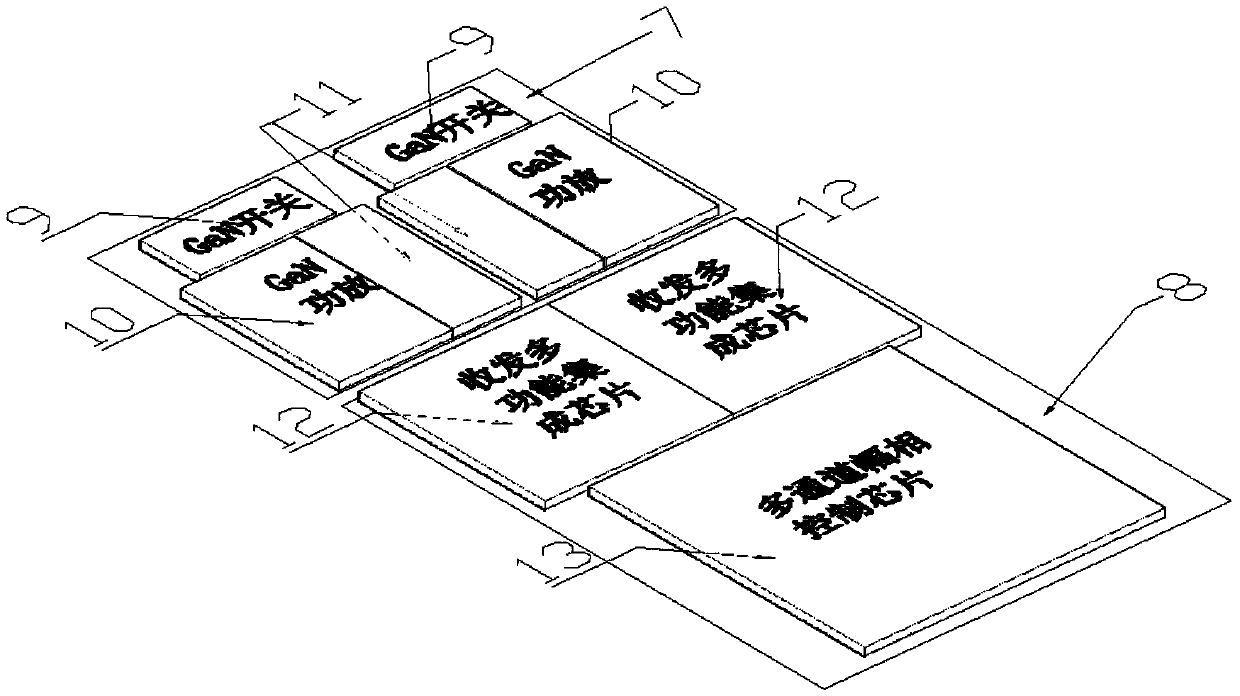

Millimeter wave tile-type phased-array antenna TR module

ActiveCN105514566AReduce thermal resistanceShort cooling pathAntenna supports/mountingsModular arraysHigh densityRadio frequency signal

The invention relates to a millimeter wave tile-type phased-array antenna TR module, and the invention aims at providing a TR module realization scheme with advantages of high reliability, low cost and high density integration for a millimeter wave frequency range high-power active phased-array antenna (APAA). The millimeter wave tile-type phased-array antenna TR module can be realized by the following scheme: a radio-frequency signal is fed from a radio-frequency vertical interconnection interface of a common port of the lower cavity bottom of the TR module, after the radio-frequency signal is performed the power distribution through a power divider mounting on the surface of a multi-layer circuit board and the like, the radio-frequency signal is fed in a multichannel amplitude-phase control chip connected with every transmit-receive channel, after the radio-frequency signal is performed the second power distribution by the multichannel amplitude-phase control chip, the amplitude-phase information of each channel radio-frequency signal is adjusted according to the state of the external control code and is outputted to a TR multi-function chip, the signal is amplified and outputted to the final power amplifier until saturation, the signal is outputted to a power switch, the emission access is gated, and the signal is transmitted to antenna radio-frequency vertical interconnection interfaces arranged on two ends of the cavity on the TR module; when the TR module receives a work, the radio-frequency signal passes through the TR module in a reverse direction.

Owner:10TH RES INST OF CETC

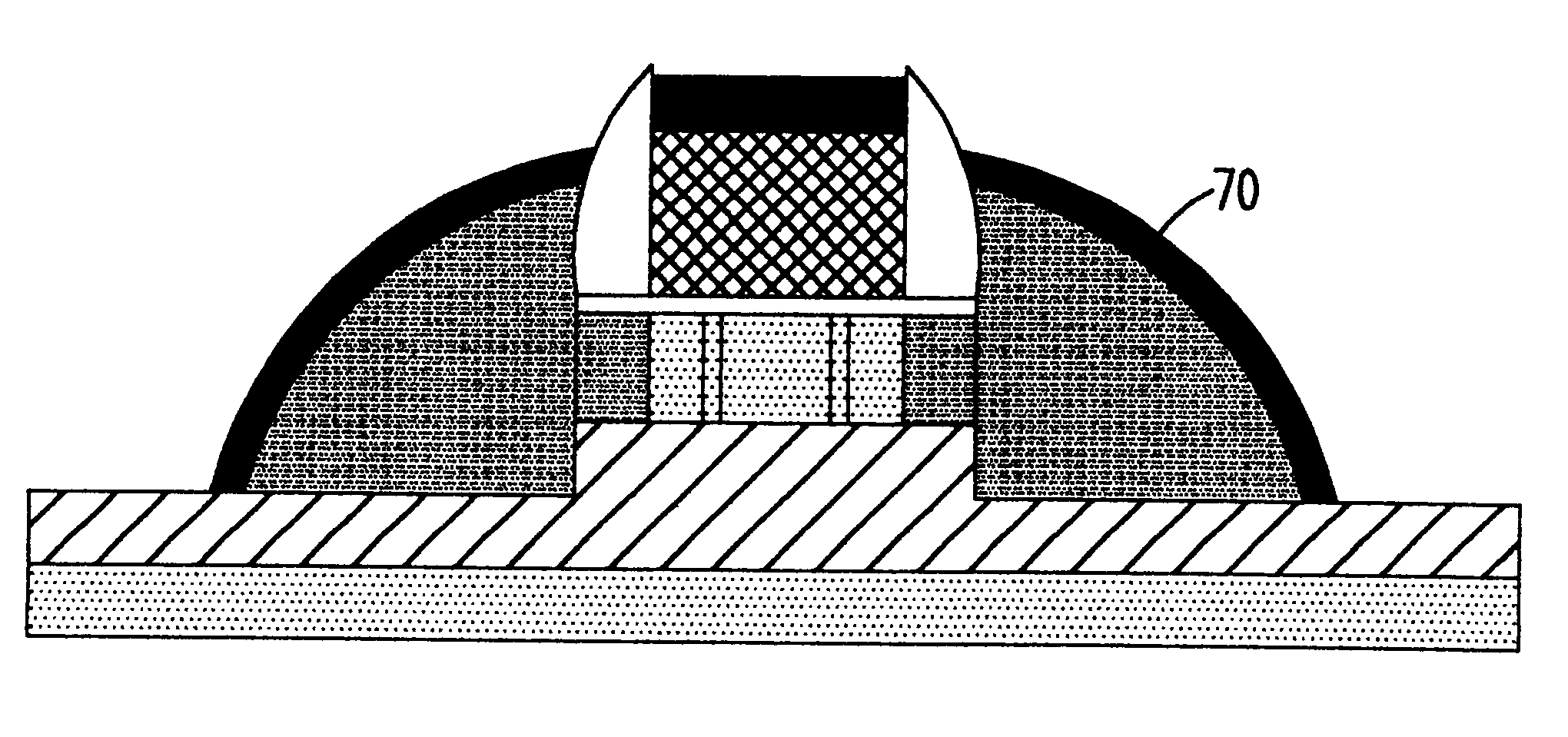

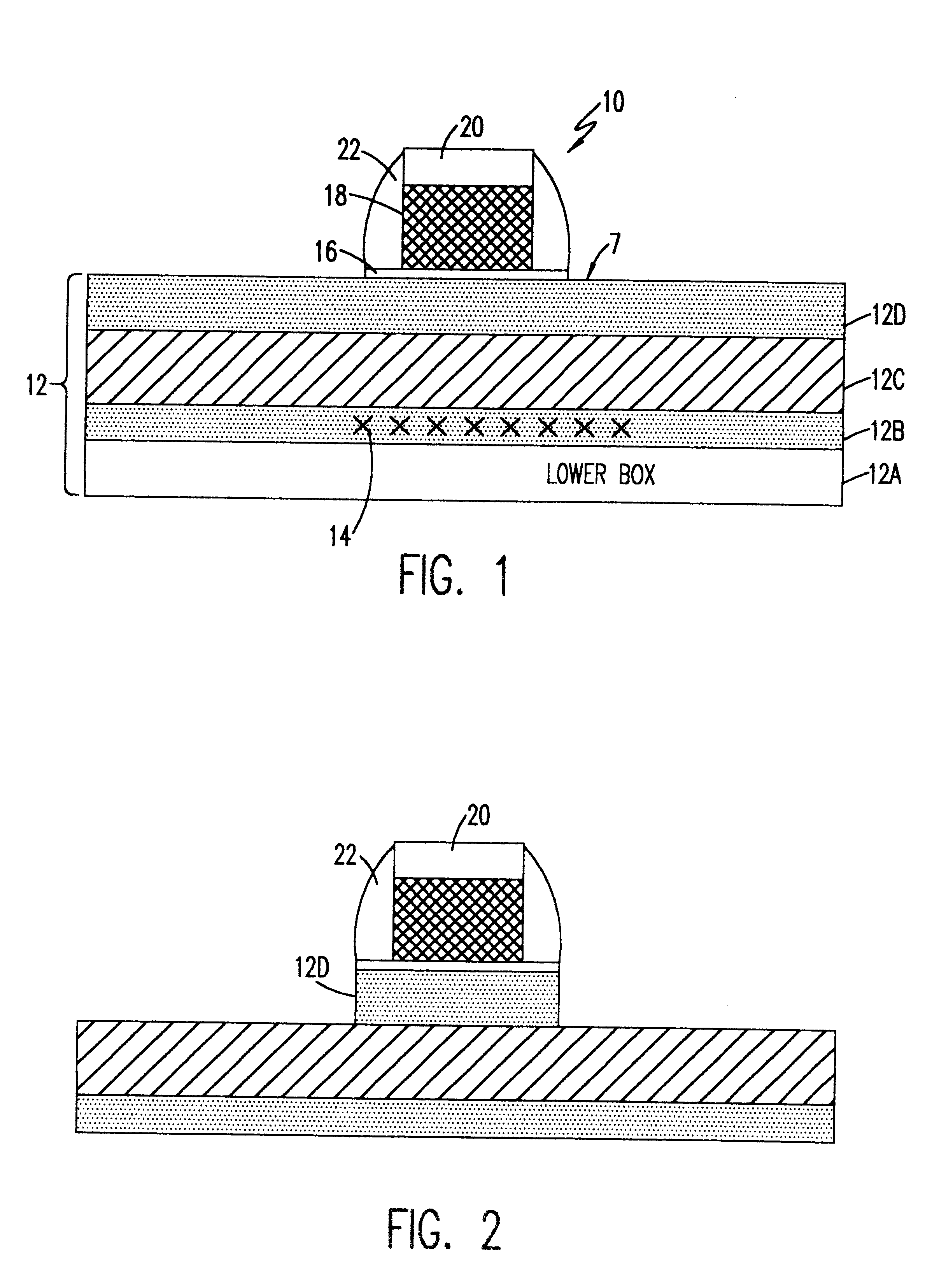

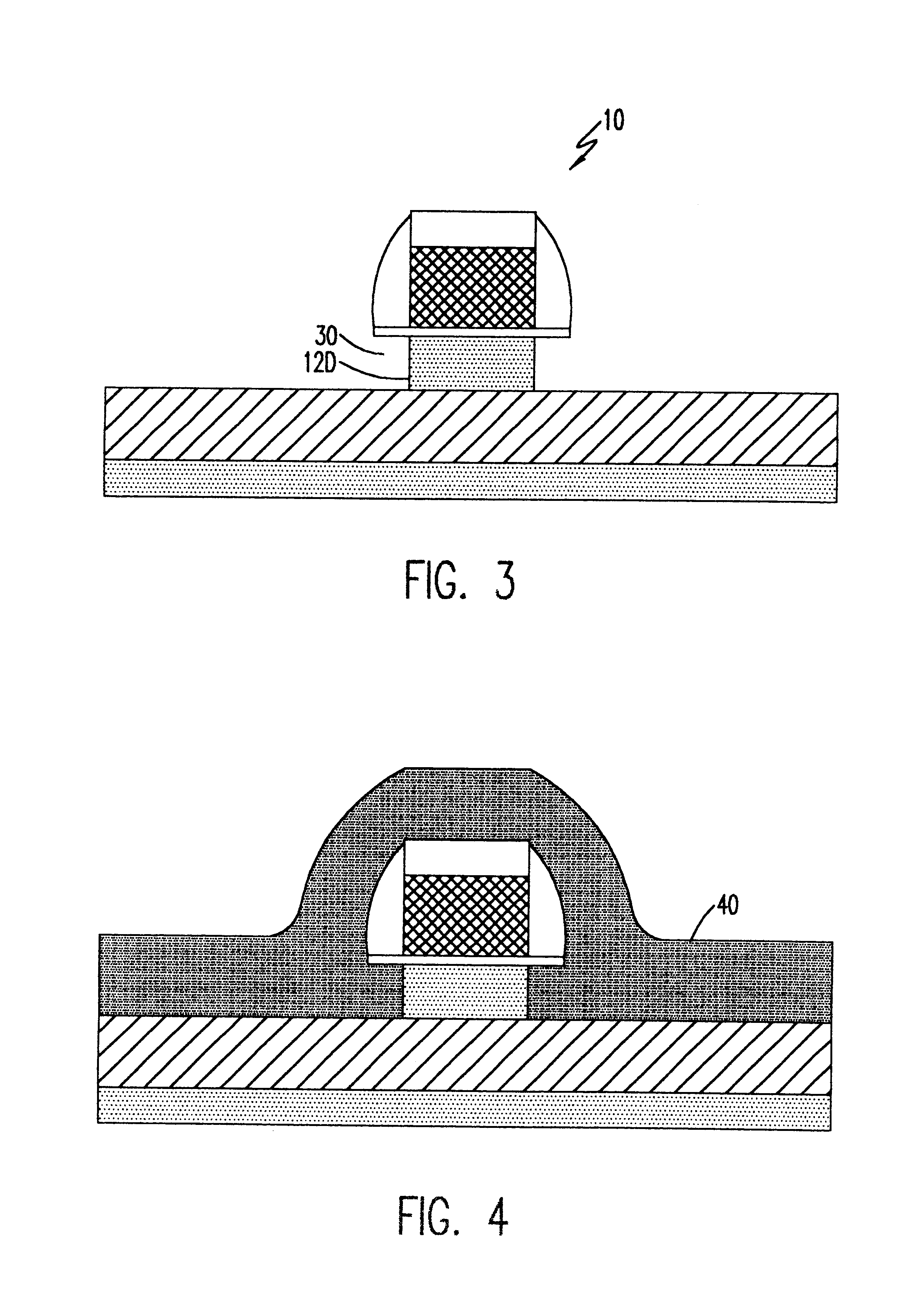

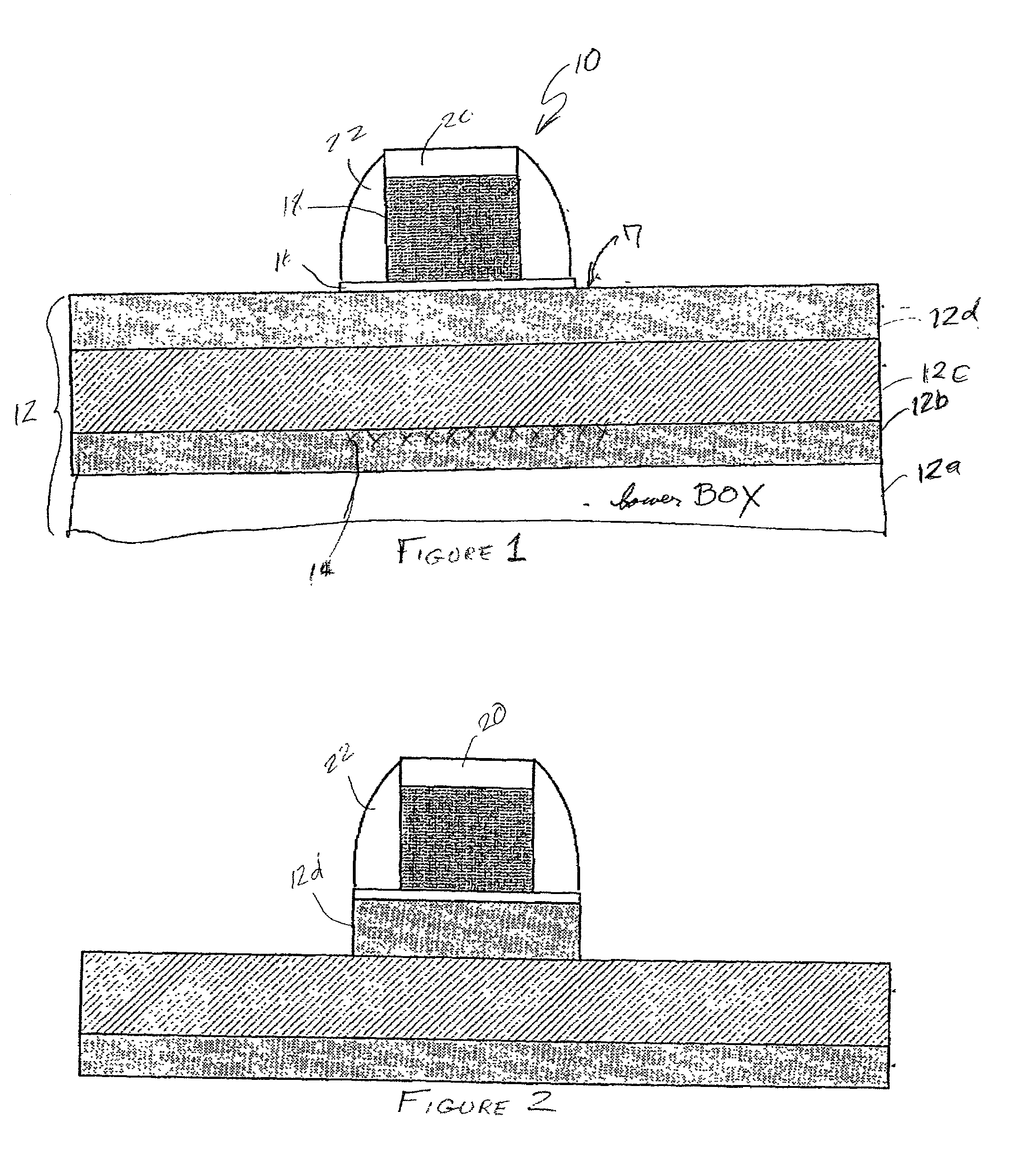

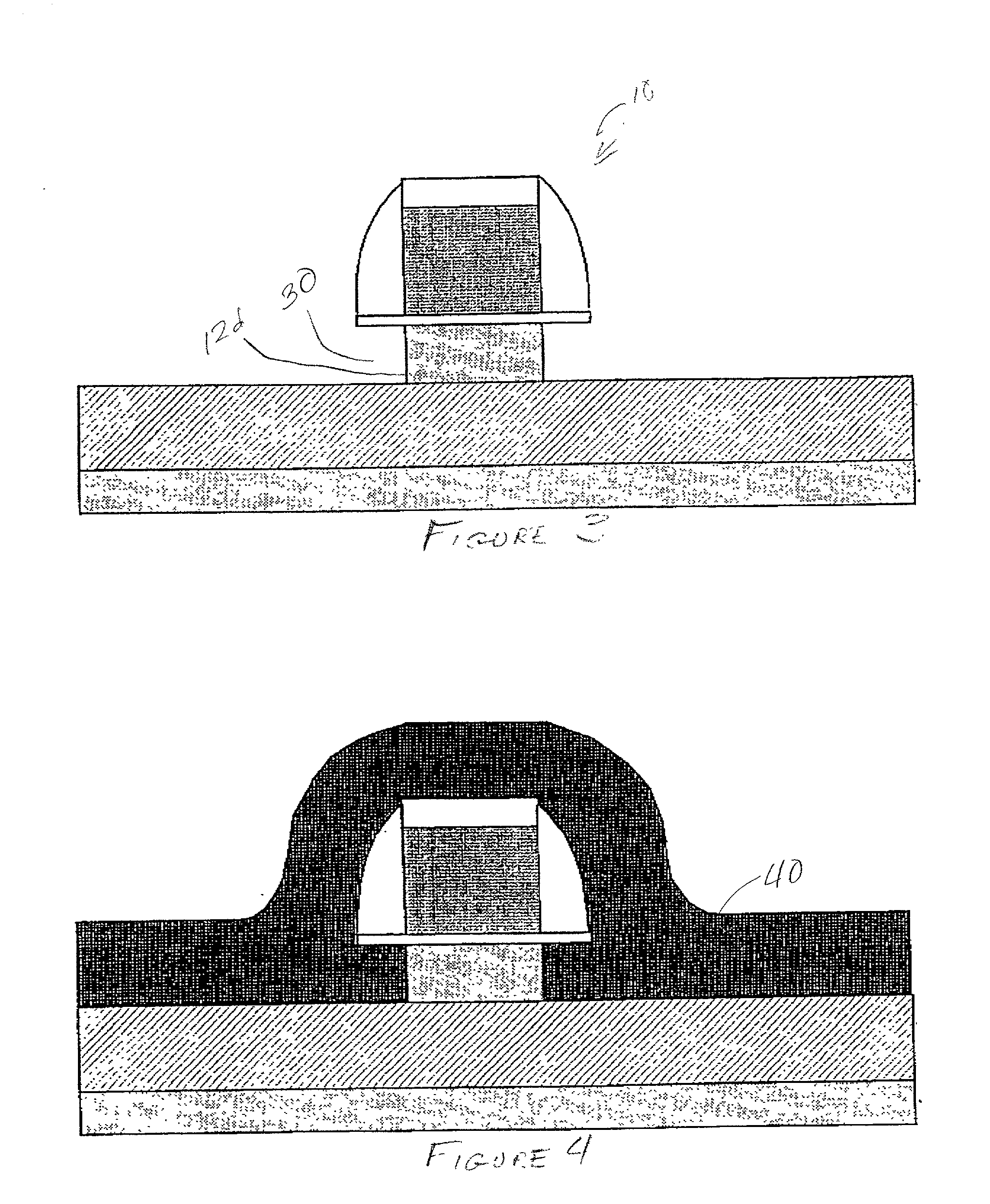

SOI transistor with polysilicon seed

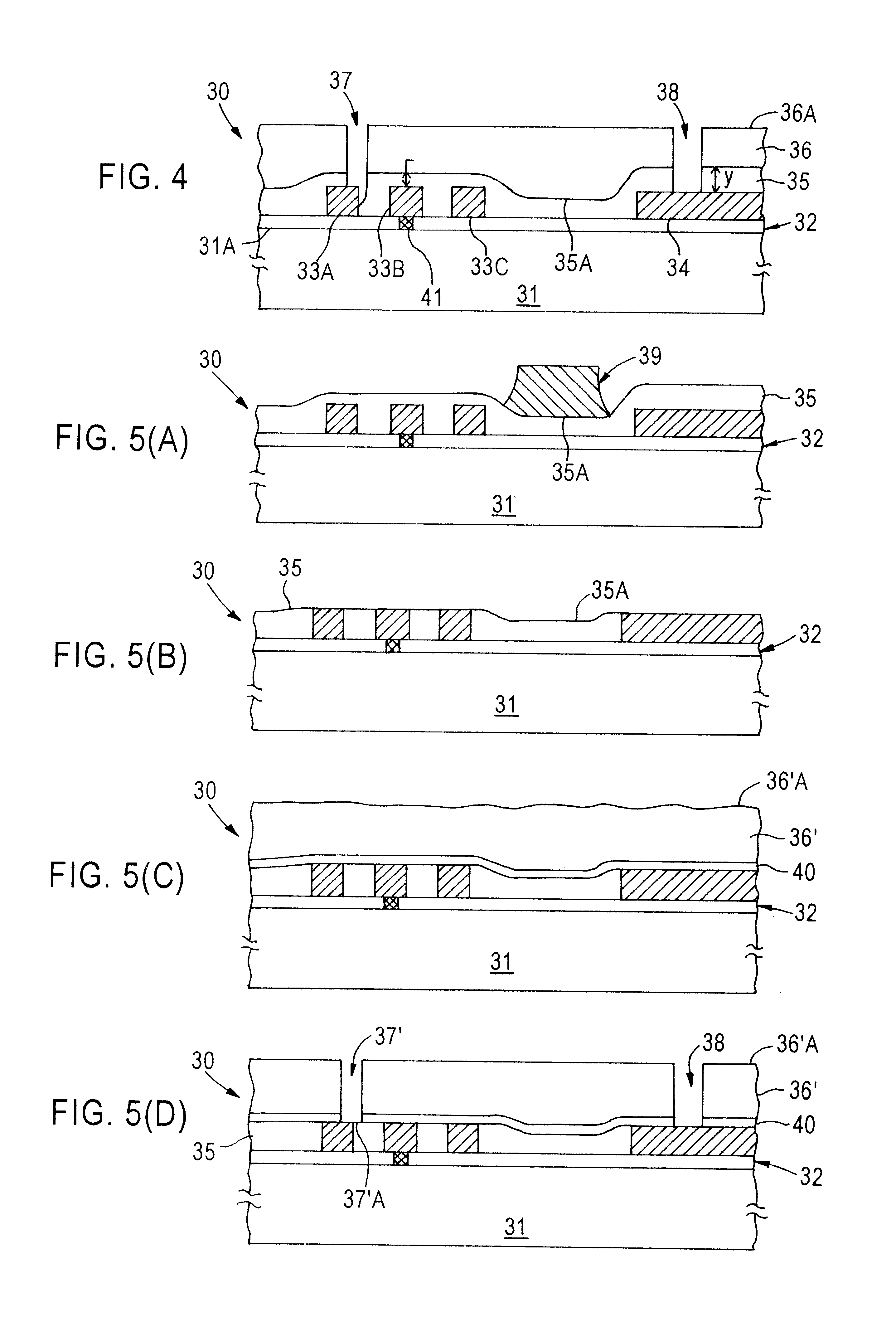

InactiveUS6521949B2High density integrationHigh precisionTransistorSolid-state devicesPath lengthConcentration gradient

Short channel effects are effectively suppressed by steep impurity concentration gradients which can be placed with improved accuracy of location and geometry while relaxing process tolerances by implanting impurities in a polysilicon seed adjacent a conduction channel of a transistor and diffusing impurities therefrom into the conduction channel. The polysilicon seed also allows the epitaxial growth of polysilicon source / drain contacts therefrom having a configuration which minimizes current density and path length therein while providing further mechanical advantages.

Owner:GLOBALFOUNDRIES US INC

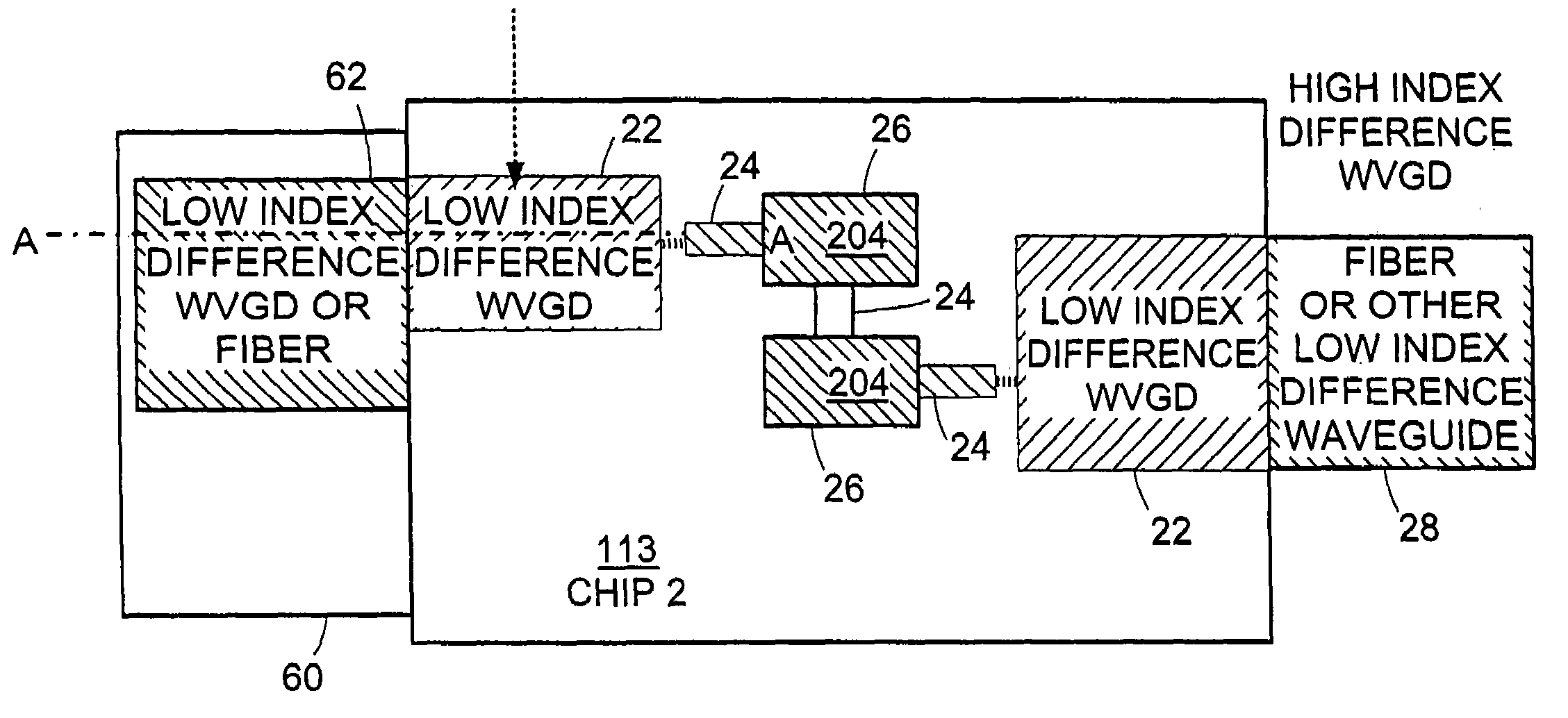

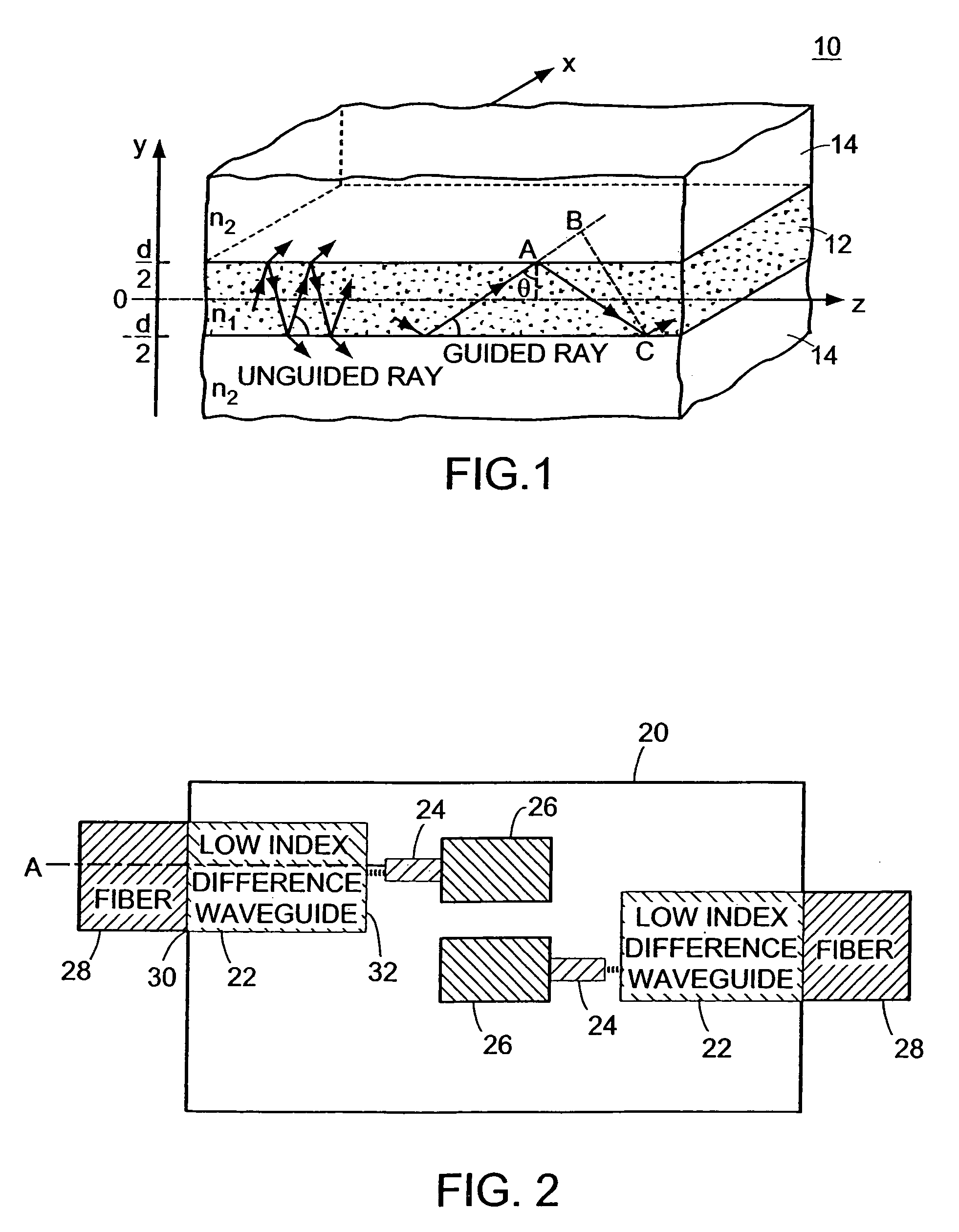

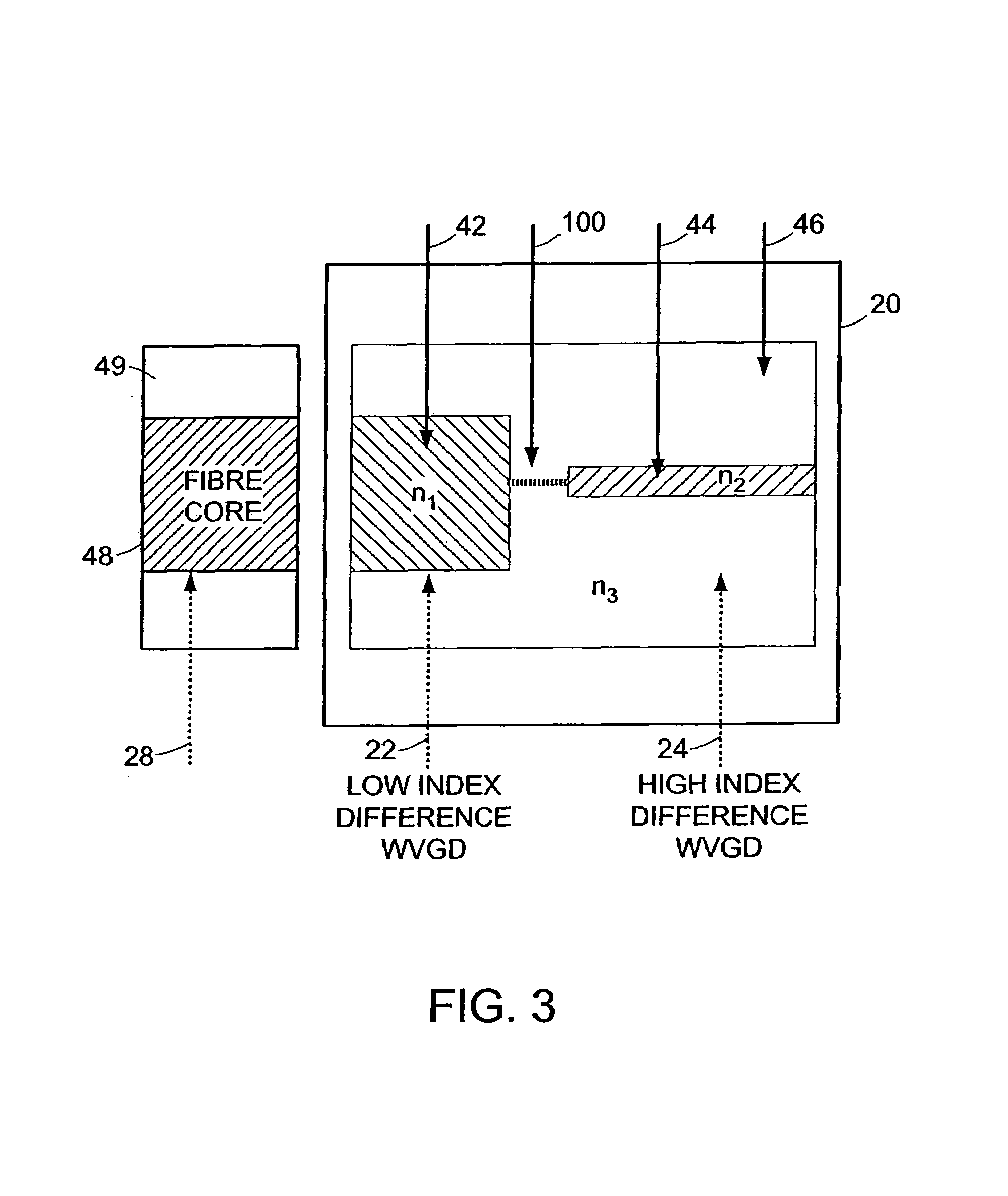

High density integrated optical chip

InactiveUS7103245B2High density integrationSmall footprintCoupling light guidesOptical waveguide light guideElectricityDielectric

A high density integrated optical chip. The optical chip features an optical function connected to a low minimum bending radius dielectric waveguide, and a large mode field size dielectric waveguide to interface with an external optical device, such as an optical fiber. The large mode field size dielectric waveguide is optically connected to the low minimum bending radius dielectric waveguide on the optical chip.

Owner:MASSACHUSETTS INST OF TECH

Flash memory cell, flash memory device and manufacturing method thereof

InactiveUS7087950B2High density integrationReducing parasitic coupling noiseTransistorSolid-state devicesDielectric layerSilicon

Owner:POLARIS INNOVATIONS LTD

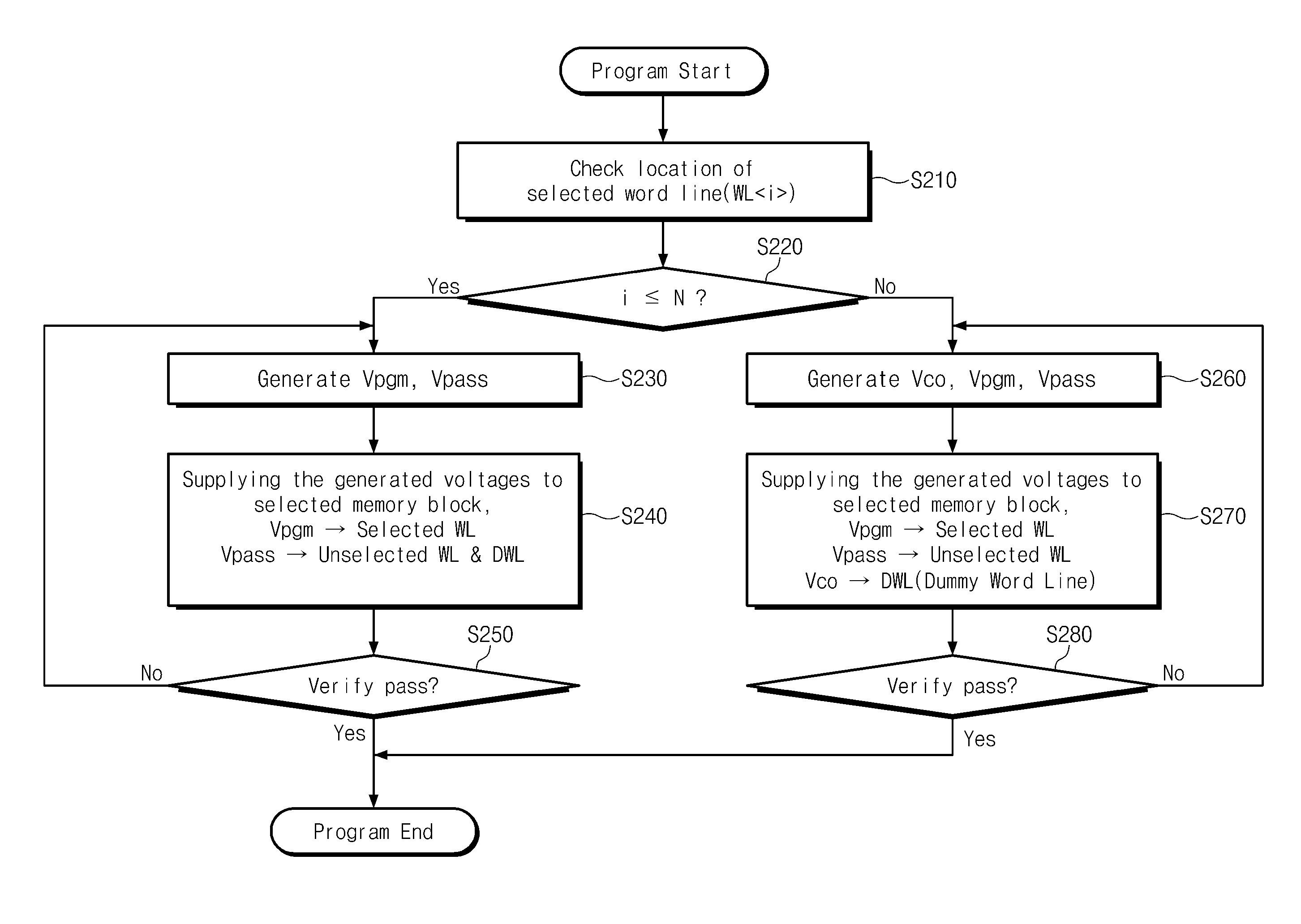

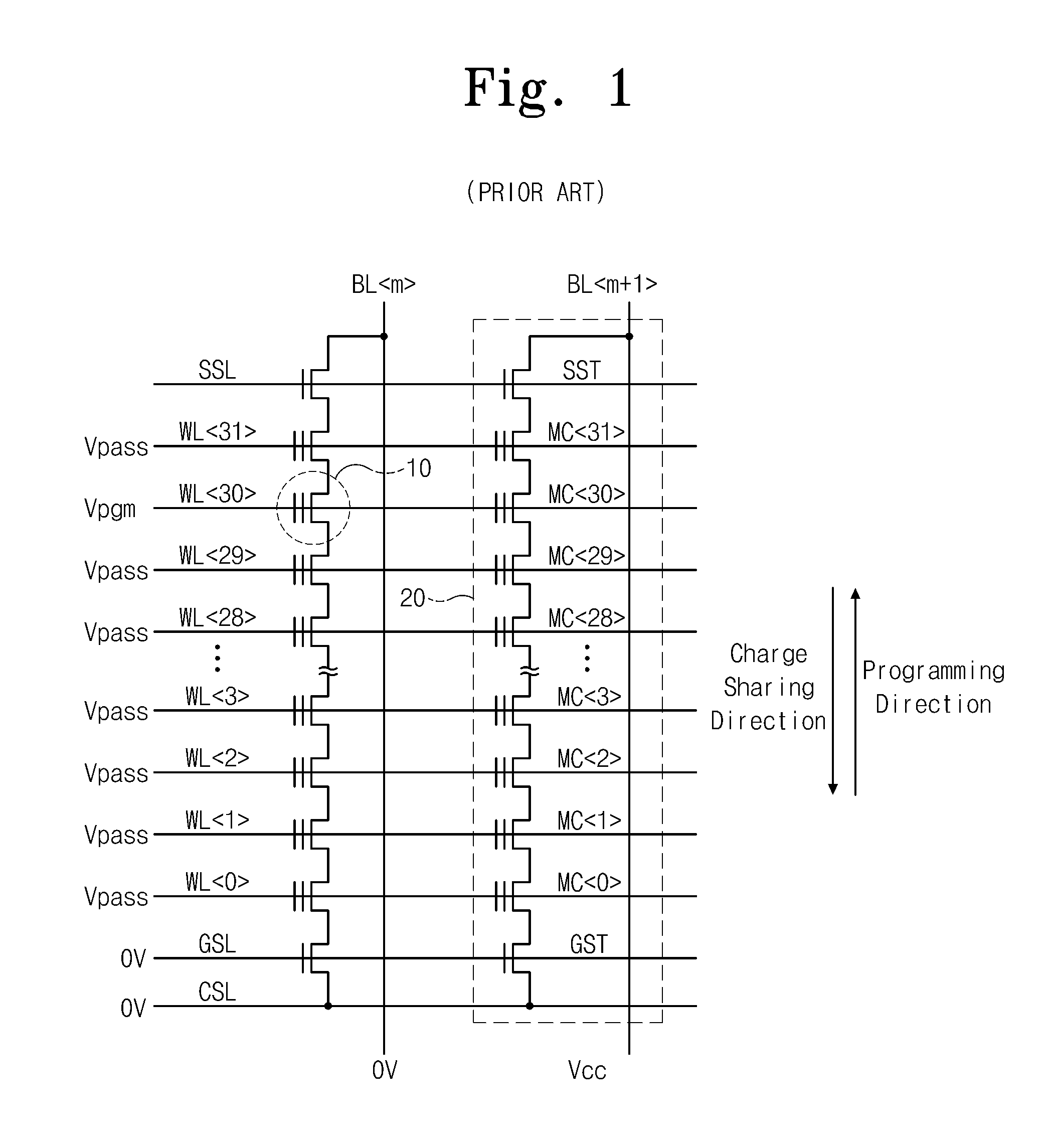

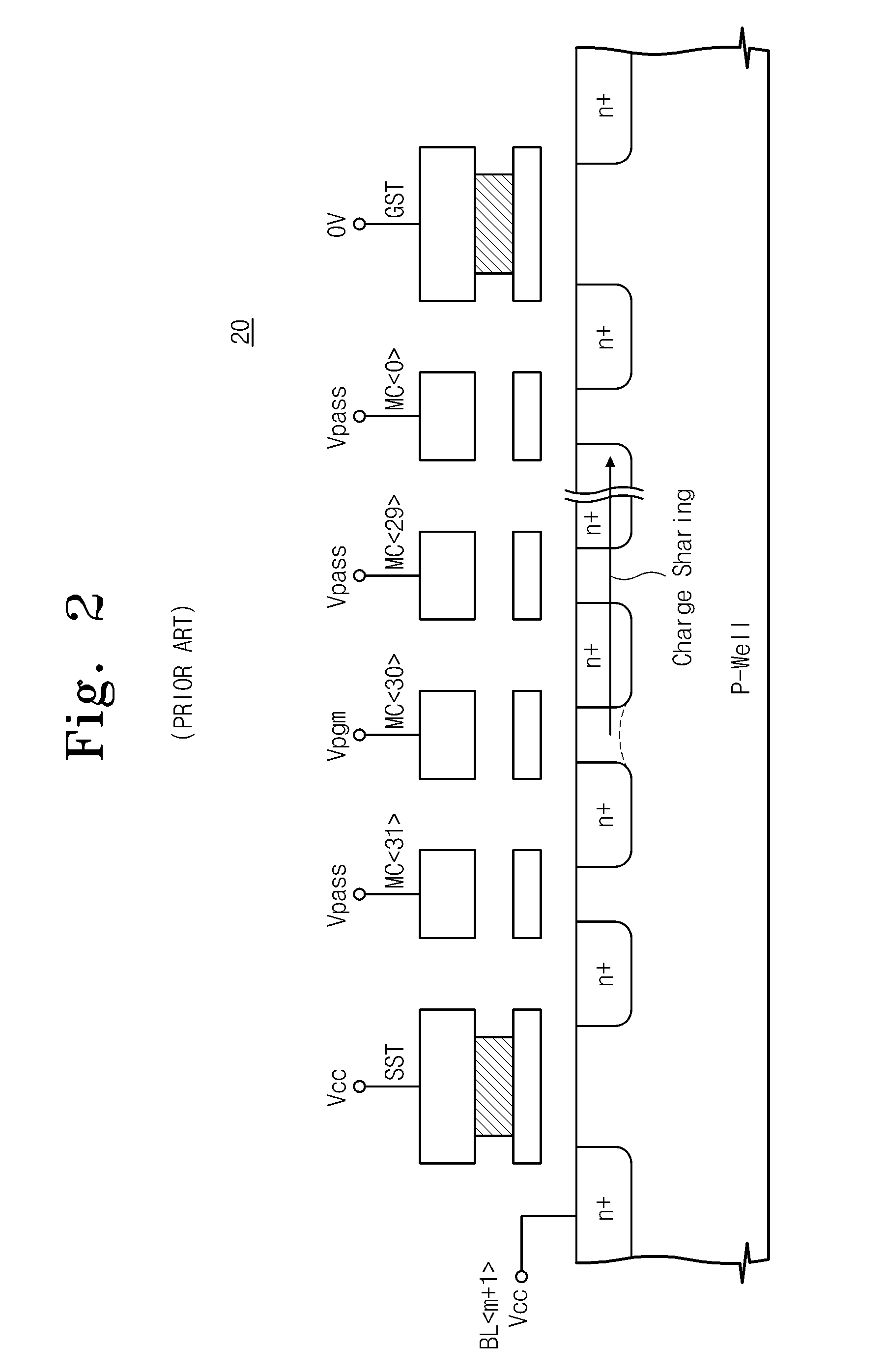

Flash memory device including a dummy cell

ActiveUS20090180317A1Raise the possibilityIncrease capacitanceRead-only memoriesDigital storageBit lineVirtual cell

A non-volatile memory device includes a selection transistor coupled to a bit line. The device also includes a plurality of memory cells serially coupled to the selection transistor and at least one dummy cell located between the plurality of memory cells. The dummy cell is turned off during a programming operation of a memory cell located between the dummy cell and the selection transistor.

Owner:SAMSUNG ELECTRONICS CO LTD

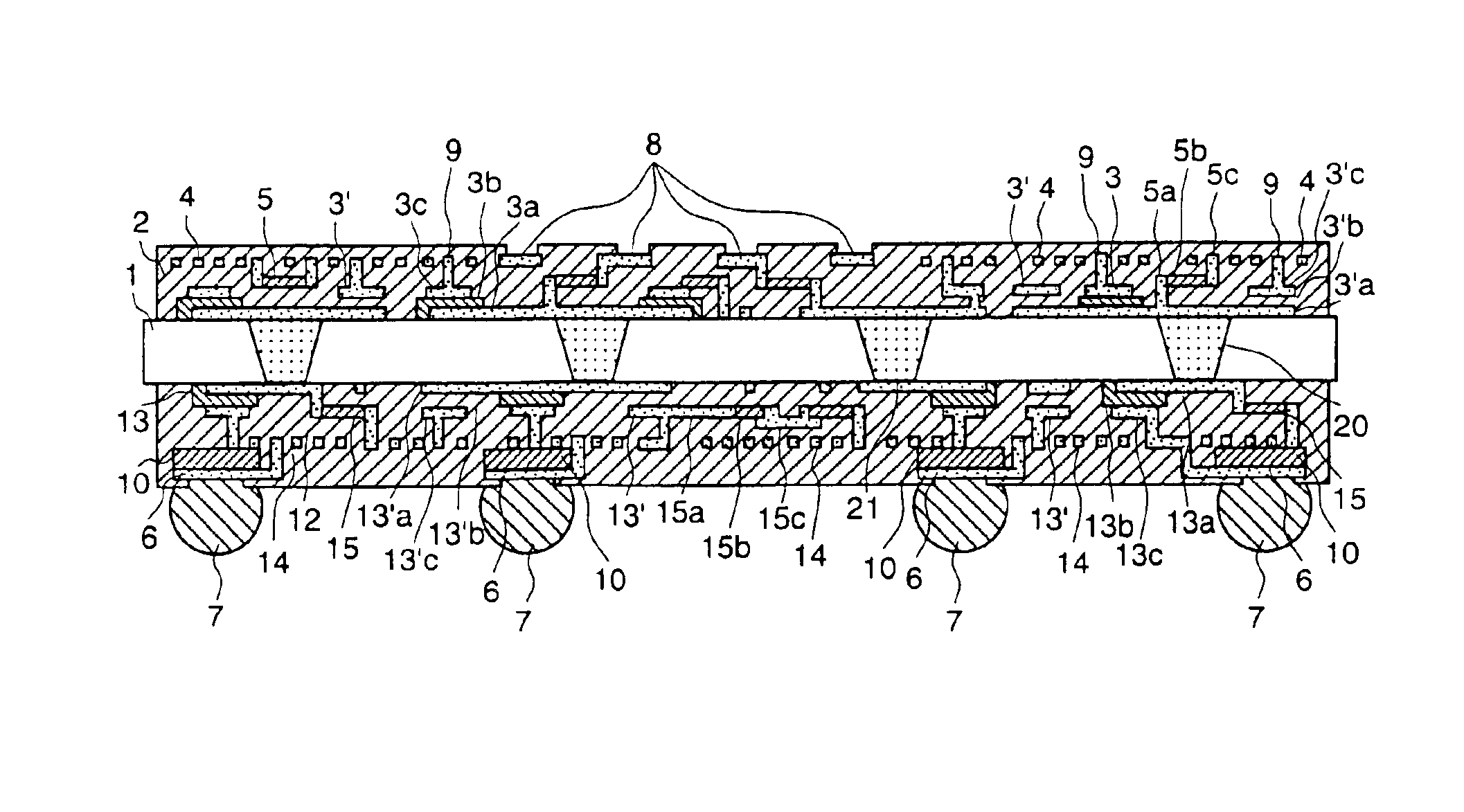

Optoelectronic integrated circuit board and communications device using the same

InactiveUS7680367B2Precise positioningHigh refractive indexLaser detailsCircuit optical detailsRefractive indexOpto electronic

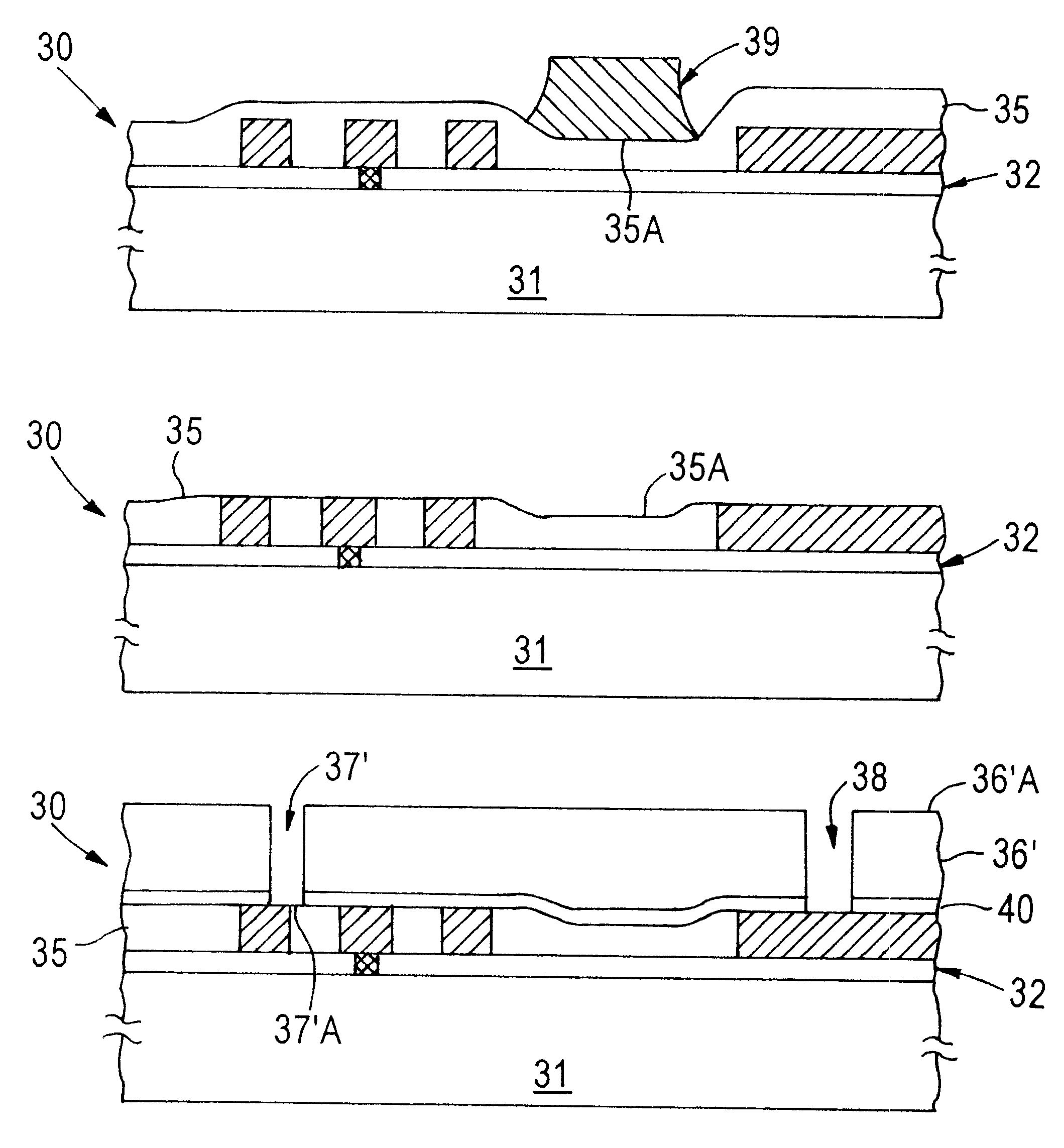

In the optical connection between multi-layered optical waveguides and photoelectric converting elements or optical waveguide array connectors formed on a substrate, the optical coupling efficiency is to be prevented from degrading due to deviation of the optical axis positions between optical elements and the optical waveguide layers that is caused by a radiation due to a beam expansion or by a deviation of positioning layers in producing the optical waveguides. There are stacked, on a substrate, optical waveguide layers, each of which comprises a clad layer and a core having a higher refractive index than the clad layer, and optical elements formed on the uppermost optical waveguide layer. The optical elements are positioned such that they correspond to the optical path conversion mirrors of the cores of the underlaying optical waveguide layer. The light transmission / reception between the optical elements and the optical path conversion mirrors of the cores of the underlaying optical waveguide layer is performed via the cores of overlying optical waveguide layer.

Owner:RESONAC CORPORATION

Semiconductor connection substrate

InactiveUS6933601B2Desirable manufacturing yieldHigh density integrationSemiconductor/solid-state device detailsPrinted circuit aspectsInductorInductance

A semiconductor connection substrate which connects a semiconductor element to a mounting substrate such as a printed substrate comprises an insulator substrate, a plurality of electrodes having different areas provided on the insulator substrate, one or more elements selected from a capacitor element of dielectric material sandwiched between the electrodes, an inductor element and resistor element, a metal wiring connecting the elements, a metal terminal part of part of the metal wiring and an organic insulator material covering the elements and the circumference of the metal wiring portion excluding the metal terminal portion.

Owner:RENESAS ELECTRONICS CORP

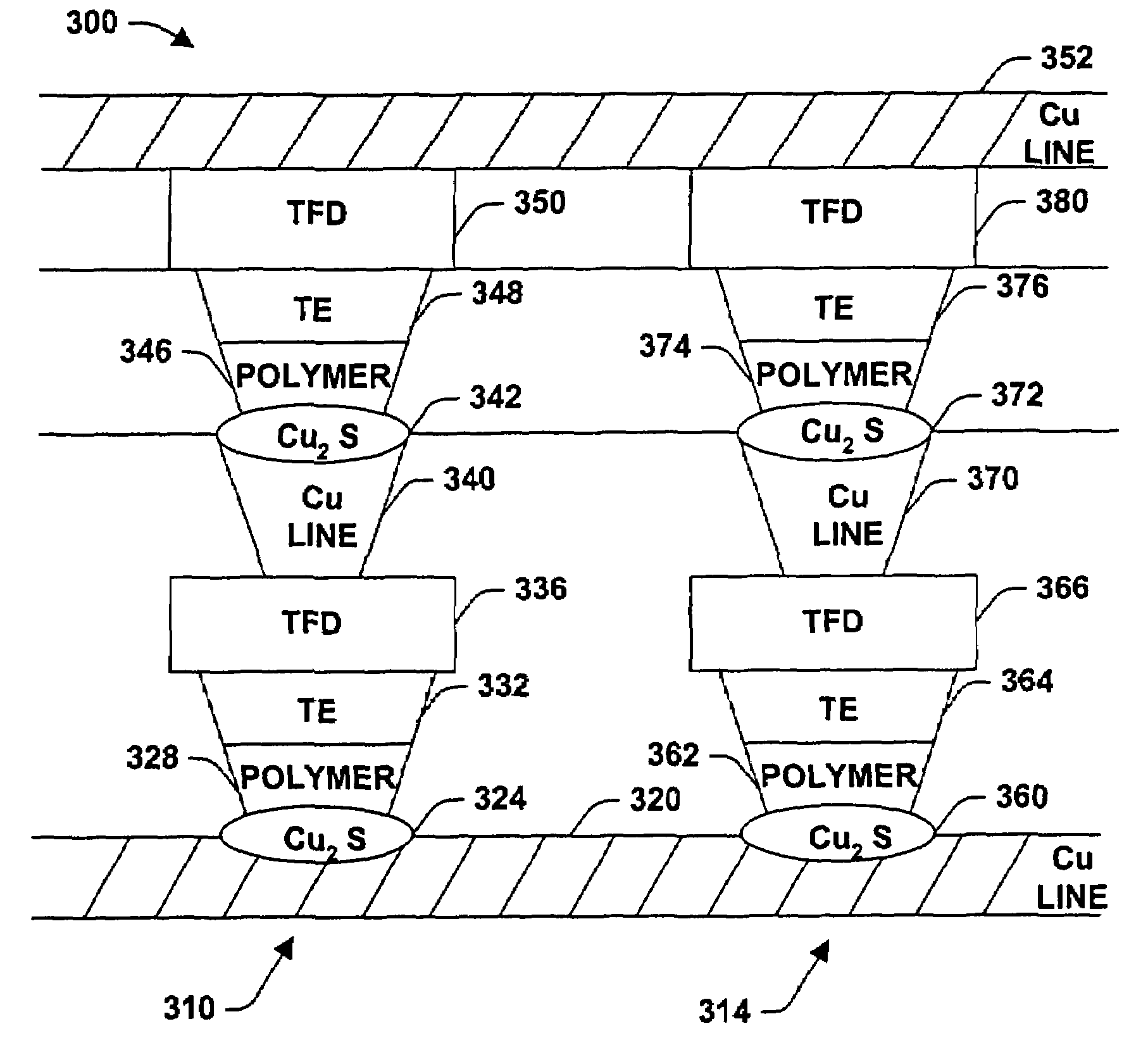

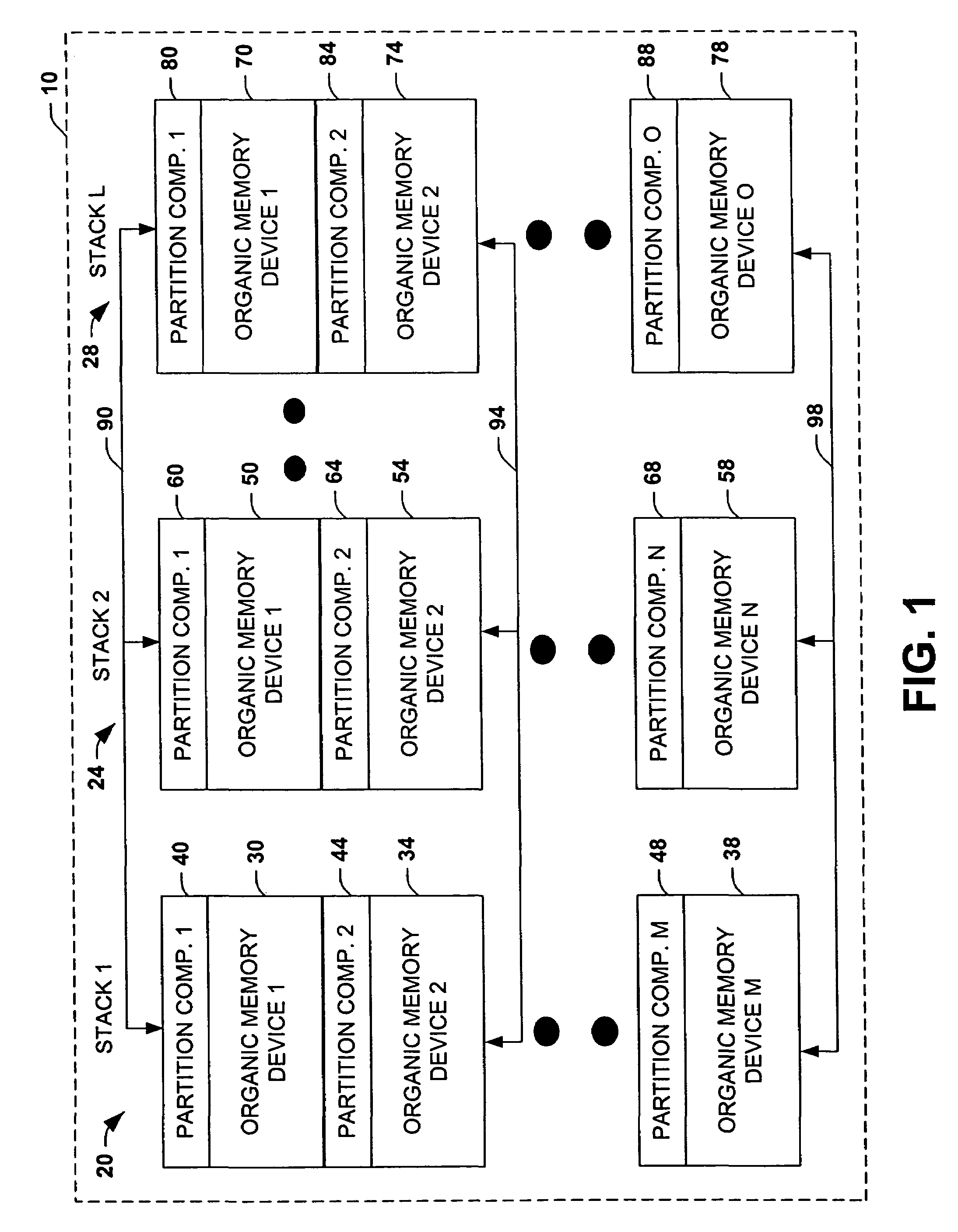

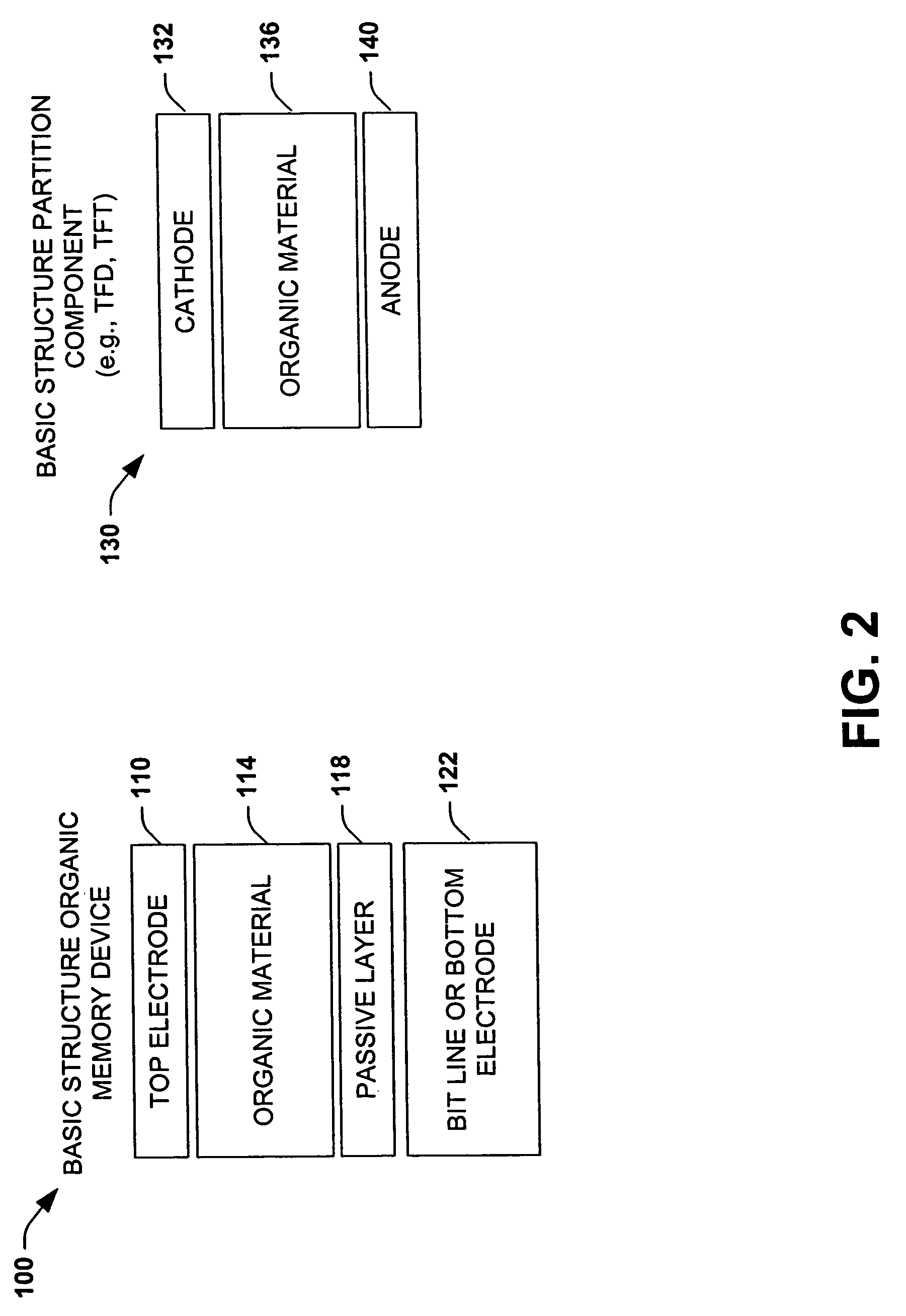

Stacked organic memory devices and methods of operating and fabricating

InactiveUS6979837B2Easy to stackEasy constructionNanoinformaticsSolid-state devicesOrganic memoryHigh density

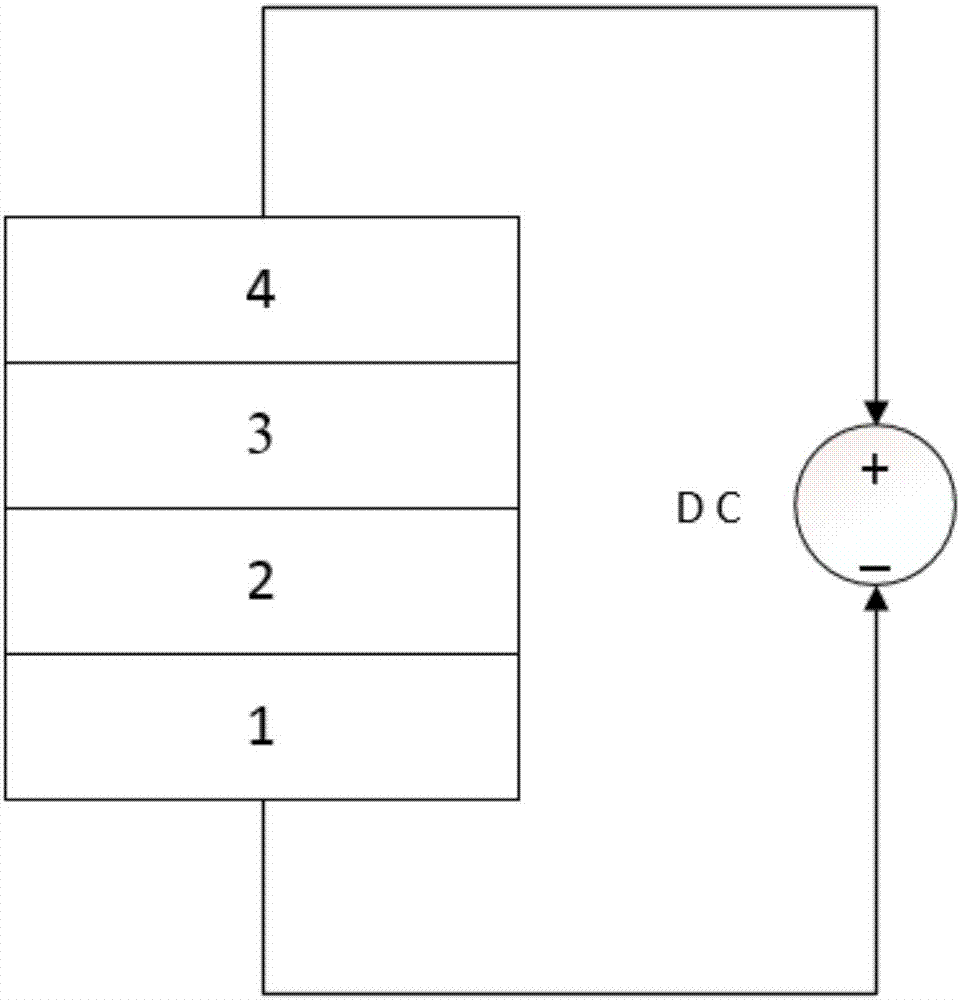

The present invention provides a multi-layer organic memory device that can operate as a non-volatile memory device having a plurality of stacked and / or parallel memory structures constructed therein. A multi-cell and multi-layer organic memory component can be formed with two or more electrodes having a selectively conductive media between the electrodes forming individual cells, while utilizing a partitioning component to enable stacking of additional memory cells on top of or in association with previously formed cells. Memory stacks can be formed by adding additional layers—respective layers separated by additional partitioning components, wherein multiple stacks can be formed in parallel to provide a high-density memory device.

Owner:MONTEREY RES LLC

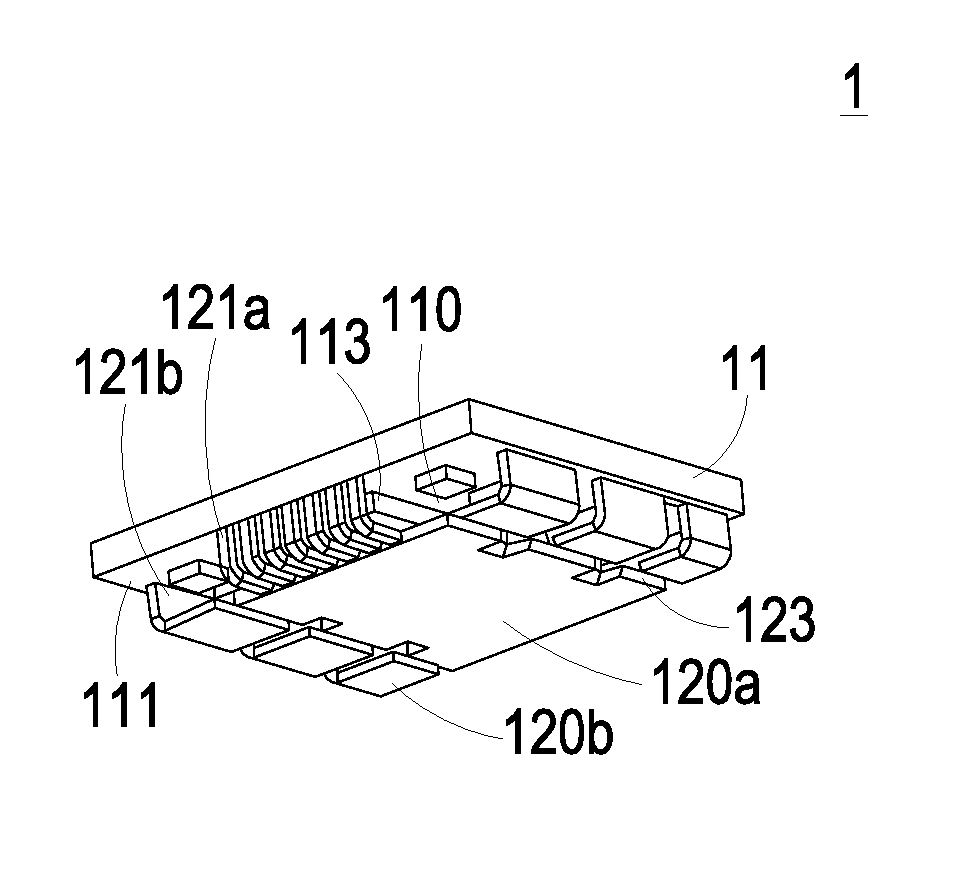

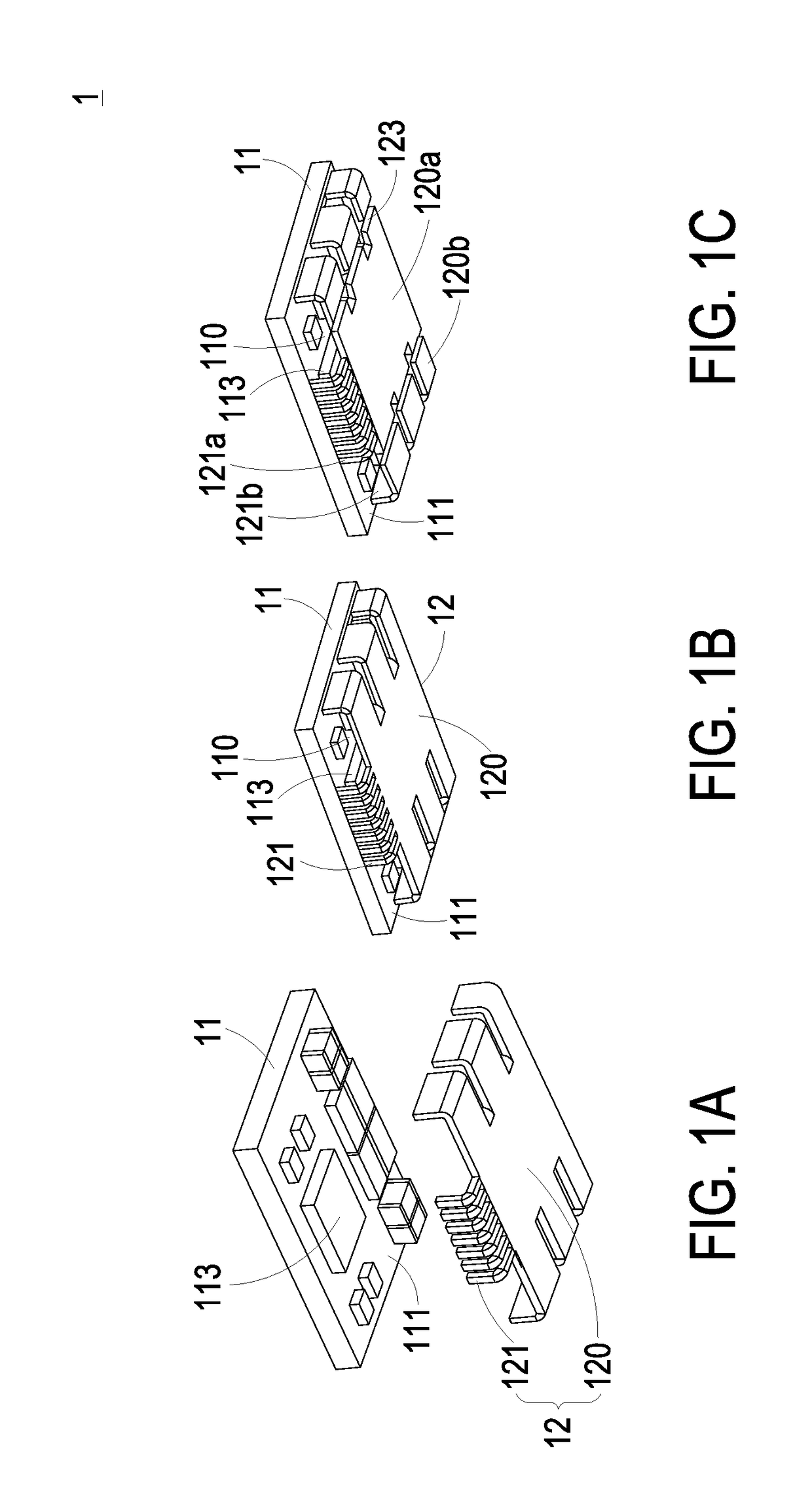

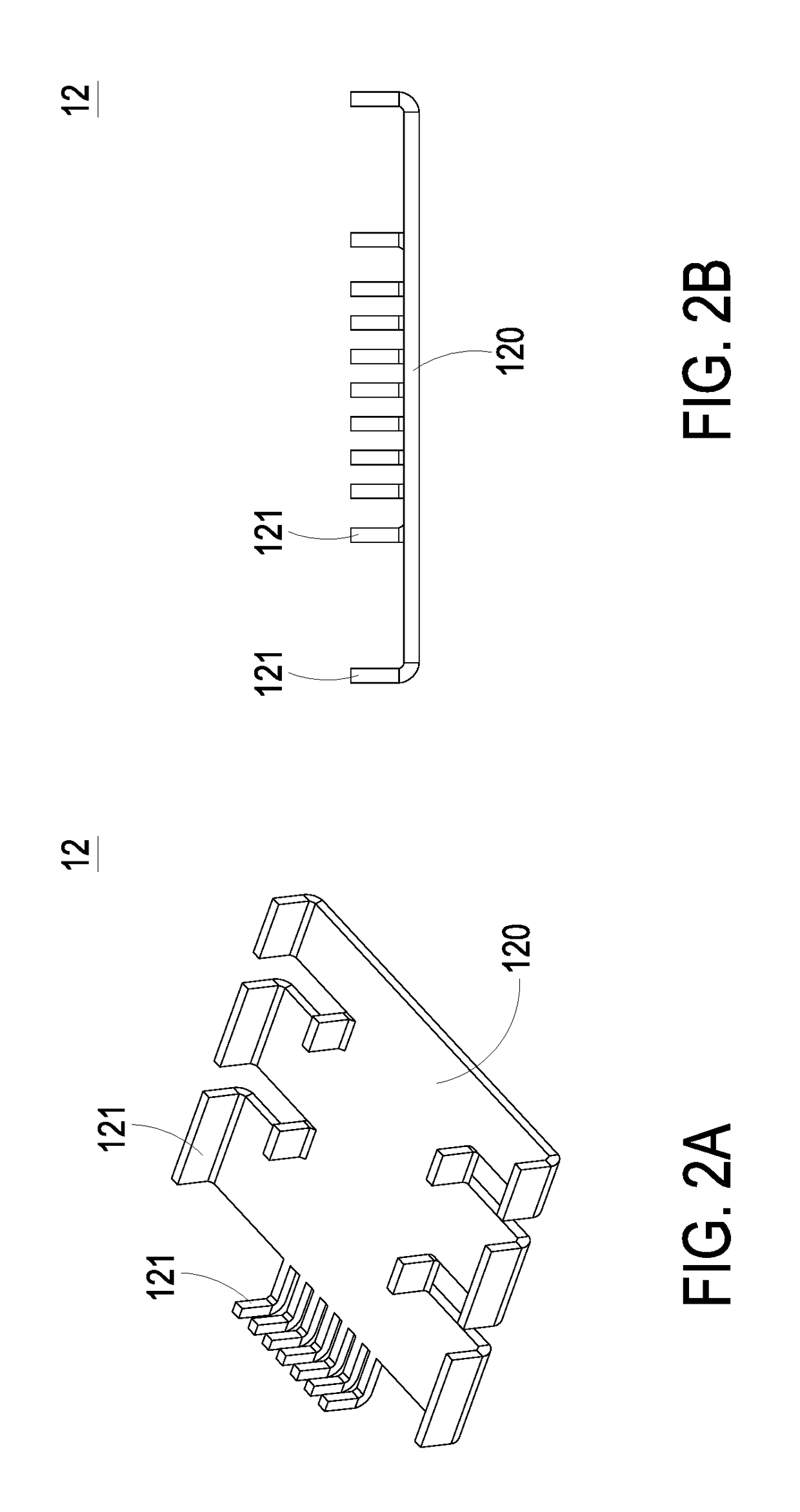

Power module with lead component and manufacturing method thereof

ActiveUS20180124922A1High-density integrationReduced footprint and volumePrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringPower module

The present invention provides a power module and a manufacturing method thereof. The power module includes a carrier board and a lead component stacked relative to the carrier board. The lead component includes an initial plane, plural first pins and plural second pin. The initial plane includes a vertical projection overlapping with the carrier board. The first pins are electrically connected to the carrier board and vertical to the initial plane. The second pins are electrically connected to the carrier board and vertical to the initial plane. An isolation gap is disposed in the initial plane and located between the first pins and the second pins. The initial plane is separated into a first plane and a second plane by the isolation gap, so as to electrically isolate the first pins and the second pins from each other.

Owner:DELTA ELECTRONICS INC

Pyroelectric infrared detector for planarization thermal isolation structure and method for making same

ActiveCN101419092AImprove performanceImprove yieldPyrometry using electric radation detectorsThermal isolationCMOS

The invention discloses a pyroelectric infrared detector provided with a planarized heat-insulated structure and a preparation method thereof. The pyroelectric infrared detector comprises a substrate and the heat-insulated structure, wherein the heat-insulated structure is as follows: a deep notch of a corresponding figure of a lower electrode of a detector is etched on the silicon or sapphire substrate; a porous silicon dioxide layer is deposited inside the deep notch; and silicon dioxide layers or silicon nitride layers are deposited on the porous silicon dioxide layer and the substrate. The detector is easy to be integrated with other devices by means of single scale intergration, is favorable for high-density integration of detector units, has simple manufacturing technique and low processing cost, simultaneously greatly reduces the vertical height difference of steps of a mesa device structure, is easy to interconnect metals, reduces the difficulty of the processing technique of devices and the surface leakage current of the devices, improves the performance and the finished product rate of the pyroelectric infrared detector, and obviously improves the reliability of the devices. The detector provided with the structure is suitable for infrared-ultraviolet dual-range single scale intergration and manufacture of the infrared detector and a CMOS ROIC one chip integrated focal plane device.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

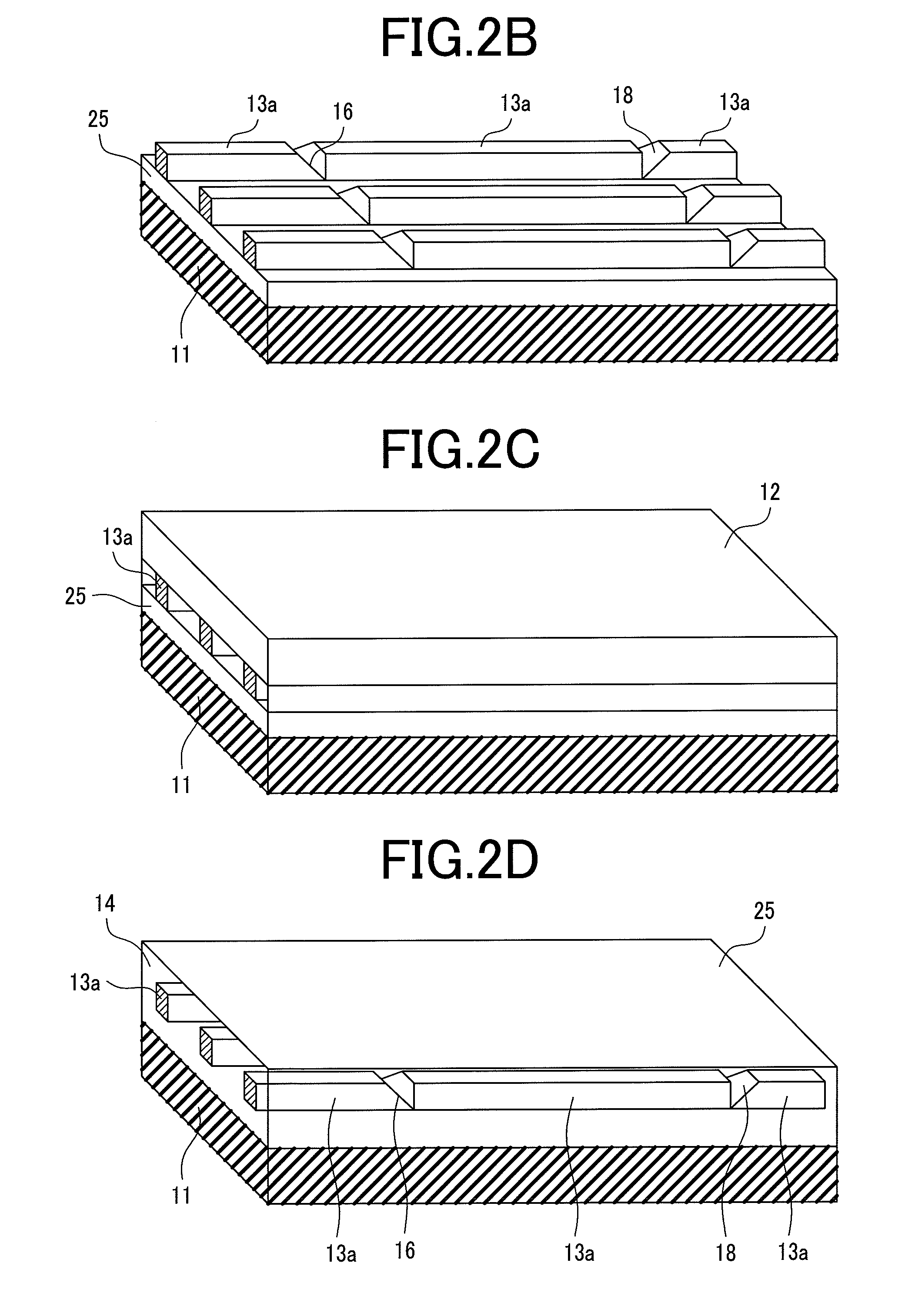

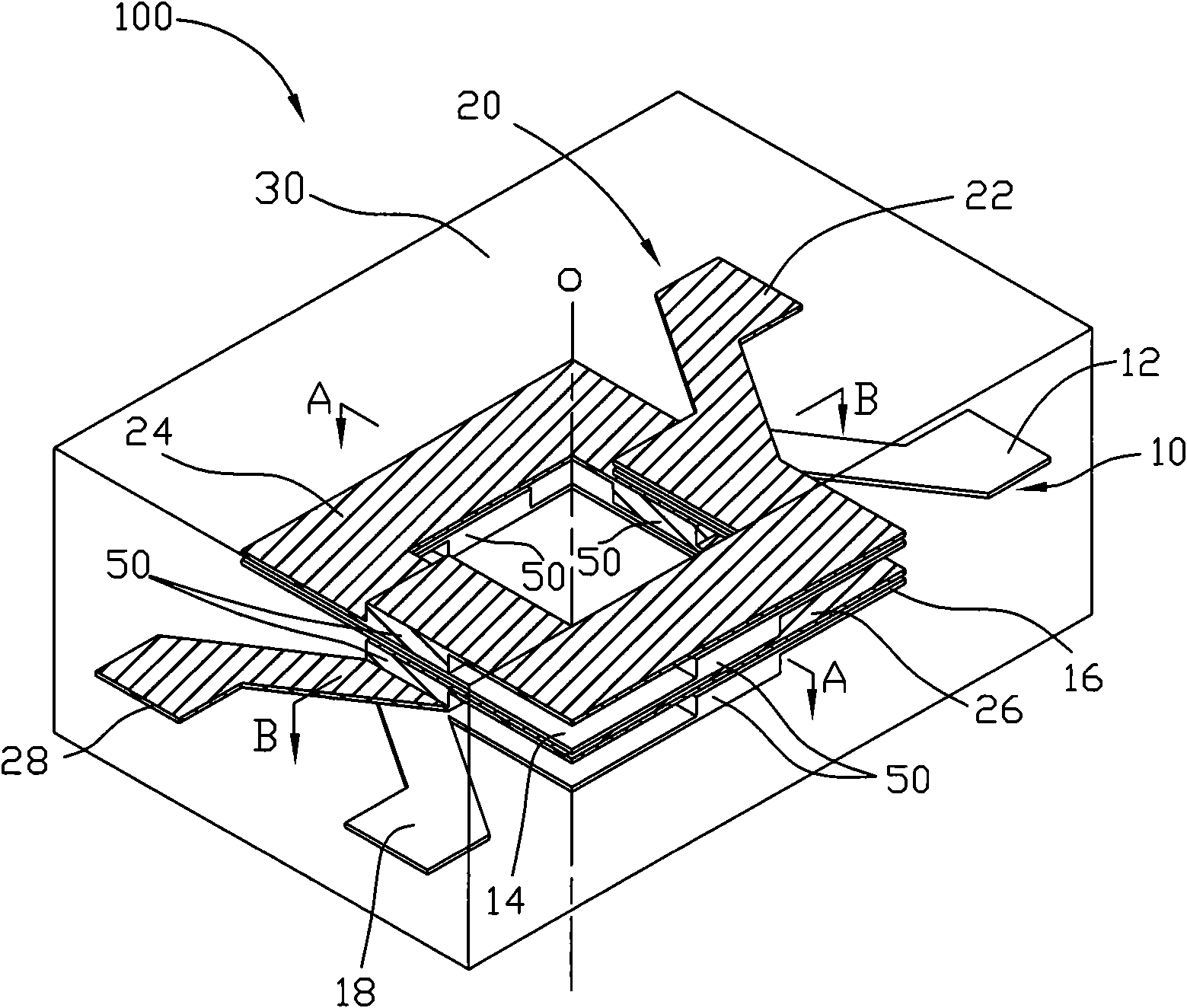

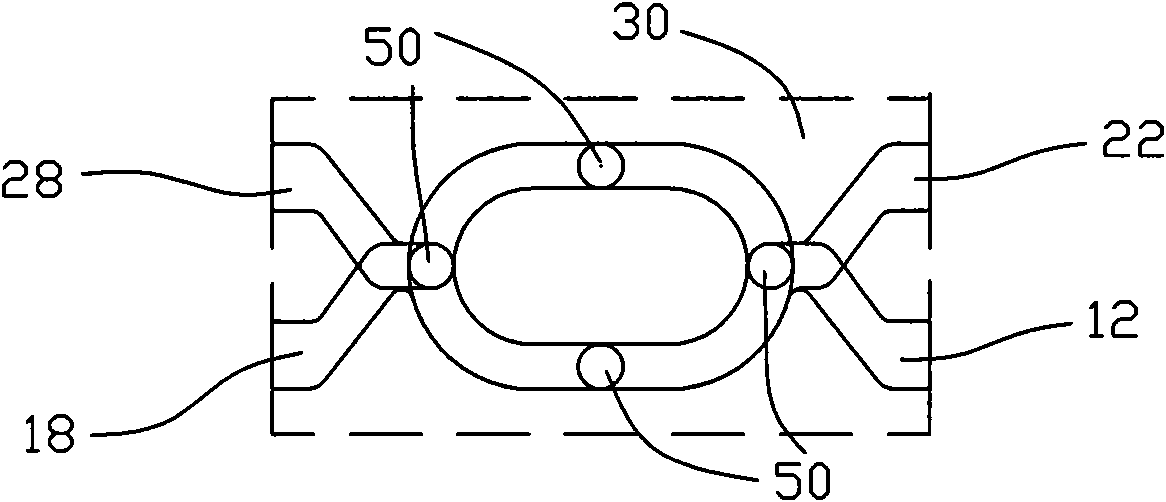

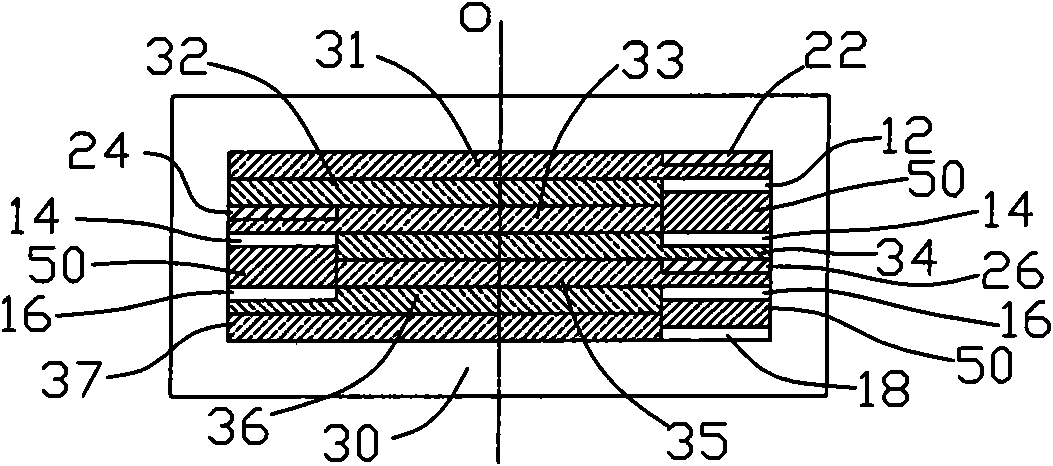

Lamination sheet type coil integration member and manufacturing method thereof

ActiveCN101556854ASmall sizeImprove space utilizationInductances/transformers/magnets manufactureCoilsForce factorHigh density

The invention provides a lamination sheet type coil integration member, comprising at least two coils and a plurality of insulating layers. Each coil comprises multi-layer electrode patterns connected layer upon layer in a spiral shape, the electrode pattern layers in different coils are embedded, staggered and overlapped with each other, the insulating layers are positioned between the adjacent electrode pattern layers in the different coils at intervals, and the adjacent electrode pattern layers in the same coil are electrically connected with each other by spanning the insulating layers positioned between the same. The invention also provides a forming method of the lamination sheet type coil integration member. The multi-layer electrode patterns of the two coils of the lamination sheet type coil integration member are embedded, staggered and overlapped with each other, thereby enhancing the utility ratio of space, the force factor of the coils and the integration density, being suitable for the requirement of the high-density assembly of a surface mounting technique and also being used for an inductance component, common mode signal inhibition, signal transformation, voltage change, and the like.

Owner:SHENZHEN ZHENHUA FU ELECTRONICS

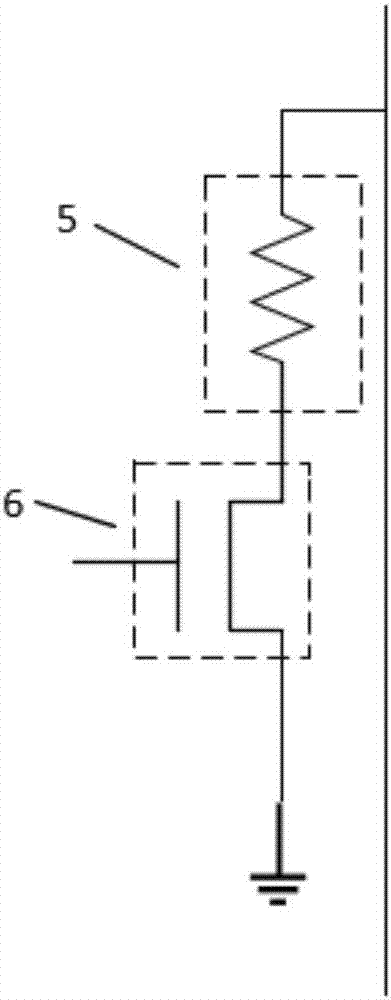

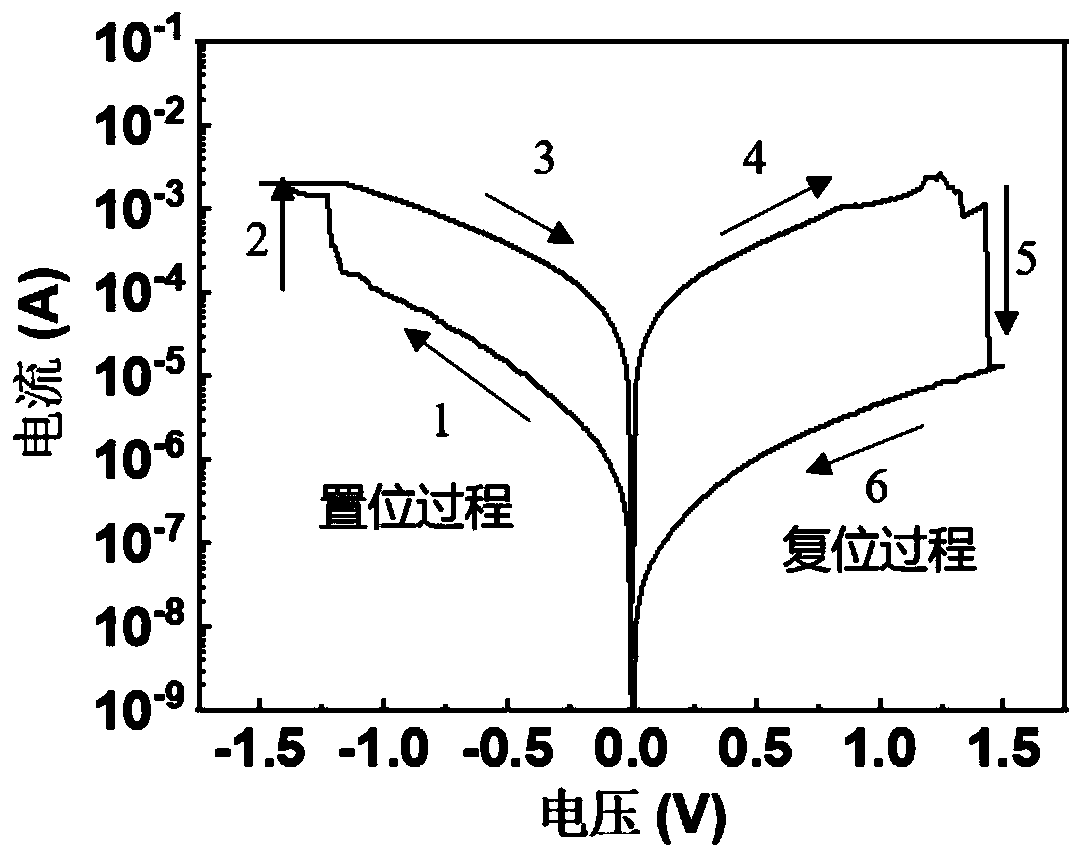

Phase change storage unit based on VOx gate tube

ActiveCN106992251AAchieve High Density StorageSimple preparation processElectrical apparatusDigital storagePhase-change memoryLow voltage

The invention discloses a phase change storage unit based on a VOx gate tube. The storage unit comprises a lower electrode layer, a VOx gating layer, a phase change function layer and an upper electrode layer. According to the invention, by use of the VOx, the gating of the phase change function layer is achieved; storage of the data is achieved on the basis of gating of the phase change function layer; by imposing voltage on the VOx, the state switching of the VOx is controlled, so an objective that the phase change storage unit is in a non-gating state during low voltage and in a gating system during high voltage can be achieved; through the switch control of the VOx, leakage current of the a phase change memory array can be effectively reduced and enough big Reset current is provided; a high-temperature technique condition is not required; preparation technique of the phase change memory is simplified; cost is reduced; and it is possible to commercialize the highly integrated phase change memory.

Owner:HUAZHONG UNIV OF SCI & TECH

Jet-printing head based on double-carbon nanotube microbubble generator and preparation method thereof

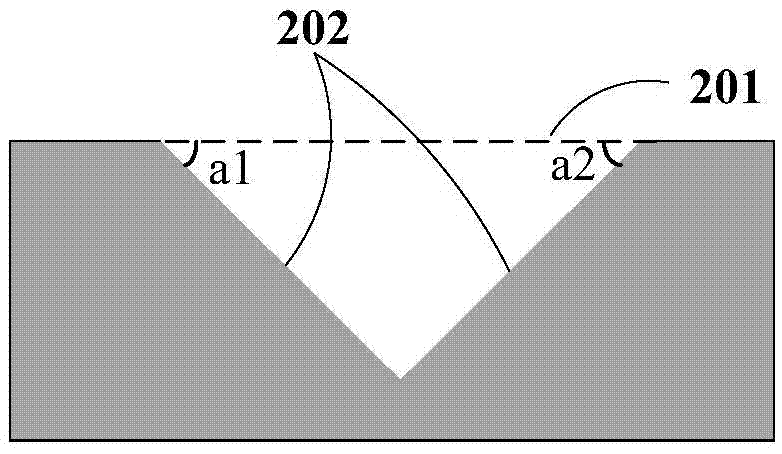

ActiveCN101817256AImprove integration densityReduce power consumptionPrintingCapillary channelMain channel

The invention discloses a jet-printing head based on a double-carbon nanotube microbubble generator and a preparation method thereof. The jet-printing head comprises a carbon nanotube microbubble generator and a microfluid structure comprising a main channel, a capillary channel, a microcavity and a nozzle. The carbon nanotube microbubble generator and the microfluid structure are manufactured independently. A jet-printing head structure is prepared by adopting the silicon surfacing and bulk silicon processing technologies, wherein the silicon surfacing technology mainly comprises steps of manufacturing figures by photoetching, manufacturing a masking film by a magnetron sputtering technology, etching the masking film by wet process, and the like; and the bulk silicon processing technology mainly comprises the step of manufacturing the microfluid structure by combining the wet etching and dry etching. The double-carbon nanotube microbubble generator and the microfluid structure are jointed by an ultraviolet curing bonding method to form the whole jet-printing head structure. The invention has very high spatial resolution and frequency response and very low power consumption, eliminates the problem of secondary droplets, effectively enhances the quality of jet-printing figures, and has favorable superintegration potential, thereby having side application prospect in the advanced manufacturing field.

Owner:HUAZHONG UNIV OF SCI & TECH

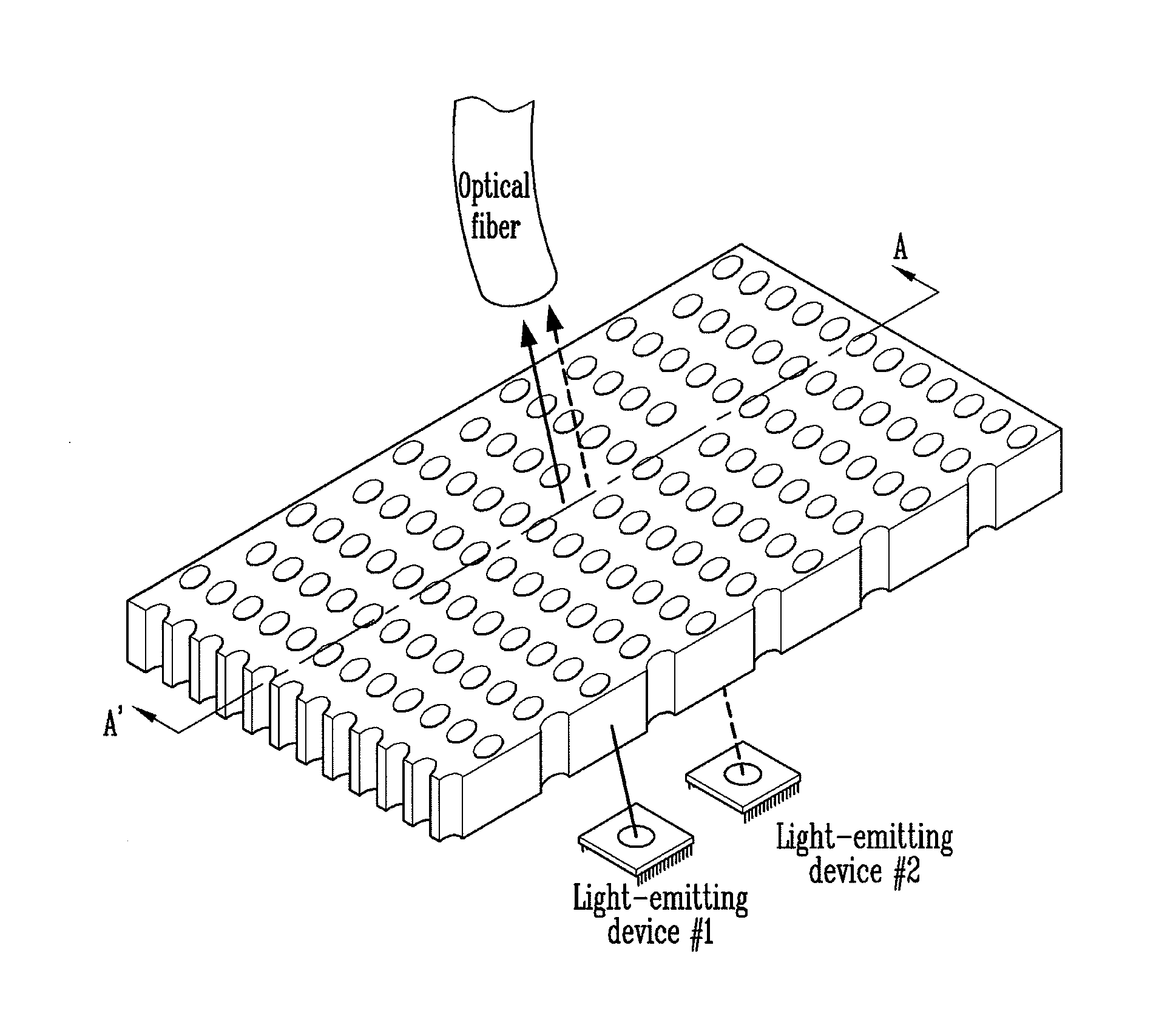

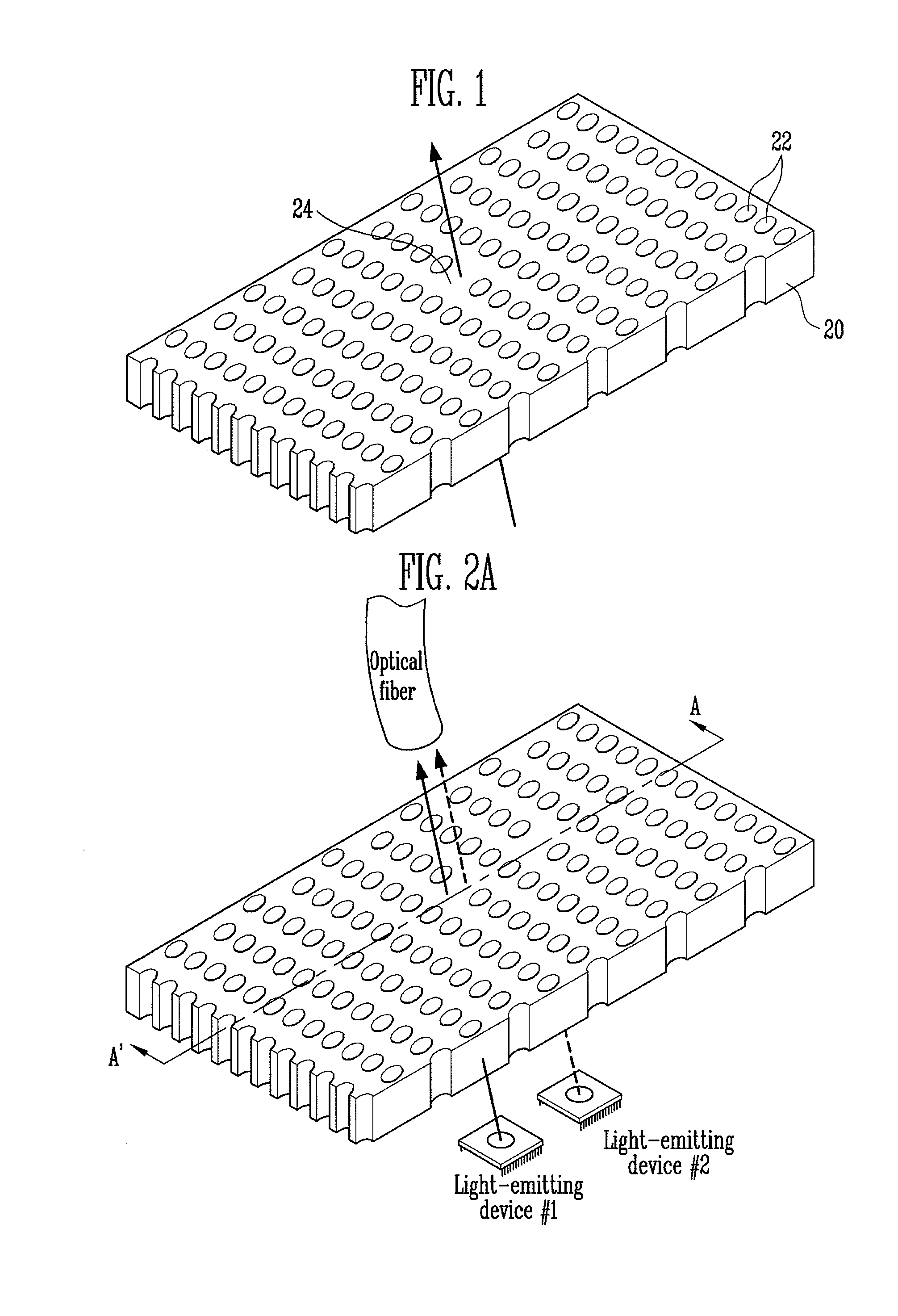

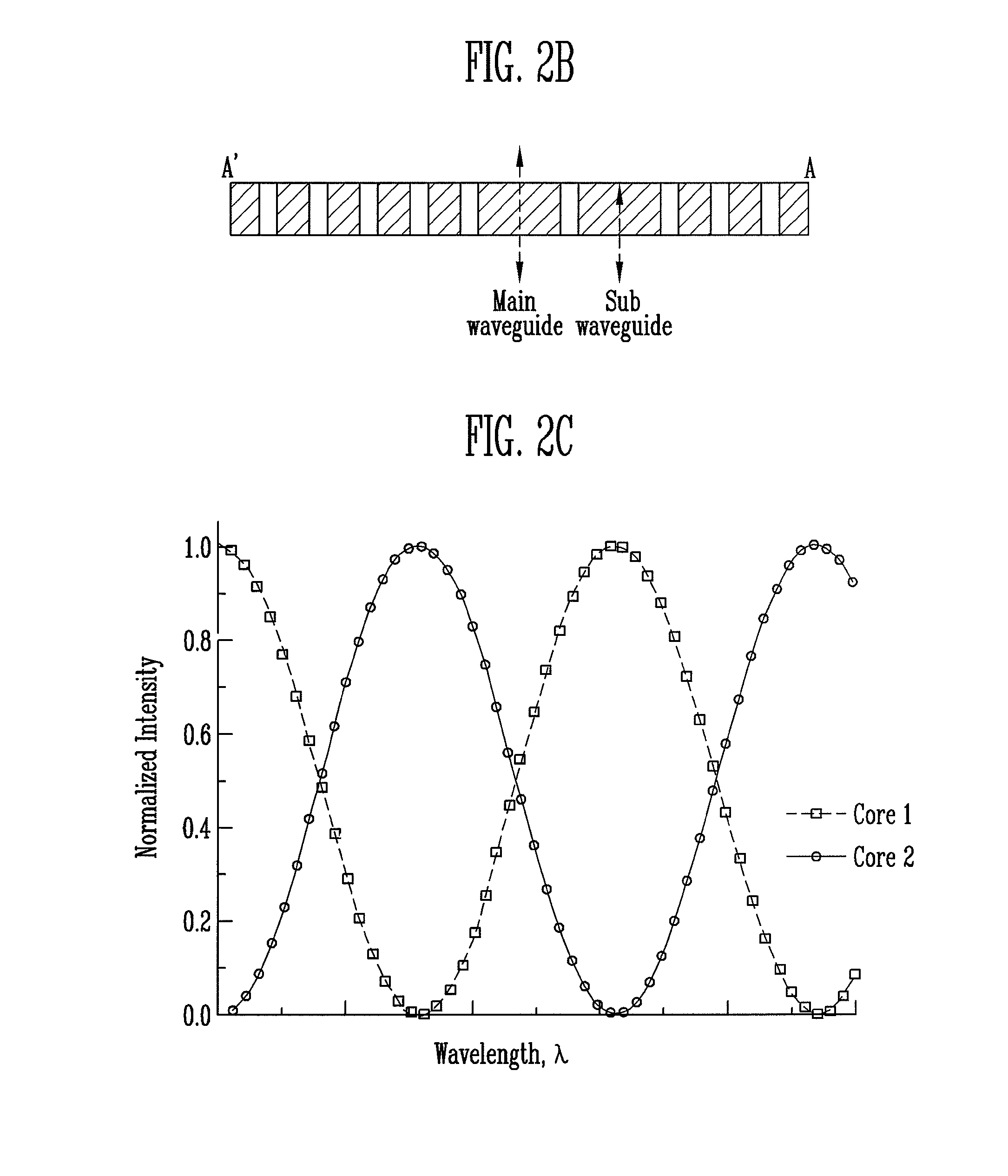

Vertical-type photonic-crystal plate and optical device assembly

InactiveUS20080138015A1High density integrationNanoopticsCoupling light guidesLattice defectsPhotonic crystal

Provided are a photonic-crystal plate that forms an optical waveguide and an optical device assembly using the same, and more particularly, a vertical-type photonic-crystal plate and an optical device assembly configured to be easily integrated with surface-emitting light source devices and surface-receiving light detector devices. The photonic-crystal plate includes a plurality of cylindrical through holes formed in a thickness direction and arranged in a periodic crystal lattice structure. The plate further includes: a main crystal lattice defect that forms a main optical waveguide for passing lights in a direction perpendicular to the photonic-crystal plate; and a sub-crystal lattice defect that forms a sub-optical waveguide for causing light in a specific wavelength band among the lights passing through the main optical waveguide to be optically coupled and passing the coupled light in the direction perpendicular to the photonic-crystal plate.

Owner:ELECTRONICS & TELECOMM RES INST

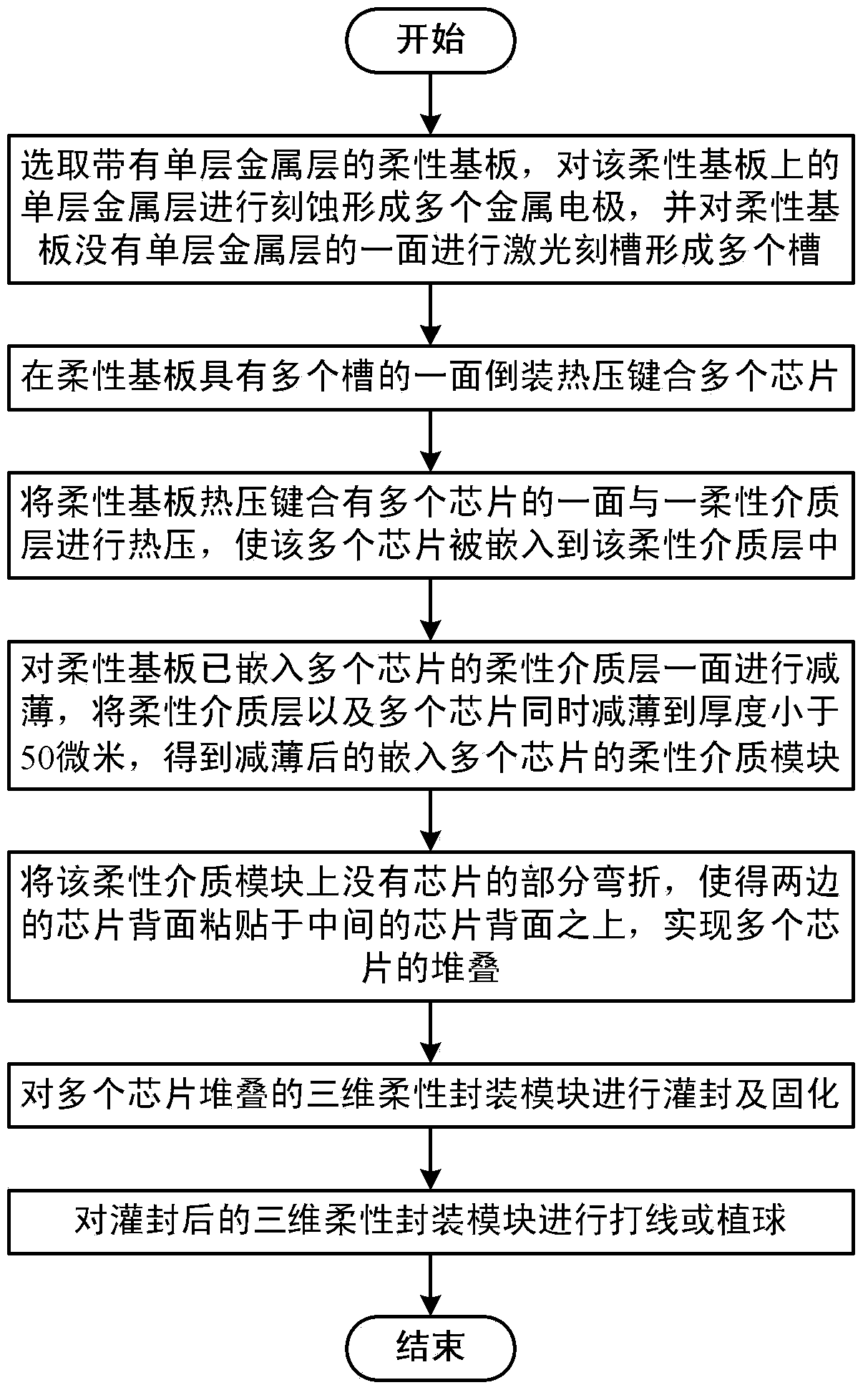

Method for manufacturing three-dimensional flexible stacked encapsulating structure of embedded ultrathin chip

ActiveCN103681458AEfficient use ofEffective coolingSolid-state devicesSemiconductor/solid-state device manufacturingComputer moduleEngineering

The invention discloses a method for manufacturing a three-dimensional flexible stacked encapsulating structure of an embedded ultrathin chip. The method comprises choosing a flexible substrate with a single-layer metal layer, etching the single-layer metal layer on the flexible substrate to form a plurality of metal electrodes, conducting laser grooving on one side of the flexible substrate without the single-layer metal layer to form a plurality of grooves, conducting flipped thermocompression bonding with a plurality of chips on one side of the flexible substrate, provided with the plurality of grooves, thermally compressing the side of the flexible substrate, provided with the plurality of chips through thermocompression bonding and a flexible medium layer to embed the plurality of chips into the flexible medium layer, thinning one side of flexible medium layer embedded with the plurality of chips of the flexible substrate to obtain a thinned flexible medium module embedded with the plurality of chips, bending a part of the flexible medium module without the chips to stack the chips, encapsulating and curing a three-dimensional flexible encapsulating module with the plurality of stacked chips, and routing or reballing the encapsulated three-dimensional flexible encapsulating module.

Owner:NAT CENT FOR ADVANCED PACKAGING

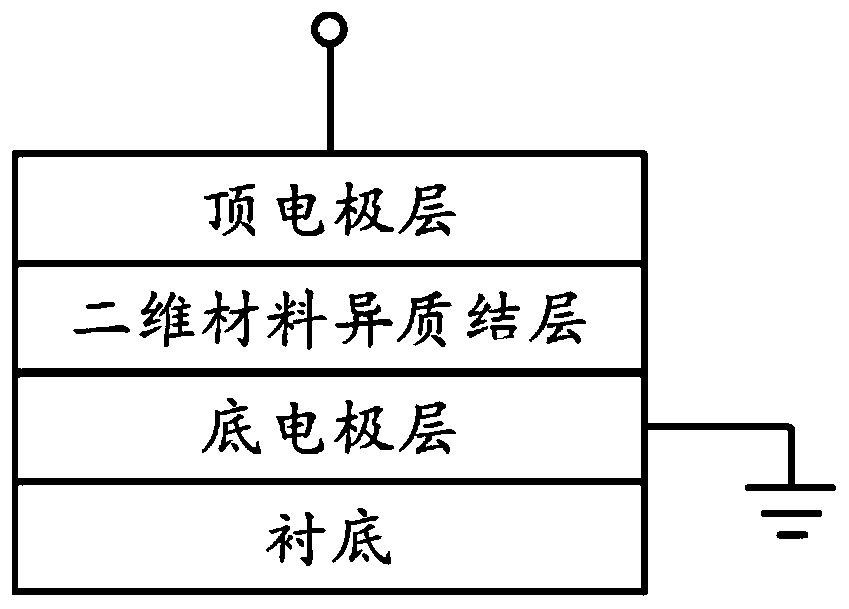

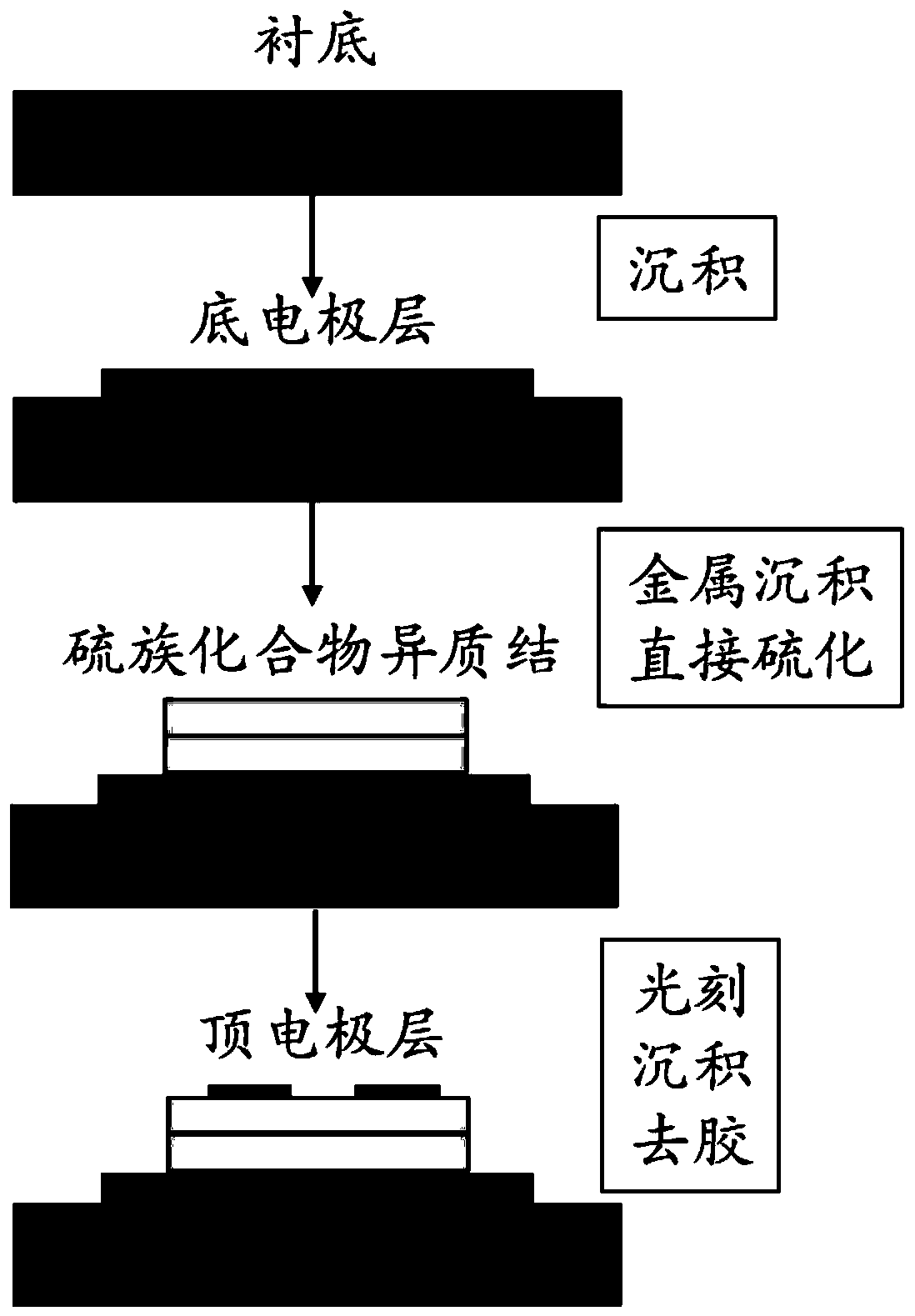

Memristor with two-dimensional material heterojunction and preparation method thereof

ActiveCN110518117AImprove growth efficiencyAvoid time costNanoinformaticsSemiconductor/solid-state device manufacturingHeterojunctionInformation transmission

The invention belongs to the technical field of microelectronics, and discloses a memristor with a two-dimensional material heterojunction and a preparation method of the memristor. The memristor comprises a substrate, a bottom electrode layer, a two-dimensional material heterojunction layer and a top electrode layer from bottom to top, wherein the two-dimensional material heterojunction layer serves as an intermediate dielectric layer and is of a two-layer laminated structure composed of two different metal sulfur compounds, and each layer in the laminated structure corresponds to one metal sulfur compound. Compared with the prior art, the novel memristor is constructed completely based on a two-dimensional material by improving a key functional layer material adopted by the device, the overall structural design of the device and the like, the traditional MIM structure is overturned, and the memristor has the characteristics of low working voltage, fatigue resistance and cycling stability. In addition, the memristor shows high similarity with synapses in information transmission on the aspect of simulating information transmission of neuron, and has a great application prospect onthe development of brain-like structures in the future.

Owner:HUAZHONG UNIV OF SCI & TECH

Soi transistor with polysilicon seed

InactiveUS20020164841A1High density integrationHigh precisionTransistorSolid-state devicesPath lengthEngineering

Short channel effects are effectively suppressed by steep impurity concentration gradients which can be placed with improved accuracy of location and geometry while relaxing process tolerances by implanting impurities in a polysilicon seed adjacent a conduction channel of a transistor and diffusing impurities therefrom into the conduction channel. The polysilicon seed also allows the epitaxial growth of polysilicon source / drain contacts therefrom having a configuration which minimizes current density and path length therein while providing further mechanical advantages.

Owner:GLOBALFOUNDRIES US INC

Square micro-cavity laser with output waveguide

InactiveCN101325311ALower the thresholdHigh density integrationOptical wave guidanceLaser detailsResonant cavityWaveguide

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Reverse mask and nitride layer deposition for reduction of vertical capacitance variation in multi-layer metallization systems

InactiveUS6511904B1Improved multi-level metallizationHigh density integrationSemiconductor/solid-state device manufacturingCapacitanceRC time constant

Excessive variation in vertical (i.e., inter-level) capacitance of multi-level metallization semiconductor devices resulting in poor RC time constants of finished devices, and over-etching of borderless vias leading to inter-level short-circuits, are simultaneously eliminated or substantially reduced by selectively providing an etch-resistant masking material at thinner, i.e., recessed, portions of a first, low k gap fill material blanket-deposited over spaced-apart features of a metallization pattern and in the spaces therebetween. The surfaces of thicker, non-recessed portions thereof are etched so as to be substantially co-planar with the feature surfaces and the recessed portions. The etch-resistant mask is then removed, and second and third dielectric layers deposited over the planarized surface. The second and third dielectric layers are selected such that the second dielectric layer etches at a substantially slower rate than the third dielectric layer, thereby serving as a partial etch stop layer preventing deleterious over-etching of the borderless via.

Owner:ADVANCED MICRO DEVICES INC

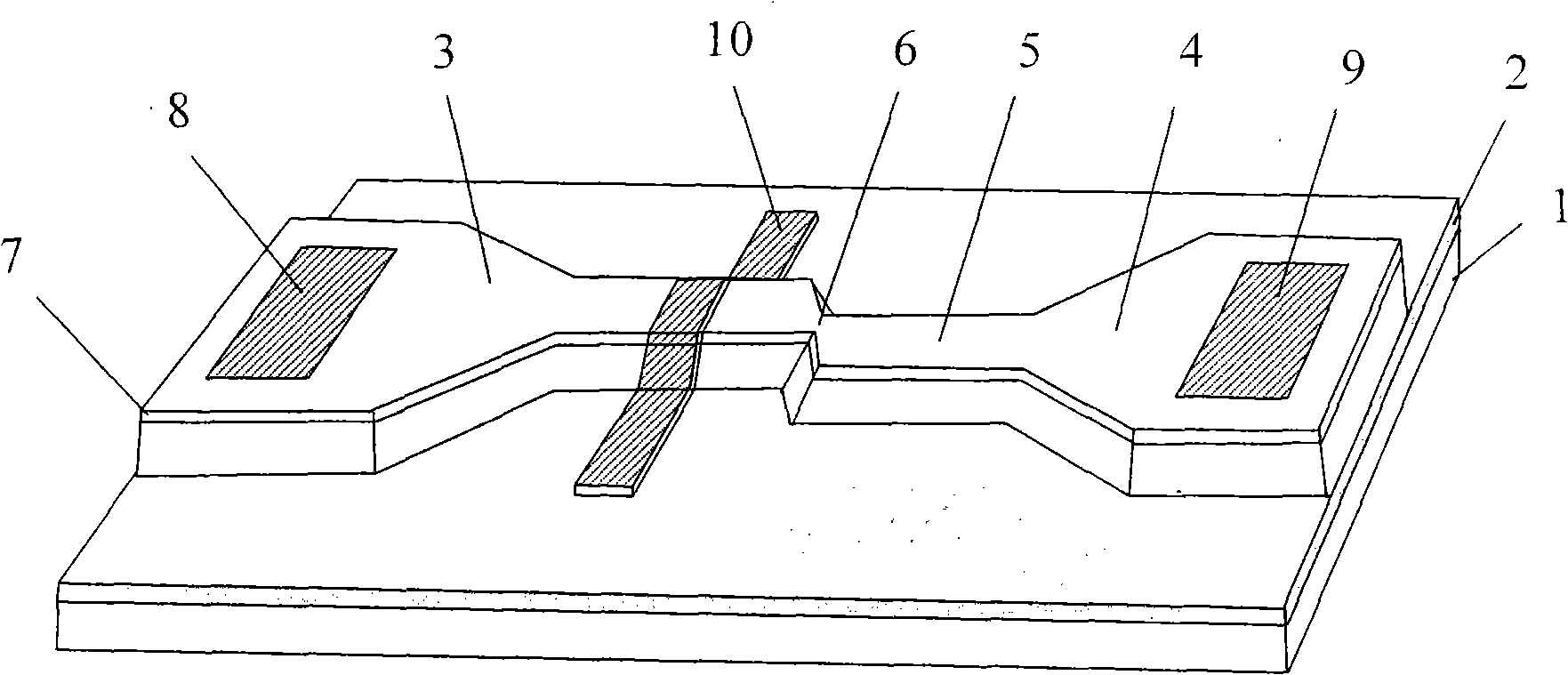

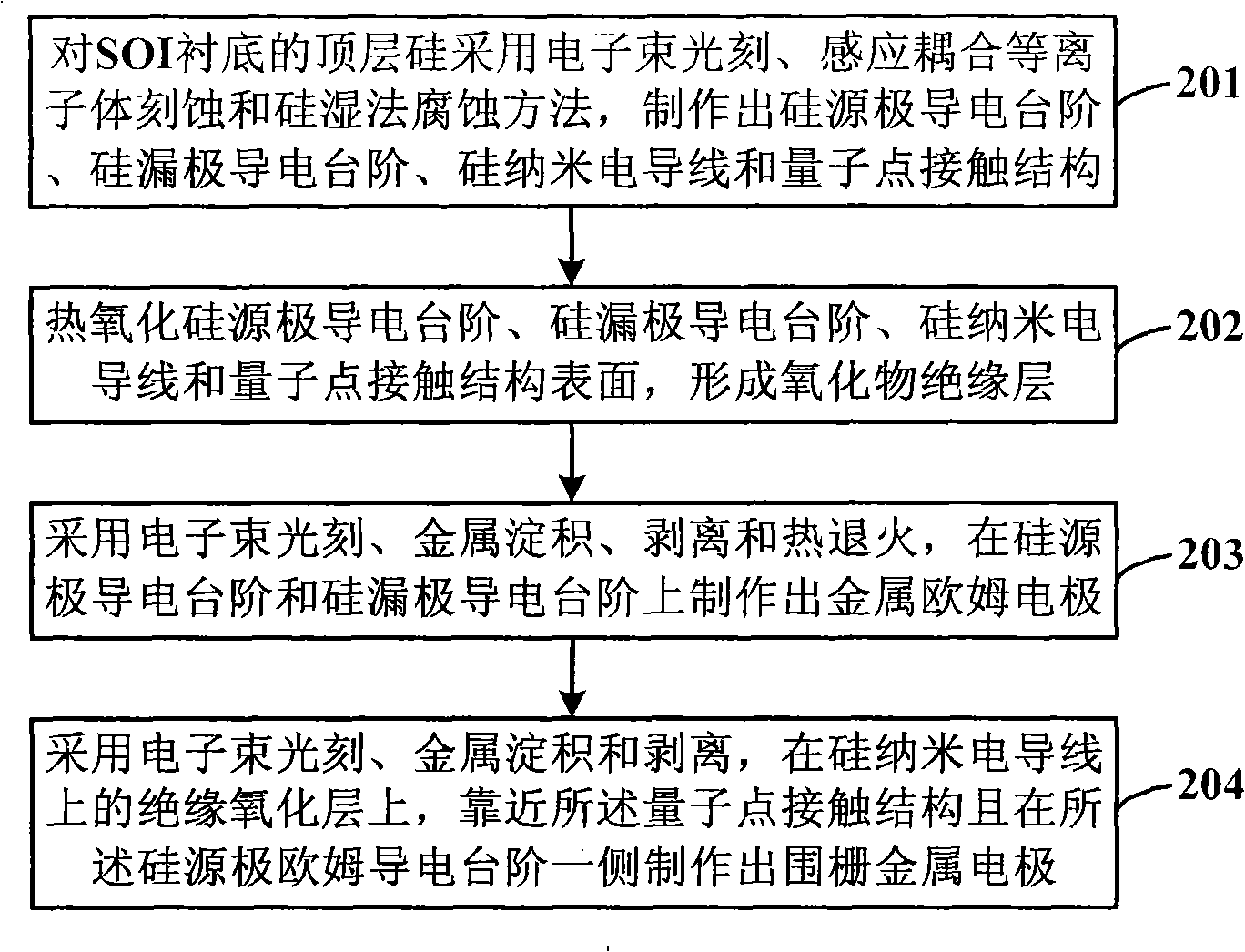

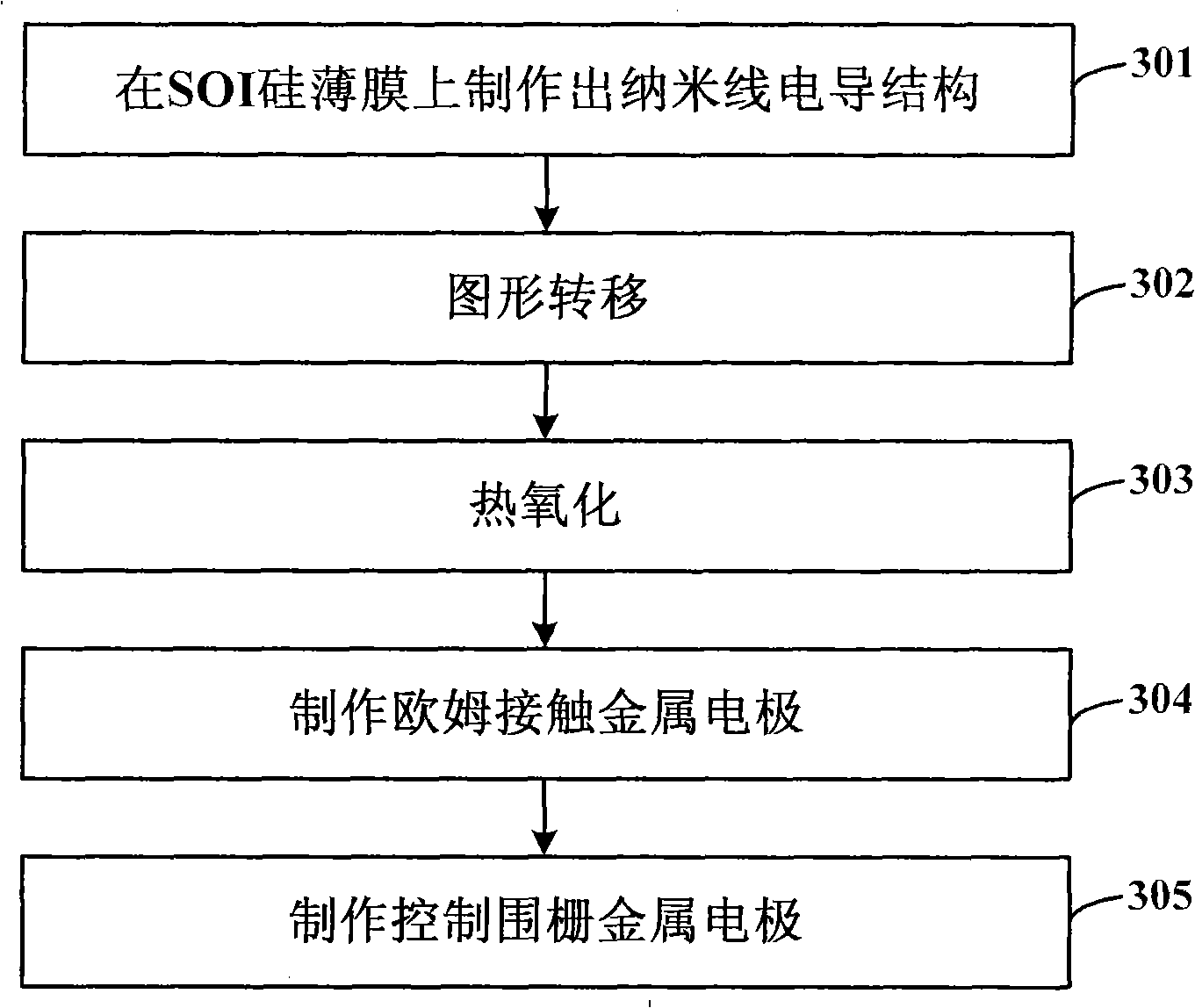

Silicon based single electron transistor of wrap gate control construction and manufacturing method thereof

InactiveCN101359684AControl chargeStable control transportSemiconductor/solid-state device manufacturingSemiconductor devicesSingle electronQuantum dot

The invention discloses a silicon single-electron transistor with an all-round gate control structure, comprising a silicon source electrode conduction step, a silicon drain electrode conduction step, a silicon nanometer conduction line and a quantum point contact structure, which are made on a SOI substrate from silicon on the top layer. The silicon source electrode conduction step and the silicon drain electrode conduction step are symmetrically arranged at the left and the right of the surface of an insulating layer and are connected through the silicon nanometer conduction line. The quantum point contact structure is arranged on the silicon nanometer conduction line, at the middle between the silicon source electrode conduction step and the silicon drain electrode conduction step. The invention further comprises a source ohmic metal electrode arranged on the silicon source electrode conduction step, a silicon drain ohmic metal electrode arranged on the silicon drain electrode conduction step, and an all-around-gate metal electrode which is arranged on the silicon nanometer conduction line, close to the quantum point contact structure and at one side of the silicon source electrode conduction step. The invention also discloses a method for fabricating such a silicon single-electron transistor with an all-round control structure. The silicon single-electron transistor is capable of steadily controlling single electron transport in batches.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

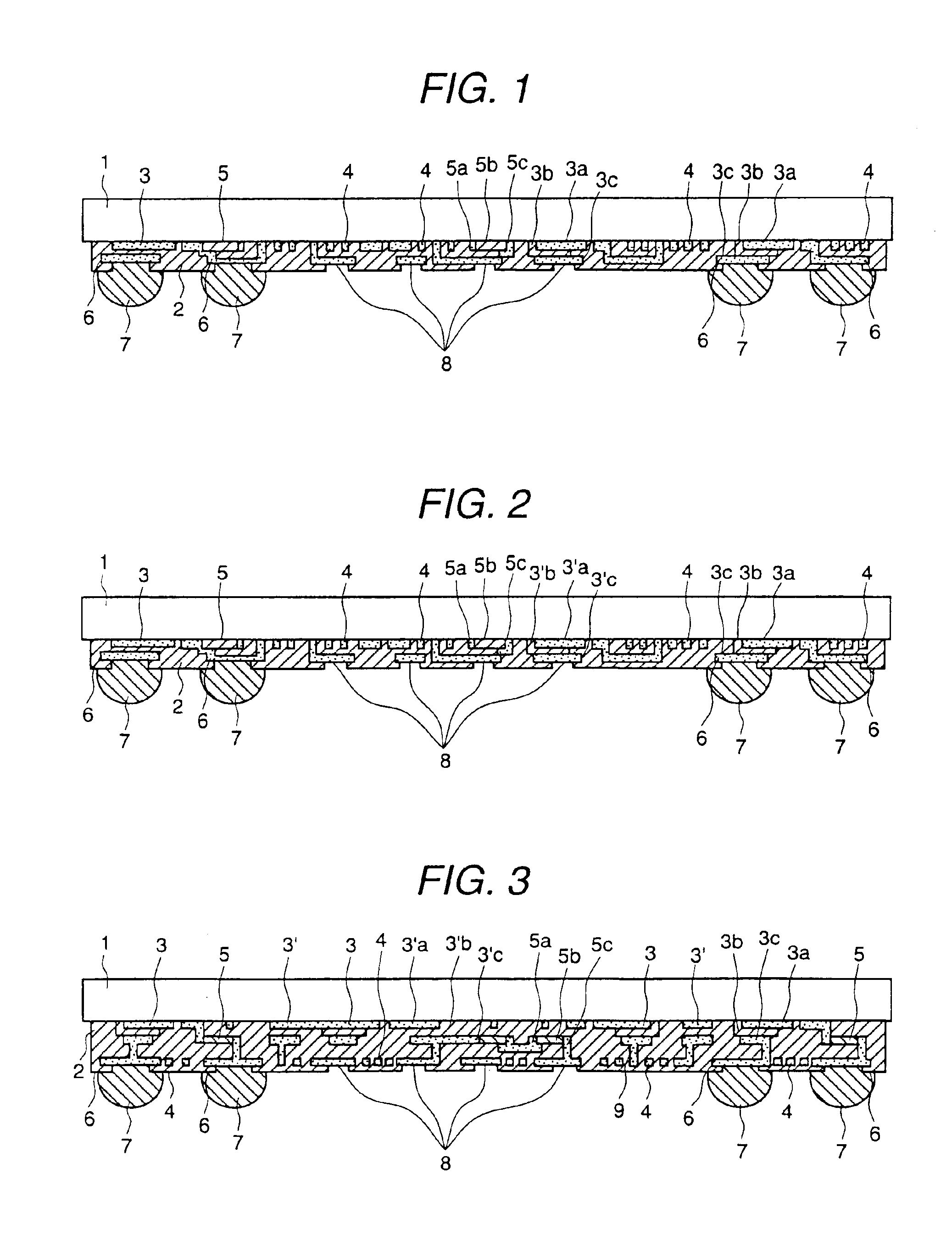

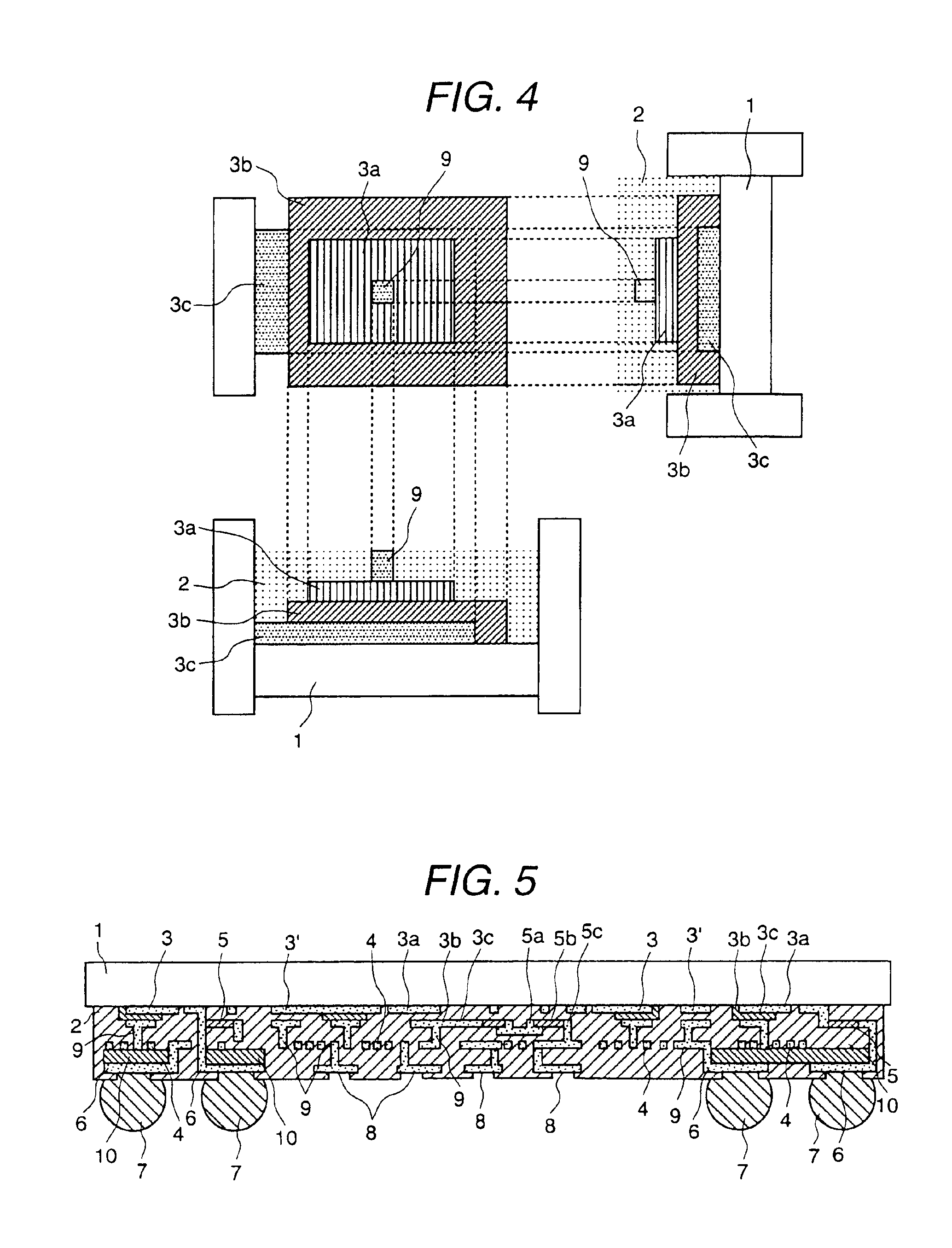

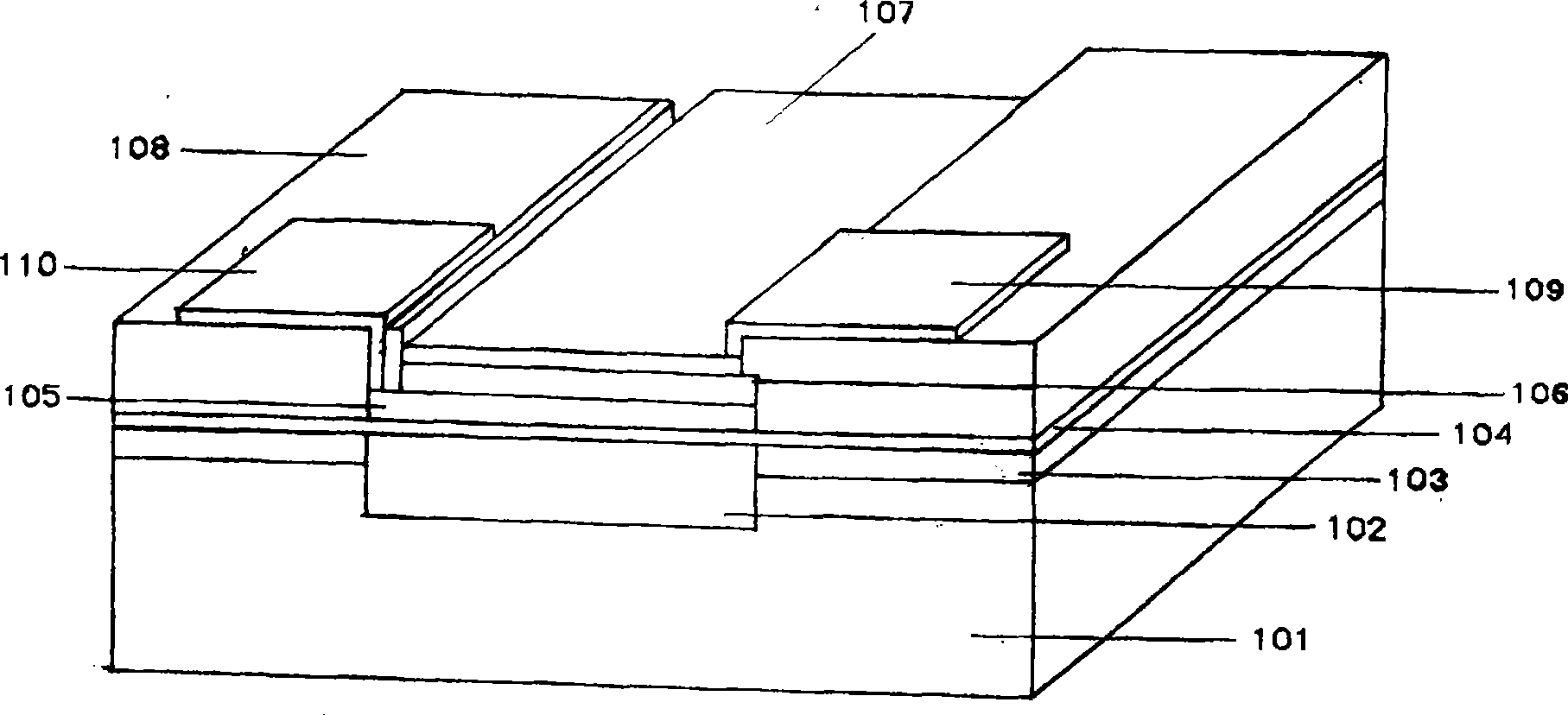

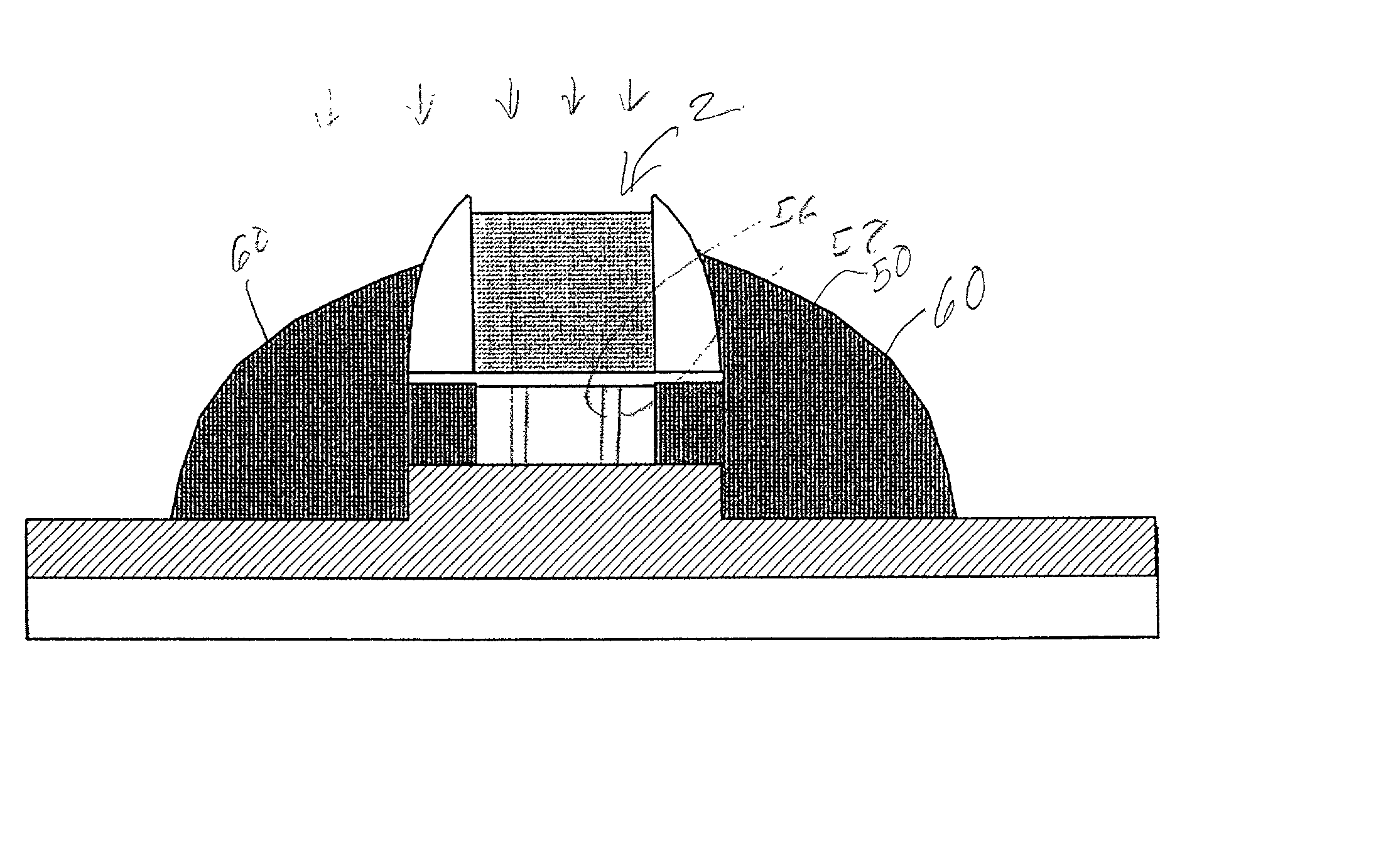

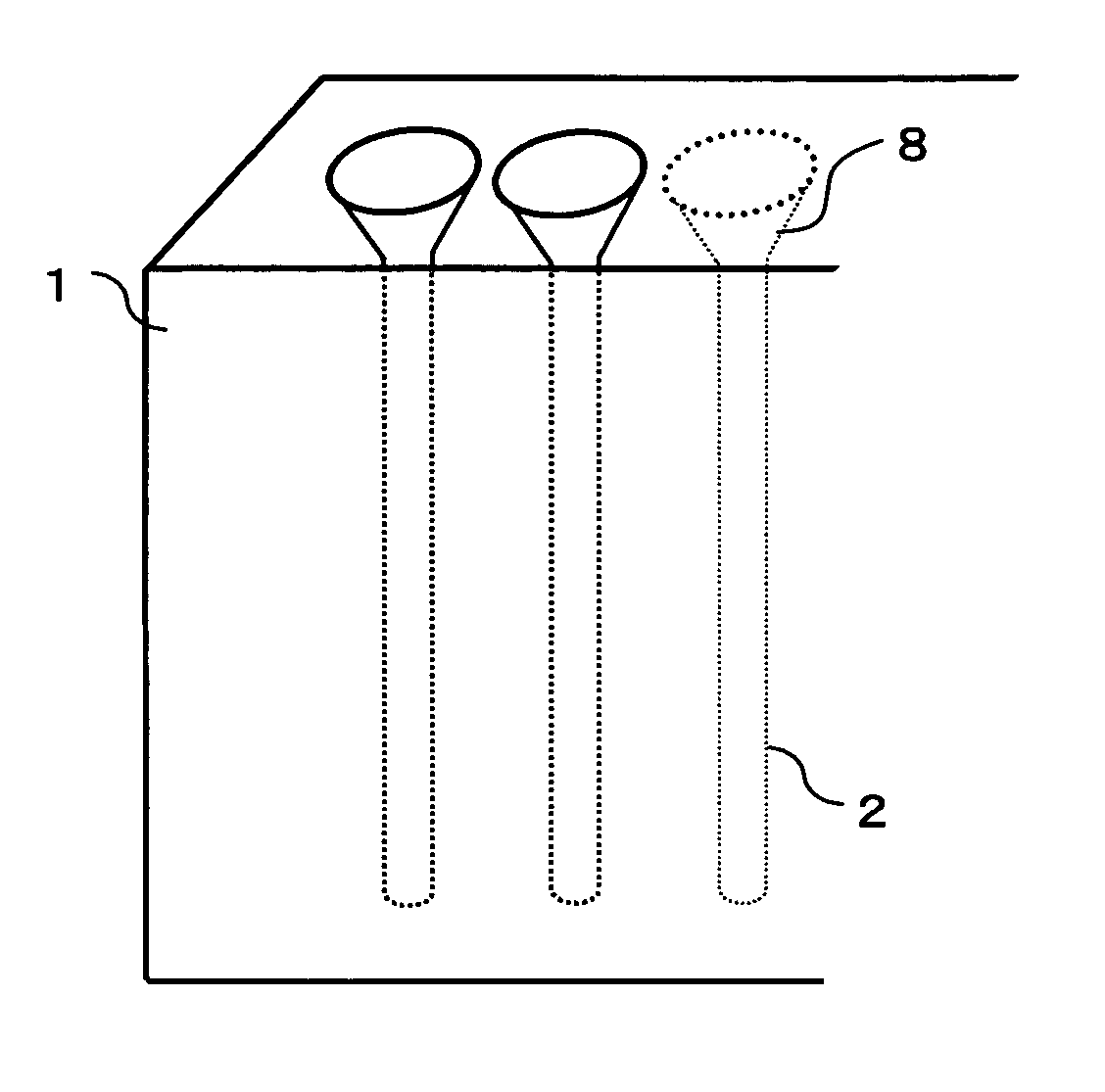

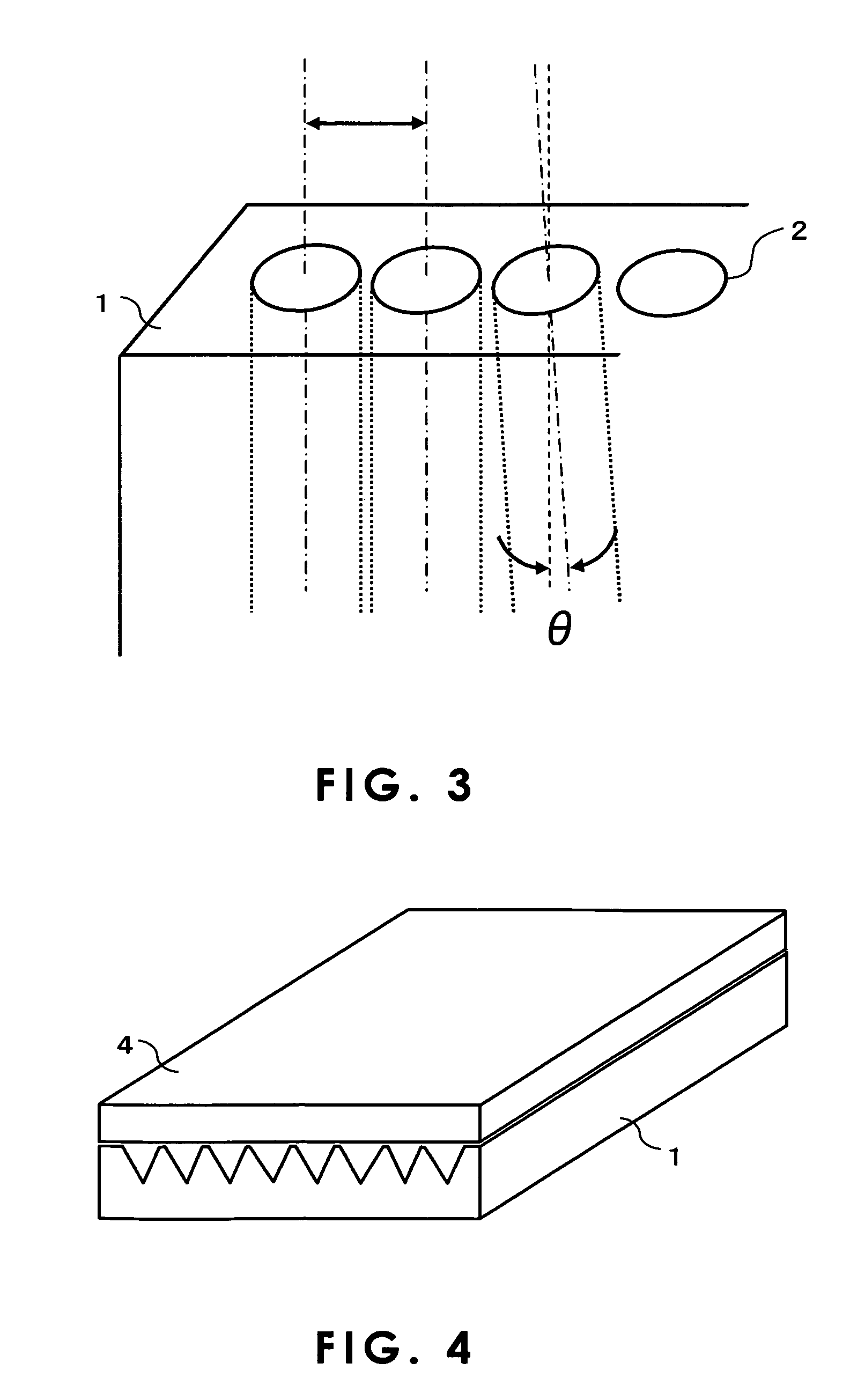

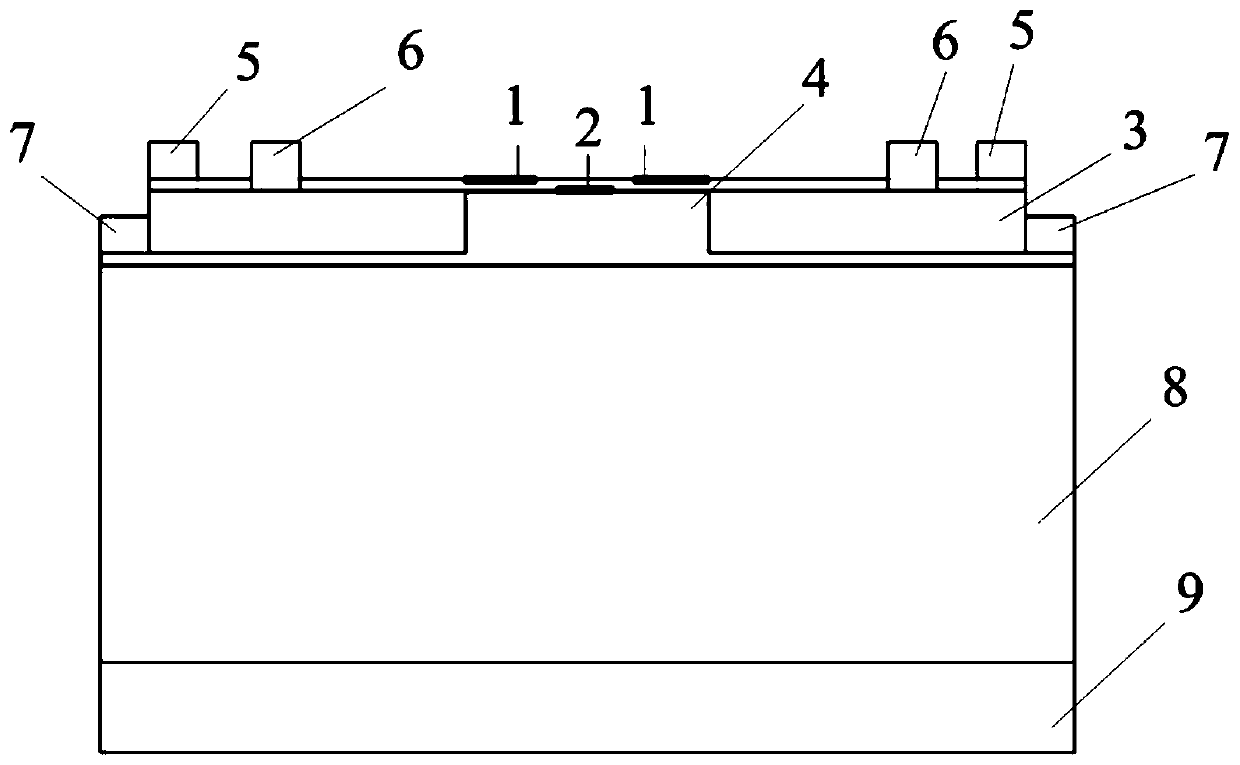

Image pickup system with MOS sensors and microlenses

InactiveUS6987537B2Good image pickup characteristicHigh density integrationTelevision system detailsTelevision system scanning detailsSignal processing circuitsSignal on

The image pickup system includes: MOS sensors arranged in an image pickup region of a semiconductor substrate in the form of a matrix and having photoelectric transfer layers; a peripheral circuit part formed in a region of the semiconductor substrate except for the image pickup region and having a driving circuit for driving the MOS sensors and a signal processing circuit for processing output signals from the MOS sensors; and microlenses, formed on the photoelectric transfer layers via a first insulating film, for condensing picture signals on the photoelectric transfer layers, wherein the driving circuit and the signal processing circuit in the peripheral circuit part are covered by a second insulating film, and the distance between the surface of the first insulating film and the semiconductor substrate is shorter than the distance between the surface of a second insulating film and the semiconductor substrate.

Owner:SK HYNIX INC

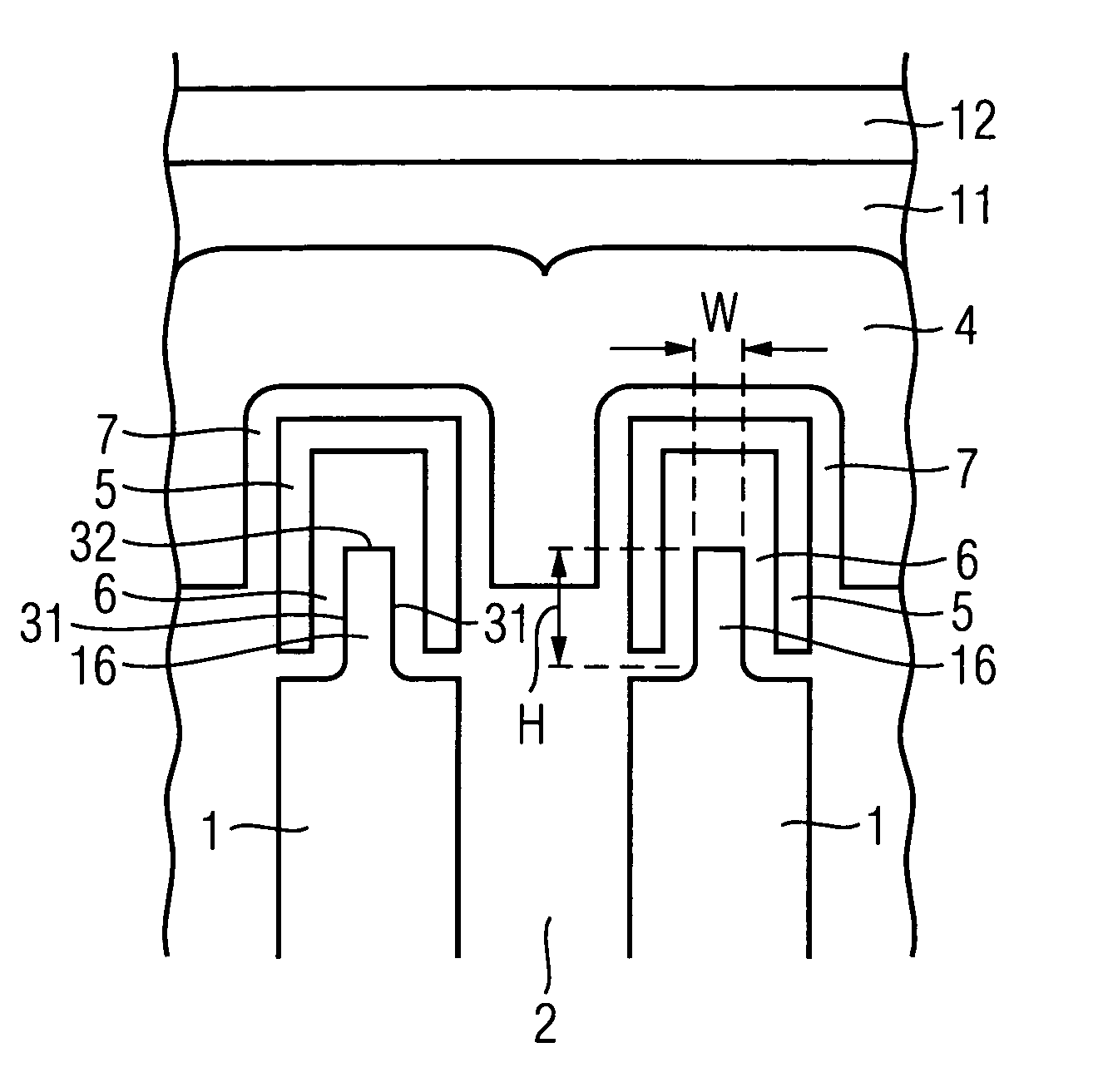

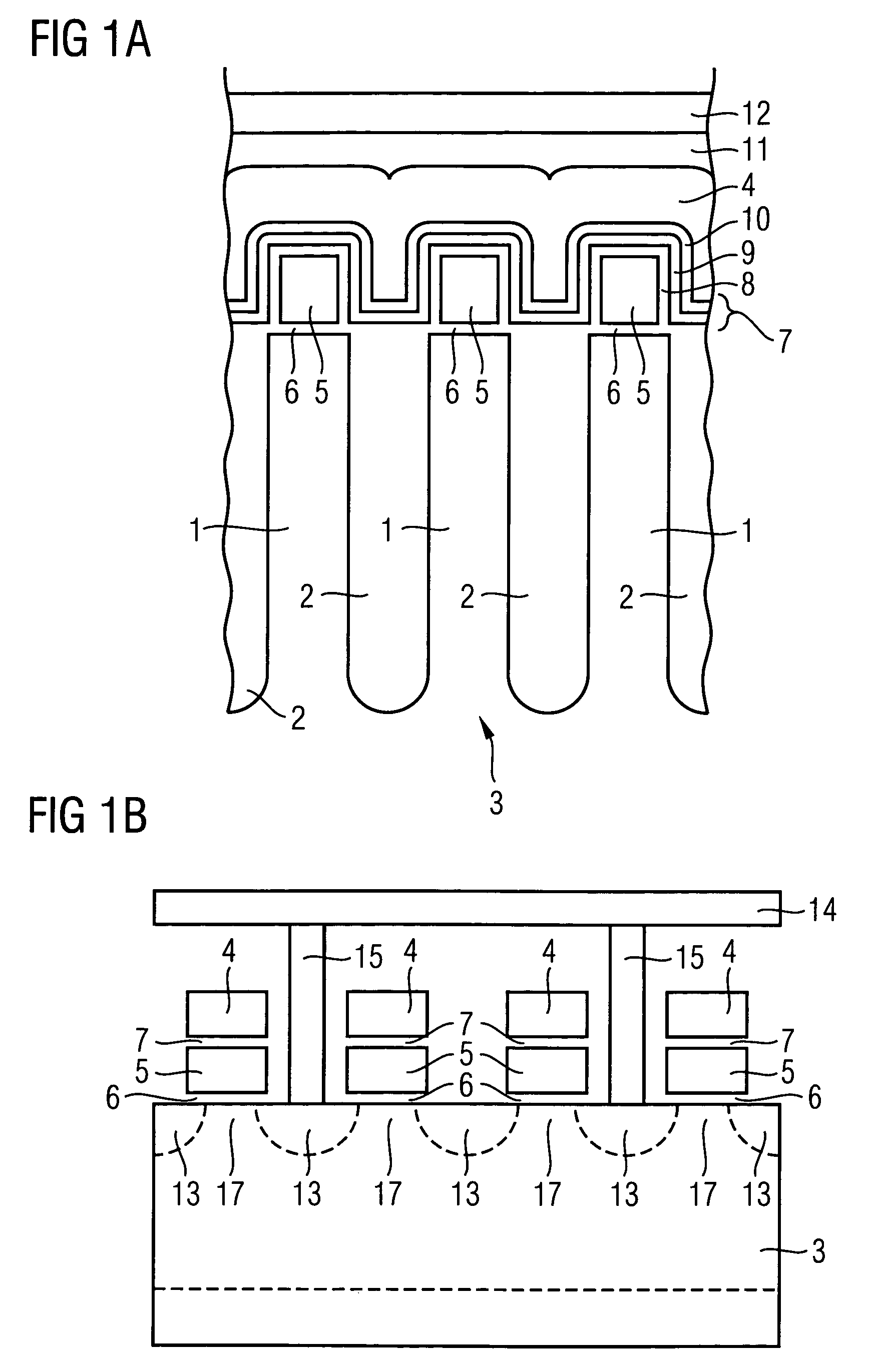

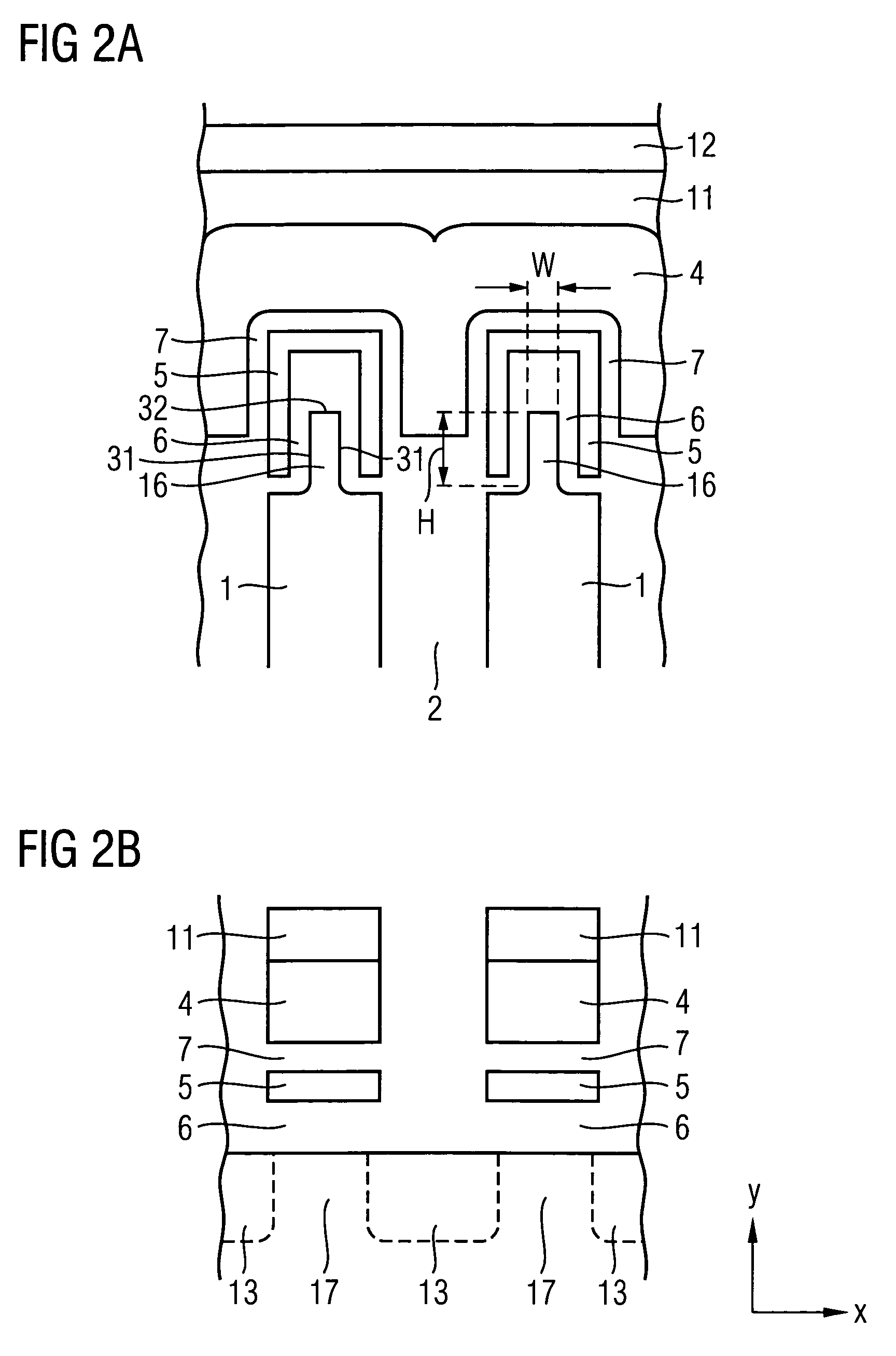

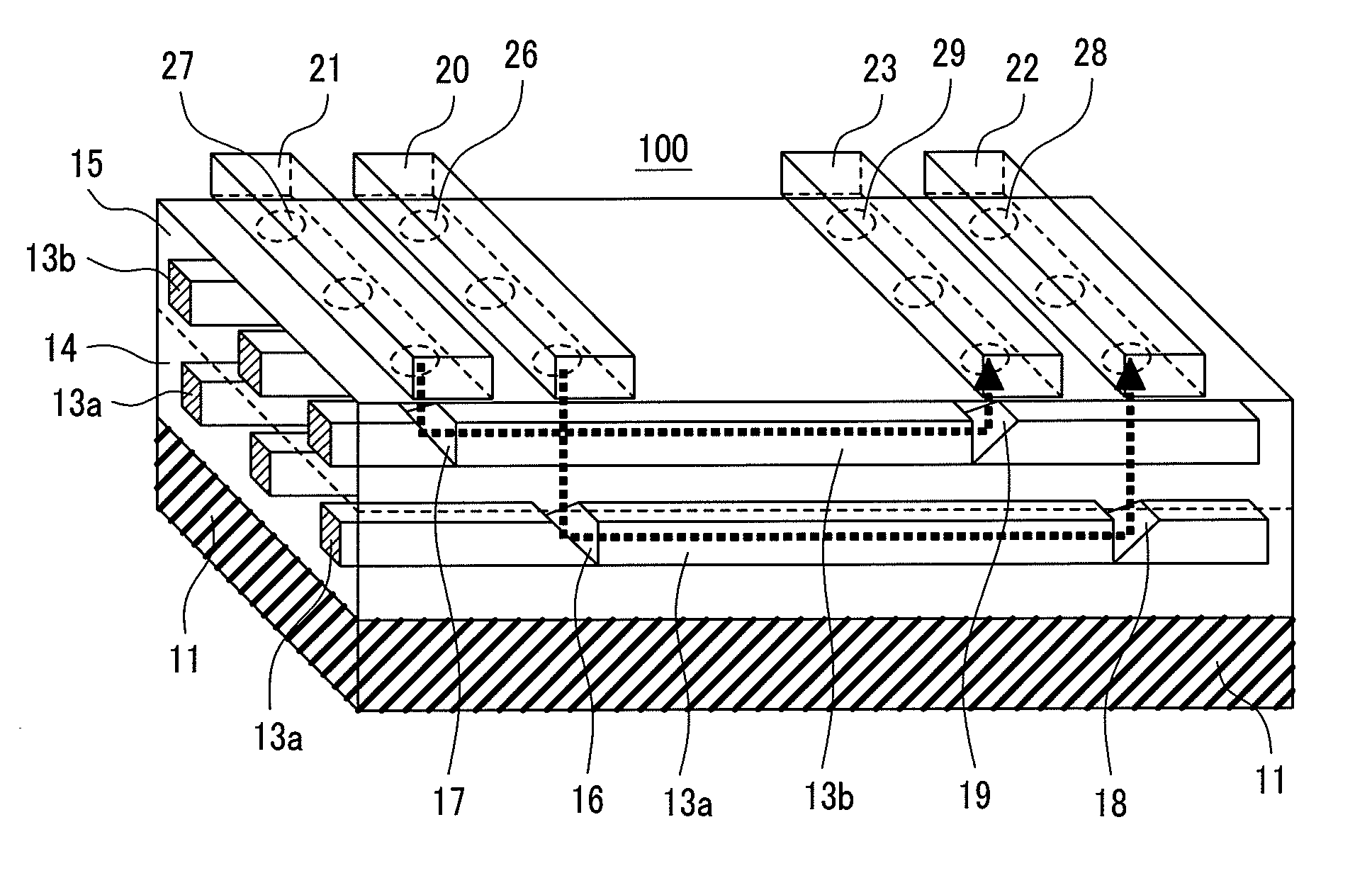

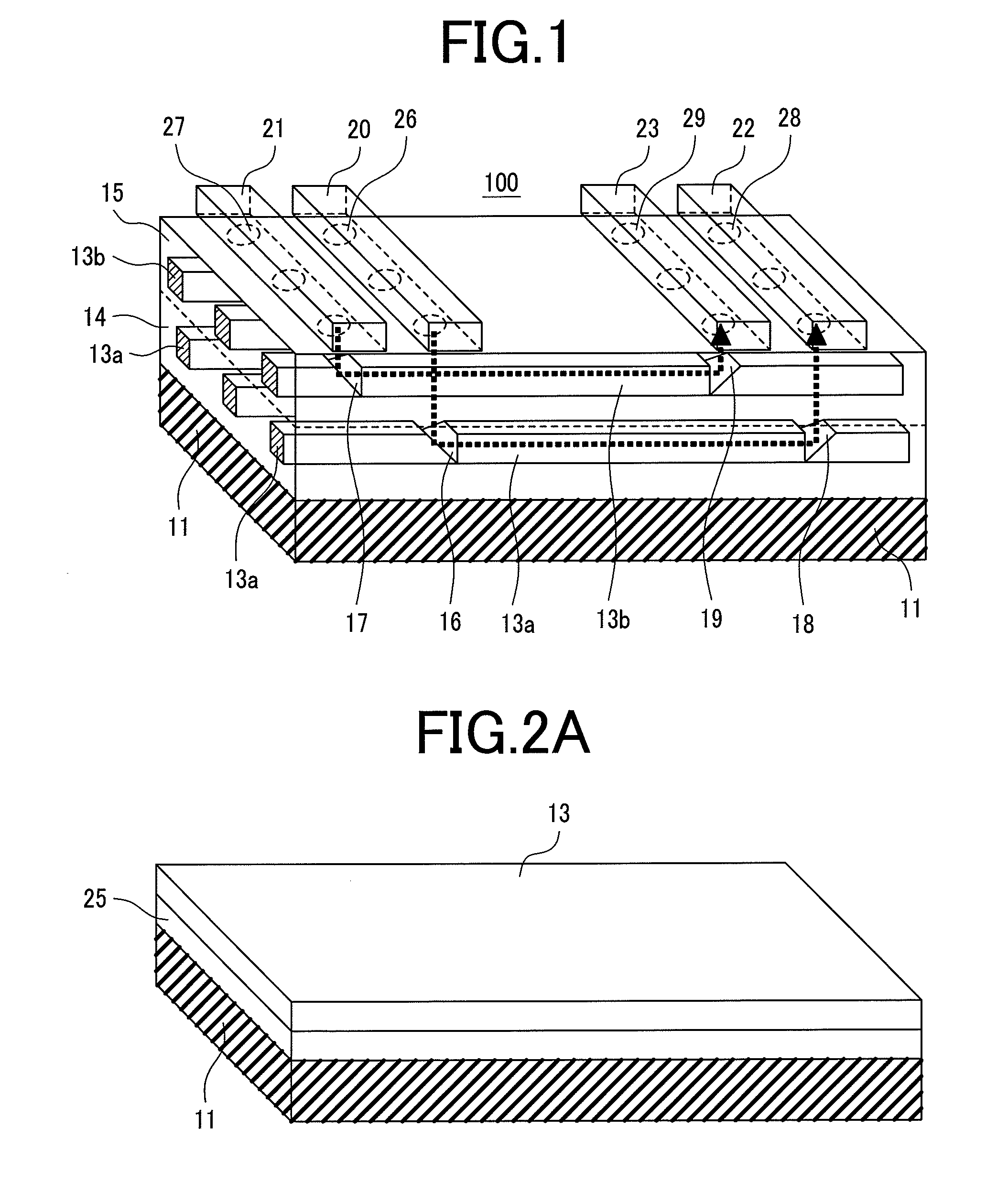

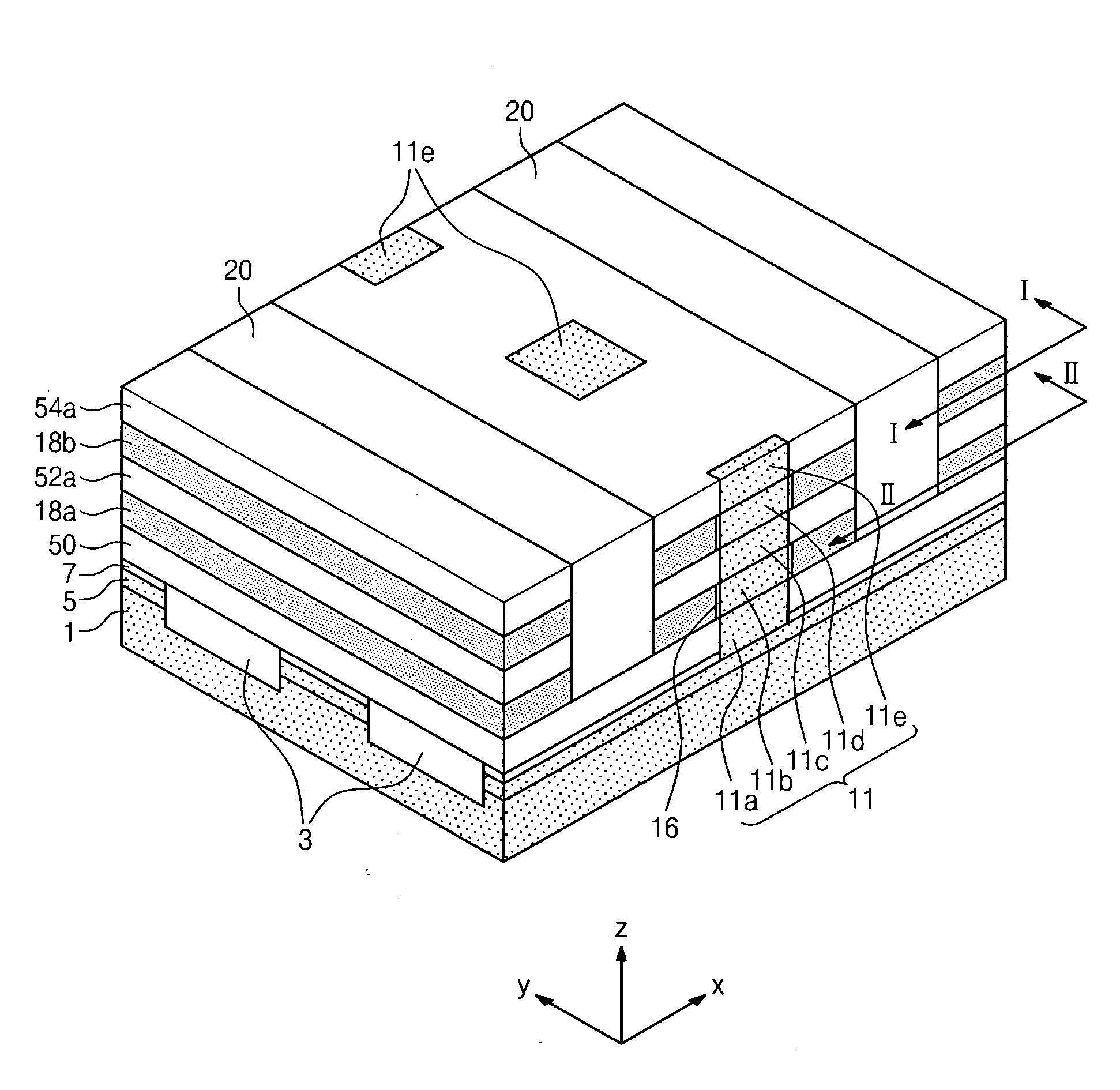

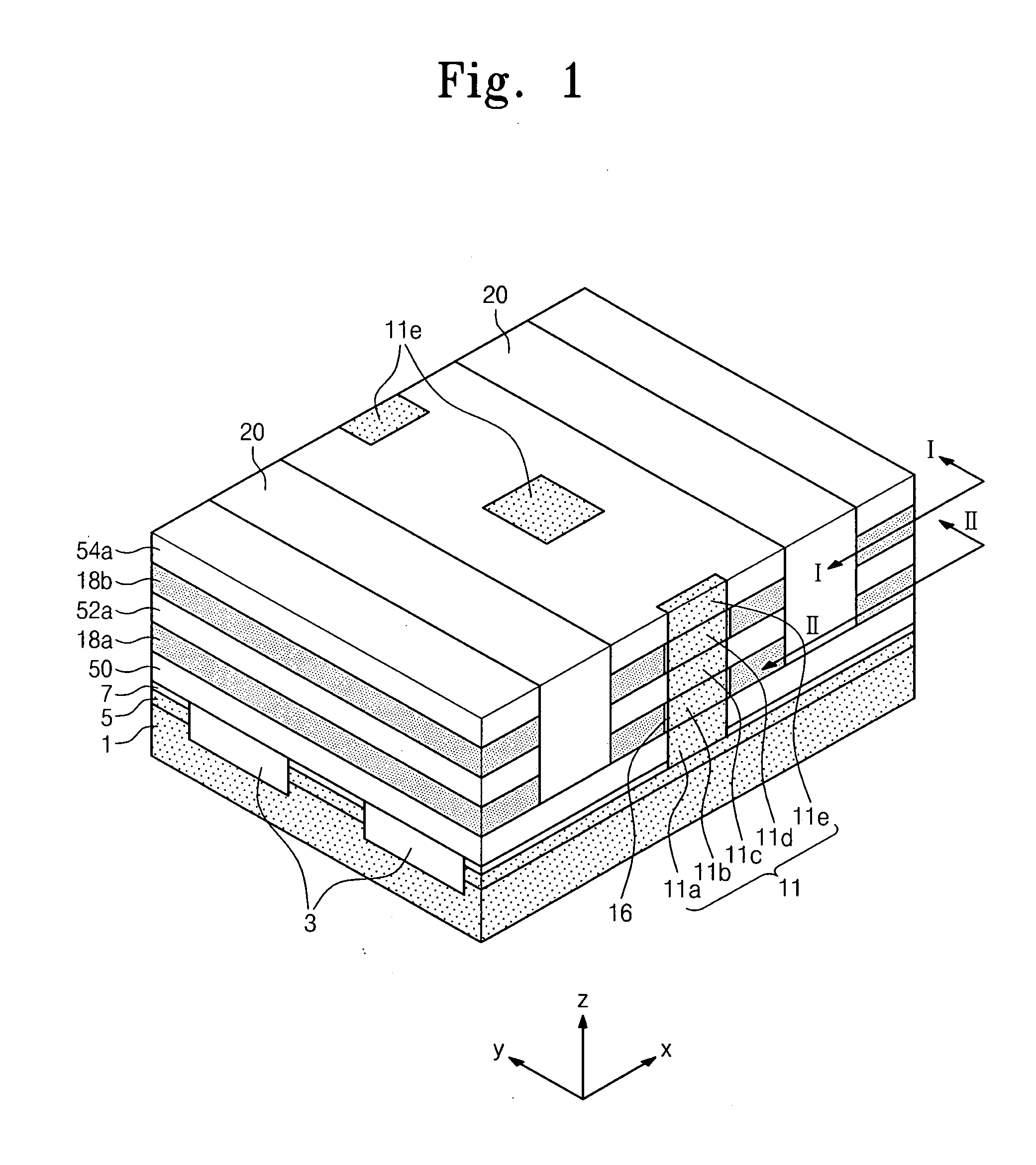

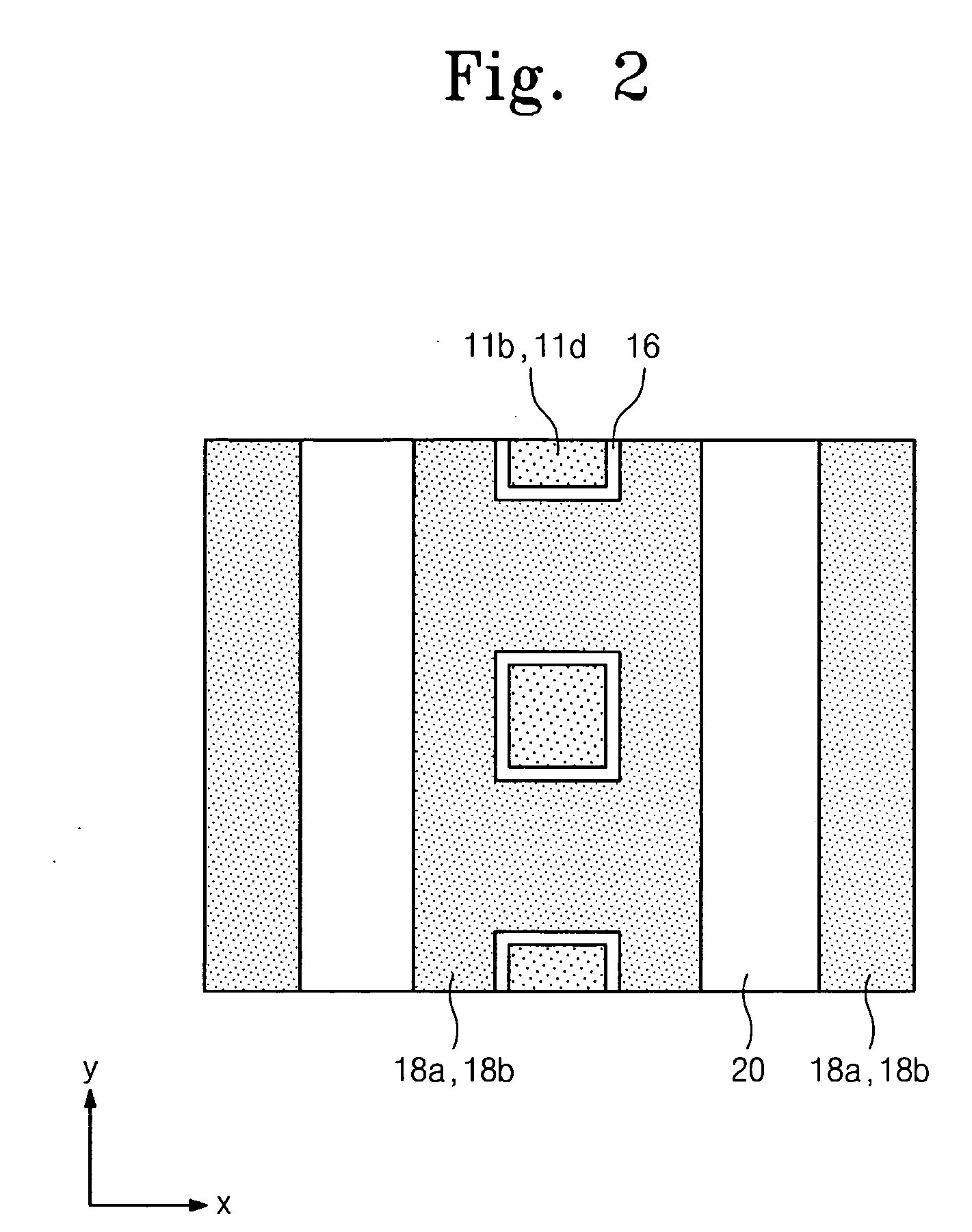

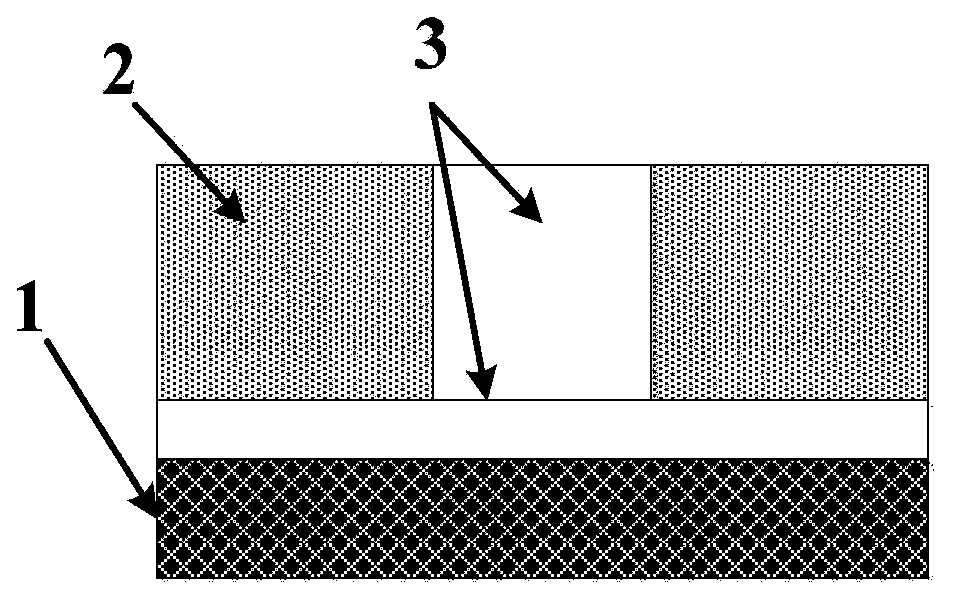

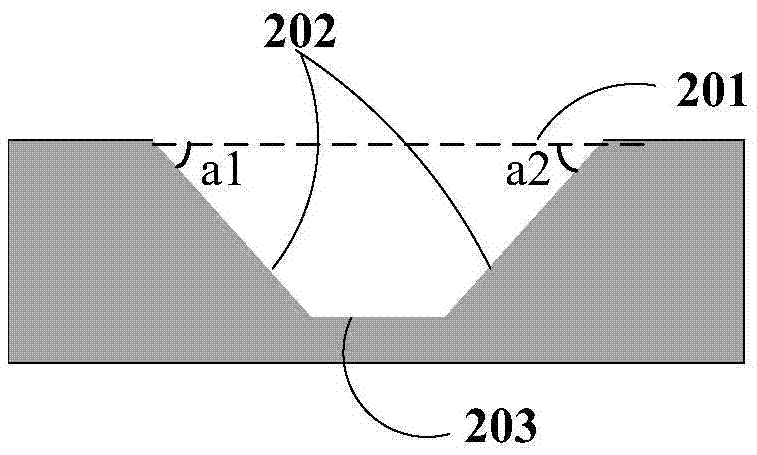

Semiconductor memory device and method of manufacturing the same

A semiconductor memory device includes a plurality of active pillars protruding from a semiconductor substrate, a first gate electrode disposed on at least one sidewall of the active pillar, a first gate insulating layer being disposed between the active pillar and the first gate electrode, a second gate electrode disposed on at least one sidewall of the active pillar over the first gate electrode, a second gate insulating layer being disposed between the active pillar and the second gate electrode, first and second body regions in the active pillar adjacent to respective first and second respective electrodes, and first through third source / drain regions in the active pillar arranged alternately with the first and second body regions.

Owner:SAMSUNG ELECTRONICS CO LTD

High-speed, high-density and lower power consumption phase-change memory unit and preparation method thereof

InactiveCN103682089AImprove thermal stabilityLow thermal conductivityElectrical apparatusPhase-change memoryHigh density

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

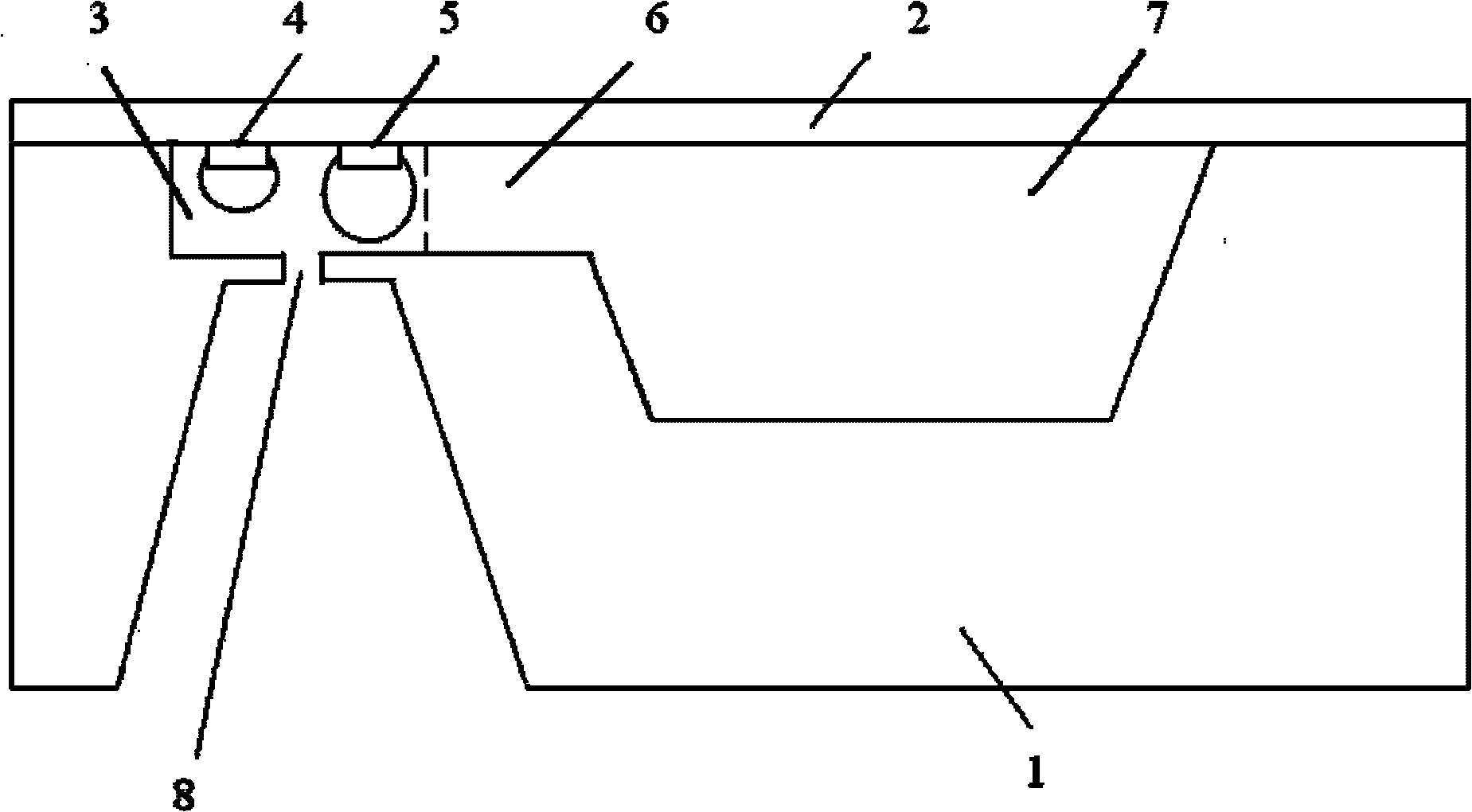

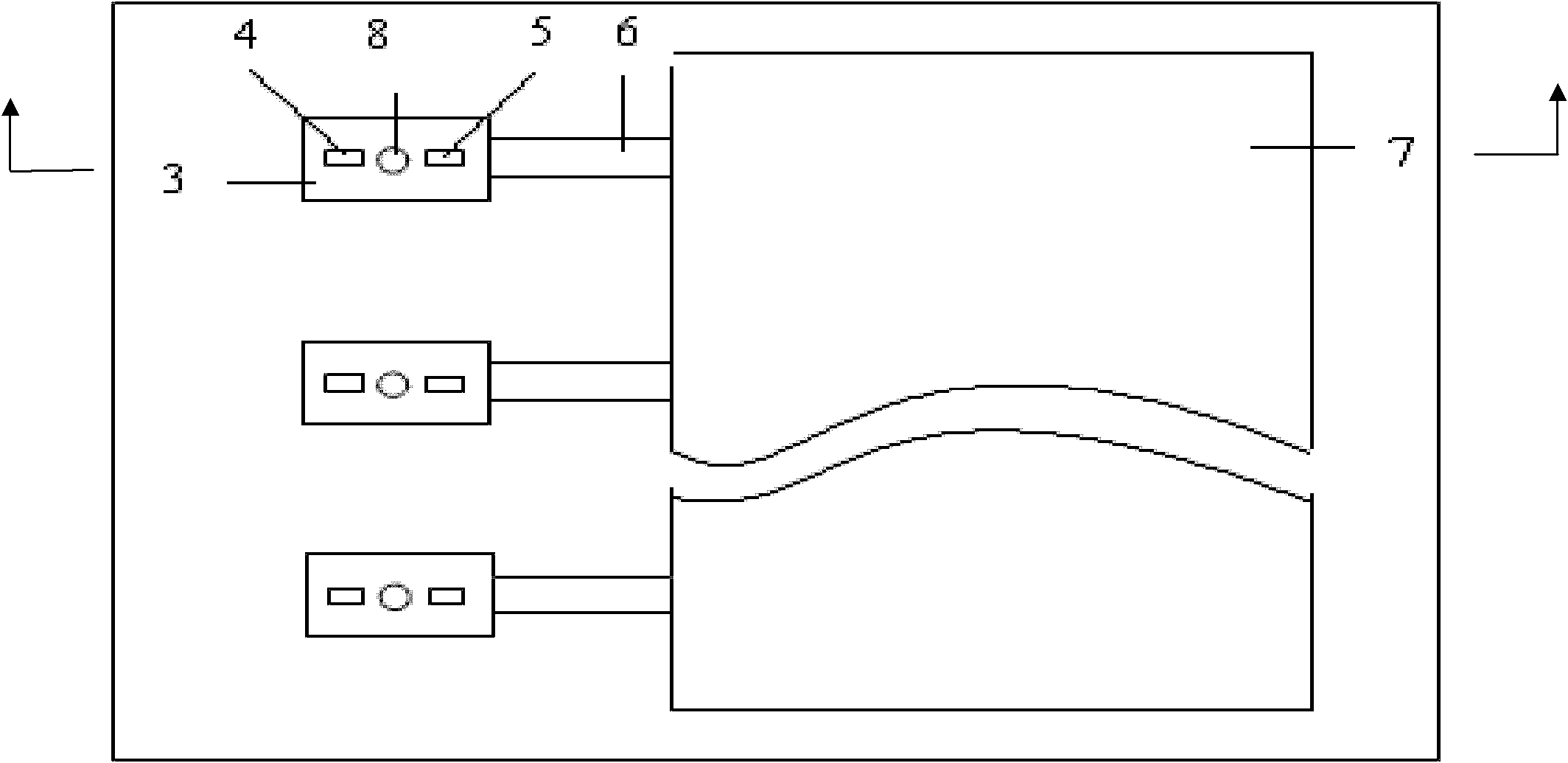

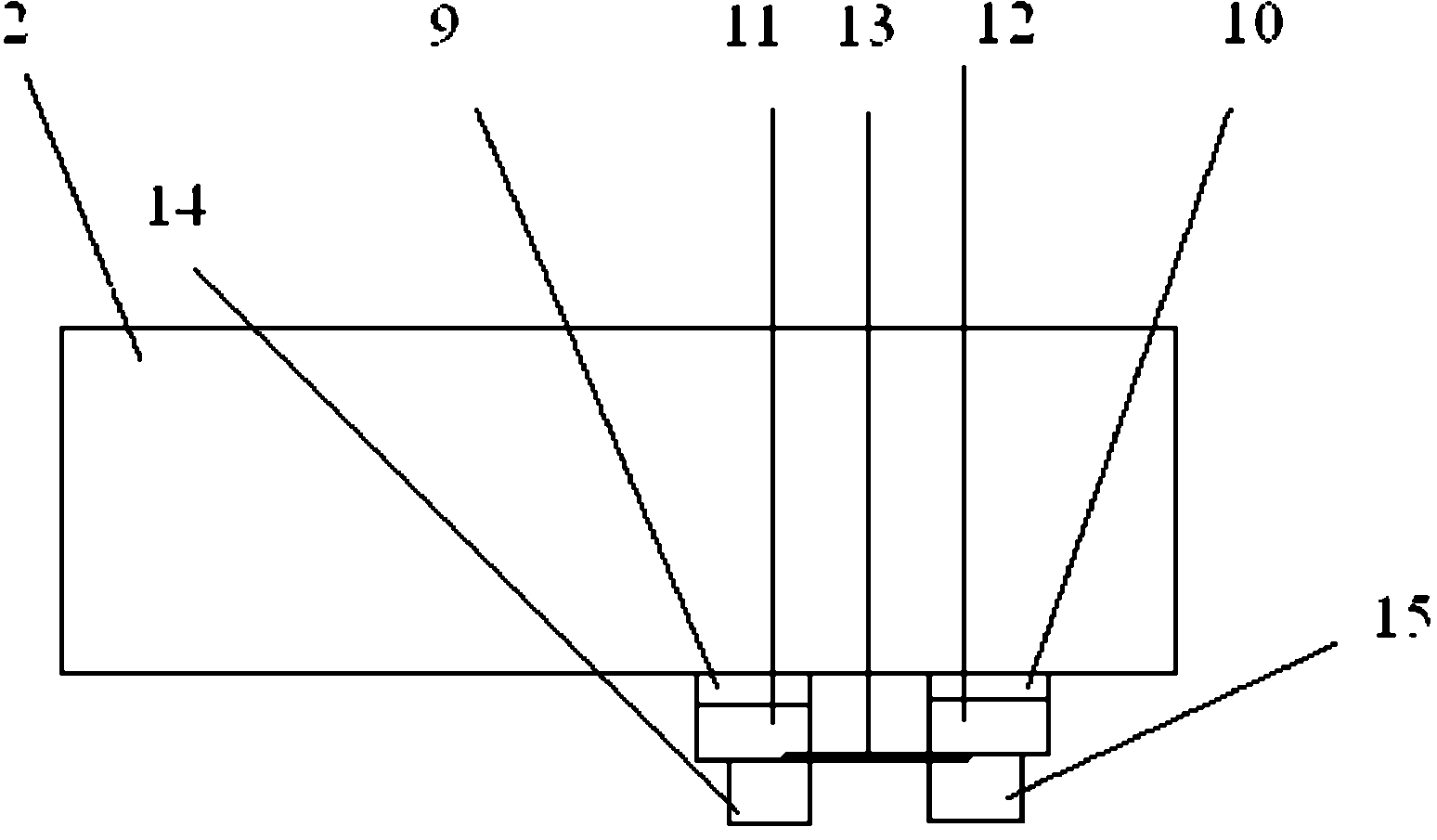

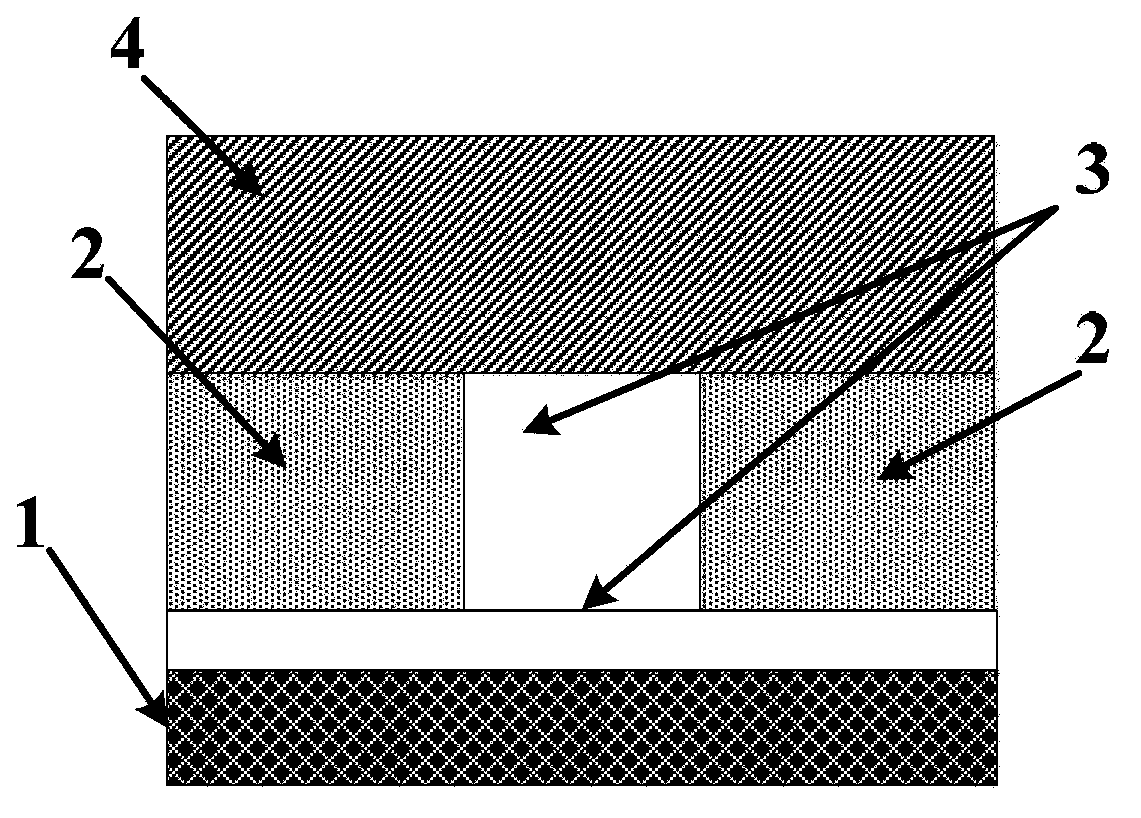

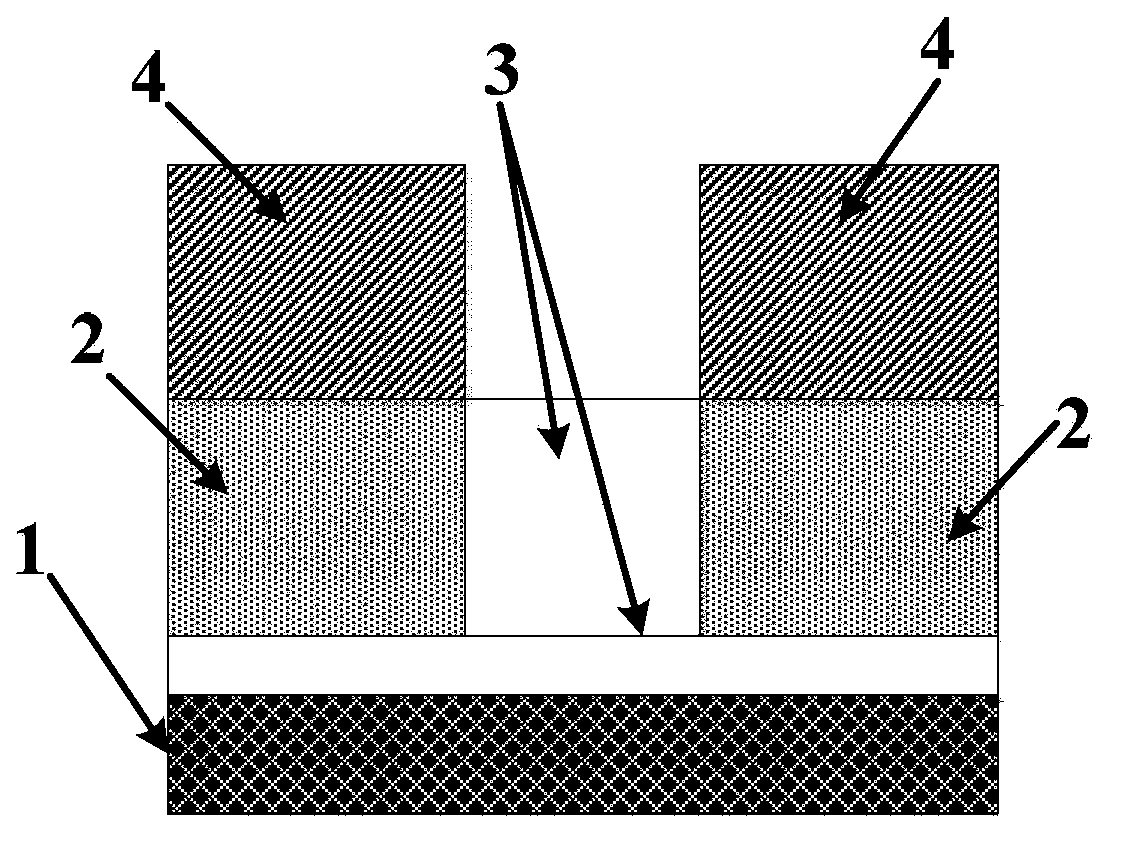

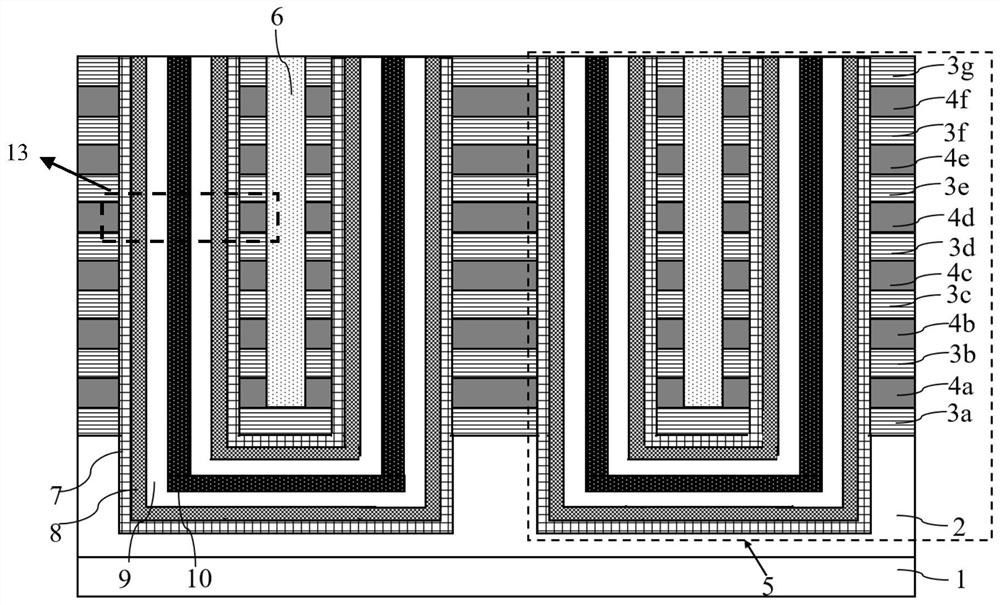

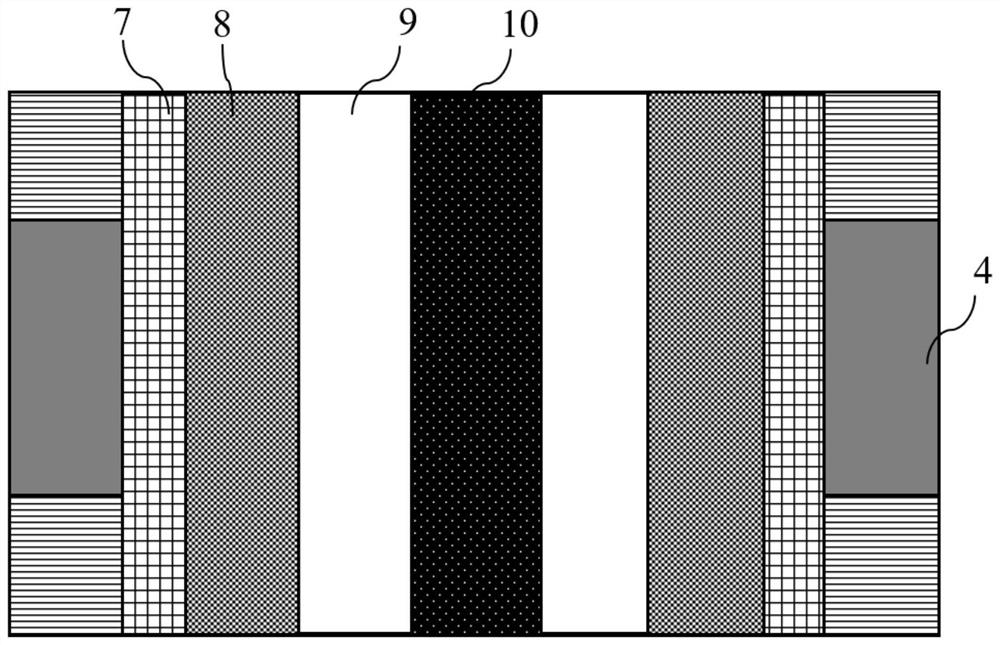

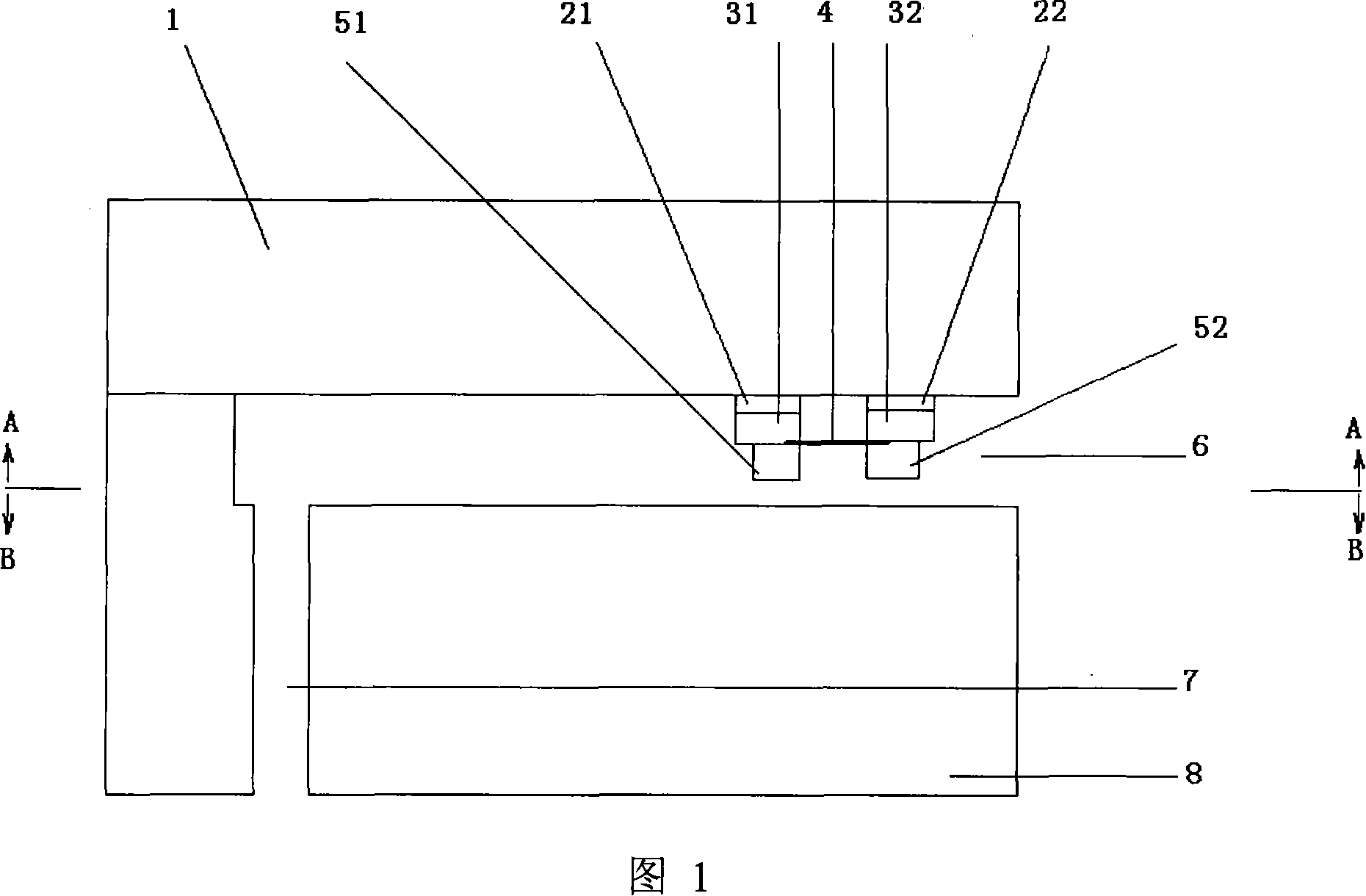

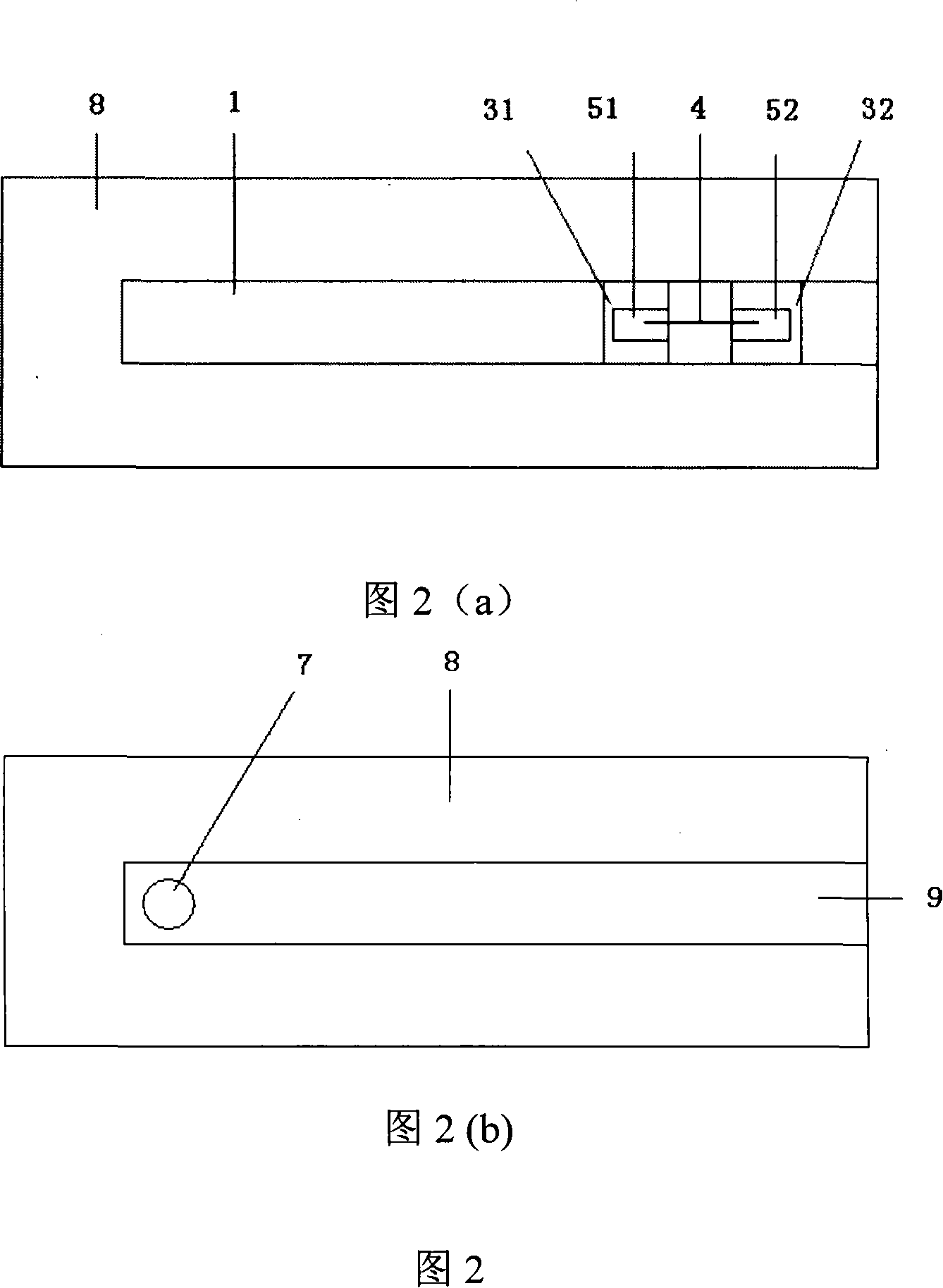

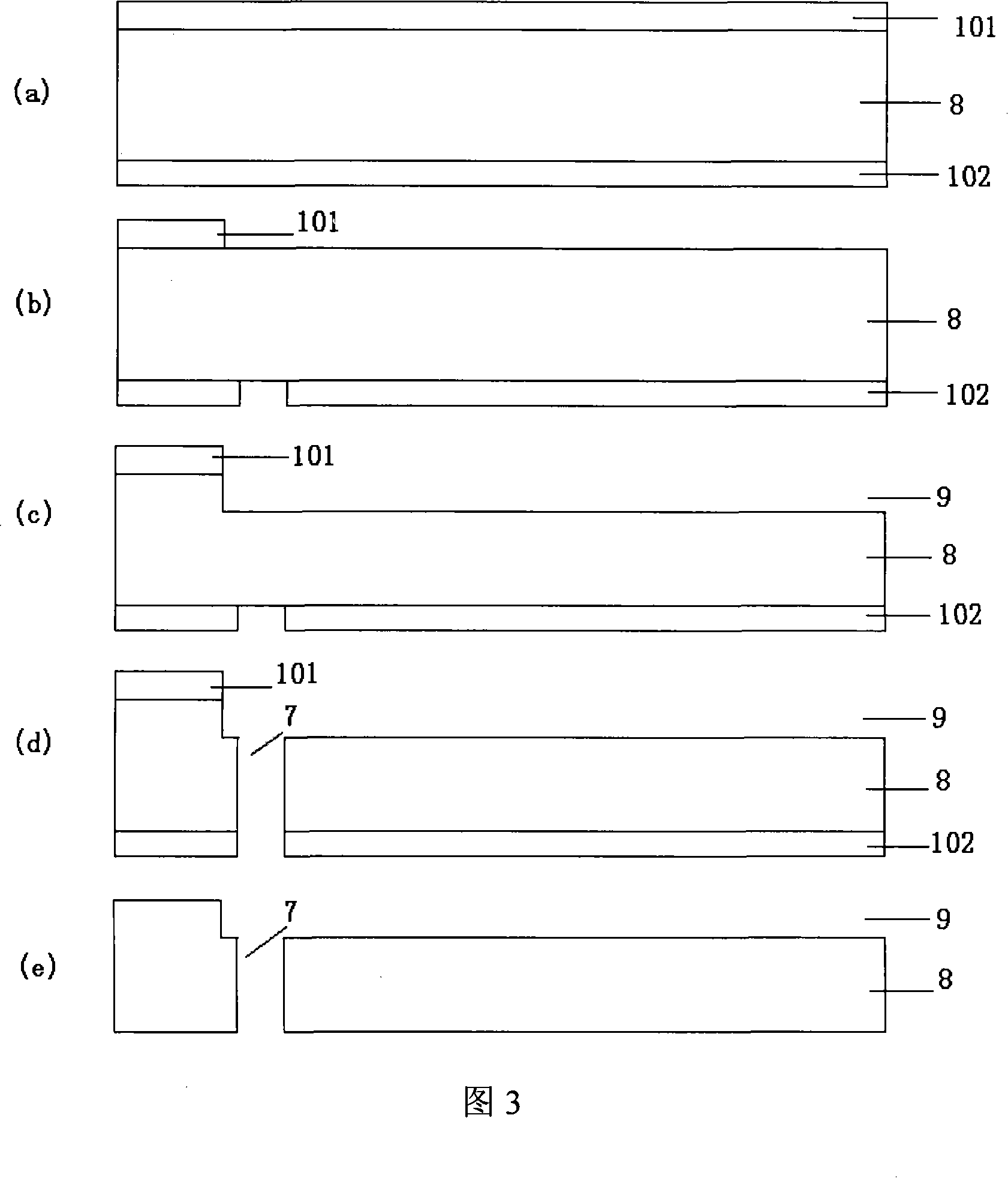

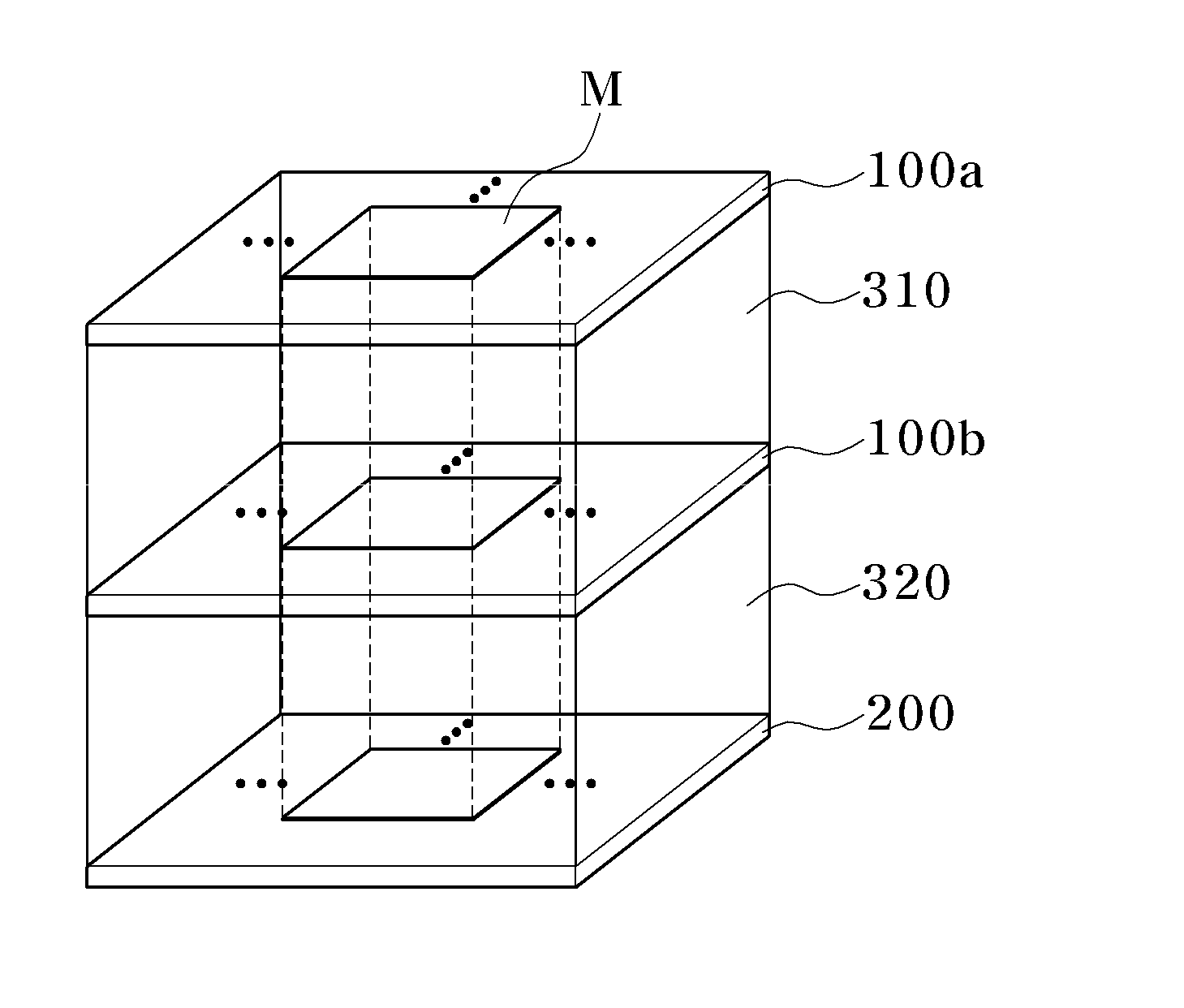

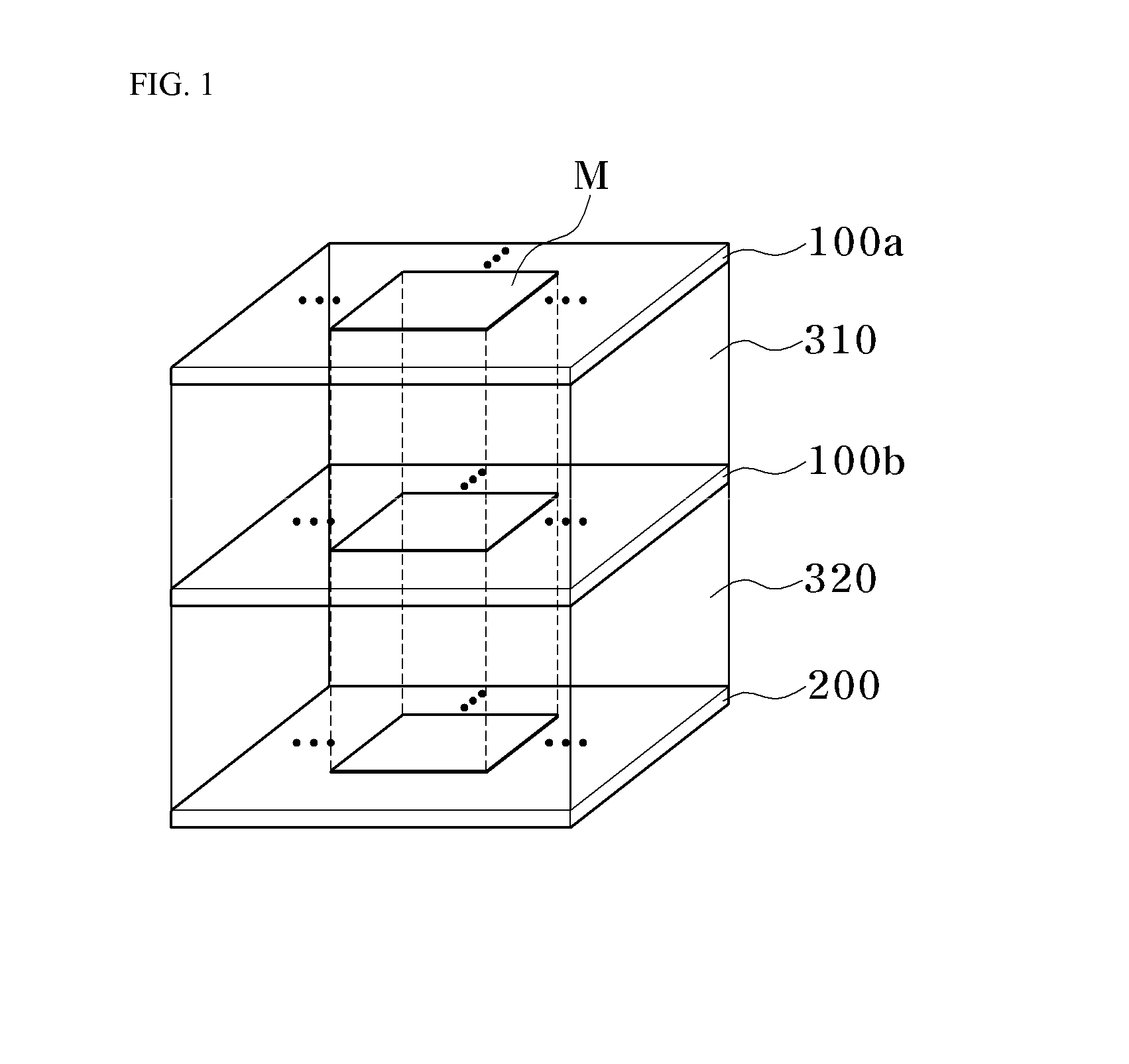

Three-dimensional NAND ferroelectric memory and preparation method thereof

PendingCN111799263ACompact wiringHigh density integrationTransistorSolid-state devicesFerroelectric thin filmsIsolation layer

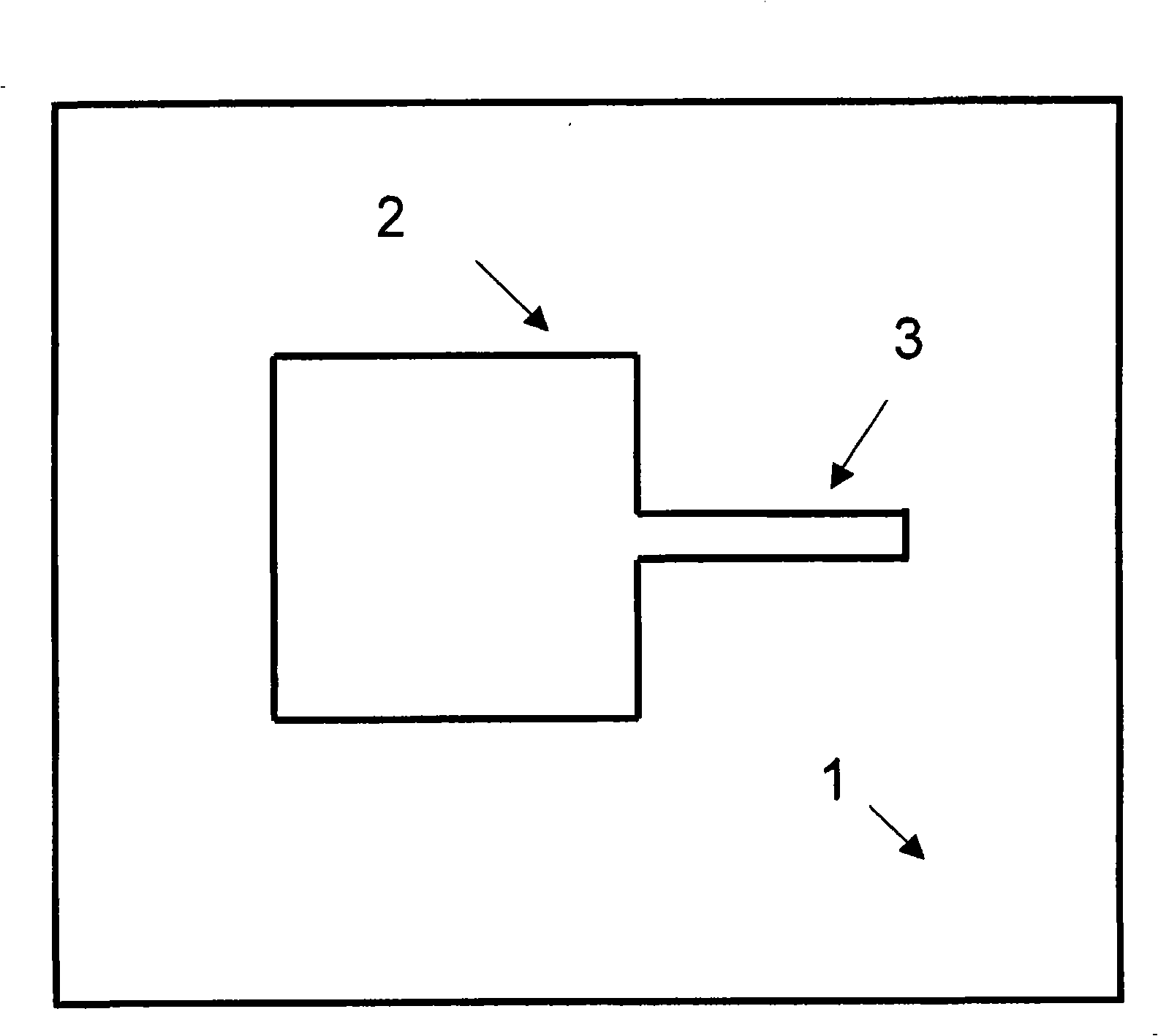

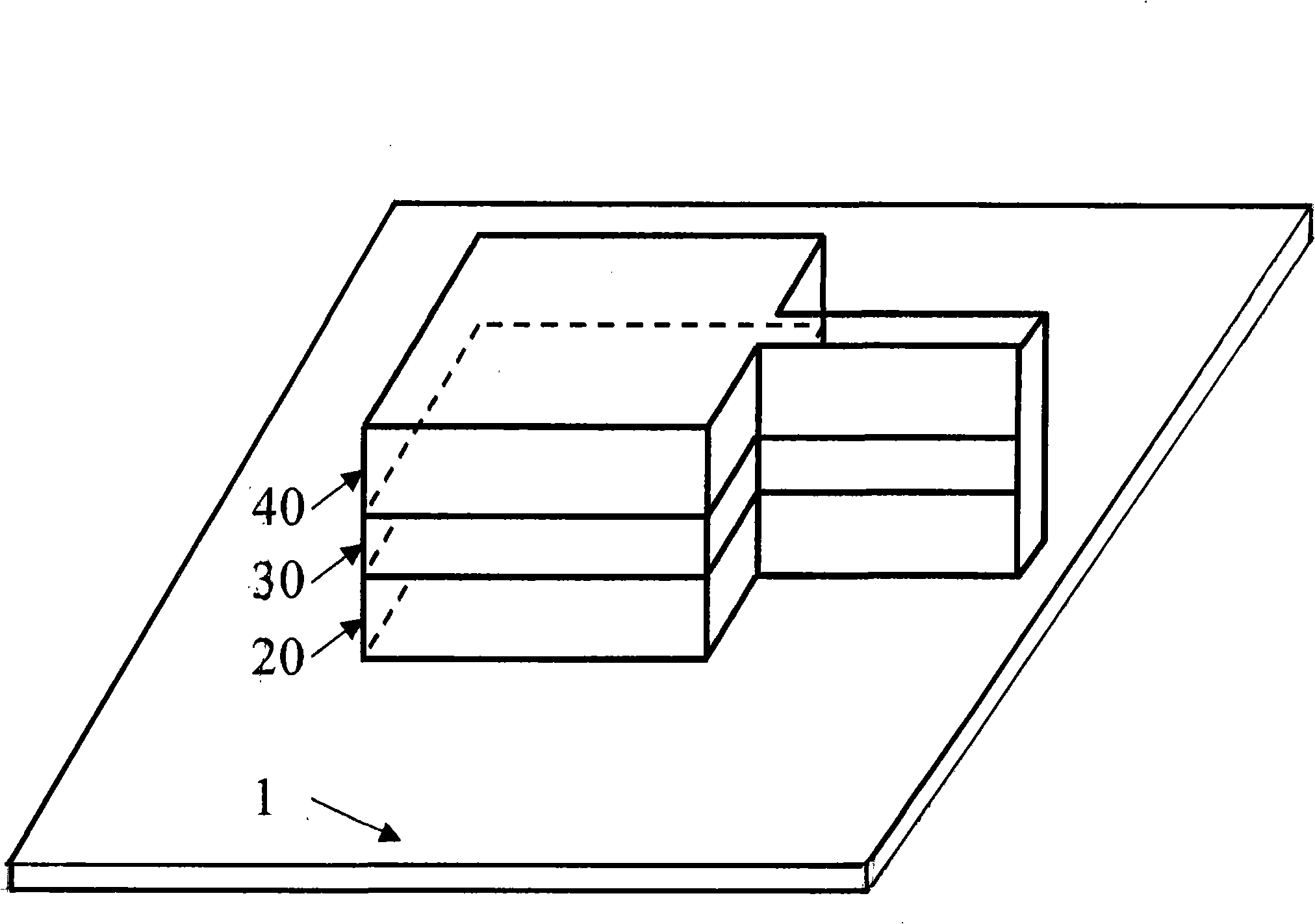

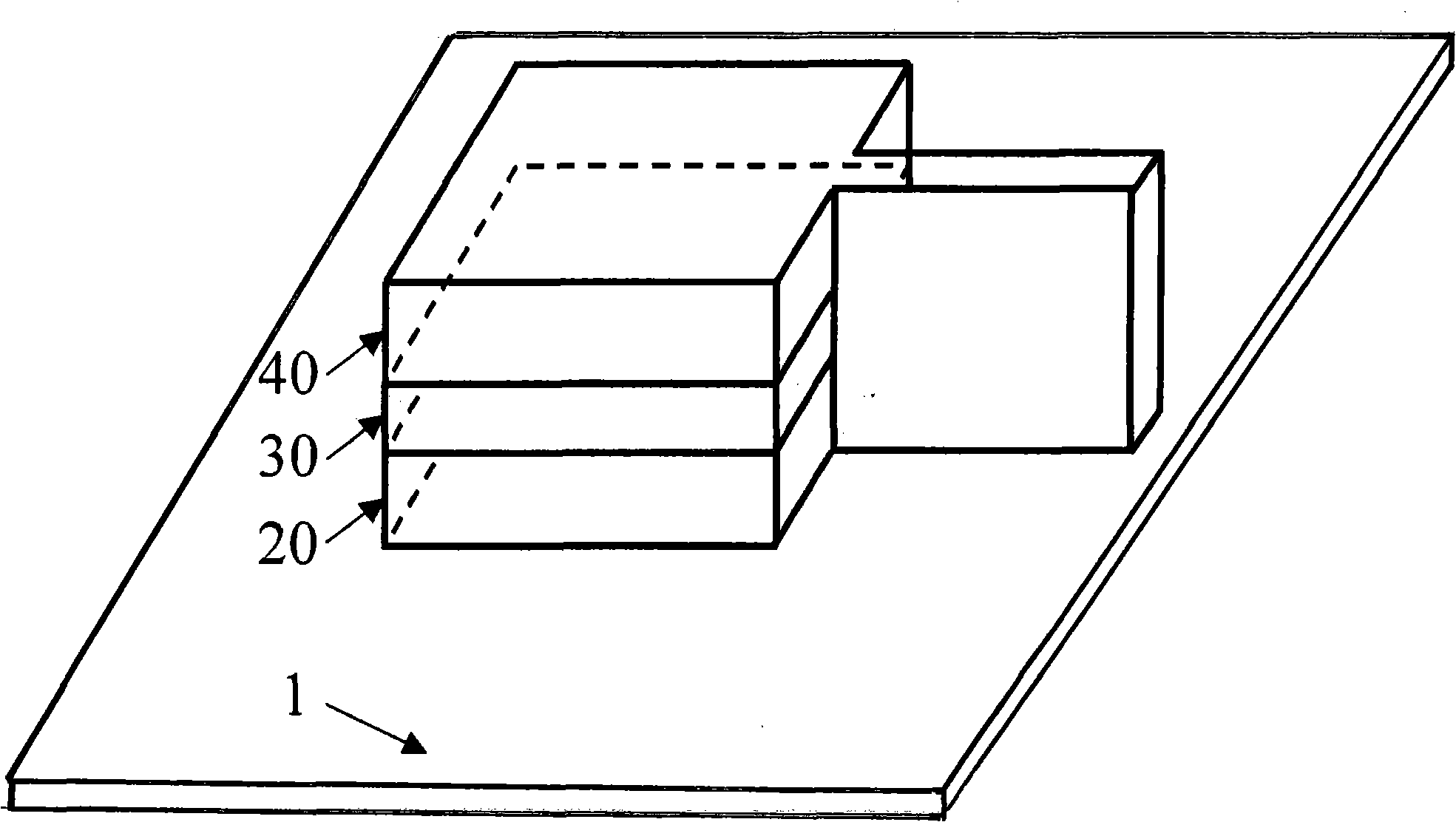

The invention discloses a three-dimensional NAND ferroelectric memory and a preparation method thereof, and the three-dimensional NAND ferroelectric memory comprises a substrate layer (1), a conductive layer (2) and a stacked layer which are sequentially stacked, and the stacked layer comprising a plurality of isolation layers and a plurality of control gate electrode layers which are stacked; anda plurality of channel groups, each channel group in the plurality of channel groups comprising two channels; the two channels being arranged in a manner of penetrating through the laminated layer; the bottom ends of the two channels being embedded into the conductive layer (2). The bottom ends of the two channels are communicated, a separation layer (6) for separating the control gate electrodelayers of the two channels is arranged between the two channels, and a buffer layer (7), a ferroelectric film layer (8), a channel layer (9) and a channel group (5) formed by connecting a plurality offerroelectric field effect transistors (13) in series are sequentially arranged on the inner walls of the channels. More compact wiring can be obtained through channel group arrangement of the memory, higher-density integration is realized, and the reliability is higher.

Owner:XIANGTAN UNIV

Jet printing valve based on carbon nano-tube tiny bubble generator and method of producing the same

InactiveCN101130300AOvercome the disadvantage of high power consumptionHigh density integrationPrintingMicro bubbleCarbon nanotube

The invention discloses a spraying and printing valve of micro bubble generator based on carbon nano-tube and the preparing method. The spraying and printing valve comprises glass substrate or silicon substrate of micro bubble generator with carbon nano-tube and silicon bottom substrate by micro machining. The micro bubble generator with carbon nano-tube is constituted by carbon nano-tube, two golden electrodes and silicon dioxide layer. The carbon nano-tube is set between two golden electrodes. The silicon dioxide layer is covered at the position where the carbon nano-tube is contacted with two golden electrodes. Via hole is set on the silicon bottom substrate as fluid inlet pipe and groove connected with the fluid inlet pipe is set on the surface of silicon bottom substrate. The substrate is bonded with the silicon bottom substrate so as to make the micro bubble generator with carbon nano-tube face to the groove to form nozzle. The preparing method is that the micro bubble generator with carbon nano-tube is prepared on the substrate; fluid inlet pipe and groove are prepared on the silicon bottom substrate; they are bonded together. The invention conquers the shortage that power consumption of conventional micro bubble generator is large and possesses the potentiality of good high density integration. The invention has a wide application prospect in advanced manufacturing field.

Owner:HUAZHONG UNIV OF SCI & TECH

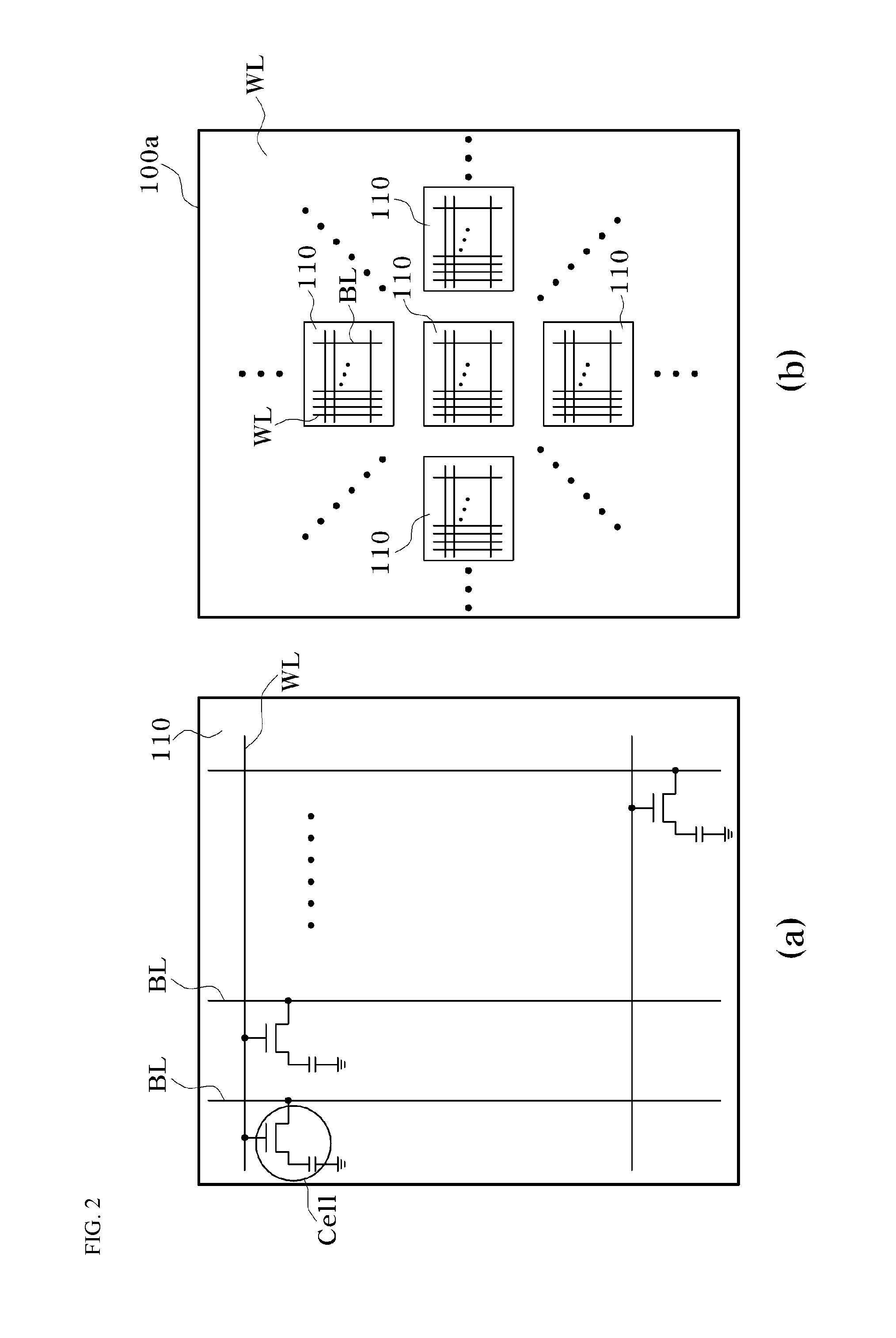

Stacked dynamic random access memory

ActiveUS20140119090A1High densityIncrease demandDigital storageStatic random-access memoryAudio power amplifier

A memory includes at least one first substrate on which unit memory arrays are disposed as a matrix type, each unit memory array including unit memory cells disposed in an array, a second substrate stacked with the at least one first substrate, the second substrate including a sense amplifier region in which sense amplifiers configured to sense information stored in the unit memory cells are disposed, and a plurality of vertical conduction traces configured to electrically connect the at least one first substrate with the second substrate. The sense amplifier region is disposed in a memory region of the second substrate, wherein the memory region of the second substrate corresponds to the memory region of the first substrate.

Owner:SEOUL NAT UNIV R&DB FOUND

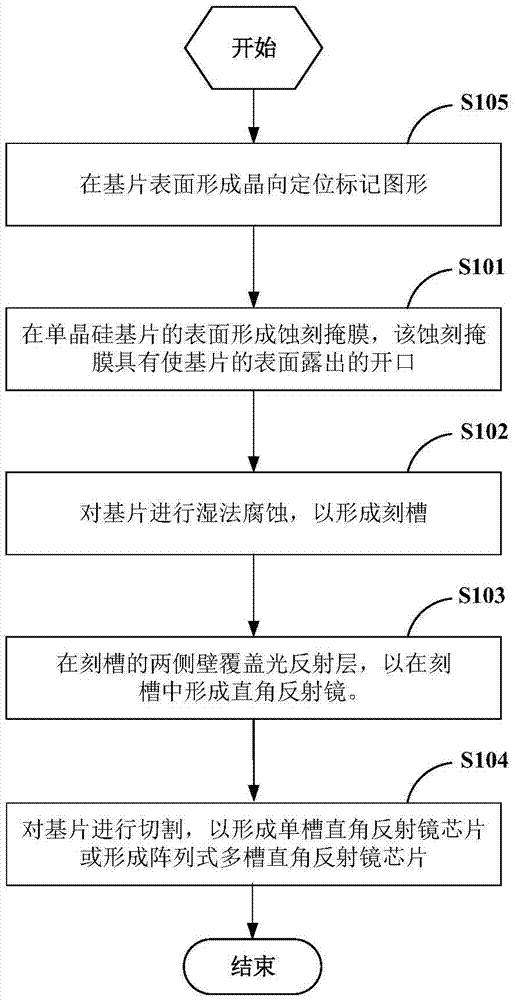

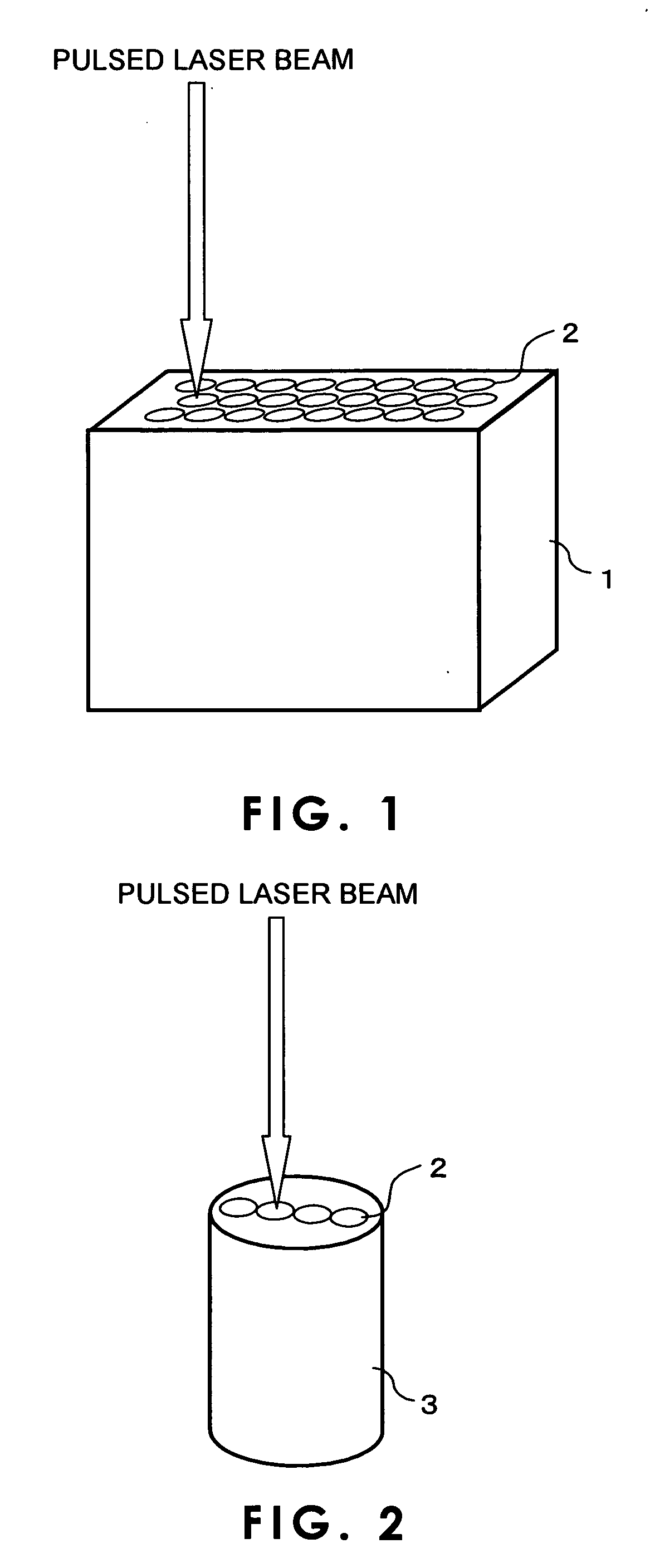

Optical right-angle reflector and manufacture method thereof

ActiveCN106986299AImprove manufacturing precisionLow manufacturing costTelevision system detailsImpedence networksMonocrystalline siliconOptical quality

The invention provides an optical right-angle reflector and a manufacture method thereof. The method is used for manufacturing the optical right-angle reflector on a monocrystal silicon substrate, and comprises the steps of forming an etching mask on the surface of the substrate, wherein the etching mask comprises an opening for exposing the surface of the substrate, and the substrate is the monocrystal silicon substrate; wet etching the substrate with the etching mask to form an etched groove, wherein the etched groove at least comprises two side walls perpendicular to each other, the two side walls are silicon (110) crystal faces, and an included angle between each of the two side walls and the surface of the substrate is 45 degrees; and covering optical reflecting layers on the two side walls of the etched groove to form the right-angle reflector in the etched groove. The optical right-angle reflector manufactured according to the method provided by the invention is good in optical quality, high in precision, small in size and low in cost, a multi-groove right-angle reflector array can be conveniently manufactured, and thus the right-angle reflectors with large area can be acquired.

Owner:ANHUI CHINA SCI MW ELECTRONIC TECH CO LTD

Optical connector and method of manufacturing the optical connector

InactiveUS20050254769A1Improve productivityImprove manufacturing precisionCoupling light guidesLaser beam welding apparatusFiber arrayEngineering

An optical connector capable of providing a multicore ferrule for optical communication or a fiber array for optical communication having a high dimensional accuracy and easily manufactured at a low cost, comprising a plurality of insert holes for inserting optical fibers therein arranged at specified intervals, characterized in that the accuracy of the center-to-center distances between the adjacent insert holes is within ±0.5 μm and a parallelism between the adjacent insert holes in hole axial direction is within ±0.1°.

Owner:KOHOKU KOGYO CO LTD

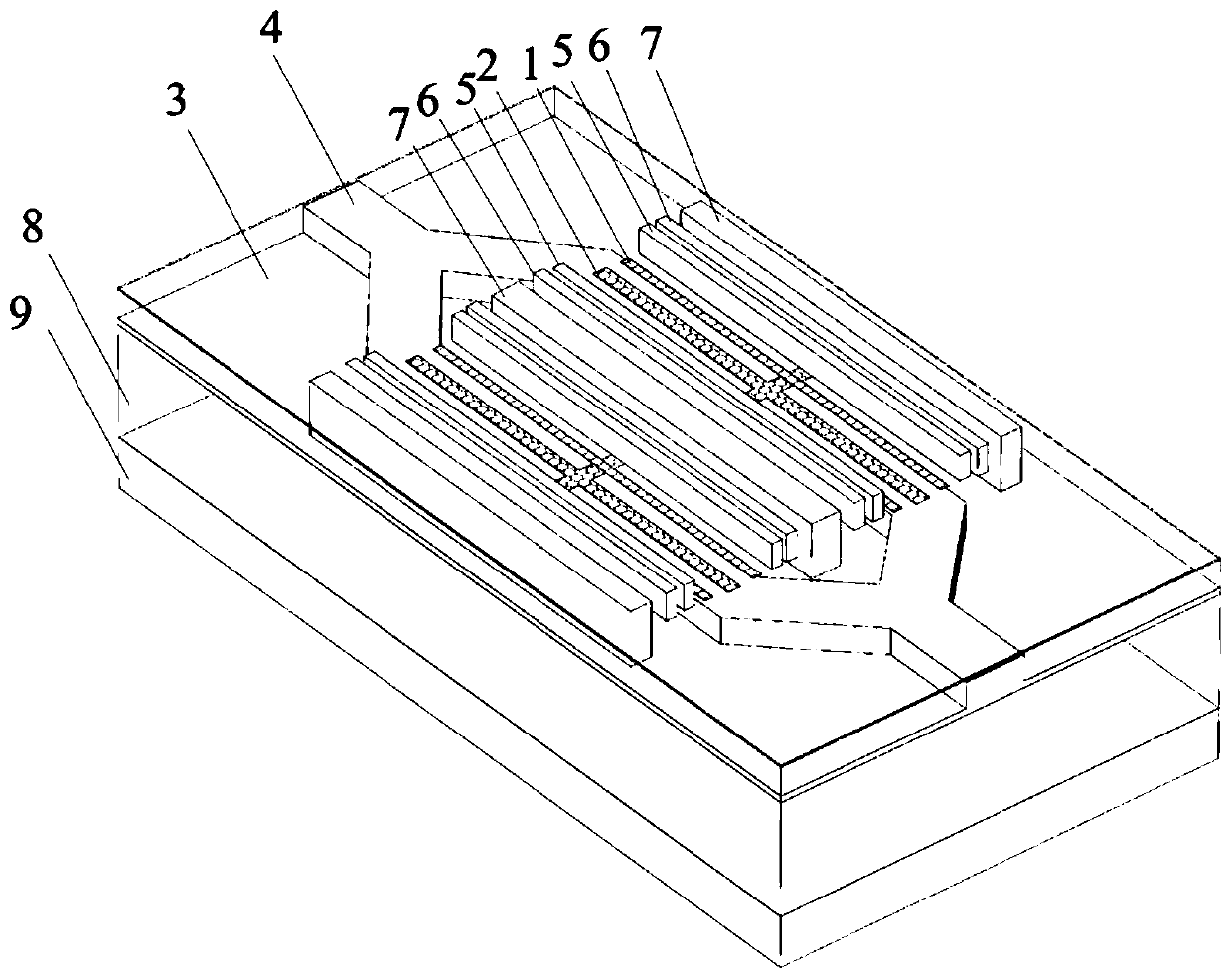

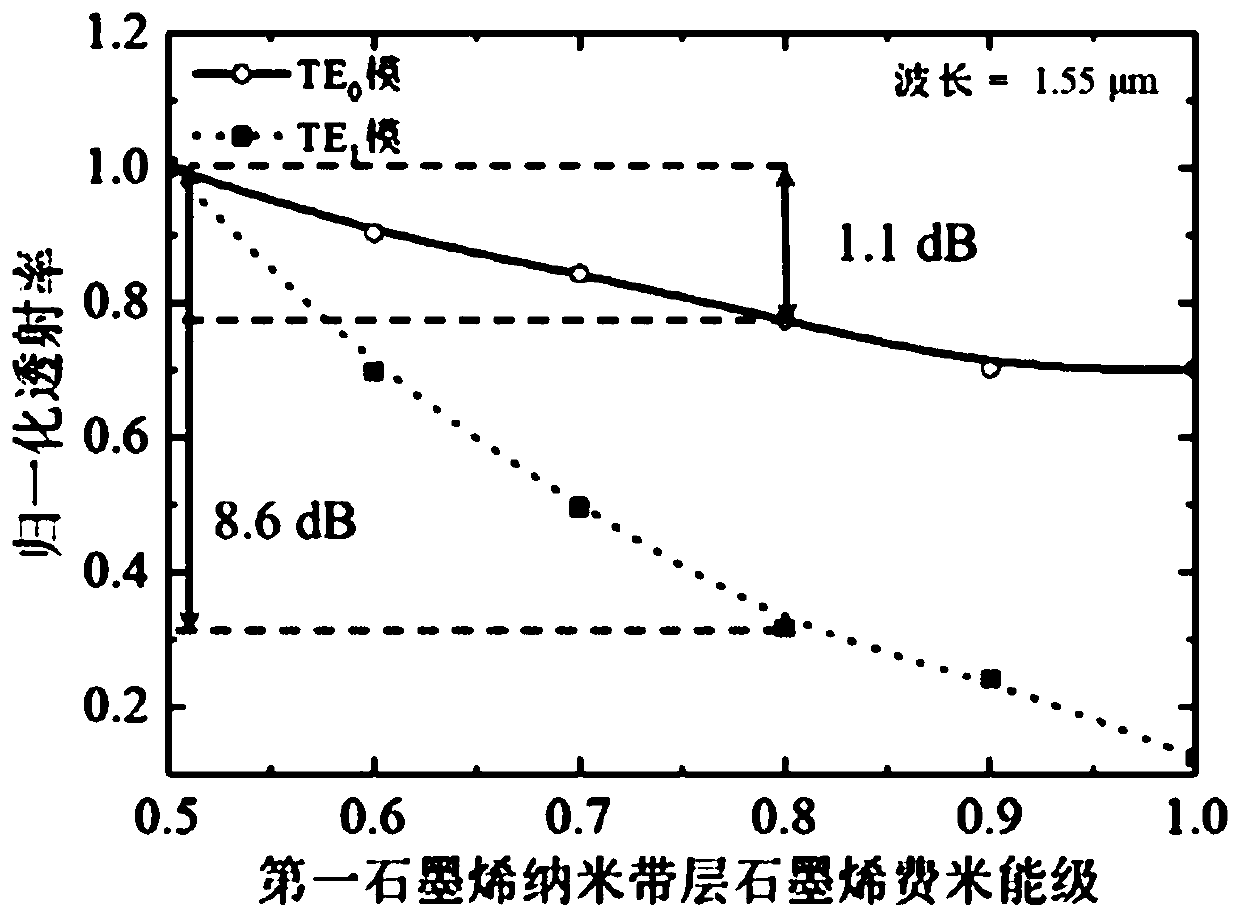

Graphene-based waveguide integrated multimode electro-optic modulator and manufacturing method thereof

ActiveCN110221385AHighly integratedReduce in quantityOptical waveguide light guideGraphene nanoribbonsEngineering

The invention discloses a graphene-based waveguide integrated multimode electro-optic modulator and a manufacturing method thereof. The modulator comprises a first graphene nanoribbon layer, a secondgraphene nanoribbon layer, an insulator cladding, a multimode ridge waveguide, a first electrode pair, a second electrode pair, a third electrode pair, an insulating layer and a substrate layer, wherein the multimode ridge waveguide supports two transverse electric modes (TE), that is, a TE0 mode and a TE1 mode are simultaneously transmitted; the first graphene nanoribbon layer and the second graphene nanoribbon layer are integrated above the multimode ridge waveguide; the insulator cladding is used to achieve electrical isolation of the multimode ridge waveguide from the first graphene nanoribbon layer and the second graphene nanoribbon layer; the first electrode pair is connected to the first graphene nanoribbon layer, the second electrode pair is connected to the second graphene nanoribbon layer, and the third electrode pair is coupled to the multimode ridge waveguide for providing a back gate voltage to the graphene.

Owner:TIANJIN UNIV