Source-field-plate heterojunction field-effect transistor and manufacturing method thereof

A heterojunction field effect and source field plate technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the complex manufacturing process of heterojunction field effect transistors, the reduction of device yield and uniformity, Can not completely shield the gate-drain capacitance and other problems, to achieve the effect of high yield, improved power gain characteristics, and easy implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

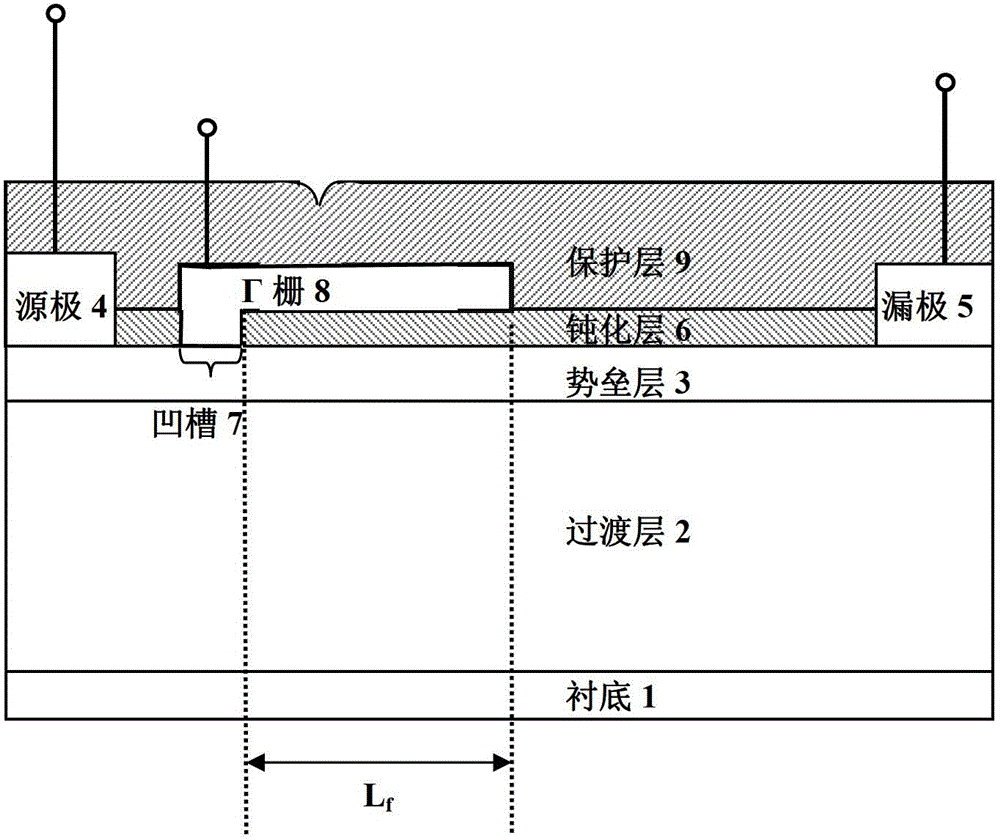

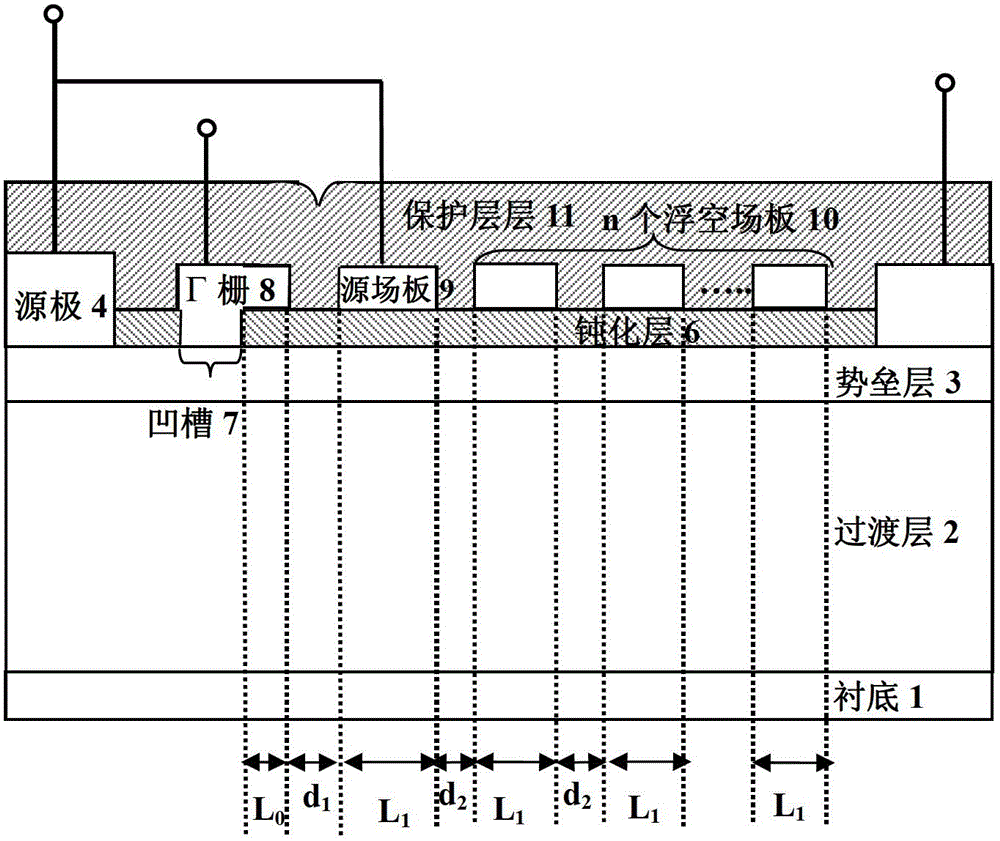

Problems solved by technology

Method used

Image

Examples

Embodiment 1

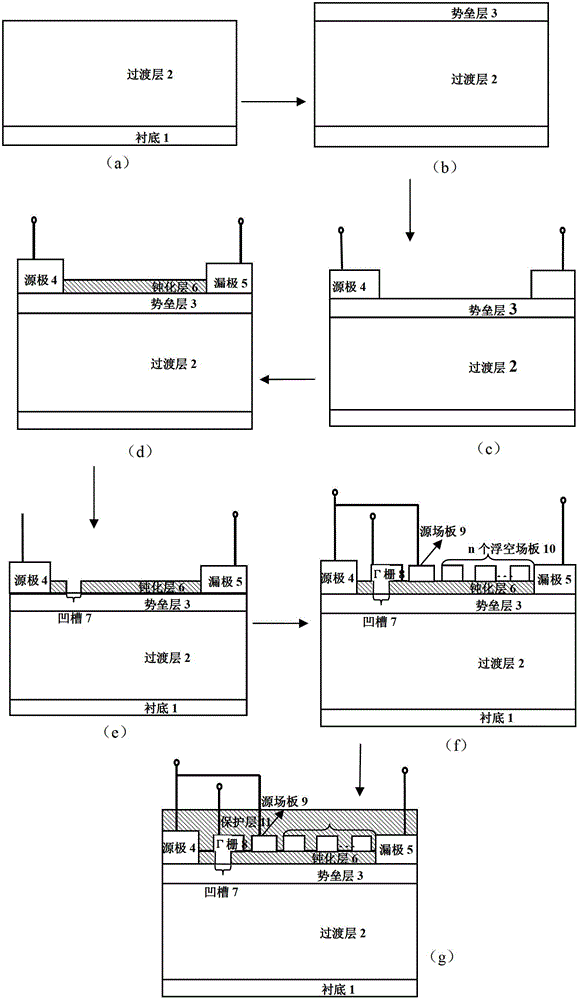

[0052] Embodiment 1: Made on a SiC substrate, the passivation layer medium is SiN, the protective layer is SiN, the Γ grid, the source field plate and the floating metal field plate are metal stacks composed of Ni and Au from bottom to top A source field plate heterojunction field effect transistor, the steps of which include the following:

[0053] The first step is to grow 100nm AlN at 1050°C on the SiC substrate using metal organic chemical vapor deposition technology MOCVD, and then grow a 1μm unintentionally doped GaN layer at 1000°C to form a buffer layer 2 .

[0054] In the second step, a barrier layer 3 with a thickness of 27 nm is deposited on the buffer layer 2 by metal organic chemical vapor deposition technique MOCVD. The barrier layer is composed of 1.2nm thick AlN, 25nm thick AlGaN layer with 27% Al composition and 0.8nm GaN layer from bottom to top. The temperature of layer AlGaN is 1110°C, and the temperature of deposition of top layer GaN is 1110°C.

[0055...

Embodiment 2

[0068] Embodiment 2: making passivation layer medium on sapphire substrate is Al 2 o 3 , the protective layer is AlN, the Γ gate, the source field plate and the floating metal field plate are a source field plate heterojunction field effect transistor composed of metal stacks composed of Pt and Au from bottom to top.

[0069] The production steps of this example are as follows:

[0070] Step A, on the sapphire substrate, use metal organic chemical vapor deposition technology MOCVD, first grow 100nm AlN at 1050°C, and then grow 2.5μm unintentionally doped AlGaN layer at 1000°C, Al composition 10 %, forming a buffer layer (2).

[0071] In step B, a barrier layer 3 with a thickness of 27 nm is deposited on the buffer layer 2 by metal organic chemical vapor deposition technique MOCVD. The barrier layer is composed of 1.2nm-thick AlN, 25nm-thick AlGaN layer with Al composition of 40% and 0.8nm GaN layer from bottom to top. The temperature of the AlGaN layer is 1110°C, and the t...

Embodiment 3

[0079] Embodiment 3: Making a passivation layer medium on a GaN substrate is HfO 2 , the protective layer is SiO 2 , The Γ gate, the source field plate and the floating metal field plate are source field plate heterojunction field effect transistors composed of Ni, Au and Ni metal stacks from bottom to top.

[0080] The steps in this example are as follows:

[0081] Step 1: On the GaN substrate, use metal organic chemical vapor deposition technology MOCVD to grow 100nm AlN at 1050°C, and then grow a 4μm unintentionally doped GaN layer at 1000°C to form a buffer layer 2 .

[0082] In the second step, a barrier layer 3 with a thickness of 9 nm is deposited on the buffer layer 2 by metal organic chemical vapor deposition technique MOCVD.

[0083] The barrier layer is 1nm thick AlN and 8nm thick InAlN layer with 83% Al composition from bottom to top; the temperature for growing the AlN layer is 1000°C, and the temperature for growing the top layer InAlN is 750°C.

[0084] The ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More