Patents

Literature

103results about How to "Raise the barrier height" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

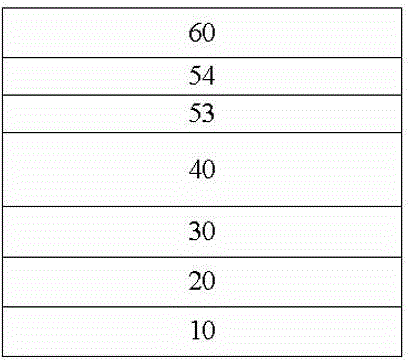

Application Year

Inventor

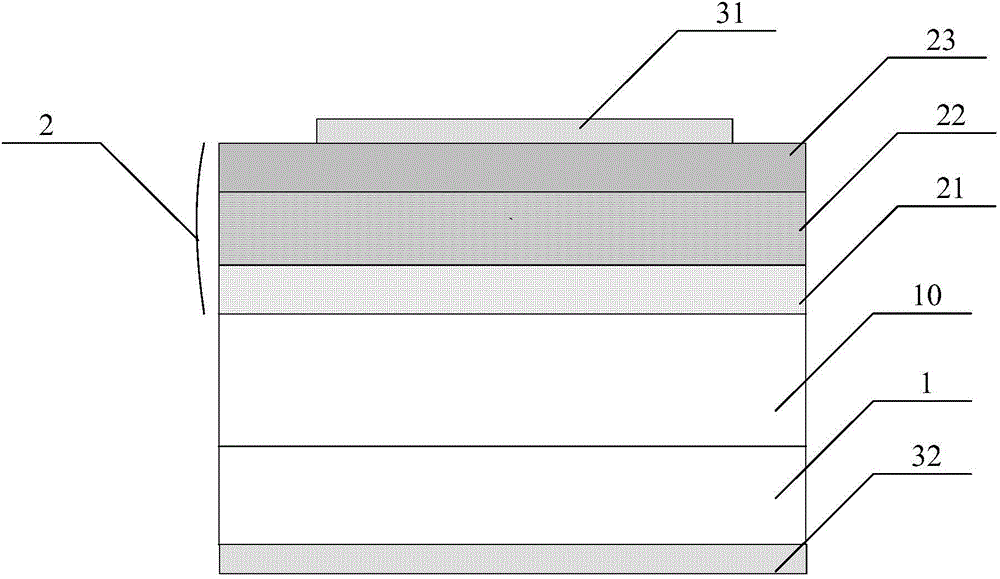

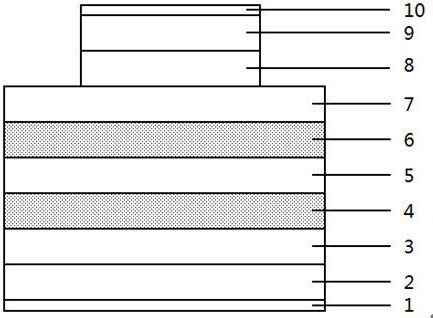

Method of fabricating light-emitting device and light-emitting device

InactiveUS20050285127A1Enhance carrier confinement effectImprove internal quantum efficiencySemiconductor/solid-state device detailsSolid-state devicesContact layerLattice constant

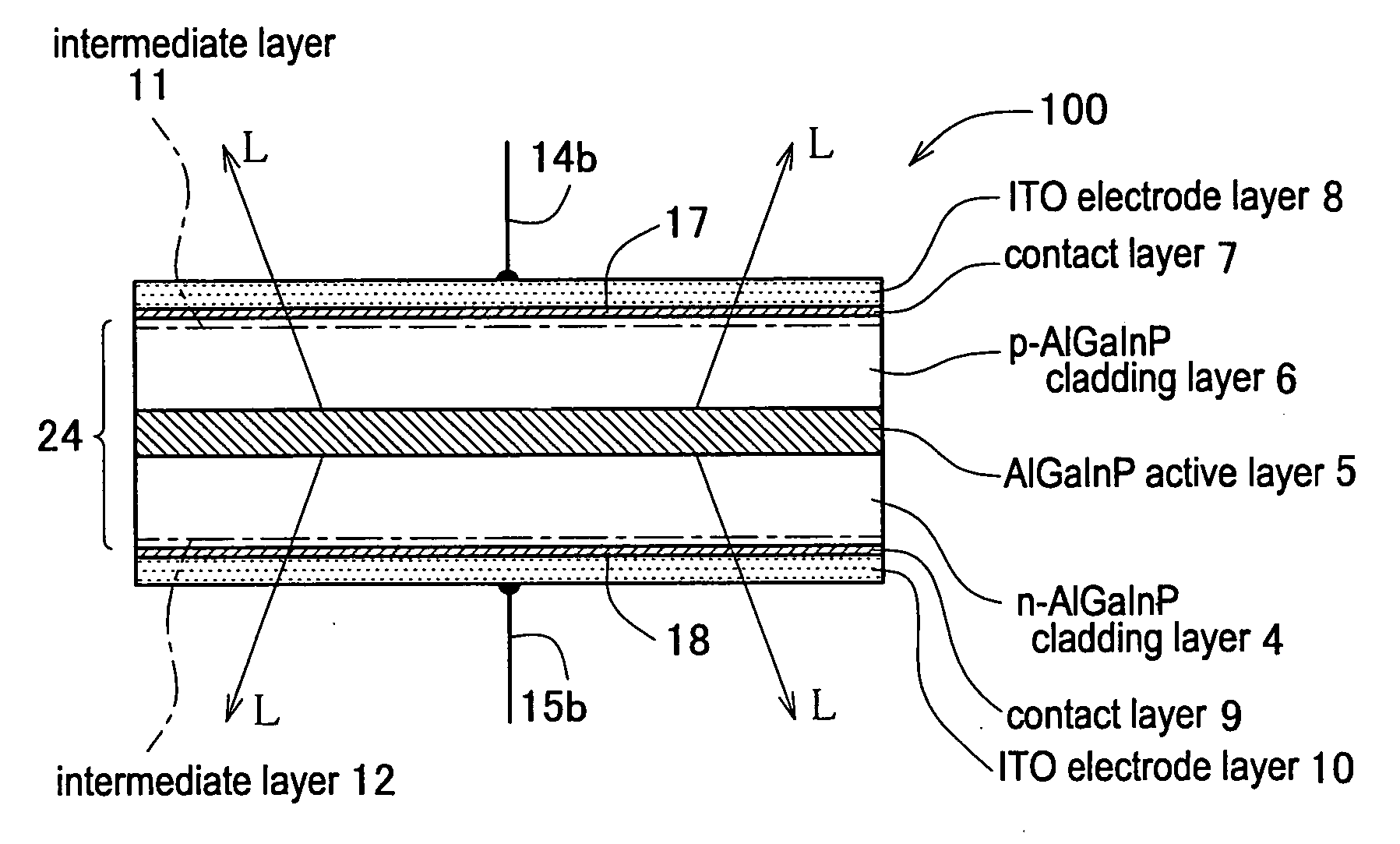

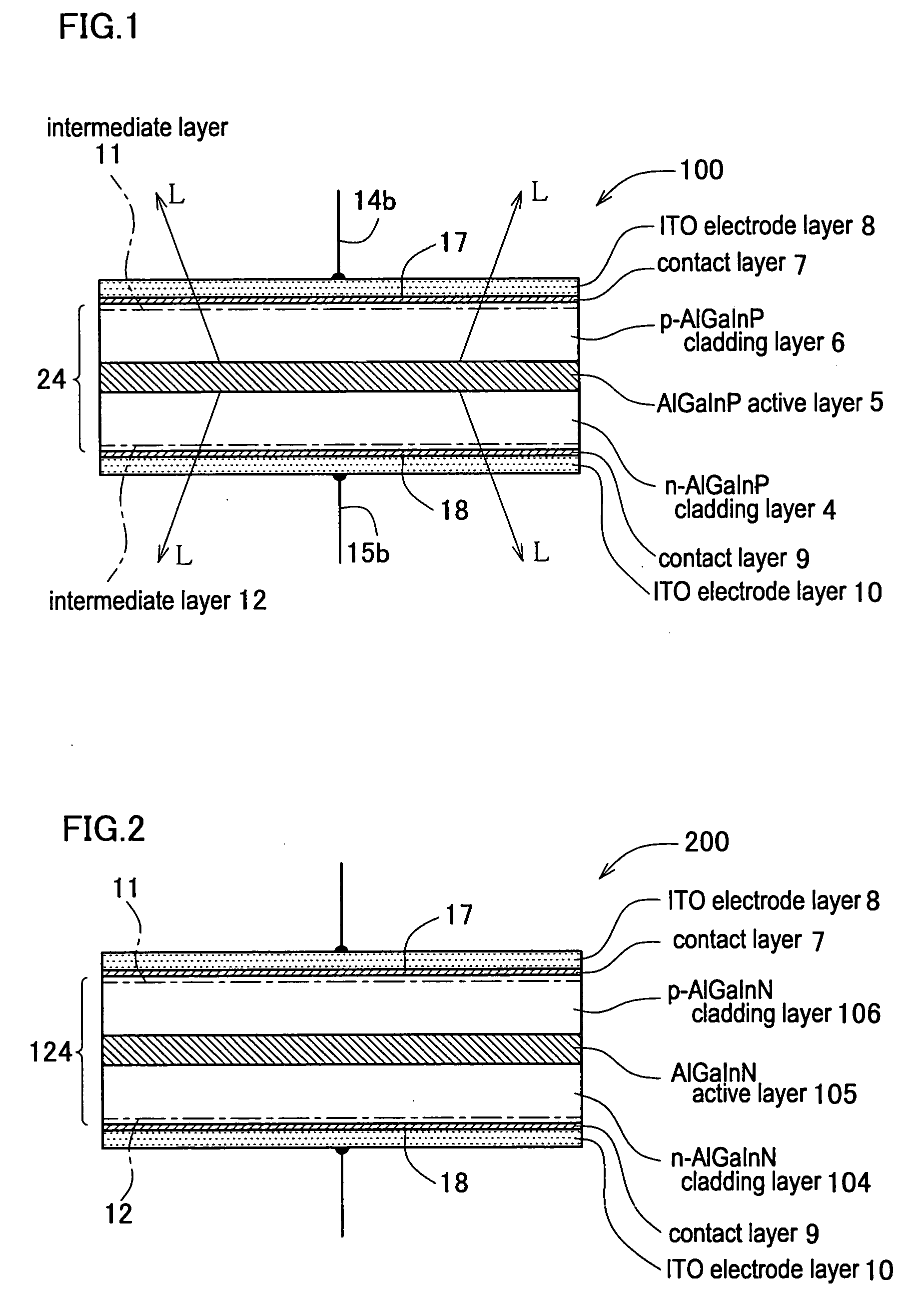

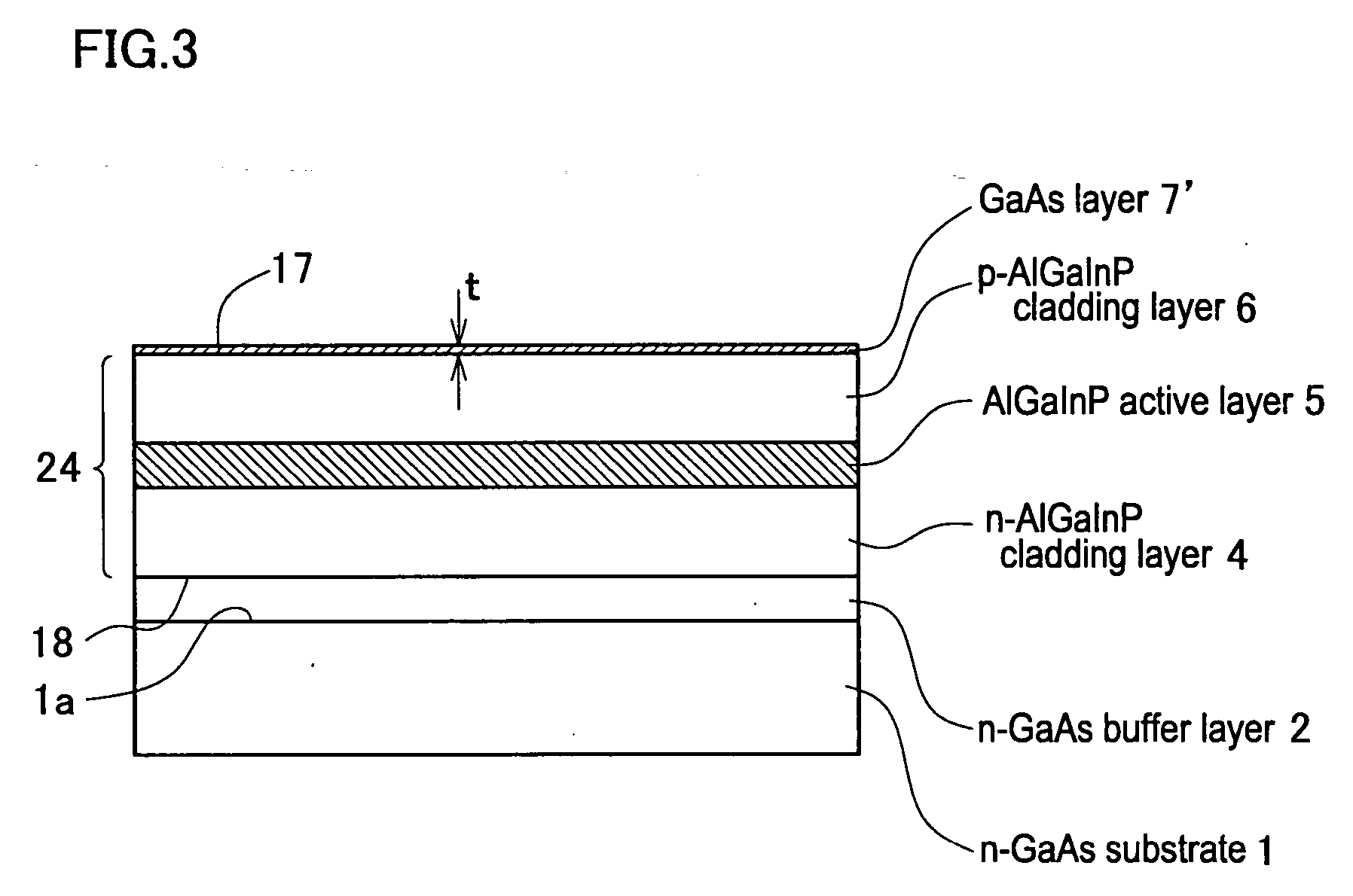

A light-emitting device 100 has ITO transparent electrode layers 8, 10 used for applying drive voltage for light-emission to a light-emitting layer section 24, and is designed so as to extract light from the light-emitting layer section 24 through the ITO transparent electrode layers 8, 10. The light-emitting device 100 also has contact layers composed of In-containing GaAs, formed between the light-emitting layer section 24 and the ITO transparent electrode layers 8, 10, so as to contact with the ITO transparent electrode layers respectively. The contact layers 7, 9 are formed by annealing a stack 13 obtained by forming GaAs layers 7′, 9′ on the light-emitting layer section, and by forming the ITO transparent electrode layers 8, 10 so as to contact with the GaAs layers 7′, 9′, to thereby allow In to diffuse from the ITO transparent electrode layers 8, 10 into the GaAs layers 7′, 9′. This provides a method of fabricating a light-emitting device, in which the ITO transparent electrode layers as the light-emission drive electrodes are bonded as being underlain by the contact layers, to thereby reduce contact resistance of these electrodes, and to thereby make the contact layers less susceptible to difference in the lattice constants with those of the light-emitting layer section during the formation thereof.

Owner:SHIN-ETSU HANDOTAI CO LTD

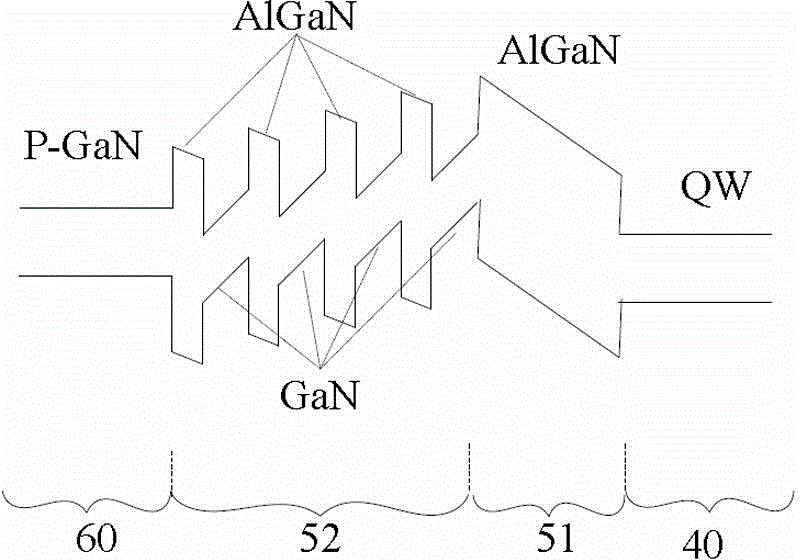

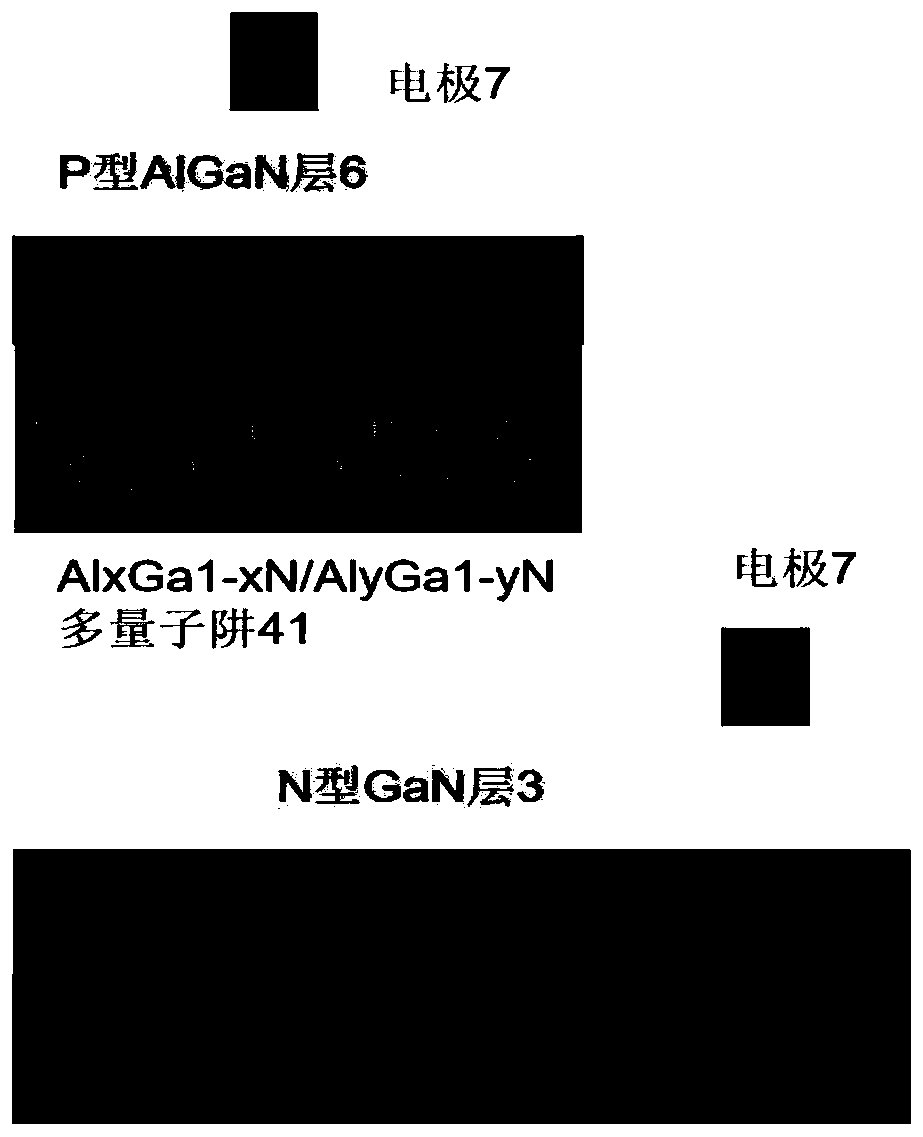

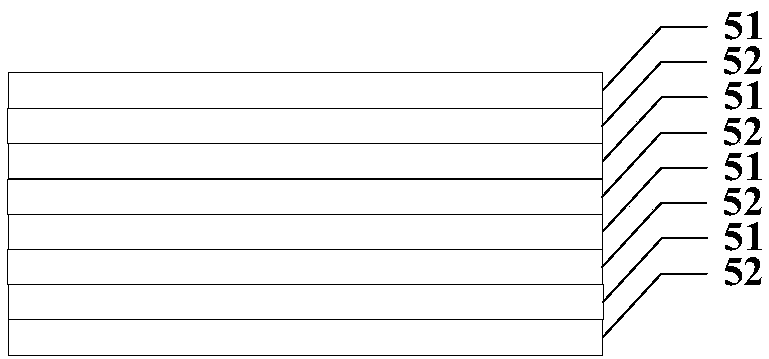

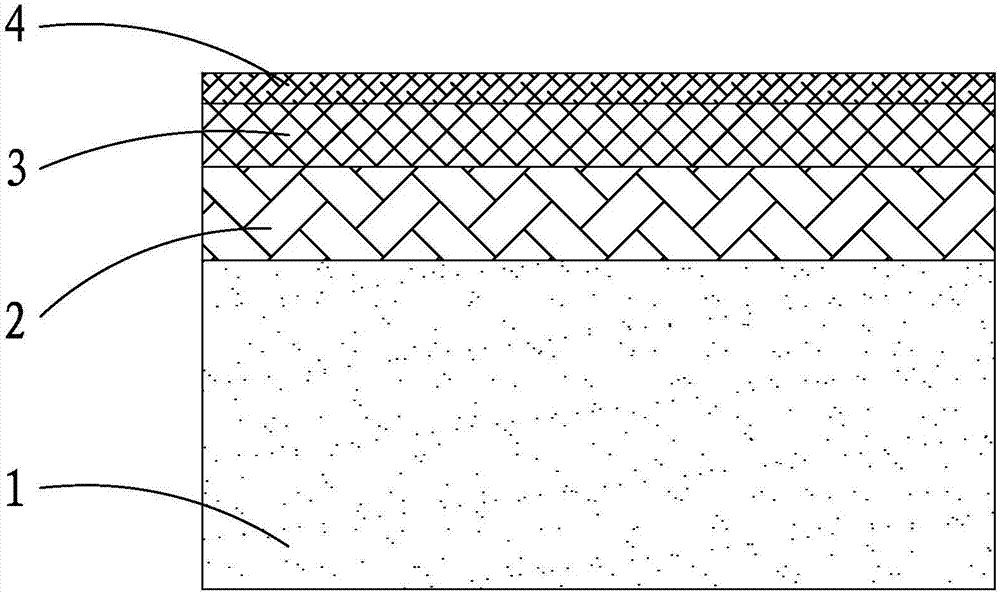

Light-emitting diode epitaxial wafer and manufacture method thereof

ActiveCN103681985ARaise the barrier heightImprove injection efficiencySemiconductor devicesQuantum efficiencyNon doped

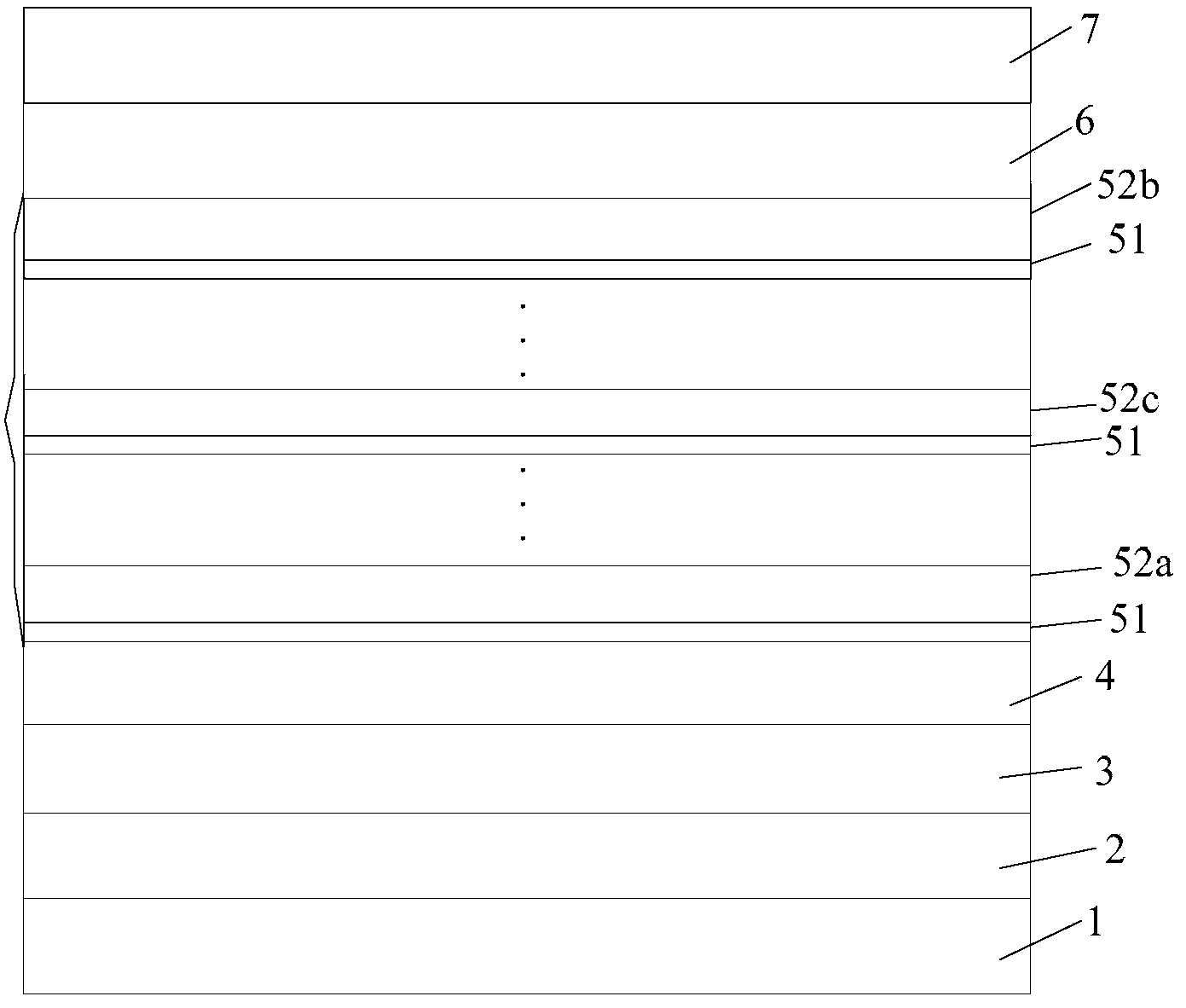

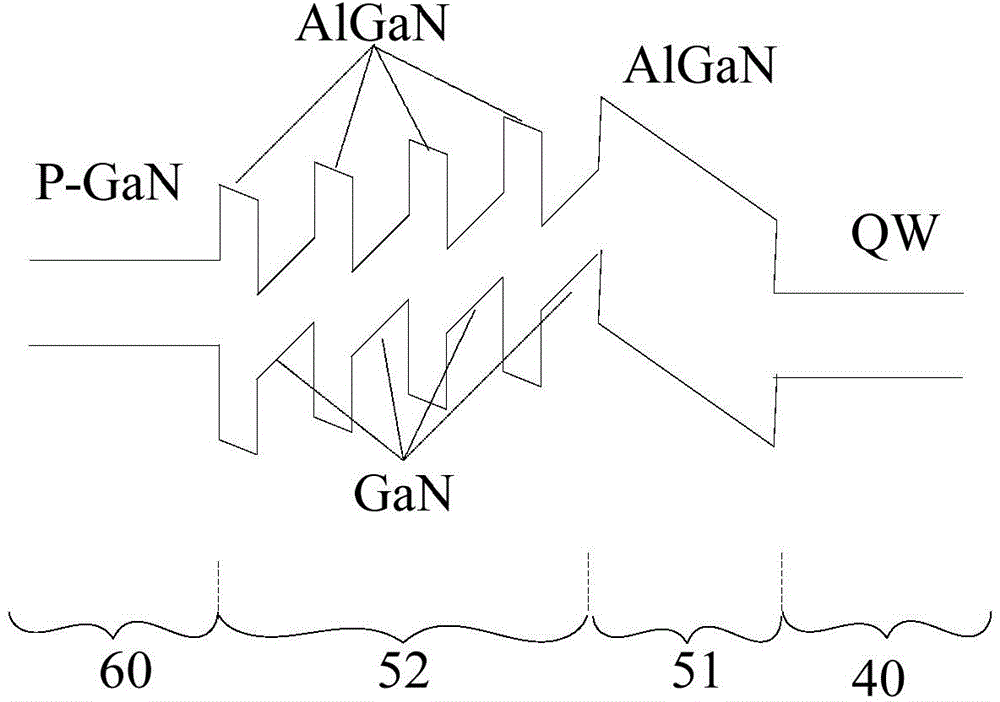

The invention discloses a light-emitting diode epitaxial wafer and a manufacture method thereof and belongs to the field of semiconductor technology. The epitaxial wafer comprises a substrate, a low-temperature buffer layer grown on the substrate, a non-doped gallium nitride layer, a type-N gallium nitride layer, a multiple-quantum well layer and a type-P gallium nitride layer. At least one quantum barrier from one side of the type-N gallium nitride layer is grown by AlxGa1-xN; 0<x<0.3. At least one quantum barrier layer from one side of the type-P gallium nitride layer is grown by InzGa1-zN; 0<z<0.15. The type-P gallium nitride layer is directly grown on the multiple-quantum well layer. The quantum barrier layers close to the type-N gallium nitride layer are provided with high potential barrier, the quantum barrier layers close to the type-P gallium nitride layer are provided with low potential barrier, electron overflow is reduced, hole injection efficiency is improved, more electrons and holes are composited in the quantum well layer, and internal quantum efficiency of the light-emitting diode is improved accordingly.

Owner:HC SEMITEK SUZHOU

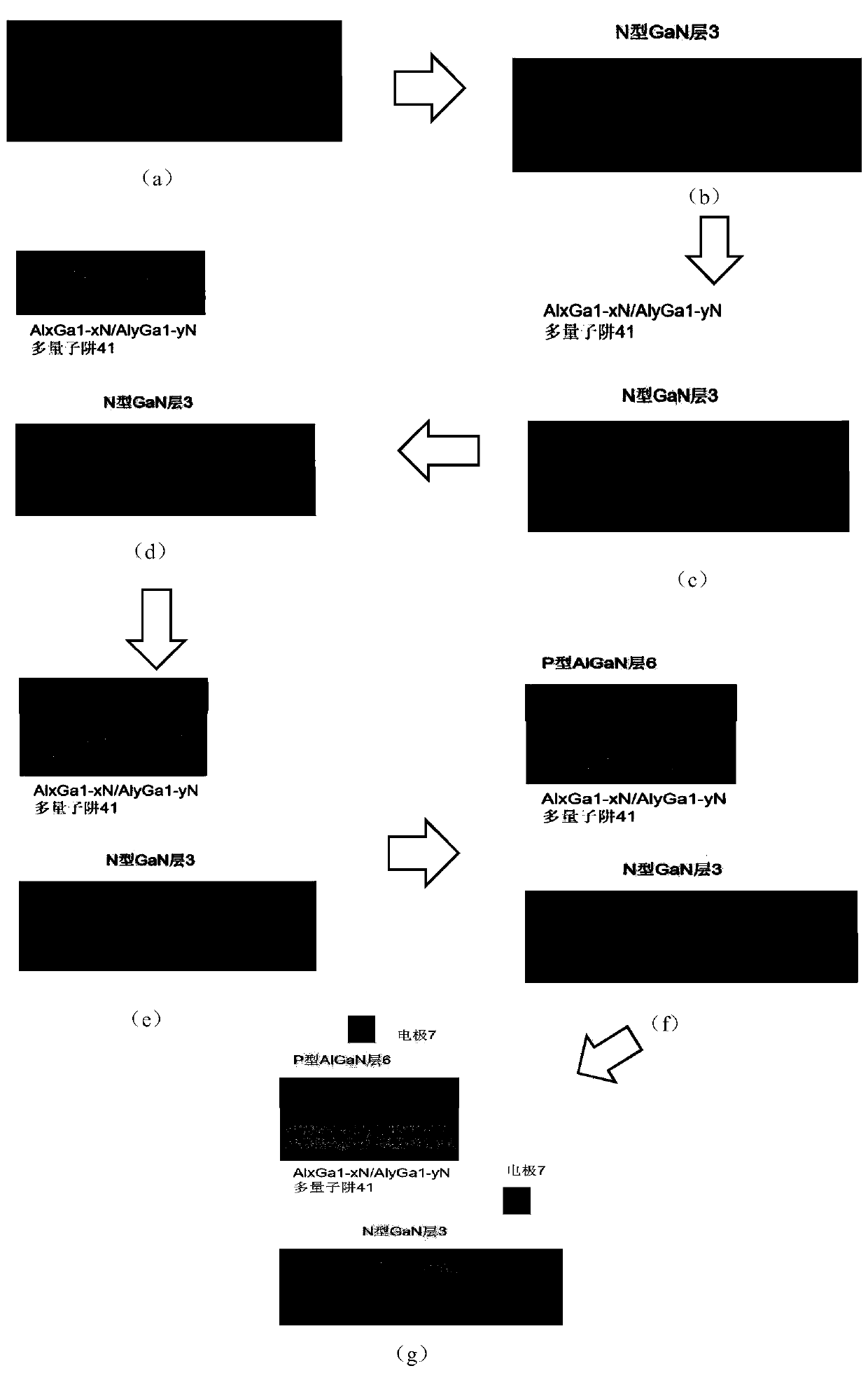

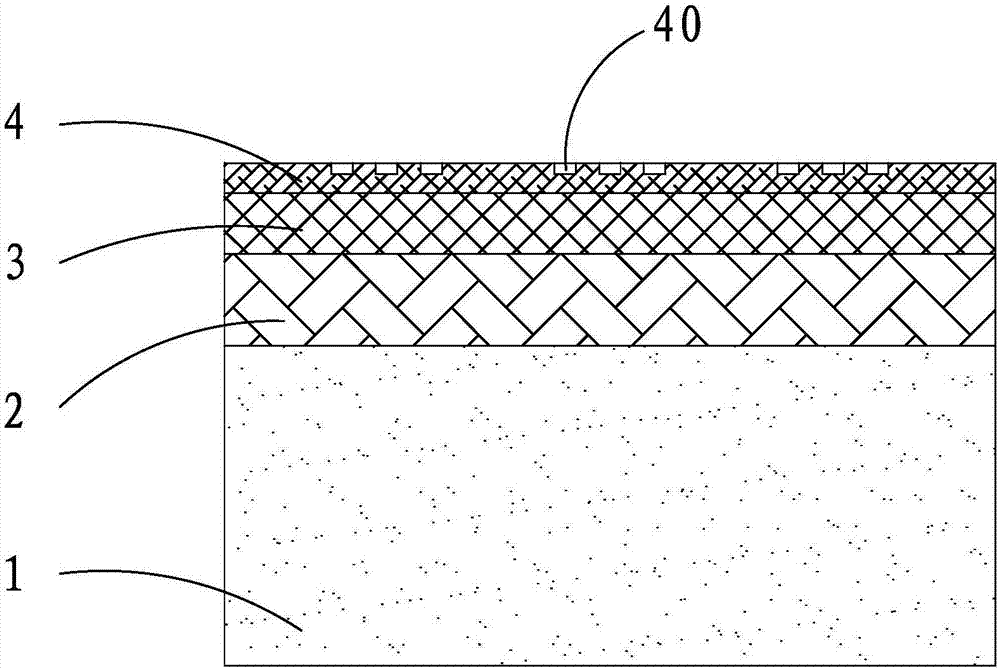

Gallium nitride-based light emitting diode and preparation method thereof

ActiveCN105826440ALower the barrierRaise the barrier heightSemiconductor devicesBand bendingPower flow

The invention provides a gallium nitride-based light emitting diode with high luminous efficiency and a preparation method thereof, and belongs to the field of photoelectric device preparation. The LED can maintain higher photoelectric conversion efficiency and a lower Droop effect under bulk current injection. The LED comprises a bottom layer and a light emitting layer which are grown through an MOCVD technology and a P-type layer which is grown through a molecular beam epitaxy technology, namely, a gallium polar buffer layer, a non-doped nitride layer, an N-type nitride layer and a multiple-quantum-well light emitting layer are grown through the MOCVD technology, and then, a sample is transferred to the reaction chamber of molecular beam epitaxy equipment, and a nitrogen polar electron blocking layer, a P-type nitride layer and a P-type nitride contact layer are grown. Through the method, band bending caused by polarization between the electron blocking layer and the multiple-quantum-well light emitting layer is reduced, the barrier height of electron overshoot to the P-type layer is increased, and the barrier height of hole injection to the multiple-quantum-well region is reduced.

Owner:TIANJIN SANAN OPTOELECTRONICS

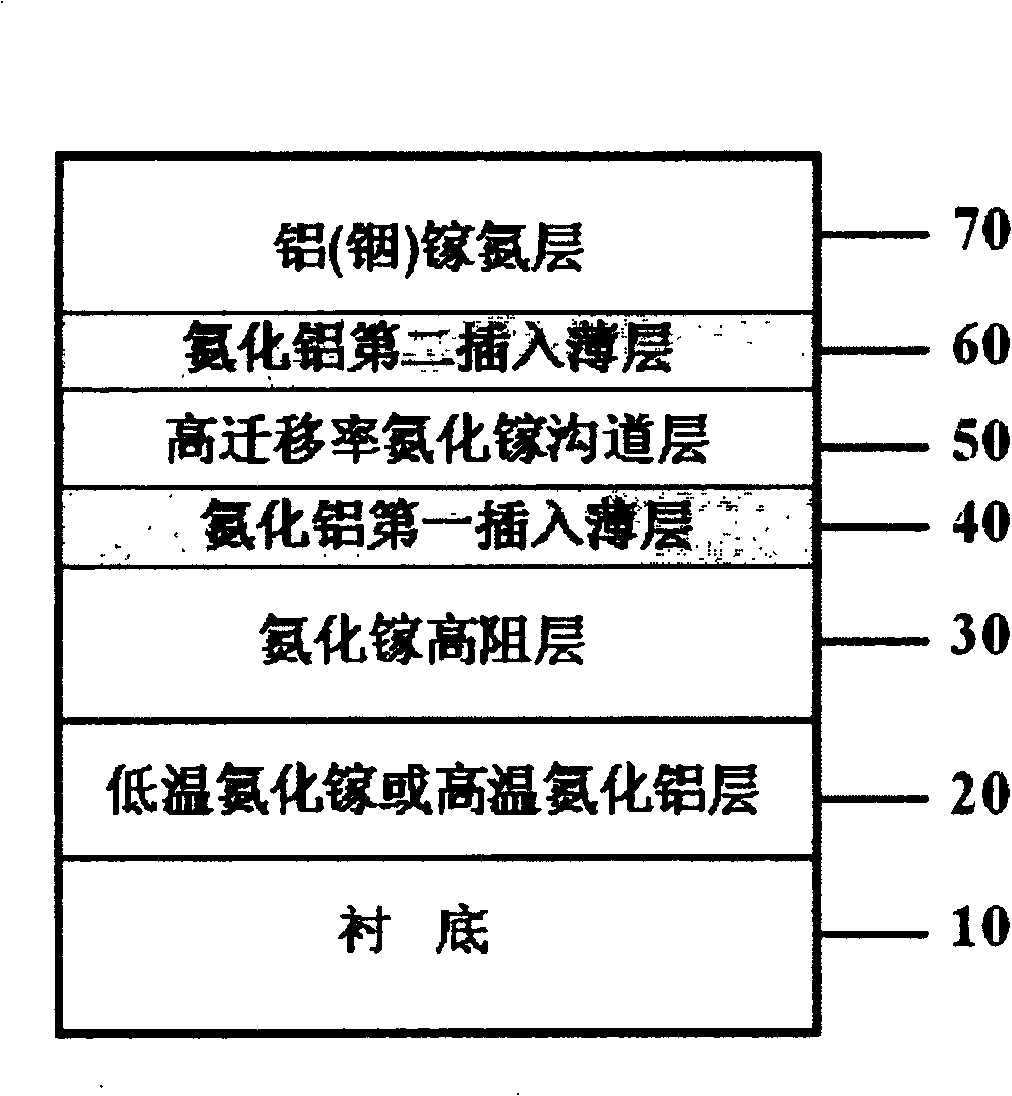

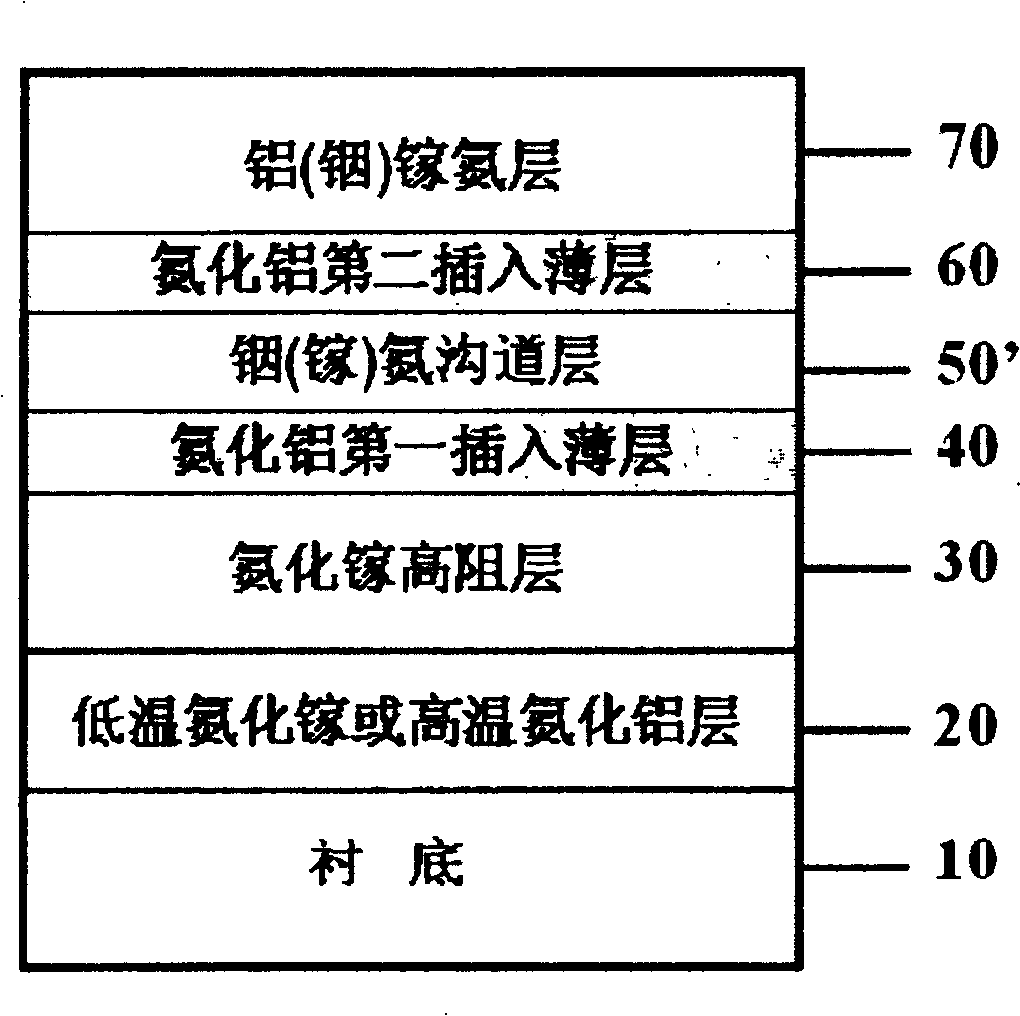

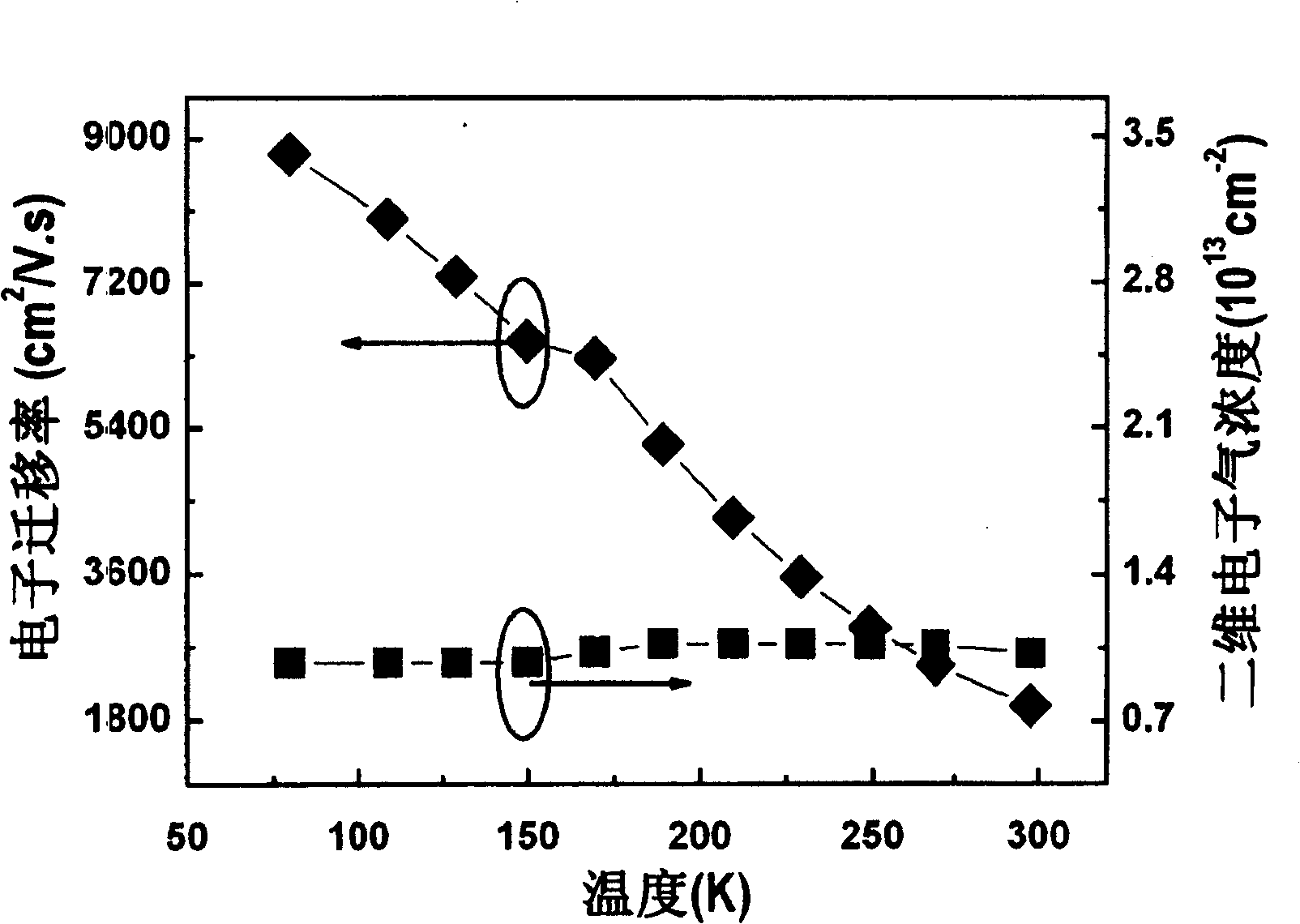

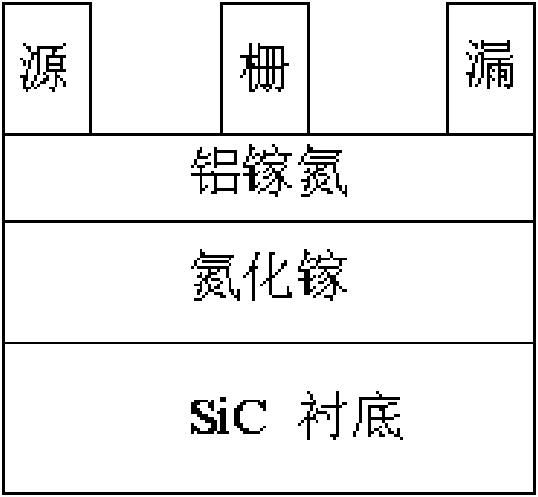

GaN dual heterogeneity node field effect transistor structure and its making method

InactiveCN101266999ARaise the barrier heightImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerGallium nitride

A gallium nitride-based double heterojunction field effect transistor structure comprises a substrate, a low temperature gallium nitride layer or high temperature aluminum nitride layer formed on the substrate; a high insulation layer with unintentional-doped or doped gallium nitride; the high insulation layer with unintentional-doped or doped gallium nitride is formed on a low temperature gallium nucleation layer or a high temperature gallium nitride nucleation layer; a first aluminum nitride inserting layer, the first aluminum nitride inserting layer is formed on the high insulation layer with unintentional-doped or doped gallium nitride; a unintentional-doped gallium nitride channel layer, the unintentional-doped gallium nitride channel layer is formed on the first aluminum nitride inserting layer; a second aluminum nitride inserting layer, the second aluminum nitride inserting layer is formed on the unintentional-doped gallium nitride channel layer, an unintentional-doped or n-type doped AlxInyGazN layer, the unintentional-doped or n-type doped AlxInyGazN layer is formed on the second aluminum nitride inserting layer.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

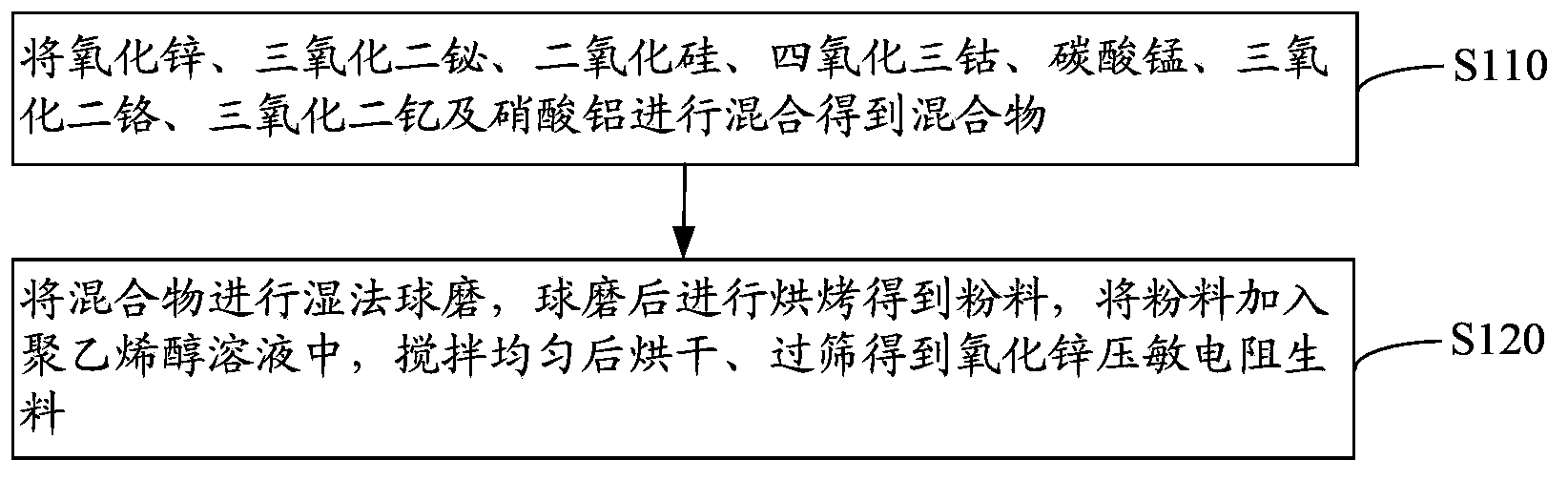

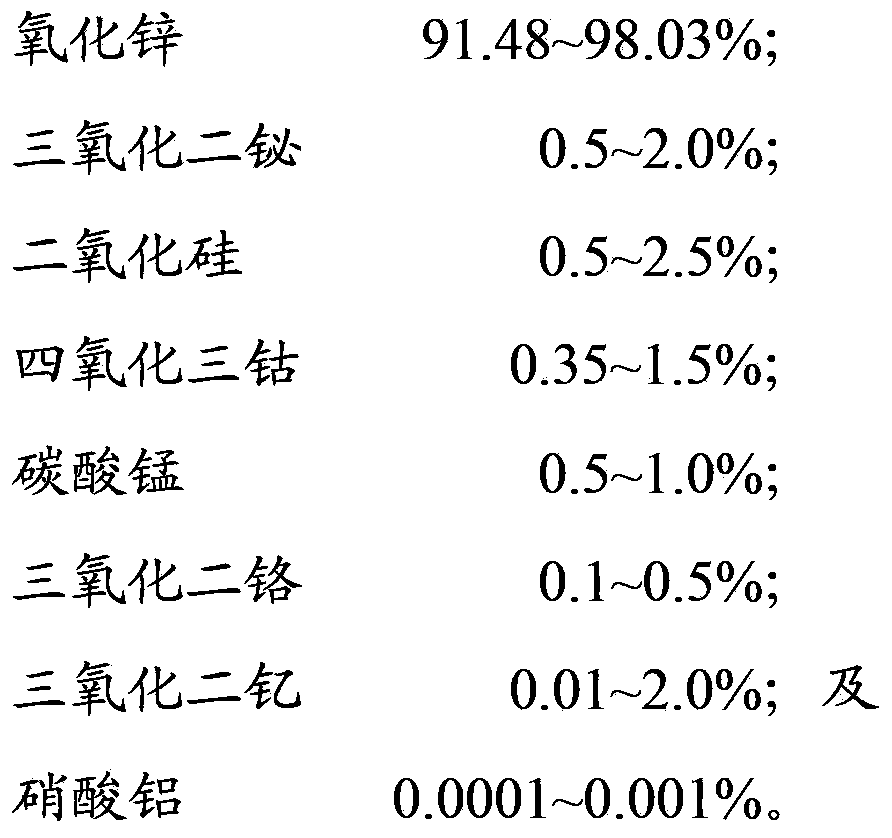

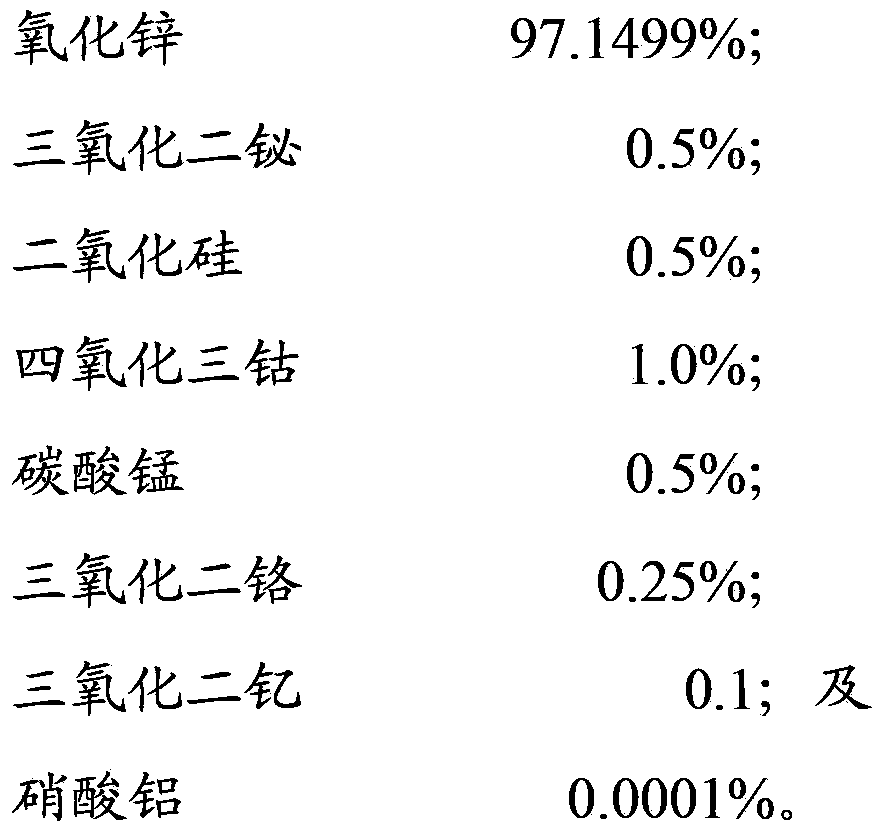

Zinc-oxide piezoresistor raw material, preparation method thereof and piezoresistor

ActiveCN103396116AImprove uniformityIncreased surface state densityVaristor coresOvervoltage protection resistorsManganeseVoltage gradient

The invention relates to a zinc-oxide piezoresistor raw material, a preparation method thereof and a piezoresistor. The zinc-oxide piezoresistor raw material comprises the following components by mole percent: 91.48-98.03% of zinc oxide, 0.5-2.0% of bismuth trioxide, 0.5-2.5% of silicon dioxide, 0.35-1.5% of cobaltosic oxide, 0.5-1.0% of manganese carbonate, 0.1-0.5% of chromium oxide, 0.01-2.0% of yttria and 0.0001-0.001% of aluminium nitrate. The zinc-oxide piezoresistor raw material does not antimony, and due to the silicon dioxide, the characteristic of the piezoresistor is improved, the surface state density is increased, the voltage gradient, the barrier height and the nonlinear coefficient are improved, the leakage current is reduced and the current impact resistance is enhanced; due to the yttria, the conductivity, the current impact resistance, the nonlinear coefficient and the voltage gradient are improved, the limiting voltage rate and the leakage current are reduced, the grain growth is inhibited and the zinc-oxide piezoresistor has higher voltage gradient and excellent electrical property.

Owner:GUANGDONG FENGHUA ADVANCED TECH HLDG

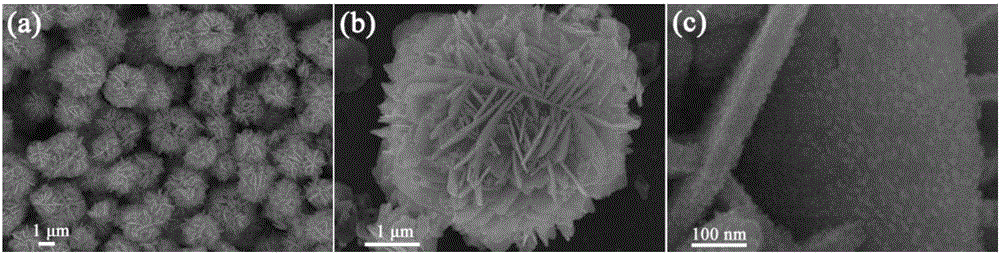

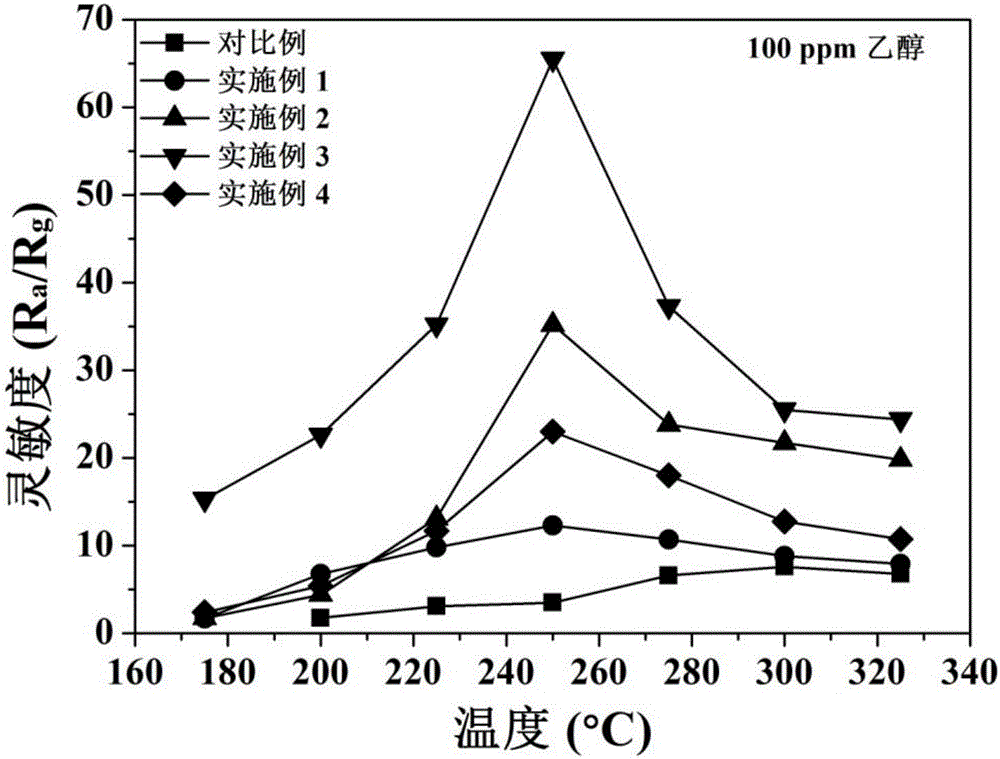

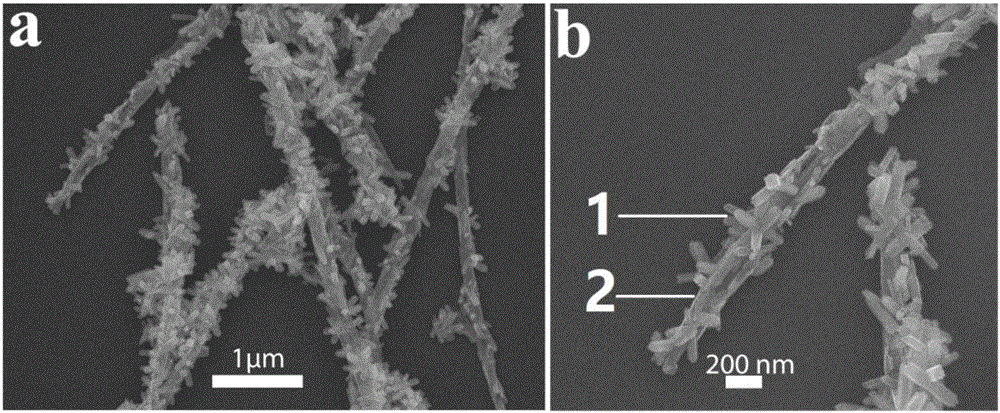

Ethanol gas sensor based on ZnO hollow flower ball and CdO nano-particle composite nanomaterial and preparation method of ethanol gas sensor

The invention discloses an ethanol gas sensor based on a ZnO hollow flower ball and CdO nano-particle composite nanomaterial and a preparation method of the ethanol gas sensor and belongs to the technical field of oxide semiconductor gas sensors. The method comprises the steps of firstly taking zinc acetate dihydrate, glycine, sodium sulfate decahydrate and sodium hydroxide as starting raw materials, and a mixed solution of water and ethanol as a solvent and successfully preparing a ZnO hollow flower ball precursor by using a hydrothermal method; and burning in air to obtain ZnO hollow flower ball powder; and taking the ZnO hollow flower ball powder, cadimium nitrate tetrahydrate and thiourea as the starting raw materials, and a mixed solution of dimethylformamide (DMF) and isopropyl alcohol as the solvent, compounding CdO nano-particles on the ZnO hollow flower balls by using the hydrothermal method and then burning in air to obtain the ZnO hollow flower ball and CdO nano-particle composite nanomaterial. The defect that two materials are relatively poor in gas-sensing characteristics is overcome, and improvement of the detection sensitivity of an ethanol gas and reduction of a lower detection limit are achieved.

Owner:JILIN UNIV

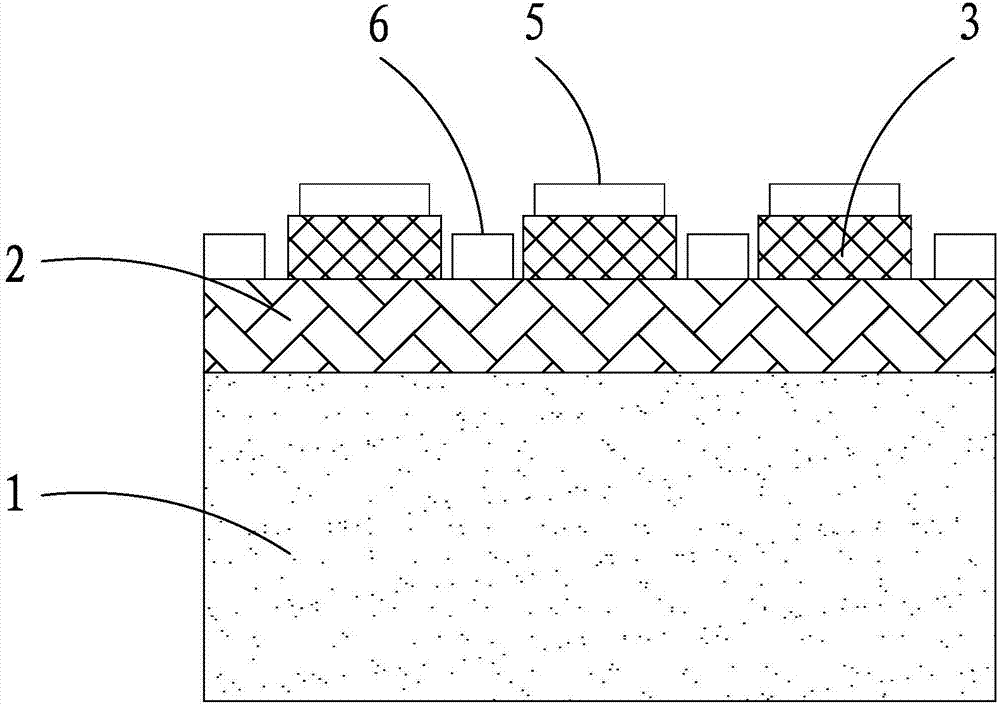

GaN-based LED structure and formation method thereof

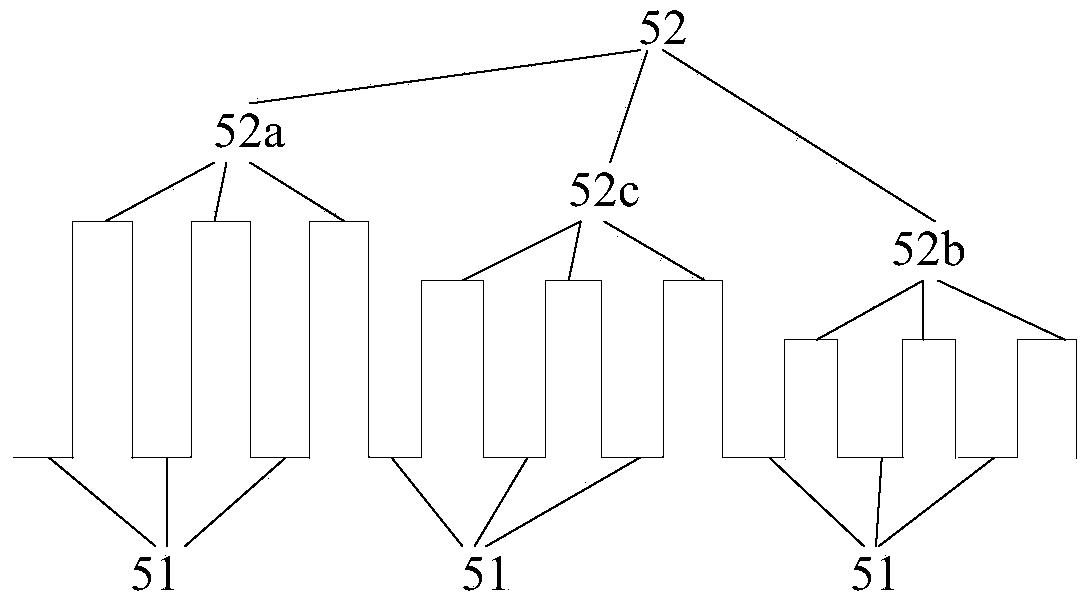

InactiveCN105304779ASimple structureRaise the barrier heightSemiconductor devicesElectron holeQuantum well

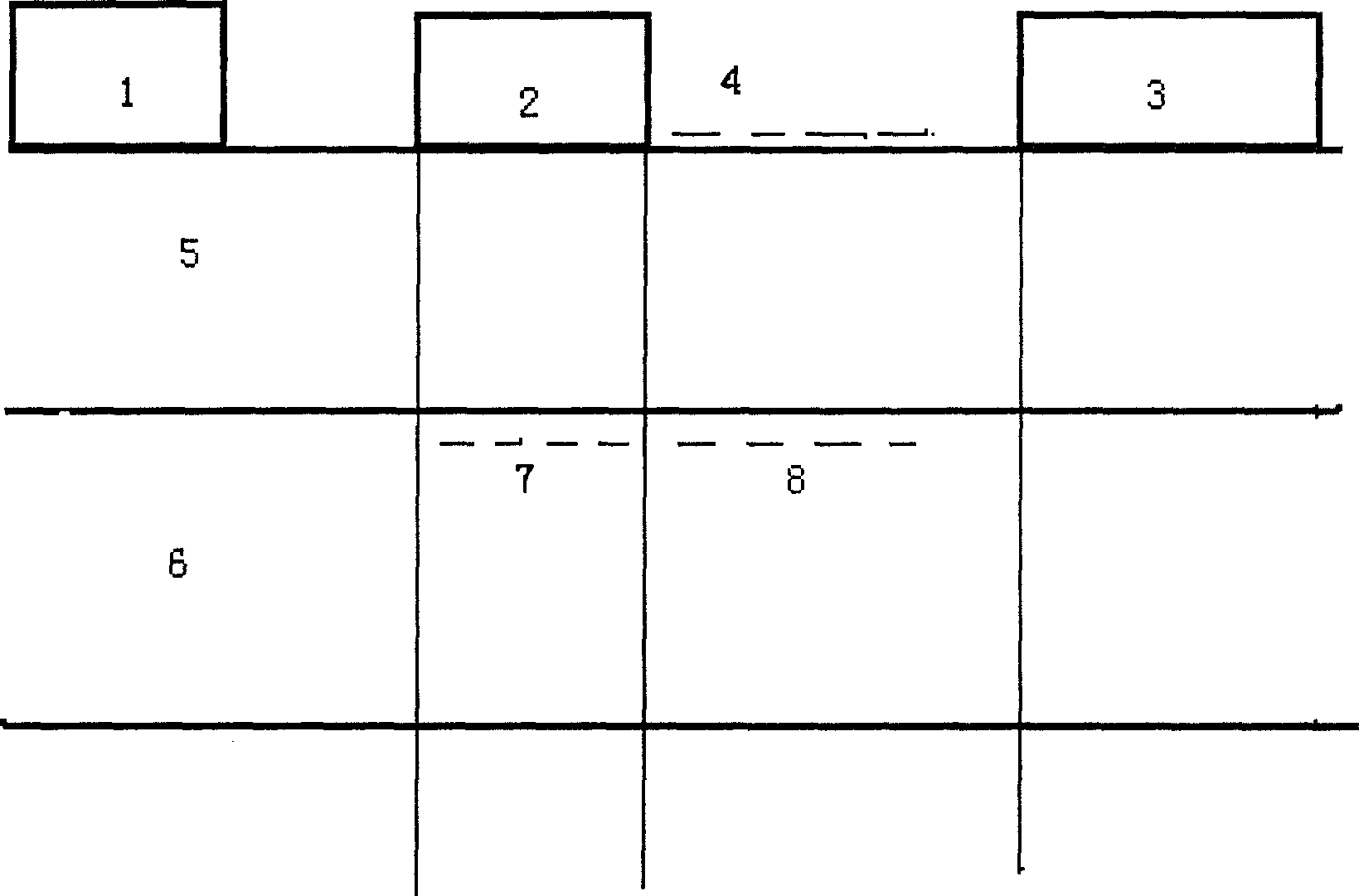

The invention discloses a GaN-based LED structure and a formation method thereof. The GaN-based LED structure comprises a substrate; a GaN buffer layer formed on the substrate; a first-doping-type GaN layer arranged on the GaN buffer layer; a quantum well luminous layer arranged on the first-doping-type GaN layer; a second-doping-type GaN layer arranged on the quantum well luminous layer; an electronic barrier layer arranged between the quantum well luminous layer and a P-doping-type GaN layer, wherein the electronic barrier layer comprises a block structure layer and a superlattice structure layer, the forbidden band width of the block structure layer being larger than that of the GaN, and the superlattice structure layer is used for adjusting the energy band inclination degree between the P-doping-type GaN layer and the block structure layer so as to reduce hole barrier height; and a P electrode and an N electrode. The GaN-based LED structure adopts a composite structure of the block structure layer and the superlattice structure layer, so that composite luminescence efficiency of electron holes in the quantum well luminous layer is greatly improved; and the GaN-based LED structure has the advantage of simple structure and the like.

Owner:HUIZHOU BYD IND

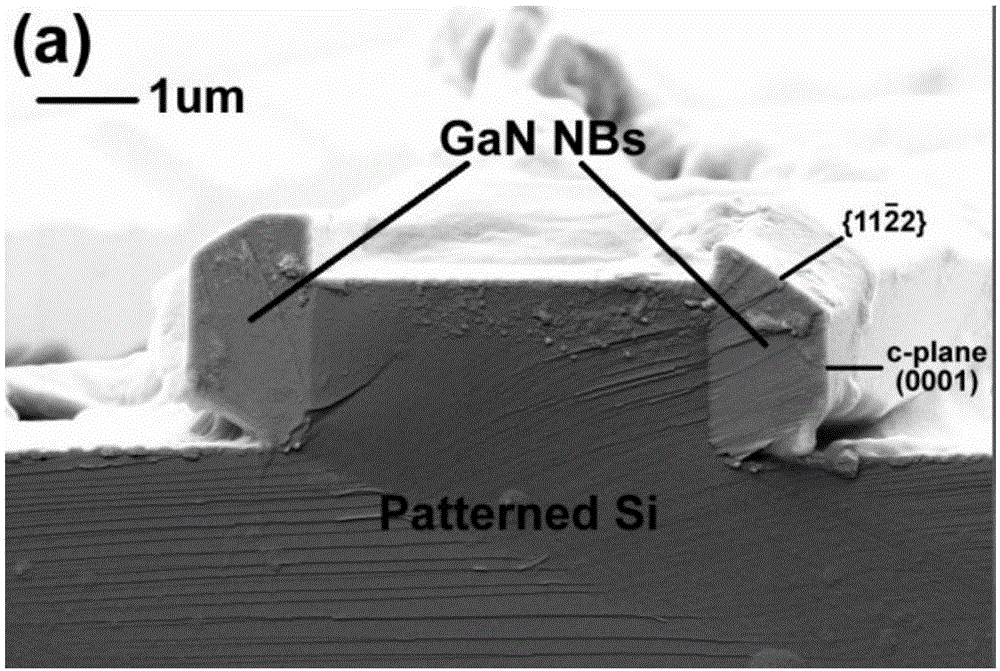

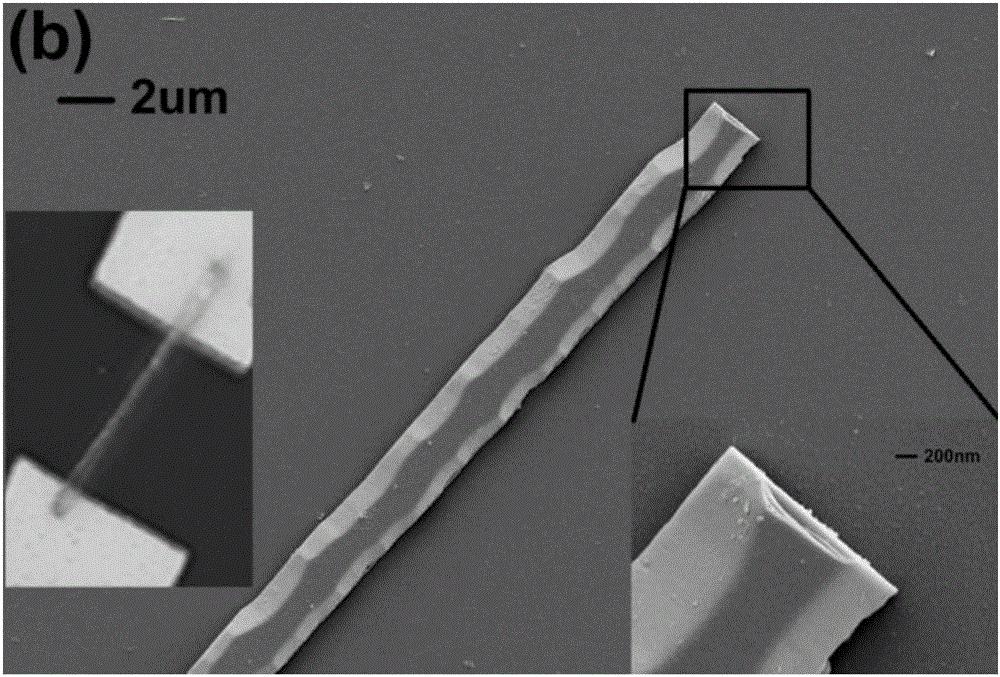

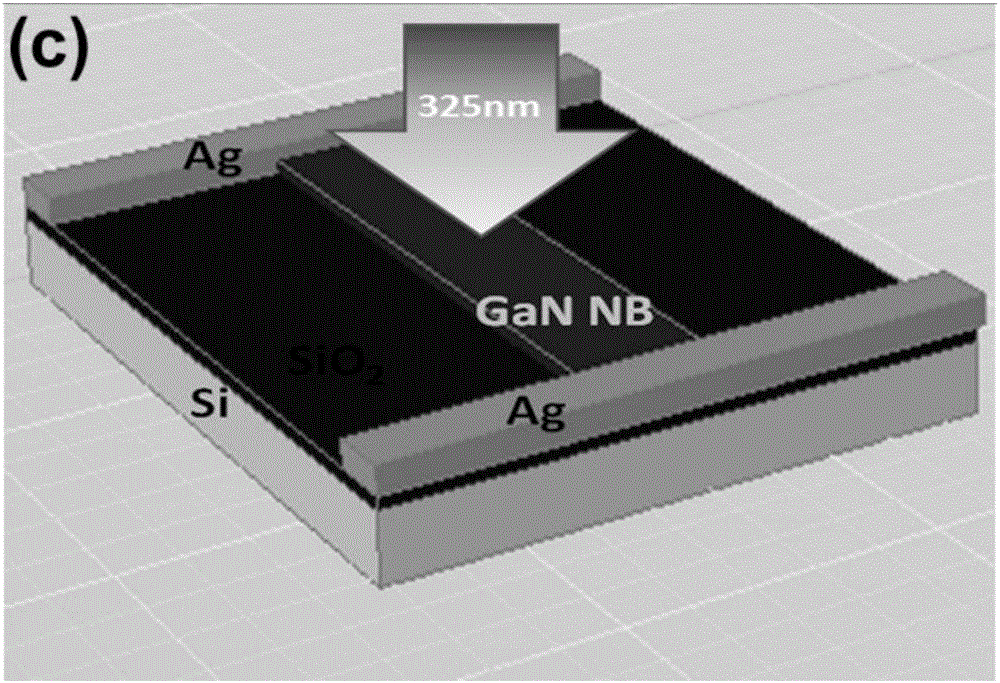

Silicon-doped gallium nitride nanoribbon ultraviolet detector and preparation method thereof

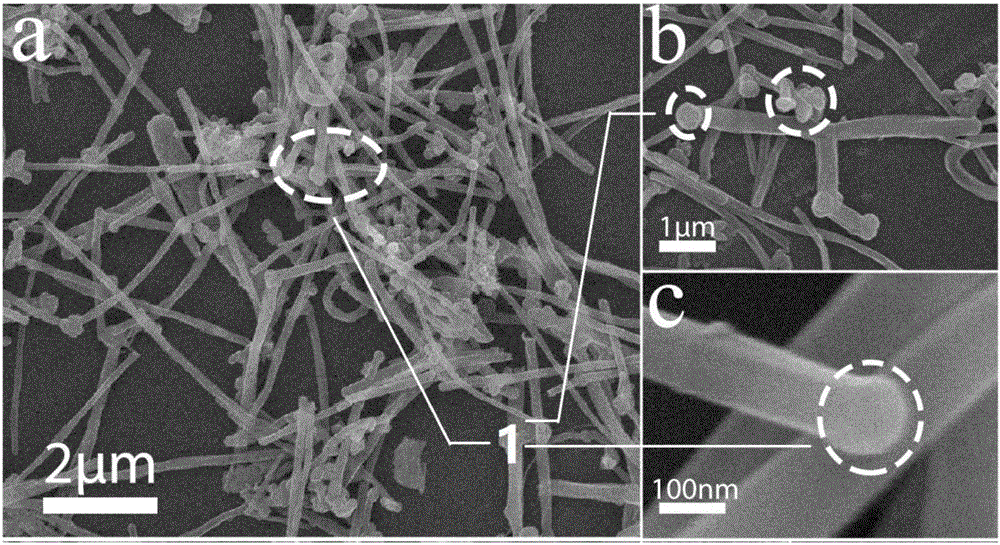

ActiveCN106229382AIncrease electron concentrationIncrease the barrier height of the contactFinal product manufactureSemiconductor devicesSilver electrodeEtching

The invention provides a silicon-doped gallium nitride nanoribbon ultraviolet detector and a preparation method thereof. The method comprises the following steps: (1) performing pattern photoetching and potassium hydroxide wet etching on a silicon substrate which is plated with silicon dioxide serving as a mask; (2) growing a silicon-doped gallium nitride nanoribbon on the groove side wall of the pattern; (3) peeling the nanoribbon, and transferring the peeled nanoribbon to the silicon dioxide plated silicon wafer substrate; and (4) plating a silver electrode on the nanoribbon of the substrate obtained in the step (3) so as to obtain the silicon-doped gallium nitride nanoribbon ultraviolet detector. According to the technical scheme, the photoswitch ratio and optical gain of a micro / nano measurement gallium nitride ultraviolet detector can be improved. Experimental results indicate that the silicon-doped gallium nitride nanoribbon ultraviolet detector has a photoswitch ratio of 5.4*10<4>, optical gain and optical sensitivity of 8.8*10<5> and 2.3*10<-5>A / W respectively.

Owner:SOUTH CHINA NORMAL UNIVERSITY

Method for manufacturing medium/nitride composite structure enhanced field effect transistor

ActiveCN102064108AHigh densityReduced series resistanceSemiconductor/solid-state device manufacturingHeterojunctionEngineering

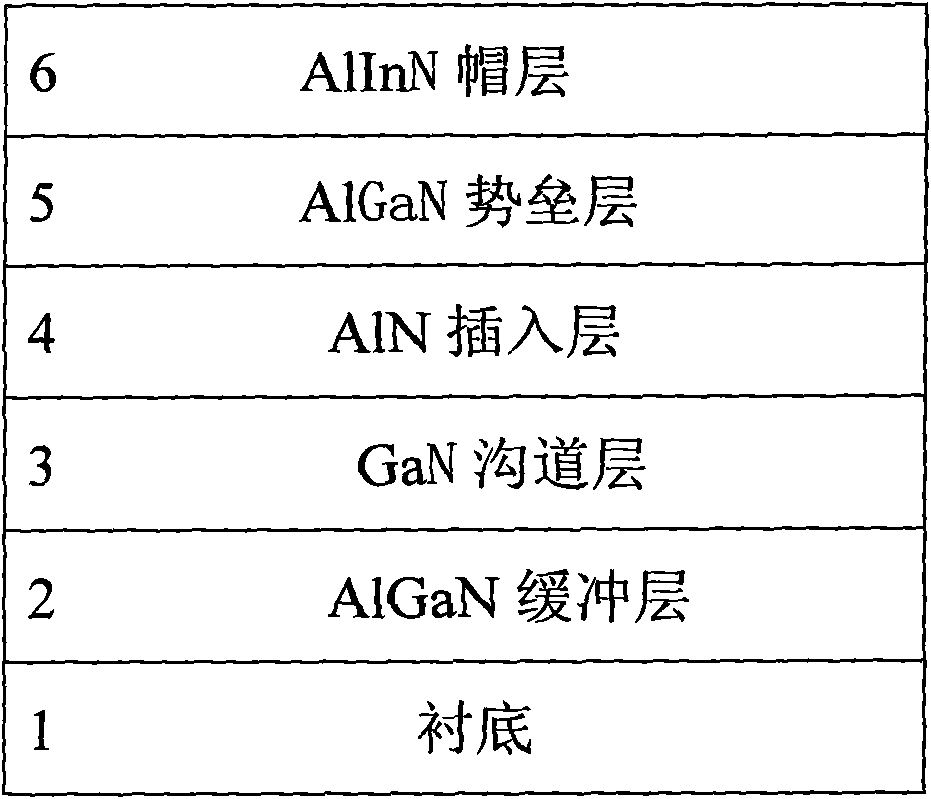

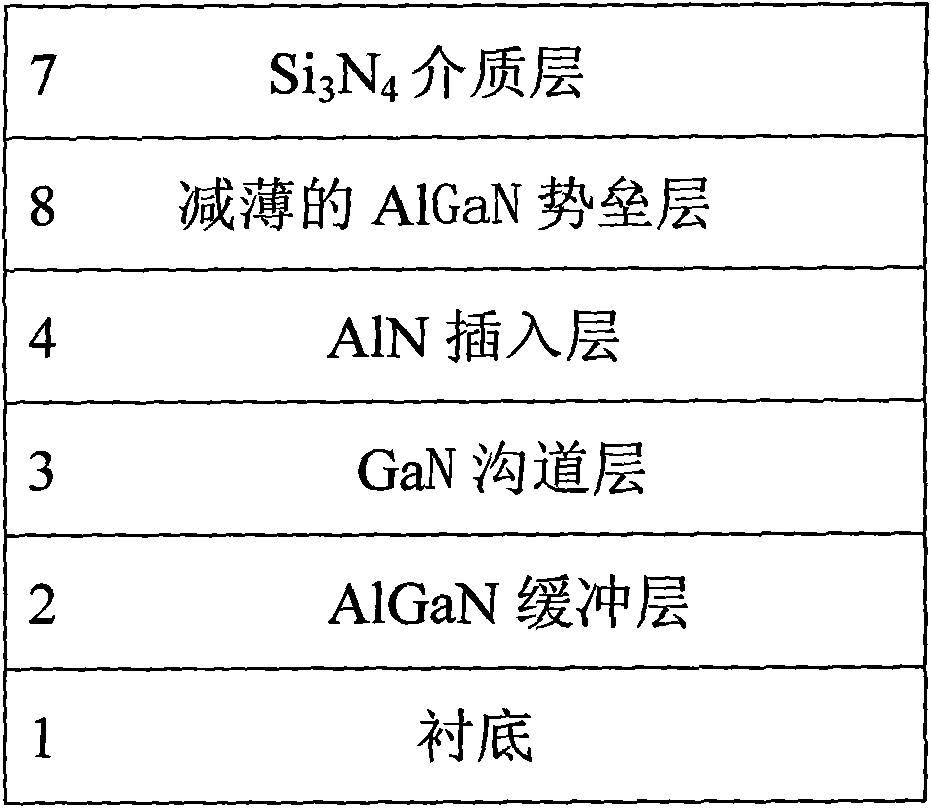

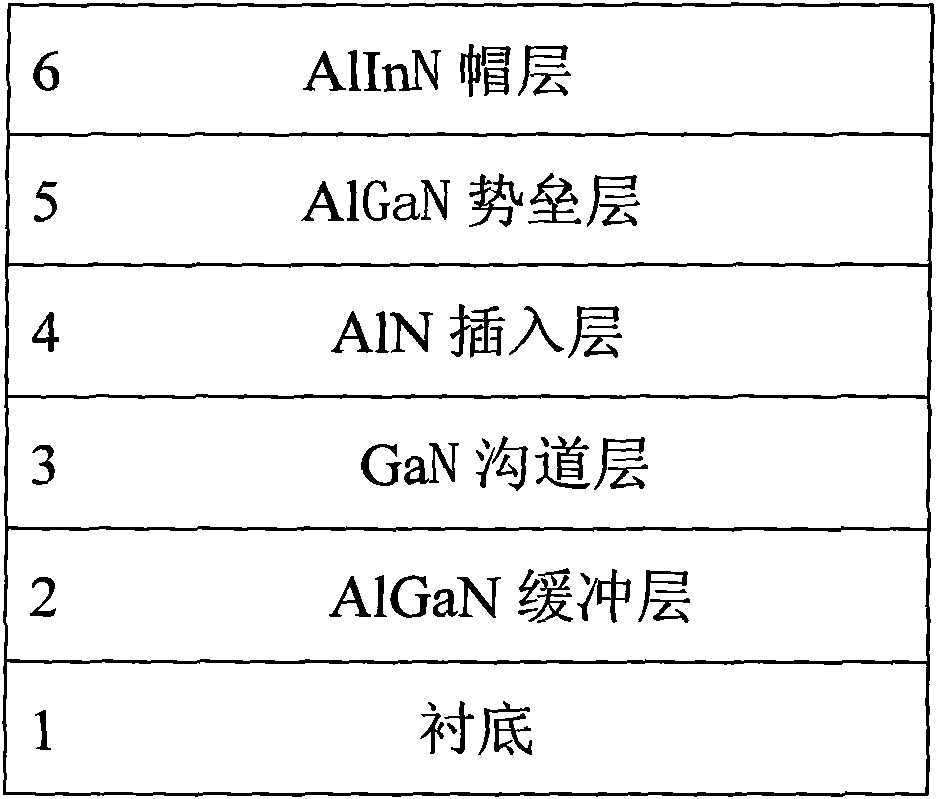

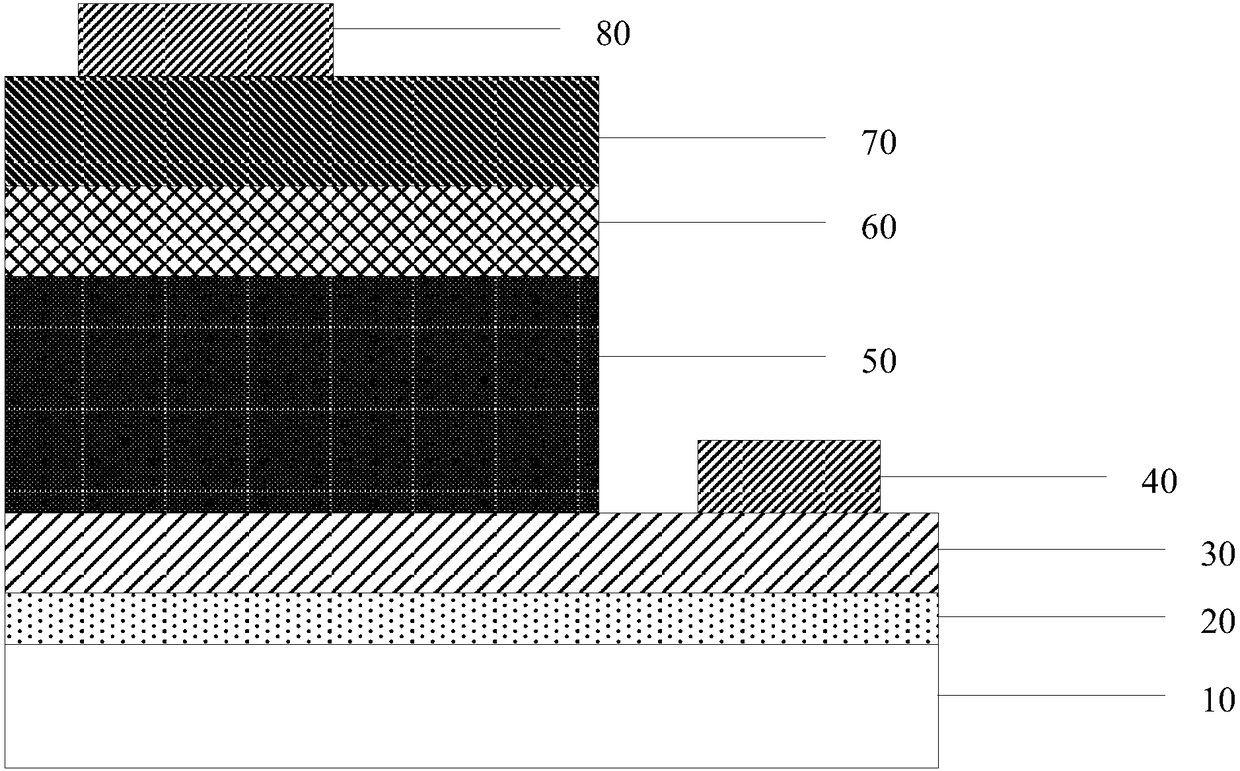

The invention discloses a method for manufacturing a medium / nitride composite structure enhanced field effect transistor, which comprises the steps of: sequentially growing a AlGaN buffer layer, a GaN channel layer, a AlN inserting layer, a AlGaN barrier layer and a AlInN cap layer on a substrate; and forming a AlInN / AlGaN / AlN composite front barrier and a GaN / AlGaN back barrier into a high electronic air tightness external channel well limited by strong electrons. The thick AlInN cap layer with lattice match remarkably improves the electronic air tightness of an external channel, and the high and wide barriers provided by the AlInN cap layer strengthen the quantum restriction of the channel well, thus the serial resistance of the external channel is lowered and the ohmic contact resistance is reduced. After the AlInN layer is corroded by using a dry method channeling process and the AlGaN barrier layer is thinned, a Si3N4 medium layer with set thickness is deposited by using an atom layer deposition (ALD) process, thus the quantum restriction of an internal channel well is strengthened, and the ON state current of the element is improved by band distortion of a heterojunction, caused in a way that an electron wave function does not permeate into the barrier layer, under the condition that a large grid voltage change is ensured. A negative space charge is introduced on the surface of the Si3N4 medium layer by using a fluorine plasma process, thus the barrier height is increased, electron air in the internal channel well is consumed fully to ensure that the inner channel is pinched off under zero grid voltage. An ideal module enhancing work is realized.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

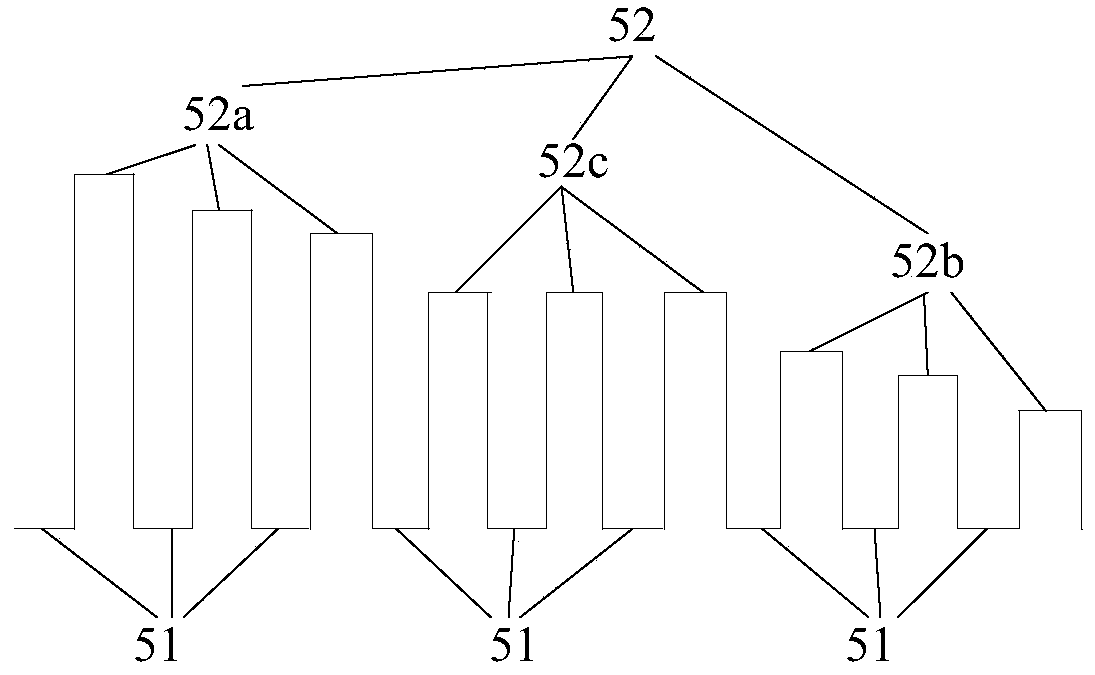

Light emitting diode and preparation method thereof

ActiveCN108110104AIncreased electron-hole wavefunction overlapConducive to radiative recombination luminescenceSemiconductor devicesContact layerBlocking layer

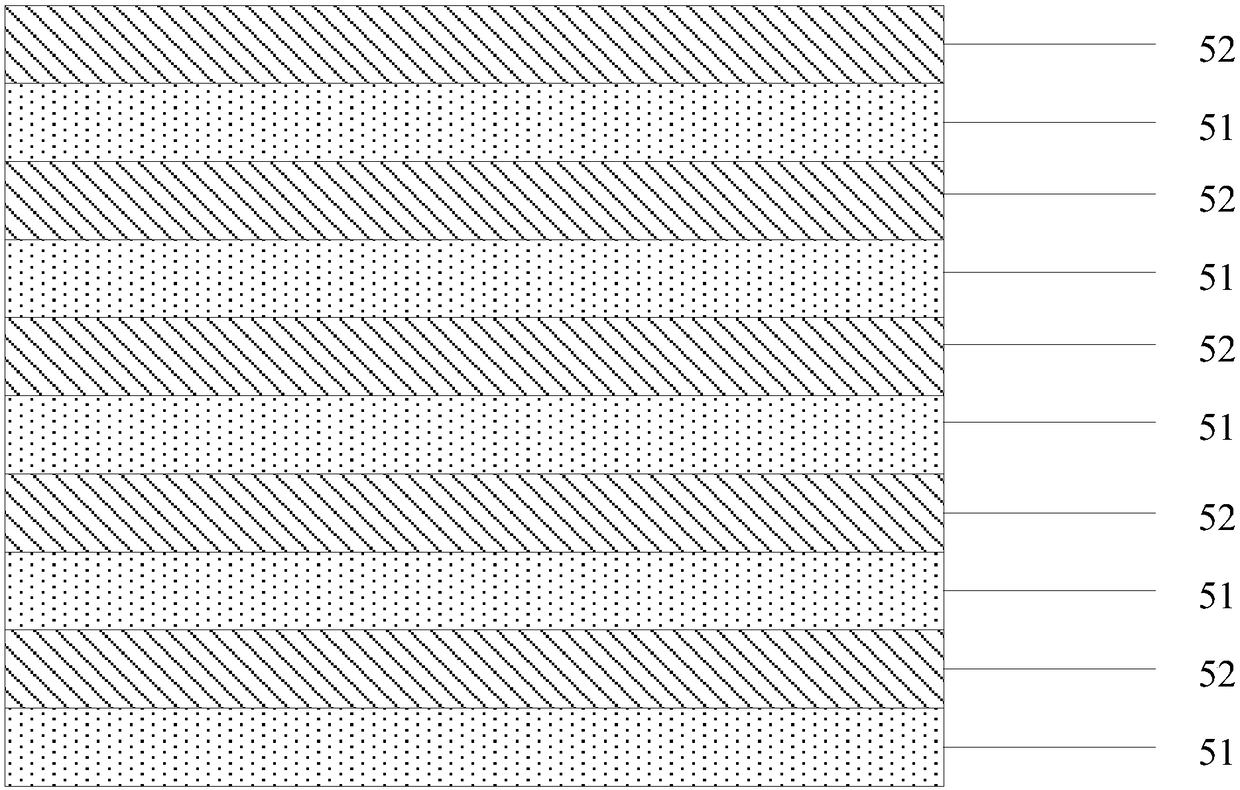

The application discloses a light emitting diode and a preparation method thereof. According to the light emitting diode, the last quantum barrier layer of a plurality of quantum well layers and an electron blocking layer in a conventional structure are replaced with a super lattice structure comprising a plurality of first-type super lattice layers and a plurality of second-type super lattice layers; the super lattice structure reduces polarization electric field intensity of the last quantum barrier layer, improves an electron hole wave function overlapping degree of the light emitting diodeand is beneficial to radiation composite light emitting of the light emitting diode; and the super lattice structure not only reduces the preparation difficulty of the light emitting diode, but alsoenables growth of the high-quality super lattice structure and second-type contact layer to be possible. In addition, existence of the super lattice structure also enables a electronic barrier heightof a conduction band of the integral second-type structural layer to be further increased, greatly reduces electron leakage, meanwhile, reduces a barrier height of a valence band hole, promotes transmission of the hole, greatly promotes internal quantum efficiency of multiple quantum well layers, reduces sudden reduction of efficiency, and greatly promotes integral light emitting power of the light emitting diode.

Owner:XIAMEN CHANGELIGHT CO LTD

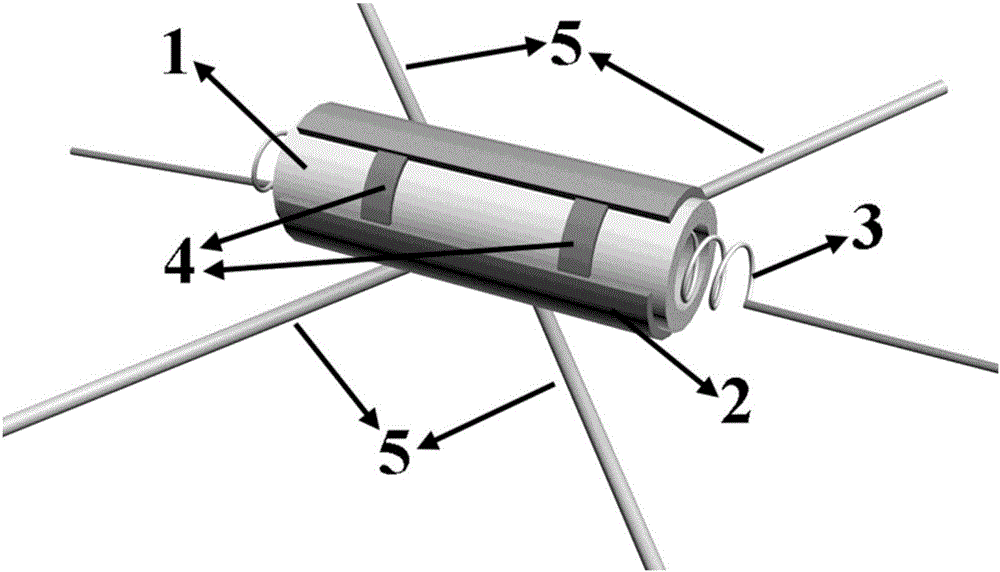

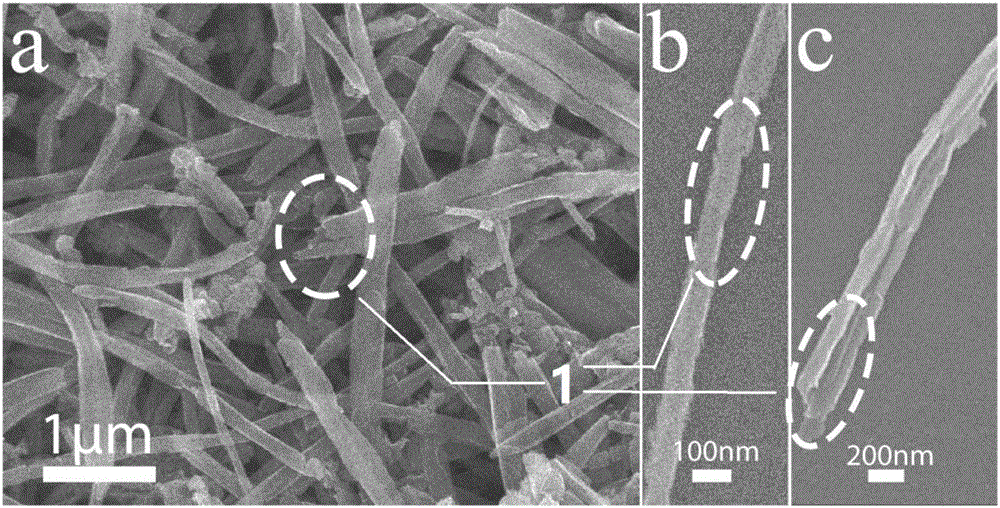

CNTs@alpha-Fe2O3 heterojunction composite material-based acetone gas sensor and preparation method thereof

ActiveCN106770493AHigh sensitivityExcellent gas sensitivityMaterial resistanceHeterojunctionHigh volume manufacturing

The invention discloses a CNTs@alpha-Fe2O3 heterojunction composite material-based acetone gas sensor and a preparation method thereof, and belongs to the technical field of gas sensors. The acetone gas sensor comprises an insulating alumina ceramic tube substrate with two parallel and separate annular gold electrodes on the outer surface, a semiconductor metal oxide gas sensitive material coated on the outer surface of the insulating alumina ceramic tube substrate and the gold electrodes, and a nichrome heating coil arranged in the insulating alumina ceramic tube, wherein each gold electrode is provided with a platinum wire; the sensitive material is a CNTs and alpha-Fe2O3 nano-rod-compounded heterojunction hierarchical structure nanomaterial. The sensor has the advantages of being simple in structure, low in price, relatively small in volume, solid and durable, is suitable for massive production; and the gas-sensitivity characteristic testing result shows that the sensor can detect low-concentration acetone, has excellent long-term stability and has an important application prospect in detection and alarming of acetone leakage in industrial production and medical detection.

Owner:JILIN UNIV

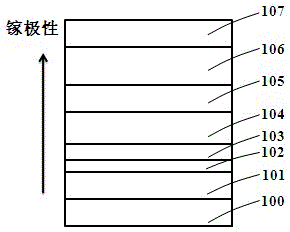

Epitaxial structure for improving light output power of ultraviolet LED

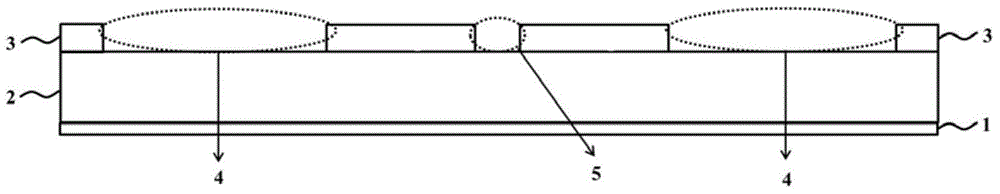

PendingCN106935690AImprove blocking efficiencyReduce leakageSemiconductor devicesUltravioletElectron blocking layer

The invention discloses an epitaxial structure for improving light output power of an ultraviolet LED. The epitaxial structure comprises a substrate, a GaN buffer layer, a non-doped GaN layer, a doped N-type GaN layer, a AlGaN / GaN multi-quantum well structure, an insertion layer, an electron barrier layer EBL and a P-type GaN layer which are sequentially arranged from bottom to top, wherein the substrate employs a sapphire substrate, the thickness of the GaN buffer layer is 20-25 nanometers, the growth temperature of the GaN buffer layer is 530-550 DEG C, the GaN buffer layer is recrystallized under heat preservation for 6 minutes at 1,050 DEG C, the thickness of the non-doped GaN layer is 2.0-2.5 micrometers, the growth temperature of the non-doped GaN layer is 1,050 DEG C, the thickness of the doped N-type GaN layer is 2.5-3.0 micrometers, the Si doping concentration is 5*10<18>cm<-3>, the growth temperature is 1,050 DEG C, and the multi-quantum well AlGaN / GaN structure is formed by alternatively growing multi-quantum well AlGaN layers and multi-quantum well GaN layers according to six periods. By improving the crystal quality of an ultraviolet LED chip, the electron barrier effect of the electron barrier layer is optimized, the electron leakage is reduced, so that the efficiency reduction of an ultraviolet LED device is improved, and the light output power is improved.

Owner:GUANGDONG UNIV OF TECH

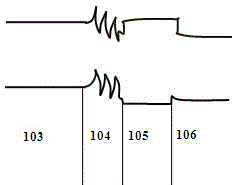

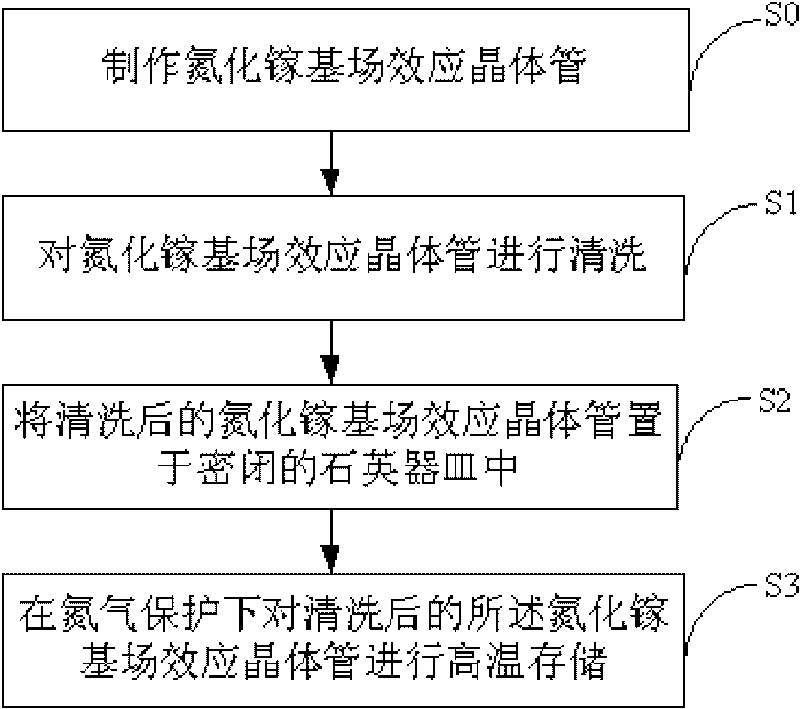

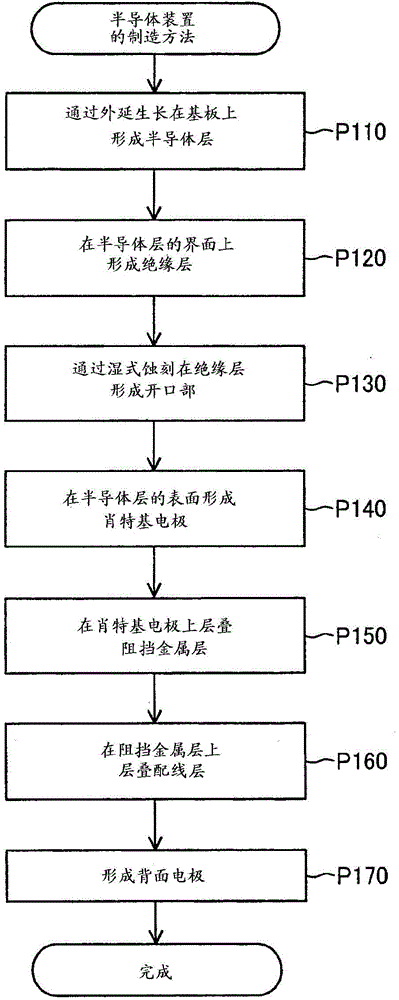

Method for improving Schottky barrier of gallium nitride-based field effect transistor

InactiveCN101707184ARaise the barrier heightImprove stabilitySemiconductor/solid-state device manufacturingSchottky barrierSemiconductor materials

The invention discloses a method for improving a Schottky barrier of a gallium nitride-based field effect transistor, belonging to the technical field of manufacture of semiconductor material device. The method comprises the following steps: cleaning the gallium nitride-based field effect transistor; and storing the cleaned gallium nitride-based field effect transistor under the protection of nitrogen at high temperature. By means of the invention, the height of the Schottky barrier of gallium nitride-based field effect transistor is increased, the reverse leakage f the Schottky barrier of gallium nitride-based field effect transistor is reduced, and the power characteristic and the breakdown characteristic of the gallium nitride-based field effect transistor are improved; therefore, the problem of parameter drift of the gallium nitride-based field effect transistor in the work is solved, and the stability and reliability of the gallium nitride-based field effect transistor are improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

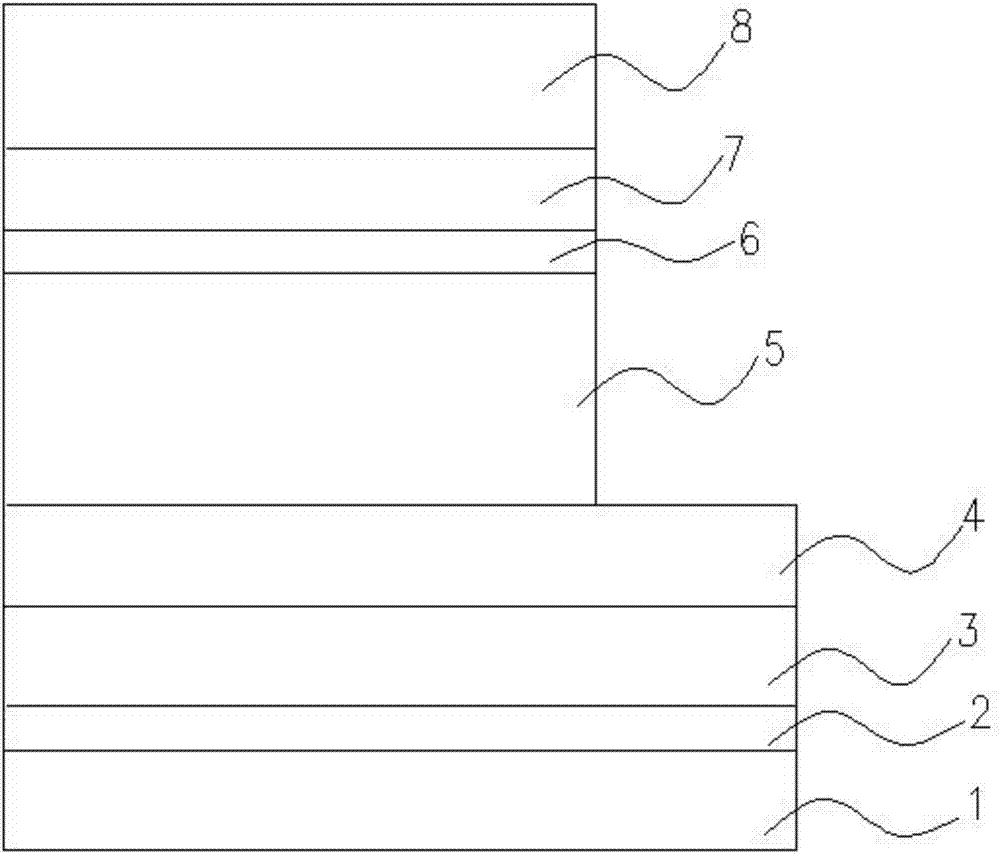

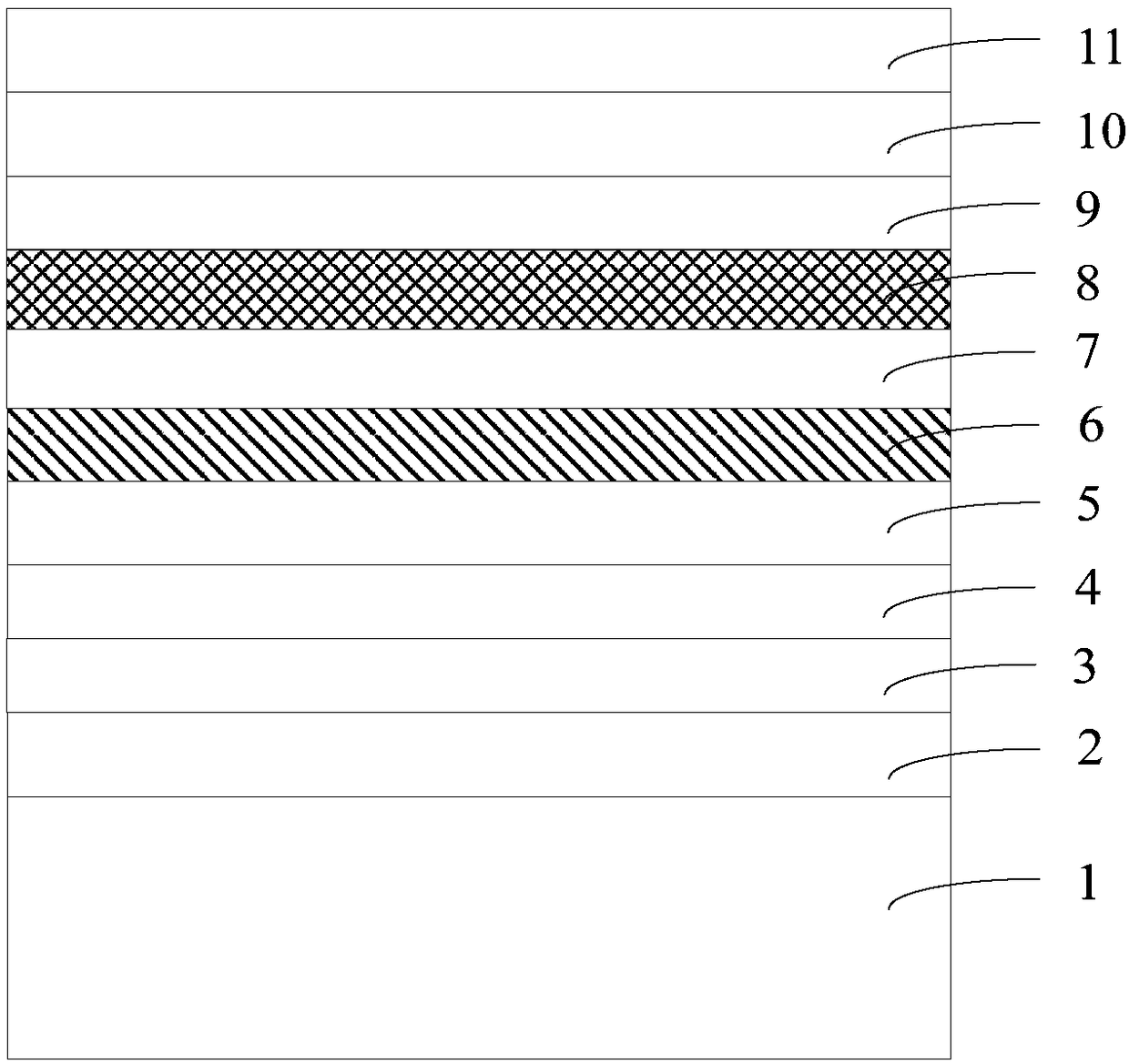

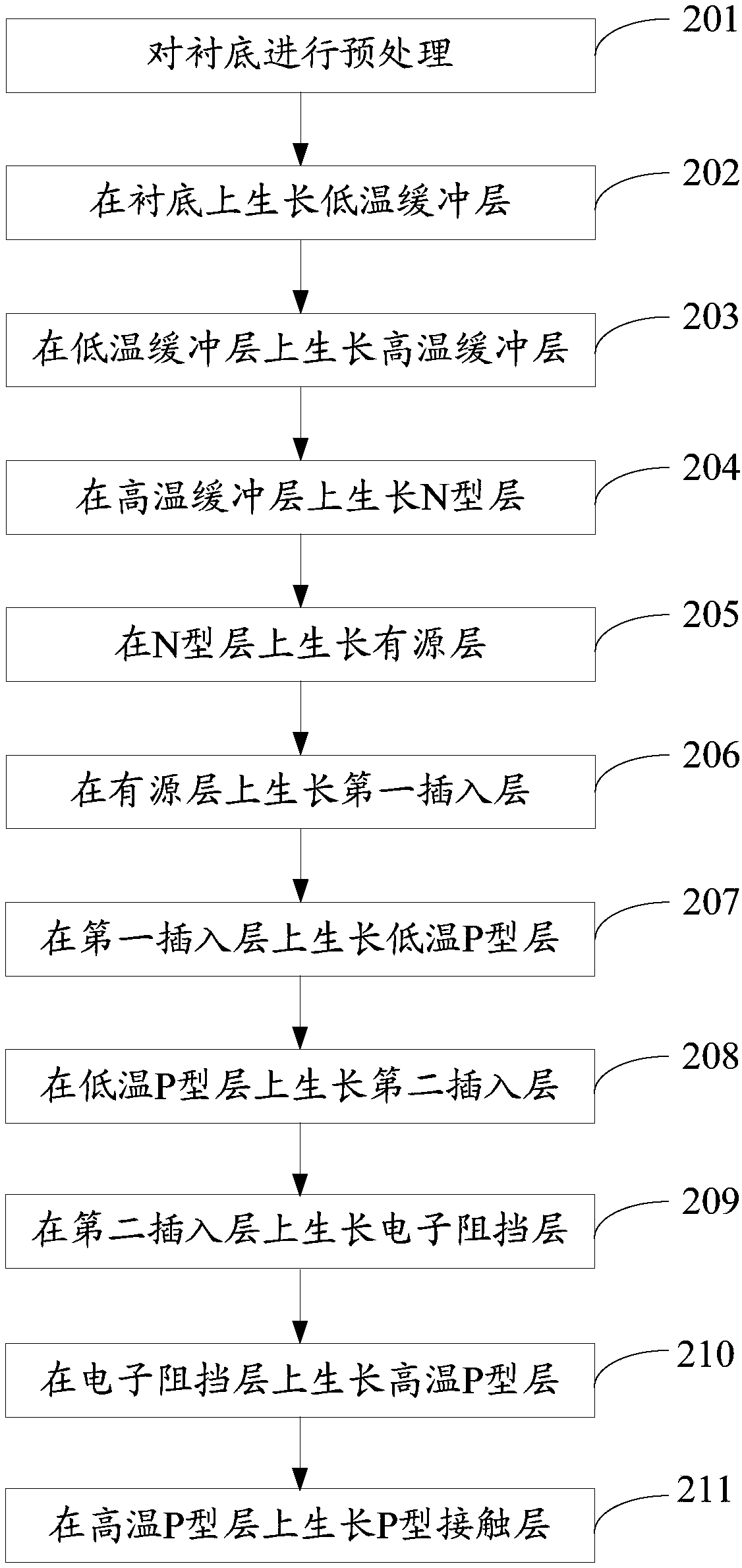

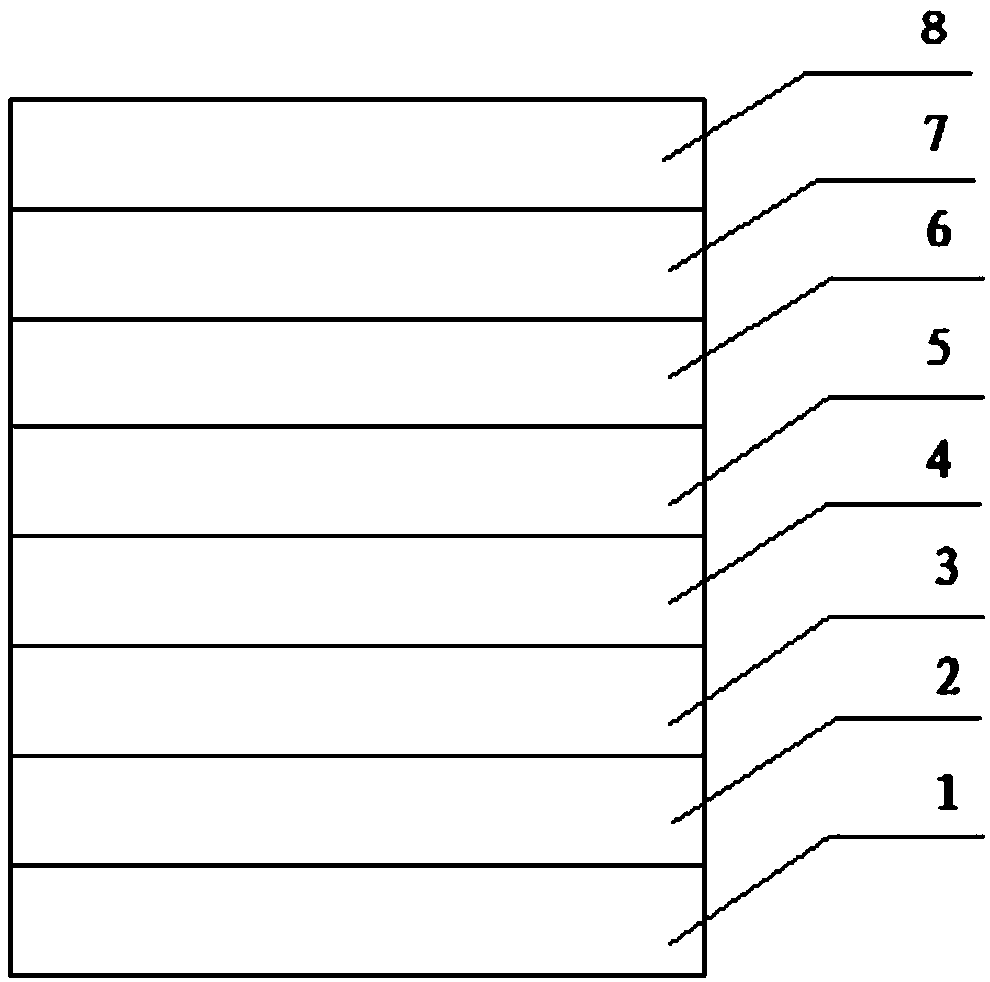

Light emitting diode epitaxial wafer and manufacturing method thereof

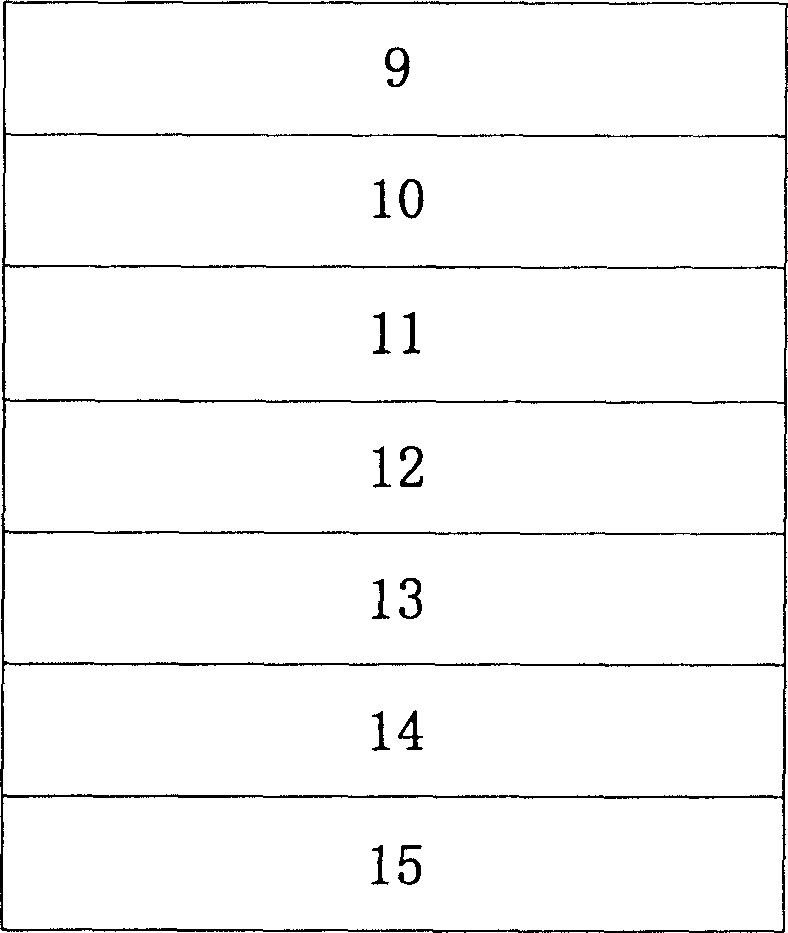

ActiveCN108470805AImprove crystal qualityPrevent leakageSemiconductor devicesElectron blocking layerActive layer

The invention discloses a light emitting diode epitaxial wafer and a manufacturing method thereof and belongs to the technical field of semiconductors. The light emitting diode epitaxial sheet comprises a substrate, a low-temperature buffering layer, a high-temperature buffering layer, an N-type layer, an active layer, a low-temperature P-type layer, an electronic blocking layer, a high-temperature P-type layer and a P-type contract layer, wherein the low-temperature buffering layer, the high-temperature buffering layer, the N-type layer, the active layer, the low-temperature P-type layer, theelectronic blocking layer, the high-temperature P-type layer and the P-type contract layer are successively laminated on the substrate. The growth temperature of the low-temperature P-type layer is 720-790 DEG C. A first insertion layer is arranged between the low-temperature P-type layer and the active layer. The first insertion layer is of an Al-GaN / GaN superlattice structure with the period ofn, wherein 2<=n<=10. The growth temperature of the first insertion layer is the same as that of the low-temperature P-type layer. A second insertion layer is arranged between the low-temperature P-type layer and the electronic blocking layer. The second insertion layer is of a GaN structure doped with Al. The growth temperature of the second insertion layer is 10-50 DEG C higher than the growth temperature of the low-temperature P-type layer. By setting the first insertion layer and the second insertion layer, production of defects is reduced and light emitting efficiency of the light emitting diode can be improved.

Owner:HC SEMITEK ZHEJIANG CO LTD

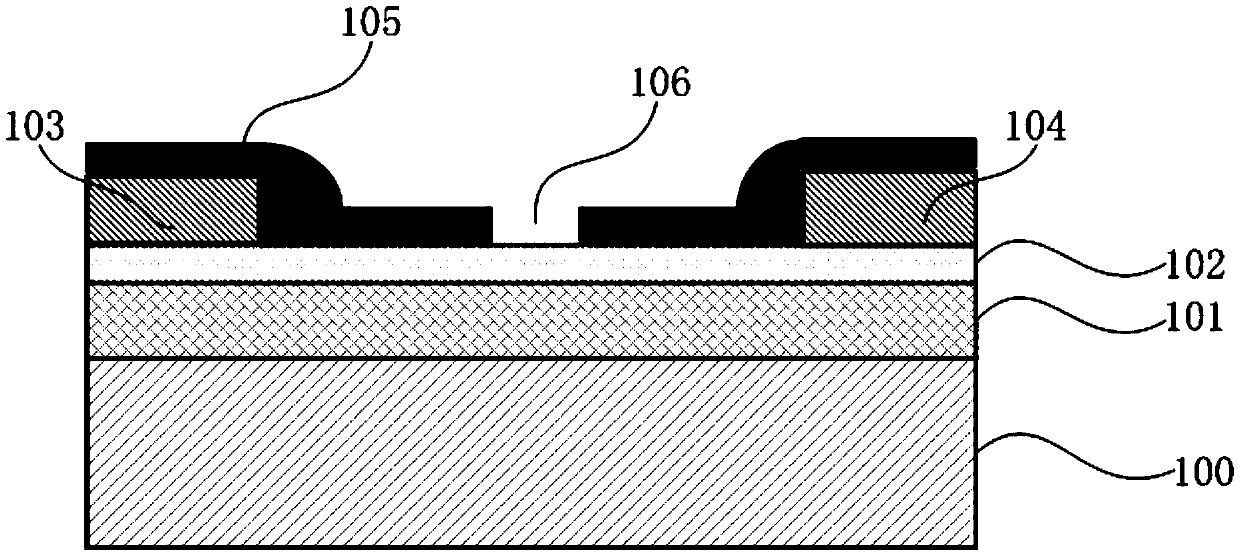

GaN-based LED structure and forming method thereof

InactiveCN105470355ARaise the electron barrier heightSimple structureSemiconductor devicesElectron blocking layerLead structure

The invention discloses a GaN-based LED structure and a forming method thereof. The GaN-based LED structure provided by an embodiment of the invention comprises the components of a substrate; a first-doping-type GaN layer on the substrate; a quantum well light emitting layer on the first-doping-type GaN layer; a second-doping-type GaN layer on the quantum well light emitting layer; an electron barrier layer between the quantum well light emitting layer and a P-doping-type GaN layer, wherein the electron barrier layer comprises a block structure layer and a superlattice structure layer, the forbidden band width of the block structure layer is larger than that of the GaN, the superlattice structure layer is used for adjusting energy band inclination degree between the P-doping-type GaN layer and the block structure layer for reducing a hole potential barrier height; and a P electrode and an N electrode. According to the GaN-based LED structure, a composite structure in which the block structure layer and the superlattice structure layer are combined is utilized, thereby greatly improving composite light emitting efficiency of electron holes in the quantum well light emitting layer. Furthermore the GaN-based LED structure has advantages of simple structure, etc.

Owner:BYD CO LTD

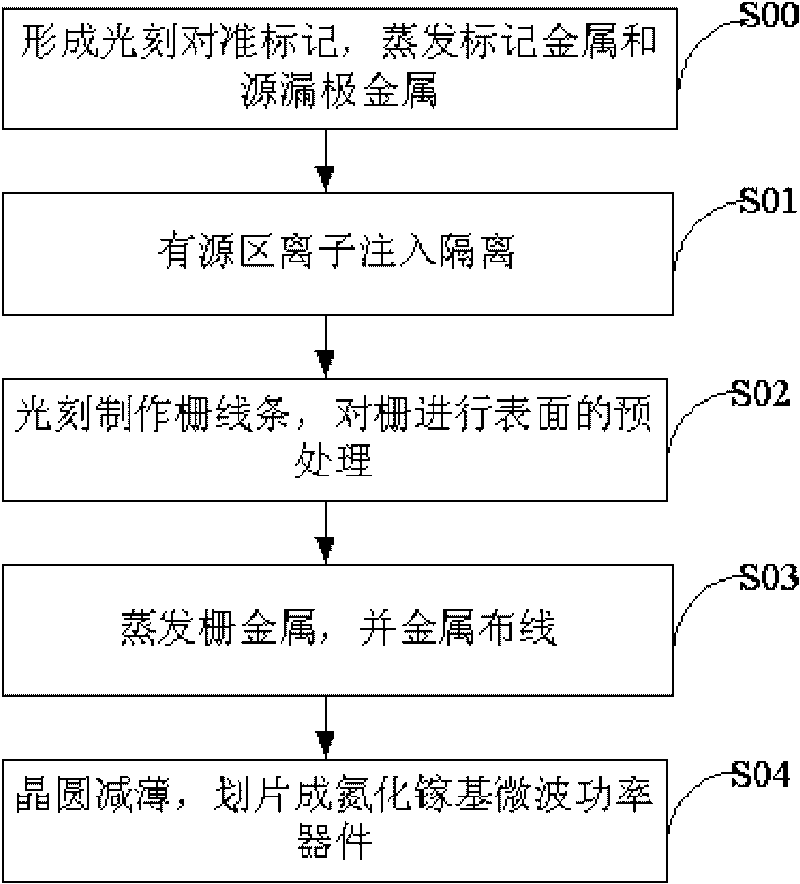

Method for producing heavy blended gallium nitride field effect transistor

InactiveCN1901144AIncrease electron densityIncrease leakage currentSemiconductor/solid-state device manufacturingOhmMetal

This invention provides a method for manufacturing heavy doped GaN field effect transistors including: growing a nucleation layer, a buffer layer and a channel layer on a substrate, then growing an AlN isolation layer and a heavy doped AlGaN potential barrier layer and finally making mesa-isolation and ohm contact to photo-etch a grating electrode window after growing a non-doped cap layer then to be processed by CF4 fluorin plasma process to control the emission power and process time to adjust the pinch off voltage to a designed sphere, then self-aligning the deposited grating metal on the barrier layer of the window to manufacture the Schottky barrier and annealing in the N2 atmosphere to eliminate defect generated in the plasma process to get the heavy doped field effect transistor.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

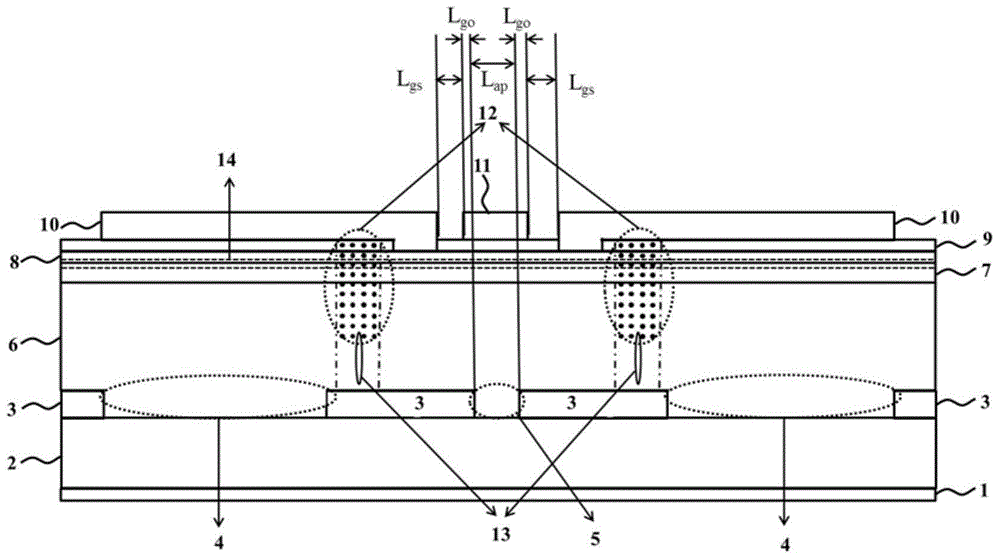

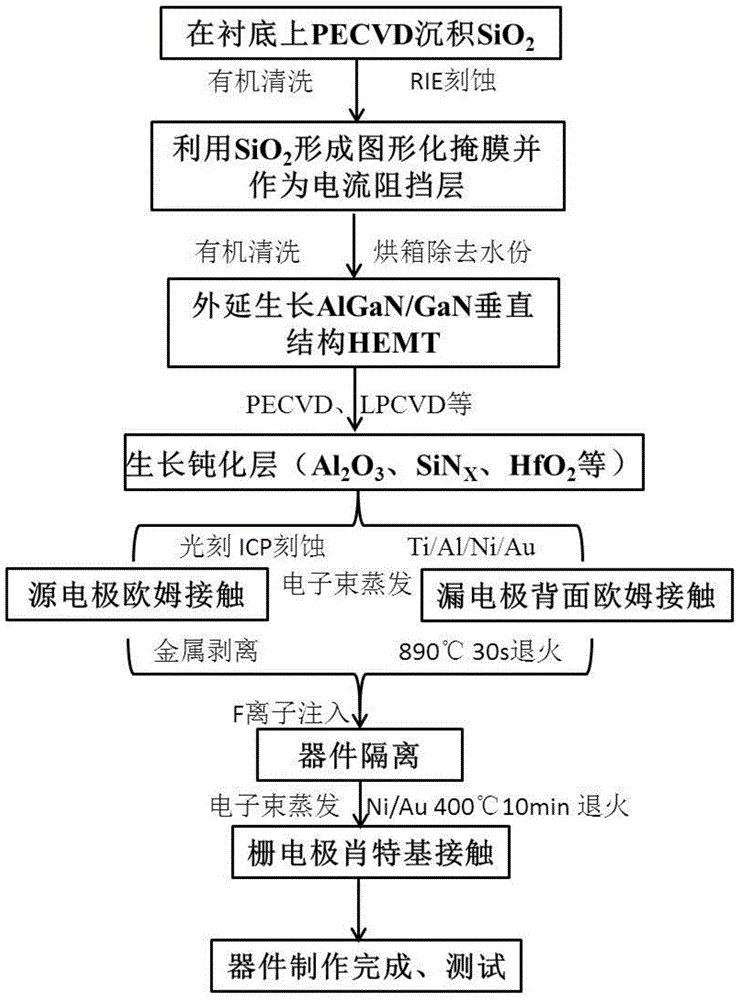

Lateral epitaxial technique based longitudinal structure AlGaN/GaN HEMT device and manufacture method thereof

ActiveCN104659089ARaise the barrier heightImprove crystal qualitySemiconductor/solid-state device manufacturingSemiconductor devicesElectricitySelf-diffusion

The invention discloses a lateral epitaxial technique based longitudinal structure AlGaN / GaN HEMT device and a manufacture method thereof. The device comprises a substrate, a current blocking layer and an epitaxial layer, wherein the current blocking layer is formed on the substrate; the epitaxial layer laterally epitaxially grows on the current blocking layer; a current conducting through hole is formed in the current blocking layer. According to the invention, the current blocking layer acts as an insulation layer, so that the problems that the two-dimensional electron gas concentration, self-diffusion, high electricity leakage and the like are caused by ion implantation damage due to Mg doping, barrier height improvement by Mg ion implantation and formation of a similar insulation layer by Al ion implantation in a traditional technology can be solved; meanwhile, the defects of high cost, long time consumption, technology complexity and the like due to secondary epitaxial growth are also prevented; in addition, a clearance region formed by incomplete healing is isolated via F ion implantation, so that the clearance region is not involved in the device structure, and the problems of electric leakage and the like caused by the clearance region are relieved effectively.

Owner:SUZHOU NENGWU ELECTRONICS TECH

Image sensor and manufacturing method and control method thereof

InactiveCN109950265AReduce blooming phenomenonRaise the barrier heightRadiation controlled devicesImaging qualityEngineering

The invention relates to the technical field of semiconductor manufacturing, in particular to an image sensor and a manufacturing method and a control method thereof. The image sensor comprises a substrate which is provided with a plurality of pixel units, wherein each pixel unit comprises a photoelectric doping area, a transistor area and an isolation area which are located at the two opposite sides of the photoelectric doping area, and the isolation area is used for isolating the adjacent pixel units; a transmission grid structure which is located on the surface of the substrate and is corresponding to the transistor region; and a bias electrode structure which is located at the position, corresponding to the isolation region, of the surface of the substrate and used for increasing the potential barrier between the adjacent pixel units. The image sensor reduces the probability that photo-induced electrons in the photoelectric doped region overflow to the adjacent pixel units under strong light, and improves the imaging quality.

Owner:HUAIAN IMAGING DEVICE MFGR CORP

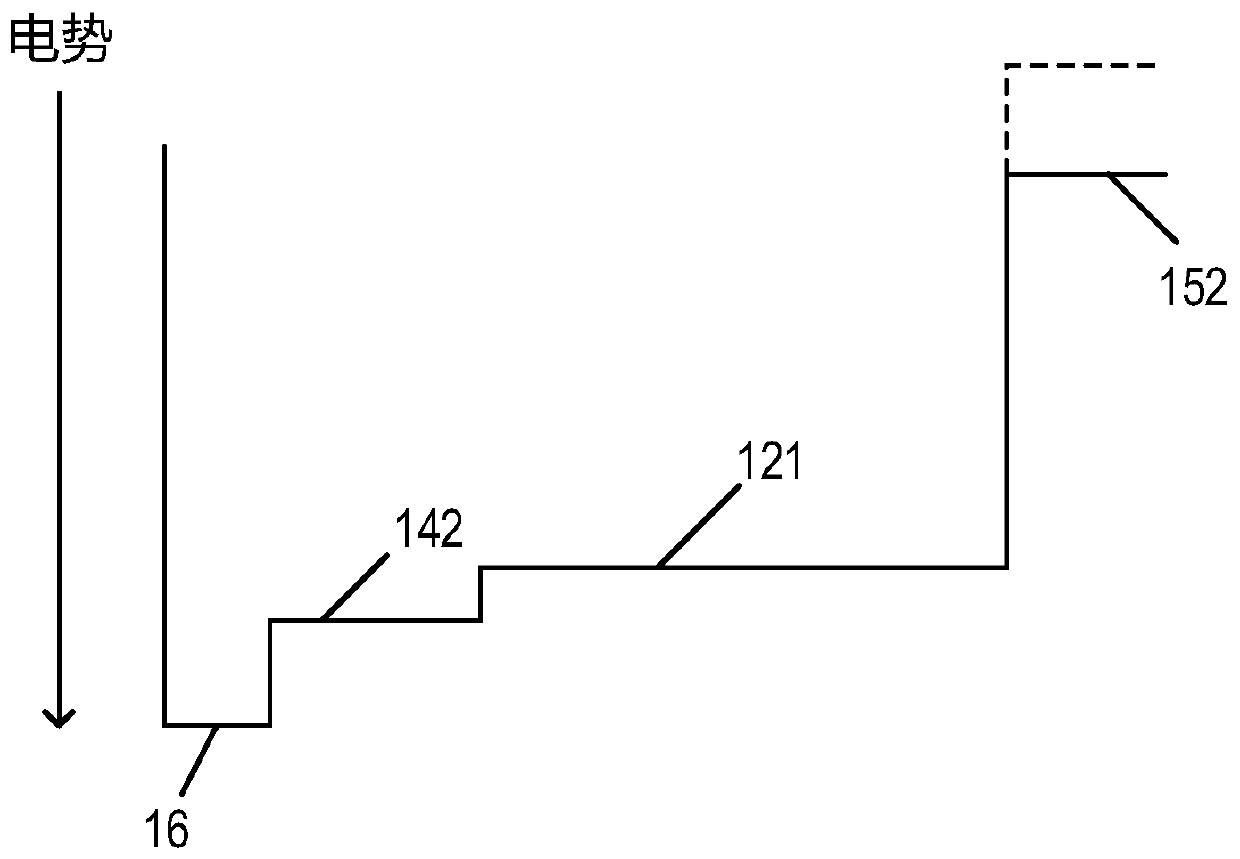

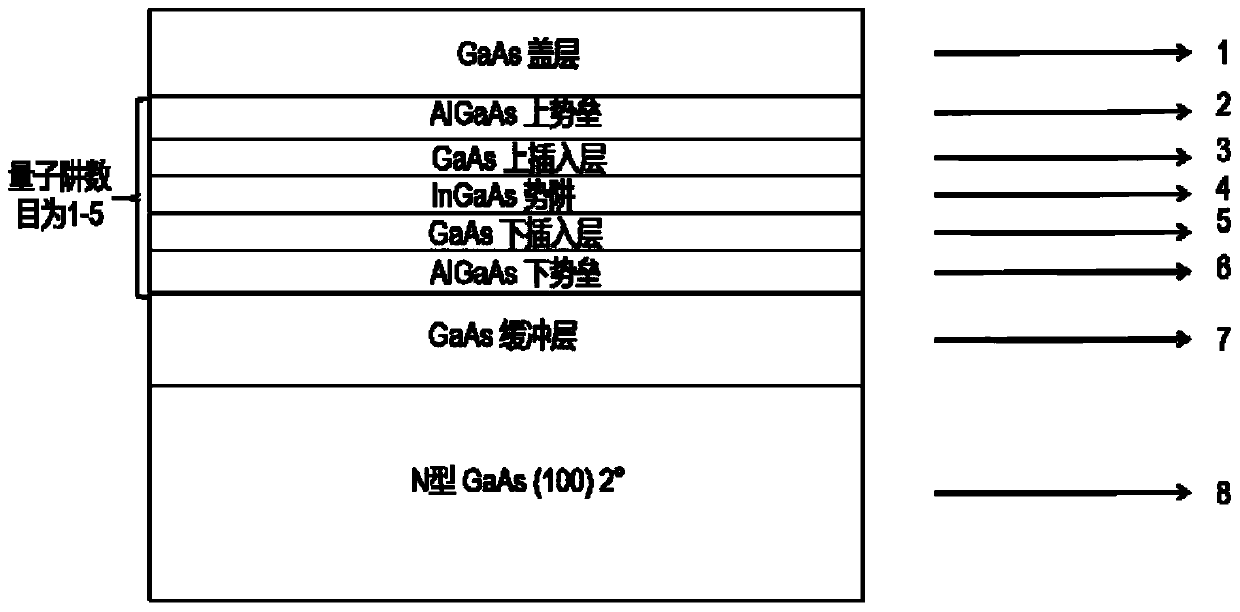

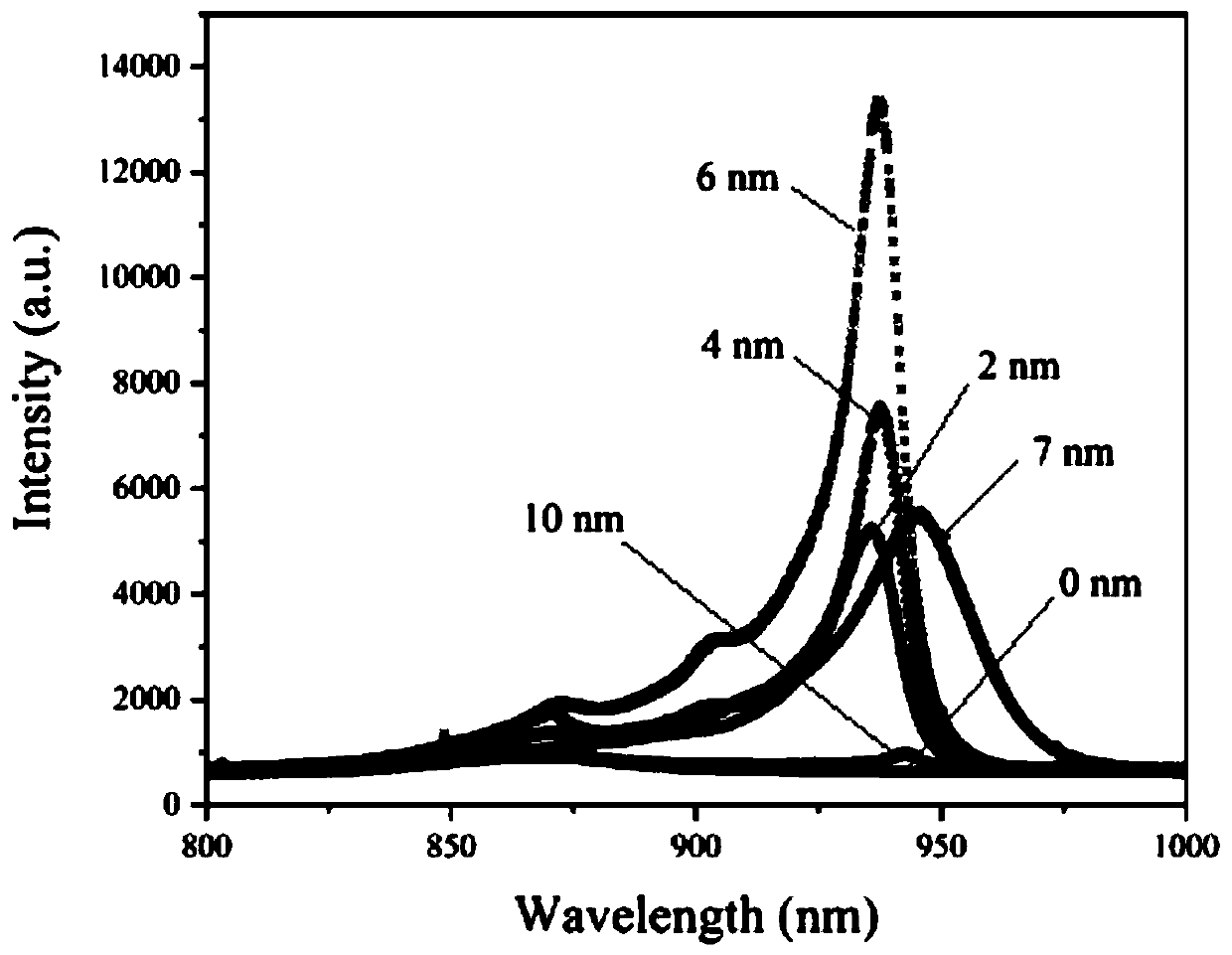

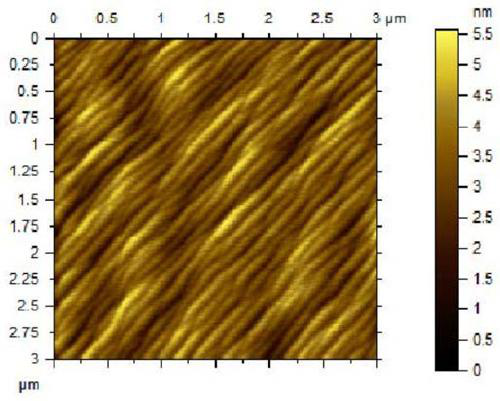

InGaAs/AlGaAs single quantum well and multi-quantum well semiconductor laser active region epitaxial structure

InactiveCN111490456APerformance enhancements and improvementsEnhanced photoluminescence intensityLaser detailsSemiconductor lasersChemistryMultiple quantum

Owner:CHANGCHUN UNIV OF SCI & TECH

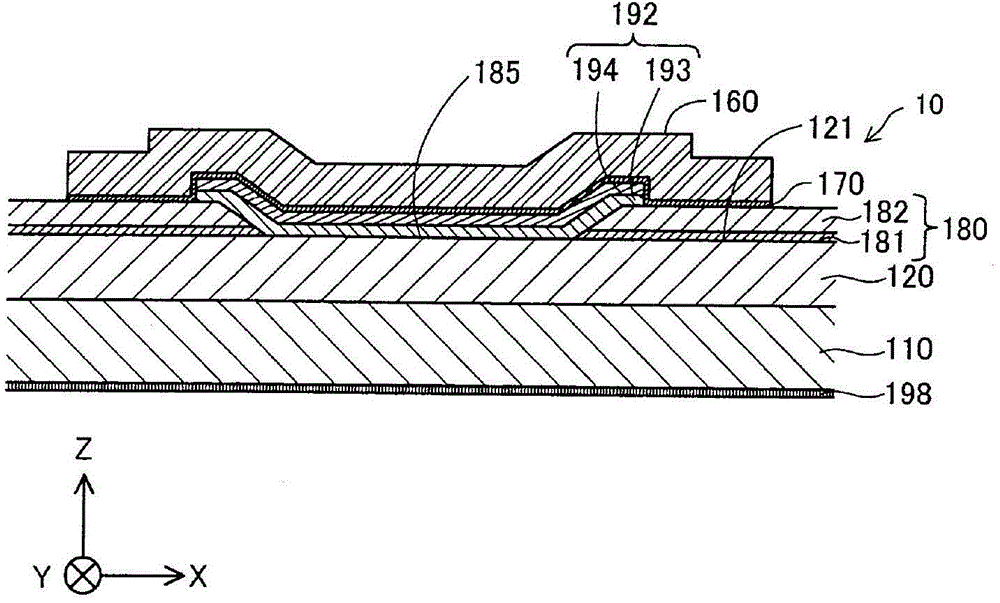

Semiconductor device and manufacturing method thereof

ActiveCN104979407ARaise the barrier heightSemiconductor/solid-state device manufacturingDiodePlatinumIridium

The present invention provides a technology for improving the barrier height of an electrode layer and a semiconductor layer. The semiconductor device comprises a semiconductor layer which is formed by semiconductors, and an electrode layer, wherein at least one part of the semiconductor layer is in Schottky connection with the electrode layer; the electrode layer comprises a first layer and a second layer successively from the semiconductor layer side; the first layer is mainly formed by nickel, and the film thickness is 50-200nm; the second layer is mainly formed by at least one metal of palladium, platinum and iridium; and the film thickness of the second layer is greater than the film thickness of the first layer.

Owner:TOYODA GOSEI CO LTD

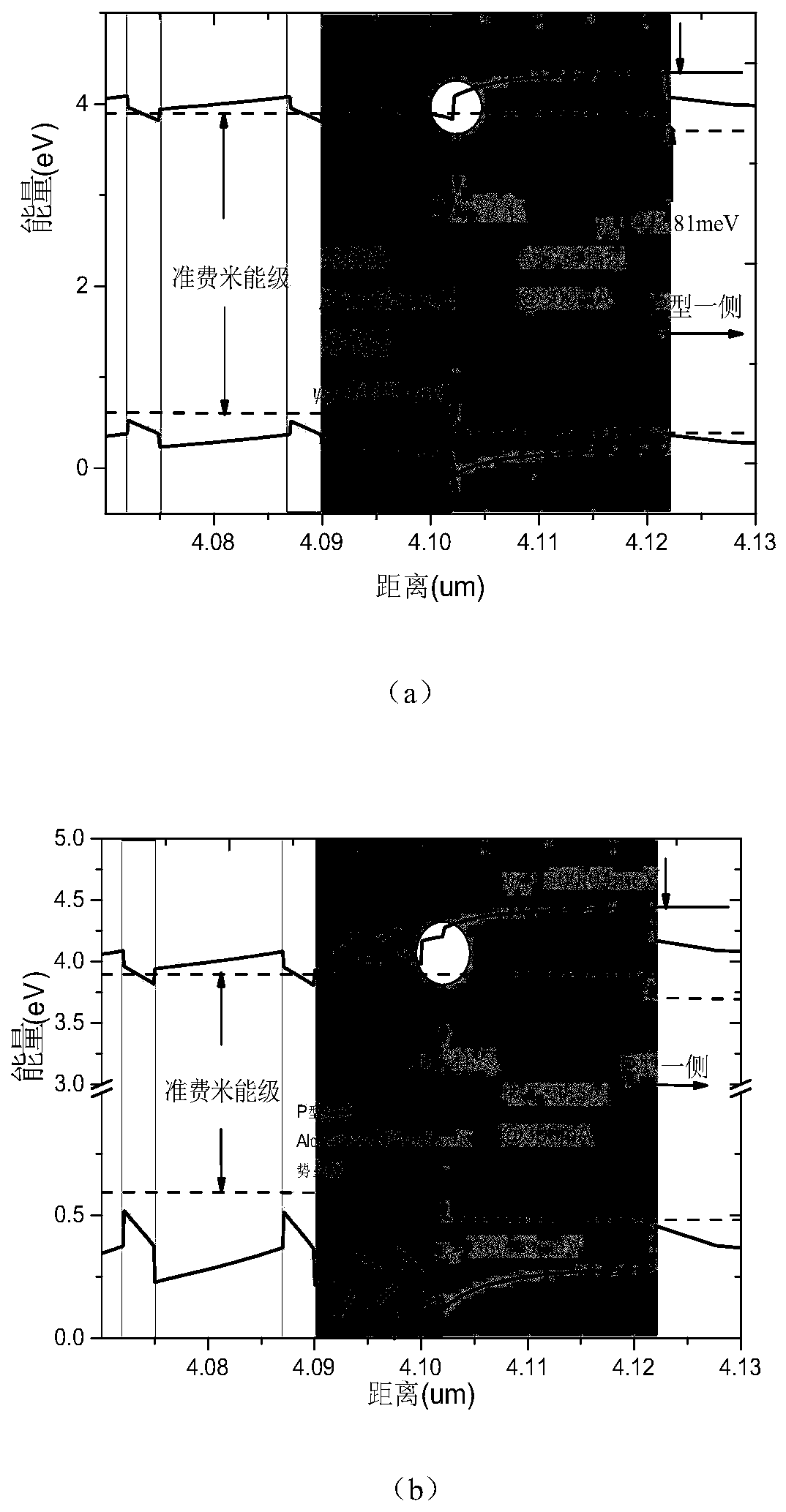

P-type doped AlScN/AlScN superlattice barrier layer-based efficient light-emitting diode and preparation method

ActiveCN110224047ARaise the barrier heightAchieve exhaustionSemiconductor devicesQuantum wellUltraviolet lights

The invention discloses a P-type doped AlScN / AlScN superlattice barrier layer-based efficient light-emitting diode and preparation method, and mainly solves the problems that an existing p-type regionis low in hole injection efficiency, and electronic leakage exists in a quantum well. The efficient light-emitting diode comprises a gallium oxide substrate layer, a high-temperature AlN nucleating layer and an n-type GaN layer from bottom to top, wherein an electrode and a working region layer are arranged on the n-type GaN layer; an electron blocking layer, a p-type layer and an electrode are sequentially arranged on the upper surface of the working region layer, and the working region layer comprises six periods AlxGa1-xN / AlyGa1-yN multi-quantum-well layer and a barrier layer; and the barrier layer adopts a P-type doped AlmSc1-mN / AlnSc1-nN superlattice structure, so that electron depletion with the electron blocking layer is realized. According to the light-emitting diode, electronic leakage is reduced, the hole injection potential barrier is reduced, the hole concentration in the quantum well is improved, and the light-emitting diode can be used for preparing efficient ultravioletand deep ultraviolet light-emitting equipment.

Owner:XIDIAN UNIV

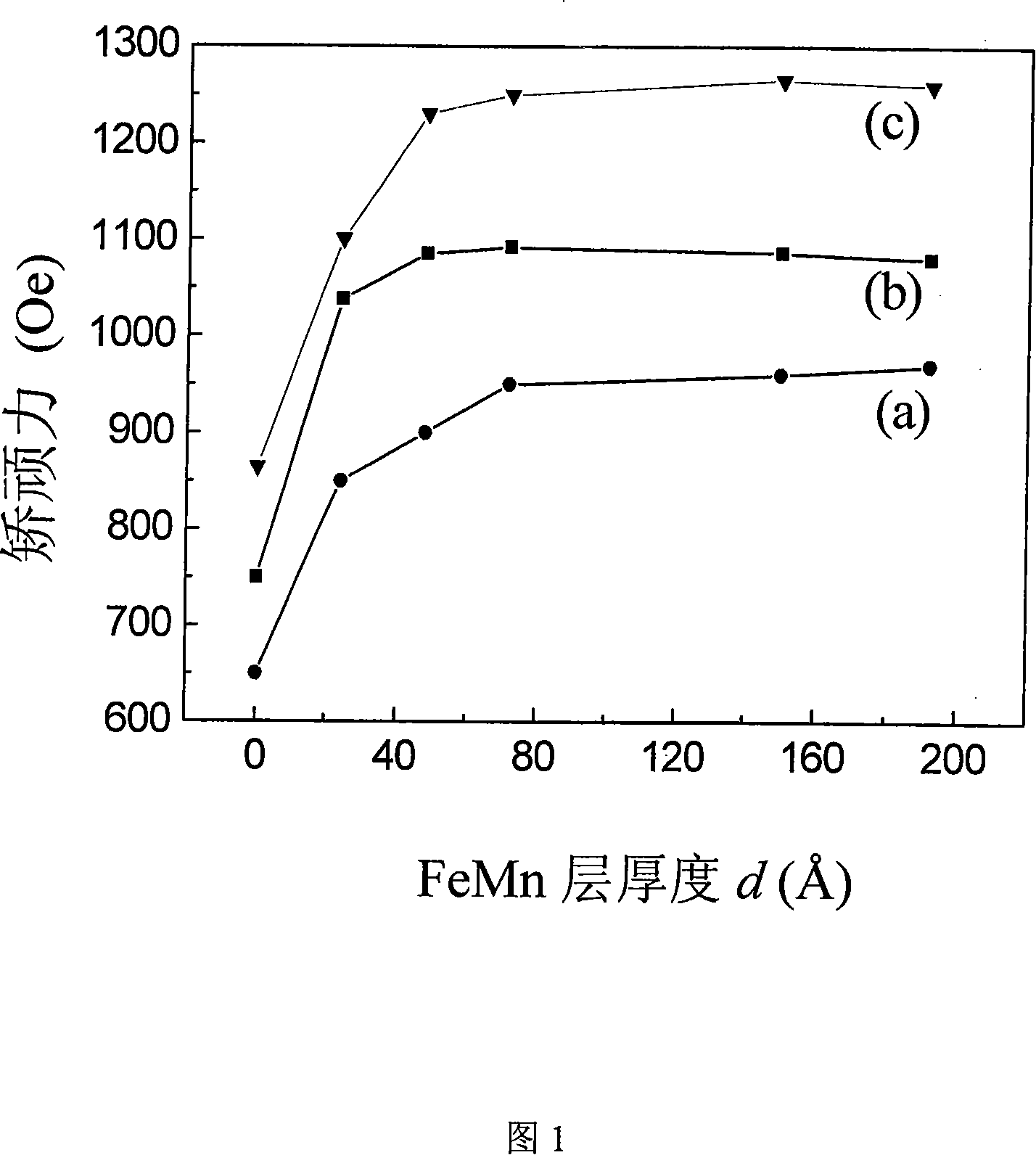

Method for increasing metal magnetic multilayer film coercive force

InactiveCN101148751AEnhanced perpendicular magnetic anisotropyImprove coercive forceVacuum evaporation coatingSputtering coatingVolumetric Mass DensityFuture application

The present invention is method of raising the coercive force of multilayer magnetic metal film with antiferromagnetic material. Multilayer Pt / [CoCr / Pt]5 / FeMn / Pt film is formed through depositing on cleaned glass substrate by means of using one magnetically controlled sputtering instrument. The multilayer magnetic metal film has the advantages of small thickness, excellent vertical magnetic anisotropy and high coercive force, and is suitable for use in ultrahigh density vertical magnetic record. In addition, the deposited film needs no annealing treatment, so that the present invention has also the advantages of low cost, simple preparation, etc and is suitable for future application.

Owner:UNIV OF SCI & TECH BEIJING

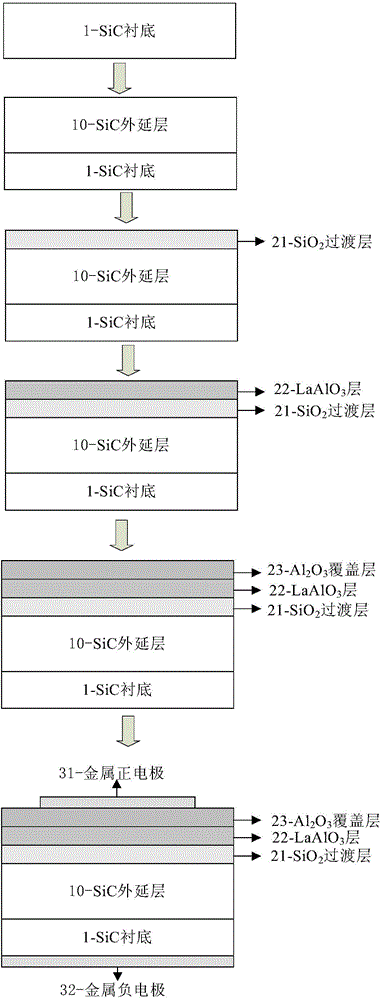

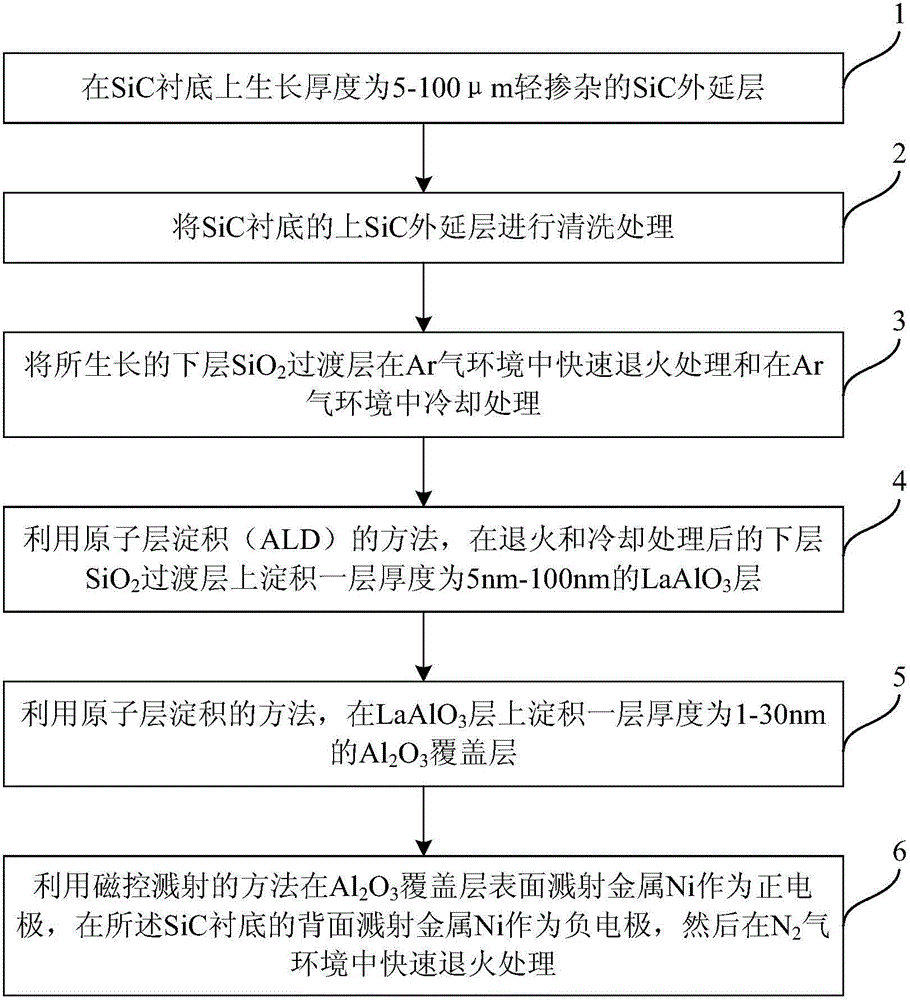

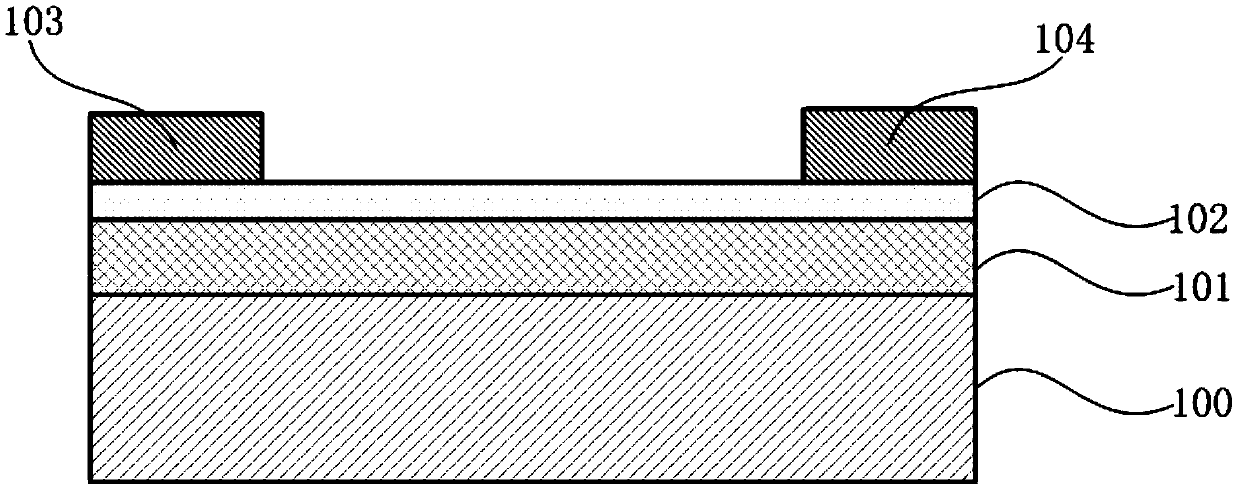

SiC MOS capacitor of Al2O3/LaAlO3/SiO2 stacking gate medium layer and manufacturing method

InactiveCN104576766AIncrease the critical breakdown electric fieldImprove breakdown characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceGate leakage current

The invention relates to a SiC MOS capacitor of an Al2O3 / LaAlO3 / SiO2 stacking gate medium layer and a manufacturing method. According to the capacitor, a SiC substrate is a heavy-doped SiC substrate layer, and a light-doped SiC epitaxial layer is arranged on the SiC substrate layer. The stacking gate medium layer comprises a lower SiO2 transition layer, an LaAlO3 layer and an Al2O3 covering layer. The lower SiO2 transition layer is arranged on the SiC epitaxial layer, the LaAlO3 layer is arranged on the lower SiO2 transition layer and provided with the Al2O3 covering layer, and a positive electrode and a negative electrode are connected with the surface of the Al2O3 covering layer and the back surface of the SiC substrate respectively. According to the SiC MOS capacitor of the stacking gate medium layer, the interface state density and boundary trap density are lowered, the MOS channel mobility is increased, gate leakage current is reduced, the voltage endurance capability of the medium layer is improved, and the quality and reliability of the SiC MOS capacitor are improved.

Owner:XIDIAN UNIV

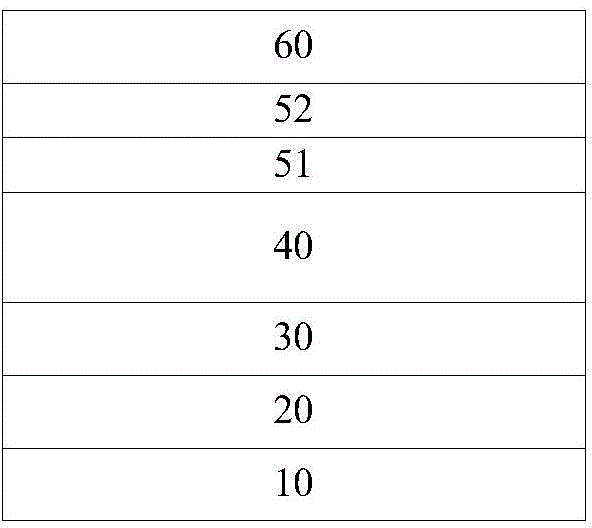

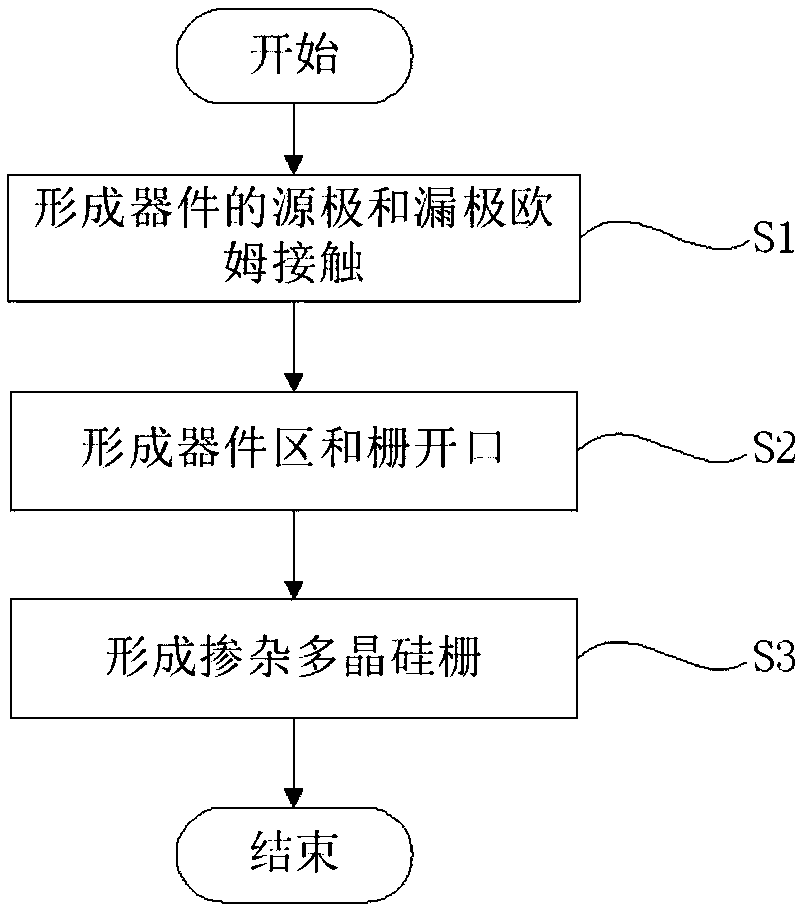

Gate-ballast structure RF AlGaN/GaN HEMTs device and preparation method thereof

ActiveCN109545760AImprove cooling effectRaise the barrier heightSemiconductor/solid-state device detailsSolid-state devicesBallast resistorRadio frequency

The invention belongs to the technical field of a semiconductor and relates to a gate-ballast structure RF AlGaN / GaN HEMTs device and a preparation method thereof. The device includes a AlGaN / GaN substrate on SiC, a gate, a source and a drain, wherein the gate is a doped polysilicon, and square resistance is in a range of 20-40omega / sq. The doped polysilicon is taken as a gate, barrier potential height is high, a gate leakage is smaller compared with a conventional Ni / Au schottky gate, power consumption of a radio frequency power device is reduced, efficiency is improved, and the doped polysilicon has relatively low Rg and has the ballast resistor function. The device can be applied to a multi-finger gate device AlGaN / GaN HEMTs, through adjusting Lg length, the purpose of optimizing Wg length is achieved, heat radiation of the device is effectively improved, the device can be further applied to AlGaN / GaN HEMTs, and the polysilicon gate can be biased by wider Vgs swing.

Owner:FUDAN UNIV

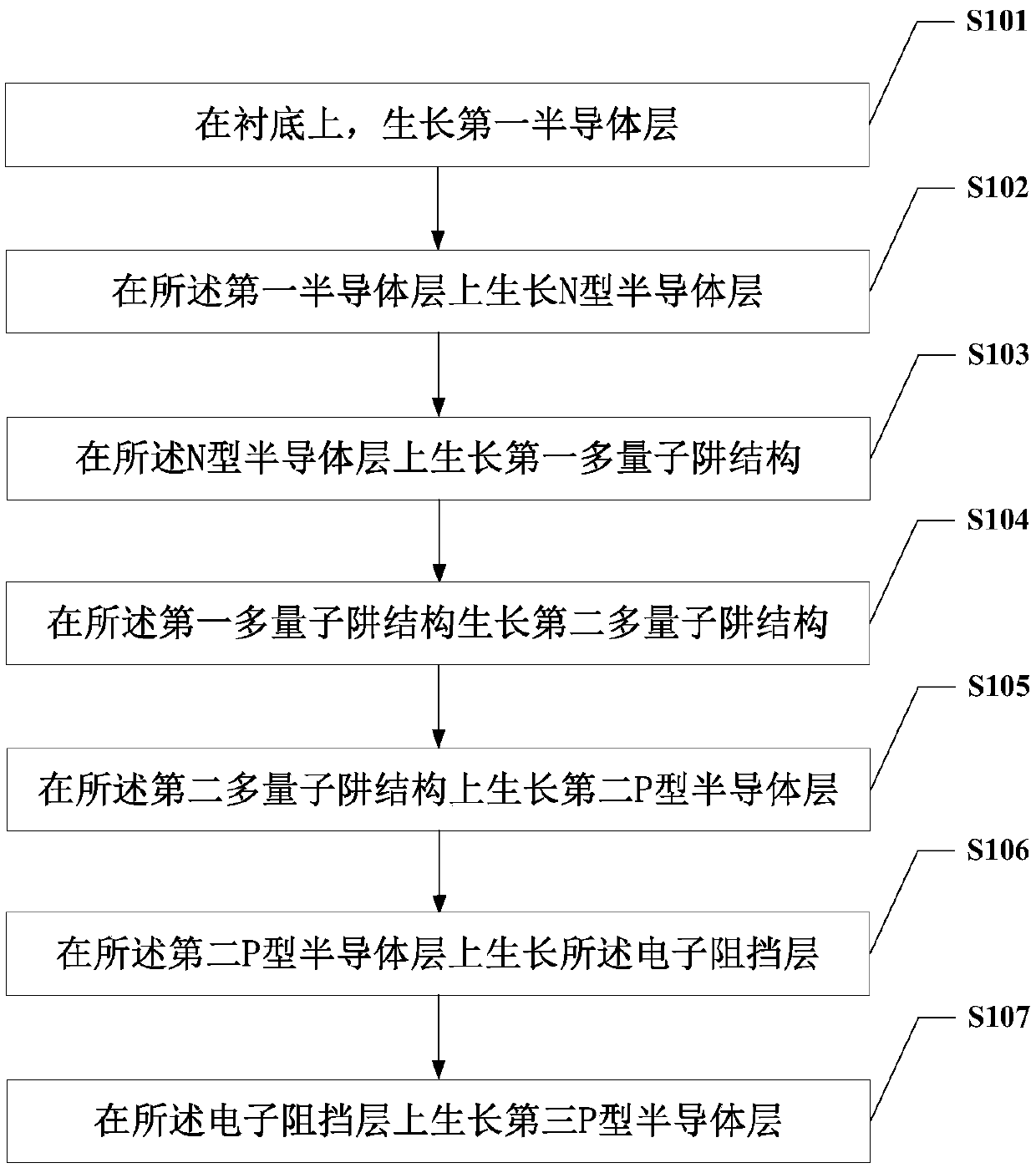

Light-emitting diode epitaxial structure growth method

ActiveCN110911529APrevent overflowImprove compound efficiencySemiconductor devicesElectron blocking layerNitride

The invention provides a light-emitting diode epitaxial structure growth method, which comprises the following steps of: growing a first semiconductor layer on a substrate; growing an N-type semiconductor layer on the first semiconductor layer; growing a first multi-quantum well structure on the N-type semiconductor layer; growing a second multi-quantum well structure on the first multi-quantum well structure, wherein the second multi-quantum well structure at least comprises at least two multi-quantum wells and a multi-quantum potential barrier, the multi-quantum potential barrier comprises afirst nitride containing aluminum and gallium and a second nitride containing aluminum, and the first nitride and the second nitride grow alternately; growing a second P-type semiconductor layer on the second multi-quantum well structure; growing the electron blocking layer on the second P-type semiconductor layer; and growing a third P-type semiconductor layer on the electron blocking layer.

Owner:宁波安芯美半导体有限公司

GaN-based LED epitaxial wafer and preparation method therefor

InactiveCN105428477AIncreases chance of radiative recombinationImprove crystal qualitySemiconductor devicesPower flowSilicon

The invention discloses a GaN-based LED epitaxial wafer and a preparation method therefor, and relates to the technical fields of a device characterized by a semiconductor and a preparation method for the device. The epitaxial wafer comprises a four-inch silicon substrate; and an AlN / AlGaN buffer layer, an unintentional doped U type GaN layer, a silicon doped N type GaN layer, an InGaN / GaN multiple quantum well luminous layer, a low temperature P type GaN layer, a P type superlattice AlInGaN / InGaN electronic barrier layer and a high temperature P type GaN layer are arranged on the upper surface of the four-inch silicon substrate from the bottom up in sequence. The epitaxial wafer improves the light output power of the LED under high electric current density injection; compared with the conventional P-AlGaN potential barrier structured epitaxial wafer, the light output power is improved by approximate 5-10% by the GaN-based LED epitaxial wafer provided by the invention; and meanwhile, the anti-static capability of the LED chip is improved by approximate 3-6%.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

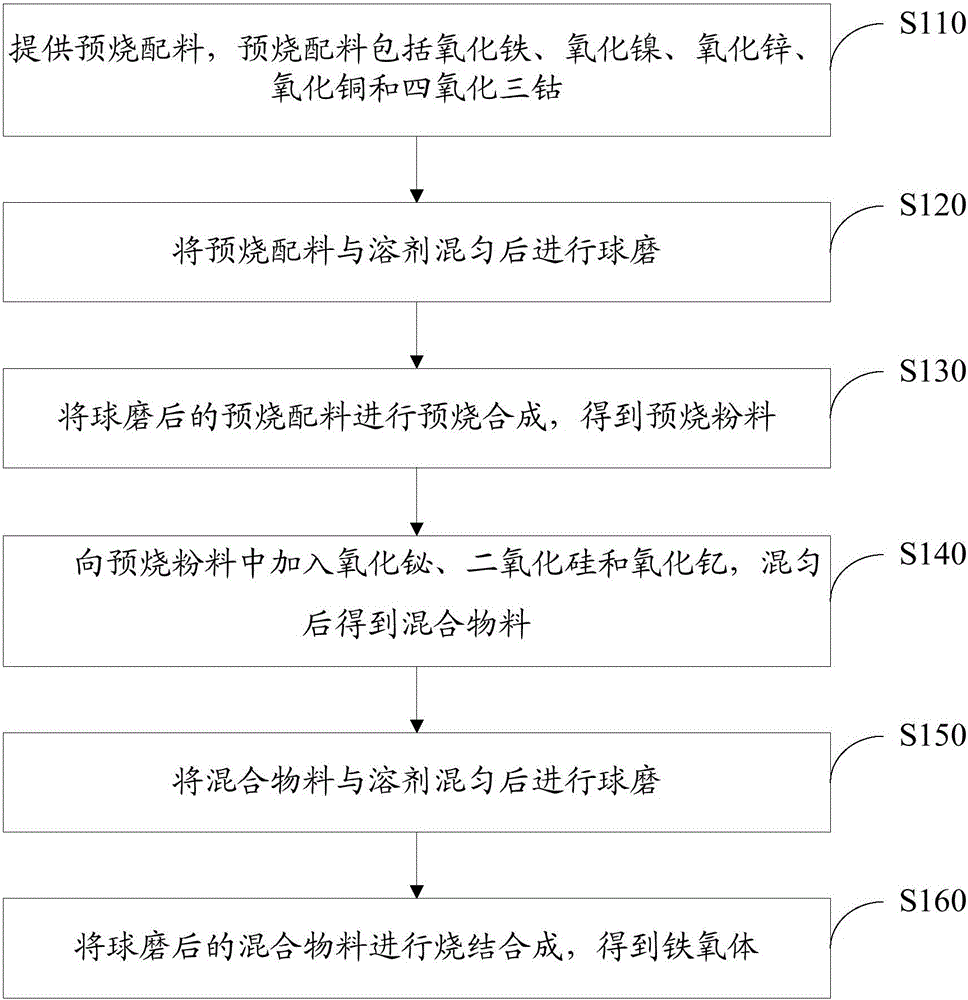

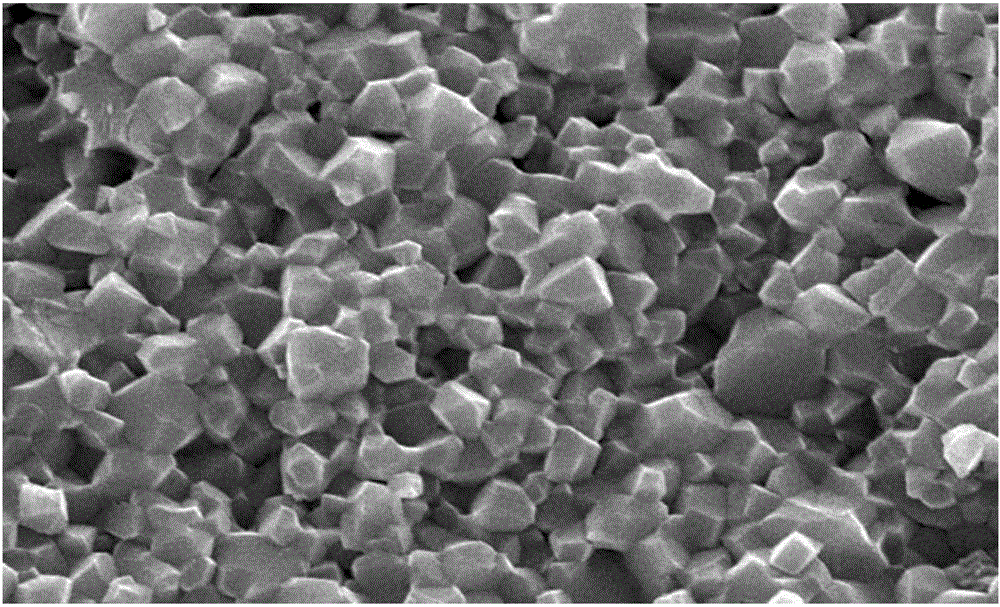

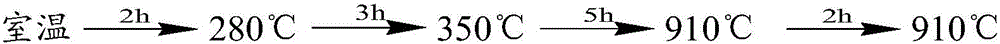

Preparation method for ferrite, ferrite and inductor

ActiveCN105777098AMagnet grains are small and uniformIncrease impactTransformers/inductances magnetic coresCopper oxideGrain structure

The invention discloses a preparation method for a ferrite, the ferrite prepared by the method and an inductor which comprises the ferrite. A crystal grain structure is formed by adding raw materials in batches and ball-milling, pre-sintering and synthesizing the main materials, such as iron oxide, nickel oxide, zinc oxide, copper oxide and cobaltosic oxide. Later, bismuth oxide, silicon dioxide and yttrium oxide are added into a pre-sintered powder material; the yttrium oxide can enter the pre-sintered and synthesized zinc oxide crystal grains, so that the density of the ferrite is improved, and the current impact resistance of the ferrite is improved. The prepared ferrite crystal grains are small; the crystal grain uniformity is high; the magnetic conductance change rate is low. According to the inductor which comprises the ferrite, the inductance value of the inductor is reduced slightly along with the increase of a superimposed current.

Owner:GUANGDONG FENGHUA ADVANCED TECH HLDG

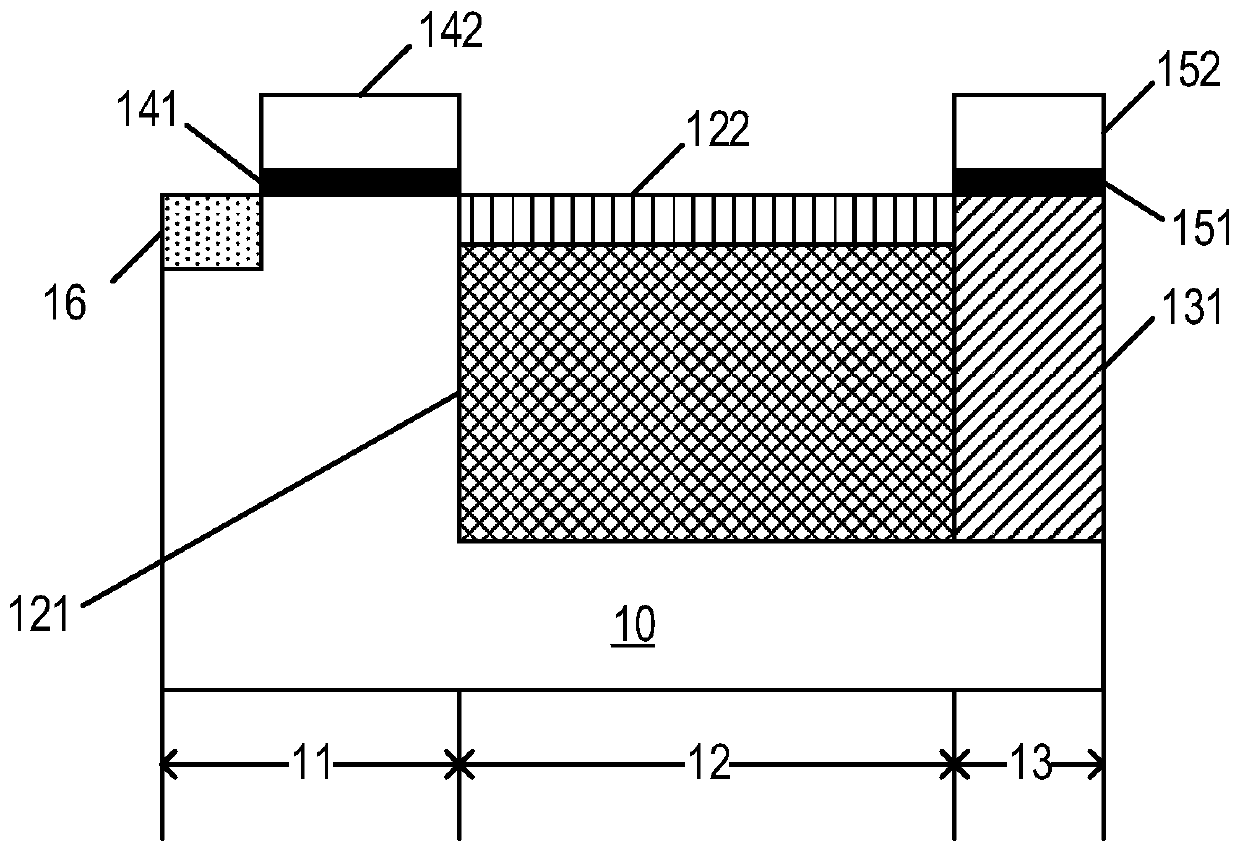

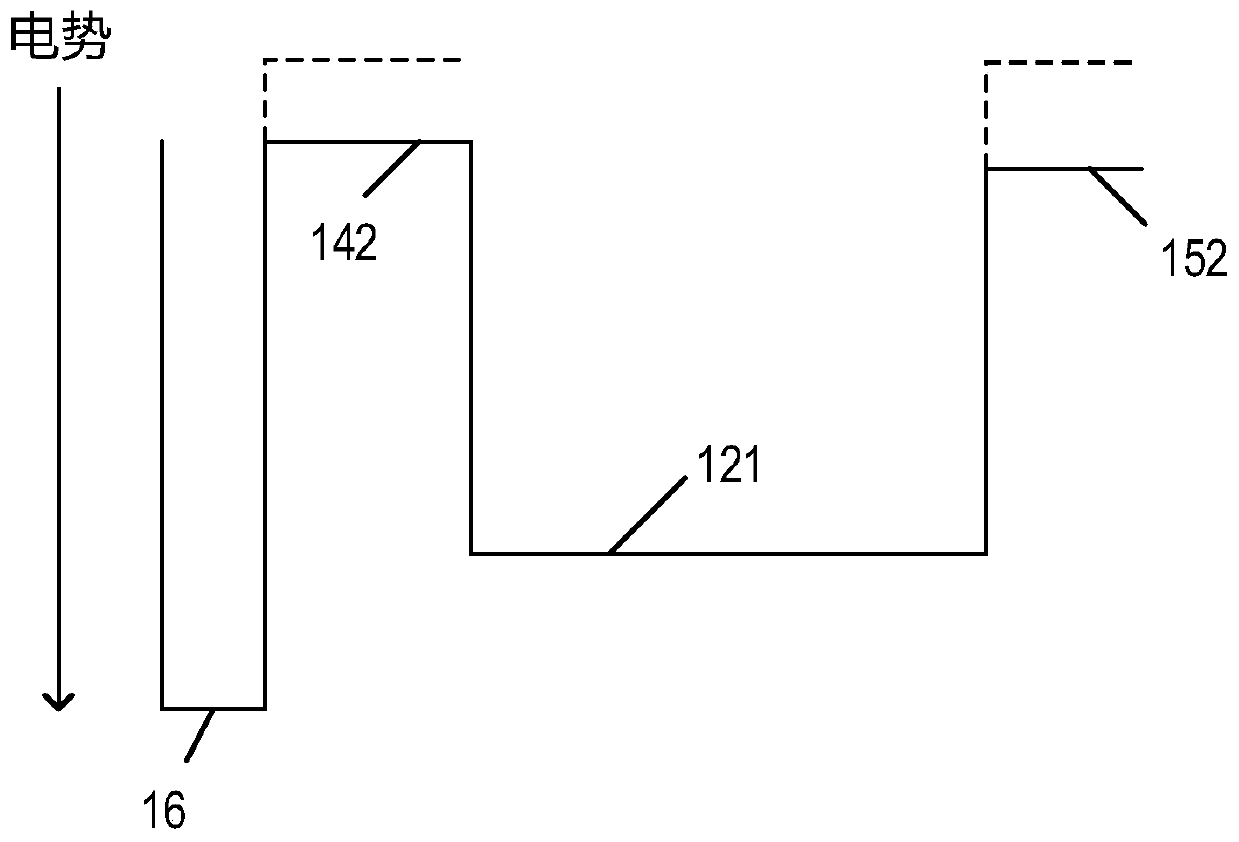

GaN Schottky diode and fabrication method thereof

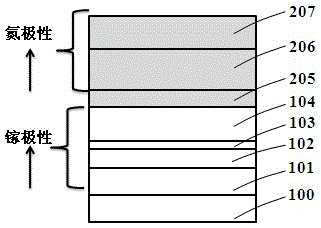

ActiveCN106952966ARaise the barrier heightReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideSchottky barrier

The invention relates to a GaN Schottky diode. The GaN Schottky diode comprises a substrate, an N+ GaN layer, an N-GaN layer table surface and a P-type GaN layer, wherein grooves are etched in the P-type GaN layer, Schottky metal layers are formed on the P-type GaN layer and are used as positive electrodes, and ohmic metal layers are formed on the N+ GaN layer and are used as negative electrodes. A fabrication method of the GaN Schottky diode comprises the steps of sequentially growing the N+ GaN layer, the N-GaN layer and the P-type GaN layer on an upper surface of the substrate; forming the table surface with the P-type GaN layer and the N-GaN layer, and partially etching the P-type GaN layer on each table surface to form a series of grooves; and depositing the Schottky metal layers on the P-type GaN layer to used as the positive electrodes, and depositing the ohmic metal layers on the N+GaN layer to be used as the negative electrodes. By the GaN Schottky diode, carriers under a Schottky electrode can be consumed, the Schottky barrier height is increased, the leakage current is reduced, the breakdown voltage is increased, the grooves under the Schottky electrode can be used for reducing the positive conduction voltage, so that the positive characteristic and the negative characteristic of the device are simultaneously improved.

Owner:JIANGSU CORENERGY SEMICON CO LTD

Limitation-enhanced GaN-based deep ultraviolet laser

InactiveCN111817137AIncrease the restrictive effectReduce distributionOptical wave guidanceQuantum wellUltraviolet

The invention provides a limitation-enhanced GaN-based deep ultraviolet laser, which comprises an N-type electrode, a substrate, an N-type lower limiting layer, an N-type AlxGa1-xN lower waveguide layer, an active region, a P-type AlxGa1-xN upper waveguide layer, a P-type electron blocking layer, a P-type upper limiting layer, a P-type GaN ohmic contact layer and a P-type electrode from bottom totop in sequence. The N-type AlxGa1-xN lower waveguide layer and the P-type AlxGa1-xN upper waveguide layer are both of an Al component gradual change type, and through Al component gradient design ofthe N-type AlxGa1-xN lower waveguide layer and the P-type AlxGa1-xN upper waveguide layer, a light field is guided to be close to the active region, so that the optical loss is reduced, the limitationof a quantum well to carriers is enhanced, the electron leakage is inhibited, and the threshold value and the output power are improved.

Owner:北京蓝海创芯智能科技有限公司

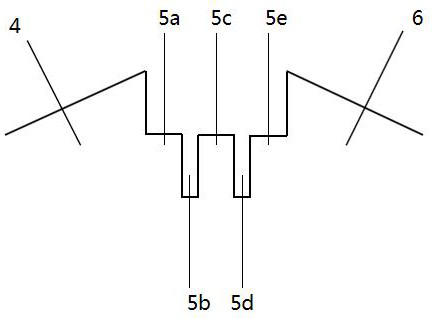

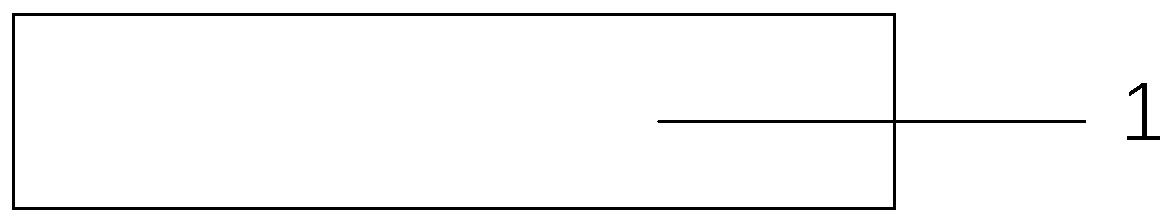

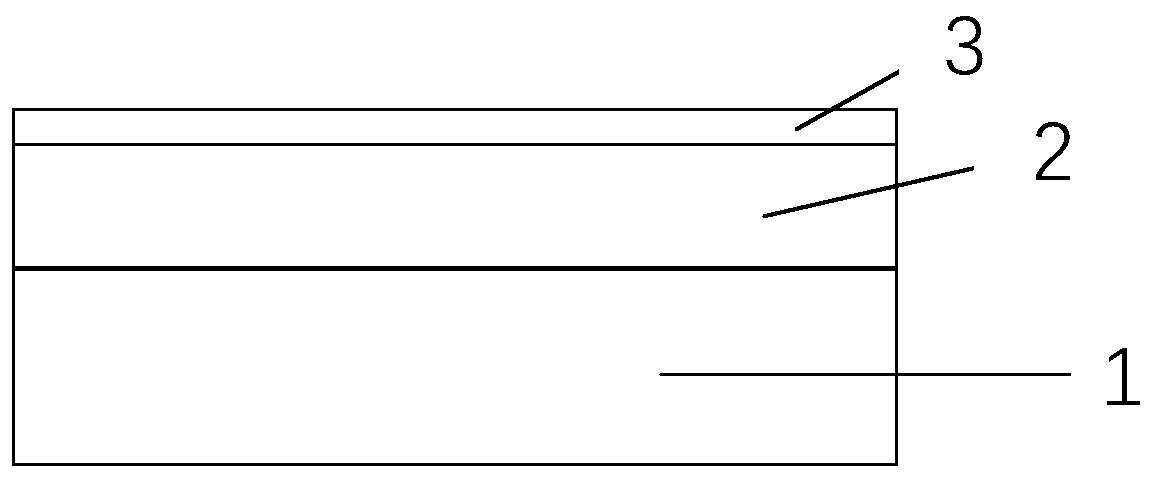

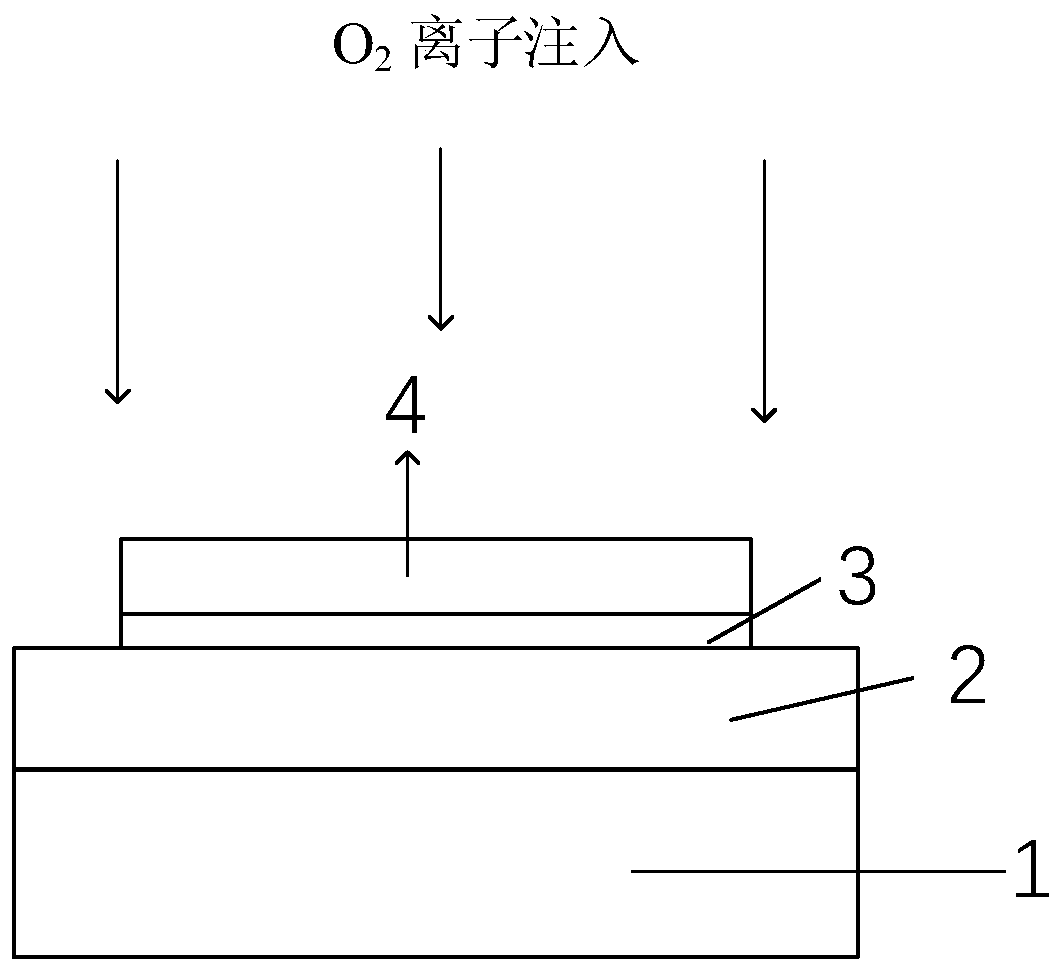

GaN-based vertical diode and preparation method thereof

PendingCN111180335AImprove breakdown voltageSurface Differentiation Electric Field StrengthSemiconductor/solid-state device manufacturingDiodeOxygen ionsPhysical chemistry

The invention provides a GaN-based vertical diode and a preparation method thereof. The preparation method comprises the steps: S1, sequentially growing an n-GaN layer and an AlGaN layer on a GaN substrate; S2, growing a barrier layer on the AlGaN layer, etching the end part of the barrier layer and the end part of the AlGaN layer, and exposing the end part of the n-GaN layer; S3, sequentially injecting energy from low to high through oxygen ion injection, and forming a Ga2O3 high-resistance region at the end part of the n-GaN layer; S4, removing the barrier layer, and depositing an anode on the AlGaN layer; S5, depositing an oxide layer on the AlGaN layer, and forming a hole in the top of the oxide layer; and S6, depositing a cathode on the back surface of the GaN substrate. A large number of electrons are attracted through an oxygen ion implantation technology, so that an electric field is distributed more uniformly, the breakdown voltage is improved, a 5nm n-AlGaN thin layer grows epitaxially, the current transport capacity is enhanced through a polarization effect, and the SBD breakdown voltage is improved by adopting an oxide layer terminal structure.

Owner:SOUTH UNIVERSITY OF SCIENCE AND TECHNOLOGY OF CHINA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com