Method for manufacturing medium/nitride composite structure enhanced field effect transistor

A composite structure, field effect transistor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as energy band distortion, reduce open-channel current, etc., to prevent energy band distortion, reduce series resistance, Improve the effect of 2D features

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

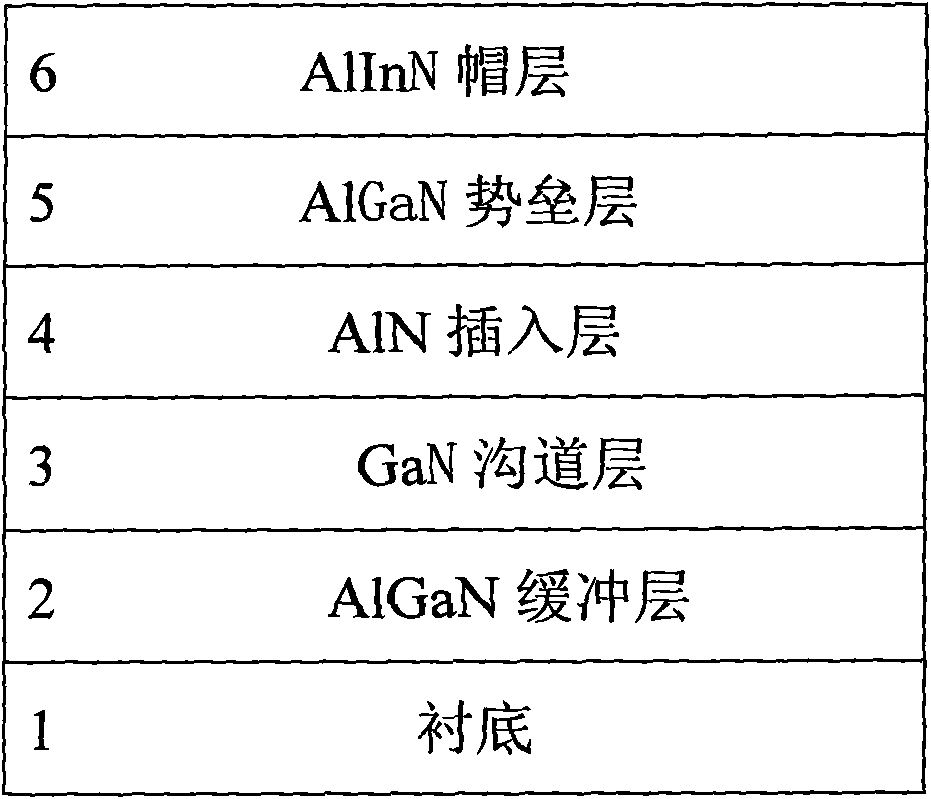

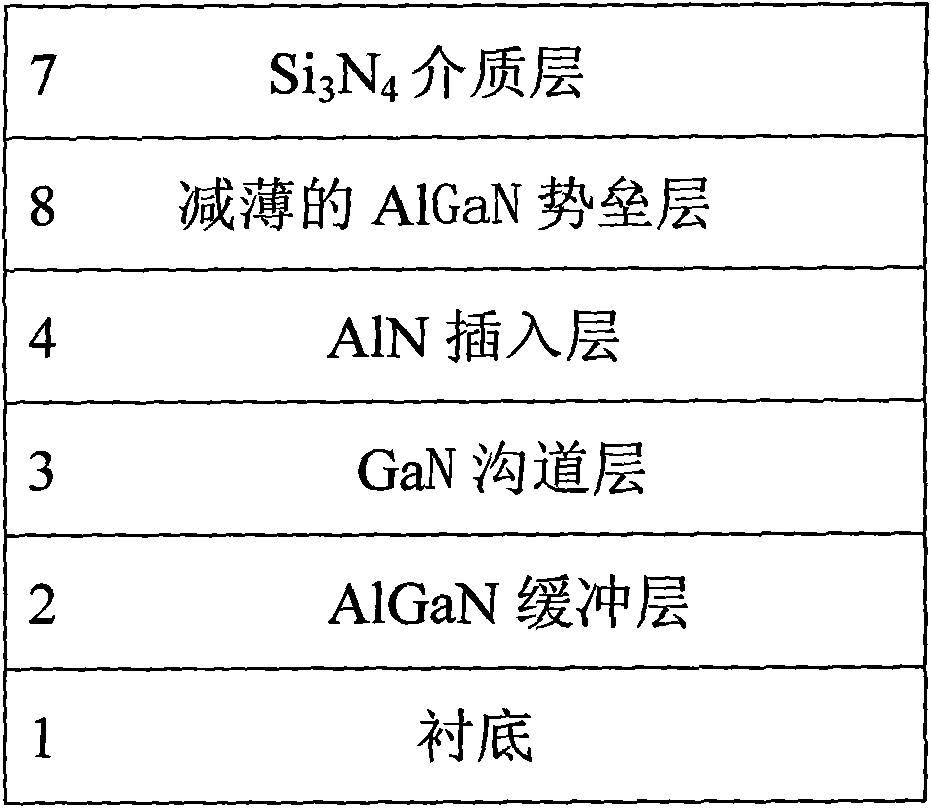

[0027] Growth of Al on substrate 1 0.04 Ga 0.96 The N buffer layer 2 and the 10nm undoped GaN channel layer 3 constitute a back barrier. Then grow a 1nm undoped AlN insertion layer 4, 5nm undoped Al on the channel layer 3 0.25 Ga 0.75 N barrier layer and 14nm undoped Al 0.83 In 0.17 The N cap layer 6 constitutes the front barrier. Calculate the band order and polarization charge on various heterogeneous interfaces, and self-consistently solve the Schrodinger equation and Poisson equation based on the effective mass and dielectric constant of each layer of material, and the electron gas density of the outer channel is calculated as 1.775*10 13 cm -2 . The electron wave function is all quantum confined in the GaN channel well, and the electron has strong two-dimensional characteristics and high transport performance. The series resistance of the outer channel and the ohmic contact resistance are reduced. Then use dry trenching process to etch the AlInN cap layer 6 and thin the A...

Embodiment 2

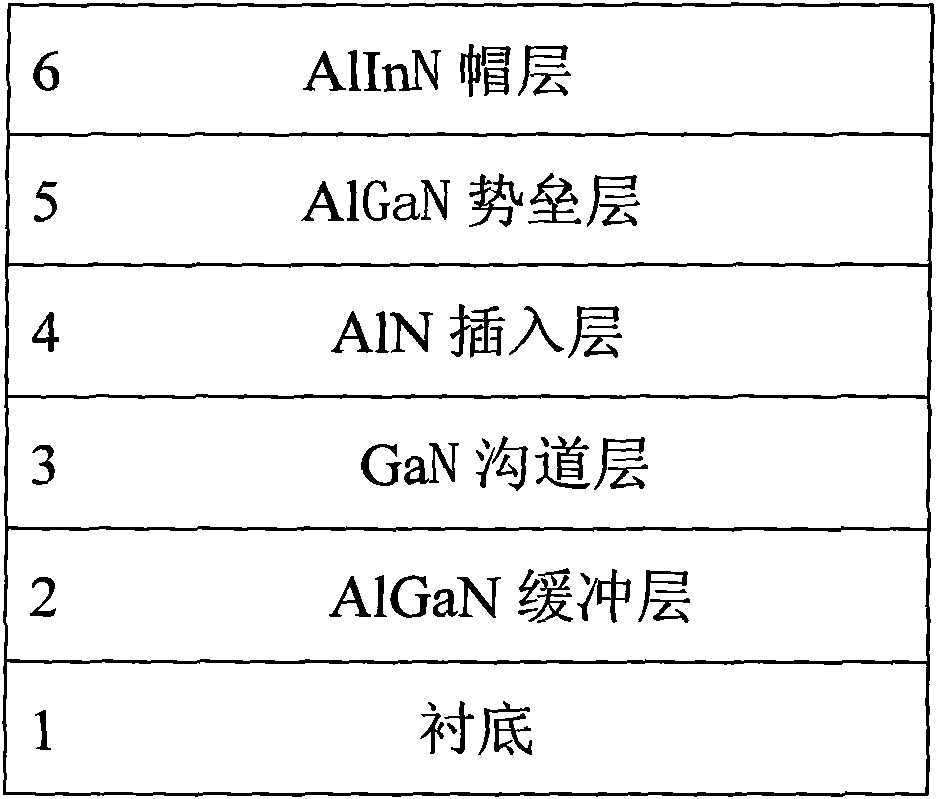

[0029] Growth of Al on substrate 1 0.07 Ga 0.93 The N buffer layer 2 and the 10nm undoped GaN channel layer 3 constitute a back barrier. Then grow a 1nm undoped AlN insertion layer 4, 5nm undoped Al on the channel layer 3 0.3 Ga 0.7 N barrier layer and 20nm undoped Al 0.83 In 0.17 The N cap layer 6 constitutes the front barrier. Solving the Schrodinger equation and Poisson equation in a self-consistent manner, the electron gas density of the outer channel is calculated as 1.789*10 13 cm -2 . The electron wave function is all quantum confined in the GaN channel well, and the electron has strong two-dimensional characteristics and high transport performance. The series resistance of the outer channel and the ohmic contact resistance are reduced. Then use dry trenching process to etch the AlInN cap layer 6 and thin the AlGaN barrier layer, leaving a 2nm AlGaN barrier layer, and deposit 5nm Si by ALD process 3 N 4 Layer 7, using fluorine plasma process in Si 3 N 4 Introduce 2*10 i...

Embodiment 3

[0031] Growth of Al on substrate 1 0.1 Ga 0.9 The N buffer layer 2 and the 10nm undoped GaN channel layer 3 constitute a back barrier. Then grow a 1nm undoped AlN insertion layer 4, 5nm undoped Al on the channel layer 3 0.35 Ga 0.65 N barrier layer and 25nm undoped Al 0.83 In 0.17 The N cap layer 6 constitutes the front barrier. Solving the Schrodinger equation and Poisson equation in a self-consistent manner, the electron gas density of the outer channel is calculated to be 1.738*10 13 cm -2 . The electron wave function is all quantum confined in the GaN channel well, and the electron has strong two-dimensional characteristics and high transport performance. The series resistance of the outer channel and the ohmic contact resistance are reduced. Then use dry trenching process to etch the AlInN cap layer 6 and thin the AlGaN barrier layer, leaving 2nm AlGaN barrier layer, and deposit 5nm Si by ALD process 3 N 4 Layer 7, using fluorine plasma process in Si 3 N 4 Introduce 2*10 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More