Test method for lateral insulated gate bipolar transistor interface state and five-port device

A bipolar transistor and interface state technology, which is applied in the reliability field of power semiconductor devices, can solve the problems that the polysilicon gate field plate and the field plate end interface state and interface damage cannot be measured.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

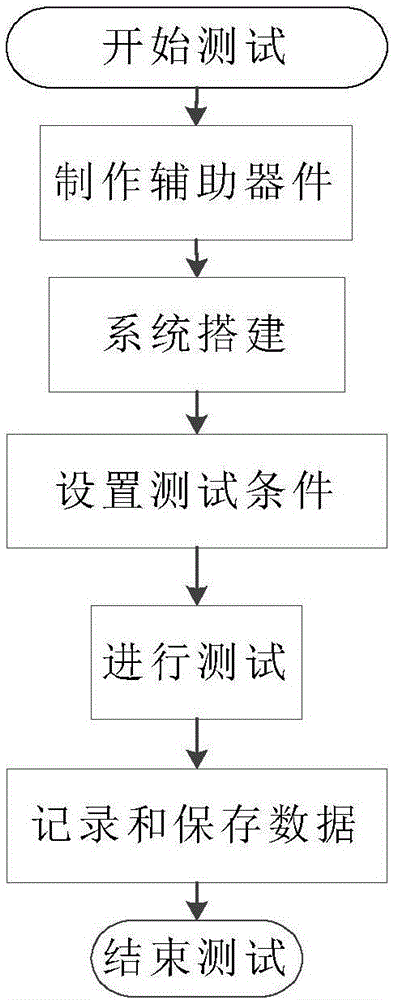

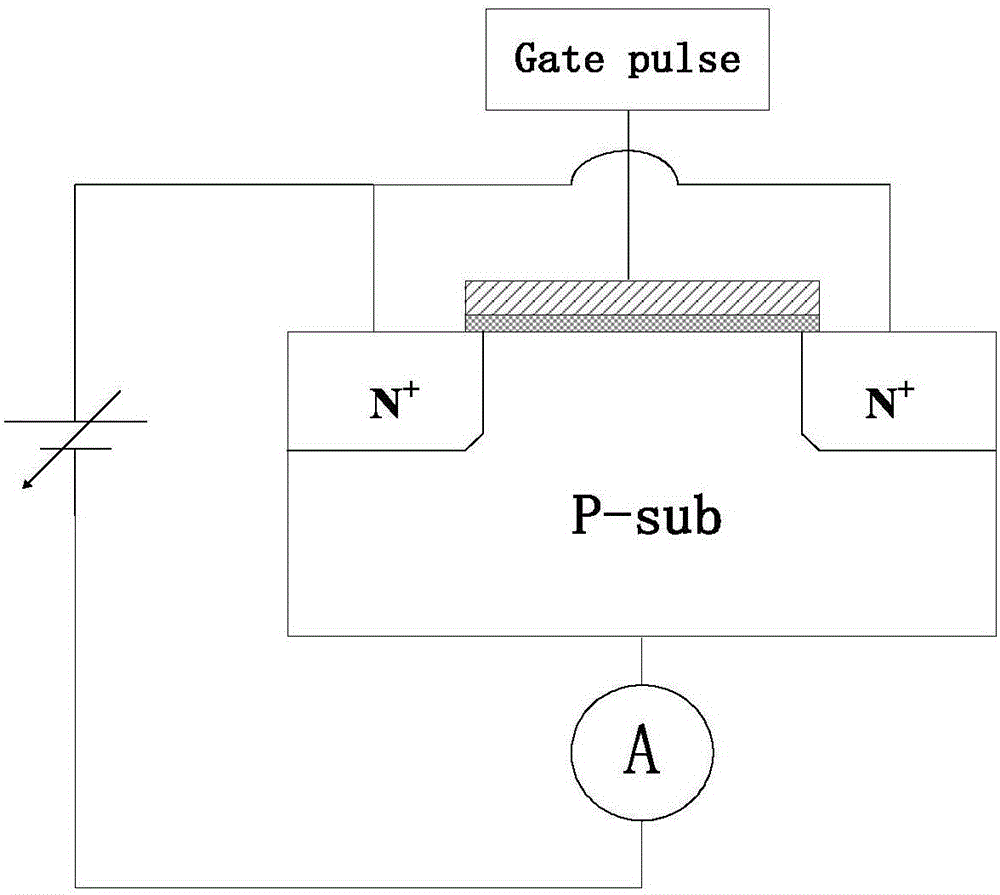

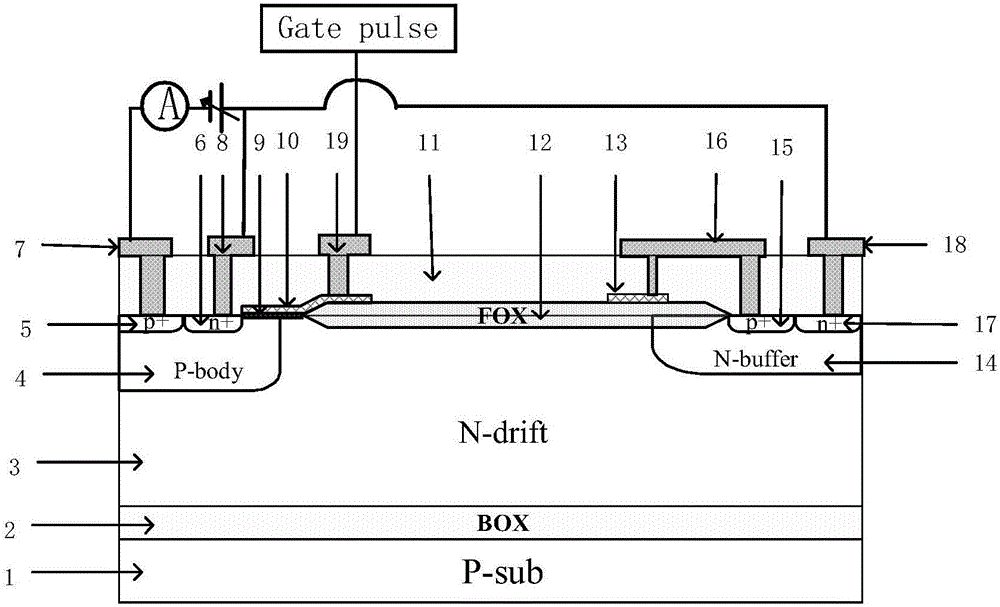

[0028] A test method for the interface state of a lateral insulated gate bipolar transistor, including the test of the charge pump current in the channel region and the beak region, and is characterized in that it also includes the test of the charge pump current in the field plate region of the polysilicon gate and the end region of the field plate , the test of the polysilicon gate field plate region and the field plate end region charge pump current adopts the following method:

[0029] First manufacture a 5-port device next to the target device on the same wafer, and the auxiliary 5-port device is to set a charge pump electron supply area 17 in the N-type buffer zone 14 of a traditional lateral insulated gate bipolar transistor; then carry out system construction, In the test of the number of interface states in the charge pump experiment, the instrument we use is the semiconductor tester Keithley4200. Three leads are drawn from Keithley4200, and one is the cathode N + Reg...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com