Field effect transistor adapted for extra-dup submicrometer field and preparation process thereof

A field-effect transistor, ultra-deep sub-micron technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., to achieve the effects of ensuring overdrive capability, suppressing inter-band tunneling current, and reducing source-drain parasitic capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

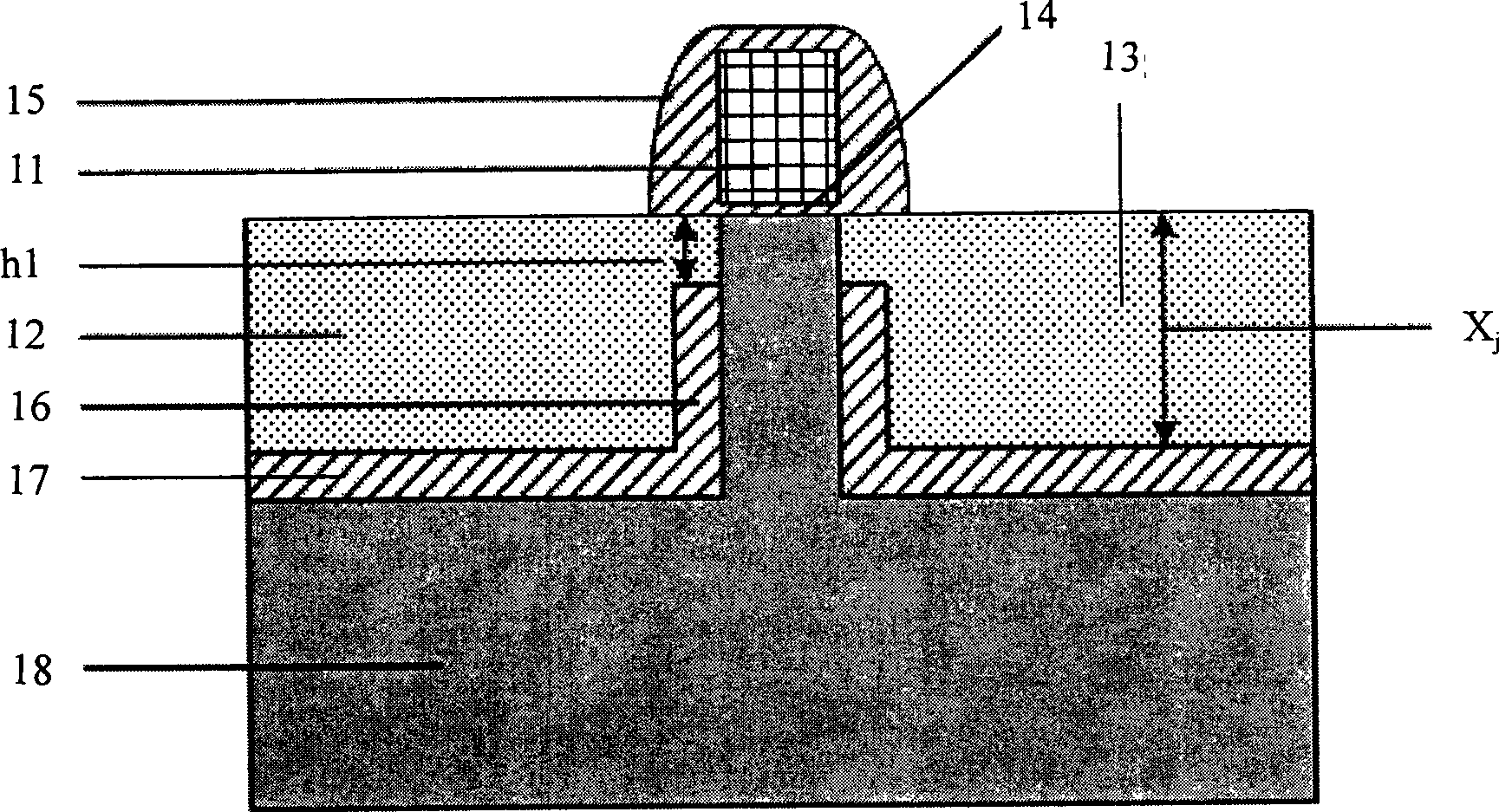

[0056] As shown in FIG. 1( a ), it is a schematic diagram of the field effect transistor structure of the present invention. In this field effect transistor structure, the most important components are the first dielectric isolation layer and the second dielectric isolation layer. The first dielectric isolation layer is between the source and drain and the body region, and is perpendicular to the direction of the channel. The second dielectric isolation layer is located under the source and drain and parallel to the direction of the channel. The two are connected into an "L" shape. There is a certain distance between "L" and the surface of the silicon chip, which is the connection between the source and drain and the channel. The first dielectric isolation layer of the vertical part is formed of silicon nitride, and the second dielectric isolation layer of the horizontal part is formed of a void layer.

[0057] The above-mentioned field effect transistor is manufactured usi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com