Patents

Literature

146results about How to "Avoid over etching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

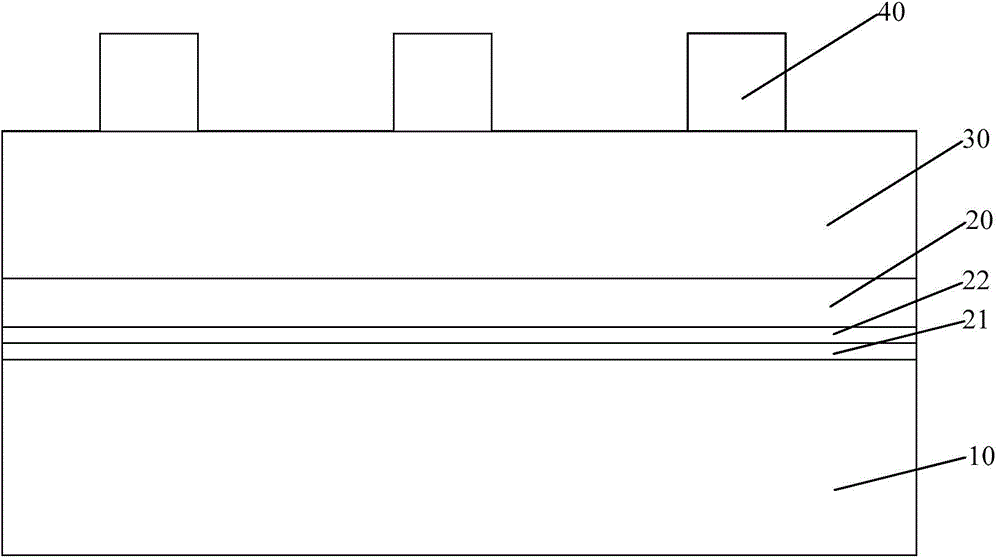

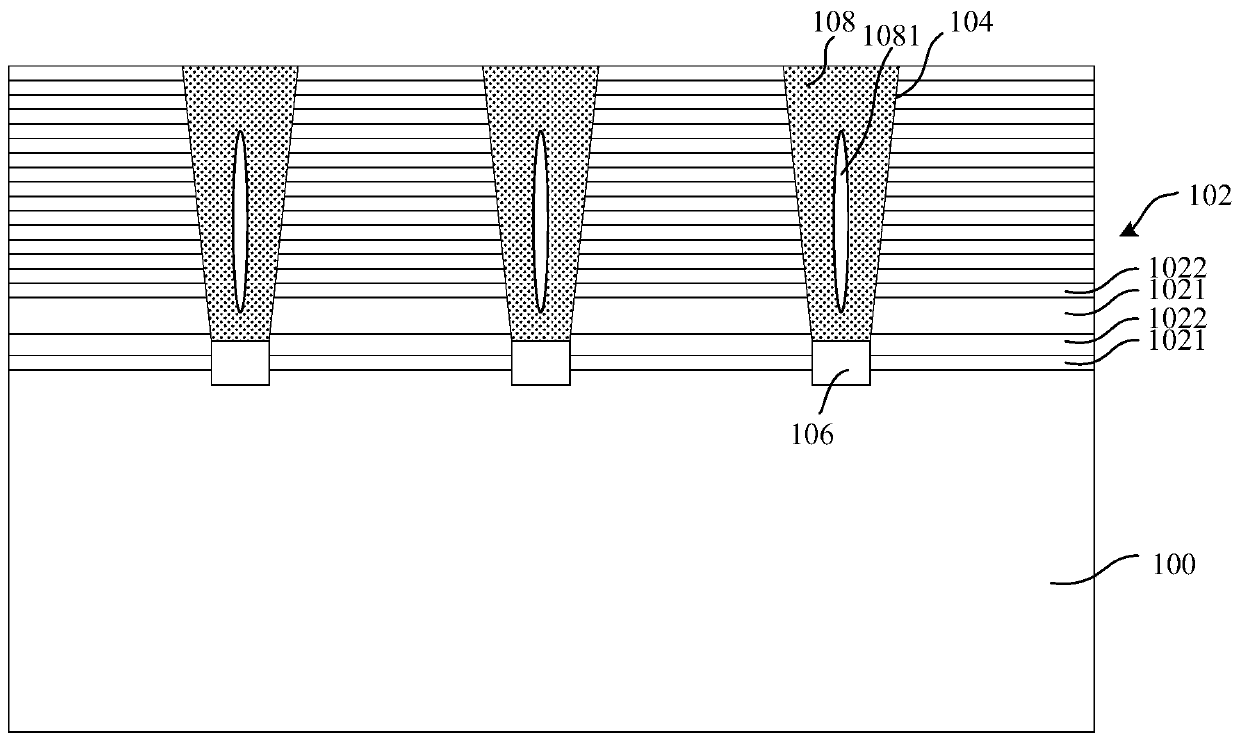

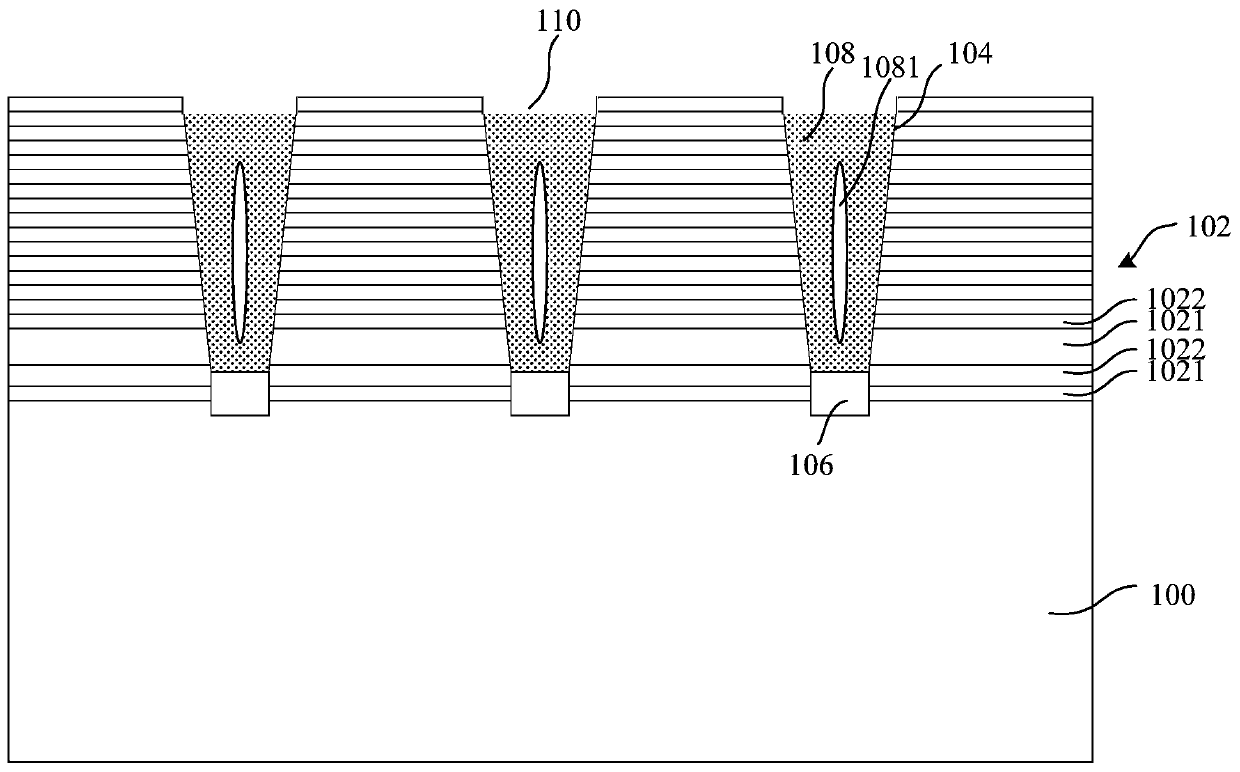

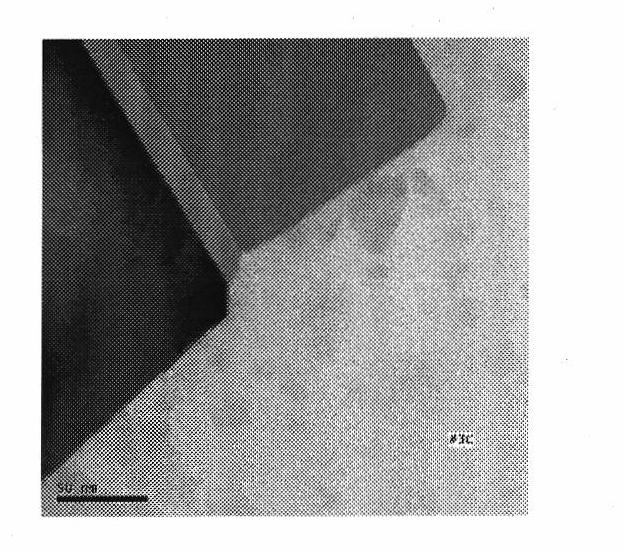

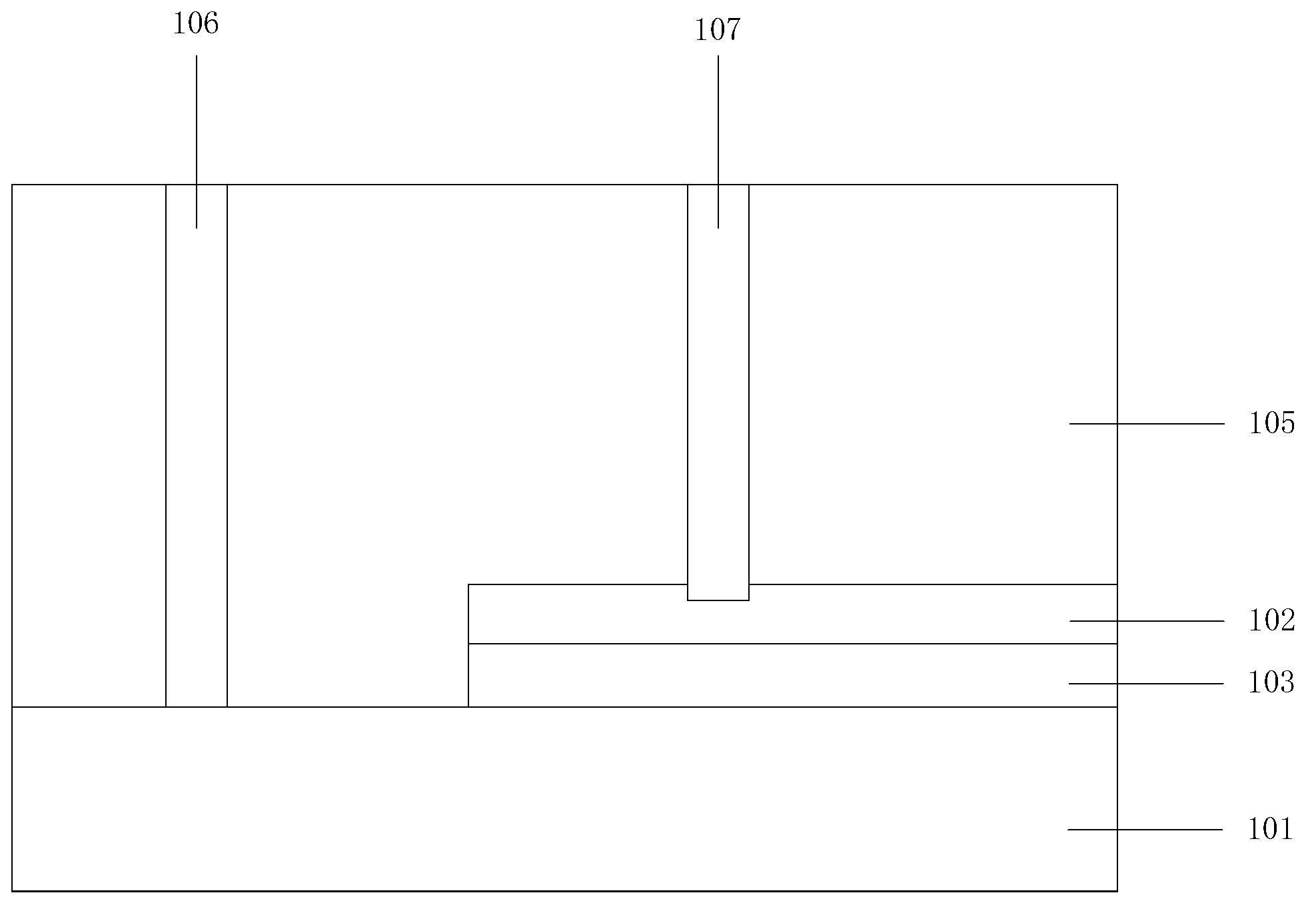

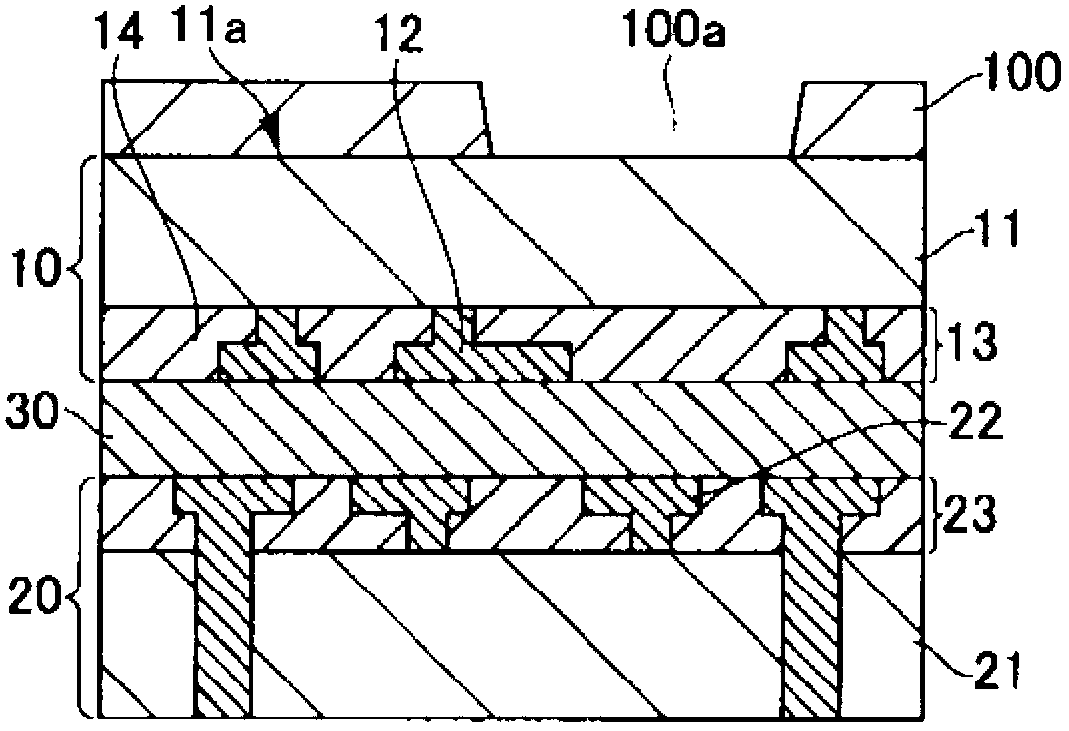

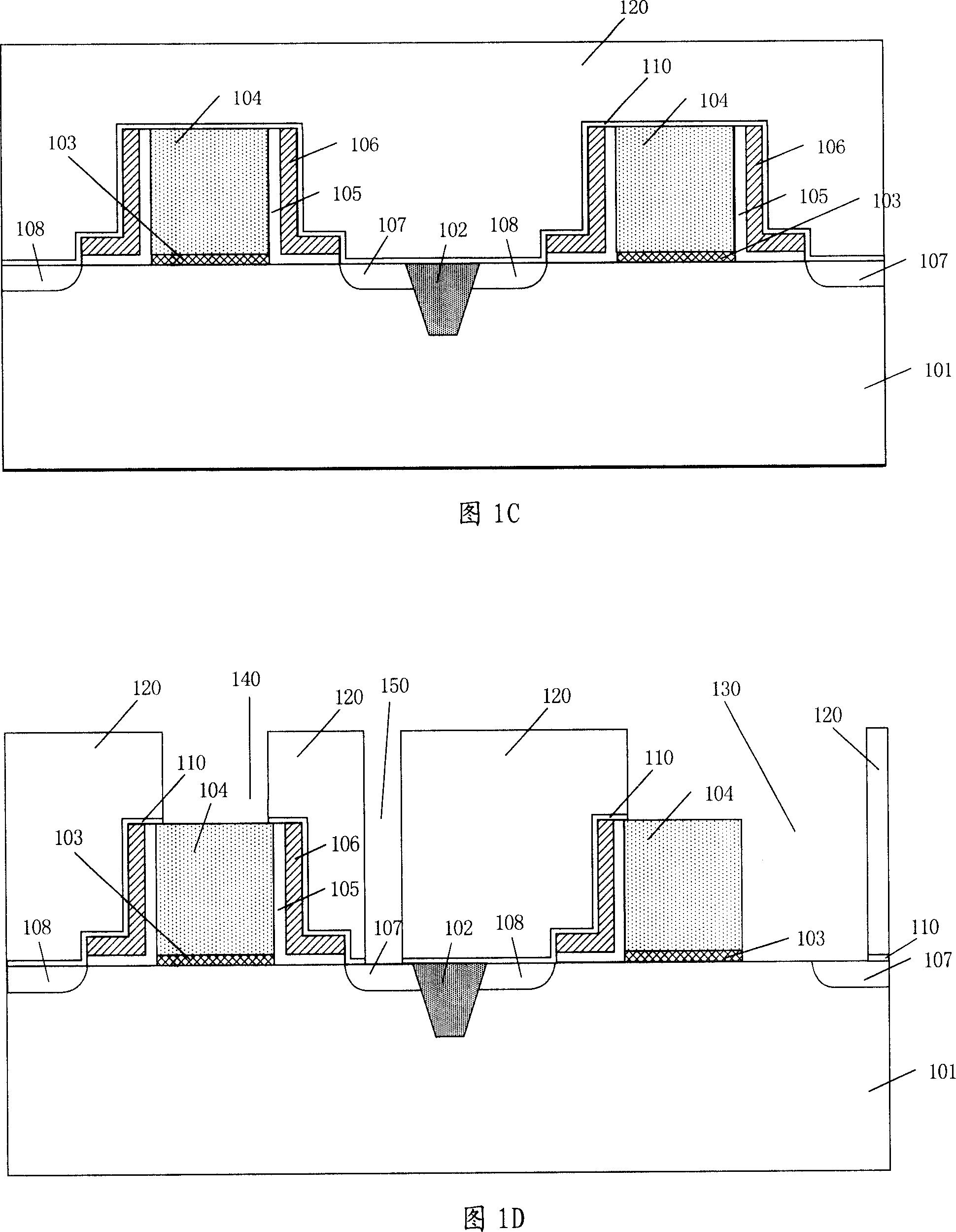

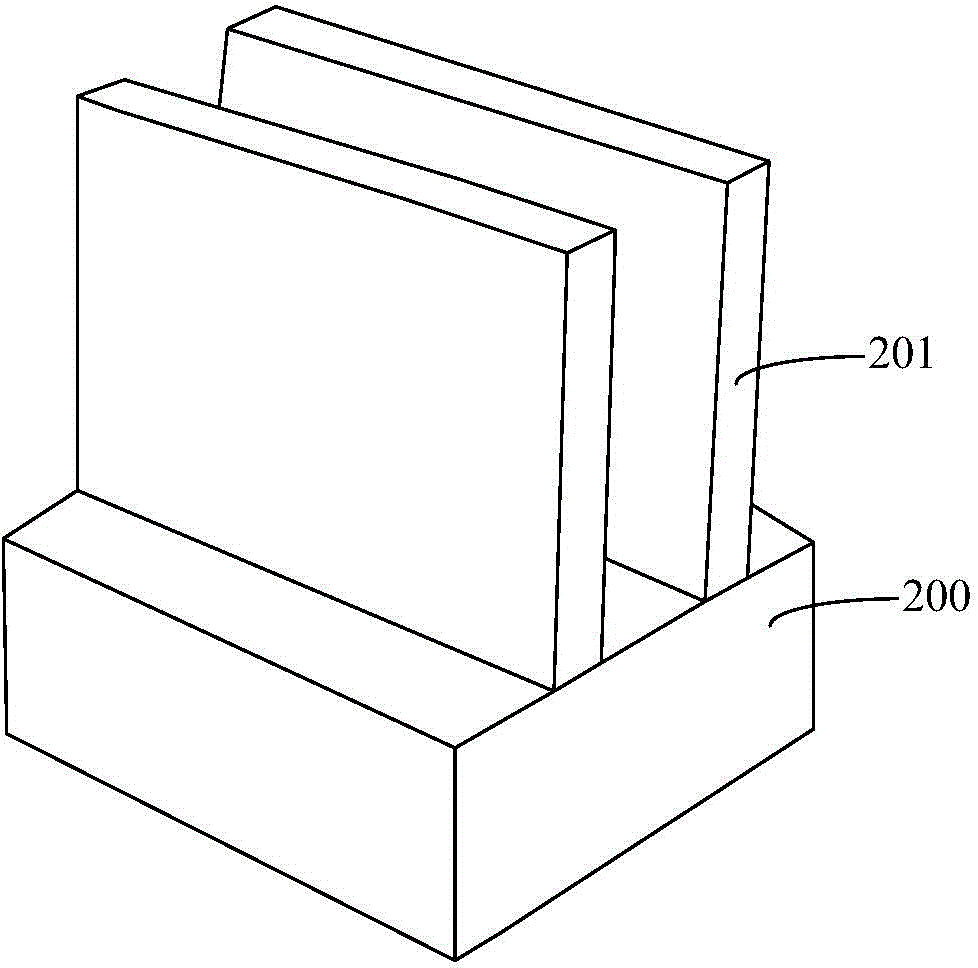

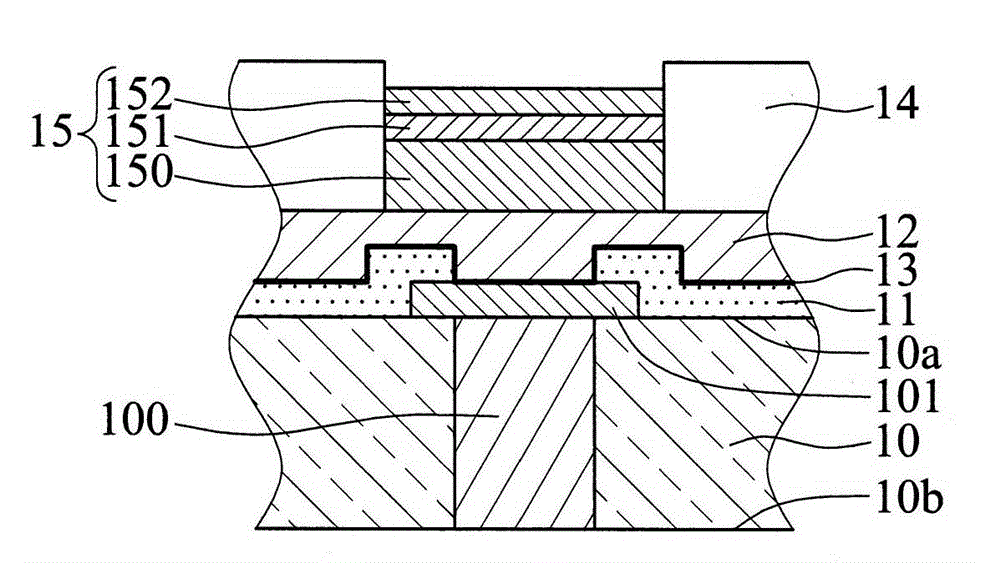

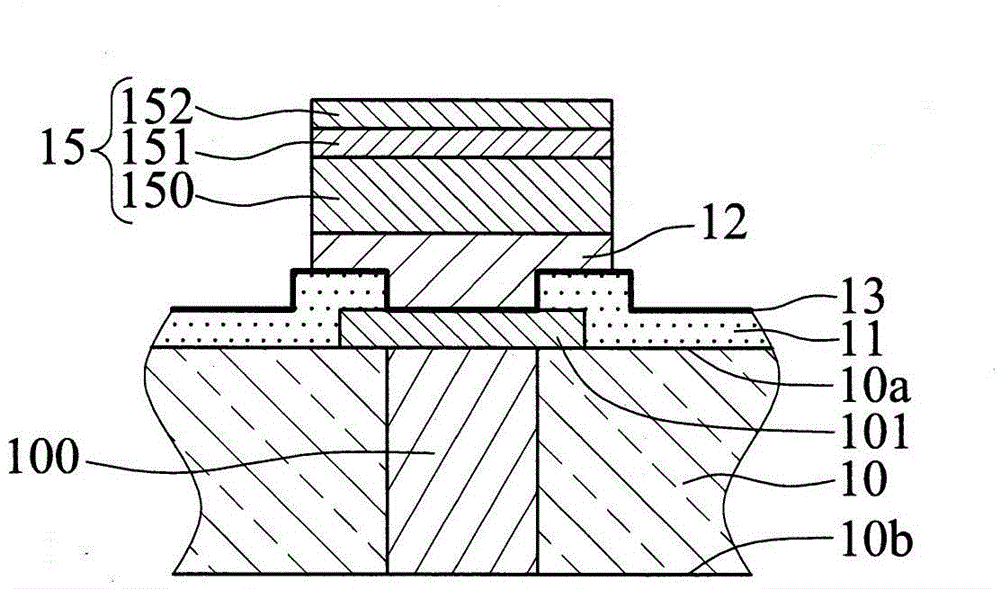

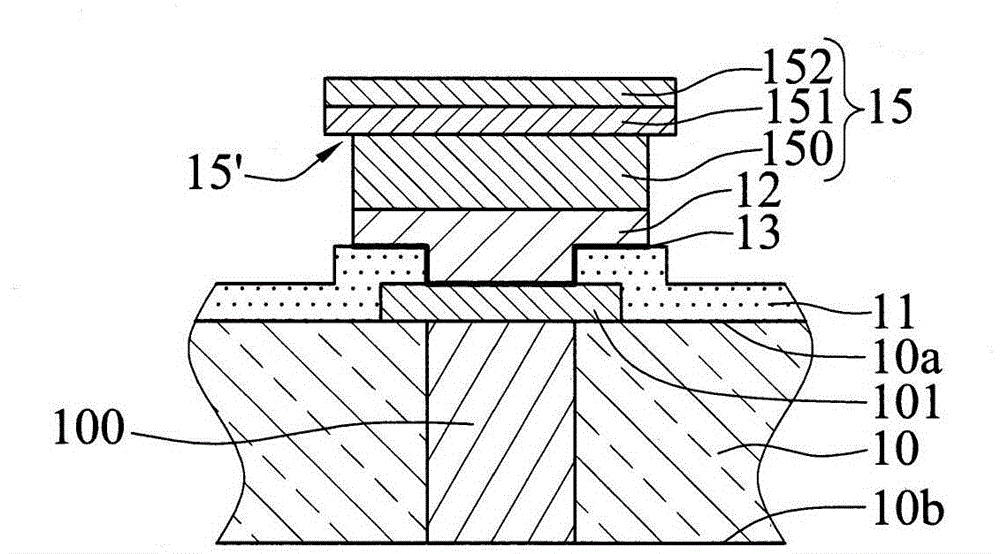

Three-dimensional semiconductor device and manufacturing method thereof

ActiveCN104022121AImprove reliabilityImprove control characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETVertical channel

The invention discloses a three-dimensional semiconductor device comprising a plurality of memory unit transistors and a plurality of selection transistors, wherein the plurality of memory unit transistors are at least partially overlapped in the vertical direction; each selection transistor comprises a first drain electrode distributed along the vertical direction, an active region, a common source electrode formed in a substrate and a metal grid electrode distributed around the active region; each memory unit transistor comprises a channel layer distributed vertical to the surface of the substrate, wherein a plurality of interlayer insulating layers and a plurality of grid electrode stacking structures are alternately stacked along the side wall of the channel layer, and a second drain electrode is located at the top of the channel layer; the channel layer is electrically connected with the first drain electrode. According to the three-dimensional semiconductor device and a manufacturing method thereof disclosed by the invention, multi-grid MOSFETs (Metal-Oxide-Semiconductor Field Effect Transistors) are formed below memory unit string stacks comprising vertical channels so as to be used as the selection transistors, thus the threshold voltage control characteristic of the grid electrode is improved, the off-state leakage current is reduced, the over-etching for the substrate is avoided, and the reliability of the device is effectively improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

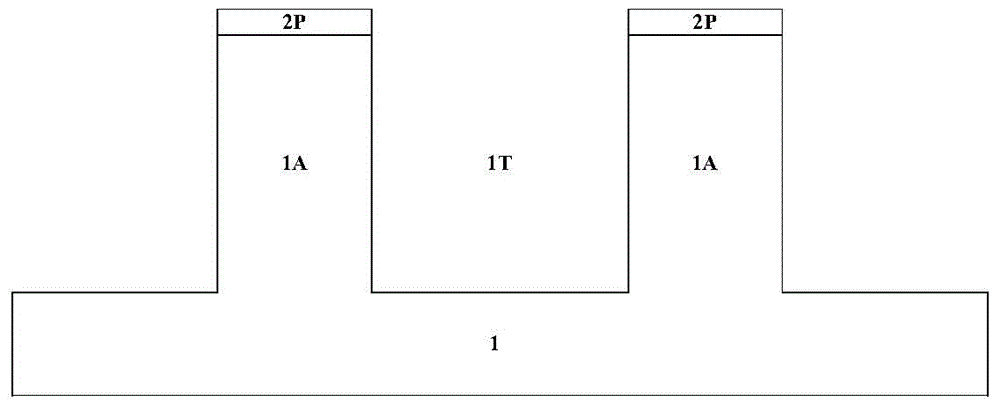

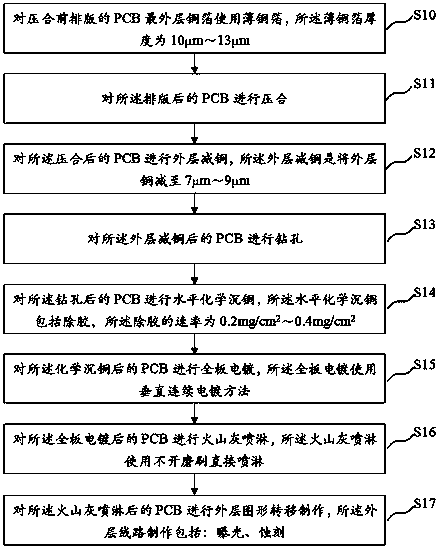

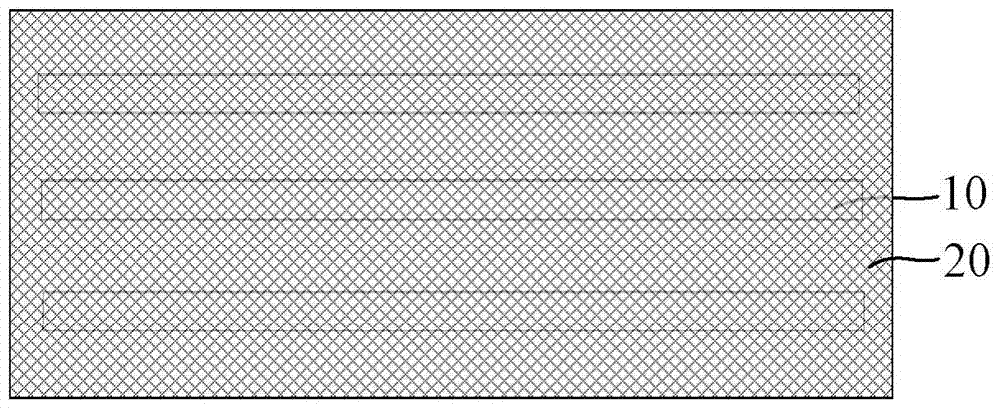

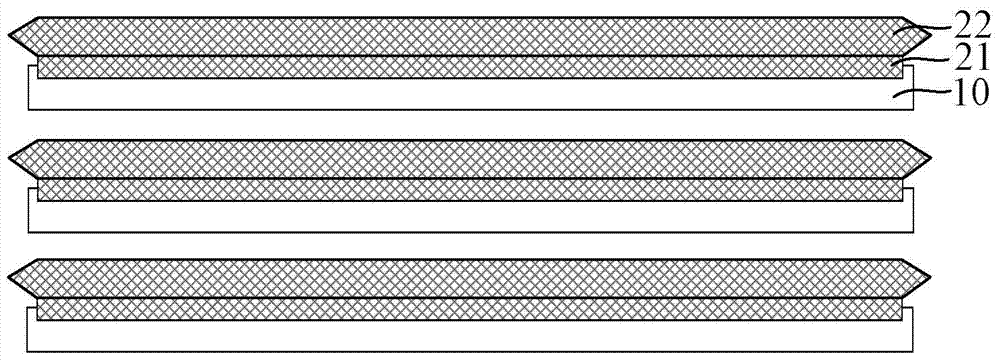

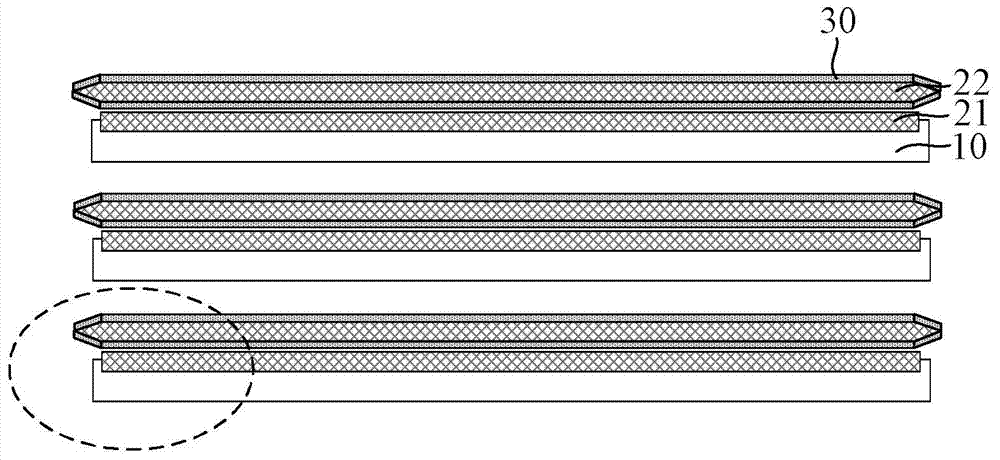

PCB circuit manufacturing method and PCB

InactiveCN110213895AAvoid over etchingMeet production needsInsulating substrate metal adhesion improvementInsulating layers/substrates workingEtchingDirect imaging

The invention discloses a PCB circuit manufacturing method and a PCB. The method comprises the following steps: using a thin copper foil with the diameter of 10 to 13 microns as the outermost layer ofcopper foil of a type setting PCB, then laminating, reducing the copper on the outer layer to be 7 to 9 microns after laminating, then carrying out hole drilling and low-speed chemical adhesive cleaning, using vertically continuous electroplating manufacturing in later electroplating working procedure, controlling the thickness of copper on the inner wall of the hole to be 15 to 20 microns and the thickness of copper on the surface to be 24 to 30 microns, then carrying out surface roughening in a cinerite spraying mode for turning off a polishing brush, then using a laser direct imaging exposure machine for exposure in the manufacturing process of an outer circuit, carrying out developing and etching by using a low-pressure and high-speed mode, and presetting 10% to 20% of a circuit compensating value in advance. The problems, such as a great number of too thin and too wide lines, excessive etching, under developing, short circuits and open circuits existing in the circuit manufacturing process, of the PCB product with fine circuits (for example, the ratio of line width to line gap is smaller than or equal to 2 mil / 2 mill) can be solved.

Owner:深圳市鼎盛电路技术有限公司

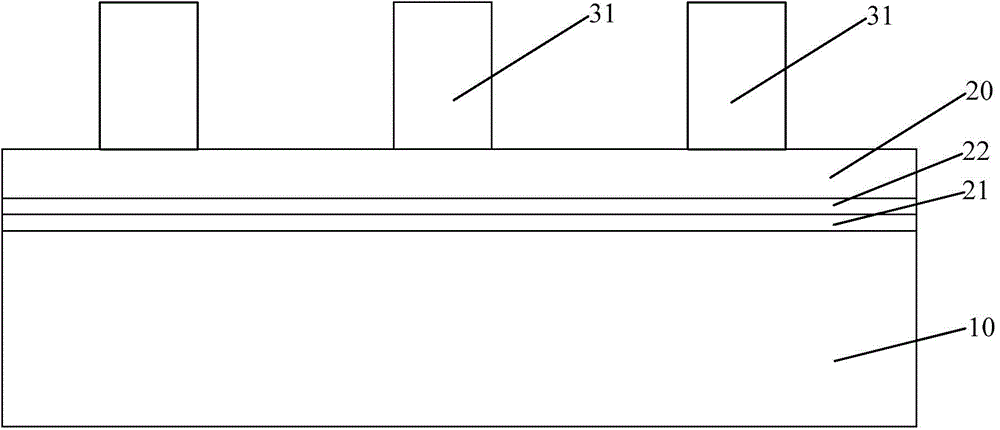

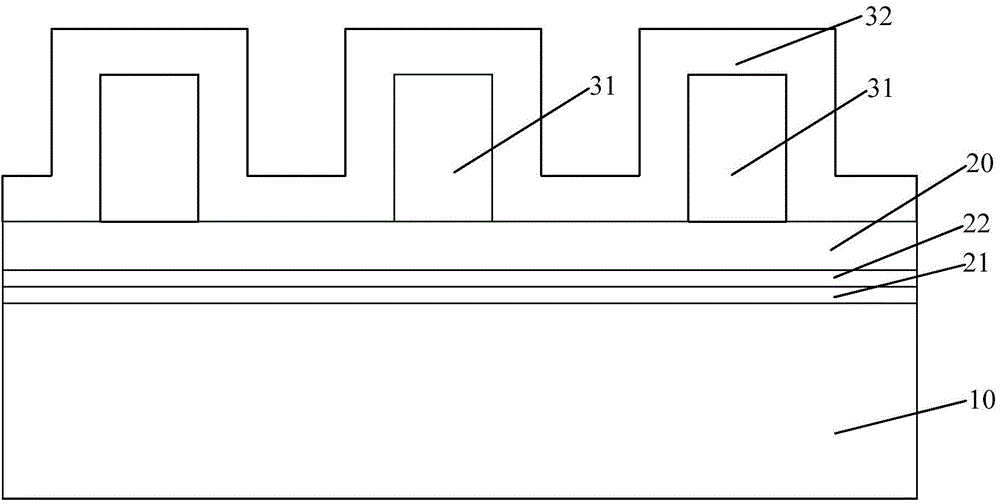

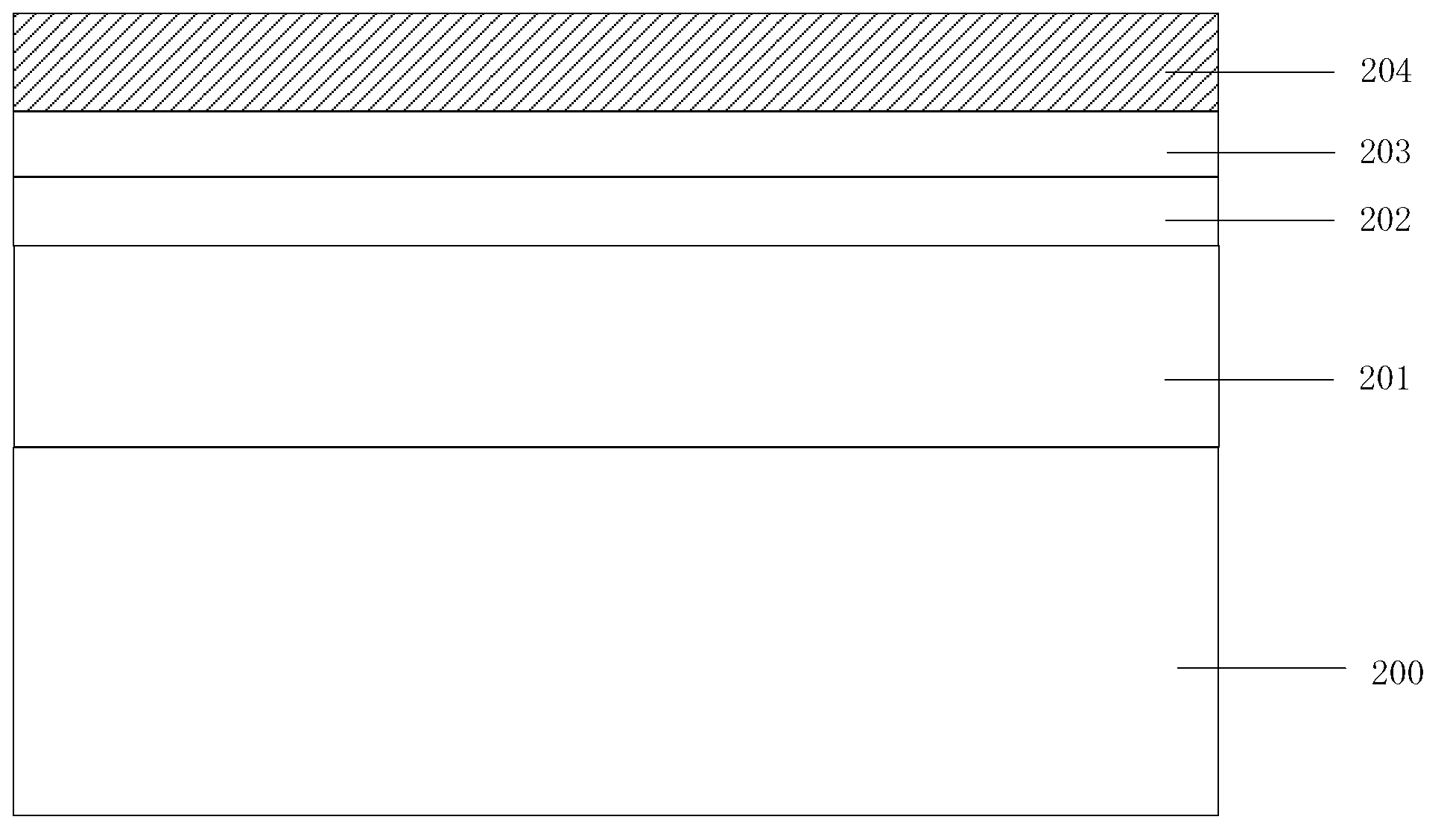

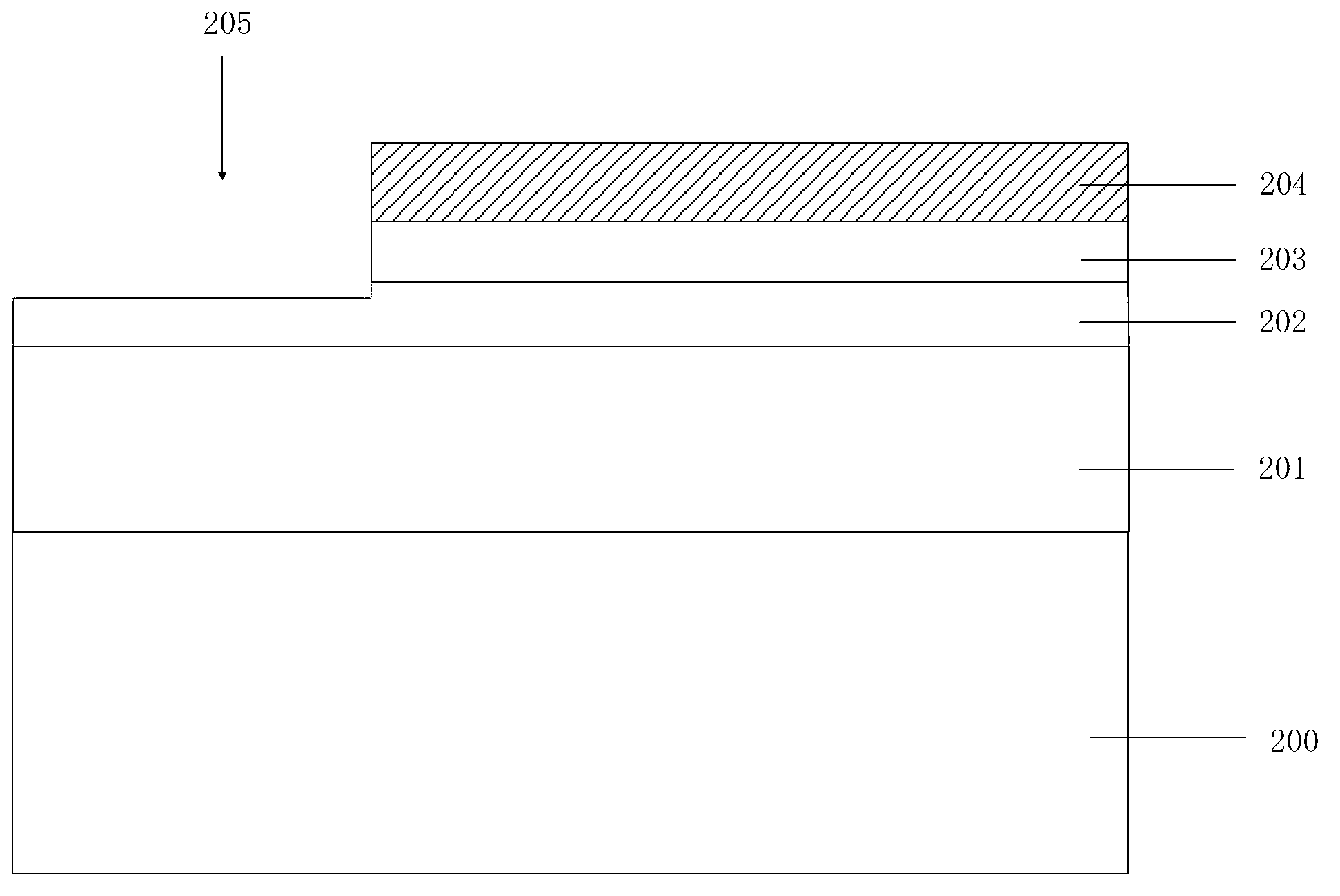

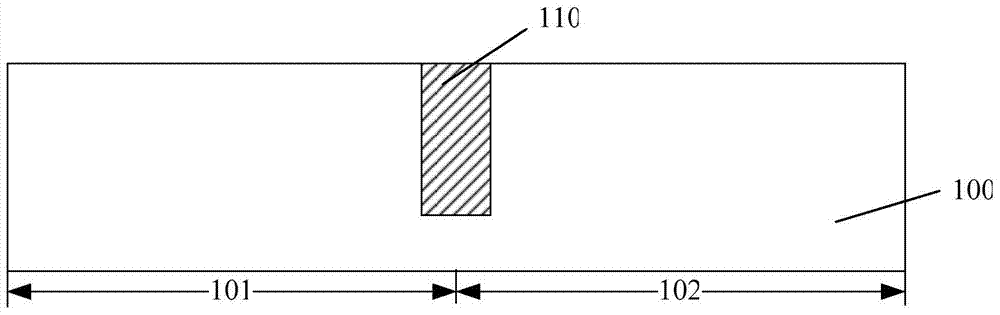

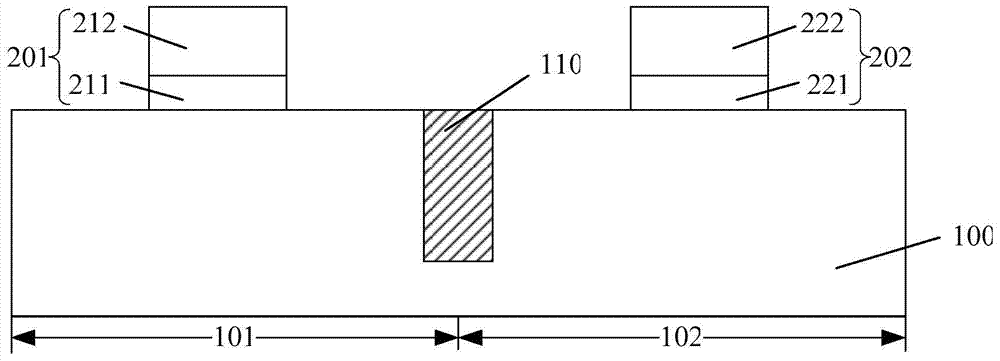

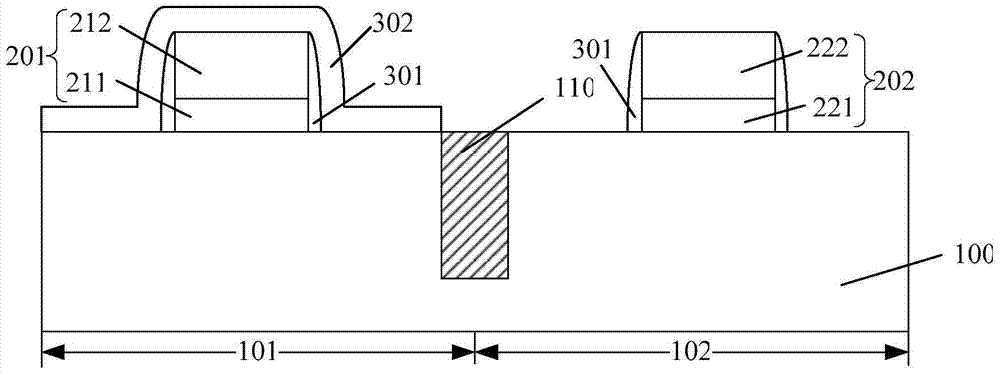

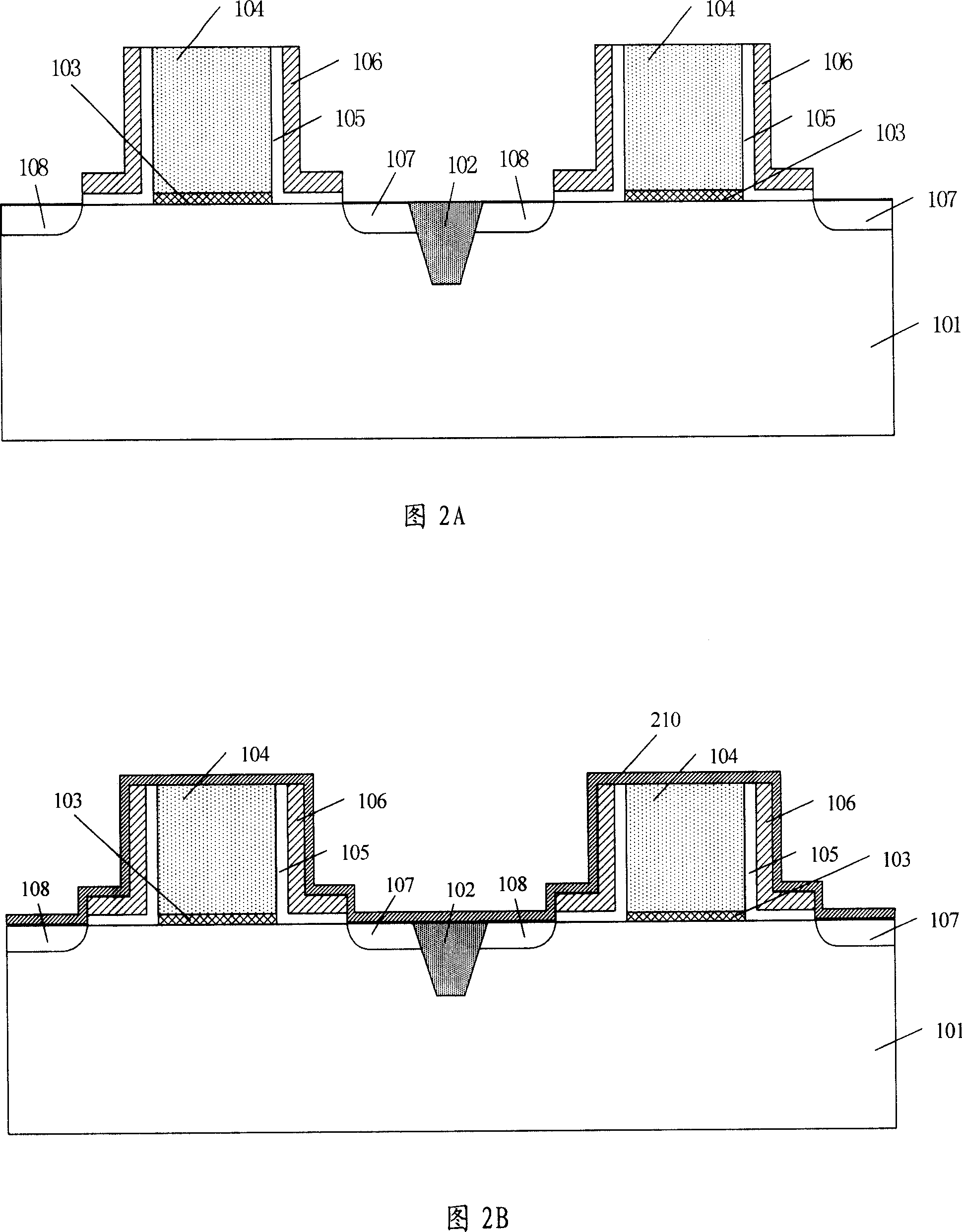

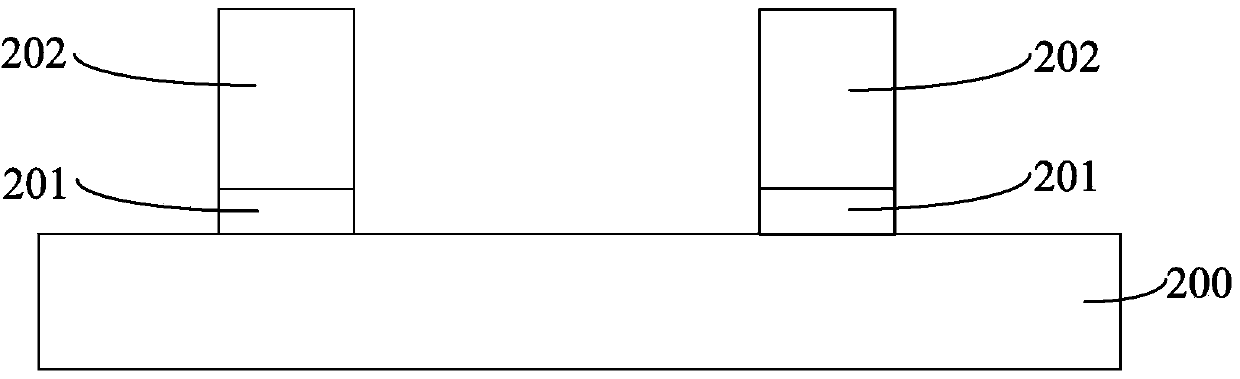

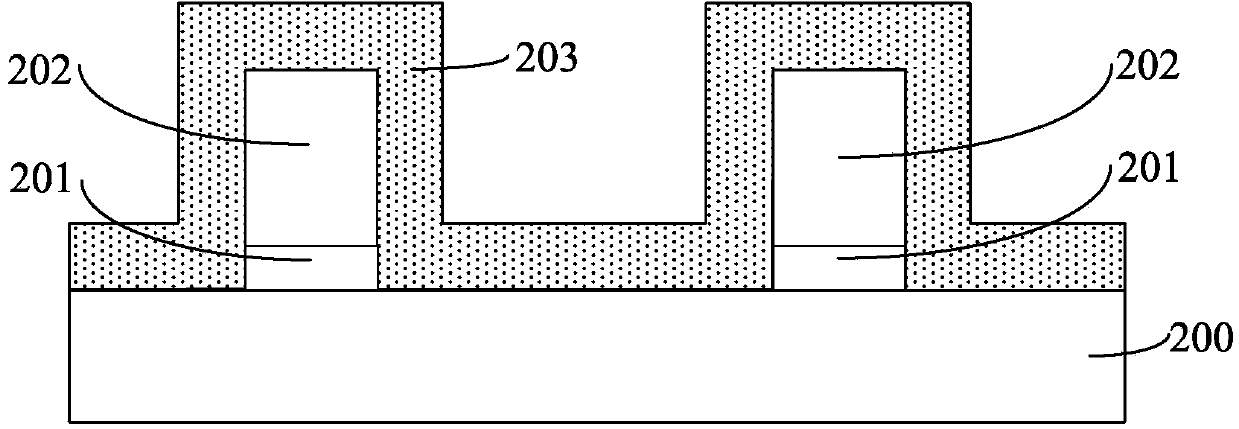

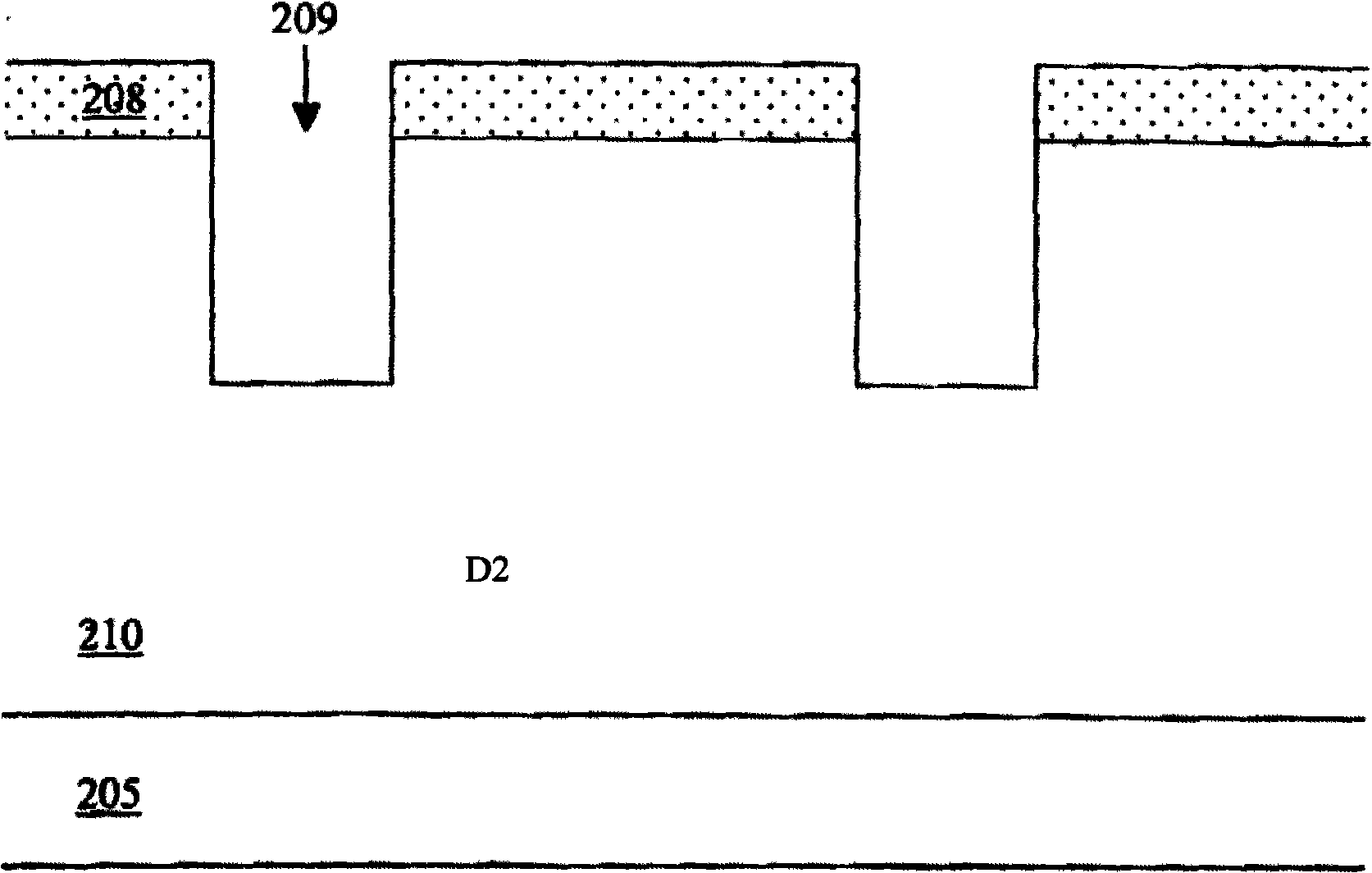

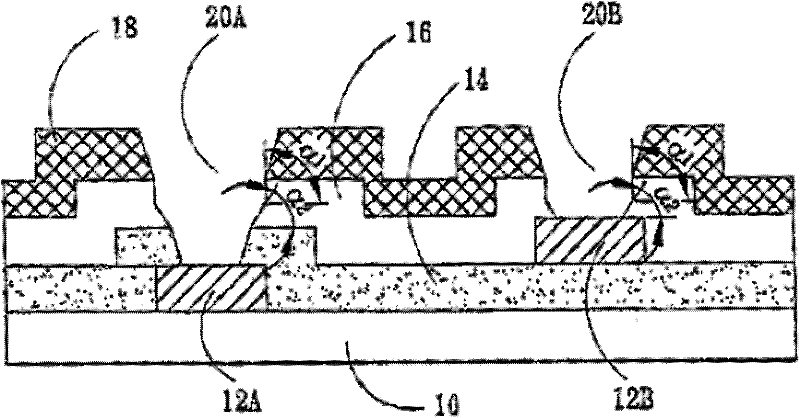

Semiconductor structure and forming method thereof

ActiveCN106206307ASmall sizeConsistent widthSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureEngineering

The invention provides a semiconductor structure and a forming method thereof. The forming method of the semiconductor structure comprises the steps that a semiconductor substrate is provided; a mask layer and a sacrificial material layer located on the surface of the mask layer are sequentially formed on the surface of the semiconductor substrate; the sacrificial material layer is etched to form a plurality of discrete sacrificial layers; side walls are formed on the side wall surfaces of the sacrificial layers; the sacrificial layers are removed; and supplement side walls are formed on the side wall surfaces of the side walls. By the method, improvement of the performance of the formed semiconductor structure is facilitated.

Owner:SEMICON MFG INT (SHANGHAI) CORP

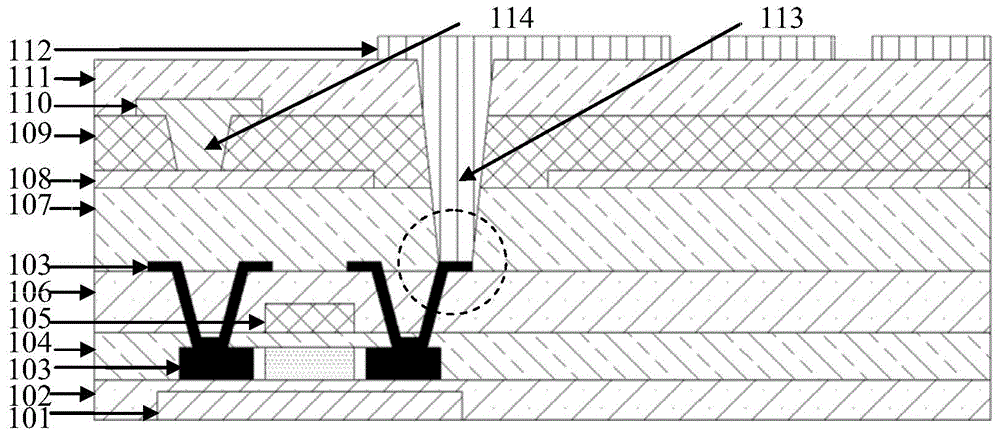

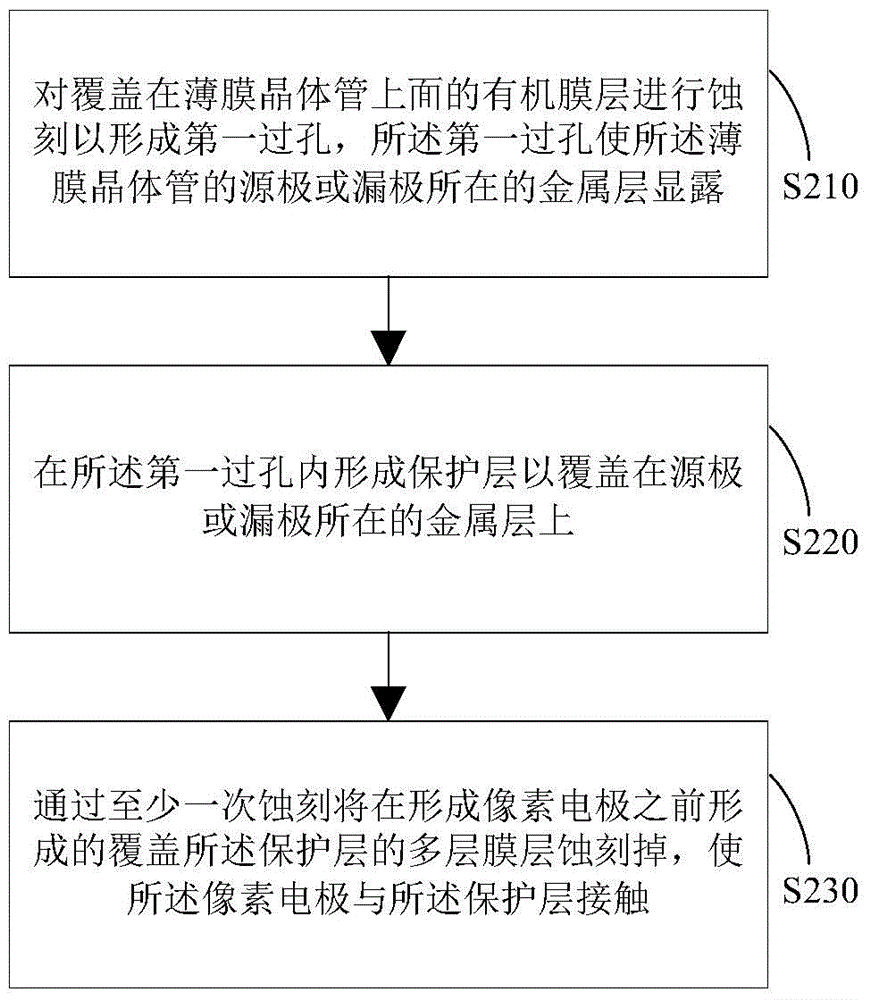

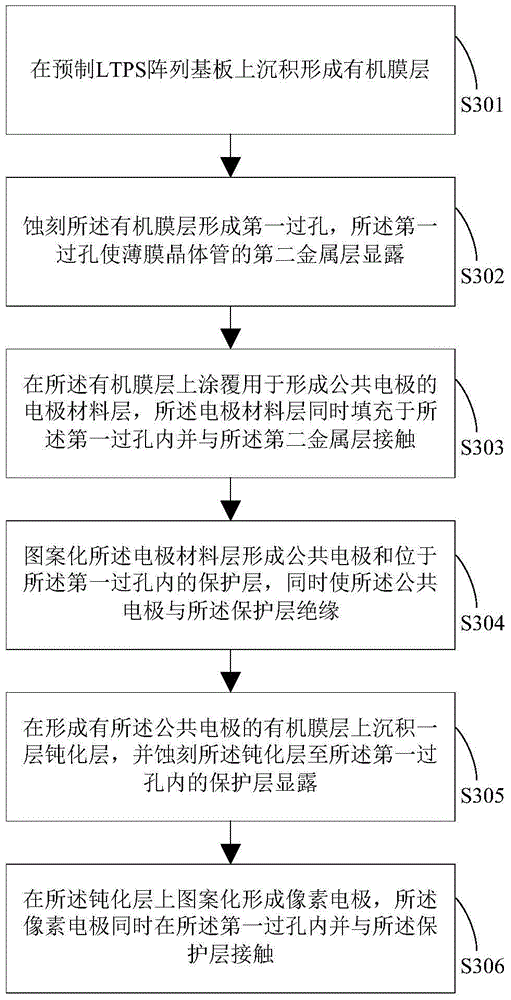

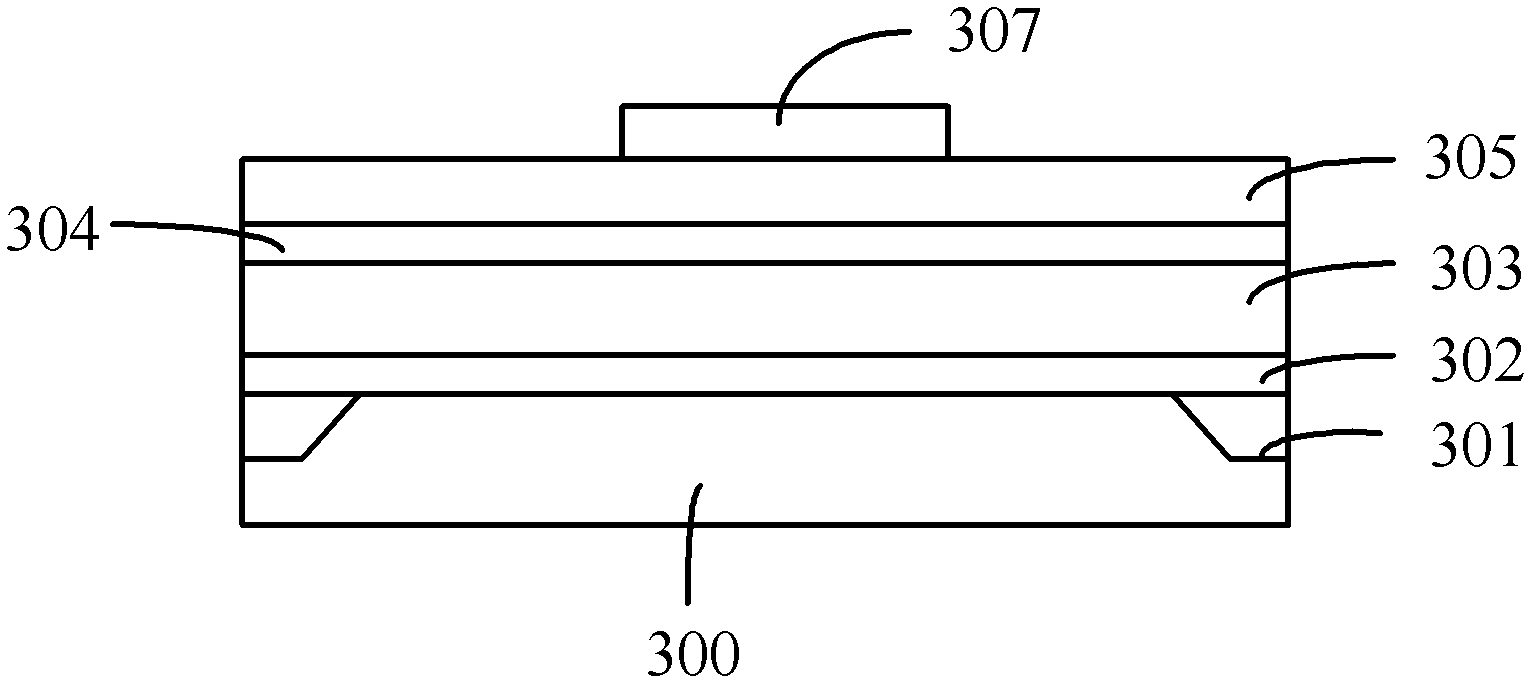

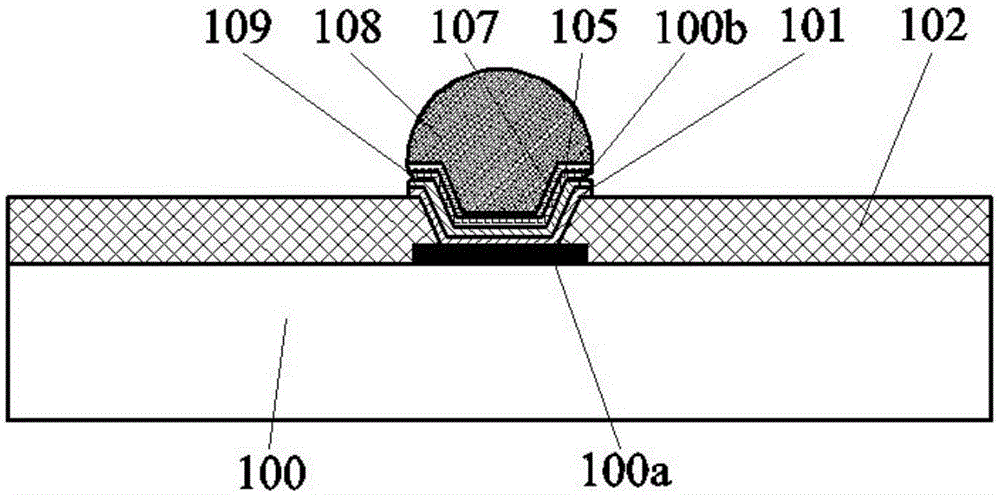

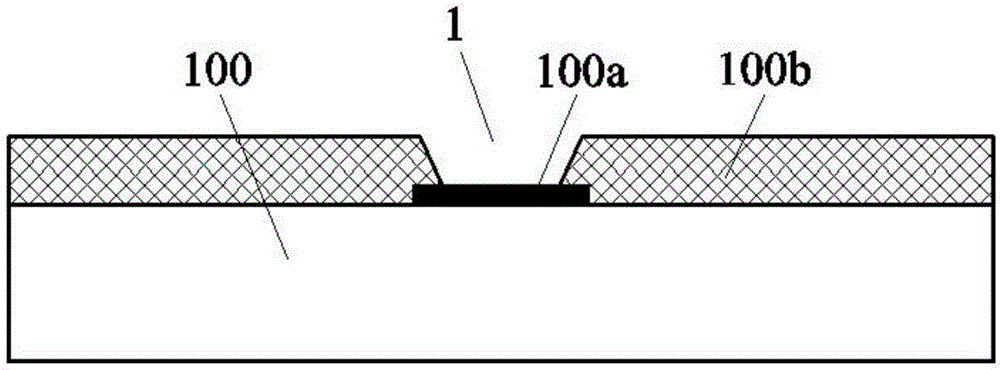

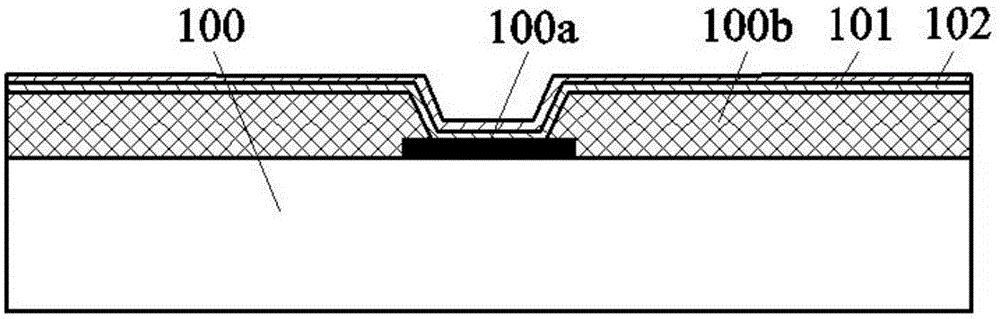

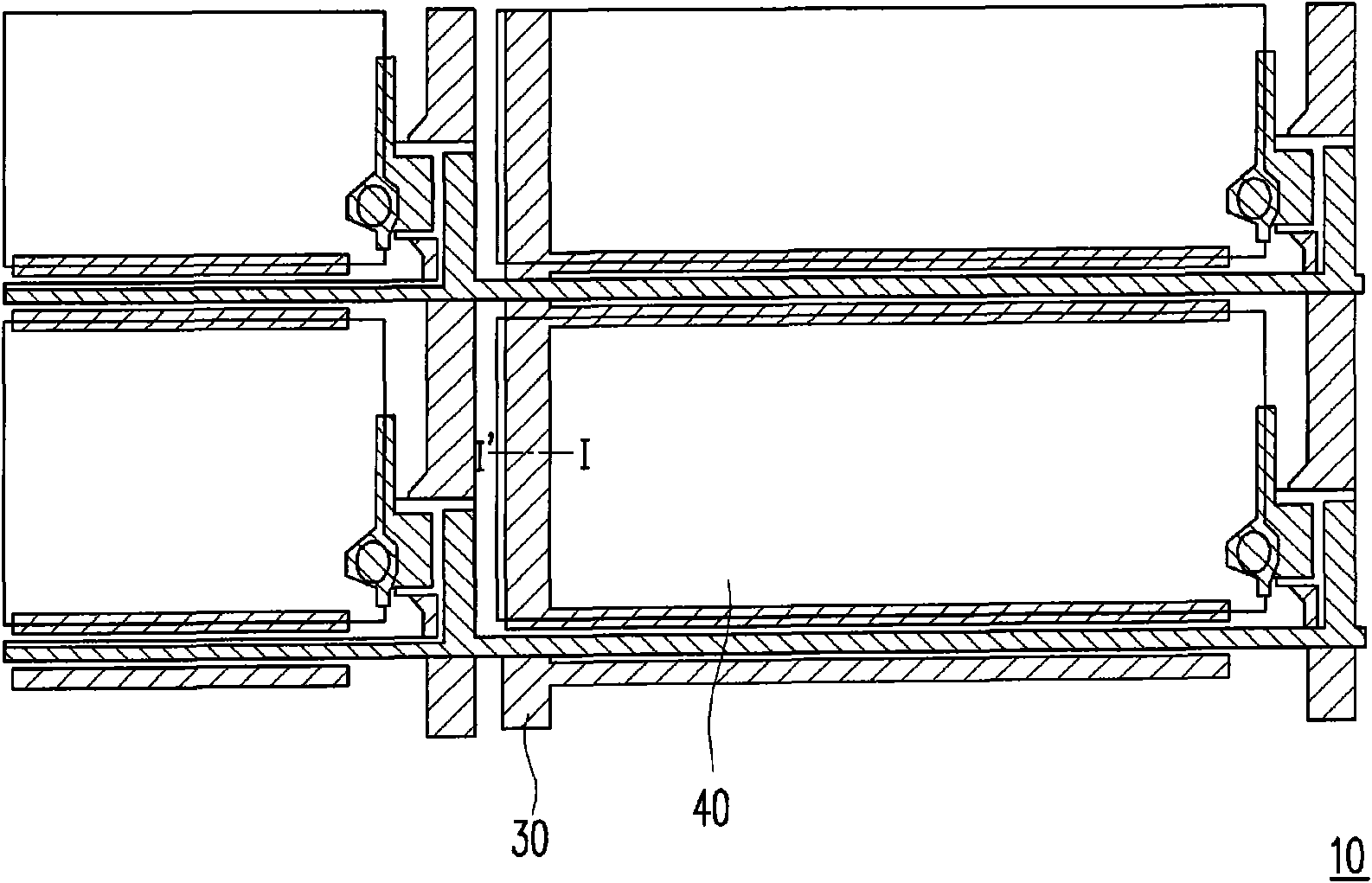

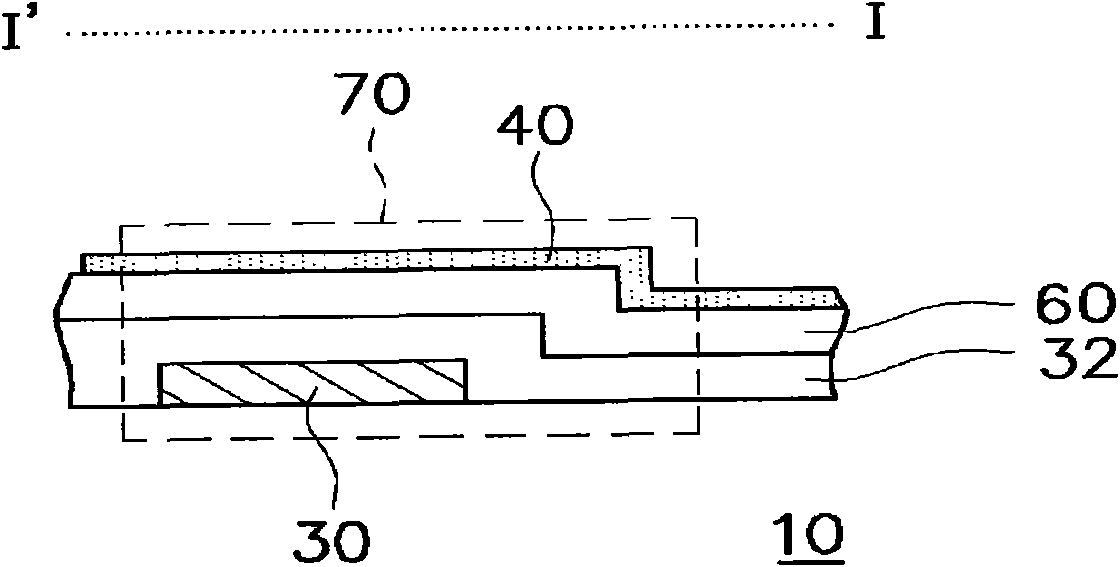

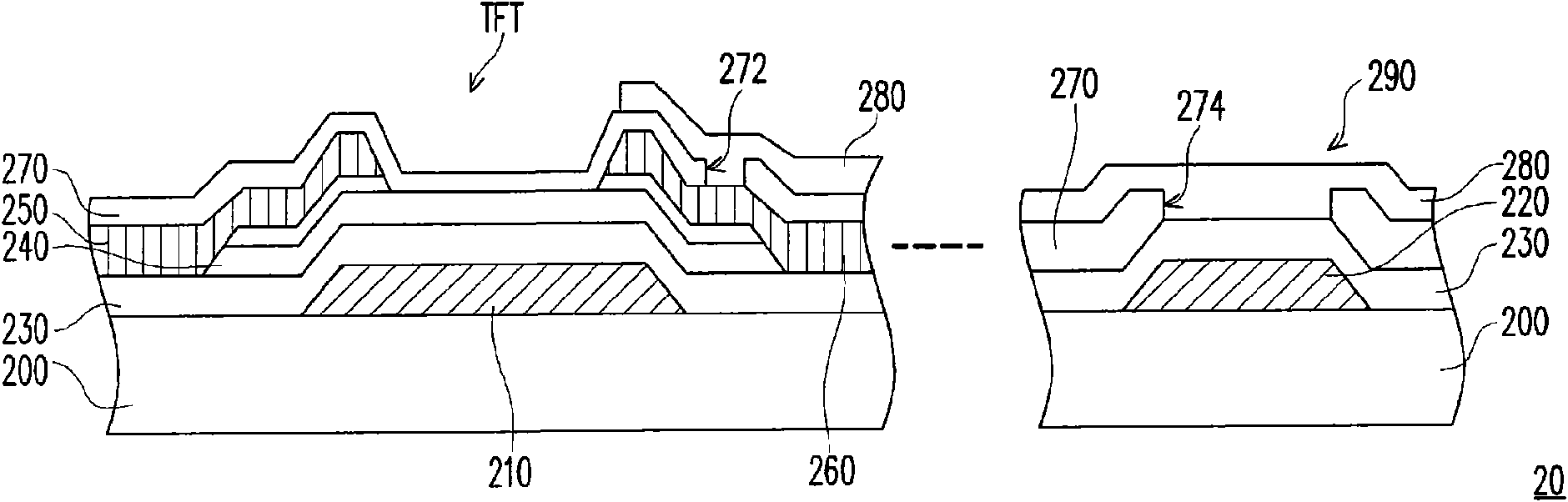

LTPS array substrate and manufacturing method thereof

InactiveCN104867878AAvoid over etchingThe method is simple and fastSolid-state devicesSemiconductor/solid-state device manufacturingOrganic filmProtection layer

The invention discloses a LTPS array substrate and a manufacturing method thereof; the array substrate manufacturing method comprises the following steps: etching an organic film covering a film transistor so as to form a first through hole, and the first through hole exposes a metal layer on which a source electrode or drain electrode of the film transistor are located; forming a protection layer in the first through hole so as to cover the metal layer on which the source electrode or the drain electrode are located; using at least one etching so as to etch a multilayer film formed before a pixel electrode and covering the protection layer, so the pixel electrode makes contact with the protection layer; the method can effectively prevent the source electrode or the drain electrode from being overly etched in a through hole processing step, is simple and fast, and can be promoted by using an existing production line.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

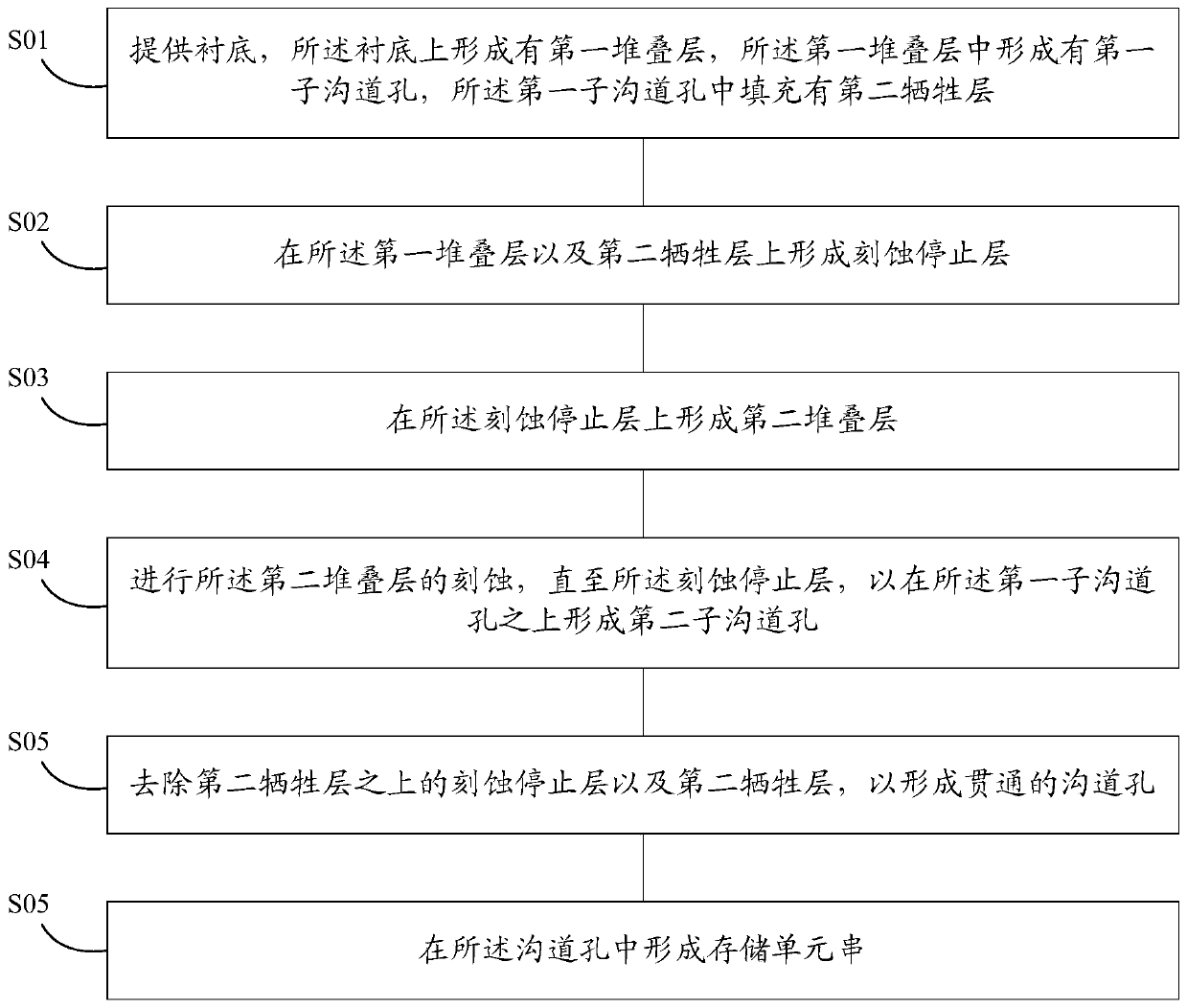

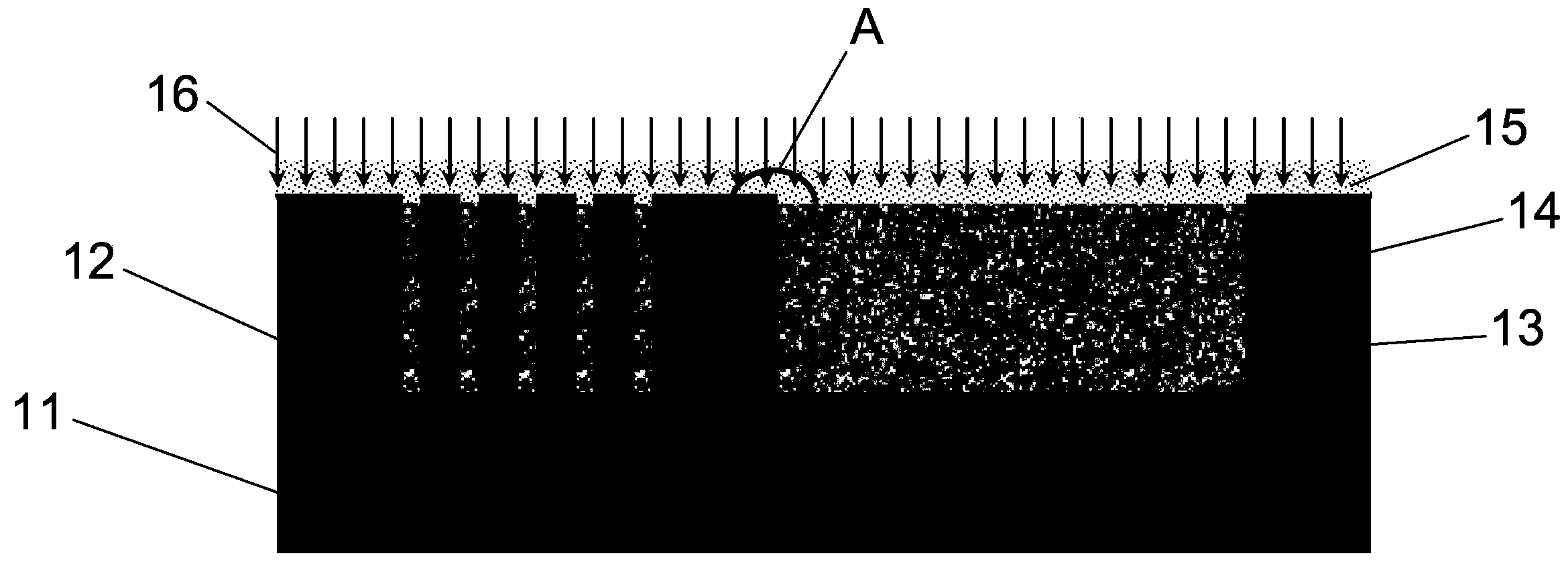

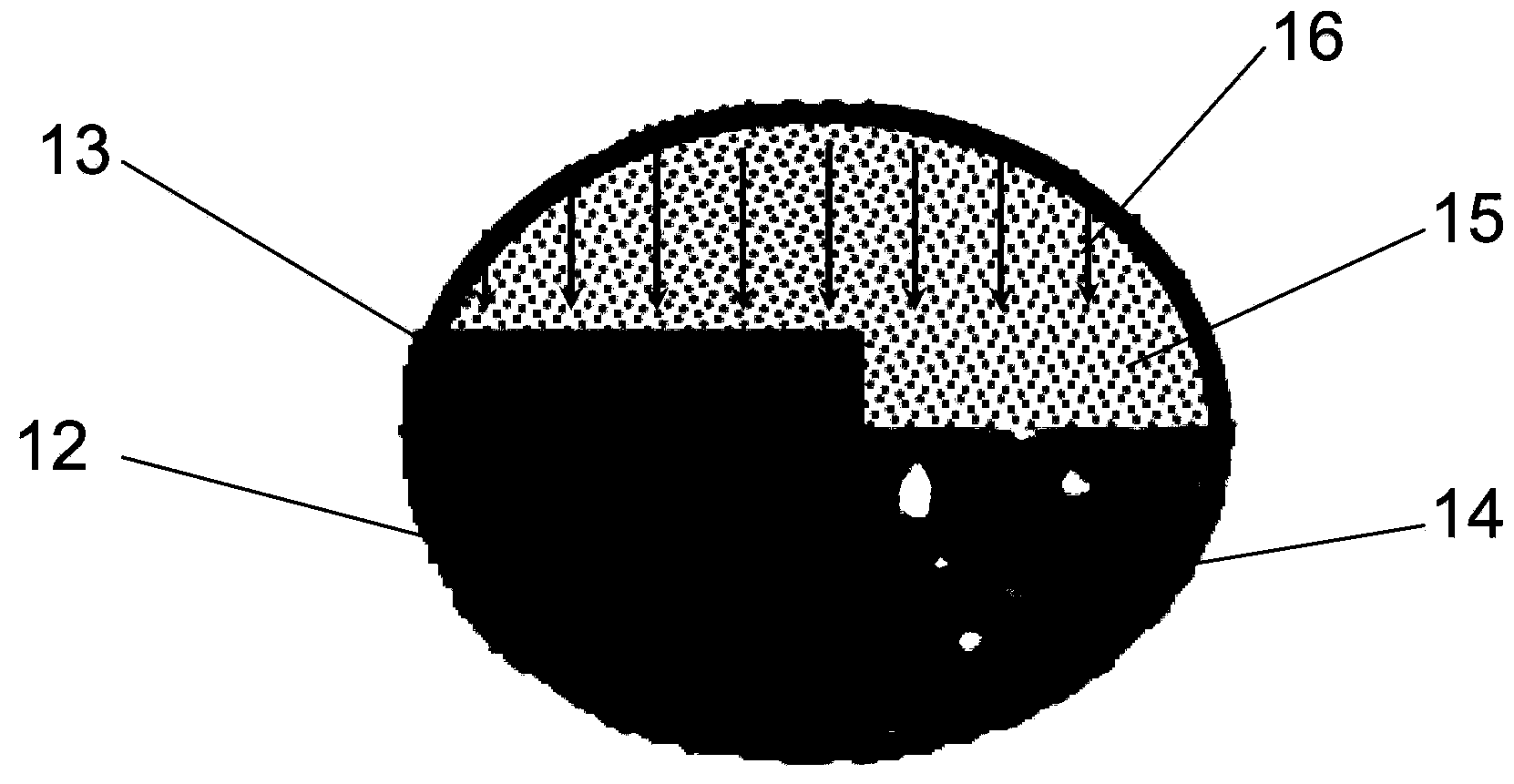

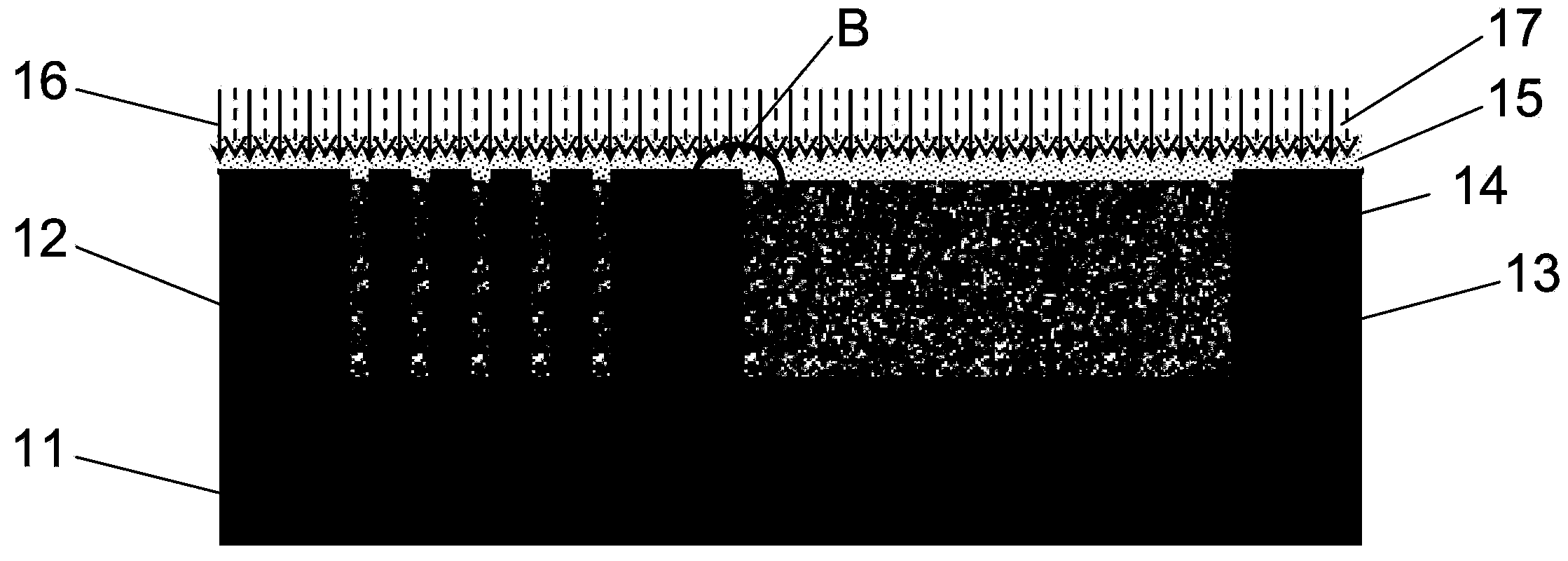

Memory device and manufacturing method thereof

ActiveCN109755252AImprove yieldAvoid over etchingSolid-state devicesSemiconductor devicesEngineeringElectrical and Electronics engineering

The invention provides a memory device and a manufacturing method thereof. Forming a sacrificial layer in a first sub-channel hole in a first stacked layer; then forming an etch stopping layer; and then continuing to form a second stacked layer over the etch stopping layer; forming a second sub-channel hole above the first sub-channel hole using the etch stopping layer as an etching focus when thesecond sub-channel hole is formed in the second stacked layer; so that a through channel hole is formed after the etch stopping layer above a second sacrificial layer and the second sacrificial layerare removed. Therefore, the integration of the memory device is effectively improved; meanwhile, the over etching to the second sacrificial layer is avoided during etching of the second sub-channel hole by setting the etch stopping layer; therefore, the process stability is improved, and the device yield is increased.

Owner:YANGTZE MEMORY TECH CO LTD

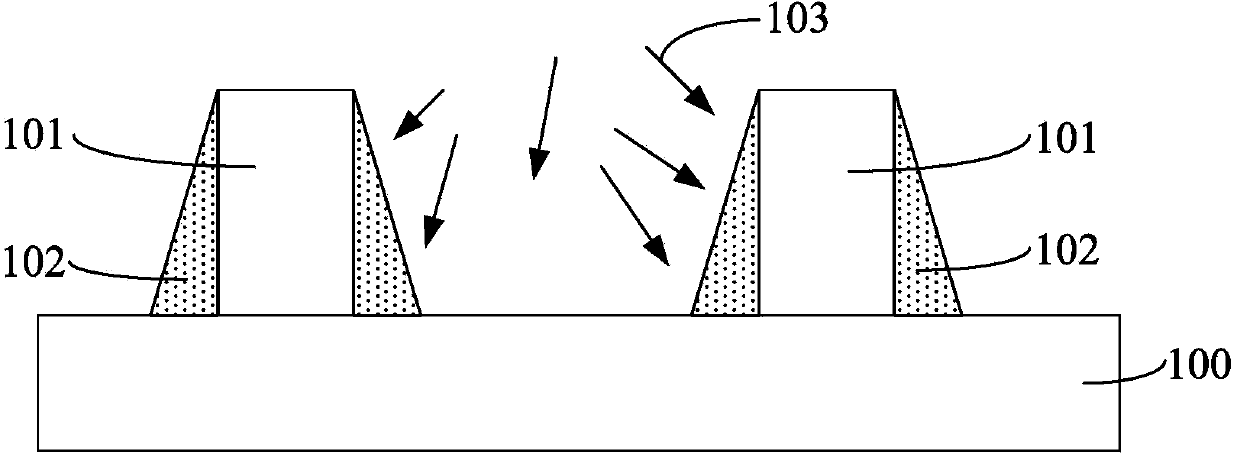

Wet process method for improving chamfer smoothness on top of shallow trench isolation

ActiveCN102117761AImprove smoothnessImprove roundnessSemiconductor/solid-state device manufacturingHydrofluoric acidEtching

The invention discloses a wet process method for improving chamfer smoothness on top of shallow trench isolation. The method comprises the following steps: (1) etching a shallow trench and removing photoresist; (2) etching a nitride film back, and cleaning with hydrofluoric acid; (3) adjusting the appearance of the chamfer on the top of the shallow trench isolation by wet APM liquor treatment; and (4) growing a substrate oxide film in the shallow trench. In the method, the wet APM liquor treatment is added after the back etching of the nitride film, the appearance of the chamfer is adjusted through micro-etching on silicon, and over etching to the substrate oxide film is avoided. The chamfer is etched in the upper side and the lateral side, so that the smoothness of the chamfer on the topof the shallow trench isolation (STI) can be increased, and the use reliability of the device is prevented from being influenced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

MIM (metal-insulator-metal) capacitor and manufacturing method thereof

InactiveCN103021813AAvoid over etchingReduce the chance of breakdownSemiconductor/solid-state device detailsSolid-state devicesMetal-insulator-metalCapacitance

Disclosed are a MIM capacitor and a manufacturing method thereof. The manufacturing method includes: setting a covering layer on a second conducting layer (used for forming an upper electrode plate of an MIM capacitor). Etching gas which is slower in etching the covering layer than etching dielectric layers is selected in the process of dry etching performed to form through holes respectively exposing a first conducting layer (a lower electrode plate) and a second conducting layer, so that excessive etching of the second conducting layer (the upper electrode plate) is avoided when the dielectric layers embedding the second conducting layer and the first conducting layer are etched simultaneously at the same height. Thus, probability of breakdown of the MIM capacitor is lowered, and reliability of the MIM capacitor is increased.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

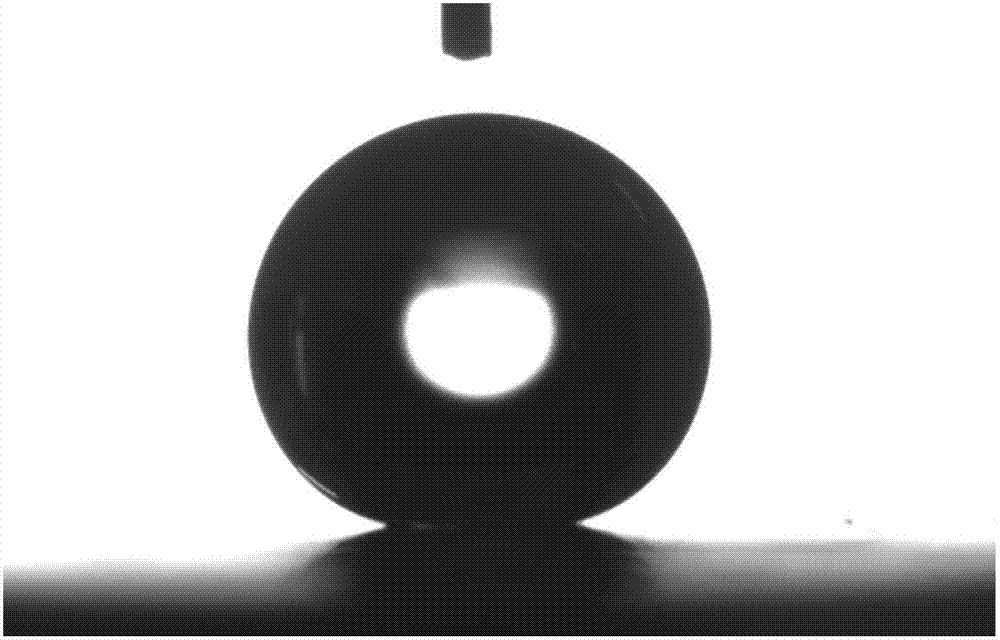

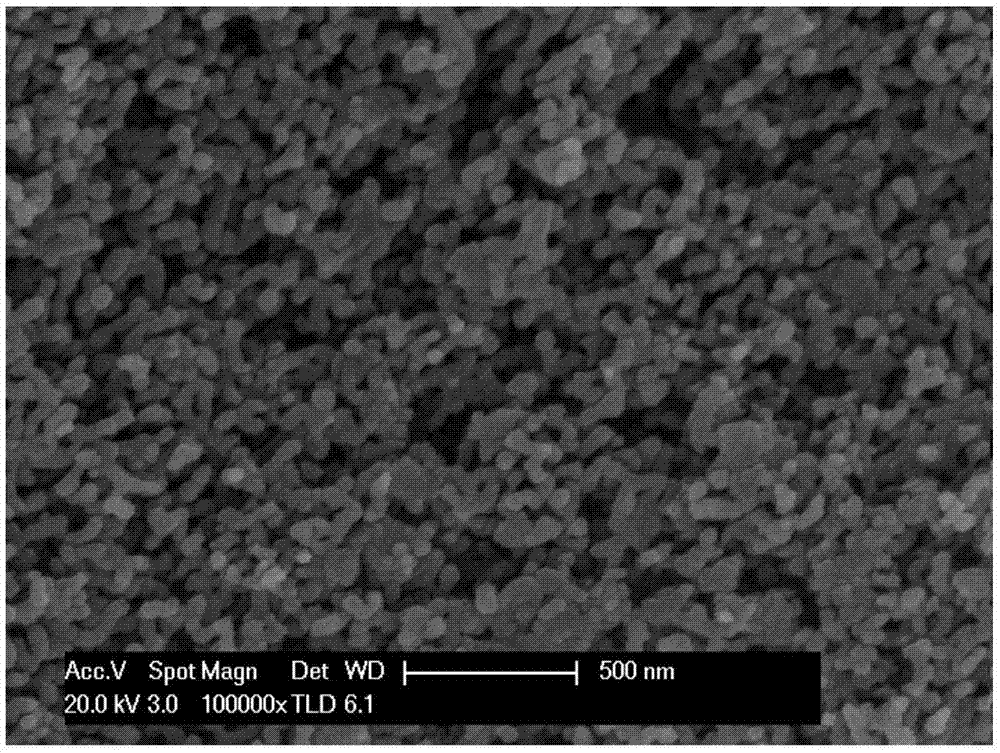

Transparent super-hydrophobic glass with anti-fog and dewdrop self-cleaning functions and preparation method of transparent super-hydrophobic glass

ActiveCN107879610AAvoid over etchingWith anti-reflection effectGlass tempering apparatusAcid etchingOxygen

The invention discloses transparent super-hydrophobic glass with anti-fog and dewdrop self-cleaning functions and a preparation method of the transparent super-hydrophobic glass. The preparation method comprises the steps of: performing high-temperature phase splitting treatment on sodium borosilicate glass to form an alkali-rich sodium-boron phase and a silicon-rich oxygen phase which are interpenetrated, then removing the alkali-rich sodium-boron phase through an acid etching process to reserve a high-silicon-content glass-phase porous three-dimensional network structure coating, and finallyreducing the surface energy through a fluorination process to obtain a transparent super-hydrophobic glass coating. The transparent super-hydrophobic glass with anti-fog and dewdrop self-cleaning functions and the preparation method of the transparent super-hydrophobic glass have the advantages of a simple process, easy operation, low requirements for equipment and low cost, and a new idea is provided for the preparation of transparent glass with a self-cleaning property.

Owner:SOUTHEAST UNIV

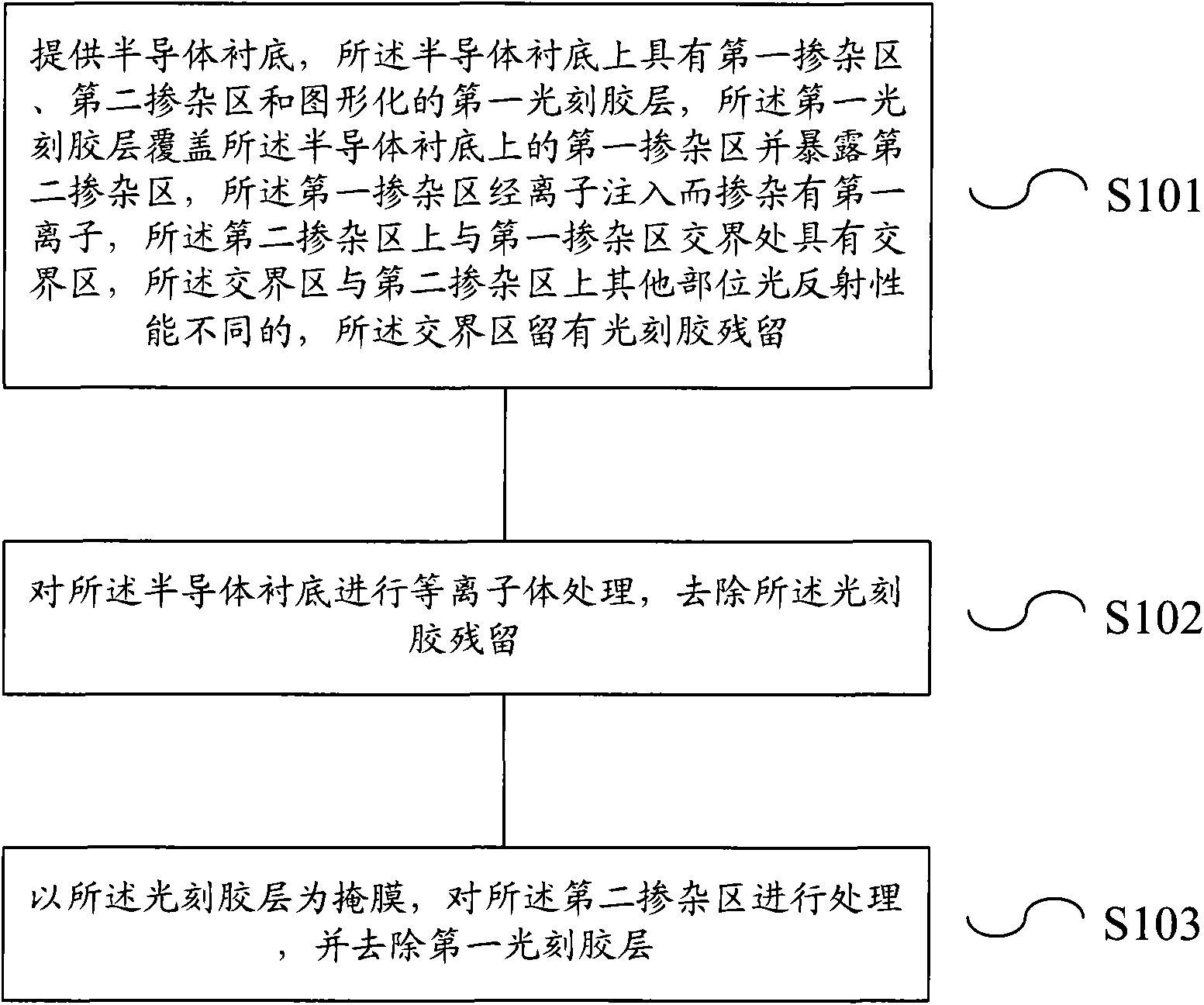

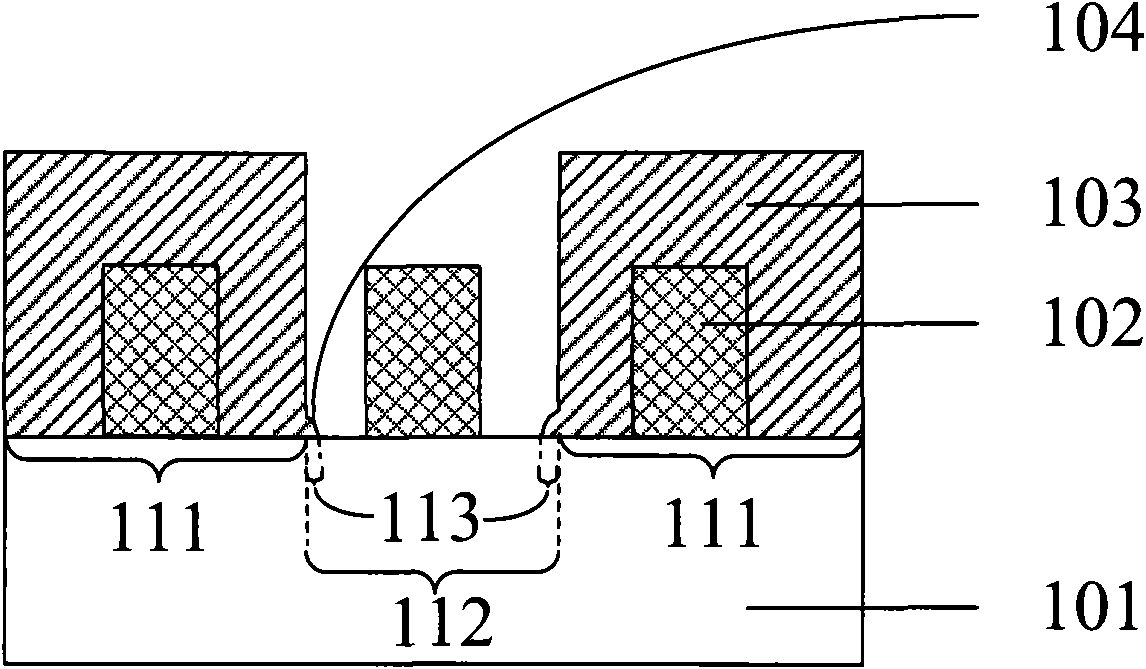

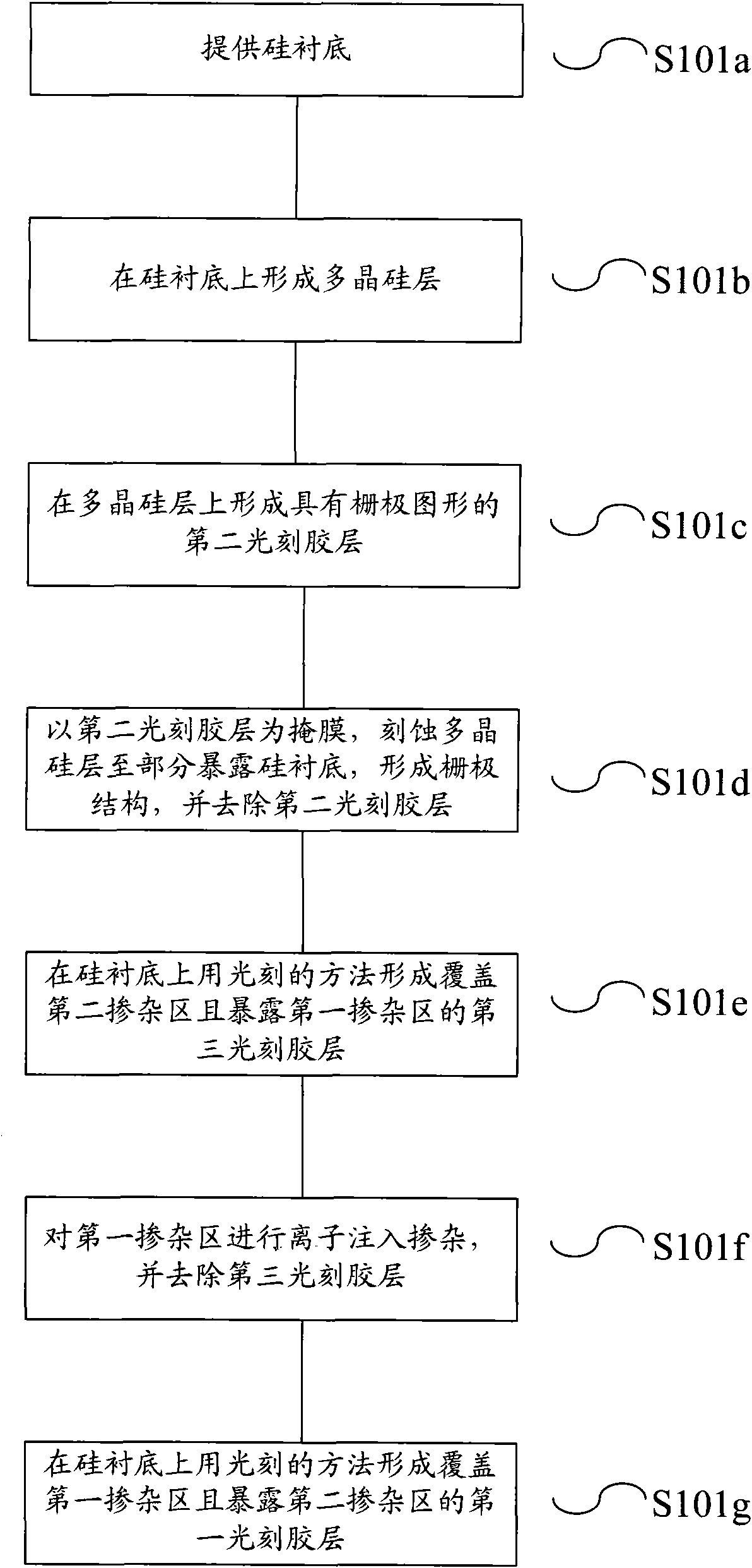

Method for removing residual photoresist

ActiveCN101587833AMaintain sidewall shapeImprove process resultsSemiconductor/solid-state device manufacturingPhotosensitive material processingLight reflectionPhotoresist

The invention provides a method for removing residual photoresist, which comprises the following steps: providing a semiconductor substrate; performing plasma treatment on the semiconductor substrate to remove the residual photoresist; and taking a photoresist layer as a mask to treat a second doped region and remove the photoresist layer, wherein the semiconductor substrate is provided with a first doped region, a second doped region and a graphic photoresist layer; the photoresist layer covers the first doped region on the semiconductor substrate and exposes the second doped region; the first doped region is doped with first ions by injecting ions; a junction region is arranged at the junction of the second doped region and the first doped region; the junction region has different light reflection performances with other parts of the second doped region; and the junction region is reserved with the residual photoresist. The residual photoresist generated by the difference of the light reflection performances on the junction region is removed by the method, and the influence of the residual photoresist on the process of the second doped region for subsequent treatment is prevented.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

Preparation method of NiAu projection and NiAu projection assembly

ActiveCN105355574AGuaranteed bonding areaGuaranteed binding effectSemiconductor/solid-state device detailsSolid-state devicesGalvanic cellTitanium

The invention provides a preparation method of a NiAu projection. The method comprises that a Ti or TiW metal layer and an Au metal layer are formed between a wafer and the NiAu projection from top to bottom, the Au metal layer outside the projection is removed from top to bottom in a physical dry etching manner, the Ti or TiW metal layer is removed via a wet etching manner, and reaction of a galvanic cell and excessive etching of the Ni material of the projection caused by the wet etching manner are avoided. The invention also provides a NiAu projection assembly which comprises the projection, a seed metal layer and a substrate metal layer, wherein the projection comprises a reserved layer, the Au metal layer and a Ni metal layer are successively from top to bottom, the seed metal layer and the substrate metal layer are arranged at the bottom of the projection, the lateral side of the Au metal layer and the lateral side of the projection are leveled in the vertical direction, and relatively large combination area and combination force between the projection and the wafer are ensured.

Owner:CHIPMORE TECH CORP LTD

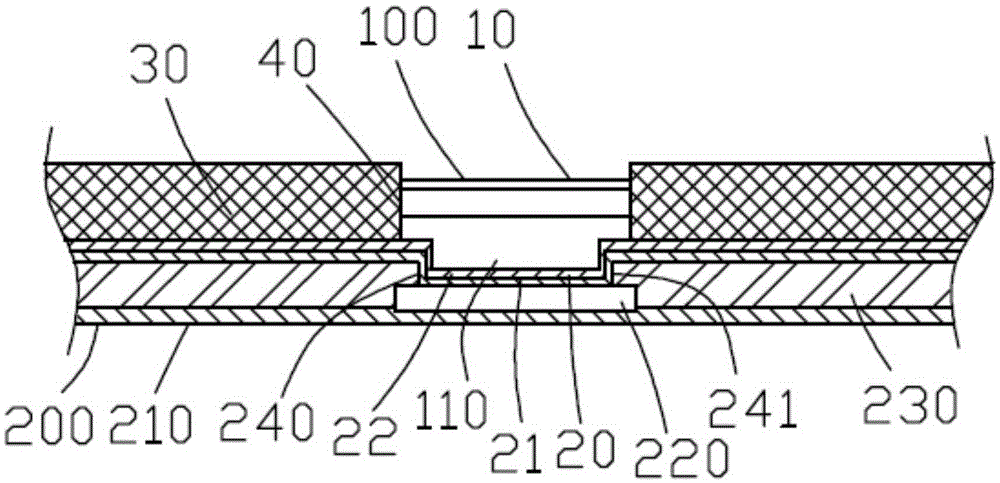

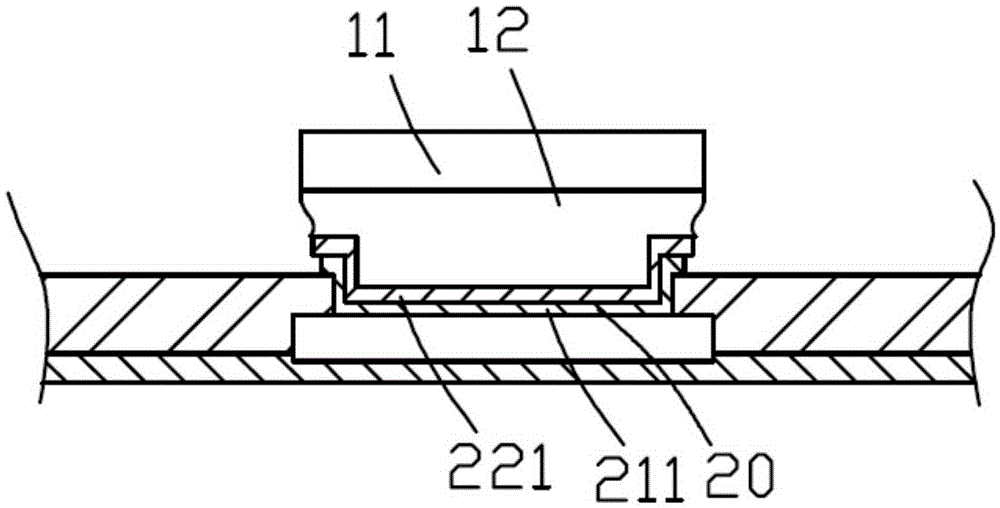

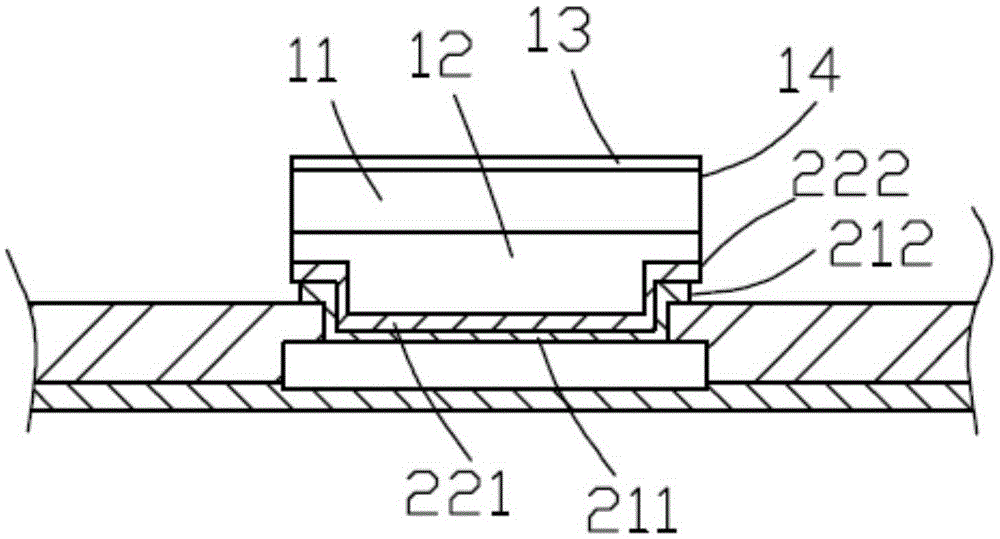

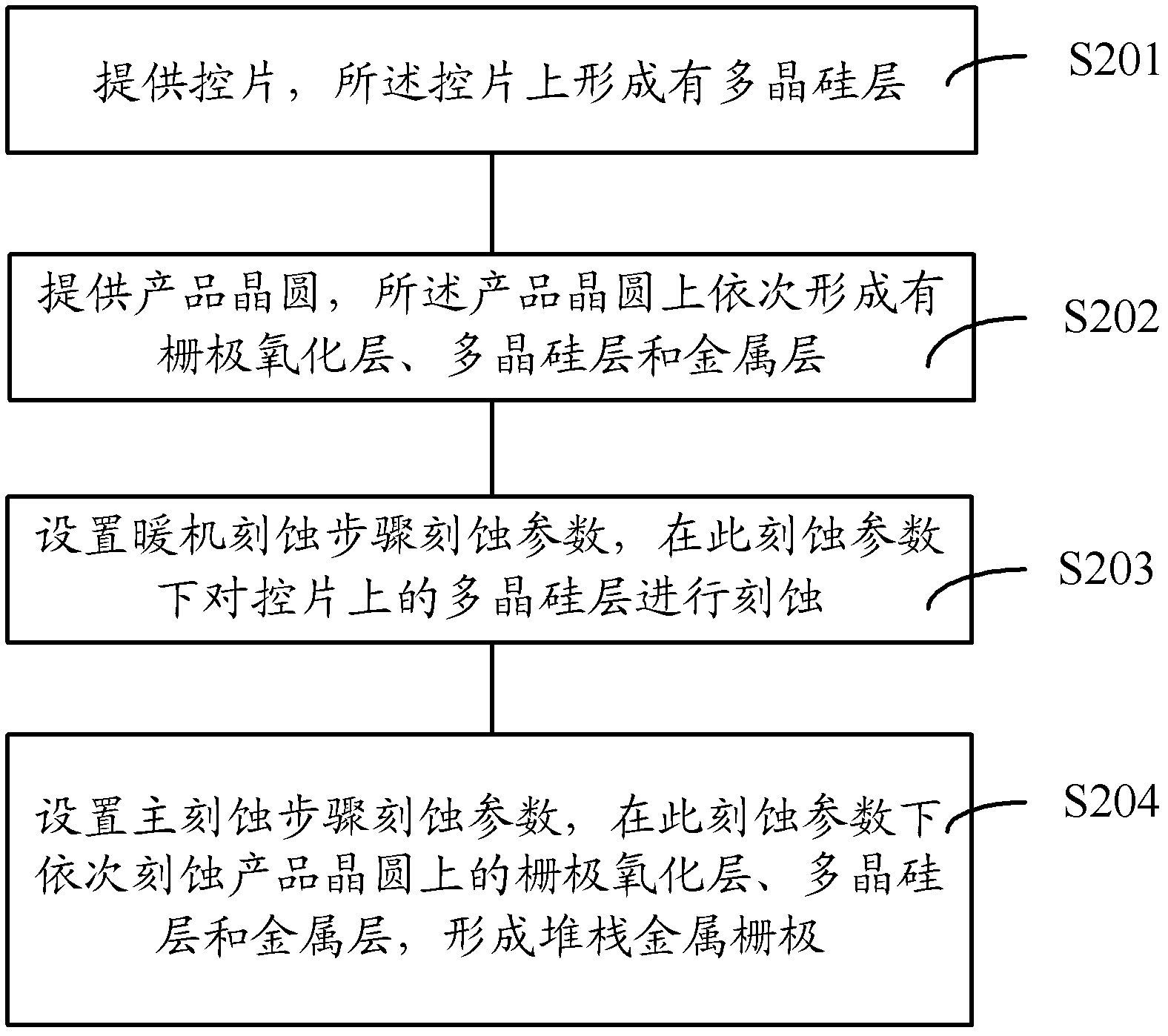

Etching method for stacked metal gate

ActiveCN102315112AAvoid over etchingImprove stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesEtchingMetal

The invention relates to an etching method for a stacked metal gate. The method comprises the following steps that: a control wafer is provided and a polysilicon layer is formed on the control wafer; a product wafer is provided, wherein a gate oxide, a polysilicon layer and a metal layer are successively formed on the product wafer; an etching parameter of a season etching step is arranged and the polysilicon layer on the control wafer is etched on the basis of the etching parameter; an etching parameter of a main etching step is arranged and the gate oxide, the polysilicon layer and the metal layer on the product wafer are successively etched on the basis of the etching parameter, so that a stacked metal gate is formed. On the basis of the utilization of the etching method provided in the invention, an effect of small linewidth of a stacked metal gate of a first piece of product wafer after the season etching can be eliminated, so that stability of a device is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

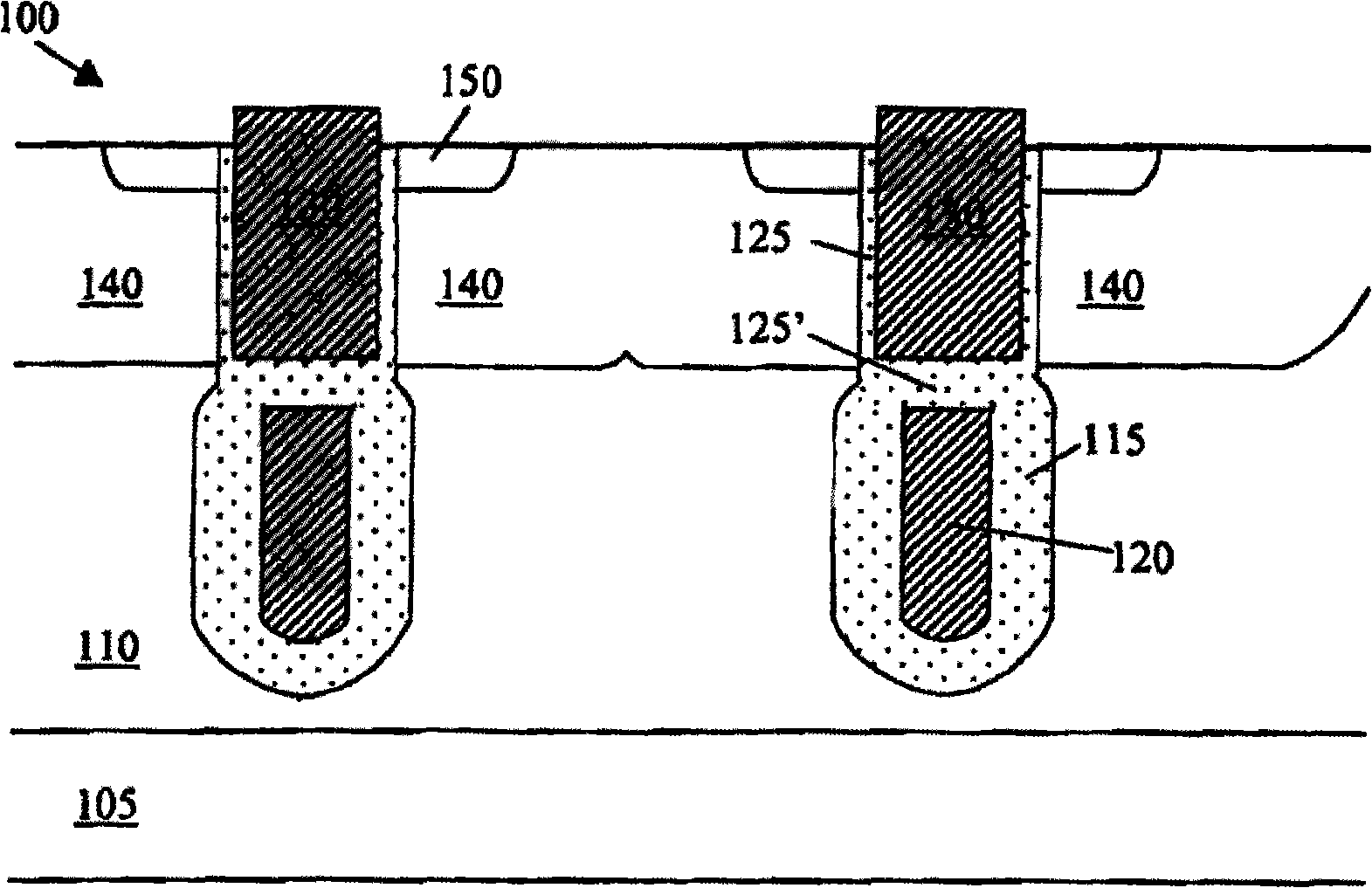

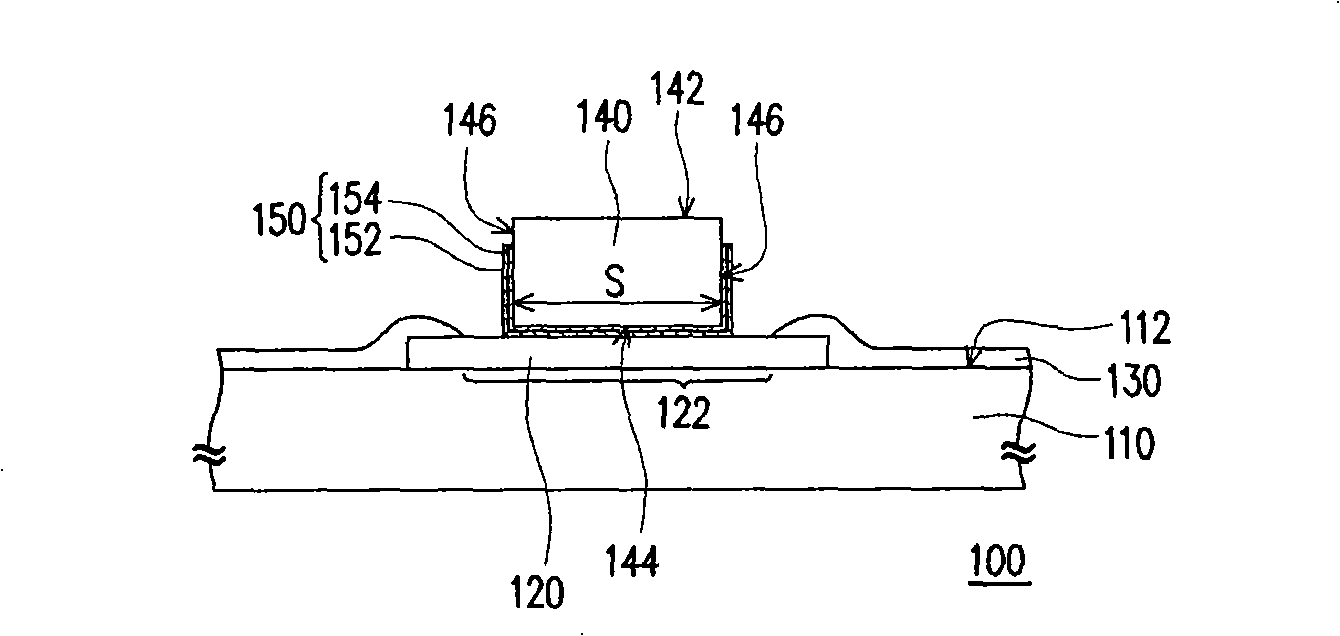

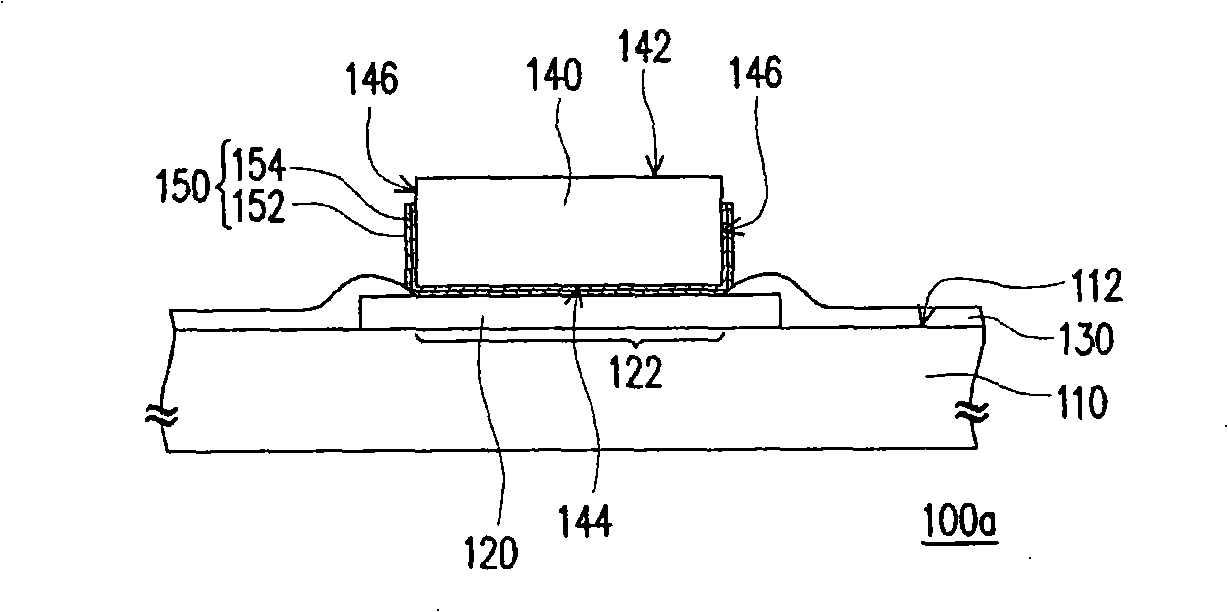

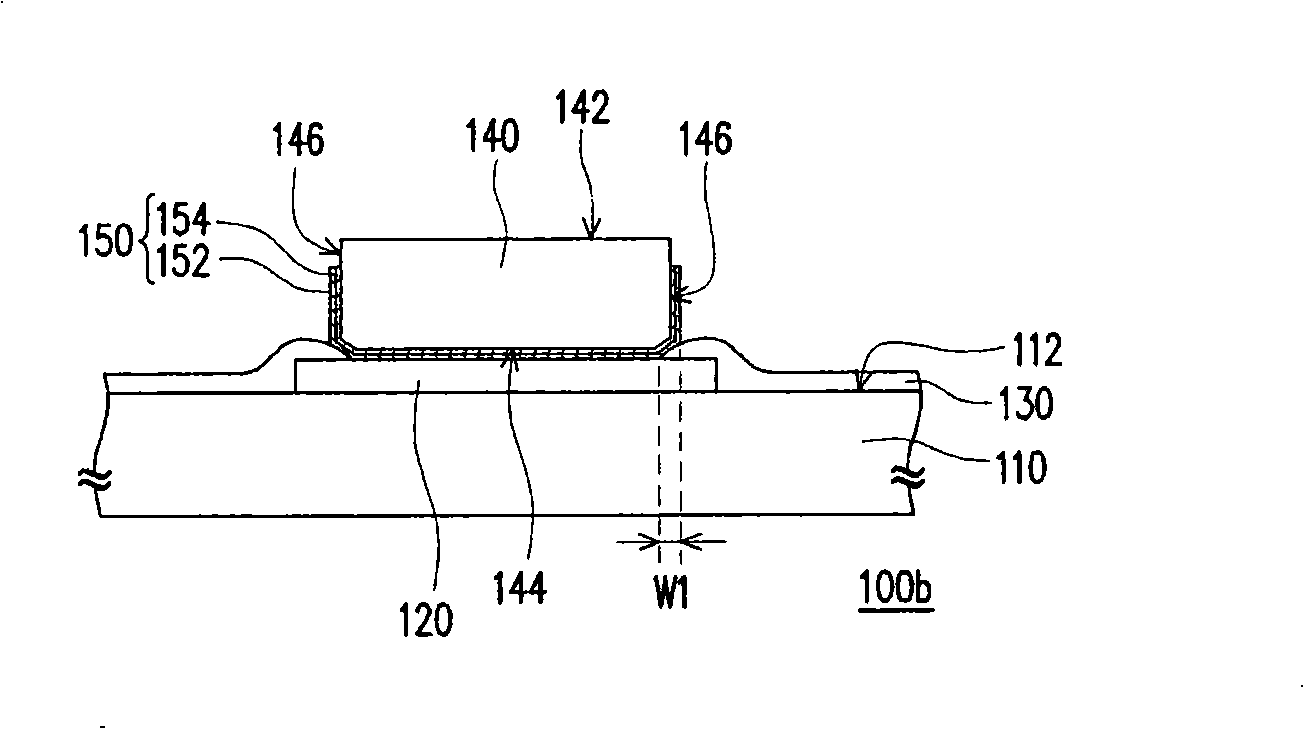

Semiconductor device and manufacturing method of the same

ActiveCN103035615AAvoid over etchingPrevent thinningSemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceDevice material

Disclosed herein is a semiconductor device including: a substrate having a first conductive layer and a second conductive layer arranged deeper than the first conductive layer; a large-diameter concave portion having, on a main side of a substrate, an opening sized to overlap the first and second conductive layers, with the first conductive layer exposed in part of the bottom of the large-diameter concave portion; a small-diameter concave portion extended from the large-diameter concave portion and formed by digging into the bottom of the large-diameter concave portion, with the second conductive layer exposed at the bottom of the small-diameter concave portion; and a conductive member provided in a connection hole made up of the large- and small-diameter concave portions to connect the first and second conductive layers.

Owner:SONY CORP

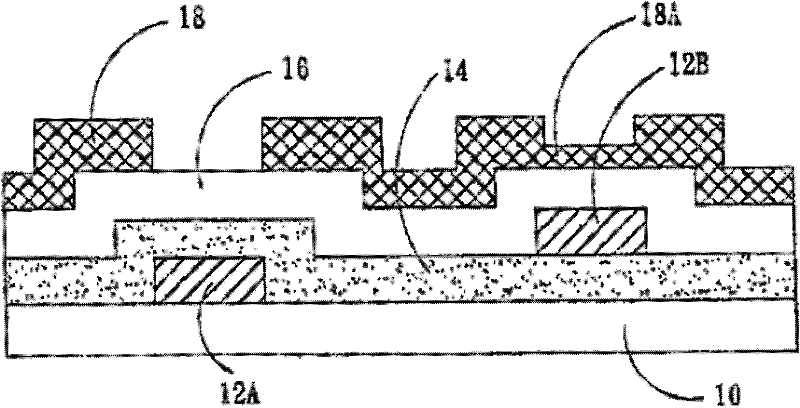

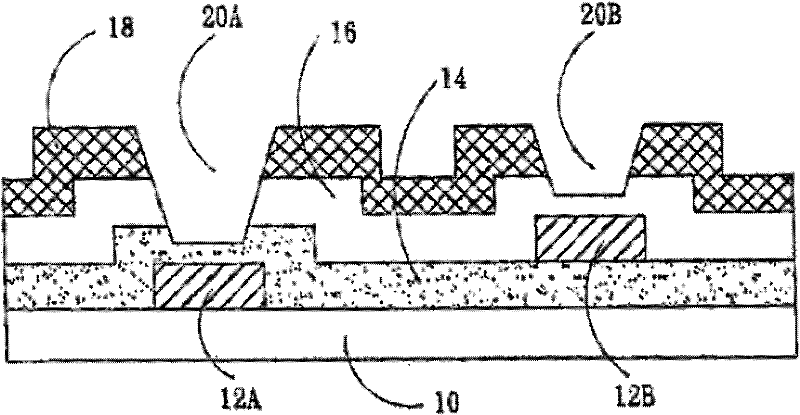

Method for forming CMOS transistor

ActiveCN104517901AIncrease stressImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSEngineering

A method for forming a CMOS transistor comprises the following steps: providing a semiconductor substrate consisting of a first region and a second region, wherein a first dummy gate structure, first spacers on the two side surfaces of the first dummy gate structure and a first hard mask layer on the first dummy gate structure are formed on the first region, and a second dummy gate structure and second spacers on the two side wall surfaces of the second dummy gate structure are formed on the second region; forming a second hard mask layer; forming a filling layer covering the second hard mask layer and a mask layer disposed on part of the surface of the filling layer on the second region on the surface of the semiconductor substrate; etching a partial thickness of the filling layer on the first region and part of the second hard mask layer on the top of the first dummy gate structure; and removing the filling layer, the mask layer and the second hard mask layer, and forming a first stress layer covering the first dummy gate structure and a second stress layer covering the second dummy gate structure. By adopting the method of the invention, the performance of a formed CMOS transistor can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Novel wafer level tin solder micro bump manufacturing method

InactiveCN105140140AAvoid over etchingImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor chipCopper

The invention provides a novel wafer level tin solder micro bump manufacturing method, and belongs to the field of semiconductor chip packaging. Photoresist of which the opening is formed through exposure development is utilized to act as a mask film firstly. A copper layer, a barrier layer and solder alloy are electroplated on an under bump metal layer in turn, and the solder alloy is enabled to completely wrap a copper layer-barrier layer of the bottom part. Then tin solder micro bumps are formed via a method of backflow and then photoresist removing. Finally the micro bumps act as an etching mask film and a wet etching technology is adopted to remove the excess under bump metal layer. Excessive etching of electroplating copper of a bump layer in isotropic etching of the under bump metal layer can be avoided, and bridging caused by collapsing of backflow of the micro bumps can be avoided so that reliability of the micro bumps and packaging products can be enhanced.

Owner:BEIJING UNIV OF TECH

Forming method for contact hole

ActiveCN101123212AIncreasing the thicknessImprove protectionSemiconductor/solid-state device manufacturingDevice PropertiesEngineering

A method for forming contact holes is disclosed and comprises: an underlayer, on which a plurality of grids is formed, is provided and the side walls of the grids have side wall layers; an added medium layer is deposited on the undeerlayer; the added medium layer is corroded and added side wall layers are formed at the side walls of the grids; a corroding and stopping layer is deposited on the underlayer; an interlaminar medium layer is deposited on the corroding and stopping layer; the interlaminar medium layer is made into a design and is corroded to form contact holes. The invention, through thickening the thickness of the side wall layer of the grids, strengthens the protection of the side wall of the grids, avoids over-corrosion of side wall layers, prevents the damage of groove and the drift of the device properties, and increases the rate of finished products and the reliability of devices while the device parameter remains the same.

Owner:SEMICON MFG INT (SHANGHAI) CORP

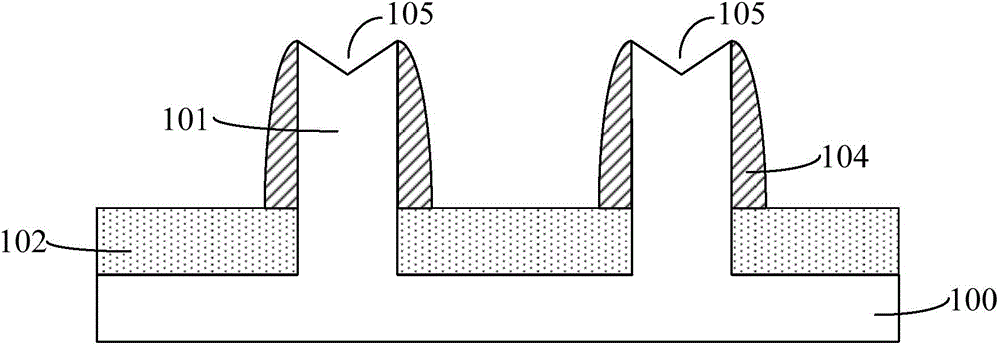

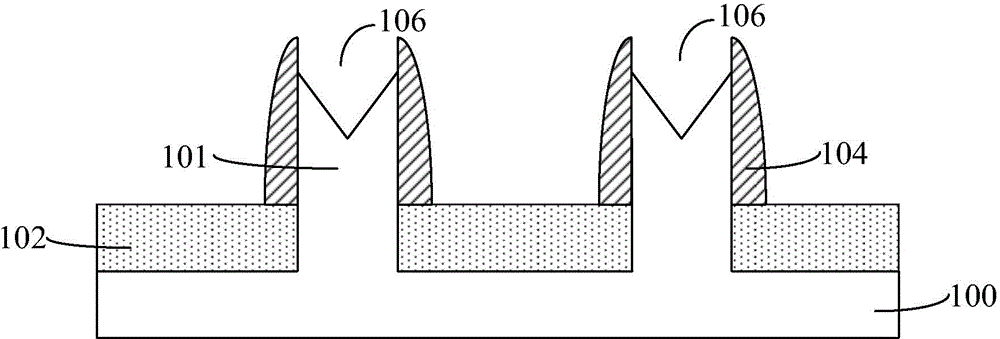

Fin-type field effect transistor forming method

ActiveCN105719969AImprove electrical performanceUniform etch rateSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingElectrical performance

The invention discloses a fin-type field effect transistor forming method, and the method comprises the steps: providing a substrate, wherein the surface is provided with a plurality of separated fin parts; forming a separation layer on the surface of the substrate, wherein the top of the separating layer is lower than the top of the fin parts, and covers the surface of a part of side walls of the fin parts; forming a side wall layer covering the surfaces of the side walls of the fin parts, and exposing the top surfaces of the fin parts; carrying out the selective nitrogen treatment of the tops of the fin parts, and enabling the fin parts at a certain thickness to be converted into a semiconductor nitridation layer; carrying out the etching of the semiconductor nitridation layer through employing a wet etching method, so as to form openings between the adjacent side wall layers and the remaining fin parts; and placing stress layers in the openings. The method improves the flatness of the bottom of the opening, improves the quality of the formed stress layers, and optimizes the electrical performances of a fin-type field effect transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP

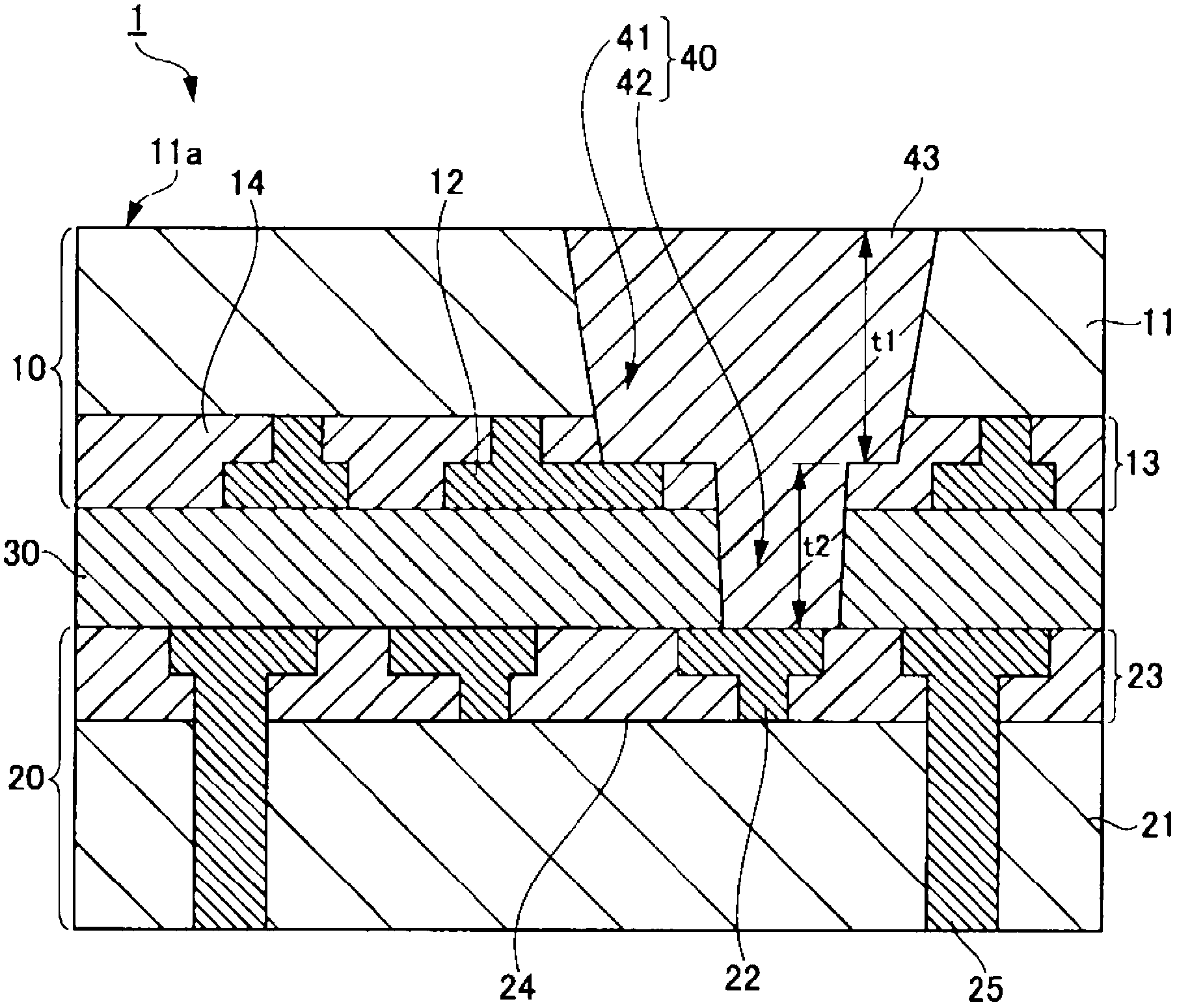

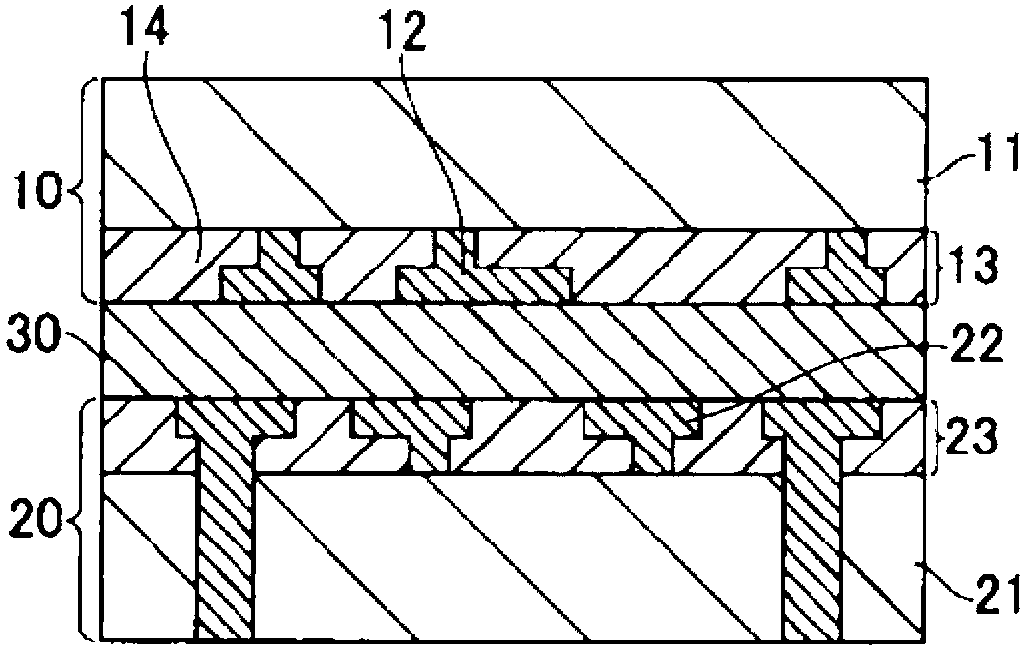

Substrate having electrical interconnection structure and fabrication method thereof

ActiveCN105023906AWon't corrodeAvoid over etchingSemiconductor/solid-state device detailsSolid-state devicesOptoelectronicsInterconnection

A method for fabricating a substrate having an electrical interconnection structure is provided, which includes the steps of: providing a substrate body having a plurality of conductive pads and first and second passivation layers sequentially formed on the substrate body and exposing the conductive pads; forming a seed layer on the second passivation layer and the conductive pads; forming a first metal layer on each of the conductive pads, wherein the first metal layer is embedded in the first and second passivation layers without being protruded from the second passivation layer; and forming on the first metal layer a second metal layer protruded from the second passivation layer. As such, when the seed layer on the second passivation layer is removed by etching using an etchant, the etchant will not erode the first metal layer, thereby preventing an undercut structure from being formed underneath the second metal layer.

Owner:SILICONWARE PRECISION IND CO LTD

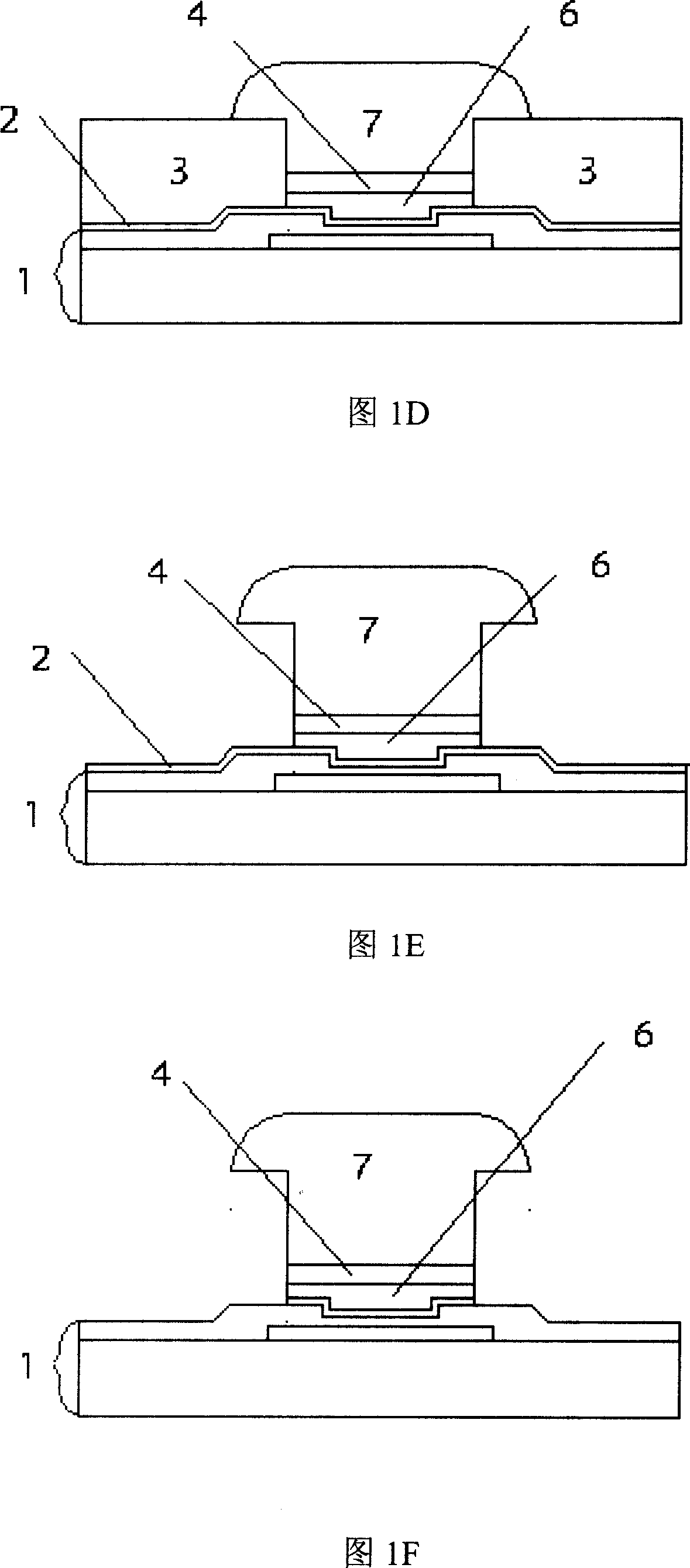

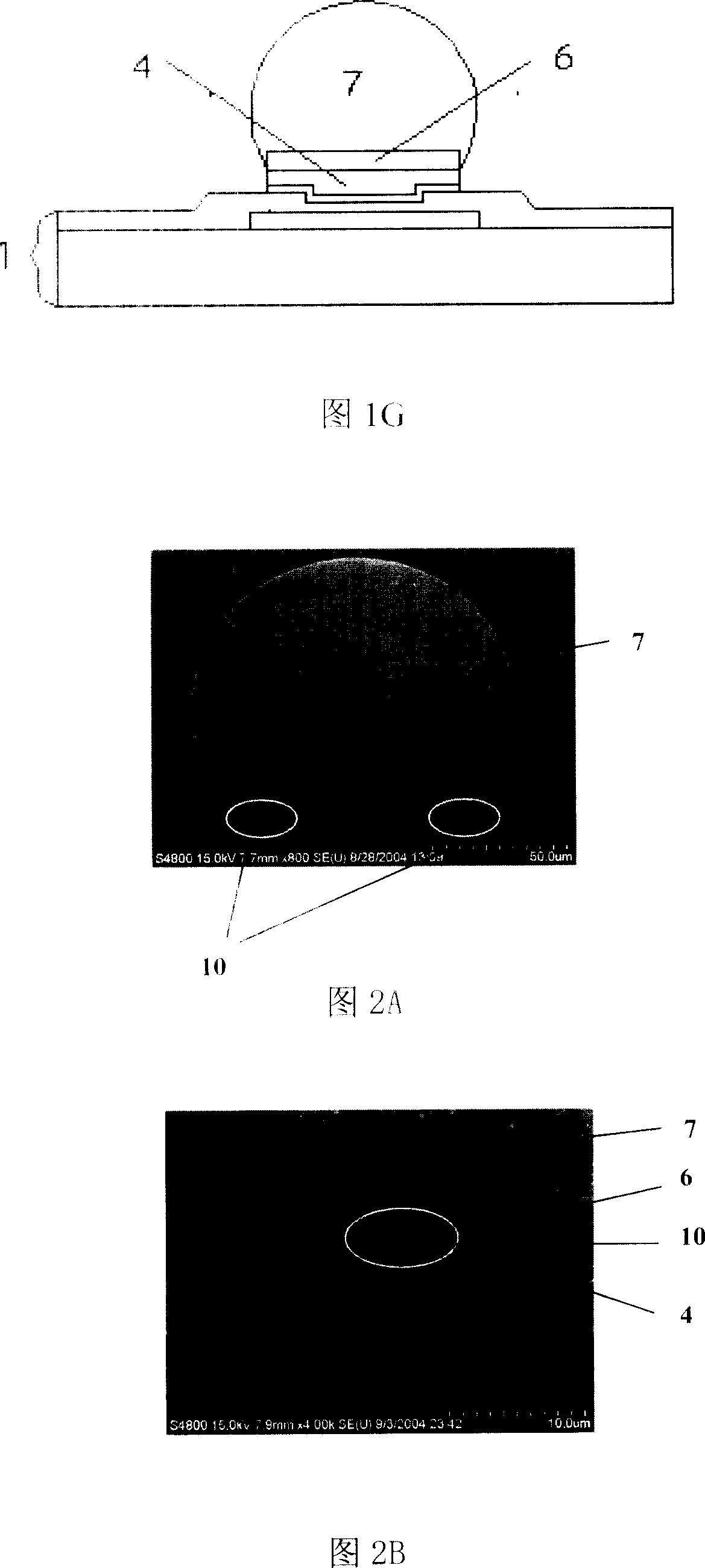

Method for making solder bump

InactiveCN101071778AAvoid over etchingDoes not reduce interfacial resistanceSolid-state devicesSemiconductor/solid-state device manufacturingIsolation layerCopper

The invention provides a new solder bump making method, able to prevent metal layers under solder bumps from being over etched. And it is characterized in: separately forming plated copper layers under solder bumps and nickel isolation layers on the plated copper layers and making the nickel isolation layers completely cover the plated copper layers under them to prevent the plated copper layers from being etched in the following isotropic etching and forming bottom cut, i.e. concave cut, in all plated copper layers. Thus, it can prevent the conductivity of the formed solder bumps from decreasing and improves reliability of solder bumps and semiconductor devices.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Semiconductor plasma etching technology

ActiveCN101615579AImprove the selection ratioIncrease topSemiconductor/solid-state device manufacturingSemiconductor plasmaShielding gas

The invention provides a plasma etching technology comprising a dielectric layer penetrating and etching step and a silicon main etching step, wherein, technical gas in the dielectric layer penetrating and etching step comprises fluorine-base etching gas, first light resistance protection gas and dilution gas; technical gas in the silicon main etching step comprises main etching gas, carbon-base by-product removing gas and second light resistance protection gas. In a preferable embodiment, the fluorine-base etching gas is CF4 or SF6, the first light resistance protection gas is CH2F2 or CHF3 or HBr, and the dilution gas is He, Ar or N2; the main etching gas is Cl2, the carbon-base by-product removing gas is O2, and the second light resistance protection gas is HBr. In semiconductor plasma etching, the invention can improve sidewall steepness in figure etching and prevent the upper edge and the lower edge of a line from producing fillets.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

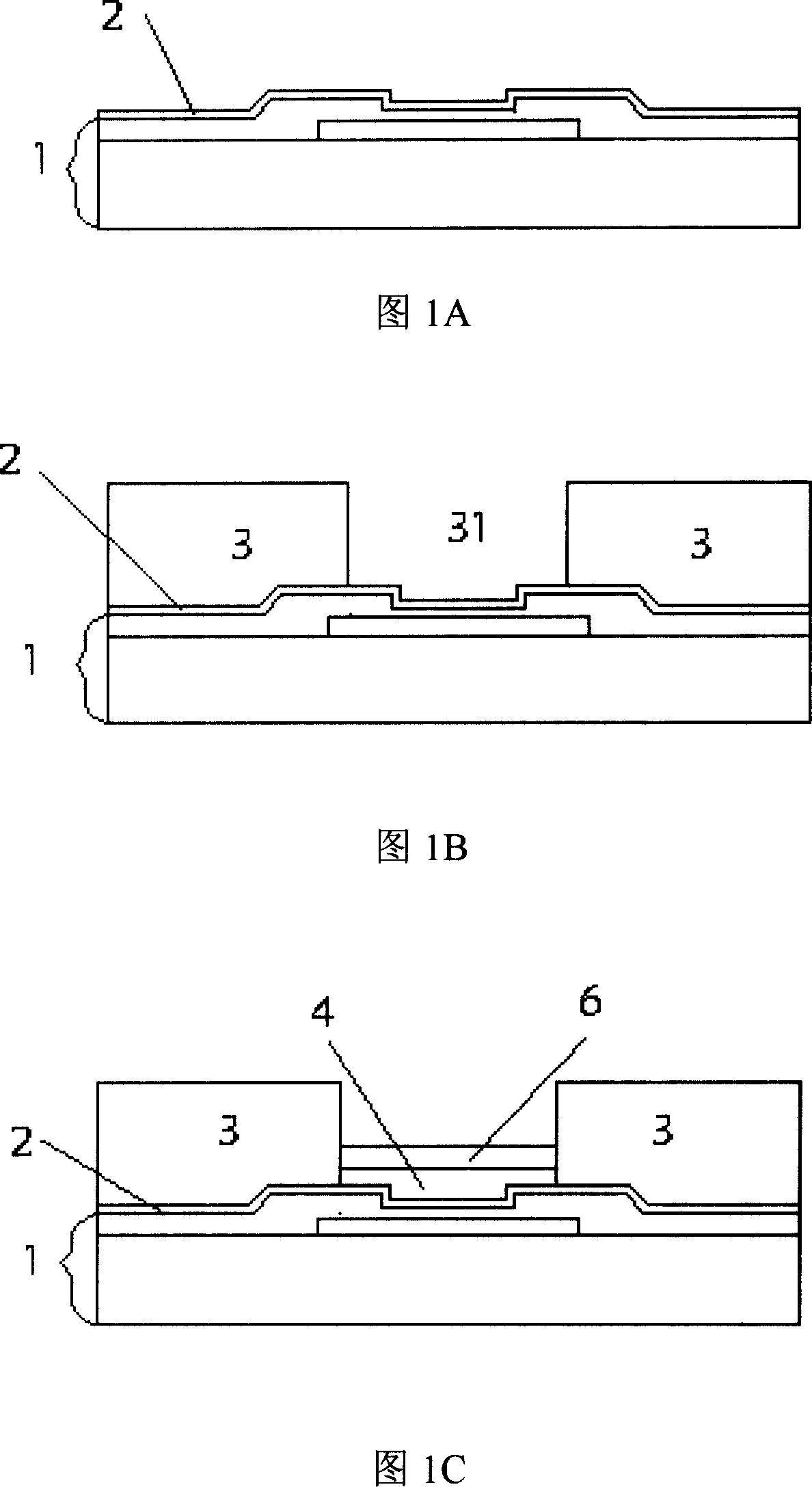

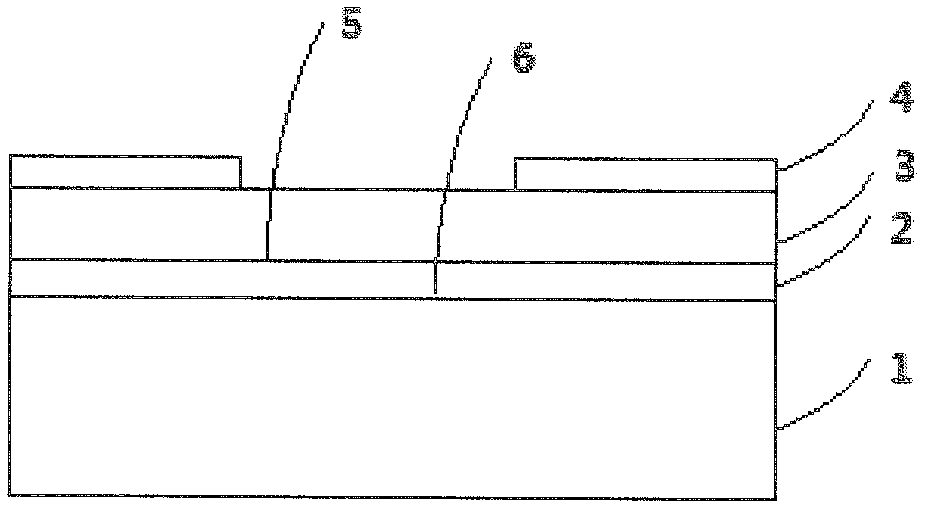

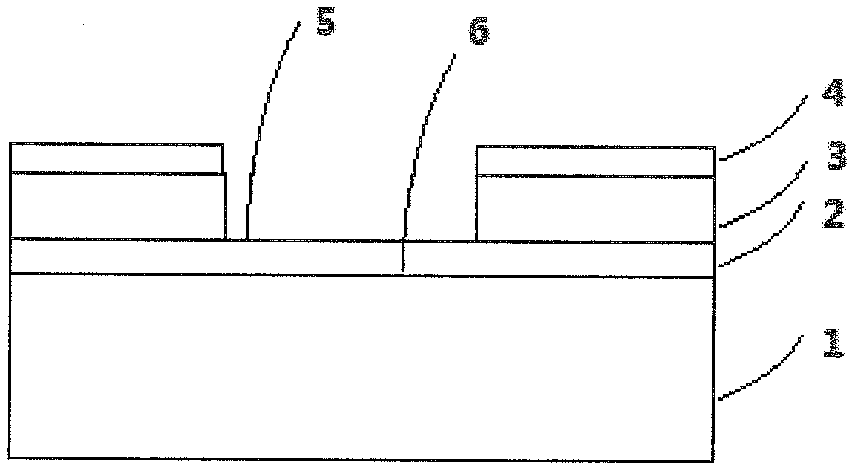

Manufacturing method of active element array substrate

InactiveCN101562152AGood process yieldAvoid over etchingSemiconductor/solid-state device manufacturingNon-linear opticsEtchingCapacitance

The invention is applicable to the technical field of display panel, and provides a manufacturing method of an active element array substrate, comprising the following steps of: firstly, forming a gate, a capacitor electrode, a first insulating layer, a channel layer, a source electrode and a drain electrode; secondly, forming a second insulating layer on the substrate on all sides, and forming a patterning photo-resistant layer on the substrate; thirdly, removing the second insulating layer above the drain electrode and the capacitor electrode to form a contact window and an opening by taking the patterning photo-resistant layer as a mask, wherein the contact window is exposed out of the drain electrode, while the opening is exposed out of the first insulating layer positioned above the capacitor electrode; and fourthly, forming a pixel electrode on the substrate, wherein the pixel electrode passes through the contact window so as to be electrically connected with the drain electrode and filled in the opening. A storage capacitor is formed by the pixel electrode, the capacitor electrode, and the first insulating layer positioned between the pixel electrode and the capacitor electrode. In the invention, the manufacturing method of the active element array substrate has good process yield, and can avoid the occurrence of over-etching or insufficient etching.

Owner:CPT TECH GRP +1

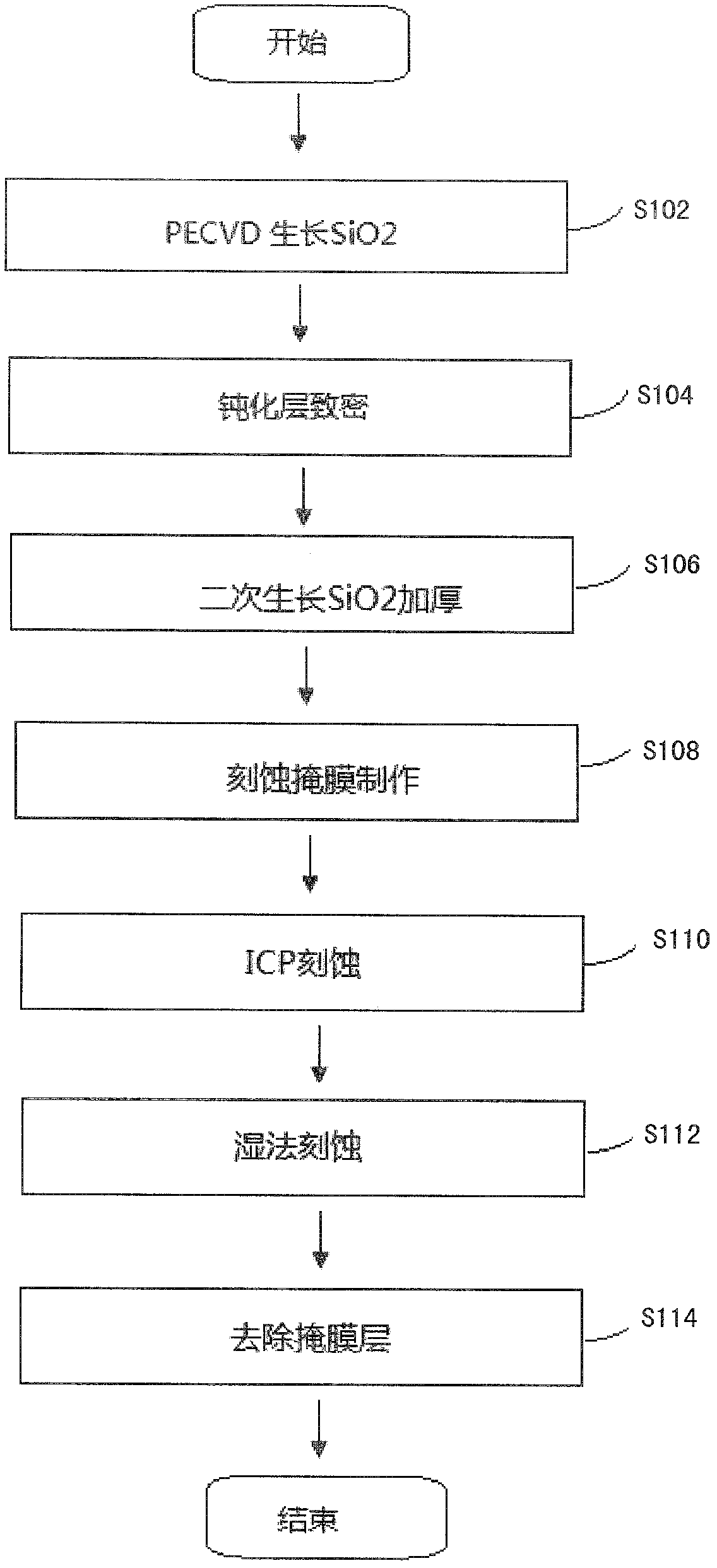

Method for preventing over etching of passivation layers

ActiveCN103021840AAvoid over etchingGuaranteed etching qualitySemiconductor/solid-state device manufacturingPhotoresistDry etching

The invention discloses a method for preventing over etching of passivation layers, comprising the following steps of: step A, preparing two passivation layers different in compactness on a substrate, wherein the passivation layer close to the side of the substrate is a compact passivation layer, while the passivation layer far away from the side of the substrate is a loose passivation layer; step B, applying a photoresist on the passivation layers through spin coating, and exposing and developing the photoresist according to a predetermined element template; step C, with the photoresist left after exposure and development on the substrate as the mask, performing dry etching on the loose passivation layer; and step D, with the photoresist left after exposure and development on the substrate as the mask, performing wet etching on the compact passivation layer. The method provided by the invention avoids over etching of the base layer SiC and also guarantees the etching quality by growing two SiO2 layers different in compactness and separately etching the two SiO2 layers different in compactness by combining the advantages of the wet etching and the dry etching.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Forming method of semiconductor structure

ActiveCN104217938ALarge plasma contentReduced chance of bombardmentElectric discharge tubesSemiconductor/solid-state device manufacturingEtchingSemiconductor structure

A forming method of a semiconductor structure includes: providing a substrate having a plurality of gate structures on the surface, with the sidewall surface, provided with a sidewall, of each gate structure and impurity arranged on the surface of the substrate between each two adjacent sidewalls; putting the substrate in a sputtering etching chamber, subjecting the surface of the substrate between the adjacent sidewalls to primary sputtering etching which is used for primary removal of the impurity and which provides a first radio frequency power and a first direct-current bias voltage; and subjecting the surface of the substrate to secondary sputtering etching which is used for secondary removal of the impurity and which provides a second radio frequency power and a second direct-current bias voltage. The second radio frequency power is less than the first radio frequency power; the second direct-current bias voltage is greater than the first direct-current bias voltage. The forming method has the advantages that an advancing direction of a plasma beam is perpendicular to the surface of the substrate in the sputtering etching process, the impurity is more effectively removed by etching, and impact of the plasma beam upon the surfaces of the sidewalls is decreased.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

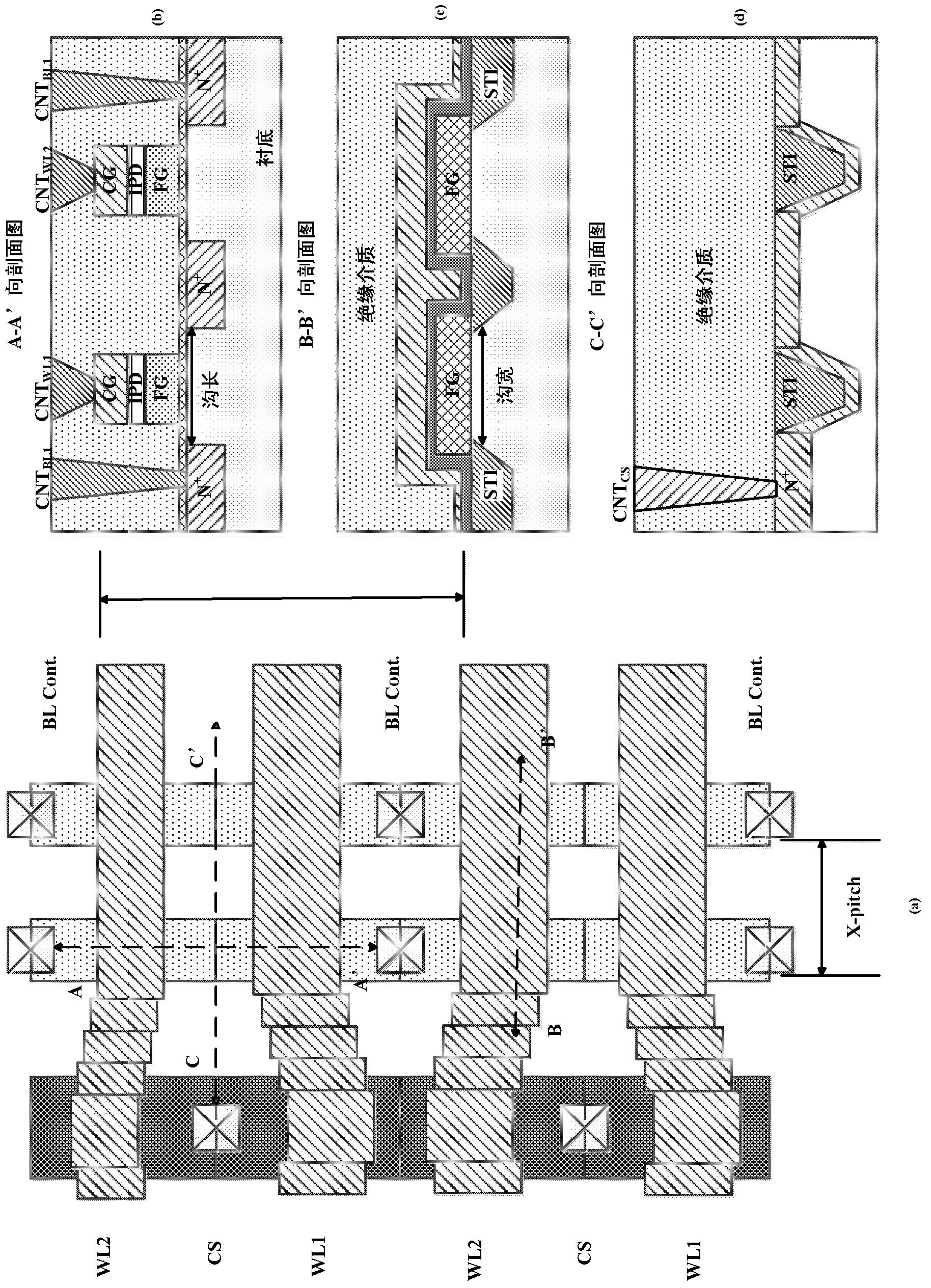

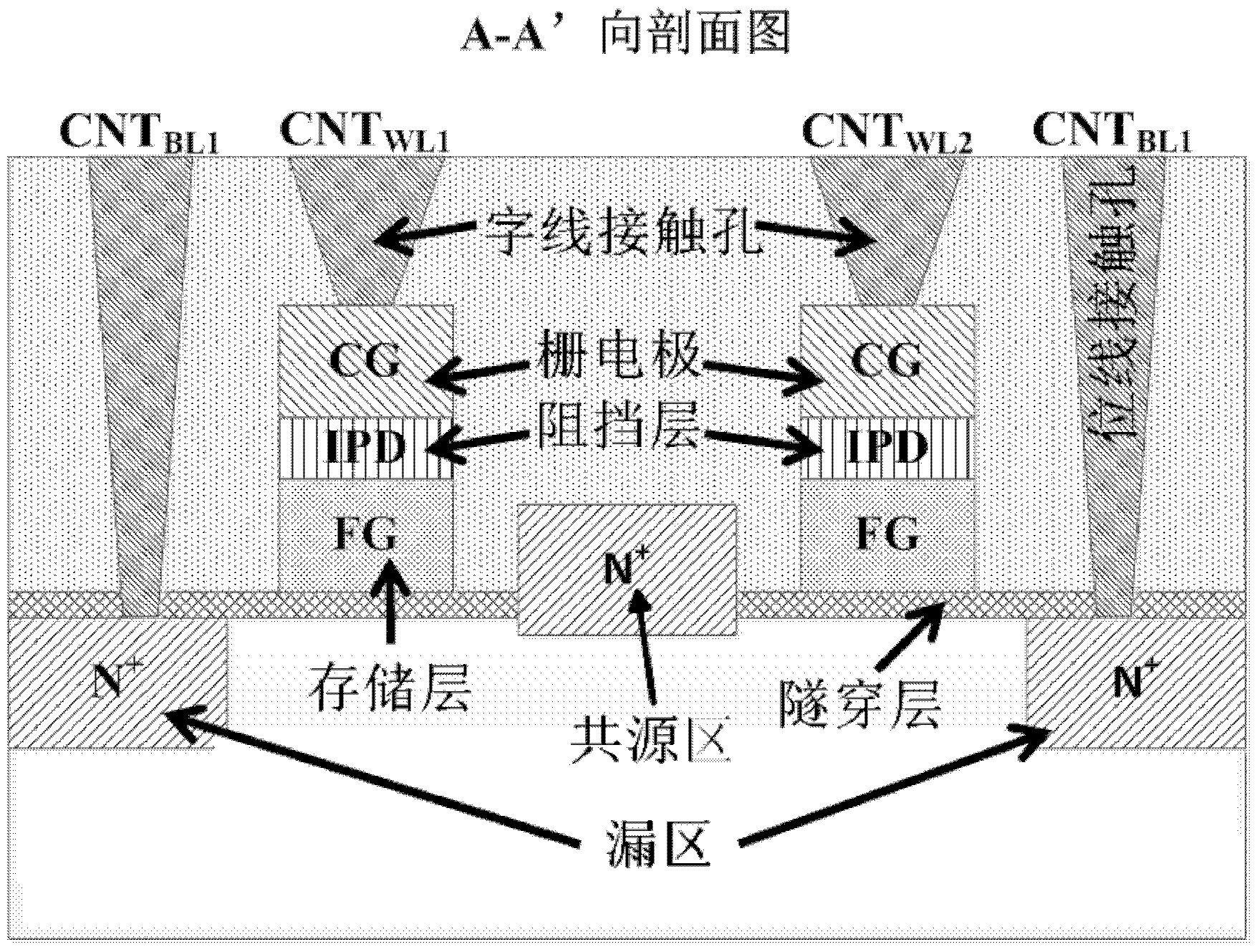

NOR-type flash memory unit for lifting common source region and preparation method thereof

ActiveCN104124248AOver etchReduce short groove effectSolid-state devicesSemiconductor/solid-state device manufacturingChannel widthCommon source

The invention discloses an NOR-type flash memory unit for lifting a common source region and a preparation method thereof. The flash memory unit comprises a substrate; common source and drain regions formed below the surface of the substrate through injection; a channel region formed on the surface of the substrate between the common source and drain regions; a tunneling layer formed over the channel region; a storage layer formed over the tunneling layer; a barrier layer formed over the storage layer; and a gating electrode formed over the barrier layer. In the forming process of the common source region, an epitaxial process is first used for lifting the common source region, and then low resistance connection is formed between below the shallow slot isolation region and the common source region through ion injection for below a shallow slot isolation region and the common source region of the flash memory unit. Through the introduction of the epitaxial process, the shallow slot isolation region expands along an active region in a channel width direction along while the common source region is lifted, punch-through effects are effectively simulated in the size reduction process of a conventional NOR-type flash memory device, and the NOR-type device is further scaled down in a channel length direction.

Owner:合肥中科微电子创新中心有限公司

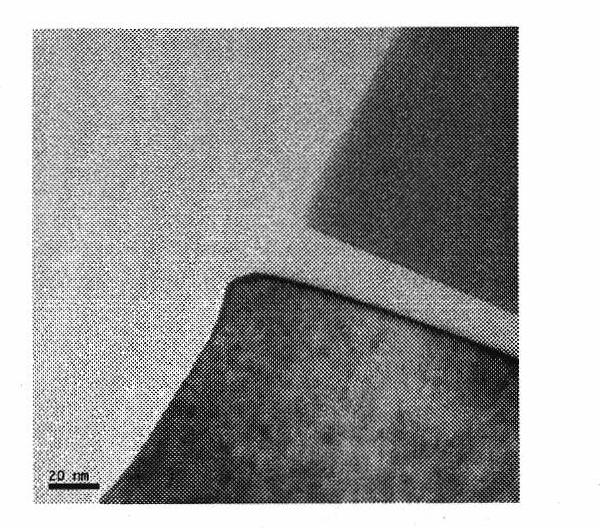

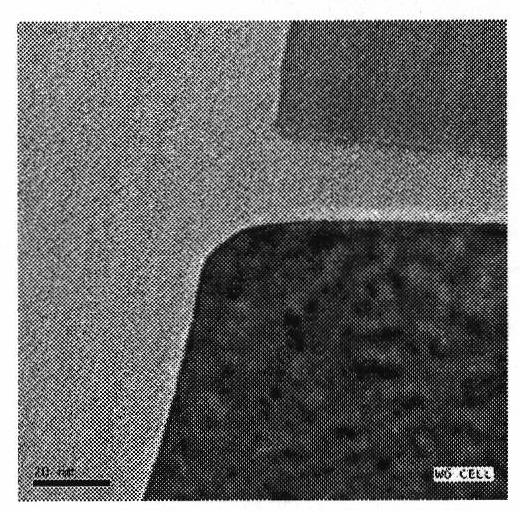

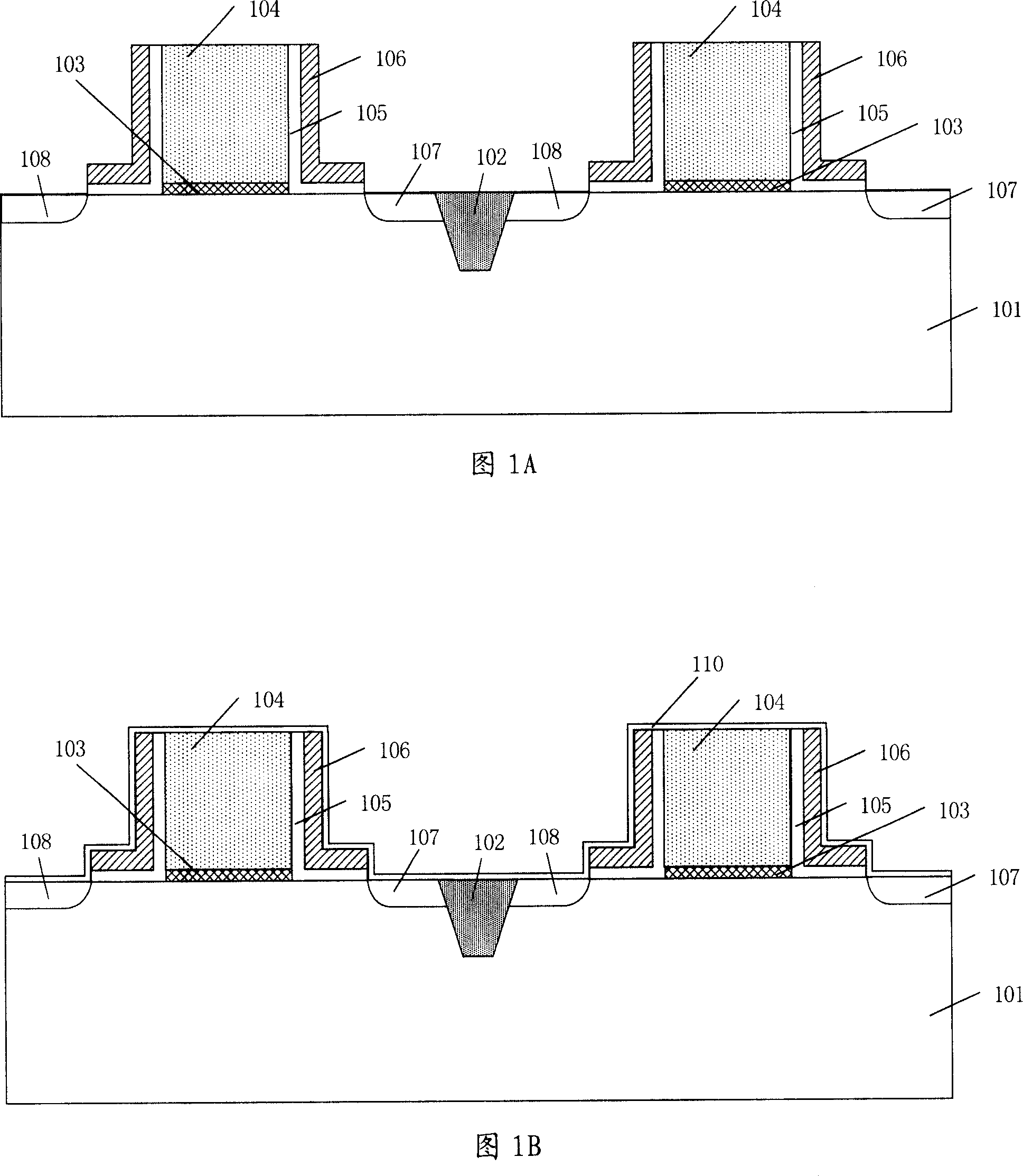

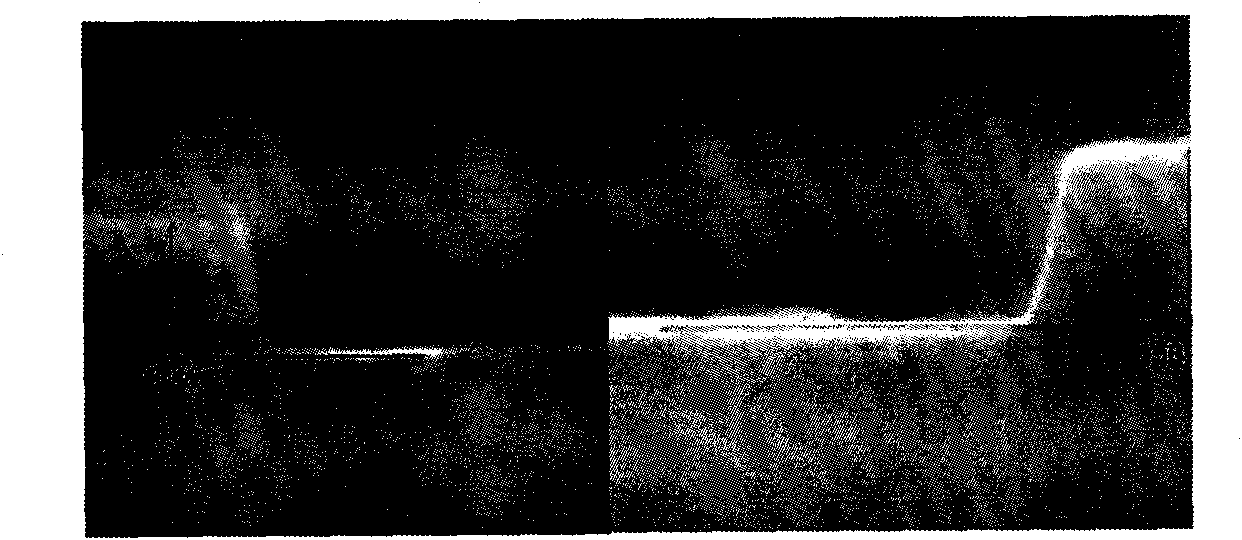

Double gate manufactured with locos techniques

ActiveCN101320753AAvoid over etchingAvoid stretchingTransistorSemiconductor/solid-state device manufacturingInsulation layerLOCOS

This invention discloses a trenched semiconductor power device that includes a trenched gate surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a substrate. The trenched gate further includes at least two mutually insulated trench-filling segments with a bottom insulation layer surrounding a bottom trench-filling segment having a bird-beak shaped layer on a top portion of the bottom insulation attached to sidewalls of the trench extending above a top surface of the bottom trench-filling segment.

Owner:ALPHA AND OMEGA SEMICONDUCTOR (CAYMAN) LIMITED

Xenon difluoride gas-phase etching method for barrier layer

ActiveCN103700615AIncrease etch rateAvoid over etchingSemiconductor/solid-state device manufacturingGas phaseLight beam

The invention discloses a xenon difluoride gas-phase etching method for a barrier layer. The method comprises the following steps: (1) spraying xenon difluoride to the surface of an exposed barrier layer; (2) only irradiating the barrier layer on the upper surface of a dielectric layer to increase the etching rate of the barrier layer on the upper surface of the dielectric layer to be higher than that of the barrier layer on the sidewalls of grooves and connecting holes by adopting light beams. According to the method, the barrier layer on the upper surface of the dielectric layer is irradiated by the light beams to increase the etching rate of the barrier layer on the upper surface of the dielectric layer to be higher than that of the barrier layer on the sidewalls of the grooves and the connecting holes, so that the barrier layer on the sidewalls of the grooves and the connecting holes is prevented from being excessively etched, the microcosmic etching uniformity is improved, and better process effects are achieved.

Owner:ACM RES SHANGHAI

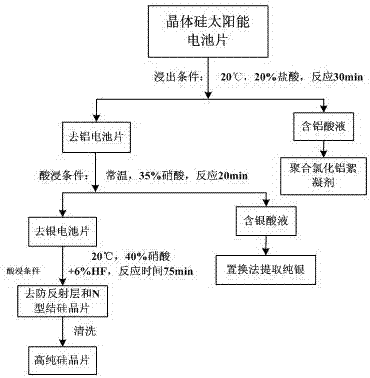

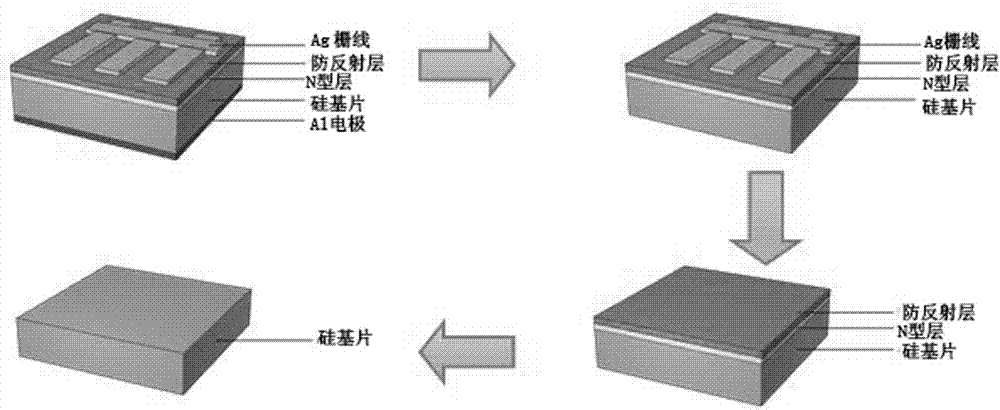

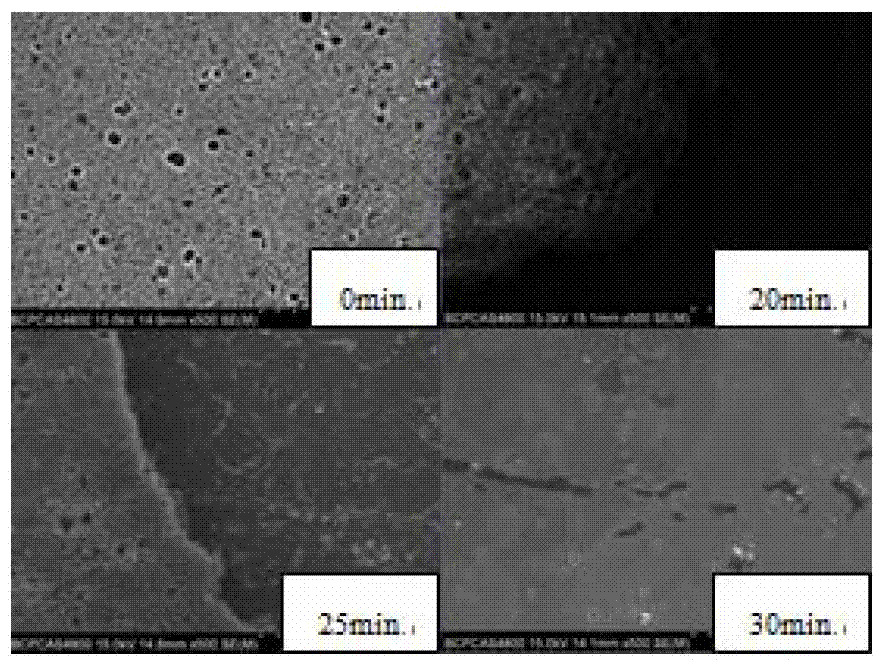

Crystalline silicon solar cell resource classifying recycling method

ActiveCN107457250AAvoid over etchingIncrease the difficultyWaste processingSolid waste disposalRecovery methodHydrofluoric acid

The invention discloses a crystalline silicon solar cell resource classifying recycling method. The crystalline silicon solar cell resource classifying recycling method comprises the following steps: cleaning crystalline silicon solar cells to obtain clean silicon wafers; removing aluminium from the surfaces of the silicon wafers; removing silver from the surfaces of the silicon wafers; removing anti-reflecting layers and N-type knots from the surfaces of the silicon wafers; at room temperature, cleaning the silicon wafers from which the aluminium and the silver are removed, and placing the silicon wafers in a mixed acid aqueous solution, wherein the mixed acid aqueous solution comprises HNO3 with the volume fraction of 39 to 41 percent and HF with the volume fraction of 5.5 to 6.5 percent; and enabling the silicon wafers to react for over 75 minutes in the mixed acid aqueous solution to obtain pure silicon wafers. According to the crystalline silicon solar cell resource classifying recycling method, the aluminium is removed by adopting hydrochloric acid; a good effect of removing the blue anti-reflecting layers and the N-type knots from the silicon wafers is achieved in a mode of mixed acid of nitric acid and hydrofluoric acid; and the silicon wafers with high purity can be obtained.

Owner:CHINESE RES ACAD OF ENVIRONMENTAL SCI

Semiconductor device and method of bump formation

InactiveCN101404268AFlat surfaceAvoid over etchingSemiconductor/solid-state device detailsSolid-state devicesContact padProtection layer

The present invention discloses a semiconductor device including a semiconductor substrate, a contact pad, a passivation layer, a bump, and a seeding layer is provided. The semiconductor substrate has an active surface. The contact pad is disposed on the active surface. The passivation layer is disposed on the active surface and exposes a central part of the contact pad. The seeding layer is disposed on the exposed central part of the contact pad. The bump has a top surface, a bottom surface opposite to the top surface, and a side surface connecting the top surface and the bottom surface. The bump is disposed on the seeding layer. The bump is placed in contact with the seeding layer by the bottom surface and by part of the side surface. The present invention also discloses a bump preparing method.

Owner:HIMAX TECH LTD

Display device contact hole forming method

ActiveCN102683266ARemove defects with poor uniformity controlAvoid over etchingSemiconductor/solid-state device manufacturingDisplay devicePhotoresist

The embodiment of the invention discloses a display device contact hole forming method which includes the following steps of: providing a substrate on which a first metal layer, an insulating layer, a second metal layer, a passivated layer and a patterning photoresist layer are sequentially formed; performing a first etching step to remove the entire thickness of the passivated layer and the partial thickness of the insulating layer above the first metal layer, and at the same time to remove the partial thickness of the corresponding halftone photoresist above the second metal layer; performing an ashing step to totally remove the corresponding halftone photoresist above the second metal layer; and performing a second etching step to remove the insulating layer retained in a deep hole above the first metal layer so as to expose the surface of the first metal layer and at the same time to remove the passivated layer retained in a shallow hole above the second metal layer so as to expose the surface of the second metal layer. The scheme of the invention can overcome the disadvantage that the uniformity of the remnant film of the photoresist is difficult to control, and the etching processes are optimized; the process of controlling the etching speed is simple; and over etching of the metal wirings can be avoided to the largest extent.

Owner:SHANGHAI AVIC OPTOELECTRONICS

Preparing method of triaxial anisotropic magnetoresistor

ActiveCN104505460AAvoid over etchingGuaranteed performanceGalvano-magnetic device manufacture/treatmentMagnetic reluctanceMaterials science

The invention provides a preparing method of a triaxial anisotropic magnetoresistor. The preparing method includes: in first etching, etching only magnetic material on the bottom surface of a trench; in second etching, etching the magnetic material on the surface of a substrate to form planar magnetic resistance and vertical resistance spaced, thereby forming the triaxial anisotropic magnetoresistor. The bottom surface of the trench and the surface of the substrate are never etched at the same time, and thus, the surface of the substrate being over-etched due to difference of etching rates is avoided. Therefore, separate etching of the magnetic material on the trench and that on the surface of the substrate leads to no over-etching and ensures performance of the triaxial anisotropic magnetoresistor.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

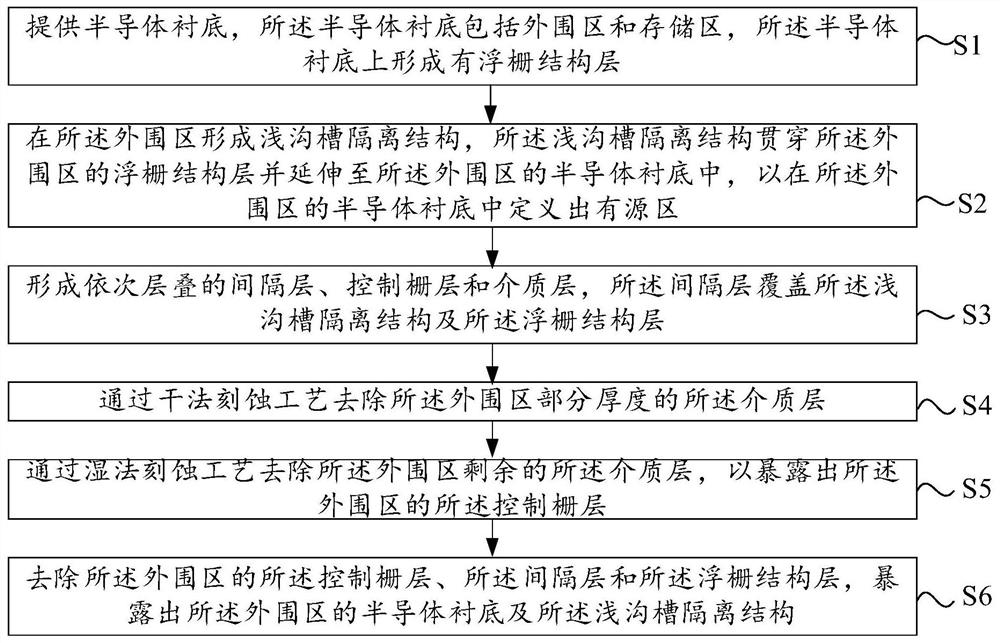

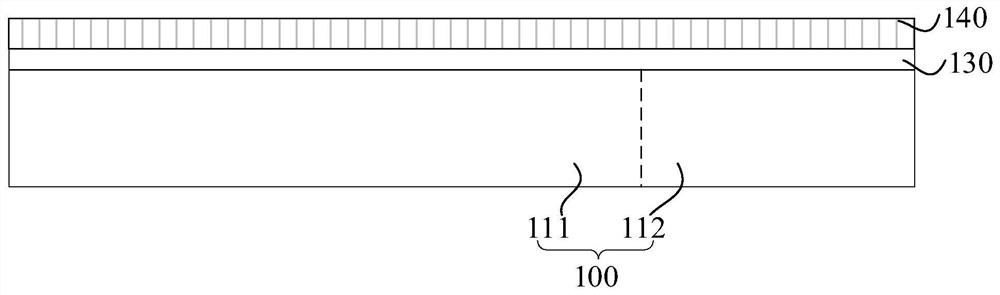

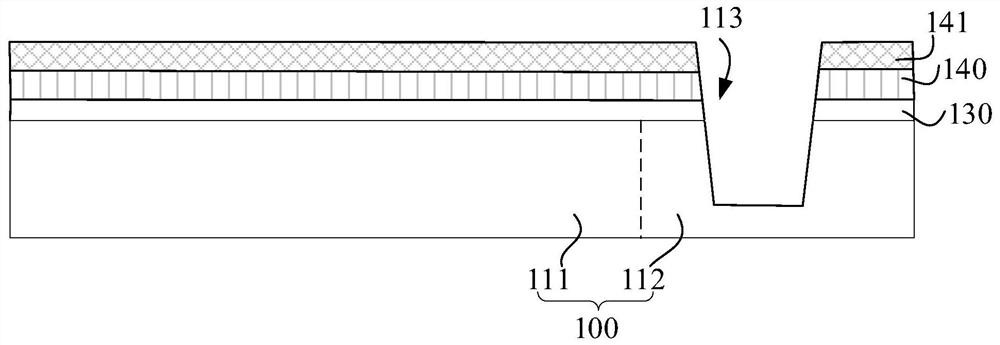

Manufacturing method of semiconductor device

PendingCN112382635AIncrease the amount of etchingAvoid over etchingSolid-state devicesSemiconductor devicesDevice materialEngineering

The invention provides a manufacturing method of a semiconductor device, which comprises the following steps of: removing a dielectric layer with partial thickness in a peripheral region through a dryetching process, so that over etching of the dielectric layer can be avoided, and pits are prevented from being formed in a control gate layer; then removing the residual dielectric layer in the peripheral region through a wet etching process, removing pollutants generated in dry etching in the previous step, avoiding the residual of the dielectric layer, and then removing a control gate layer, aspacer layer and a floating gate structure layer in the peripheral region. Since pits are prevented from being formed in the control gate layer, when the control gate layer, the spacer layer and thefloating gate structure layer in the peripheral region are removed, pits can be prevented from being formed in the semiconductor substrate in the active region, and the problems of defects caused by the pits and pollution to a semiconductor device are solved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP