Novel wafer level tin solder micro bump manufacturing method

A fabrication method and micro-bump technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as excessive etching and affect the reliability of micro-bumps, avoid excessive etching, reduce Interfacial connection strength, the effect of avoiding delamination failure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] In order to understand the technical content of the present invention more clearly, the following embodiments are given in detail, and the above-mentioned features and advantages of the present invention are described in detail in conjunction with the accompanying drawings. Its purpose is only to better understand the content of the present invention but not to limit the protection scope of the present invention. The semiconductor packaging structure of the embodiment of the present invention can be used in the preparation of micro-bumps. But its application is not limited to this.

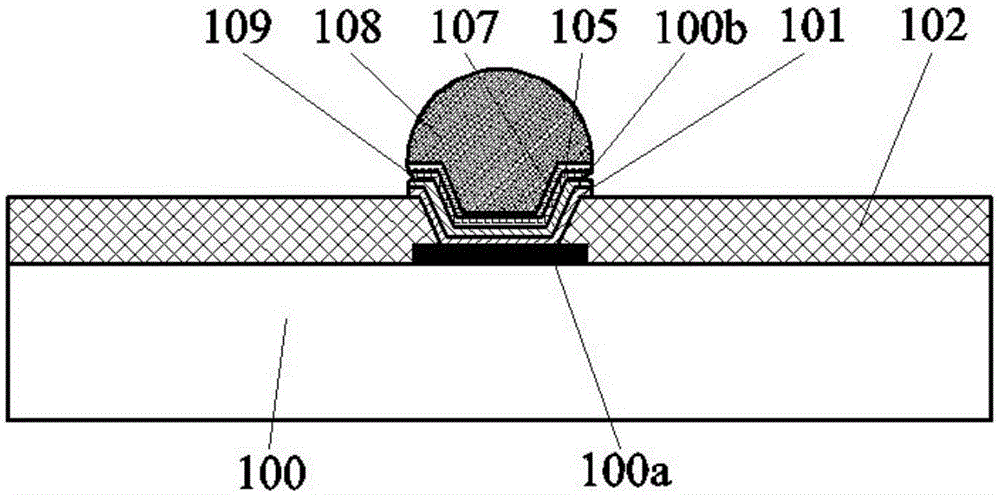

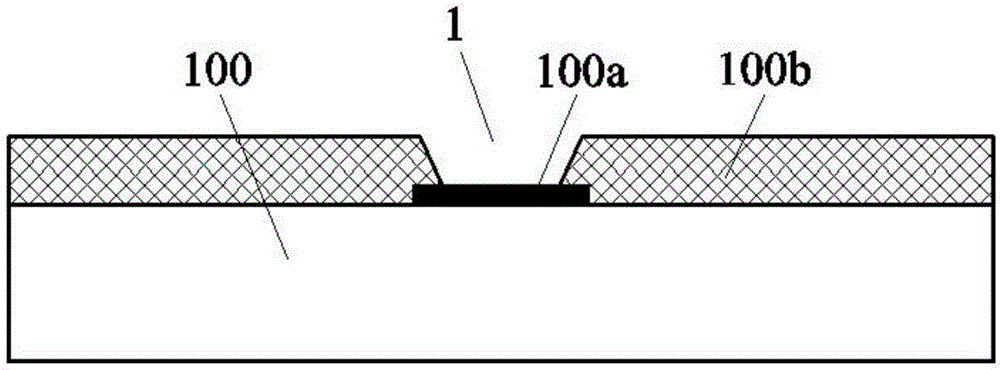

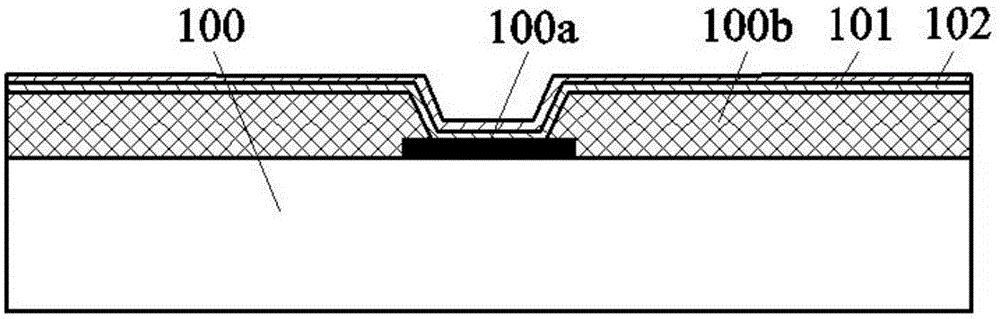

[0039] see Figure 2 to Figure 10 , the manufacturing process of solder micro-bumps of the present invention is as follows:

[0040] An IC wafer (100) is provided, the front side of the wafer has a passivation layer (100b) and several pads (100a), the passivation layer (100b) is formed with several first openings (1) exposing the pads ;

[0041] Such as image 3 As shown, an UBM titani...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More