Semiconductor device and method of bump formation

A manufacturing method and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as inability to compress, reduce the conductivity of chips and carriers, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

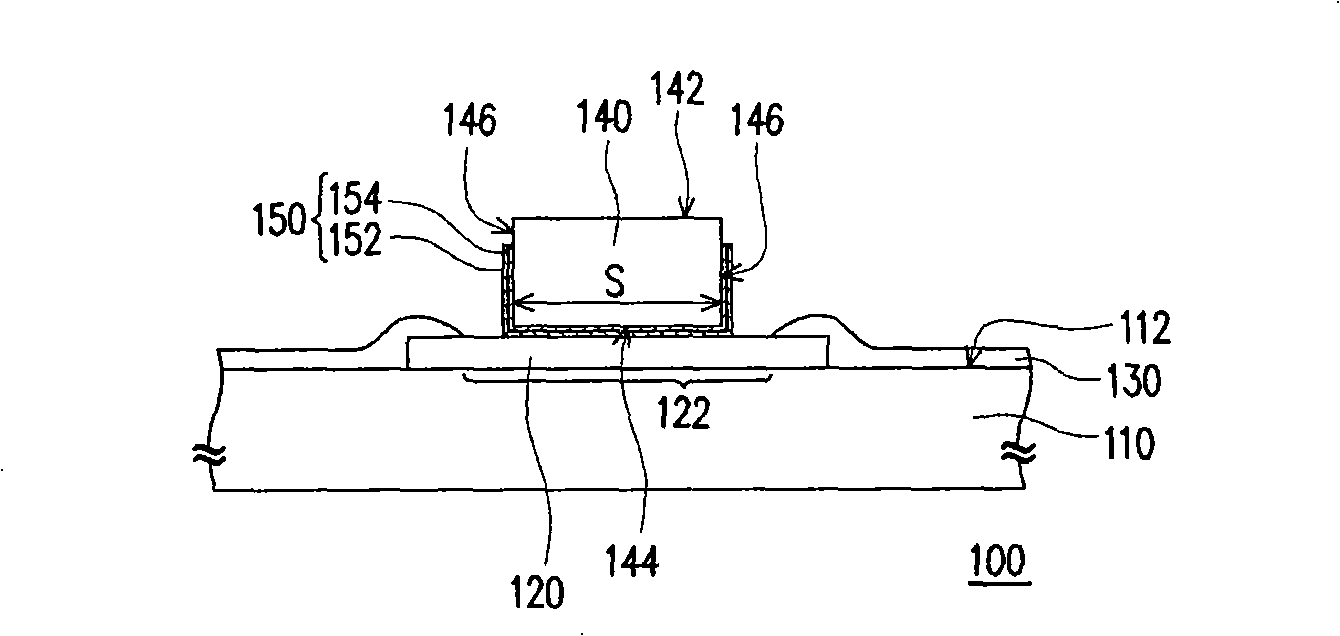

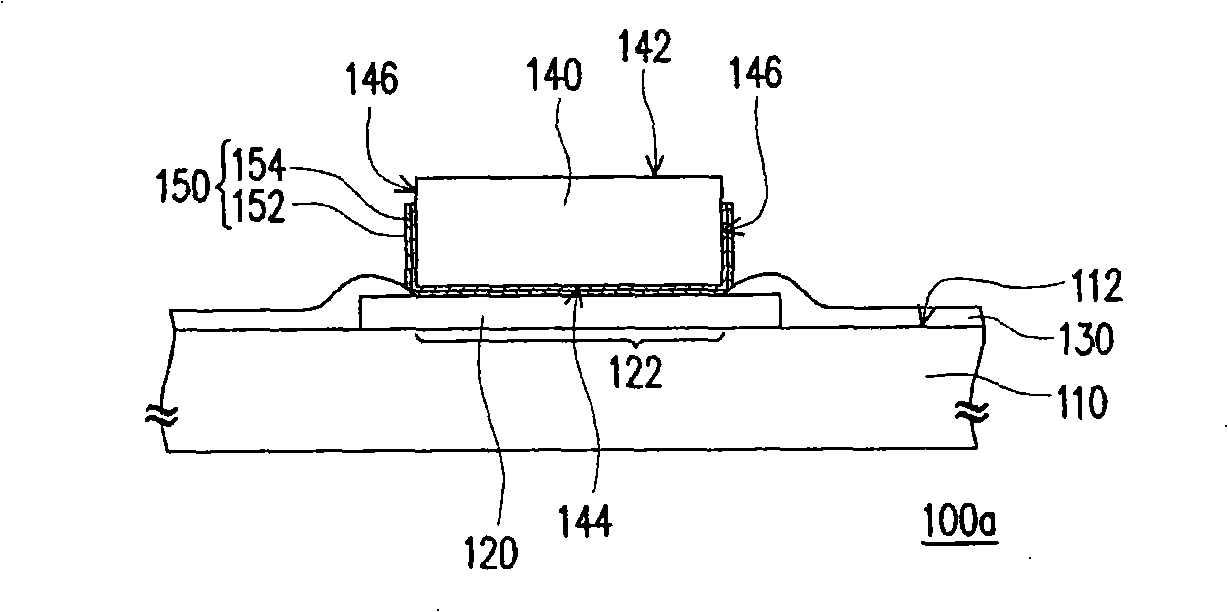

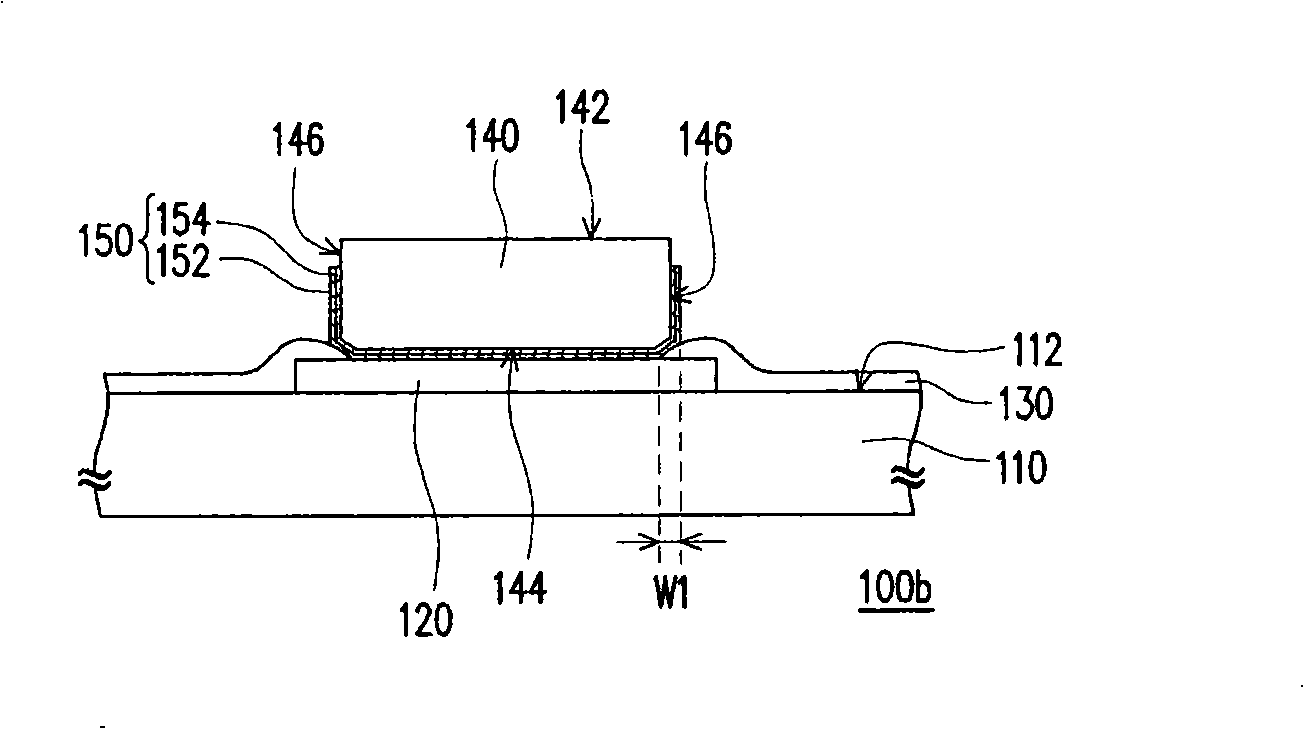

[0042] figure 1 is a schematic cross-sectional view of a semiconductor device according to an embodiment of the present invention. Please refer to figure 1 , the semiconductor device 100 of this embodiment includes a semiconductor substrate 110 , a plurality of pads 120 , a passivation layer 130 , a plurality of bumps 140 and a plurality of seed layers 150 . However, in figure 1 A pad 120 , a bump 140 and a seed layer 150 are represented in the figure. The semiconductor substrate 110 has an active surface 112 . Each pad 120 is disposed on the active surface 112 and is, for example, a metal pad. In the present embodiment, the semiconductor substrate 110 is, for example, a chip, which includes an integrated circuit electrically connected to the pads 120 . The passivation layer 130 is disposed on the active surface 112 and exposes the central portion 122 of each pad 120 . The protective layer is, for example, an insulating layer.

[0043] The seed layer 150 is disposed on ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More