Double gate manufactured with locos techniques

一种栅极、厚氧化层的技术,应用在半导体功率器件领域,达到消除回侵现象、改进灵活性、减少Ciss的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

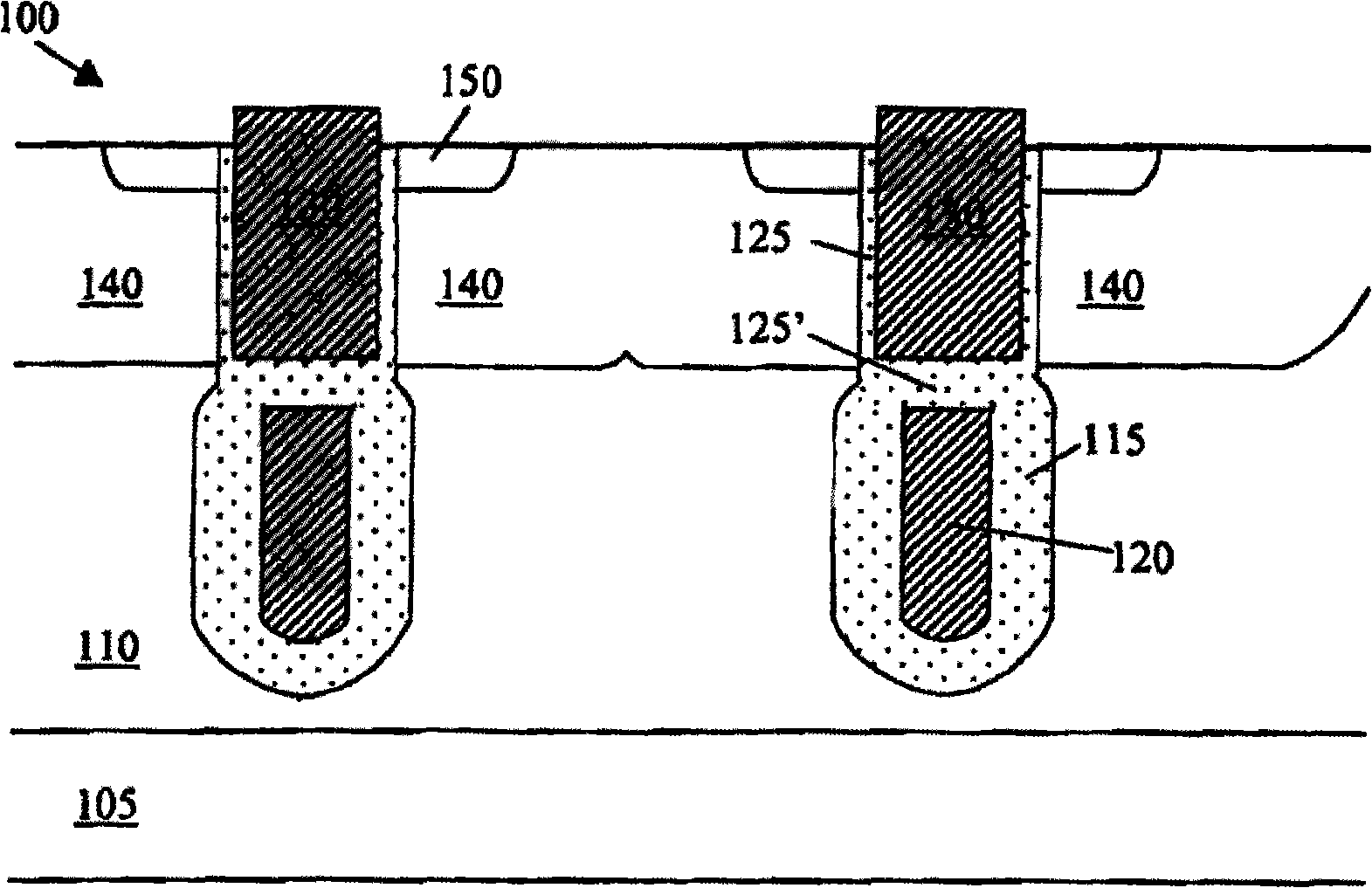

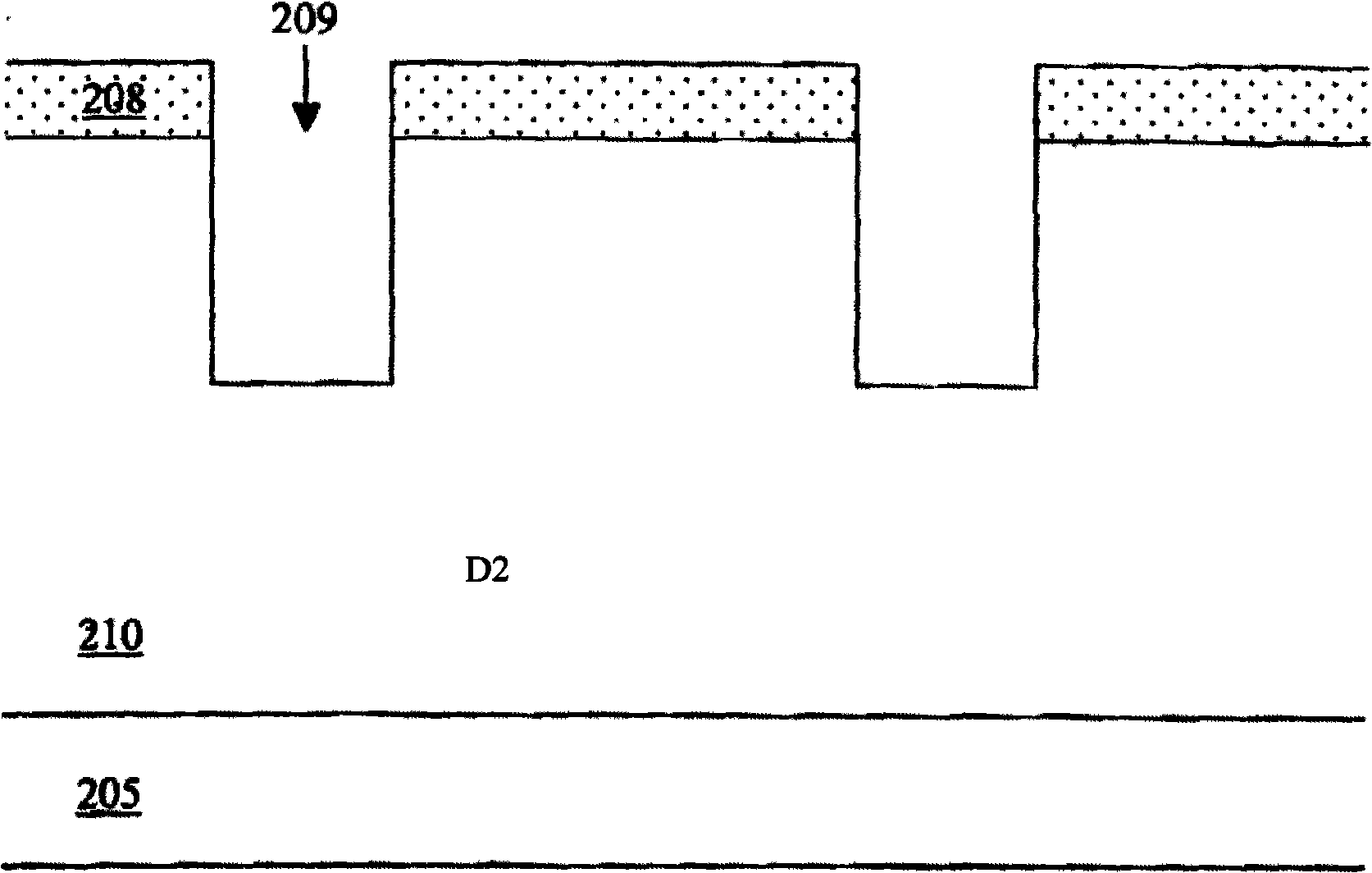

[0032] The following will refer to the attached figure 2 ~ Accompanying drawing 3 describes the present invention in detail.

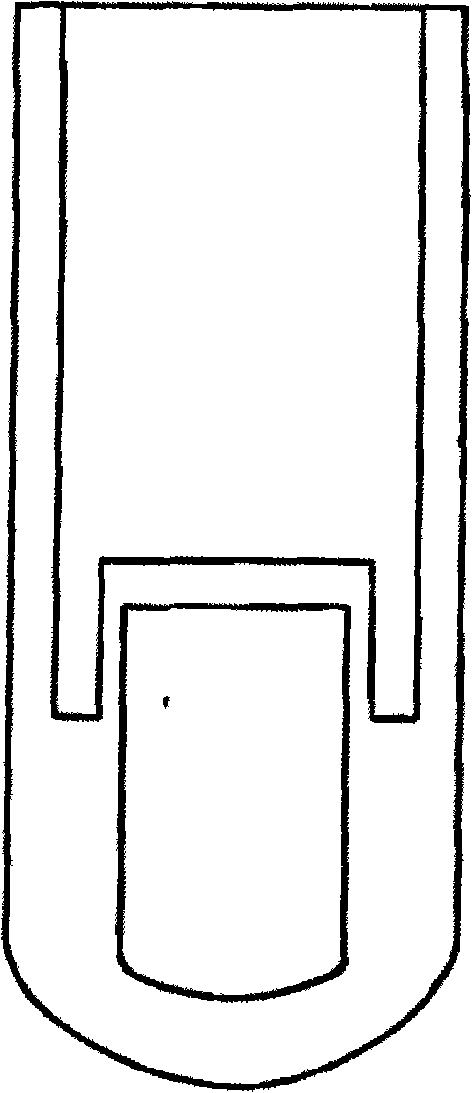

[0033] refer to figure 2 Shown is a schematic cross-sectional view of the trench MOSFET device 100 of the present invention. Trench MOSFET device 100 is supported on substrate 105 on which epitaxial layer 110 is formed. Trench MOSFET device 100 includes a bottom gate segment 120 below a top trench gate segment 130 , the bottom of which is filled with polysilicon. The polysilicon-filled bottom gate segment 120 is shielded and insulated from the top gate polysilicon segment 130 by an insulating oxide layer 125' disposed between the top and bottom segments. The bottom channel segment is also insulated from the drain disposed below 105 by an insulating layer 115 surrounding the bottom surface of the trench gate. The top trench gate segment 130 is also polysilicon filled at the top of the trench surrounded by a gate insulating layer 125 covering ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More