Method for forming CMOS transistor

A transistor and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., to improve performance, reduce etching time, and improve efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

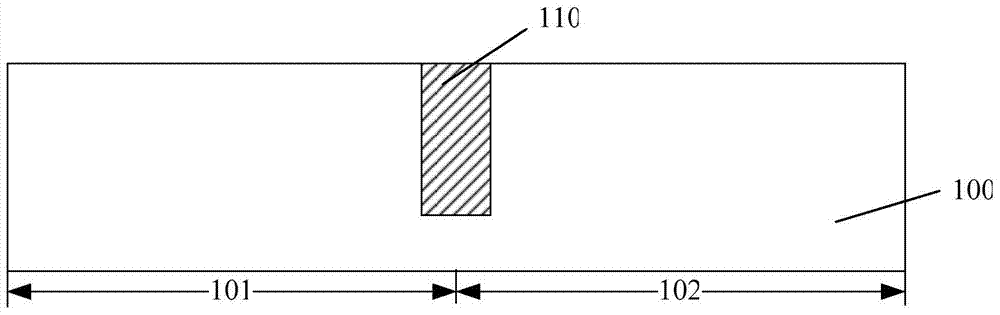

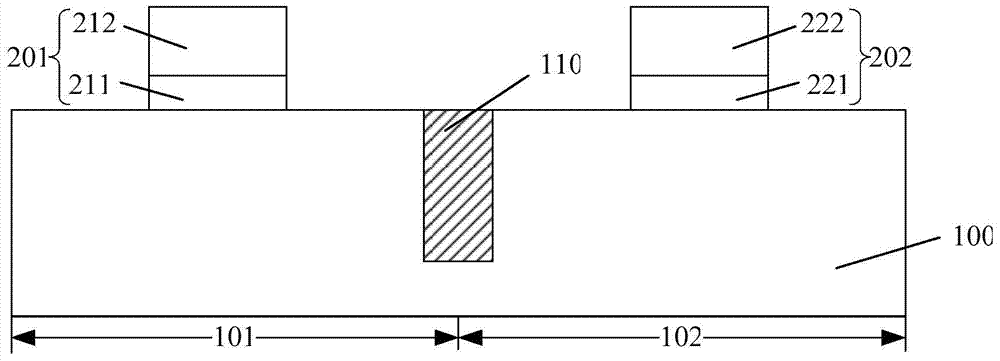

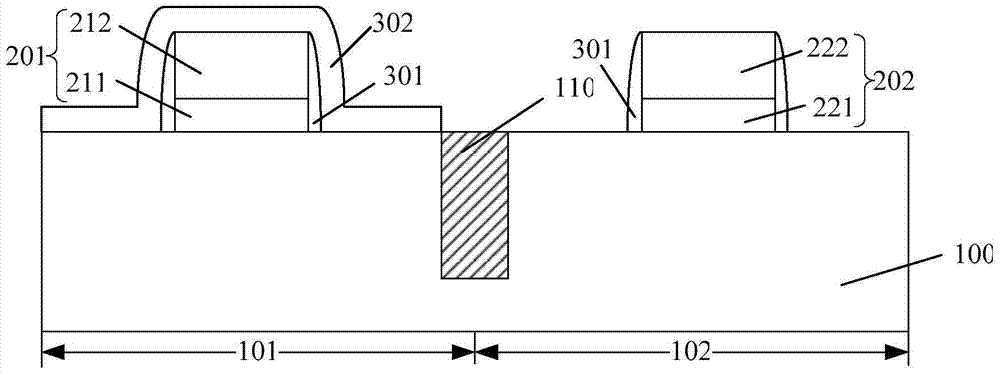

[0029] As mentioned in the background art, the performance of the CMOS transistors formed in the prior art still needs to be further improved.

[0030] In the process of forming a CMOS transistor using the "gate-last" process, in order to improve the performance of the PMOS transistor in the CMOS transistor, it is necessary to form grooves in the source and drain regions of the semiconductor substrate on both sides of the dummy gate structure on the PMOS region, and then form grooves in the PMOS region. The groove is filled with SiGe as the source and drain; before the groove is formed in the source and drain regions of the PMOS region, a hard mask layer needs to be formed on the surface of the NMOS region to protect the groove during the formation of the groove. NMOS region, and subsequently retain the part of the hard mask layer on the top and both sides of the dummy gate structure of the NMOS region when forming the source and drain regions of the NMOS region, as a mask when...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More