Patents

Literature

165results about How to "Increase saturation current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

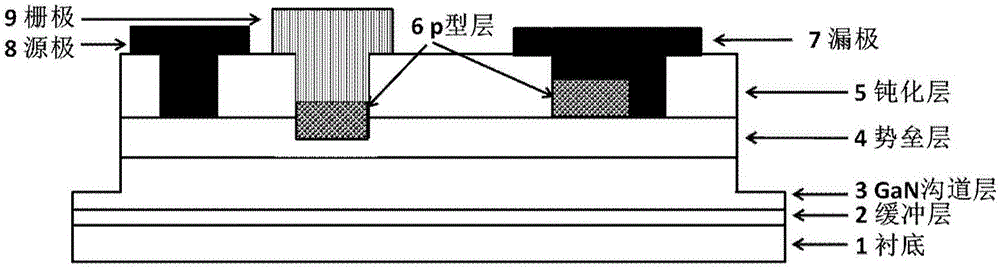

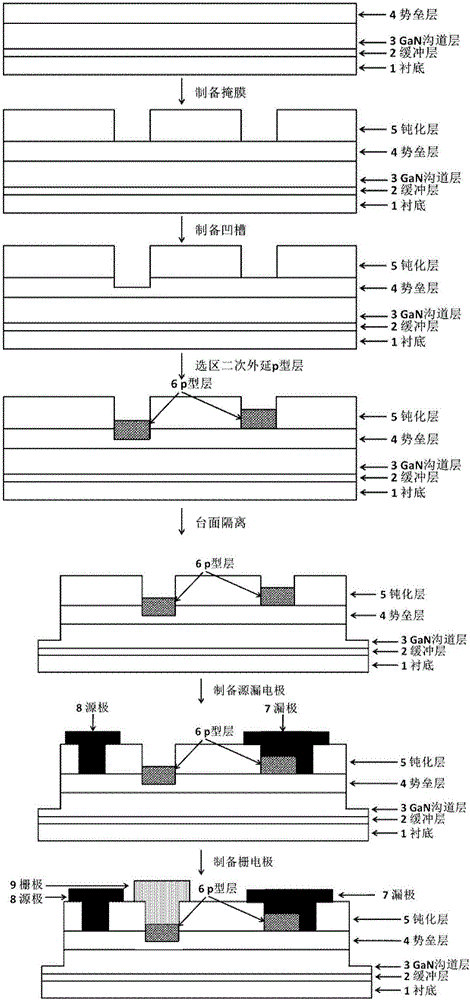

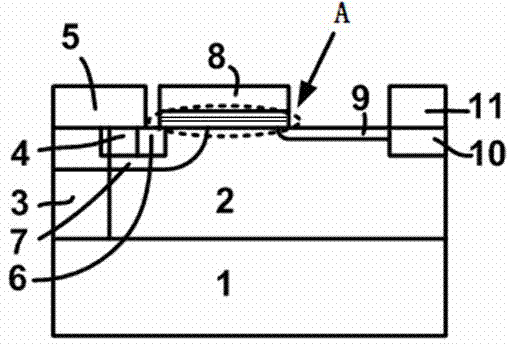

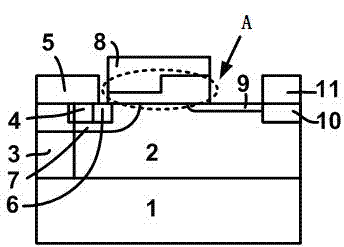

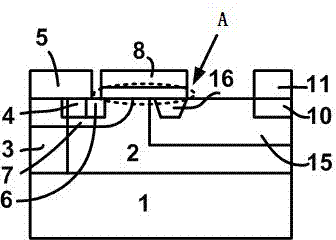

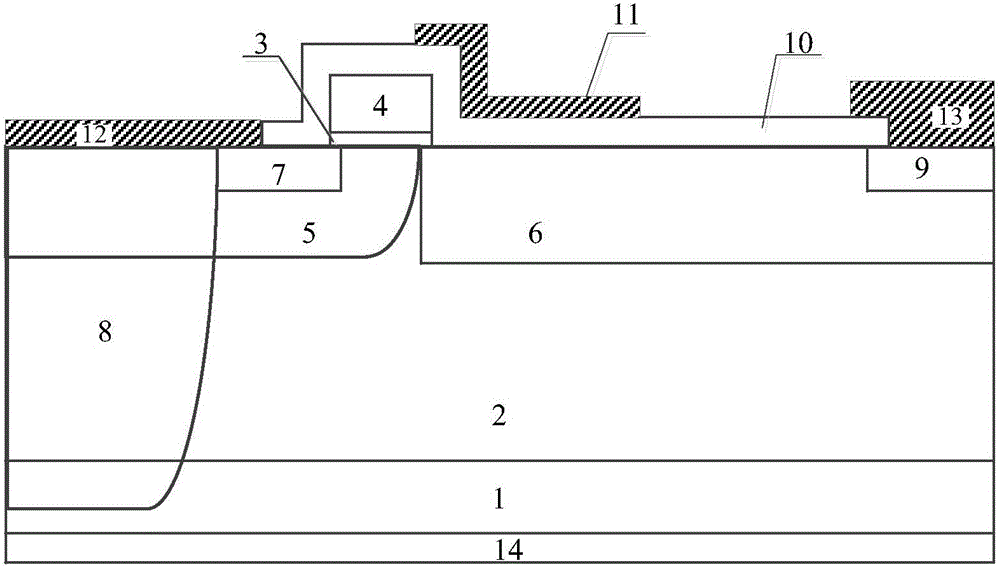

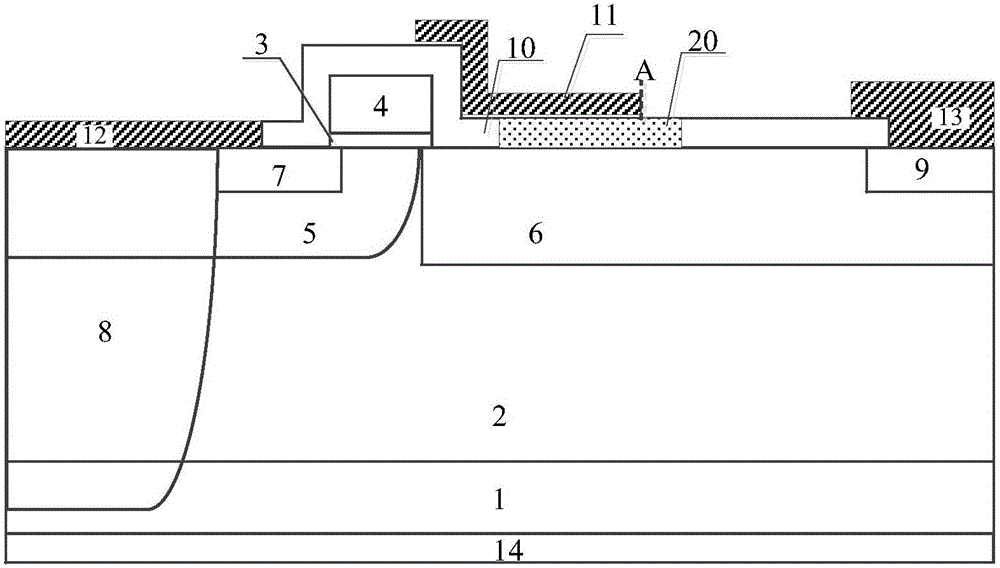

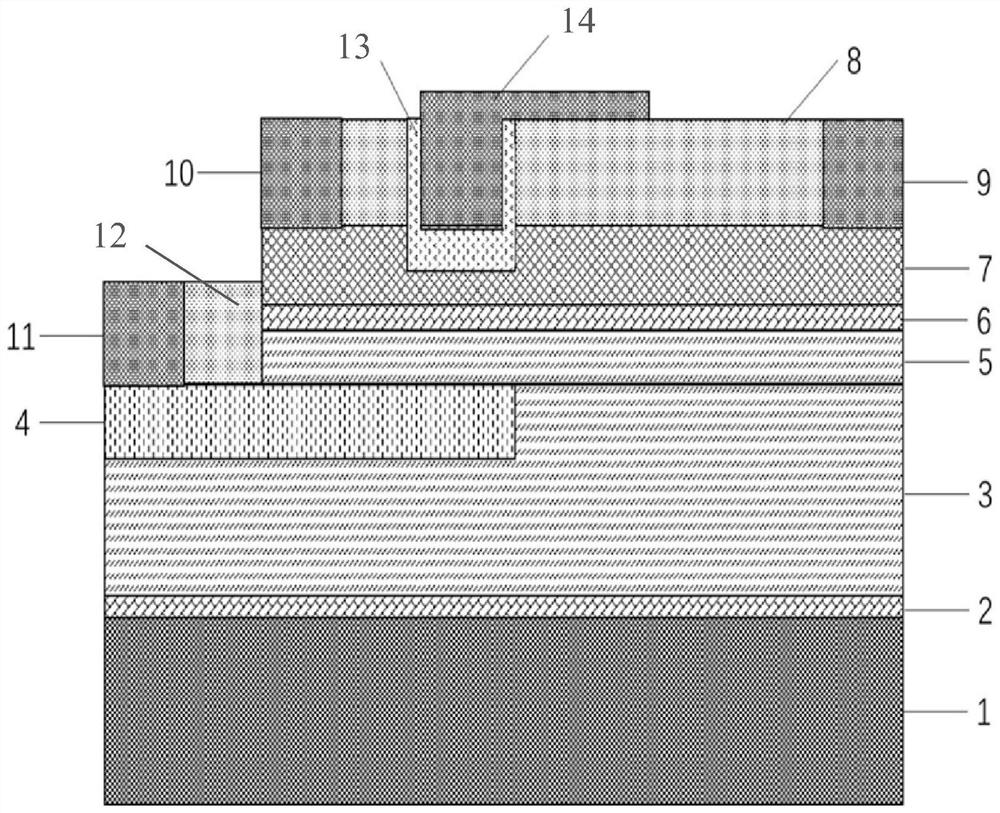

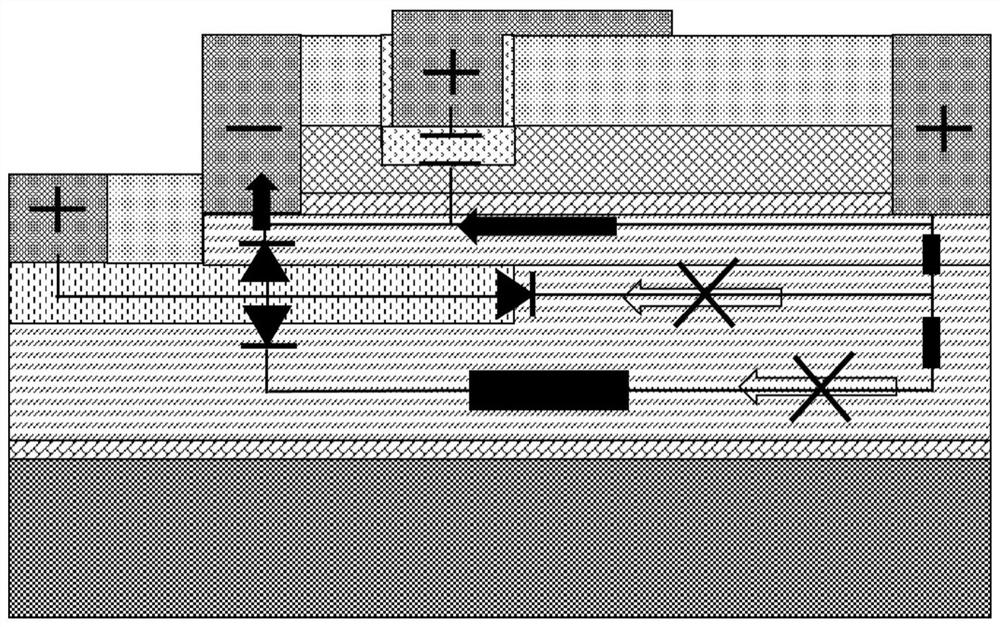

Enhanced-mode high electron mobility transistor, preparation method thereof, and semiconductor device

InactiveCN105720097ARaise the threshold voltageImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowSemiconductor

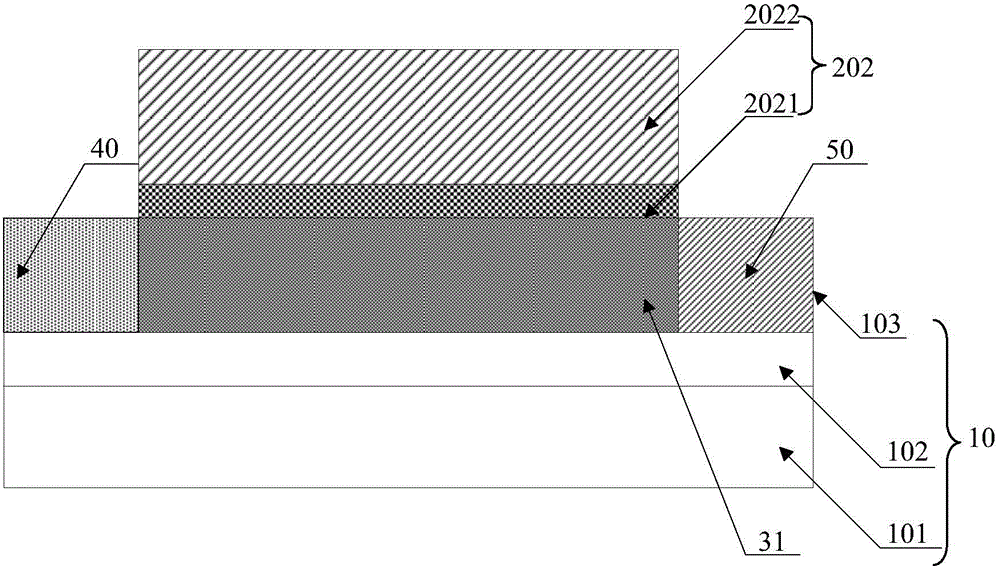

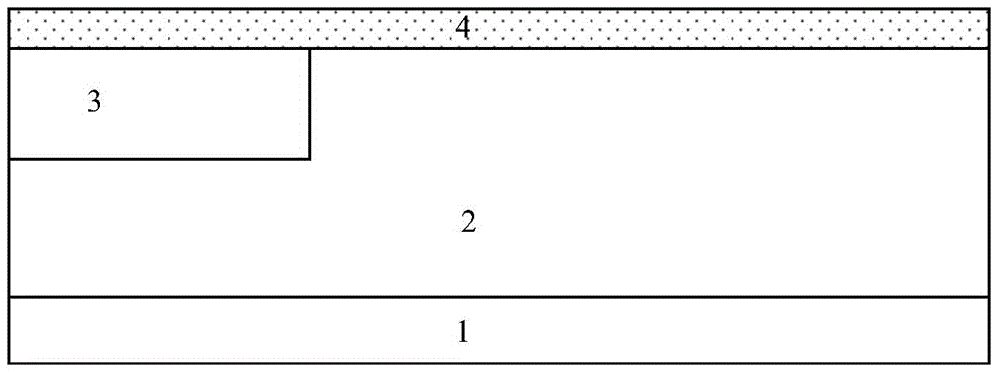

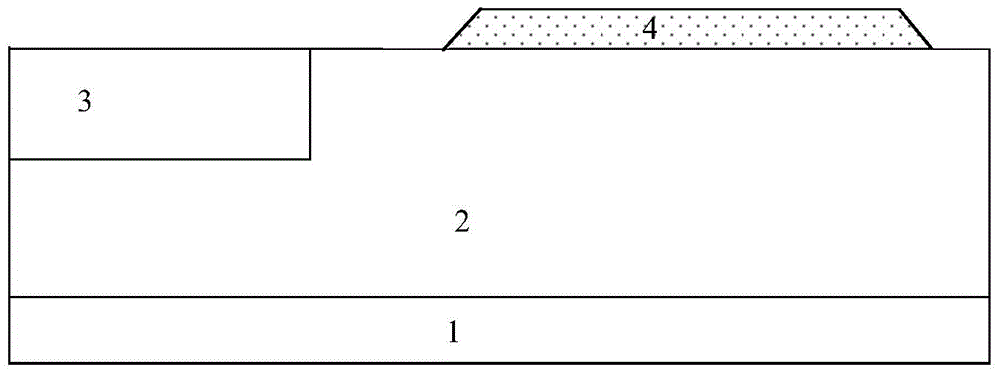

The present invention provides an enhanced-mode high electron mobility transistor. The transistor includes a grid electrode, a source electrode, a drain electrode, a p type layer, a barrier layer, and a passivation layer arranged on the barrier layer. A part region on the passivation layer is provided with a secondary epitaxy figure formed by etching to the upper surface of the barrier layer. The barrier layer also includes a trench formed by further etching to the inner side of the barrier layer in a local region of the figure. The p type layer that is grown through secondary epitaxy is in the figure and the trench. The p type layer in the trench is contacted with a grid electrode metal on the p type layer in the trench. The p type layer that is not in the trench is contacted with a drain electrode metal on the p type layer that is not in the trench. The present invention also provides a preparation method of the transistor and a semiconductor device including the transistor. According to the transistor, due to a trench grid and the p type layer grown through secondary epitaxy in a selected region, a threshold voltage of the device is increased; and a part of the barrier layer is etched, so that a saturated current of the device is greater than the current of the trench grid type high electron mobility transistor (HEMT). In addition, the p type layer is also grown in a selected region of the drain electrode metal, so that the turn-off effect of the device is improved.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

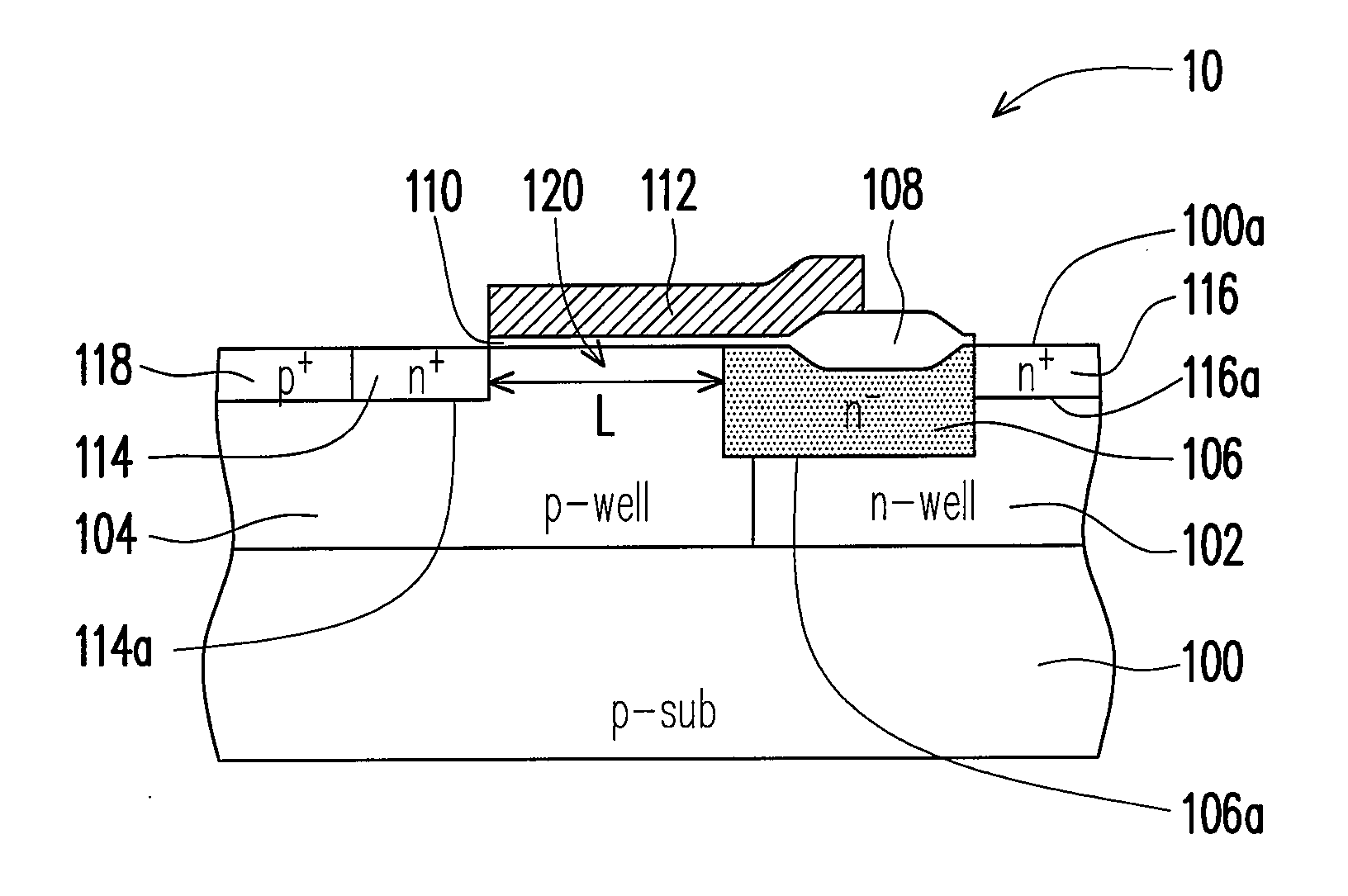

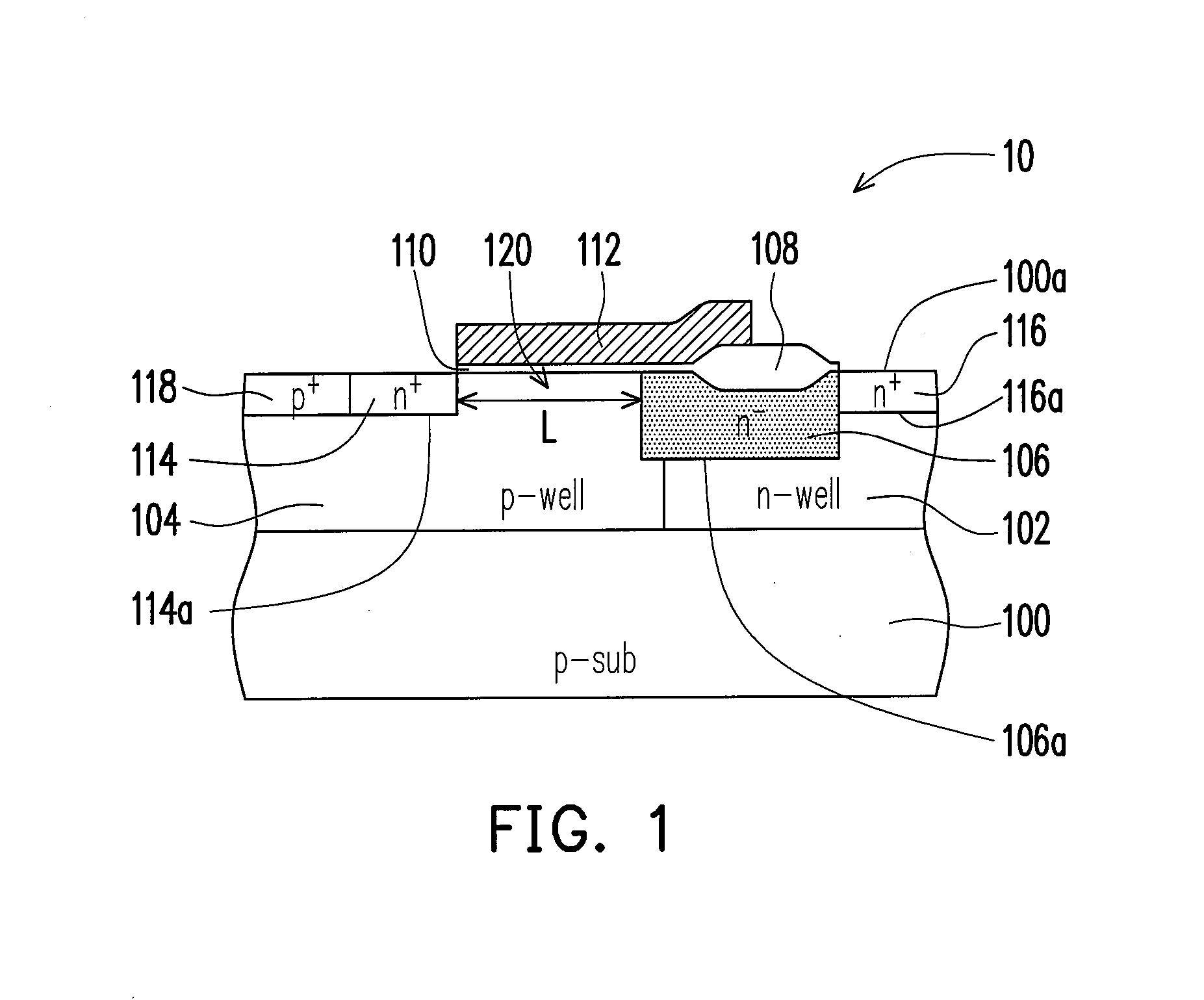

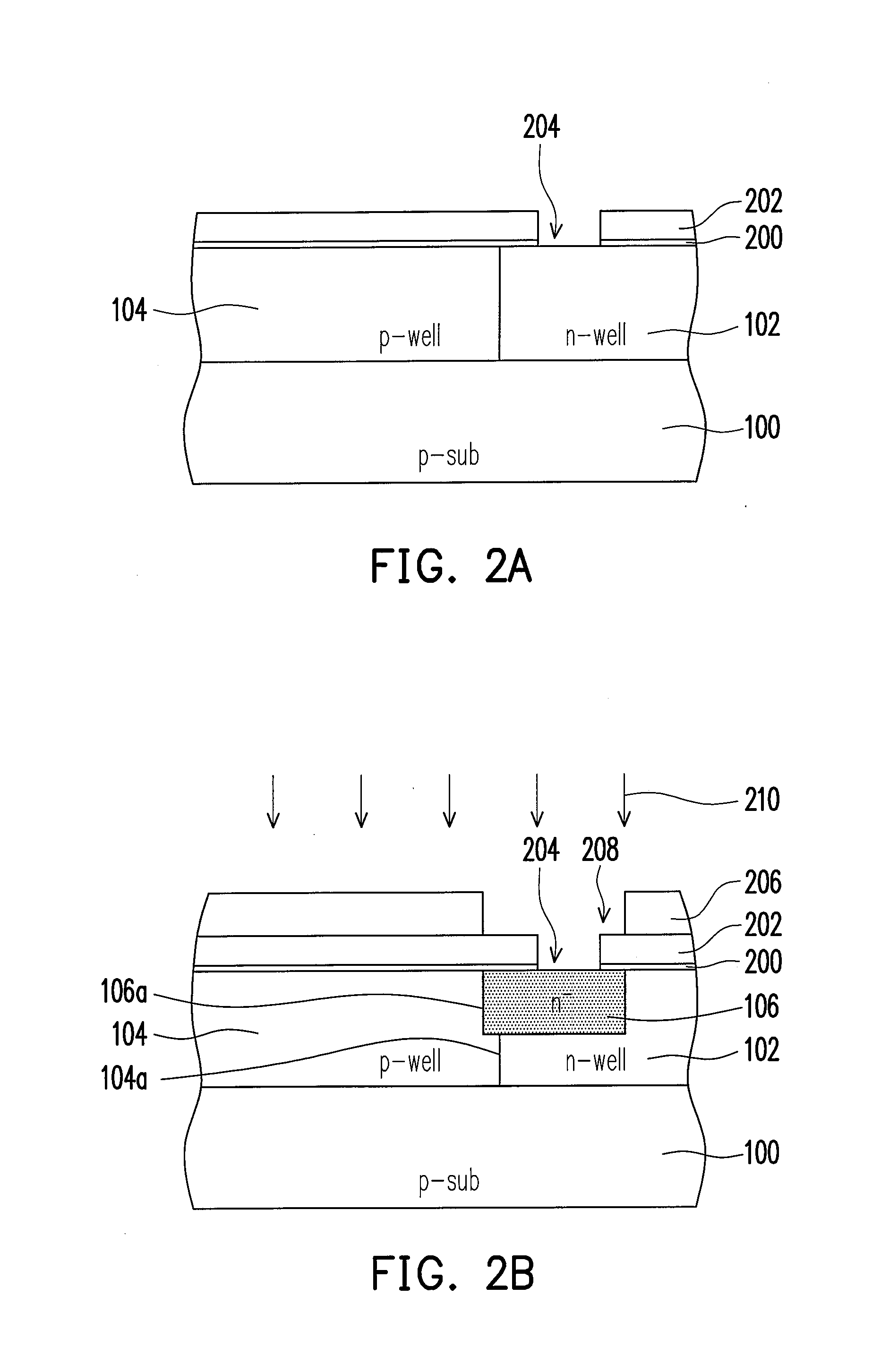

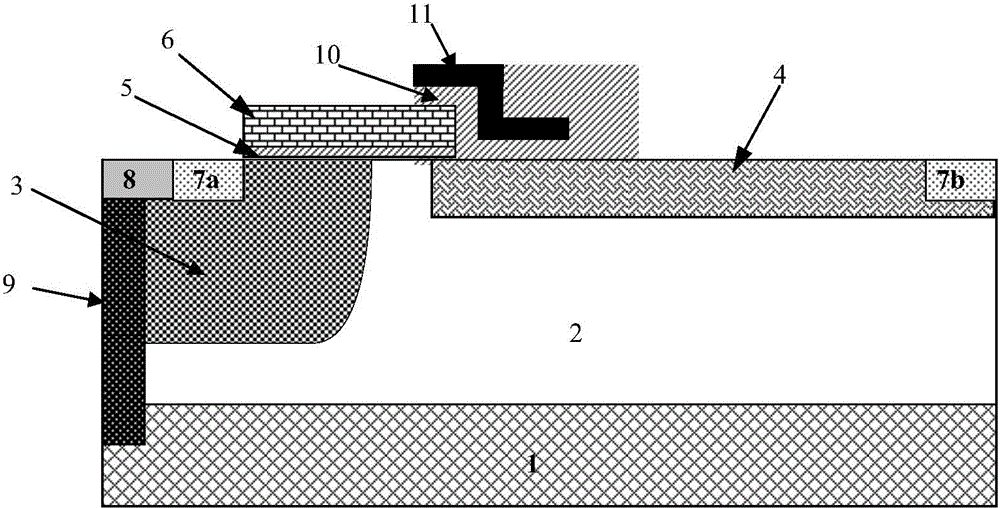

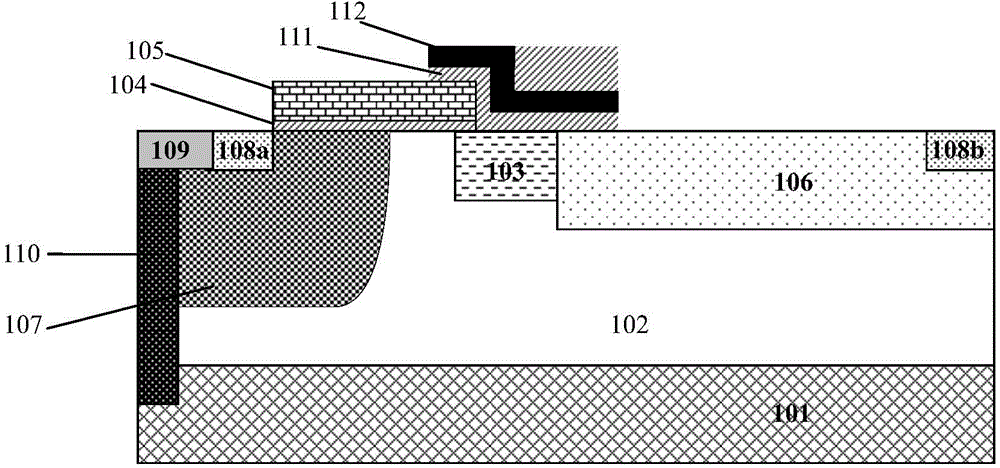

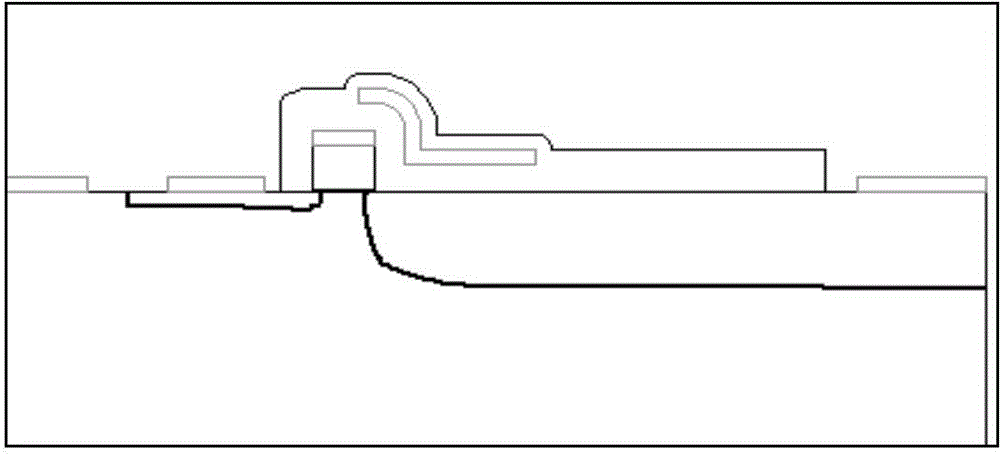

Low on-resistance lateral double-diffused mos device and method of fabricating the same

ActiveUS20080315308A1Lower on-state resistanceIncrease saturation currentSemiconductor/solid-state device detailsSolid-state devicesEngineeringField oxide

A lateral-double diffused MOS device is provided. The device includes: a first well having a first conductive type and a second well having a second conductive type disposed in a substrate and adjacent to each other; a drain and a source regions having the first conductive type disposed in the first and the second wells, respectively; a field oxide layer (FOX) disposed on the first well between the source and the drain regions; a gate conductive layer disposed over the second well between the source and the drain regions extending to the FOX; a gate dielectric layer between the substrate and the gate conductive layer; a doped region having the first conductive type in the first well below a portion of the gate conductive layer and the FOX connecting to the drain region. A channel region is defined in the second well between the doped region and the source region.

Owner:MACRONIX INT CO LTD

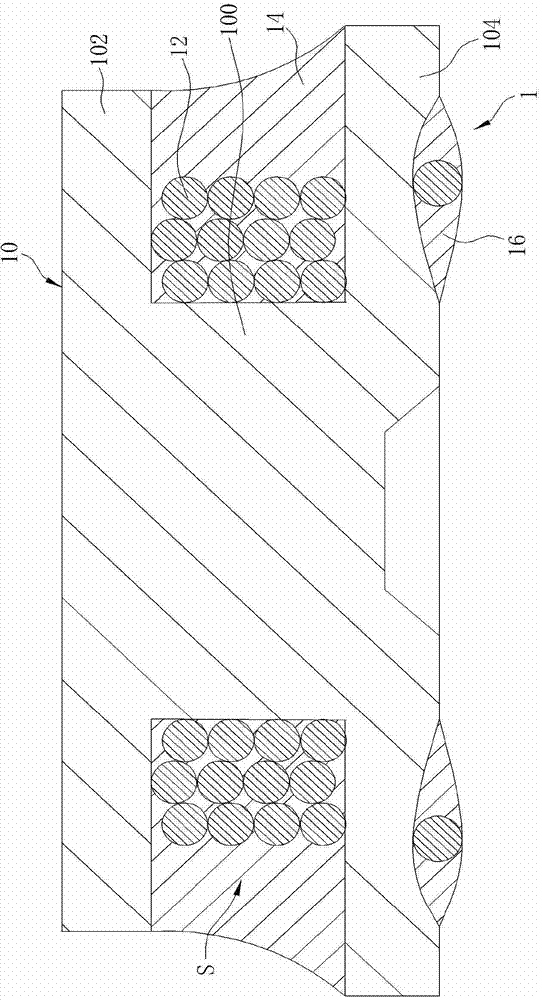

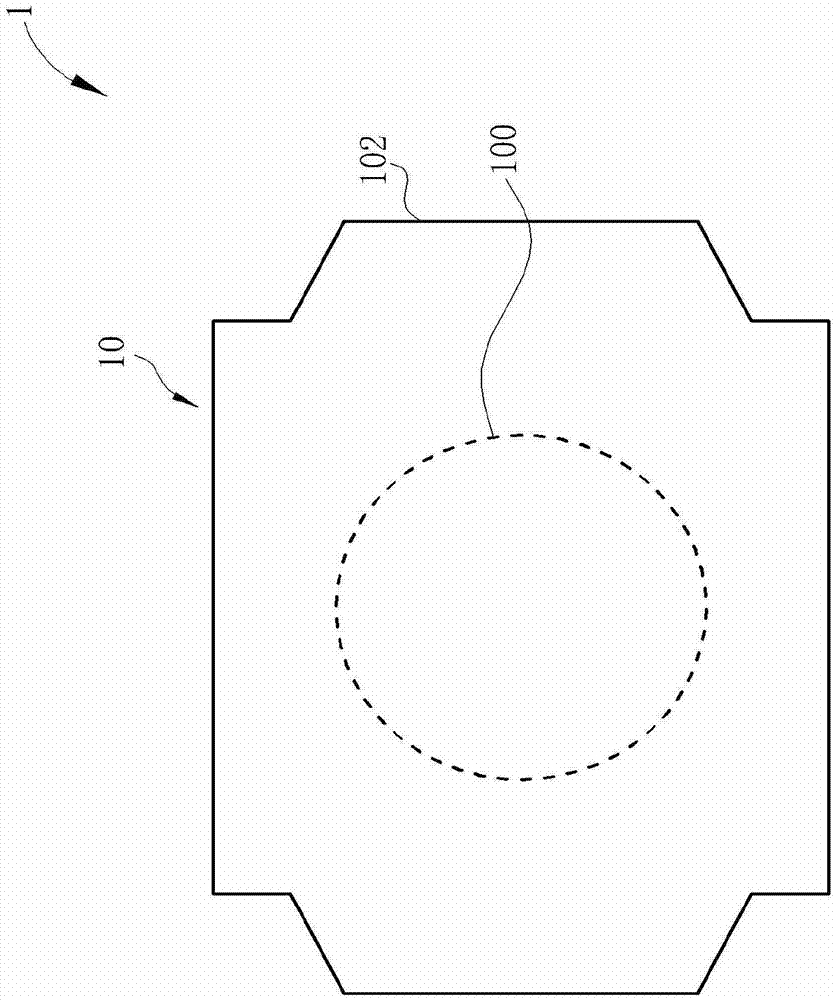

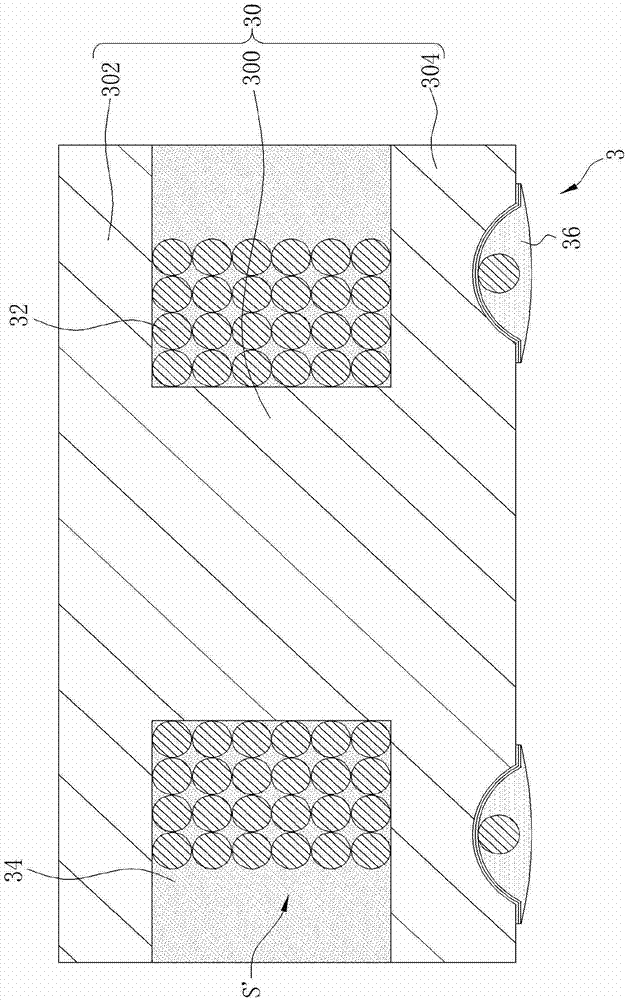

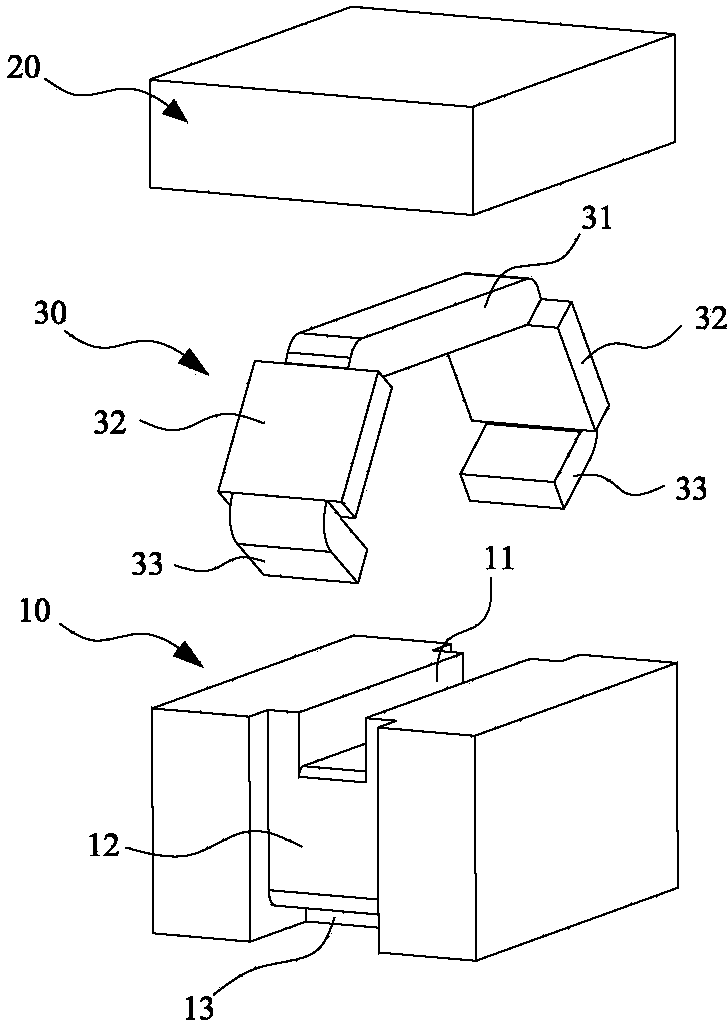

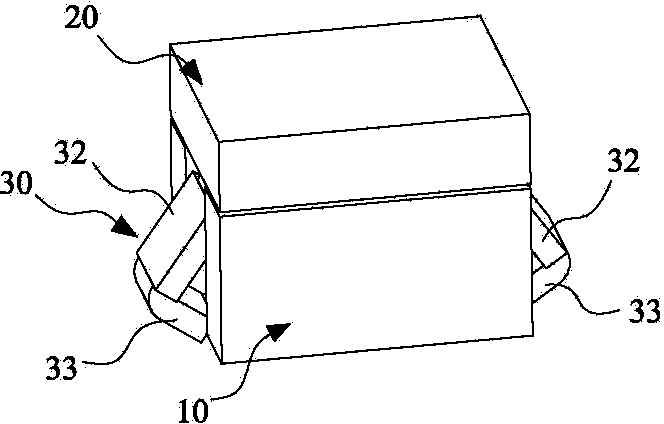

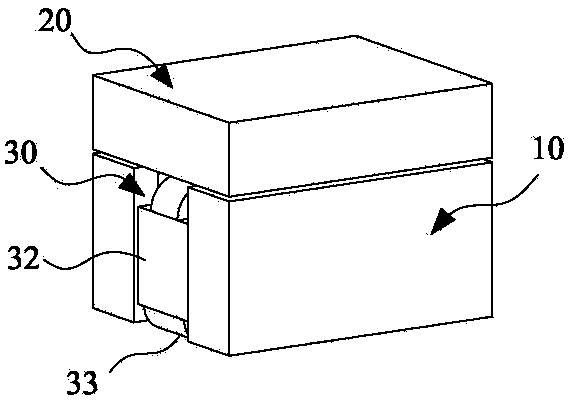

Choke

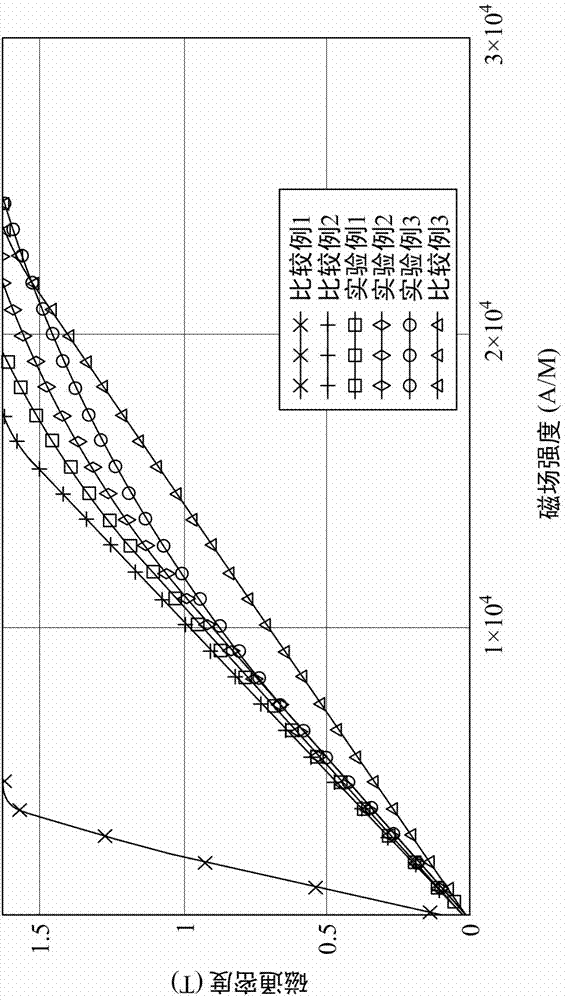

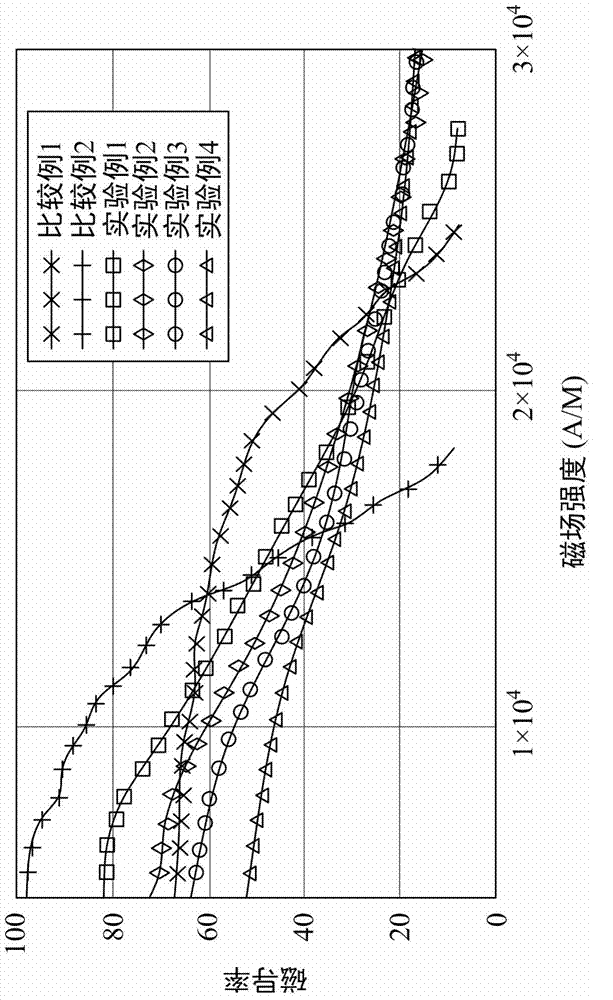

ActiveCN103177850AIncrease saturation currentImprove featuresTransformers/inductances coils/windings/connectionsTransformers/inductances magnetic coresPower flowEngineering

A choke includes a single-piece core entirely made of a same material, the single-piece core having two boards and a pillar located between the two boards, a winding space being located among the two boards and the pillar, wherein the pillar has a non-circular and non-rectangular cross section along a direction substantially perpendicular to an axial direction of the pillar, the cross section of the pillar has a first axis and a second axis intersecting with each other at a center of the cross section of the pillar and are substantially perpendicular with each other, the first axis is longer than the second axis, and the cross section of the pillar is substantially symmetrical to both of the first axis and the second axis. The cross section area of the pillar can be effectively increased. Therefore, the saturation current of the choke can be effectively enhanced.

Owner:CYNTEC

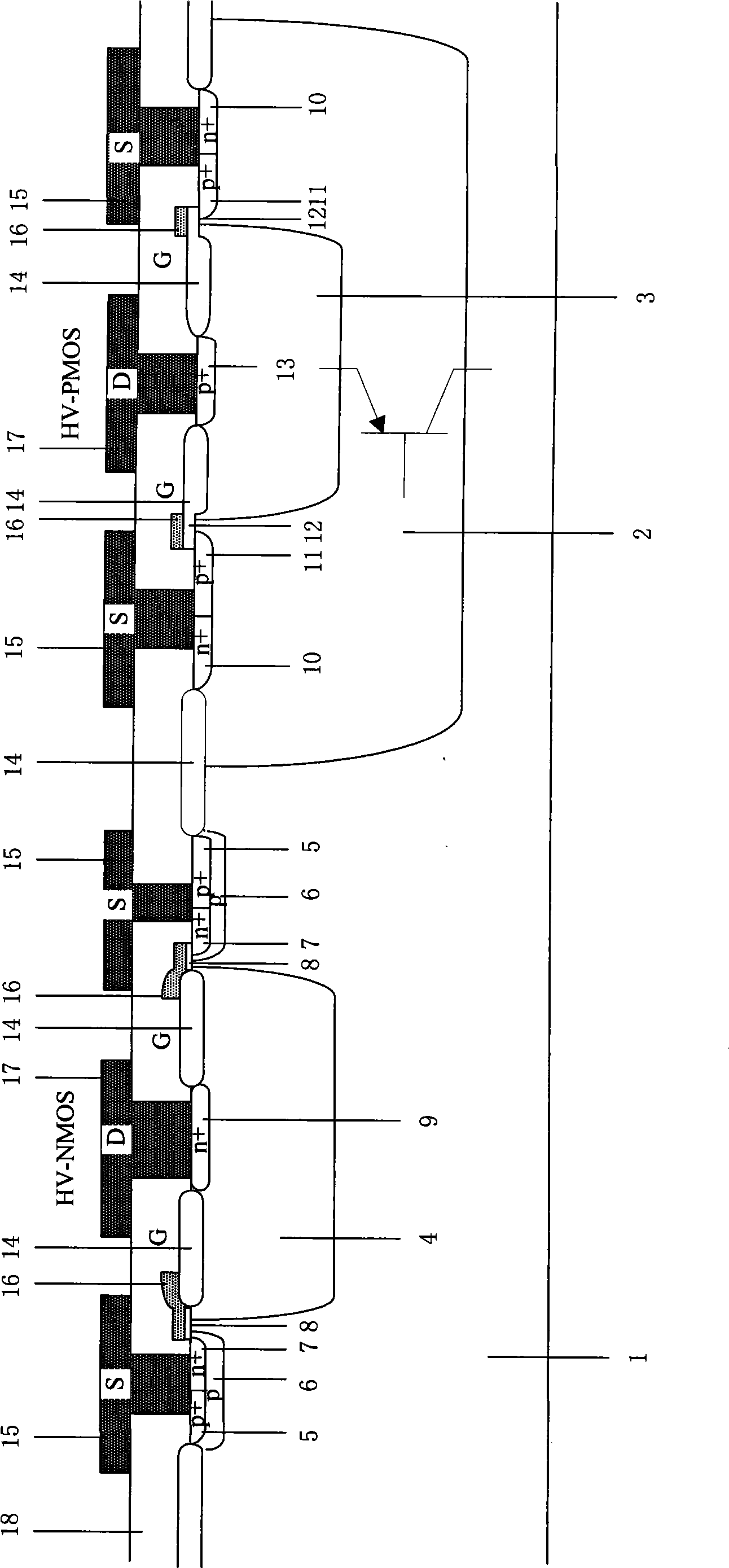

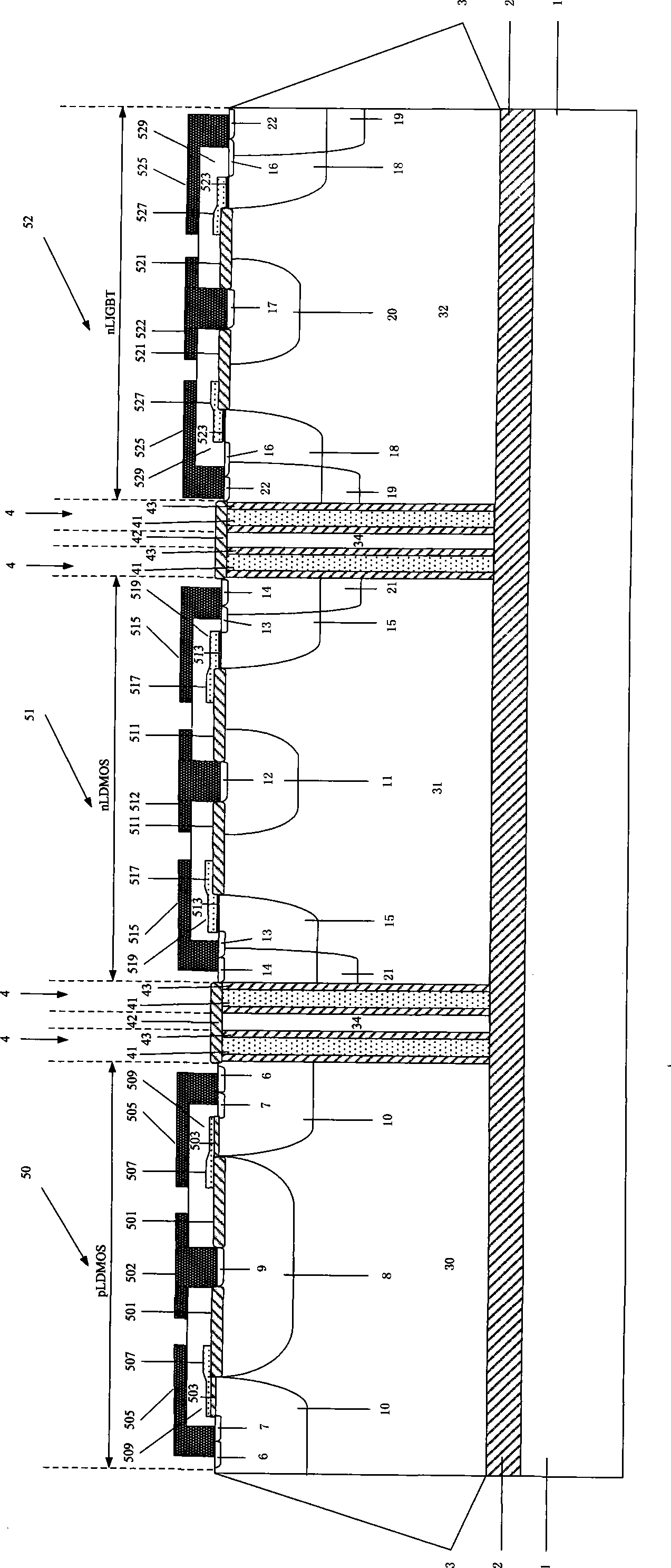

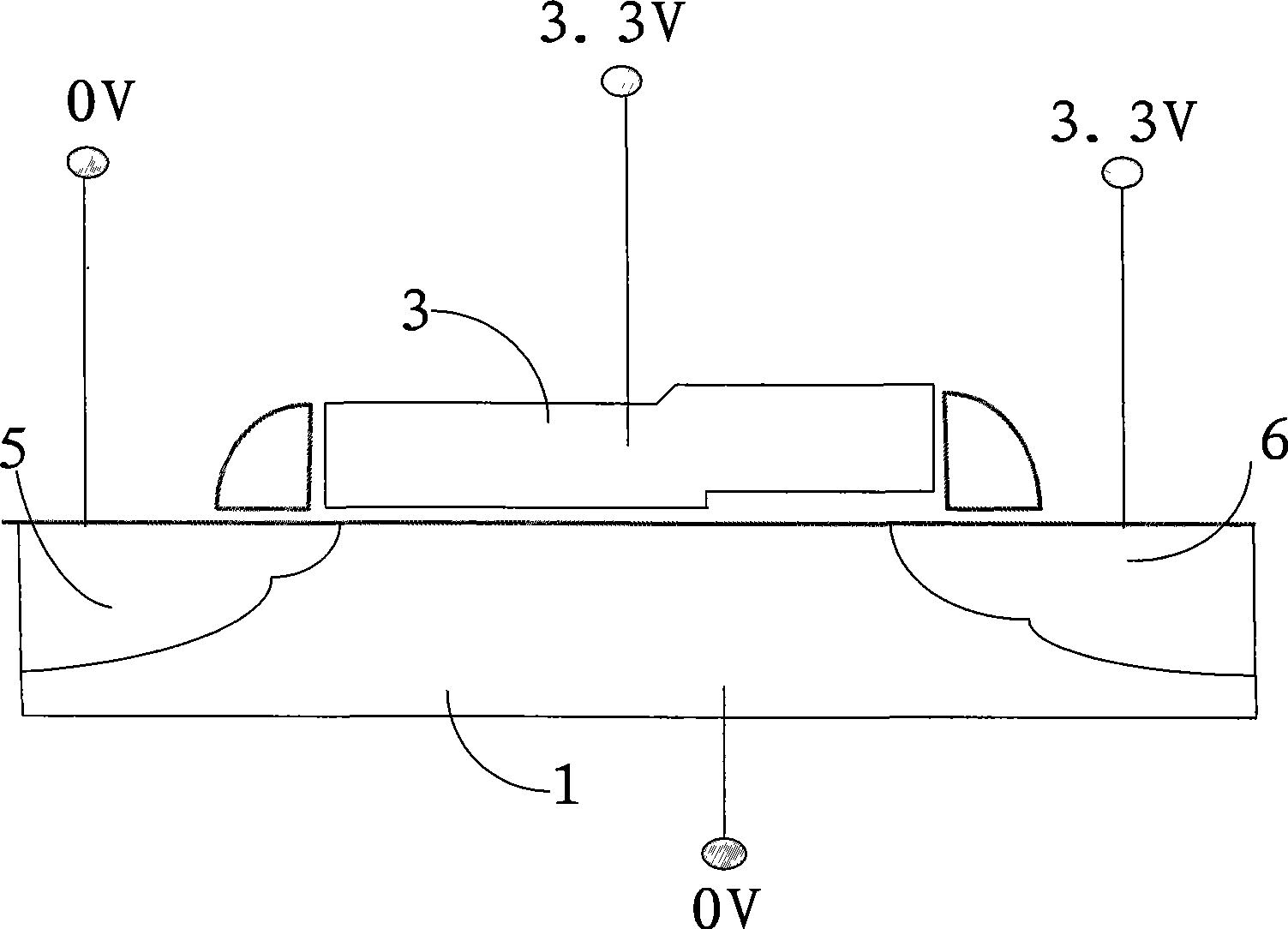

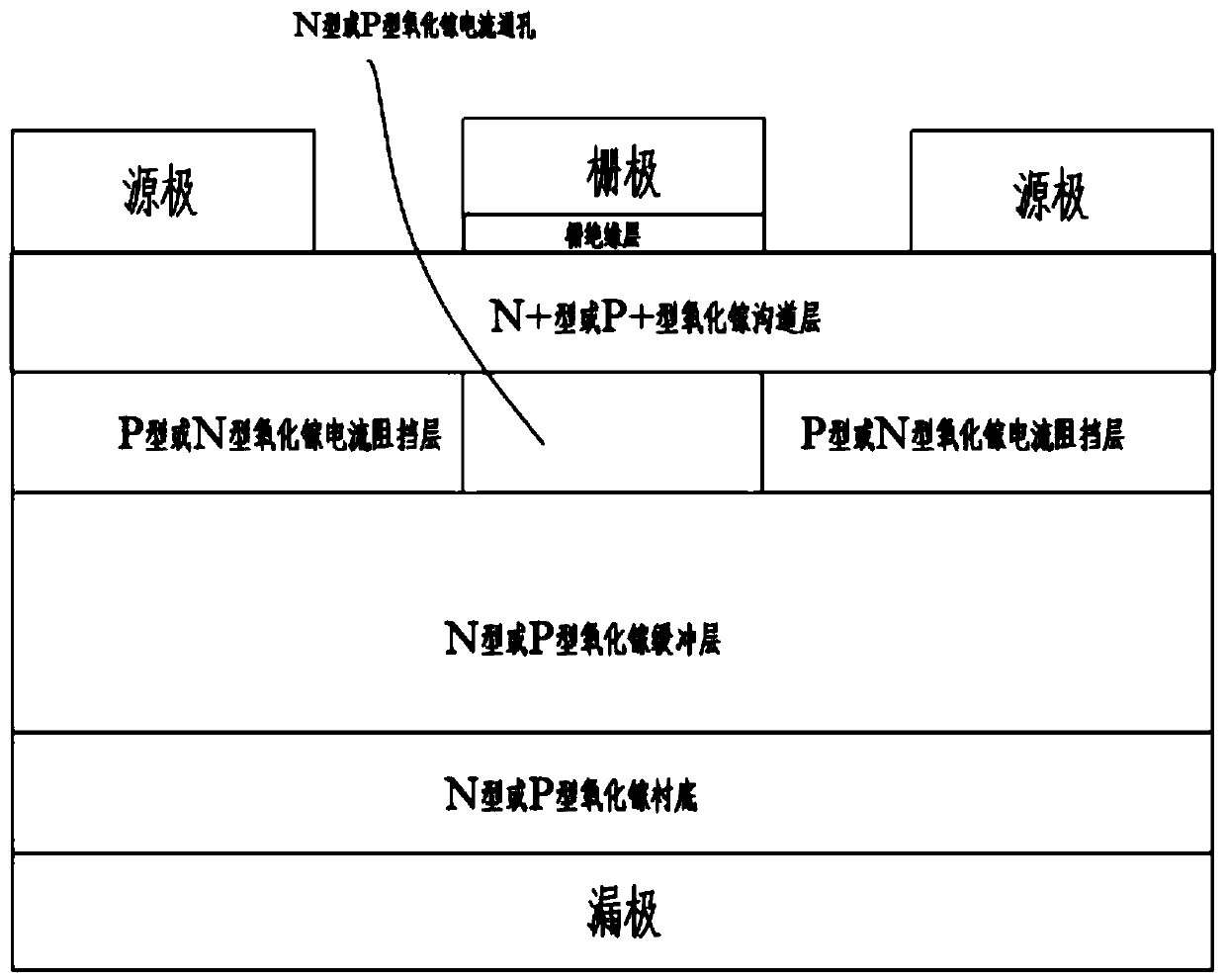

High voltage device for drive chip of plasma flat-panel display

InactiveCN101510551AIncrease load capacityImprove safe work areaSolid-state devicesSemiconductor devicesHigh densityLow voltage

The invention provides a high-voltage device for a drive chip of a plasma flat-panel display, pertaining to the field of a semi-conductor power device. A high-voltage pLDMOS device, a high-voltage nLDMOS device and a high-voltage nLIGBT device are established on a substrate, an oxygen burying layer and an SOI layer and separated by deep-slot medium isolation areas. The oxygen burying layer and the deep-slot medium isolation areas positioned between the substrate and the SOI layer realize the full medium isolation of the device and low-voltage logic circuits. The thickness of the SOI layer is 8 micrometers and can meet the requirements of the device for high-voltage resistance. Compared with the thin SOI technology, the self-heating effect is relieved obviously and the nLIGBT device has low conduction resistance. The group of the high-voltage device for the drive chip of the plasma flat-panel display based on the thick SOI layer fully utilizes the characteristics of the SOI technology, such as low leak, small chip occupying area, high speed, high density of integration and low power consumption, thus meeting the development requirements of the large-sized plasma flat-panel display.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

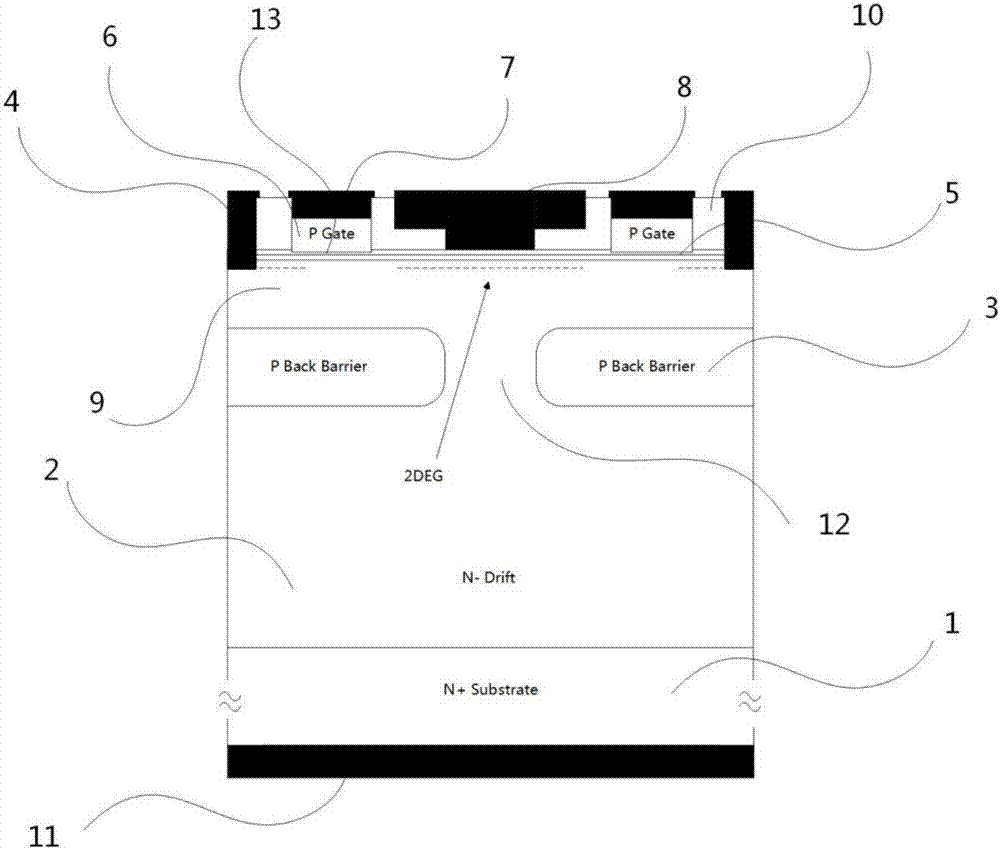

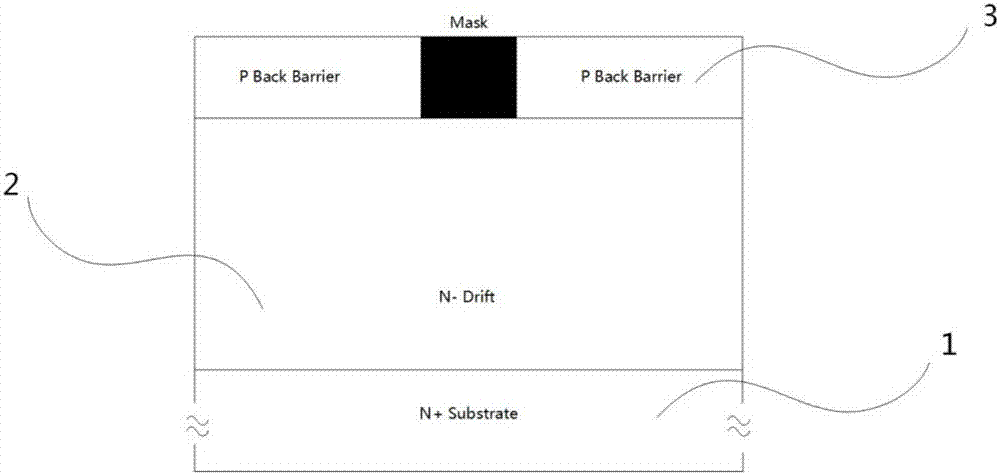

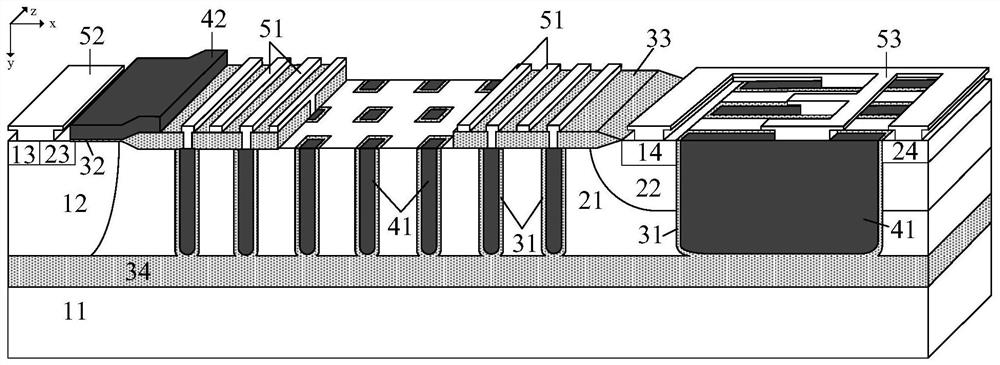

GaN hetero-junction longitudinal inverse-conduction field effect tube

ActiveCN107482059ALower on-resistanceIncrease saturation currentSemiconductor devicesField-effect transistorElectron

The invention relates to the technical field of semiconductor devices, and relates to a GaN hetero-junction inverse-conduction field effect tube. According to the invention, a longitudinal discrete gate structure is adopted; a schottky source electrode is deposited between the gate electrodes so as to form an anode of an inverse-conduction diode; and through the joint action of the back barrier formed in the p-type base region and the p-type gate, the two-dimensional electron gas (2 DEG) below the gate can be depleted; and through the adjustment of the re-growth thickness of the ALMN barrier layer, the threshold voltage can be accurately regulated and controlled. The effect tube has the beneficial effects that under the working state of a forward switch, the threshold voltage is adjustable, that the on-resistance is low, that the saturation current is large, that the off-state withstanding voltage is high, and that working frequency is high and power consumption is low and the like; and under the inverse-conduction working state, the starting voltage is low, the on-resistance is low, the inverse withstanding voltage is large, the inverse recovery time is short, and the power consumption is low and the like. Meanwhile, the manufacturing process is compatible with a traditional GaN hetero-junction HEMT device and is particularly suitable for a GaN hetero-junction longitudinal power field effect tube.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Wide temperate zone terahertz wave detector and preparation method thereof

ActiveCN107331729AStrong ionic bondImprove transconductanceFinal product manufactureSemiconductor devicesSignal-to-noise ratio (imaging)Ohmic contact

The present invention belongs to the detector technology field, in particular relates to a wide temperate zone terahertz wave detector and a preparation method thereof. According to the present invention, by taking an aluminum gallium nitrogen / gallium nitrogen high electron mobility field effect transistor (HEMT) as a basic structure, by the substrate and by utilizing an epitaxy method, an aluminum gallium nitrogen / gallium nitrogen layer is prepared; then an active area table-board, a gate medium, an ohmic contact window and an electrode are prepared, so that an obtained two-dimensional electron gas in the field effect transistor has the higher electron concentration and mobility, a spectral detector of realizing the high speed, high sensitivity and high signal to noise ratio detection of a THz wave on an over room temperature condition is obtained, and finally, the wide temperate zone detection of the THz wave is realized.

Owner:SUZHOU UNIV OF SCI & TECH

SOI dynamic threshold transistor

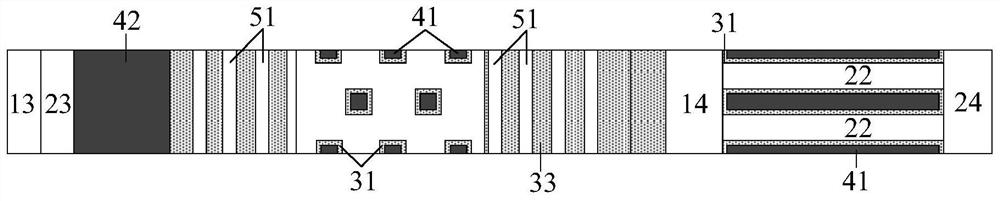

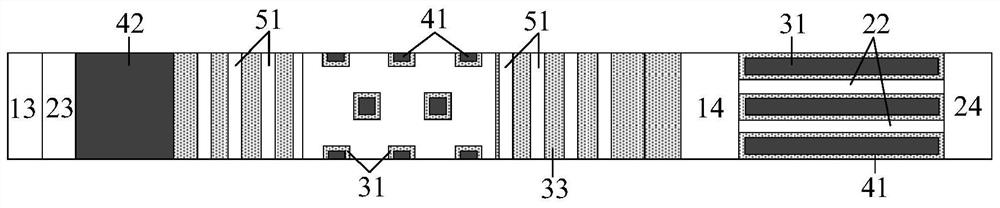

ActiveCN104362174AImprove RF performanceReduce areaSemiconductor devicesParasitic capacitorCapacitance

The invention provides an SOI dynamic threshold transistor which comprises a semiconductor substrate, a first multi-interdigital gate structure, a second multi-interdigital gate structure, a body contact region, a source region, a drain region and a first contact hole. A grid electrode is connected with the body contact region through the first contact hole. By the adoption of a body contact region sharing method, the utilization rate of the body contact region can be increased, and parasitic capacitance can be lowered; meanwhile, by the adoption of a multilateral connection mode, low gate resistance can be obtained. When a device is in a cut-off state, the threshold of the device is high, and the leaked current is low; when the device is in an on state, the threshold voltage of the device is lowered and the current is increased under the influence of the bulk effect. As a result, the device can have a steep sub-threshold slope and a large saturation current; meanwhile, the working voltage of the device is low, and the device is quite suitable for application at low power consumption. By the adoption of the design method, a parasitic resistor and a parasitic capacitor can be improved, and the SOI dynamic threshold transistor has certain application value in the radio frequency application field.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Flat coil inductor, flat coil and manufacture method of flat coil

ActiveCN103680861ASmooth linesEasy to fold and processTransformers/inductances coils/windings/connectionsCoils manufactureEngineeringInductor

The invention discloses a flat coil inductor, a flat coil and a manufacture method of the flat coil. The flat coil inductor comprises a magnetic core, a magnetic cover covering the magnetic core and the flat coil coiled on the magnetic core, wherein the magnetic core is provided with, at least, a first groove and a second groove. The flat coil comprises, at least, the top end base portion and two side edge flattening portions, wherein the base portion is larger than the side edge flattening portions in thickness, the side edge flattening portions are larger than the base portion in width, the base portion is embedded into the first groove, and the side edge flattening portions are embedded into the second groove. The side edge flattening portions are formed by locally flattening the flat coil of the inductor, so that different thicknesses are obtained, the side edge flattening portions are larger than the base portion in width but are smaller than the base portion in thickness, and a magnetic core accommodating space defined by the flat coil is increased. The magnetic core can be matched and assembled with a large corresponding magnetic core, so that the direct-current resistance of the inductor in a limited size range is decreased, the saturation current is increased, and the inductor can obtain the best electrical characteristics.

Owner:DONGUAN PULSE ELECTRONICS CO LTD

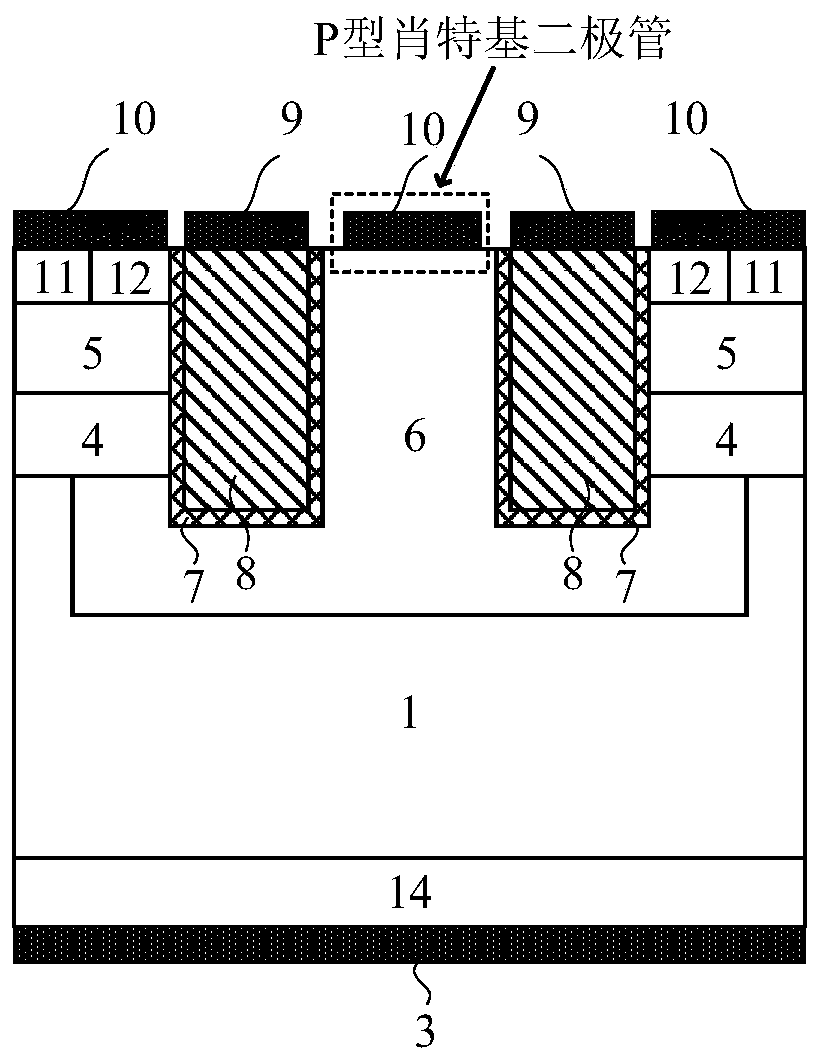

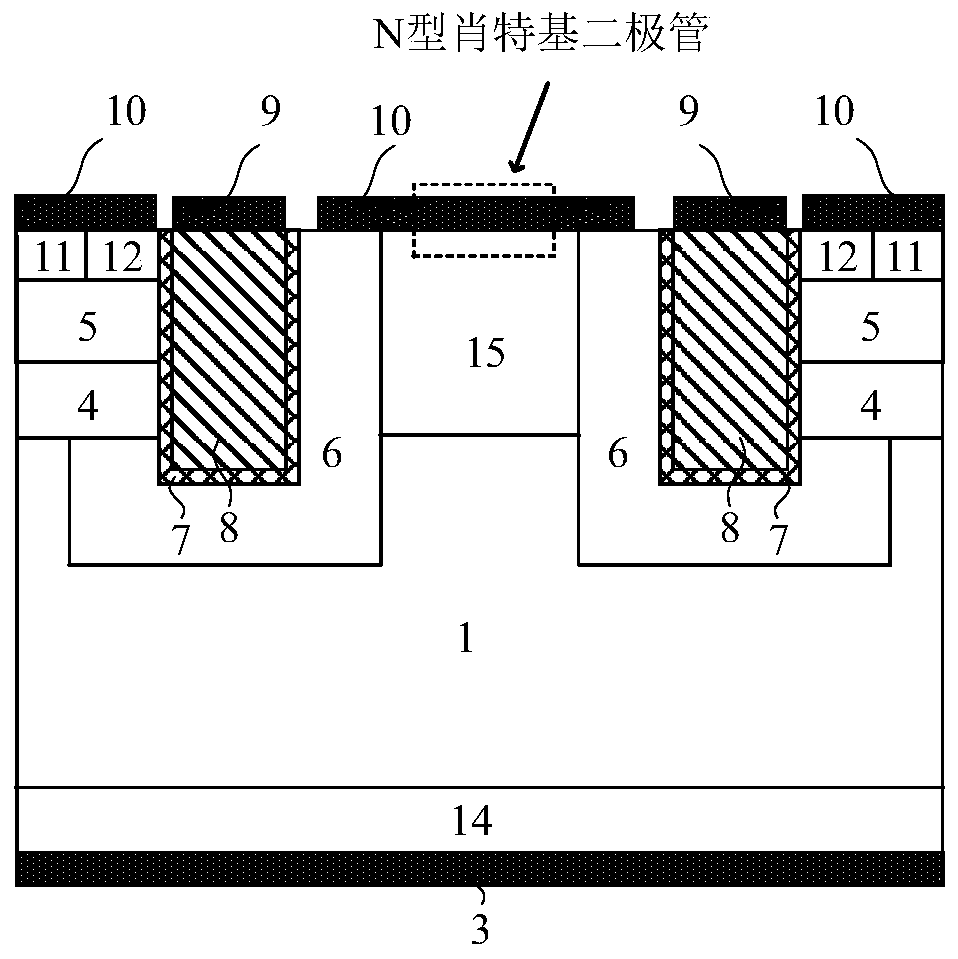

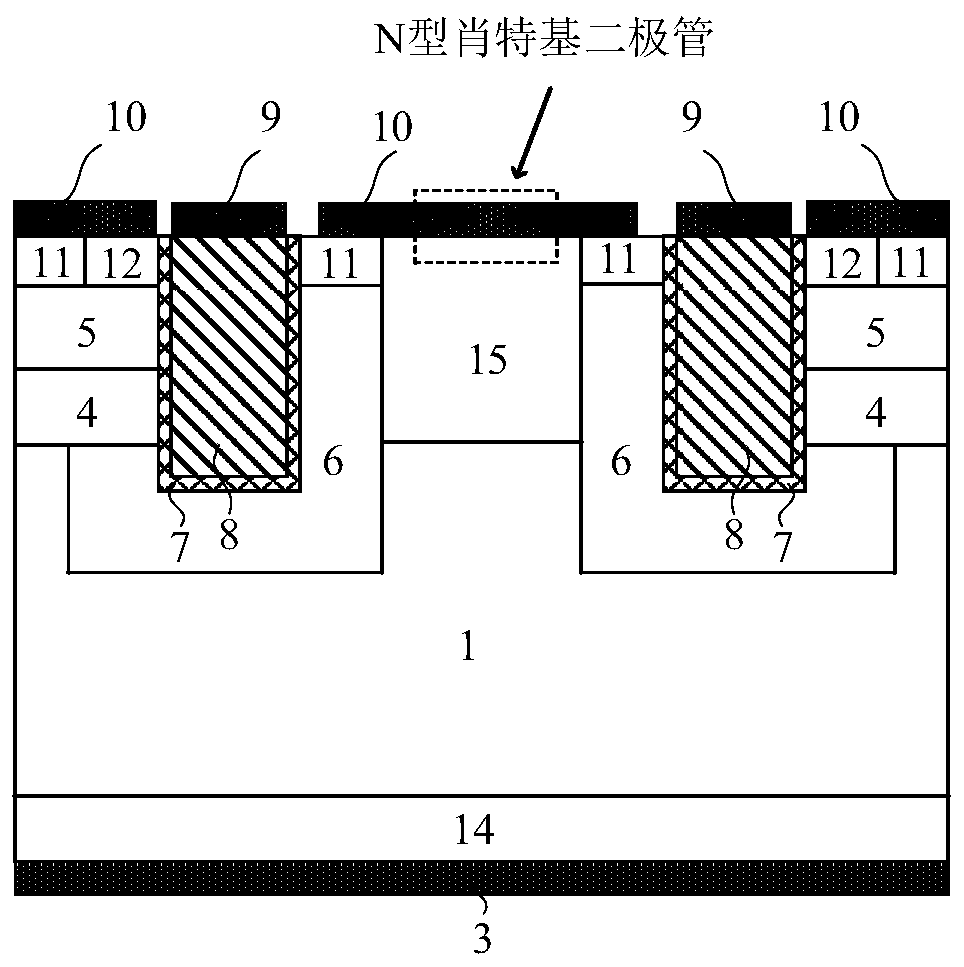

SiC power device

ActiveCN110767753ASmall pressure dropEliminate minority carrier injection effectDiodeHeterojunction diodeMinority carrier injection

The invention belongs to the field of power semiconductors, and particularly provides a SiC power device. The SiC power device comprises a SiC MOSFET and a SiC IGBT. For the SiC MOSFET device integrated with a PN junction body diode, the reverse recovery charge and related loss of the body diode can be greatly reduced, the reverse recovery peak current is reduced, and the EMI noise is reduced; forthe SiC MOSFET device integrated with an N-type Schottky diode or an integrated heterojunction diode, the voltage drop during reverse conduction of the MOSFET can be reduced, and the minority carrierinjection effect is eliminated, so that the conduction loss and reverse recovery loss of the diode are reduced; for the reverse conduction type SiC IGBT device integrated with the PN junction body diode, the reverse recovery charge and related loss of the body diode can be greatly reduced, the reverse recovery peak current is reduced, and the EMI noise is reduced; and moreover, for the reverse conduction type SiC IGBT device integrated with the N-type Schottky diode or the heterojunction diode, the voltage drop during reverse conduction of the reverse conduction IGBT can be reduced, the minority carrier injection effect is eliminated, and the conduction loss and reverse recovery loss of the diode are reduced.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

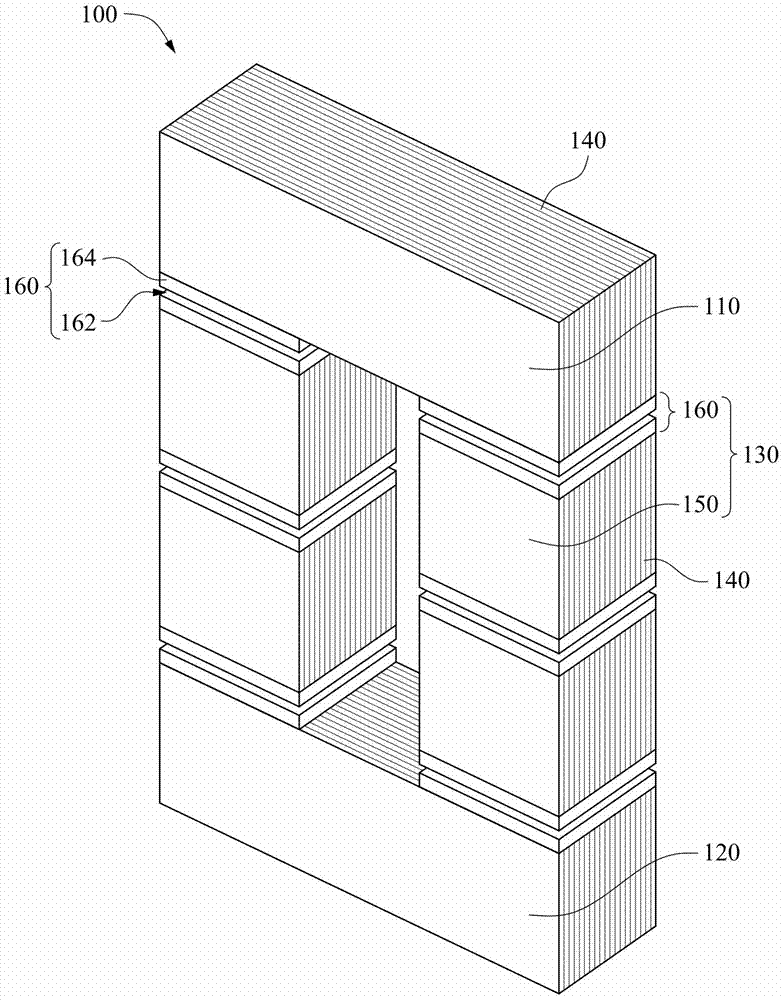

Magnetic core applied to reactor and reactor

ActiveCN104851563AReduce volumeIncrease saturation currentTransformers/inductances magnetic coresMagnetic materialsEngineeringMagnetic loop

A magnetic core utilized in a reactor includes an upper yoke, a bottom yoke, and at least two core columns. The closed magnetic loop is formed by the upper yoke, the bottom yoke, and the core columns. The core columns include at least one first magnetic column. The first magnetic column includes a core body, a balance magnetic unit and an air gap. The balance magnetic unit and the adjacent air gap form a composite air gap for dividing the first magnetic column into different parts. The upper yoke, the bottom yoke, and the two core columns constitute a closed magnetic loop. The composite air gap is disposed at a side of the core body. The upper yoke, the bottom yoke, and the core body are made of planar laminated magnetic material. The magnetic permeability of the balance magnetic unit is lower than which of the planar laminated magnetic material.

Owner:DELTA ELECTRONICS (SHANGHAI) CO LTD

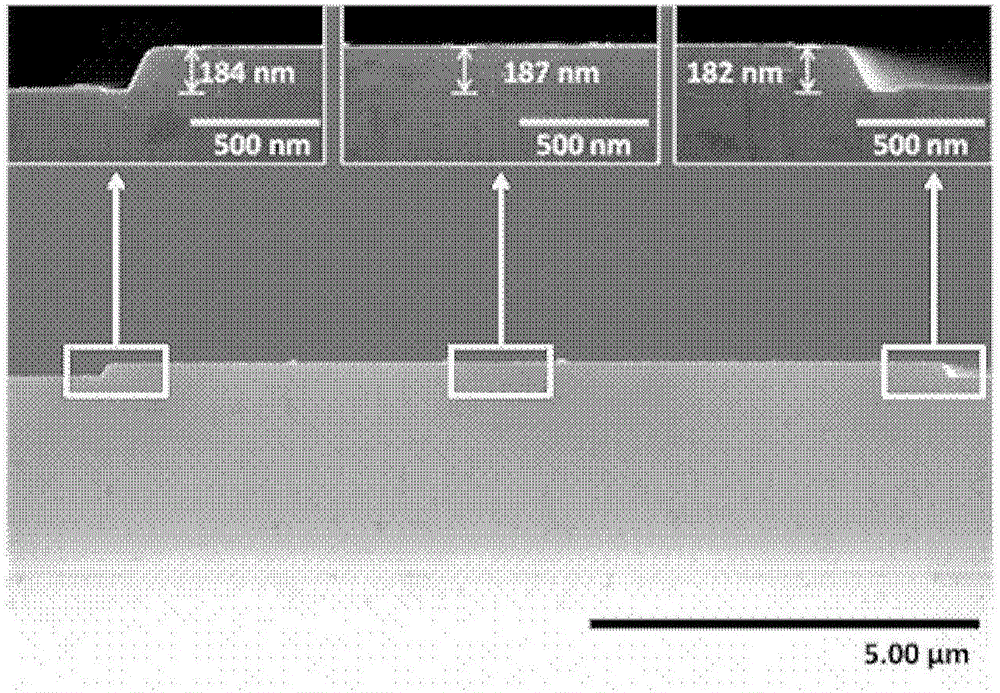

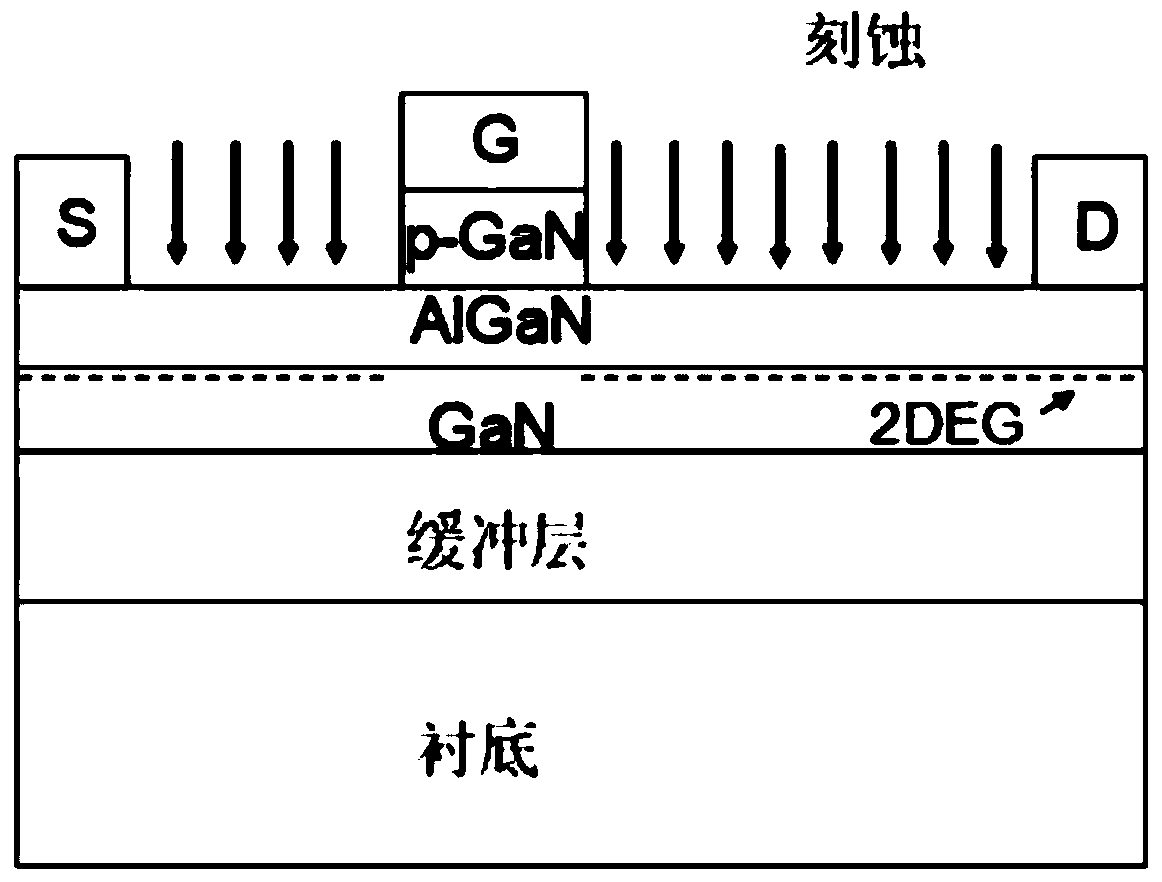

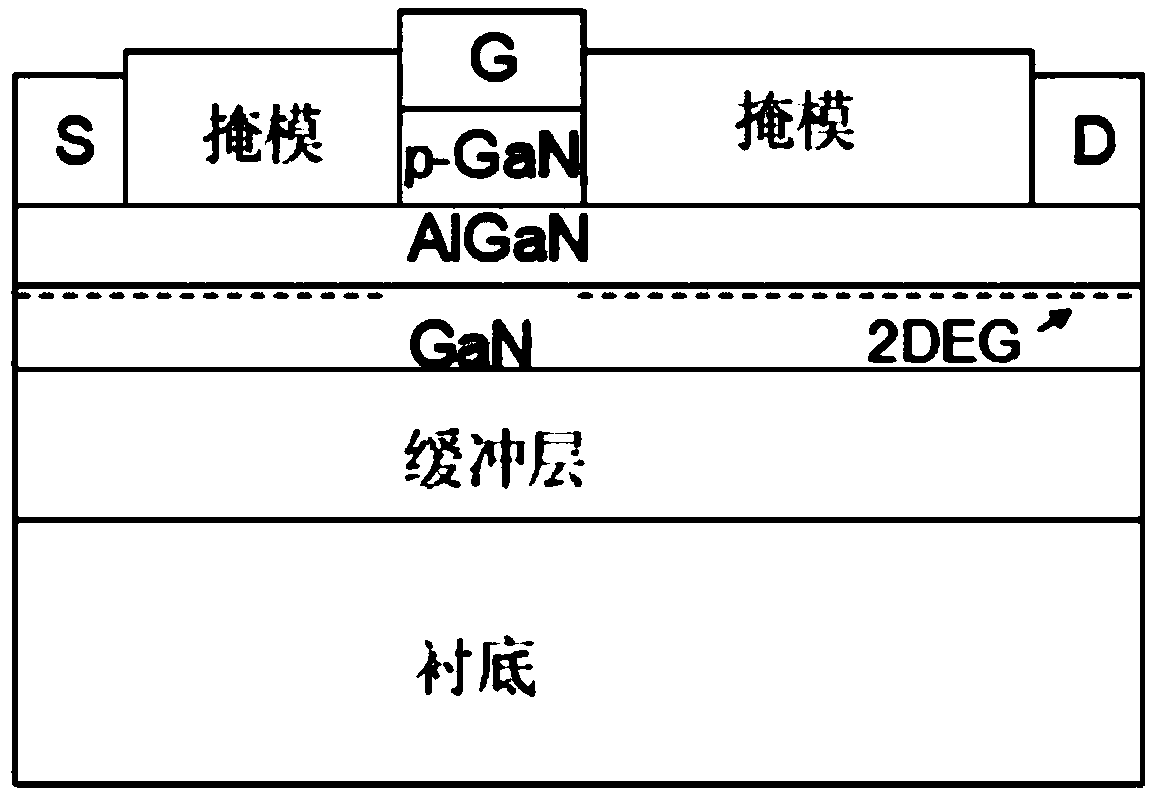

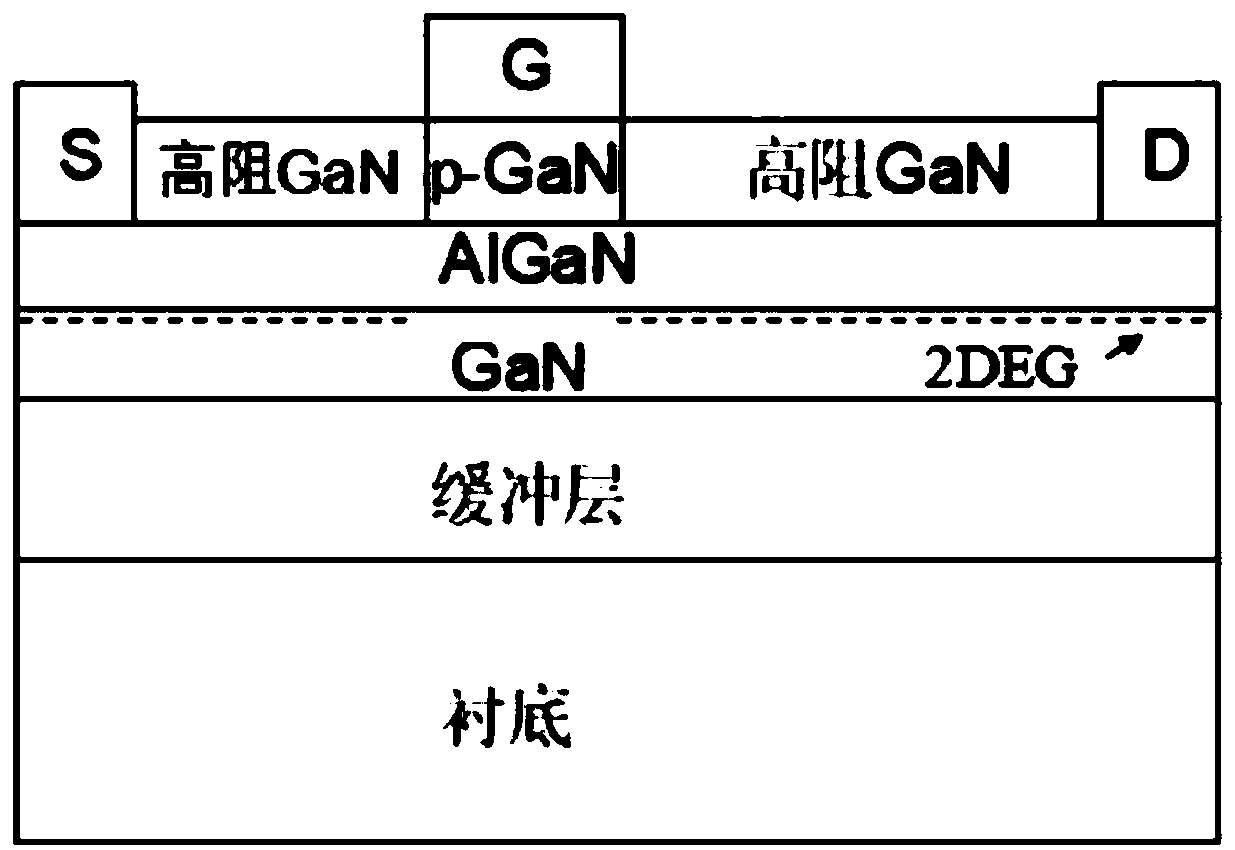

P-type gate enhanced HEMT device and manufacturing method thereof

InactiveCN108962752AAvoid uniformityAvoid duplicationSemiconductor/solid-state device manufacturingSemiconductor devicesHigh resistanceHeterojunction

The invention discloses a P-type gate enhanced HEMT device and a manufacturing method thereof. The method comprises steps that a heterojunction is manufactured, a gate, a source and a drain matched with the heterojunction are manufactured, a third semiconductor is formed on the heterojunction, the third semiconductor in the non-gate region is thinned, the third semiconductor in the non-gate regionis then converted into a fourth semiconductor, the third semiconductor in the gate region is retained, and the fourth semiconductor is a high-resistance semiconductor. The manufacturing method is advantaged in that no secondary extension is required, etching the gate region of the device is further not required, uniformity, repeatability and introduction of damage caused in the etching process are avoided, partial etching is performed on an active region besides the gate region of the device, and damage is reduced.

Owner:SUZHOU NENGWU ELECTRONICS TECH

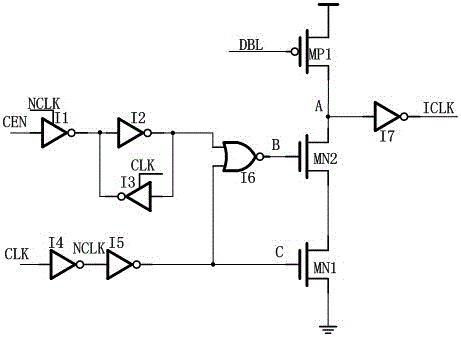

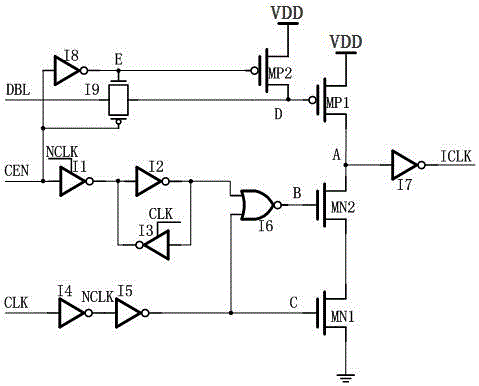

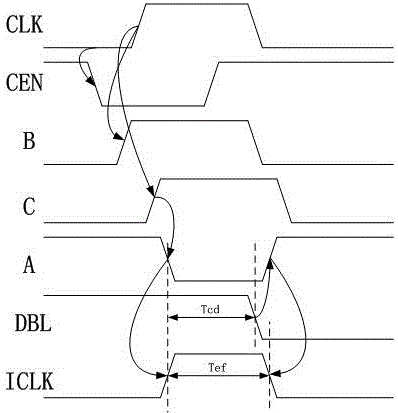

Recovery circuit for improving negative bias-temperature instability of memory clock circuit

ActiveCN105825878ALittle impact on performanceGuarantee normal implementationDigital storageTransmission gateEngineering

The invention discloses a recovery circuit for improving the negative bias-temperature instability of a memory clock circuit. The recovery circuit comprises an enable signal terminal CEN, a clock signal terminal CLK, phase inverters I1, I2, I3, I4, I5, and I7, NOR gate I6, PMOS tube MP1, and NMOS tubes MN1 and MN2, and also comprises a recovery circuit with a NBTI effect. The recovery circuit with a NBTI effect comprises a PMOS tube MP2, a phase inverter I8, and a transmission gate I9. The source electrode of MP2 is connected to a high level terminal VDD, the drain electrode of MP2 is connected to the grid electrode of the MP1 tube, the grid electrode of MP2 is connected to the output terminal of the phase inverter I8 and NMOS grid terminal of transmission gate I9, the input terminal of the phase inverter I8 is connected to the enable signal terminal CEN and the PMOS grid terminal of transmission gate I9, one end of transmission gate I9 is connected to the grid electrode of MP1, and the other end is connected to a virtual bit line DBL. The provided recovery circuit can reduce the influence of NBTI effect on PMOS tube in the circuit so as to guarantee the highest work frequency of circuit and low energy consumption performance.

Owner:SUZHOU XIANLIN LIQI ELECTRONICS TECH

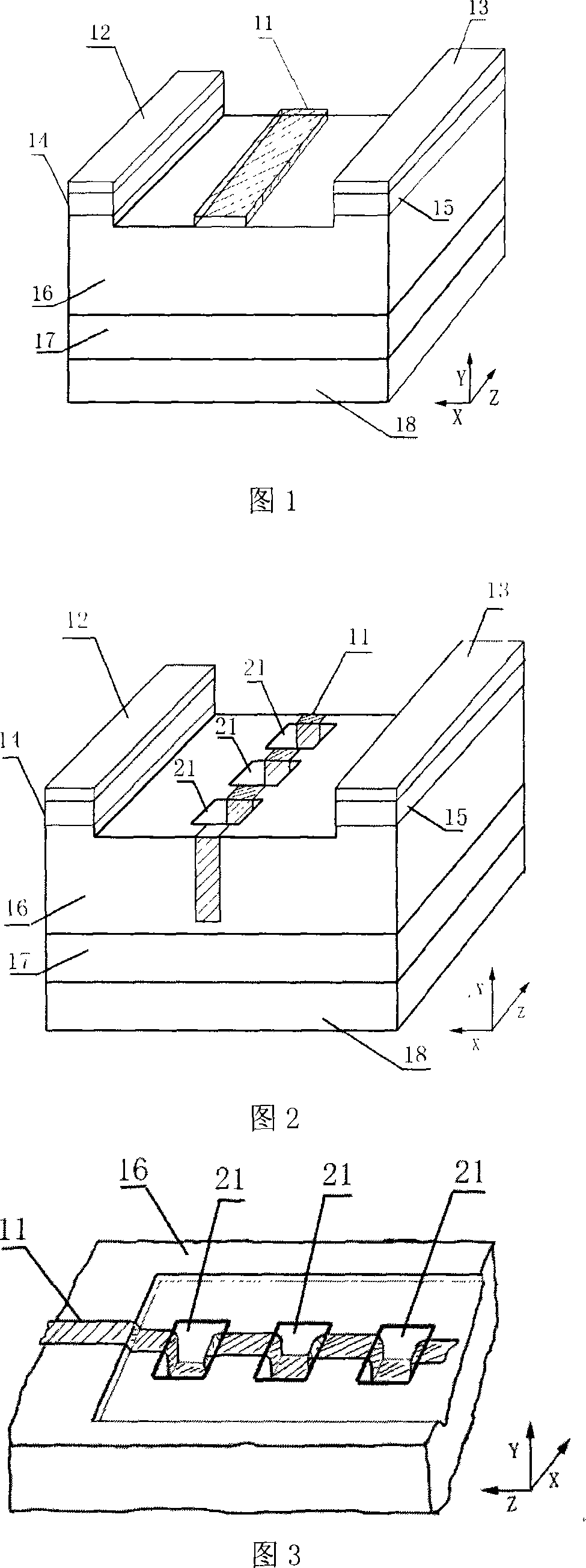

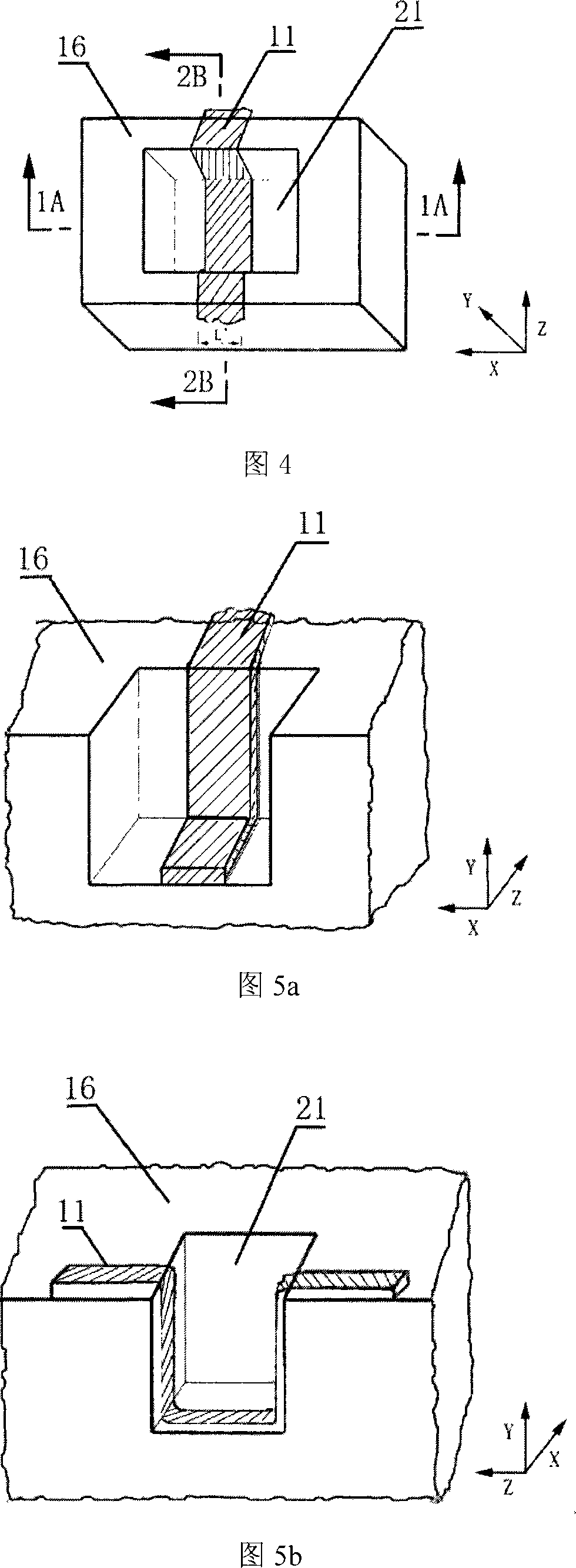

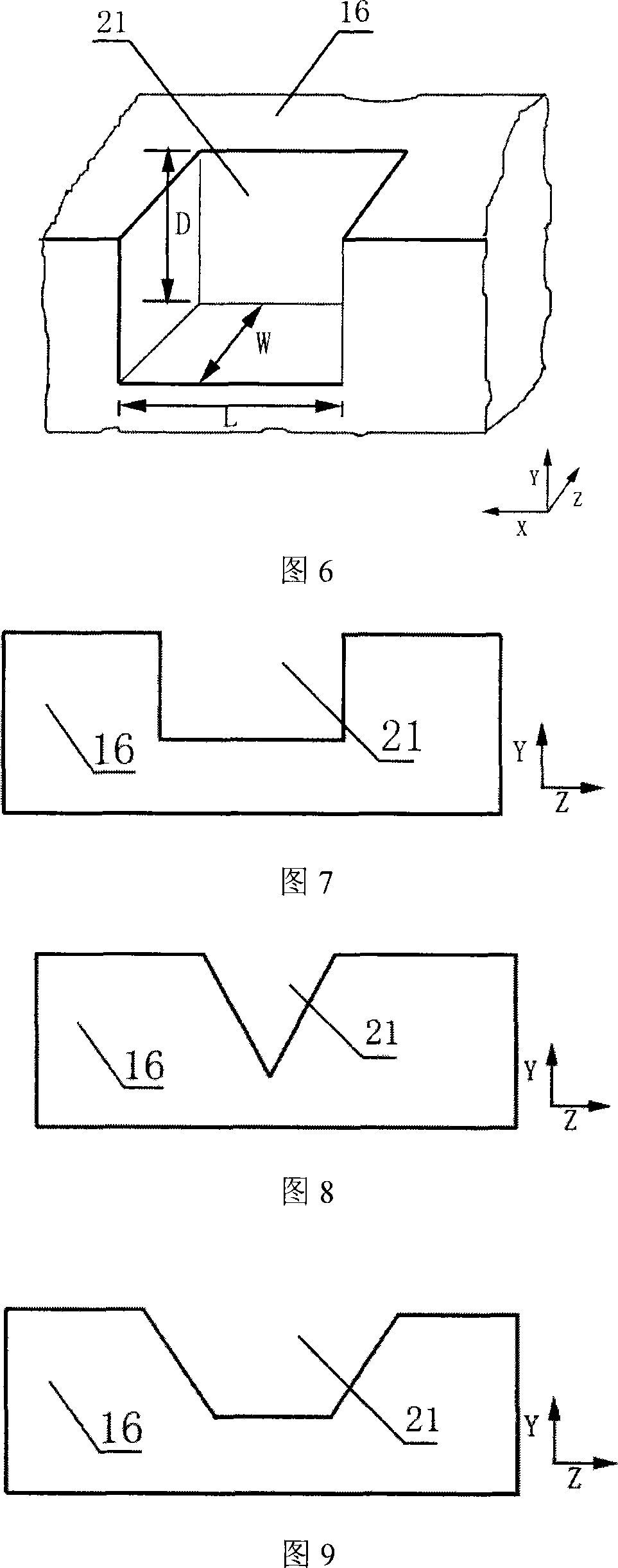

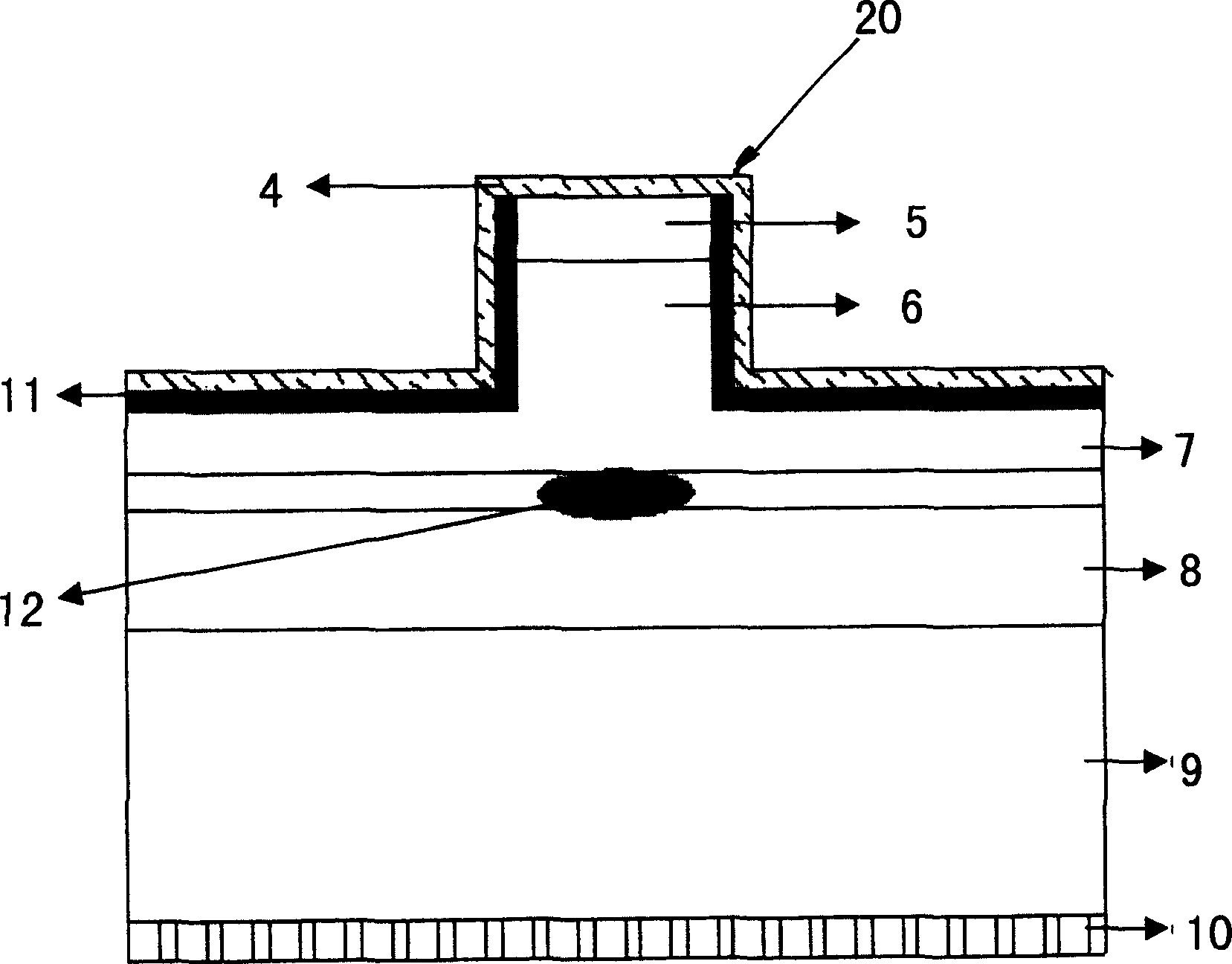

Three-dimensional slot grid metal semiconductor field effect transistor

InactiveCN101022127AImprove breakdown voltageIncrease saturation currentSemiconductor devicesGratingMESFET

This invention puts forward a kind of 3-D groove grating metal semiconductor field effect transistor structure, which opens one or many grooves in an active layer between the source and drain regions in the shape of a square, V, trapezia or a ladder designed according to the actual needs and the grating electrode is covered in the grooves continuously, which greatly increases grating width in the same surface areas of devices due to the existence of the grating grooves compared with the traditional MESFET structure.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

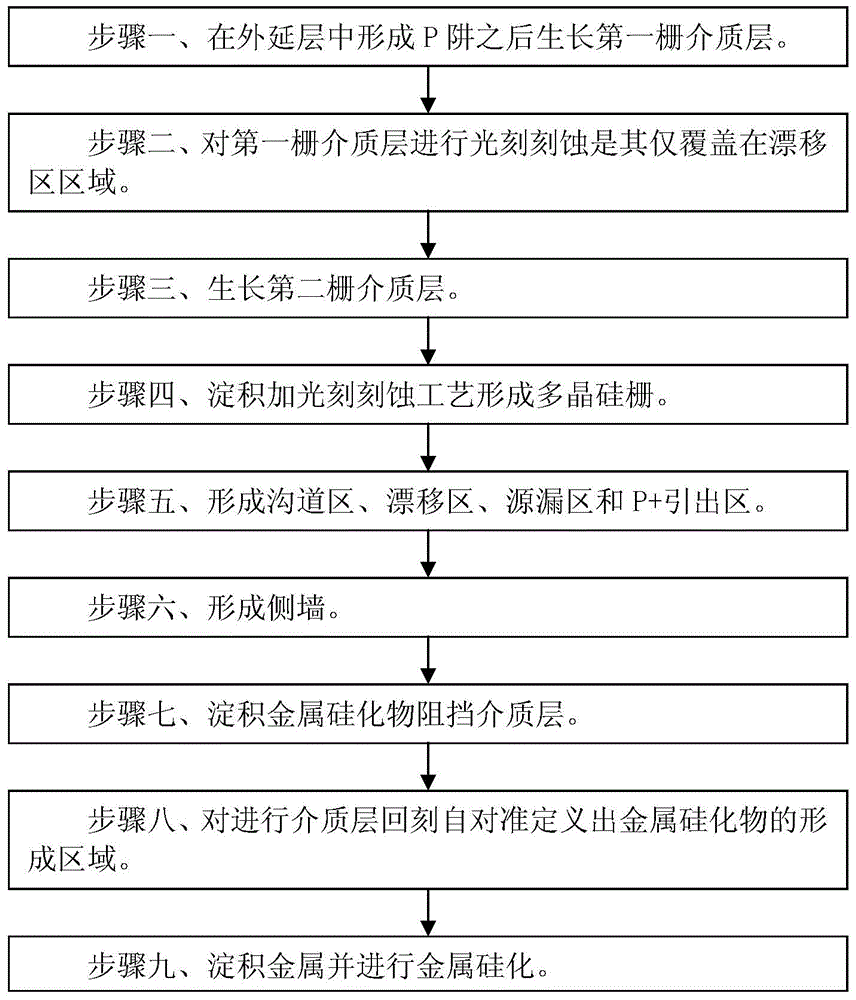

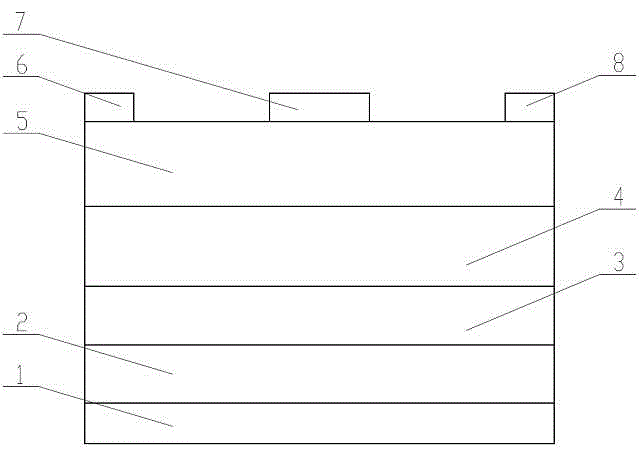

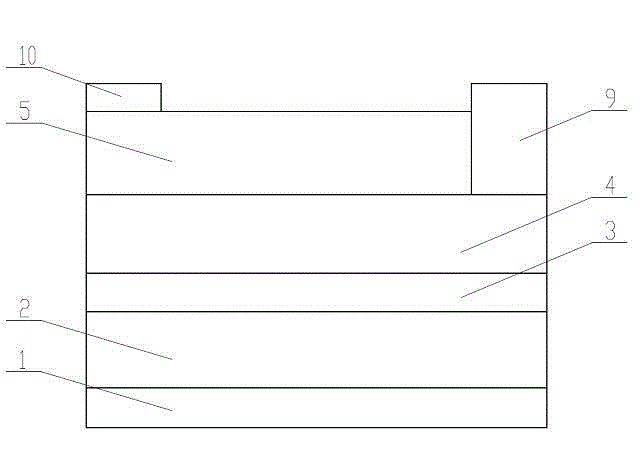

Manufacturing method of radio frequency LDMOS device

ActiveCN104465404ASmall sizeEliminate Registration IssuesSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEtching

The invention discloses a manufacturing method of a radio frequency LDMOS device. The manufacturing method comprises the steps that after a trap P is formed in an epitaxial layer, a first gate dielectric layer grows; photoetching is carried out on the first gate dielectric layer so that the first gate dielectric layer can only cover a drift region; a second gate dielectric layer grows; a polysilicon gate is formed through the deposition and photoetching technology; a channel region, the drift region, a source region, a drain region and a P+ leading-out region are formed; a side wall is formed; a metal silicide barrier dielectric layer is deposited; repeated etching is carried out on the dielectric layers, and a metal silicide forming region is defined through self-alignment; metal silicification is carried out on the deposited metal. The metal silicide forming region of the device can be defined through self-alignment, and the coupling capacitance between a gate electrode and the drain electrode of the device can be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Ridged wave-guiding high-power semiconductor laser structure with conical gain zone

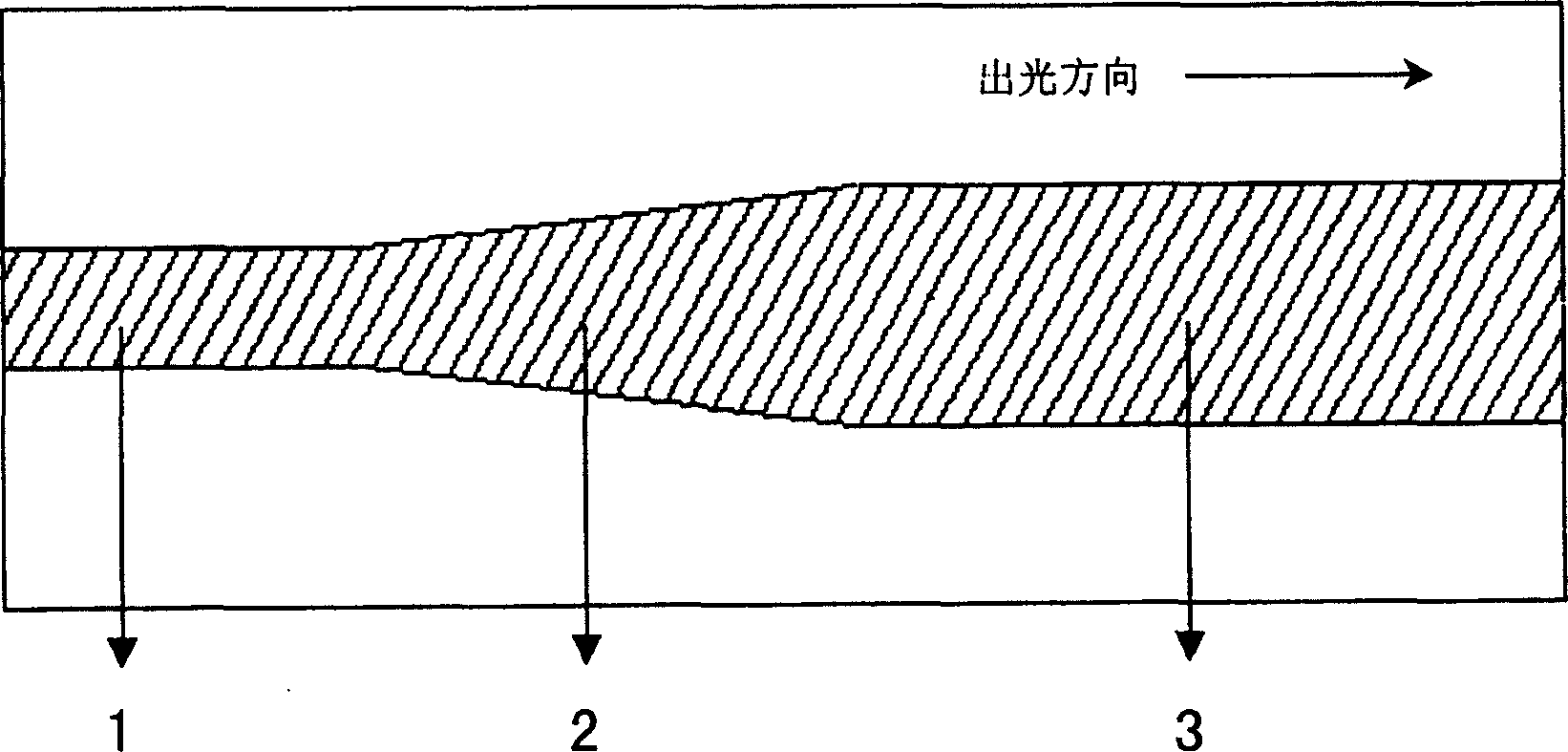

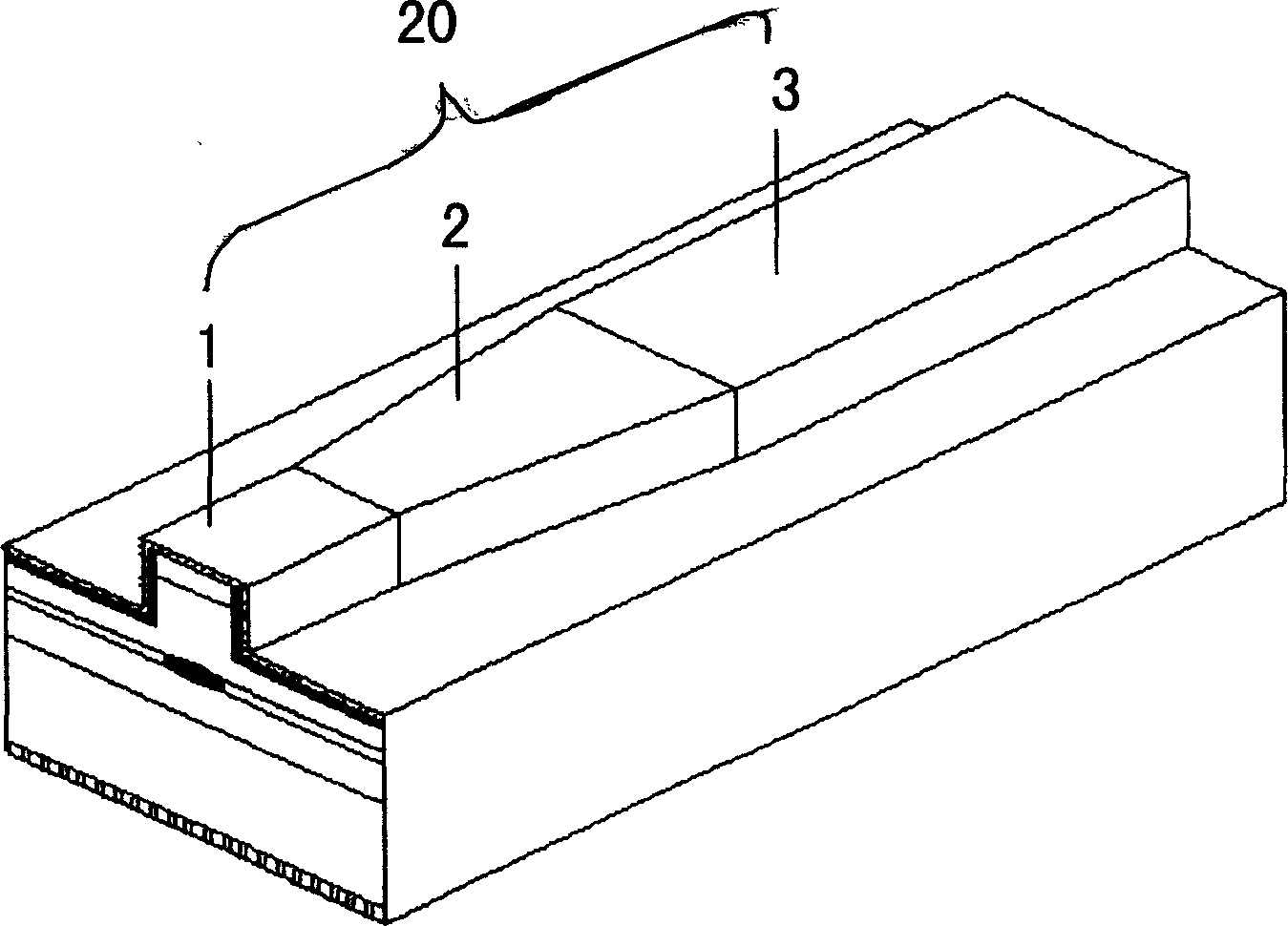

InactiveCN1681176ASuppress catastrophic light damageImprove saturation characteristicsOptical wave guidanceLaser active region structureIndiumGallium

The invention consists of a substrate, an AlGaAs layer that is made on the substrate, an AlGaInPAs active layer that is made on AlGaAs layer, an AlInAs layer that is made on AlGaInPAs active layer, an InP layer that is made on the AlInAs layer and has less area than AlInAs layer, an InGaAs layer that is made on InP layer and forms a ridge shape area with InGaAs layer, a media film layer that is made on both sides of the ridge shape area and AlInAS layer, a p-side electrode layer that is made on top of ridge shape area and media film, a n-side electrode that is made under the substrate.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Device used for terahertz wave detection and preparation method therefor

ActiveCN107195729AEmbodies mechanical strengthHigh mechanical strengthFinal product manufacturePhotometry using electric radiation detectorsGate dielectricSignal-to-noise ratio (imaging)

The invention belongs to the technical field of a detector, and specifically relates to a device used for terahertz wave detection and a preparation method therefor. By taking aluminum-gallium-nitride / gallium-nitride high-electron-mobility field effect transistor (HEMT) as a basic structure, an aluminum-gallium-nitride / gallium-nitride layer is prepared through substrate design and an epitaxial method; and next, an active region table surface, gate dielectric, an ohmic contact window and an electrode are prepared, wherein the two-dimensional electron gas in the obtained field effect transistor is relatively high in electron concentration and mobility, a wave spectrum detection apparatus with high-speed, high-sensitivity and high signal to noise ratio detection can be realized on THz at a room temperature, and terahertz wave detection is realized finally.

Owner:SUZHOU UNIV OF SCI & TECH

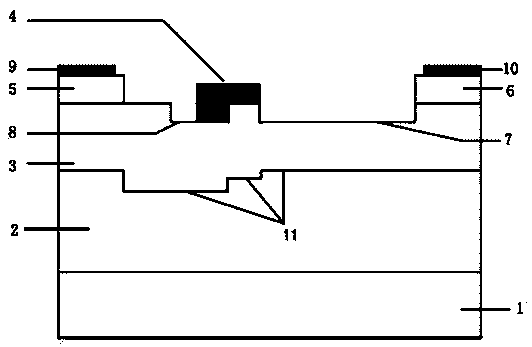

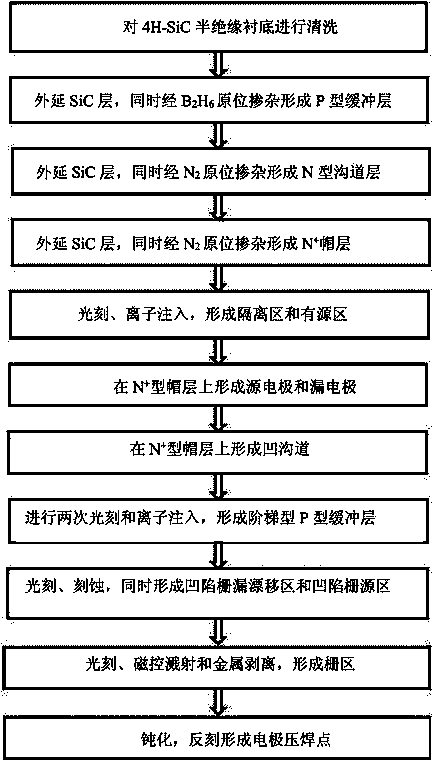

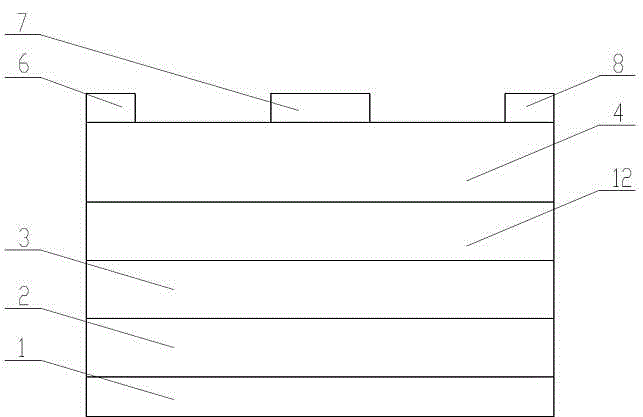

4H-SiC metal semiconductor field effect transistor with step buffer layer structure

ActiveCN104393047AIncrease saturation currentLower breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesSemi insulatingBreakdown voltage

The invention discloses a 4H-SiC metal semiconductor field effect transistor with a step buffer layer structure. The 4H-SiC metal semiconductor field effect transistor comprises a 4H-SiC semi-insulating substrate, a P-type buffer layer and an N-type channel layer from the bottom to the top. The two sides of the N-type channel layer are respectively provided with a source electrode cap layer and a drain electrode cap layer. The surface of the source electrode cap layer and the drain electrode cap layer is respectively provided with a source electrode and a drain electrode. A gate electrode is formed on one side which is arranged above the N-type channel layer and close to the source electrode cap layer. A concave gate source drift region is formed between the gate electrode and the source electrode cap layer. A concave gate drain drift region is formed between the gate electrode and the drain electrode cap layer. The position, which is arranged on the upper end surface of the P-type buffer layer and close to the source electrode cap layer, is provided with a groove. One side, which is arranged in the groove and close to the drain electrode cap layer, is provided with two steps. The 4H-SiC metal semiconductor field effect transistor with the step buffer layer structure has advantages of being stable in breakdown voltage and high in output drain electrode current.

Owner:XIDIAN UNIV

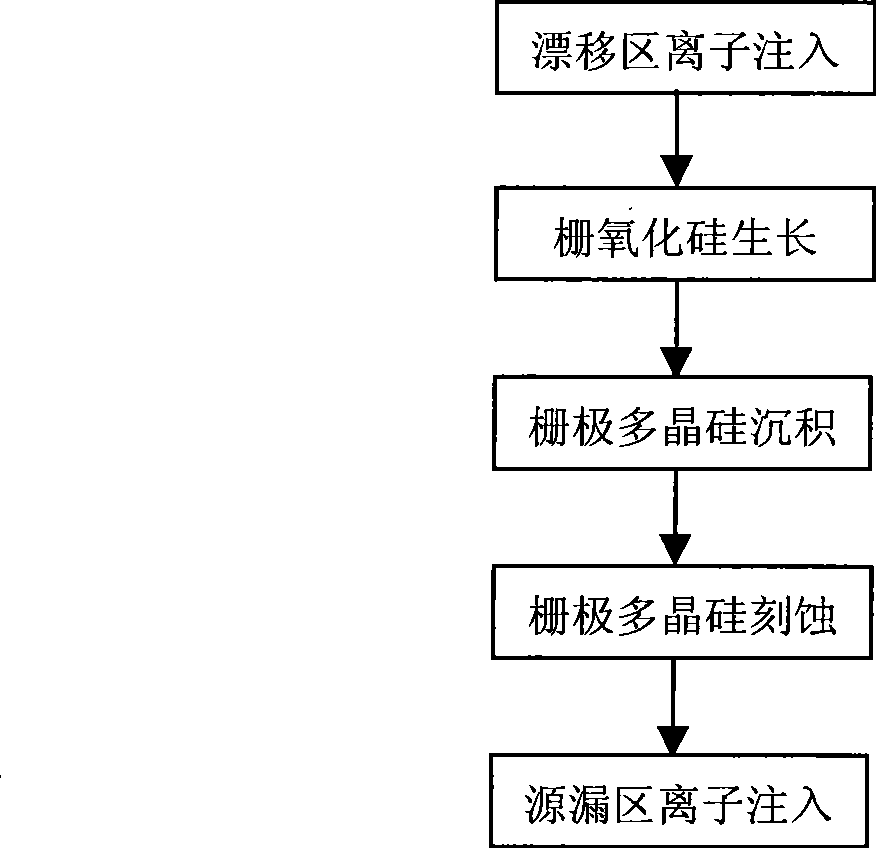

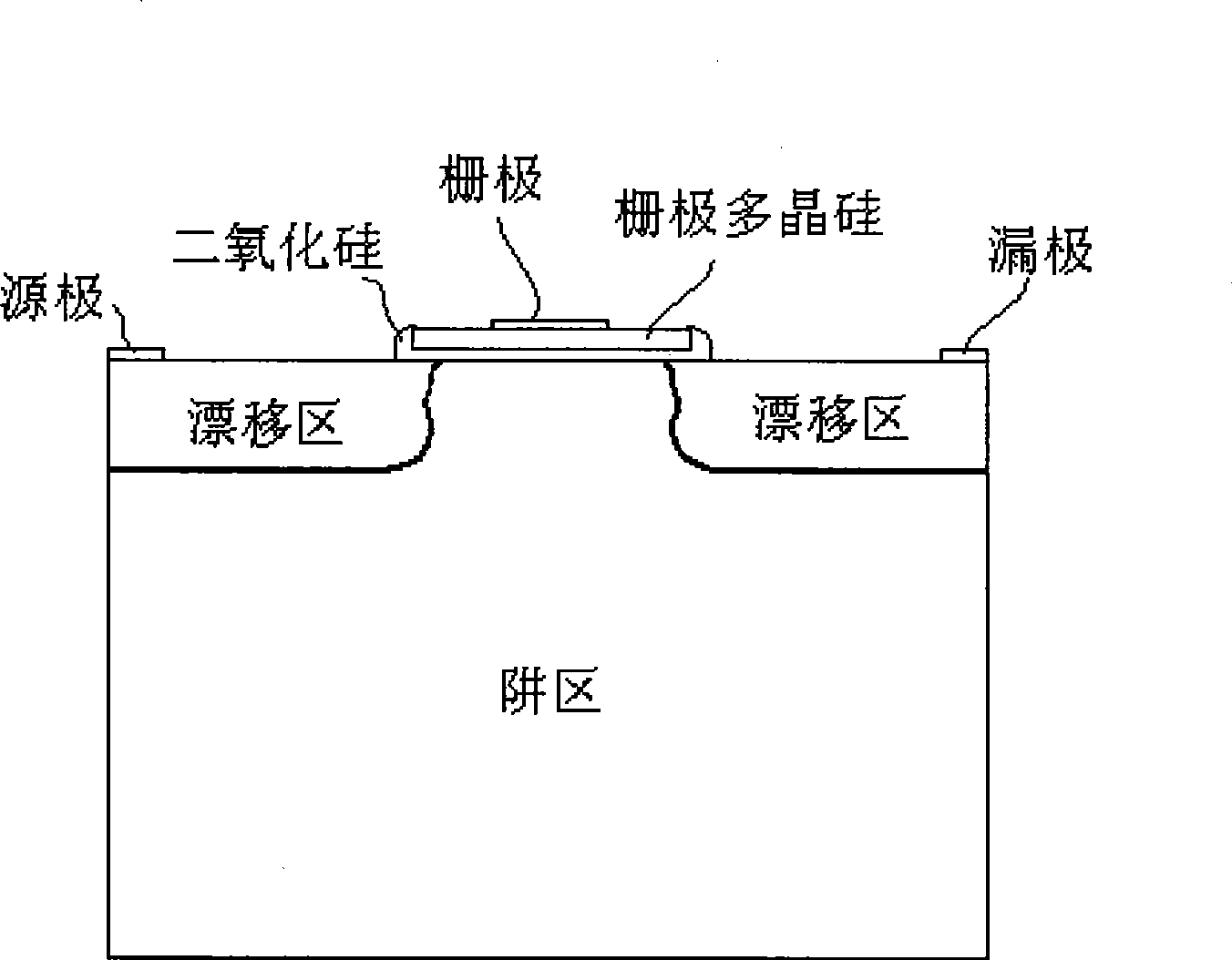

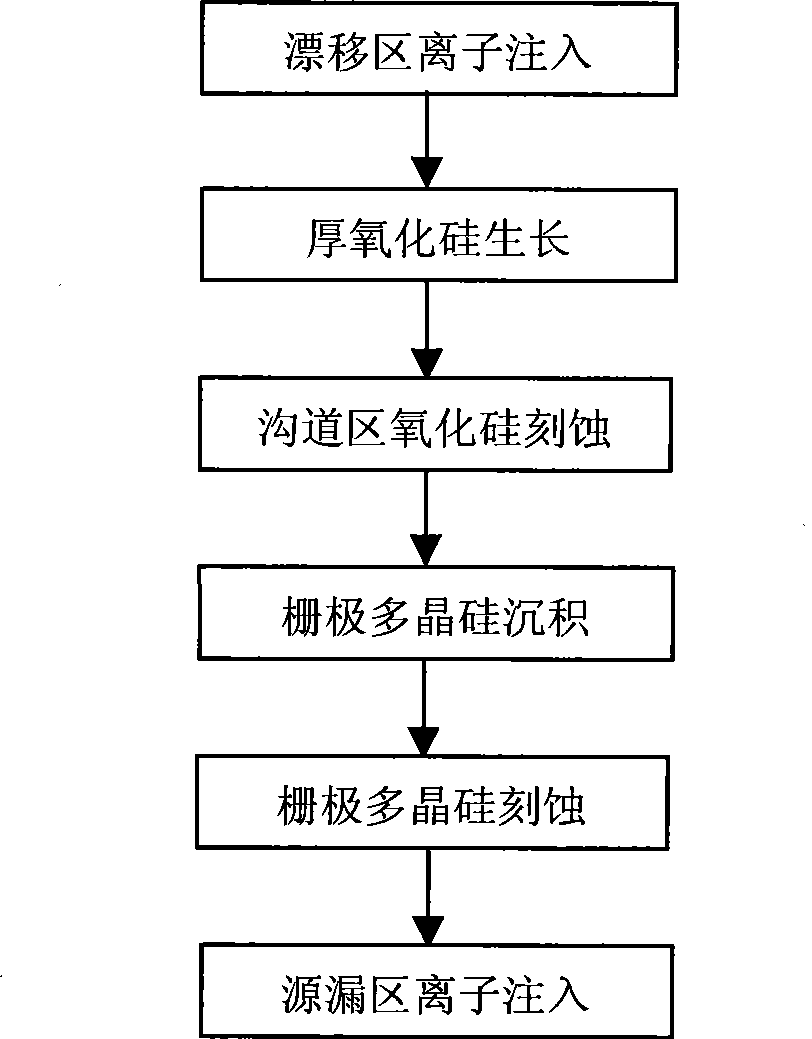

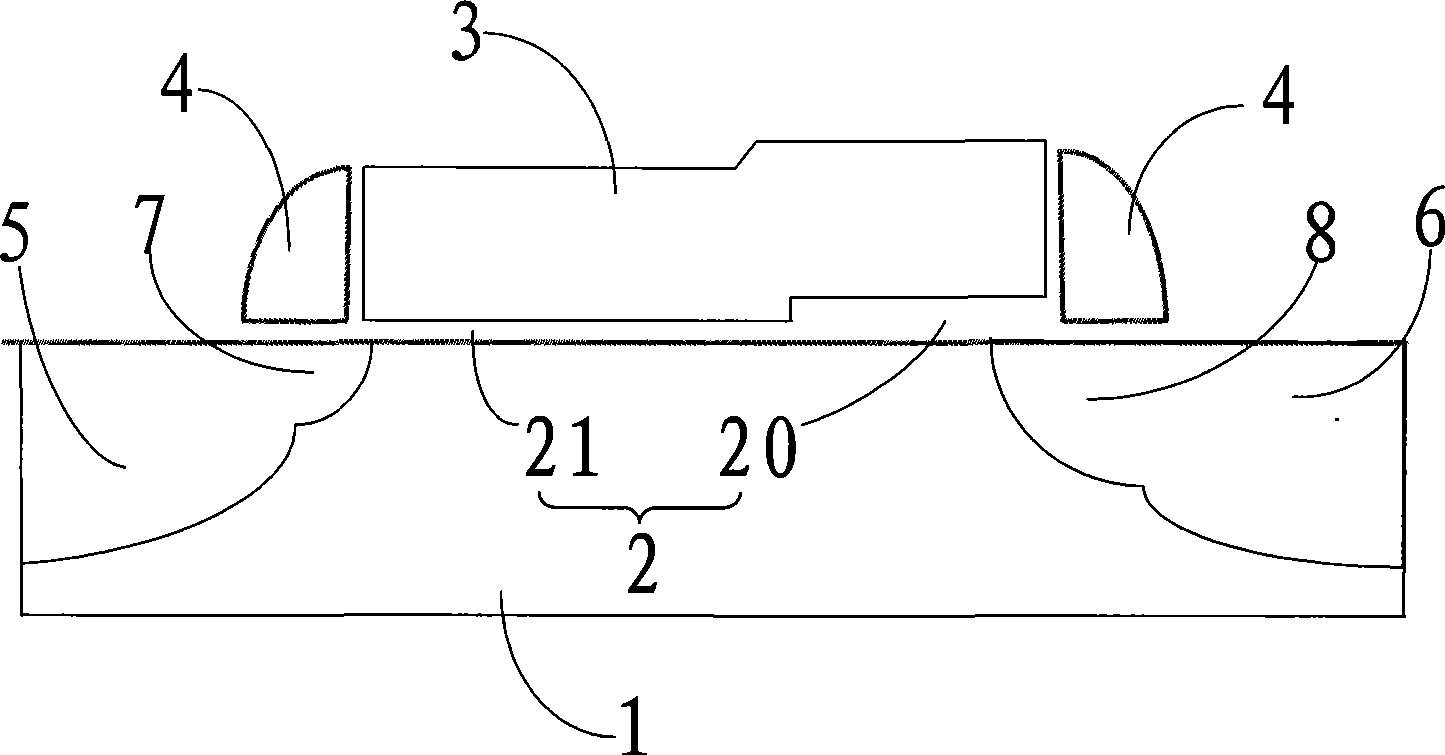

Manufacturing method of double diffusion field effect transistor

InactiveCN101447432AIncrease saturation currentImprove withstand voltage characteristicsSemiconductor/solid-state device manufacturingDouble diffusionEngineering

The invention discloses a manufacturing method of a double diffusion field effect transistor, comprising the following steps: greatly increasing the saturation currents of the transistor by increasing the overlapped area of a transistor gate and drift region; changing the electric field distribution on the drift region using an extended grid potential so as to increase breakdown voltages; and synchronously, inhibiting the GIDL effect resulted from the overlapped area using the thick silicon dioxide under the gate at the overlapped area so as to reduce drain currents of transistor. In addition, the method can change the high-voltage breakdown position of the transistor from a transverse junction area to a longitudinal junction area, namely, the high-voltage breakdown position of the transistor is at the strongest junction area, thereby improving the voltage endurance of the double diffusion field effect transistor.

Owner:SHANGHAI HUA HONG NEC ELECTRONICS

III-nitride-based device structure containing multi-layer back-barrier

ActiveCN103337517AImprove breakdown voltageLittle influence on frequency characteristicsSemiconductor devicesPeak valueMono layer

The invention discloses an III-nitride-based device structure containing multi-layer back-barrier, which belongs to the field of semiconductor devices. The device structure comprises a substrate layer, a back-barrier structure layer and a channel layer from the top down, wherein the back-barrier structure layer is composed of two or more back-barriers of AlxGaN (0<x<1) with different Al components; the Al component increases gradually from the channel layer to the substrate layer, and remains unchanged within the same back-barrier layer. The back-barrier structure layer reduces channel electric field peak value, effectively regulates the channel electric field, and increases the breakdown voltage of the device; compared with the field plate technology, the multi-layer back-barrier structure does not increase the gate capacitance, thereby having a small influence of frequency characteristic of the device; compared with single-layer back-barrier structure, the multi-layer back-barrier structure can use multi-layer low-component back-barriers to regulate the channel electric field together without introducing 2DHG (two-dimensional hole gas), so as to effectively increase device voltage withstanding on the basis of a higher device saturation current.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

LDMOS device based on high K material

The invention discloses an LDMOS (Laterally Diffused Metal Oxide Semiconductor) device based on a high K material. The LDMOS device comprises a substrate on which a source electrode and a drain electrode are arranged; the drain electrode is connected with an N-type drift region; the source electrode and the N-type drift region are connected via a channel; a grid electrode is arranged on the channel; an insulation layer is arranged between the grid electrode and the channel. The LDMOS device is characterized in that the insulation layer comprises a high K layer made from a high K material, and sequentially comprises three layers, i.e. a SiO2 layer, a high K layer and another SiO2 layer. According to the invention, on the premise of no incensement of leakage current of a grid, the high K material with higher dielectric constant is adopted to lower thickness of the insulation layer.

Owner:KUNSHAN HUATAI ELECTRONICS TECH CO LTD

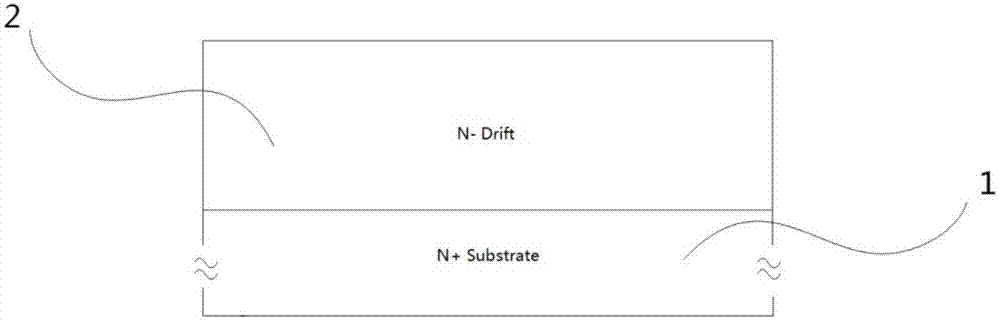

Method for preparing grooved anode Schottky diode

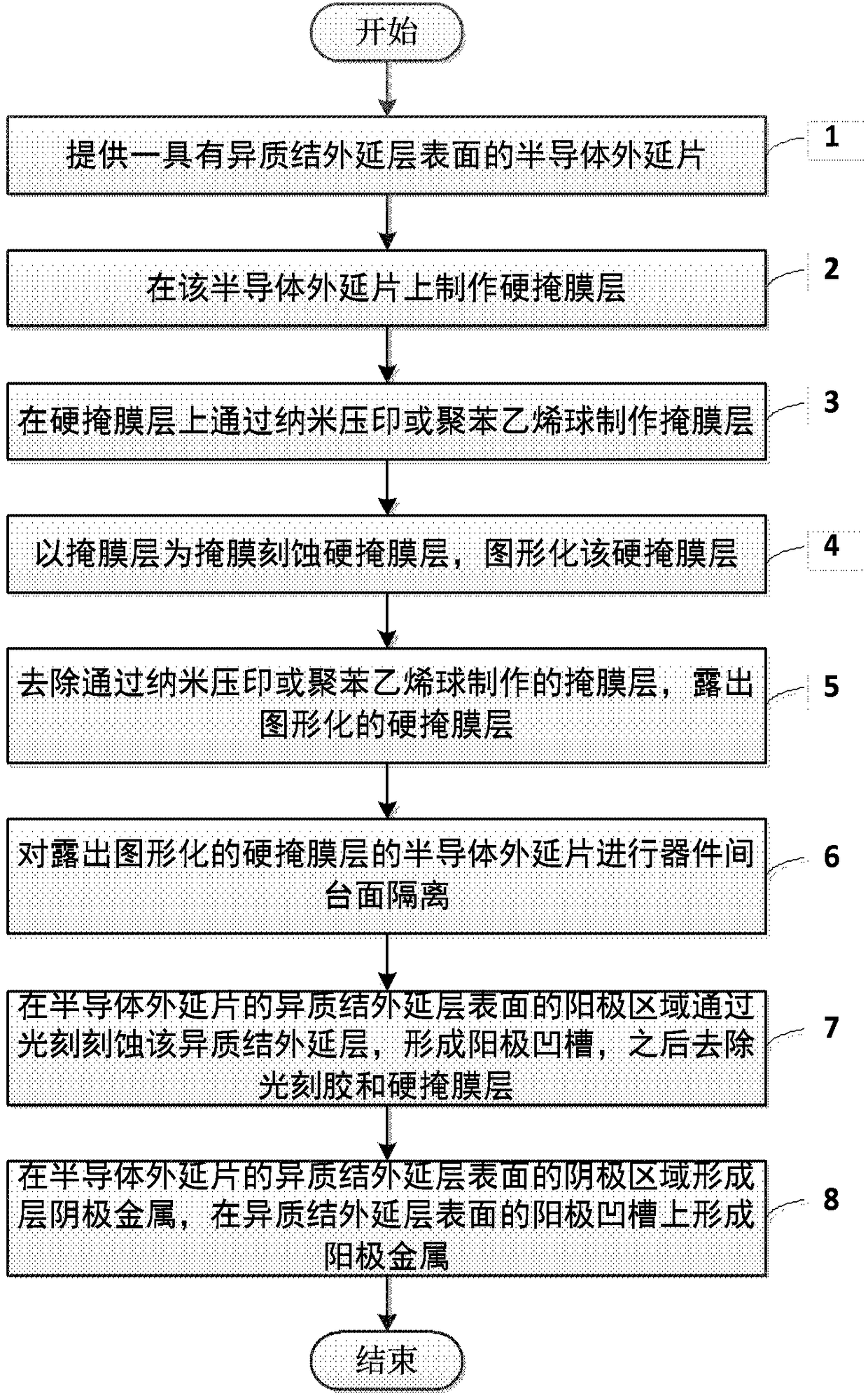

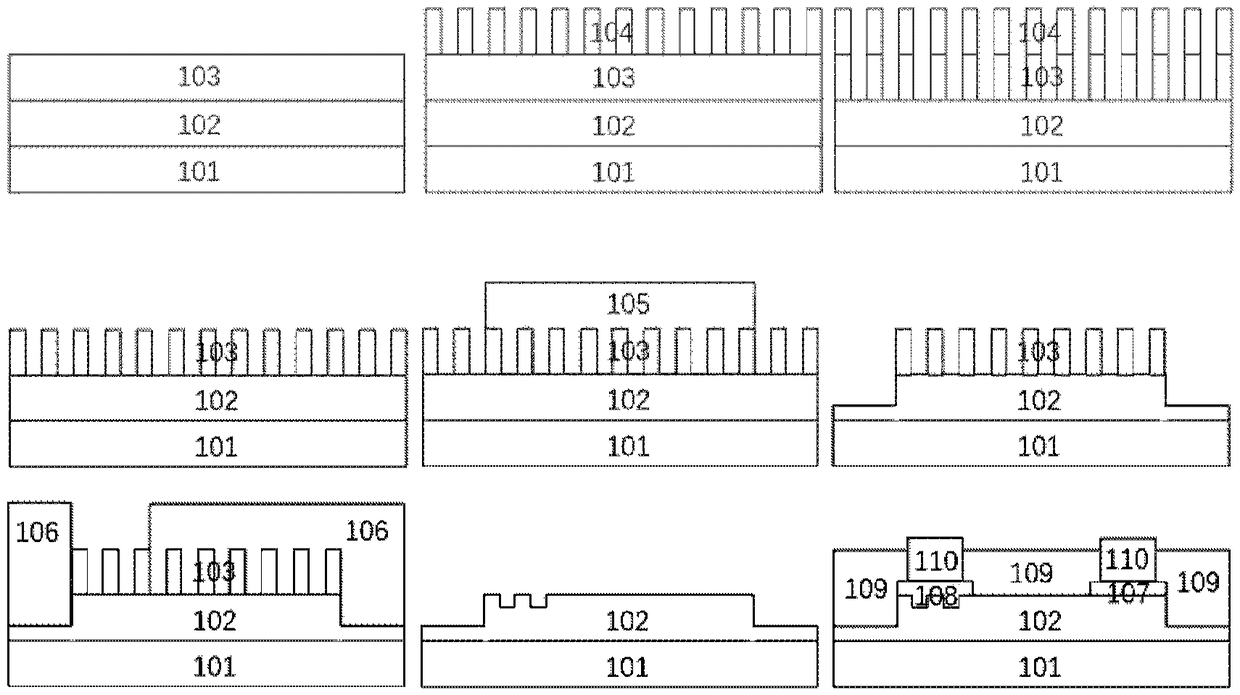

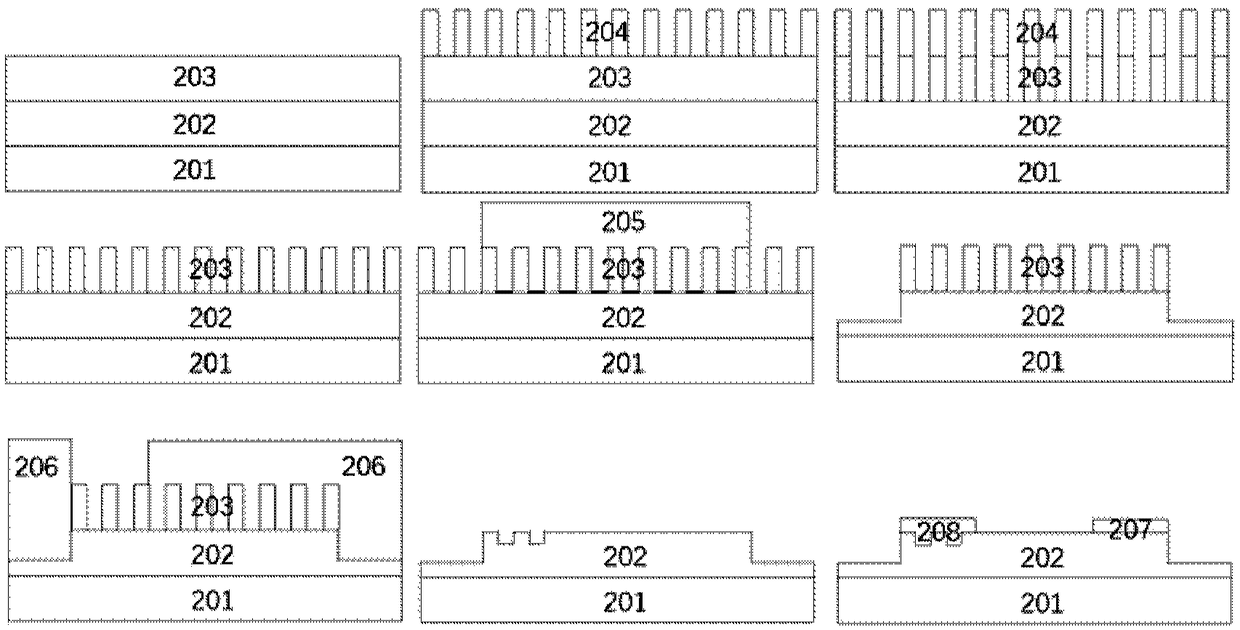

InactiveCN108091566AImprove forward conduction characteristicsGood high breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPhotoresistPolystyrene spheres

The invention discloses a method for preparing a grooved anode Schottky diode. The method comprises the steps of: providing a semiconductor epitaxial wafer; manufacturing a hard mask layer on the semiconductor epitaxial wafer; manufacturing a mask layer on the hard mask layer; and using the mask layer as a mask for etching the hard mask layer, and patterning the hard mask layer; removing the masklayer to expose the patterned hard mask layer; performing inter-device mesa isolation on the semiconductor epitaxial wafer on which the patterned hard mask layer is exposed; etching a heterojunction epitaxial layer to form an anode groove in an anode region on the surface of the heterojunction epitaxial layer of the semiconductor epitaxial wafer, and then removing a photoresist and the hard mask layer; and forming a layer of cathode metal in a cathode region on the surface of the heterojunction epitaxial layer of the semiconductor epitaxial wafer. The method utilizes a nanoimprint technology or a polystyrene ball paving technology to realize the nanoscale anode groove, so as to prepare the Schottky diode having the good positive conducting features such as low turn-on voltage, low conducting resistance and high saturation current as well as good reverse turn-off features such as low electric leakage and high breakdown voltage simultaneously.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

SOI lateral insulated gate bipolar transistor

ActiveCN111969049AIncrease saturation currentLower forward voltage dropSemiconductor devicesEngineeringElectrode Contact

The invention provides an SOI transverse insulated gate bipolar transistor, which is characterized in that a first dielectric oxide layer and a floating field plate polycrystalline silicon electrode form a longitudinal floating field plate which is distributed in a whole second conduction type drift region to form a longitudinal floating field plate array; and a longitudinal field plate connectedwith the collector contact electrode is formed in the collector region by the same process, and a second conductive type well region is inserted in parallel to form an anode resistance structure. Whenthe transistor is in an on state, an accumulation layer can be formed on the surface of the longitudinal floating field plate, and the saturation current of the device is improved. The longitudinal field plate introduced into the well region of the second conductive type can accurately control the size of the anode resistance, eliminates the impact on the output characteristics of the device fromthe snapback phenomenon, and improves the stability of the device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

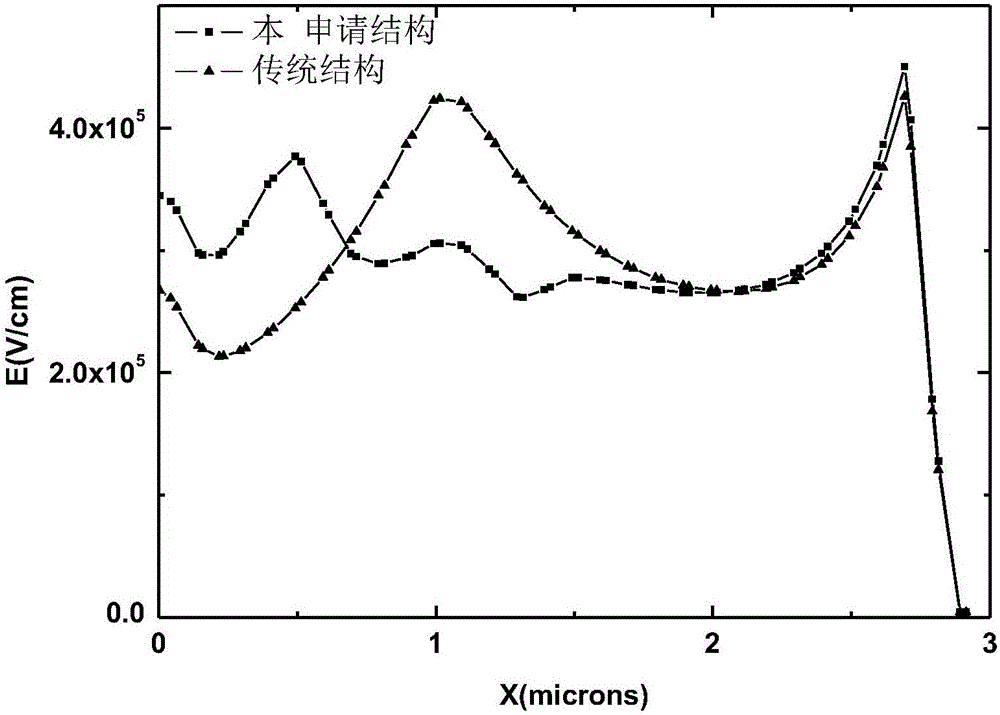

RF LDMOS device

InactiveCN105140288AReduce high electric fieldReduced drain on-resistanceSemiconductor devicesLDMOSDielectric layer

The present invention provides an RF LDMOS device including: a P+ substrate, a P type epitaxial layer, a substrate metal, a P+ sinker region inside the P type epitaxial layer, a P trap, a N- drift region, a N+ region, polycrystalline silicon, and a Faraday cage arranged above the N- drift region and above the right side of the polycrystalline silicon. One layer of low k dielectric material is arranged between the Faraday cage and the drift region, a dielectric constant of the low k dielectric material is less than a dielectric constant of SiO2. An insulation dielectric layer arranged over the drift region and below the Faraday cage is made of low k dielectric material, and the structure can efficiently reduce a high electric field of the Faraday cage near to a drain terminal edge. Compared to a traditional structure, the device can efficiently optimize the electric field distribution on the surface of the drift region so as to uniformize the electric field distribution and improve a breakdown voltage of the device; and the device also can reduce a source-drain on resistance of the device and improve an output power of the device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

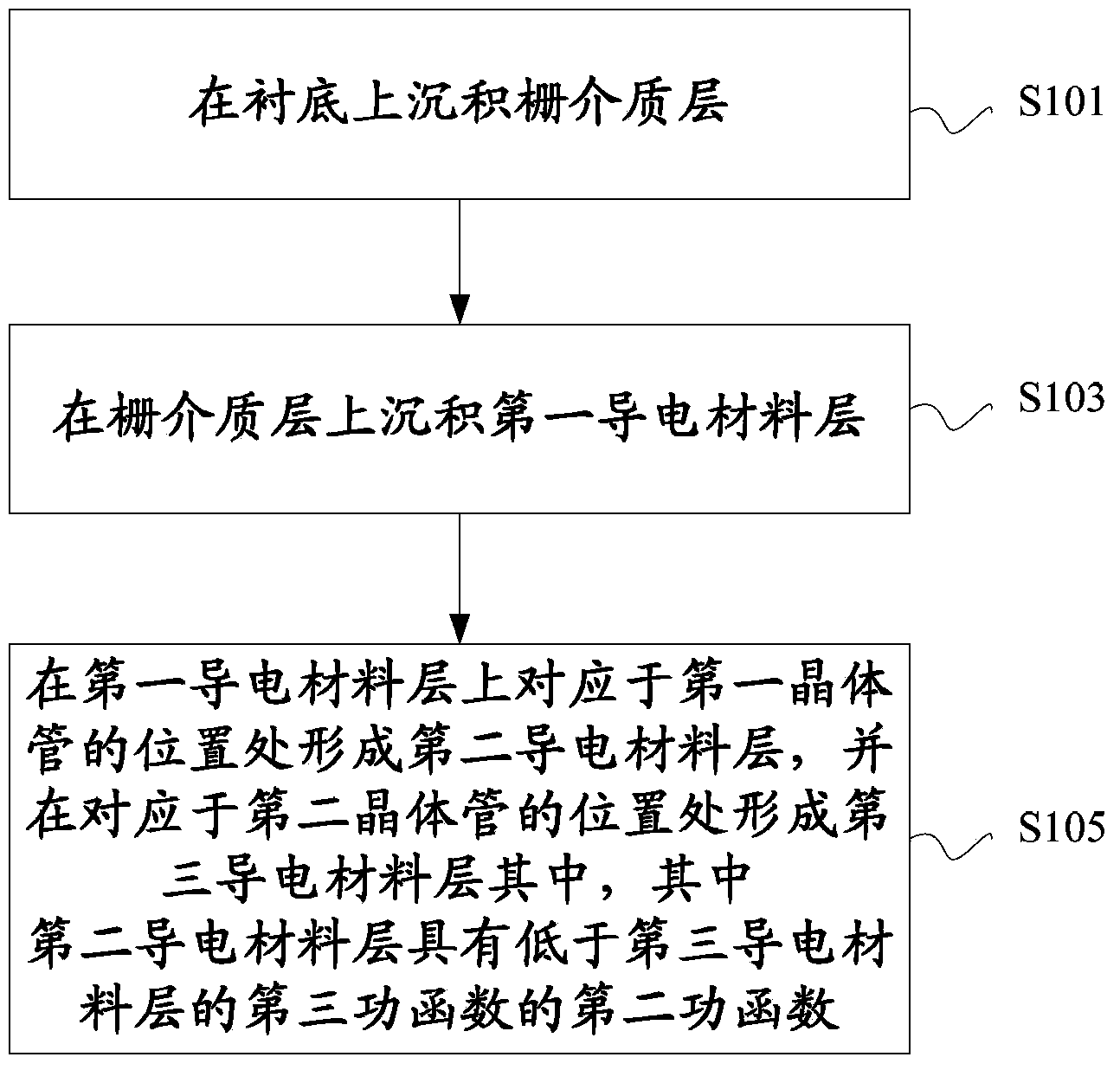

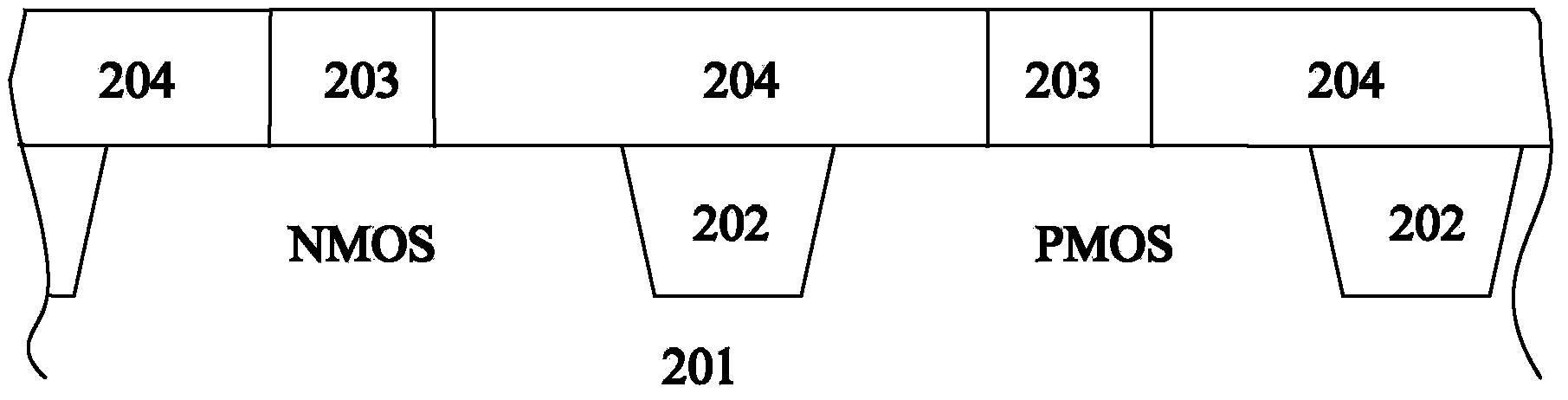

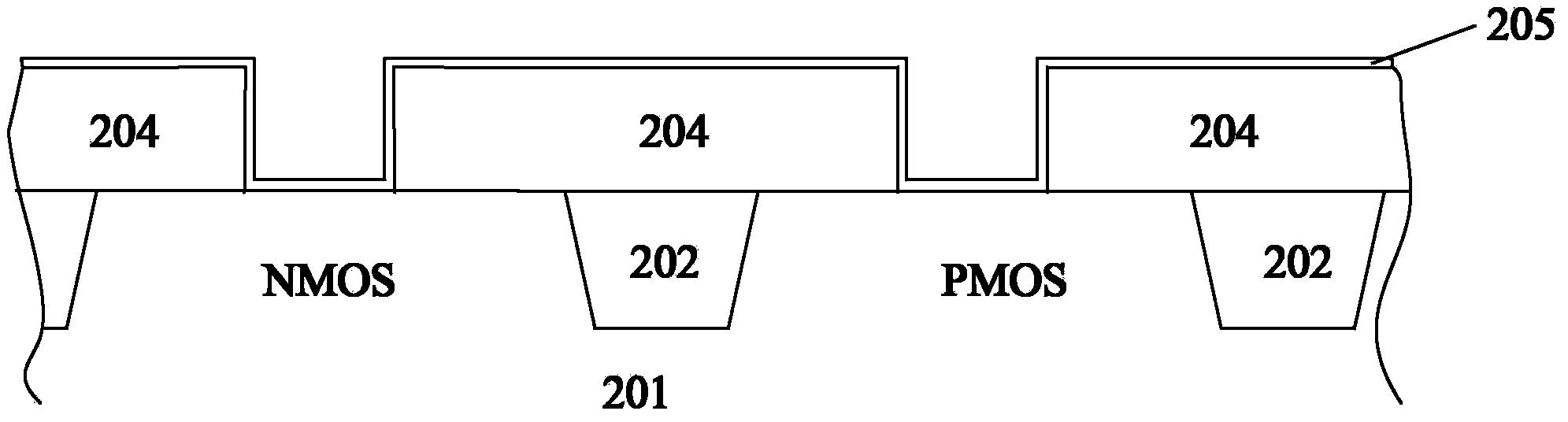

Complementary field effect transistor with double-work function metal gates and manufacturing method thereof

ActiveCN103579113AIncrease saturation currentLower threshold voltageTransistorSolid-state devicesWork functionCMOS

The invention relates to a manufacturing method of a complementary field effect transistor with double-work function metal gates. The complementary field effect transistor comprises a first transistor, a second transistor and an isolation structure used for isolating the first transistor and the second transistor. The manufacturing method is characterized by comprising the steps of depositing a gate dielectric layer on a substrate, depositing a first conducting material layer on the gate dielectric layer, forming a second conducting material layer at the position, corresponding to the first transistor, of the first conducting material layer, and forming a third conducting material layer at the position corresponding to the second transistor, wherein the second conducting material layer has a second work function lower than a third work function of the third conducting material layer. In addition, the invention further relates to the complementary field effect transistor with the double-work function metal gates. By means of the technical scheme, the double-work function metal gates can be obtained through the simple process, so that the large saturation current of a CMOS is obtained, and the threshold voltage is reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Radio-frequency LDMOS (Laterally Diffused Metal Oxide Semiconductor) device and manufacturing method thereof

ActiveCN104538441AIncrease drive currentLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceRadio frequency

The invention discloses a radio-frequency LDMOS (Laterally Diffused Metal Oxide Semiconductor) device. A drift region is in a nonuniform structure formed by a first ion injection region and a second ion injection region; the first ion injection region is self-aligned to a polysilicon gate; the second ion injection region is defined by photoetching and is at a distance from the polysilicon gate; a crossover region of the first ion injection region and the second ion injection region has higher doping concentration which can improve driving current of the device and reduce switch-on resistance of the device; the lower doping concentration of the first ion injection region can reduce the intensity of an electric field on the edge of the polysilicon gate, improve breakdown voltage of the device, reduce injection capacity of a hot carrier on the edge of the polysilicon gate and improve robustness of the device; and the lower doping concentration and great depth of the second ion injection region can reduce output capacitance of the device. The invention further discloses a manufacturing method of the radio-frequency LDMOS device.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Metal oxide semiconductor field effect transistor

ActiveCN101447514AImprove controlIncrease saturation currentSemiconductor devicesPhysicsOxide semiconductor

The invention discloses a metal oxide semiconductor field effect transistor which comprises a semiconductor substrate, a grid insulation dielectric layer which is arranged on the surface of the semiconductor substrate, a grid which is piled on the grid insulation dielectric layer and a source electrode area and a drain electrode area which are arranged in the surface area of the semiconductor substrate at two sides of the grid and are separated by a channel region. A first part of the grid insulation dielectric layer is close to the drain electrode area, a second part thereof is close to the source electrode area, and the thickness of the first part is thicker than the thickness of the second part. The thickness of the second part near the source electrode area of the metal oxide semiconductor field effect transistor is thinner, thereby improving the control capacity of the grid on the channel, increasing saturation current, improving the drive capacity of the apparatus and also reducing the area of the apparatus. The thickness of the first part near the drain electrode area is thicker, thereby controlling leakage current caused by GIDL effect.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

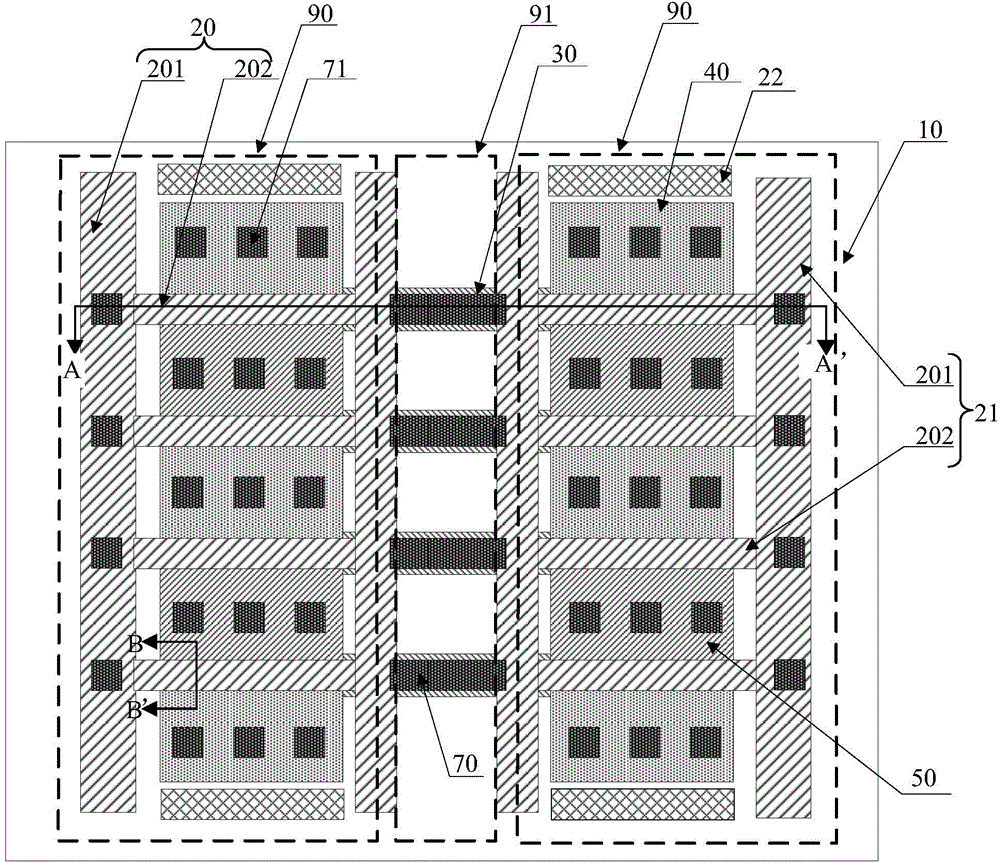

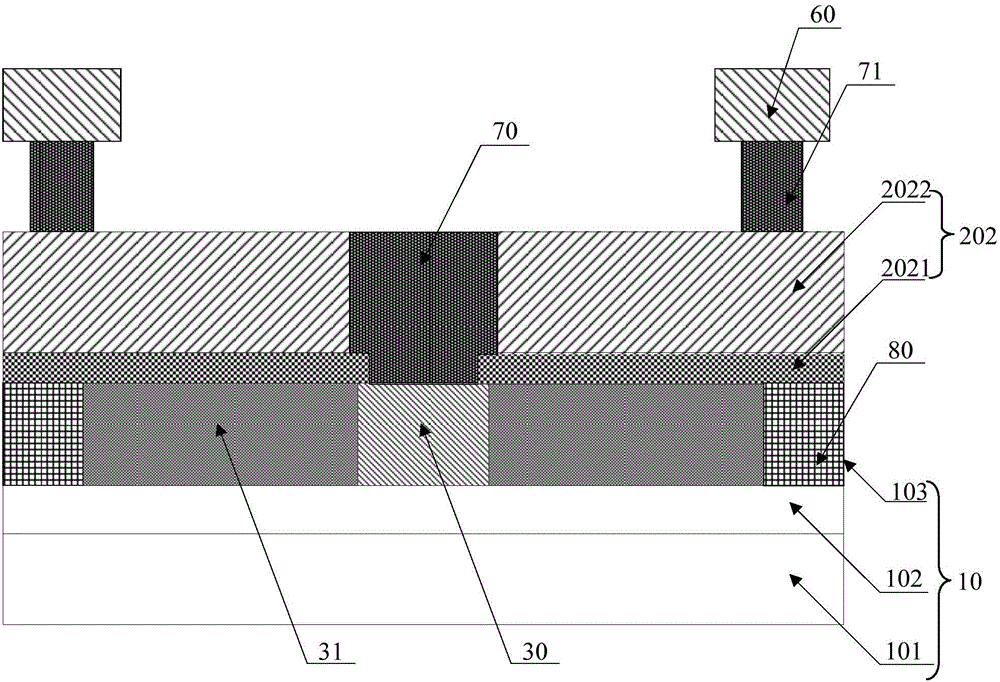

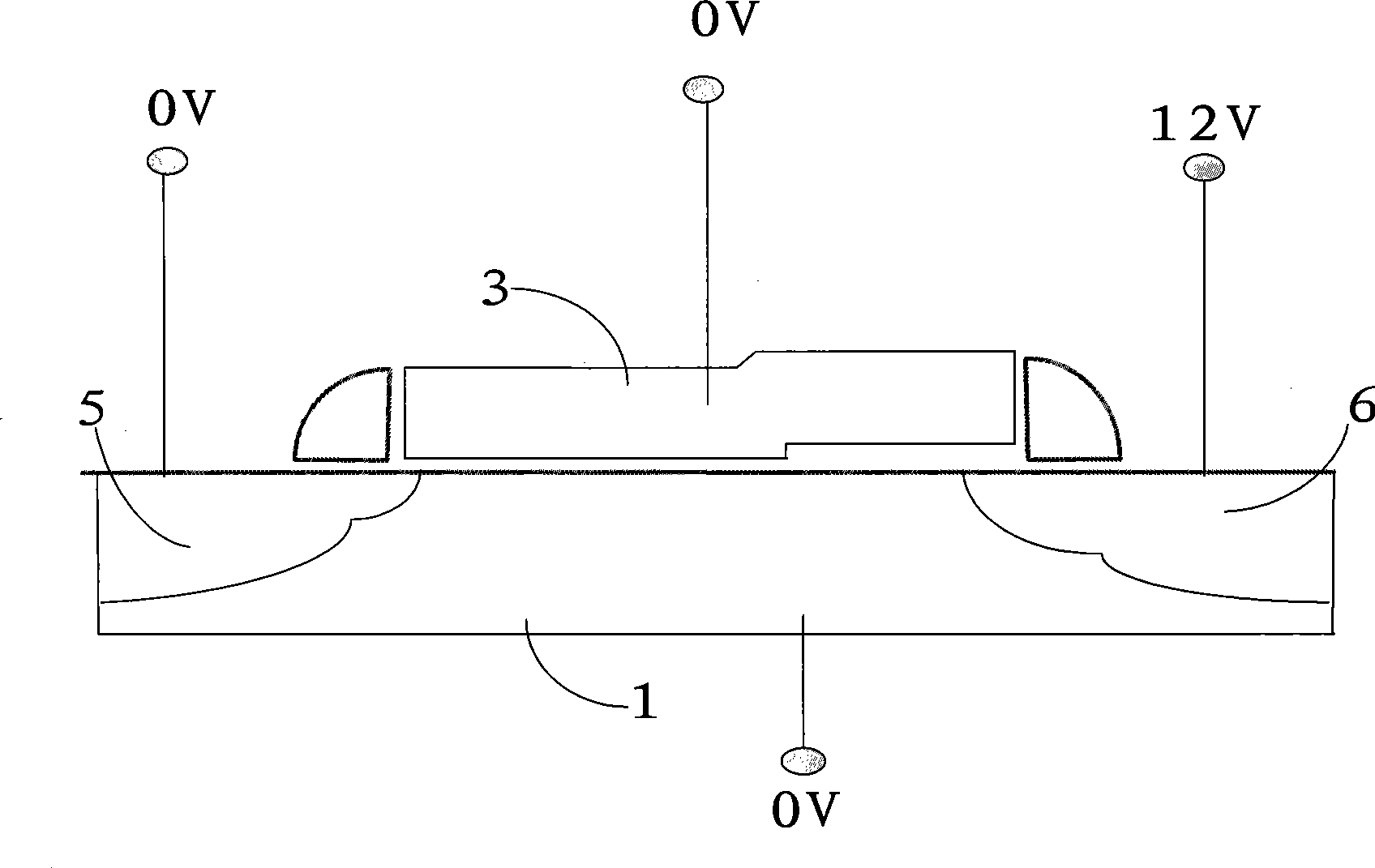

Gallium oxide vertical structure semiconductor electronic device and manufacturing method thereof

InactiveCN110634950ASimple structureIncrease saturation currentSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsBlock layer

The invention discloses a gallium oxide vertical structure semiconductor electronic device and a preparation method thereof. The gallium oxide vertical structure semiconductor electronic device comprises a buffer layer, a current blocking layer and a channel layer which are arranged in sequence, wherein current through holes formed through ion implantation processing are further distributed in thecurrent blocking layer; a source electrode and a gate electrode are arranged on the channel layer; the buffer layer is connected with a drain electrode; the drain electrode and the current blocking layer are arranged back to back; the current through holes are located below the gate electrode; and the channel layer is electrically connected with the buffer layer through the current through holes.The gallium oxide vertical structure semiconductor electronic device provided in the invention is simple in structure, can well meet the requirements of a high-power switch, has a series of advantages of large saturation current, high breakdown voltage and the like, greatly exerts the characteristics of a Ga2O3 material, and plays a greater role in the field of power semiconductor electronic devices.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

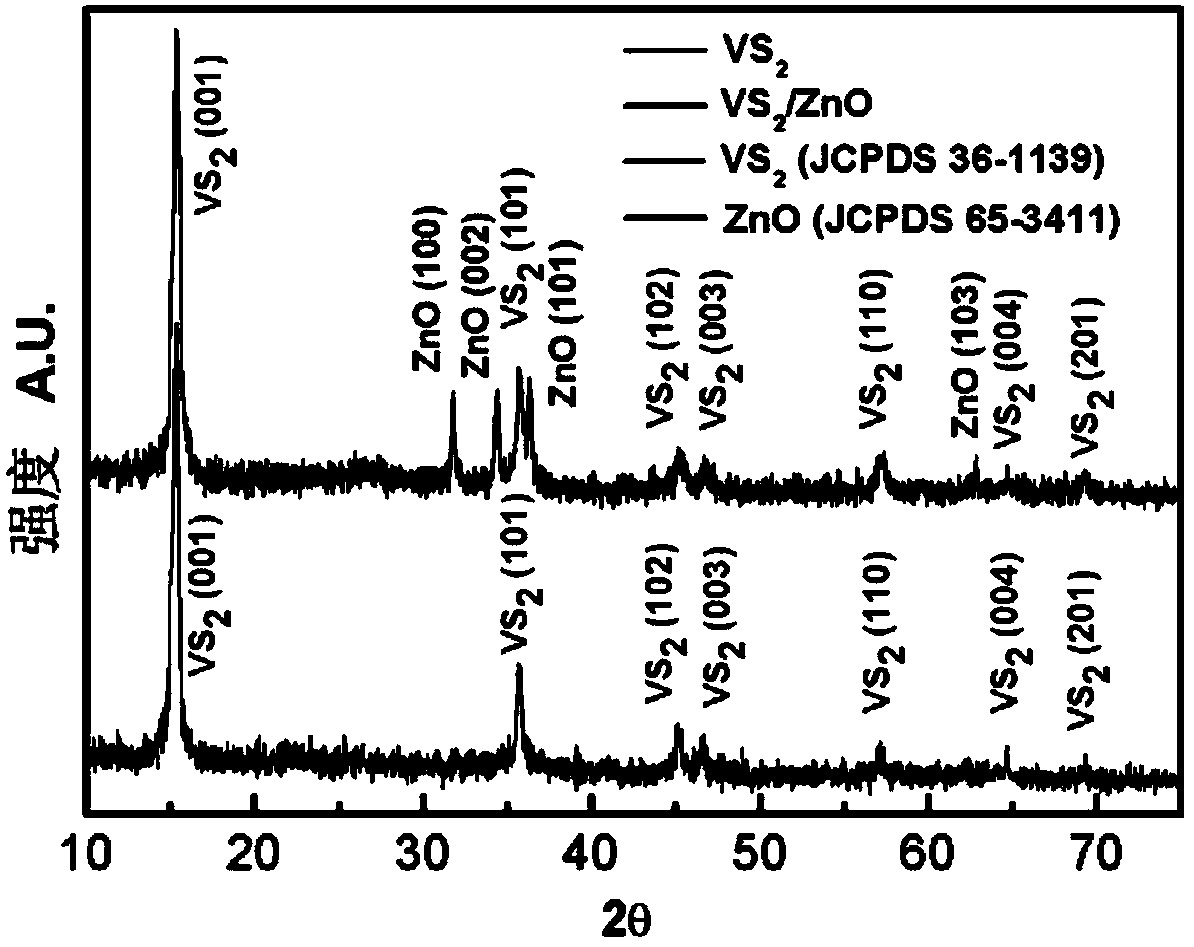

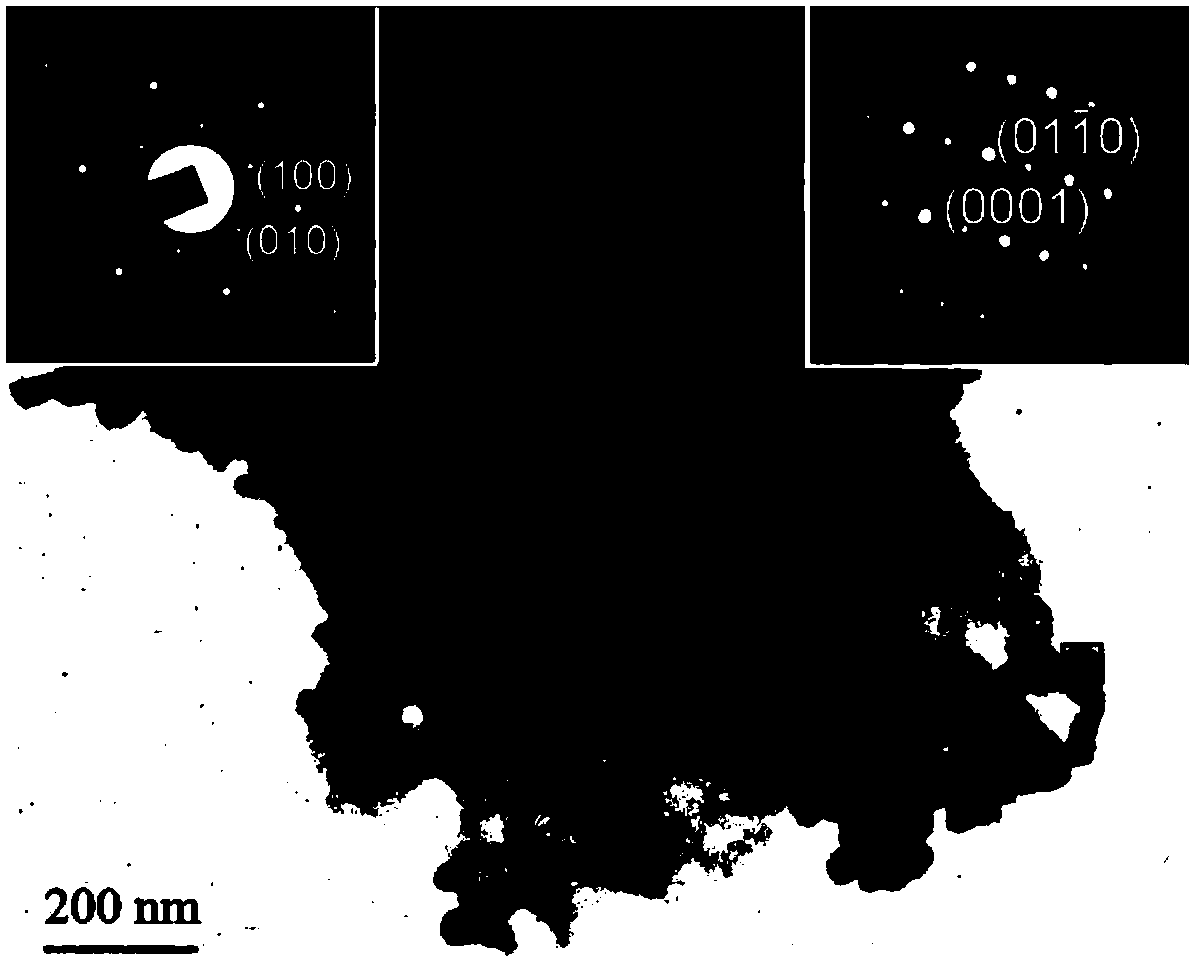

Flexible field electron emission cathode material based on three-dimensional VS2/Zno composite nano-structure and preparation method thereof

InactiveCN103762133ASolve the problem of launch stabilityReduce manufacturing costMaterial nanotechnologyDischarge tube/lamp detailsNano structuringPolyethylene terephthalate glycol

The invention discloses a three-dimensional VS2 / Zno composite nano-structure and a preparation method. The three-dimensional VS2 / Zno composite nano-structure comprises VS2 nano-sheet and ZnO nano-particles, the VS2 nano-sheet serves as a framework, the ZnO nano-particles are evenly distributed on the surface and the edge of the VS2 nano-sheet to form the VS2 / Zno composite nano-structure. The invention further provides a flexible reinforced PET (polyethylene terephthalate) substrate field electron emission cathode material based on three-dimensional VS2 / Zno composite nano-structure and a preparation method. The preparation method has the advantages of being low in cost, simple in preparation condition, high in complexity and the like. In addition, impurities are less. The three-dimensional VS2 / Zno composite nano-structure and the field electron emission cathode material are high in crystallinity, stable in structure and large in specific area, the edge is ultrathin, and excellent flexible field electron emission performance is achieved.

Owner:EAST CHINA NORMAL UNIV

High-voltage-resistant bigrid transverse HEMT device and preparation method thereof

ActiveCN113113469AIncrease saturation currentImprove breakdown voltageFinal product manufactureSemiconductor/solid-state device manufacturingHeterojunctionLow leakage

The invention relates to a high-voltage-resistant bigrid transverse HEMT device, which comprises a buffer layer positioned on a substrate, and a laminated layer consisting of a GaN channel layer, an AlN insertion layer and an AlGaN barrier layer which are sequentially laminated on the buffer layer, and also comprises a p-type buried layer, a grid positioned on the p-type buried layer, and a source / drain electrode and an inverted L-shaped grid which are positioned on the barrier layer; in the thickness direction, the p-type buried layer extends by a certain depth from the surface, close to the channel layer, of the buffer layer to the side, away from the channel layer, of the buffer layer; the source and the drain are located on the surface of the barrier layer; a gate groove is formed between the source electrode and the drain electrode, and the inverted L-shaped gate is located in the gate groove and extends towards one side of the drain electrode; and in the length direction, the p-type buried layer extends from the position below the grid electrode to the position below the grid groove. Through the introduction of the p-type buried layer and the structural arrangement of double gates combined with the AlGaN / AlN / GaN heterojunction, the HEMT device with low on-resistance, high saturation current, high breakdown voltage and low leakage current is obtained.

Owner:SOUTH CHINA NORMAL UNIVERSITY

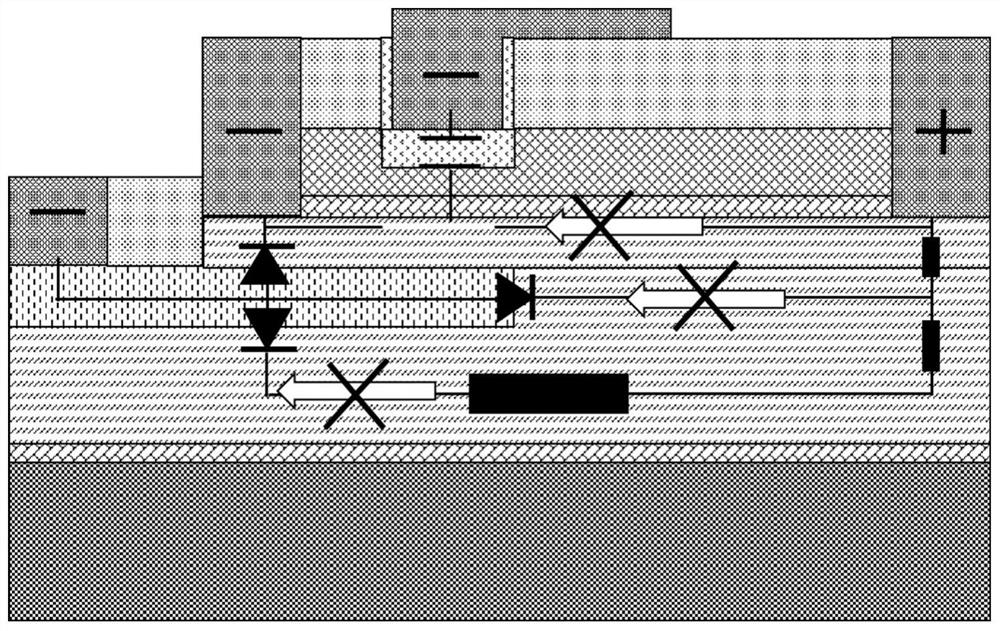

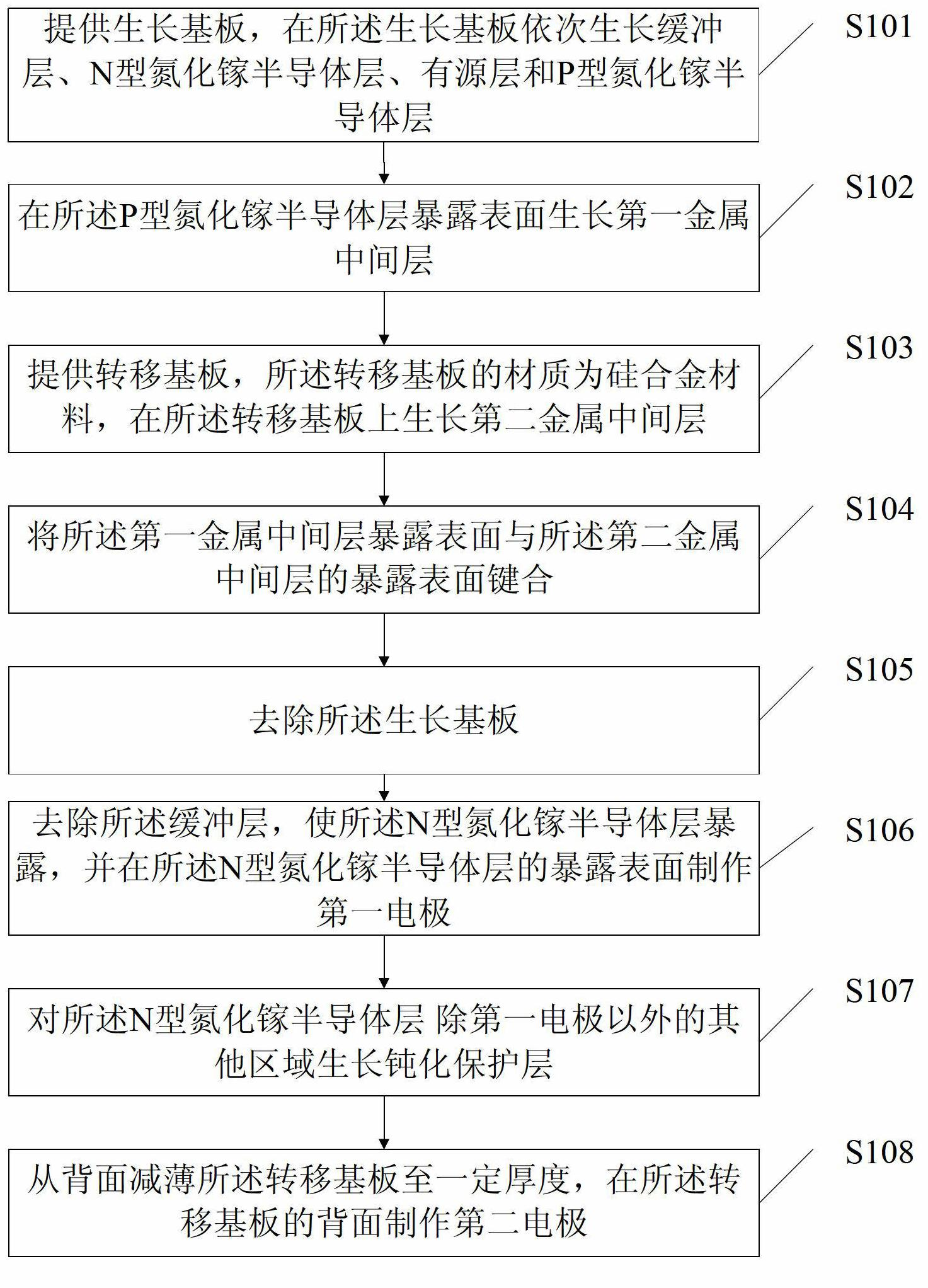

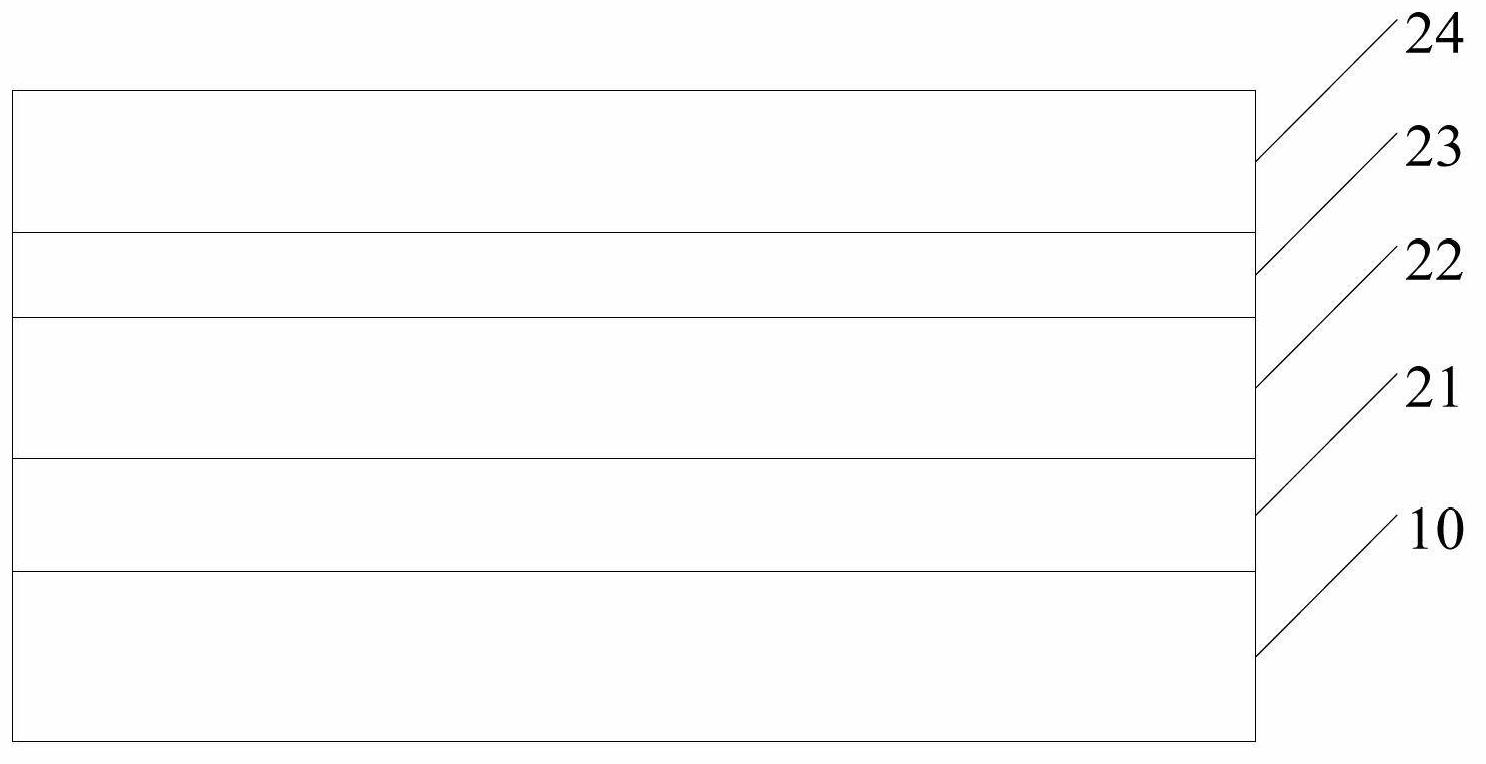

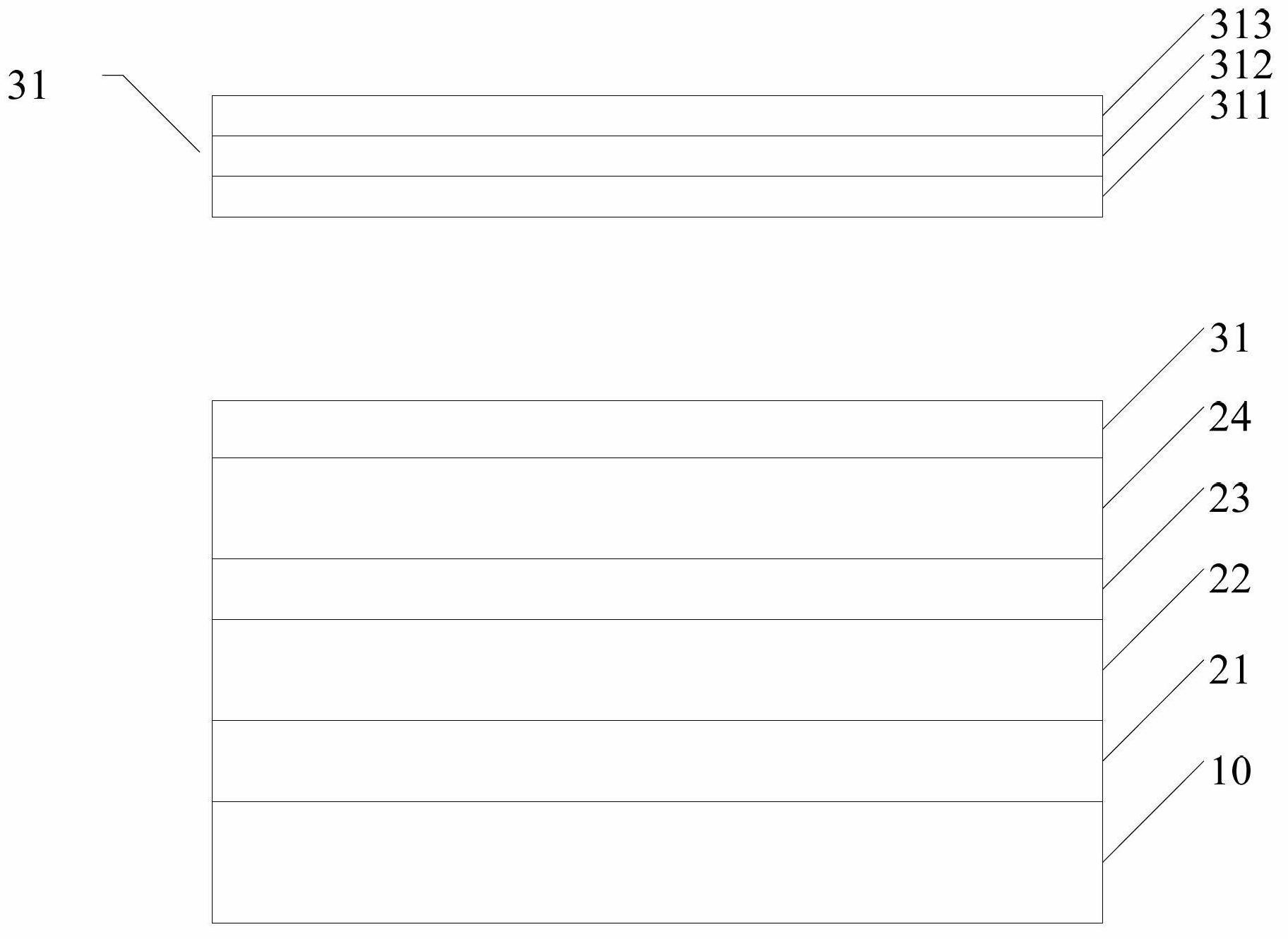

Inversed LED (Light Emitting Diode) chip structure and preparation method of inversed LED chip

InactiveCN102683524AReduce warpageIncrease saturation currentSemiconductor devicesSilicon alloyThermal expansion

The invention provides an inversed LED (Light Emitting Diode) chip structure which comprises a silicon alloy substrate, a metal middle layer, a P-type gallium nitride semiconductor layer, an active layer and a N-type gallium nitride semiconductor layer sequentially stacked from bottom to top. According to the inversed LED chip structure, a transfer substrate made of silicon alloy which is approximate to a growth substrate in thermal expansion coefficient is adopted as the substrate of the LED chip to reduce the staggered damage of lattices of an LED chip apparatus layer, therefore, the leakage current is reduced, and the performance of product is improved. The invention further provides a preparation method of the inversed LED chip structure.

Owner:HANGZHOU SILAN AZURE