Patents

Literature

67results about How to "Improve forward conduction characteristics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Silicon carbide TrenchMOS device and manufacturing method thereof

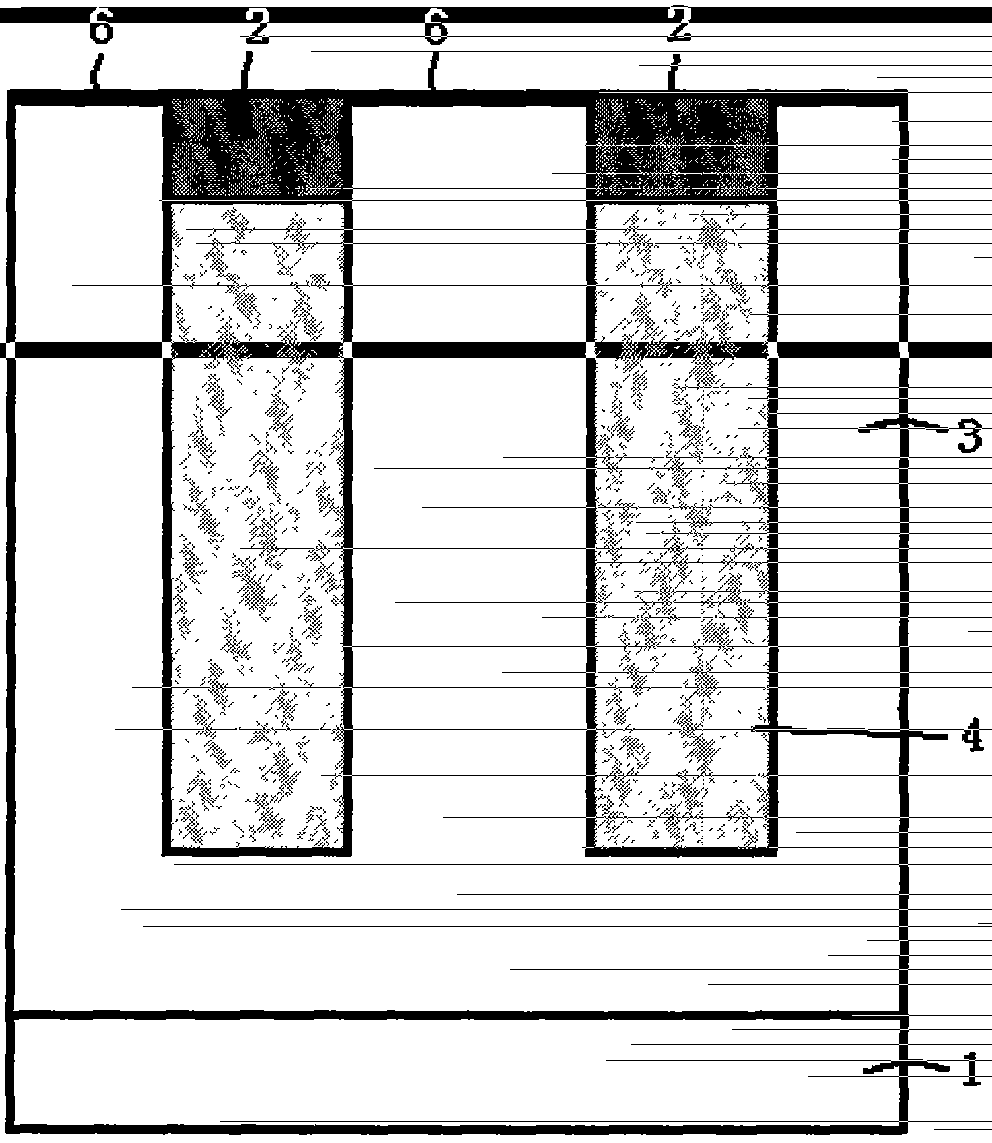

ActiveCN107256864AImprove performanceReduce power lossTransistorSolid-state devicesHeterojunctionReverse recovery

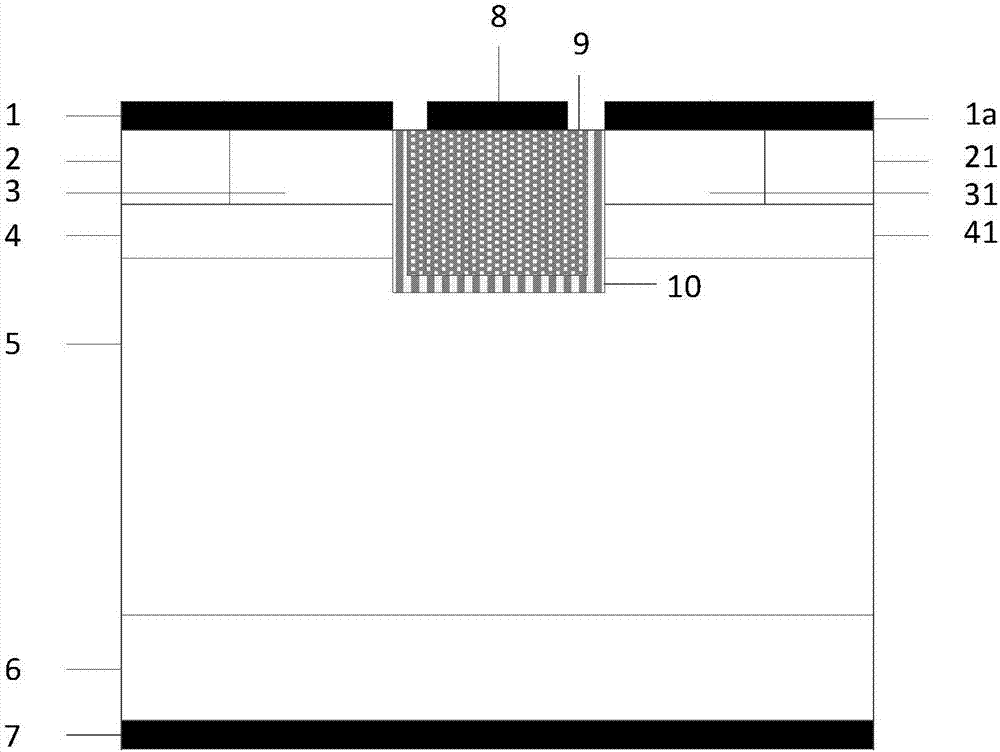

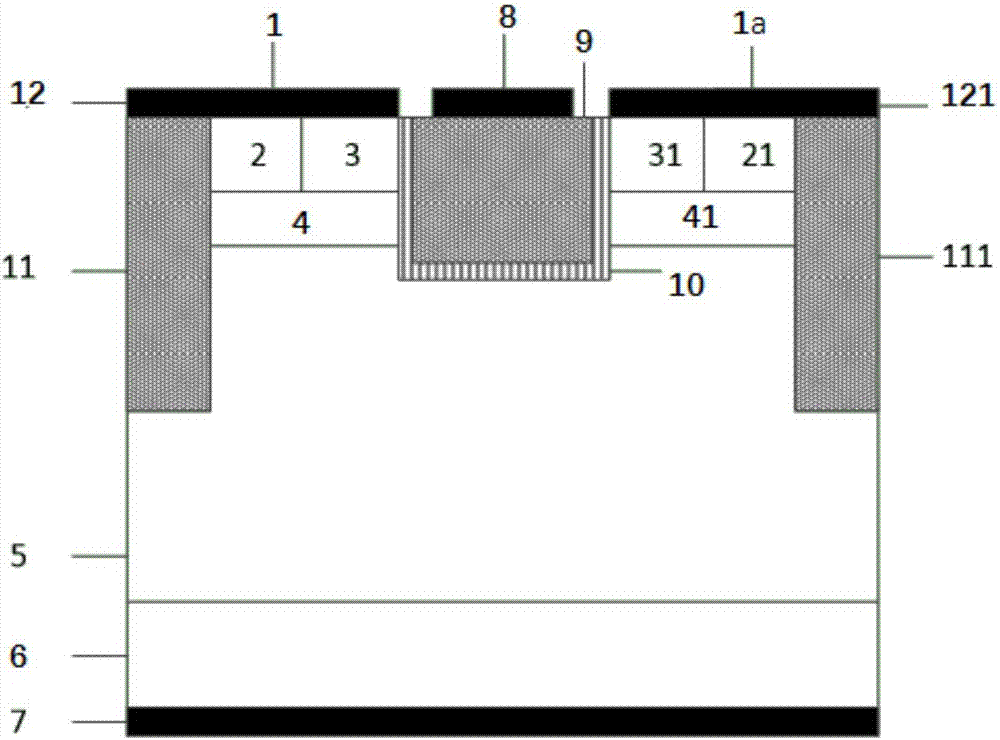

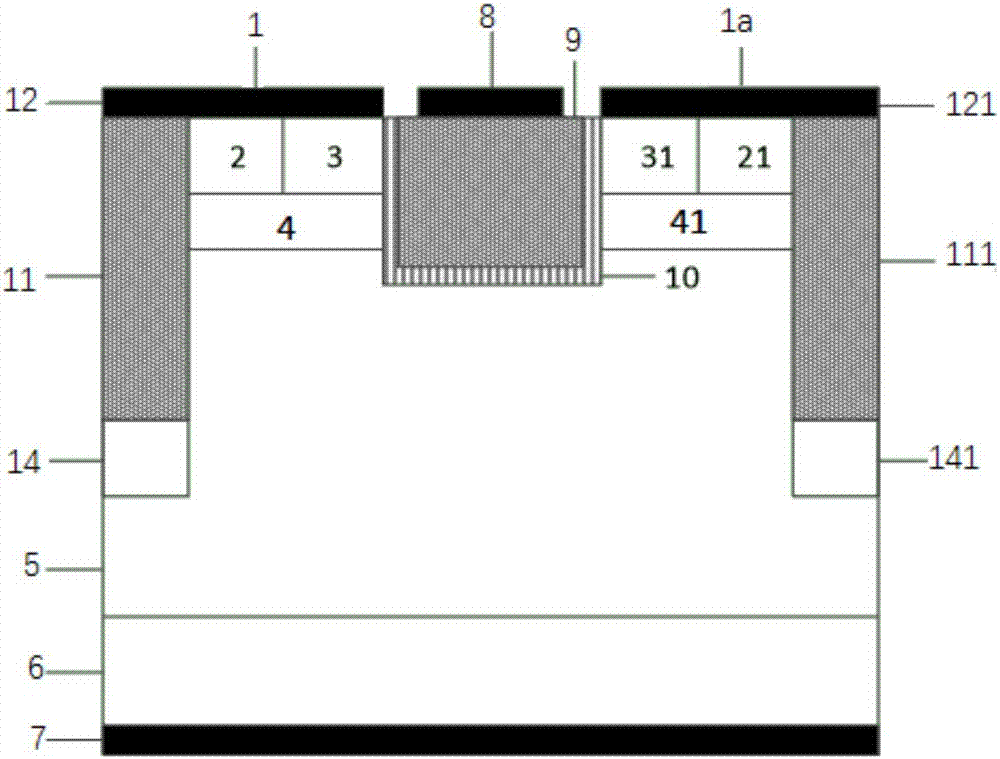

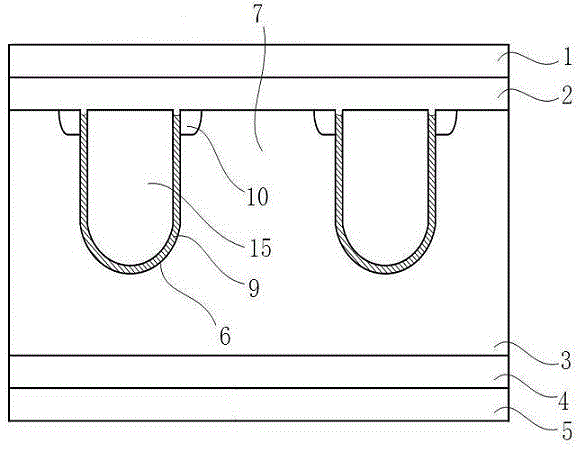

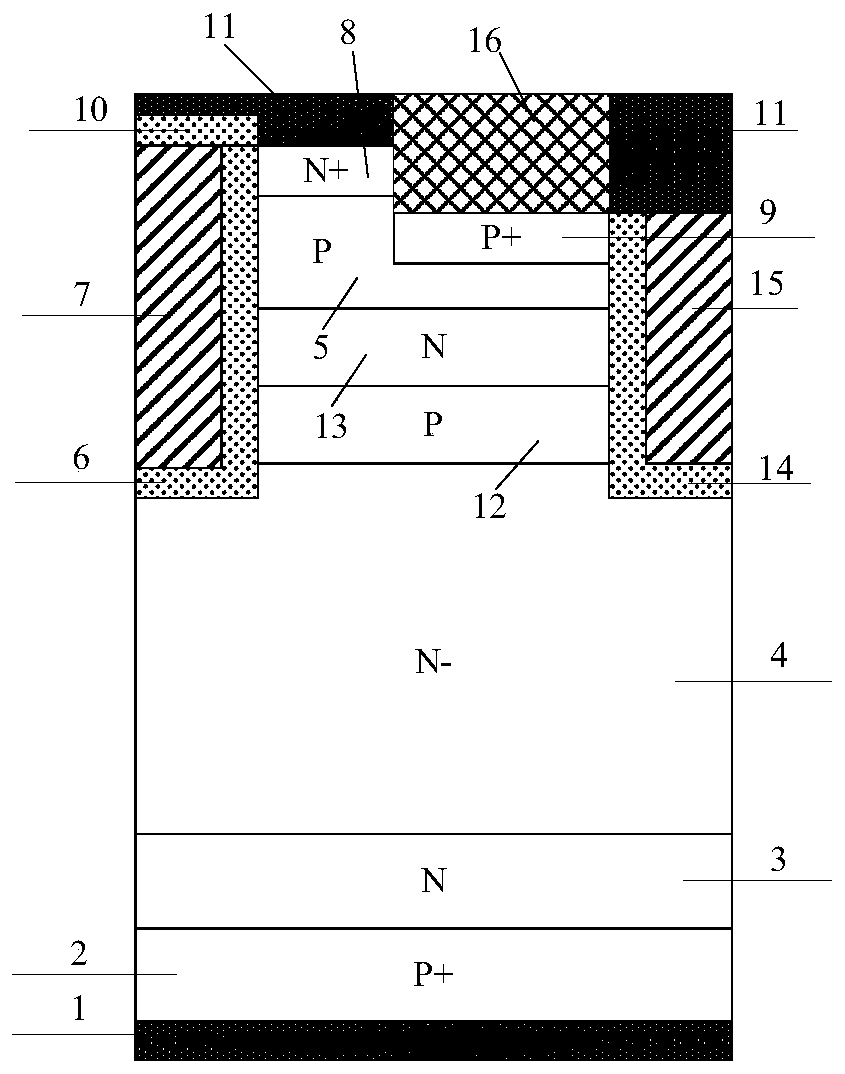

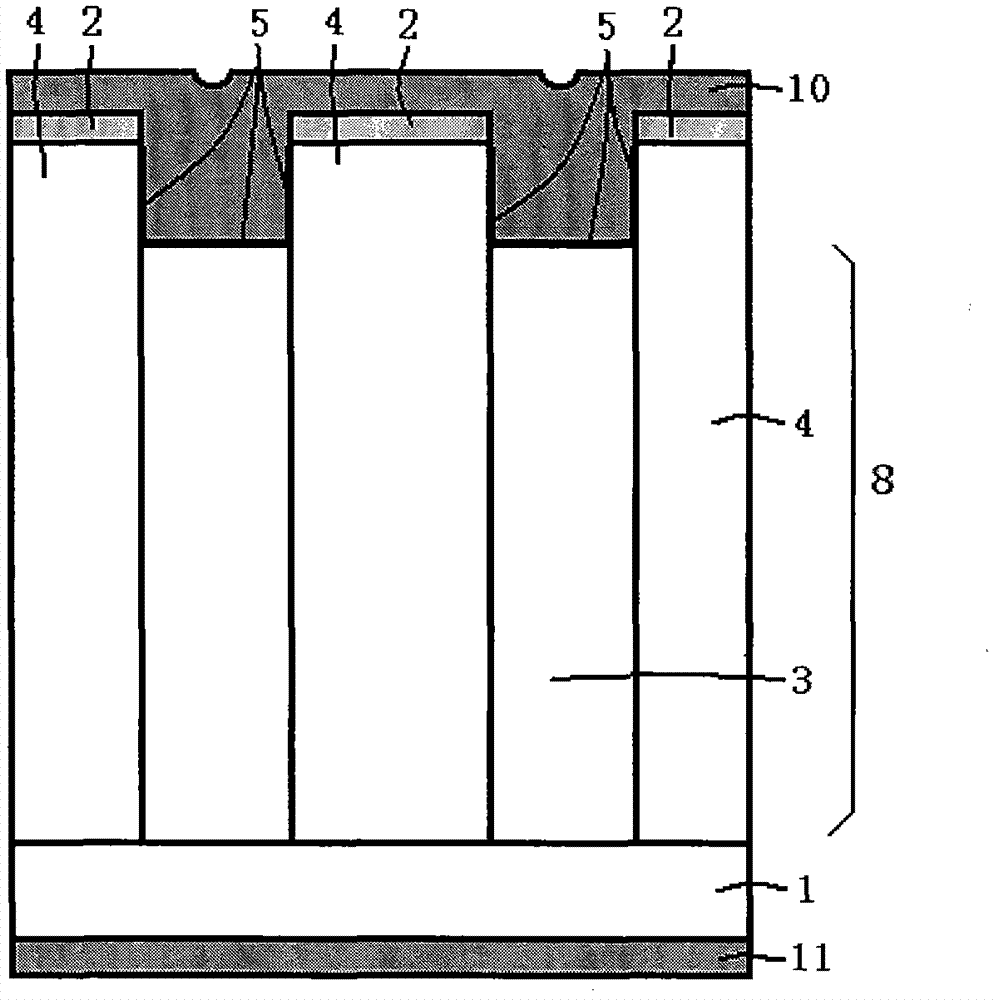

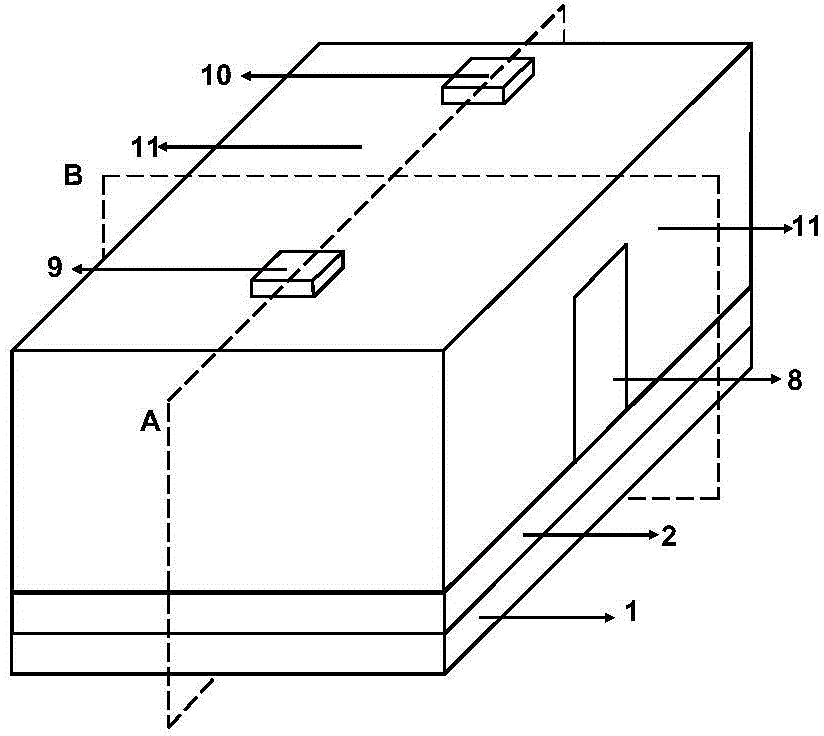

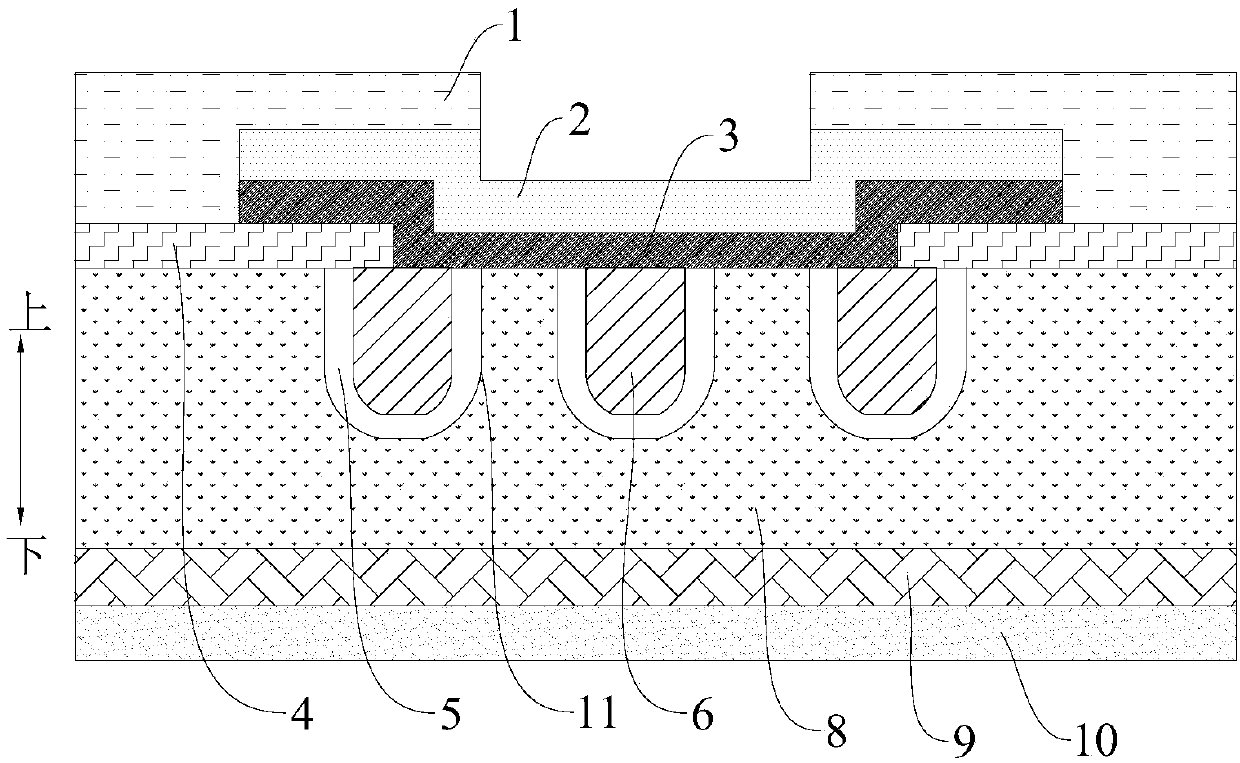

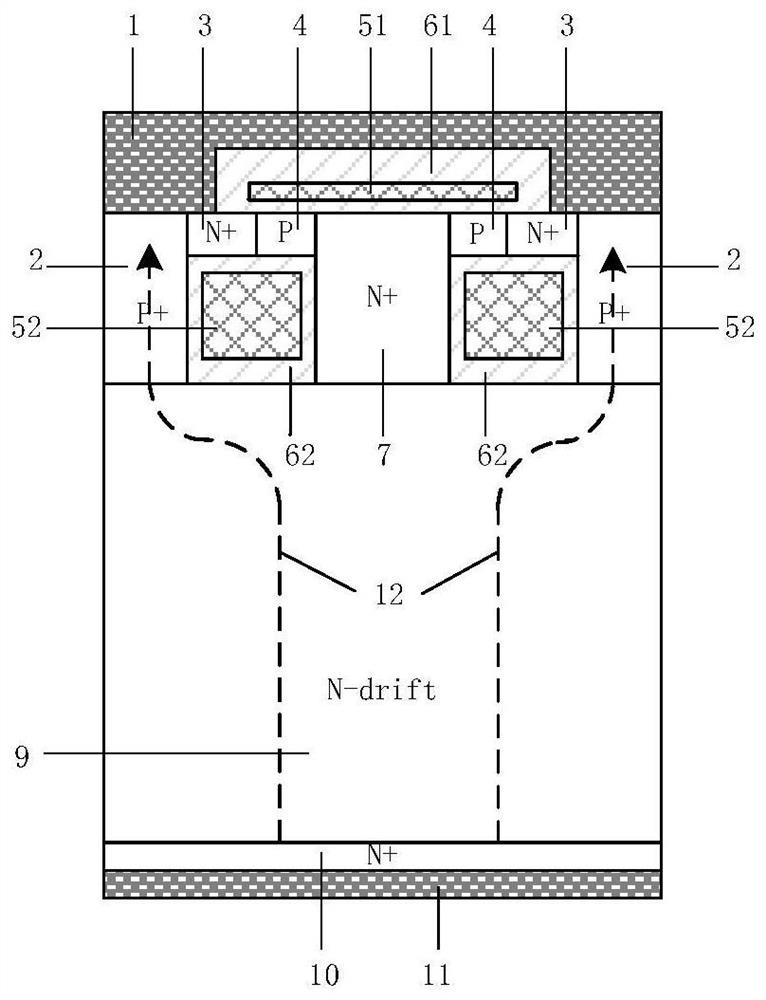

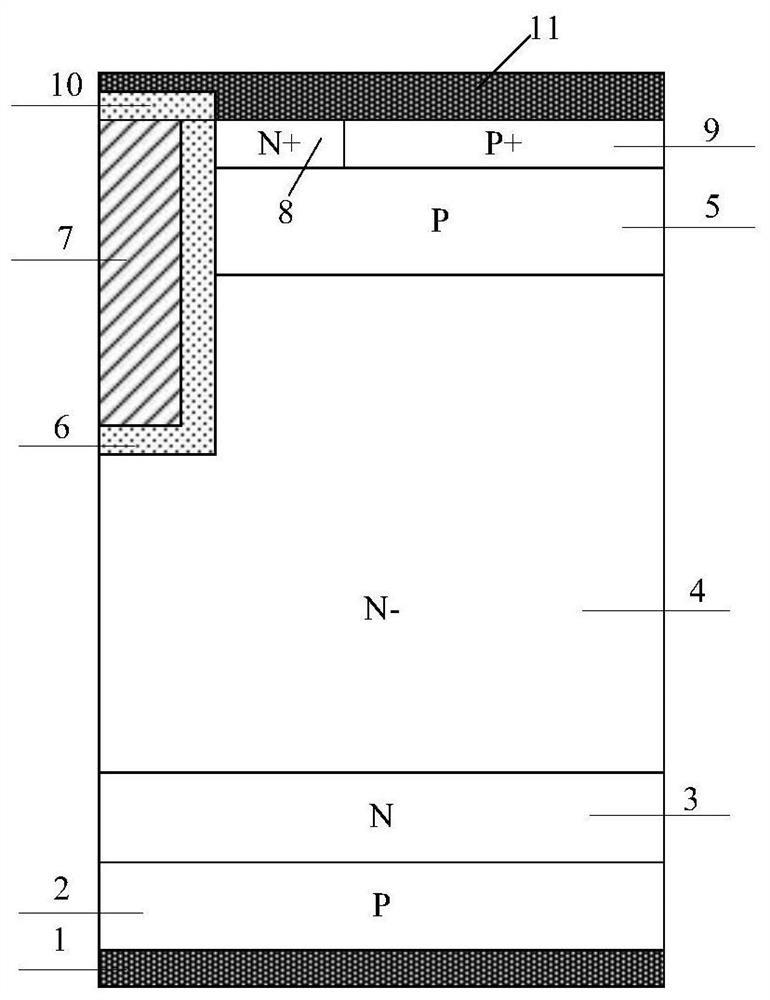

The invention discloses a silicon carbide TrenchMOS device and manufacturing method thereof, belonging to the technical field of power semiconductors. Considering the defects of an external anti-parallel fast recovery diode (FRD) and a parasitic diode directly using a silicon carbide TrenchMOS device, a polysilicon area is additionally arranged in the p+ contact area of a conventional device, so that a Si / SiC heterojunction is formed by the polysilicon and silicon carbide epitaxial layer material, and furthermore, a diode is integrated in the device. The junction voltage drop is significantly reduced when a device diode is applied, and the conductive mode during the diode application is converted from bipolar conduction into single polar conduction, so that the silicon carbide TrenchMOS device has the advantages of short reverse recovery time and less reverse recovery charge. The device structure also has the advantages of low parasitic silicon carbide diode reverse leakage, high breakdown voltage and good device temperature stability. Therefore, the silicon carbide TrenchMOS device has wide prospects in circuits such as an inversion circuit and a chopper circuit.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

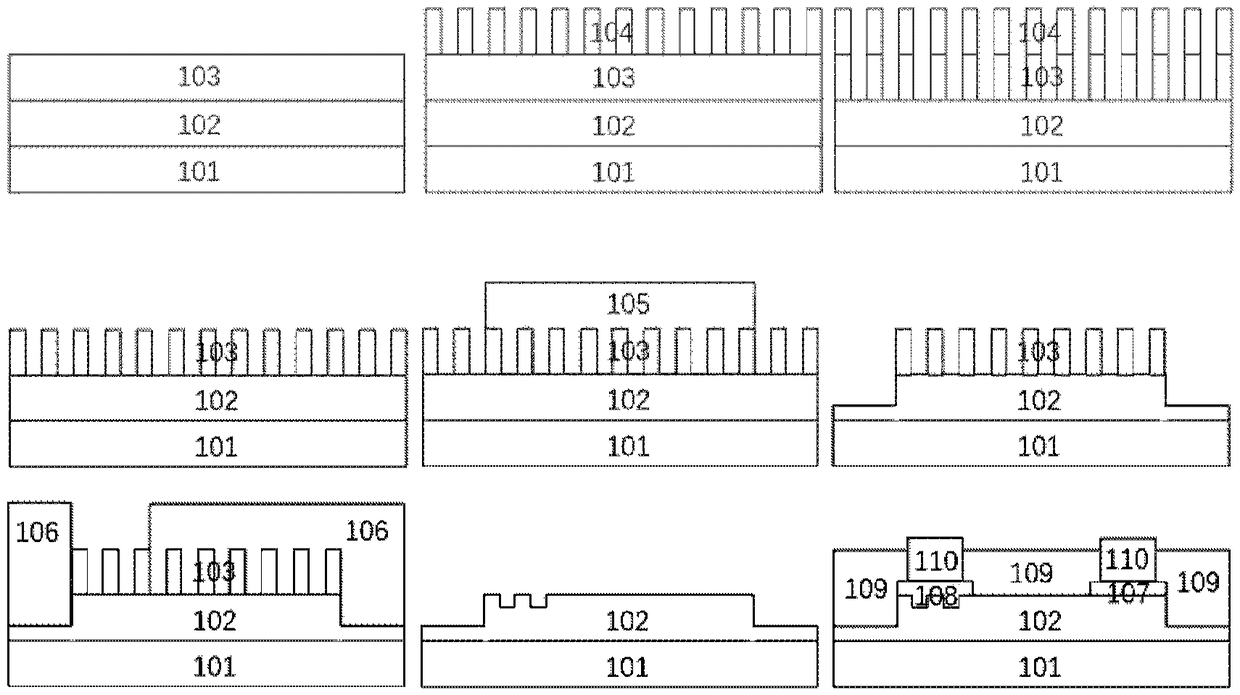

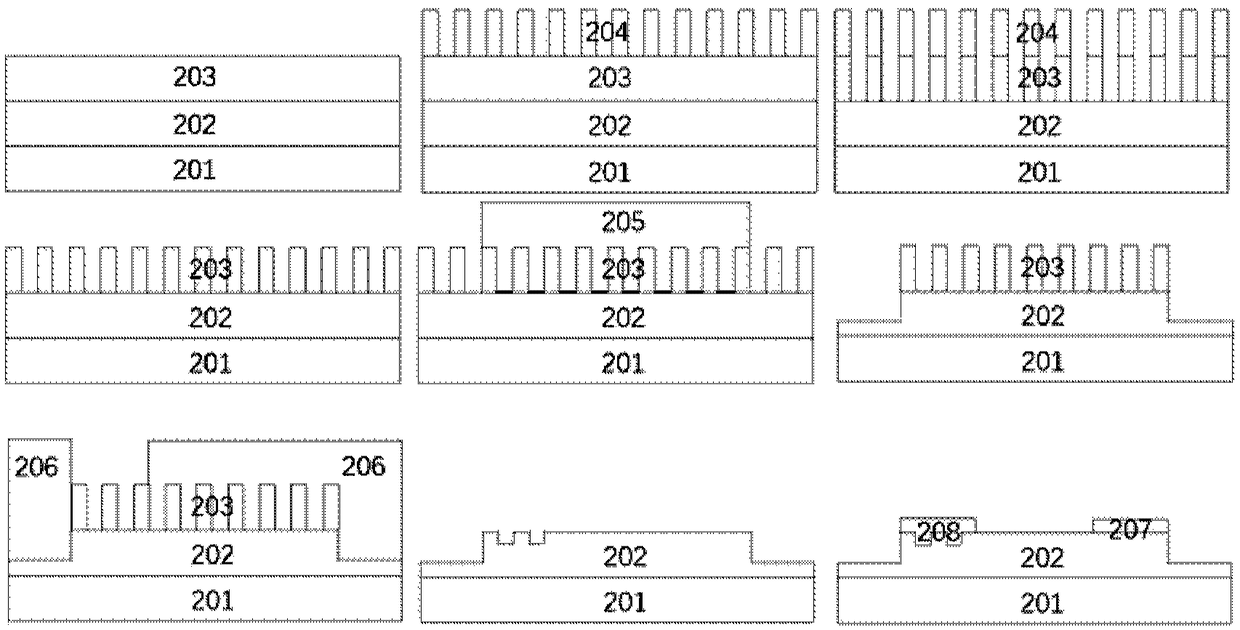

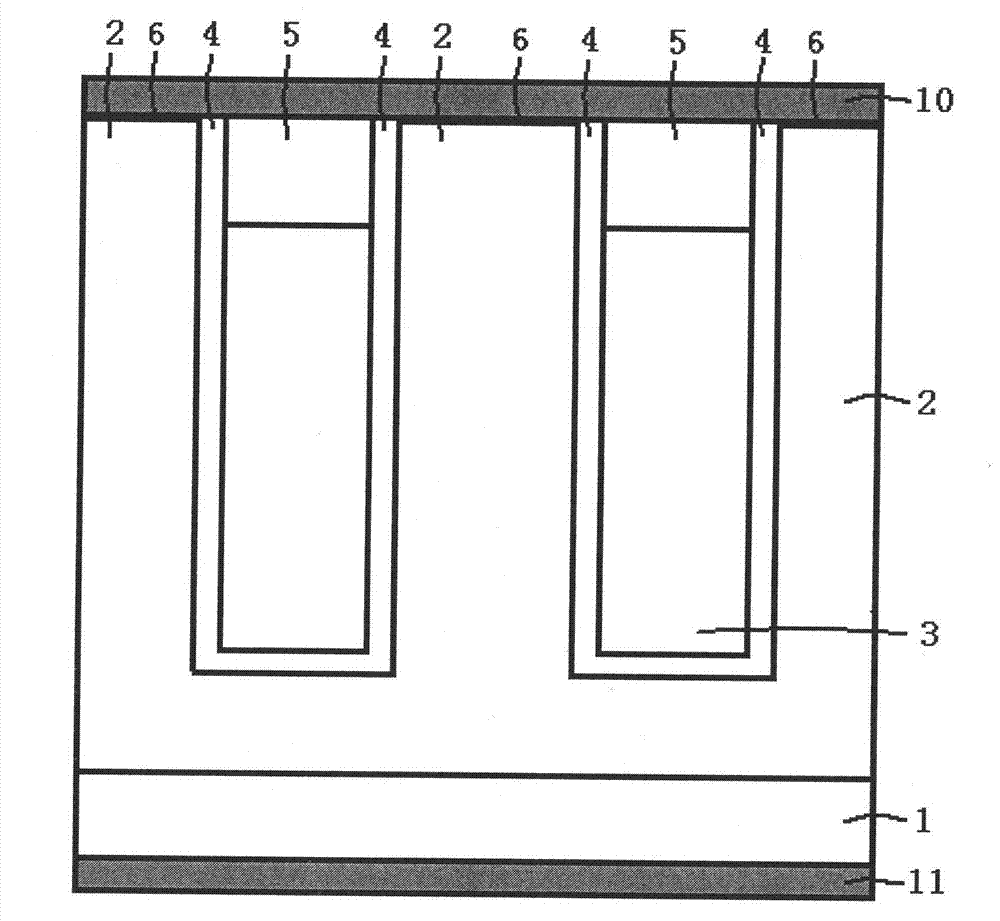

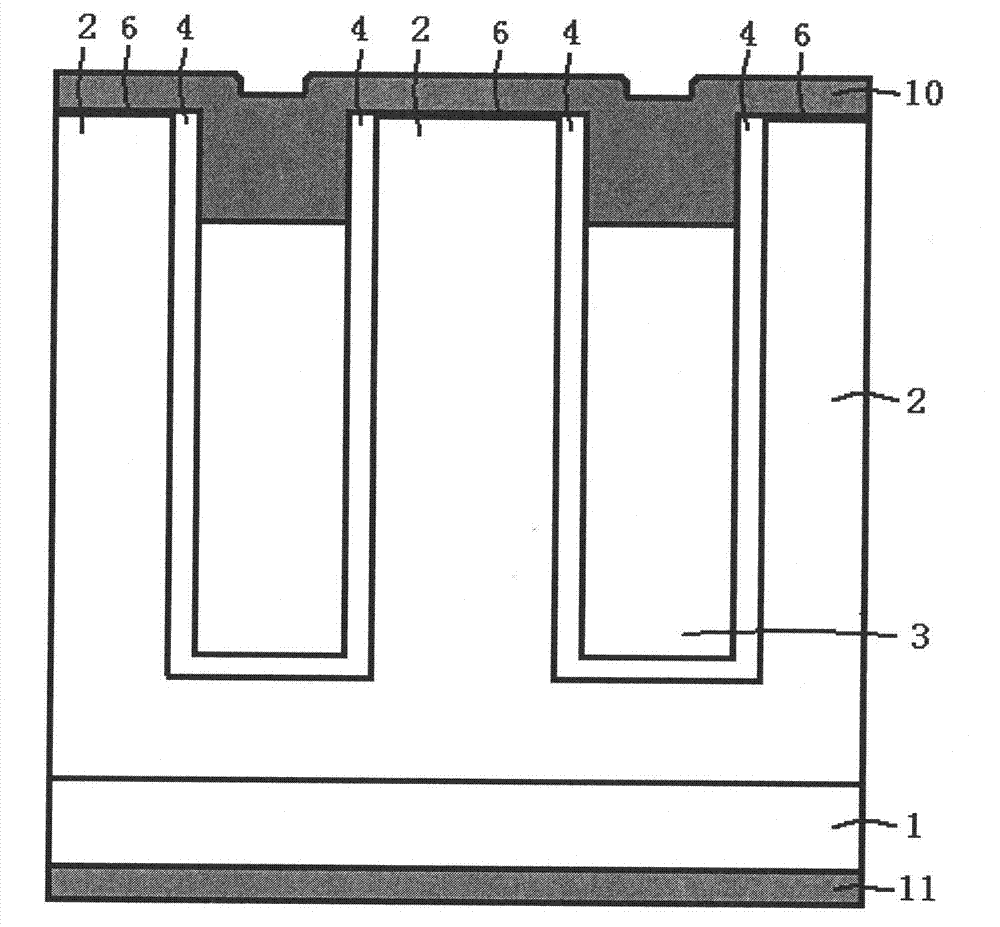

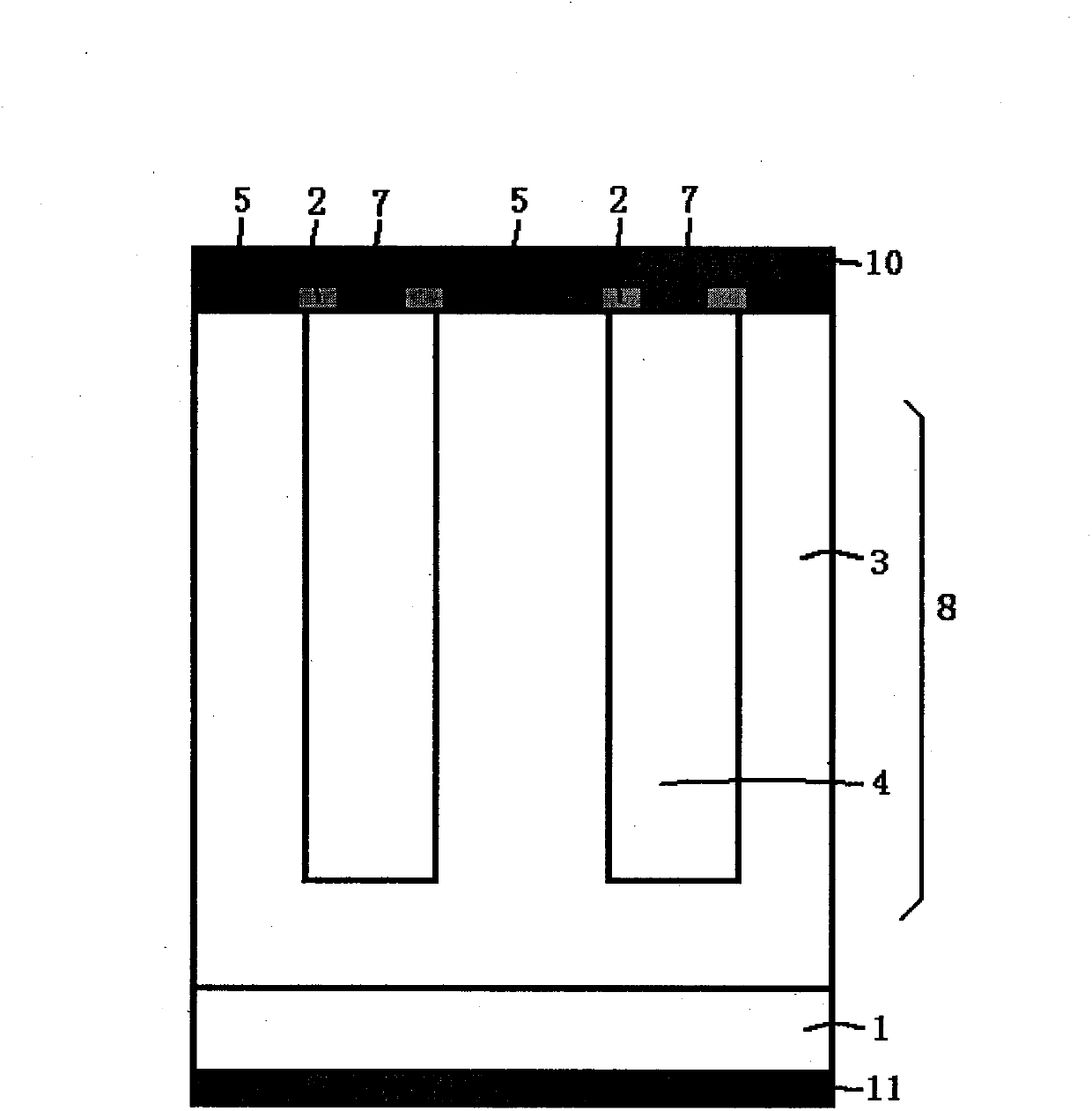

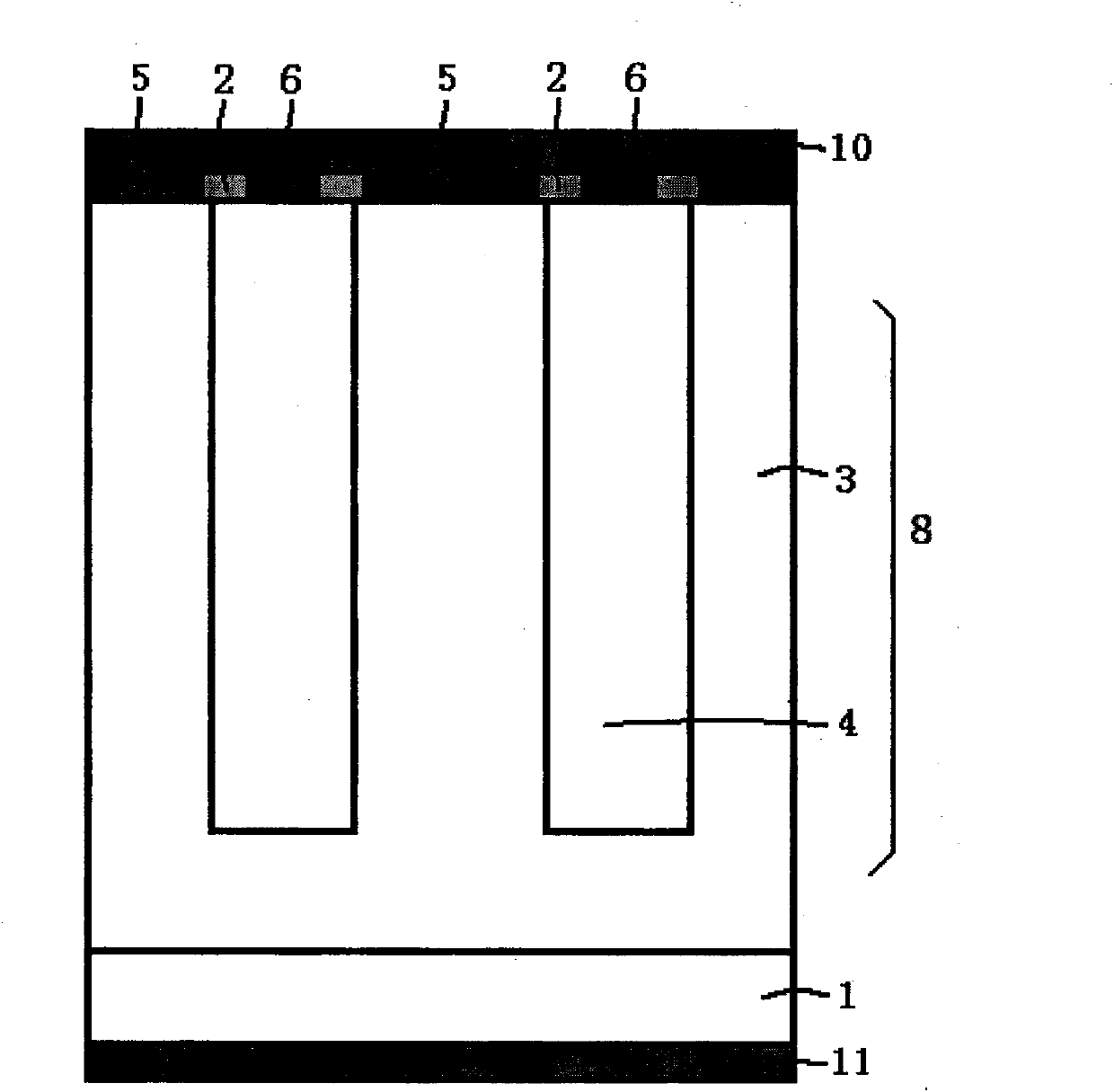

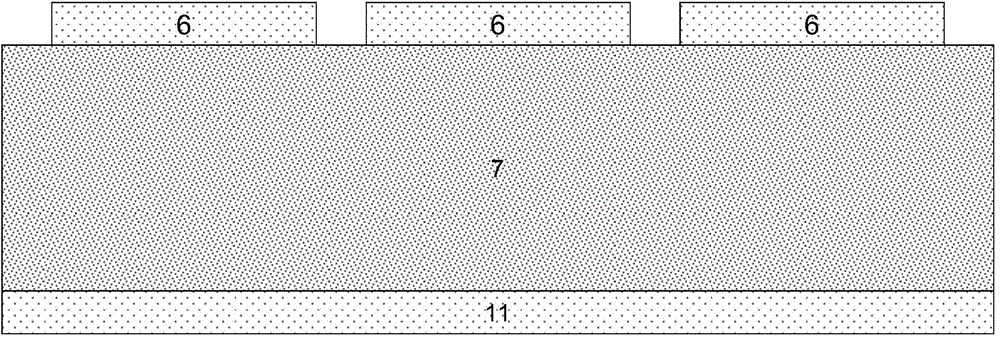

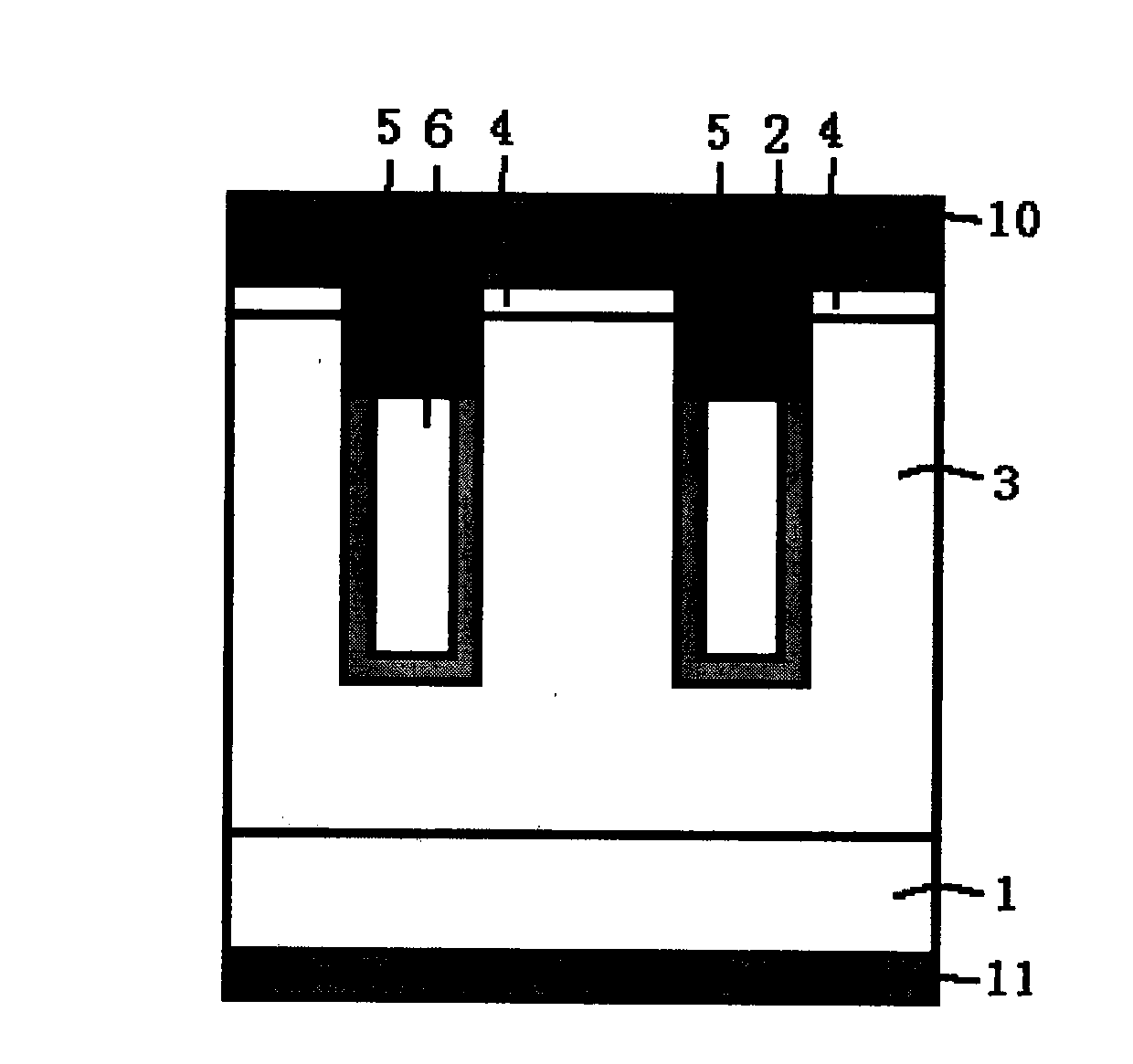

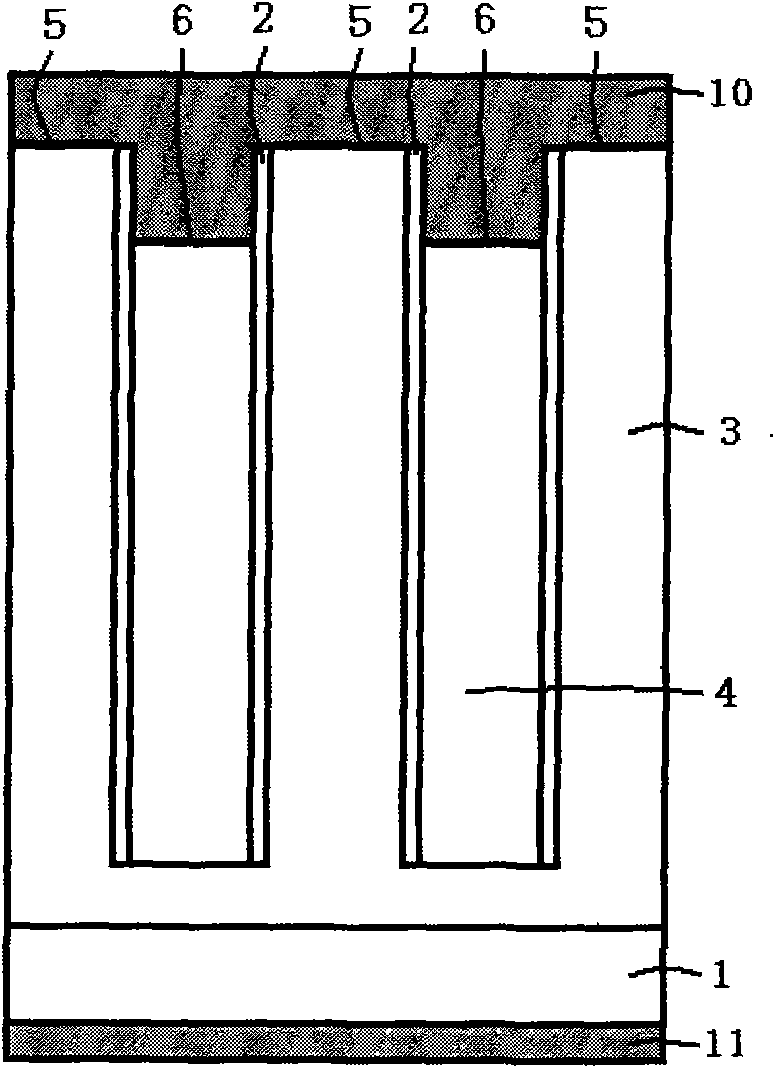

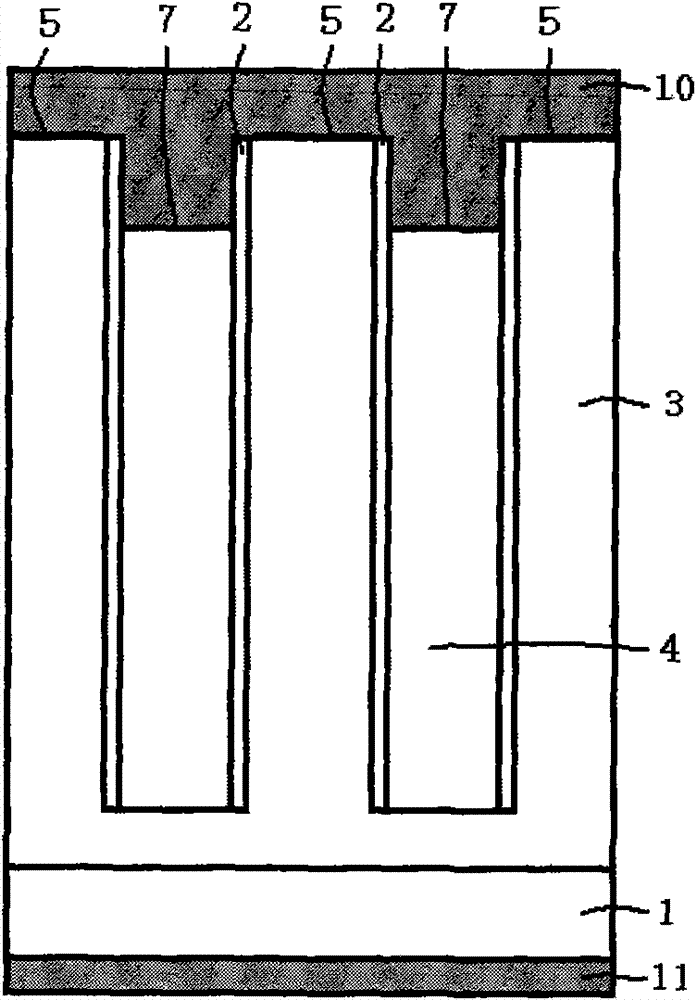

Trenched Schottky-barrier diode and manufacturing method thereof

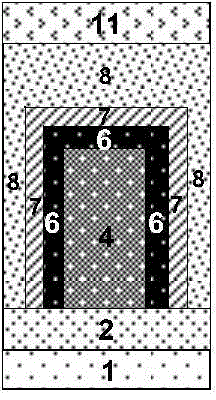

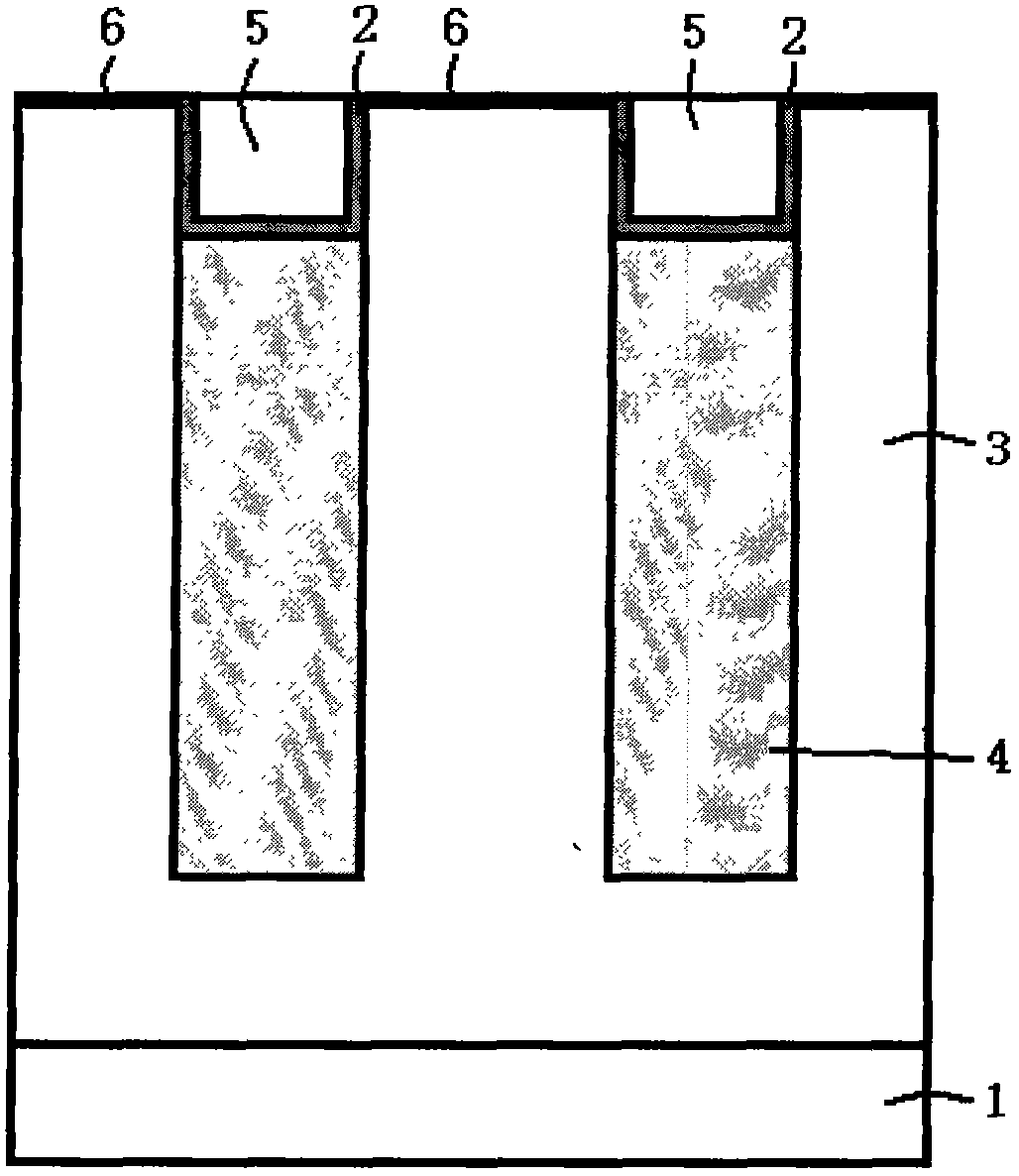

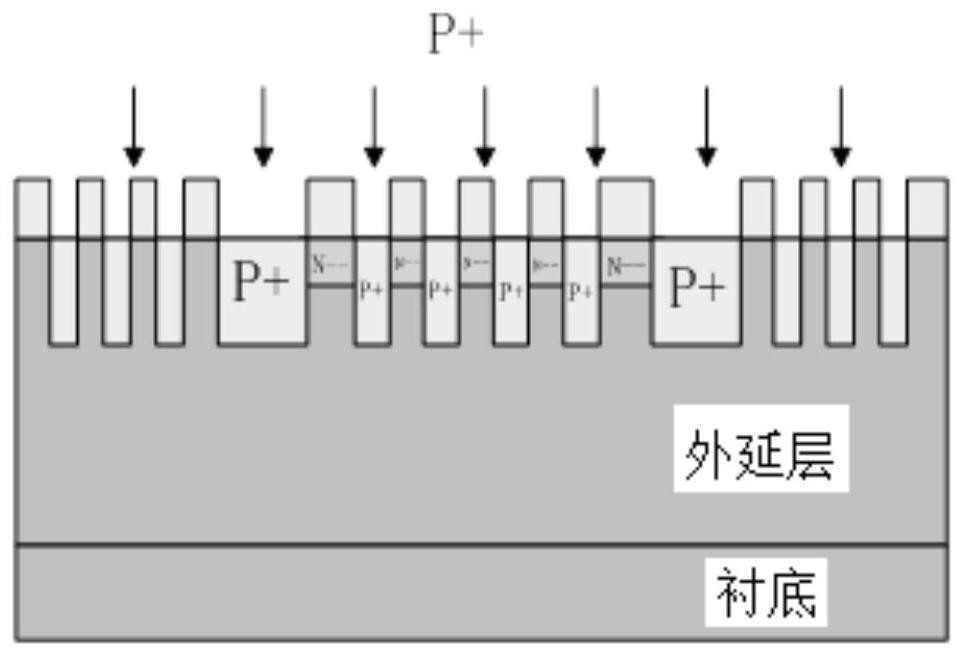

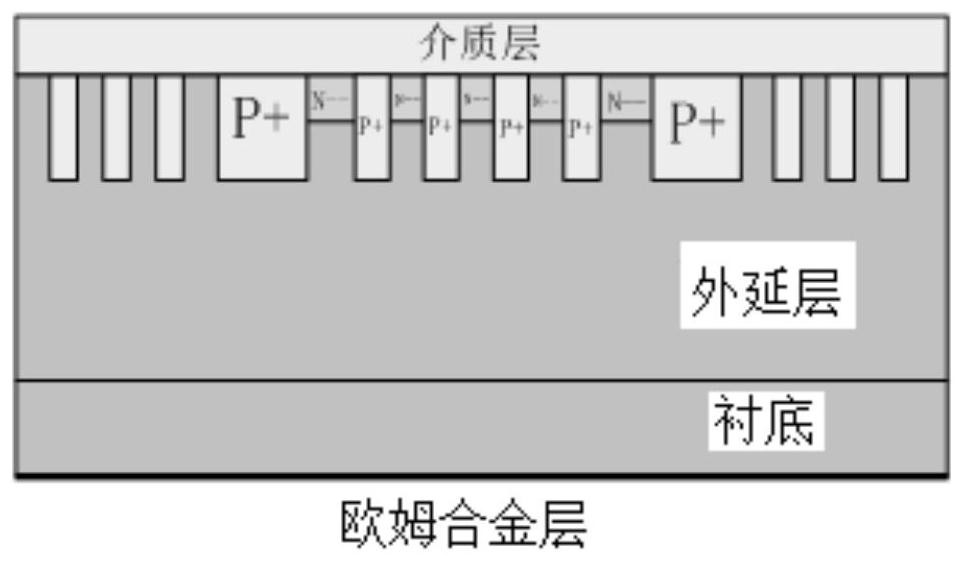

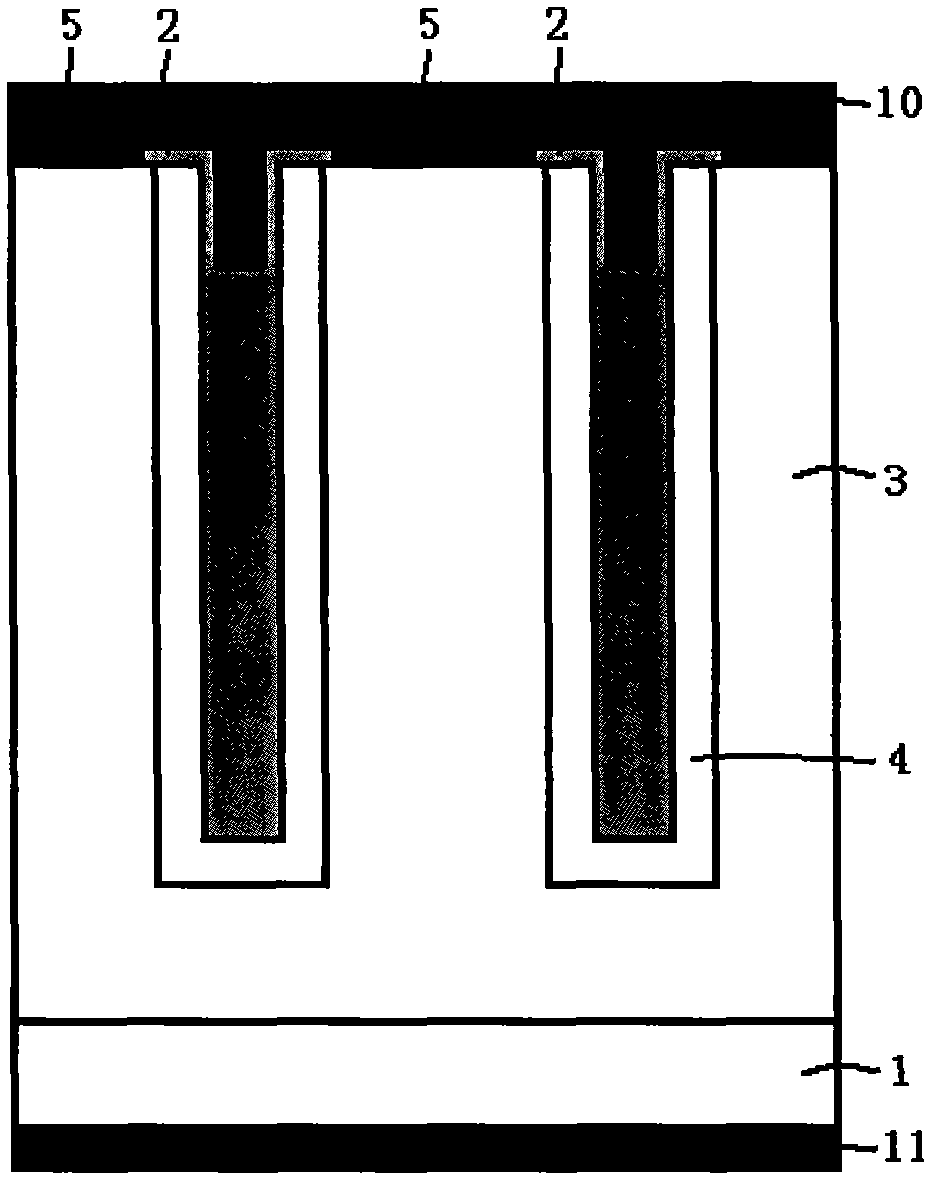

ActiveCN102916055ALower doping concentration is lowReduce reverse leakageSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierOhmic contact

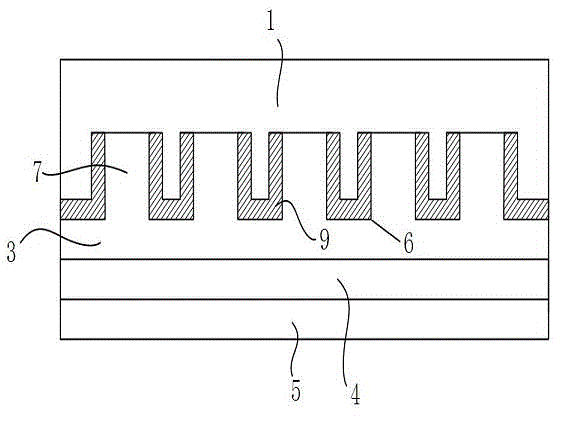

The invention discloses a trenched Schottky-barrier diode, and solves the problems that a conventional trenched Schottky-barrier diode is lower in performance and reliability, high in reverse current leakage and poor in reverse blocking capability. The doping density of an epilayer gradually increases from the top to bottom, a second conduction type non-uniformly doped conductive polycrystalline silicon of which the doping density gradually decreases from the top to bottom is filled in trenches, second conduction type heavily doped lug boss apex angle protection areas are formed at the apex angles on two sides of lug bosses, and a Schottky-barrier metal layer in ohmic contact with the top surfaces of both the conductive polycrystalline silicon and the lug boss apex angle protection areas is added to the bottom surface of an anodal metal layer. The trenched Schottky-barrier diode provided by the invention has the advantages of low reverse current leakage, good voltage reverse blocking capability and excellent reliability. The invention also provides a manufacturing method of the trenched Schottky-barrier diode, which has the advantages of less steps and low manufacturing cost and can effectively isolate areas from damage by the technological process and contamination of impurities due to local impairment of isolating layers.

Owner:HANGZHOU LION MICROELECTRONICS CO LTD

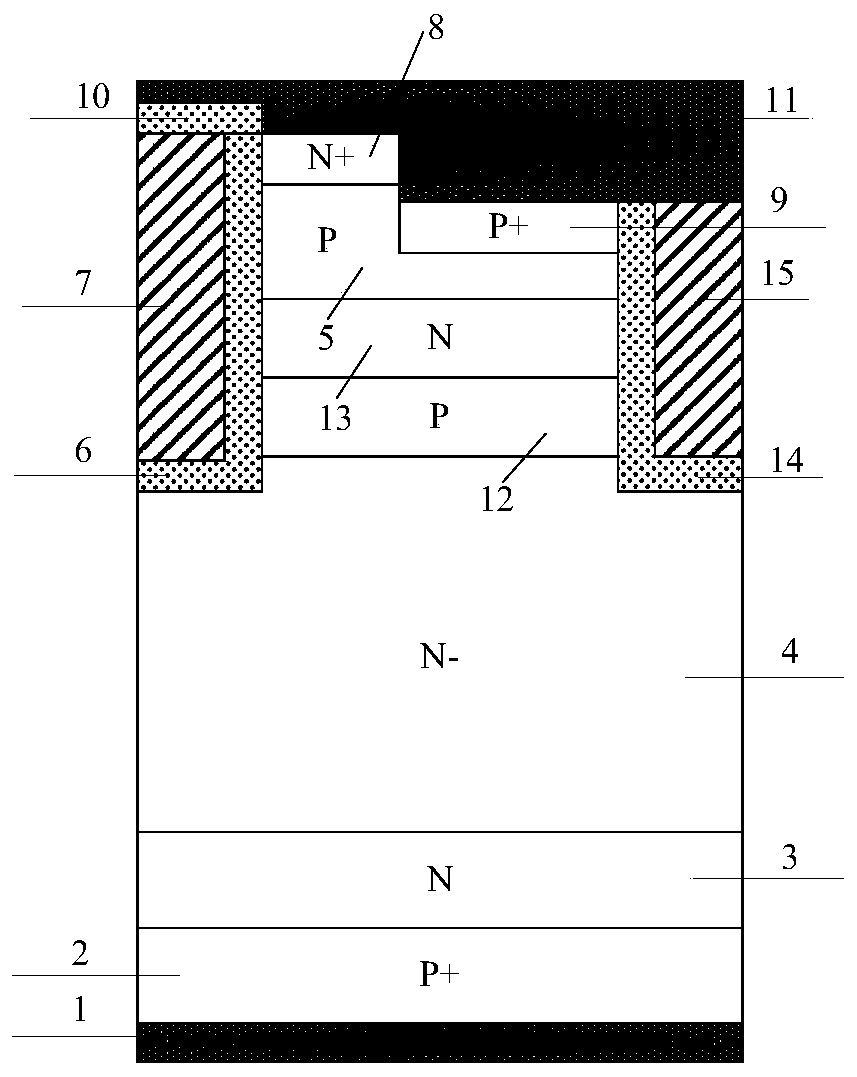

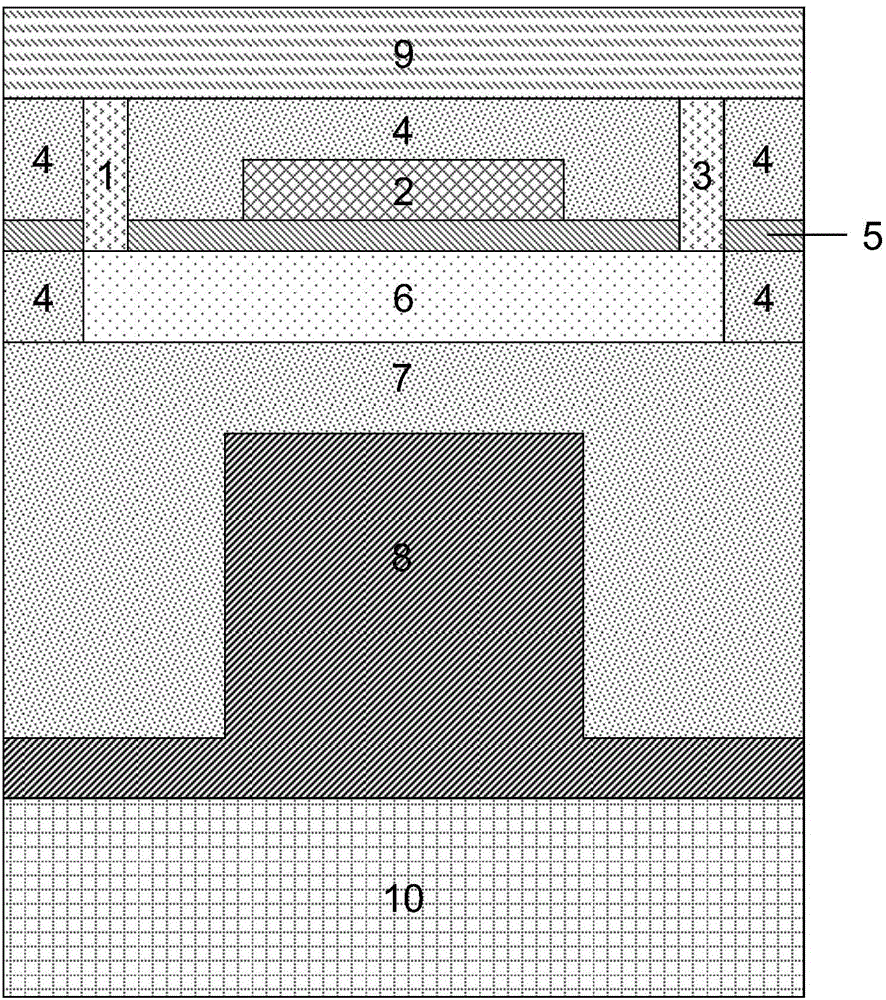

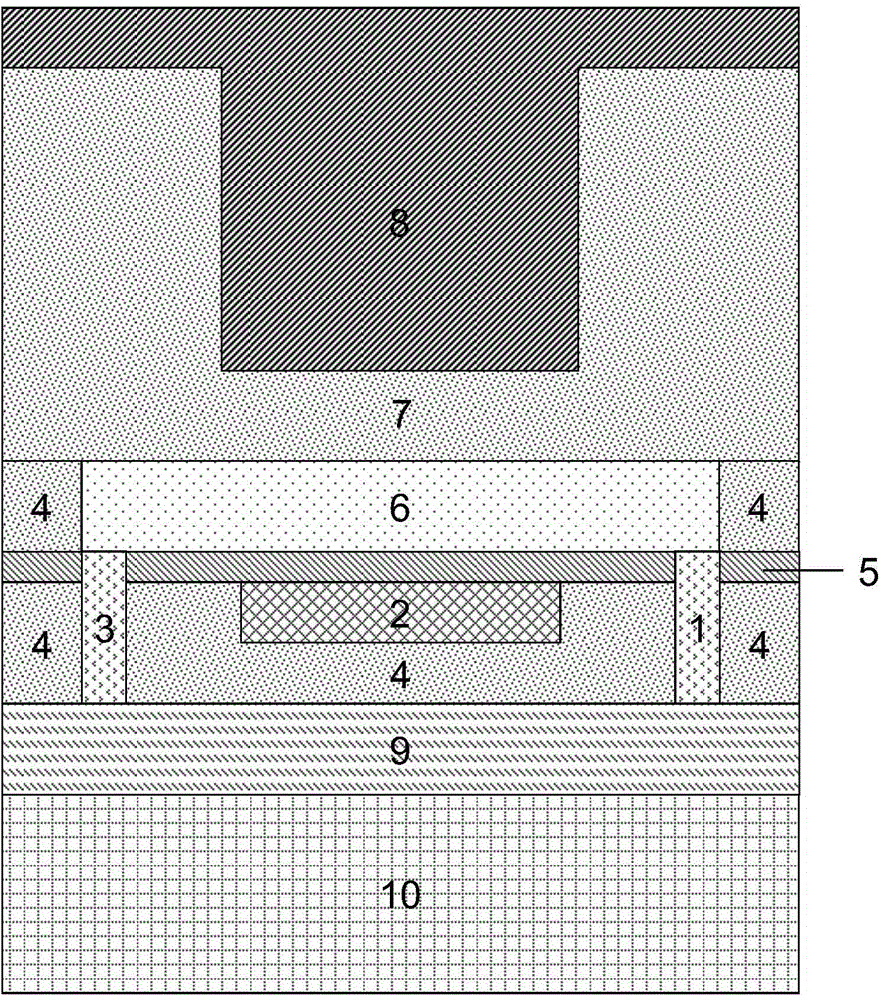

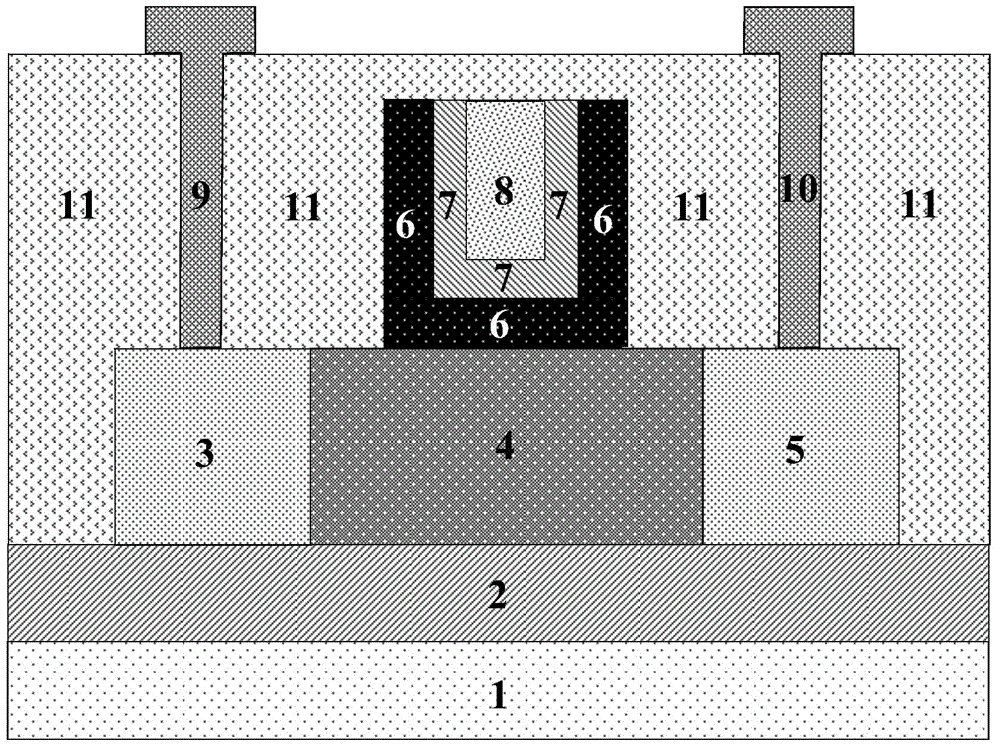

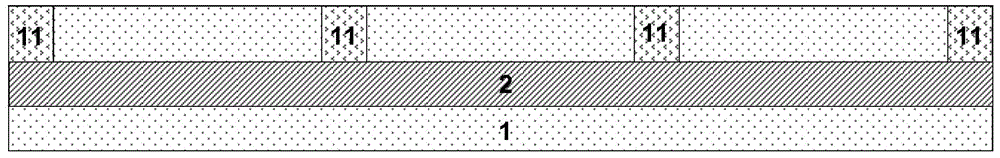

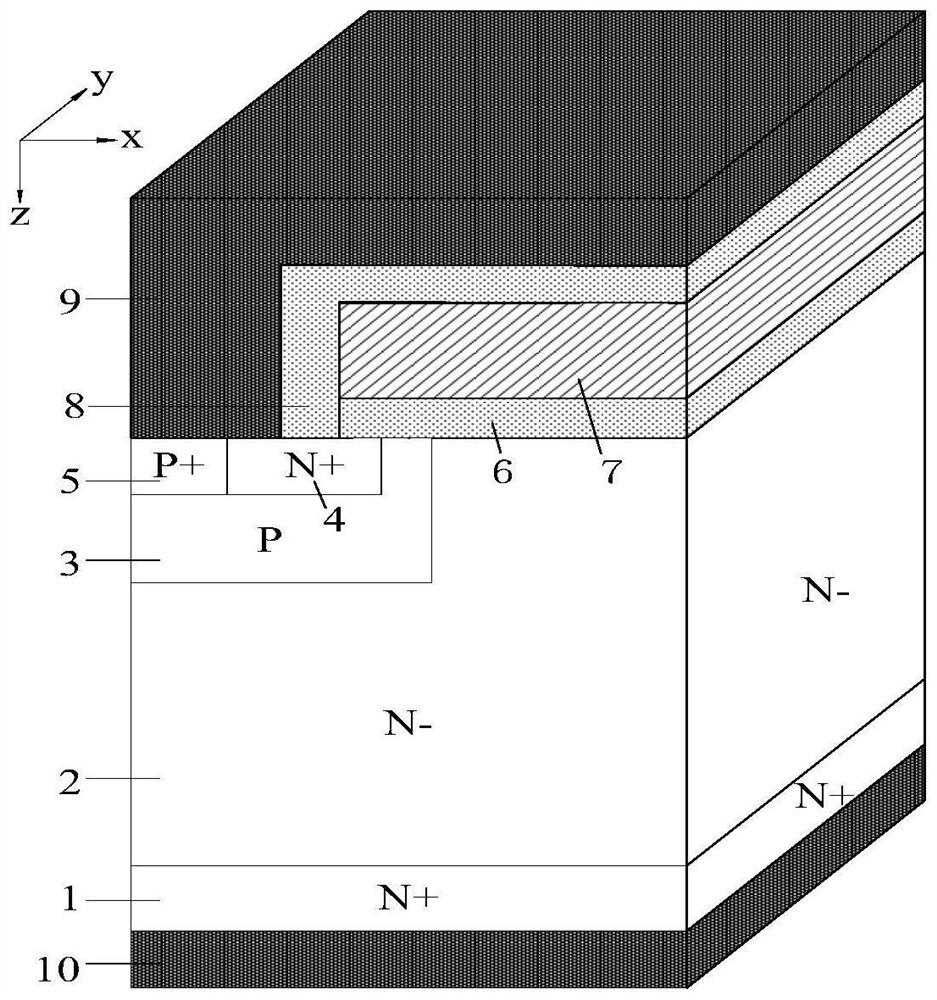

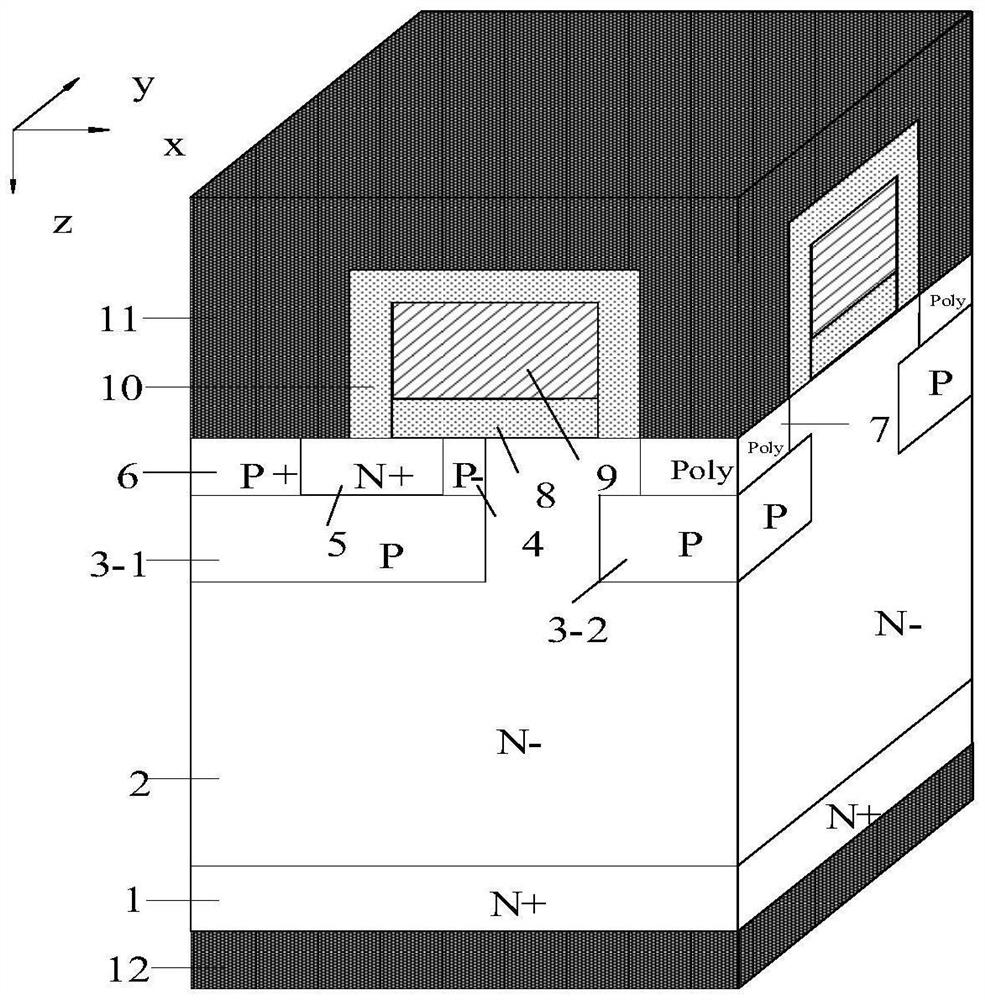

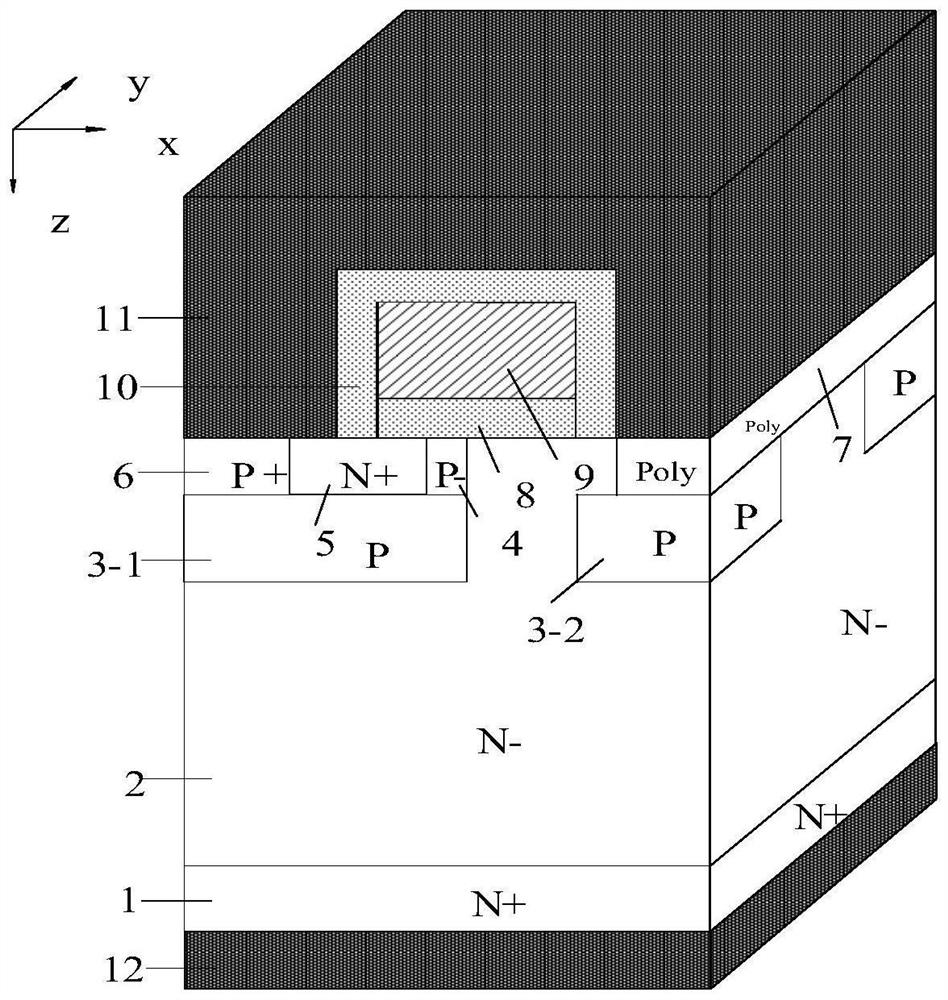

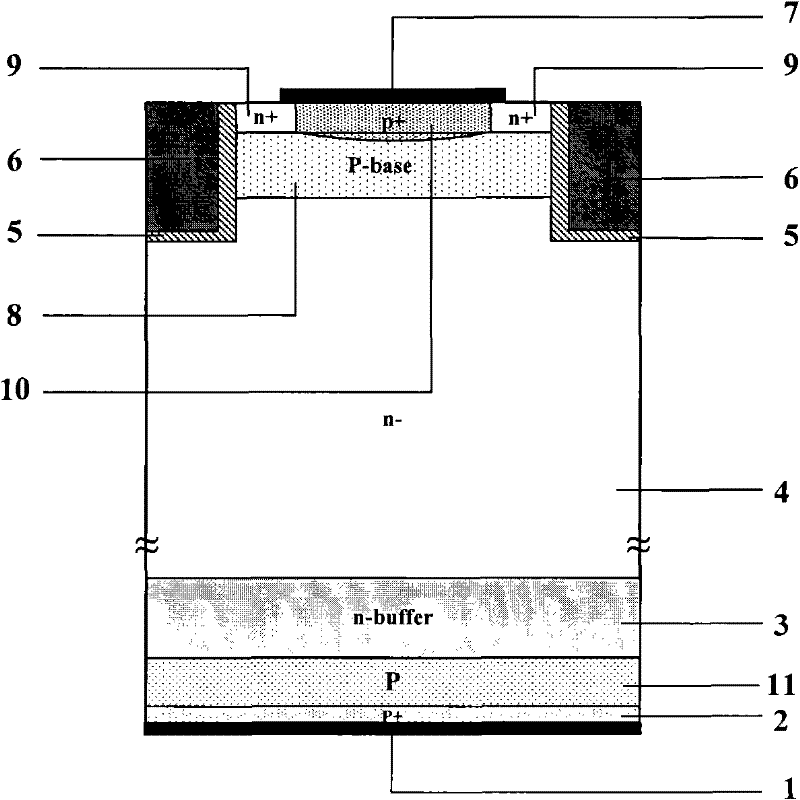

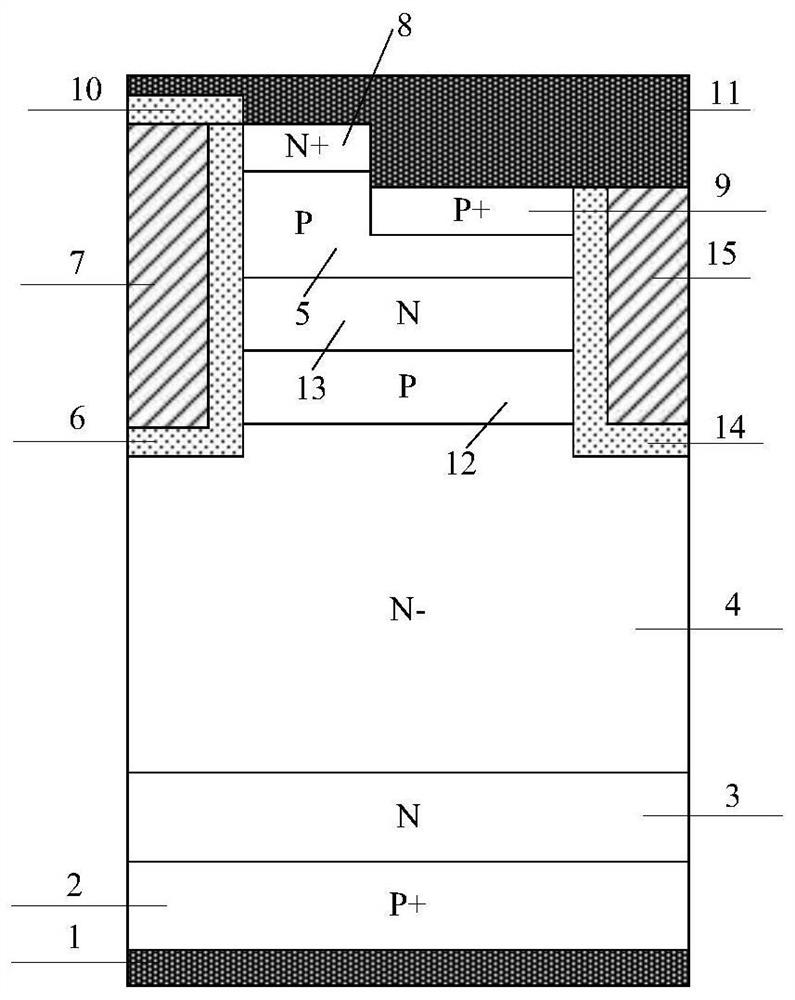

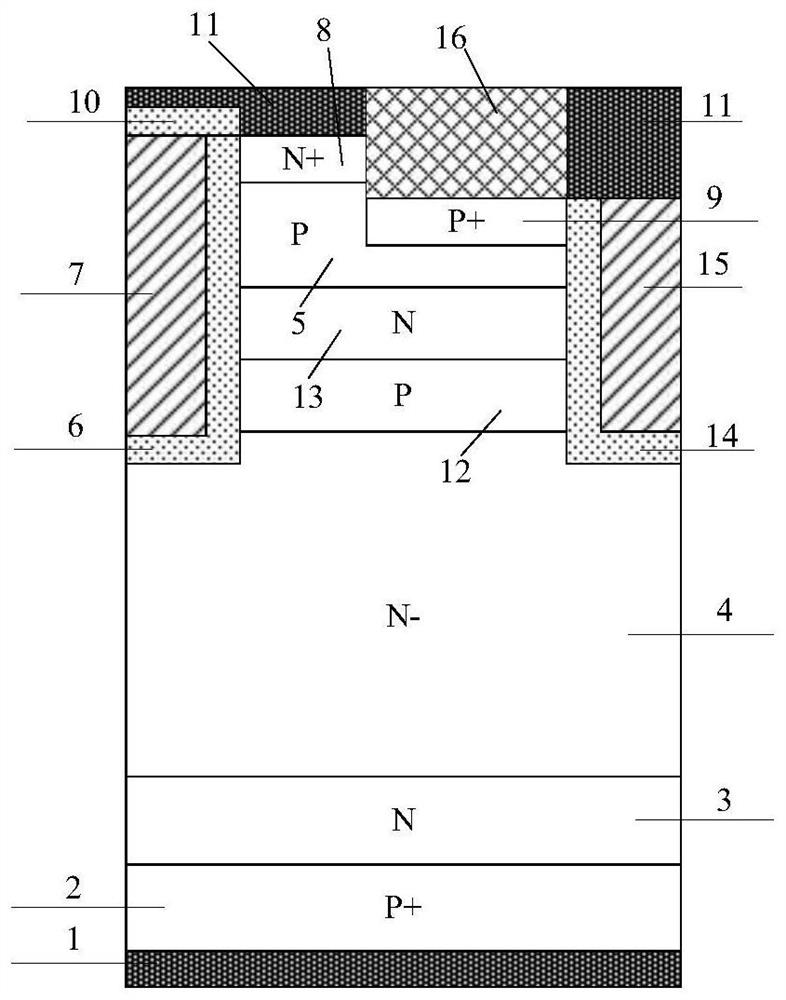

RET IGBT with self-bias PMOS and manufacturing method thereof

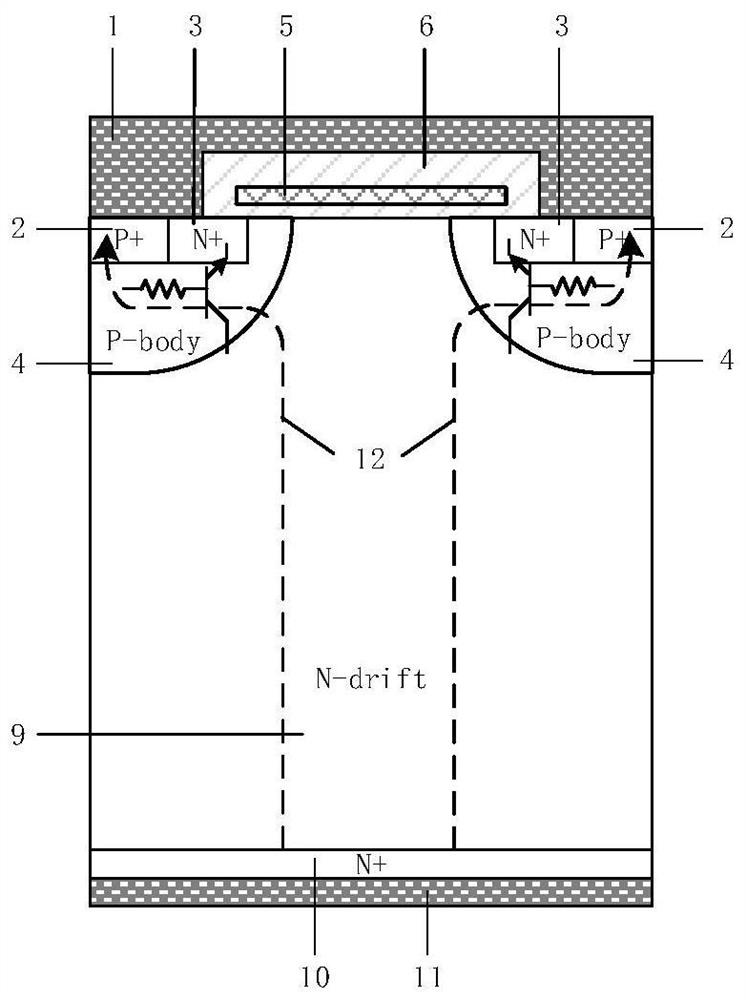

ActiveCN110504310AImprove forward conduction characteristicsEffect of shield breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceCapacitance

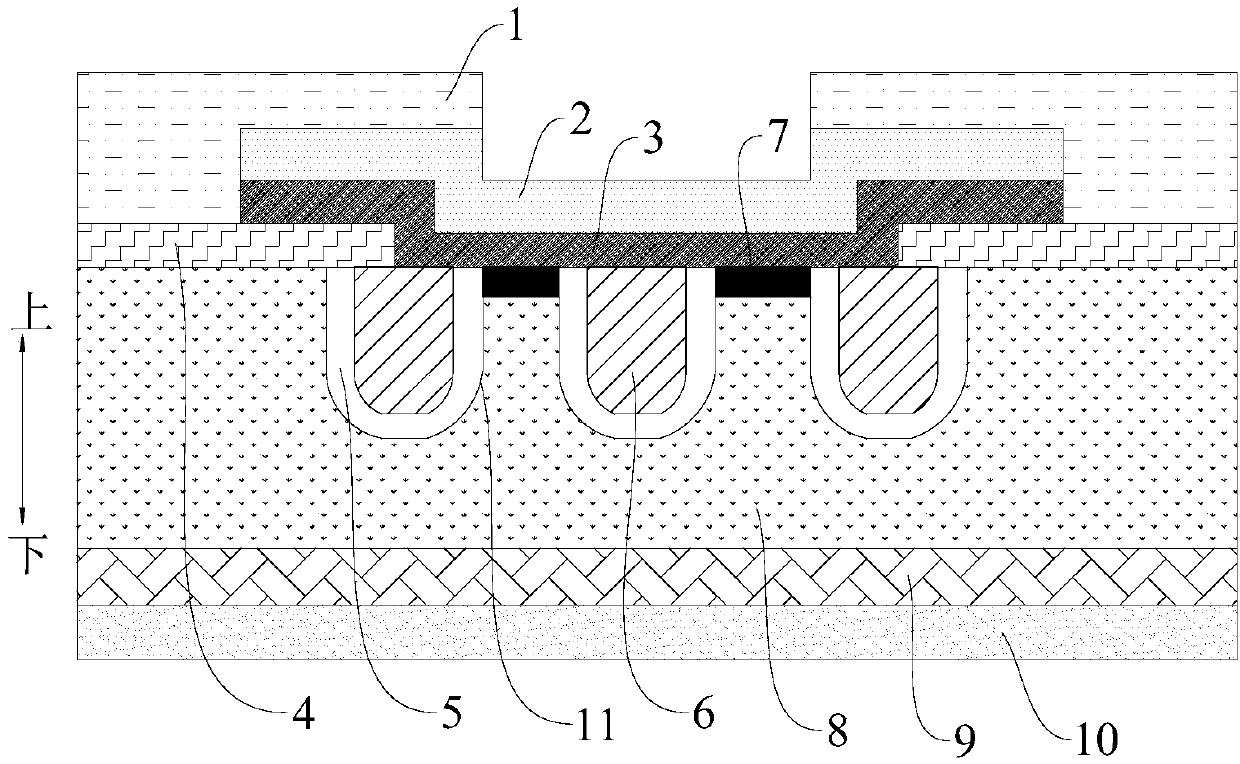

The invention belongs to the technical field of power semiconductor devices, and relates to a RET IGBT with a self-biased PMOS and a manufacturing method thereof. According to the RET IGBT with the self-biased PMOS and the manufacturing method thereof, a N-type charge storage layer is arranged between a P-type base region and a P-type buried layer, so that the influence of the N-type charge storage layer on the breakdown voltage of the device can be shielded while the forward conduction characteristic of the device is improved; by introducing a PMOS structure, an extra path is provided for theextraction of holes, the extraction speed of current carriers is accelerated, the switching speed of the device is improved, and the turn-off loss of the device is reduced; and meanwhile, an emitterembedded type separation gate structure can meet the requirement that a table top of the device is further narrowed to improve the forward conduction characteristic of the device, metal and contact holes of the emitter of the device can be easily and irregularly made, and meanwhile, the Miller capacitance of the device can be reduced further.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

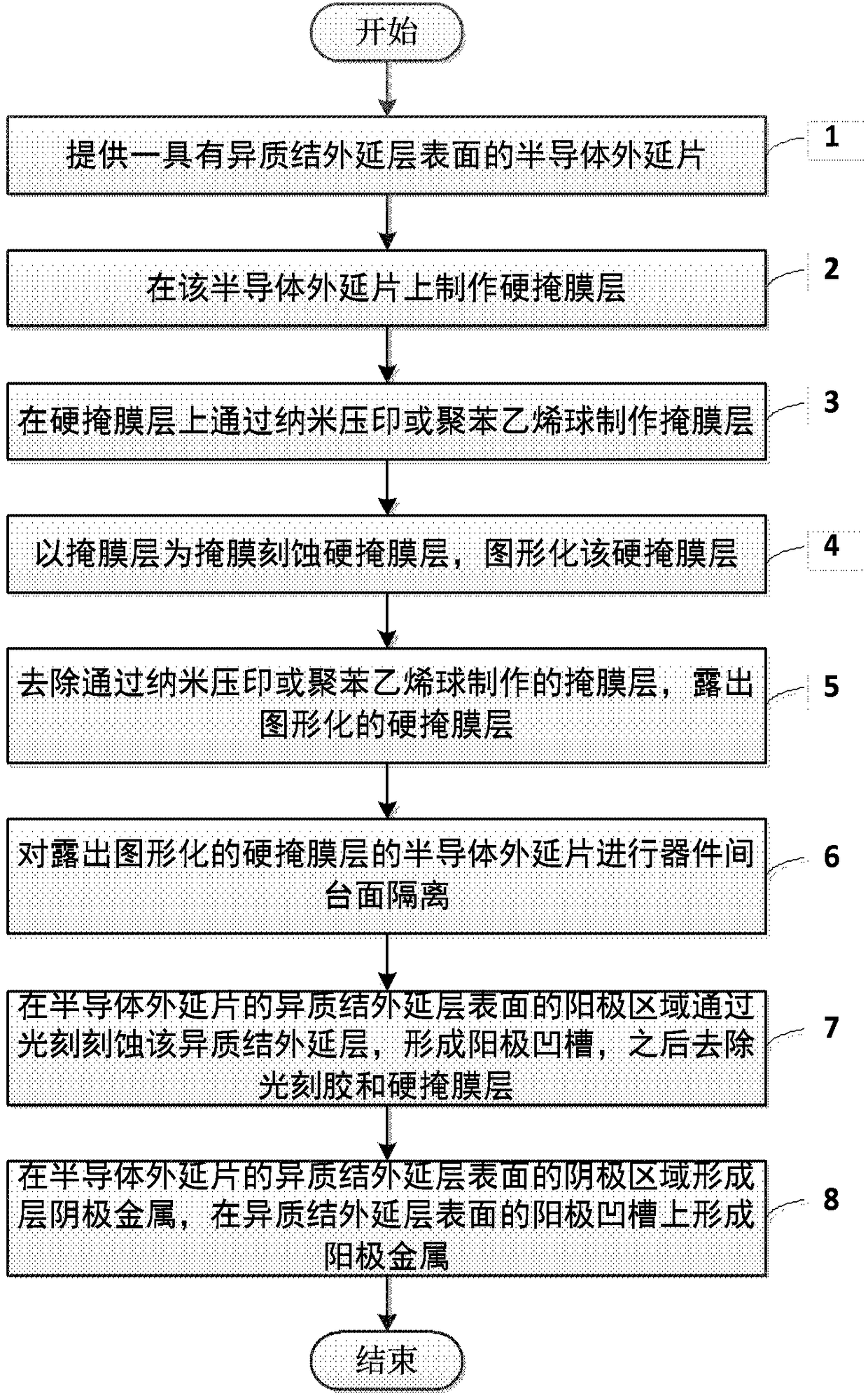

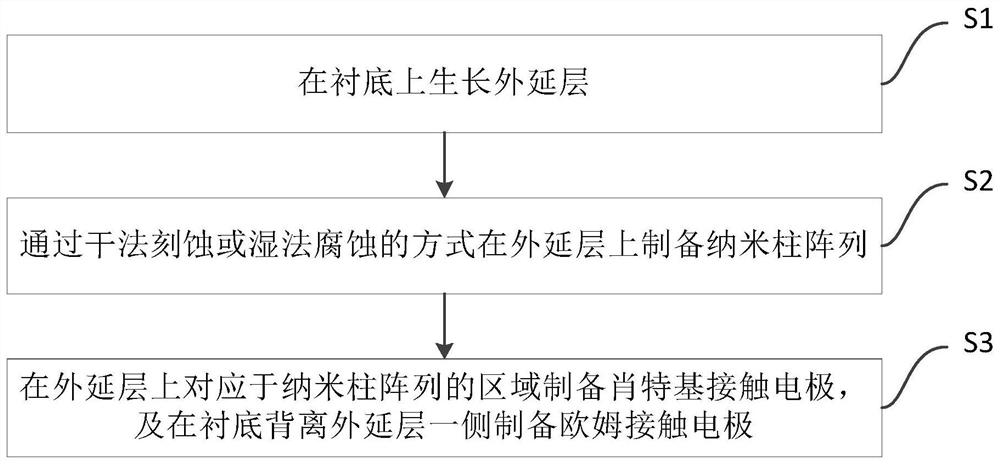

Method for preparing grooved anode Schottky diode

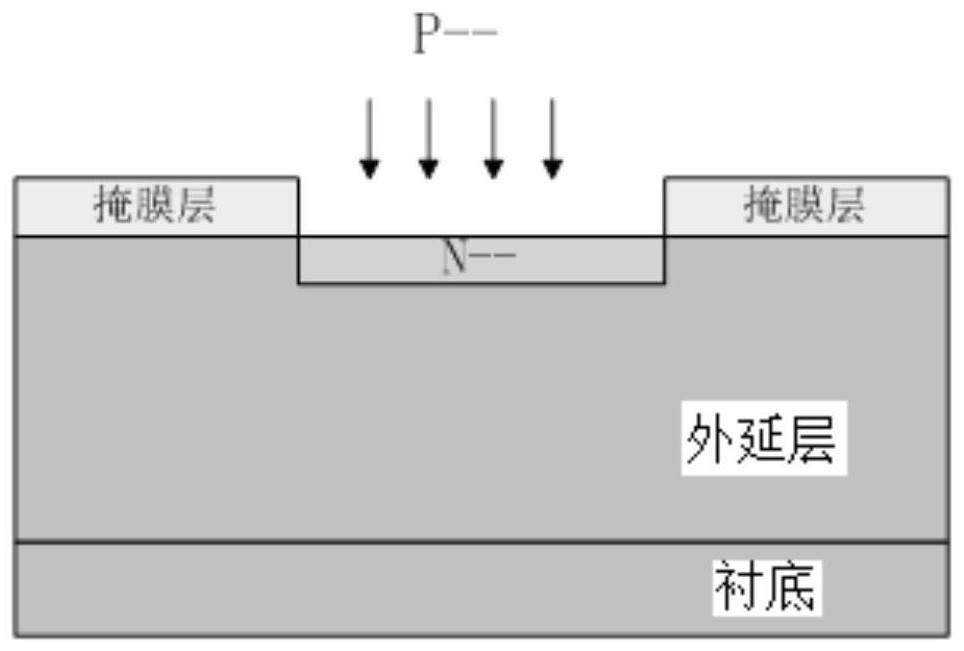

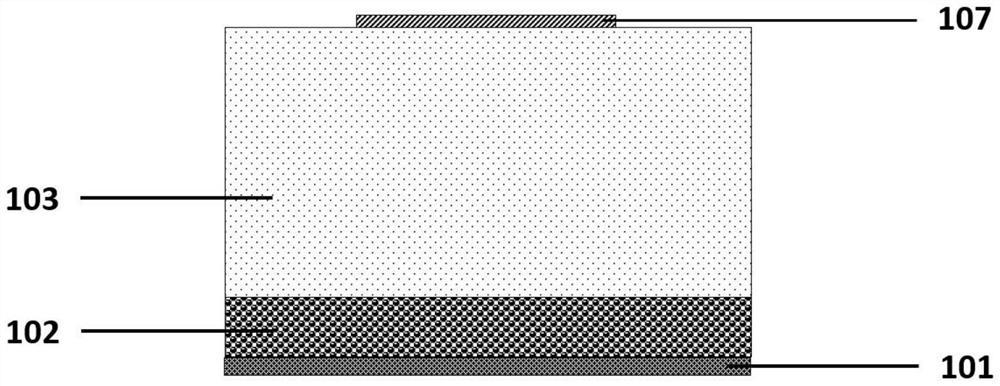

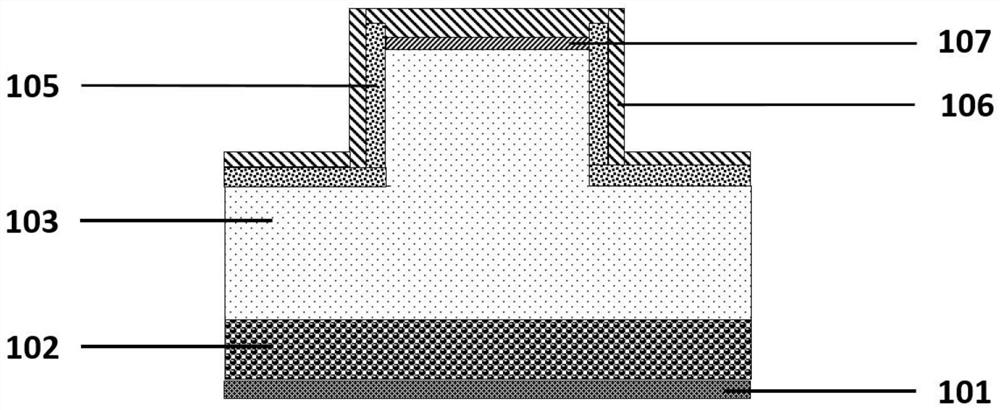

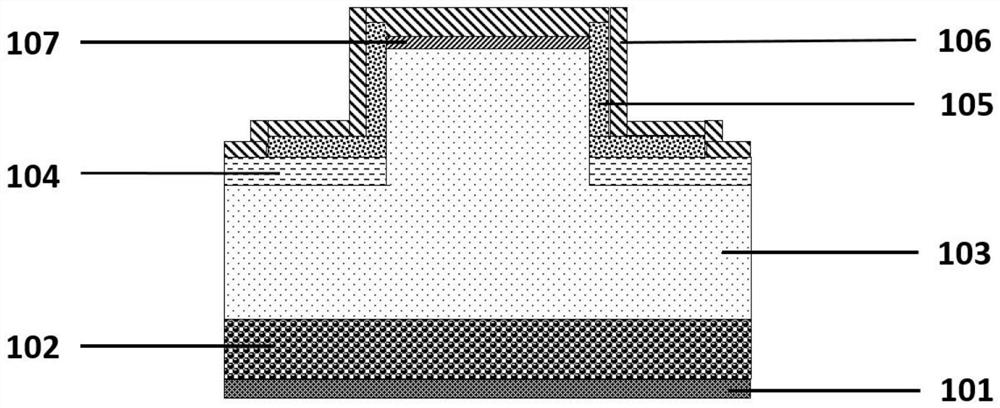

InactiveCN108091566AImprove forward conduction characteristicsGood high breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPhotoresistPolystyrene spheres

The invention discloses a method for preparing a grooved anode Schottky diode. The method comprises the steps of: providing a semiconductor epitaxial wafer; manufacturing a hard mask layer on the semiconductor epitaxial wafer; manufacturing a mask layer on the hard mask layer; and using the mask layer as a mask for etching the hard mask layer, and patterning the hard mask layer; removing the masklayer to expose the patterned hard mask layer; performing inter-device mesa isolation on the semiconductor epitaxial wafer on which the patterned hard mask layer is exposed; etching a heterojunction epitaxial layer to form an anode groove in an anode region on the surface of the heterojunction epitaxial layer of the semiconductor epitaxial wafer, and then removing a photoresist and the hard mask layer; and forming a layer of cathode metal in a cathode region on the surface of the heterojunction epitaxial layer of the semiconductor epitaxial wafer. The method utilizes a nanoimprint technology or a polystyrene ball paving technology to realize the nanoscale anode groove, so as to prepare the Schottky diode having the good positive conducting features such as low turn-on voltage, low conducting resistance and high saturation current as well as good reverse turn-off features such as low electric leakage and high breakdown voltage simultaneously.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

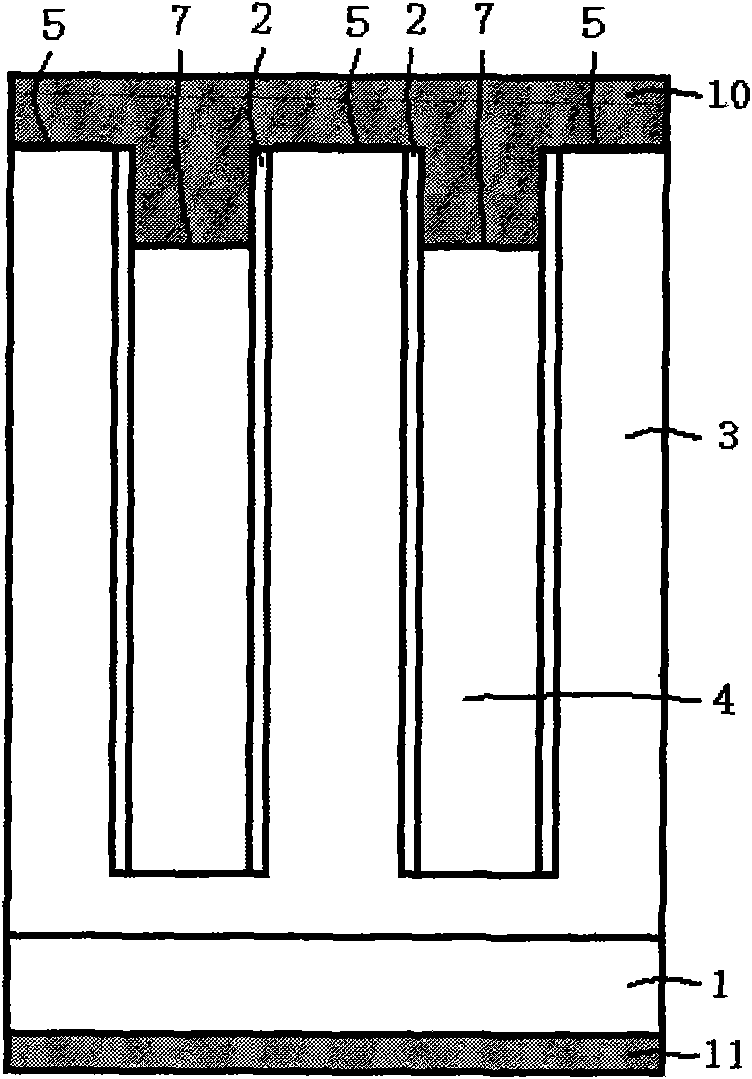

Groove schottky semiconductor device with super junction structure and manufacturing method thereof

ActiveCN103199119AImprove reverse breakdown voltageRealize manufacturingSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationSemiconductor materials

The invention discloses a groove schottky semiconductor device with a super junction structure. Charge compensation can be formed by second conductive semiconductor materials located on the lower portions inside grooves and first conductive semiconductor materials among the grooves, then the super junction structure is formed, and reverse breakdown voltages of devices are improved; meanwhile, when a semiconductor device is connected with a certain reverse bias voltage, a metal oxide semiconductor (MOS) structure is constructed by the second conductive semiconductor materials which are doped with metal or high-concentration impurities and arranged on the upper portions inside the grooves and insulating medium located on the side surfaces of the grooves, electric field intensity of drifting materials nearby schottky barrier can be restrained, the pheromone that the barrier height of the schottky barrier is reduced along with rising of the reverse bias voltage is reduced, accordingly reverse leakage current of the devices is reduced, and a reverse blocking characteristic of the devices is improved.

Owner:SEMICON MFG ELECTRONICS (SHAOXING) CORP

Super junction Schottky semiconductor device and preparation method thereof

ActiveCN103367396AImprove reverse breakdown voltageIncrease the doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSchottky barrier

The invention discloses a super junction Schottky semiconductor device. When the semiconductor device is accessed to a certain reverse bias voltage, charge compensation is formed by a second conductive semiconductor material and a first conductive semiconductor material, a super junction structure is formed, the reverse breakdown voltage of the device is enhanced, and characteristics of conduction or blocking of the device are improved. Meanwhile, when the semiconductor device is accessed to a certain forward bias voltage, a first type Schottky barrier junction (assuming that the first conductive semiconductor layer adopts an N type semiconductor material) is in the forward bias conduction state, and a second type Schottky barrier junction (assuming that the second conductive semiconductor layer adopts a P type semiconductor material) is in the reverse bias cut-off state, therefore when in the forward conduction state, the device is still a conductive device with a single carrier, and minority carrier injection does not exist in the conductive device with the single carrier. The device has good switching characteristics. The invention also provides a preparation method of the super junction Schottky semiconductor device.

Owner:北海惠科半导体科技有限公司

SOI (Silicon on Insulator) substrate folding grid insulating tunneling enhanced transistor and manufacturing method thereof

InactiveCN104485354AIncrease incidenceImprove switching characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGeneration rate

The invention relates to an SOI (Silicon on Insulator) substrate folding grid insulating tunneling enhanced transistor. The transistor is provided with insulating tunneling structures on the two sides and the upper surface of a base region simultaneously, so the insulating tunneling effect occurs on the two sides and the upper surface of the base region simultaneously under the control effect of a grid electrode, and thus the generation rate of tunneling current is improved; compared with MOSFETs (Metal Oxide Semiconductor Field Effect Transistor) or TFETs (Tunneling Field-Effect Transistor) devices of the same size, superior switching characteristic is realized by using the extremely sensitive mutual relation between the impedance of a tunneling insulating layer and the field intensity in the tunneling insulating layer; superior forward turn-on characteristic is realized by enhancing a tunneling signal through an emitter electrode; besides, the invention also provides specific manufacturing methods of an SOI substrate folding grid insulating tunneling enhanced transistor unit and an array of the enhanced transistor unit. According to the transistor, the working characteristic of a nanoscale integrated circuit unit is obviously improved; the transistor is suitable for popularization and application.

Owner:SHENYANG POLYTECHNIC UNIV

Schottky semiconductor device with super junction and preparation method thereof

InactiveCN103378170AImprove reverse breakdown voltageIncrease the doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceElectricity

The invention discloses a Schottky semiconductor device with a super junction. When the semiconductor device is connected with certain reverse bias voltage, a first electricity-conductive semiconductor material and a second electricity-conductive semiconductor material can form charge compensation and form a super junction structure, and therefore the reverse breakdown voltage of a component can be increased, and the conduction character or the blocking character of the component can be improved. The invention further provides a preparation method of the Schottky semiconductor device with the super junction.

Owner:朱江

High performance SOI non-junction transistor of non-monolithic substrate insulation layer thickness

InactiveCN104538443AAchieve local enhancementReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerVoltage regulation

The invention relates to a high performance SOI non-junction transistor of a non-monolithic substrate insulation layer thickness. An employed SOI wafer insulation layer thickness is not single-valued in the unit length of a transistor. By properly increasing the thickness of the parts, near a source region and a drain region, of an SOI wafer insulation layer, the resistance of the source region and the drain region is greatly reduced, and the positive onset property of a component is greatly improved. By properly decreasing the thickness of the parts, under corresponding gate electrodes, of the SOI wafer insulation layer, local enhancement on the voltage regulating effect of a substrate can be achieved, the substrate voltage bias needed for auxiliary grid control can be lowered, and voltage control over the lower part of the substrate can be achieved. By optimizing the relative positions and sizes of the thicker part and the thinner part of the insulation layer of the SOI wafer, the reverse leakage current caused by band-to-band tunneling around the junctions of a component channel and drain electrodes when reversal of biasing of the gate electrodes occurs is effectively reduced. Therefore, the high performance SOI non-junction transistor is suitable for widespread application.

Owner:SHENYANG POLYTECHNIC UNIV

Groove charge compensation Schottky semiconductor device and manufacturing method thereof

ActiveCN103515450AImprove reverse breakdown voltageIncrease the doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSemiconductor materials

The invention discloses a groove charge compensation Schottky semiconductor device which is provided with a charge compensation structure. When the semiconductor device is connected with certain back bias voltage, a first conducting semiconductor material and a second conducting semiconductor material can form charge compensation and the back blocking property of a device is improved. A polycrystal semiconductor material is led into the upper portion of the groove so that strength of a peak electric field of Schottky junction surface can be reduced when the semiconductor device is connected with the back bias voltage and the back blocking property of the device is further improved. The invention further provides a manufacturing method of the groove charge compensation Schottky semiconductor device.

Owner:北海惠科半导体科技有限公司

Interface charge compensation Schottky semiconductor device and manufacturing method for same

InactiveCN103383968AImprove reverse breakdown voltageLower forward conduction resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsCharge compensation

The invention discloses an interface charge compensation Schottky semiconductor device. When the semiconductor device is connected with a certain reverse biased voltage, charge compensation is generated by interface charge compensation regions and drifting semiconductor materials, depletion layers between the interface charge compensation regions are made to be overlapped, and therefore the reverse breakdown voltage of the device is improved, or the forward breakover resistance of the device is lowered, and the forward breakover feature of the device is improved. The invention further provides a manufacturing method for the interface charge compensation Schottky semiconductor device.

Owner:朱江

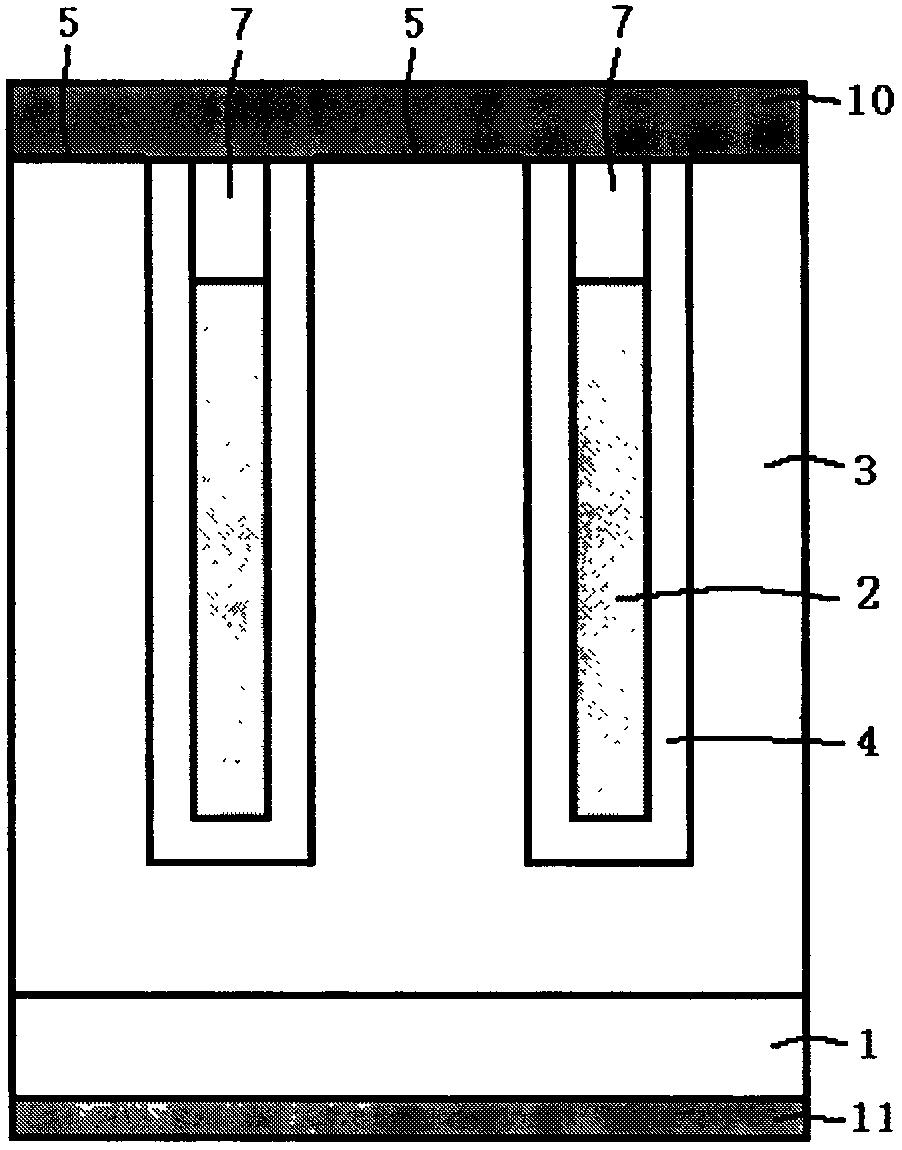

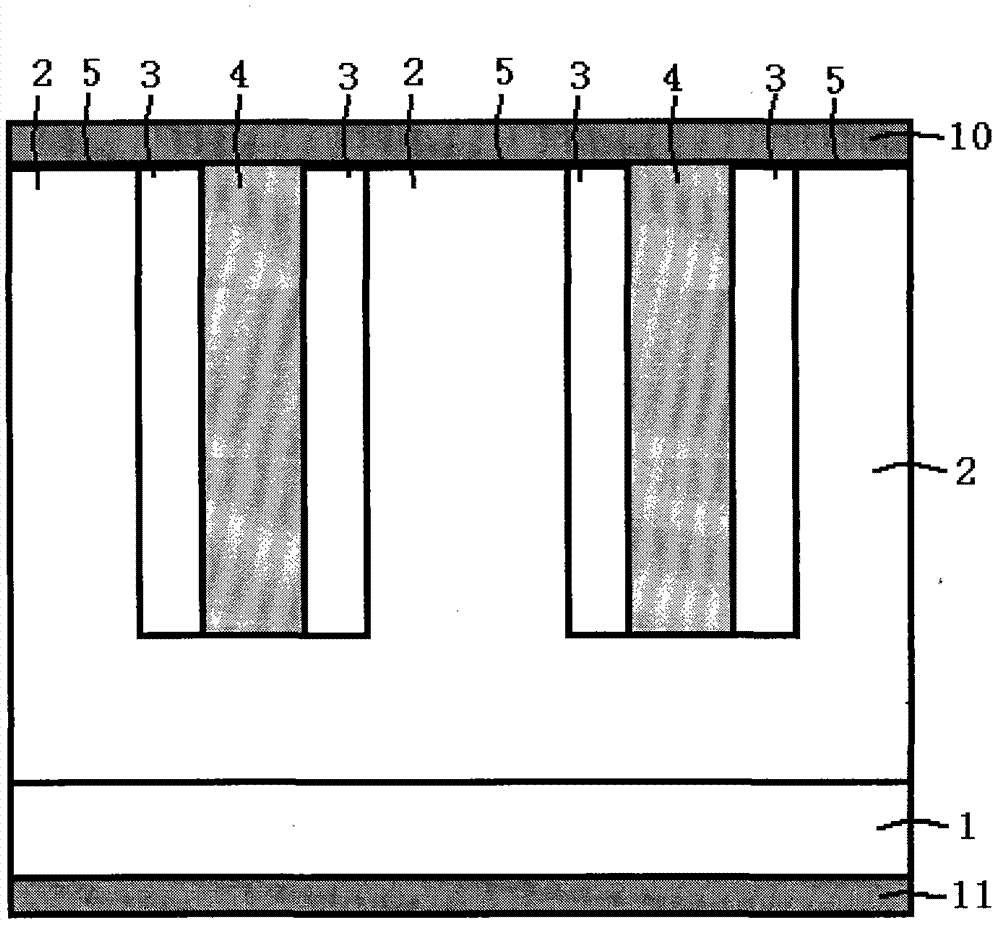

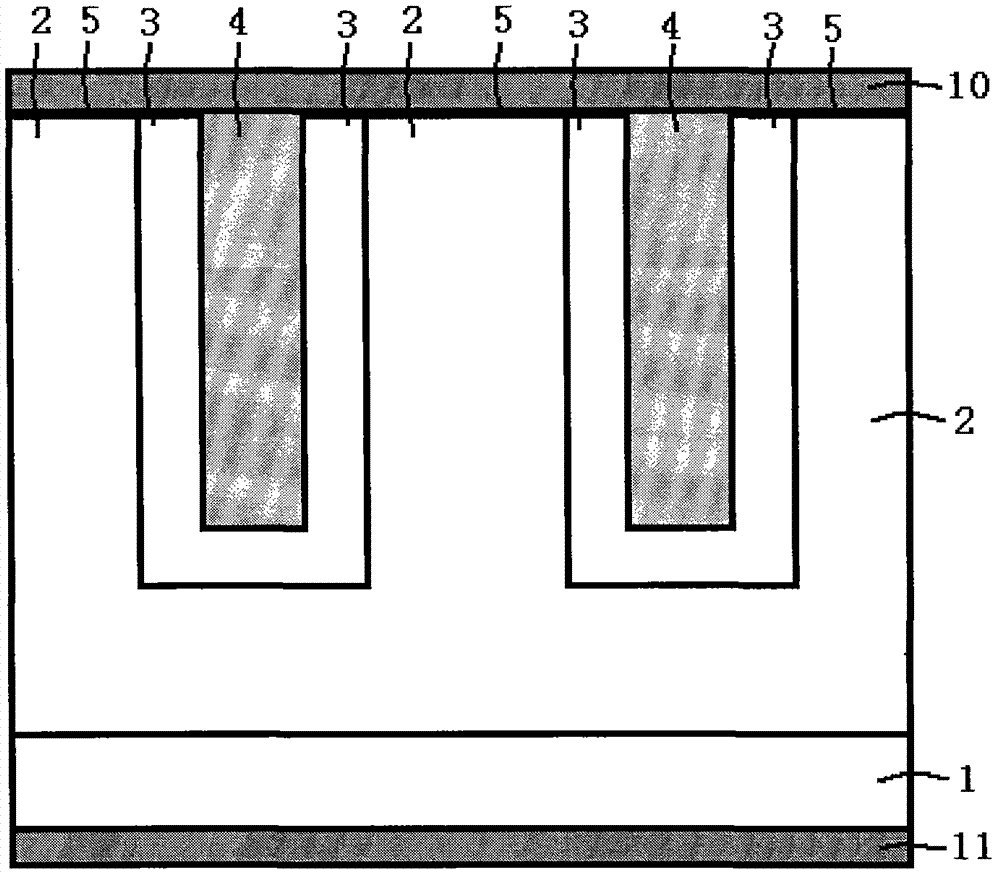

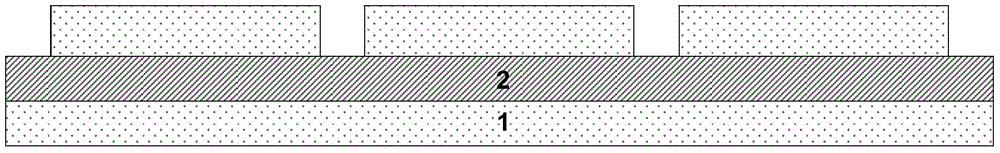

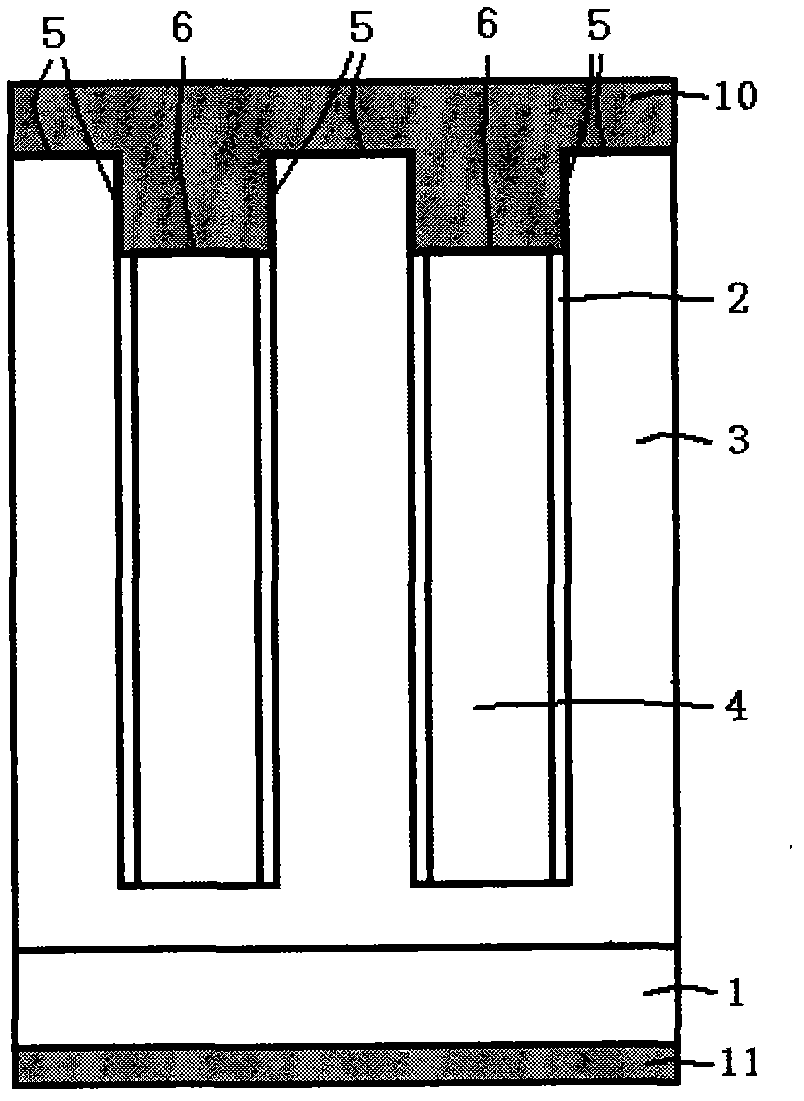

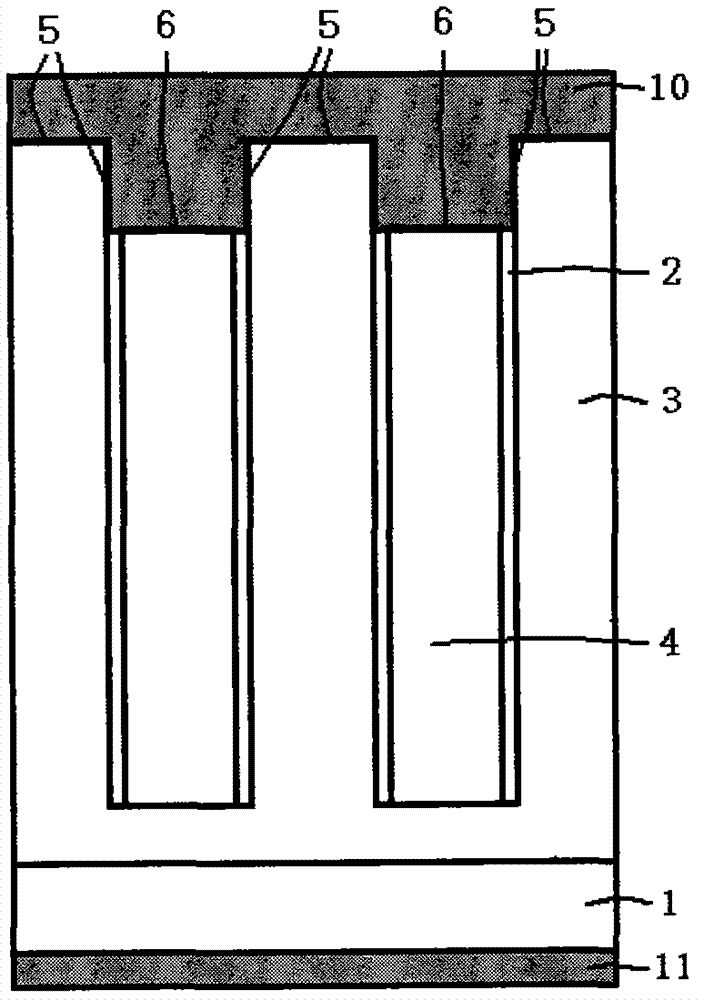

Schottky semiconductor device with insulating layer isolation structure and preparation method thereof

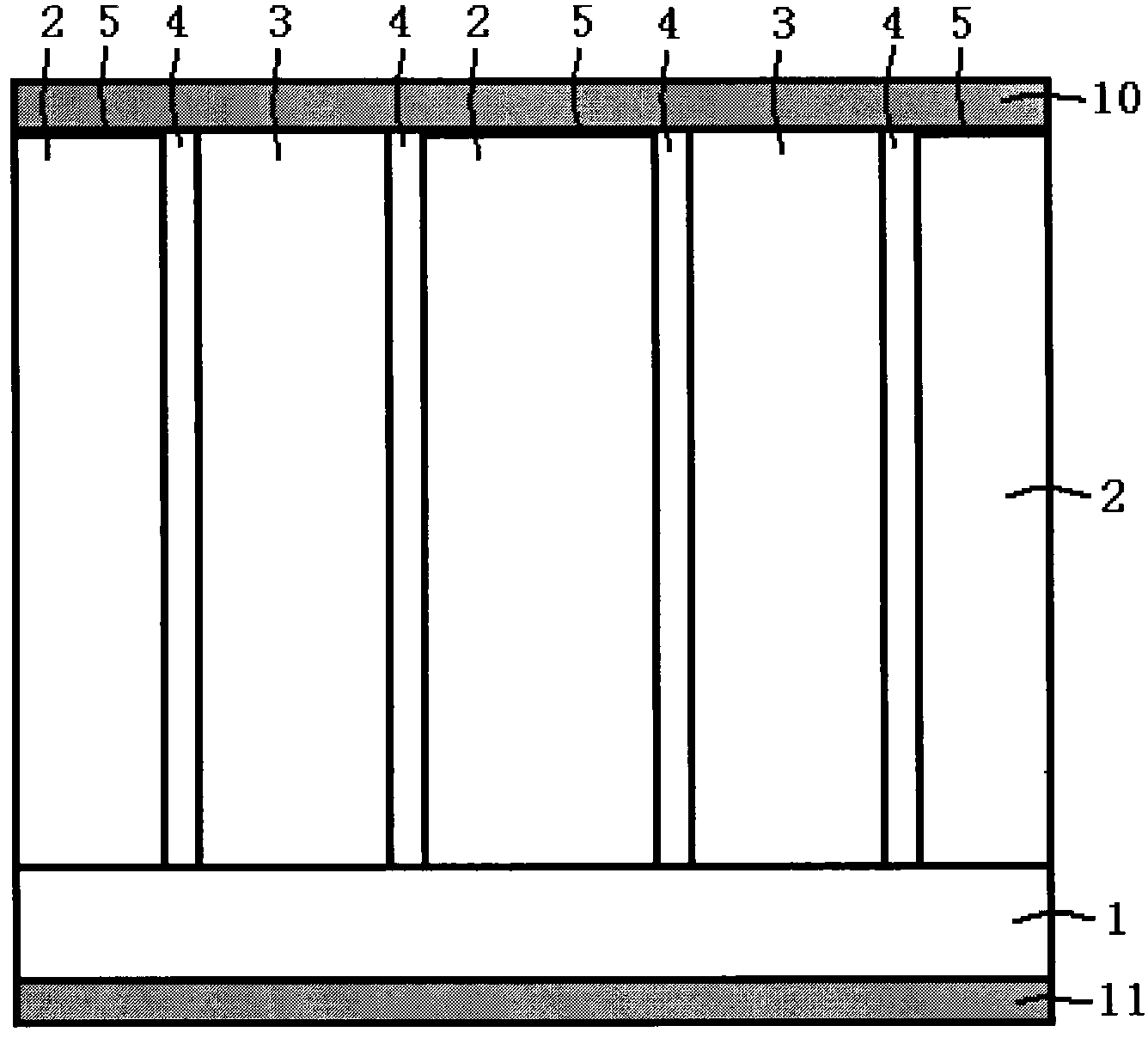

InactiveCN103137711AImprove reverse breakdown voltageLower forward conduction resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSemiconductor materials

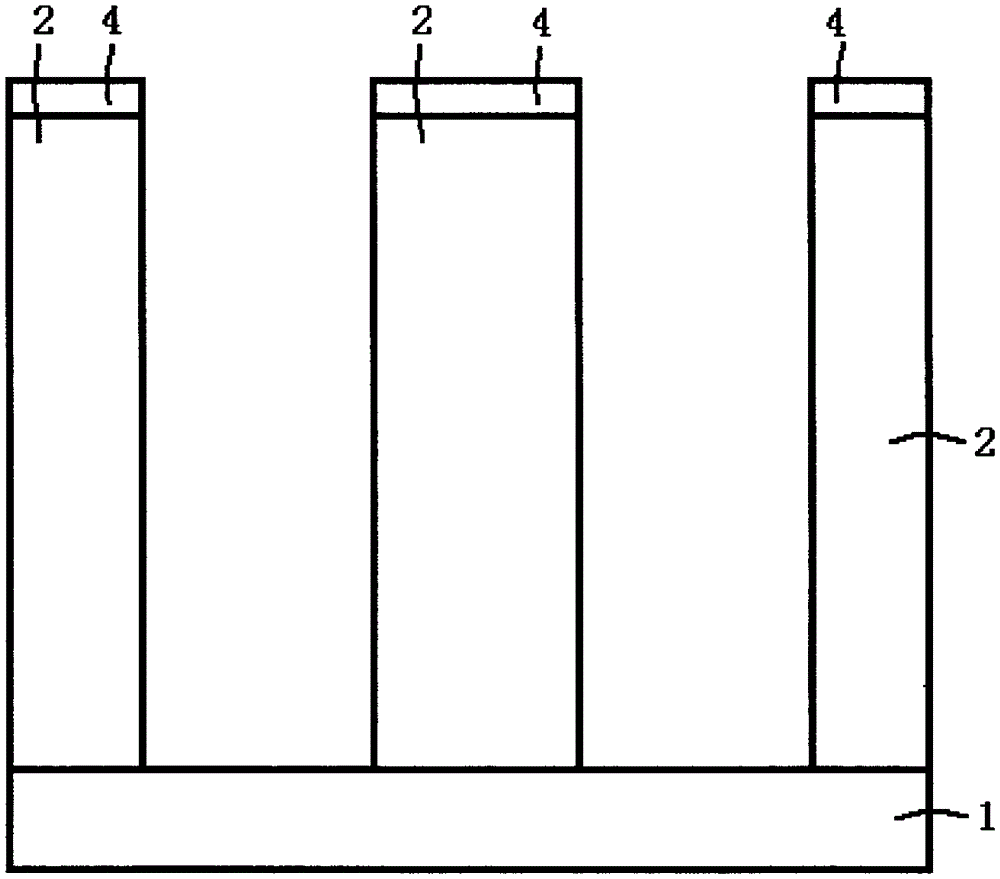

The invention discloses a Schottky semiconductor device with an insulating layer isolation structure. Through a trench structure, deep strip P-type semiconductor silicon materials 3 can be achieved, and ideal vertical strip semiconductor materials can be achieved through insulating layer isolation. When an apparatus is connected with a reverse bias voltage, the strip P-type semiconductor silicon materials 3 and strip N-type semiconductor silicon materials 2 form charge complementation to form a super-junction structure, and accordingly, the electric field intensity distribution of drift regions is changed, and flat field intensity distribution curves are formed. The invention further provides a preparation method of the Schottky semiconductor device with the insulating layer isolation structure.

Owner:朱江 +1

Schottky semiconductor device with super junction structure and manufacturing method thereof

InactiveCN103199102AImprove reverse breakdown voltageRealize manufacturingSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationPower semiconductor device

The invention discloses a schottky semiconductor device with an insulating layer isolation structure and particularly discloses a schottky semiconductor device with a super junction structure and a manufacturing method thereof. Charge compensation can be formed by second conductive semiconductor materials located on the lower portions inside the grooves and first conductive semiconductor materials among the grooves, then the super junction structure is formed; when a semiconductor device is connected with a certain reverse bias voltage, a metal oxide semiconductor (MOS) structure is constructed by the second conductive semiconductor materials which are doped with metal or high-concentration impurities and arranged on the upper portions inside the grooves and insulating medium located on the side surfaces of the grooves, and the pheromone that the barrier height of a schottky barrier is reduced along with rising of the reverse bias voltage is reduced; and besides, the schottky barrier which is capable of forming semiconductor materials P is formed by metal located on the upper portions inside the grooves and the second conductive semiconductor materials located on the lower portions inside the grooves, when the semiconductor device is connected with a forward bias voltage, the schottky barrier is in a reverse bias state, so that forward communication of PN junctions can be effectively restrained, accordingly injection of minority carriers to a drift region is reduced, and a switching characteristic of a device is improved.

Owner:盛况 +1

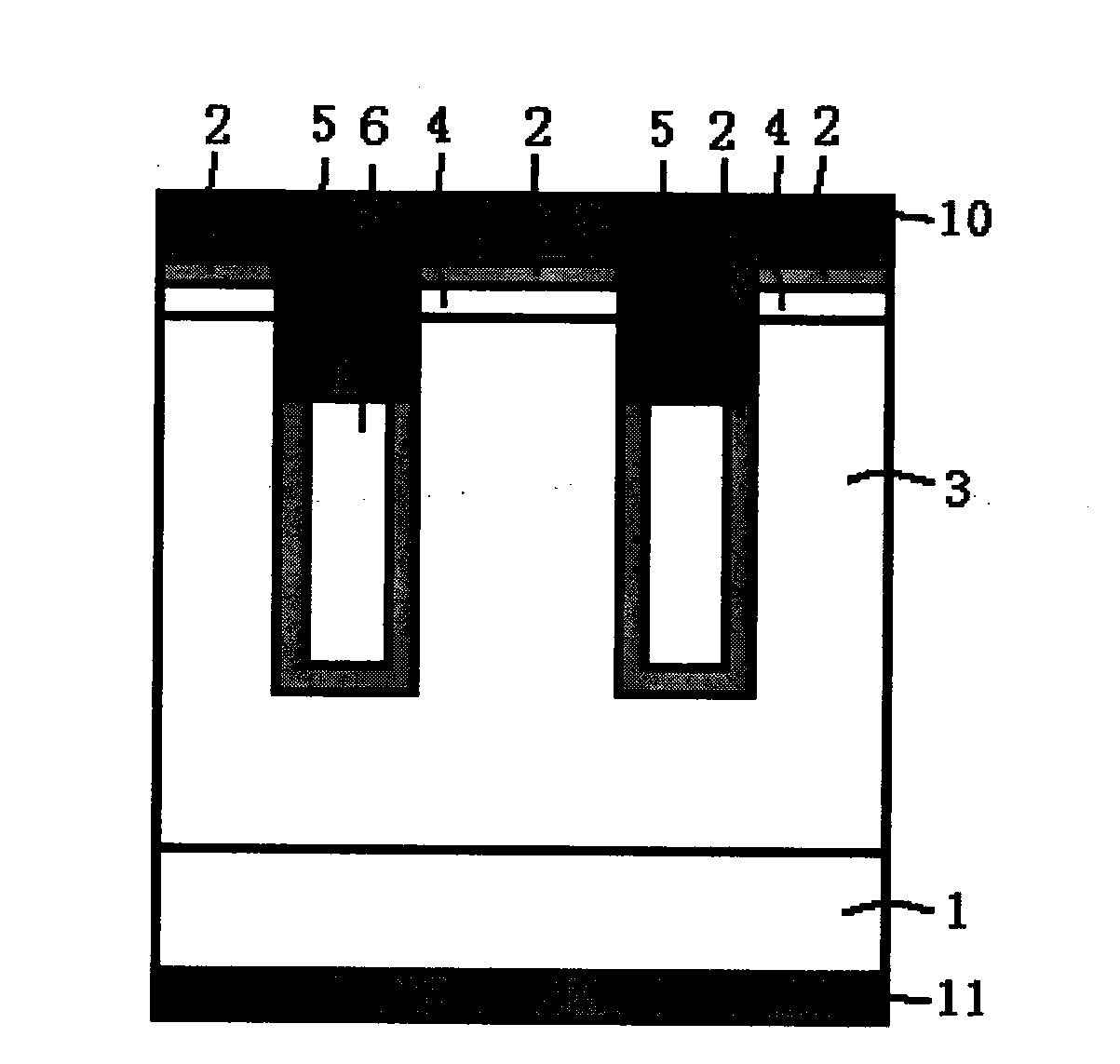

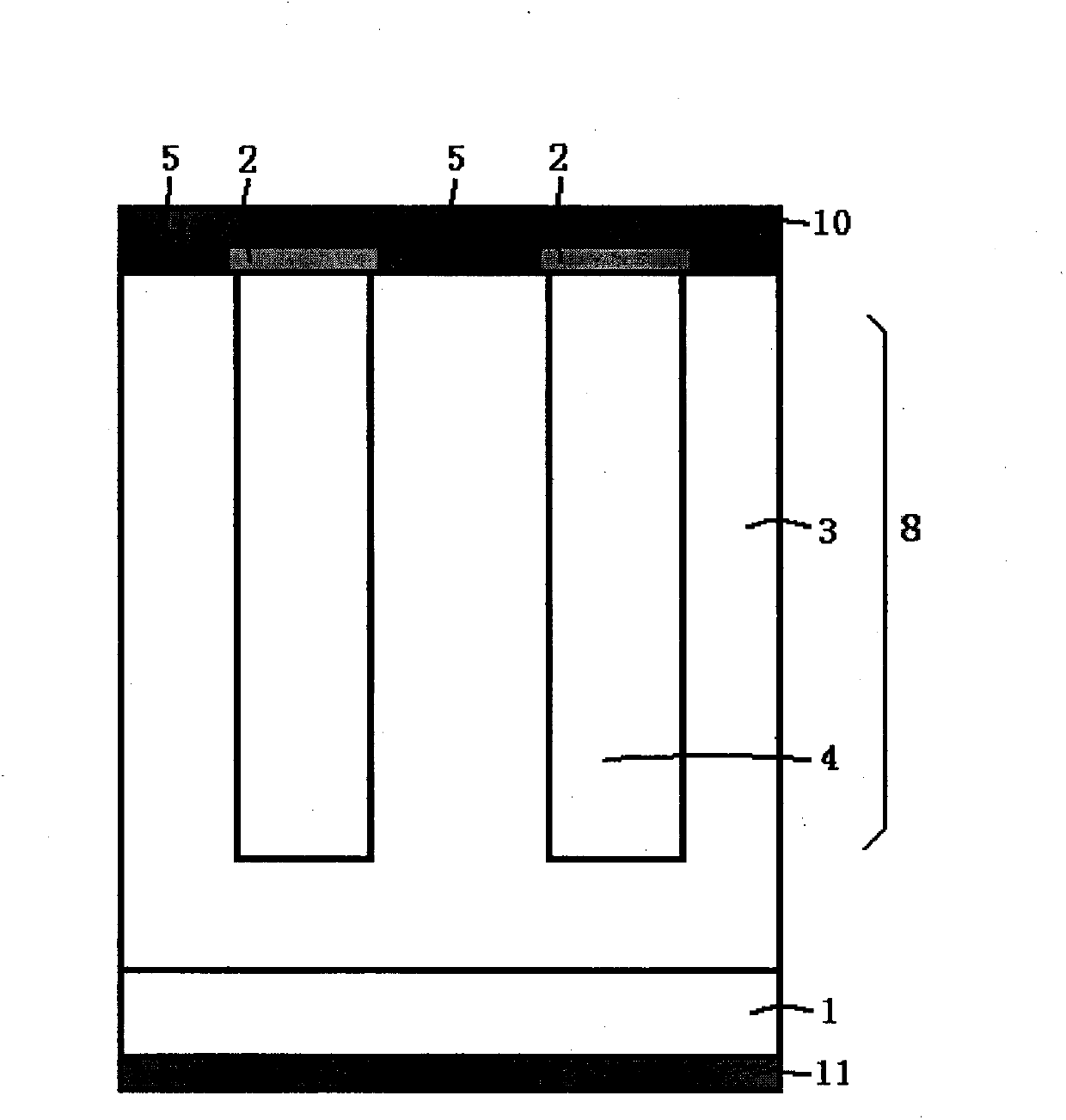

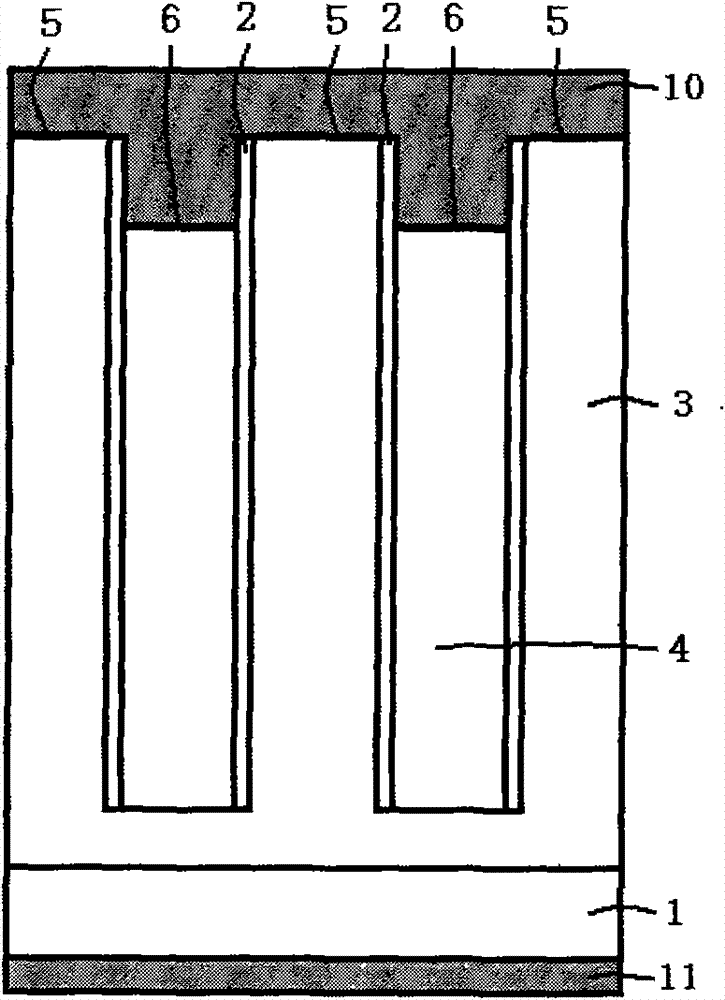

Trench type MOS structure Schottky diode and preparation method thereof

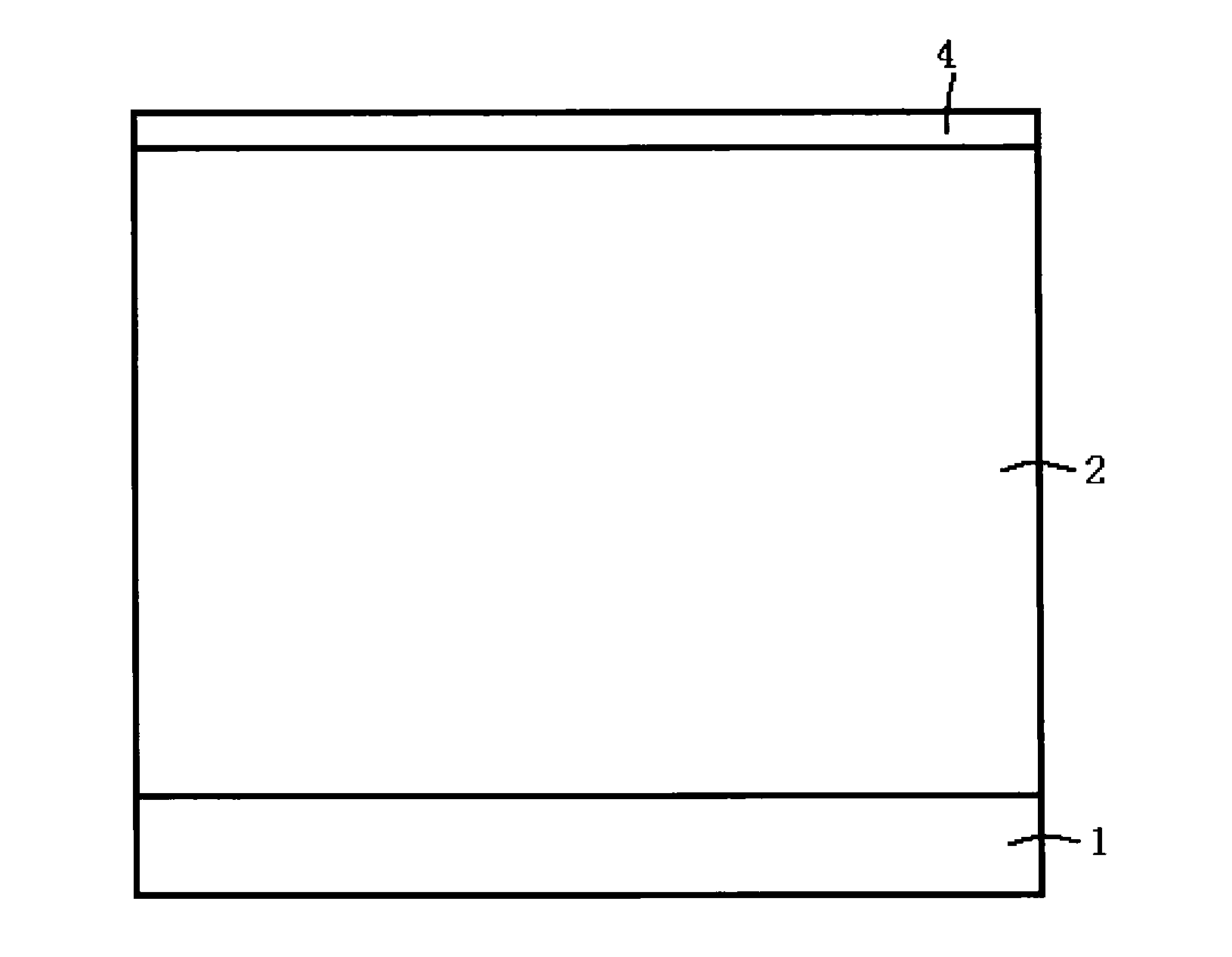

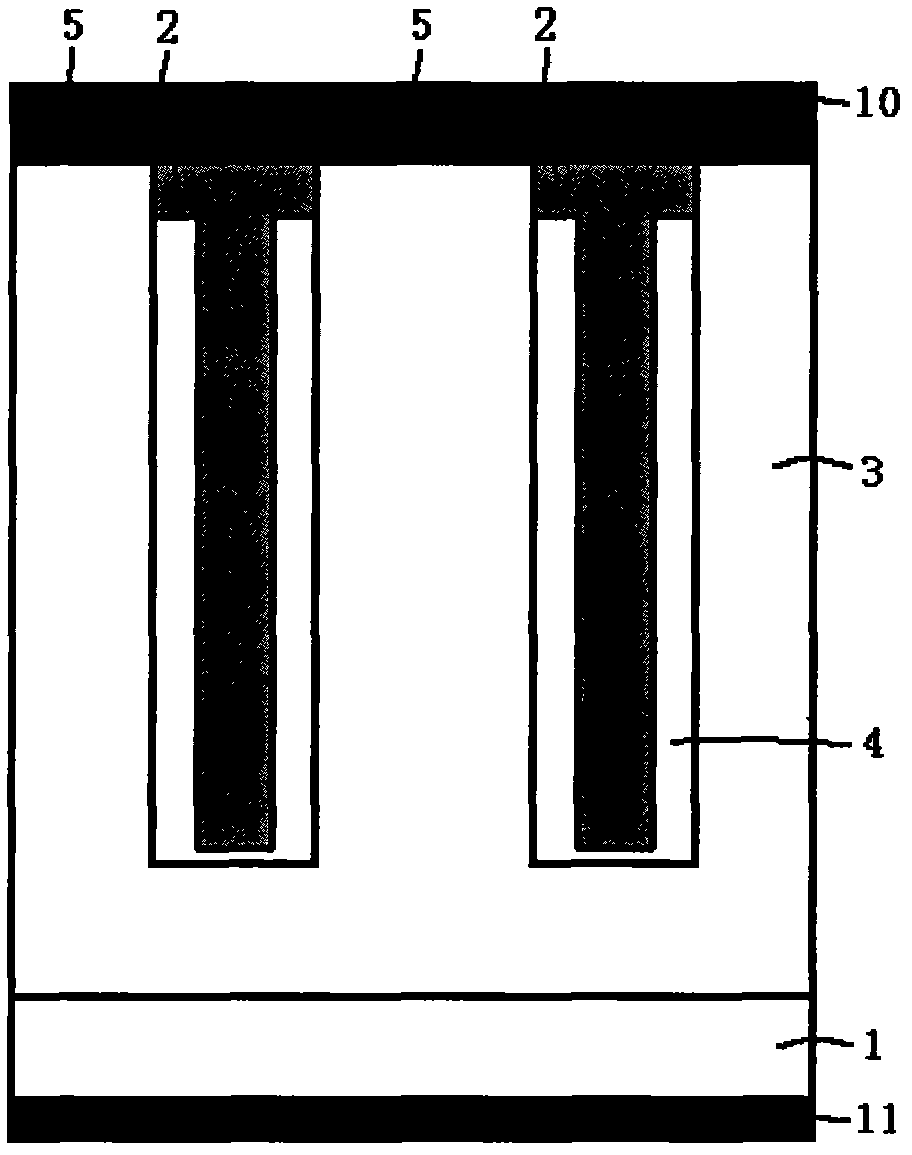

PendingCN111081754AImproved reverse blocking characteristicsThe reverse blocking feature does not affect theSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical field strengthImpurity doping

The invention provides a trench type MOS structure Schottky diode and a preparation method thereof. The trench type MOS structure Schottky diode comprises an N-type doped substrate, an N-type doped epitaxial layer arranged on the upper surface of the N-type doped substrate, and a plurality of trenches extending from the upper surface of the N-type doped epitaxial layer to the N-type doped epitaxial layer; doping concentration in the N-type doped epitaxial layer is gradually increased from top to bottom. Therefore, the impurity doping concentration of the N-type doped epitaxial layer in the Schottky diode is changed (the doping concentration in the N-type doped epitaxial layer is gradually increased from top to bottom); the electric field intensity distribution of the N-type doped epitaxiallayer can be changed, so that peak electric fields at the corners of the bottoms of the trenches are reduced; the reverse blocking characteristic of the Schottky diode and the forward conduction characteristic of the device are improved, namely, the reverse leakage current of the Schottky diode is reduced, and the reverse breakdown voltage of the Schottky diode is increased.

Owner:BYD SEMICON CO LTD +1

High-barrier SiC JBS device and preparation method thereof

PendingCN112310227AReduce manufacturing costHigh electron affinitySemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryDielectric layer

The invention discloses a high-barrier SiC JBS device and a preparation method thereof. The device comprises a first electrode layer, a SiC substrate, an N-SiC epitaxial layer, a second electrode layer, a dielectric layer and a PI layer which are arranged from top to bottom. According to the SiC device, a JBS structure and a surface low-concentration structure are formed on the epitaxial layer, sothat the barrier height of the device is increased, and meanwhile, the electric leakage characteristic of the device is reduced.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

Schottky semiconductor device with insulating layer isolated super-junction structure and preparation method for Schottky semiconductor device

InactiveCN103367462AImprove reverse breakdown voltageLower forward conduction resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceReverse bias

The invention discloses a Schottky semiconductor device with an insulating layer isolated super-junction structure. By a groove structure, a deeper strip-shaped P-type semiconductor silicon material can be realized, when the device is connected with reverse bias, the strip-shaped P-type semiconductor silicon material and an N-type semiconductor silicon material form charge complementation to form the super-junction structure, and the electric field intensity distribution of a drift region is changed to form a flat electric field intensity distribution curve. The invention also provides a preparation method for the Schottky semiconductor device with the insulating layer isolated super-junction structure.

Owner:朱江

Schottky semiconductor device with grooves and preparation method thereof

ActiveCN103378177AImprove forward conduction characteristicsImprove affordabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierEngineering

The invention discloses a Schottky semiconductor device with grooves. The Schottky semiconductor device with the grooves comprises an MOS structure, a PN junction and a Schottky barrier junction. The electric field distribution of reverse bias voltage is changed through the MOS structure, and therefore the forward-direction conductive character of a component is improved. The bearing capacity of transient high voltage of the component is improved through the PN junction. When the semiconductor device is under the forward-direction small electric current density state, the PN junction is not opened, and therefore minority carrier injection of the component is reduced, and the reverse recovery character of the component is improved. The invention provides a preparation method of the Schottky semiconductor device with the grooves.

Owner:北海惠科半导体科技有限公司

Insulated gate tunneling bipolar transistor with U-shaped tunneling insulating layer and manufacturing process

InactiveCN104485353AImprove switching characteristicsIncrease the forward conduction currentSemiconductor/solid-state device manufacturingSemiconductor devicesUltimate tensile strengthElectric field

The invention relates to an insulated gate tunneling bipolar transistor with a U-shaped tunneling insulating layer. A gate electrode tunneling current is generated by the U-shaped tunneling insulating layer, and the very sensitive mutual relation between impedance of the tunneling insulating layer and intensity of an internal electric field of the tunneling insulating layer is utilized to enable the U-shaped tunneling insulating layer to implement conversion between a high impedance state and a low impedance state in a very short electric potential change interval of a gate electrode, and thus, compared with the prior art, the insulated gate tunneling bipolar transistor can realize a better switching characteristic; by bipolar amplification, the positive conduction characteristic of a nanoscale insulated gate transistor is obviously improved. The invention also discloses a specific manufacturing method of the insulated gate tunneling bipolar transistor with the U-shaped tunneling insulating layer. Therefore, the working characteristic of a nanoscale integrated circuit unit is obviously improved, and the insulated gate tunneling bipolar transistor and the manufacturing method are suitable for being popularized and applied.

Owner:SHENYANG POLYTECHNIC UNIV

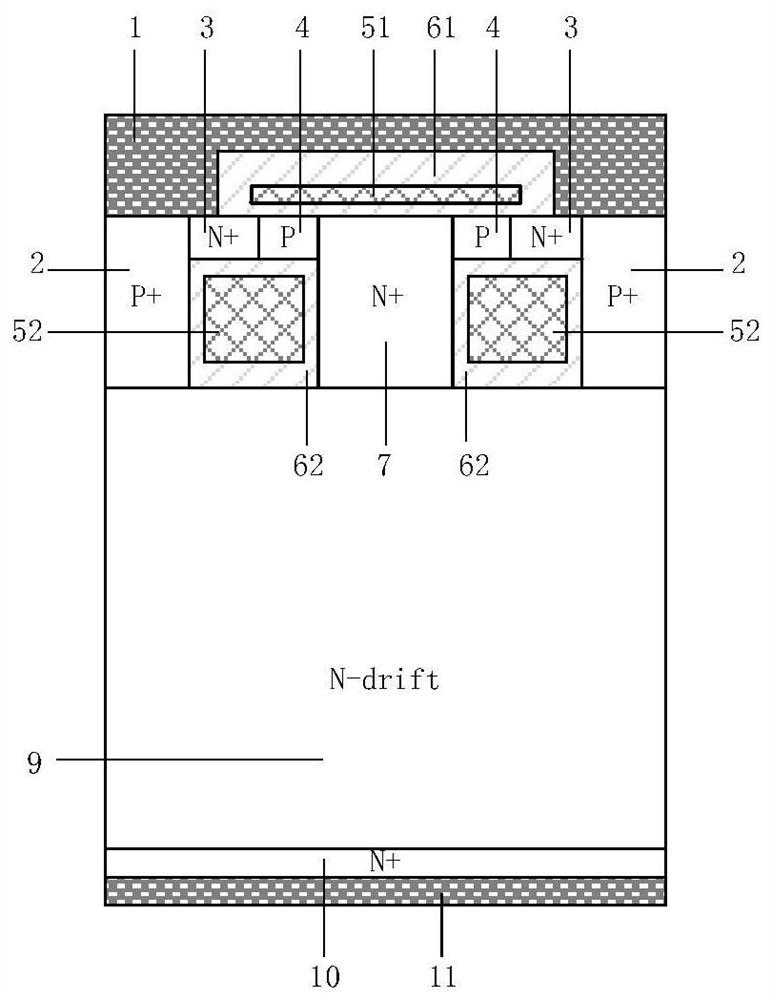

Separation gate SiC MOSFET integrated with heterojunction diode and manufacturing method thereof

ActiveCN114664929APerformance is not affectedConvenient timeEfficient power electronics conversionSemiconductor/solid-state device manufacturingMOSFETHigh concentration

The invention belongs to the technical field of power semiconductor devices, and relates to a separation gate SiCMOSFET of an integrated heterojunction diode and a manufacturing method of the separation gate SiCMOSFET. According to the invention, the heterojunction diode is integrated in the three-dimensional y direction of the SiC MOSFET, so that the cell width of the SiC MOSFET is not increased, the problems of overlarge forward turn-on voltage drop, overlong reverse recovery time and the like of a parasitic diode can be effectively solved, and compared with an internally integrated SBD, the integrated heterojunction diode has smaller forward voltage drop. According to the mode of integrating the heterojunction diode, the area of an active region does not need to be additionally increased, the integration level is higher, and the width of the JFET region is not increased. Meanwhile, the spaced P-type doped regions are introduced in the y direction of the JFET region, so that the electric field distribution of the JFET region of the device and the peak electric field in the oxide layer during blocking work can be improved, a CSL layer with higher concentration can be adopted during design, and the forward conduction characteristic of the device is improved and the resistance of the device during forward conduction is reduced while the reverse blocking characteristic of the device is not reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

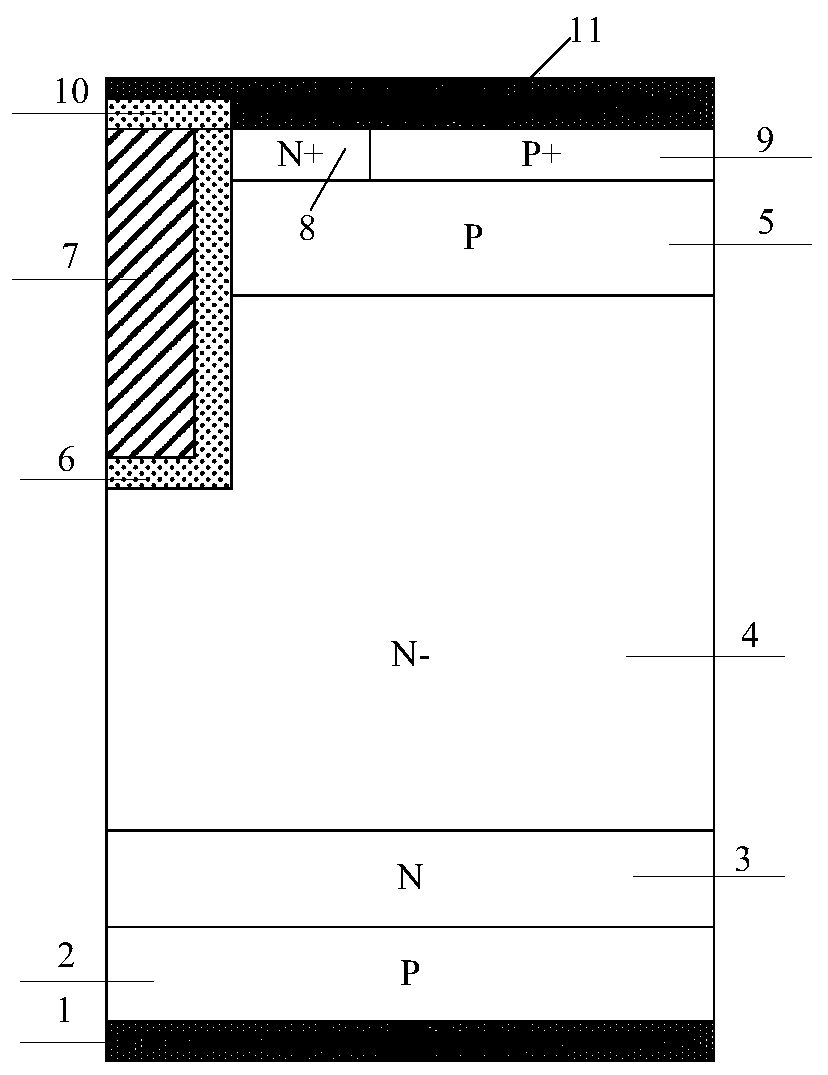

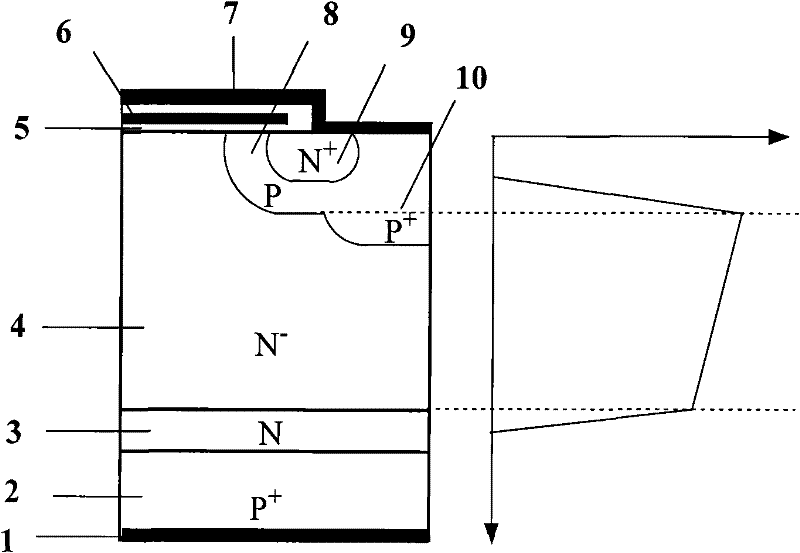

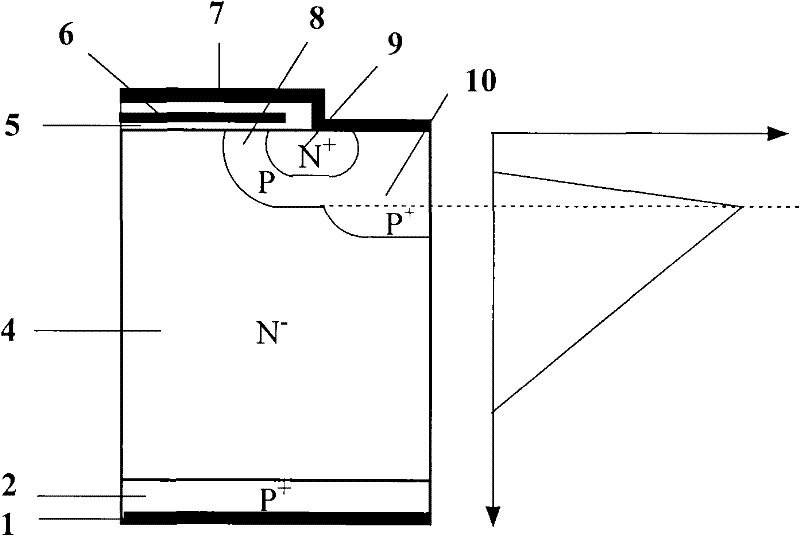

Carrier-storing grooved gate IGBT with P-type floating layer

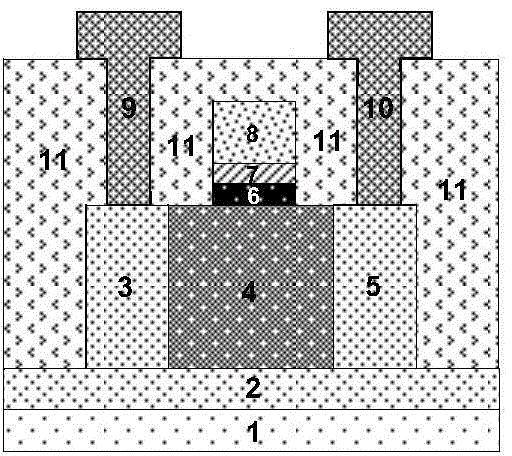

InactiveCN101694850BImprove the electric field concentration effectImprove breakdown voltageSemiconductor devicesHigh concentrationPeak value

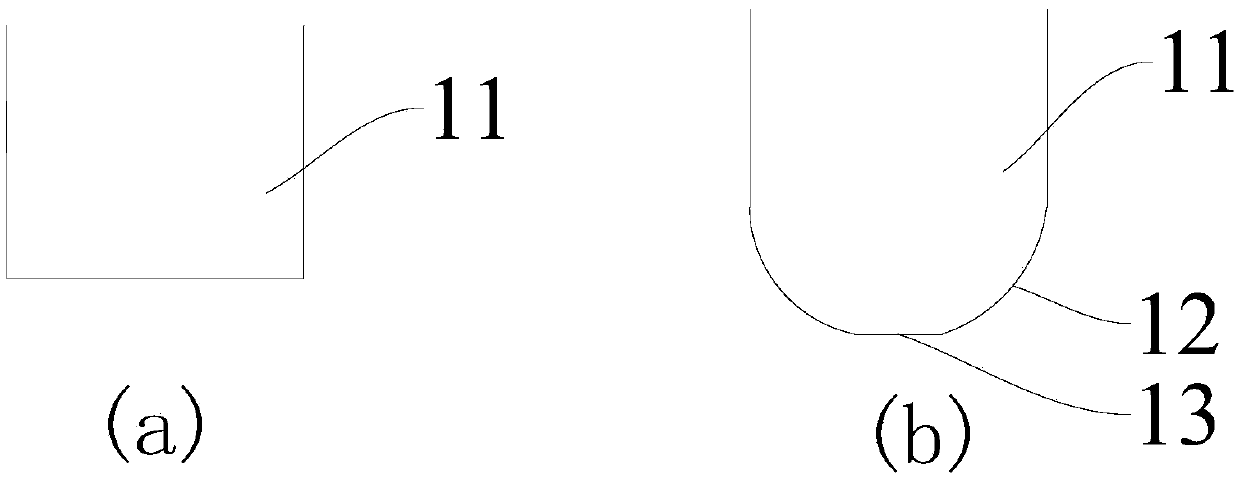

The invention relates to a carrier-storing grooved gate IGBT with a P-type floating layer, belonging to the technical field of semiconductor power devices. On a basis of the prior carrier-storing grooved gate bipolar transistor, a P-type floating layer (13) is introduced to almost free a carrier-storing layer from bearing a withstanding voltage and decrease a forward conducted voltage drop; and the P-type floating layer (13) also improves the electric-field integration effect of the bottom of the grooved gate, thereby effectively decreasing an electric filed with a maximum peak value, preventing the bottom of the grooved gate and the vicinity of the high-concentration carrier-storing layer from being broken down by an overhigh electric field and greatly increasing the breakdown voltage ofthe device. A JFET zone is introduced due to the existence of the P-type floating layer. When the device is forwardly conducted, the resistance of the JFET zone continuously increases along with the continuously increasing voltage of a collector so that the saturation current of the device is decreased, and a lower conducted voltage drop is obtained while maintaining a greater short-circuit safety operation area (SCSOA).

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

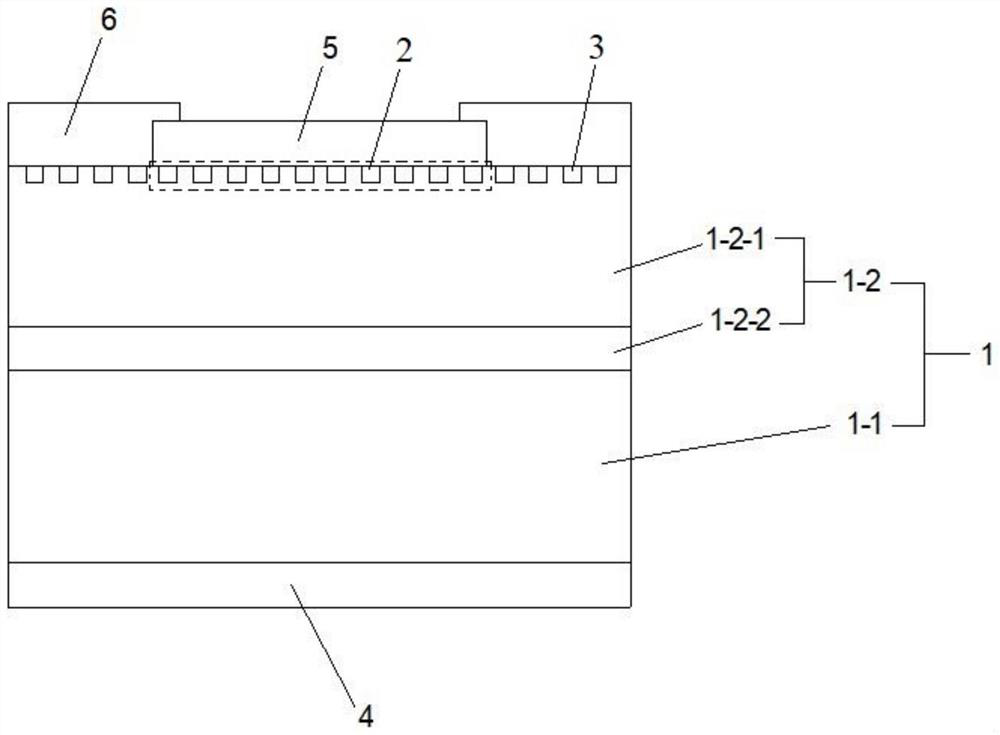

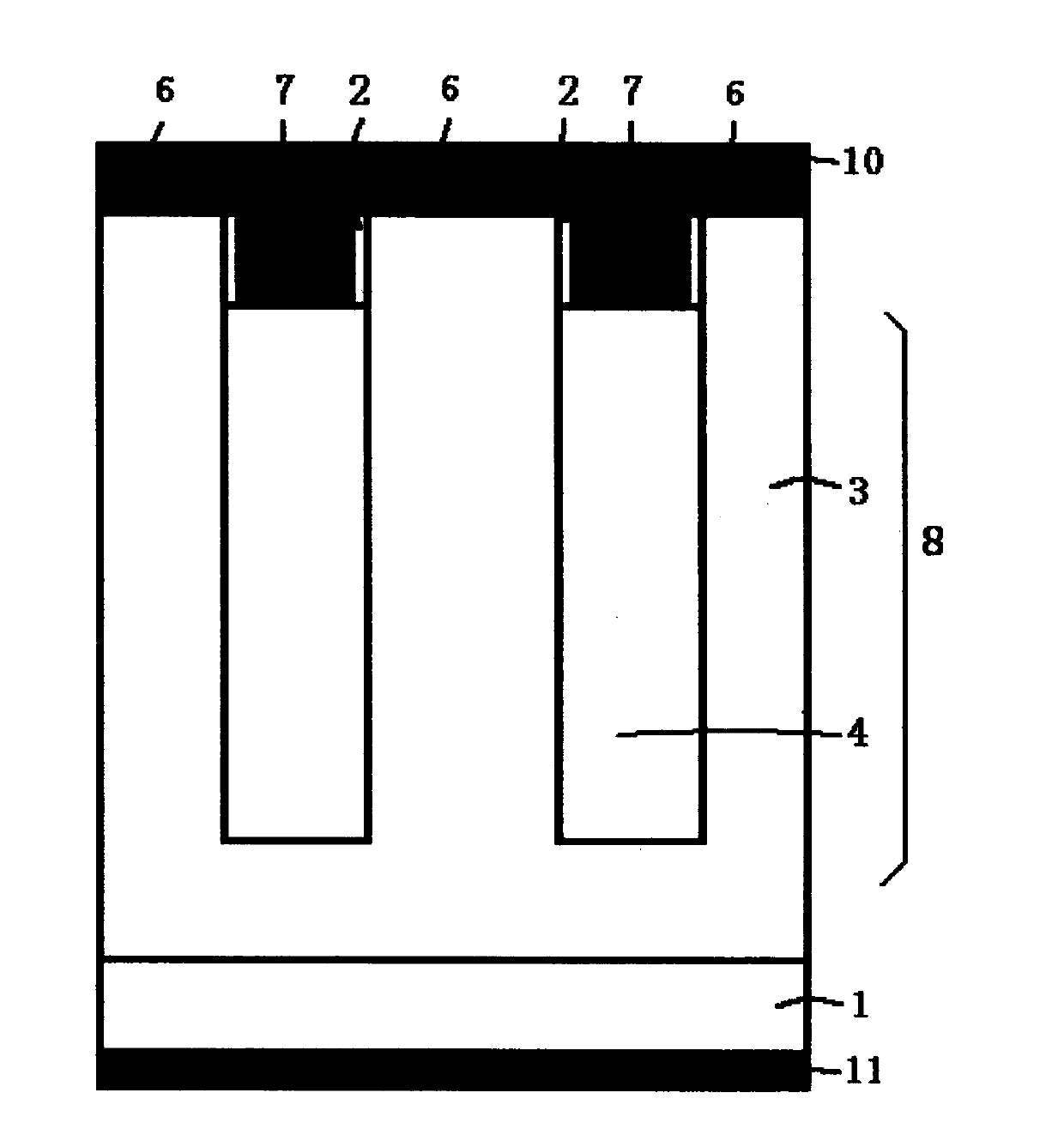

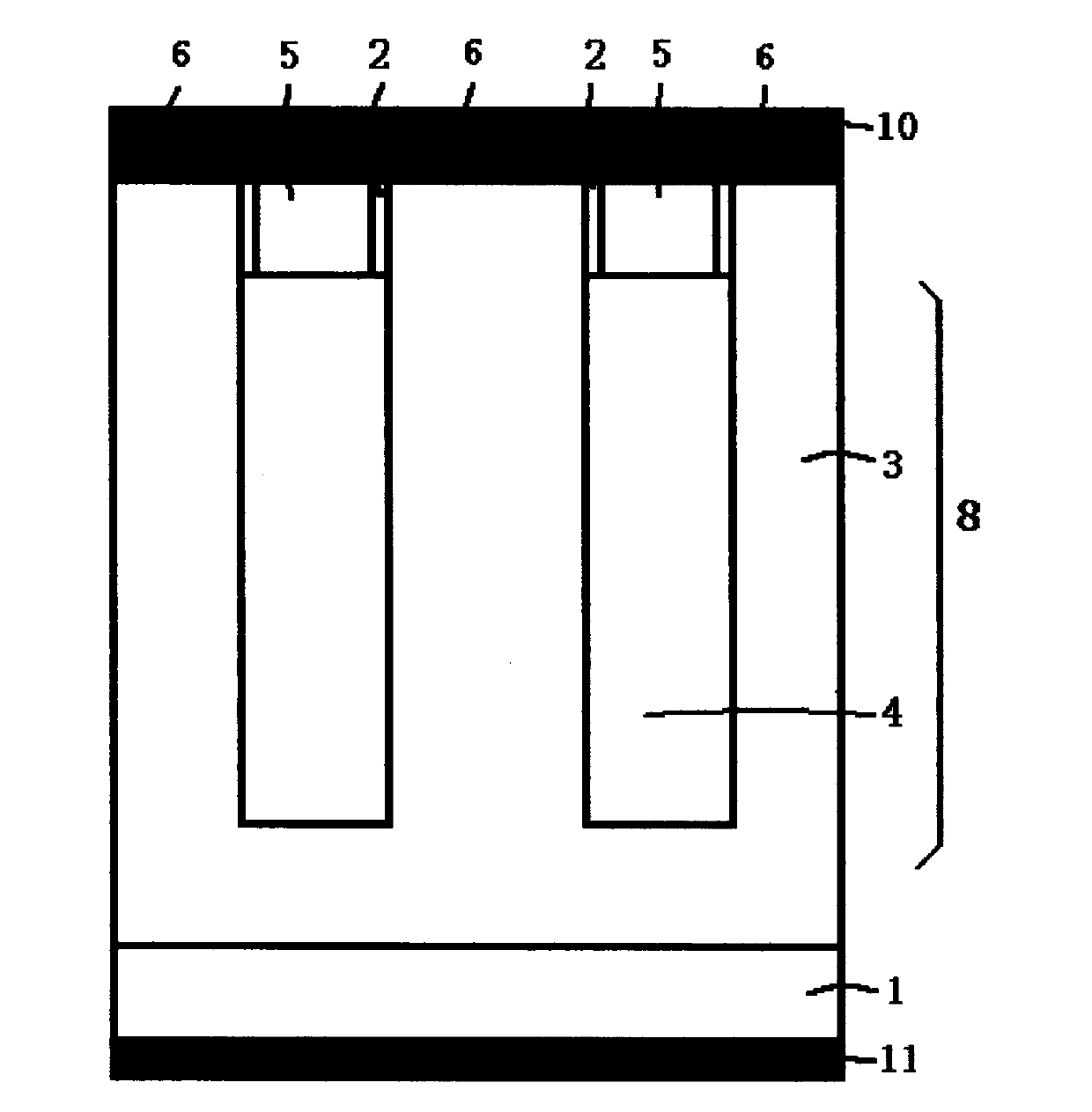

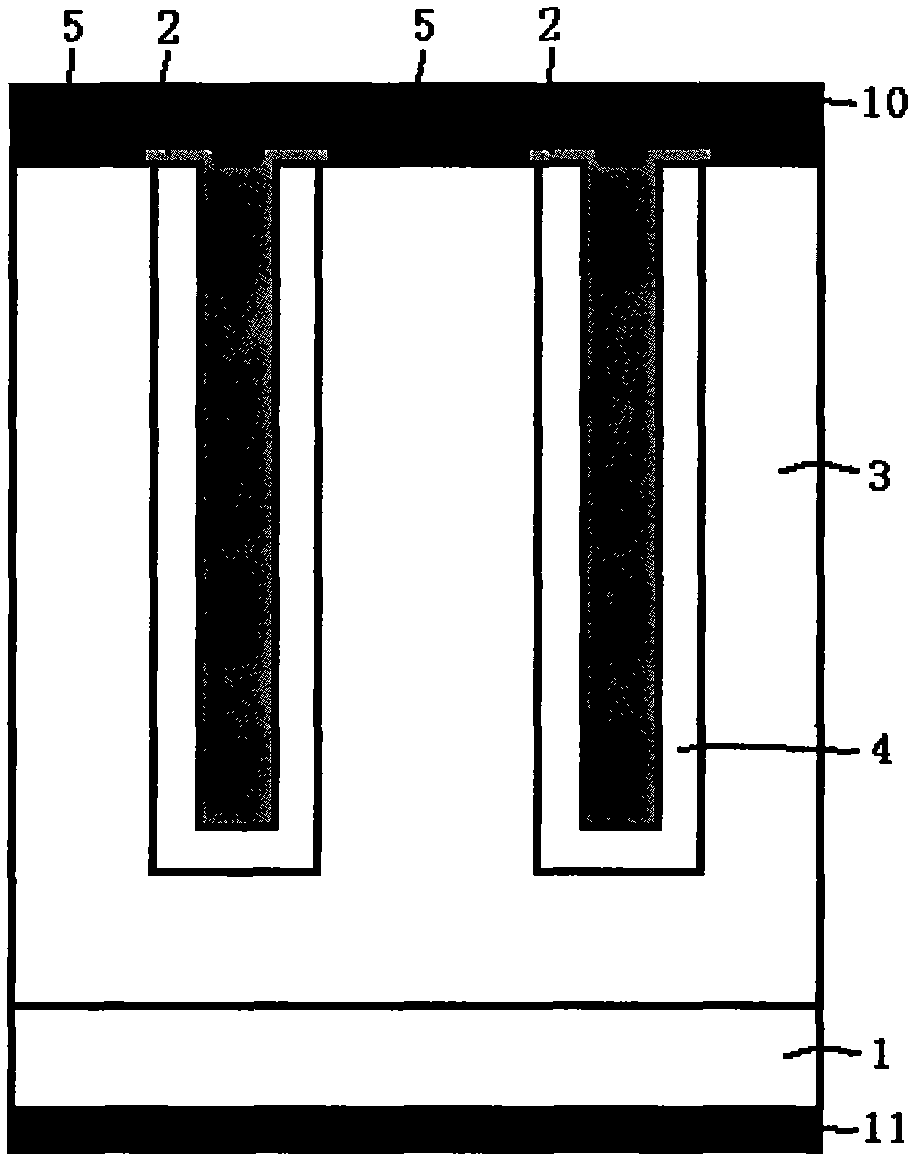

SBD device structure and preparation method thereof

ActiveCN111785785AIncrease current densityIncrease saturation currentSemiconductor/solid-state device manufacturingDiodePhysicsChemistry

The invention provides an SBD device structure and a preparation method thereof. The SBD device structure comprises a substrate, an epitaxial layer grown on the substrate, a nanopillar array preparedin an accommodating groove in the epitaxial layer, a Schottky contact electrode prepared on the epitaxial layer and located in a nanopillar array region, and an ohmic contact electrode prepared on oneside, deviating from the epitaxial layer, of the substrate. According to the method, the Schottky contact area of the anode Schottky type metal-semiconductor of the SBD device is increased by utilizing the nanorods, and the forward conduction characteristic of the SBD device is comprehensively improved from two aspects: on one hand, the nanorods can increase the current density during conduction,so that the saturation current is increased, and the conduction resistance is reduced; and on the other hand, the nanopillar can enhance the control capability of the external bias voltage on the epitaxial layer, and the current driving capability of the SBD device is effectively improved, so that the turn-on voltage of the SBD device is reduced, and the switching loss is reduced.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

Charge compensation Schottky semiconductor device and manufacturing method thereof

InactiveCN103378131AIncrease the doping concentrationLower forward conduction resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceEngineering

The invention discloses a charge compensation Schottky semiconductor device. When a certain reverse bias voltage is connected to the semiconductor device, first electric conduction semiconductor material and second electric conduction semiconductor material can form charge compensation and improve reverse breakdown voltage of the device or improve the forward direction communication characteristic of the device. The invention further provides a manufacturing method of the super junction Schottky semiconductor device.

Owner:朱江

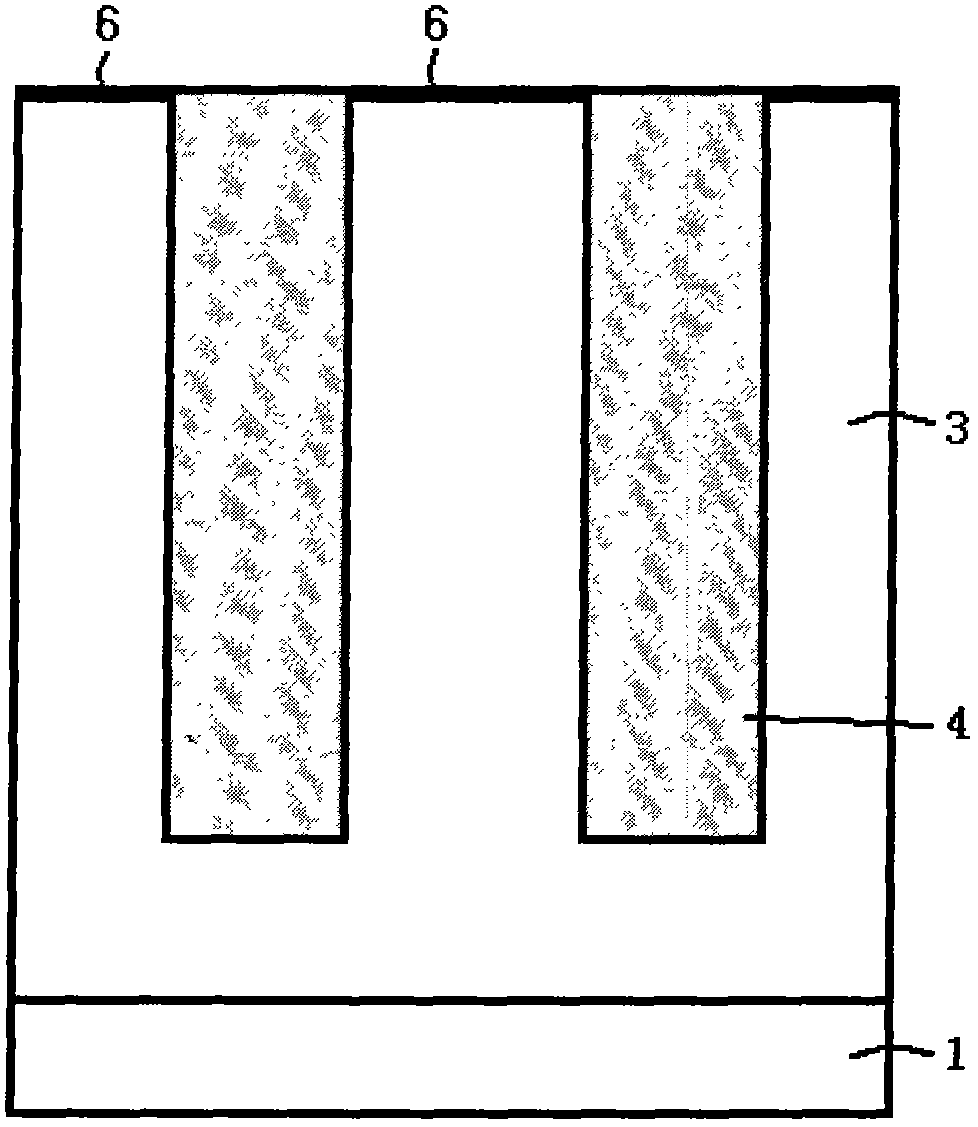

Groove schottky semiconductor device and manufacturing method thereof

ActiveCN103390651AIncrease the doping concentrationLower forward conduction resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSemiconductor materials

The invention discloses a groove schottky semiconductor device which is provided with a charge compensation structure. First conducting semiconductor materials and second conducting semiconductor materials can form charge compensation when the semiconductor device is connected with a certain reverse bias, so that positive conducting or reverse blocking characteristics of the device can be improved. The invention further provides a manufacturing method of the groove schottky semiconductor device.

Owner:北海惠科半导体科技有限公司

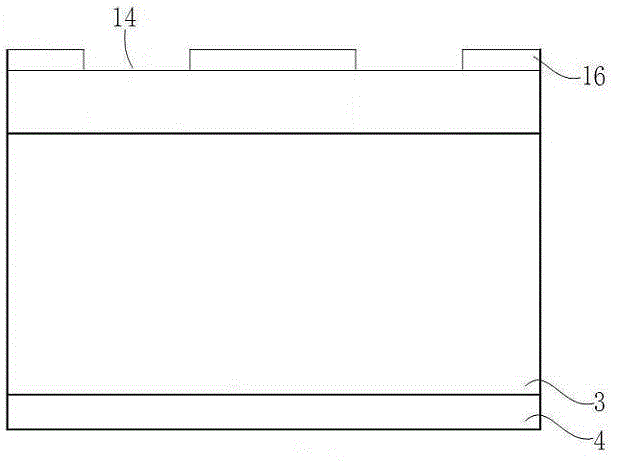

VDMOS device with high avalanche tolerance and preparation method

InactiveCN111697078AImprove forward conduction characteristicsImprove anti-UIS abilitySemiconductor/solid-state device manufacturingSemiconductor devicesBody regionAvalanche breakdown

The invention relates to the technical field of power semiconductor devices. The invention relates to a VDMOS with improved avalanche tolerance and a preparation method. According to the invention, asecond polysilicon gate electrode is introduced into the device to replace part of abody region underasource region of atraditional VDMOS structure; aJEFT region is subjected to medium doping with thesame impurity type as adrift region; when the device is in forward conduction, afirst polysilicon gate electrode and the second polysilicon gate electrode can form a double-inversion-layer channel inthe body region inthe side part of the source region, and an accumulation layer of majority carriers is formed in the JEFT region, so that the forward conduction characteristic of the VDMOS is improved; when the device is in an avalanche breakdown state, there is no parasitic triode under the source region any more, the breakdown position can be fixed to the interface of anohmic contact region onthe side of the source region and the drift region, avalanche current can only flow out of the source electrode through the ohmic contact region, and the avalanche tolerance of the VDMOS is improved.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Hybrid Schottky barrier diode structure with P-type nickel oxide material

ActiveCN112909076ASolve difficultySolve process problemsSemiconductor devicesSchottky barrierSemiconductor materials

The invention relates to a hybrid Schottky barrier diode structure with a P-type nickel oxide material. The structure comprises a bottom ohmic contact electrode, an N+ substrate, an N-drift layer, a groove, a P-type layer, a field plate dielectric layer, field plate metal and a Schottky contact electrode, the N-drift layer is of a step structure, and p-NiO materials are grown on selected areas on the two sides of a table top to replace P-type wide bandgap semiconductor materials. Therefore, the problem that a P-type epitaxial growth technology and an ion implantation technology of a wide bandgap semiconductor material at the present stage are immature can be well solved. The structure is high in operability, low in cost, simple and reliable in process and suitable for industrial application and popularization.

Owner:HEBEI UNIV OF TECH

Schottky semiconductor device with charge compensation groove and preparing method thereof

ActiveCN103515449AIncrease the doping concentrationLower forward conduction resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsEngineering

The invention discloses a Schottky semiconductor device with a charge compensation groove. According to the Schottky semiconductor device with the charge compensation groove, a charge compensation structure can be formed by a first conductive semiconductor material and a second conductive semiconductor material, electric field intensity which can reduce Schottky junctions on the surface of the first conductive semiconductor material exists in the groove in the surface of the device, and then reverse breakdown voltage of the device is improved. The invention further provides a preparing method of the Schottky semiconductor device with the charge compensation groove.

Owner:北海惠科半导体科技有限公司

Schottky semiconductor device and method for preparing same

ActiveCN103378172AIncrease the doping concentrationLower forward conduction resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsDevice material

The invention discloses a schottky semiconductor device which is provided with a charge compensation structure. When the semiconductor device is connected to a certain reverse bias voltage, first electric conduction semiconductor material and second electric conduction semiconductor material can form charge compensation, and the characteristic of forward conduction or reverse blocking of the device is improved. The invention further provides a method for preparing the schottky semiconductor device.

Owner:北海惠科半导体科技有限公司

A ret IGBT with self-biased pmos and its fabrication method

ActiveCN110504310BImprove forward conduction characteristicsEffect of shield breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceCapacitance

The invention belongs to the technical field of power semiconductor devices, and relates to a RET IGBT with self-biased PMOS and a manufacturing method thereof. In the present invention, by placing the N-type charge storage layer between the P-type base region and the P-type buried layer, while improving the forward conduction characteristics of the device, it can shield the influence of the N-type N-type charge storage layer on the breakdown voltage of the device. , by introducing a PMOS structure, an additional path is provided for the extraction of holes, which accelerates the extraction speed of carriers, improves the switching speed of the device, and reduces the turn-off loss of the device. The structure can meet the requirement that the device mesa is further narrowed to improve the forward conduction characteristic of the device, and it is easy to make the metal contact hole of the emitter of the device, and at the same time, the Miller capacitance of the device can be further reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

A Schottky semiconductor device with charge compensation trench and its preparation method

ActiveCN103515449BImprove reverse breakdown voltageReduce electric field strengthSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsEngineering

The invention discloses a Schottky semiconductor device with a charge compensation groove. According to the Schottky semiconductor device with the charge compensation groove, a charge compensation structure can be formed by a first conductive semiconductor material and a second conductive semiconductor material, electric field intensity which can reduce Schottky junctions on the surface of the first conductive semiconductor material exists in the groove in the surface of the device, and then reverse breakdown voltage of the device is improved. The invention further provides a preparing method of the Schottky semiconductor device with the charge compensation groove.

Owner:北海惠科半导体科技有限公司

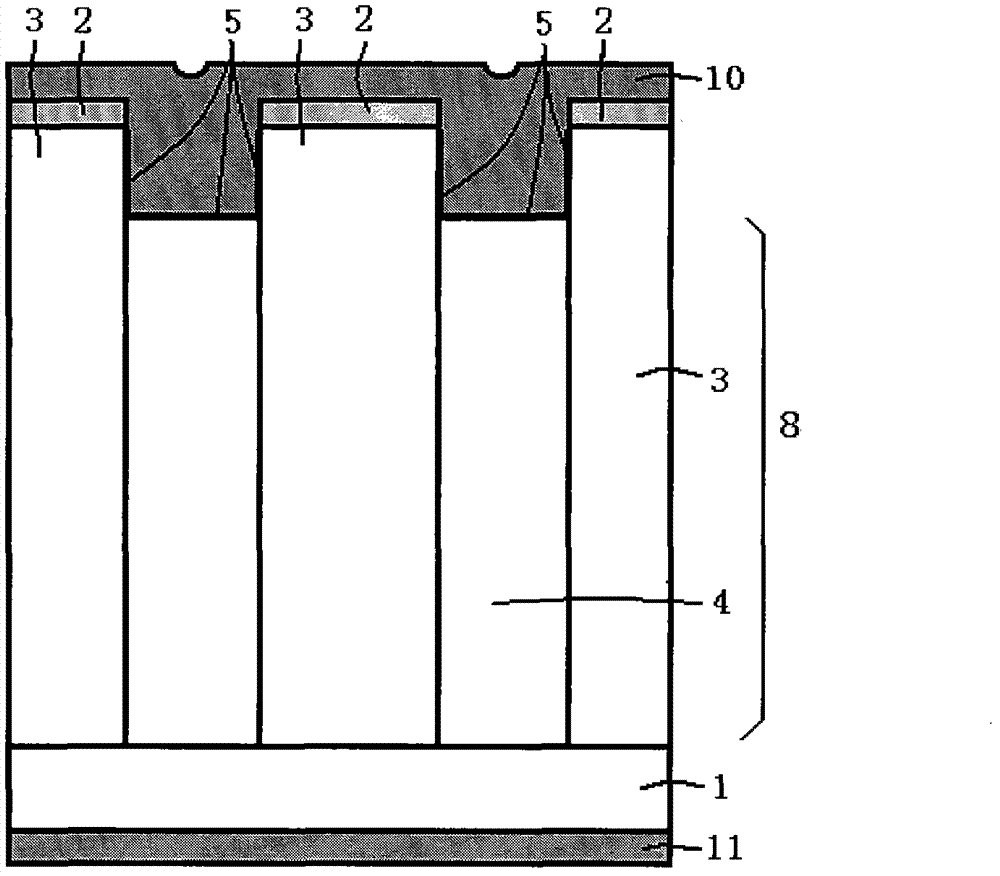

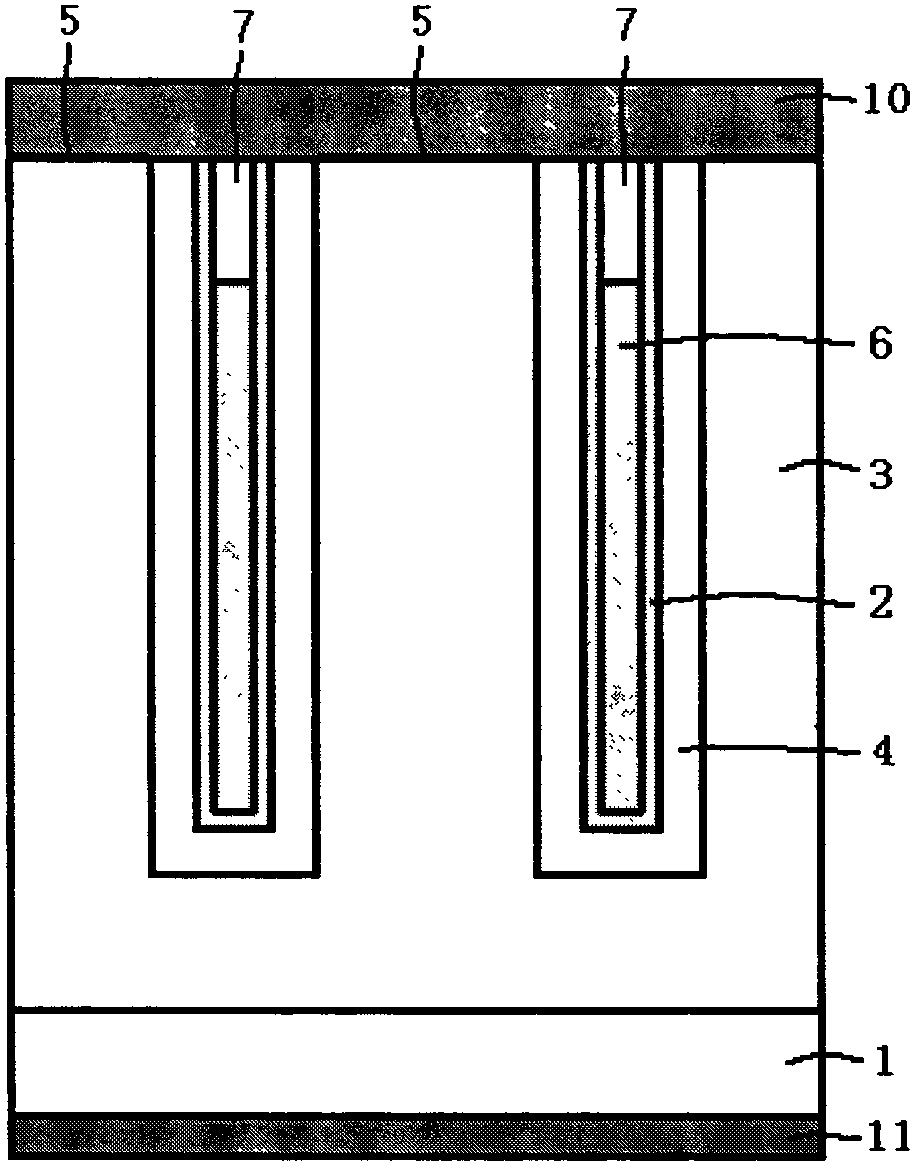

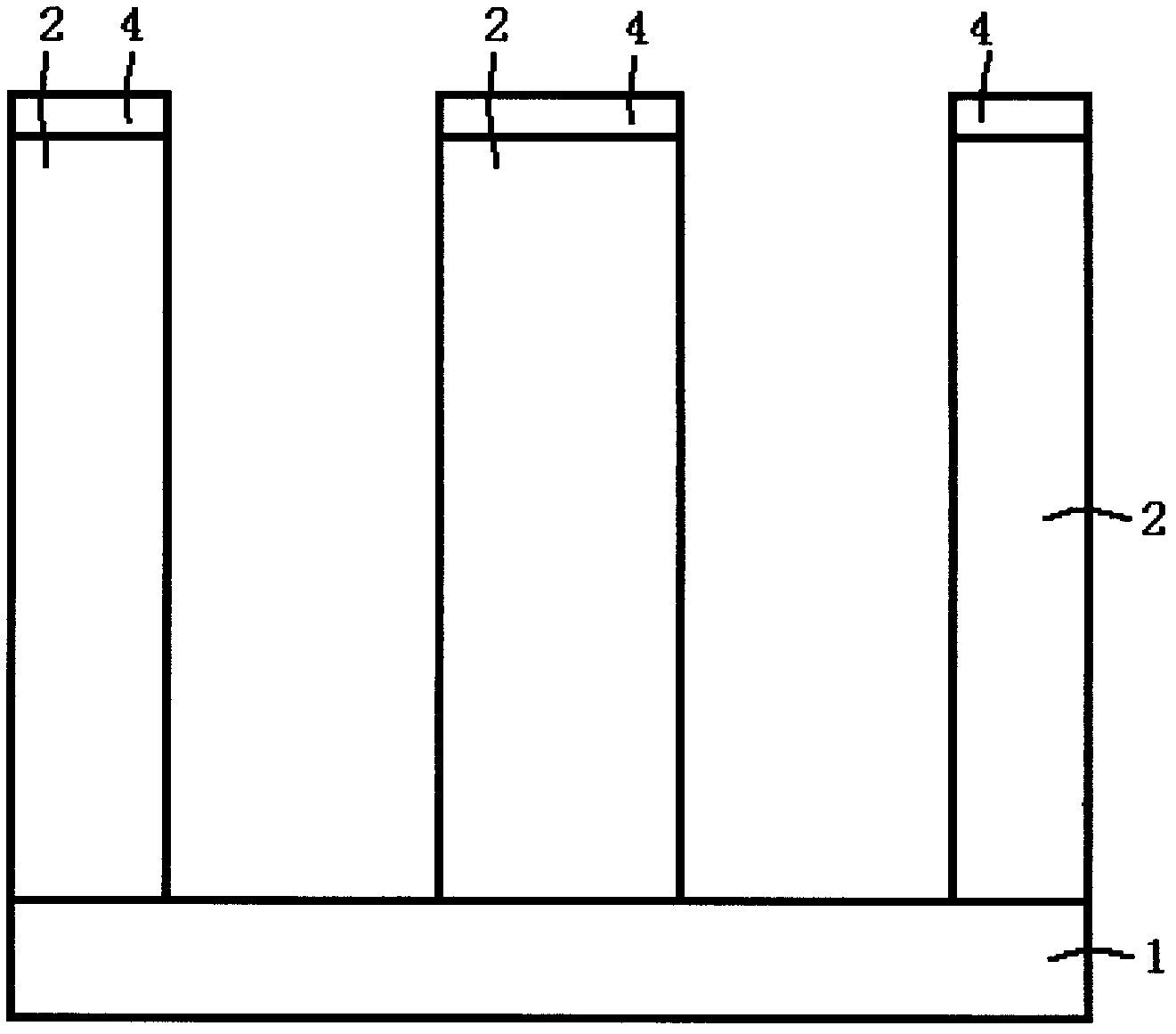

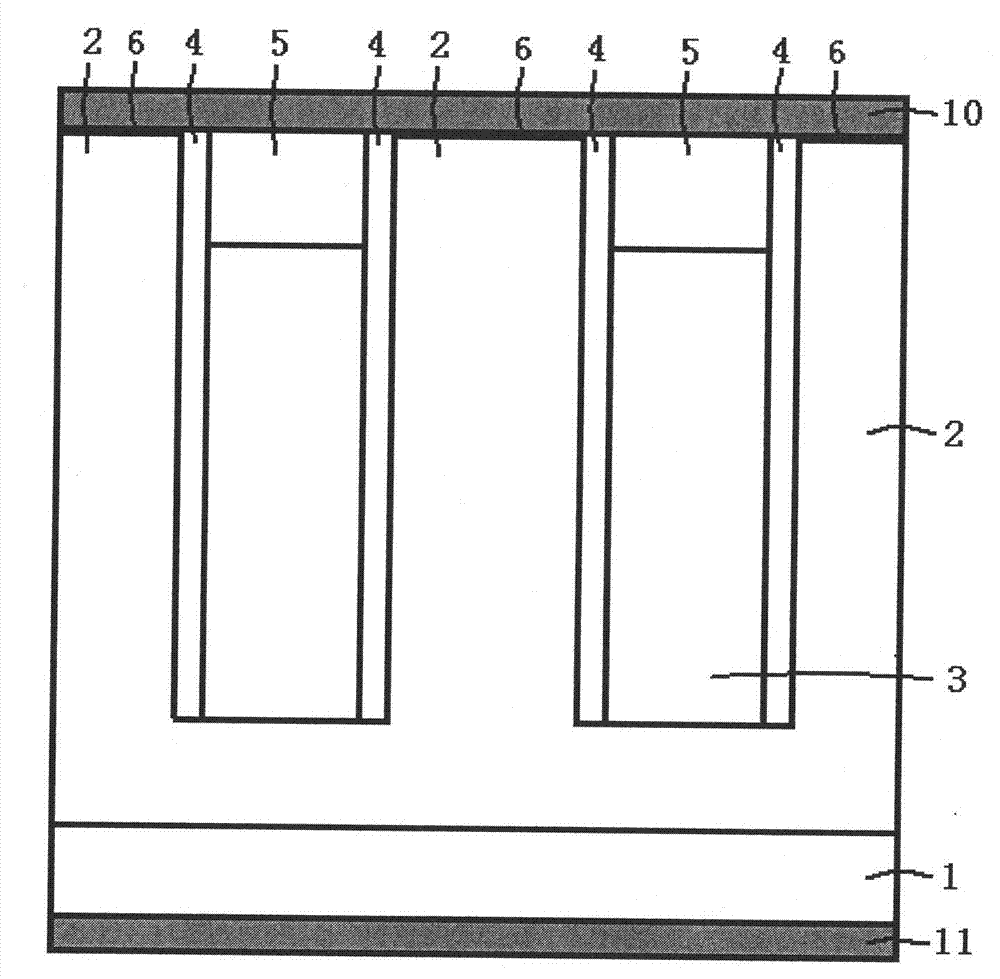

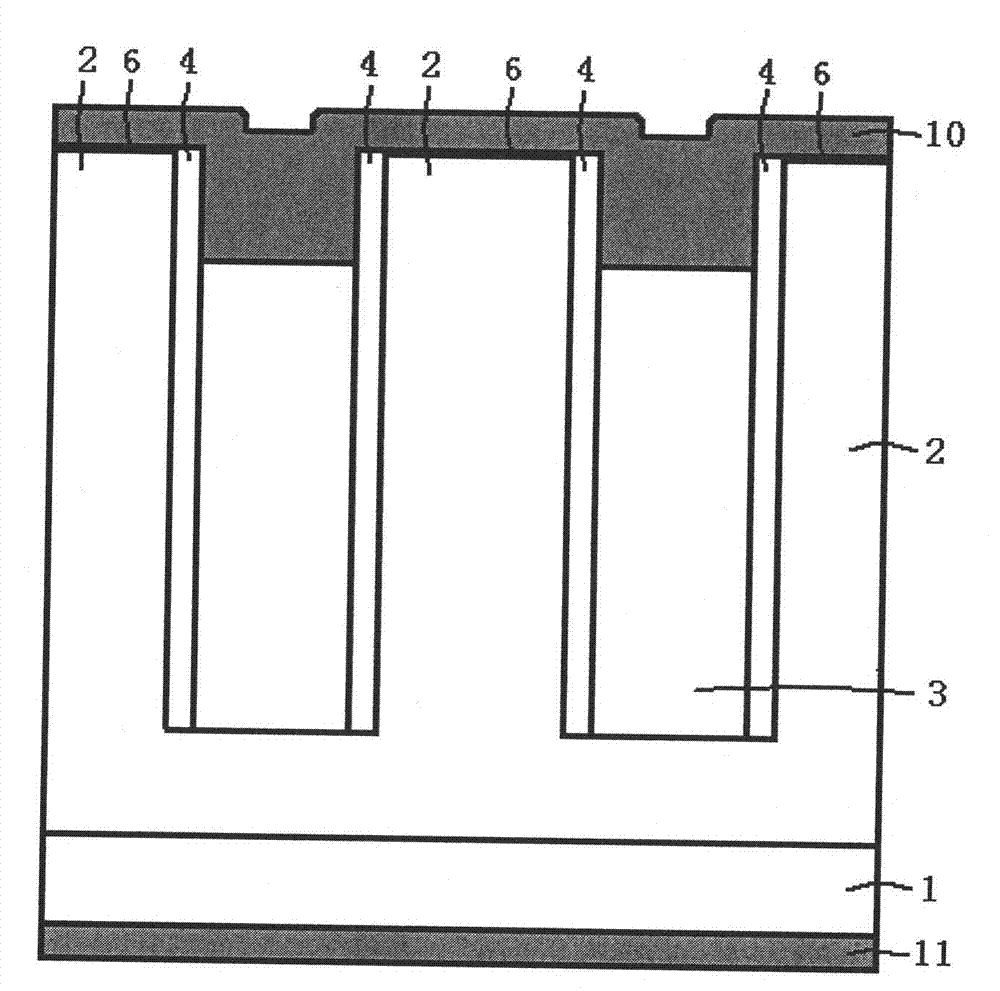

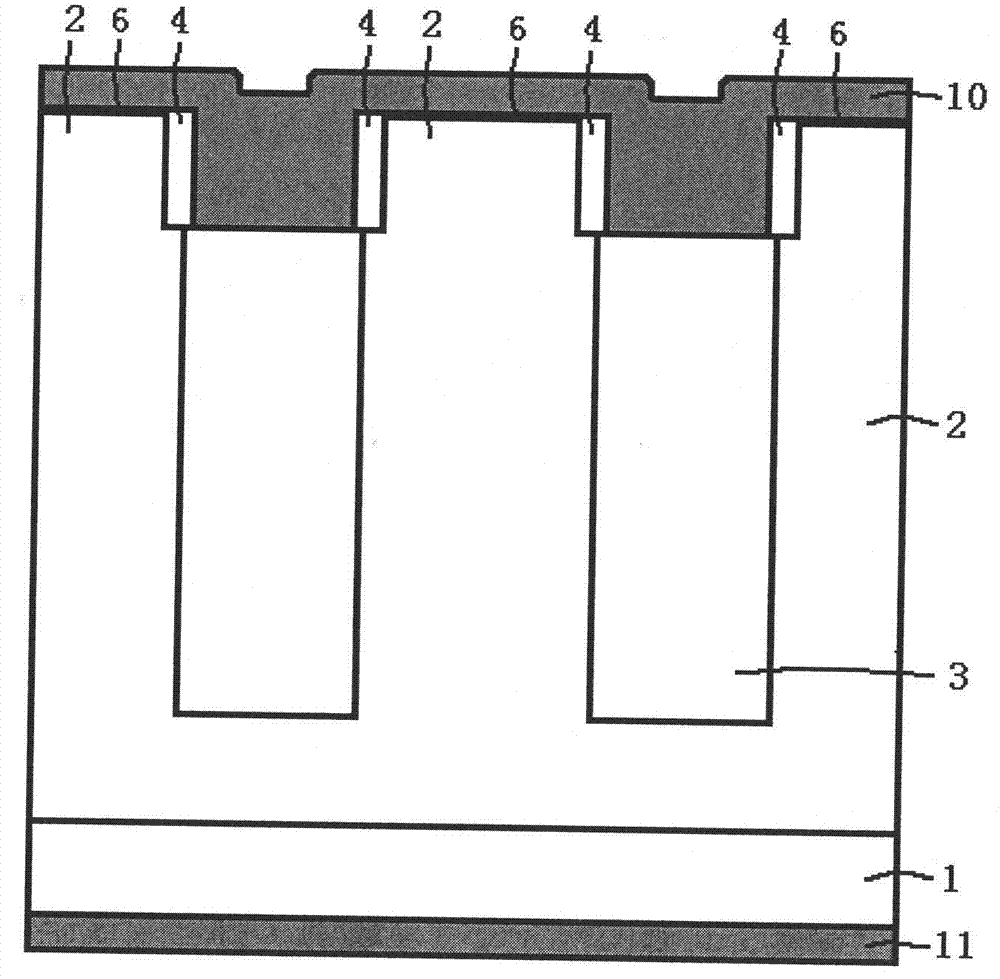

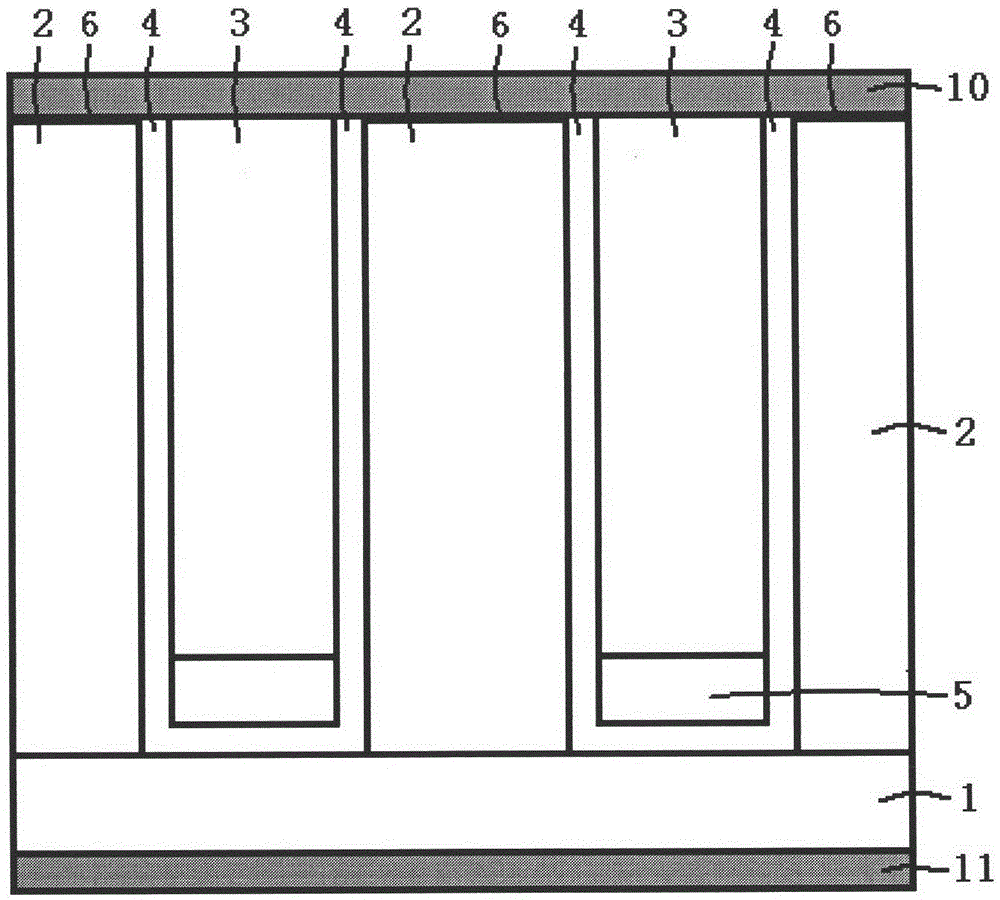

A trench Schottky semiconductor device with multiple insulating layer isolation and its preparation method

ActiveCN103137710BImprove concentrationImprove forward conduction characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceManufactured apparatus

The invention discloses a trench Schottky semiconductor device with various insulating layer isolation. Through various insulating layer structures, the electric field intensity distribution of drift regions is changed, and inverse voltage blocking properties of apparatuses are improved. The invention further provides a preparation method capable of achieving two-time photolithography processes to manufacture apparatuses.

Owner:SEMICON MFG ELECTRONICS (SHAOXING) CORP