SOI (Silicon on Insulator) substrate folding grid insulating tunneling enhanced transistor and manufacturing method thereof

A gate insulation and transistor technology, applied in the field of ultra-large-scale integrated circuit manufacturing, can solve the problems of small forward conduction current, increase the difficulty of the process, and cannot substantially improve the tunneling probability of silicon materials, and achieve the effect of improving the production rate.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

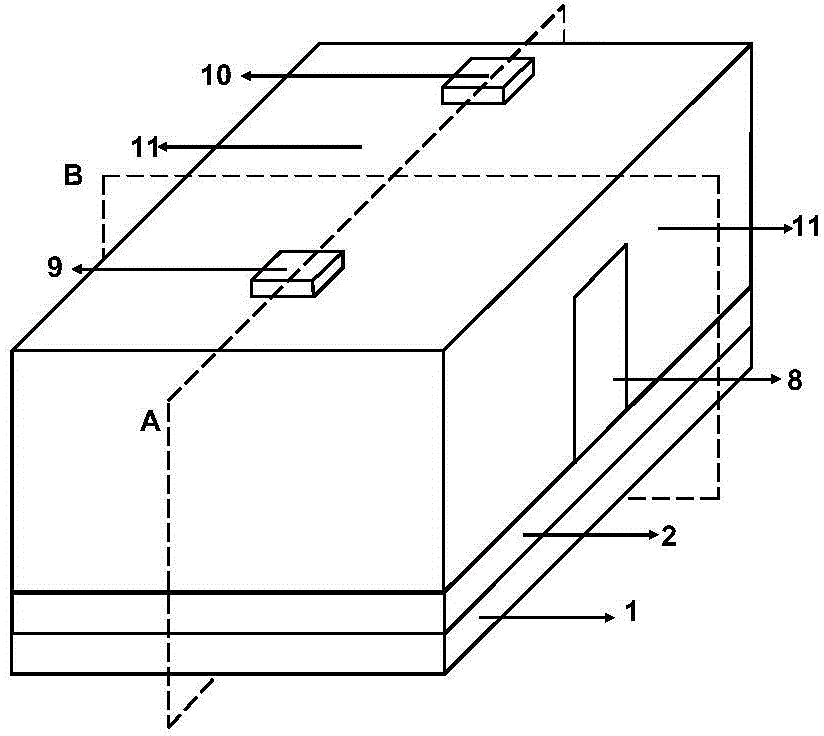

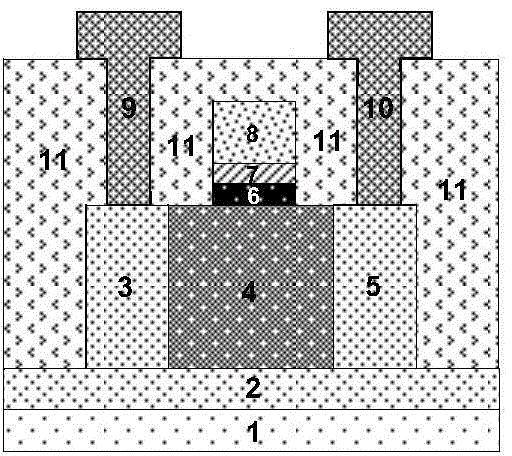

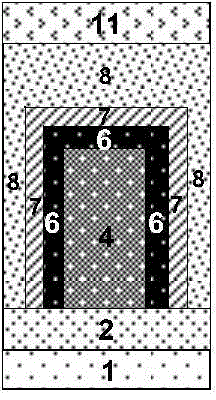

[0079] Below in conjunction with accompanying drawing, the present invention will be further described: figure 1 It is a schematic diagram of the three-dimensional structure of the SOI substrate folded gate insulation tunneling enhancement transistor formed on the SOI substrate of the present invention; figure 2 SOI substrate folded gate insulation tunneling enhanced transistor edge of the present invention figure 1 The two-dimensional cross-sectional view obtained after cutting on the middle A plane; image 3 SOI substrate folded gate insulation tunneling enhanced transistor edge of the present invention figure 1 The two-dimensional cross-sectional view obtained after cutting in the middle B plane; Figure 4 A schematic diagram of a three-dimensional structure after peeling off the blocking insulating layer 11 for the SOI substrate folded gate insulation tunneling enhancement transistor of the present invention; Figure 5 A schematic diagram of a three-dimensional structu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More