VDMOS device with high avalanche tolerance and preparation method

An avalanche tolerance and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of inability to completely eliminate parasitic BJT turn-on, device failure, etc., to improve forward conduction characteristics and improve UIS resistance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

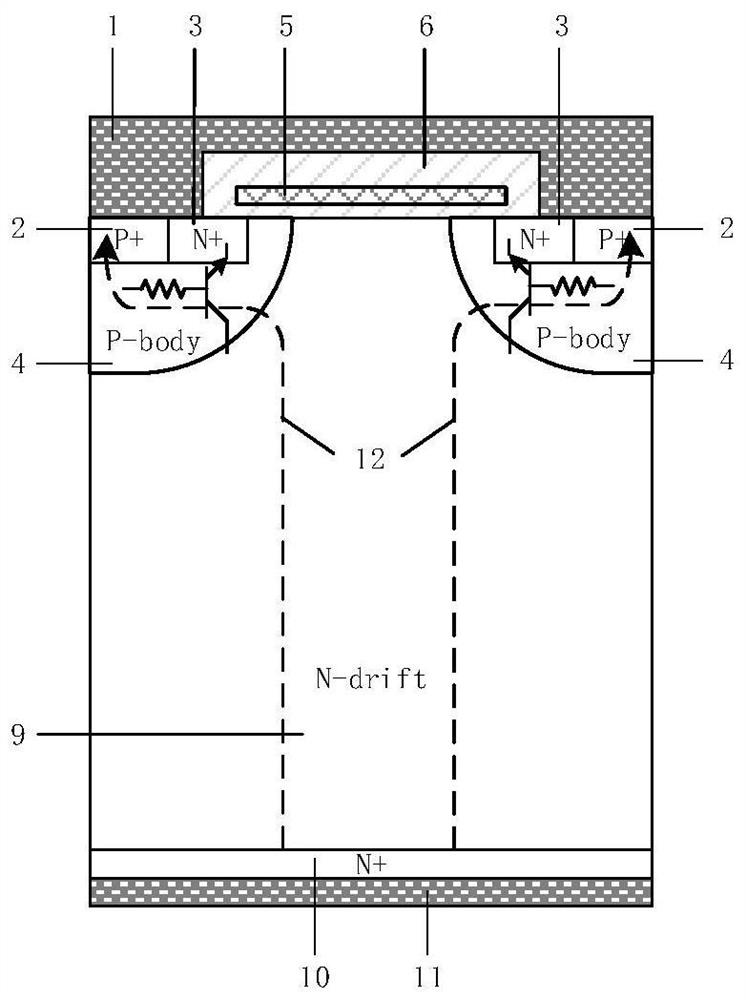

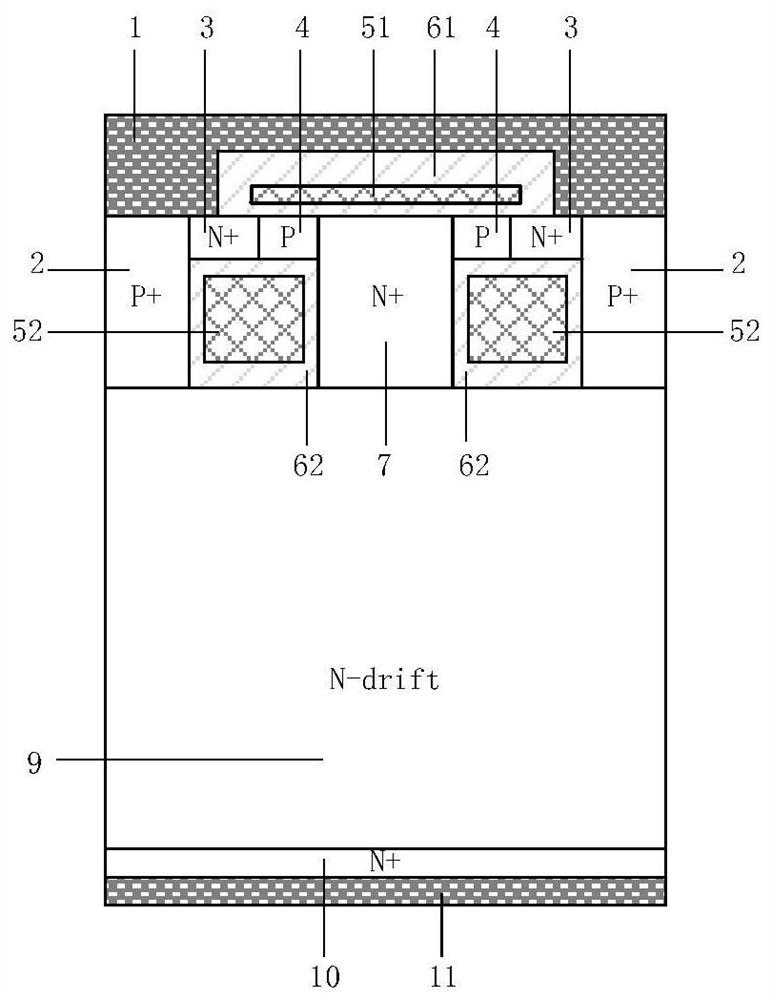

[0050] A high avalanche withstand VDMOS device, the structure of which is as figure 2 As shown, including drain structure, drift region structure, JEFT region structure, source structure, gate structure;

[0051] The drain structure includes a drain metal layer 11, a heavily doped second conductivity type semiconductor drain region 10 above the drain metal layer 11, the lower surface of the heavily doped second conductivity type semiconductor drain region 10 and the drain The metal layer 11 is in direct contact;

[0052] The drift region structure includes a lightly doped second conductivity type semiconductor drift region 9 above the second conductivity type semiconductor drain region 10; the lower surface of the lightly doped second conductivity type semiconductor drift region 9 is heavily doped The doped semiconductor drain region 10 of the second conductivity type is in direct contact with, and the lightly doped semiconductor drift region 9 of the second conductivity typ...

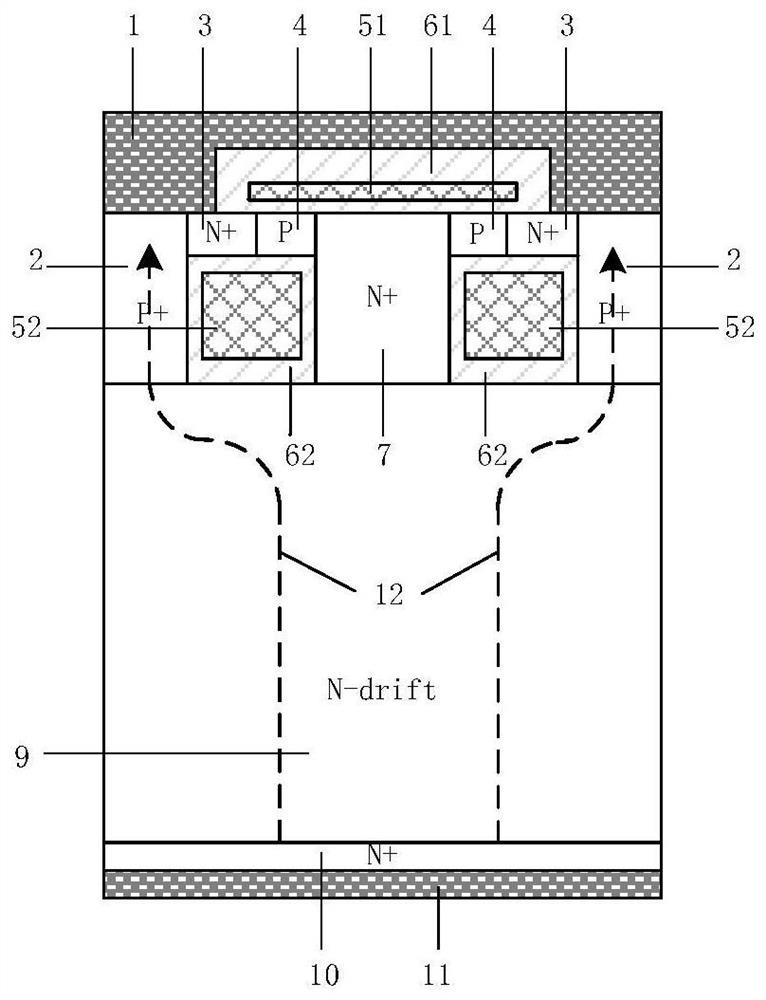

Embodiment 2

[0076] Based on the structure of Example 1, the structure of this example replaces the lightly doped semiconductor drift region structure of the second conductivity type with a super junction structure, such as Figure 4As shown, the drift region is alternately arranged with lightly doped semiconductor drift regions 8 of the first conductive type and semiconductor regions 9 of lightly doped second conductive type with the same width and doping concentration, so that a high The avalanche-resistant double-channel super-junction VDMOS can further reduce the on-resistance of the device and obtain a higher blocking voltage compared with Example 1.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More