High performance SOI non-junction transistor of non-monolithic substrate insulation layer thickness

A technology with insulating layer thickness and junction-free transistors, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the influence of carrier distribution, increase the resistance of source and drain regions, and affect the forward conduction characteristics of devices, etc. problems, achieve the effect of optimizing relative position and size, reducing leakage current, and realizing substrate voltage control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

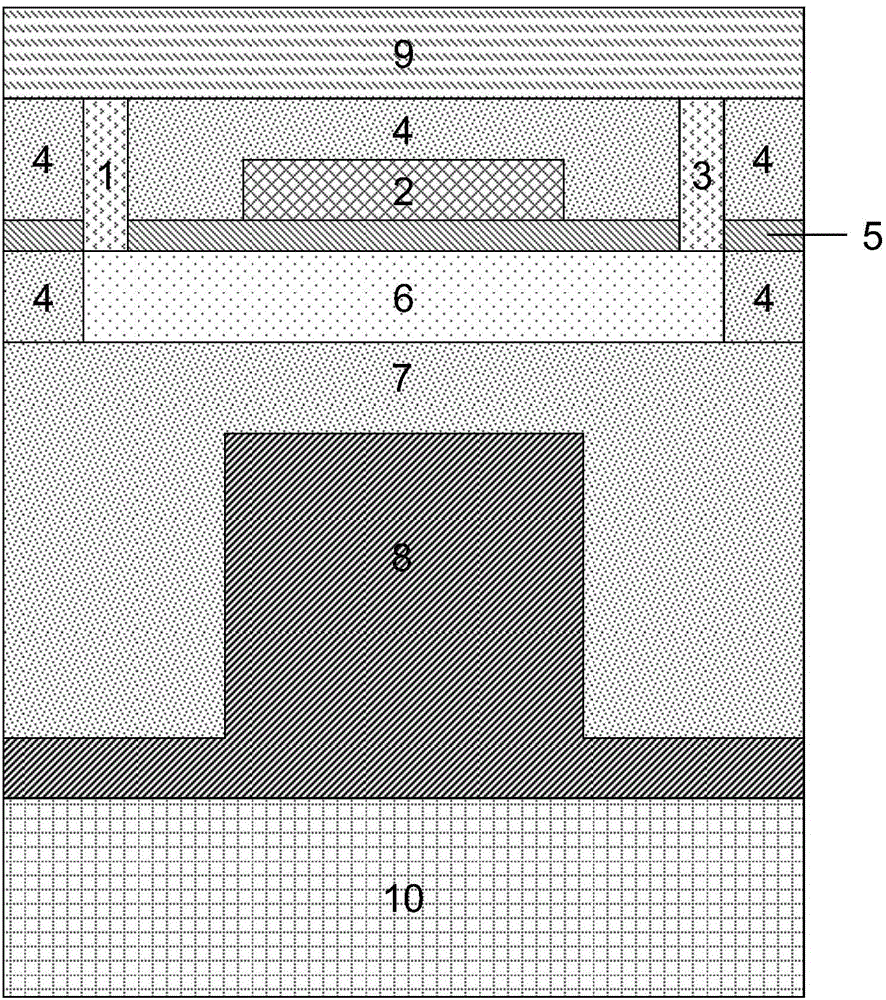

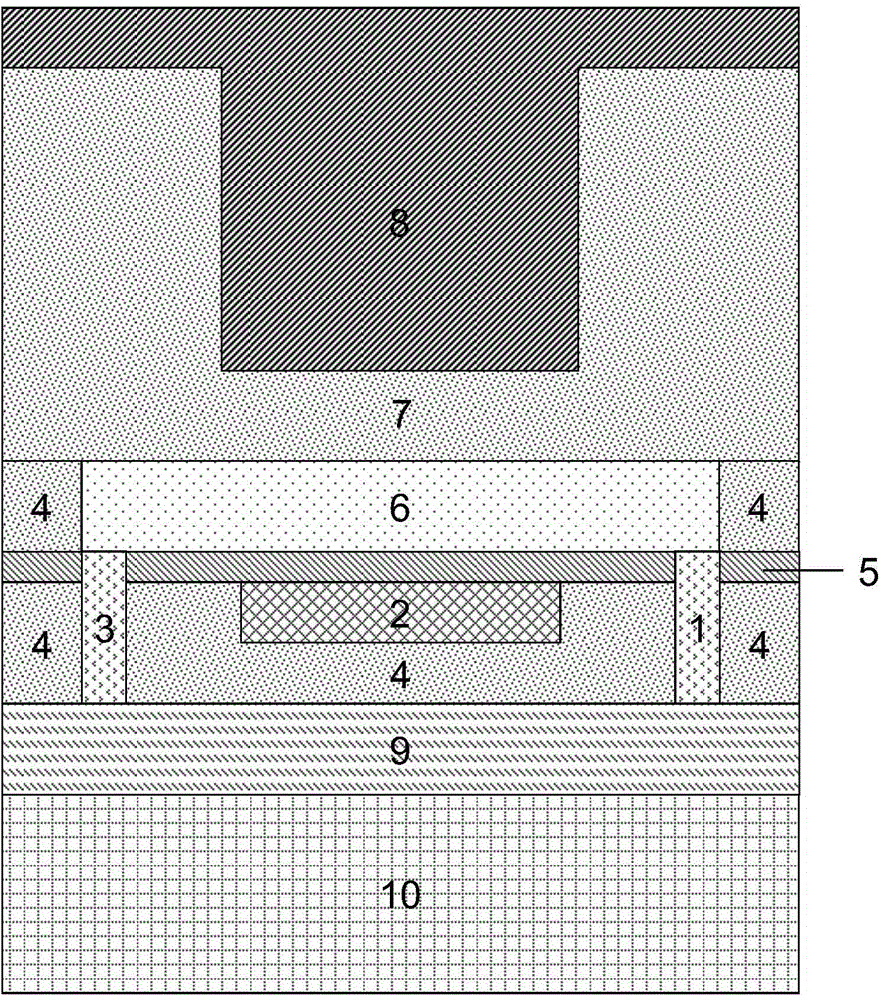

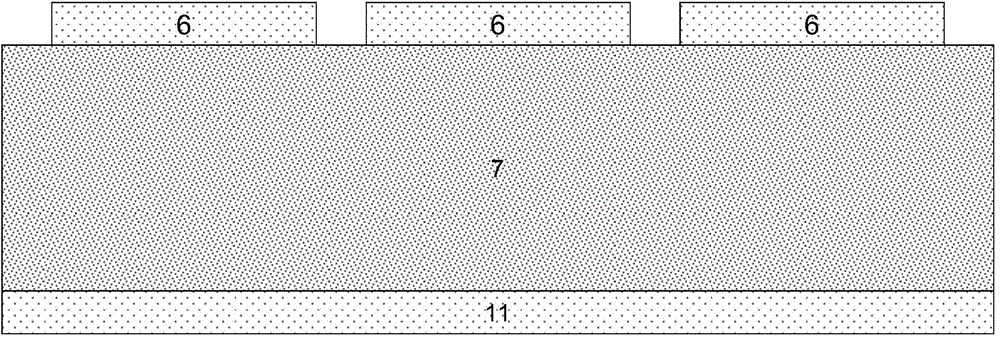

[0043] The present invention provides a high-performance SOI junction-free transistor with a non-single substrate insulating layer thickness. By applying an appropriate voltage bias to the voltage-adjustable substrate electrode 8, it can be equivalent to a double-gate or surrounding-gate structure, and the auxiliary gate electrode 2. Adjusting the distribution of carriers in the single crystal silicon thin film 6. Since the thickness of the insulating layer 7 of the SOI wafer is not a single value within a unit length of the device, the voltage bias on the voltage-adjustable substrate electrode 8 has different effects on the electric field distribution at different positions of the device, that is, in the SOI wafer The influence of the device part corresponding to the thinner part of the round insulating layer 7 is greater than the influence of the device part corresponding to the thicker part. When the device is turned off, the voltage bias on the voltage-adjustable substrate...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More