Patents

Literature

8460results about "Coils manufacture" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

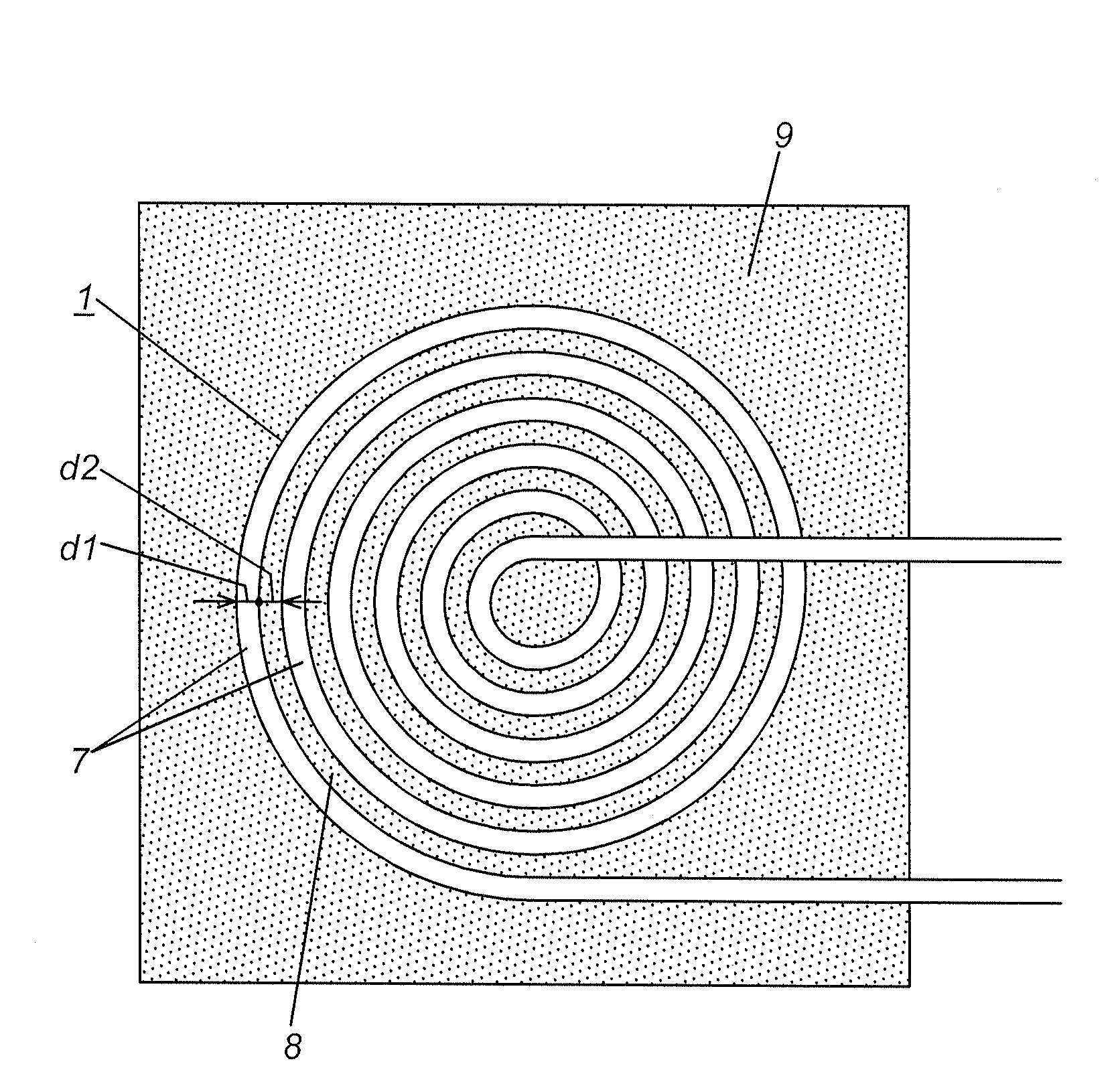

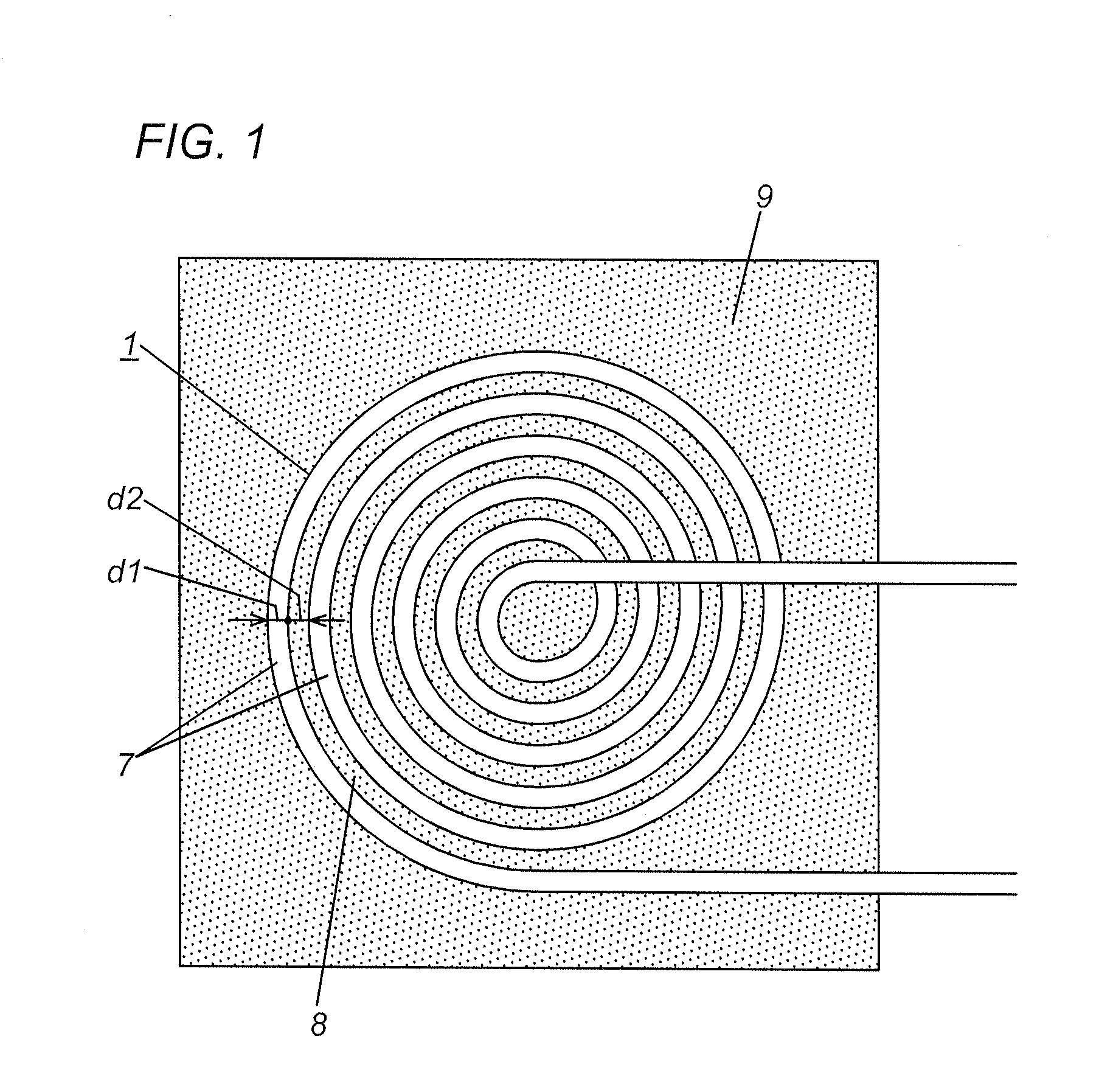

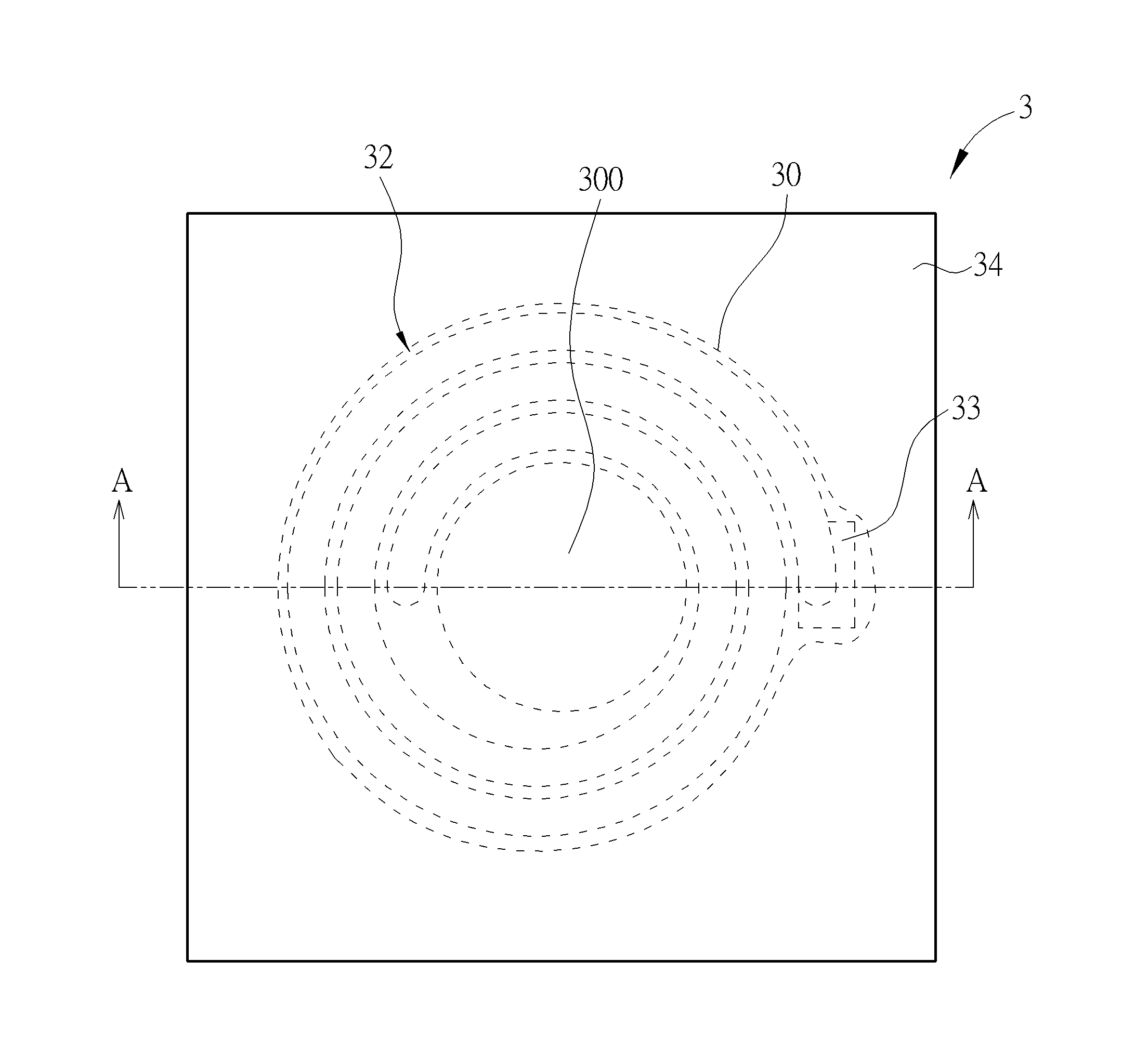

Planar coil and contactless electric power transmission device using the same

InactiveUS20100277004A1Avoid it happening againImprove productivityBatteries circuit arrangementsElectromagnetic wave systemElectric power transmissionEddy current

This invention has an object to a planar coil, a contactless electric power transmission device using the same. This planar coil is configured to suppress an eddy current developed between adjacent turns of wire for minimizing adverse effects on ambient electrical appliances resulting from heat generation. The planar coil 1 in the present invention is formed of spiral shaped wire 7 coated with thinned insulative film, in which adjacent turns of the wire 7 are spaced in radial direction at such a predetermined interval to suppress an eddy current. This planar coil 1 is preferably employed as a power transmission coil or power receiving coil.

Owner:PANASONIC CORP

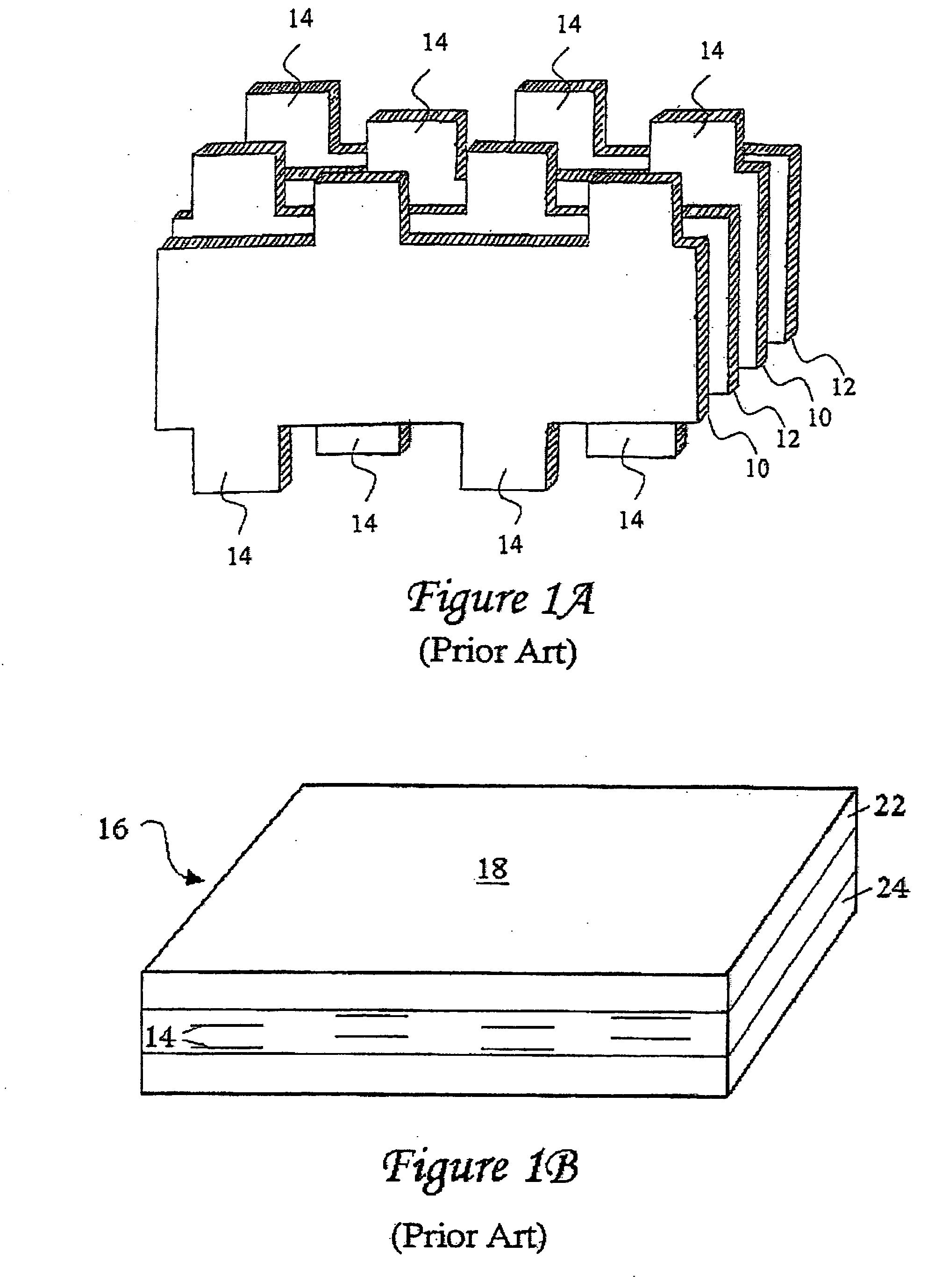

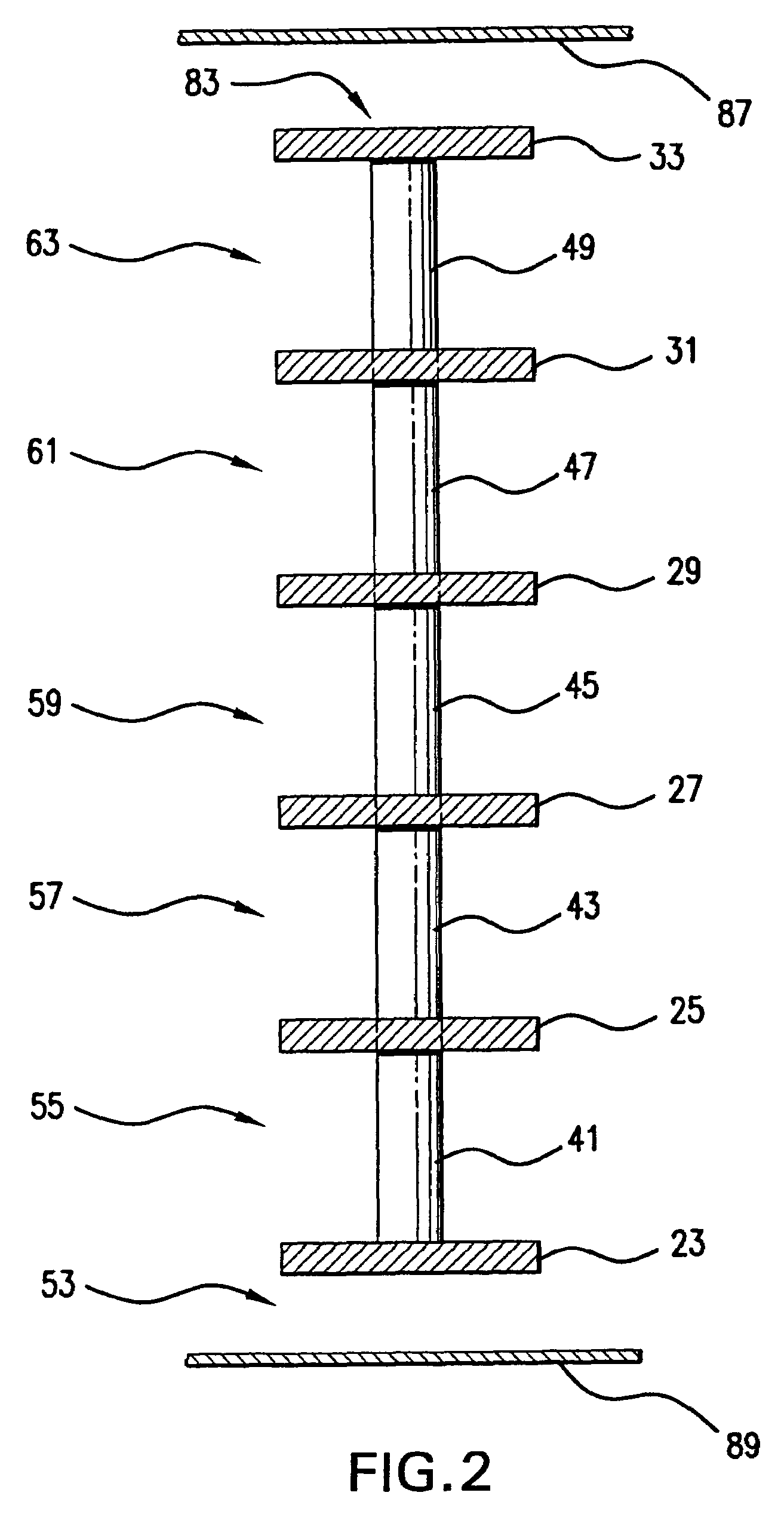

Method for forming plated terminations

InactiveUS7152291B2Improved termination featureEliminate or greatly simplify thick-film stripesElectrolytic capacitorsSemiconductor/solid-state device detailsTermination problemEngineering

Improved method steps for terminating multilayer electronic components are disclosed. Monolithic components are formed with plated terminations whereby the need for typical thick-film termination stripes is eliminated or greatly simplified. Such termination technology eliminates many typical termination problems and enables a higher number of terminations with finer pitch, which may be especially beneficial on smaller electronic components. Electrode and dielectric layers are provided in an interleaved arrangement and selected portions of the electrode layers are exposed. Electrically isolated anchor tabs may optionally be provided and exposed in some embodiments. Termination material is then plated to the exposed portions of the electrode layers until exposed portions of selected such portions thereof are connected. A variety of different plating techniques and termination materials may be employed in the formation of the subject self-determining plated terminations.

Owner:KYOCERA AVX COMPONENTS CORP

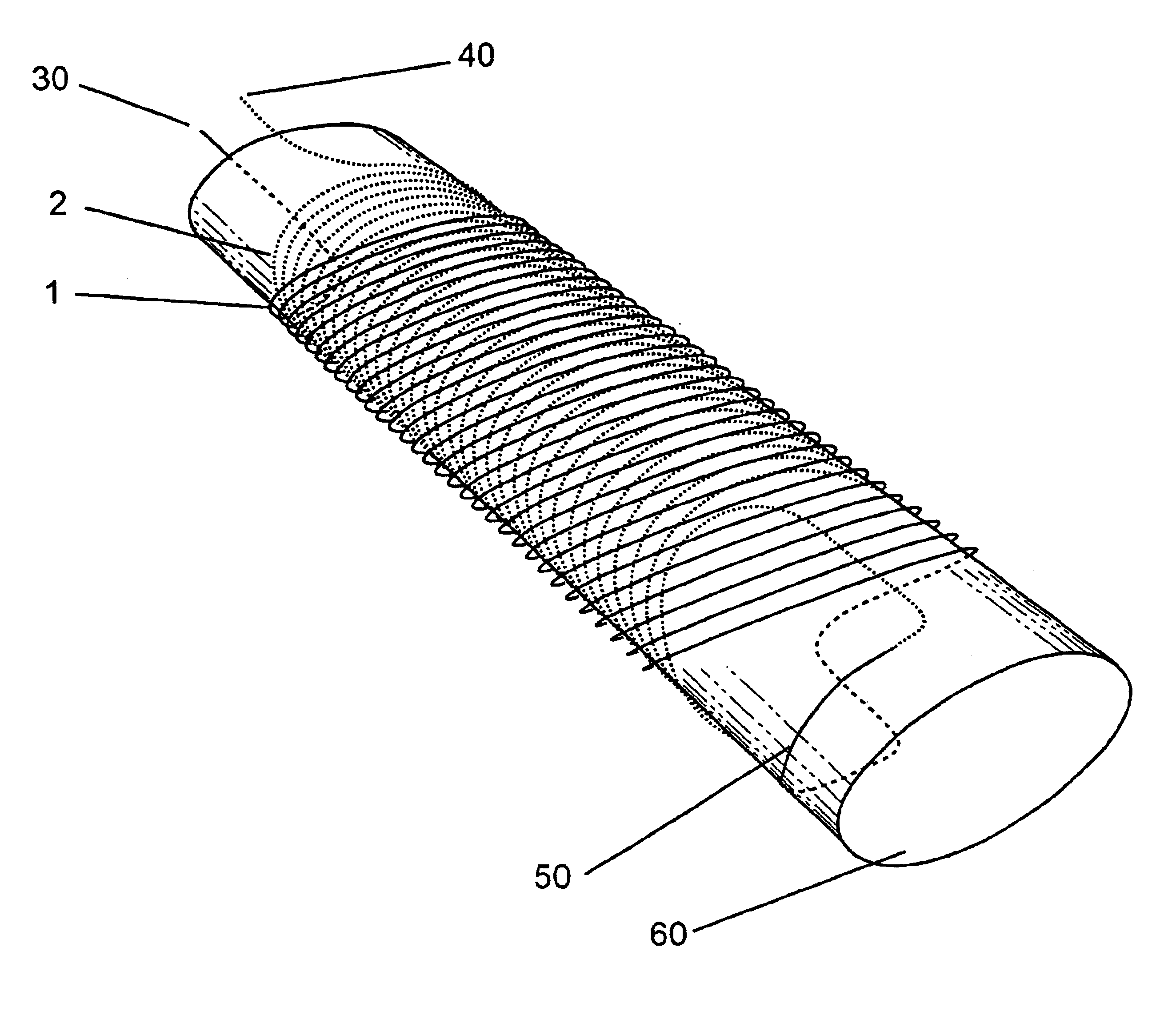

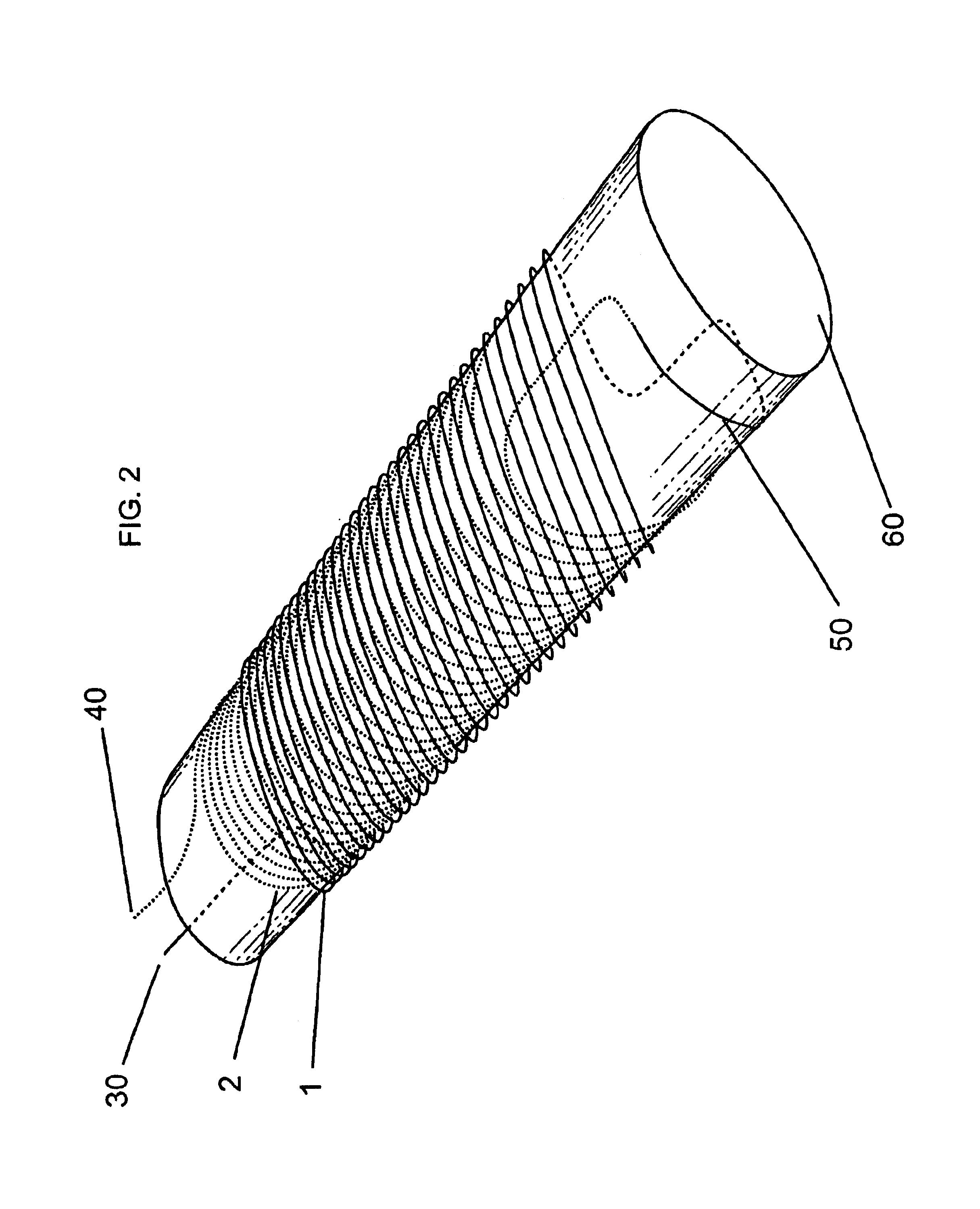

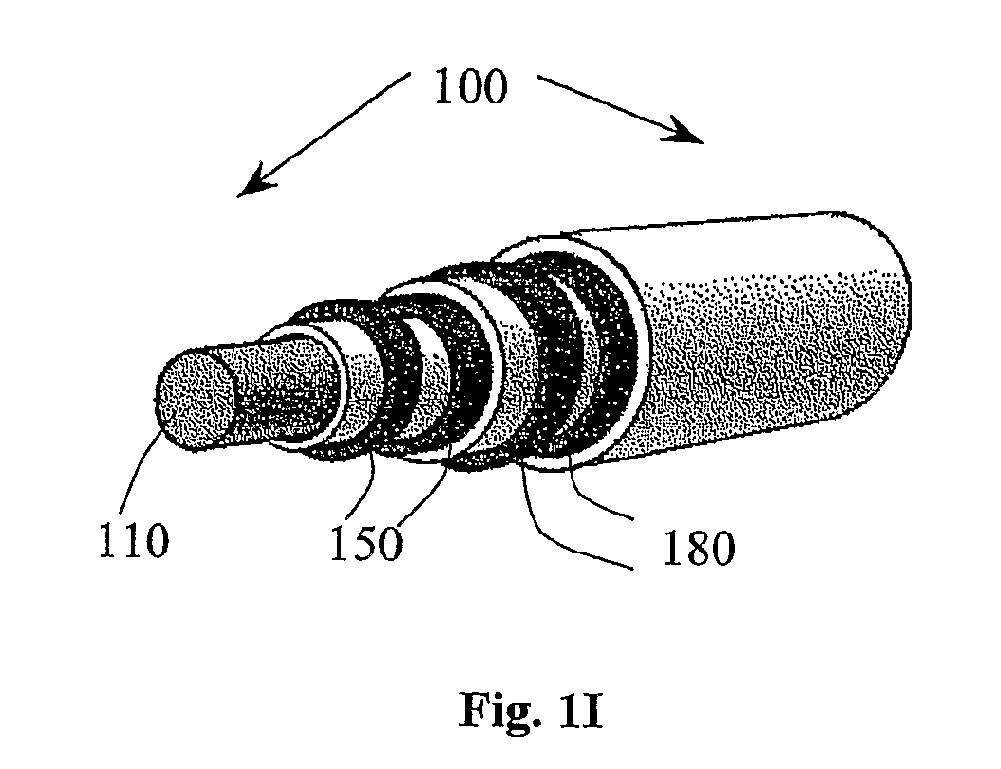

Concentric tilted double-helix dipoles and higher-order multipole magnets

InactiveUS6921042B1Simple processLess costlyElectromagnets without armaturesFilament handlingElectric machineryMagneto hydrodynamic

Concentric tilted double-helix magnets, which embody a simplified design and construction method for production of magnets with very pure field content, are disclosed. The disclosed embodiment of the concentric tilted double-helix dipole magnet has the field quality required for use in accelerator beam steering applications, i.e., higher-order multipoles are reduced to a negligibly small level. Magnets with higher multipole fields can be obtained by using a simple modification of the coil winding procedure. The double-helix coil design is well-suited for winding with superconducting cable or cable-in-conduit conductors and thus is useful for applications that require fields in excess of 2 T. The coil configuration has significant advantages over conventional racetrack coils for accelerators, electrical machinery, and magneto-hydrodynamic thrusting devices.

Owner:GOODZEIT CARL L +2

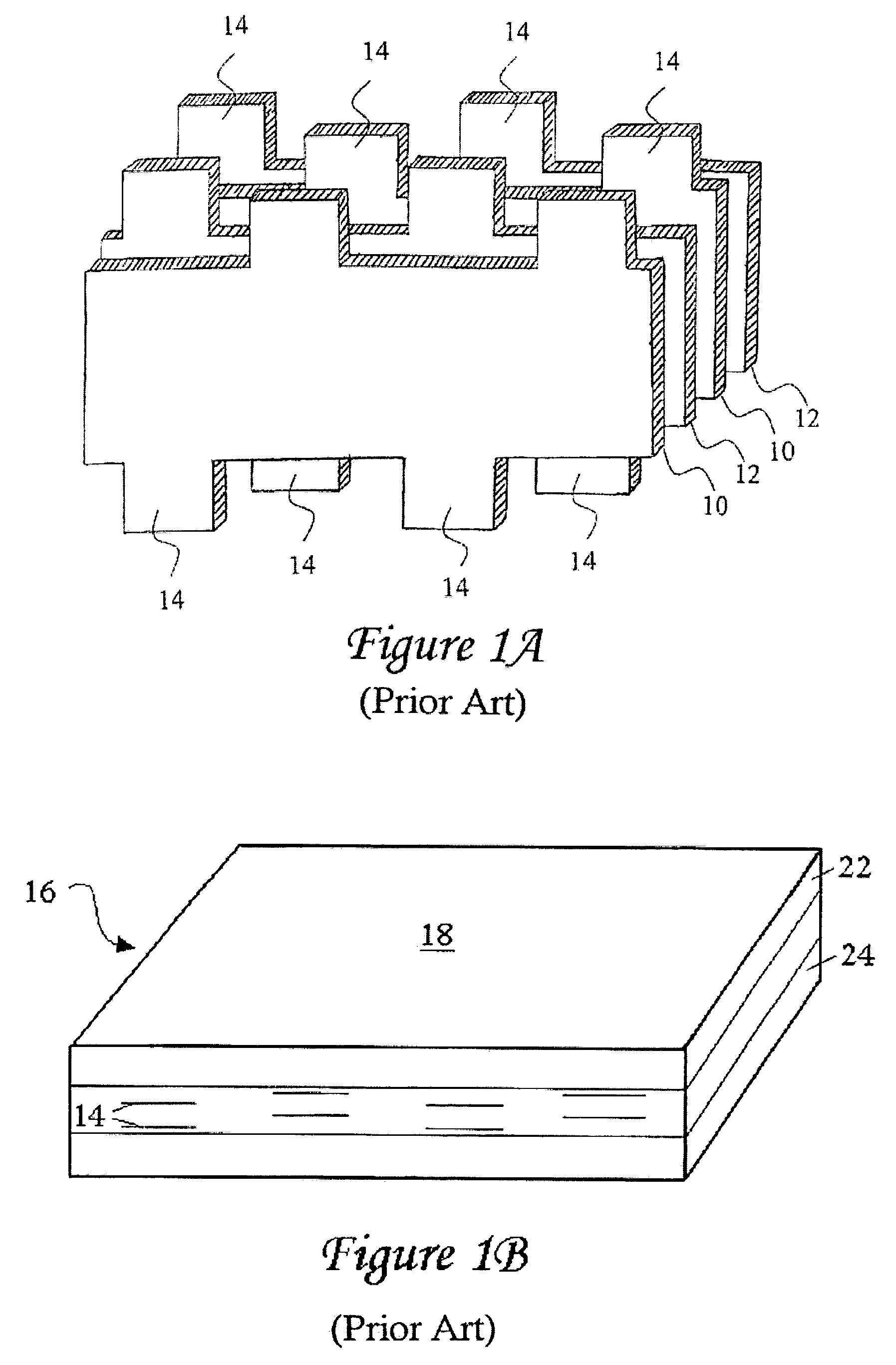

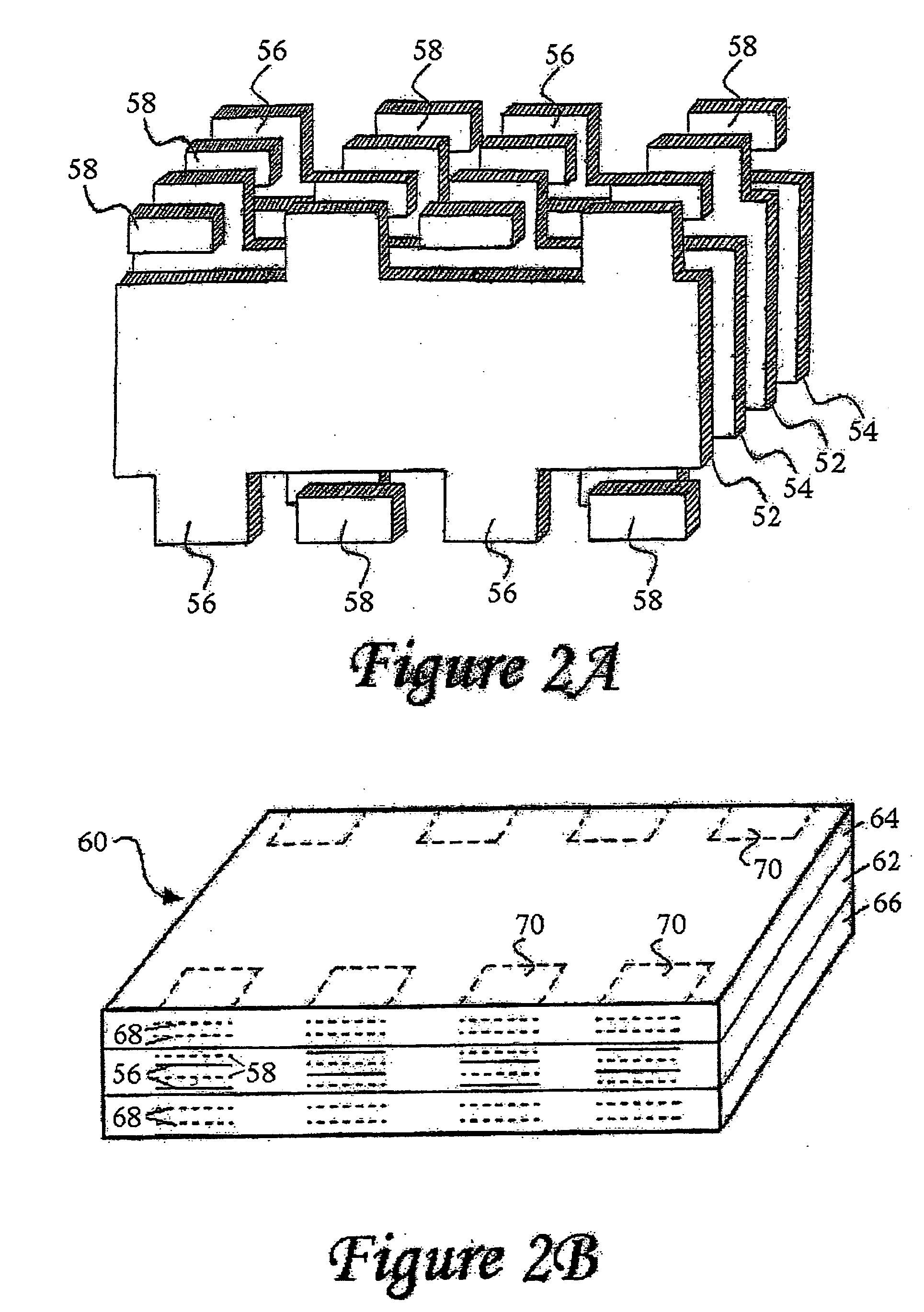

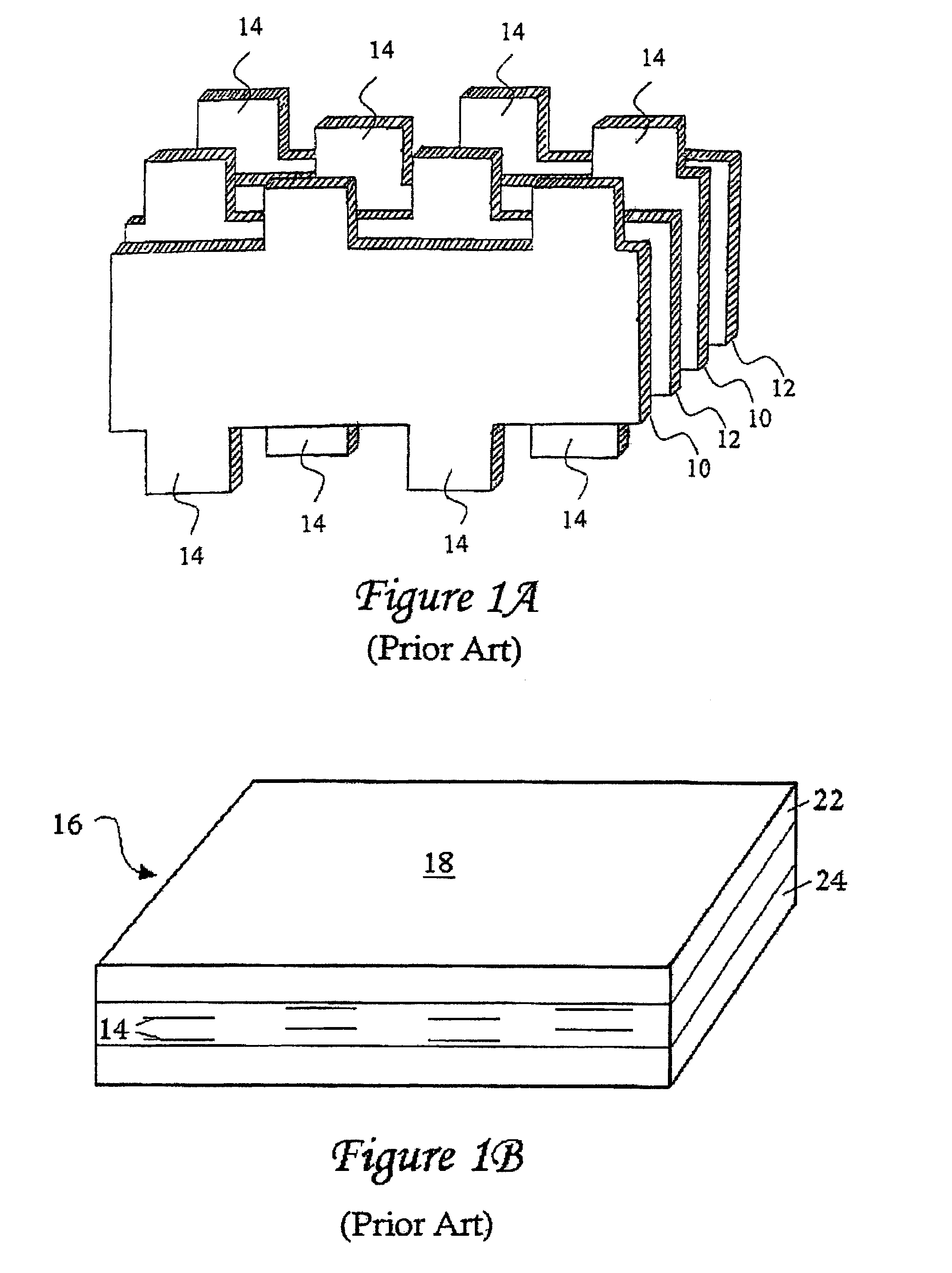

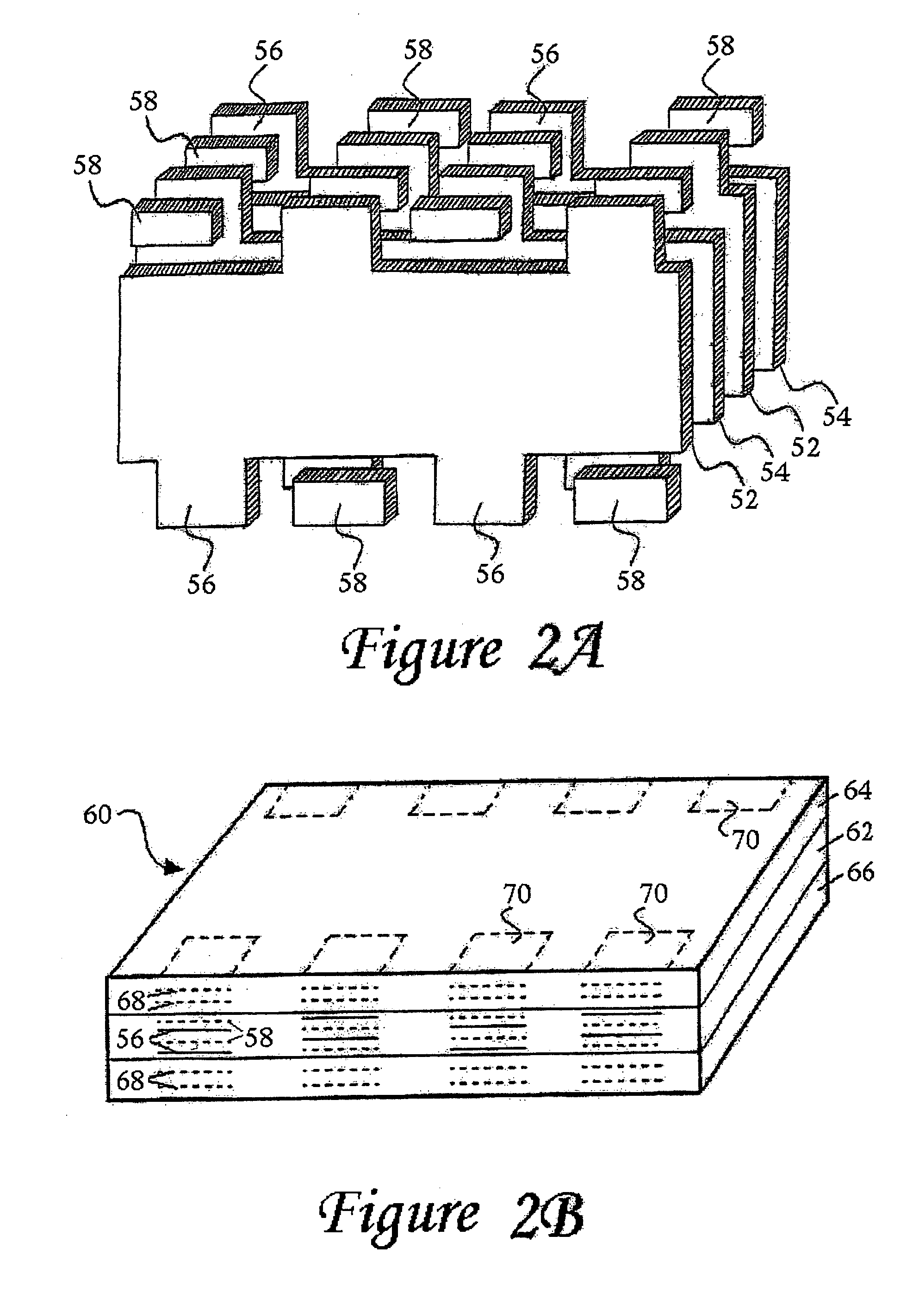

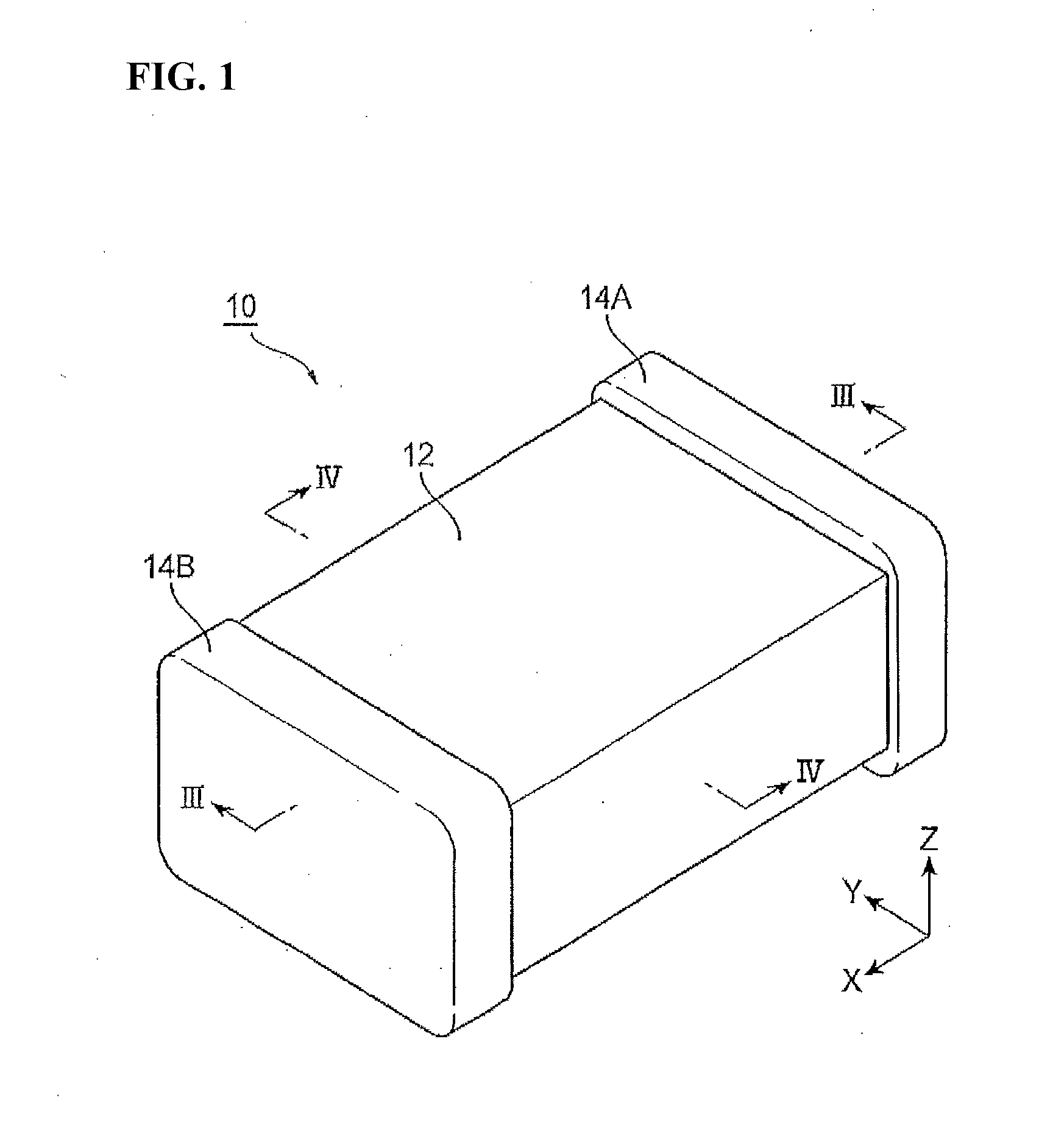

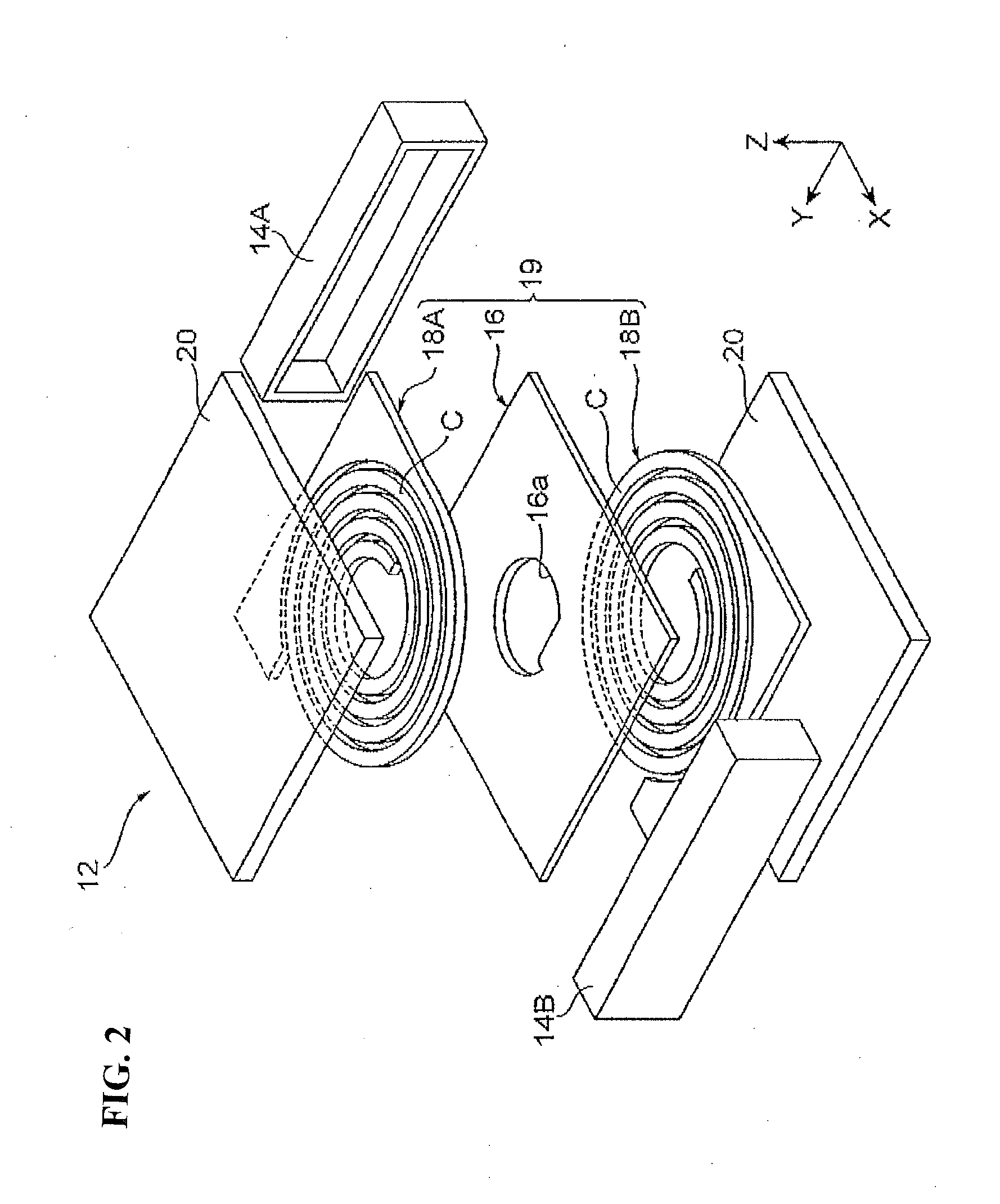

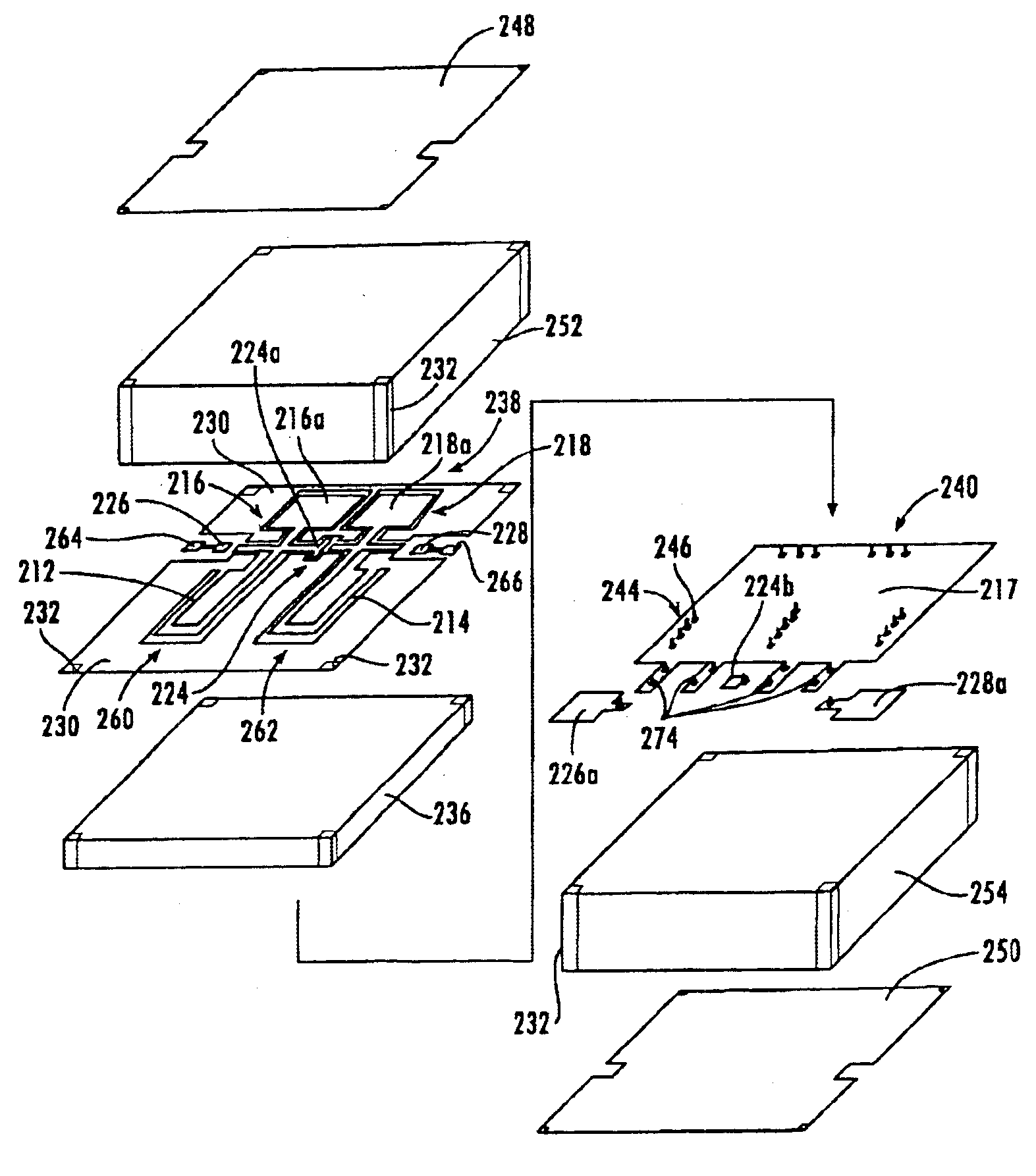

Plated terminations

InactiveUS20050046536A1Improved termination featureEliminate and greatly simplifyWave amplification devicesResistor terminals/electrodesTermination problemEngineering

Improved termination features for multilayer electronic components are disclosed. Monolithic components are provided with plated terminations whereby the need for typical thick-film termination stripes is eliminated or greatly simplified. Such termination technology eliminates many typical termination problems and enables a higher number of terminations with finer pitch, which may be especially beneficial on smaller electronic components. The subject plated terminations are guided and anchored by exposed internal electrode tabs and additional anchor tab portions which may optionally extend to the cover layers of a multilayer component. Such anchor tabs may be positioned internally or externally relative to a chip structure to nucleate additional metallized plating material. External anchor tabs positioned on top and bottom sides of a monolithic structure can facilitate the formation of wrap-around plated terminations. The disclosed technology may be utilized with a plurality of monolithic multilayer components, including interdigitated capacitors, multilayer capacitor arrays, and integrated passive components. A variety of different plating techniques and termination materials may be employed in the formation of the subject self-determining plated terminations.

Owner:KYOCERA AVX COMPONENTS CORP

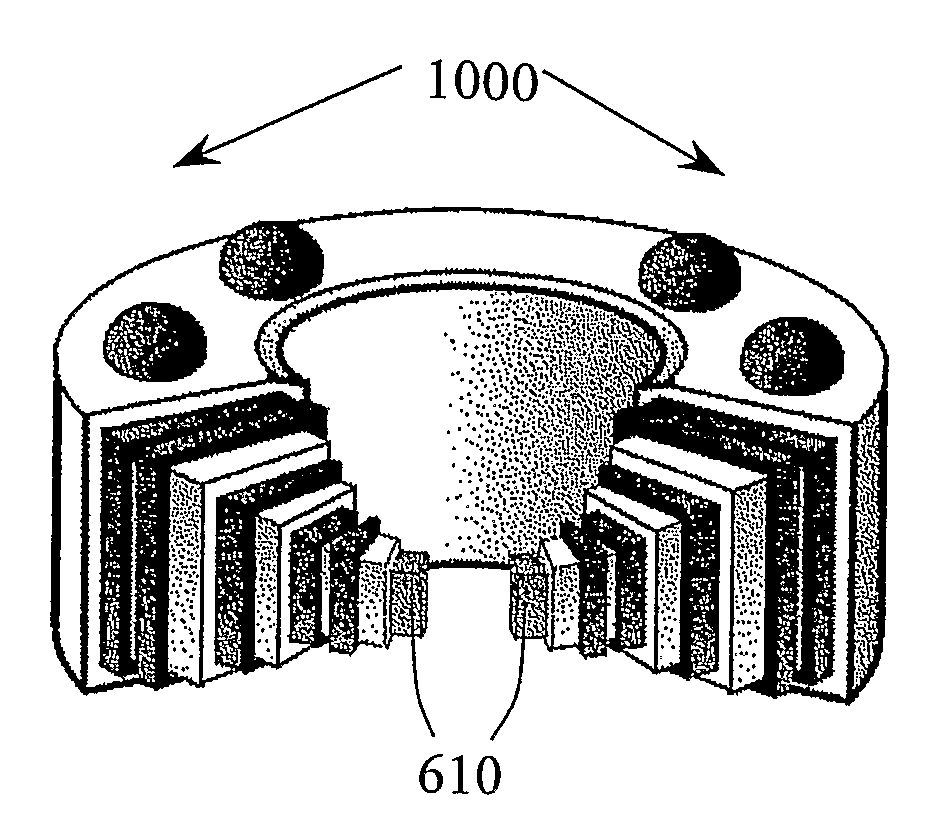

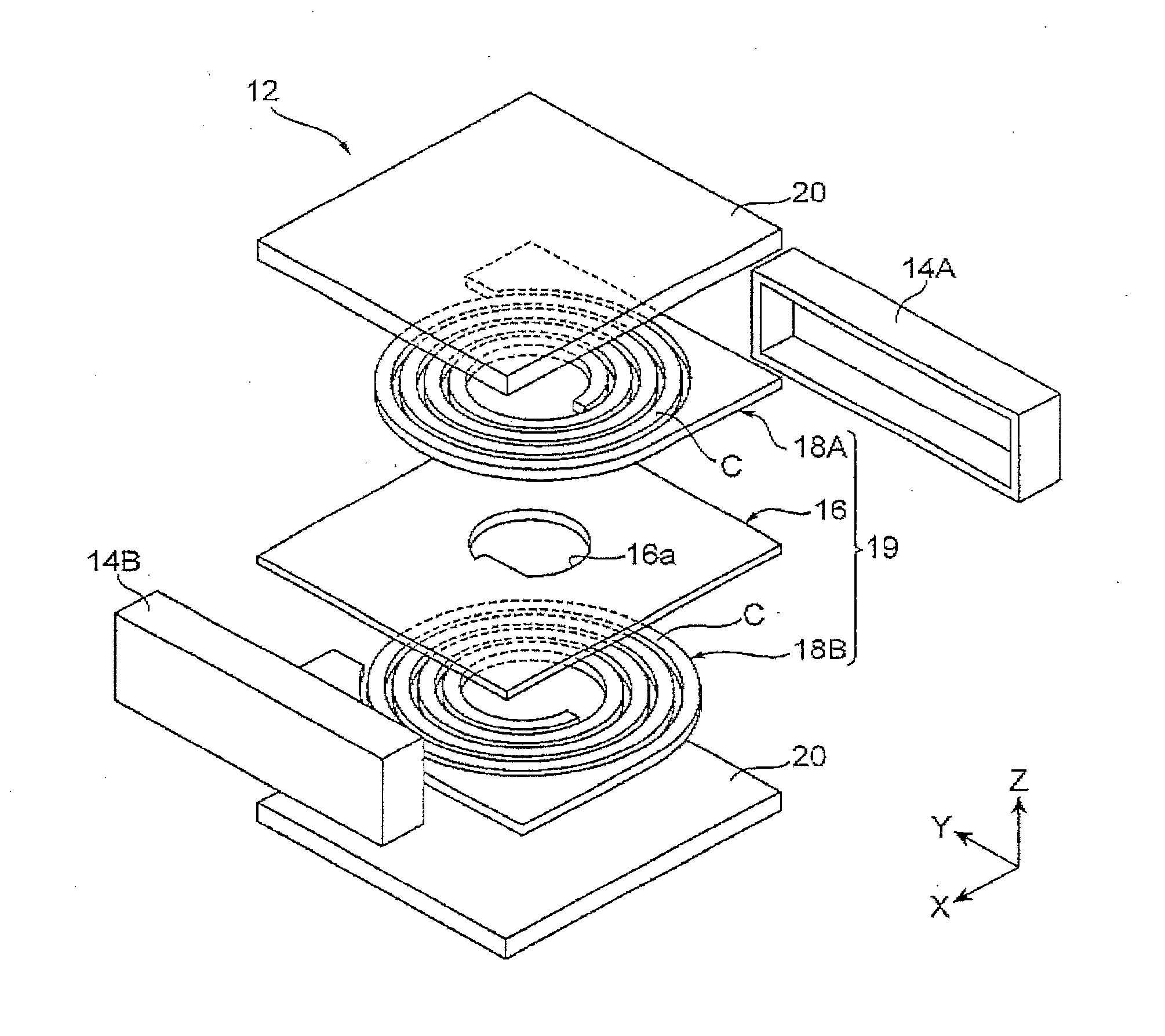

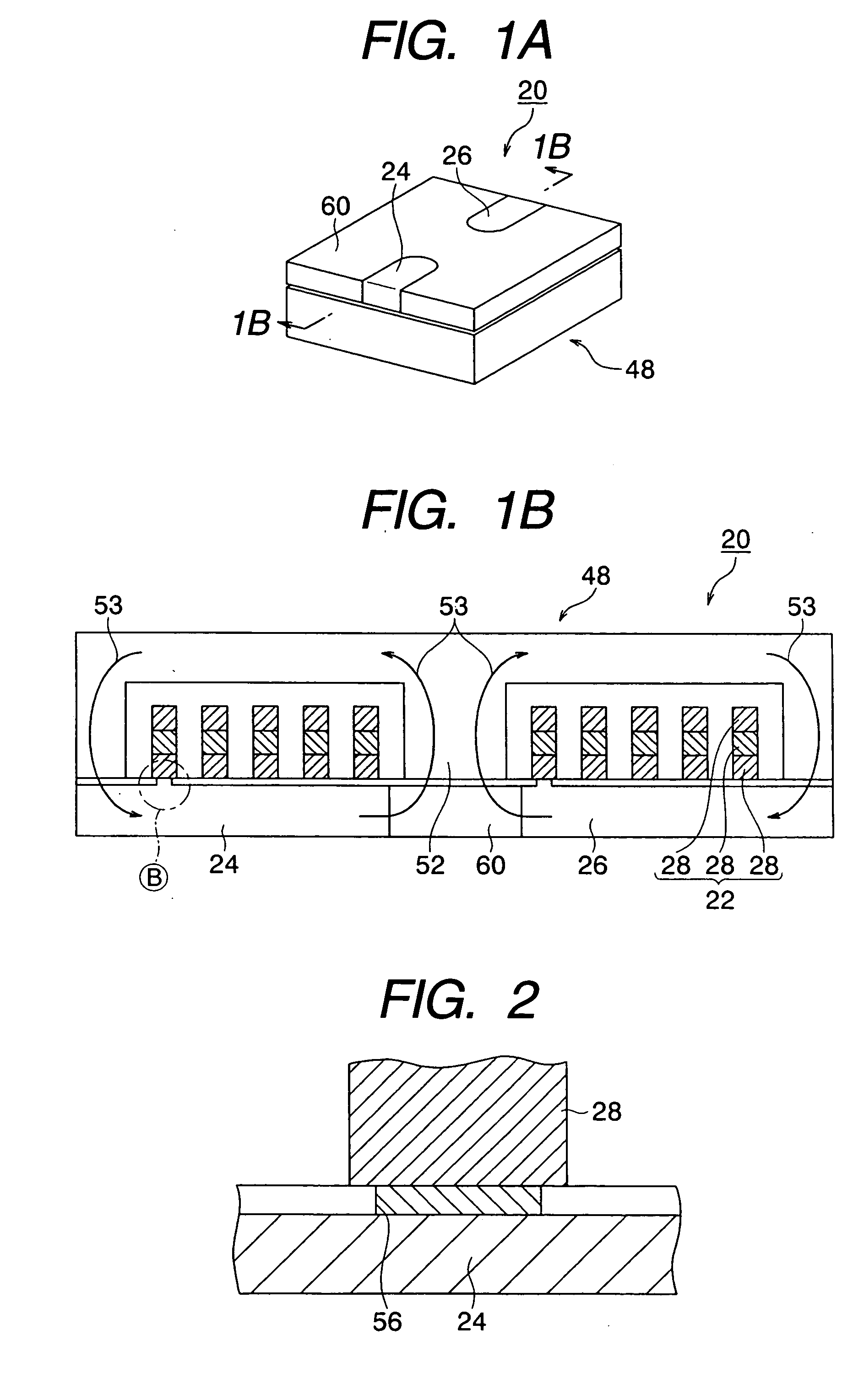

Microfabricated system for magnetic field generation and focusing

InactiveUS20050275497A1Easily of circuitryWell formedTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesDielectricMicro coil

A method of forming, in or on a Si substrate, planar micro-coils with coil windings of high aspect ratio (>3) and a wide variety of geometric shapes. The micro-coils may be formed on a Si substrate and be embedded in a dielectric, or they may be formed in trenches within a Si substrate. The micro-coils may have field enhancing ferromagnetic pillars rising above the micro-coil plane, formed at positions of maximum magnetic field strength and the micro-coils may also include magnetic layers formed beneath the substrate and contacting the pillars to form a substantially closed pathway for the magnetic flux. The substrate may be thinned to membrane proportions. These micro-coils produce strong magnetic fields with strong field gradients and can be used in a wide variety of processes that involve the exertion of strong magnetic forces at small distances or the creation of magnetic wells for trapping and manipulating small particles.

Owner:AGENCY FOR SCI TECH & RES +1

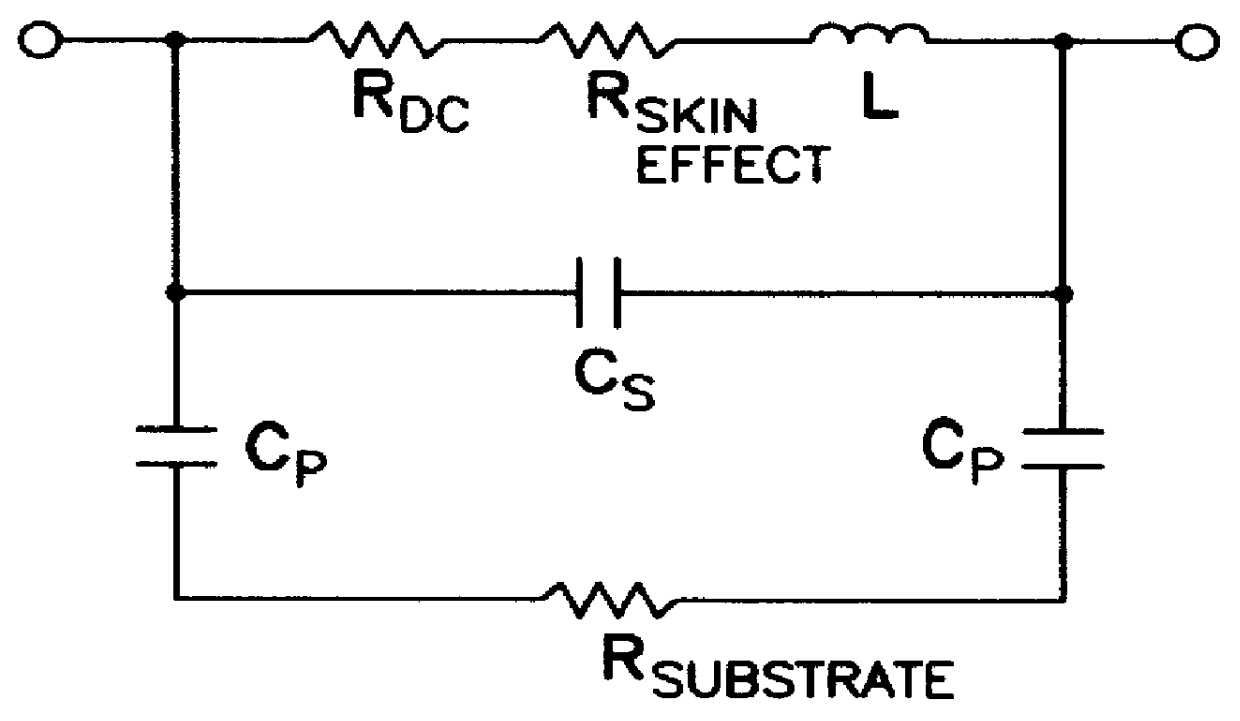

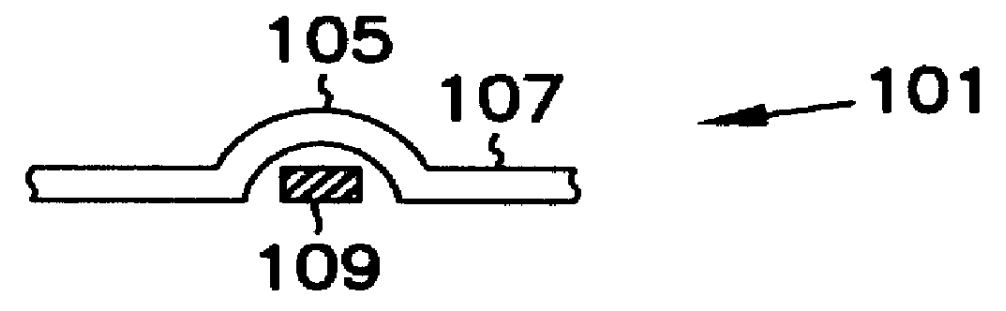

Method for making high-Q inductive elements

InactiveUS6025261ARaise the self-resonant frequencyHigh selectivitySemiconductor/solid-state device detailsSolid-state devicesElectrical conductorInductance

Owner:MICRON TECH INC

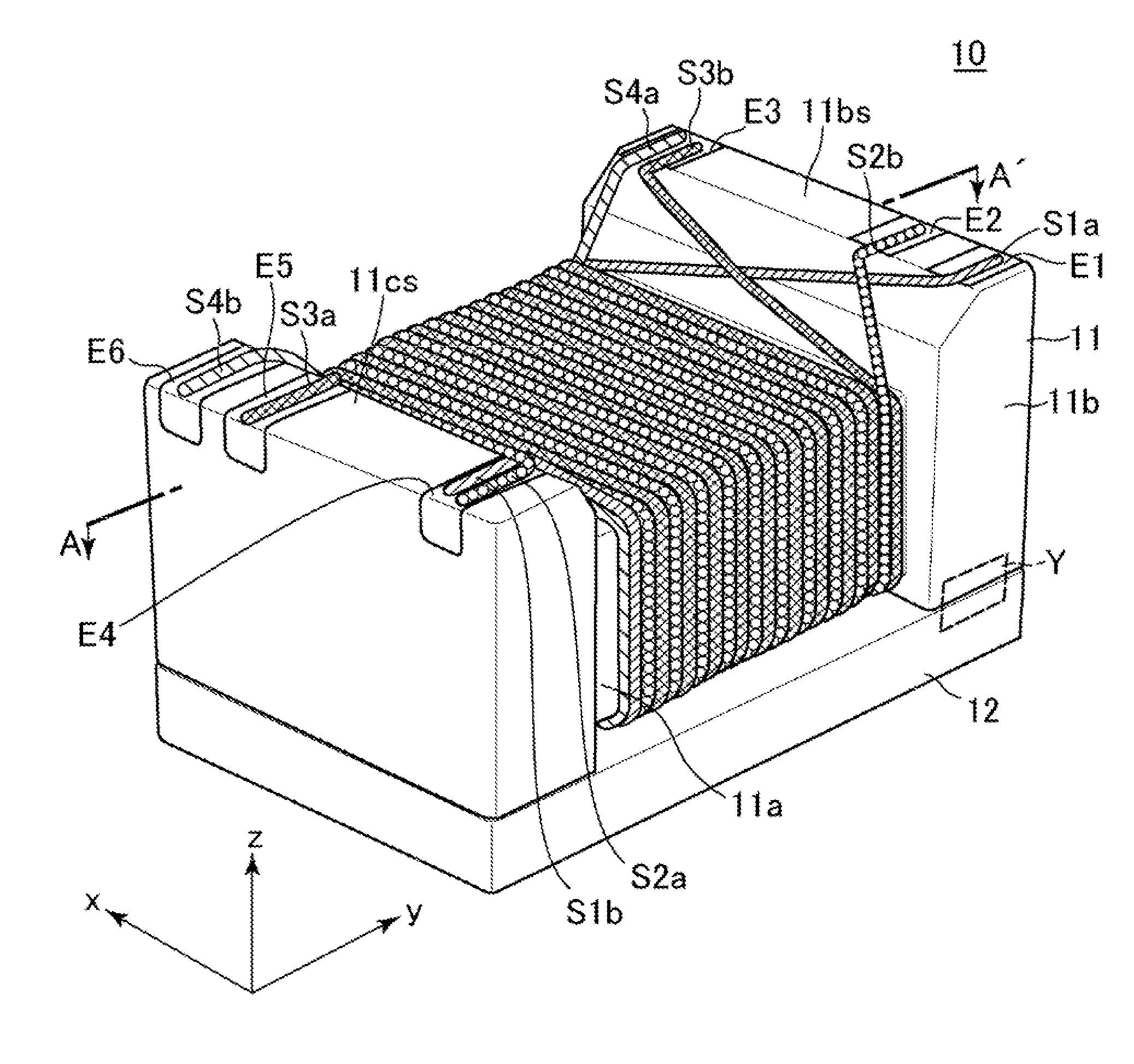

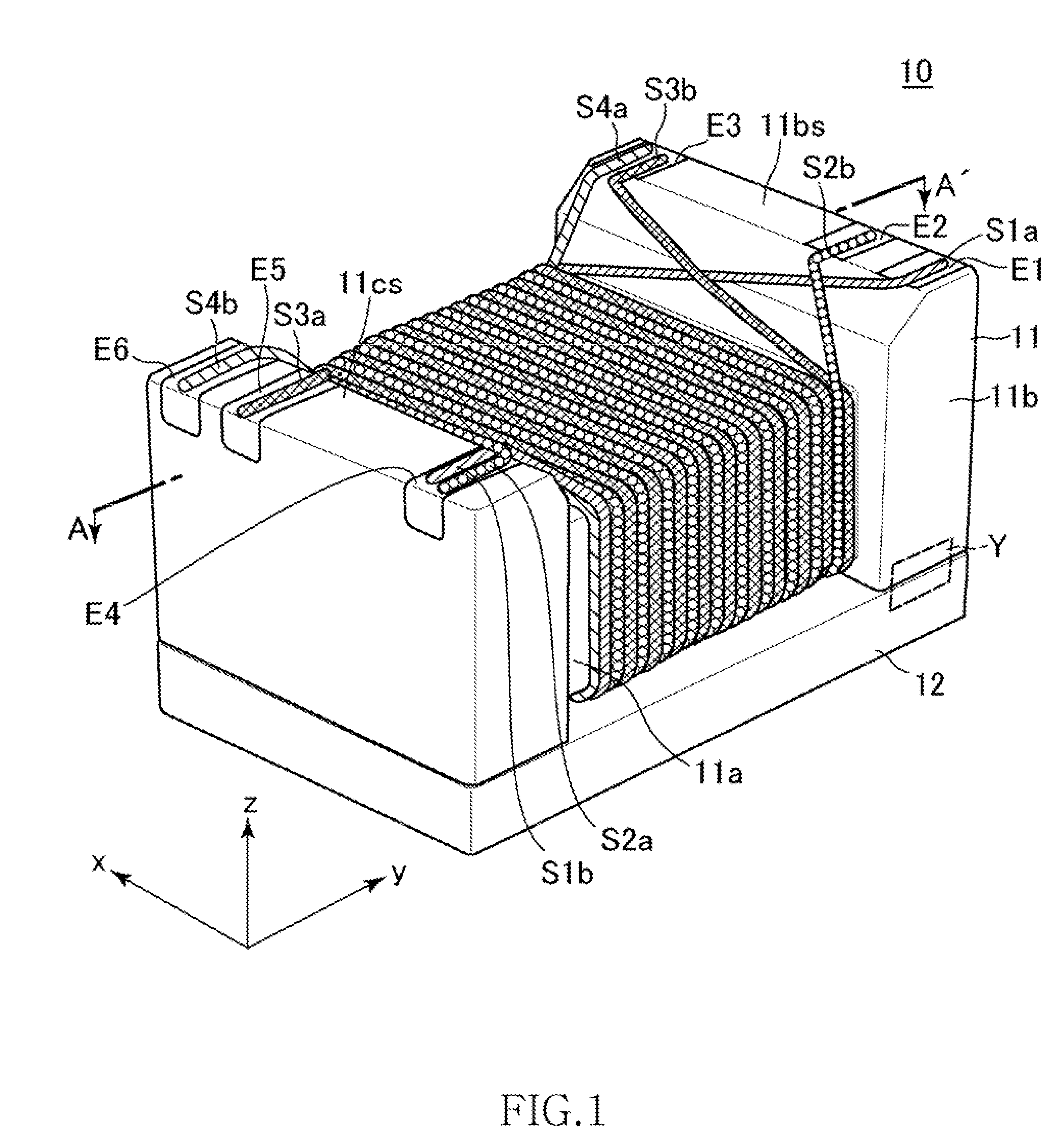

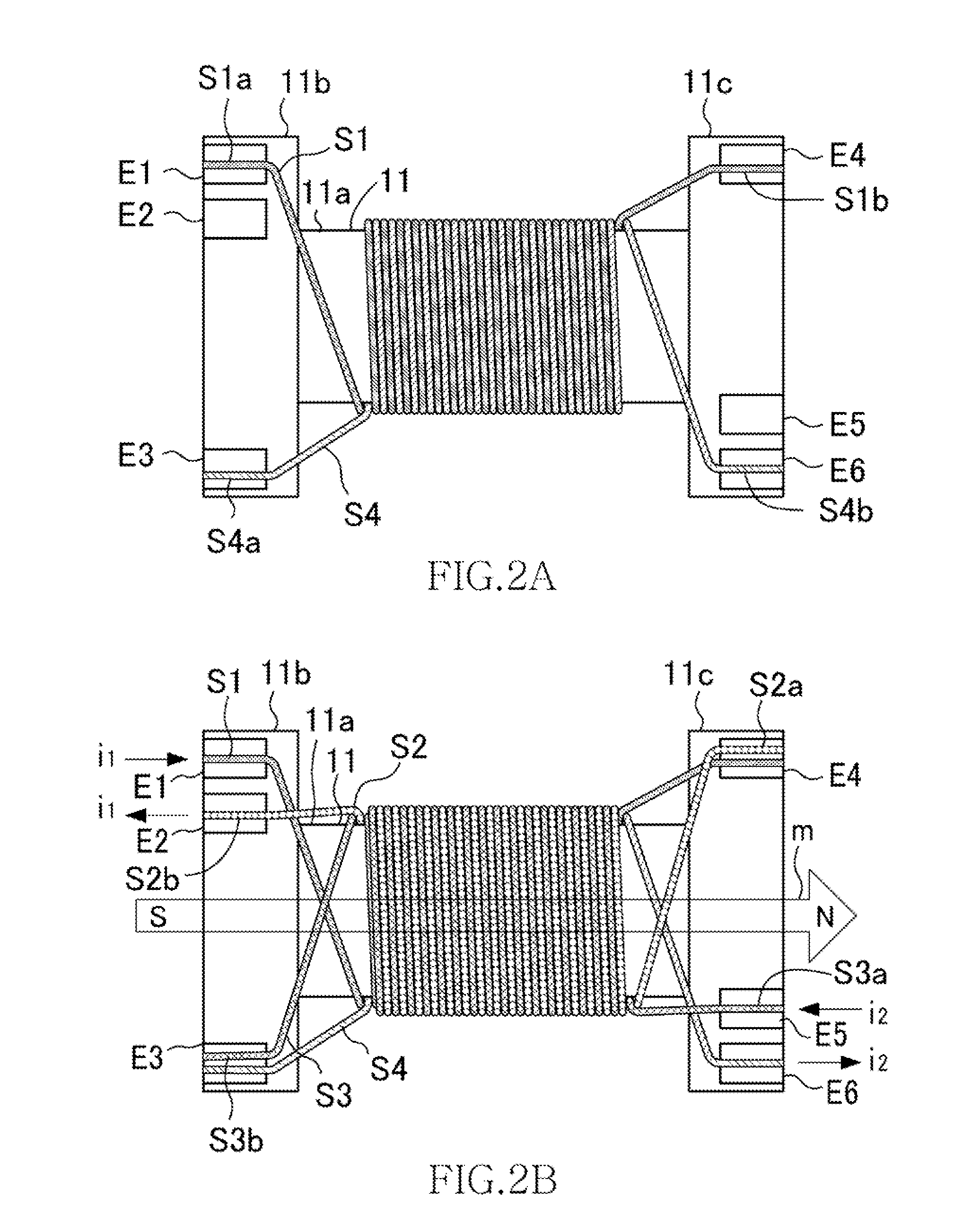

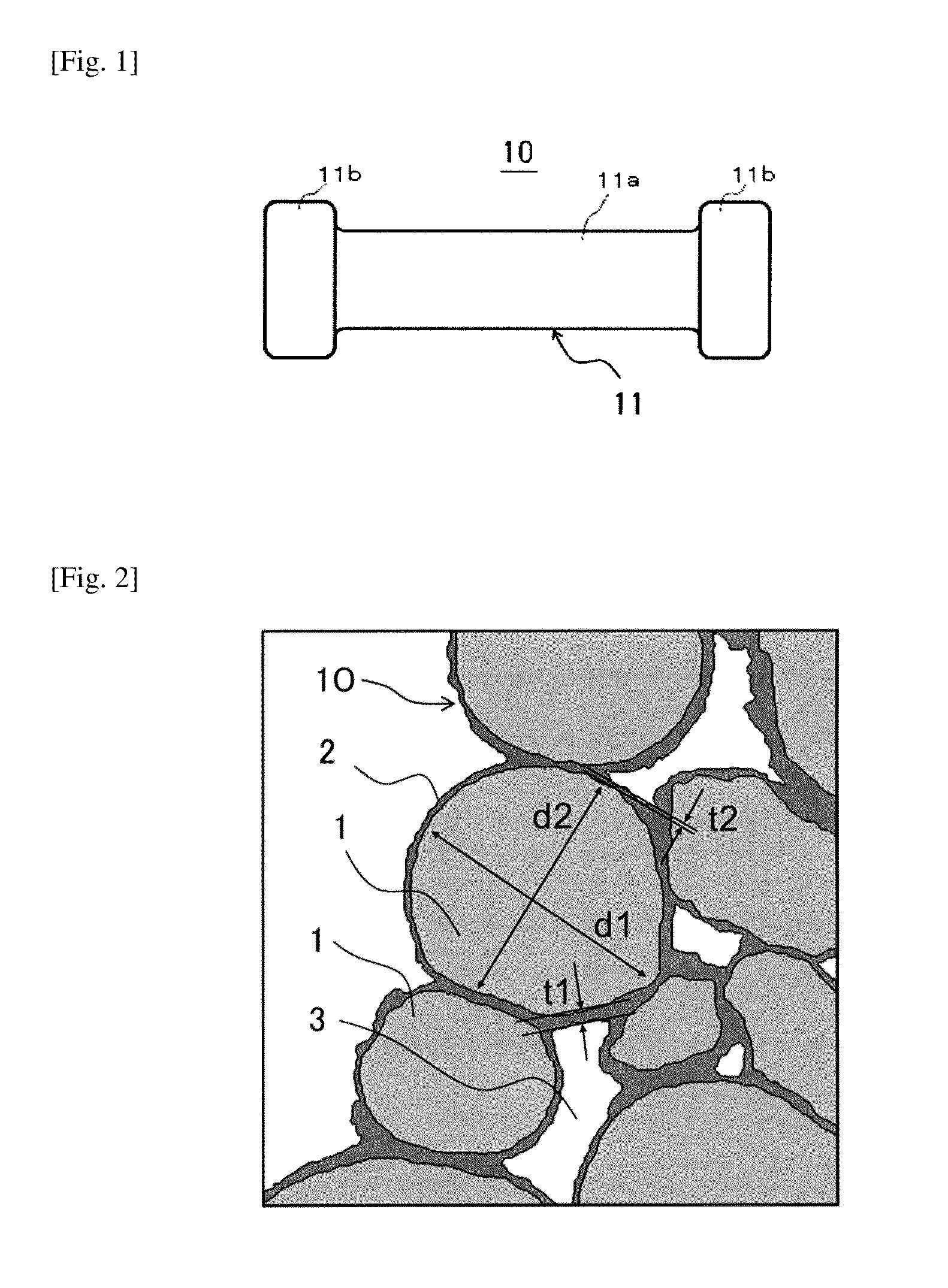

Surface mount pulse transformer and method and apparatus for manufacturing the same

ActiveUS20100109827A1Short working hoursShorten the timeTransformers/inductances casingsTransformers/inductances coils/windings/connectionsSurface mountingEngineering

A surface mount pulse transformer has a drum type core including a core and first and second flanges disposed on both ends of the core and installed on a substrate and a primary winding wire and a secondary winding wire wound around the core and provided with an intermediate tap, respectively, wherein first and second terminal electrodes being connected to each of both ends of the primary winding wire and a third terminal electrode for connecting being connected to the intermediate tap of the secondary winding wire are disposed on the surface of the first flange and a fourth terminal electrode being connected to the intermediate tap of the primary winding wire and fifth and sixth terminal electrodes being connected to each of both ends of the secondary winding wire are disposed on the surface of the second flange.

Owner:TDK CORPARATION

Plated terminations

InactiveUS7154374B2Improved termination featureEliminate or greatly simplify thick-film stripesResistor terminals/electrodesSemiconductor/solid-state device detailsTermination problemEngineering

Improved termination features for multilayer electronic components are disclosed. Monolithic components are provided with plated terminations whereby the need for typical thick-film termination stripes is eliminated or greatly simplified. Such termination technology eliminates many typical termination problems and enables a higher number of terminations with finer pitch, which may be especially beneficial on smaller electronic components. The subject plated terminations are guided and anchored by exposed internal electrode tabs and additional anchor tab portions which may optionally extend to the cover layers of a multilayer component. Such anchor tabs may be positioned internally or externally relative to a chip structure to nucleate additional metallized plating material. External anchor tabs positioned on top and bottom sides of a monolithic structure can facilitate the formation of wrap-around plated terminations. The disclosed technology may be utilized with a plurality of monolithic multilayer components, including interdigitated capacitors, multilayer capacitor arrays, and integrated passive components. A variety of different plating techniques and termination materials may be employed in the formation of the subject self-determining plated terminations.

Owner:KYOCERA AVX COMPONENTS CORP

Magnetic Induction Devices And Methods For Producing Them

InactiveUS20100188183A1Simple methodTransformers/inductances coils/windings/connectionsSemiconductor/solid-state device manufacturingEngineeringConductor Coil

Owner:ADVANCED MAGNETIC SOLUTIONS

Inductive device including bond wires

ActiveUS6998952B2Transformers/reacts mounting/support/suspensionSemiconductor/solid-state device detailsEngineeringInductance

Owner:NXP USA INC

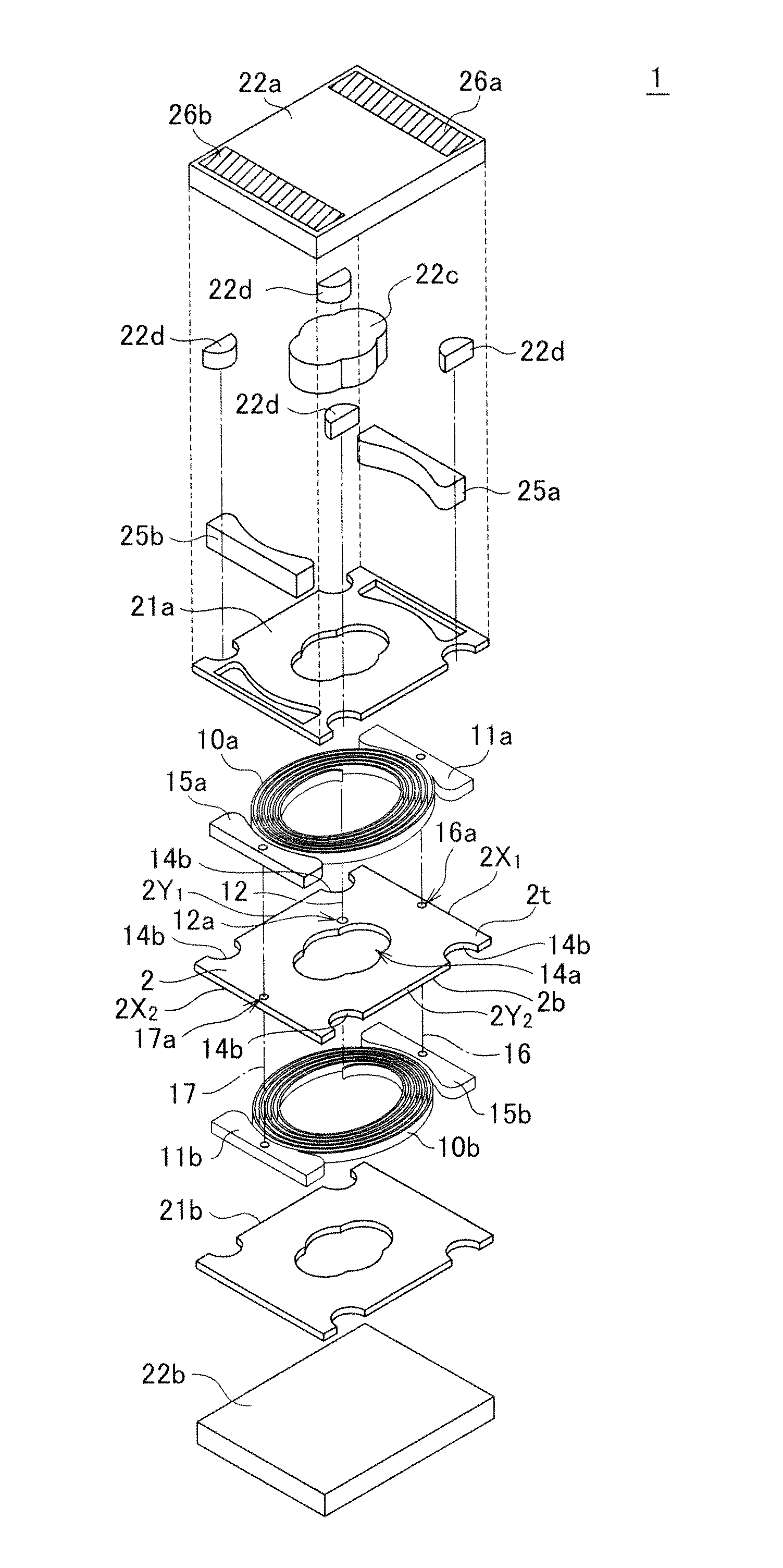

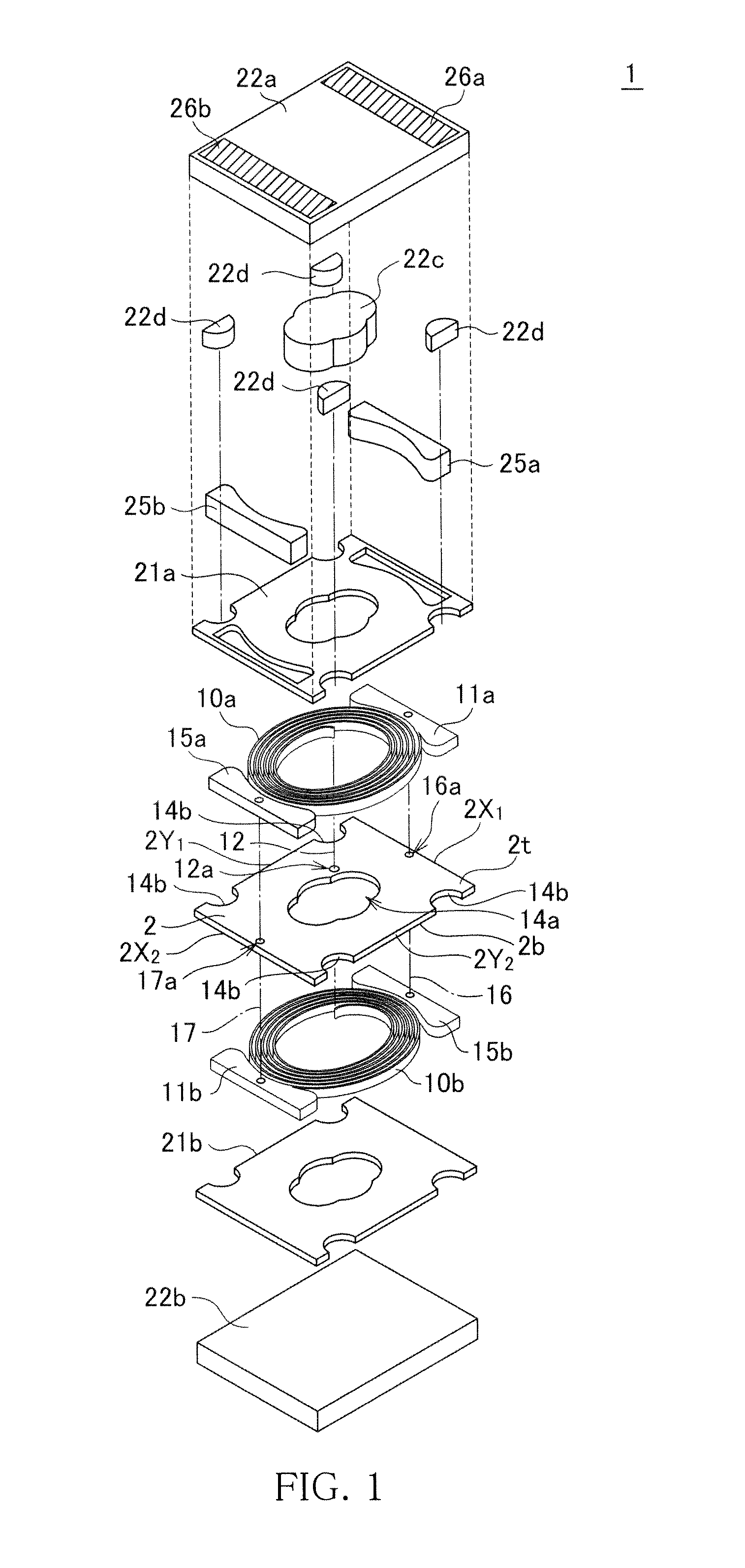

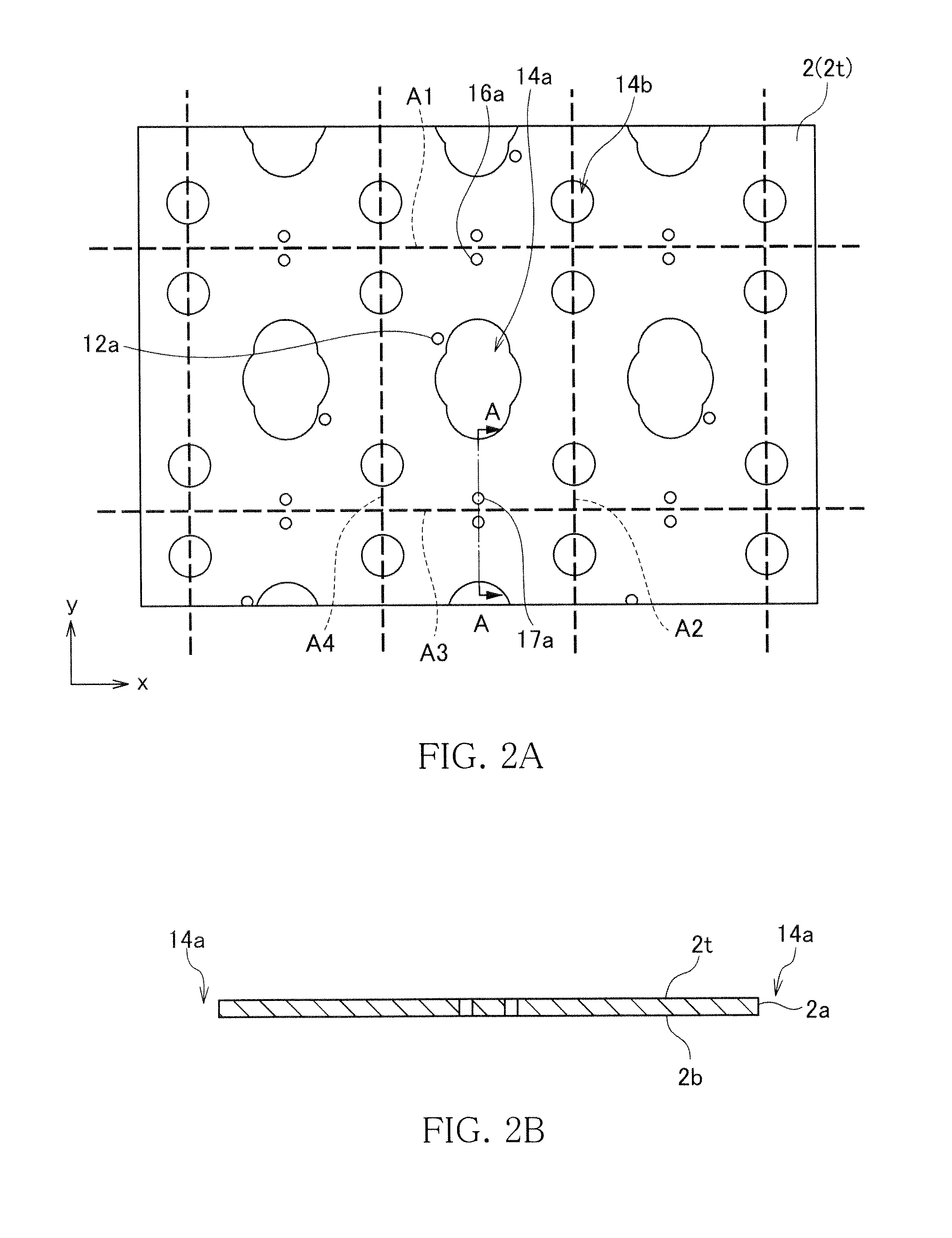

Coil component

ActiveUS20140009254A1Prevent thickening of outermost turnImprove installation strengthTransformers/inductances coils/windings/connectionsCoils manufactureElectrical connectionEngineering

A coil component 1 includes a substrate 2, a planar spiral conductor 10a formed on a top surface 2t of the substrate 2, a lead conductor 11a connected to an outer peripheral end of the planar spiral conductor 10a, a dummy lead conductor 15a formed on the top surface of the substrate 2 and between an outermost turn of the planar spiral conductor 10a and an end 2X2 of the substrate 2 and free from an electrical connection with another conductor within the same plane, external electrodes 26a and 26b arranged in parallel with the top surface of the substrate 2, and a bump electrode 25a formed on a surface of the lead conductor 11a and connects the lead conductor 11a with the external electrode 26a. The external terminals 26a and 26b have a larger area than the bump electrodes 15a and 15b for securing a bonding strength.

Owner:TDK CORPARATION

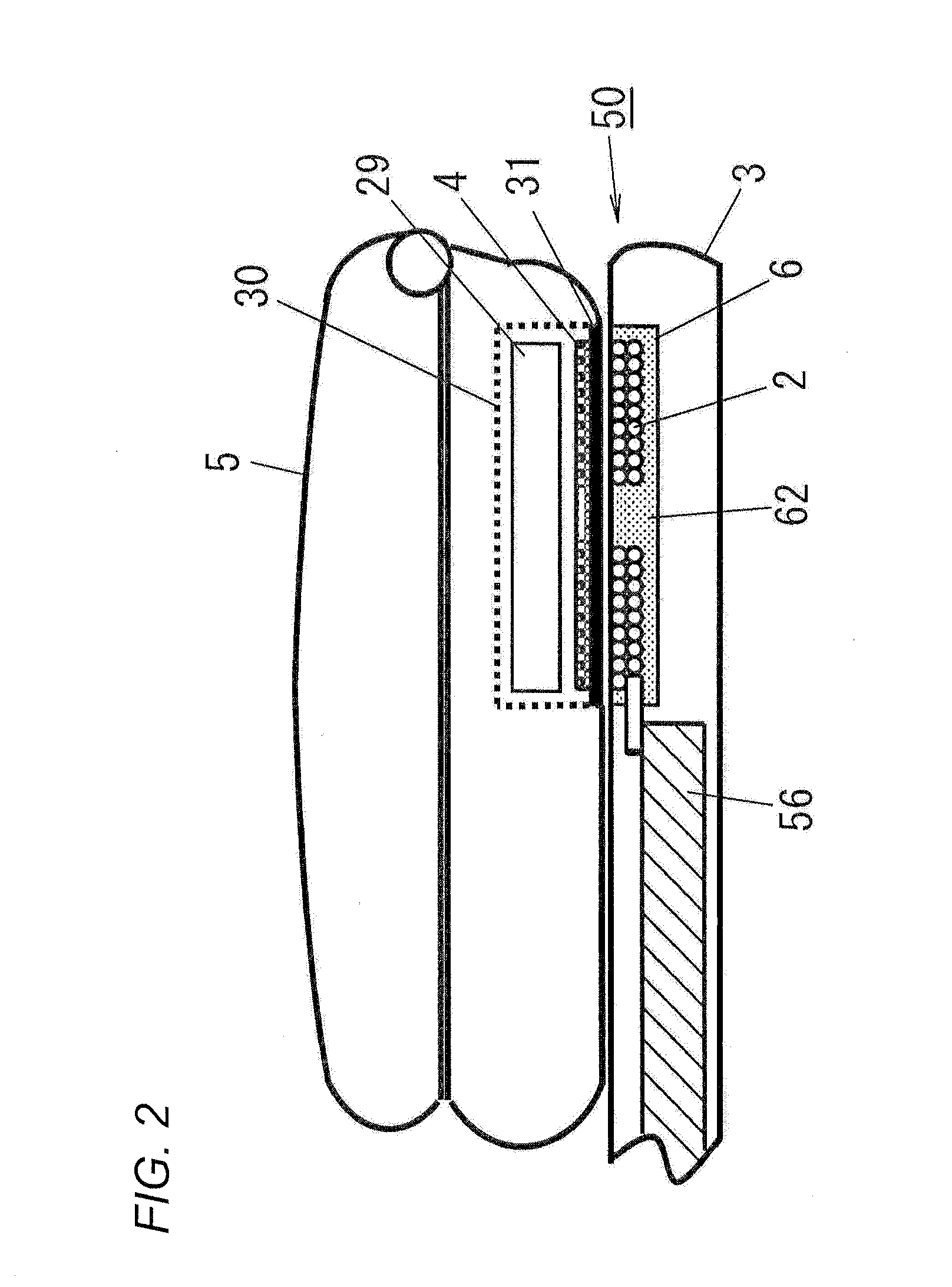

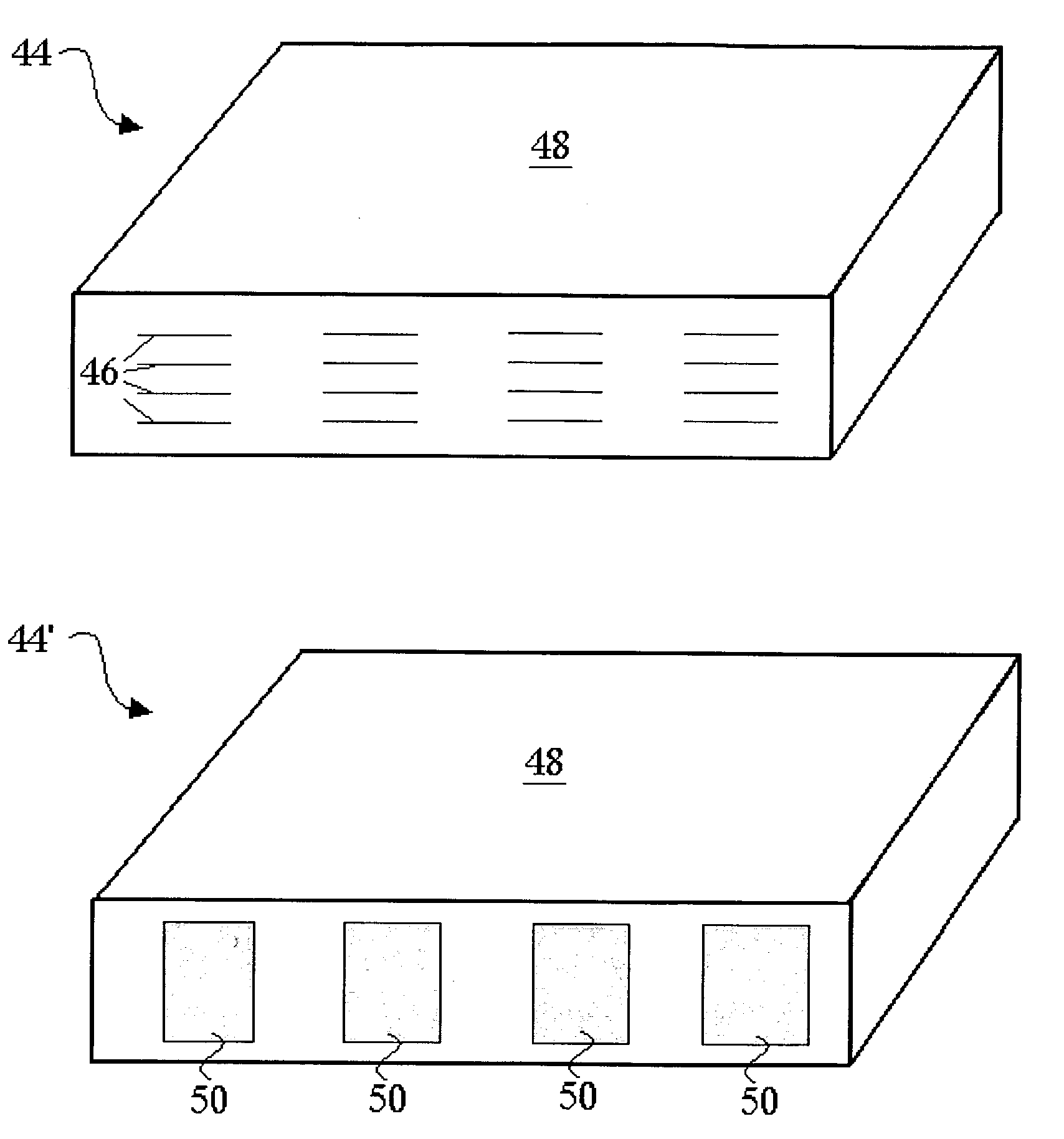

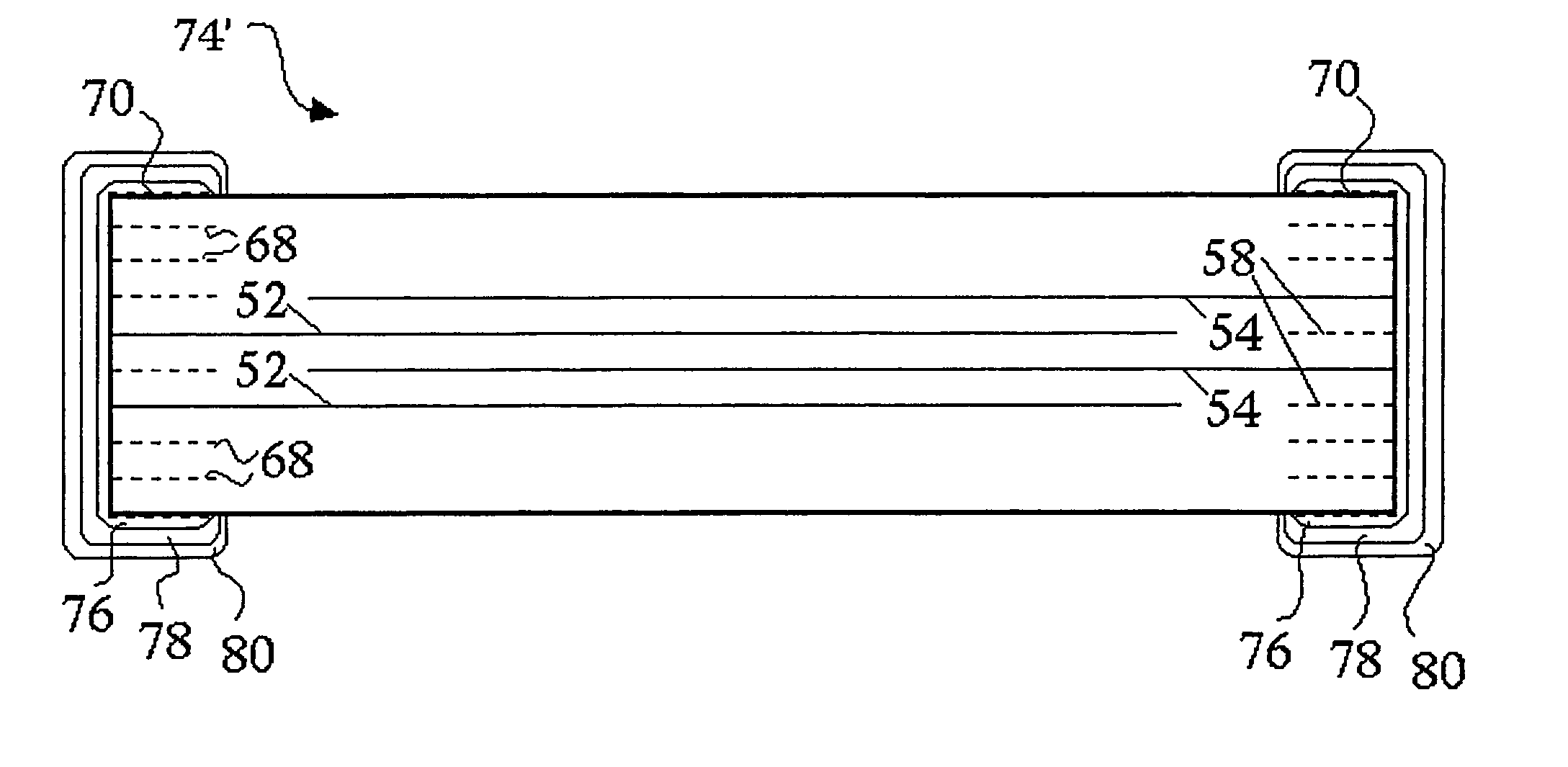

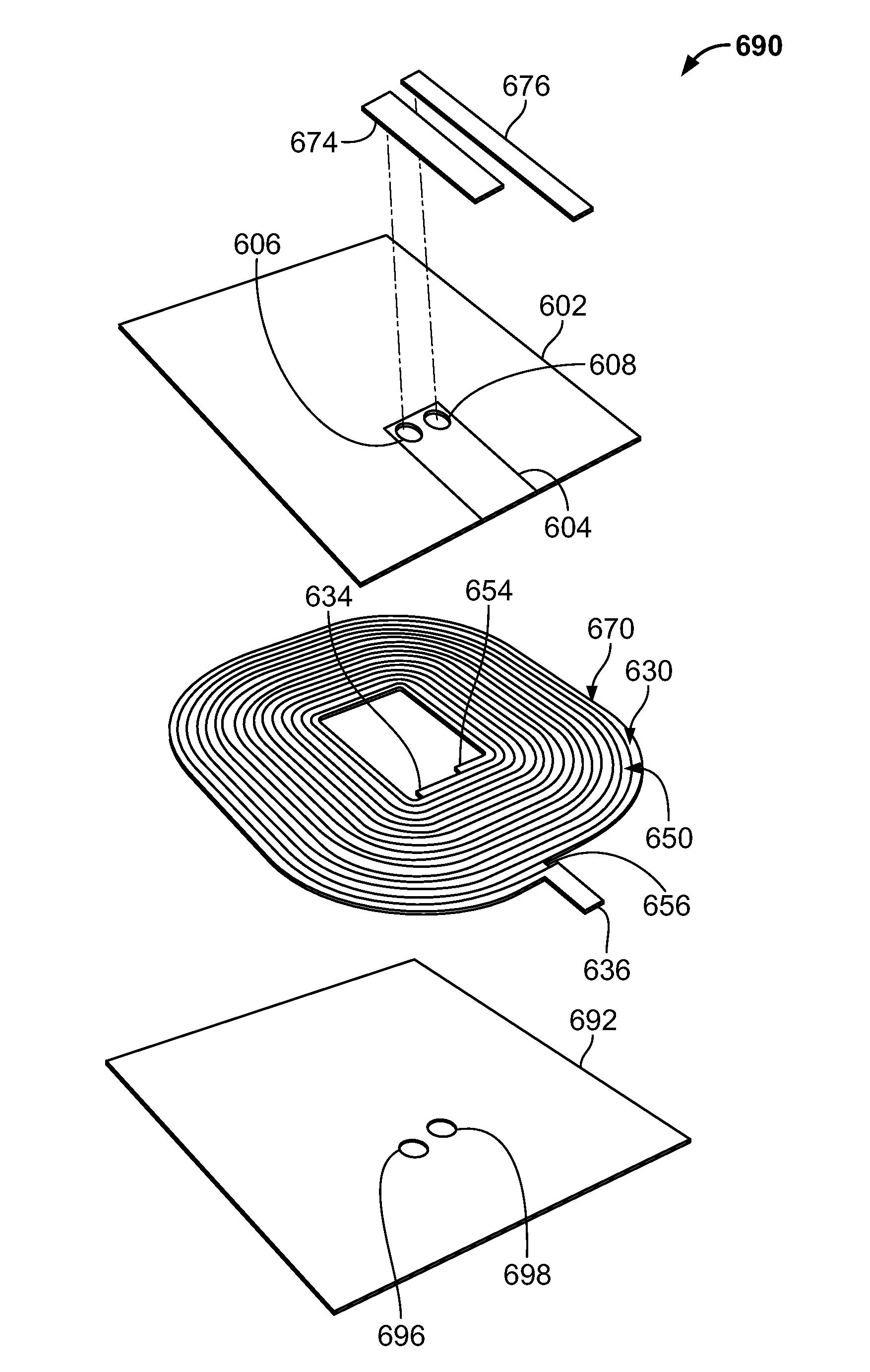

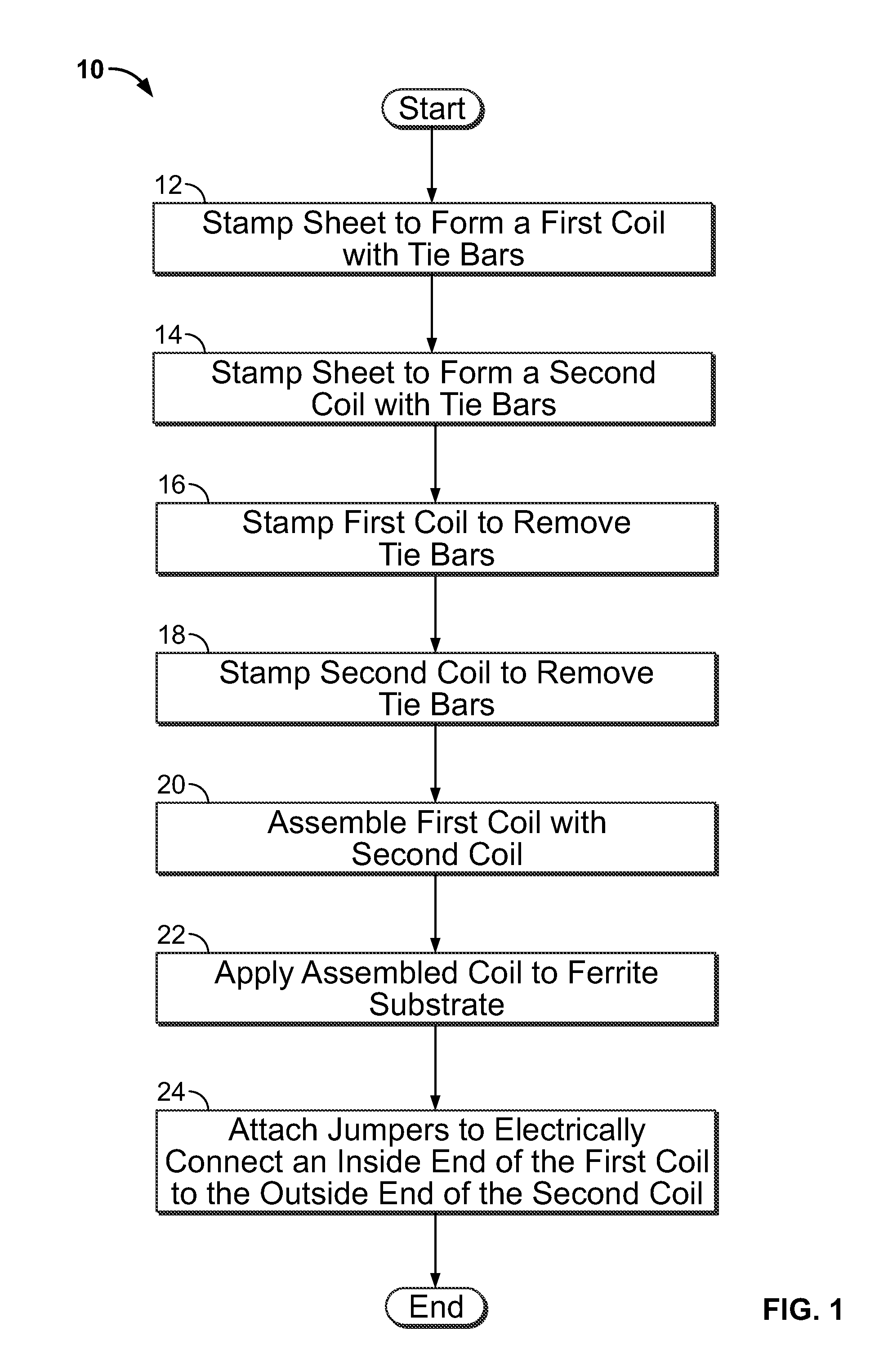

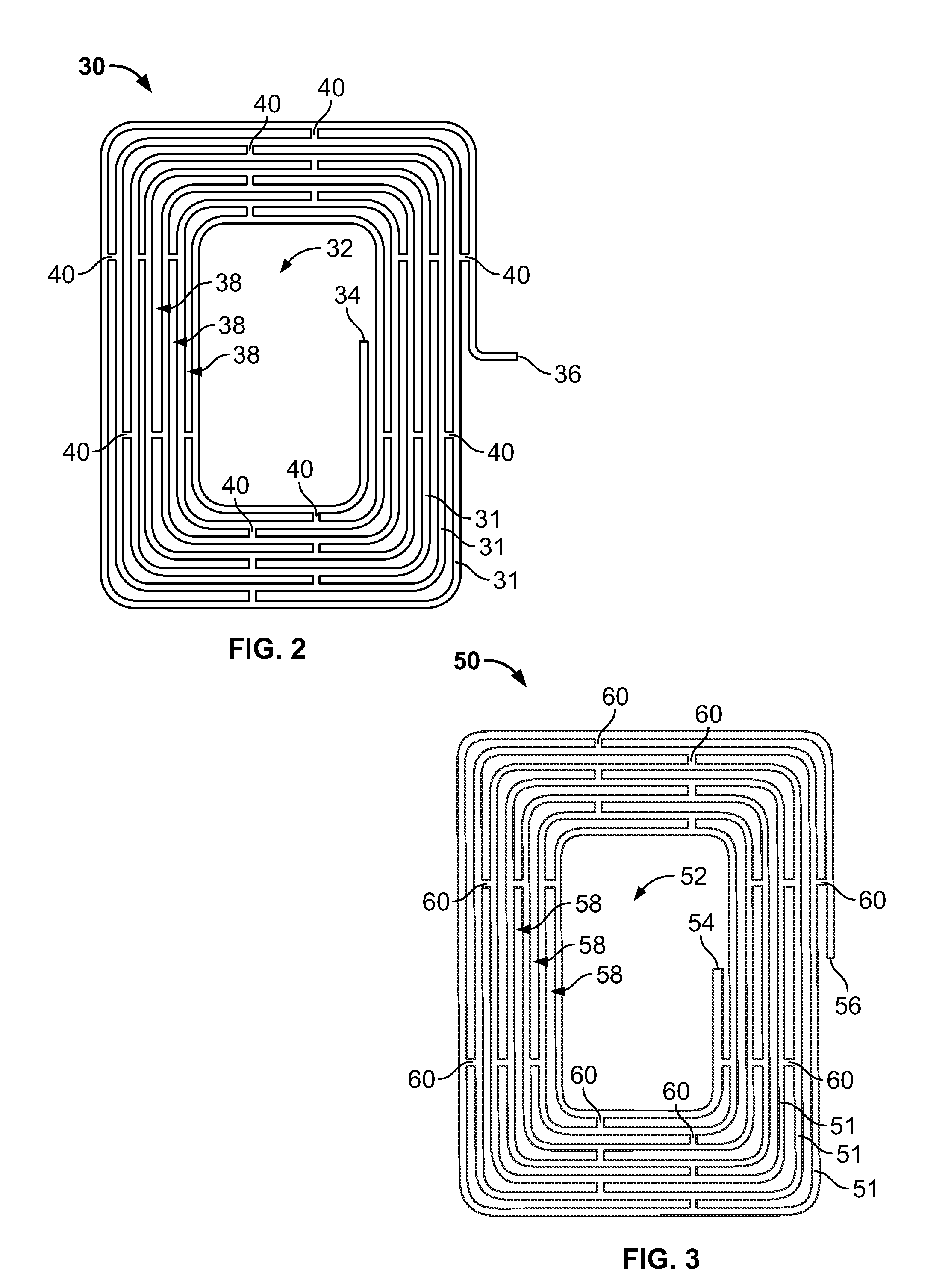

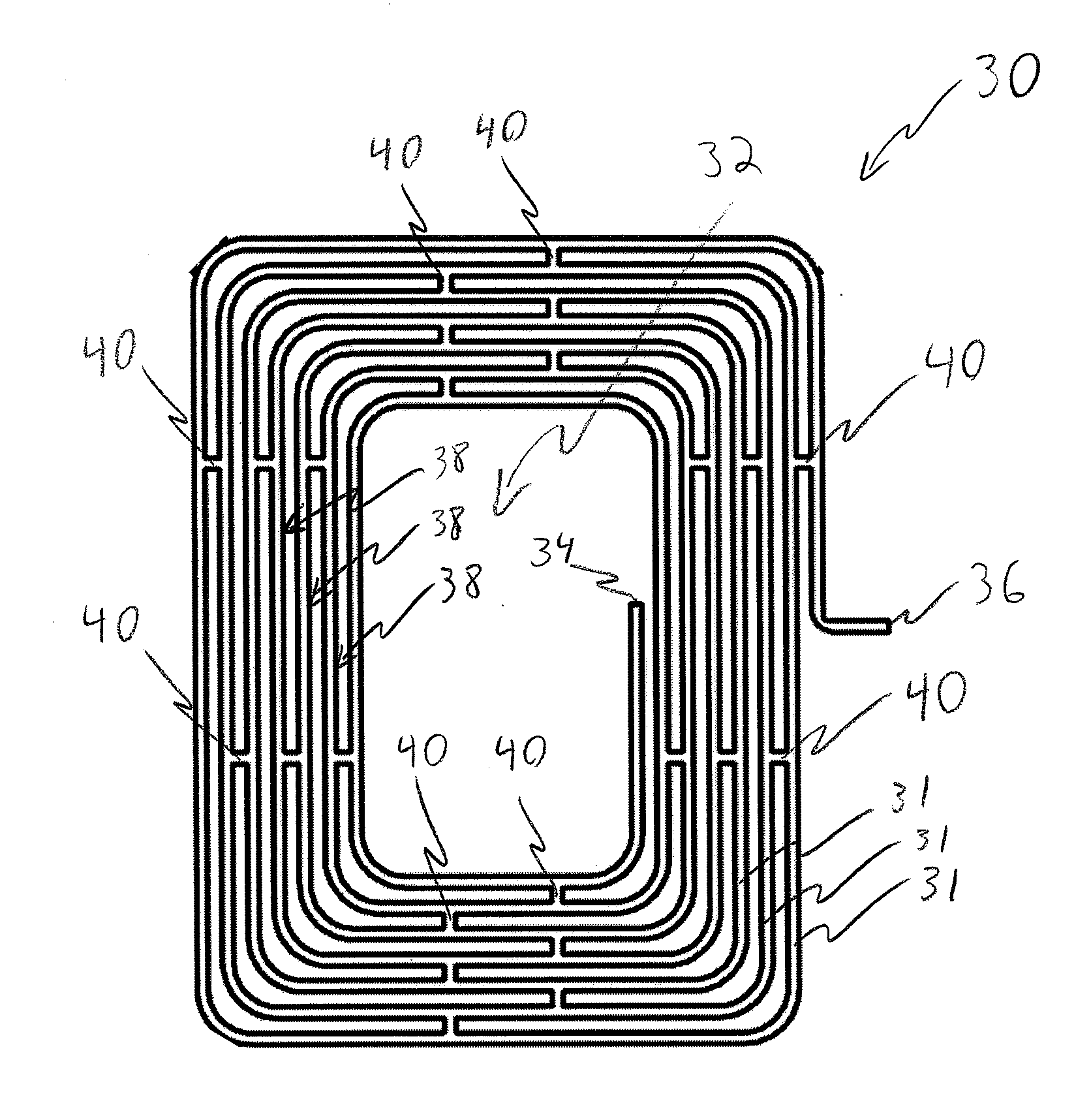

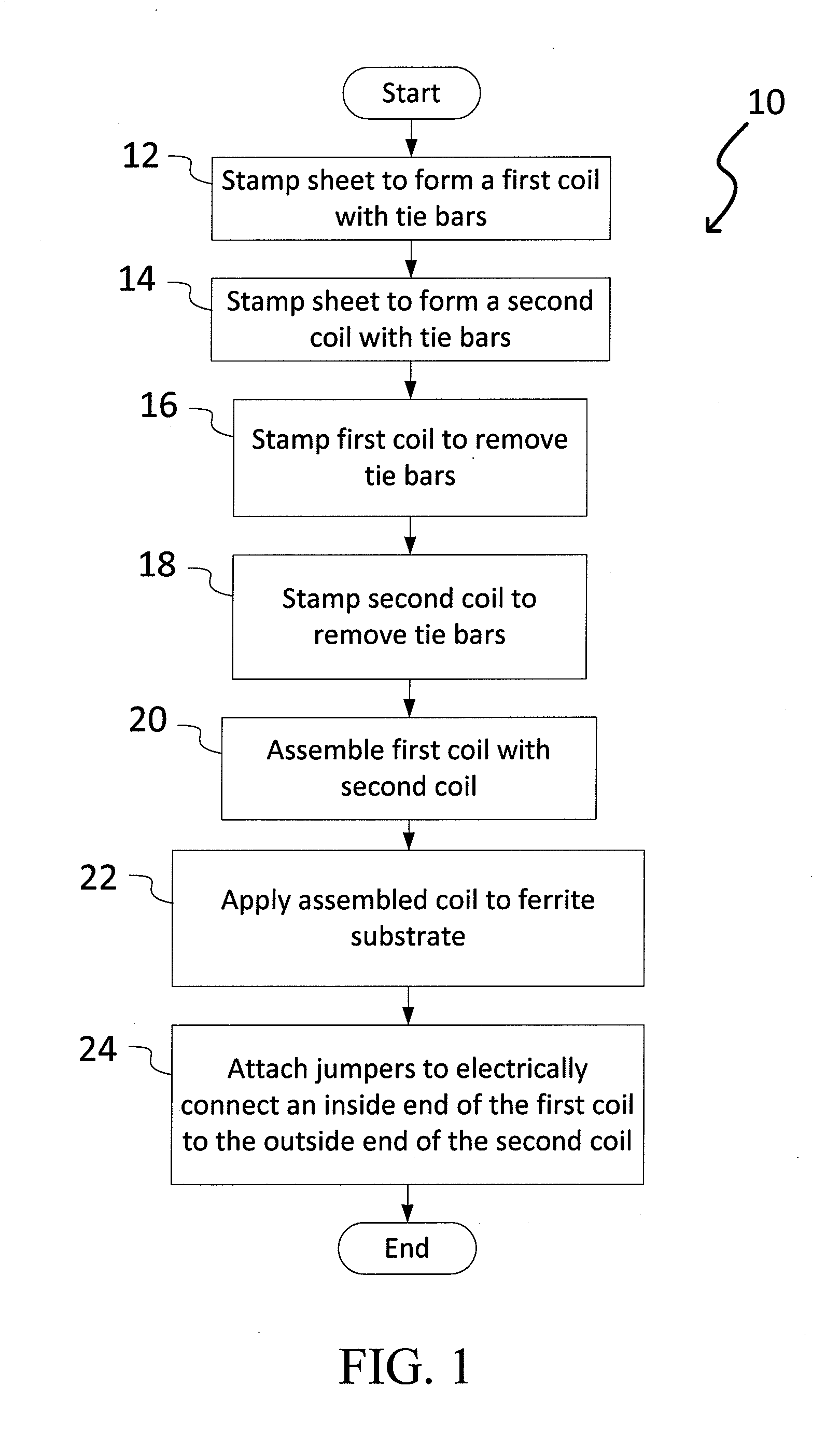

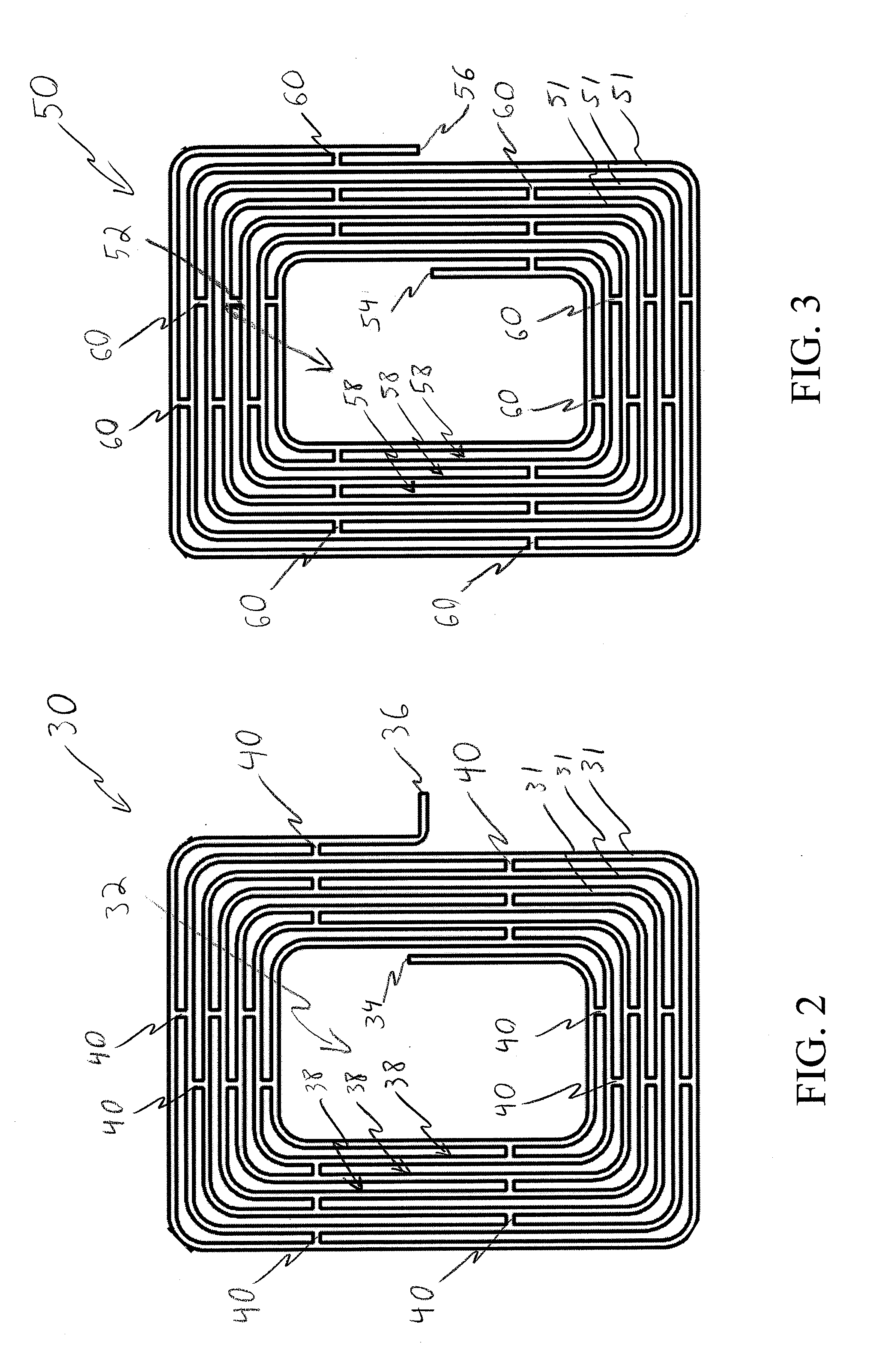

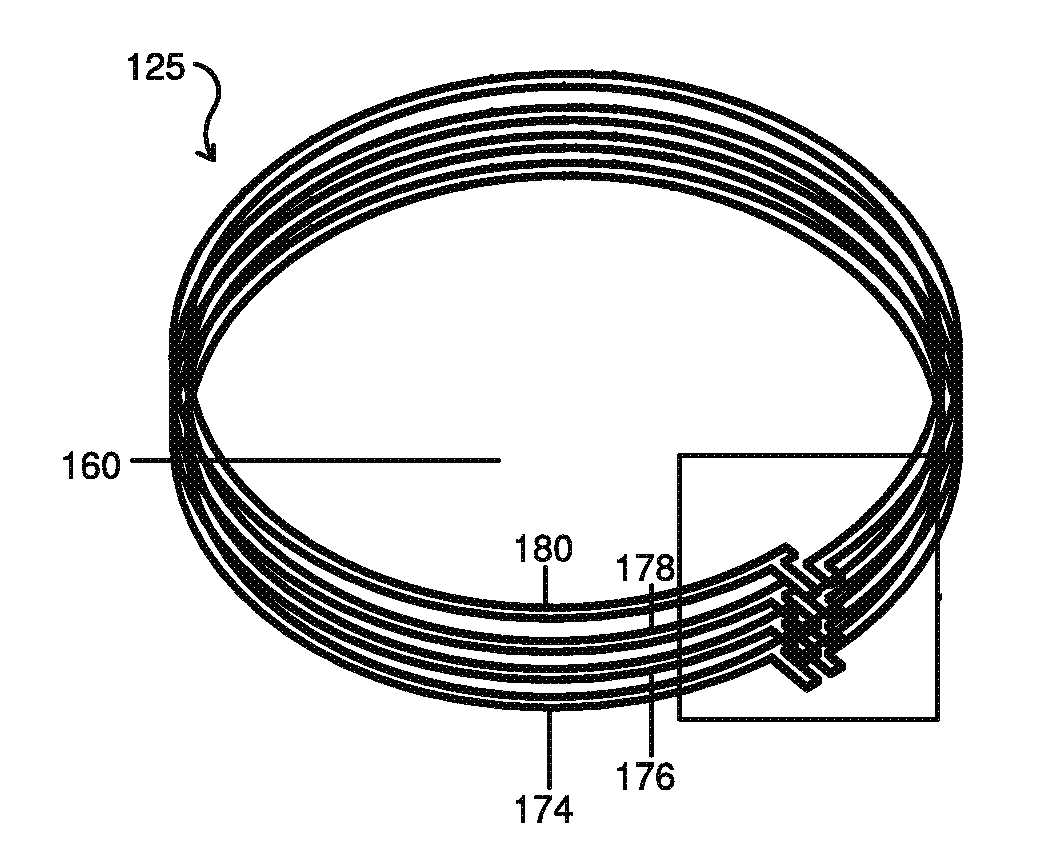

Wireless Charging Coil

ActiveUS20150145635A1Thin thicknessHigh densityNear-field transmissionBatteries circuit arrangementsConductor CoilInductive charging

A wireless charging coil is provided herein. More specifically, provided herein is a wireless charging coil comprising a first stamped coil having a first spiral trace, the first spiral trace defining a first space between windings, and a second stamped coil having a second spiral trace, the second spiral trace defining a second space between windings, the first stamped coil and second stamped coil in co-planar relation, the first stamped coil positioned within the second space of the second stamped coil, and the second stamped coil positioned within the first space of the first stamped coil, the first and second coils electronically connected and an adhesive covering and surrounding the first stamped coil and the second stamped coil to bond the coils together and to insulate the coils.

Owner:A K STAMPING

Methods for Fabricating Three-Dimensional All Organic Interconnect Structures

InactiveUS20070267138A1High frequency and high bandwidth applicationsSemiconductor/solid-state device detailsSolid-state devicesLiquid crystallineMaterials science

The present invention includes methods for making liquid crystalline polymer (LCP) interconnect structures using a high temperature and low temperature single sided LCP, where both the high and low temperature LCP are provided with a z-axis connection. The single sided conductive layer is a bus layer to form z-axis conductive stud within the high and low temperature LCP. High and low temperature LCP layers are etched or built up to form circuit patterns and subsequently bonded together to form final multilayer circuit pattern where the low temperature LCP melts to form both dielectric to dielectric bond to high temperature LCP circuit layer, and dielectric to conductive bond.

Owner:GEORGIA TECH RES CORP

Planar coil element and method for producing the same

ActiveUS20130249664A1Easy to produceLow viscosityInorganic material magnetismTransformers/inductances detailsViscositySpherical form

In a planar coil element and a method for producing the same, a metal magnetic powder-containing resin containing an oblate or needle-like first metal magnetic powder contains a second metal magnetic powder having an average particle size (1 μm) smaller than that (32 μm) of the first metal magnetic powder, which significantly reduces the viscosity of the metal magnetic powder-containing resin. Therefore, the metal magnetic powder-containing resin is easy to handle when applied to enclose a coil unit, which makes it easy to produce the planar coil element.

Owner:TDK CORPARATION

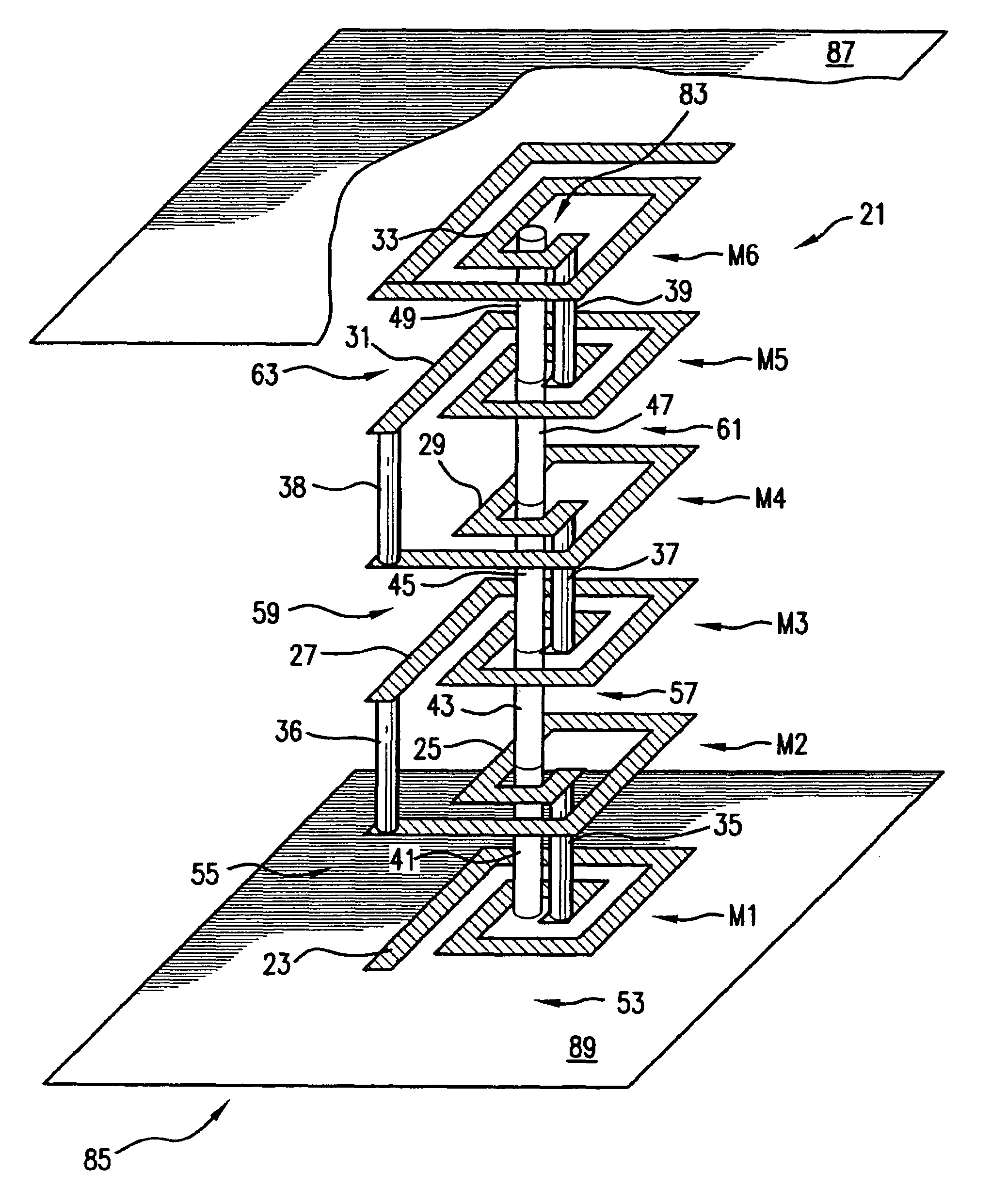

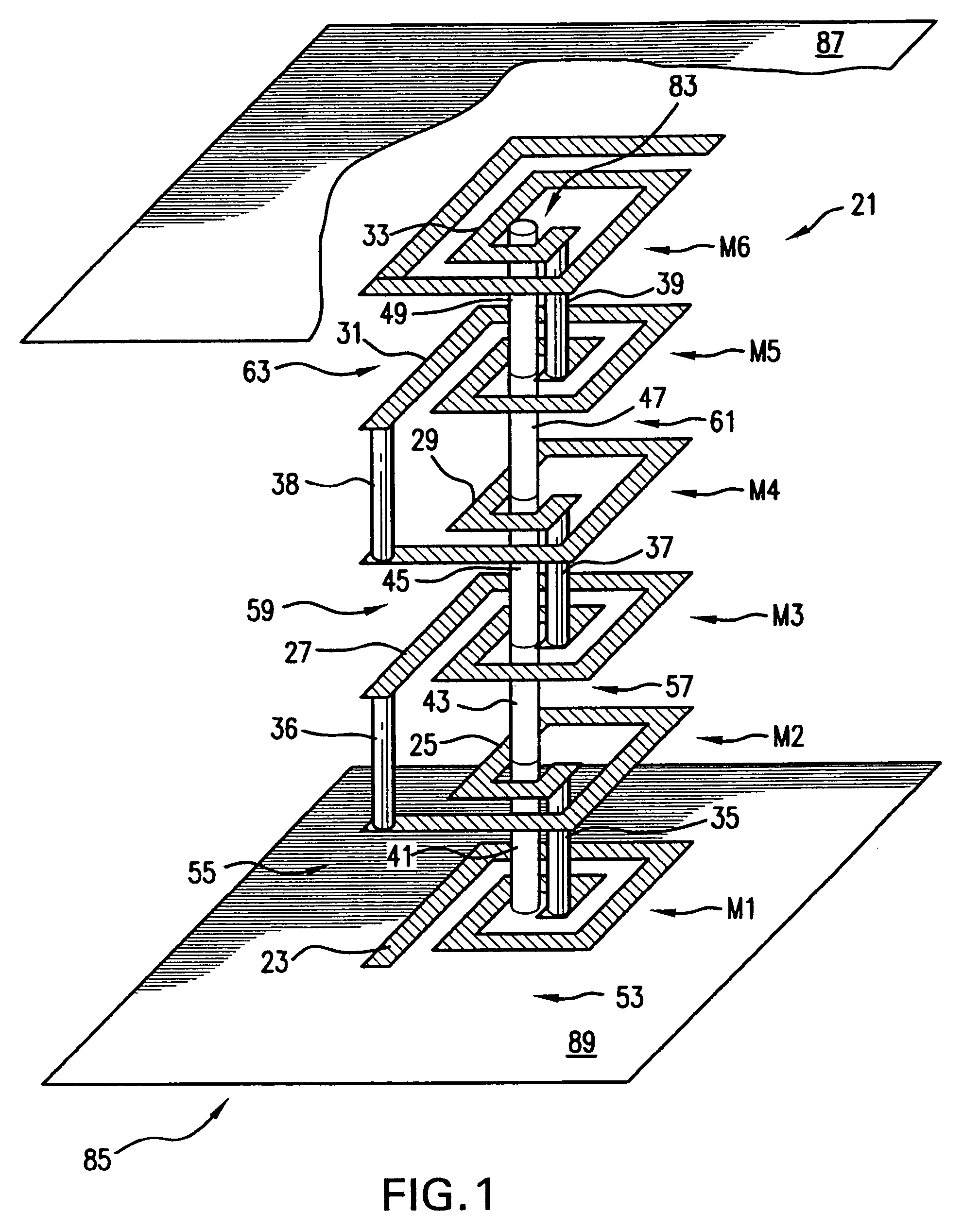

Compact inductor with stacked via magnetic cores for integrated circuits

InactiveUS7262680B2Small sizeReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit designIntegrated circuit

An on-chip inductor device for Integrated Circuits utilizes coils on a plurality of metal layers of the IC with electrical connectors between the coils and a magnetic core for the inductor of stacked vias running between the coils. The magnetic core is made from a series of stacked vias which are deposited between each metal layer of the IC having a coil. The magnetic core desirably includes an array of magnetic bars comprising the magnetic core. The via material of the magnetic core may be both magnetic and electrically conductive. The magnetic and electrically conductive via material may also be used for the planar coil electrical connectors or other electrically conductive parts of the IC, or both, thereby lessening fabrication steps. Films of magnetic material may be formed at the ends of the inductor to provide a closed magnetic circuit for the inductor. A high Q factor inductor of small (e.g., transistor) size is thus obtained. The materials and processes which enable the on-chip inductor device are compatible with ordinary IC fabrication methods.

Owner:ILLINOIS INSTITUTE OF TECHNOLOGY

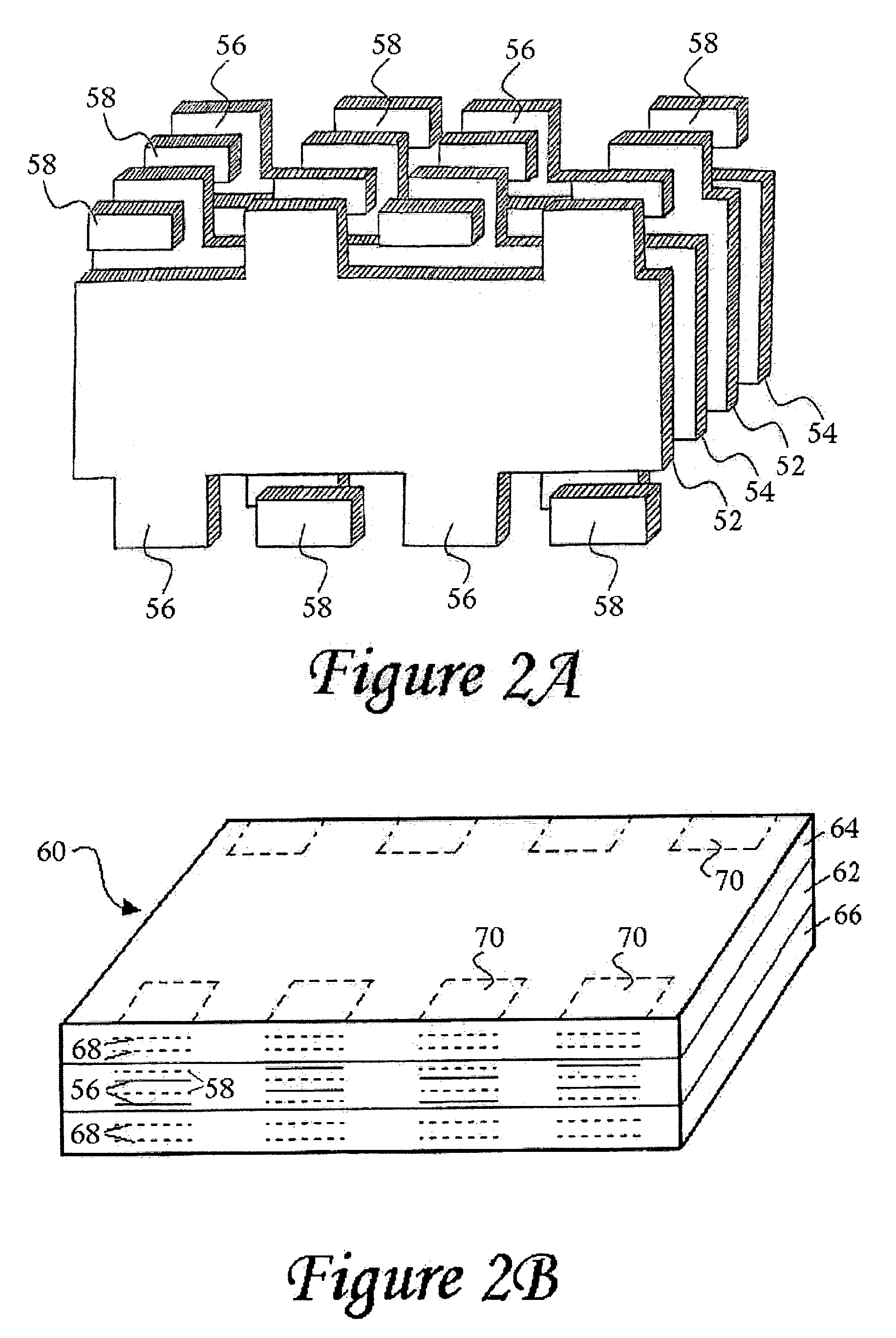

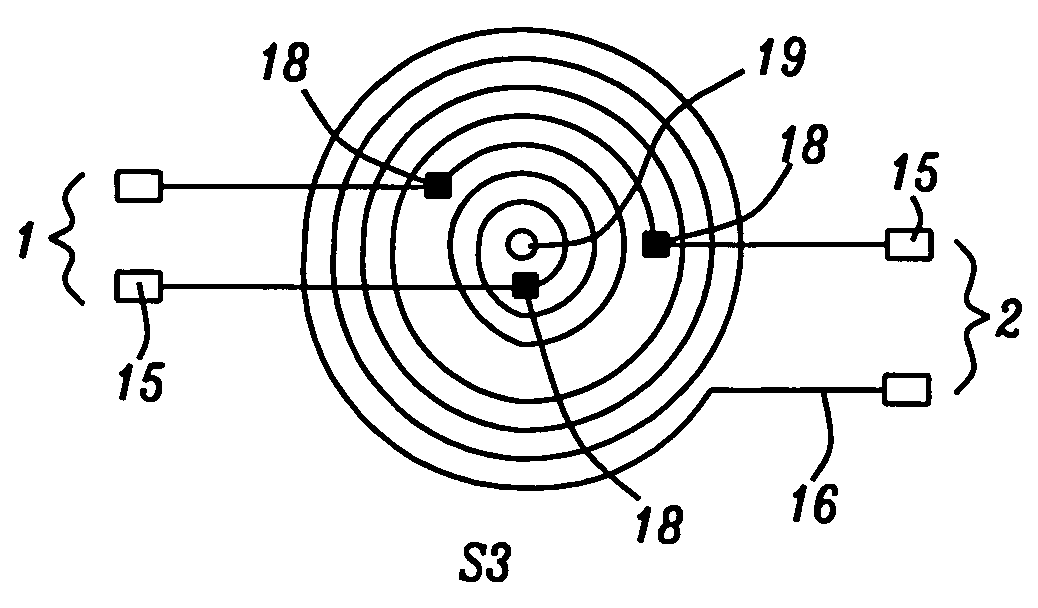

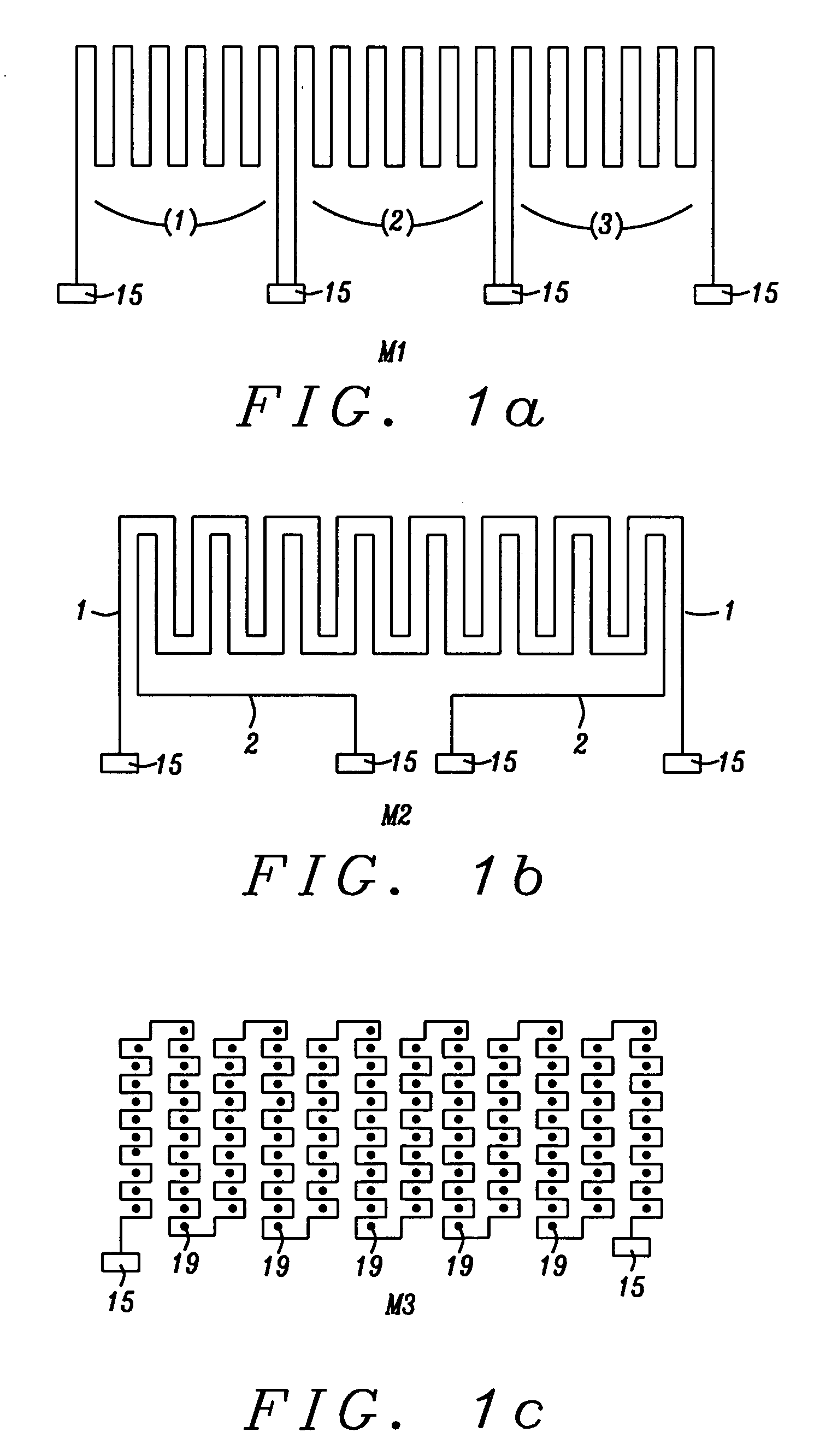

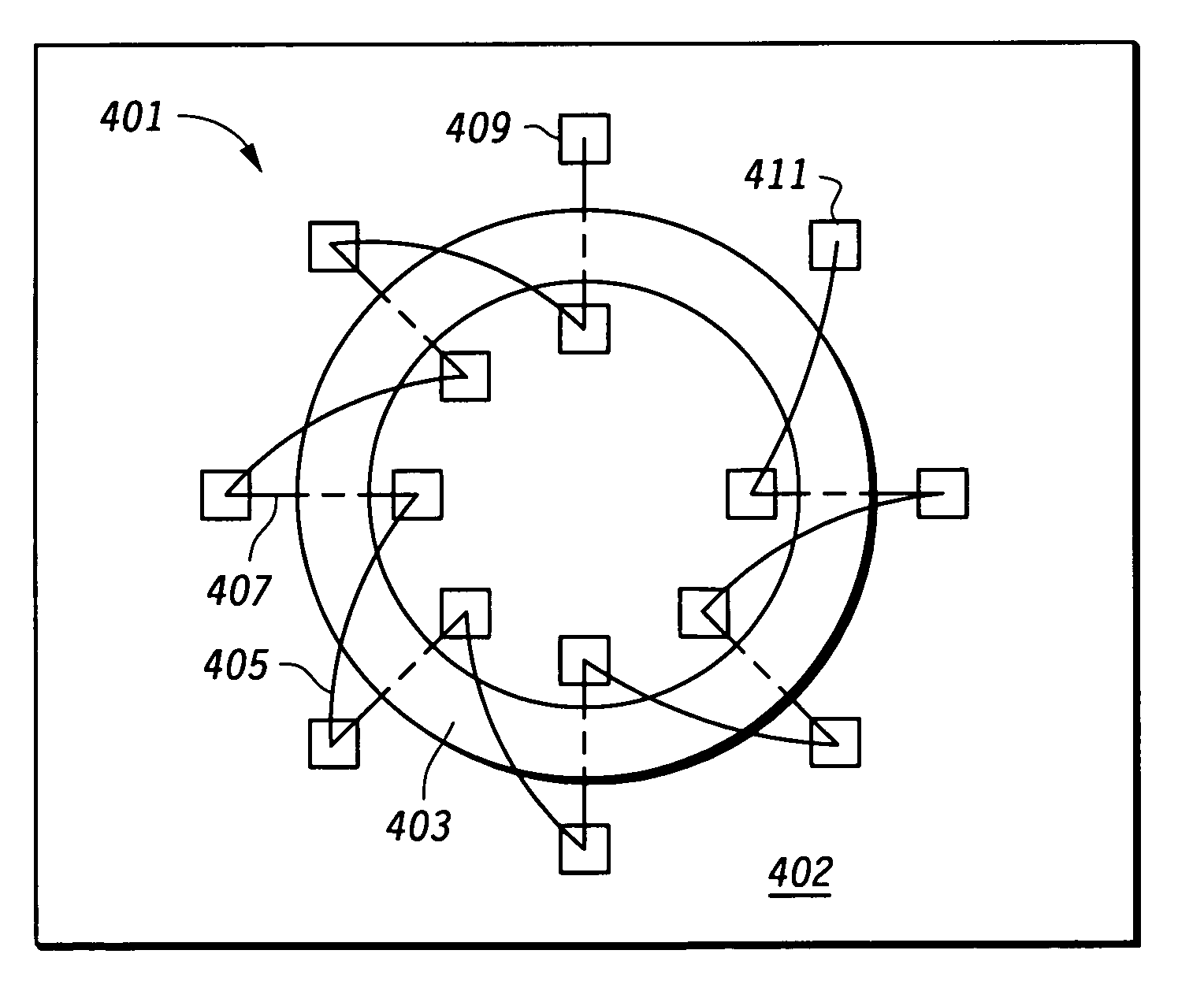

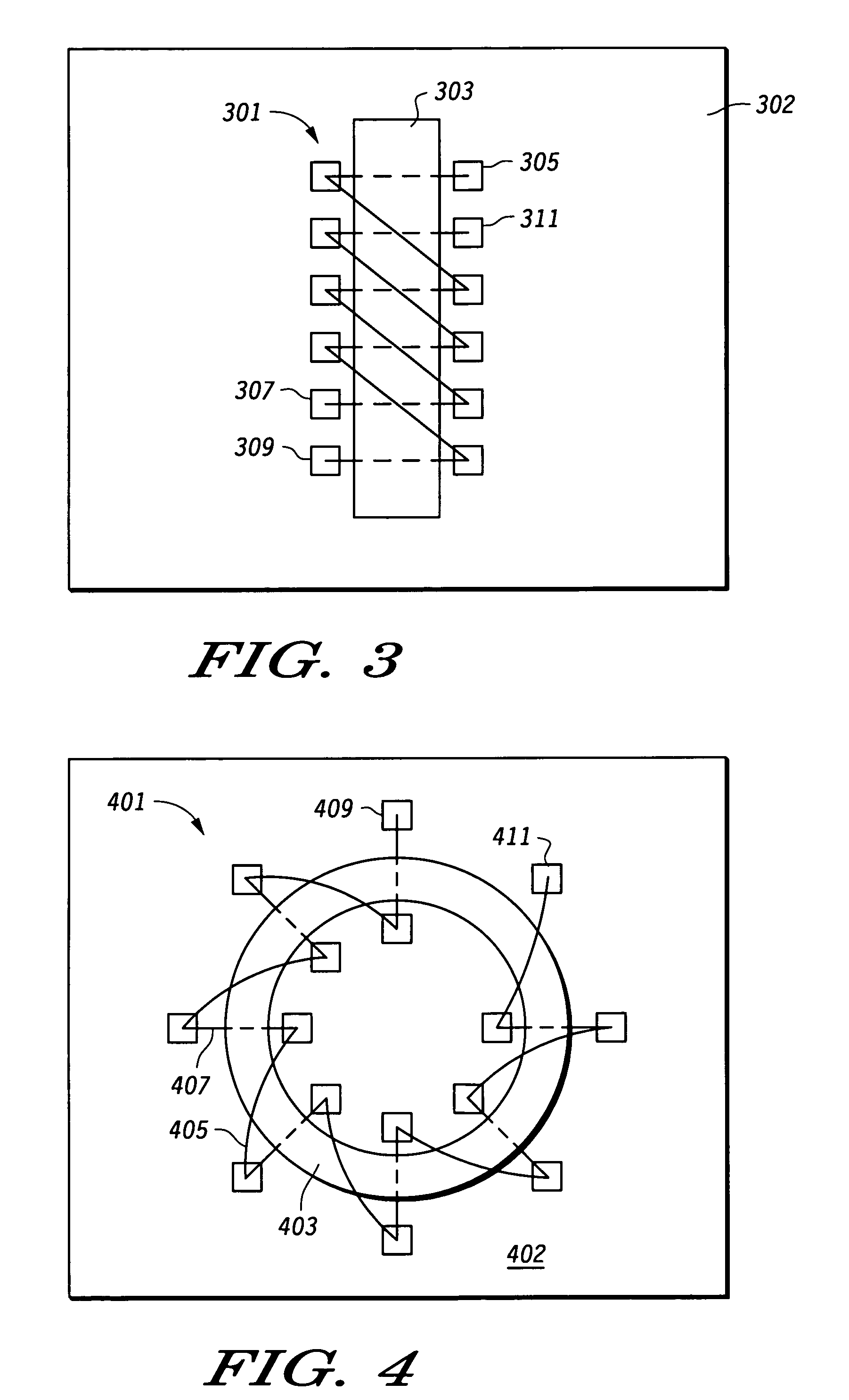

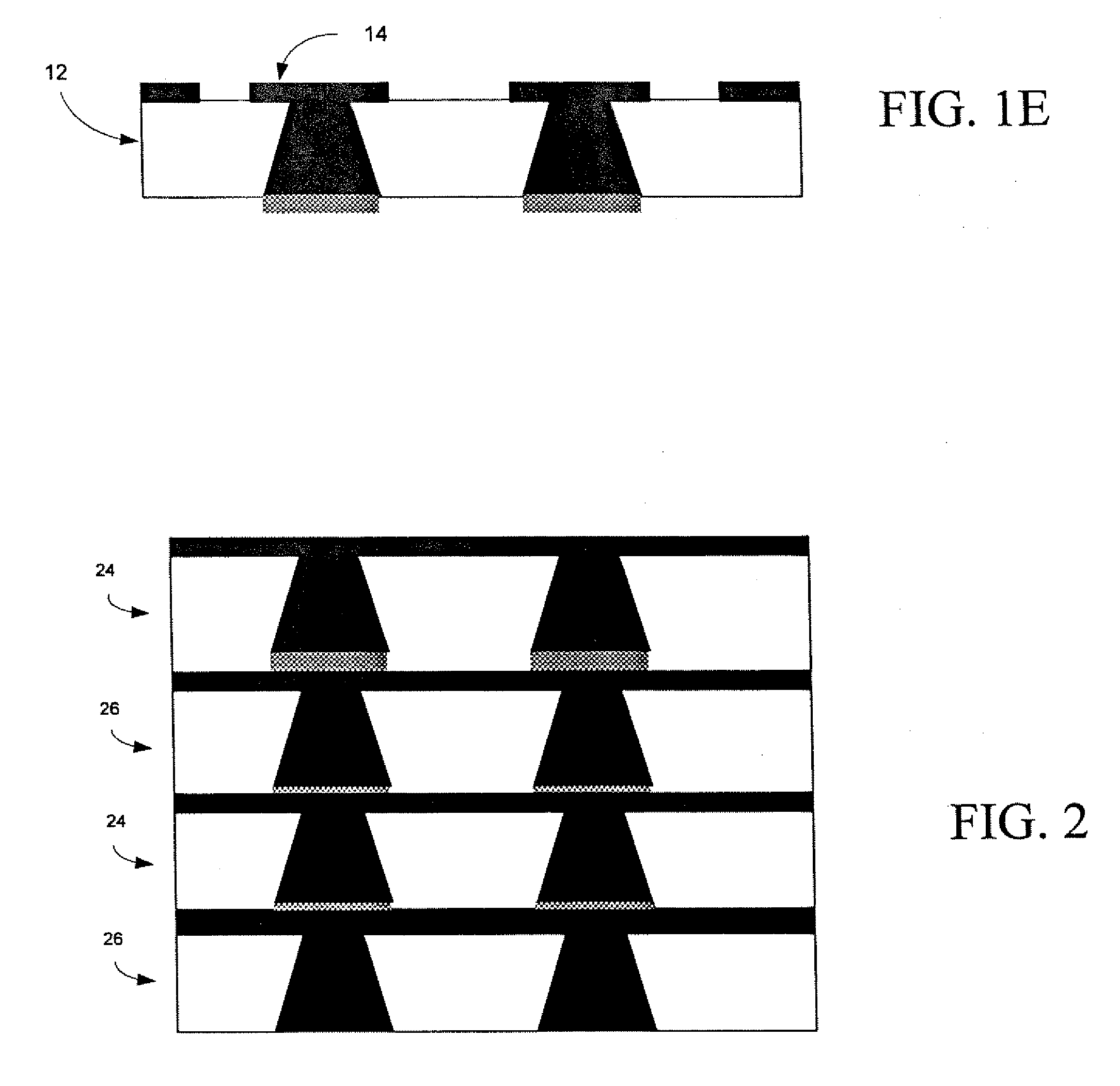

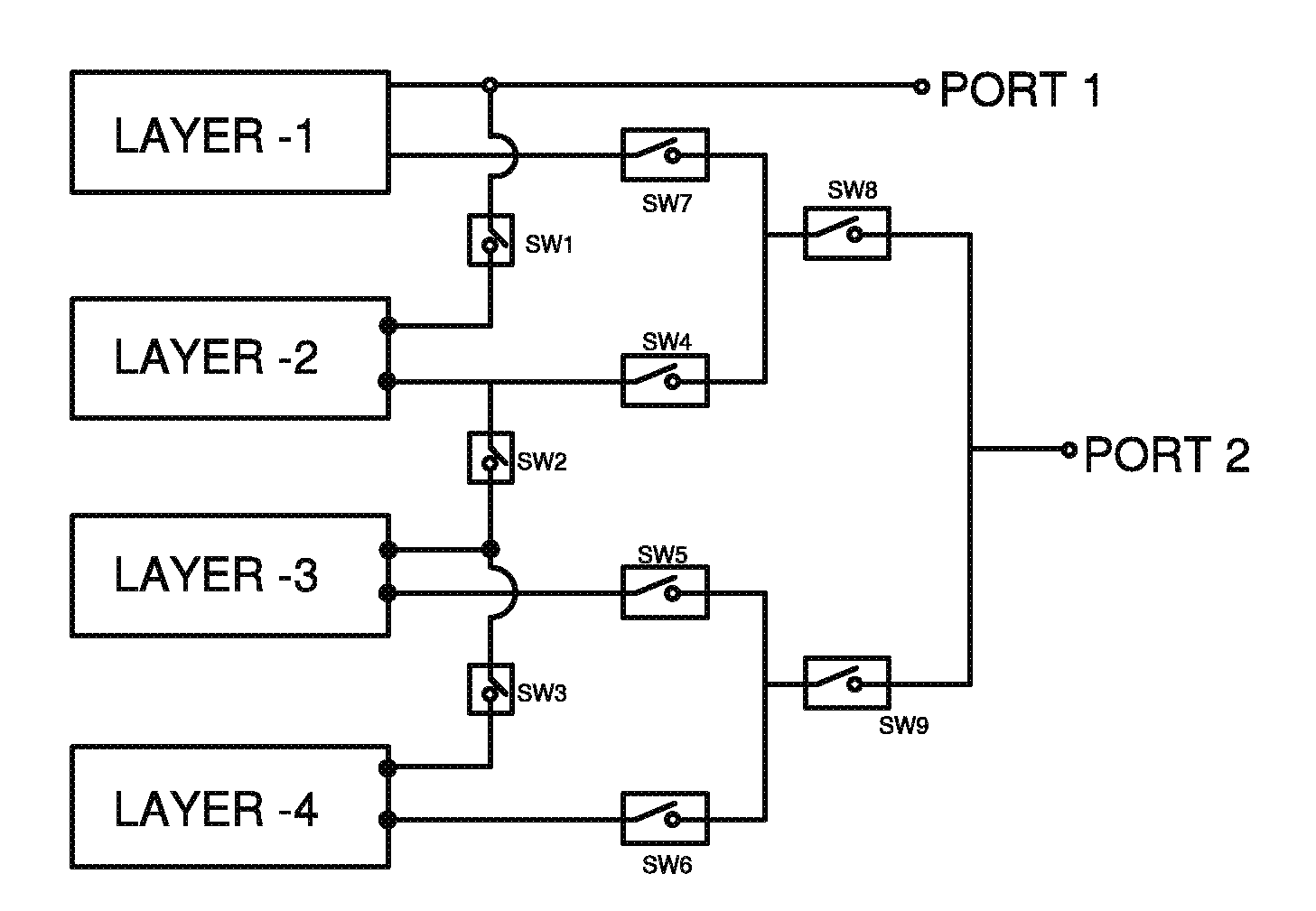

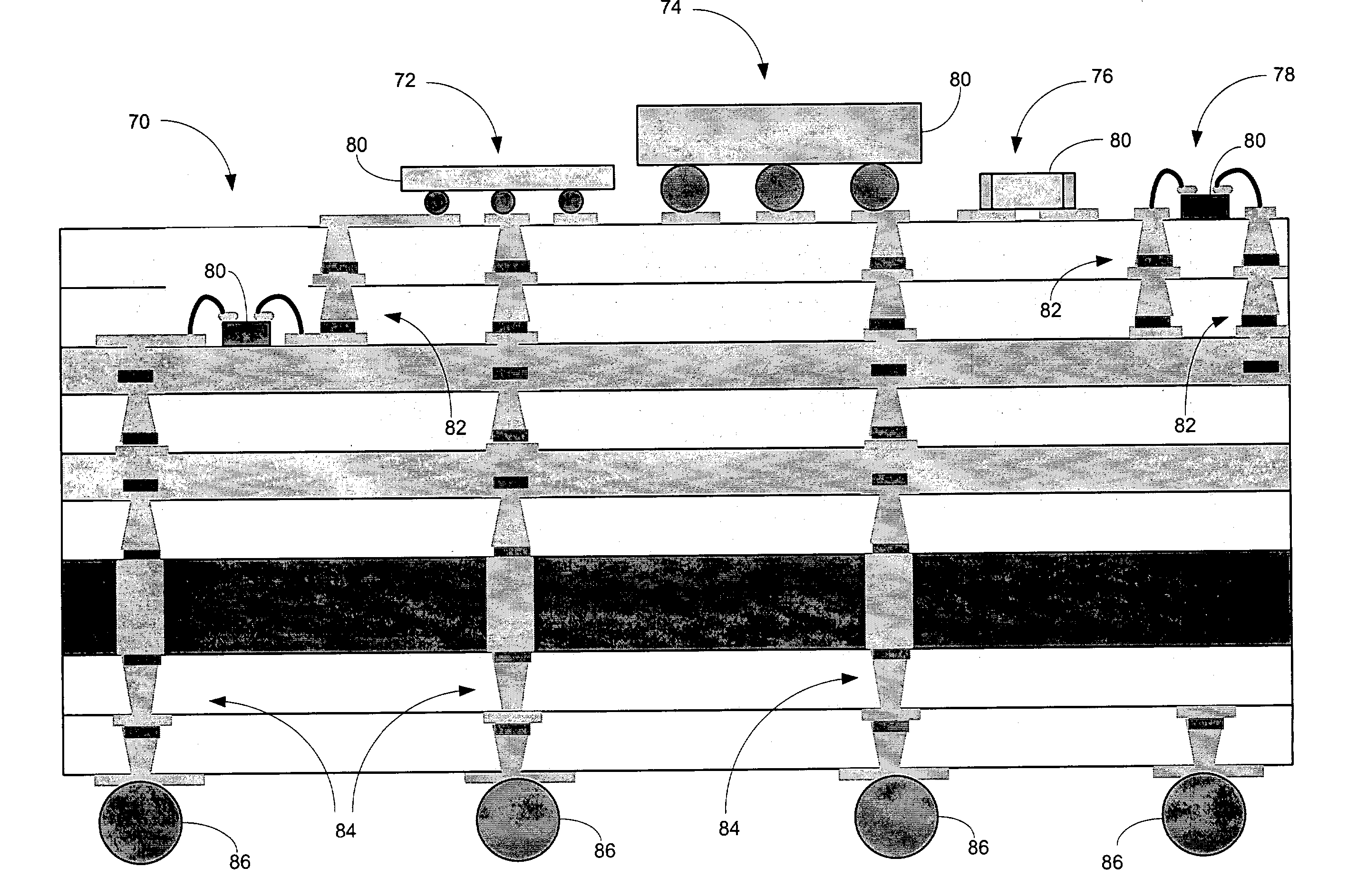

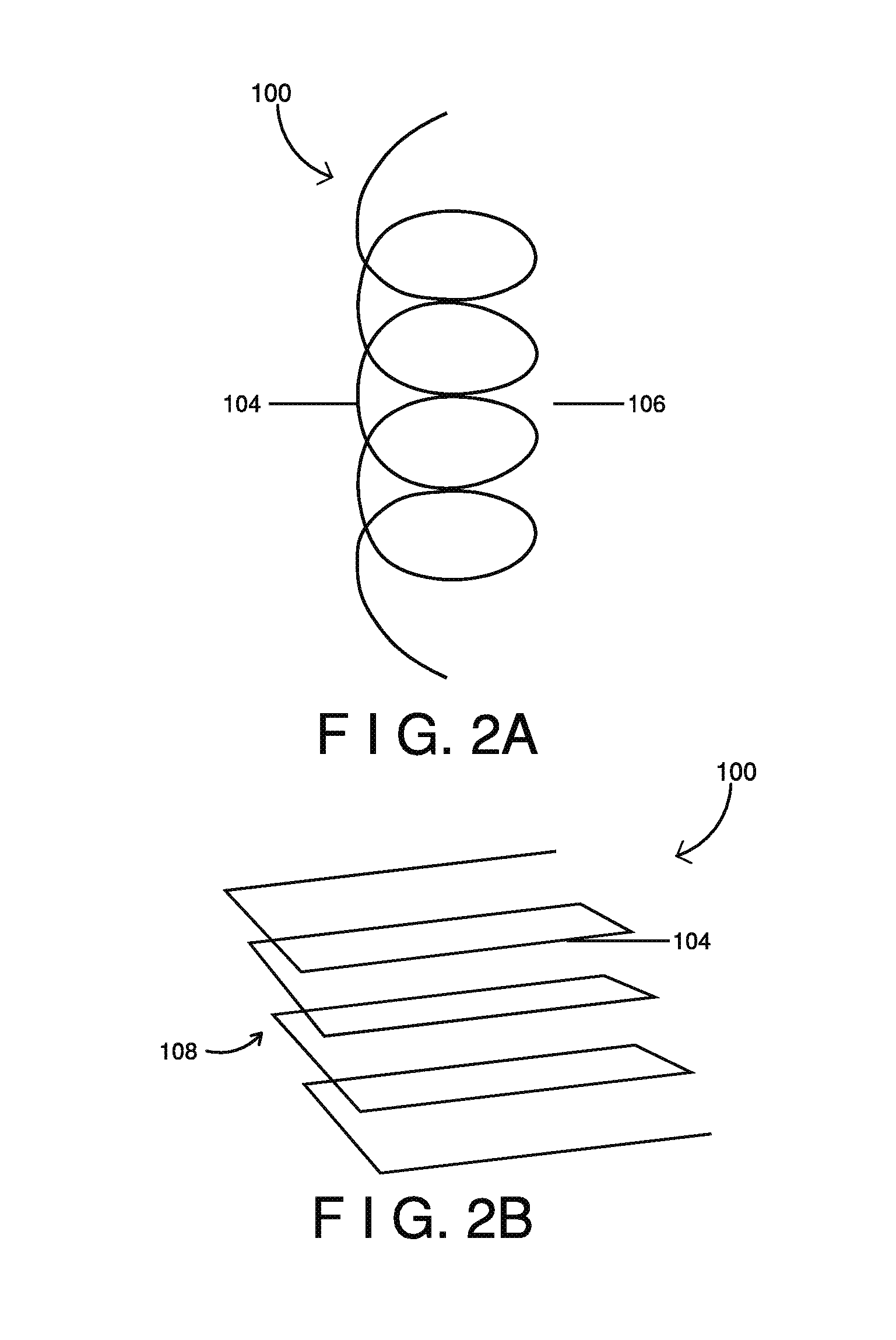

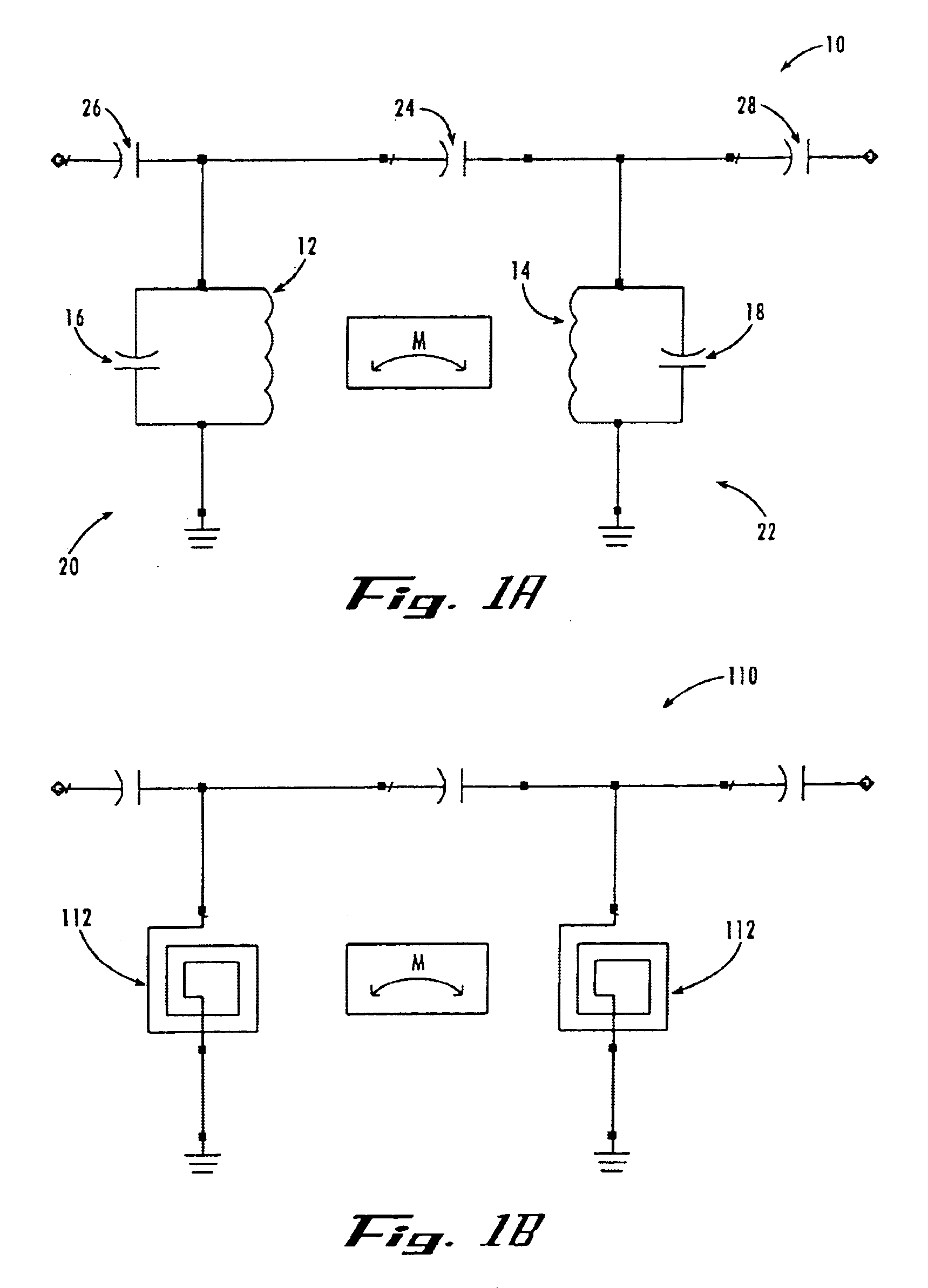

Systems using multi-layer-multi-turn high efficiency inductors

ActiveUS20130208390A1Higher resistive lossIncrease qualify factorTransformers/inductances coils/windings/connectionsInternal electrodesElectrical resistance and conductanceElectricity

Owner:NUCURRENT INC

Wireless Charging Coil

ActiveUS20150145634A1Thin thicknessHigh densityNear-field transmissionTransformersWirelessElectrical and Electronics engineering

A wireless charging coil is provided herein. The wireless charging coil comprising a first stamped coil having a first spiral trace, the first spiral trace defining a first space between windings, and a second stamped coil having a second spiral trace, the second spiral trace defining a second space between windings, wherein the first stamped coil and second stamped coil are planar to and interconnected with one another, such that the first stamped coil is positioned within the second space of the second stamped coil, and the second stamped coil is positioned within the first space of the first stamped coil.

Owner:A K STAMPING

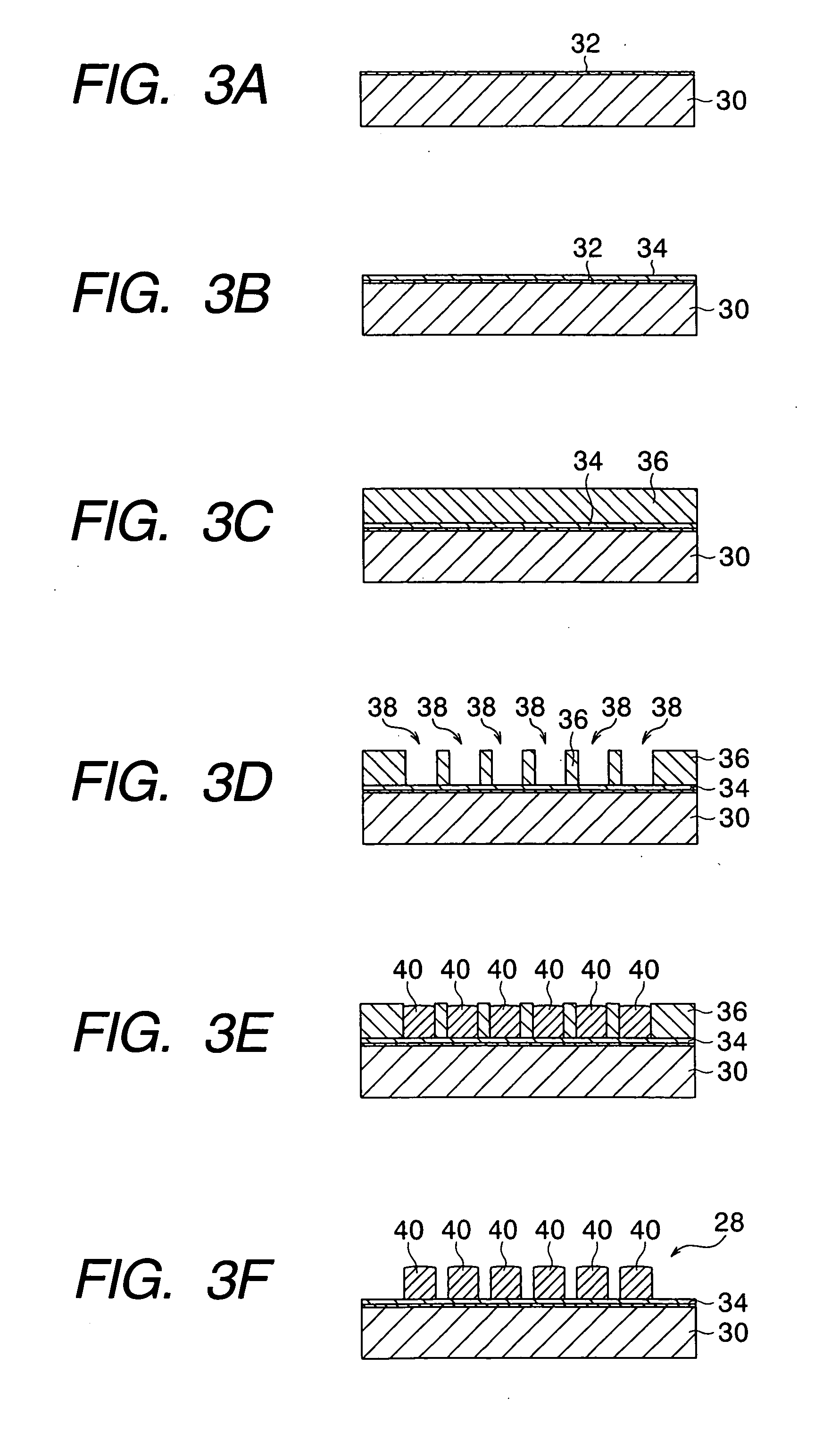

Method of manufacturing multi-layer coil and multi-layer coil device

ActiveUS20150035640A1Less spaceImprove featuresTransformers/inductances coils/windings/connectionsPrinted inductancesEngineeringElectroplating

A method of manufacturing a multi-layer coil includes steps of providing a substrate; forming a seed layer on the substrate; and plating the seed layer with N coil layers by N current densities according to N threshold ranges, so as to form the multi-layer coil on the substrate, wherein an i-th current density of the N current densities is lower than an (i+1)-th current density of the N current densities. A first coil layer of the N coil layers is plated on the seed layer by a first current density of the N current densities. When an aspect ratio of an i-th coil layer of the N coil layers is within an i-th threshold range of the N threshold ranges, an (i+1)-th coil layer of the N coil layers is plated on the i-th coil layer by the (i+1)-th current density.

Owner:CYNTEC

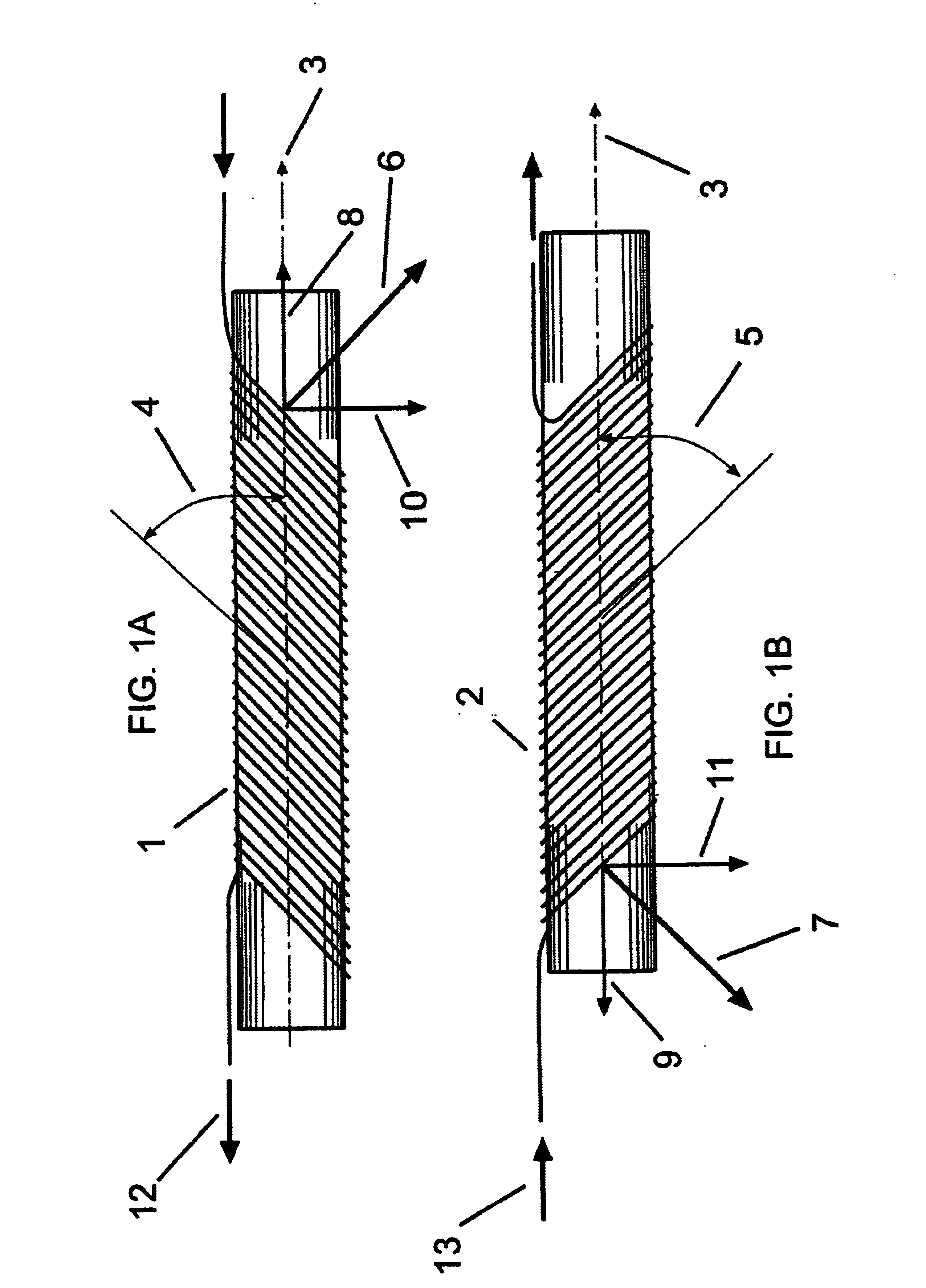

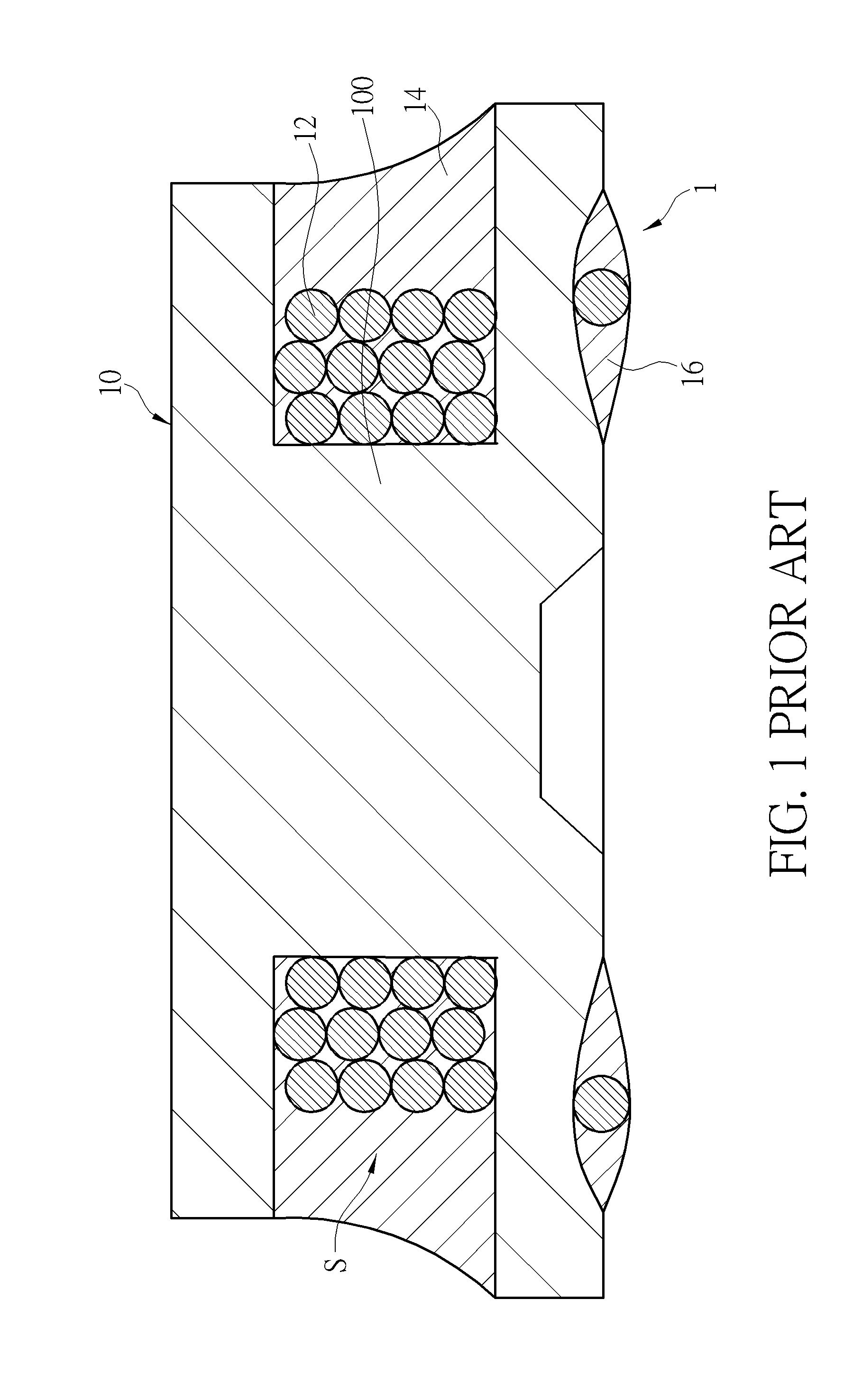

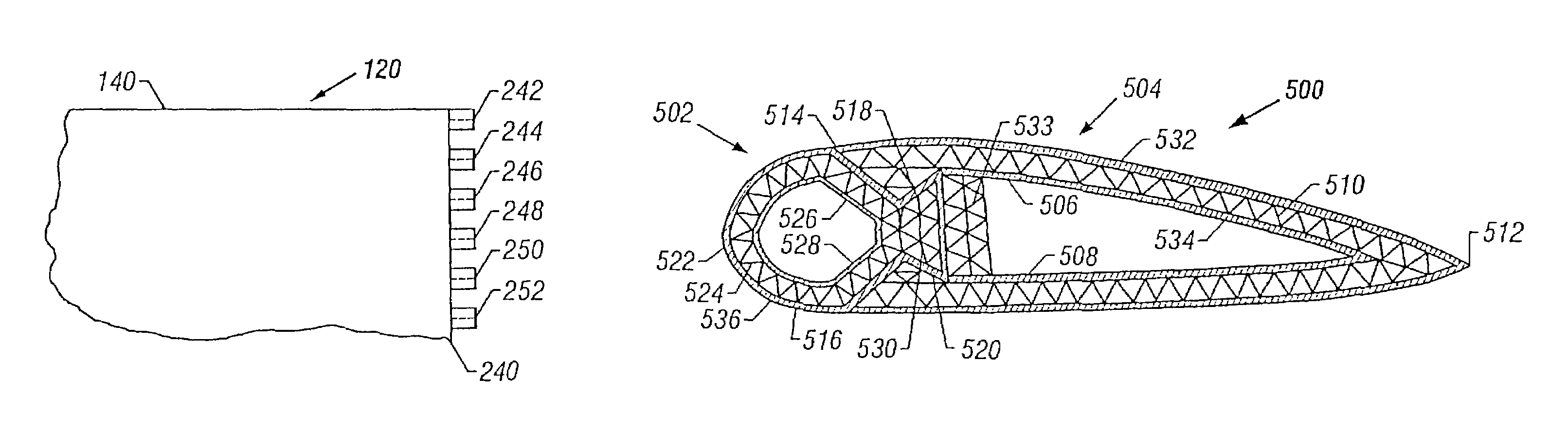

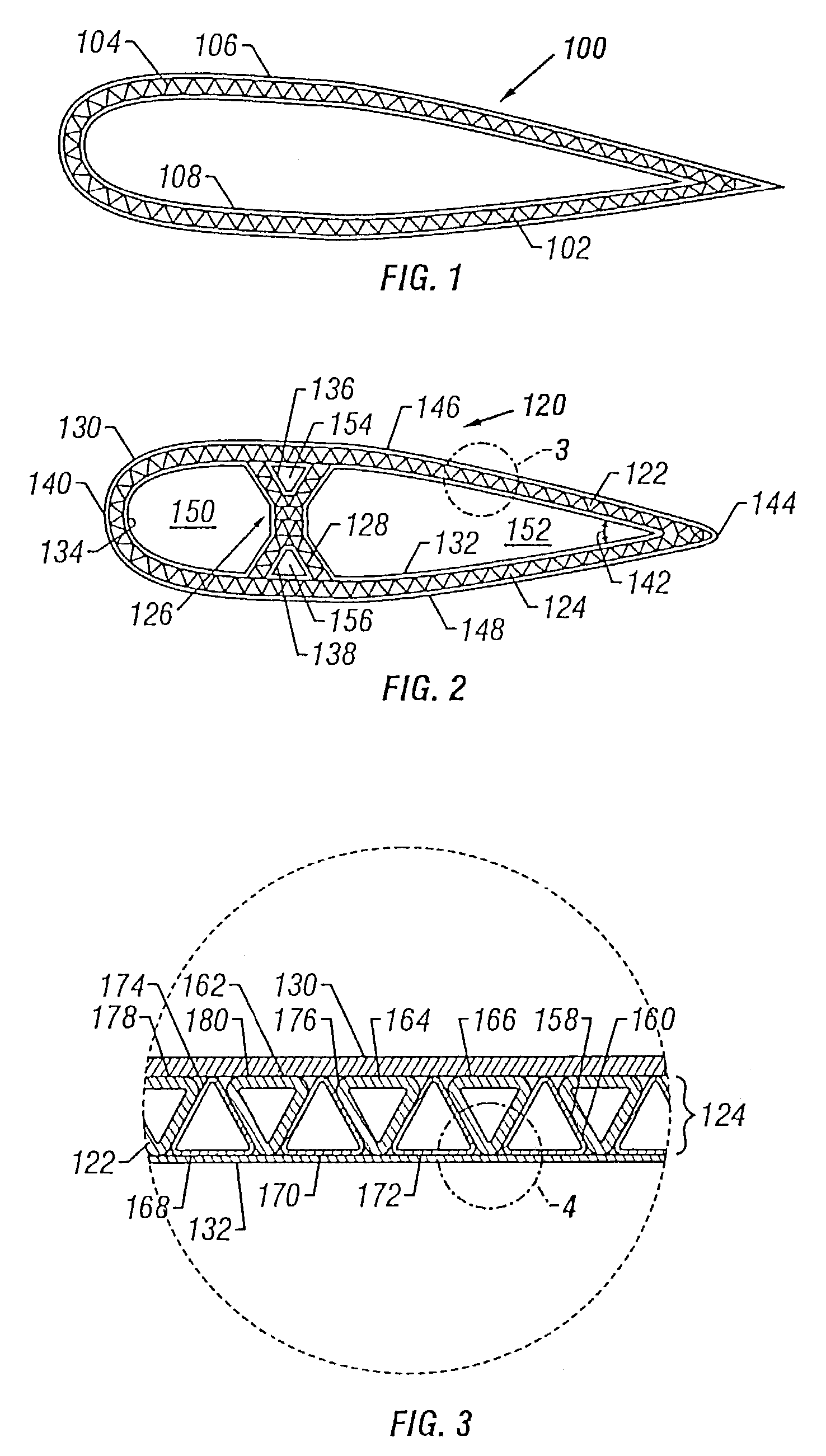

Tubular members integrated to form a structure

InactiveUS7063763B2Eliminate needEffective carryFuselage framesAircraft stabilisationMechanical engineeringFilament winding

Integrally stiffened and formed, load carrying structures comprising a plurality of elongated thin-walled tubes placed co-extensively in a complementary side-by-side fashion which together form a hollow structure having a desired external contour. Integral skins forming the external and internal surfaces of the structure cooperatively therewith. The structure can be formed with an underlying internal support member spanning the interior of the load carrying structure, thereby connecting opposite sides of the structure together. Also, each of the tubes are wound with fibers in controlled orientations generally paralleling the direction of the loads applied to the tubes to optimize the strength to weight ratio of the tubes.

Owner:CHAPMAN JR W CULLEN

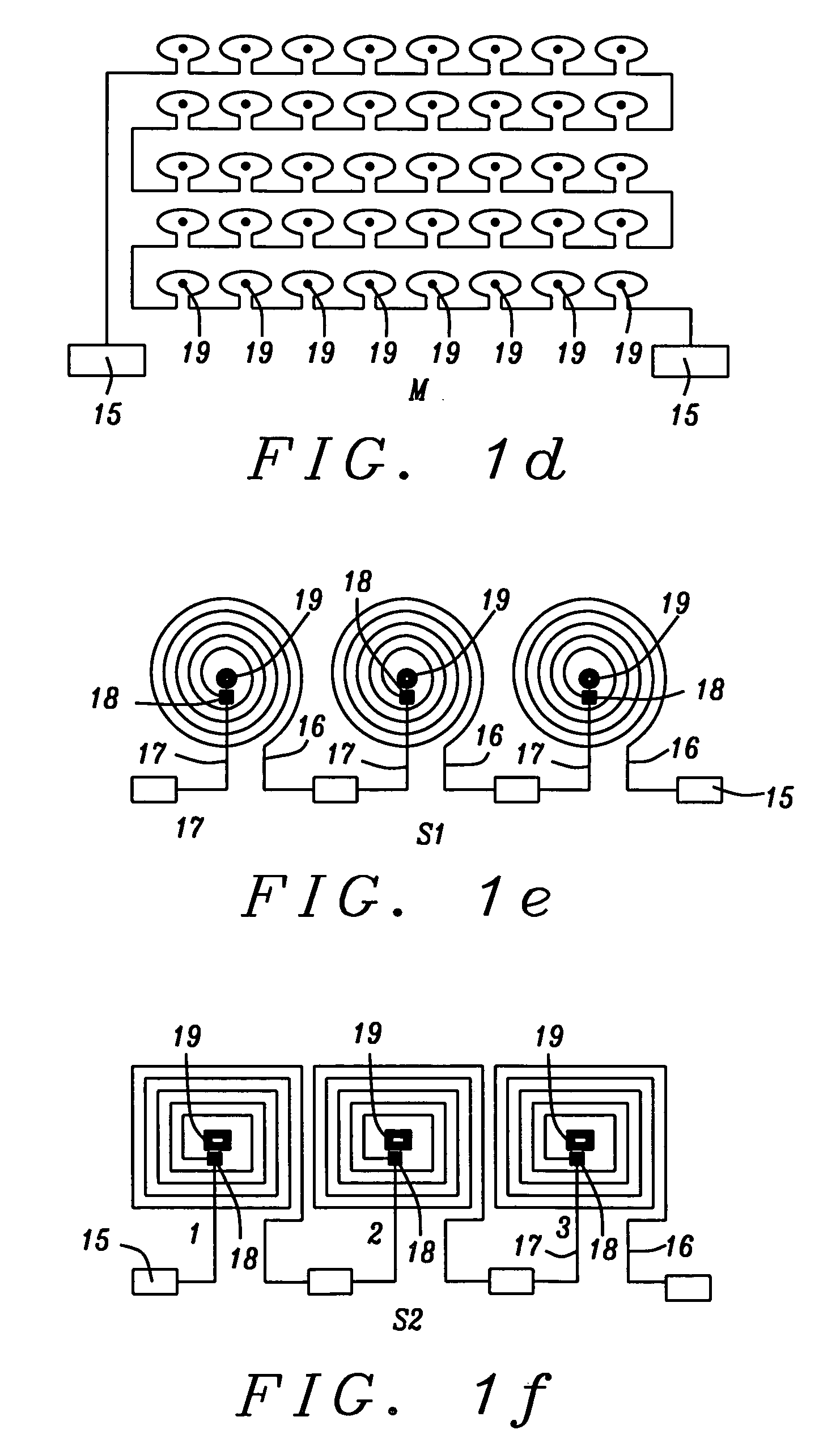

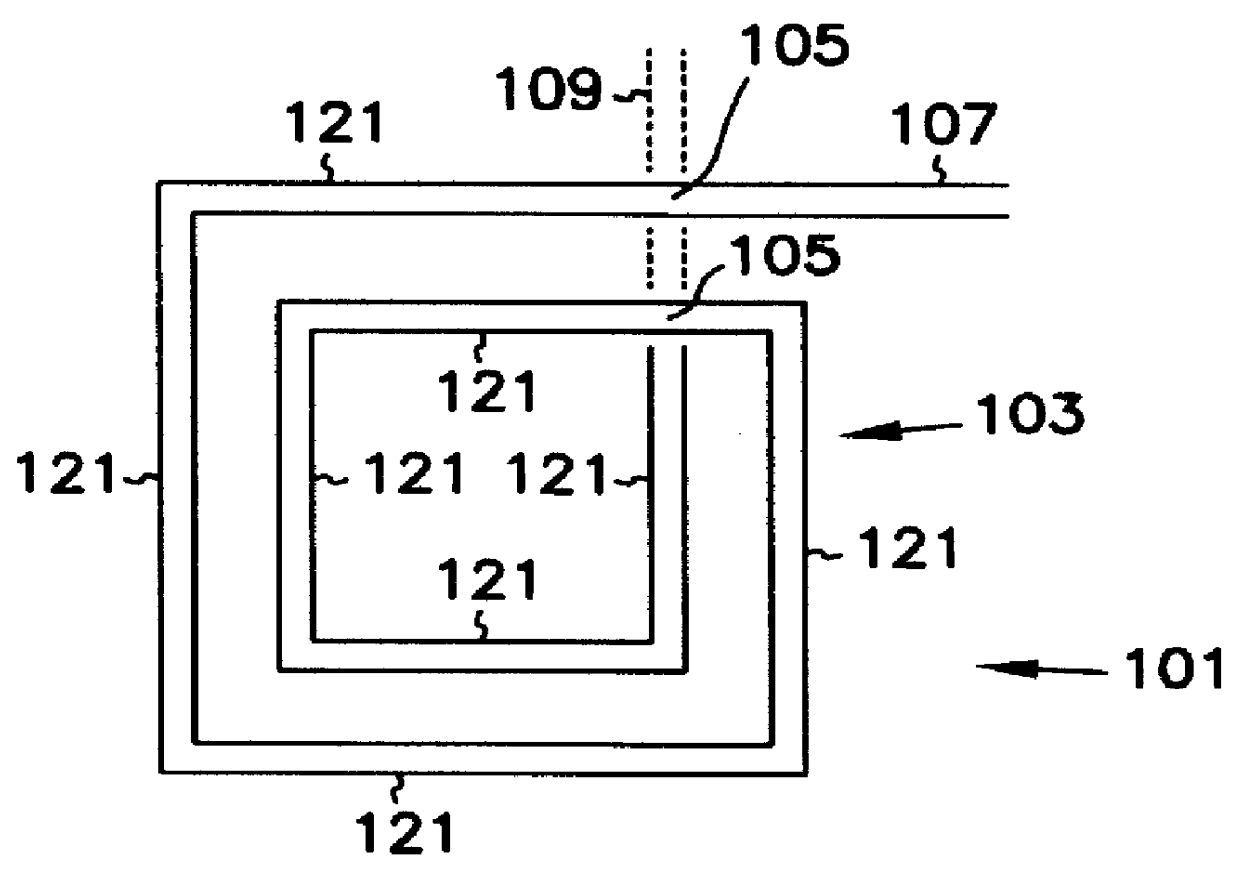

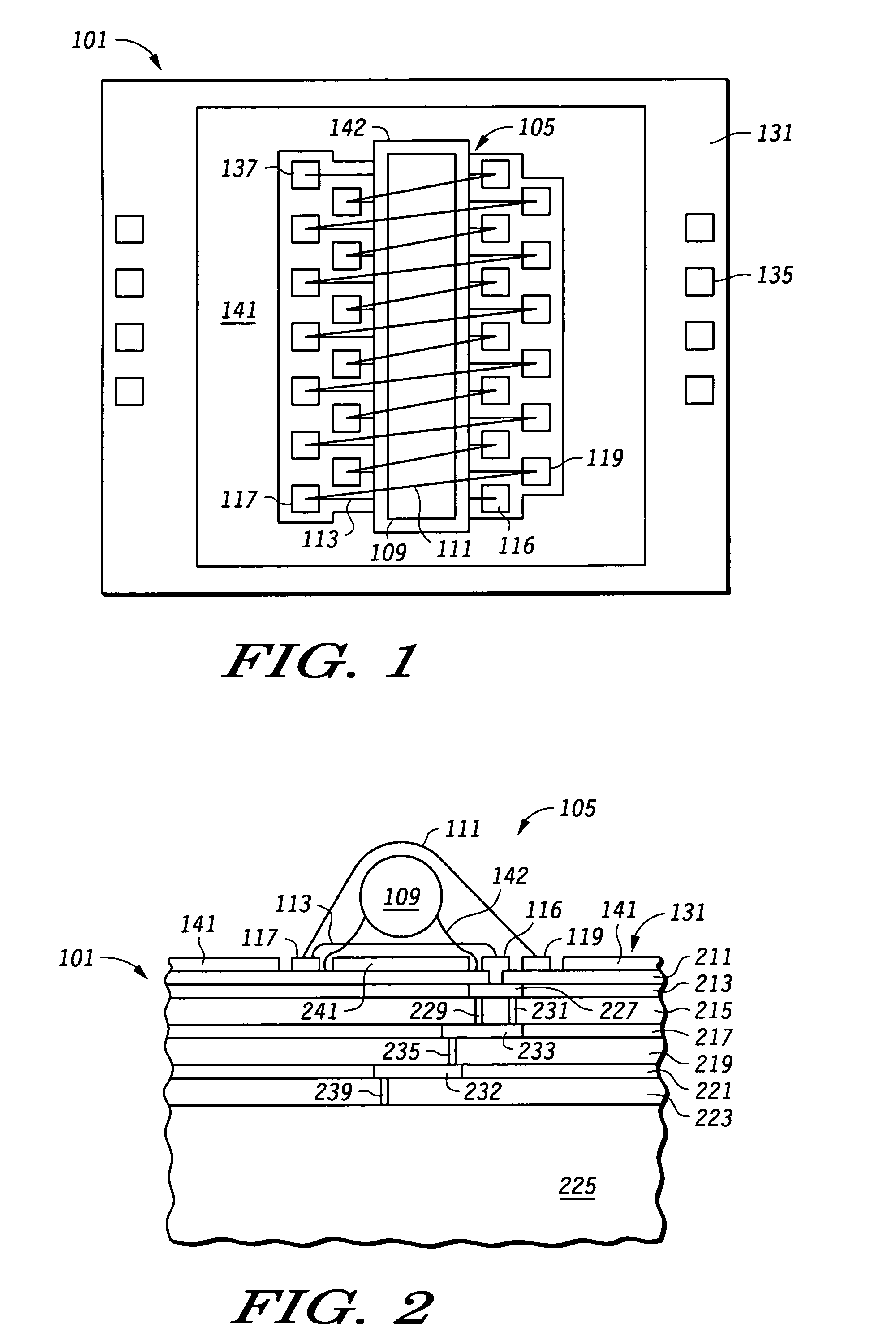

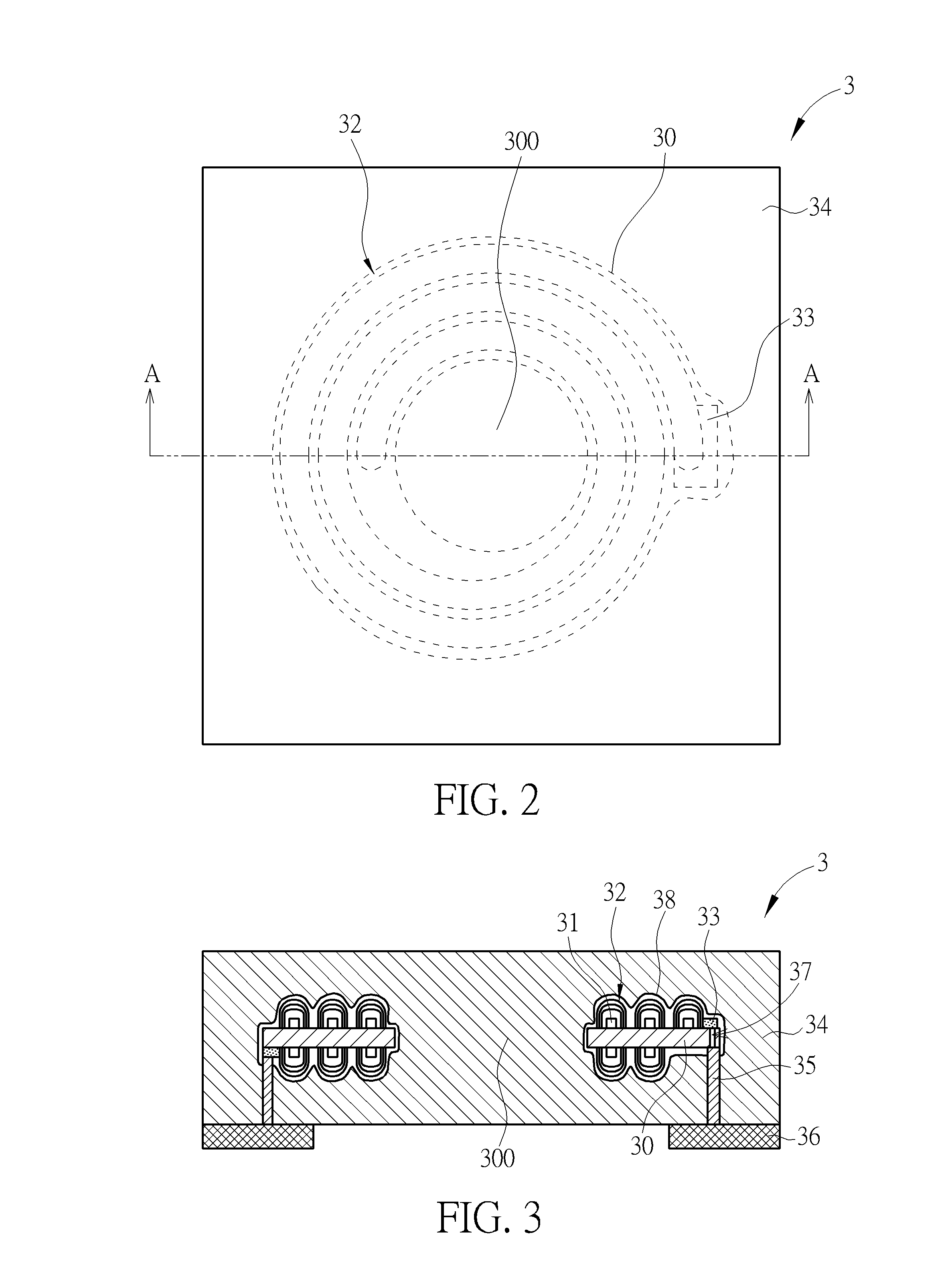

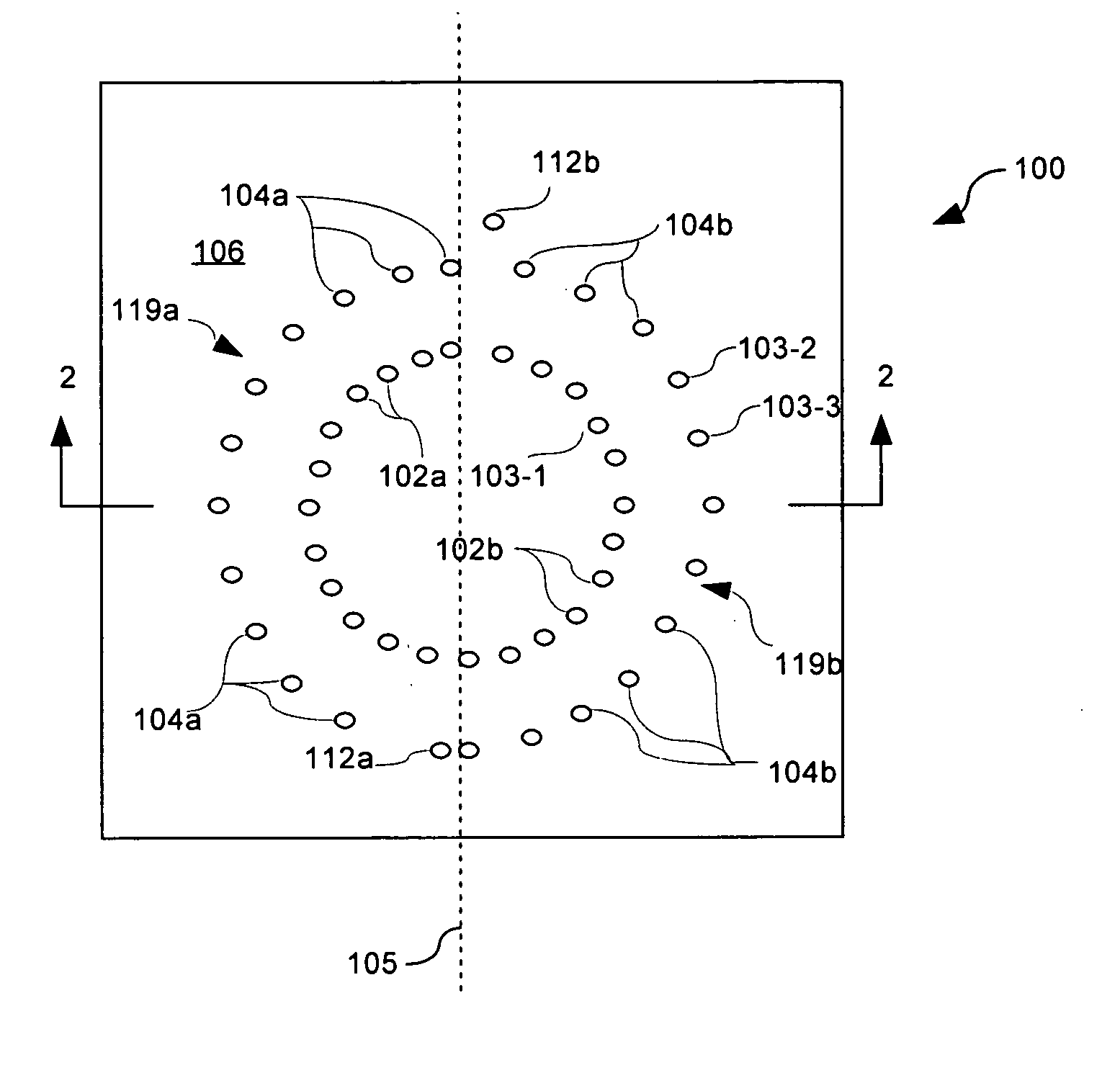

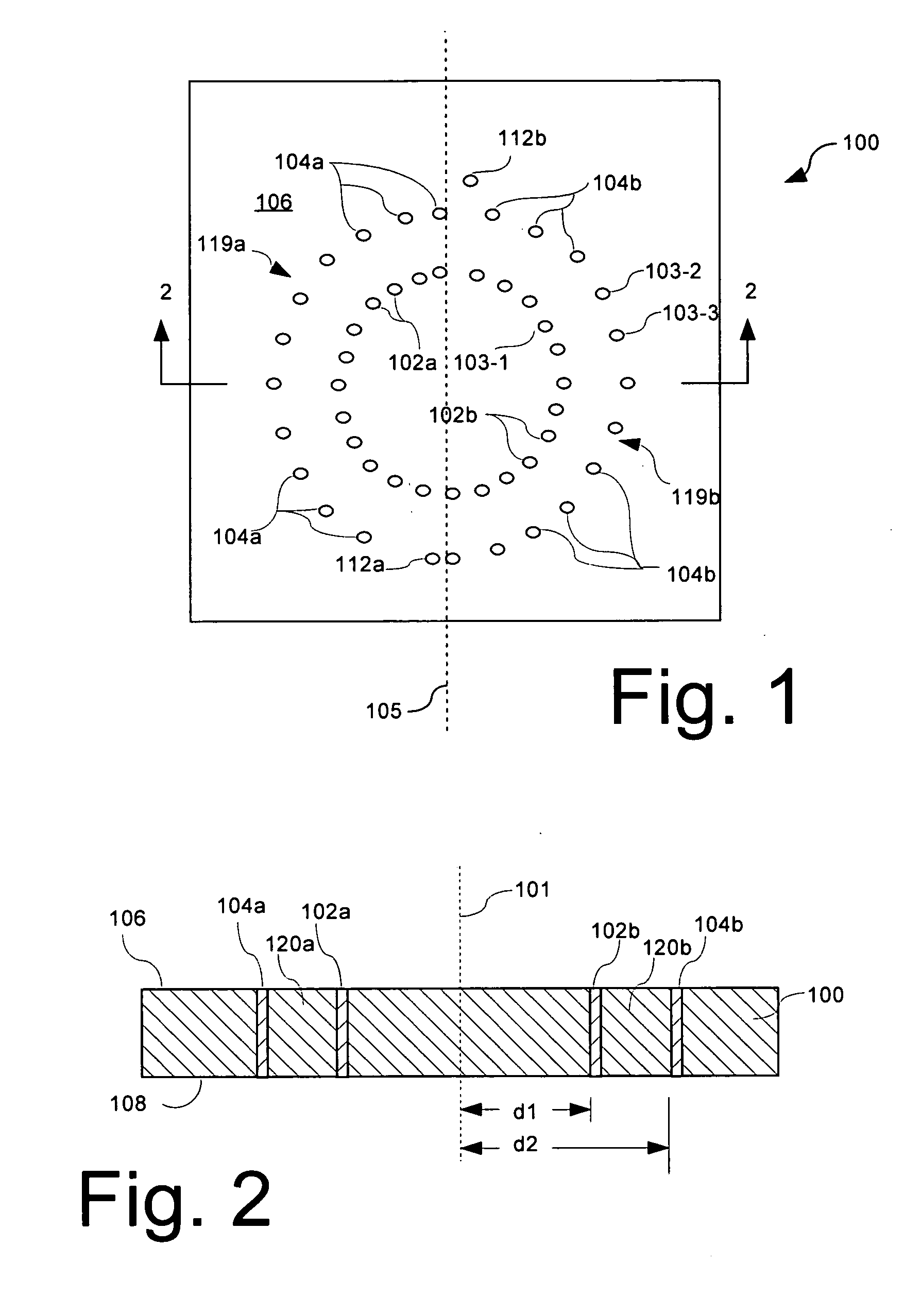

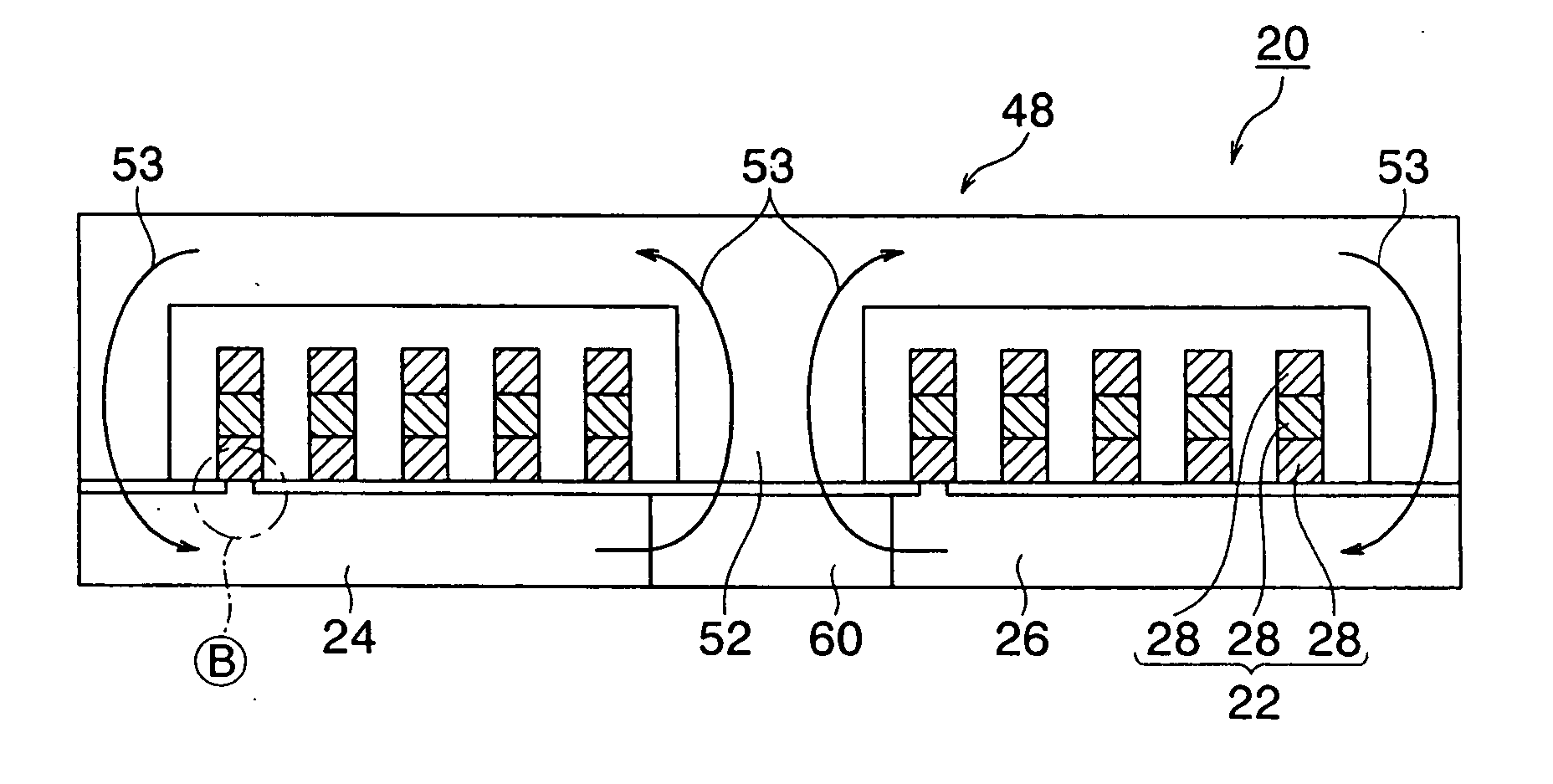

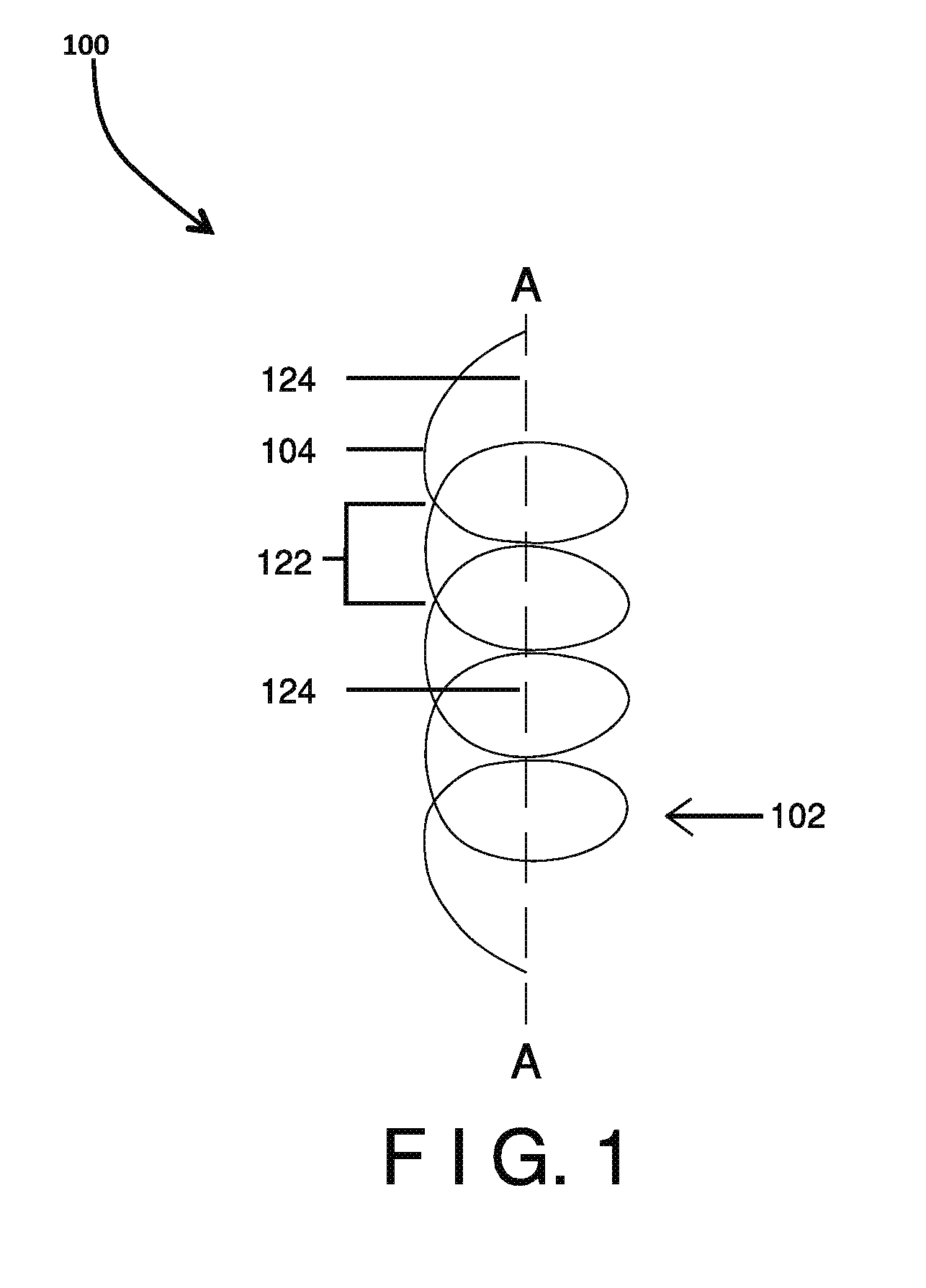

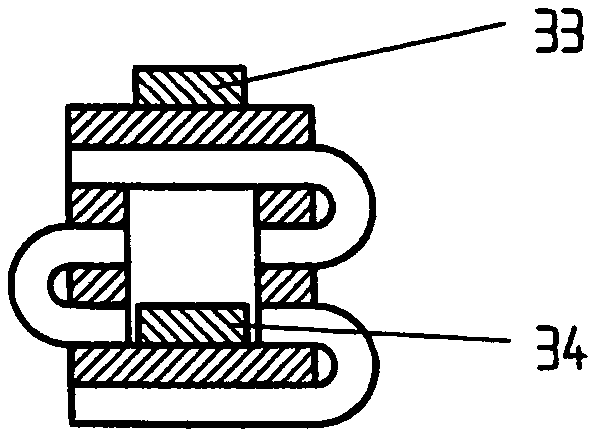

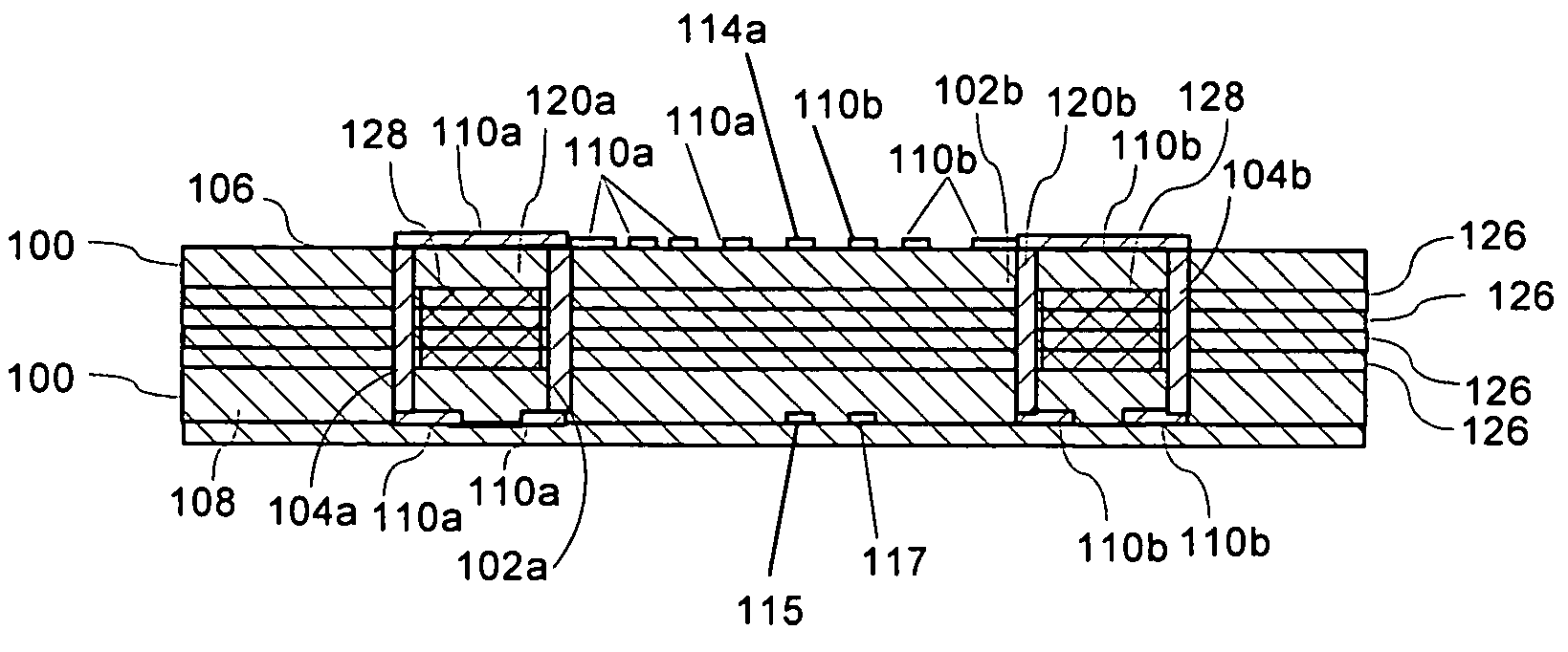

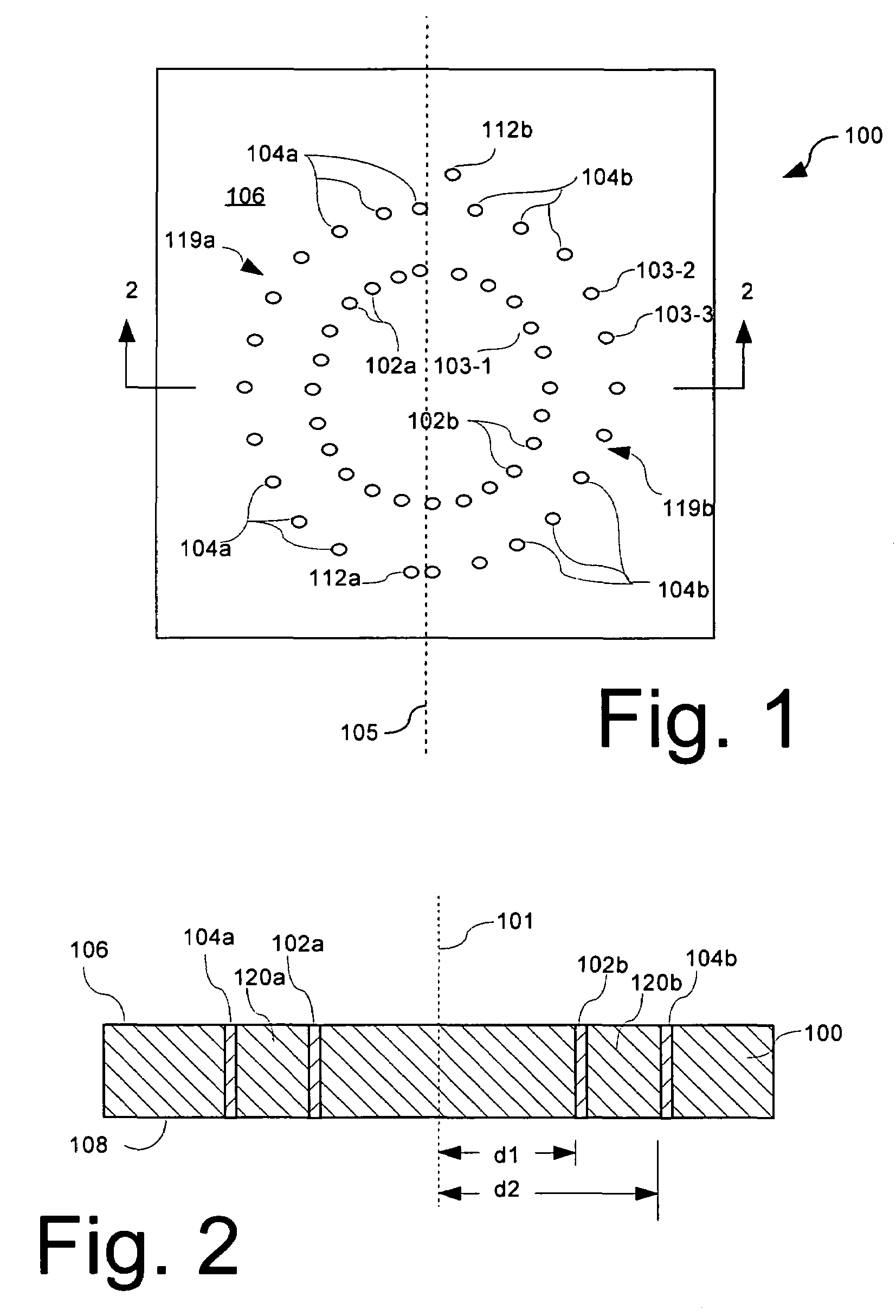

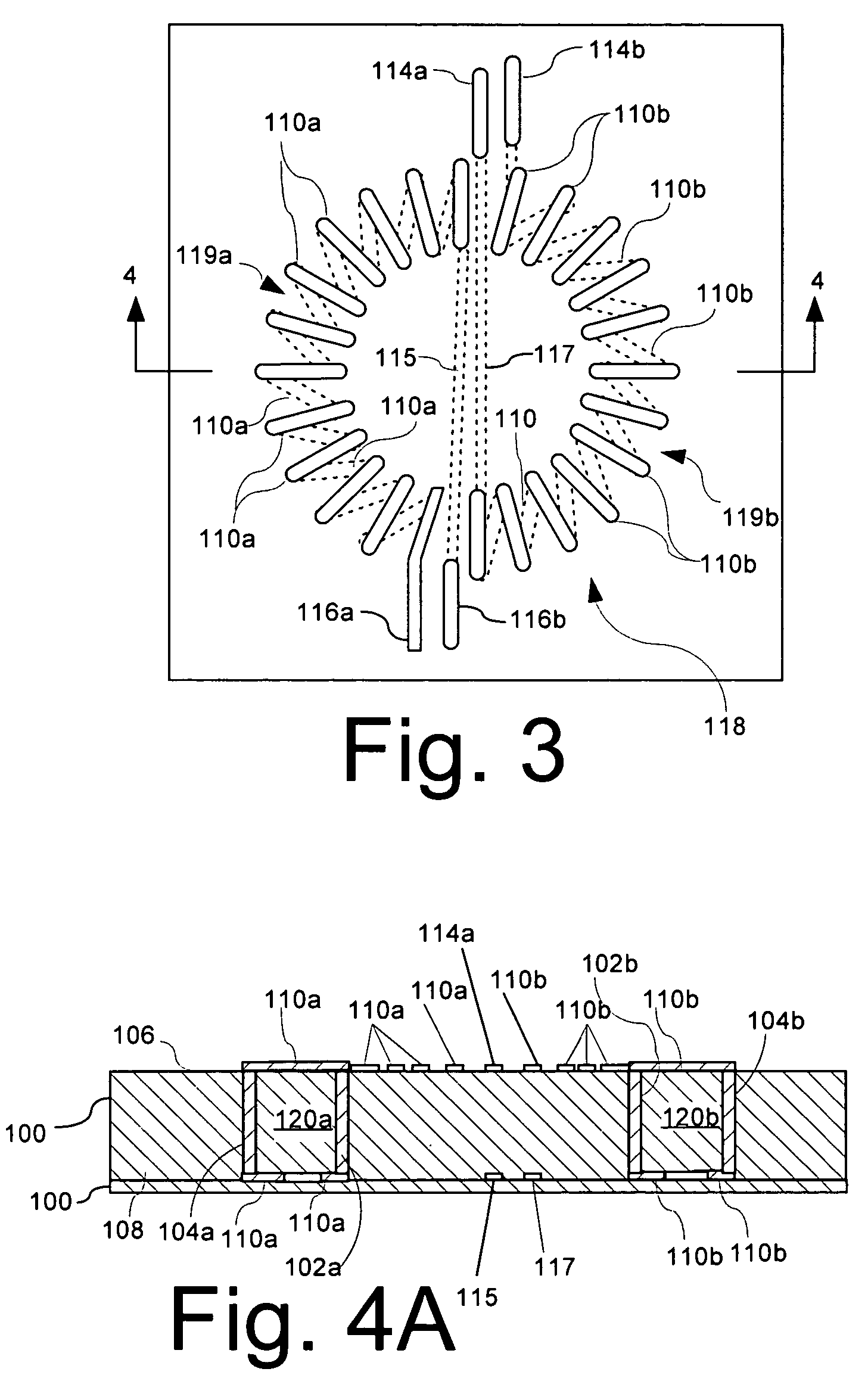

Embedded toroidal transformers in ceramic substrates

ActiveUS20050212642A1Semiconductor/solid-state device detailsTransformers/inductances coils/windings/connectionsMetallurgyTransformer

Method for forming a transformer (118) in a ceramic substrate. The method can include the steps of forming at least one conductive coil (119a, 119b) comprising a plurality of turns about an unfired ceramic toroidal core region (120a, 120b) defined within an unfired ceramic substrate (100). The method can also include the step of co-firing the unfired ceramic toroidal core region (120a, 120b), the unfired ceramic substrate (100), and the conductive coil (119a, 119b) to form an integral ceramic substrate structure with the conductive coil at least partially embedded therein.

Owner:HARRIS CORP

Methods for fabricating three-dimensional all organic interconnect structures

InactiveUS20040000425A1Semiconductor/solid-state device detailsSolid-state devicesLiquid crystallineAdhesive

The present invention comprises methods for making three-dimensional (3-D) liquid crystalline polymer (LCP) interconnect structures using a high temperature singe sided liquid crystalline polymer, and low temperature single sided liquid crystalline polymer, whereas both the high temperature LCP and the low temperature LCP are drilled using a laser or mechanical drill or mechanically punch to form a z-axis connection. The single sided Conductive layer is used as a bus layer to form z axis conductive stud conductive stud within the high temperature and low temperature LCP, followed by deposition of a metallic capping layer of the stud that serves as the bonding metal between the conductive interconnects to form the z-axis electrical connection. High temperature and low temperature LCP circuit layers are etched or built up to form circuit patterns and subsequently bonded together to form final 3-D multilayer circuit pattern whereas the low temperature LCP melts to form both dielectric to dielectric bond to high temperature LCP circuit layer, and dielectric to conductive bond, whereas, metal to metal bonding occurs with high temperature metal capping layer bonding to conductive metal layer. The resultant structure is then packaged using two metallized organic cores that are laminated onto either side of the device using a low temperature adhesive with similar electrical properties and subsequently metallized to form the input output terminals and EM shielding.

Owner:GEORGIA TECH RES CORP

High density inductor and method for producing same

InactiveUS20040164835A1Reduce core sizeAccurate shapeTransformers/inductances coils/windings/connectionsSolid-state devicesHigh densityInductor

A method for producing a high density inductor includes the steps of forming a coil having a spiral shape, sealing the coil in the interior of a core member, and forming a terminal electrode for allowing electric conduction to said coil on the outside of said core member. In this method, the coil is formed by repeating a process of forming a wire layer by means of a thin film forming process and a process of forming an additional wire layer on top of the wire layer by means of the thin film forming process to pile up the wire layers. With this production method, it is possible to form a coil with a high aspect ratio. In addition, the inductor is designed in such a way that the core member envelopes only the coil. With that design, it is possible to make the inductor compact.

Owner:TDK CORPARATION

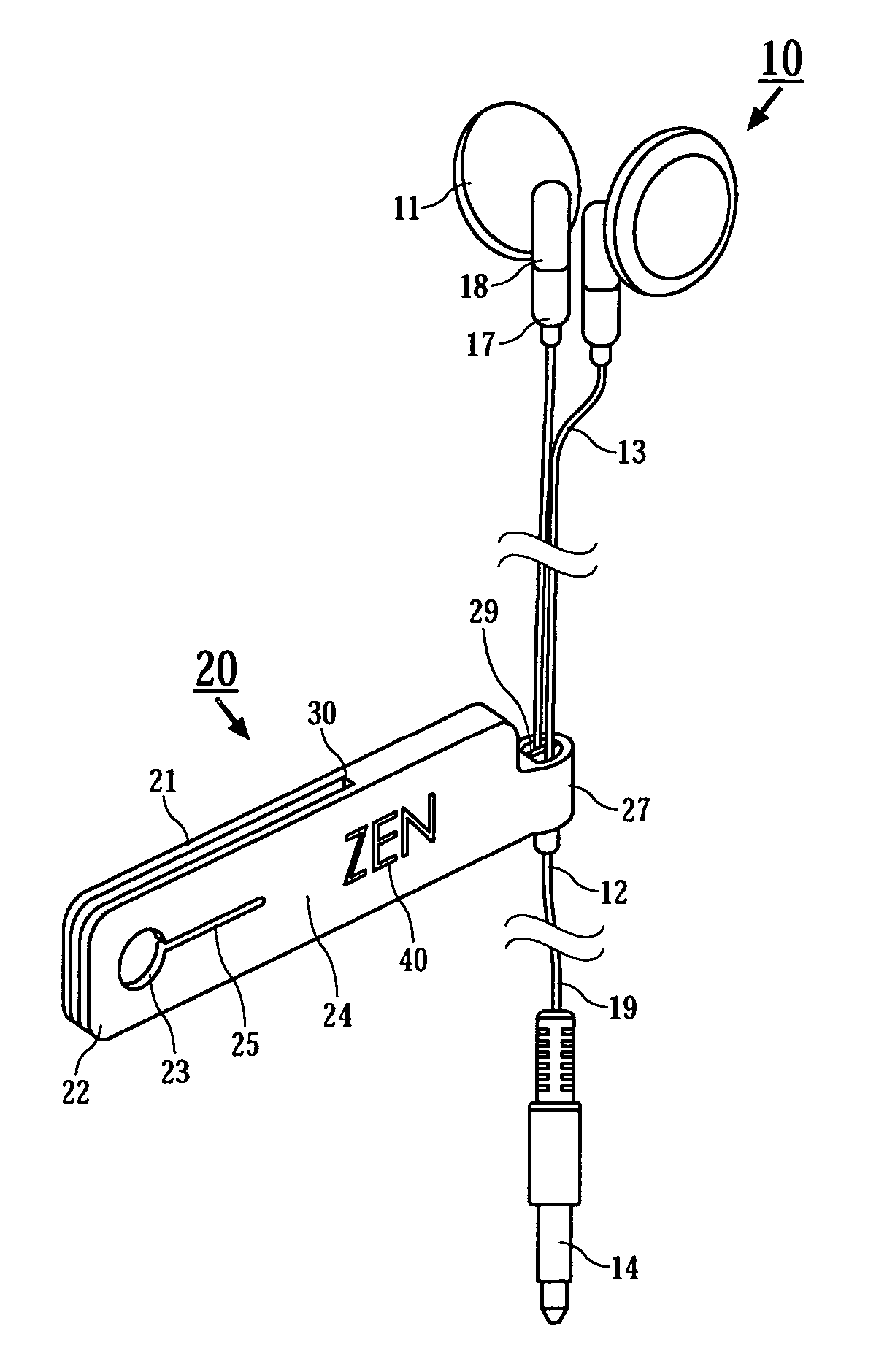

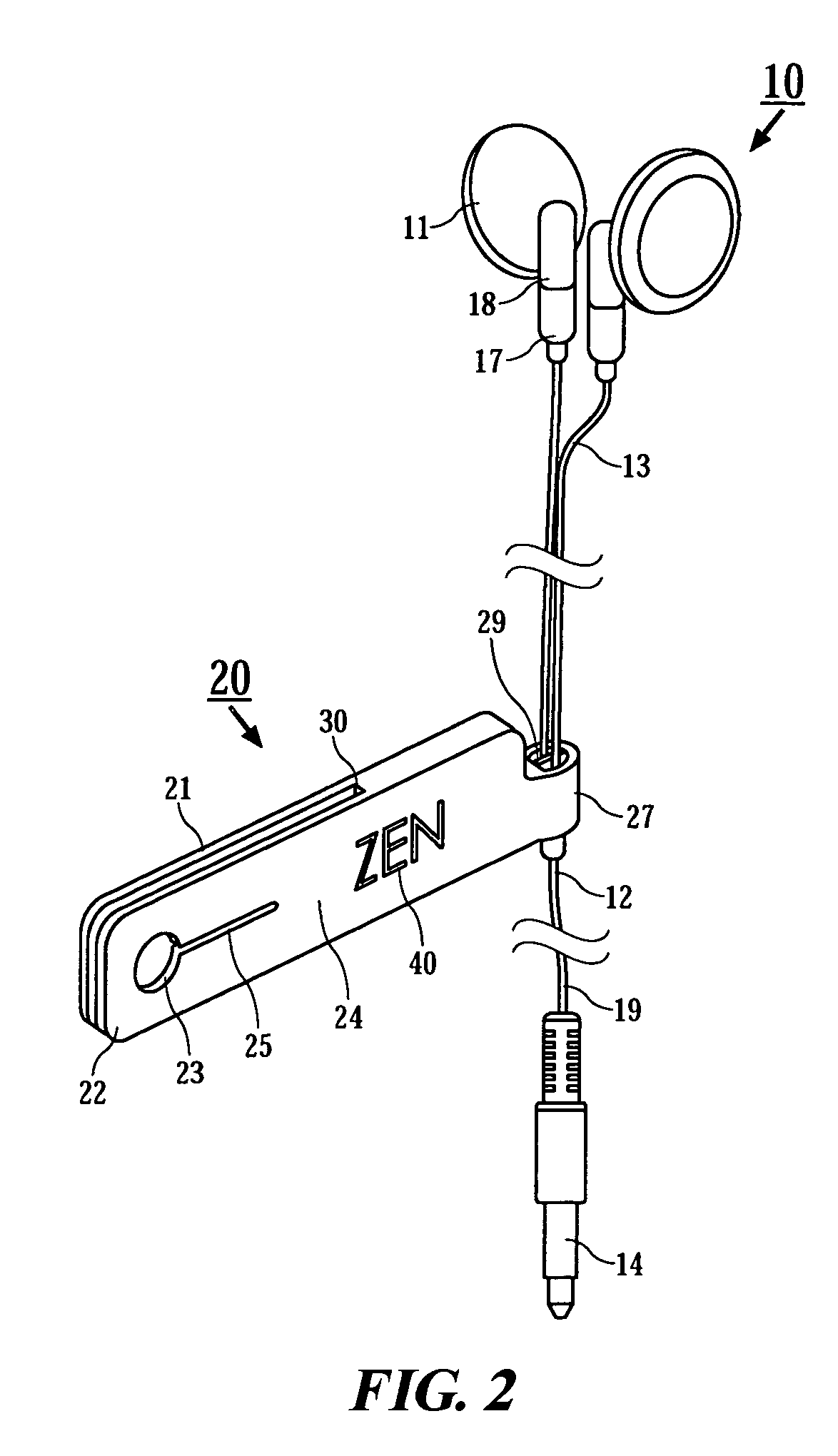

Cable coiling method and apparatus

Owner:CREATIVE TECH CORP

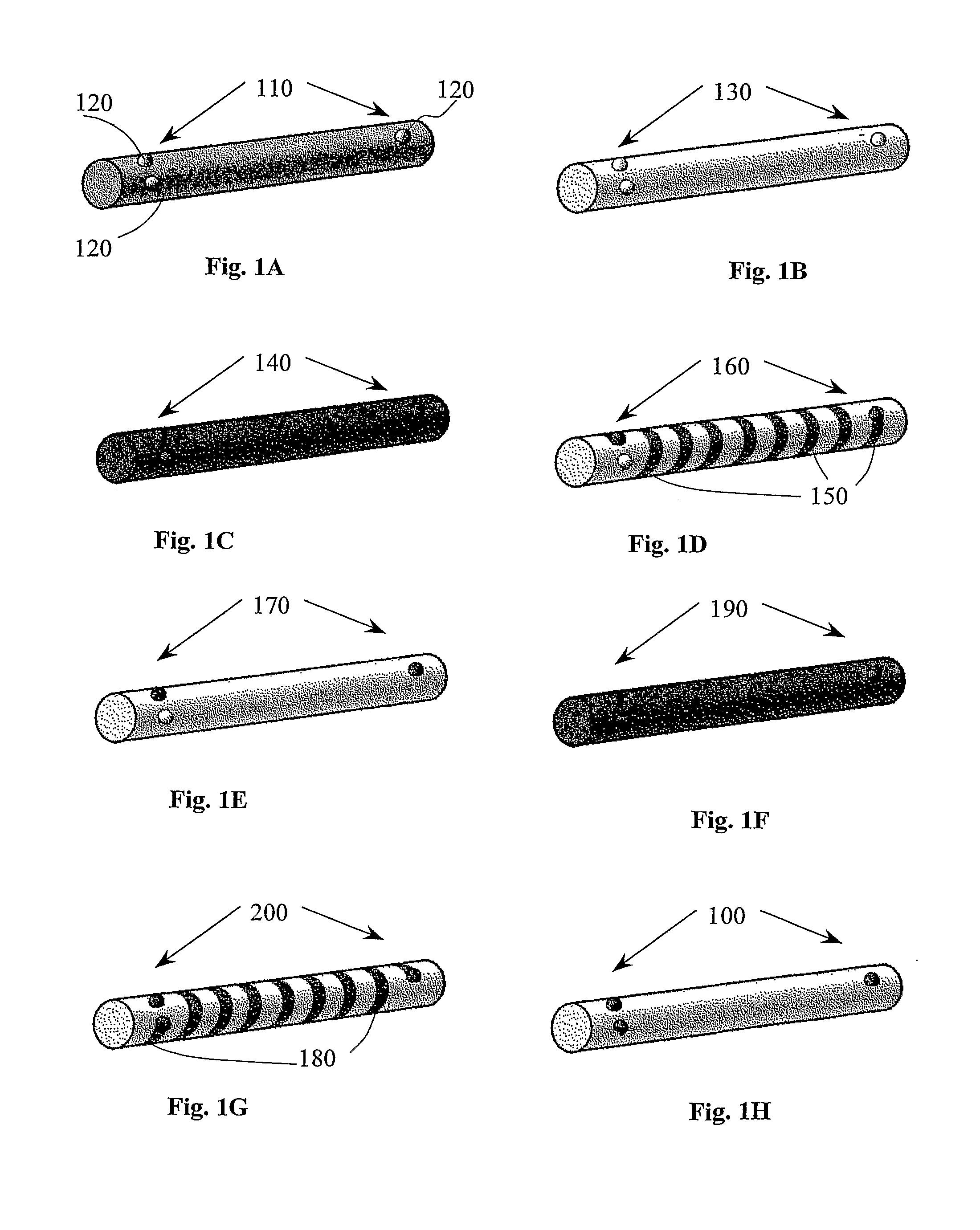

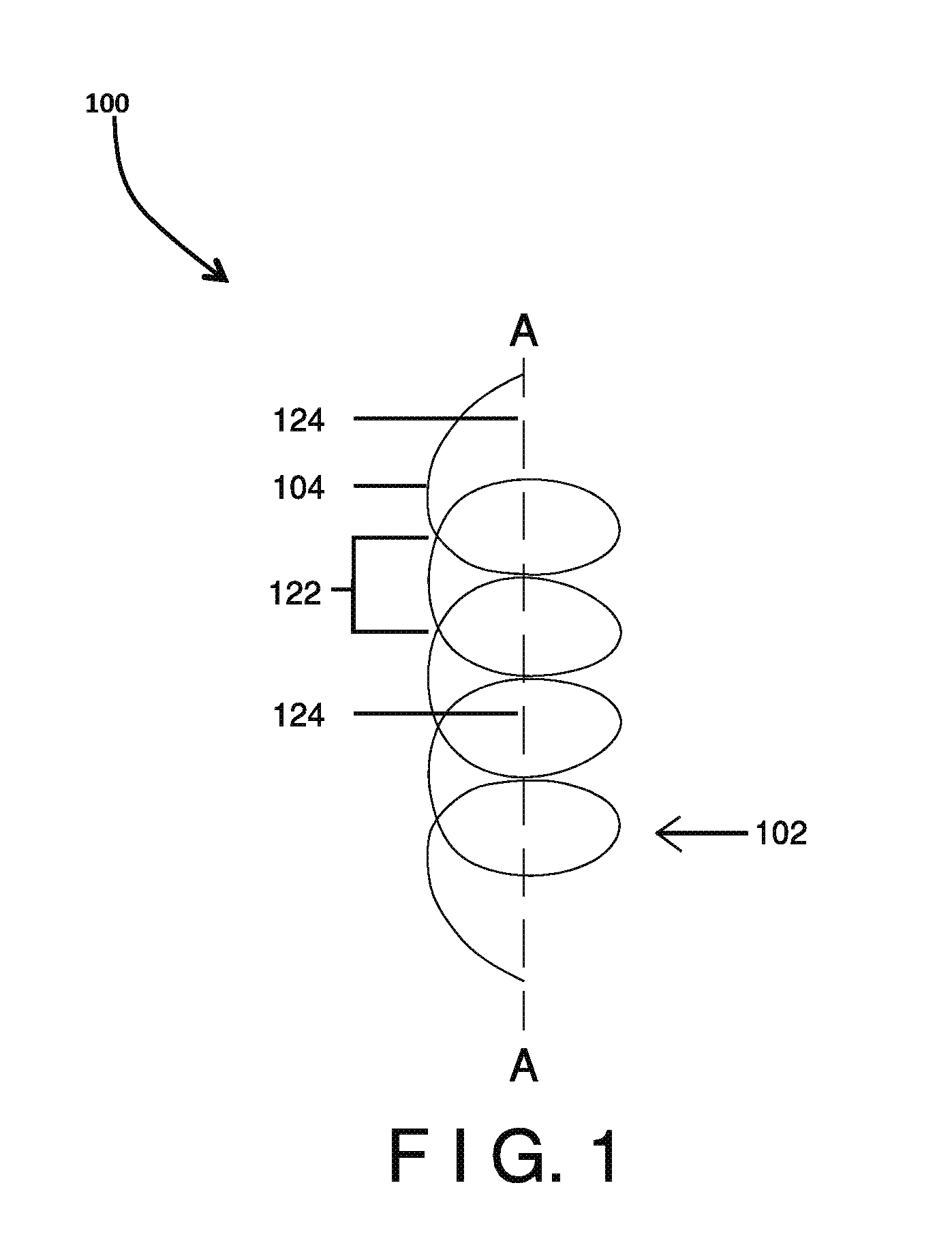

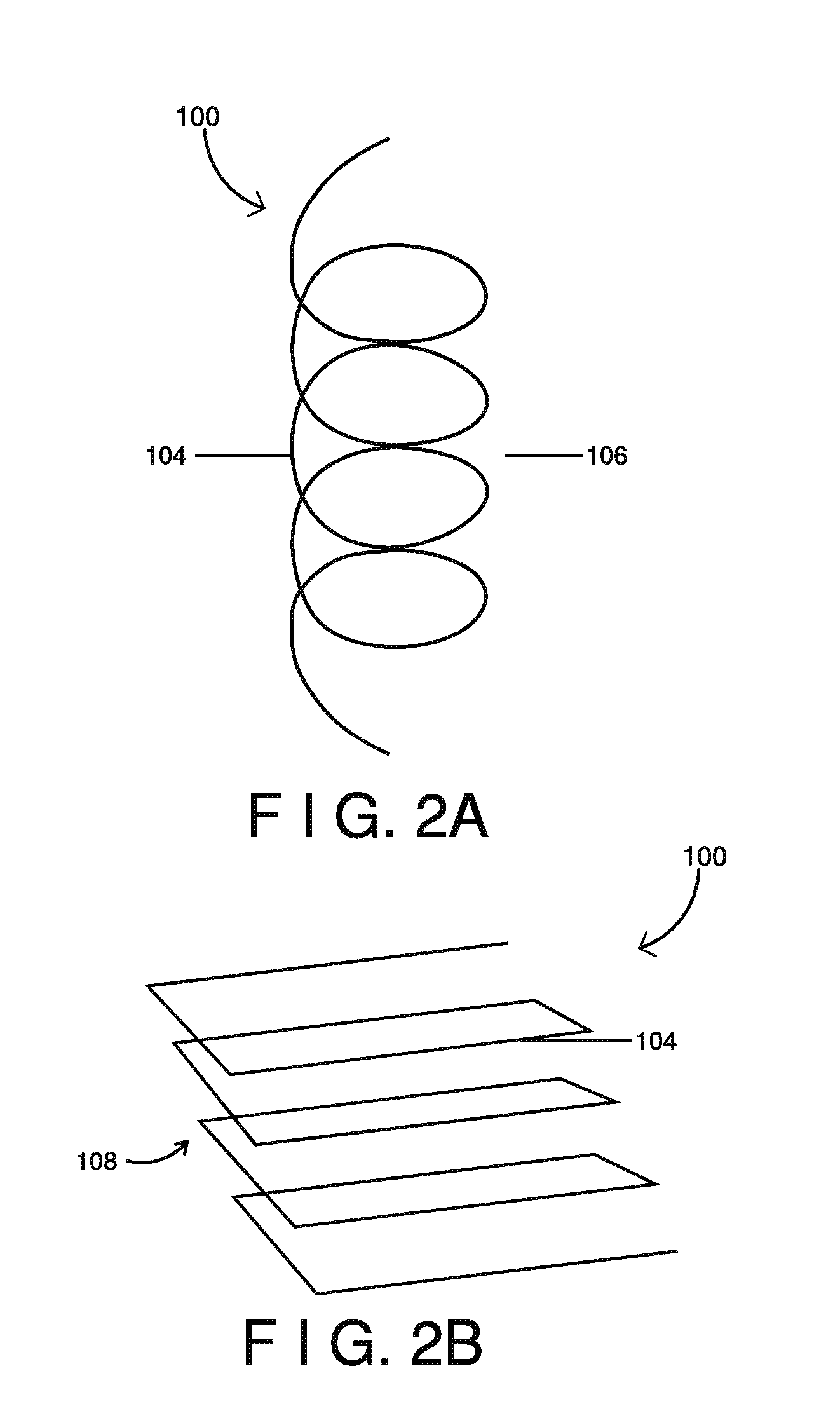

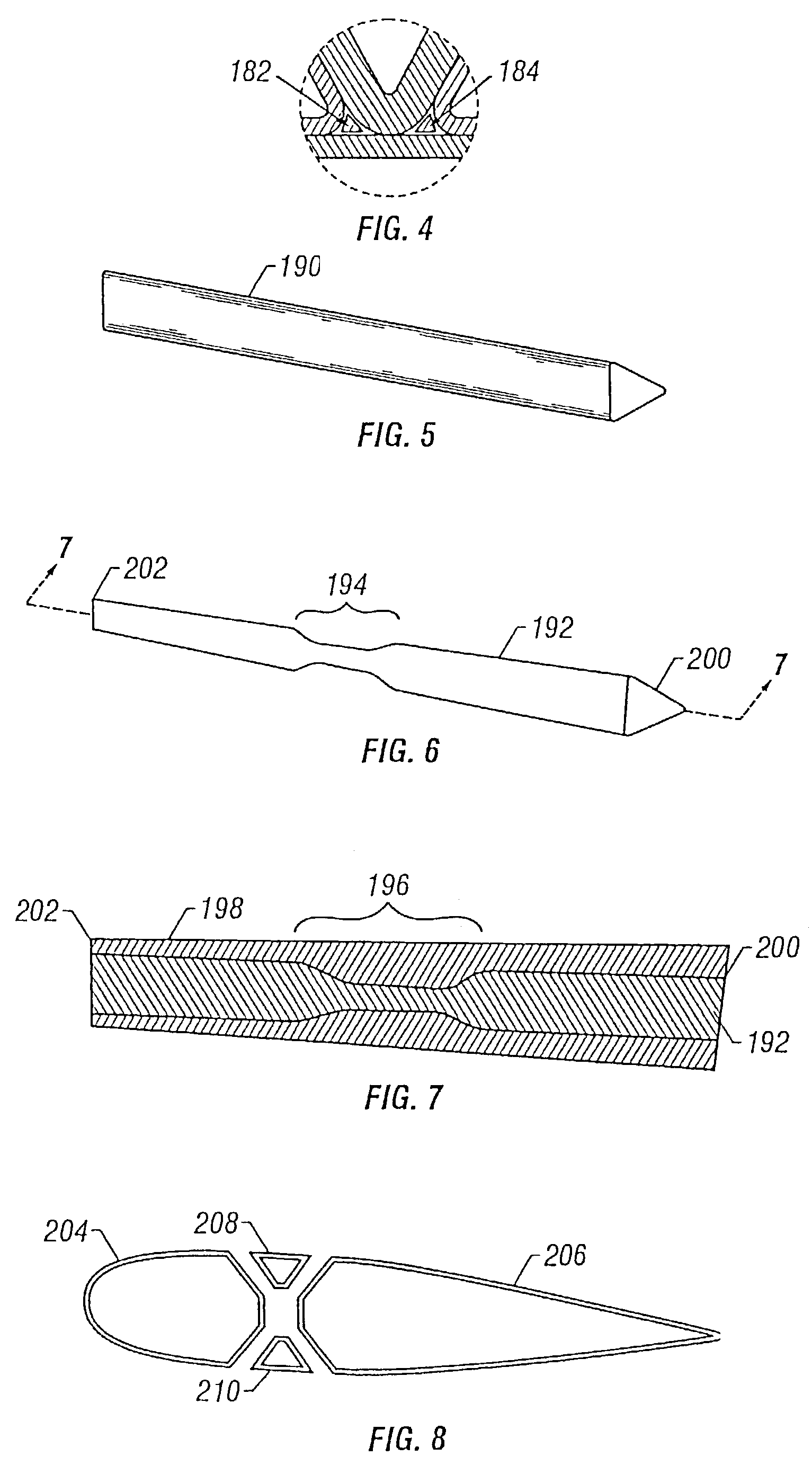

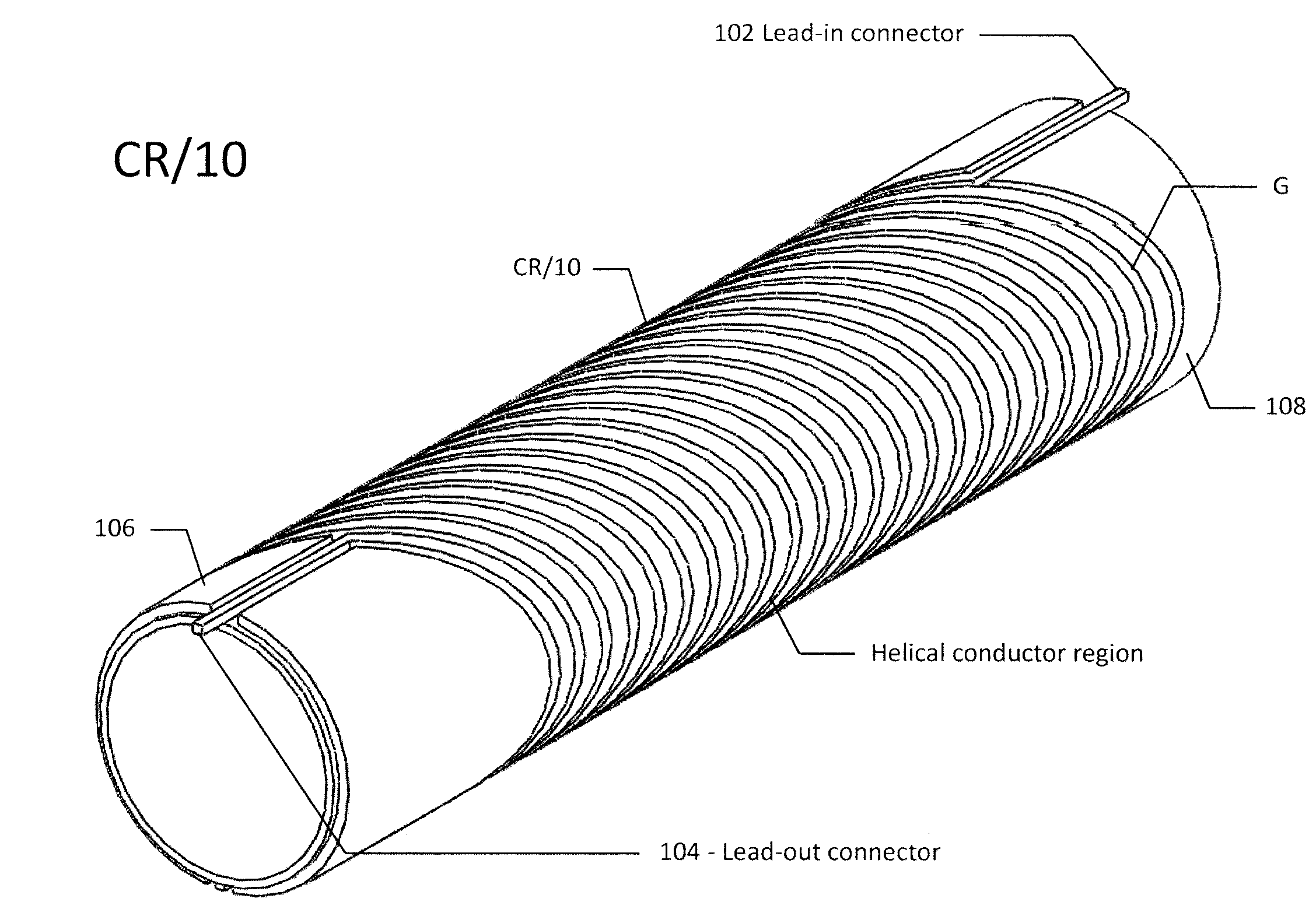

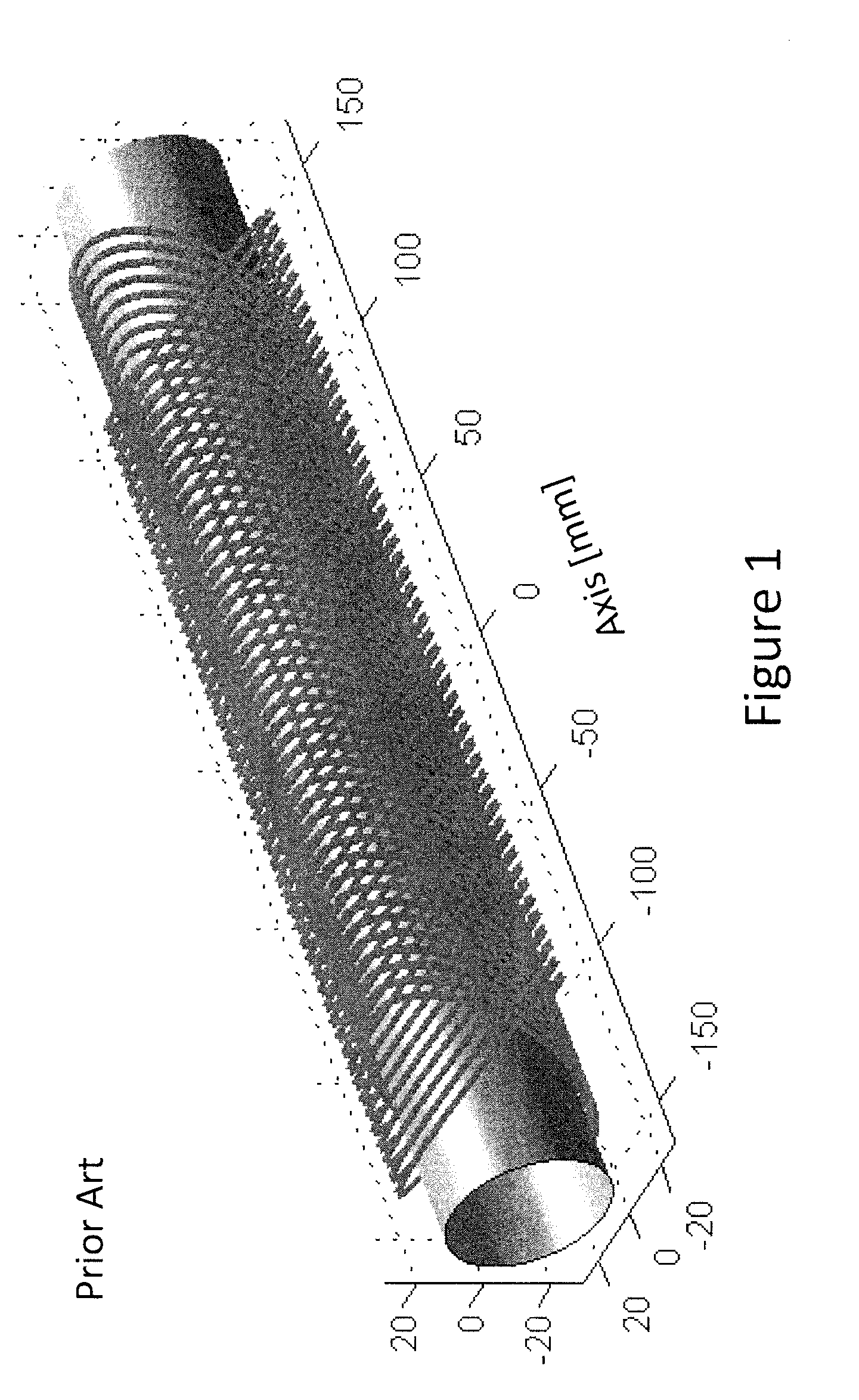

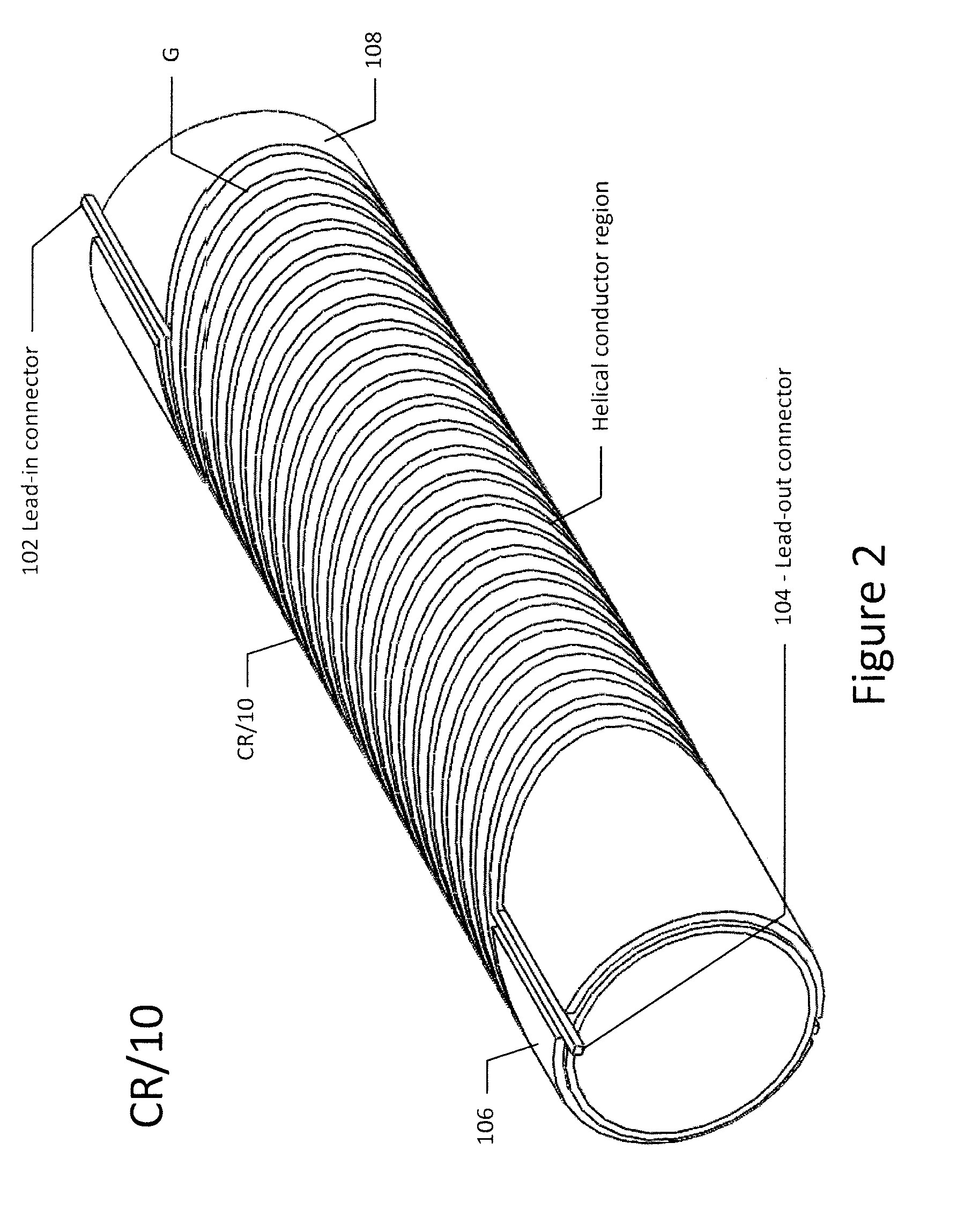

Helical Coil Design and Process For Direct Fabrication From A Conductive Layer

InactiveUS20090206974A1Reduce resistanceOptimize field shapeTransformers/inductances coils/windings/connectionsCoils manufactureElectrical conductorHelical coil

A conductor assembly of the type which, when conducting current, generates a magnetic field or in which, in the presence of a changing magnetic field, a voltage is induced. According to an exemplary embodiment a conductor is positioned along a path of variable direction relative to a reference axis. The conductor has a width measurable along an outer surface thereof and along a series of different planes transverse to the path direction. The measured conductor width varies among the different planes. In one example, the conductor path is helical, positioned about the axis between turns of helical spaces, and the conductor width varies as a function of the azimuth angle.

Owner:ADVANCED MAGNET LAB

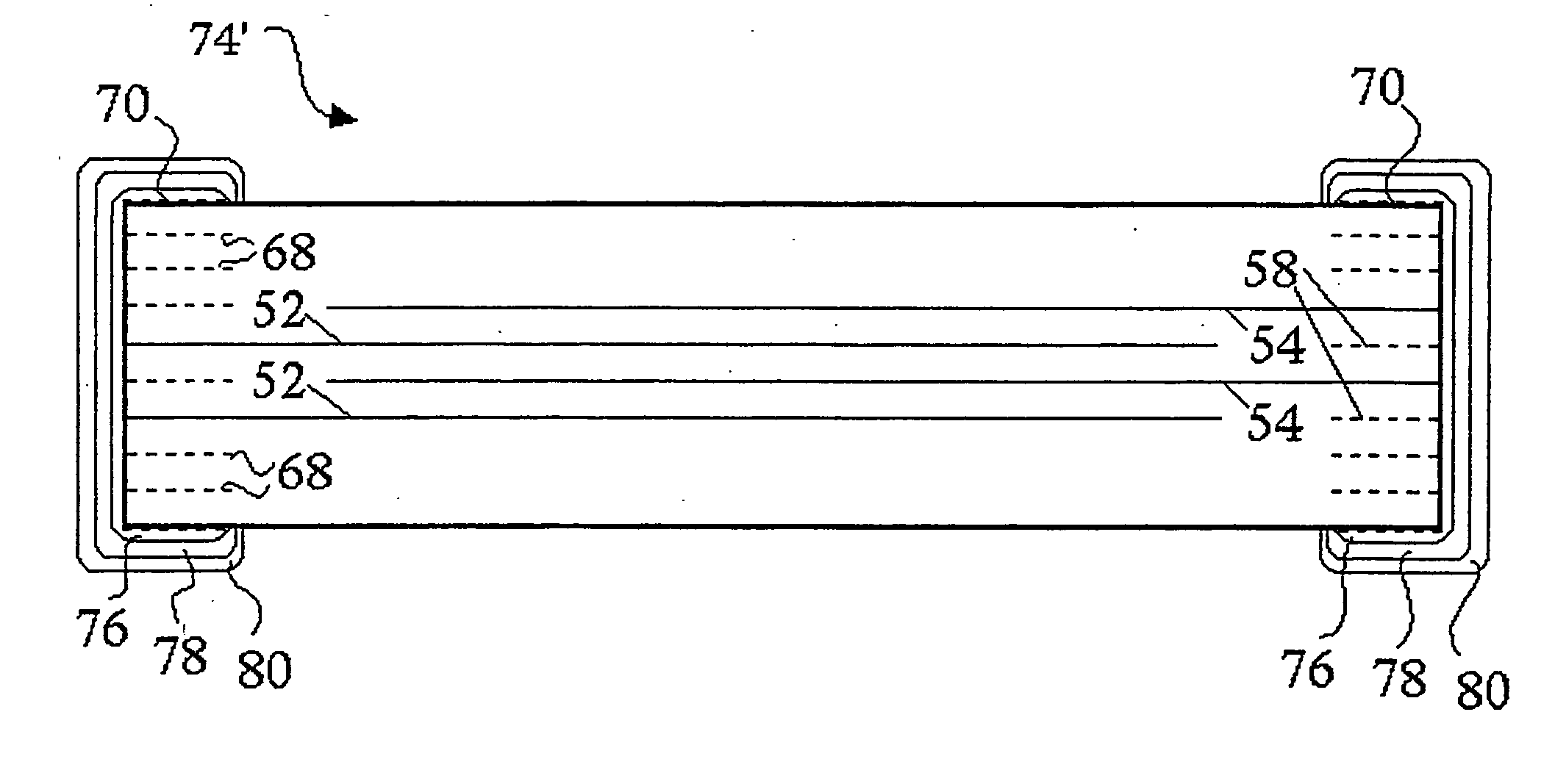

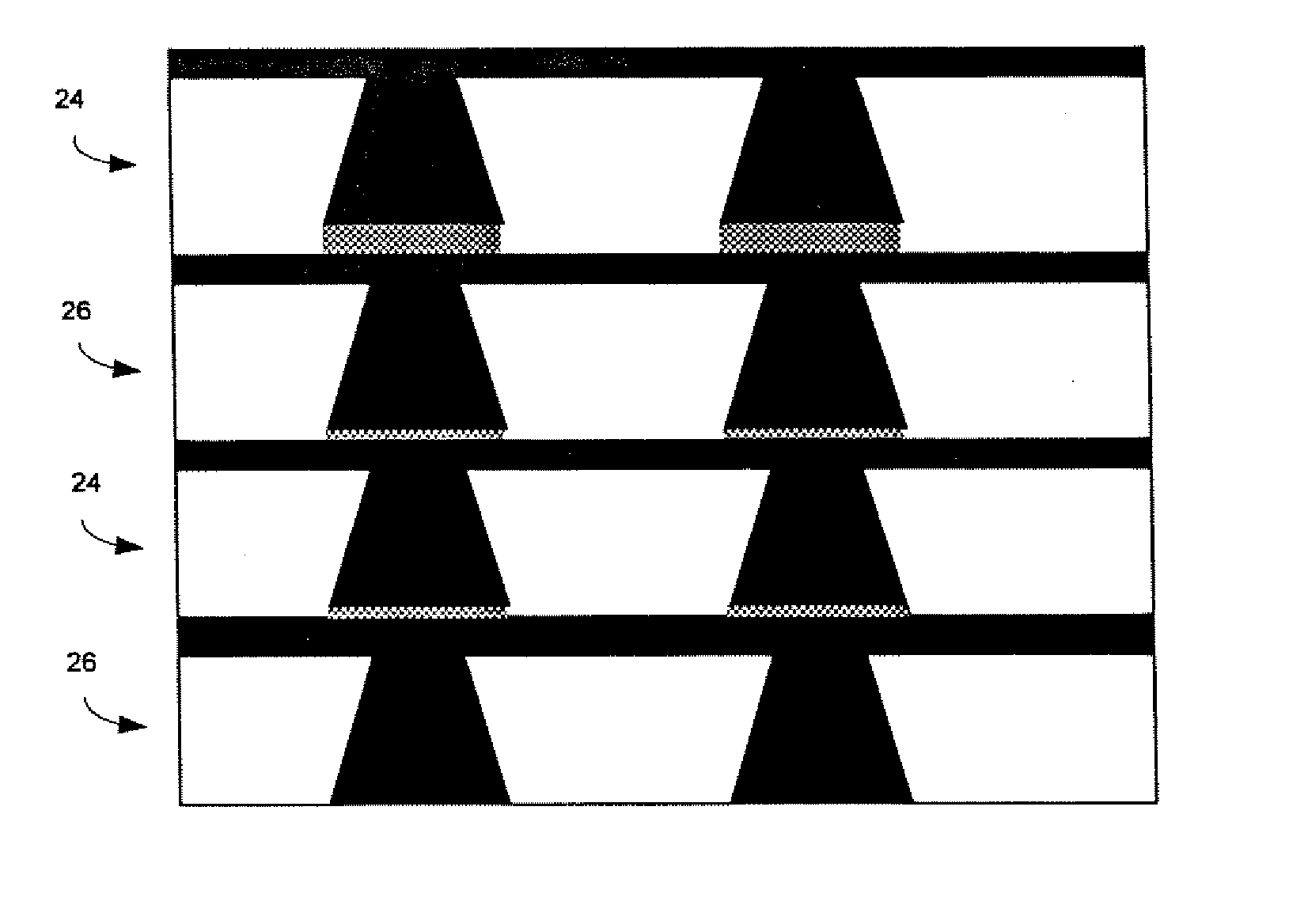

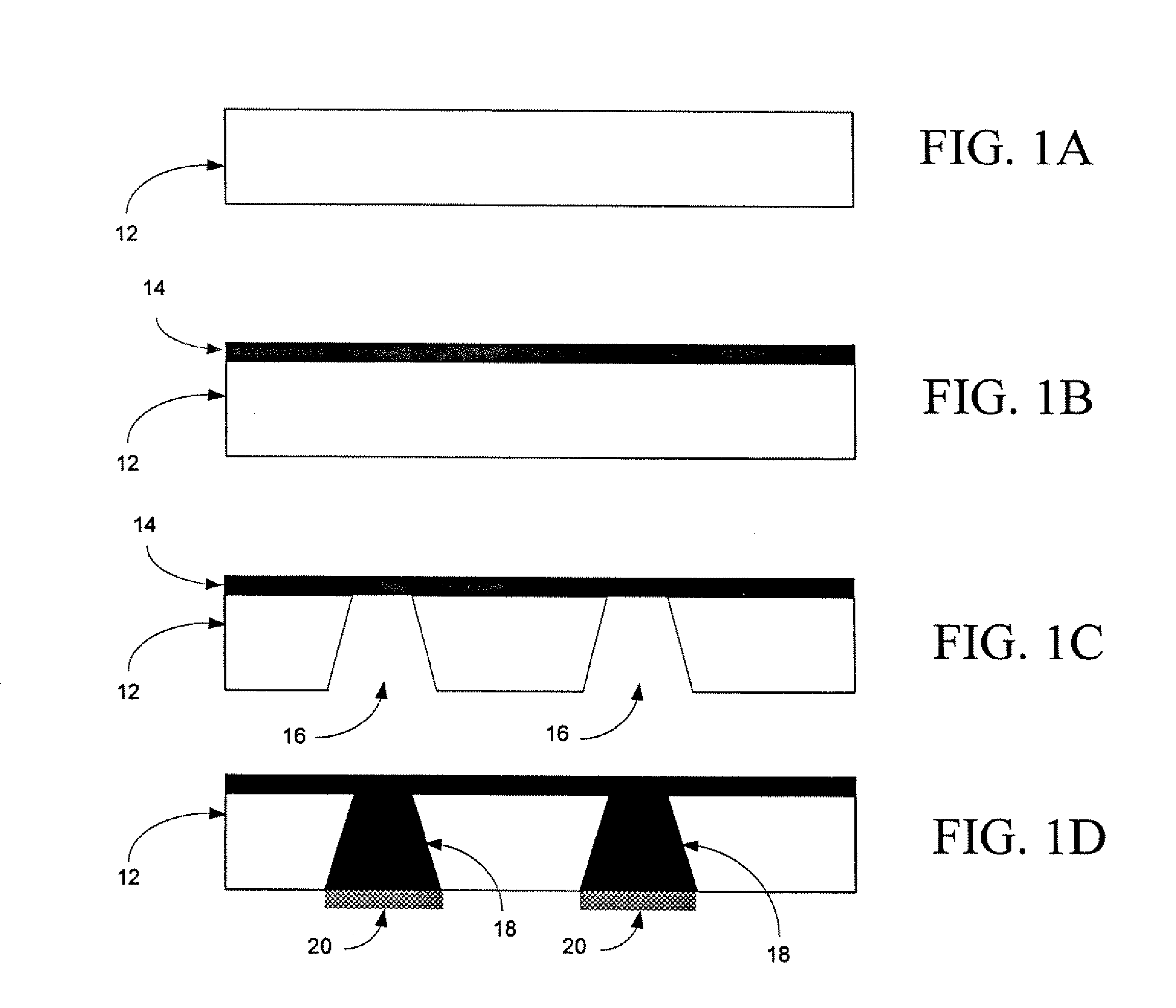

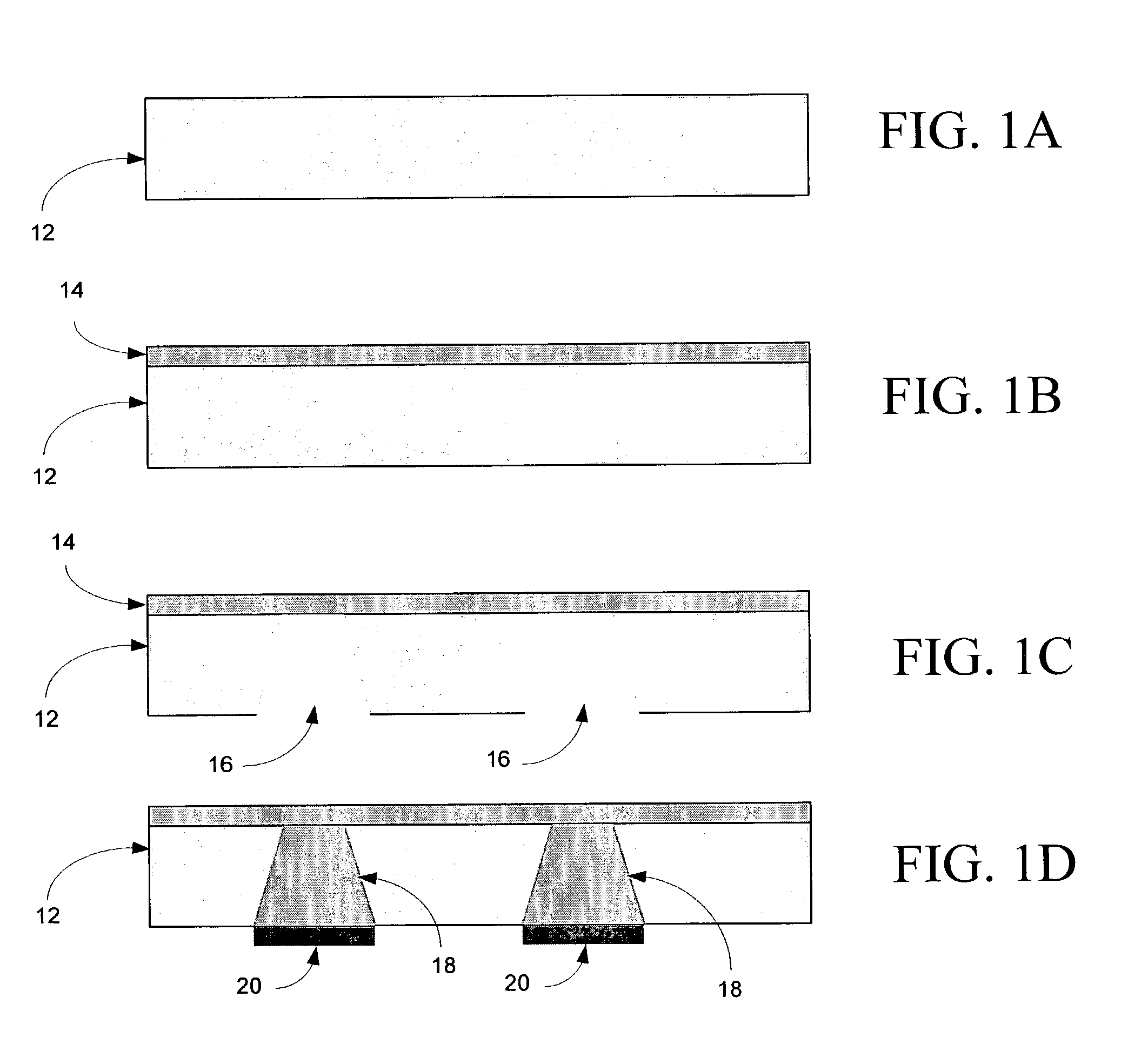

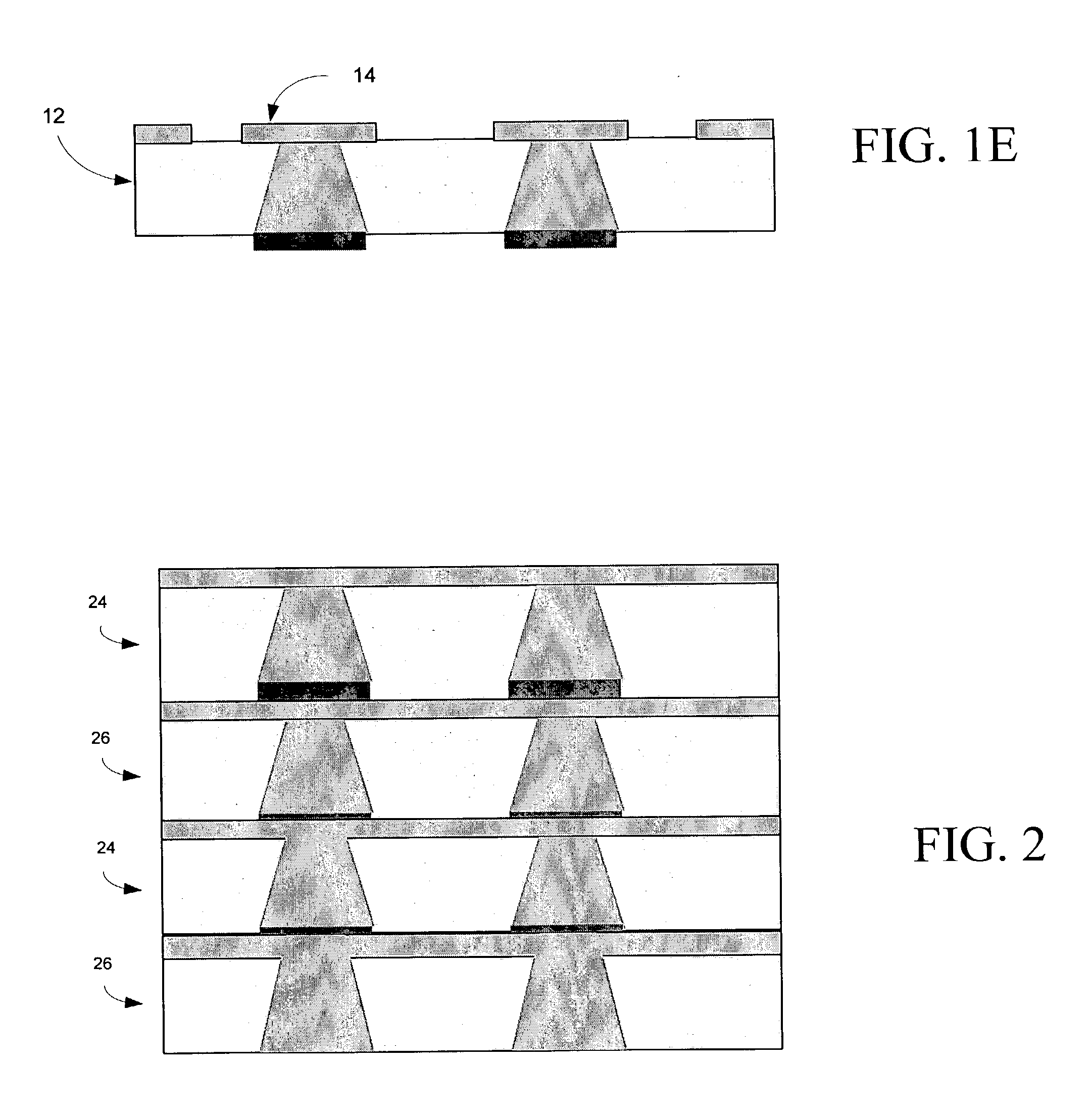

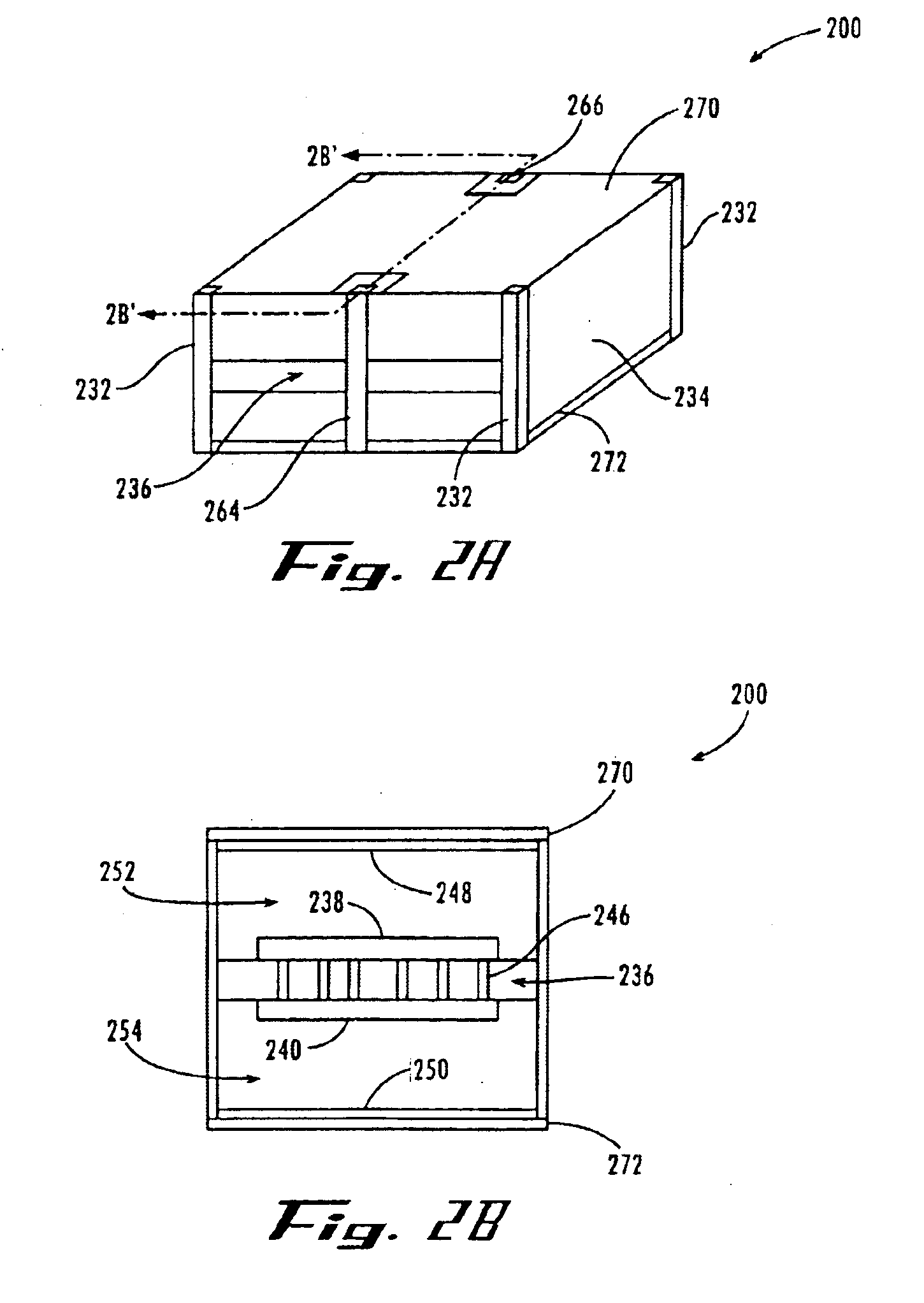

Method for manufacture of multi-layer-multi-turn high efficiency inductors with cavity

ActiveUS20130205582A1Higher resistive lossIncrease qualify factorMultiple-port networksInternal electrodesElectrical resistance and conductanceElectrical conductor

A multi-layer, multi-turn structure for an inductor having a plurality of conductor layers separated by layers of insulator is described. The inductor further comprises a connector electrically connected between the conductor layers. The structure of the inductor may comprise a cavity therewithin. The structure of the inductor constructed such that electrical resistance is reduced therewithin, thus increasing the efficiency of the inductor. The inductor is particularly useful at operating within the radio frequency range and greater.

Owner:NUCURRENT INC

Integrated passive devices fabricated utilizing multi-layer, organic laminates

InactiveUS6900708B2Easy to integrateLow costMultiple-port networksSolid-state devicesSurface mountingBall grid array

The present invention includes an organic device that can be integrated in a multilayer board made of organic material. The passive devices can be integrally fabricated on a circuit board in either surface mount device (SMD) or ball grid array (BGA) form. Alternatively, the passive device can be constructed in a stand alone SMD or BGA / chip scale package (CSP) form to make it mountable on a multilayer board, ceramic carrier or silicon platform in the form of an integrated passive device. The passive device includes side shielding on two sides in the SMD form and four sides in the BGA / CSP form. The side shielding can be external or in-built.

Owner:GEORGIA TECH RES CORP

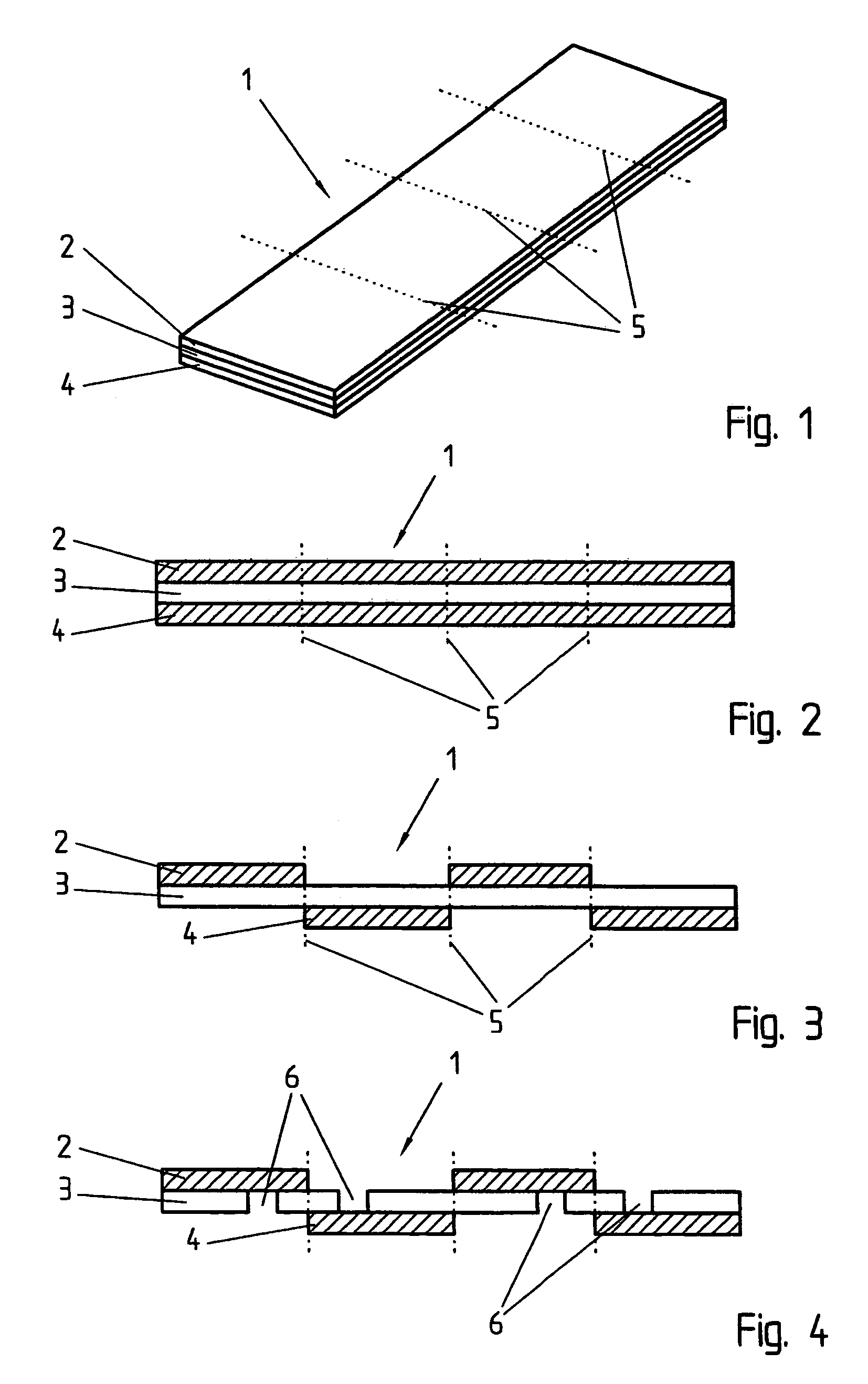

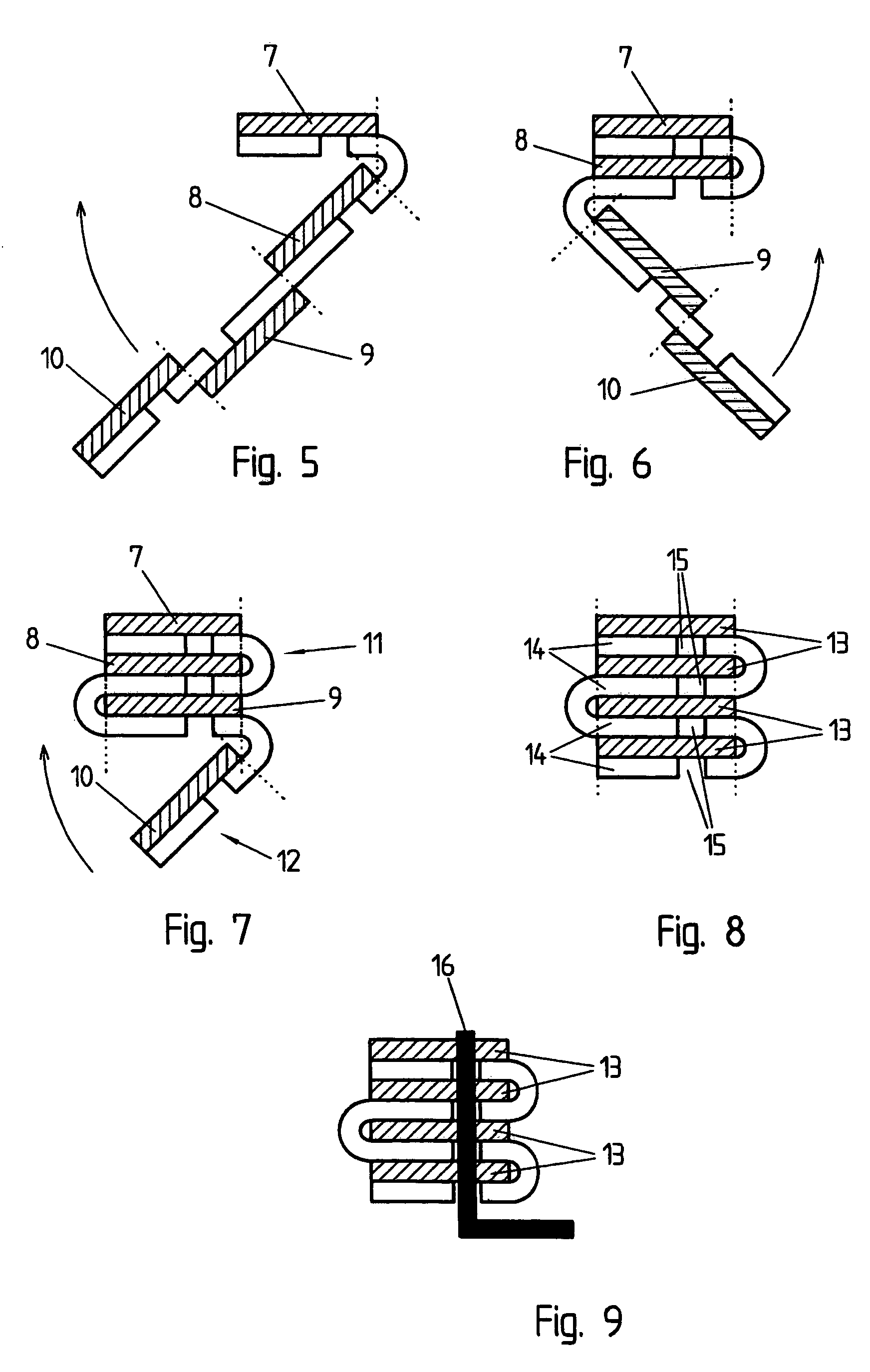

Multilayer circuit including stacked layers of insulating material and conductive sections

InactiveUS7205655B2Improve power densityEasy to manufactureSemiconductor/solid-state device detailsTransformers/inductances coils/windings/connectionsElectrical conductorTransformer

The invention relates to the manufacturing of a multilayer structure and especially it relates to the manufacturing of a three-dimensional structure and its use as an electronics assembly substrate and as a winding for transformers and inductors. When a multilayer structure is manufactured by folding a conductor-insulator-conductor laminate, where the conductor layers to be separated from each other follow each other on opposite sides of the conductor-insulator-conductor laminate in the sections following each other and where the insulator has been removed from the places where the conductor layers are to be connected together after folding, it is possible to manufacture a wide range of three-dimensional multilayer structures where the volume occupied by the windings over the total volume can be maximized. Alternatively, by using the method it is also possible to manufacture a multilayer structure where components have been buried inside. The method makes it also possible to make connections between layers in a flexible manner. Among other issues, the method can be easily automated for mass-production.

Owner:SCHAFFNER EMV AG

Embedded toroidal transformers in ceramic substrates

ActiveUS7196607B2Semiconductor/solid-state device detailsTransformers/inductances coils/windings/connectionsTransformerMetallurgy

Method for forming a transformer (118) in a ceramic substrate. The method can include the steps of forming at least one conductive coil (119a, 119b) comprising a plurality of turns about an unfired ceramic toroidal core region (120a, 120b) defined within an unfired ceramic substrate (100). The method can also include the step of co-firing the unfired ceramic toroidal core region (120a, 120b), the unfired ceramic substrate (100), and the conductive coil (119a, 119b) to form an integral ceramic substrate structure with the conductive coil at least partially embedded therein.

Owner:HARRIS CORP

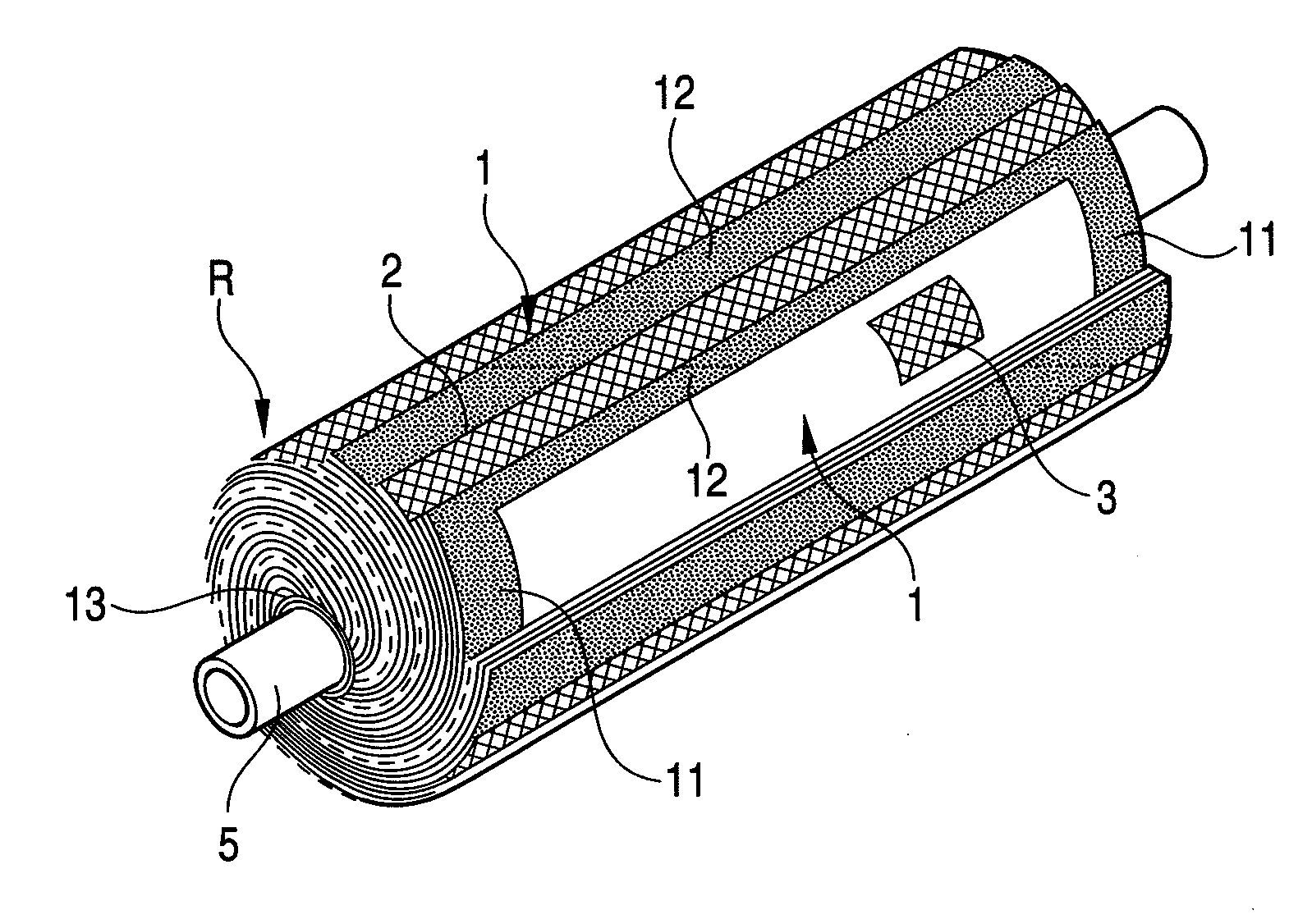

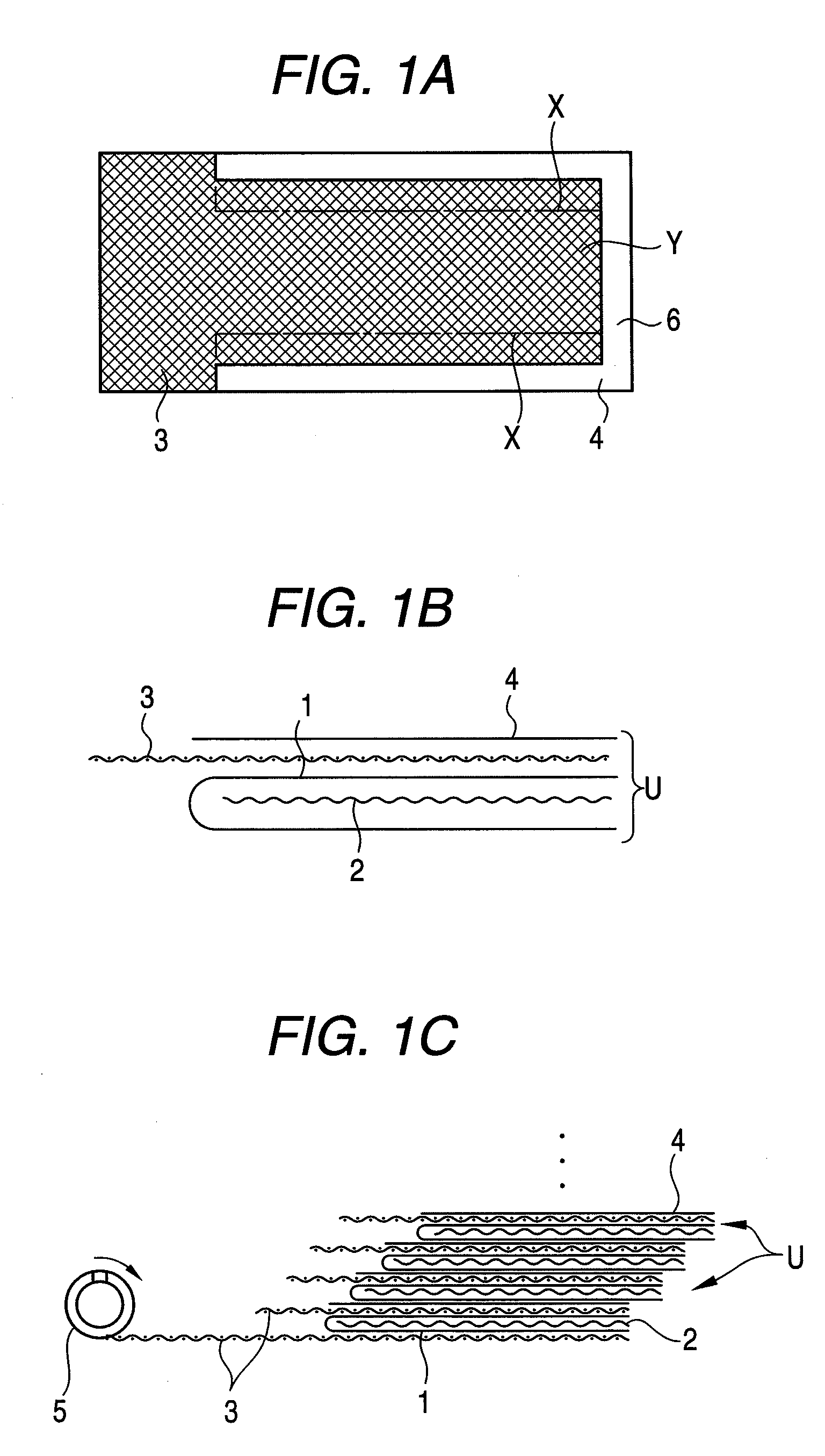

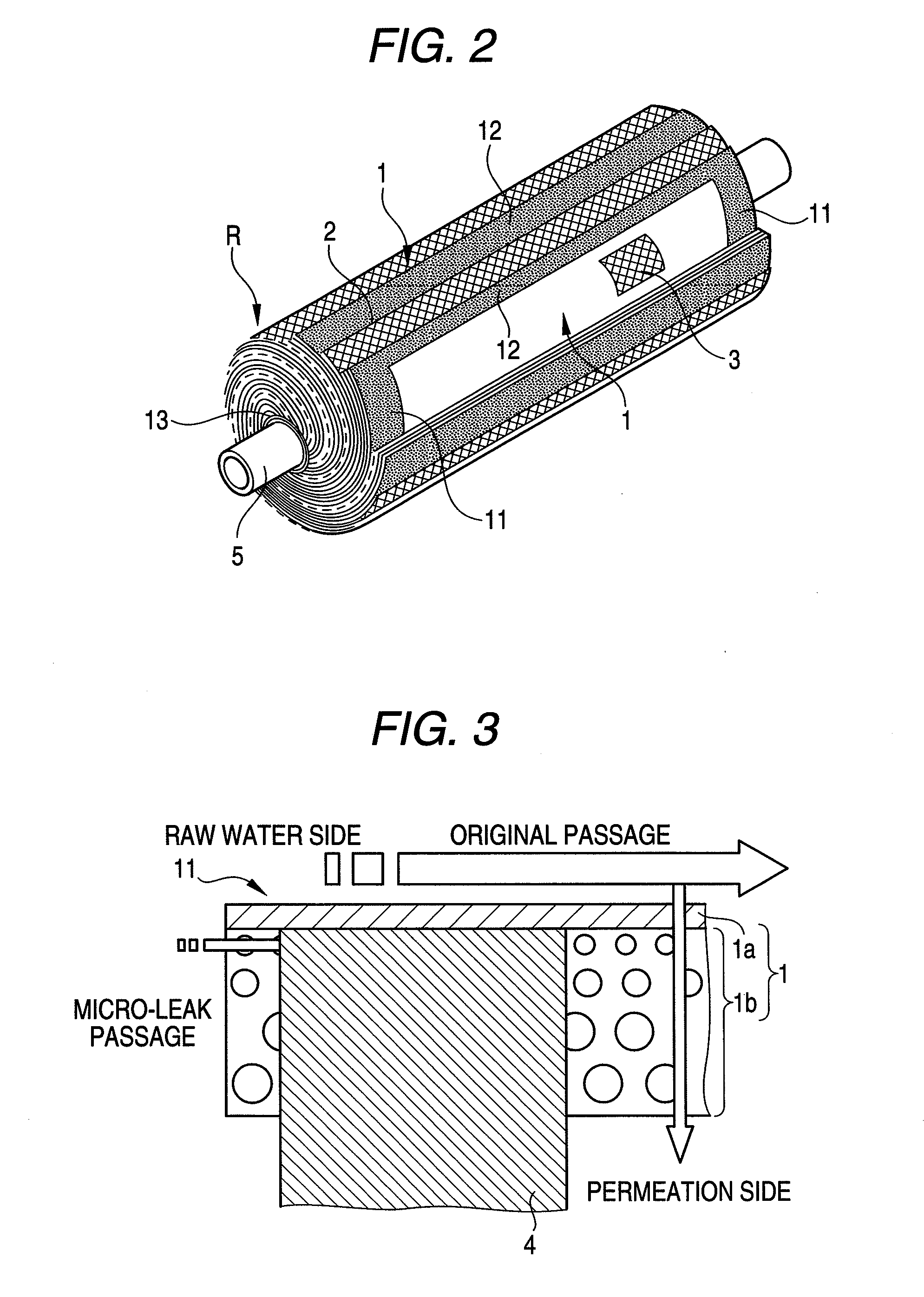

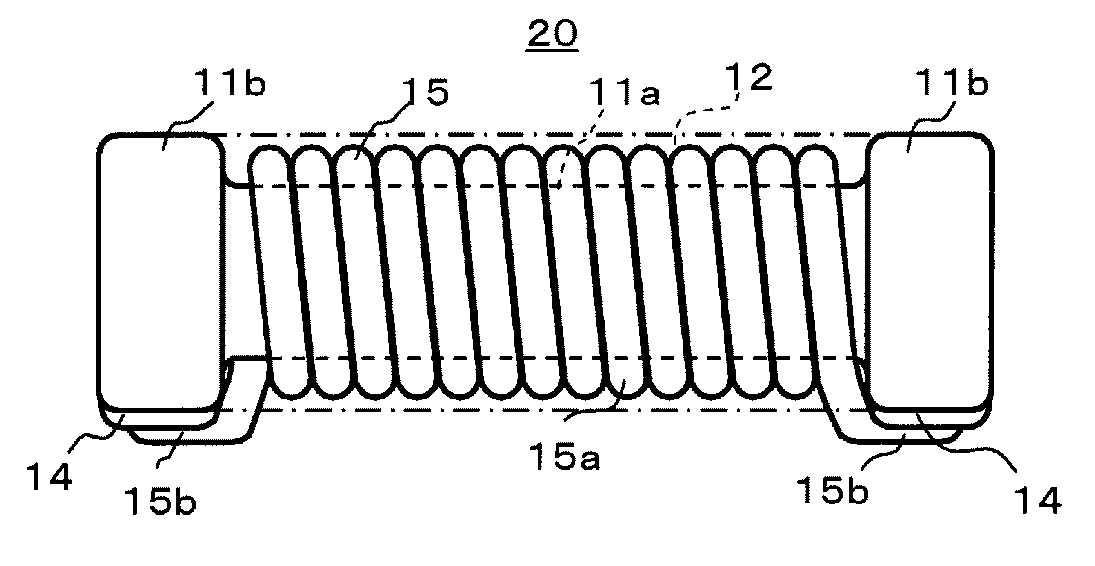

Spiral reverse osmosis membrane element, method of manufacturing the same, and its use method

ActiveUS20080295951A1Improve impregnation effectEffectively prevent micro-leaksSemi-permeable membranesPaper/cardboard wound articlesReverse osmosisPermeation

Owner:NITTO DENKO CORP

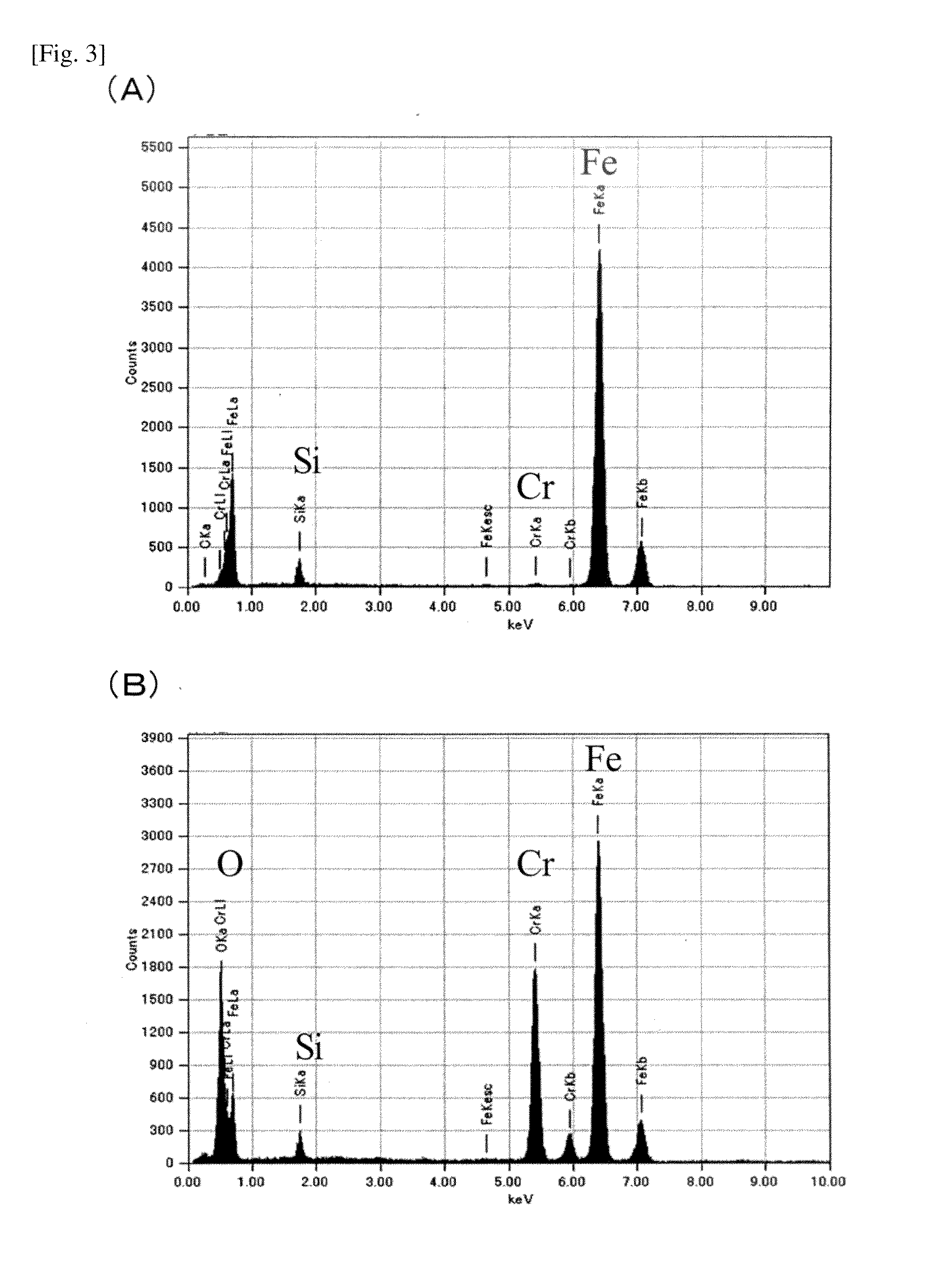

Coil-type electronic component and its manufacturing method

ActiveUS20110267167A1Low costHigh magnetic flux densityTransformers/inductances coils/windings/connectionsInorganic material magnetismElectronic componentElectron

A coil-type electronic component has a coil inside or on the surface of its base material and is characterized in that: the base material is constituted by a group of grains of a soft magnetic alloy containing iron, silicon and other element that oxidizes more easily than iron; the surface of each soft magnetic alloy grain has an oxide layer formed on its surface as a result of oxidization of the grain; this oxide layer contains the other element that oxidizes more easily than iron by a quantity larger than that in the soft magnetic alloy grain; and grains are bonded with one another via this oxide layer.

Owner:TAIYO YUDEN KK

Popular searches

Transformers/inductances circuits Fixed signal inductances Resistor manufacture Printed circuit manufacture Electrical connection printed elements Metallic pattern materials Semiconductor devices Piezoelectric/electrostrictive device manufacture/assembly Printed circuit aspects Piezoelectric/electrostrictive transducers