Recovery circuit for improving negative bias-temperature instability of memory clock circuit

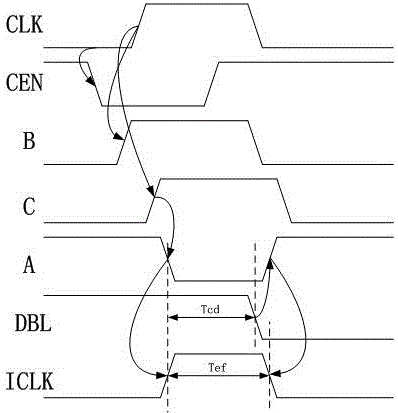

A technology of negative bias temperature and recovery circuit, which is applied in the direction of static memory, digital memory information, information storage, etc., can solve the problems of clock frequency, reading and writing speed drop, unable to end the circuit in time, MP1 performance degradation, etc., to reduce internal The effect of widening the effective pulse, reducing the NBTI effect, and reducing the working time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be described in detail below with reference to the accompanying drawings and in combination with embodiments.

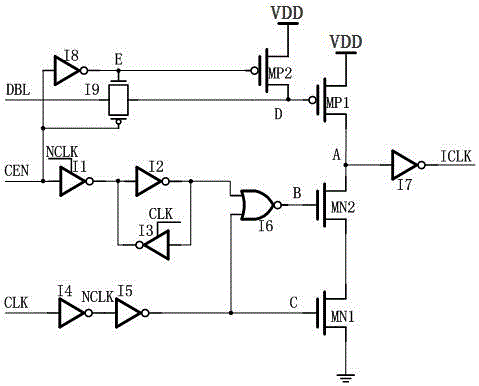

[0023] refer to figure 2 As shown, a recovery circuit for improving the temperature instability of the negative bias voltage of the memory clock circuit, the circuit includes a clock input circuit and a recovery circuit for the NBTI effect;

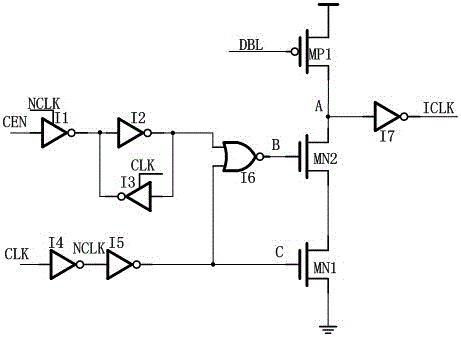

[0024] The clock input circuit includes an enabling signal terminal CEN, a clock signal terminal CLK, inverters I1, I2, I3, I4, I5, I7, a NOR gate I6, a PMOS transistor MP1, and an NMOS transistor MN1 and MN2. The energy signal terminal CEN is connected to the input terminal of the inverter I1, the output terminal of the inverter I1 is respectively connected to the input terminal of the inverter I2 and the output terminal of the inverter I3, and the output terminal of the inverter I2 is connected to the output terminal of the inverter I3 The input ends of the inverters are connected to the fir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More