Manufacturing method of radio frequency LDMOS device

A manufacturing method and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., to achieve the effects of reducing vertical electric field, improving robustness, and eliminating registration problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

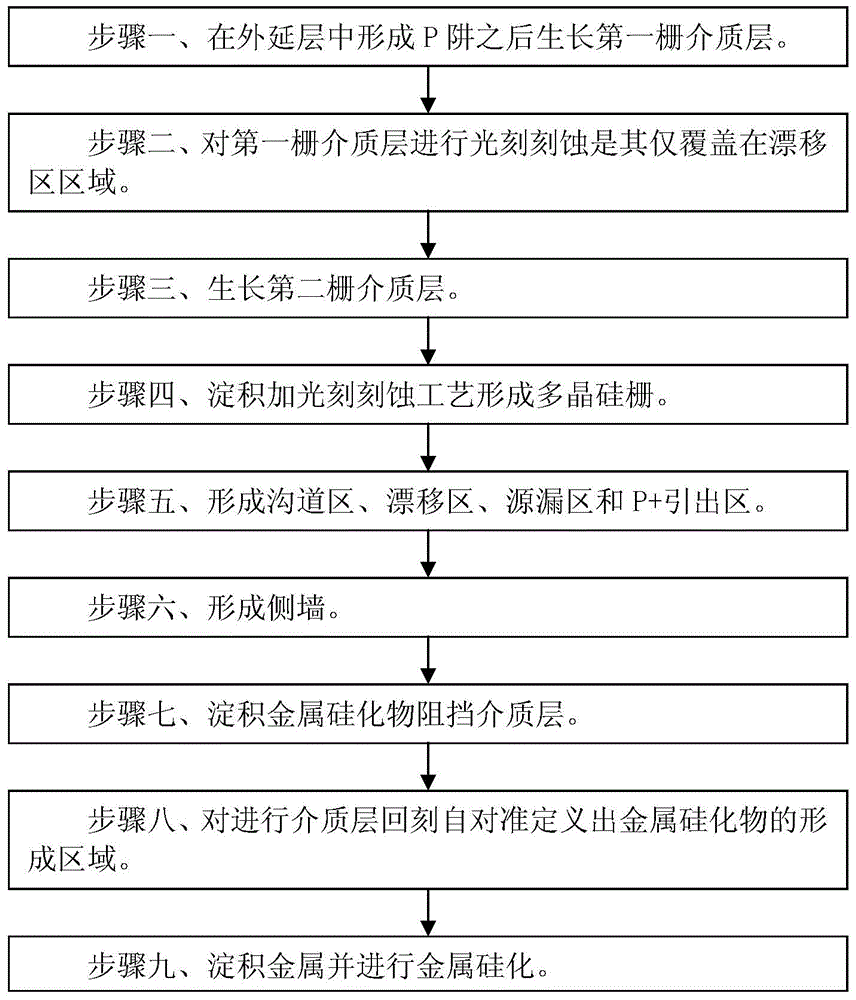

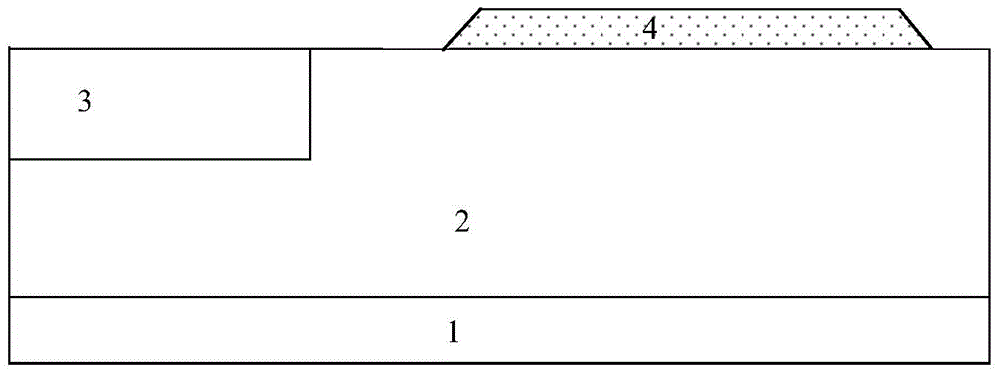

[0041] Such as figure 1 Shown is the flow chart of the manufacturing method of the radio frequency LDMOS device of the embodiment of the present invention; Figure 2A to Figure 2I Shown is a schematic diagram of the device structure in each step of the manufacturing method of the radio frequency LDMOS device of the embodiment of the present invention; the manufacturing method of the radio frequency LDMOS device of the embodiment of the present invention includes the following steps:

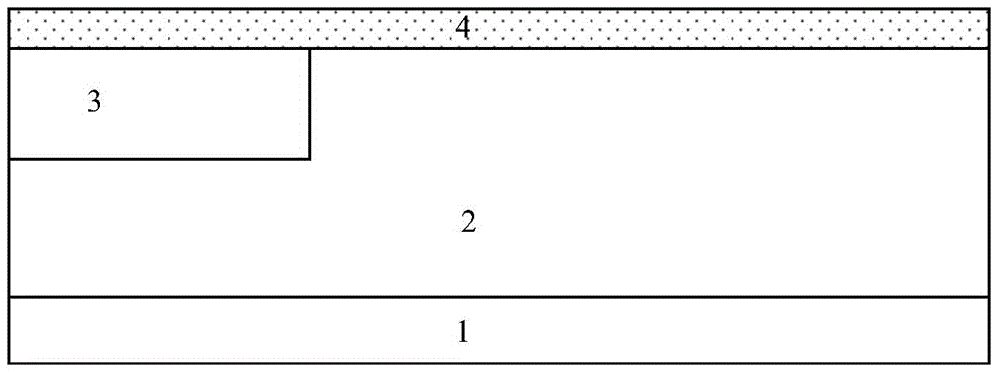

[0042] Step 1, such as Figure 2AAs shown, an epitaxial layer 2 is formed on the surface of a silicon substrate 1 , a P well 3 is formed in the epitaxial layer 2 , and then a first gate dielectric layer 4 is grown. In the embodiment of the present invention, the silicon substrate 1 is heavily doped with P type, and the epitaxial layer 2 is lightly doped with P type, and the epitaxial layer 2 can be formed by stacking multiple epitaxial layers.

[0043] The material of the first gate dielectric ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More