High voltage device for drive chip of plasma flat-panel display

A flat-panel display and driver chip technology, applied in the direction of electric solid devices, semiconductor devices, electrical components, etc., can solve the problems of increased leakage current, increased device power consumption, etc., to achieve low conduction loss, improve integration density, and large saturation current. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

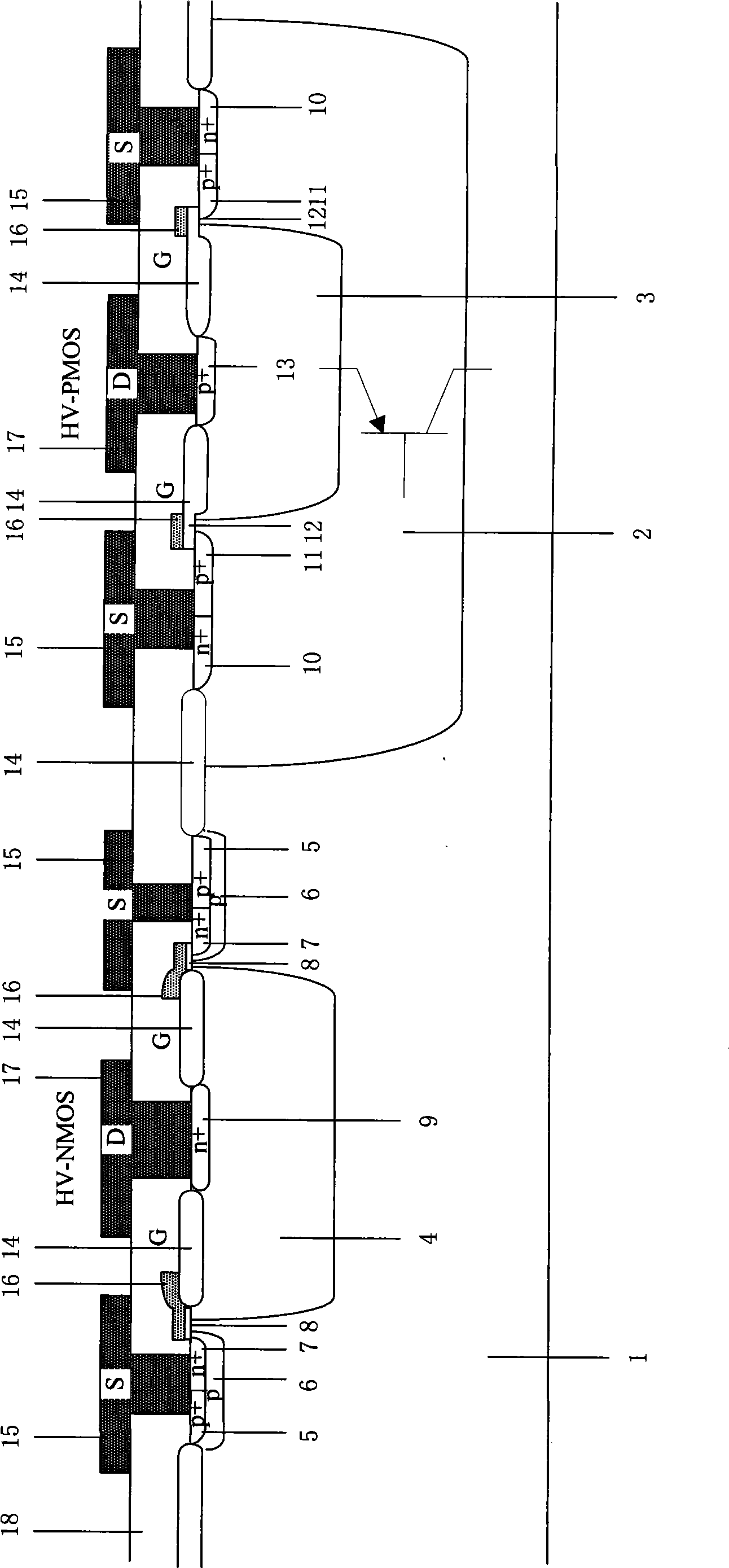

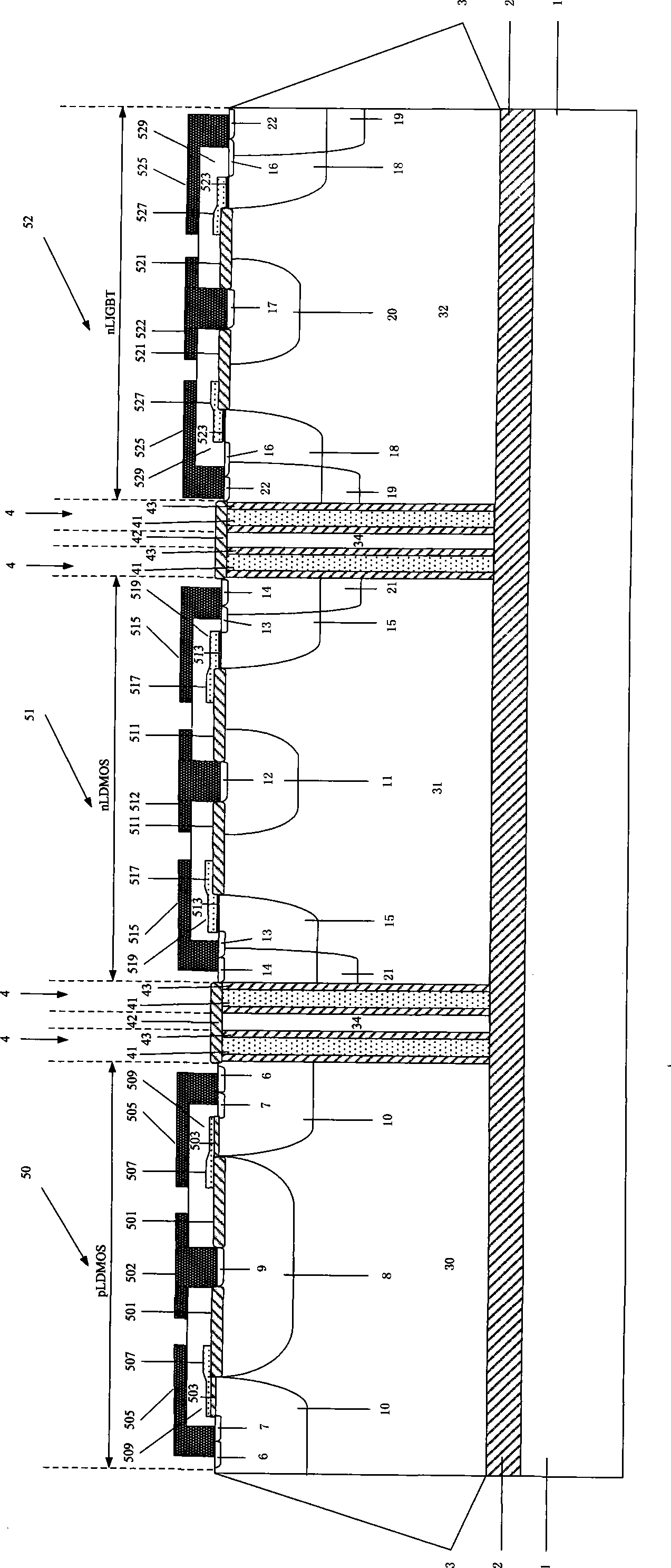

[0025] The invention realizes a 60V-300V high-voltage device based on the thick-layer SOI material, and has the characteristics of high speed, high integration and low power consumption. It satisfies the requirements of plasma flat panel display driver chips for high-voltage devices.

[0026] The high-voltage device for the plasma panel display driver chip of the present invention includes a high-voltage pLDMOS 50 , a high-voltage nLDMOS 51 and a high-voltage nLIGBT 52 . Wherein, 1 is a substrate, 2 is a buried oxide layer, 3 is an SOI layer, and 4 is a deep trench dielectric isolation region. The buried oxide layer 2 is located between the substrate 1 and the SOI layer 3, and the thickness of the SOI layer is 8-15 μm. The high-voltage pLDMOS 50, the high-voltage nLDMOS 51 and the high-voltage nLIGBT 52 are separated by the dielectric isolation region 4 to realize electrical isolation between high-voltage devices or high-voltage and low-voltage devices.

[0027] The high-vol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More