Internal gettering process of Czochralski silicon wafer

A Czochralski silicon wafer and process technology, applied in the direction of crystal growth, electrical components, circuits, etc., can solve problems such as reducing thermal budget, and achieve the effect of reducing thermal budget, temperature and time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0020] (1) The diameter is 300mm, the crystal orientation is , and the interstitial oxygen concentration is 8×10 17 cm -3 The Czochralski silicon wafers are subjected to rapid thermal treatment (RTP) under a high-purity (purity greater than 99.99%) nitrogen atmosphere. The conditions are: the temperature is raised to 1250°C at a rate of 100°C / s, maintained for 60 seconds, and then heated at a rate of 5°C / s Cool at a rate of 800°C, then cut off the power supply to allow the silicon wafer to cool naturally;

[0021] (2) Annealing the silicon wafer treated in step (1) at 900° C. for 8 hours under an argon atmosphere.

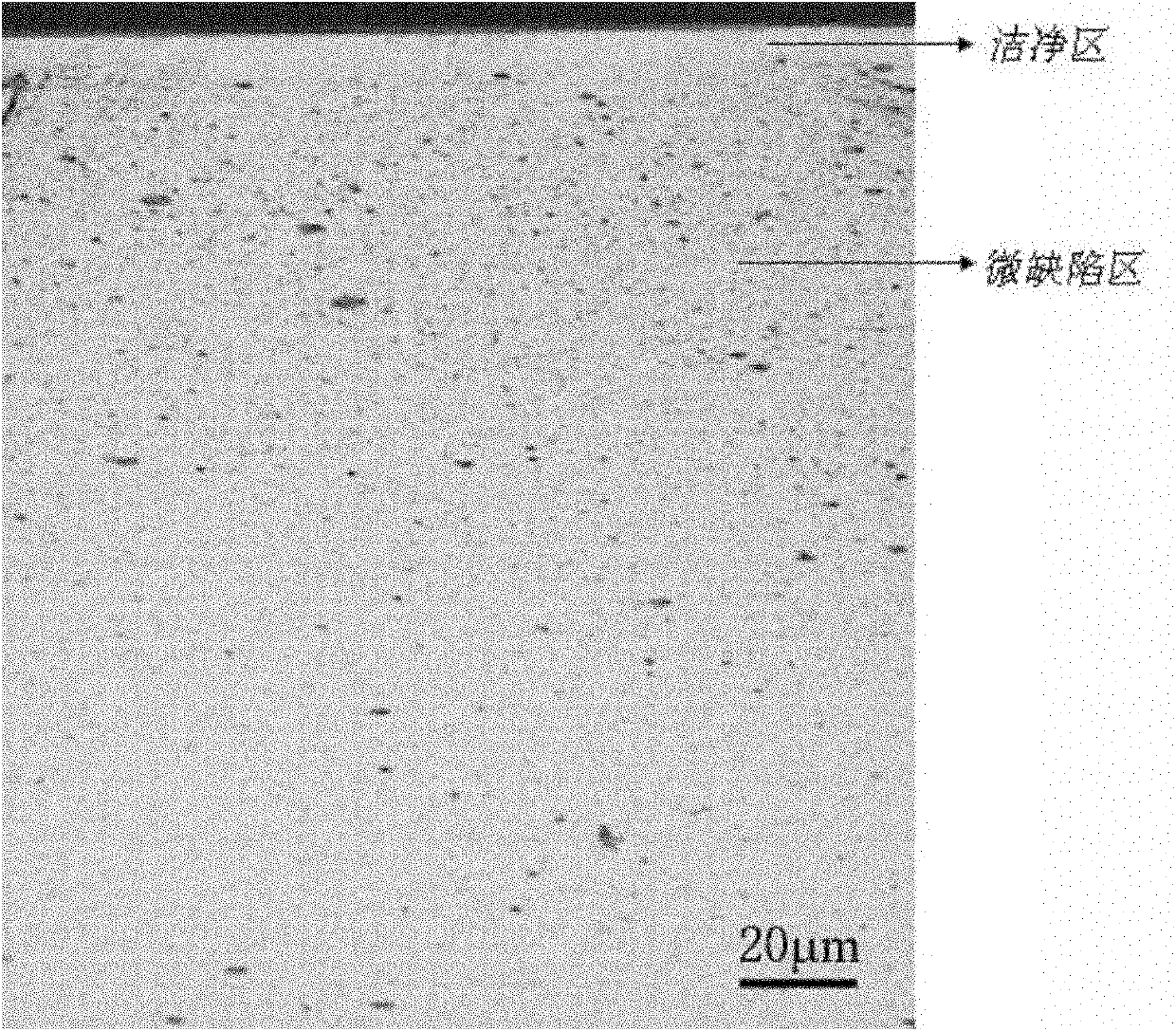

[0022] figure 1 It is an optical microscope photo of the silicon wafer section obtained after the treatment in Example 1 after preferential etching. From figure 1 It can be seen that a defect-free clean area is formed near the surface of the silicon wafer, and a dense bulk micro-defect area is next to it below it, which will play the role of internal gettering....

Embodiment 2

[0024] (1) The diameter is 200mm, the crystal orientation is , and the interstitial oxygen concentration is 8×10 17 cm -3 The Czochralski silicon wafer is subjected to rapid thermal treatment (RTP) in a high-purity nitrogen atmosphere. The conditions are: heating up to 1200°C at a rate of 100°C / s, maintaining for 120 seconds, and then cooling to 1000°C at a rate of 50°C / s. Then cut off the power supply to let the silicon wafer cool down naturally;

[0025] (2) Annealing the silicon wafer treated in step (1) at 900° C. for 16 hours under an argon atmosphere.

[0026] The effect after implementation is similar to that of Example 1, and the silicon wafer includes a clean area and a bulk micro-defect area.

Embodiment 3

[0028] (1) The diameter is 300mm, the crystal orientation is , and the interstitial oxygen concentration is 9×10 17 cm -3 The Czochralski silicon wafers were subjected to rapid thermal treatment (RTP) under a nitrogen atmosphere. The conditions were: heating up to 1200 °C at a rate of 100 °C / s, maintaining for 150 seconds, and then cooling to 1000 °C at a rate of 5 °C / s, and then Cut off the power supply and let the silicon wafer cool down naturally;

[0029] (2) Annealing the silicon wafer treated in step (1) at 900° C. for 16 hours under an argon atmosphere.

[0030] figure 2 It is an optical microscope photo of the silicon wafer section obtained after Example 3 after preferential etching. From figure 2 It can be seen that a defect-free clean area is formed near the surface of the silicon wafer, and a dense bulk micro-defect area is next to it below it, which will play the role of internal gettering.

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More