Forming method of CMOS (complementary metal-oxide-semiconductor) transistor

A technology of transistors and semiconductors, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems that affect the performance of CMOS transistors, and the performance of CMOS transistors needs to be further improved, so as to reduce thermal budget, improve performance, and achieve good results Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

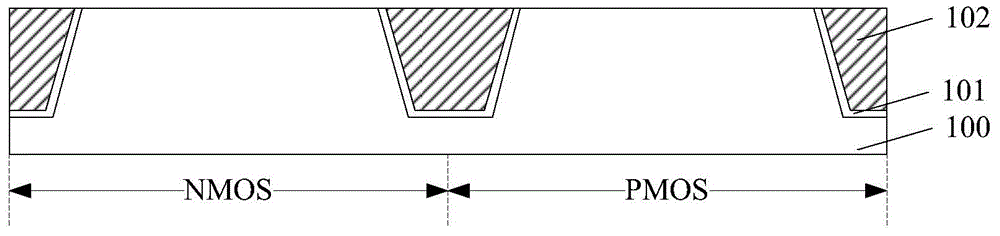

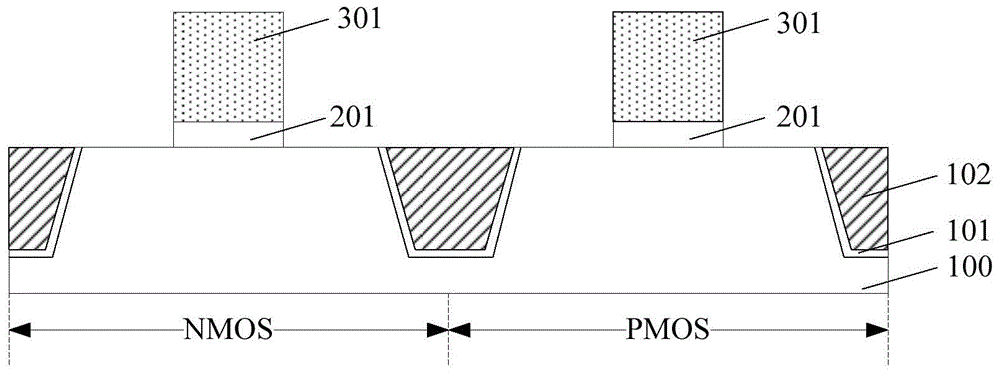

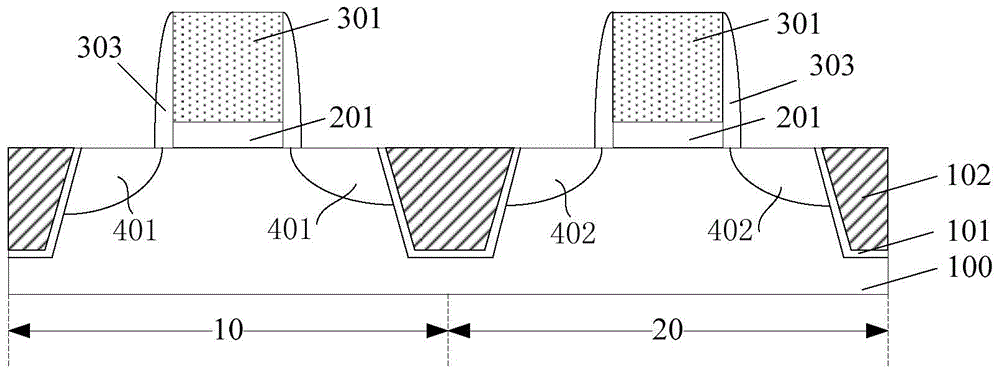

[0027] As mentioned in the background art, in the prior art, there are a large number of defects in the high-K gate dielectric layer formed by the gate-last process, which will greatly affect the performance of the CMOS transistor.

[0028] Research has found that in the gate-front process, the source and drain are formed after the high-K gate dielectric layer and the gate are formed, and the high-K gate dielectric layer is subjected to high temperature at the same time during the annealing process of the source and drain. annealing to reduce the number of defects in the high-K gate dielectric layer. And because in the gate-last process, the high-K gate dielectric layer is formed after the source, drain and dielectric layer, compared with the gate-last process, the high-K gate dielectric layer formed in the gate-last process is subjected to less heat treatment process, This further leads to a large number of defects in the high-K gate dielectric layer formed in the gate-last p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More