Surrounding-gate field effect transistor and fabrication method thereof

A field-effect transistor and gate-around technology, which is applied in the field of gate-around field effect transistors and its preparation, can solve problems such as the complexity of GAA source and drain design, and achieve the effects of solving thermal stability problems, good gate control ability, and suppressing short channel effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

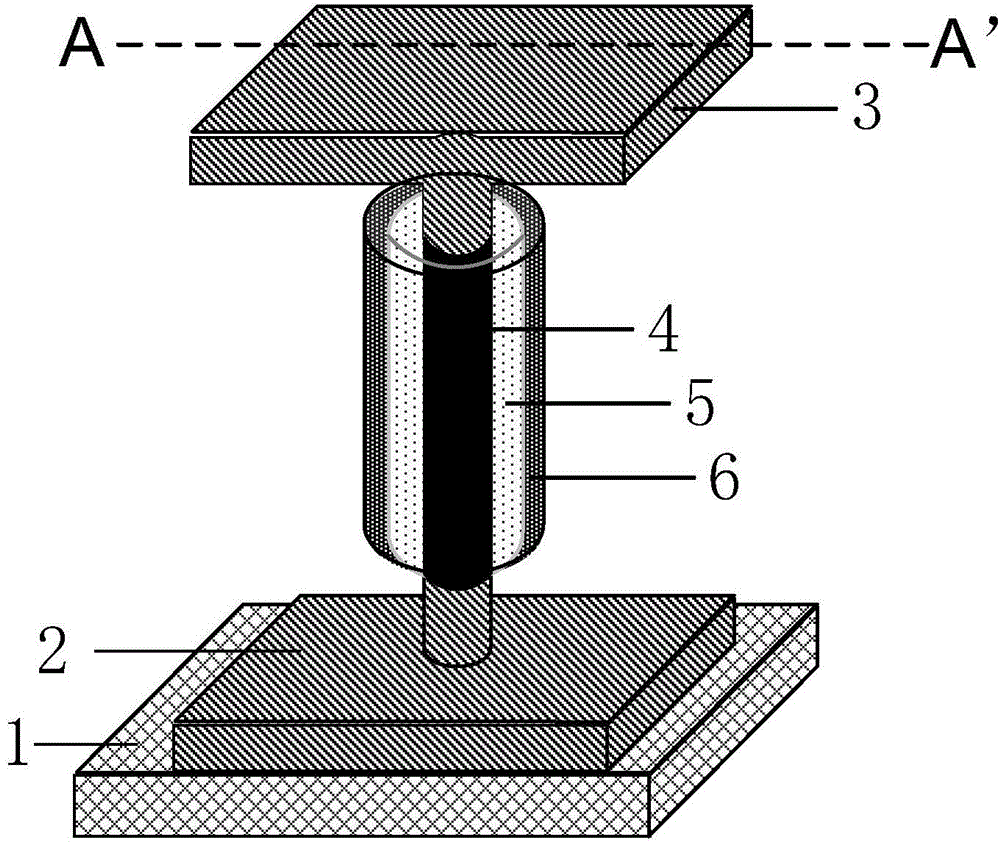

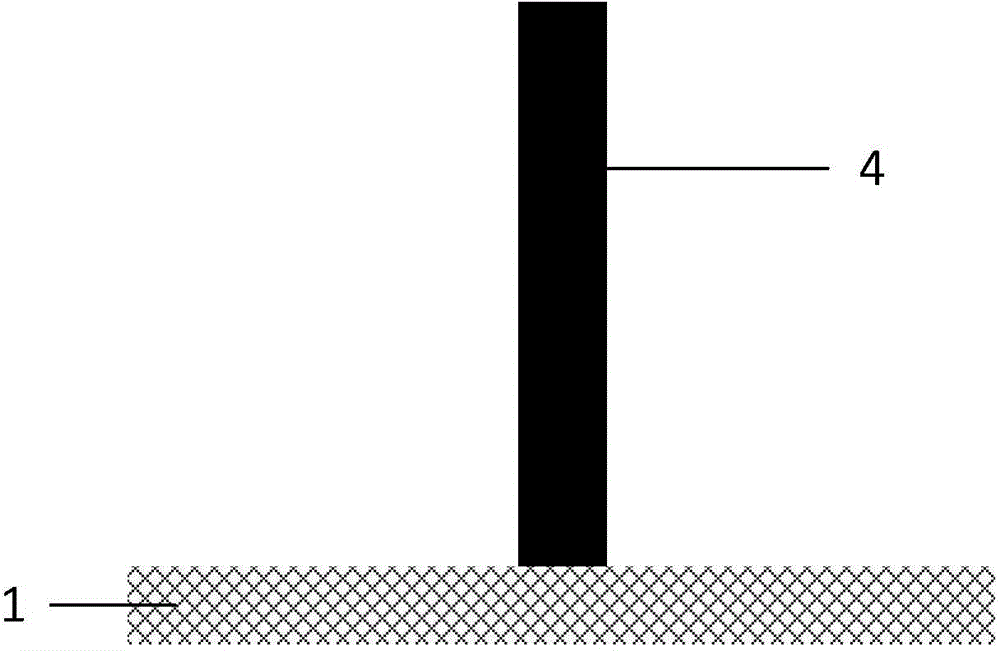

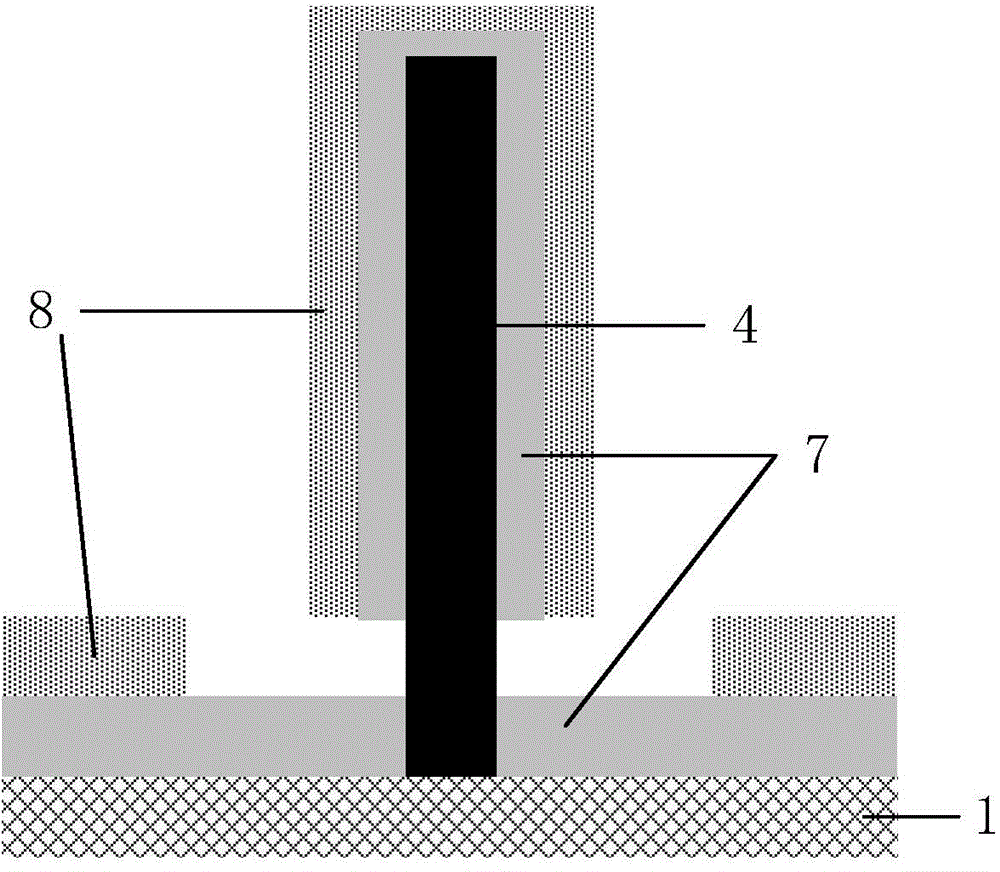

[0041] The present invention provides a field effect transistor with a novel structure, specifically a gate-around field effect transistor combined with a vertical channel and a Schottky barrier source / drain structure (such as figure 1 shown), including a ring-shaped semiconductor channel 4 in a vertical direction, a ring-shaped gate electrode 6, a ring-shaped gate dielectric layer 5, a source region 2, a drain region 3, and a semiconductor substrate 1; wherein, the source The region 2 is located at the bottom of the vertical channel 4 and is in contact with the substrate 1. The drain region 3 is located at the top of the vertical channel 4. The gate dielectric layer 5 and the gate electrode 6 surround the vertical channel 4 in a ring shape; the source region 2 and the The drain regions 3 form Schottky contacts with the channels 4 respectively.

[0042] The source region and the drain region can be any metal with good conductivity or a compound formed of metal and substrate ma...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com