Junction-free field-effect transistor and preparation method thereof

A field-effect transistor and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of complex GAA source-drain design, achieve good modulation effect, improve integration, and simplify the process.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

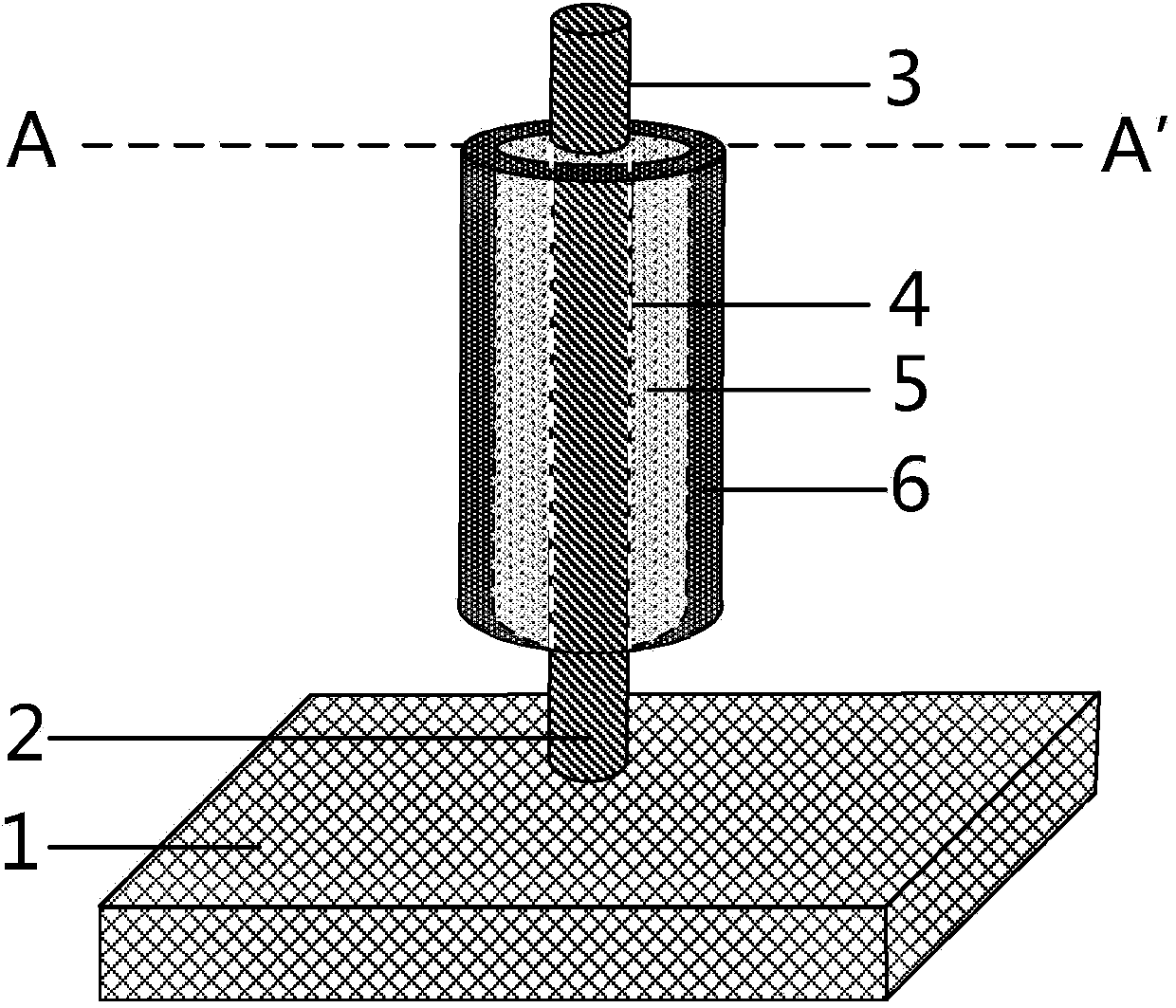

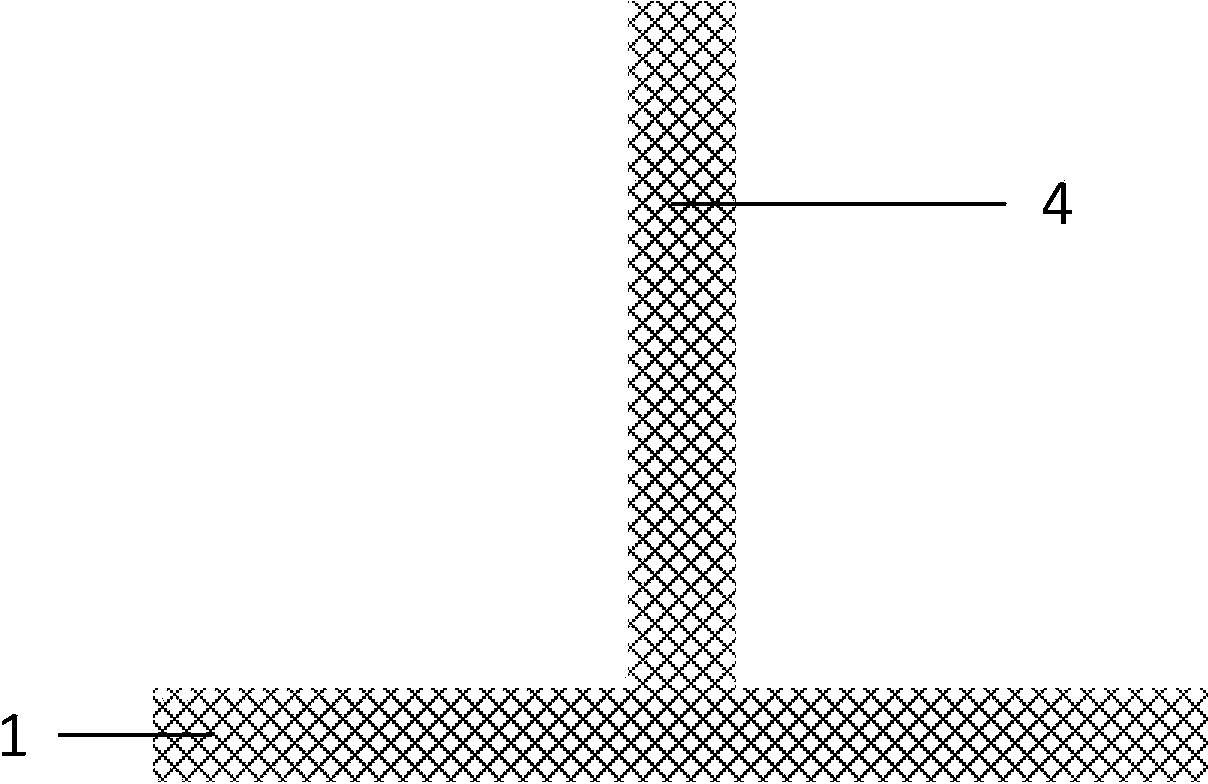

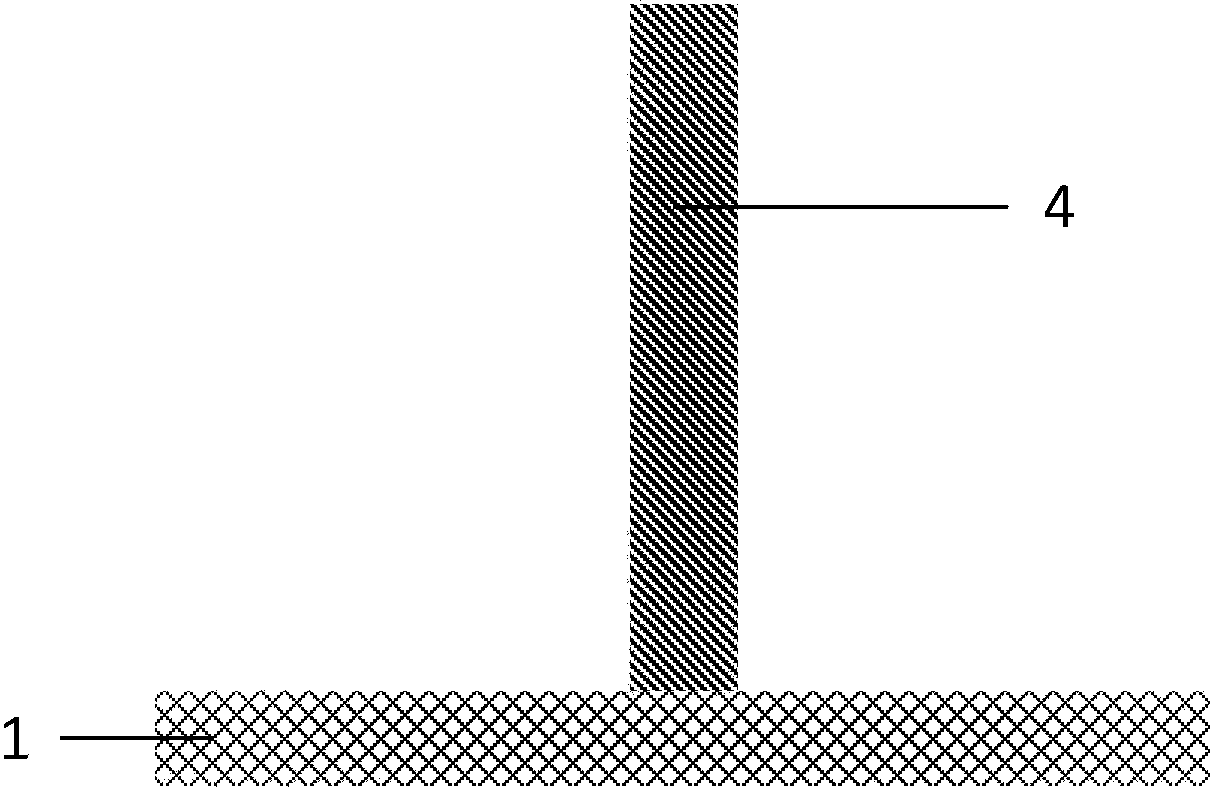

[0038] The present invention provides a field effect transistor with a novel structure, specifically a gate-around field effect transistor (such as figure 1 shown), including a ring-shaped semiconductor channel 4 in a vertical direction, a ring-shaped gate electrode 6, a ring-shaped gate dielectric layer 5, a source region 2, a drain region 3, and a semiconductor substrate 1; wherein, the source The region 2 is located at the bottom of the vertical channel 4 and is in contact with the substrate 1. The drain region 3 is located at the top of the vertical channel 4. The gate dielectric layer 5 and the gate electrode 6 surround the vertical channel 4 in a ring shape; the source region 2 and the The drain region 3 and the channel 4 are doped with the same type and concentration of impurities.

[0039] Doping impurity concentration is higher, generally should be 10 19 -10 20 cm -3 above.

[0040] Specific examples of the preparation method of the present invention include Fig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More