Manufacturing method for gate lateral wall layer and semi-conductor device

A gate sidewall layer and gate sidewall technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc. Bottom sag, leakage current and other problems, to reduce the probability of contamination, save time, and simplify process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

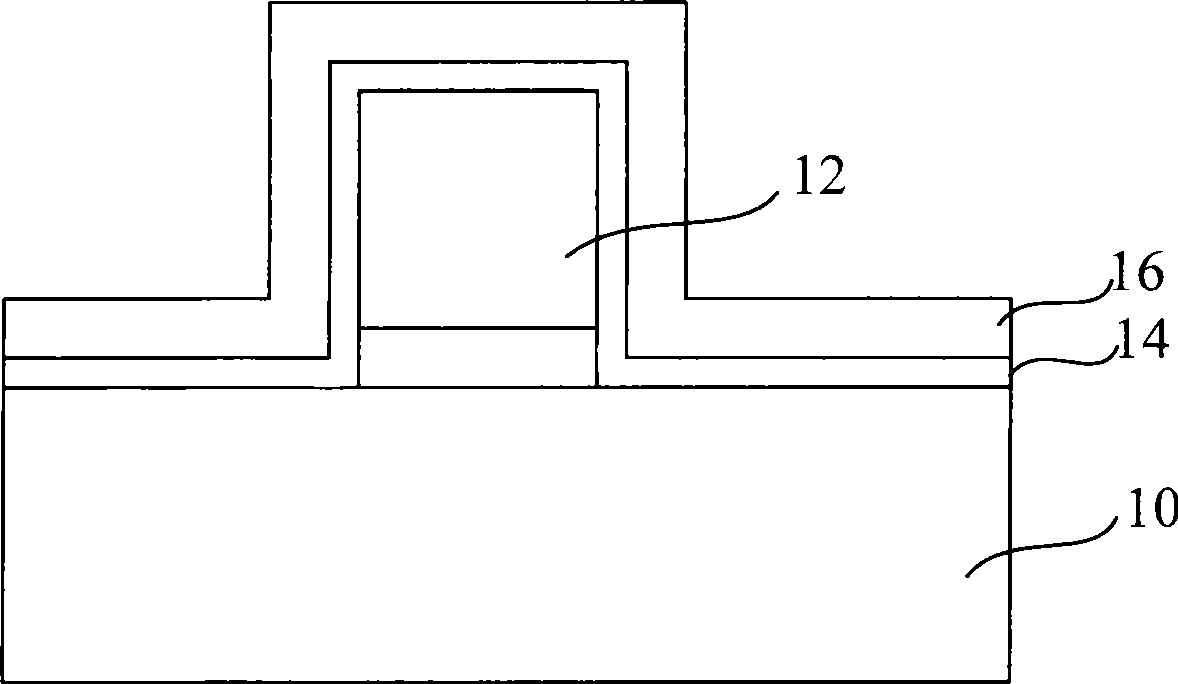

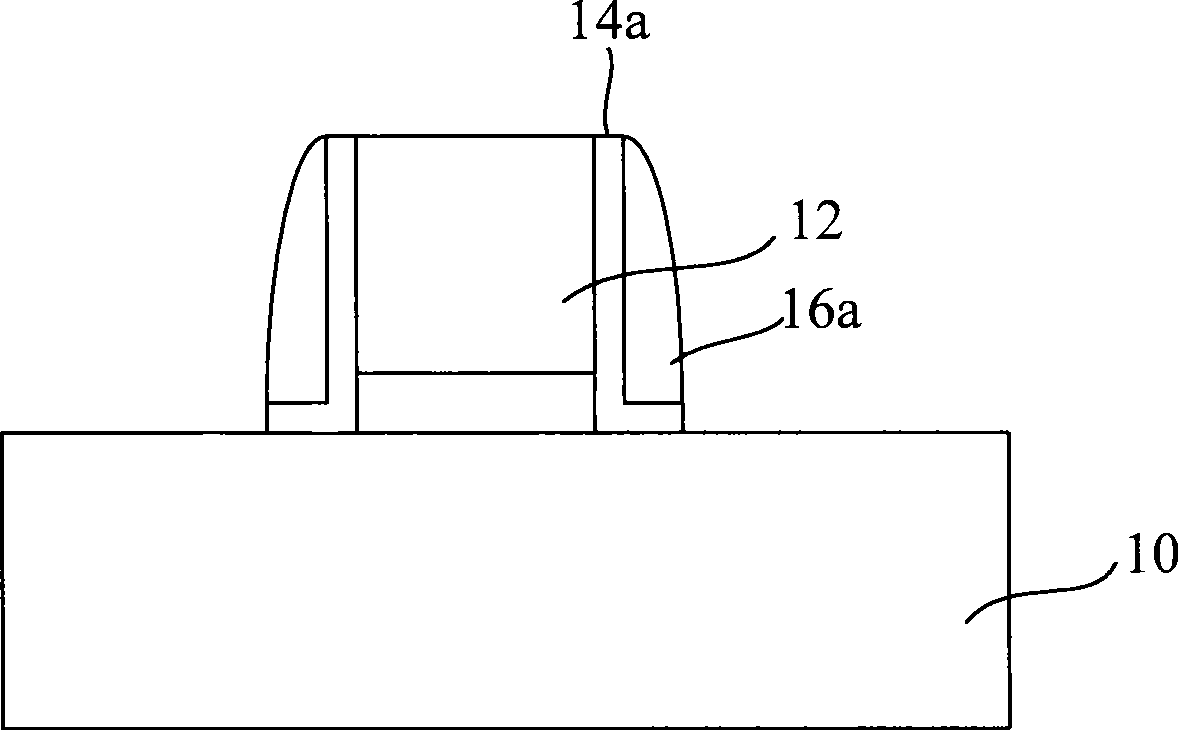

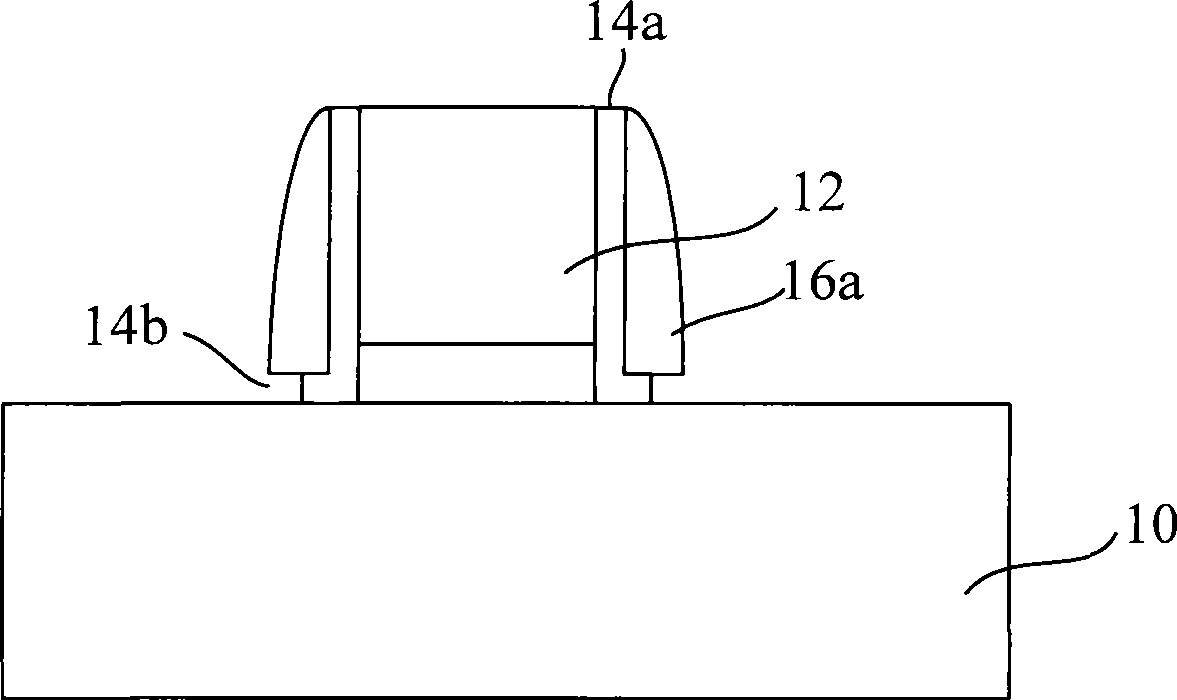

[0080] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0081] In the manufacturing process of the metal oxide semiconductor device, after the gate is formed, a gate sidewall layer needs to be formed on the sidewall of the gate to protect the formed gate. The present invention proposes a method for forming gate sidewall layers of a silicon oxide-silicon nitride (ON) structure or a silicon oxide-silicon nitride-silicon oxide (ONO) or multi-layer ON structure, which can improve or eliminate gate The bottom of the extreme sidewall layer is recessed, and the process is simple and the thermal budget is low, which helps to form a metal oxide semiconductor device with stable performance.

[0082] Figure 4 It is a flow chart of an embodiment of the method for forming the gate sidewall layer of the present invention. Figure 5 to Figure 10 A schematic cross-sectional structure diagram illustrating an...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More